# Battery-powered BLDC motor drive design using the 6EDL71x1 series

Design guide and recommendations

Author: Peter B. Green

#### About this document

#### Scope and purpose

This document discusses the design of three-phase motor drive inverters primarily for battery-powered brushless DC (BLDC) motor drives, based on the 6EDL71x1 series of three-phase smart gate drivers. The focus of this document is on system design and recommended practices to achieve best performance and avoid potential issues.

The purpose of this document is to provide designers with a useful design guide, which also describes how to use Infineon's motor control design software tools tailored to this smart gate driver family. In addition, hardware design and component selection recommendations are provided as well as PCB layout guidelines to help achieve best performance and avoid known system issues.

#### Intended audience

This document addresses the market for cordless power tools, outdoor power equipment (OPE), robotics and other battery-powered BLDC motor drive applications. It is intended for design engineers, applications engineers and students working on BLDC motor drive designs.

Table of contents

#### **Table of contents**

| About this document |                                                             |       |  |  |

|---------------------|-------------------------------------------------------------|-------|--|--|

| Table of contents   |                                                             |       |  |  |

| 1                   | Introduction                                                |       |  |  |

| 1.1                 | Brushless DC motors and drives                              |       |  |  |

| 1.2                 | 6EDL71x1 series driver functional overview                  |       |  |  |

| 1.2.1               | PWM modes                                                   | 7     |  |  |

| 1.2.2               | Current sense amplifiers and comparators                    | 8     |  |  |

| 1.2.3               | Integrated buck, linear regulators, and charge pumps        | 9     |  |  |

| 2                   | System functional description                               | 11    |  |  |

| 2.1                 | Commutation methods                                         |       |  |  |

| 2.1.1               | Trapezoidal/six-step (block) commutation                    |       |  |  |

| 2.1.2               | Field-oriented control                                      |       |  |  |

| 2.2                 | 6EDL71x1 smart gate driver features                         |       |  |  |

| 2.2.1               | Slew rate control                                           |       |  |  |

| 2.2.1               | Switch-on transient                                         |       |  |  |

| 2.2.2               | Switch-off transient                                        |       |  |  |

| 2.2.3               | Configuration of the gate driver                            |       |  |  |

| 2.2.3.              | 1 Gate drive current and timing                             |       |  |  |

| 2.2.3.2             | 2 Gate pre-charging feature                                 |       |  |  |

| 2.2.3.              | 3 Gate drive voltage                                        |       |  |  |

| 3                   | Motor drive inverter design                                 | 24    |  |  |

| 3.1                 | Defining the system parameters                              | 24    |  |  |

| 3.2                 | MOSFET selection                                            | 25    |  |  |

| 3.2.1               | Breakdown voltage BV <sub>DSS</sub>                         |       |  |  |

| 3.2.2               | On-resistance R <sub>DS(on)</sub>                           | 25    |  |  |

| 3.2.3               | Maximum drain current I <sub>D(MAX)</sub>                   |       |  |  |

| 3.2.4               | Gate charge ratio                                           |       |  |  |

| 3.2.5               | Safe operating area                                         |       |  |  |

| 3.2.6               | Body diode recovery                                         |       |  |  |

| 3.2.7               | Package selection                                           | 27    |  |  |

| 3.3                 | Gate drive optimization                                     |       |  |  |

| 3.3.1               | Selecting the gate drive voltage                            | 28    |  |  |

| 3.3.2               | Gate switch-on configuration procedure                      |       |  |  |

| 3.3.3               | Gate switch-off configuration procedure                     |       |  |  |

| 3.3.4               | Setting the dead time                                       |       |  |  |

| 3.3.5               | Minimum pulse widths                                        |       |  |  |

| 3.3.6               | Procedure for tuning the gate drive parameters on the bench |       |  |  |

| 3.4                 | Input capacitor selection                                   |       |  |  |

| 3.4.1               | Electrolytic capacitors                                     |       |  |  |

| 3.4.2               | Ceramic capacitors                                          |       |  |  |

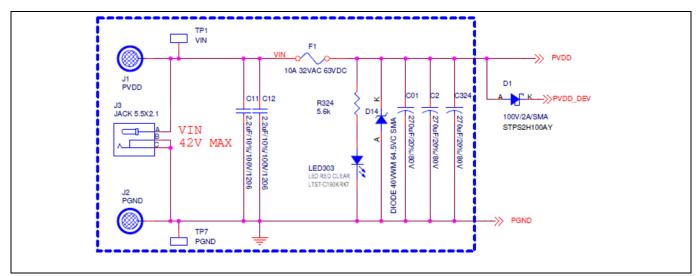

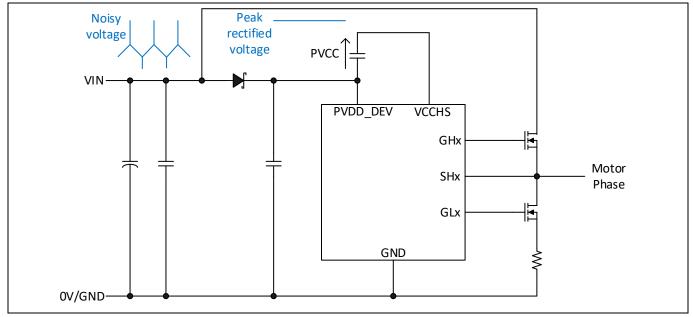

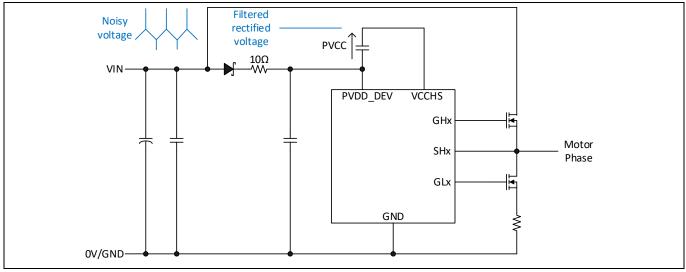

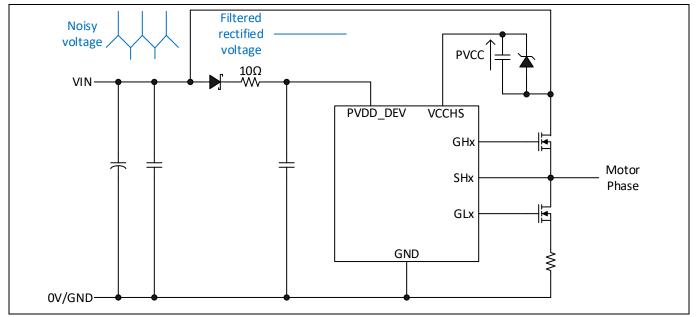

| 3.5                 | PVDD connection                                             |       |  |  |

| 3.6                 | Configuration of the buck and linear regulators             |       |  |  |

| 3.7                 | Configuration of the charge pumps                           |       |  |  |

| 3.8                 | Configuration of the current sense amplifiers               |       |  |  |

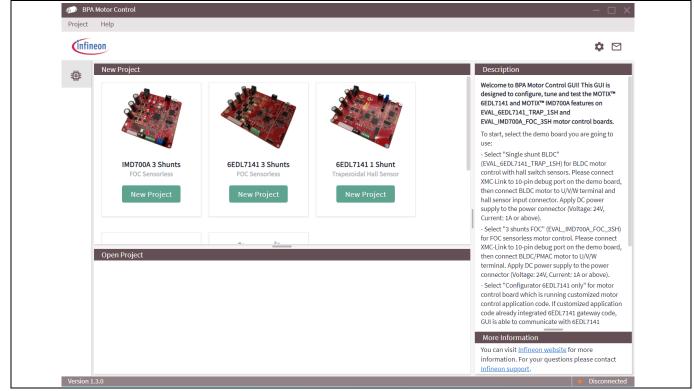

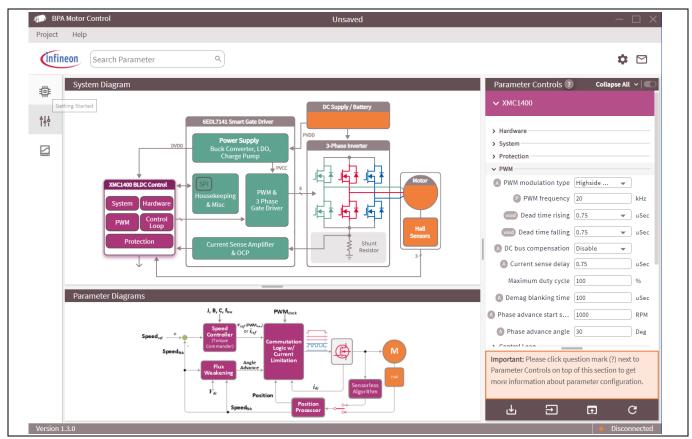

| 4                   | Using the BPA motor control GUI                             | 46    |  |  |

| 4.1                 | Creating a project in the BPA motor control GUI             |       |  |  |

| 4.2                 | Downloading the motor control firmware from the GUI         | 47    |  |  |

| Applica             | ation note 2                                                | V 1.0 |  |  |

Table of contents

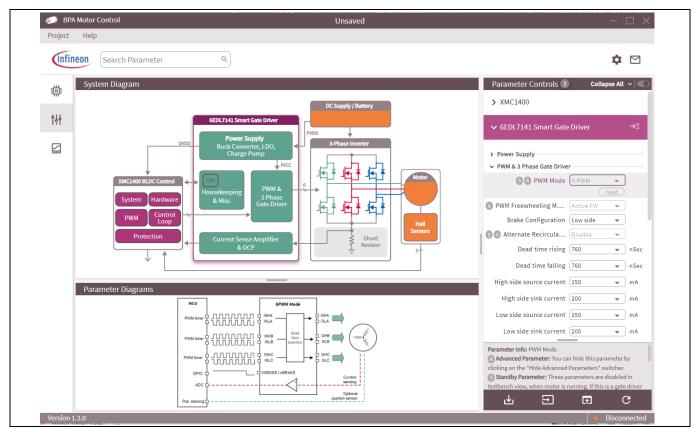

| 4.3              | Configuring the 6EDL71x1 parameters | 50 |  |

|------------------|-------------------------------------|----|--|

| 4.3.1            | MOSFET tuning tool                  |    |  |

| 4.3.2            | Adjusting the parameters manually   | 52 |  |

| 4.4              | Using the GUI to operate the board  |    |  |

| 5                | PCB layout design guidelines        | 56 |  |

| 6                | Thermal management                  | 59 |  |

| 7                | Summary                             | 61 |  |

| References       |                                     |    |  |

| Revision history |                                     |    |  |

|                  | Disclaimer                          |    |  |

#### **1.1** Brushless DC motors and drives

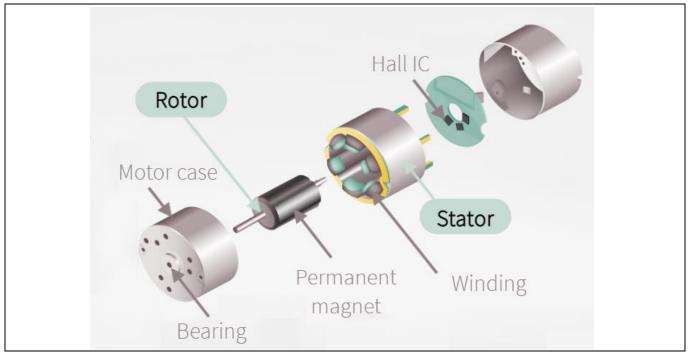

The basic construction of a BLDC motor (also known as an electronically commutated or EC motor) consists of a stator containing multiple wound coils and a rotor containing permanent magnets forming one or more pole pairs. Unlike brushed DC (BDC) motors, BLDC motors are commutated by controlled switching of the inverter connected to the stator windings instead of using mechanical brushes in contact with the rotor. The windings are arranged in two or three phases and energized in a determined sequence to generate a rotating magnetic field. The rotor permanent magnet attempts to align with the stator field, producing torque and rotary motion. Maximum torque is produced when the rotor and stator field vectors are positioned at 90 degrees to each other. Hall effect or other sensor types are often embedded in the stator to detect the rotor angular position, which may or may not be required depending on the control scheme used.

Figure 1 Three-phase BLDC motor exploded diagram

The stator windings may be connected in wye or delta configuration:

- The wye (Y-shaped) configuration, sometimes called a star winding, connects all of the windings to a central point, and power is applied to the remaining end of each winding. Wye configuration gives high torque at low speed but a lower top speed.

- The delta configuration connects three windings to each other in a triangle-like circuit, and power is applied at each of the connections. A motor with windings in delta configuration gives low torque at low speed but can give a higher top speed.

The wye winding is normally more efficient because delta-connected windings have a closed loop which allows parasitic currents that create losses. The control method used to drive these different BLDC motor types is basically the same.

Permanent magnet synchronous motors (PMSM) are of similar construction except that they has sinusoidal back-emf, whereas BLDC motors have trapezoidal back-emf.

Application note

#### Introduction

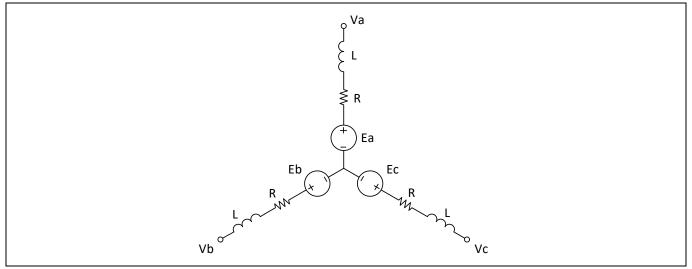

The electrical behavior of the motor is determined by the phase winding inductance and resistance coupled with the back EMF produced when the motor is rotating. These elements are represented in **Figure 2**.

Figure 2 Three-phase BLDC motor electrical model (wye configuration)

The following equation describes the winding voltage and current:

$$V_{a,b,c} = \frac{di_{a,b,c}}{dt} \cdot L + i_{a,b,c} \cdot R + E_{a,b,c}$$

<sup>[2]</sup>

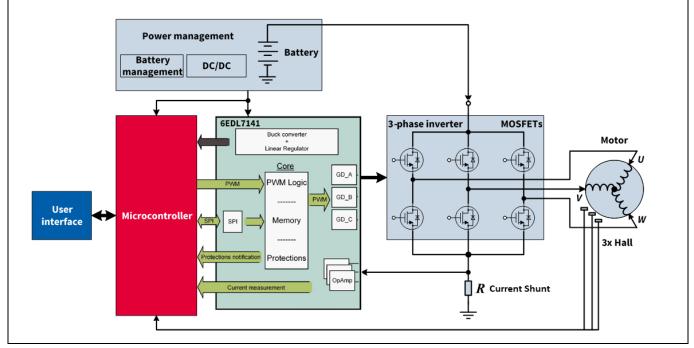

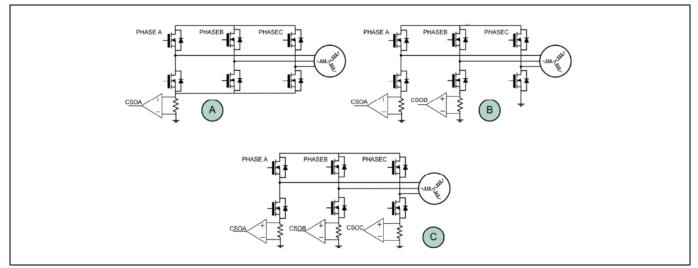

The three-phase motor drive inverter consists of a microcontroller running firmware that executes a control algorithm that produces pulse-width modulated (PWM) signals supplied to the 6EDL71x1 gate driver PWM inputs. The driver outputs are connected to the MOSFETs forming the six switches of the power stage. Additional circuitry is included for battery management, which is not covered in this application note. The inverter may include one, two or three current shunts for sensing the low-side MOSFET source currents.

Figure 3 6EDL7141-based BLDC motor drive inverter system block diagram (one shunt example)

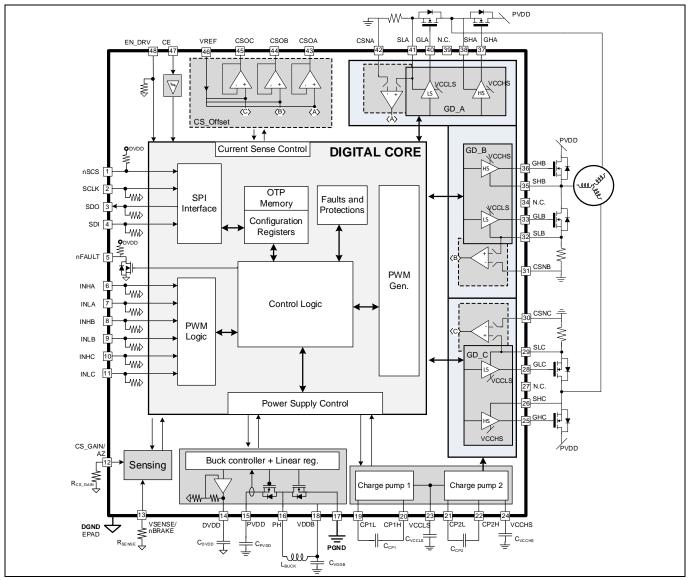

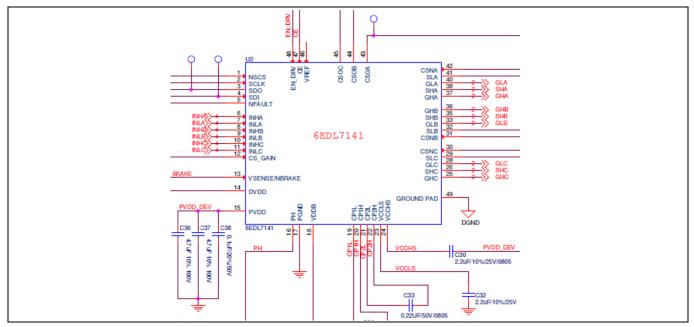

#### 1.2 6EDL71x1 series driver functional overview

The 6EDL7141 and 6EDL7151 are three-phase smart gate drivers designed for BLDC or permanent magnet synchronous motor drive systems. They consist of a configurable three-phase half-bridge gate driver able to operate in multiple PWM modes from an input voltage PVDD range of 5.5 V up to 60 V for the 6EDL7141 and 70 V for the 6EDL7151. These smart driver ICs also include an integrated DC-DC synchronous buck converter and low-dropout linear voltage regulator as well as configurable precision current sense (CS) amplifiers. System parameters are stored in a digital core, which includes a serial peripheral interface (SPI) for communication with a microcontroller to allow configuration of a wide range of system parameters. Configuration may also be performed via a PC using Infineon's BLDC motor control workbench graphical user interface (GUI) software tool.<sup>1</sup> This works with the 6EDL\_SPI\_LINK interface board, which connects to a USB type A port. Configuration settings can be stored in RAM or made permanent by burning to one-time programmable (OTP) memory.

Figure 4 6EDL7141 internal block diagram

<sup>&</sup>lt;sup>1</sup> The BPA motor control workbench GUI may be downloaded using the Developer Center Launcher: <u>https://www.infineon.com/cms/en/design-support/tools/utilities/infineon-developer-center-idc-launcher/</u>

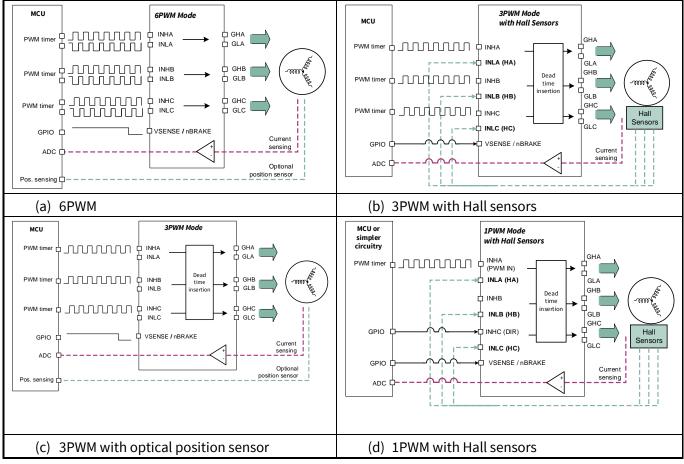

#### 1.2.1 PWM modes

PWM signals from the microcontroller provide the gate drive control pulses, which can be decoded in several different ways. The 6EDL71x1 provides gate drive pulses to the three-phase inverter low- and high-side MOSFETs. The gate drive output voltages (PVCC) can be selected from several different levels between 7 V and 15 V. Here are some of the PWM modes supported:

- 6PWM

- 3PWM with Hall or optical position sensing

- 1PWM with Hall sensors

This allows the designer flexibility in terms of microcontroller selection to cover a variety of different applications. In 1PWM and 3PWM modes the dead time is configurable in the 6EDL71x1.

Figure 5 PWM switching modes supported by the 6EDL71x1

### Note: It should be noted that in 6PWM mode the dead time is set by the microcontroller PWM outputs. In 3PWM and 1PWM modes the dead time is set by the 6EDL71x1.

A key feature of the 6EDL71x1 driver is the ability to control the slew rate of the phase node voltages at each of the half-bridge nodes connecting to the motor phases shown in **Figure 3**. This is achieved by digital configuration of the gate drive sink and source currents and timing. The 6EDL71x1 series gate driver outputs can be connected directly to each MOSFET gate without any external resistors or other components. Switch-on and switch-off profiles can be optimized to determine the slew rate and thereby minimize EMI and switch-off transients by configuration of the gate drive current during the switching process.

Note: The PWM drive pulses produced by the microcontroller that connect to the 6EDL71x1 inputs should not be less than a defined minimum pulse width! The microcontroller firmware must define a minimum pulse width and ensure that pulses shorter than this are not generated under any condition. This is necessary because the 6EDL71x1 gate drive outputs require a certain amount of time to complete the turn-on and turn-off transitions. A typical value is stated in the 6EDL71x1 datasheet; however, this time period will vary depending on the gate drive configuration settings and the type of MOSFET used in the inverter.

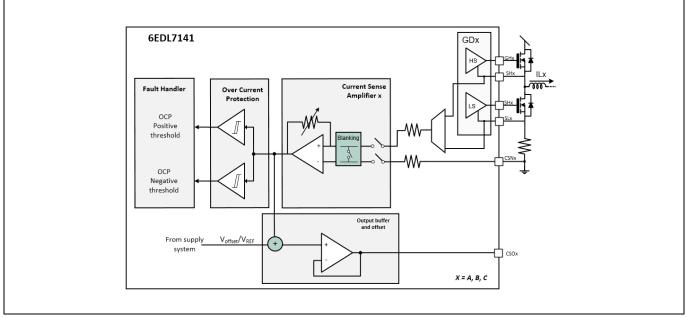

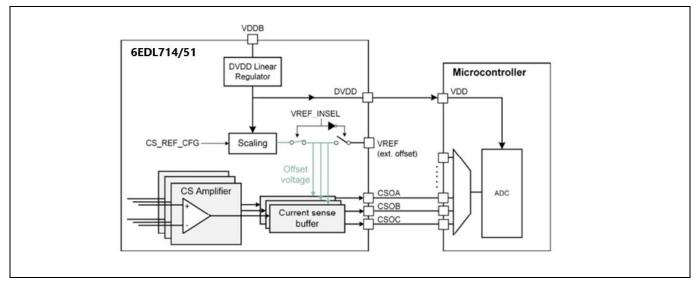

#### **1.2.2** Current sense amplifiers and comparators

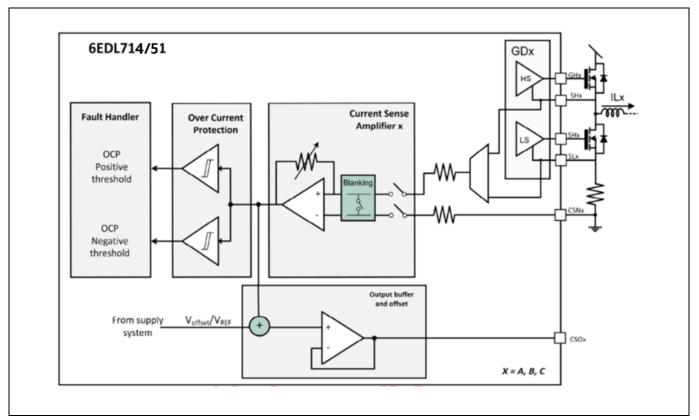

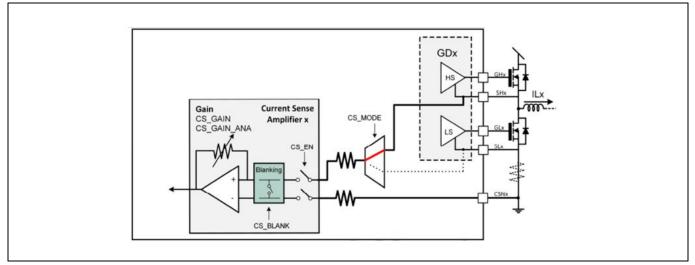

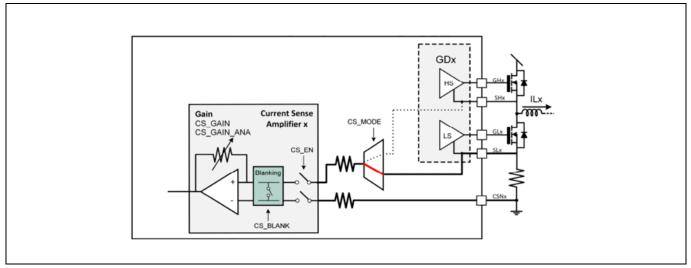

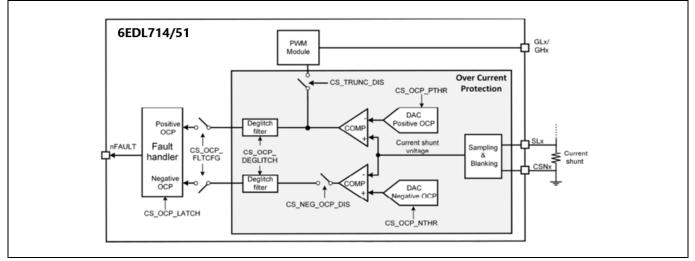

The 6EDL7141 and 6EDL7151 integrate three precision CS amplifiers, which can be used to measure the current in the inverter via shunt resistors. Single-, double- or triple-shunt measurements are supported. Each CS amplifier can be enabled individually. The gain and offset are configured internally and can be set via the user interface. An additional output buffer allows adding a variable offset voltage to the sense amplifier output, which can be set to four different values either by programming the internally generated level or by applying an external voltage at the VREF input pin so that negative current in current shunts can also be measured.

A positive overcurrent comparator detects an overcurrent condition on a motor winding for a positive shunt voltage. This comparator can be used to apply PWM cycle-by-cycle pulse truncation, terminating the gate drive to limit the maximum motor current. An additional negative overcurrent comparator is also used for detecting the overcurrent condition on motor winding for negative shunt currents. A built-in DAC is used for programming the thresholds of the overcurrent comparators.

6EDL71x1 CS amplifiers and comparators

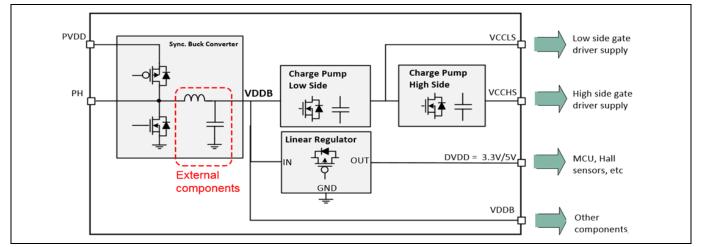

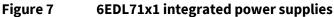

#### 1.2.3 Integrated buck, linear regulators, and charge pumps

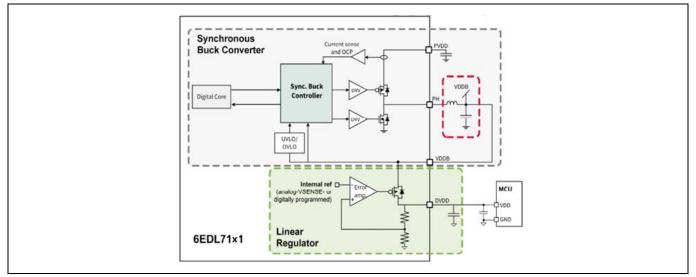

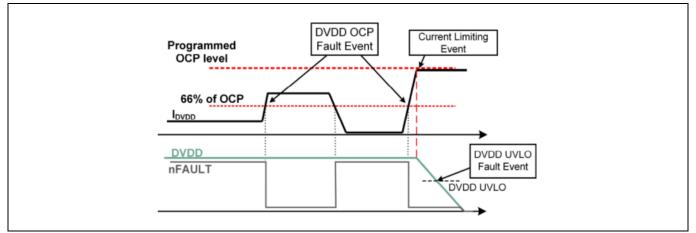

The 6EDL7141 and 6EDL7151 also include an integrated power system infrastructure based on a synchronous buck regulator and linear regulator (LDO). This converts the battery voltage to an internal voltage (VDDB), which is set to 6.5 V, 7 V, or 8 V depending on the gate drive voltage setting, able to supply up to 300 mA. The only external components required are the inductor and capacitor. The buck regulator output (VDDB) supplies the linear regulator, which can provide a noise-free 3.3 V or 5 V supply (DVDD) for the internal digital circuitry and external microcontroller.

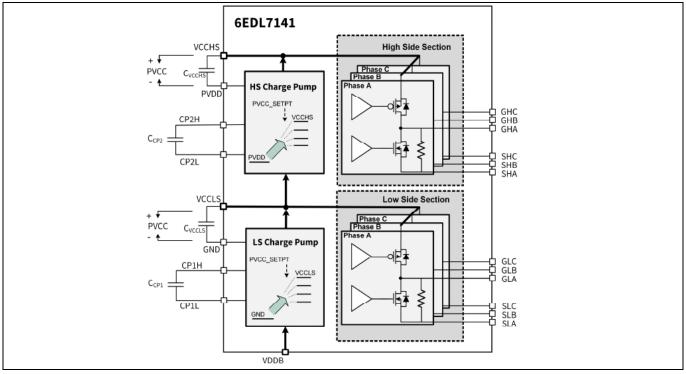

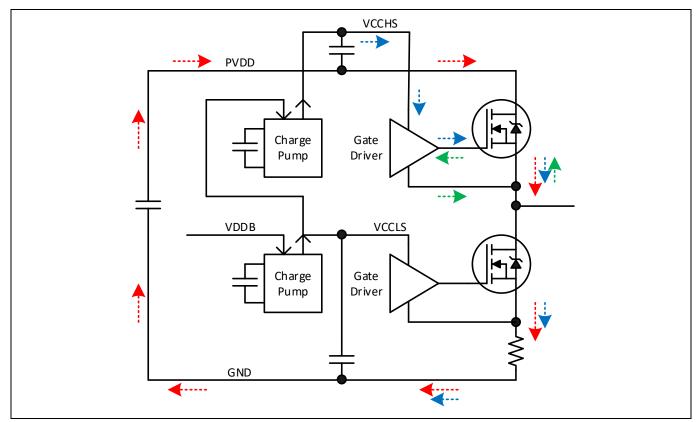

Integrated low- and high-side charge pumps supplied from the buck regulator provide the gate driver supply voltages, which enable duty cycles up to 100 percent. Each charge pump uses an external switched capacitor (CP1 for the low-side and CP2 for the high-side) to transfer charge from the buck converter output to the gate driver bias supplies: VCCLS and VCCHS. VCCLS is referenced to the system zero-volt rail and VCCHS is referenced to the system positive supply rail. The voltage level is referred to as PVCC, which is equal to VCCLS and VCCHS-PVDD. Unlike conventional half-bridge drivers, the 6EDL71x1 includes an advanced high-side driver scheme that enables VCCHS to able to supply the switch-on voltage and current to the high-side gate drivers for all three phases without the need for separate floating supplies for each phase. The values of the switched capacitors and bias supply capacitors, CVCCLS and CVCCHS, need to be selected according to the datasheet instructions for the charge pumps to operate correctly. The charge pump clock frequency is selectable from 195.3 kHz, 390.6 kHz, 781.3 kHz, or 1.56 MHz with optional frequency modulation to reduce EMI.

#### Introduction

Figure 8 6EDL71x1 integrated charge pumps and gate drivers

The 6EDL71x1 also incorporates the following additional protection functions:

- Overcurrent protection (OCP) for the internal power supplies and inverter phases

- Undervoltage lock-out (UVLO) for the input bus voltage and digital supply voltage

- Overtemperature detection, warning and shutdown

- A configurable watchdog (WD) timer

- Locked rotor detection based on Hall sensor inputs and memory fault detection

System functional description

### 2 System functional description

#### 2.1 Commutation methods

The three-phase BLDC motor drive inverter may employ either trapezoidal/six-step commutation (also known as block commutation) or field-oriented control (FOC). Implementations may be sensed using some type of position sensor (e.g., Hall sensors) or may be sensor-less, utilizing more complex control algorithms capable of determining the rotor position from phase current measurements.

In the various different cases different PWM switching modes may be used, which are supported by the 6EDL71x1 as described in **Section 1.2.1**. In each case the PWM operates at a fixed frequency and the duty cycle is adjusted to control the stator winding currents in each phase. The switching frequency is typically around 10 kHz. The winding inductances remove most of the PWM switching frequency component but a certain amount of high-frequency (HF) ripple remains. If used, position sensors may be connected to the microcontroller or directly to the 6EDL71x1, depending on which PWM mode is being used. More complex control algorithms such as sensor-less FOC would require 6PWM mode. 3PWM and 1PWM modes may be used with more basic microcontrollers in cost-sensitive applications.

#### 2.1.1 Trapezoidal/six-step (block) commutation

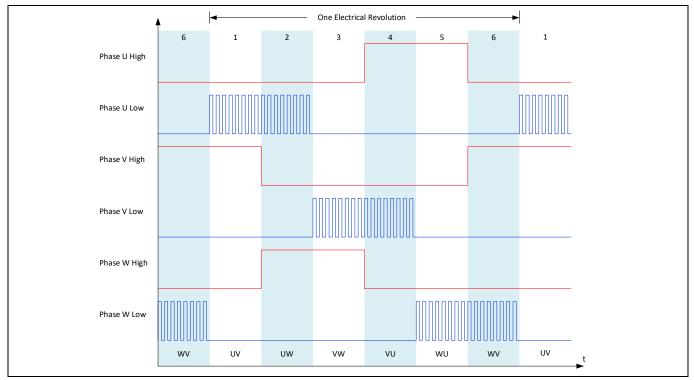

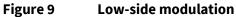

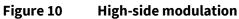

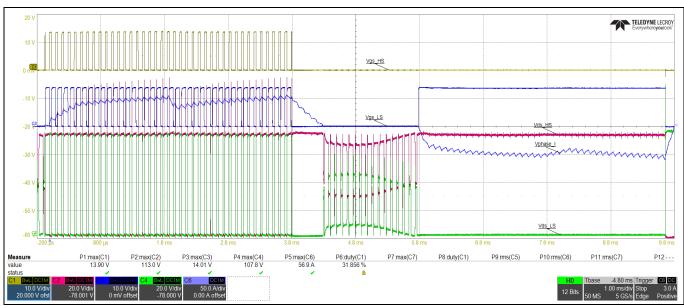

Th 6EDL71x1 series of gate drivers can support the trapezoidal PWM schemes listed in the table below, which may be selected by firmware.

| Modulation scheme                                   | Description                                                                                         |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Low-side modulation                                 | Modulation is applied to the low-side switches                                                      |

| High-side modulation                                | Modulation is applied to the high-side switches                                                     |

| High-side modulation with synchronous rectification | Modulation is applied to the high-side switches with a complementary pulse to the low-side switches |

Table 1

Trapezoidal commutation PWM schemes

Basic low- and high-side modulation schemes do not use synchronous rectification (SR) and rely on the MOSFET body diode to conduct during the PWM off periods. This adds to the conduction losses in these devices; therefore, it is preferable to use SR. In this case the complementary MOSFET is switched on during the freewheeling period with a dead time inserted to avoid any overlap and resulting shoot-through current.

### Battery-powered BLDC motor drive design using the 6EDL71x1 series

Design guide and recommendations

#### System functional description

### Battery-powered BLDC motor drive design using the 6EDL71x1 series

Design guide and recommendations

#### System functional description

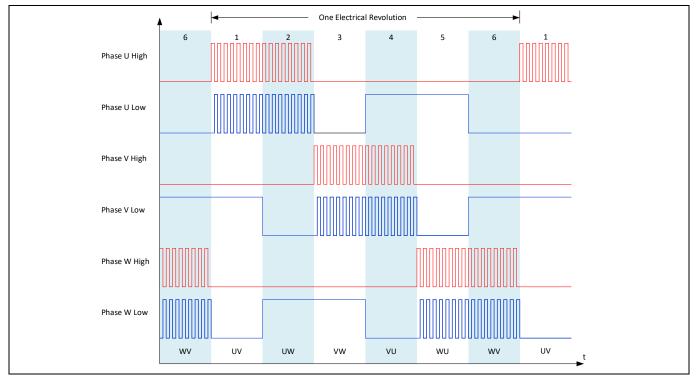

Figure 11 High-side modulation with SR

Figure 12High-side modulation with SR phase waveforms – VGS\_HS (yellow), VGS\_LS (blue), VDS\_HS (red)VDS\_LS (green), IPHASE (purple)

During high-side modulation with SR the switching dead time is inserted between the rising and falling edges of the PWM signals to prevent the high- and low-side MOSFETs of each inverter phase from being on at the same time during switching transitions (shoot-through condition). The body diode of each MOSFET conducts current when the MOSFET is off.

System functional description

#### 2.1.2 Field-oriented control

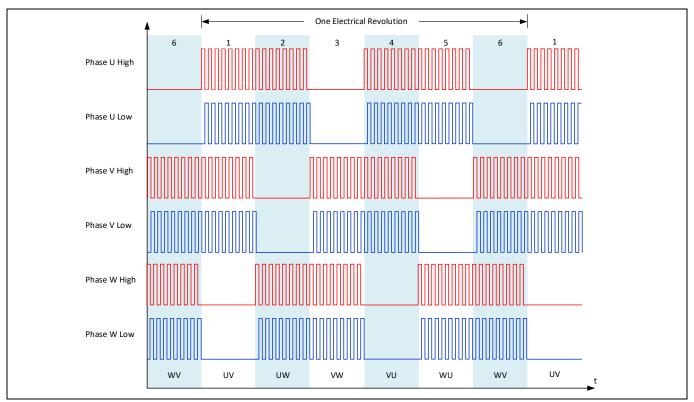

FOC is a form of sinusoidal phase current control. A simplified representation of the PWM gate drive switching patterns used in FOC is shown in **Figure 13**.

Figure 13 FOC switching pattern (simplified, modulation is not shown)

In the real implementation the pulse widths are modulated to produce sinusoidal phase currents.

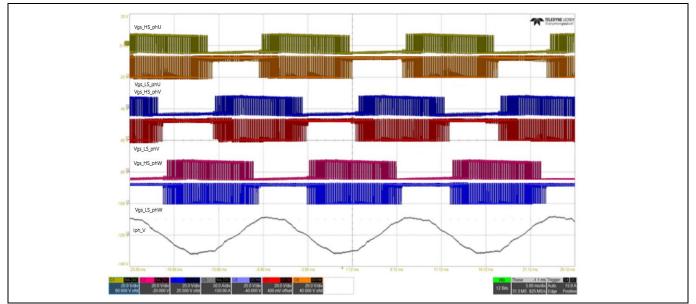

Figure 14High- and low-side gate drive pulses (5 ms/div) - V<sub>GS\_HS\_phU</sub> (yellow), V<sub>GS\_LS\_phU</sub> (orange),<br/>V<sub>GS\_HS\_phV</sub> (blue) V<sub>GS\_LS\_phV</sub> (red), V<sub>GS\_HS\_phW</sub> (pink), V<sub>GS\_LS\_phW</sub> (purple), I<sub>PHASE\_phV</sub> (gray)

System functional description

FOC is often implemented in sensor-less control schemes, for which 6PWM mode is mostly used. Sensor-less FOC requires a microcontroller with sufficient processing power to support calculations needed to generate the vectors required based on the phase current measurements. Careful selection of the microcontroller is necessary for a successful design, based on the control method used and the required switching frequency. Higher frequencies are sometimes used with FOC to reduce torque ripple, which reduces mechanical power losses in the motor.

#### 2.2 6EDL71x1 smart gate driver features

The high- and low-side gate drivers allow operation over the full duty-cycle range up to 100 percent by virtue of the onboard charge pumps. The gate drive voltages can be selected from the following levels: 7 V, 10 V, 12 V, and 15 V. The charge pumps allow the selected voltage levels to be maintained even if the battery voltage drops to a lower level, which allows standard gate-level MOSFETs to be used in low input voltage conditions.

Unlike typical gate drivers, the 6EDL71x1 gate drive outputs are current driven such that the source and sink currents supplied to the MOSFET gates are constant and digitally configurable. This permits the designer to eliminate diode-resistor networks commonly used with standard voltage-driven gate driver ICs. In most cases, gate resistors can be removed altogether, reducing component count and at the same time simplifying and allowing further optimization of the circuit layout. Where more than one MOSFET is used in parallel a gate resistor is still needed to connect from the gate driver output to each MOSFET gate terminal.

Control of the drain-source rise and fall times is one of the most important system optimization points for drive systems, affecting critical factors such as switching losses, dead time optimization and drain voltage ringing that can lead to possible MOSFET avalanching. Correct configuration of the gate drive also helps to minimize EMI emissions.

#### 2.2.1 Slew rate control

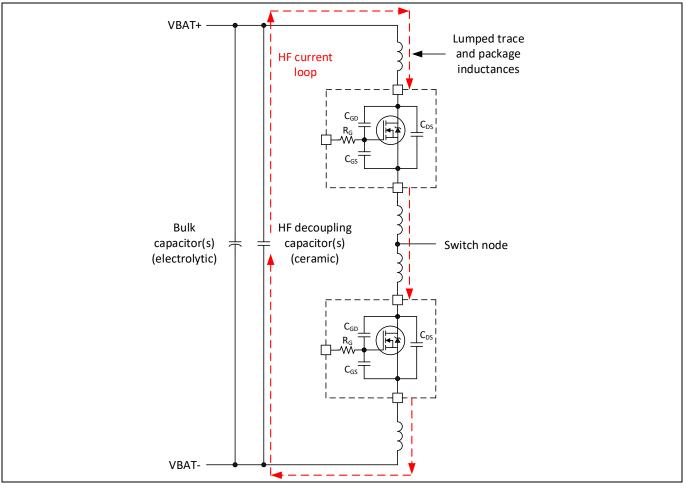

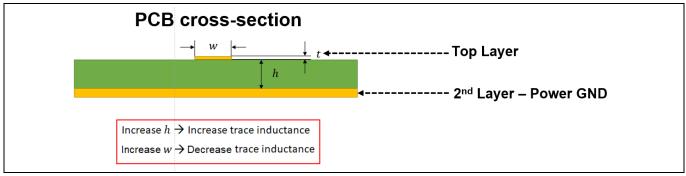

In the three-phase motor drive inverter, the half-bridge switch node voltages transition between 0 V and the DC bus voltage. Depending on the control scheme and switching patterns used in the system design, hard- or softswitching transitions may occur.

Slew rate control is relevant to hard-switching transitions, where the voltage transition can be defined as  $dv_{DS(U,V,W)}/dt$  and the current transition as  $di_{D(U,V,W)}/dt$ .  $dv_{DS(U,V,W)}/dt$  is generally measured during the linear part of the switching transition during the Miller plateau period of the gate drive waveform, between 10 and 90 percent of the bus voltage. Slew rate is the determining factor in reaching the best tradeoff between switching losses and radiated EMI. That is to say a faster slew rate offers lower switching losses but gives rise to higher levels of ringing and HF harmonics that produce EMI. Battery-powered motor drives are required to meet radiated emission limits, defined in standards such as CISPR 14-1, which applies to household appliances, electric tools and similar apparatus.

The 6EDL71x1 series of drivers have the ability to optimize switching by controlling the rise and fall slew rates by means of advanced current-driven gate drive outputs, which control the gate drive sink and source currents during different time segments during the MOSFET switch-on and switch-off processes. This process is described in detail in the following sections.

System functional description

#### 2.2.1 Switch-on transient

Switch-on transients typically occur across the drain and source of the low-side MOSFET when the high-side MOSFET switches on. These are the result of fast-changing current interacting with MOSFET package and PCB trace inductances ( $L_{package}$  and  $L_{PCB}$ ). The ringing shown in the blue waveform below is a result of the low-side MOSFET body diode recovery, which occurs when the high-side MOSFET is switching on and the current is being diverted from the low-side body diode to the high-side channel.

Figure 15 Example V<sub>DS(LS)</sub> switch-on transient shown in blue

This will be discussed in more detail.

#### 2.2.2 Switch-off transient

Switch-off voltage transients appear between the drain and source of the high-side MOSFET again due to package and trace inductances ( $L_{package}$  and  $L_{PCB}$ ) when large channel currents ( $I_D$ ) are interrupted, since this current is commutated to the low-side body diode. The worst-case condition is at the highest current, which would normally occur under a motor stall condition. If the transient is sufficiently high to exceed the MOSFET-rated BV<sub>DSS</sub>, it is likely to cause the MOSFET to avalanche, which can lead to device damage and premature failure.

The peak amplitude of this transient is determined by these inductances and how rapidly the current in the device is switched off, according to:

$$V_{DS} = (L_{package} + L_{PCB}) \cdot \frac{di_{DS}}{dt}$$

[1]

Where  $V_{DS}$  refers to the voltage seen at the MOSFET die inside the package. This explains why a low-inductance SMD package is preferable to a high-inductance leaded package, since  $L_{package}$  will be much lower. Since it is only possible to measure the external drain and source connections of the MOSFET, the designer should allow for package inductance and leave a safety margin of at least 50 percent between the peak transient voltage and the device-rated  $BV_{DSS}$ . Measurements should be made using a differential oscilloscope probe with a bandwidth of at least 100 MHz.

#### System functional description

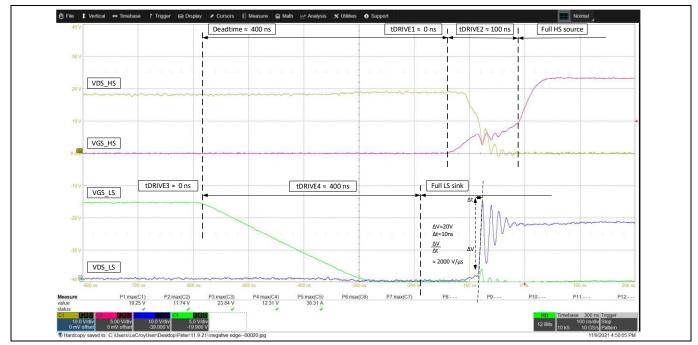

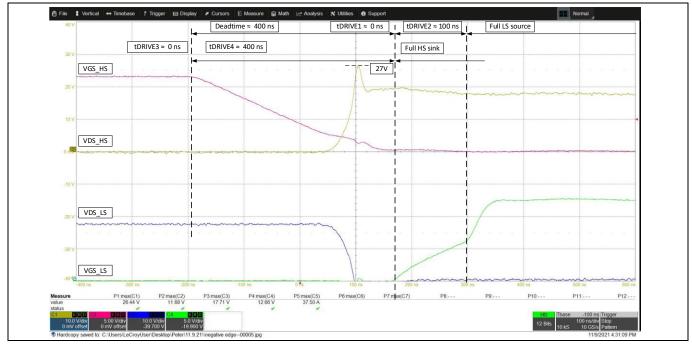

The yellow waveform shown in the oscilloscope screen capture in **Figure 16** is a measurement of the high-side MOSFET V<sub>DS</sub> measured at the device terminals when this device is being switched off. The switch-off transient can be observed, which in this case is due to PCB trace inductances. In this example, a 40 V rated MOSFET is used in a PQFN 5x6 (SuperSO8) package with very low inductance. It can be seen that the peak voltage at switch-off reaches 27 V. However, this was measured at full load not under a stall condition, in which case the peak would be expected to be several volts higher.

Figure 16 Example V<sub>DS(HS)</sub> switch-off transient shown in yellow

Since the transient is dependent on di<sub>D</sub>/dt, it is possible to reduce it if necessary by slowing down the switch-off transition by reducing the gate drive sink current. This can be done while the inverter is running with 6EDL71x1 series drivers using the motor control GUI. However, care should be taken when making such on-the-fly adjustments to gate driver settings. In some cases it will still be necessary to add series resistor-capacitor snubber networks between the drain and source of each MOSFET; however, this should be avoided if possible since it adds to switching losses.

Design guide and recommendations System functional description

#### 2.2.3 Configuration of the gate driver

#### 2.2.3.1 Gate drive current and timing

The designer is able to configure the 6EDL71x1 gate driver currents and timing with the following parameters via SPI-accessible registers:

| Gate drive parameters <sup>2</sup>                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                    | Minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Source current value for switching on high-side MOSFETs                                                                                        | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Sink current value for switching off high-side MOSFETs                                                                                         | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Current value for switching on low-side MOSFETs                                                                                                | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Current value for switching off low-side MOSFETs                                                                                               | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pre-charge current value for switching on both high- and low-side                                                                              | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pre-(dis)charge current value for switching off both high- and low-<br>side                                                                    | 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Amount of time that I <sub>PRE_SRC</sub> is applied.<br>Shared configuration between high- and low-side drivers.                               | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.59 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Amount of time that I <sub>HS_SRC</sub> and I <sub>LS_SRC</sub> are applied.<br>Shared configuration between high- and low-side drivers.       | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.55 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Amount of time that I <sub>PRE_SNK</sub> is applied.<br>Shared configuration between high- and low-side drivers.                               | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.59 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Amount of time that I <sub>HS_SINK</sub> and I <sub>LS_SINK</sub> and are applied.<br>Shared configuration between high- and low-side drivers. | 0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.55 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                | DescriptionSource current value for switching on high-side MOSFETsSink current value for switching off high-side MOSFETsCurrent value for switching on low-side MOSFETsCurrent value for switching off low-side MOSFETsPre-charge current value for switching on both high- and low-sidePre-(dis)charge current value for switching off both high- and low-sideAmount of time that IPRE_SRC is applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SRC are applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SNK is applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SNK is applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SNK is applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SNK is applied.Shared configuration between high- and low-side drivers.Amount of time that IPRE_SNK and ILS_SINK and are applied. | DescriptionMinimumSource current value for switching on high-side MOSFETs10 mASink current value for switching off high-side MOSFETs10 mACurrent value for switching on low-side MOSFETs10 mACurrent value for switching off low-side MOSFETs10 mAPre-charge current value for switching on both high- and low-side10 mAPre-(dis)charge current value for switching off both high- and low-side10 mAPre-(dis)charge current value for switching off both high- and low-side0 mAShared configuration between high- and low-side drivers.0 nsAmount of time that I <sub>PRE_SRC</sub> and I <sub>LS_SRC</sub> are applied.<br>Shared configuration between high- and low-side drivers.0 nsAmount of time that I <sub>PRE_SNK</sub> is applied.<br>Shared configuration between high- and low-side drivers.0 nsAmount of time that I <sub>PRE_SNK</sub> is applied.<br>Shared configuration between high- and low-side drivers.0 nsAmount of time that I <sub>PRE_SNK</sub> is applied.<br>Shared configuration between high- and low-side drivers.0 nsAmount of time that I <sub>PRE_SNK</sub> is applied.<br>Shared configuration between high- and low-side drivers.0 ns |

#### Table 2Gate drive parameters1

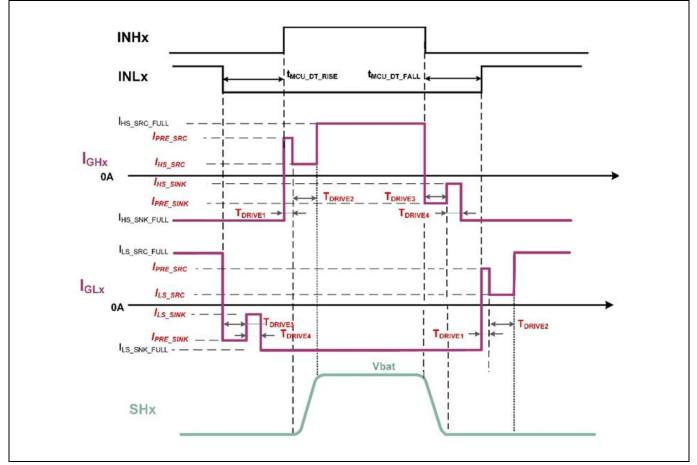

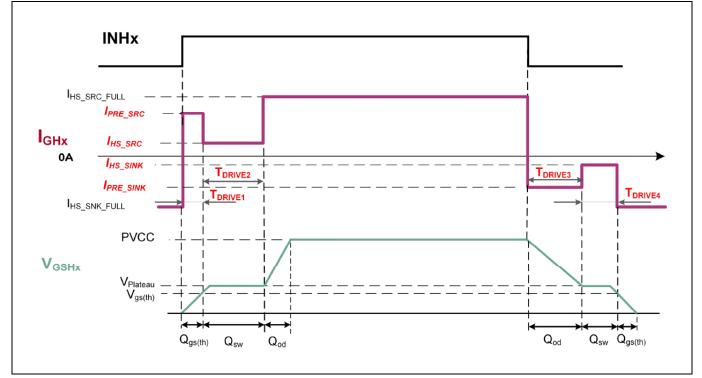

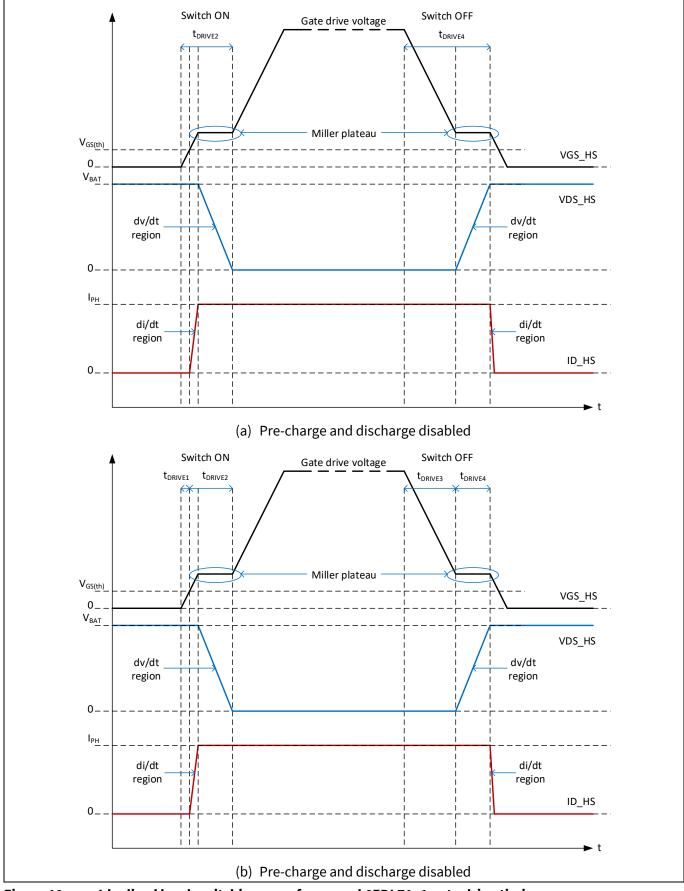

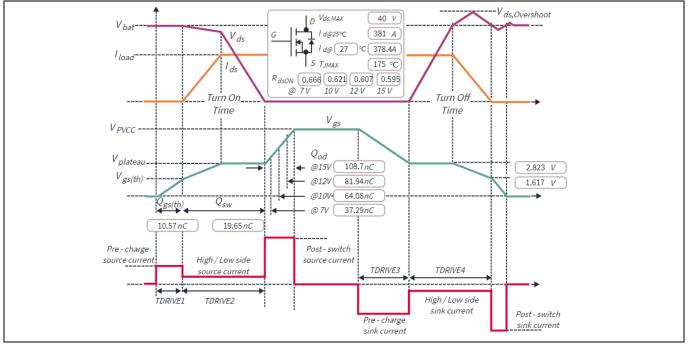

When the input signal from the microcontroller transitions from low to high, the gate drive output first applies a constant current defined by the user-programmable value  $I_{PRE\_SRC}$  for a time defined by  $T_{DRIVE1}$ , at the end of which the MOSFET gate voltage should have reached the threshold voltage  $V_{GS(TH)}$ . The next period of the gate switch-on sequence is defined by the parameter  $T_{DRIVE2}$ , which begins immediately after the completion of  $T_{DRIVE1}$ . The current applied during  $T_{DRIVE2}$  determines both  $dI_D/dt$  and  $dV_{DS}/dt$  of the MOSFETs, as it will supply the current to charge the Q<sub>SW</sub> of the MOSFET being driven.

## It is necessary to set the correct values for $T_{DRIVE1}$ and $T_{DRIVE2}$ , which are dependent on the values of $I_{PRE\_SRC}$ and $I_{H,LS\_SRC}$ , meaning that if the gate drive current settings are changed then $T_{DRIVE1}$ and $T_{DRIVE2}$ must be changed accordingly. Failure to do so will result in misalignment and incorrect switching! In many cases the pre-charge is not necessary and therefore $T_{DRIVE1}$ can be set to zero. This greatly simplifies the gate drive optimization for switch-on.

In the three-phase motor drive configuration, each half-bridge operates in continuous conduction mode with non-ZVS<sup>2</sup> switch-on of the high-side. ZVS normally occurs at the low-side since the phase current is already passing through the body diode. However, non-ZVS switch-on of the low-side can occur under some conditions. Once the  $T_{DRIVE2}$  period has elapsed, the gate driver applies full current (1.5 A) to ensure fastest full turn-on of the MOSFET by supplying the remaining charge required to raise V<sub>GS</sub> to the programmed PVCC value ( $Q_{OD} = Q_G - Q_{SW} - Q_{G(TH)}$ ).

<sup>&</sup>lt;sup>1</sup> Available current and time delay values are listed in section 8 "Register Map" of the 6EDL7141 datasheet [1].

<sup>&</sup>lt;sup>2</sup> ZVS – zero voltage switching. Non-ZVS switch-on is also referred to as a "hard" switch-on.

#### System functional description

A similar process takes place during the switch-off of the MOSFET, in which the parameters T<sub>DRIVE3</sub> and T<sub>DRIVE4</sub> determine the periods for which the programmed discharge currents are applied.

Note: When adjusting the slew rate to a desired value it is necessary to set the dead time to a suitable value greater than the sum of T<sub>DRIVE1</sub> and T<sub>DRIVE2</sub> for the low to high transition and T<sub>DRIVE3</sub> and T<sub>DRIVE4</sub> for the high to low transition, or whichever is greater if both dead times are equal. Dead time is set by the microcontroller when using 6PWM mode and by the 6EDL71x1 in 3PWM and 1PWM modes.

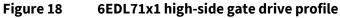

**Figure 18** shows in detail the V<sub>GS</sub> charging and discharging transitions for a high-side MOSFET in one of the inverter phases during a typical non-ZVS turn-on and turn-off. The different charging and discharging phases of the MOSFET switch-on and switch-off are illustrated above. Thanks to the flexible timing structure provided by the 6EDL71x1 gate driver with its high T<sub>DRIVE(X)</sub> resolution and ability to set the current during each interval, the designer is able to configure and optimize the switch-on and switch-off operations without the need for any external gate drive components.

During the critical Miller plateau period in hard-switching transitions, the controlled gate drive currents enable control of the slew rate  $dV_{DS}/dt$ . This is accomplished by precise control of the gate drive currents during the periods  $T_{DRIVE2}$  (switch-on) and  $T_{DRIVE4}$  (switch-off), during which the charge  $Q_{SW}$  is injected or extracted from the gate while  $V_{DS}$  transitions. Higher currents can be used for fast charging and discharging of  $Q_{GS(TH)}$  and  $Q_{OD}$ , since neither  $dI_D/dt$  nor  $dV_{DS}/dt$  are affected during these periods.

It is also an option to set T<sub>DRIVE3</sub> to zero, which simplifies the gate drive optimization for switch-off.

### Battery-powered BLDC motor drive design using the 6EDL71x1 series

Design guide and recommendations

#### System functional description

Figure 17 6EDL71x1 slew rate control for half-bridge

System functional description

#### 2.2.3.2 Gate pre-charging feature

The pre-charge function enables rapid charging of  $V_{GS}$  from zero to  $V_{GS(TH)}$  during the initial stage of switch-on. This can be useful when driving MOSFETs with a high gate charge ( $Q_G$ ) or when driving several MOSFETs in parallel with a large total  $Q_G$ . However, in most cases where a single MOSFET is used such as an OptiMOS<sup>TM</sup> device the gate charge is quite low and therefore the pre-charge feature is not necessary and should be disabled to simplify the gate drive optimization process. This is done by setting  $T_{DRIVE1}$  to zero.

When using the pre-charge function, it is important to account for the tolerance of  $V_{GS(TH)}$  by designing for the minimum value. The pre-charge current can be selected from seventeen available values. Sixteen of them are defined by  $I_{PRE\_SRC/SNK}$  with an additional 1.5 A option, which is the maximum current capability of the gate driver. In cases where larger MOSFETs with relatively high gate charge are used,  $Q_{G(TH)}$  during turn-on or  $Q_{OD}$  during turn-off may benefit from using the full gate driver capability. Full strength during the pre-charge may be selected via the GUI.

Where pre-charge is not used,  $T_{DRIVE1}$  can be set to zero, which results in the gate driver going immediately to the beginning of the  $T_{DRIVE2}$  period with its corresponding gate current setting. By doing this  $I_{HS,LS\_SRC}$  is applied from the start of the switching period to the end of the Miller plateau.

The 6EDL71x1 series gate driver configurability enables optimization for both large and small MOSFETs covering different technologies such as OptiMOS<sup>TM</sup> or StrongIRFET<sup>TM</sup>. This makes the design process much easier since the source current selected must determine the slew rate during switch-on. The selection of  $T_{DRIVE2}$  must allow a long enough period to cover the time from initial switch-on to the end of the Miller plateau. The duration of the plateau depends on the slew rate, which is determined by the source current. Therefore setting the values of  $T_{DRIVE2}$  and  $I_{HS,LSSRC}$  is an iterative process since these values are interdependent. At the end of  $T_{DRIVE2}$  the source current will revert to 1.5 A, therefore it is important to ensure this does not occur prematurely during the Miller plateau period.

During the switch-off phase  $T_{DRIVE3}$  can also be set to zero to simplify the configuration of the switch-off. By doing this  $I_{HS,LS\_SINK}$  is applied from the start of the switching period to the end of the Miller plateau.

If this option is taken, it is important to set  $T_{DRIVE4}$  to a period long enough to discharge  $V_{GS}$  from its maximum value down to the Miller plateau voltage and then pass through the full duration of the plateau. If  $T_{DRIVE4}$  is too short then the full 1.5 A sink current will be applied while the switch-off transition is still occurring. This is very undesirable as it can produce a large  $V_{DS}$  switch-off transient that risks MOSFET avalanching under high-current conditions such as a motor stall. As before, the duration of the plateau depends on the slew rate, which is determined by the sink current. Therefore setting the values of  $T_{DRIVE4}$  and  $I_{HS,LSSNK}$  is an iterative process since these values are interdependent.

For simplicity,  $T_{DRIVE1}$  and/or  $T_{DRIVE3}$  should be set to zero, resulting in these intervals being skipped unless complex gate drive configuration is absolutely necessary for system optimization. Alternatively  $T_{DRIVE2}$  and/or  $T_{DRIVE4}$  could be set to zero and  $I_{PRE_SRC}$  and  $I_{PRE_SINK}$  could be used as the gate drive currents. However, this approach does not permit different current settings for the high and low-side, though this is not a usual requirement.

Note:

When using the 6EDL7141 or IMD700/1A, when transitioning from the pre-charge current setting (at the end of  $t_{DRIVE1}$ ) to the gate drive source current setting (at the start of  $t_{DRIVE2}$ ) or from the pre-discharge current setting ( $t_{DRIVE3}$ ) to the gate drive sink current setting (at the start of  $t_{DRIVE2}$ ), a short period of reduced gate current can occur for 80 to 100 ns, before the new gate sink or source current value is established. This occurs only for certain current settings.

System functional description

To avoid interruptions in the gate drive, the designer may choose not to enable the precharge and pre-discharge functions as previously described. However, if these functions are necessary for the design, then current value combinations can be found where the delay does not occur.

Please refer to the 6EDL7141 datasheet section 3.2.2.1 [1] for further details.

This issue is not present in the 6EDL7151.

#### 2.2.3.3 Gate drive voltage

The 6EDL71x1 offers the designer several driving voltage options to select from depending on the system requirements, allowing designers to adjust the MOSFET driving voltage (PVCC voltage) via SPI registers. The same-value PVCC applies to both high- and low-side charge pumps from the four possible values: 7 V, 10 V, 12 V, and 15 V. This is done by setting bitfield PVCC\_SETPT via the GUI, where the default value is 12 V. Gate drive outputs include UVLO protection.

High-impedance MOSFET gate inputs in a motor drive inverter should never be left floating when gate drivers are not activated because electrical noise or static can cause gate voltage buildup. In some cases, such voltages can be high enough to pass the MOSFET gate turn-on threshold, partially switching on the device. If a high- and low-side MOSFET in an inverter phase were to switch on at the same time, the resulting high current could destroy the devices. In order to prevent this, it is common to add weak pull-down resistors between the gates and sources of each MOSFET. The 6EDL71x1 avoids the need for these external resistors by integrating the following functions into its gate driver outputs:

- Weak pull-down: A weak pull-down (RGS\_PD\_WEAK) is always connected between gate and source of each gate driver output. This ensures a weak pull-down during states where the gate driver is off, either because EN\_RV is turned off or because the device is fully off (CE off).

- Strong pull-down: During gate driver off periods, if the external gate-to-source voltage increases for any reason, a strong pull-down (RGD\_PD\_STRONG) is activated, ensuring a tight pull-down to prevent any partial turn-on.

**Figure 19** shows an idealized representation of hard-switching waveforms to illustrate the gate drive operation and to identify the di/dt and dv/dt transitions that occur. These waveforms do not account for MOSFET output capacitances, parasitic inductances or diode recovery that would be present in a practical motor drive inverter; however, they serve to show the timing scheme used in the 6EDL71x1 gate drivers.

Battery-powered BLDC motor drive design using the 6EDL71x1 series (infineon

Design guide and recommendations

#### System functional description

Figure 19 Idealized hard-switching waveforms and 6EDL71x1 gate drive timing

Motor drive inverter design

#### 3 Motor drive inverter design

#### **3.1** Defining the system parameters

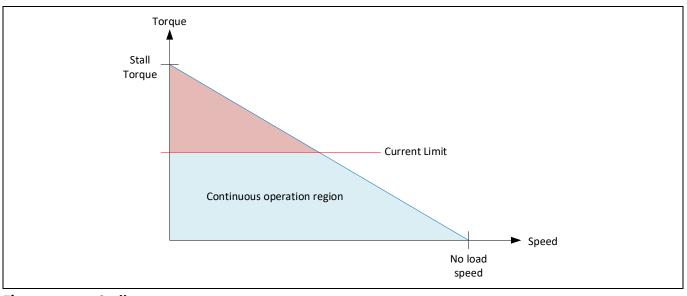

The inverter power stage design requires careful consideration of the critical parameters listed here, which include:

- Battery voltage (minimum and maximum)

- Battery capacity and impedance

- Maximum continuous and peak power requirements

- Maximum continuous and peak motor phase currents (it is essential to allow for the high current that passes through the MOSFETs during a stall condition for a limited time)

- Control method (this is typically a speed-regulated control loop)

- Commutation method; this could be six-step trapezoidal or sinusoidal

- Switching frequency

- Thermal management, heatsinking

- Form factor

- Motor winding inductance

- Motor winding resistance

$$I_{stall} = \frac{V_{ab}}{2.R} = \frac{V_{bat}}{2.R}$$

[2]

Figure 20 Stall current

Motor drive inverter design

#### 3.2 MOSFET selection

The following table lists the MOSFET parameters and design criteria that should be considered when selecting the device to use in a battery-powered BLDC motor drive inverter design.

| Table 3 | MOSFET parameters for motor drive inverter |

|---------|--------------------------------------------|

|---------|--------------------------------------------|

| Parameters                 | Quantity                 | Design criteria                                                 |

|----------------------------|--------------------------|-----------------------------------------------------------------|

| Breakdown voltage          | BV <sub>DSS</sub>        | Margin for transients                                           |

| On-resistance              | R <sub>DS(on)</sub>      | $V_{GS}$ greater than or equal to 10 V                          |

| Maximum continuous current | I <sub>D(MAX)</sub>      | Temperature derating                                            |

| Maximum peak current       | I <sub>D(PK)</sub>       | Stall current                                                   |

| Gate charges               | Q <sub>G</sub>           | $Q_{GD}/Q_{GS}$ = 0.5 to 0.8, $Q_{GD}/Q_{GS(TH)}$ less than 1.0 |

| Gate capacitance           | $C_{GS}, C_{GD}, C_{DS}$ | C <sub>GS</sub> /C <sub>GD</sub>                                |

| Gate resistance (internal) | R <sub>G</sub>           | High R <sub>g</sub> can cause C.dv/dt                           |

| Safe operating area        |                          | Switching speed                                                 |

| Body diode recovery        | t <sub>rr</sub>          | Lower value preferred                                           |

| Body diode recovery charge | Q <sub>RR</sub>          | Lower value preferred                                           |

| Body diode softness factor | RRSF                     | $t_s/t_F$ greater than 0.8 ( $t_B/t_A$ )                        |

| Package                    |                          | Parasitic resistances and inductances                           |

#### 3.2.1 Breakdown voltage BV<sub>DSS</sub>

## The first parameter to consider is BV<sub>DSS</sub>. As a general rule, consider the highest rated input voltage and add at least 50 percent safety margin.

For example, a system is designed for an 18 V battery, which is rated to operate at a maximum input of 24 V. In this case a 40 V rated MOSFET such as the BSC007N04LS6 would be suitable.

#### 3.2.2 On-resistance R<sub>DS(on)</sub>

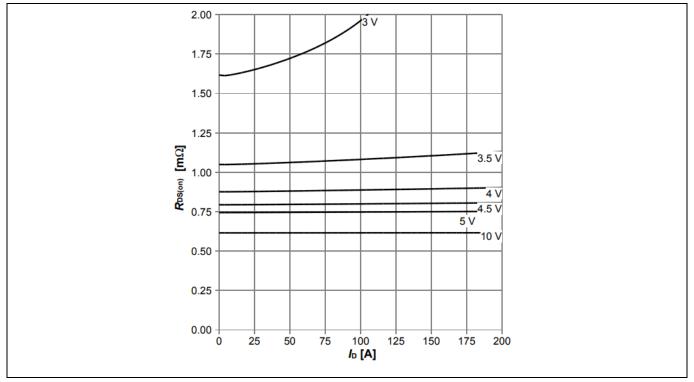

Next the R<sub>DS(on)</sub> should be considered. Best-in-class MOSFETs (i.e., the lowest R<sub>DS(on)</sub> available in a particular voltage and package) are generally used in battery-powered BLDC motor drive inverters. If necessary more than one device may be connected in parallel in each switch location to reduce conduction losses to an acceptable level. Calculation of total MOSFET losses is a moderately complex process, which is dependent on the type of commutation scheme used and the switching frequency. Both conduction and switching losses need to be evaluated. Once an estimate of device losses has been determined, the desired R<sub>DS(on)</sub> can be found based on the amount of conduction losses and bearing in mind that this should be increased by 30 percent to account for a die temperature operating at 100°C.

Motor drive inverter design

#### 3.2.3 Maximum drain current I<sub>D(MAX)</sub>

Next the maximum drain current rating should be chosen to exceed the stall current, which can be calculated from equation [1]. This may be a pulsed value  $I_{D(PK)}$  if the inverter is designed to shut down within a certain time period when a stall current is detected. This protection feature is supported with the 6EDL71x1 driver. The continuous drain current rating  $I_{D(MAX)}$  must exceed the maximum RMS current carried on the MOSFET with plenty of safety margin. It should be noted that different MOSFET manufacturers use different methods to specify the maximum current ratings of their devices, therefore designers should be wary of datasheets that claim very high current capabilities compared with devices in the similar packages with similar R<sub>DS(on)</sub> ratings.

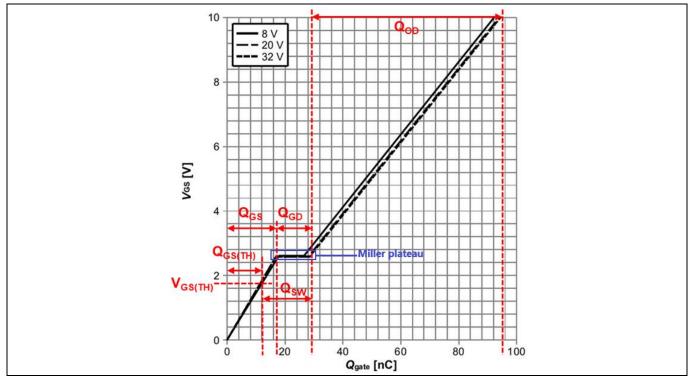

#### 3.2.4 Gate charge ratio

The ratio of  $Q_{GD}$  to  $Q_{GS}$  should be such that  $Q_{GD}/Q_{GS}$  falls between 0.5 and 0.8 so that the device will not be sensitive to induced turn-on caused by the C.dV<sub>DS</sub>/dt effect during switch-on of the complementary device. This effect can produce unwanted losses due to shoot-through currents if both devices are partially switched on at the same time even for a brief period during switching. A lower R<sub>G</sub> value is preferred as this also reduces the effect. At the same time devices with high Q<sub>G</sub> are not preferred since they require more power to switch on and off and may require use of the 6EDL71x1 gate drive pre-charge function.

#### 3.2.5 Safe operating area

The MOSFET safe operating area (SOA) should also be considered. This depends on the period of switching, which is the same as the Miller plateau period that occurs during the transition or "slew" of the switch node voltage from one bus to the other. The switching time is determined by the gate drive current, which is set by the gate driver and chosen as a tradeoff between fast switching to reduce switching losses and slower switching to reduce EMI and switching L.di/dt transients. Since the device current can be quite high during switching, it is necessary to ensure that the SOA limits are not exceeded.

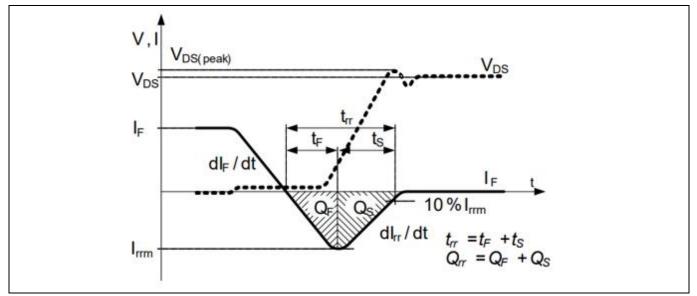

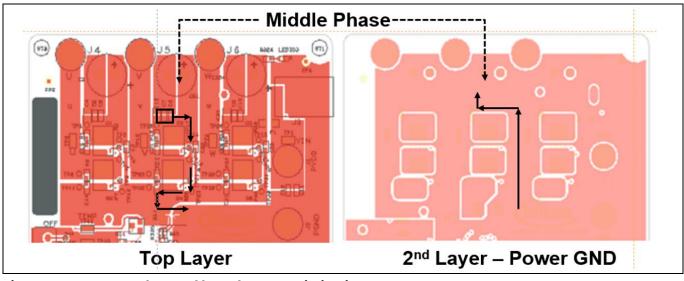

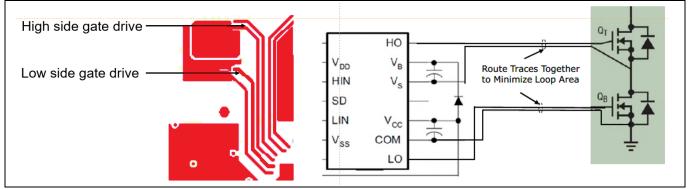

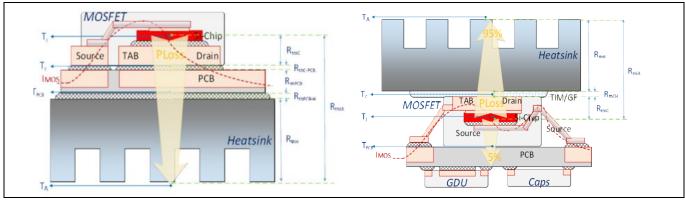

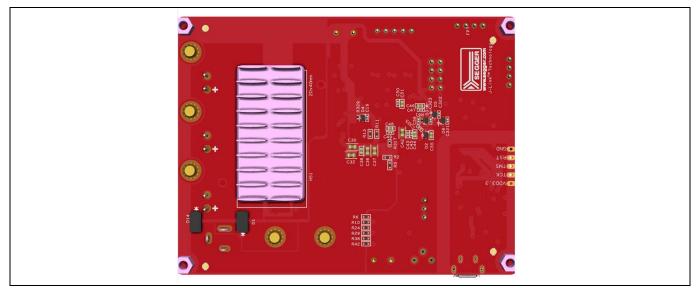

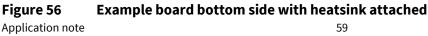

#### 3.2.6 Body diode recovery