# **Integrating 3-V Flash in 5-V Systems**

AN98559 addresses two areas that are critical to enable the integration of 3.3-V flash into a system using a System Controller with 5-V I/O: the I/O signal requirements and the flash VCC power regulation requirements.

## 1 Abstract

Today there are a number of legacy 5-V designs in production; the number of options to directly support the 5-V controllers with native 5-V flash has substantially diminished in recent years. This application note will highlight design changes in a 5-V embedded system that enables the integration of 3.3-V flash devices. This application note will address two areas that are critical to enable the integration of 3.3-V flash into a system using a System Controller with 5-V I/O: the I/O signal requirements and the flash  $V_{\rm CC}$  power regulation requirements.

# 2 3.3-V Flash Support in 5-V Legacy Designs

Flash Technology is being designed and manufactured on 65-nm, 45-nm, and even 32-nm lithography nodes; these flash devices predominately operate at Core voltages of 3.3-V or lower and support similar level I/O voltages. There are a number of legacy designs utilizing 5-V microcontrollers, but the number of options to directly support the 5-V controllers using native 5-V flash has substantially diminished. Today's lower voltage flash devices can be incorporated into a 5-V design. The following section will address both the I/O signal requirements and power regulation to allow integration of the 3.3-V flash into a 5-V based system.

## 2.1 Signal Translation

A 5-V System Controller's signals used to access the flash device include data, address, and control signals. These signals must meet the input requirements for a lower voltage flash device without impacting the system functionality. For example, a Cypress S29GL256P flash utilizes a native 3.3-V V<sub>CC</sub> and its input signals are not 5-V tolerant. The flash device requires an interface to translate incoming control, data, and address signals from 5-V levels down to acceptable 3.3-V levels. Standard voltage translators can be employed to address this issue. Buffer Drivers and Bus Transceivers can be used to translate the incoming control, data, and address signals between the 5-V I/O and 3.3-V I/O levels. The SN74LVCH16244A and SN74LVCH16245A are low cost Buffer Drivers and Bus Transceivers ideal for this purpose. The SN74LVCH16244A device is a unidirectional buffer/line driver with 5-V tolerant I/O pins, suitable for address and control signal translation. The SN74LVCH16245A is a bidirectional bus transceiver used for input/output data signals. Integrating these ICs enables the voltage translations of all control signals, address, and data lines.

The next step is to determine the total number of unidirectional and bidirectional signals used by the System Controller to access a S29GL256P flash.

### 2.1.1 Unidirectional Signals: Address and Control Lines

The S29GL256P unidirectional signals consists of the address lines and six signal control pins (WE#, OE#, CE#, WP#, RY/BY#, and RESET#). The number of address lines will vary depending on the flash density.

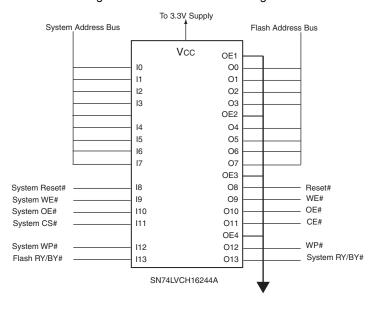

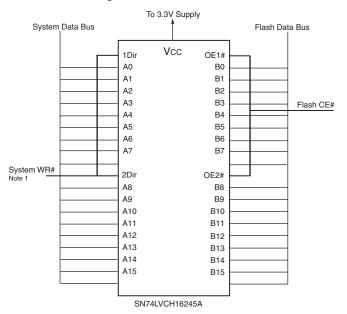

This 256 Mbit flash requires 24 address lines. Figure 1 illustrates the connection of the first 16 address lines from the 5-V address bus to the 3-V flash address pins. Figure 2 outlines the connections for eight additional address lines and the six required control signals. Since the flash address and control pins are input only the Output Enable lines of the buffer can be tied to ground to simplify the control circuitry. The total address and control signal system requires 30 translation lines for this case.

Figure 1. Address Bus Interface

Figure 2. Address and Control Signals

## 2.1.2 Bi-Directional Signal: Data Bus

The S29GL256P 16-bit data bus requires a low voltage transceiver/buffer, to allow for bidirectional data transactions. The SN74LVCH16245A a 5-V tolerant transceiver/buffer can be used for this purpose. This device is similar to the previously used address buffers, but the 245 device contains additional logic input to differentiate between reads and writes. Figure 3 shows the 16 data bus connections.

Figure 3. Data Bus Interface

#### Note:

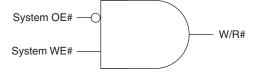

Some Controllers do not support the W/R# signal; this signal distinguishes between a bus read and a bus write cycle and can be synthesized from the System OE# and System WE# signals outlined in Figure 4. Note this circuit implementation assumes System OE# and System WR# are active low.

Figure 4. Synthesize W/R#

# 2.2 Flash V<sub>CC</sub> Power Regulation

The final point to address is the  $V_{CC}$  requirement for the S29GL256P device. To supply the correct operating voltage to this flash device, the 5-V supply must be regulated to 3.3-V to meet the flash  $V_{CC}$  range. The voltage regulation can be realized by way of a low cost LDO fixed linear regulator. Fixed linear regulators are readily available on the market from many companies such as Linear Technologies and other manufacturers. Reference the Linear Technology web site (http://www.linear.com) for data sheet and application notes for regulators such as LT1117, LT1121, or other 3.3-V regulars.

# 2.3 Summary

The proceeding information highlights a means to enable the use of 3.3-V flash in a 5-V systems design. This information addresses two critical systems-level areas: the I/O signal requirements and the flash  $V_{CC}$  power regulation requirements. There were detailed examples of interface and  $V_{CC}$  regulation devices to facilitate the use of 3-V Flash in a 5-V system design.

Please consult your device data sheet to ensure your flash software will adhere to the specified requirements. If you have further questions about using Cypress flash devices, contact Cypress support.

# **Document History Page**

| Document Title: AN98559 - Integrating 3-V Flash in 5-V Systems Document Number: 001-98559 |         |                    |                    |                             |

|-------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-----------------------------|

| Rev.                                                                                      | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change       |

| **                                                                                        | -       | _                  | 10/13/2010         | Initial version             |

| *A                                                                                        | 4958961 | MSWI               | 10/12/2015         | Updated in Cypress template |

| *B                                                                                        | 5870037 | AESATMP8           | 09/01/2017         | Updated logo and Copyright. |

# **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

## PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2010-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1s) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.