# AN98507

# **Connecting Cypress SPI Serial Flash to Configure Xilinx FPGAs**

## Author: Kuwano, Takahiro Associated Part Family: Serial NOR Flash Memory

AN98507 describes compatibility information between Cypress SPI flash and Xilinx FPGAs, SPI flash basics, and considerations required in some cases.

## 1 Introduction

Xilinx FPGAs are programmable logic devices used for basic logic functions, chip-to-chip connectivity, signal processing, and embedded processing. These devices are programmed and configured using an array of SRAM cells that need to be re-programmed on every power-up. Several different methods of configuring FPGAs are normally used. They include programming by a microprocessor, JTAG port, or directly by a serial PROM or flash. Cypress' Serial Peripheral Interface (SPI) flash can be easily connected to Xilinx FPGAs to configure the FPGA at power up. The readers of this application note are expected to understand the basics of Xilinx FPGA configuration using SPI flash, by reading user guides and application notes from Xilinx listed in Related Documents. This document intends to be a supplement for the Xilinx documents by covering specific topics for Cypress SPI flash.

## 2 SPI Basics

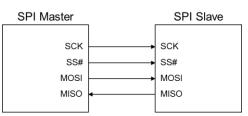

Serial Peripheral Interface (SPI) is a simple 4-wire synchronous interface protocol that enables a master device and one or more slave devices to communicate. The SPI bus consists of four signal wires:

- Master Out Slave In (MOSI) signal generated by the master (data to slave)

- Master In Slave Out (MISO) signal generated by the slave (data to master)

- Serial Clock (SCK) signal generated by the master to synchronize data transfers

- Slave Select (SS#) signal generated by master to select individual slave devices, also known as Chip Select (CS#) or Chip Enable (CE#)

Figure 1 shows the connection between a SPI Master and a SPI Slave.

Figure 1. SPI Master and SPI Slave Connection

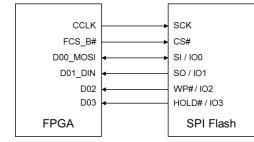

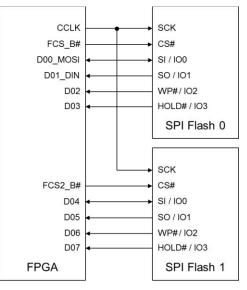

In addition to the basic x1 data width mode above, Cypress SPI flash and the Xilinx FPGAs support x2 and x4 data width mode. In the x2 data width mode, the MOSI signal becomes bidirectional. In the x4 data width mode the additional two pins are used for data transfer. Furthermore, the Xilinx UltraScale and UltraScale+ FPGAs supports the Dual x4 mode, which (=x8) uses two SPI flash devices in parallel.

# 3 SPI Flash Connections to FPGAs

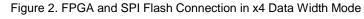

Figure 2 and Figure 3 show the FPGA-to-SPI-Flash connection in x4 and Dual x4 data width mode. The pin names and functions are explained in Table 1.

| Table 1. FPGA and SPI Flash Pins |

|----------------------------------|

|----------------------------------|

| FPGA Pin Name     | SPI Flash Pin Name | Description                                                      |

|-------------------|--------------------|------------------------------------------------------------------|

| CCLK              | SCK                | Serial Clock                                                     |

| FCS_B#<br>FCS2_B# | CS#                | Chip Select                                                      |

| D00_MODI<br>D04   | SI / IO0           | Serial Input in x1 mode<br>IO0 in x2 and x4 mode                 |

| D01_DIN<br>D05    | SO / IO1           | Serial Output in x1 mode<br>IO1 in x2 and x4 mode                |

| D02<br>D06        | WP# / IO2          | Write Protect in x1 and x2 mode<br>IO2 in x4 mode                |

| D03<br>D07        | HOLD# / IO3        | Hold (pause) serial transfer in x1 and x2 mode<br>IO3 in x4 mode |

During FPGA configuration process, the FPGA reads the configuration bitstream from SPI flash by issuing read commands. There are some variations of read command depending on the data width and addressing. Table 2 shows the read commands used by the Xilinx FPGAs. Cypress S25FL-L and S25FL-S 3.0V SPI flash families (listed in Table 3) support all commands. The Cypress S25FS-S 1.8V SPI flash family does not support DOR(3Bh), 4DOR(3Ch), QOR(6Bh), and 4QOR(6Ch).

| SPI Command Name<br>(in Xilinx Documents) | SPI Command Name<br>(in Cypress Datasheets) | Opcode |

|-------------------------------------------|---------------------------------------------|--------|

| Fast read                                 | FAST_READ                                   | 0Bh    |

| Fast read, 32-bit address                 | 4FAST_READ                                  | 0Ch    |

| Dual output fast read                     | DOR                                         | 3Bh    |

| Dual output fast read, 32-bit address     | 4DOR                                        | 3Ch    |

| Quad output fast read                     | QOR                                         | 6Bh    |

| Quad output fast read, 32-bit address     | 4QOR                                        | 6Ch    |

| Table 2. Read | Commands | Used for | FPGA  | Configuration |

|---------------|----------|----------|-------|---------------|

|               | Communus | 0300101  | 110/1 | Configuration |

# 4 Considerations for Selecting Cypress SPI Flash

#### 4.1 Supported Cypress SPI Flash for Xilinx FPGAs

Table 3 shows the supported Cypress SPI flash for Xilinx FPGA families. The table is based on supported devices listed in the Vivado Design Suite User Guide: Programming and Debugging (UG908) and ISE Help, excluding the SPI flash families not recommended for new designs (i.e., S25FL1-K and S25FL-P). The following sections describes the considerations for selecting one of Cypress SPI flash.

|                        | Cypress SPI Flash      |                |                        |                                                  |                                     |                        |           |

|------------------------|------------------------|----------------|------------------------|--------------------------------------------------|-------------------------------------|------------------------|-----------|

| FPGA Family            | IO Voltages            | SPI Modes      | S25FL064L <sup>1</sup> | S25FL128L <sup>1</sup><br>S25FL256L <sup>1</sup> | S25FL127S <sup>1</sup><br>S25FL128S | S25FL256S<br>S25FL512S | S70FL01GS |

| Artix-7                | 3.3V, 2.5V, 1.8V, 1.5V | x1, x2, x4     | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Kintex-7               | 3.3V, 2.5V, 1.8V, 1.5V | x1, x2, x4     | ~                      | ✓                                                | ~                                   | ~                      |           |

| Spartan-7              | 3.3V, 2.5V, 1.8V, 1.5V | x1, x2, x4     | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Virtex-7               | 1.8V, 1.5V             | x1, x2, x4     |                        |                                                  | ~                                   | ~                      |           |

| Kintex UltraScale      | 3.3V, 2.5V, 1.8V, 1.5V | x1, x2, x4, x8 | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Kintex UltraScale+     | 1.8V, 1.5V             | x1, x2, x4, x8 | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Virtex UltraScale      | 3.3V, 2.5V, 1.8V, 1.5V | x1, x2, x4, x8 | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Virtex UltraScale+     | 1.8V, 1.5V             | x1, x2, x4, x8 | ✓                      | ✓                                                | ~                                   | ~                      |           |

| Zynq-7000              | 3.3V, 1.8V             | x1, x2, x4, x8 | ✓                      |                                                  | ~                                   | ~                      | ✓         |

| Zynq UltraScale+ MPSoC | 3.3V, 1.8V             | x1, x2, x4, x8 |                        |                                                  | ~                                   | ✓                      | ✓         |

| Zynq UltraScale+ RFSoC | 3.3V, 1.8V             | x1, x2, x4, x8 |                        |                                                  | ~                                   | ~                      | ✓         |

| Spartan-6              | 3.3V                   | x1, x2, x4     | √2                     | √2                                               | √2                                  |                        |           |

Table 3. Supported Cypress SPI Flash for Xilinx FPGAs

Note: 1. S25FL064L, S25FL128L, and S25FL127S do not have the V<sub>IO</sub> option. A level shifter is needed if the I/O voltage of the FPGA is not 3.3 V.

Note: 2. S25FLxxP is listed in the table at Xilinx ISE Help; however, the S25FLxxP is not recommended for new designs. S25FL-L and S25FL-S families are compatible with the S25FL-P family and known to work. See KBA219147 and AN98577 for details.

## 4.2 I/O Voltage of Configuration Interface

The I/O voltage compatibility needs to be considered to select Cypress SPI flash for Xilinx FPGA configuration. As shown in Table 3, some of Xilinx FPGA families support only 1.8 V or 1.5 V for the configuration I/O voltage. All SPI flash families listed in Table 3 require 3.3 V for the core voltage (V<sub>CC</sub>). For some Cypress SPI flash families, there is an ordering option that can accept 1.8 V at the I/O voltage (V<sub>IO</sub>) pin, which is separated from the core voltage (V<sub>CC</sub>). S25FL128S, S25FL256S, S25FL152S, and S70FL01GS have the V<sub>IO</sub> option. Note that the SPI flash with the V<sub>IO</sub> option requires a higher t<sub>V</sub> (Clock Low to Output Valid) value that impacts the configuration performance (see Table 4). If the application requires higher configuration speed, it is recommended to use a part without the V<sub>IO</sub> option, and with a level shifter. Cypress offers the S25FS-S SPI flash family which operates at 1.8-V core voltage (V<sub>CC</sub>); however, the S25FS-S family does not support read commands used for x2 and x4 data width mode.

#### 4.3 Quad Output Read Support

In the master SPI configuration mode, Xilinx FPGAs can read from the SPI flash with x4 data width. It is called Quad Output Read in Cypress SPI flash. All Cypress SPI flash families listed in Table 3 support Quad Output Read; however, the option is not enabled by default. To enable it, the Quad Enable Bit in the Flash internal configuration register must be set (see Cypress SPI flash datasheets for details).

Xilinx's in-system Flash programming tools (Vivado or iMPACT) set the Quad Enable Bit when programming the FPGA configuration bitstream to Cypress SPI flash. If third-party Flash programmers are used for programming the FPGA configuration bitstream to the SPI flash before mounting it to PCB, the programmers must set the Quad Enable Bit.

## 4.4 Maximum Configuration Clock Frequency

XAPP586 and XAPP1233 use Equation 1 to determine the maximum configuration clock frequency and provide calculation examples.

$$F_{CCLK,MAX} \le \frac{1}{(T_{SPITCO} + T_{SPIDCC} + T_{TPD})}$$

Equation 1

In the calculation, a timing parameter,  $T_{SPITCO}$  is defined as the flash clock to out or SPI clock Low to Output Valid, which is represented by a symbol,  $t_V$  (Clock Low to Output Valid) in Cypress SPI flash datasheets. Table 4 shows the maximum  $t_V$  values of Cypress SPI flash families in several conditions. A lower  $t_V$  value results in a higher clock frequency. The other two parameters,  $T_{SPIDCC}$  and  $T_{TPD}$ , rely on the FPGA and PCB characteristics. Note that the  $t_V$  value increases if the SPI flash has the  $V_{IO}$  option and the  $V_{IO}$  range is lower than  $V_{CC}$ .

| Symbol | Conditions            |                       |       | S25FL064L | S25FL127S | S25FL128S<br>S25FL256S |

|--------|-----------------------|-----------------------|-------|-----------|-----------|------------------------|

|        | V <sub>cc</sub> Range | V <sub>IO</sub> Range | CL    | S25FL128L | 323FE1273 | S25FL512S              |

|        | 2.7 – 3.6 V           | = V <sub>CC</sub>     | 30 pF | 8.00 ns   | 8.00 ns   | 8.00 ns                |

| tv     | 2.7 – 3.6 V           | $= V_{CC}$            | 15 pF | 6.00 ns   | -         | -                      |

|        | 3.0 – 3.6 V           | $= V_{CC}$            | 30 pF | -         | 7.65 ns   | 7.65 ns                |

|        | 3.0 – 3.6 V           | $= V_{CC}$            | 15 pF | -         | 6.50 ns   | 6.50 ns                |

|        | 2.7 – 3.6 V           | 1.65 – 2.7 V          | 30 pF | -         | -         | 14.5 ns                |

|        | 2.7 – 3.6 V           | 1.65 – 2.7 V          | 15 pF | -         | -         | 12.0 ns                |

Table 4. Maximum tv (Clock Low to Output Valid)

The F<sub>CCLK.MAX</sub> value when T<sub>SPITCO</sub> = 6.0 ns (S25FL064L with 15-pF load), T<sub>SPIDCC</sub> = 3.0 ns, and T<sub>TPD</sub> = 2.0 ns is 90.9 MHz, for example. This value is within the maximum clock frequency (104 MHz) for read operation in S25FL064L.

## 4.5 **Power-On Sequence Precautions**

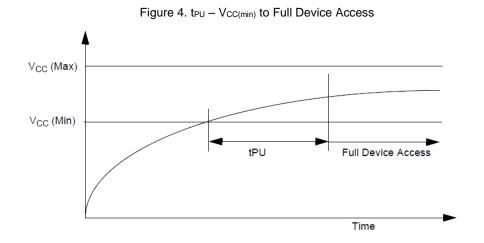

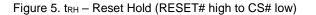

At power on, the FPGA automatically starts its configuration procedure by reading the configuration Bitstream from the SPI flash; therefore, the SPI flash used for FPGA configuration must be ready to respond to the read command. The time between power ramp to configuration start is defined as  $T_{POR}$  in Xilinx FPGA datasheets, which is 10 ms (7 series FPGA) and 5 ms (UltraScale FPGA) at minimum. In Cypress SPI flash, a timing parameter  $t_{PU}$  is defined as shown in Table 5 and Figure 4. Because  $t_{PU}$  is an order of magnitude less than  $T_{POR}$ , the SPI flash becomes ready before the FPGA issues the read command if the same power rail supplies both FPGA and SPI flash. If not, a countermeasure may be needed. In addition, if the selected Cypress SPI flash has the RESET# signal and RESET# remains LOW at  $t_{PU}$  end, you must ensure that CS# remain HIGH for a period of  $t_{RH}$  after RESET# returns HIGH (Figure 5)

| Symbol               | Conditions                                 | S25FLxxxL | S25FLxxxS |

|----------------------|--------------------------------------------|-----------|-----------|

| V <sub>CC(min)</sub> | Minimum operation voltage                  | 2.7 V     | 2.7 V     |

| t <sub>PU</sub>      | V <sub>CC(min)</sub> to Full Device Access | 300 µs    | 300 µs    |

| t <sub>RH</sub>      | Reset Hold (RESET# HIGH to CS# LOW)        | 150 ns    | 50 ns     |

#### Table 5. Power On Timing

# 5 Related Documents

| Cypress Datasheets                                                                           |  |

|----------------------------------------------------------------------------------------------|--|

| S25FL064L, 64-Mbit (8-Mbyte) 3.0 V FL-L SPI Flash Memory Datasheet                           |  |

| S25FL256L/S25FL128L, 256-MB (32-MB)/128-MB (16-MB), 3.0 V Flash Memory Datasheet             |  |

| S25FL127S, 128 Mbit (16 Mbyte) 3.0V SPI Flash Memory Datasheet                               |  |

| S25FL128S/S25FL256S, 128 Mbit (16 Mbyte)/256 Mbit (32 Mbyte) 3.0V SPI Flash Memory Datasheet |  |

| S25FL512S, 512 Mbit (64 Mbyte) 3.0V SPI Flash Memory Datasheet                               |  |

| S70FL01GS, 1 Gbit (128 Mbyte) 3.0V SPI Flash Memory Datasheet                                |  |

| Cypress Application Notes                                                                    |  |

| AN98577 – Migration from FL-P to FL-S Family SPI Interface Flash Memories                    |  |

| AN217010 – Migrating from S25FL1-K Serial NOR Flash to S25FL064L Serial NOR Flash            |  |

| Cypress Knowledge Base Articles                                                              |  |

| Using Cypress S25FL-L SPI Flash with Xilinx Spartan-6 FPGA - KBA219147                       |  |

| Xilinx User Guides / Application Notes                                                       |  |

| 7 Series FPGAs Configuration User Guide (UG470)                                              |  |

| UltraScale Architecture Configuration User Guide (UG570)                                     |  |

| Vivado Design Suite User Guide: Programming and Debugging (UG908)                            |  |

| Using SPI Flash with 7 Series FPGAs Application Note (XAPP586)                               |  |

| SPI Configuration and Flash Programming in UltraScale FPGAs Application Note (XAPP1233)      |  |

# **Document History**

Document Title: AN98507 - Connecting Cypress SPI Serial Flash to Configure Xilinx FPGAs

Document Number: 001-98507

| Revision | ECN     | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | -       | 10/25/2007         | New Application Note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *A       | -       | 03/03/2008         | Updated Figures 3.1 and 3.2<br>Added section 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *В       | _       | 03/31/2011         | Introduction: Added Spartan-6, Virtex-6<br>Updated section<br>SPI Flash Connections to FPGAs:<br>Added DOUT to table: Pin Descriptions for FPGA Configuration from SPI Flash<br>Updated table: SPI Flash Selection for Spartan Family FPGA Devices<br>Updated table: SPI Flash Selection for Virtex-5 Family FPGA Devices<br>Added table: SPI Flash Selection for Virtex-6 Family FPGA Devices<br>Added table: SPI Flash Selection for Virtex-6 Family FPGA Devices<br>Added table: SPI Flash Selection for Virtex-6 Family FPGA Devices<br>Added figure: Spartan-6 serial (x1, x2, x4) Configuration from Cypress S25FL-P<br>and<br>S25FL-K SPI Quad I/O Serial Flash Connection Diagram<br>Direct Programming SPI Flash:<br>Updated section<br>Using Cypress S25FL 3V SPI Flash with Virtex-6:<br>Added section<br>References:<br>Added references |

| °C       | 4909568 | 09/05/2015         | Added Table 1, Table 2, Table 3<br>Updated Table 1<br>Replaced detailed descriptions of Xilinx products with links to relevant Xilinx<br>application notes<br>Updated 4 Applying Voltages at Power-On<br>Updated Figure 4<br>Removed sections Direct Programming SPI Flash and Fastest Configuration<br>Time<br>Updated links in 5 References<br>Updated in Cypress template                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *D       | 5790701 | 07/05/2017         | Updated logo and copyright.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *E       | 6158274 | 04/27/2018         | Updated the content to align the latest Flash/FPGA.<br>Updated template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *F       | 6891182 | 06/02/2020         | Updated Table 3<br>Updated links in Related Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

#### **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Code Examples | Projects | Videos | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor An Infineon Technologies Company 198 Champion Court San Jose, CA 95134-1709 www.cypress.com www.infineon.com

© Cypress Semiconductor Corporation, 2007-2020. This document is the property of Cypress Semiconductor Corporation and its subsidiaries ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress' patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any use of a Cypress product as a Critical Component in a High-Risk Device. You shall indemnify and hold Cypress, its directors, officers, employees, agents, affiliates, distributors, and assigns harmless from and against all claims, costs, damages, and expenses, arising out of any claim, including claims for product liability, personal injury or death, or property damage arising from any use of a Cypress product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any High-Risk Device except to the limited extent that (i) Cypress's published data sheet for the product explicitly states Cypress has qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to use the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.