#### **About this document**

#### **Scope and purpose**

AN86439 explains how to effectively use PSoC<sup>™</sup> 4 MCU GPIO pins, with various use case examples to demonstrate their features. Major topics in this application note include GPIO basics, configuration options, mixed-signal use, interrupts, and low-power behavior.

#### **Intended audience**

This document is intended for anyone who uses the PSoC™ 4 MCU GPIO pins.

#### Table of contents

# **Table of contents**

| Abou  | ıt this document                                              | 1  |

|-------|---------------------------------------------------------------|----|

| Table | e of contents                                                 | 2  |

| L     | Introduction                                                  | 4  |

| 2     | PSoC™ Creator                                                 | 5  |

| 2.1   | PSoC™ Creator code examples                                   |    |

| 2.1.1 | !                                                             |    |

| 2.2   | ModusToolbox™ software                                        |    |

| 2.2.1 |                                                               |    |

| 2.3   | Technical support                                             |    |

| 3     | GPIO pin basics                                               | 9  |

| 3.1   | Physical structure of GPIO pins                               |    |

| 3.2   | Pin routing                                                   |    |

| 3.2.1 | Digital routing                                               |    |

| 3.2.2 |                                                               |    |

| 3.3   | Startup and low-power behavior                                |    |

| 3.4   | GPIO interrupt                                                |    |

| 3.4.1 | Limitations in GPIO interrupt                                 | 25 |

| 4     | Overvoltage-tolerant (OVT) pins                               | 26 |

| 5     | GPIO pins in PSoC™ Creator                                    |    |

| 5.1   | Pins Component symbols                                        |    |

| 5.2   | Pins component customizer                                     |    |

| 5.3   | Pins component interrupts                                     |    |

| 5.4   | Manual pin assignments                                        |    |

| 5.5   | PSoC™ Creator APIs                                            |    |

| 5.6   | Debug logic on GPIO pins                                      |    |

| 5.7   | Add multiple GPIO pins as a logical port                      |    |

| 5.8   | Represent Off-chip components                                 |    |

| 6     | GPIO pins in ModusToolbox™ software                           |    |

| 6.1   | Configuring GPIO pins using ModusToolbox™ Device Configurator |    |

| 6.1.1 | Using the Device Configurator                                 |    |

| 5.1.2 |                                                               |    |

| 6.2   | GPIO using the peripheral driver library (PDL)                |    |

| 6.2.1 |                                                               |    |

| 5.2.2 | GPIO pin initialization- fast                                 | 45 |

| 5.2.3 | GPIO port initialization                                      | 46 |

| 5.2.4 | Reading from a GPIO pin                                       | 46 |

| 6.2.5 | Writing to a GPIO pin                                         | 46 |

| 6.2.6 | GPIO interrupt                                                | 47 |

| 7     | GPIO tips and tricks in PSoC™ Creator                         | 48 |

| 7.1   | Toggle an LED                                                 |    |

| 7.2   | Read an input and write to an output                          | 50 |

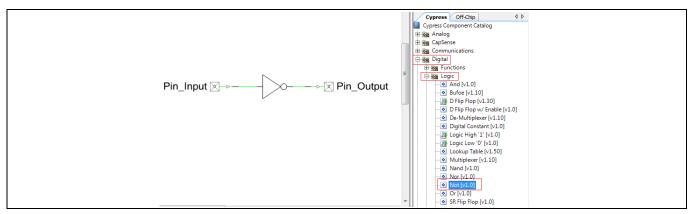

| 7.3   | Drive an output from a digital logic gate                     | 50 |

| 7.4   | Using a bidirectional pin                                     | 51 |

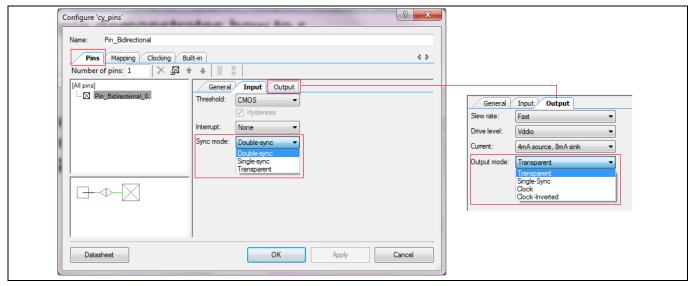

| 7.5   | Set the GPIO input/output synchronization                     | 53 |

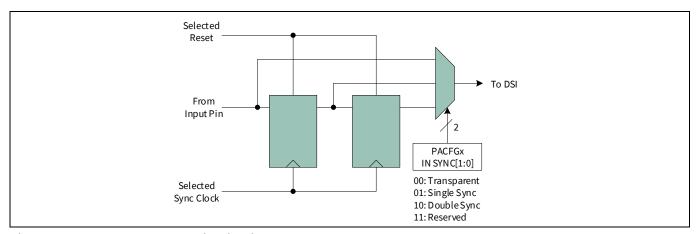

| 7.5.1 | GPIO input synchronization                                    | 55 |

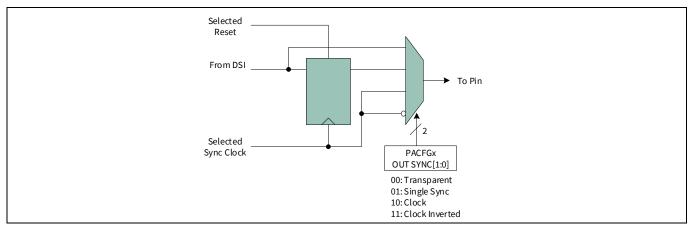

| 7.5.2 | GPIO output synchronization                                   | 57 |

## Table of contents

| 7.6  | Toggle GPIOs faster with Data registers                                                                       | 58 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 7.7  | Configure GPIO output enable logic                                                                            | 61 |

| 7.8  | Pin interrupt                                                                                                 | 63 |

| 7.9  | Configure GPIO interrupt settings with firmware                                                               | 66 |

| 7.10 | ·                                                                                                             |    |

| 7.11 | Gang pins for more drive/sink current                                                                         |    |

| 7.12 | · · · · · · · · · · · · · · · · · · ·                                                                         |    |

| 8    | GPIO tips and tricks in ModusToolbox™ software                                                                | 78 |

| 8.1  | Read an input and write to an output                                                                          |    |

| 8.2  | Pin interrupt                                                                                                 |    |

| 8.3  | More code examples                                                                                            |    |

| 9    | Related application notes                                                                                     | 79 |

| 10   | PSoC <sup>™</sup> 4 GPIO compared to PSoC <sup>™</sup> 1, PSoC <sup>™</sup> 3, and PSoC <sup>™</sup> 5LP GPIO | 80 |

| 11   | PSoC™ 4 development boards                                                                                    | 81 |

| Refe | rences                                                                                                        |    |

|      | sion history                                                                                                  |    |

|      | laimer                                                                                                        | 84 |

|      |                                                                                                               |    |

Introduction

#### 1 Introduction

PSoC<sup>™</sup> has a flexible general-purpose I/O (GPIO) architecture that provides more features than traditional MCUs. PSoC<sup>™</sup> GPIOs are controlled not only by configuring the registers in firmware, similar to traditional MCUs, but are also driven by custom digital logic and analog block signals. This application note explains the basics of PSoC<sup>™</sup> 4 GPIO pins and shows techniques for using them effectively for different functions.

This application note assumes that you are familiar with PSoC™ Creator or ModusToolbox™ and the PSoC™ 4 architecture. If you are new to PSoC™ 4, read AN79953 – Getting started with PSoC™ 4 MCU. If you are new to PSoC™ Creator, visit the PSoC™ Creator. If you are new to ModusToolbox™, visit the ModusToolbox™ software. For information on device packages or GPIO specifications, see the PSoC™ 4 datasheet. If you are already familiar with the device and development environments, you can jump to the GPIO tips and tricks in PSoC™ Creator or ModusToolbox™ software GPIO tips and tricks section.

This application note describes how to use the PSoC<sup>™</sup> peripheral driver library (PDL) and ModusToolbox<sup>™</sup> to develop with PSoC<sup>™</sup> 4 devices. This is currently supported only when using PSoC<sup>™</sup> 4 S-series devices.

Note: References to 'PSoC™' or 'device' henceforth refer to PSoC™ 4, unless specified otherwise.

**PSoC™** Creator

### 2 PSoC<sup>™</sup> Creator

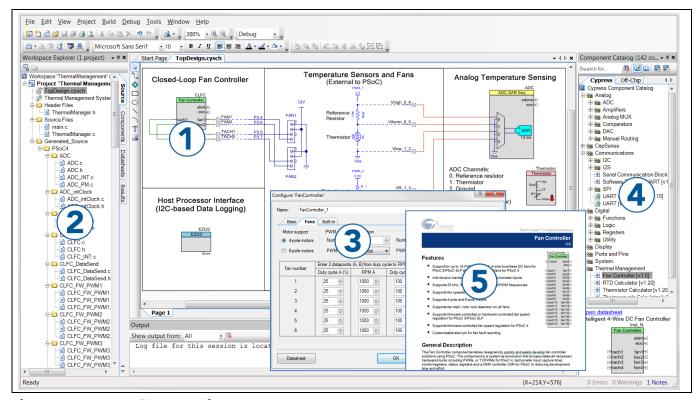

PSoC<sup>™</sup> Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of systems based on PSoC<sup>™</sup> 3, PSoC<sup>™</sup> 4, and PSoC<sup>™</sup> 5LP(see Figure 1).

- 1. Drag and drop Components to build your hardware system design in the main design workspace

- 2. Codesign your application firmware with the PSoC™ hardware

- 3. Configure Components using configuration tools

- 4. Explore the library of 100+ Components

- 5. Review Component datasheets

Figure 1 PSoC™ Creator features

# 2.1 PSoC™ Creator code examples

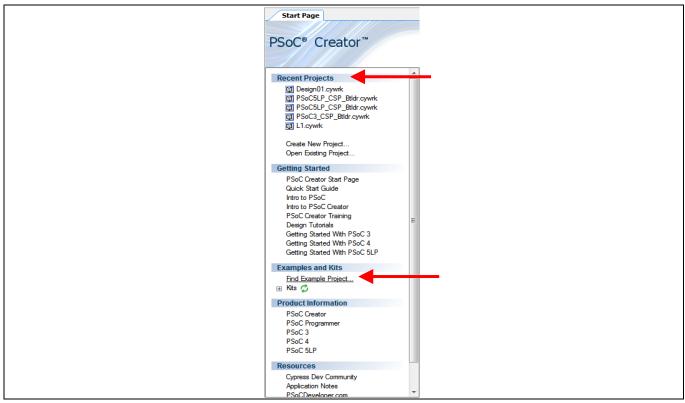

PSoC<sup>™</sup> Creator includes a large number of code example projects. These projects are available from the PSoC<sup>™</sup> Creator start page, as shown in Figure 2. PSoC<sup>™</sup> Creator code examples can also be downloaded from infineon.com.

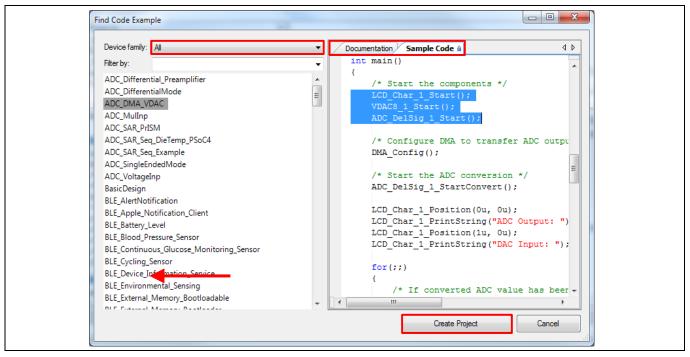

Example projects can speed up your design process by starting you off with a complete design, instead of a blank page. The example projects also show how you can use PSoC<sup>™</sup> Creator components for various applications. The code examples and datasheets are included, as shown in Figure 3.

In the Find Code Example Project dialog shown in Figure 3, you have several options:

- Filter for examples based on device family (such as PSoC™ 3, PSoC™ 4, or PSoC™ 5LP); category; or keyword

- Select from the menu of examples offered based on the **Filter** options

- Review the datasheet for the selection (on the **Documentation** tab)

#### **PSoC™** Creator

Review the code example for the selection. You can copy and paste code from this window to your project, which can help speed up code development, or

Create a new project (and a new workspace, if needed) based on the selection. This can speed up your design process by starting you off with a complete, basic design. You can then adapt that design to your application.

Figure 2 Code examples in PSoC™ Creator

Figure 3 Code example projects with sample code

infineon

**PSoC™** Creator

### 2.1.1 PSoC™ Creator help

Visit the PSoC™ Creator to download the latest version of PSoC™ Creator. Then, launch PSoC™ Creator and navigate to the following items:

- Quick start guide: Choose Help > Documentation > Quick Start Guide. This guide gives you the basics for developing PSoC™ Creator projects.

- System reference guide: Choose Help > System Reference Guides. This guide lists and describes the system functions provided by PSoC™ Creator.

- **Component datasheets**: Right-click a component and select "Open Datasheet." Visit the PSoC<sup>™</sup> 4 component datasheets page for a list of all PSoC<sup>™</sup> 4 Component datasheets.

- **Document manager**: PSoC<sup>™</sup> Creator provides a document manager to help you to easily find and review document resources. To open the document manager, choose the menu item **Help** > **Document Manager**.

#### 2.2 ModusToolbox™ software

ModusToolbox™ is a set of multi-platform development tools and a comprehensive suite of GitHub-hosted firmware libraries. Together, they enable an immersive development experience for customers creating converged MCU and wireless systems.

The firmware libraries comprise easily customizable board support packages (BSP) for Infineon PSoC™ 6 MCU, PSoC™ 4, and Bluetooth® SoC (20xxx) kits and a comprehensive set of middleware libraries enabling industry-leading features:

- CAPSENSE™

- Bluetooth® Low Energy and Mesh

- Lowest-power, most reliable Wi-Fi on the market

- Impressive set of thoroughly tested and helpful code example applications

Visit the ModusToolbox™ software to download the latest version of ModusToolbox™. The following are helpful items for getting started with ModusToolbox™:

- Quick start guide: This is a short step-by-step guide specifically for using the Eclipse-based IDE to create and build applications for ModusToolbox™.

- ModusToolbox<sup>™</sup> tools package user guide: This guide focuses on the Eclipse IDE, covering more details about the IDE and software features.

- Documentation: Refer to Quick Panel section in ModusToolbox™ IDE user guide.

Note: ModusToolbox™ is compatible with KitProg3 and MiniProg4 (CY8CKIT-005-A) programming devices.

# 2.2.1 ModusToolbox<sup>™</sup> code examples

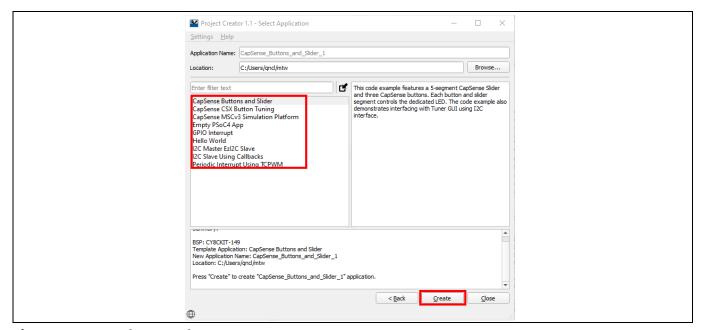

ModusToolbox<sup>™</sup> includes a growing number of code example projects. These code example projects are available in the new application wizard in ModusToolbox<sup>™</sup> or Infineon GitHub.

Example projects can speed up your design process by starting you off with a complete design instead of a blank page.

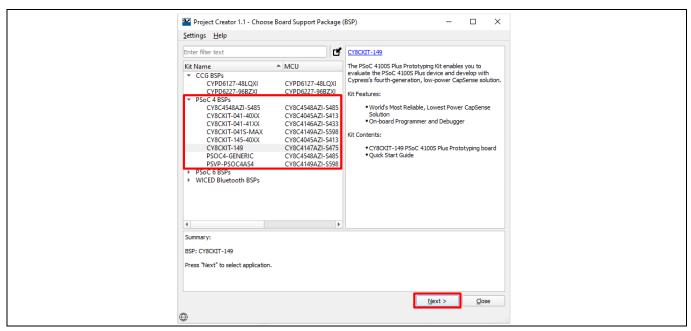

#### **PSoC™** Creator

In the New Application Wizard, as Figure 4 shows, you can choose your board support package (BSP). The BSP corresponds to the specific kit that is being used. The code examples can be viewed when a BSP is chosen, as shown in Figure 5.

Figure 4 New application wizard

Figure 5 Code examples

### 2.3 Technical support

For further assistance and clarification, create a support request on the Infineon technical support page.

Use the support resources Self-help, for quick assistance

**GPIO** pin basics

# **3 GPIO** pin basics

The PSoC™ GPIO pins offer the following features:

- Analog and digital input and output capability

- LCD segment drive support (not available in PSoC<sup>™</sup> 4000 and PSoC<sup>™</sup> 4200DS)

- CAPSENSE™ support

- Interrupt on level, rising-edge, falling-edge, or both edges

- Slew-rate control

- Input threshold select (CMOS / LVTTL)

- Overvoltage-tolerant pins (available only in PSoC<sup>™</sup> 4 Bluetooth® LE, PSoC<sup>™</sup> 4 M-Series, and PSoC<sup>™</sup> 4 L-Series) with hot-swap capability

The GPIO functionality depends on the peripherals available in the PSoC<sup>™</sup> 4 device. For a side-by-side comparison of the features available in different PSoC<sup>™</sup> 4 families, see Table1 in AN79953 – Getting started with PSoC<sup>™</sup> 4 MCU.

#### 3.1 Physical structure of GPIO pins

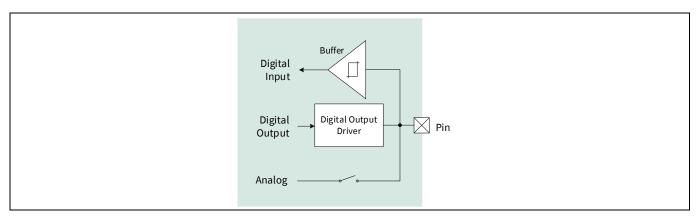

Figure 6 shows the pin connections with the resources in the PSoC<sup>™</sup> device.

Figure 6 Simplified GPIO block diagram

A detailed block diagram of the GPIO structure is available in the "I/O System" chapter of the PSoC™ 4 architecture reference manual. Each pin can act as an input or an output to the CPU and the digital peripheral such as the Timer, PWM, or I²C. It can also act as an analog pin for use with opamps and ADC. At any given time, you can use a pin for only-digital input, only-digital output, only-analog, or even combinations of these three. For example, if you enable both digital output and input, it provides a digital bidirectional pin. The input buffer provides high impedance to the external input. It is configurable to CMOS, LVTTL.

For the input threshold values, see the device datasheet.

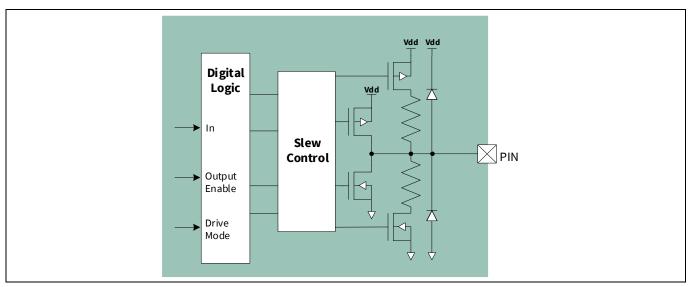

The digital output driver supports different drive modes and slew-rate control (see Figure 7).

#### **GPIO** pin basics

Figure 7 Digital output driver

Slew-rate control is provided to reduce EMI and cross-talk. There are two options – Fast and Slow. Slew rate is set to Fast by default. Use the Slow option when the signals are not speed-critical.

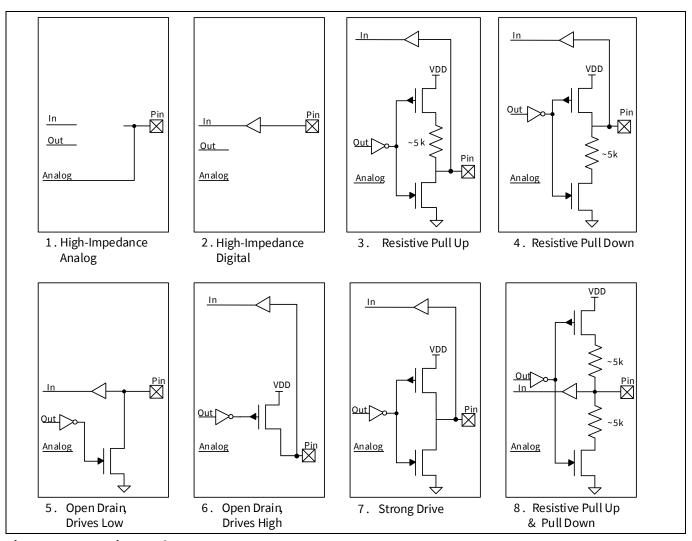

The circuit shown in Figure 7 supports eight drive modes, as listed in Table 1.

Table 1 **Drive modes and applications**

| # | Drive mode                                        | Application examples                                                                                                                                                                                   |

|---|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | High-impedance (High-Z) analog                    | Analog input/output                                                                                                                                                                                    |

| 2 | High-impedance (HIGH-Z) digital                   | Digital input                                                                                                                                                                                          |

| 3 | Resistive pull-up (~5 kΩ)                         | Interface to open-drain LOW input, such as the tachometer output from motors or a switch connected to ground. It can also be used to drive LEDs.                                                       |

| 4 | Resistive pull-down (~5 kΩ)                       | Interface to an open-drain HIGH input or a switch connected to VDD.  It can be used as an output to interface LEDs in current-sink mode.                                                               |

| 5 | Open drain, drives LOW                            | Provides high impedance in the HIGH state and a strong drive in the LOW state; this configuration is used for I <sup>2</sup> C pins. This mode works in conjunction with an external pull-up resistor. |

| 6 | Open drain, drives HIGH                           | Provides strong drive in the HIGH state and high impedance in the LOW state. This mode works in conjunction with an external pull-down resistor.                                                       |

| 7 | Strong drive                                      | CMOS output drive in both LOW and HIGH states                                                                                                                                                          |

| 8 | Resistive pull-up and resistive pull-down (~5 kΩ) | Adds a series resistor in both HIGH and LOW states                                                                                                                                                     |

#### **GPIO** pin basics

Figure 8 **Drive modes**

Note:

The resistor values for pull-up and pull-down drive modes, shown in Figure 8, are approximate values; see the device datasheet for resistor value specifications. Use an external resistor if a higher accuracy is required. In this case, the pin must be configured as Open Drain Drive High or Open Drain Drive Low.

Note:

At all times, avoid the device VDD getting powered from an external voltage at the pin through ESD clamp diodes. This can happen if the PSoC™ 4 device is not powered and an external voltage is applied at the GPIO or when an external voltage at the GPIO is greater than the device VDD. This is, however, not applicable to the Overvoltage-tolerant (OVT) pins as there are no clamp diodes.

**GPIO** pin basics

## 3.2 Pin routing

### 3.2.1 Digital routing

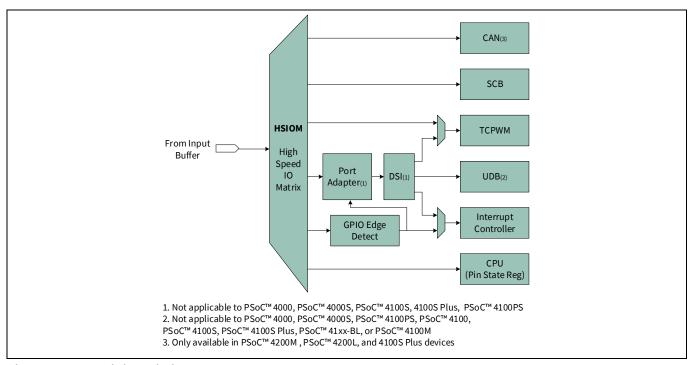

A pin can be routed to different digital peripherals, such as universal digital block (UDB), Serial Communication Block (SCB), Timer/Counter/Pulse-Width Modulator (TCPWM) block, LCD driver, CAN block, and interrupt controller; as well as the data register which is read/written by the CPU. Figure 9 shows the routing for an input pin and Figure 10 shows the routing for an output pin. As shown in these figures, peripherals are connected to the pins using the high-speed I/O matrix (HSIOM). It multiplexes the signals from different peripherals to connect to a particular pin.

In PSoC<sup>™</sup>, there are two routing possibilities: dedicated I/O routed through the HSIOM, and flexible routing using digital system interconnect (DSI). DSI usage is not limited to routing the peripheral inputs and outputs to pins; it is also used to route signals between digital resources. The Port Adapter connects the HSIOM and the DSI. It also provides hardware to synchronize pin input and output signals.

Figure 9 Digital pin input path

SCB (I<sup>2</sup>C, UART, and SPI) and TCPWM have dedicated routes to some I/Os. The flexible routing option is available for UDB inputs and outputs, generating interrupts from the pins, and even for TCPWM. The LCD driver is present in all I/Os of the PSoC<sup>™</sup> parts (except PSoC<sup>™</sup> 4000 and PSoC<sup>™</sup> 4200DS), with any I/O acting as a segment or a common driver for the LCD.

The GPIO Edge Detect block enables pin interrupts on rising-edge, falling-edge, and both edges. See the GPIO interrupt section for details.

#### **GPIO** pin basics

Figure 10 Digital pin output path

Note:

PSoC<sup>™</sup> 4 has multiple ports with a maximum of 8 pins per port. For PSoC<sup>™</sup> 4200L devices, Ports 7, 8, and 9 pins do not have the port adapter; for other devices, Port 4 and higher ports do not have the port adapter. These ports have the following restrictions:

- Cannot be routed through the DSI; thus UDB-based digital signals cannot be routed to the pins of these

- Cannot be used for analog blocks such as SAR ADC, Opamp Continuous Time Block mini (CTBm), Low-Power Comparator (applicable only to PSoC™ 4100, PSoC™ 4100PS, and PSoC™ 4200), and Continuous Time Block (applicable only to PSoC<sup>™</sup> 4100PS)

- No input/output synchronization

However, these ports are useful in the following ways:

- As a GPIO controlled in firmware

- Direct connection to TCPWM, SCB, or CAN

- LCD and CAPSESNE™ pins

- Interrupt generation

Note:

Pins of the PSoC<sup>™</sup> device are shared for dedicated connections to different peripherals. To know the functions possible at each pin, see the "Pinouts" section in the respective device datasheets.

**GPIO** pin basics

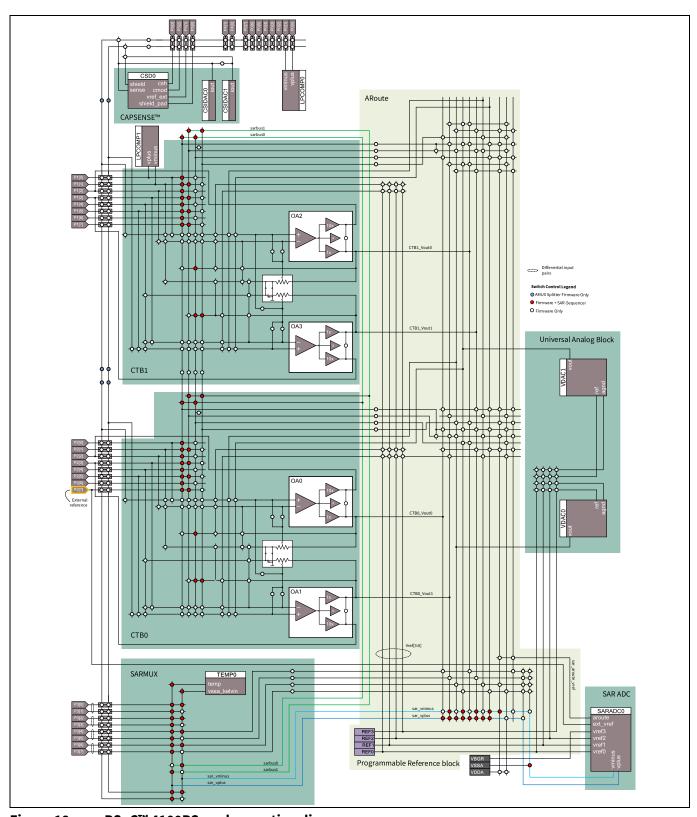

# 3.2.2 Analog routing

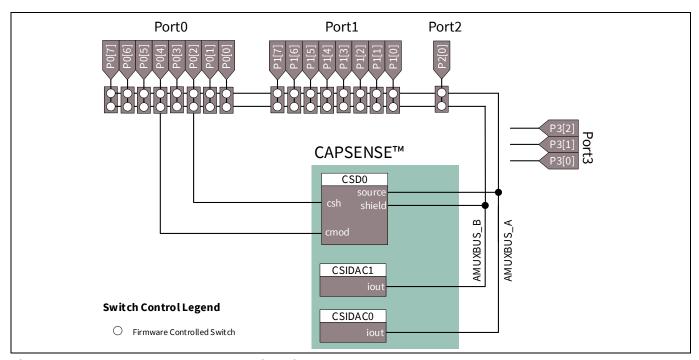

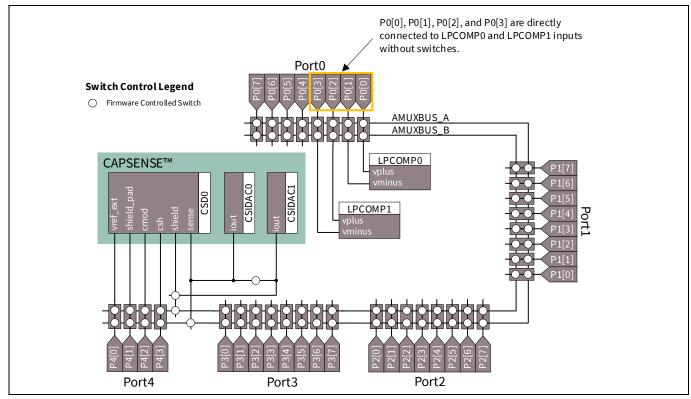

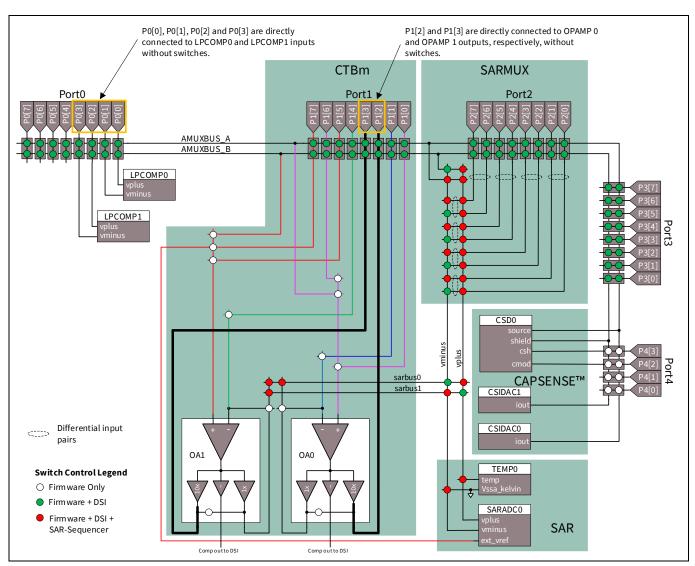

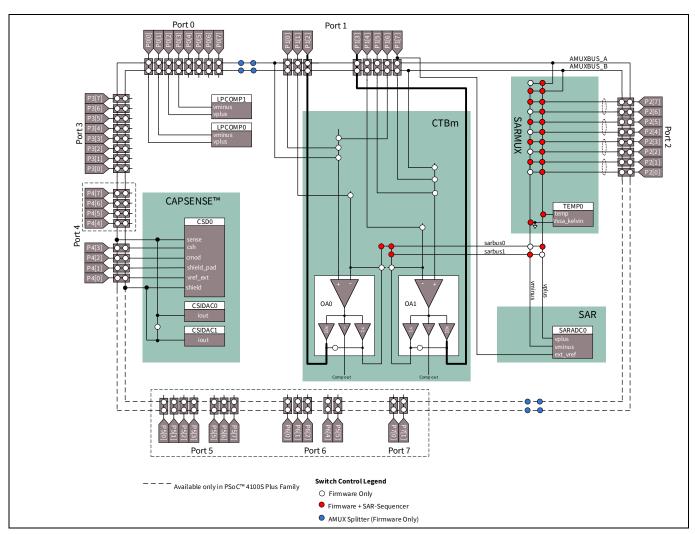

GPIO pins configured in the High-impedance analog (HIGH-Z) mode are connected to the analog resources by direct connections or through the analog switches and the analog mux (AMUX) bus, as shown in Figure 11 through Figure 16.

The following are the key highlights of the analog routing in the PSoC™ 4000 parts shown in Figure 11:

- All pins (except port 3) can connect to the AMUX buses, controlled by firmware. There are two buses: AMUXBUS\_A and AMUXBUS\_B.

- CAPSENSE™ IDAC0 is connected to AMUXBUS\_A, and IDAC1 is connected to AMUXBUS\_B.

- CAPSENSE™ CMOD is connected to P0[4], and the shield tank capacitor is connected to P0[2].

- Any pin can be used for the capacitive touch sensors (except Port 3) as the CAPSENSE™ block connects to the sensors using the AMUX bus.

Note: Place the CMOD capacitor close to the pin. See  $AN85951 - PSoC^{TM} 4 CAPSENSE^{TM}$  design guide for layout guidelines.

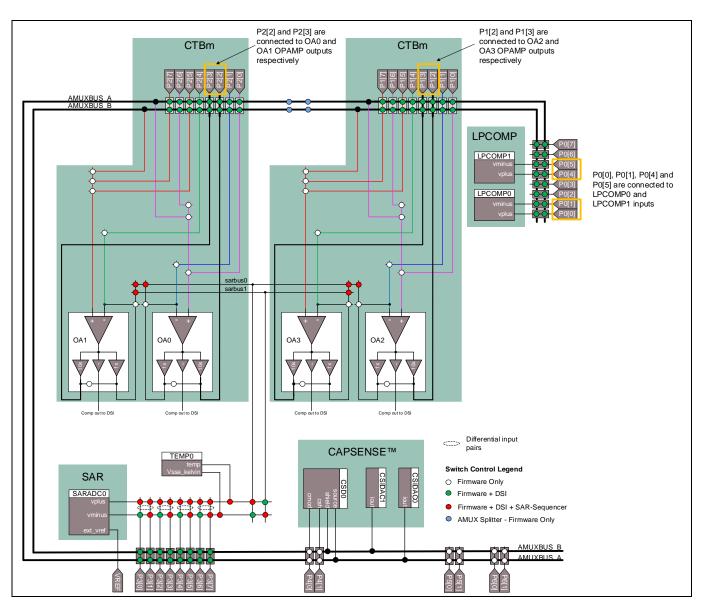

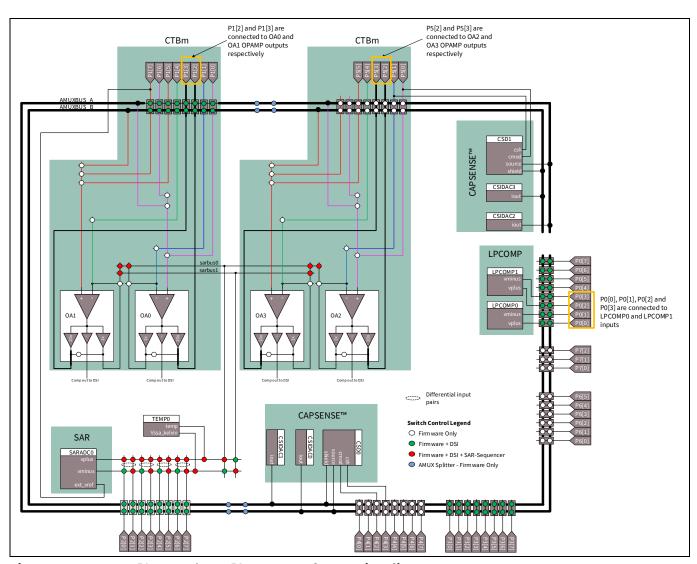

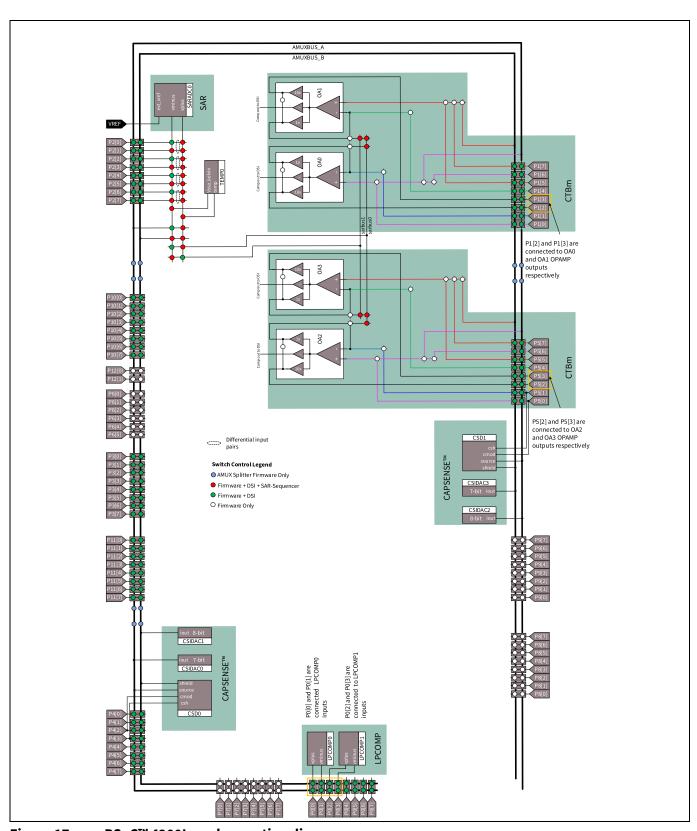

The following are the key highlights of analog routing in other PSoC<sup>™</sup> 4 parts — see Figure 13 through Figure 17.

- There are two AMUX buses. All pins have the capability to connect to AMUXBUS\_A and AMUXBUS\_B. AMUX bus connection can be controlled by firmware or by using the DSI signal. Note that in the case of Port 4 and higher port pins where the DSI connection is not available, AMUX can be connected only in firmware.

- Direct connections are available for opamp inputs and outputs, which provide better performance due to lower trace resistance and parasitic capacitance. Direct connections are also available for low-power comparator (LPCOMP) inputs without switches.

- There are dedicated pins for CAPSENSE™ CMOD and the shield tank capacitor. See Figure 13 through Figure 17 to know about the pins.

- CAPSENSE™ IDAC0 is connected to AMUXBUS\_A; IDAC1 is connected to AMUXBUS\_B.

- Any pin can be used for the capacitive touch sensors as the CAPSENSE™ block connects to the sensors using the AMUX bus.

- AMUXBUS\_A and AMUXBUS\_B can be split using switches (marked in blue) as shown in Figure 14 through Figure 17. This is useful if the AMUX buses are required for non-CAPSENSE™ applications such as opamp/comparator input and output routing along with CAPSENSE™ in the system.

- The SAR sequencer connects the SAR ADC input to:

- Port 2 in PSoC<sup>™</sup> 4100, PSoC<sup>™</sup> 4100S, PSoC<sup>™</sup> 4100S Plus, PSoC<sup>™</sup> 4200, PSoC<sup>™</sup> 4100M, PSoC<sup>™</sup> 4200M, and PSoC<sup>™</sup> 4200L

- Port 3 in PSoC<sup>™</sup> 41xx-BL, PSoC<sup>™</sup> 42xx-BL, and PSoC<sup>™</sup> 41xxPS

- CTBm, CTB outputs

- Temperature sensor output

Multiplexing is done by controlling the switches shown in red in Figure 11 through Figure 15. Note that the SAR ADC can also take the input from any pin using AMUXBUS without the sequencer.

Note:

The opamp output is connected to a dedicated pin without any switches. If the connection to AMUX bus is required, the AMUX switch associated with the dedicated pin is activated. This also allows other pins to act as opamp output pins if the corresponding AMUX switches are activated.

#### **GPIO** pin basics

Note:

When the SAR ADC is operated with differential inputs in the sequencer mode, the positive input can only be an even-numbered pin with the negative input as the adjacent odd-numbered pin. For example, in  $PSoC^{TM}$  4200, P2[0] and P2[1] are pair pins with P2[0] as positive input and P2[1] as negative input. This is shown using rings in analog routing diagrams.

Figure 11 PSoC<sup>™</sup> 4000 analog routing diagram

Figure 12 PSoC<sup>™</sup> 4000S analog routing diagram

Figure 13 PSoC<sup>™</sup> 4200/PSoC<sup>™</sup> 4100 analog routing diagram

Figure 14 PSoC<sup>™</sup> 4100S/4100S Plus analog routing diagram

Figure 15 PSoC™ 41xx-BL/PSoC™ 42xx-BL analog routing diagram

Figure 16 PSoC™ 4100M/PSoC™ 4200M analog routing diagram

Figure 17 PSoC™ 4200L analog routing diagram

# infineon

#### **GPIO** pin basics

Figure 18 PSoC™ 4100PS analog routing diagram

Note: The  $PSoC^{TM}$  Creator IDE tool provides an analog routing diagram for a design similar to those illustrated in Figure 11 through Figure 18. See the Analog tab in the .cydwr file of the project in  $PSoC^{TM}$  Creator.

**GPIO** pin basics

#### 3.3 Startup and low-power behavior

On reset/power-up, all GPIO pins start up in the high-impedance analog mode, that is, with the input buffer and output driver disabled. These GPIO pins remain in this mode until the reset is released; then the initial operating configuration of the associated registers of each GPIO pin is loaded during boot and takes effect at that time. During run time, GPIOs can be configured by writing to the associated registers.

Note:

In the PSoC<sup>™</sup> 4000 parts, pin P1[6] is temporarily configured as XRES during power-up until the device executes the start-up code. Do not pull this pin down during power-up as this keeps the device in reset. Note that the reset provision via P1[6] is only for production test purpose and not intended for user applications.

See I/O system restrictions in the PSoC<sup>™</sup> 4000 family – KBA91258 for more information.

PSoC<sup>™</sup> has up to four power modes as follows:

Table 2 Low power modes in PSoC<sup>™</sup> 4 families

| Device                   | Sleep | Deep Sleep | Hibernate | Stop |

|--------------------------|-------|------------|-----------|------|

| PSoC™ 4000               | ✓     | ✓          | ×         | ×    |

| PSoC™ 4000S              | ✓     | ✓          | ×         | ×    |

| PSoC™ 4100/4200          | ✓     | ✓          | ✓         | ✓    |

| PSoC™ 4100S              | ✓     | ✓          | ×         | ×    |

| PSoC™ 4100S Plus         | ✓     | ✓          | ×         | ×    |

| PSoC™ 4100S Max          | ✓     | ✓          | ×         | ×    |

| PSoC™ 4100S Plus 256KB   | ✓     | ✓          | ×         | ×    |

| PSoC™ 4200DS             | ✓     | ✓          | ×         | ×    |

| PSoC™ 4500S              | ✓     | ✓          | ×         | ×    |

| PSoC™ 4700S              | ✓     | ✓          | ×         | ×    |

| PSoC™ analog coprocessor | ✓     | ✓          | ×         | ×    |

| PSoC™ 4 Bluetooth® LE    | ✓     | ✓          | <b>√</b>  | ✓    |

| PSoC™ 4 M                | ✓     | ✓          | ✓         | ✓    |

| PSoC™ 4 L                | ✓     | ✓          | ✓         | ✓    |

| PSoC™ 4100PS             | ✓     | ✓          | ×         | ×    |

In the Sleep mode, the GPIOs are active and can be actively driven by the peripherals; only the CPU is inactive in this mode. In the Deep Sleep mode, the pins driven by the Deep Sleep peripherals such as I<sup>2</sup>C, LCD driver, opamp, and comparator are functional. The I<sup>2</sup>C pins can wake the device up on an address match event. The segment LCD, connected to the device pins, is periodically refreshed even in the Deep Sleep mode.

The PSoC<sup>™</sup> 4 parts (except PSoC<sup>™</sup> 4000) have an additional feature that freezes the GPIOs in Deep Sleep, Hibernate, and Stop modes. Unfreezing of GPIOs also happens automatically when the low-power mode is exited. However, note that the GPIOs driven by Deep Sleep peripherals are active in Deep Sleep mode and are not frozen.

In the case of Hibernate and Stop modes, wakeup happens with a device reset. This clears the GPIO configuration and the pin state. To retain the pin state, use the CySysPmFreezelo() and CySysPmUnfreezelo() API functions. Note that you do not need to call CySysPmFreezelo() for Stop mode

#### **GPIO** pin basics

because it is automatically called when the user invokes Stop mode using the CySysPmStop() API function. However, you should call CySysPmFreezeIo() just before the function call to enter Hibernate mode. The GPIOs are unlocked by calling CySysPmUnfreezeIo(). A call to this function is also required when the exit is made from the Stop mode. Note that the frozen pin states and configurations are not maintained on an external reset (XRES) event.

CySysPmFreezeIo() and CySysPmUnfreezeIo() are also useful in Deep Sleep mode. An example of use of this feature is shown in the Control register handling in Deep Sleep section. UDB-based Components such as control registers are not active and lose the data in Deep Sleep, Hibernate, and Stop modes. If the Control Register is driving a pin, a glitch can occur when the PSoC™ device enters or exits these modes if the last state is a '1'. To avoid this glitch, the GPIO should be frozen before entering a Low-power mode.

For information on Low-power modes, see AN86233 – PSoC<sup>™</sup> 4 MCU low-power modes and power reduction techniques.

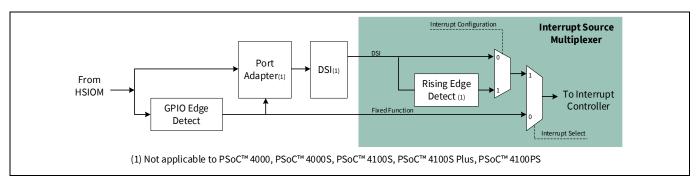

#### 3.4 GPIO interrupt

Figure 19 GPIO interrupt signal routing to the interrupt controller

At each of the 32 interrupt lines of the Interrupt Controller in the processor core, there is an Interrupt Source Multiplexer. This multiplexer block selects the source of the interrupt and provides an option of rising-edge detection or direct connection to the Interrupt Controller. There are two sources of interrupts:

- 1. Fixed-function source

- 2. DSI source

The Interrupt Select line selects the DSI or the fixed-function source. The Interrupt Configuration selects the direct connection or the rising-edge detection logic route to connect to the Interrupt Controller.

A fixed-function interrupt source has a fixed interrupt vector; this means that the interrupt source has a dedicated connection to one of the 32 interrupt lines of the Cortex® M0/Cortex® M0+ CPU. The interrupt source on this route is directly connected to the Interrupt Controller. When the interrupt source is routed through the DSI, the vector selection is not fixed. This routing also provides an option of rising-edge detection or direct connection.

Note: The interrupt vector table is available in the Interrupts chapter of the Reference manual.

The use of Interrupt Source Multiplexer is not limited to the GPIO interrupts; it is also used for all other sources. To know more about other interrupt sources, see the "Interrupt Sources" section of AN90799 - PSoC™ 4 interrupts.

#### **GPIO** pin basics

The GPIO interrupt, in addition to the resources present in the Interrupt Source Multiplexer, uses its own GPIO Edge Detect block as showin in Figure 19.

The GPIO interrupt signal from the HSIOM is routed in the following ways:

- Route 1: Fixed-function route through the GPIO Edge Detect block with the Interrupt Source Multiplexer configured to direct connection

- Route 2: DSI route through the GPIO Edge Detect block with the Interrupt Source Multiplexer configured to rising-edge

- Route 3: DSI route through the GPIO Edge Detect block with the Interrupt Source Multiplexer configured to direct connection

- Route 4: DSI route bypassing the GPIO Edge Detect block with the Interrupt Source Multiplexer configured to rising-edge

- Route 5: DSI route bypassing the GPIO Edge Detect block with the Interrupt Source Multiplexer configured to direct connection

See Pins component interrupts to know how different routes are configured.

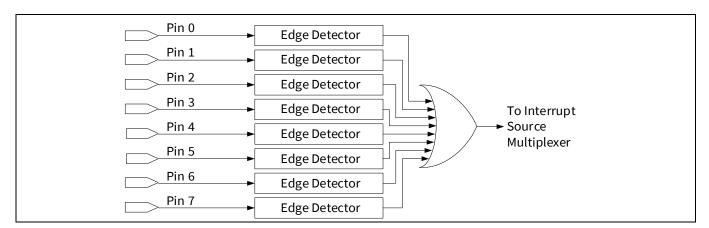

The following figure shows the GPIO Edge Detect block. This block detects rising-edge, falling-edge, and both edges in the incoming GPIO signal. Individual GPIO interrupt signals within a port are ORed together to generate a single interrupt request. Thus, there is one interrupt vector for each port.

Figure 20 GPIO edge detect

As it is clear from Figure 20, when an interrupt is triggered, the interrupt source is required to be identified. PSoC<sup>™</sup> 4 provides a status register to identify the interrupting pin. After reading the status register, it is important to clear it whenever the GPIO Edge Detect logic is used, to avoid the following:

- 1. Single interrupt trigger and nonresponsive to further interrupts when the Interrupt Source Multiplexer is configured to rising-edge. This scenario occurs if Route 2 is used.

- 2. Repetitive interrupts for a single request when the Interrupt Source Multiplexer is configured to direct connection. This scenario occurs if Route 1 or Route 3 is used.

- 3. When the GPIO interrupt takes the route without the GPIO Edge Detect block, there is no need to clear the interrupt. However, when the rising-edge detection logic in the interrupt source multiplexer is also bypassed, it results in a level type interrupt (Route 5). In this case, the interrupt is triggered repeatedly as long as the pin signal is HIGH. Thus, it is recommended to configure the interrupt source multiplexer to a rising-edge interrupt when the GPIO Edge Detect block is bypassed (Route 4).

#### **GPIO** pin basics

Note:

The GPIO interrupt logic continues to function in Sleep, Deep Sleep, and Hibernate modes; thus, any pin can be used as a wakeup source. A dedicated wakeup pin, P0[7], is available to wake the device from Stop mode in PSoC™ 4200 / PSoC™ 4100, PSoC™ 4M, and PSoC™ 4L parts. For a PSoC™ 4 Bluetooth® LE device, the wakeup pin is P2[2].

#### 3.4.1 Limitations in GPIO interrupt

- Port 4 and higher ports do not have a port adapter. Thus, pin interrupt via DSI routing is not possible for these port pins.

- PSoC<sup>™</sup> 4000 and PSoC<sup>™</sup> 4100/PSoC<sup>™</sup> 4200 have one interrupt vector for each port. PSoC<sup>™</sup> 4 Bluetooth® LE does not have a dedicated interrupt vector for the ports beyond Port 5, while PSoC<sup>™</sup> 4M does not have one for the ports beyond Port 4. However, a common port interrupt vector is allocated, which gets triggered when any port interrupt becomes active. See the Pins component datasheet to understand how to use this common port interrupt.

- See the "Interrupts" chapter in the respective device architecture reference manual to learn about ports that have a common interrupt vector.

An example project is shown in the Pin interrupt section, which explains how to use the GPIO interrupt. To understand interrupts in general, see the application note AN90799 − PSoC<sup>™</sup> 4 interrupts.

Overvoltage-tolerant (OVT) pins

# 4 Overvoltage-tolerant (OVT) pins

Pins P5[0] and P5[1] in PSoC<sup>™</sup> 4 Bluetooth<sup>®</sup> LE, and Port 6 in PSoC<sup>™</sup> 4M are the OVT pins. For PSoC<sup>™</sup> 4L, Port 6 and Port 8 have OVT pins. These are similar to regular GPIOs with the following additional features:

- 1. Overvoltage-tolerant: There is no ESD clamp diode between OVT pin and the supply rail. This enables the OVT pin to withstand an external voltage higher than VDDIO, VDDD, or VDDA voltage, up to 5.5 V.

- 2. Provides better pull-down drive strength compared to a regular GPIO

- 3. Serial Communication Block (SCB): When configured as I<sup>2</sup>C and its lines routed to OVT pins, an SCB meets the following I<sup>2</sup>C specifications:

- a) Fast Mode Plus LOW-level output current (IOL) specification

- b) Fast Mode and Fast Mode Plus hysteresis and minimum fall-time specifications

For more details on the I/O hardware, see the I/O system chapter of the Reference manual.

**GPIO** pins in PSoC™ Creator

#### **GPIO** pins in PSoC<sup>™</sup> Creator 5

This section describes how to use PSoC™ Creator to configure and use GPIO pins.

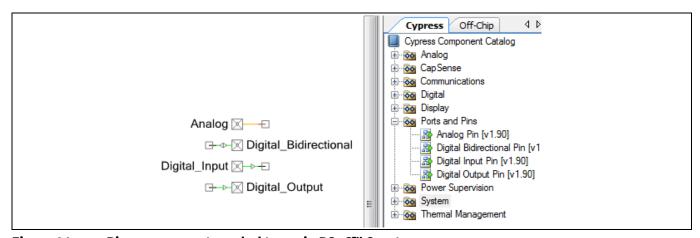

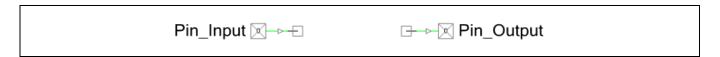

#### 5.1 Pins Component symbols

The Pins Component is the recommended method for connecting internal PSoC™ resources to a physical pin. It allows PSoC™ Creator to automatically place and route the signals within the PSoC™ device-based on the chosen pin configuration.

The standard Infineon Component Catalog contains four predefined GPIO configurations in the Ports and Pins class of symbols: analog, digital bidirectional, digital input, and digital output. Drag one of these components to the schematic to add a pin to the project, as follows:

Pins component symbol types in PSoC™ Creator Figure 21

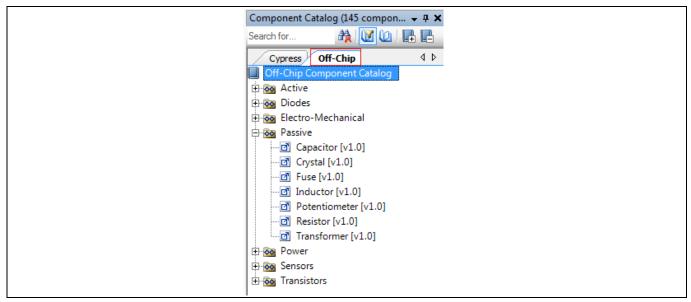

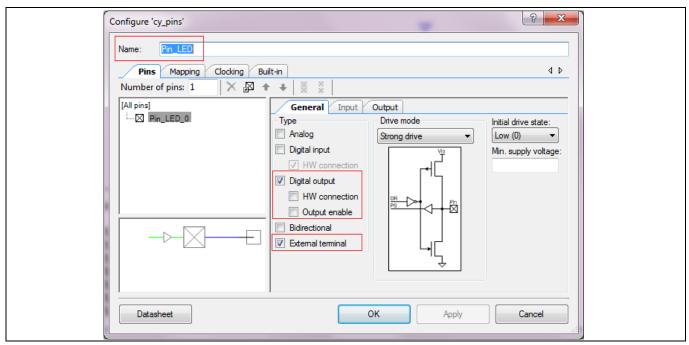

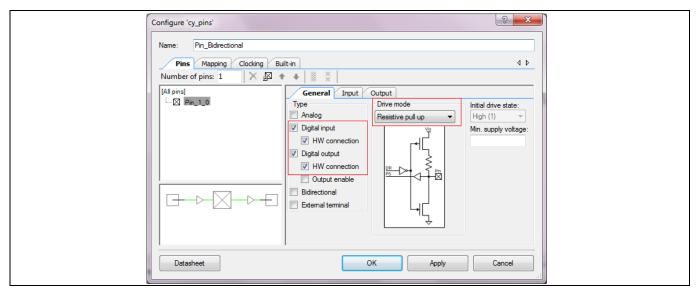

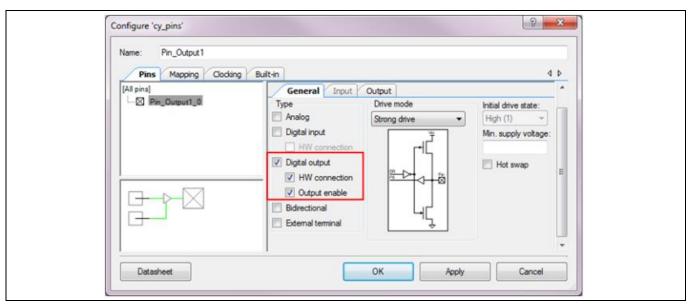

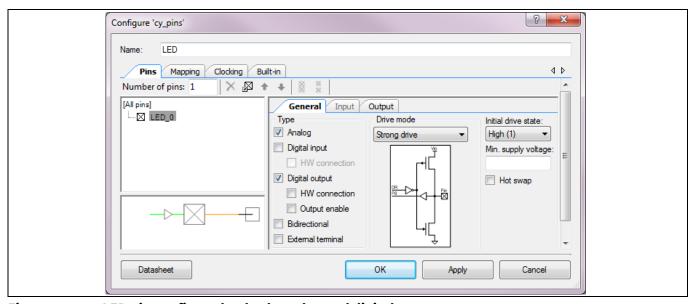

#### **5.2** Pins component customizer

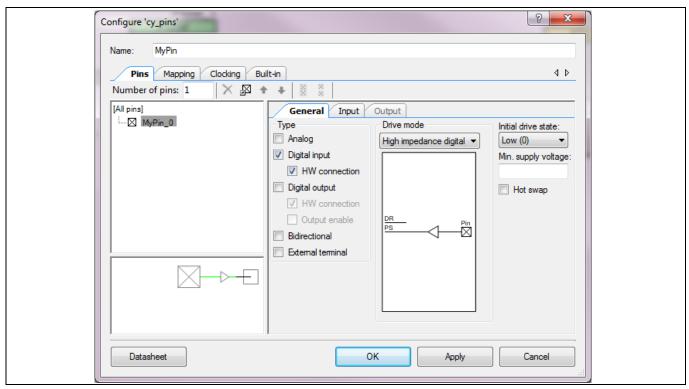

Each component in PSoC™ Creator comes with a customizer to configure the component. Figure 22 shows the Pin component customizer, which is accessed by double-clicking the component.

#### **GPIO** pins in PSoC<sup>™</sup> Creator

Figure 22 Pin component customizer

The following table describes some of the parameters in the Pin component customizer. For details of all the parameters, see the Pins component datasheet.

Table 3 Pin component settings

| Setting                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Tab ><br>Type                | This setting configures the pin type. Possible options are:  • Analog  • Digital input with or without hardware (HW) connection  • Digital output with or without HW connection and output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                      | Bidirectional pin  When the digital input or output is configured with no HW connection, it means that the pin state is controlled by the CPU. Note that more than one selection can be made at once. For example, a pin can be configured for both analog and digital input at the same time.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

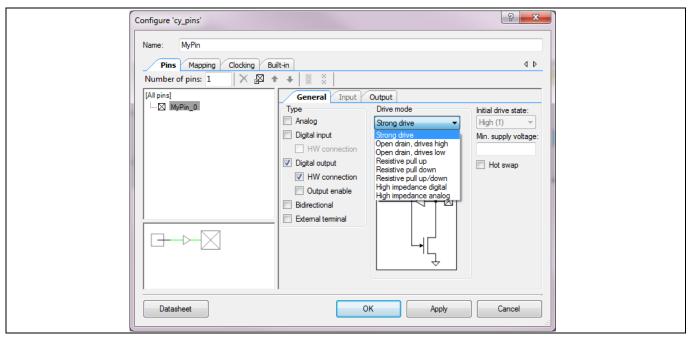

| General Tab ><br>Drive Mode          | This setting configures the pin with one of the eight drive modes described in the GPIO pin basics section. Figure 23 shows the drive mode options in the pin customizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| General Tab ><br>Initial Drive State | The Initial drive state parameter sets the data register value. This value is reflected at the pin if it is software-driven, given that the pin is set with an appropriate drive mode. If the pin is in the output mode with HW connection enabled and Output enable disabled, the initial drive state acts as the enable control. Setting the initial state to '1' enables the pin, which is done as the default value by PSoC™ Creator, as shown in Figure 23. If the pin is configured as input, initial drive state can still be useful. For example, if resistive pull-up is required at the input pin, then the drive mode should be configured to Resistive pull up with initial state as HIGH in order to turn on the pull-up path through |

#### **GPIO** pins in PSoC<sup>™</sup> Creator

| Setting                  | Description                                                                                                                                                                                                                                                  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | the resistor. Likewise, for resistive pull down, the initial drive state should be set to LOW to enable the pull-down path.                                                                                                                                  |

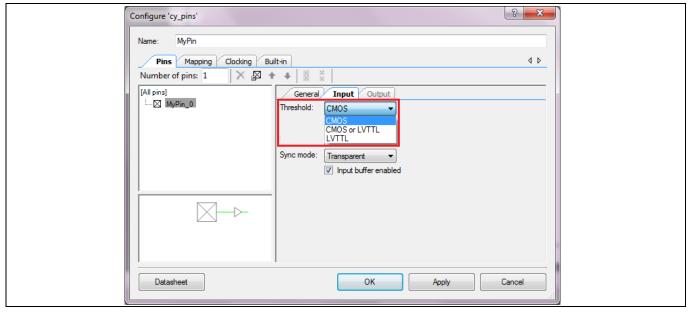

| Input Tab ><br>Threshold | CMOS and LVTTL input threshold setting is for an entire port. There are three options as shown in Figure 24. The "CMOS or LVTTL" option allows the PSoC™ Creator tool to select CMOS or LVTTL depending on the threshold setting for other pins in the port. |

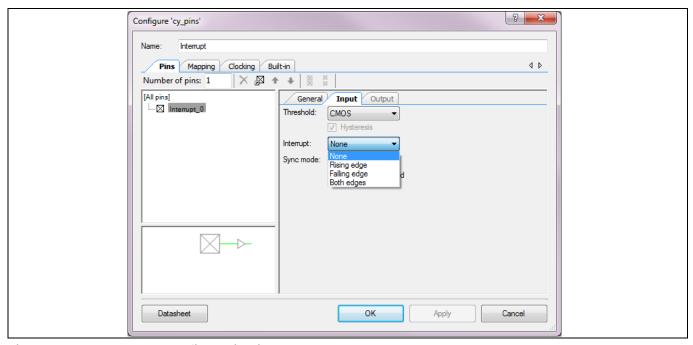

| Input Tab > Interrupt    | This setting configures the GPIO Edge Detect block described in the GPIO interrupt section. For more details on this setting, see Pins component interrupts.                                                                                                 |

Figure 23 Pin Drive mode setting and initial drive state

Figure 24 Pin input threshold selection

**GPIO** pins in PSoC™ Creator

#### 5.3 Pins component interrupts

The Interrupt parameter in the pin customizer configures the GPIO Edge Detect block described in the GPIO interrupt section.

Figure 25 Interrupt configuration in PSoC™ Creator

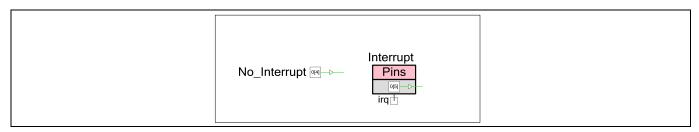

The Pins Component symbol changes when interrupts are enabled, as shown in Figure 26.

Figure 26 Pins component symbol with interrupts enabled

Note that you can use only one Pin Component with each physical GPIO port if the interrupt is enabled. The reason for this limitation is that all pin interrupts in a port are ORed together, as described in the GPIO interrupt section. Therefore, only one IRQ signal can be shown on the schematic per port. For example, consider two Pin Components with interrupts enabled. These components cannot be mapped to pins in the same physical port.

Figure 27 Two pins components with interrupts enabled

#### **GPIO** pins in PSoC<sup>™</sup> Creator

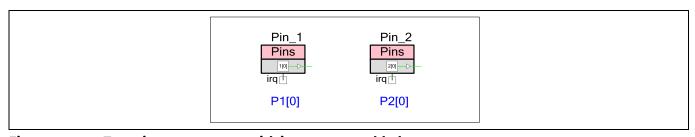

PSoC<sup>™</sup> Creator will not allow you to assign the two Components to the same port. The accepted method is to assign multiple pins to the same component. This ensures that there is only one IRQ signal in the schematic for that physical port. You can still assign each pin its own interrupt edge type. The only limitation is that the pins must be contiguous in the same port. The interrupt source should be identified in the ISR; see the Pin interrupt.

Figure 28 Multiple pins in the same port with interrupts enabled

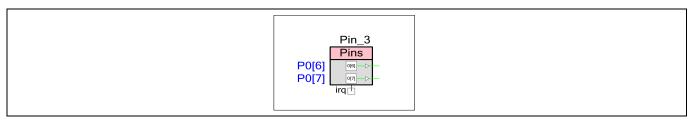

The IRQ of the Pin Ccomponent should be connected to the interrupt component. This routes the GPIO interrupt signal to the interrupt controller.

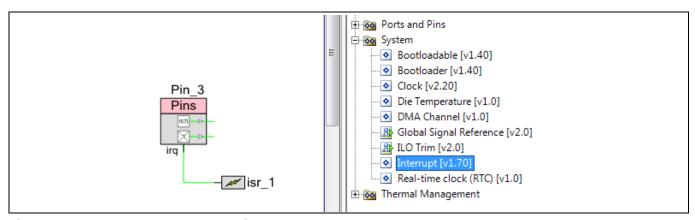

Figure 29 Interrupt component in the catalog

The interrupt component configures the interrupt source multiplexer to either direct connection (shown as "level" in the Interrupt component customizer) or rising-edge. The GPIO interrupt architecture is described in the GPIO interrupt section along with the different routes available for the interrupt signal. Different routes are configured with the help of the pin component and the interrupt component customizer settings summarized as follows:

Table 4 GPIO interrupt configurations

| Schematic              | Interrupt setting in pin component              | Interrupt<br>component<br>setting | Route   | Details                                                                                                                                                                                                                                                                                |

|------------------------|-------------------------------------------------|-----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin_1 Pins irq irq irq | Rising-edge or<br>falling-edge or<br>both edges | Level                             | Route 1 | Interrupt on edges depending on the pin component setting. It uses a fixed interrupt vector depending on the selected port. In this configuration GPIO interrupt status register should be cleared; otherwise, interrupts are triggered repeatedly on a single interrupt request. This |

# **GPIO** pins in PSoC<sup>™</sup> Creator

| Schematic              | Interrupt setting in pin component              | Interrupt<br>component<br>setting | Route   | Details                                                                                                                                                                                                                                                                                                                                |

|------------------------|-------------------------------------------------|-----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                 |                                   |         | configuration can be used to wake up the device from any low-power mode. However, note that wakeup from Stop mode requires the use of a specific pin depending on the selected device.                                                                                                                                                 |

| Pin_1 Pins irq irq irq | Rising-edge or<br>falling-edge or<br>both edges | Rising-<br>edge                   | Route 2 | Interrupt on edges depending on the pin component setting. In this configuration GPIO interrupt should be cleared; otherwise, interrupt is triggered only once. Interrupt vector is not fixed. This configuration can wake up the CPU only from Sleep mode; it will not work in other Low-power modes.                                 |

| Pin_1 Pins irq irq irq | Rising-edge or<br>falling-edge or<br>both edges | Level                             | Route 3 | This is similar to Route 1. However, Route 3 is taken only if the interrupt vector is forced on to a desired DSI vector line. See the application note AN90799 − PSoC™ 4 interrupts to know how to force the interrupt vector. This configuration can wake up the CPU from only Sleep mode; it will not work in other Low-power modes. |

| Pin_1 ⊠⊸——isr_1        | Disabled                                        | Rising-<br>edge                   | Route 4 | This configuration provides rising-edge interrupt. In this case, there is no need to clear the interrupt. This configuration can wake up the CPU only from Sleep mode; it will not work in other Low-power modes.                                                                                                                      |

| Pin_1 ⊠→isr_1          | Disabled                                        | Level                             | Route 5 | This configuration provides Level interrupt. Note that the interrupt is triggered repeatedly as long as the pin signal is high. In this case also, there is no need to clear the interrupt. This configuration can wake up the CPU from only Sleep mode; it will not work in other Low-power modes.                                    |

GPIO pins in PSoC™ Creator

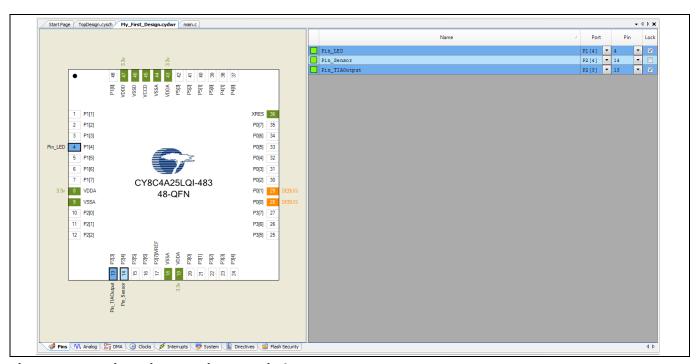

## 5.4 Manual pin assignments

You can use the **Pins** tab of the Design-Wide Resources (DWR) window to assign a Pin Component to a physical pin. PSoC<sup>™</sup> Creator automatically assigns pins if the user does not choose any but this may lead to a pin placement that is more difficult to route on a PCB.

Figure 30 shows three assigned pins. The pins highlighted in dark blue are manually assigned and the pin highlighted in light blue is automatically assigned. Selecting the **Lock** option prevents the pin from being reassigned by PSoC™ Creator.

PSoC™ Creator makes it simple to reassign pins as needed, but you should consider pin selection before the boards are designed.

Figure 30 Pin assignment in DWR window

Note:

PSoC<sup>™</sup> Creator can use the unused pin switches for routing the analog signals. This is configured using the **Unused Bonded I/O** parameter in the **System** tab of the .cydwr file. See PSoC<sup>™</sup> Creator Help for more details.

#### 5.5 PSoC™ Creator APIs

Infineon provides a set of API functions that you can use to control GPIOs dynamically through firmware. The API for the pins component enables access on both a Component-wide and per-pin basis. See the "API" section of the Pins datasheet for more details.

Per-pin API functions, which are provided as part of  $cy_{boot}$  in the *cypins.h* file, are documented in the "Pins" section of the PSoC<sup>TM</sup> Creator system reference guide (**Help > Documentation > System Reference**). You can use these functions to control the configuration registers for each physical pin.

**GPIO** pins in PSoC™ Creator

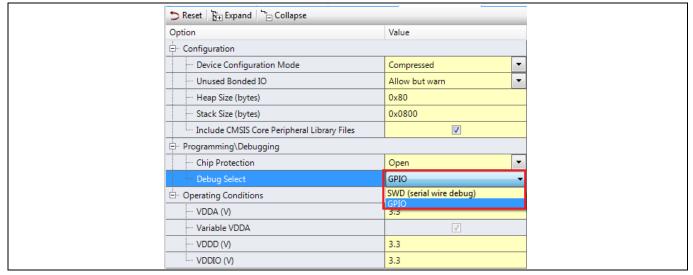

# 5.6 Debug logic on GPIO pins

The PSoC<sup>™</sup> 4 serial wire debug (SWD) pins are shared on the port pins. See the respective device datasheet for more information on the debug port pins. The debug function, however, can be disabled and the pins can be used as regular GPIOs by setting the "Debug Select" option to "GPIO" in the **System** tab of the DWR window.

Figure 31 Debug port disabled

Note that disabling the debug interface does not affect the ability to program the device.

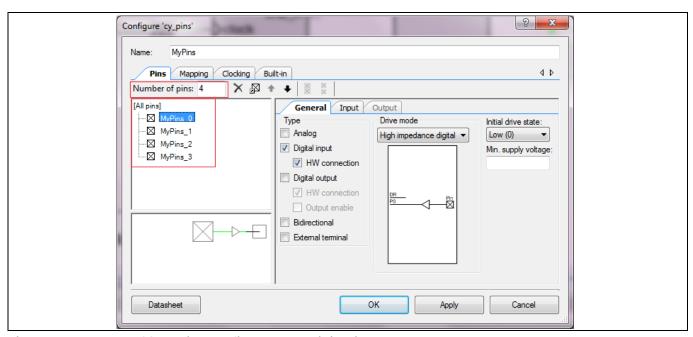

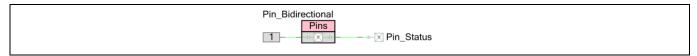

# 5.7 Add multiple GPIO pins as a logical port

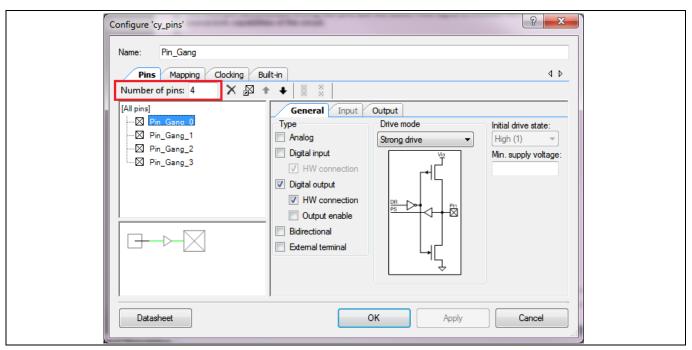

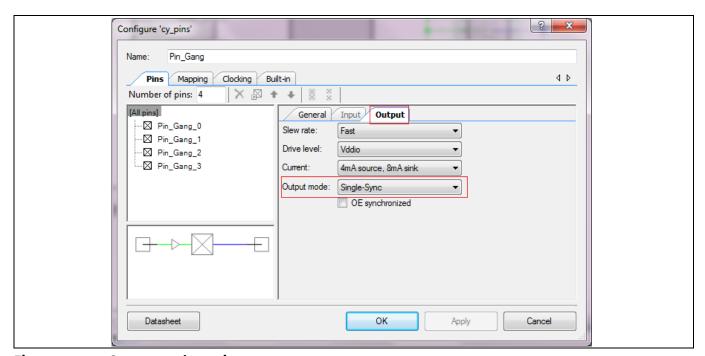

In PSoC<sup>™</sup> Creator, you can organize a group of as many as 36 pins into a logical port, which can then be referenced in code by the port's defined name. All the pins may be part of the same physical port, or they may form separate physical ports. In the Pin Component customizer, set the **Number of Pins** required in a port. The pins appear in the list below the field as shown in Figure 32. Each pin can be configured independently. Select [All Pins] to configure every pin in the component with the same settings.

#### **GPIO** pins in PSoC™ Creator

One of four pins configured as a digital input Figure 32

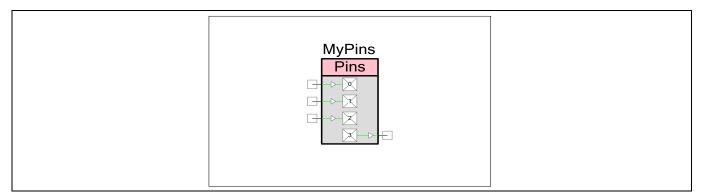

If the number of pins is configured to '4' with three digital inputs and one digital output, the schematic symbol appears as shown in Figure 33.

**Pins Component in port configuration** Figure 33

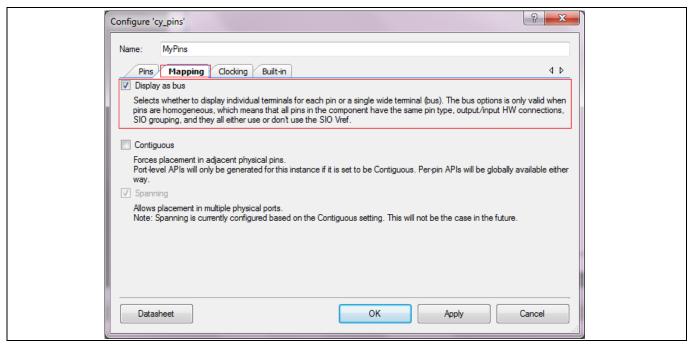

There is an option to display the port with a bus instead of individual pin terminals. Select **Display as Bus** in the Mapping tab of the Pin Configuration window to display the port as a bus. Note that all pins must be of the same type to display as a bus.

#### **GPIO** pins in PSoC™ Creator

Figure 34 Display as bus option

If the **Number of Pins** is configured to four digital outputs, the schematic symbol appears:

Figure 35 Four pins displayed with bus

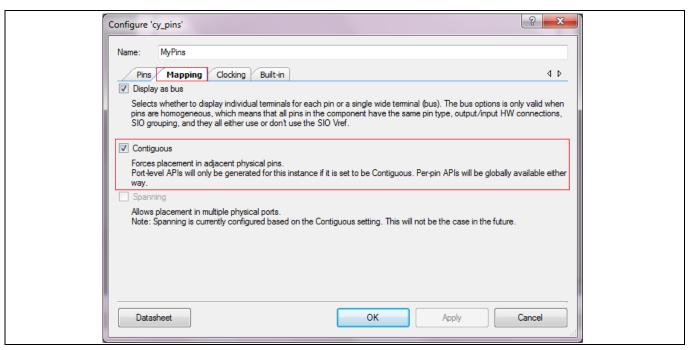

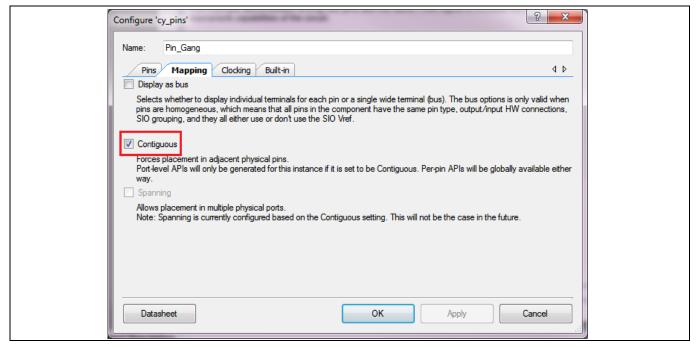

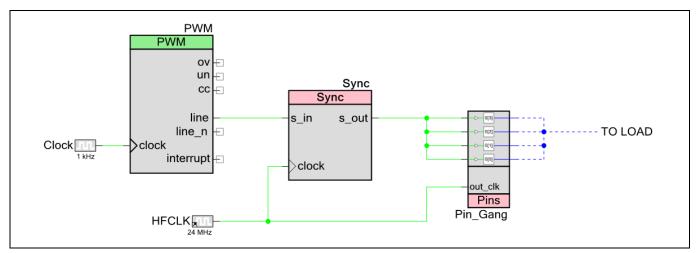

The pins with the bus terminal can be forced to map to adjacent pins by enabling **Contiguous** in the **Mapping** tab.

#### GPIO pins in PSoC™ Creator

Figure 36 Contiguous pin placement option

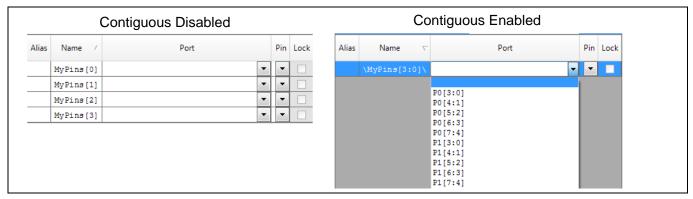

When you select **Contiguous**, PSoC<sup>™</sup> Creator modifies the list of available pin options to match the port's configuration. When the Contiguous option is disabled, any pin can be selected. When the Contiguous option is enabled, only adjacent pins can be selected.

Figure 37 Pin placement with contiguous disabled/enabled

These features are described in more detail in the Pin Configuration window and the Pins Component datasheet.

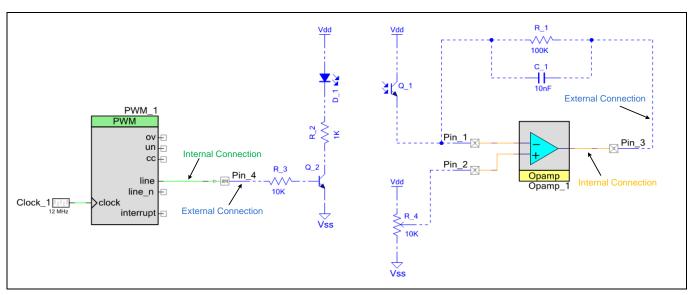

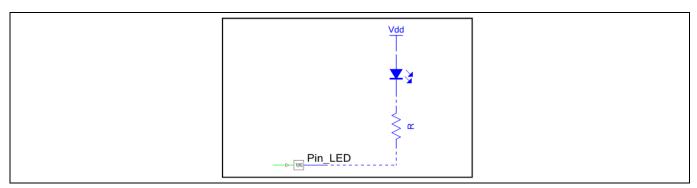

# **5.8** Represent Off-chip components

The off-chip components catalog provides a way to mix external and internal components on the same schematic. This makes it possible to improve documentation and convey clearly how the internal schematic fits in the entire design. Off-chip components serve the same function as comments in the code − they do not change the functionality of the PSoC<sup>™</sup> design but, instead, provide a clearer picture of the entire system.

#### **GPIO** pins in PSoC™ Creator

Figure 38 Design with off-chip components

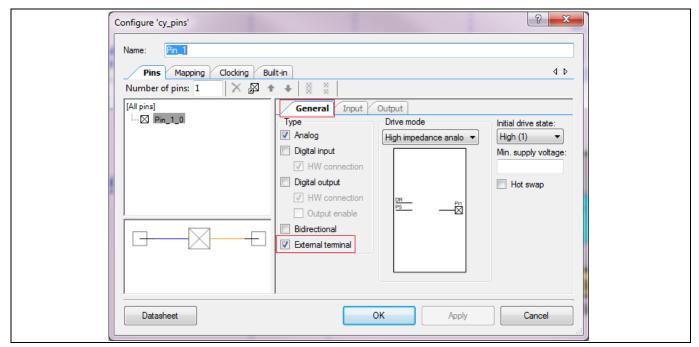

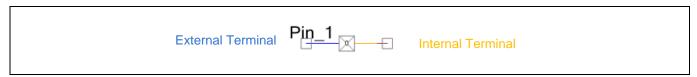

In the design shown above, PWM\_1 and Opamp\_1 are internal blocks of the device. These blocks are connected to the external components using pins Pin\_1 through Pin\_4. Green and orange wires are the internal connections (green for digital signals and orange for analog signals); whereas blue wires and components are external to the device. To make the connections with the external components in the schematic, enable the "External terminal" parameter in the Pin Component customizer. This brings out an additional terminal on the schematic.

Figure 39 Enabling external terminal

#### **GPIO** pins in PSoC™ Creator

Figure 40 Pin component with internal and external terminal

The components, to connect to the external terminals on the schematic, are available in the off-chip tab in the components catalog.

Figure 41 Off-chip Component Catalog

The components in this catalog cover those that are most likely to be connected to the pins of a PSoC<sup>™</sup> device on the board. These components consist of resistors, capacitors, transistors, inductors, switches, and others. Drag the component and place it on the schematic as it is done in the case of internal components.

GPIO pins in ModusToolbox™ software

### 6 GPIO pins in ModusToolbox™ software

This section describes how to use ModusToolbox™ to configure and use GPIO pins.

# **6.1** Configuring GPIO pins using ModusToolbox™ Device Configurator

### **6.1.1** Using the Device Configurator

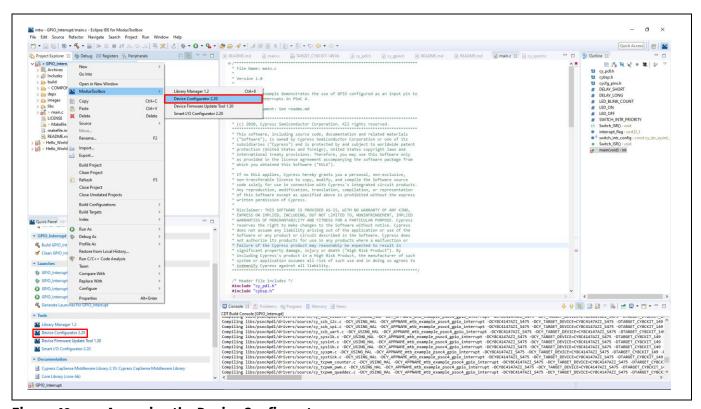

Initialization of GPIO pins can be done using two methods: using the Device Configurator as shown in this section or using GPIO using the peripheral driver library (PDL) in the next section. If you are familiar with PSoC™ Creator, the Device Configurator is similar to the configurations that can be made to components in PSoC™ Creator Top Design. The **Pins** tab in the Device Configurator allows the user to initialize GPIO pins and set the parameters for individual pins.

The Device Configurator is accessed by right-clicking on the project in ModusToolbox™, selecting ModusToolbox™ and then Device Configurator 2.20. The Device Configurator can also be accessed in the ModusToolbox™ **Quick Panel** in the bottom left.

Figure 42 Accessing the Device Configurator

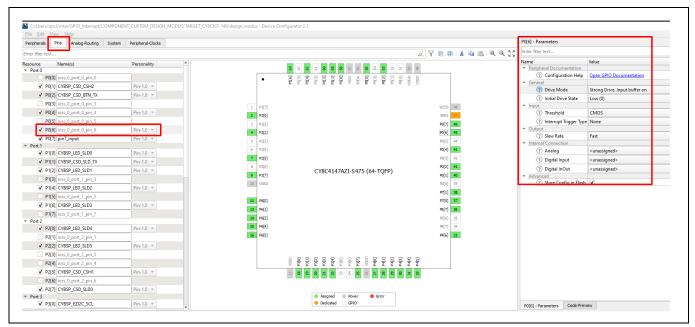

The Pins section in the Device Configurator allows the configuration of individual GPIO pins on the device. The left panel shows the pins separated by their respective ports. To configure a pin, check the box next to the pin; this will create the initialization code. The parameters for the pin can be configured on the right of the Device Configuration window.

#### GPIO pins in ModusToolbox™ software

Figure 43 Device Configurator

Table 5 Pin component settings

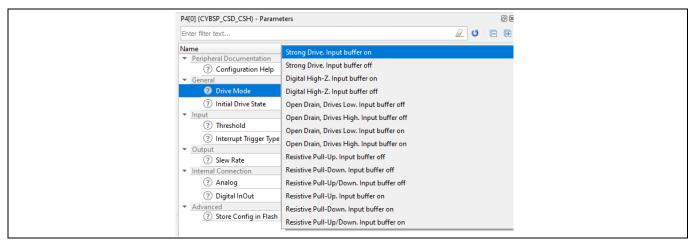

| Setting                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General > Drive<br>Mode                   | This setting configures the pin with one of the eight drive modes as shown in Figure 44. For a more detailed description of these drive modes, see the GPIO pin basics section.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| General > Initial<br>Drive State          | The Initial drive state parameter sets the data register value. This value is reflected at the pin if it is software-driven, and the pin is set with an appropriate drive mode, as shown in Figure 44. If the pin is configured as an input, the initial drive state can still be useful. For example, if resistive pull-up is required at the input pin, the drive mode should be configured to <b>Resistive pull up</b> with initial state as HIGH in order to turn on the pull-up path through the resistor. Likewise, for resistive pull down, the initial drive state should be set to LOW to enable the pull-down path. |

| Input > Threshold                         | CMOS and LVTTL input threshold setting is for an entire port. Note that an error will be displayed in the Notice List of the Device Configurator if all the pins on a port are not configured the same way. For more information, see the Pins datasheet.                                                                                                                                                                                                                                                                                                                                                                     |

| Input > Interrupt Trigger Type            | This setting configures the GPIO Edge Detect block described in the GPIO interrupt. For more details on interrupts, see the AN90799 – PSoC™ 4 Interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output > Slew Rate                        | The slew rate parameter determines the rise and fall ramp rate for the pin as it changes output logic levels. For more details on this setting, see Physical structure of GPIO pins.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Internal<br>Connection ><br>Analog        | This setting allows connecting of the pin to an analog signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Internal Connection > Digital Output      | This setting allows connecting to a digital output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Internal<br>Connection ><br>Digital InOut | This setting allows connecting to a digital input signal. Input signals are primarily used for I <sup>2</sup> C interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### GPIO pins in ModusToolbox™ software

| Setting          | Description                                                                                |

|------------------|--------------------------------------------------------------------------------------------|

| Advanced > Store | This setting controls whether the configuration structure is stored in flash (const, true) |

| Config in Flash  | or SRAM (not const, false).                                                                |

Figure 44 **Drive modes**

The Device Configurator sets up configurations of the pins, peripherals, and other device configurations. When closing the Device Configurator, go to File > Save to save the updates to the current project. After configuring the resources using the Device Configurator, PDL is used to interact with the pins and any interrupts. See the GPIO using Peripheral Driver Library (PDL) section and the PSoC™ 4 PDL API reference for more information on using GPIO pins after initialization.

Note:

The name of a GPIO pin can be changed from the default name provided by the BSP. This is helpful for naming the pins to correspond to their purpose in your design. The name of a pin can be changed by selecting the pin and typing the custom name into the text input in the "Name(s)" column as shown in Figure 43.

GPIO pins in ModusToolbox™ software

### **6.1.2** Device Configurator code preview

Figure 45 Device Configuration code preview

The Device Configurator features a Code Preview window that displays the PDL defines and functions that are created to configure the GPIO pin as shown in Figure 45. When the Device Configurator settings are saved, this code is automatically added to your project. This code can also be manually added to your projected by copying the definitions from this window.

**GPIO** pins in ModusToolbox<sup>™</sup> software

### 6.2 GPIO using the peripheral driver library (PDL)

The PDL integrates device header files, startup code, and peripheral drivers into a single package. The PDL supports the PSoC<sup>™</sup> 4 Series device family. The drivers abstract the hardware functions into a set of easy-to-use APIs. These are fully documented in the PSoC<sup>™</sup> 4 PDL API reference. The PDL reduces the need to understand register usage and bit structures, thus easing software development for the extensive set of peripherals in the PSoC<sup>™</sup> 4 series. You configure the driver for your application, and then use API function calls to initialize and use the peripheral.

The peripheral driver library (PDL) GPIO functions and other declarations used in this driver are located in  $cy\_gpio.h$ . You can optionally include  $cy\_pdl.h$  (ModusToolbox<sup>TM</sup> only) to get access to all the functions and declarations in the PDL.

Initialization can be performed either at the port level or by configuring the individual pins. See the product device header files for the list of supported ports and pins. It is recommended to use the Device Configurator for initialization of pins and other device resources. This reduces the risk of improper initialization and overflow of resources.

Single pin configuration is performed by using  $Cy_GPIO_Pin_FastInit$  (provide specific argument values) or  $Cy_GPIO_Pin_Init$  (provide a filled  $cy_stc_gpio_pin_config_t$  structure).

An entire port can be configured using  $Cy\_GPIO\_Port\_Init\_$ by providing a filled  $cy\_stc\_gpio\_prt\_config\_t$  structure. The values in the structure are bit fields representing the desired value for each pin in the port.

For the following example, the names defined in the device configurator can be used. For "base" use "user\_defined\_name"\_PORT and for the "pin\_num" use "user\_defined\_name"\_NUM. The user-defined name can be easily configured and viewed by using the ModusToolbox<sup>TM</sup> Device Configurator.

### 6.2.1 GPIO pin initialization-full

Individual GPIO initialization starts with defining all pin configuration values in the format as shown below. This initialization is not needed if a pin is already configured using the ModusToolbox™ Device Configurator.

#### **Code Listing 1 GPIO pin configuration structure**

```

cy stc gpio pin config t pinConfig = {

/*.outVal */ 1UL,

/* Output = High */

/*.driveMode */ CY GPIO DM PULLUP, /* Resistive pull-up, input buffer on */

/*.hsiom */ P0 3 GPIO,

/* Software controlled pin */

/*.intEdge */ CY GPIO INTR RISING, /* Rising edge interrupt */

/*.vtrip */ CY GPIO VTRIP CMOS,

/* CMOS voltage trip */

/*.slewRate */ CY GPIO SLEW FAST, /* Fast slew rate */

/*.vregEn */ OUL,

/* SIO-specific setting - ignored */

/*.ibufMode */ OUL,

/* SIO-specific setting - ignored */

/* SIO-specific setting - ignored */

/*.vtripSel */ OUL,

/* SIO-specific setting - ignored */

/*.vrefSel */ OUL,

/*.vohSel */ OUL

/* SIO-specific setting - ignored */

};

```

#### GPIO pins in ModusToolbox™ software

This pin configuration defines all the parameters for a GPIO pin. This is the third argument when initializing a pin.

To initialize a pin use Cy\_GPIO\_Pin\_Init (base, pinNum, config) with the following arguments as shown below:

**base** Pointer to the pin's port register base address

**pinNum** Position of the pin bit field within the port register

**config** Pointer to the pin config structure base address

#### Code Listing 2 Single GPIO pin initialization-full example

```

/* Initialize pin P0.3 */

if(CY GPIO SUCCESS != Cy GPIO Pin Init(P0_3_PORT, P0_3_NUM, &pinConfig))

{

/* Insert error handling */

}

```

### 6.2.2 GPIO pin initialization- fast

Configurator.

The GPIO Pin fast initialization Initializes the most common configuration settings for all pin types. These include, drive mode, initial output value, and HSIOM connection. Initialize a pin with CY\_GPIO\_PIN\_FastInit (base, pinNum, driveMode, outVal, hsiom) using the following arguments as shown below This initialization is not needed if a pin is already configured using the ModusToolbox<sup>TM</sup> Device

**base** Pointer to the Pin's Port register base address

**pinNum** Position of the pin bit field within the Port register

**driveMode** Pin drive mode. Options are detailed in Pin drive mode macros.

**outVal** Logic state of the output buffer driving the pin (1 or 0)

**hsiom** HSIOM (High-Speed input output multiplexer) input selection

#### Code Listing 3 Single GPIO pin initialization- fast example

```

/* Quickly initialize pin P0.3 (e.g. quickly set up a test LED) */

Cy GPIO Pin FastInit(P0_3_PORT, P0_3_NUM, CY GPIO_DM_PULLUP, 1UL, P0_3_GPIO);

```

**GPIO pins in ModusToolbox™ software**

### 6.2.3 **GPIO** port initialization

Initialize a complete port of pins from a single init structure.

The configuration structure used in this function has a 1:1 mapping to the GPIO and HSIOM registers shown below. See the device technical reference manual (TRM) for the register details on how to populate them.

#### Code Listing 4 GPIO port configuration structure example

```

cy stc gpio prt config t portConfig = {

/*.dr

=*/0x00000008u,

/* PX.3 output = 1 */

/*.intrCfg

=*/0x00000080u,

/* PX.3 rising edge interrupt */

=*/ 0x00000400u,

/*.pc

/* PX.3 resistive pull-up */

=*/ 0x0000000u,

/*.pc2

/* PX.3 input buffer on */

/*.sio

=*/ 0x0000000u,

/* PX[7:0] ignored */

/*.selActive

} ;

/* Initialize GPIO port 0 */

if(CY GPIO SUCCESS != Cy GPIO Port Init(GPIO PRT0, &portConfig))

/* Insert error handling */

```

### 6.2.4 Reading from a GPIO pin

Reading from a GPIO pin is the same if a pin is configured using the Device Configurator or PDL. The port and pin are arguments when using the CY GPIO Read function as shown in below.

#### Code Listing 5 Reading GPIO pin

```

/* Scenario: P0.3 was initialized and input buffer enabled */

/* Read the input state of P0.3 */

if(1UL == Cy GPIO Read(P0_3_PORT, P0_3_NUM))

{

/* Insert logic for High pin state */

}

else

{

/* Insert logic for Low pin state */

}

```

# 6.2.5 Writing to a GPIO pin

Writing a value to a GPIO pin is the same if a pin is configured using the Device Configurator or PDL. The port and the pin are arguments when using the CY\_GPIO\_Write function as shown below.

#### GPIO pins in ModusToolbox™ software

#### Code Listing 6 Writing to GPIO pin

```

uint32_t pinState = OUL;

/* Control P0.3 based on the pinState variable */

Cy_GPIO_Write(P0_3_PORT, P0_3_NUM, pinState);

```

### 6.2.6 **GPIO** interrupt

The GPIO interrupt for a pin is configured using one of two methods: using the Device Configurator as seen in Figure 43, or using PDL. If the device configurator is used to set up the pin, the interrupt type can be selected in the side panel as shown in Figure 43. The interrupt type can also be configured in the GPIO PDL configuration structure. See the PSoC<sup>TM</sup> 4 PDL API reference for how to configure the interrupt trigger type.

For more details of using Interrupts with PSoC<sup>™</sup> 4 S series devices in ModusToolbox<sup>™</sup>, see the CE230654 - PSoC<sup>™</sup> 4: GPIO interrupt code example on GitHub. This code example can also be found in the New Application Wizard in ModusToolbox<sup>™</sup>; for more information, see the ModusToolbox<sup>™</sup> code examples section.

# 7 GPIO tips and tricks in PSoC™ Creator

This section provides practical examples of how to use GPIO pins when using PSoC™ Creator.

Table 6 PSoC<sup>™</sup> Creator projects

| #  | Section                                         | PSoC™ 4000,<br>4000S, 4100S,<br>4100S Plus,<br>4100PS, 4500S,<br>4700S | PSoC <sup>™</sup><br>4100_BLE,<br>4100, 4100M | PSoC <sup>™</sup> 4200,<br>4200M, 4200L,<br>4200-BLE |

|----|-------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| 1  | Toggle an LED                                   | ✓                                                                      | <b>✓</b>                                      | <b>✓</b>                                             |

| 2  | Read an input and write to an output            | ✓                                                                      | <b>✓</b>                                      | <b>✓</b>                                             |

| 3  | Drive an output from a digital logic gate       |                                                                        |                                               | <b>✓</b>                                             |

| 4  | Using a bidirectional pin                       |                                                                        | <b>✓</b>                                      | <b>✓</b>                                             |

| 5  | Set the GPIO input/output synchronization       |                                                                        | <b>✓</b>                                      | <b>✓</b>                                             |

| 6  | Toggle GPIOs faster with Data                   | ✓                                                                      | <b>✓</b>                                      | <b>✓</b>                                             |

| 7  | Configure GPIO output enable logic              |                                                                        |                                               | <b>✓</b>                                             |

| 8  | Pin interrupt                                   | ✓                                                                      | <b>✓</b>                                      | <b>✓</b>                                             |

| 9  | Configure GPIO interrupt settings with firmware | <b>✓</b>                                                               | <b>✓</b>                                      | <b>✓</b>                                             |

| 10 | Using both analog and digital on a GPIO         |                                                                        | <b>√</b>                                      | ✓                                                    |

| 11 | Gang pins for more drive/sink current           |                                                                        |                                               | <b>✓</b>                                             |

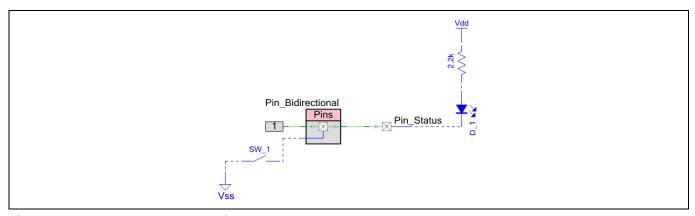

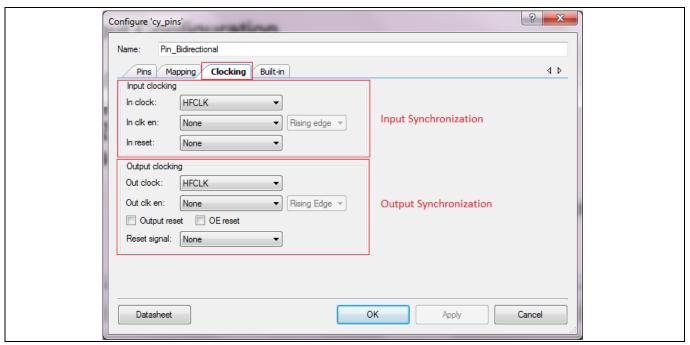

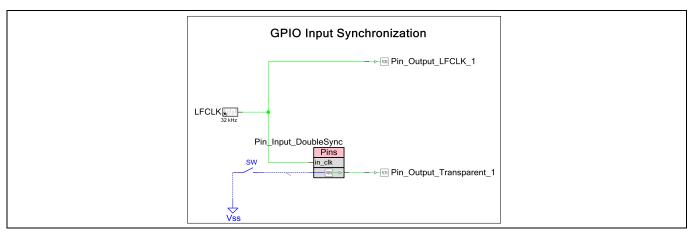

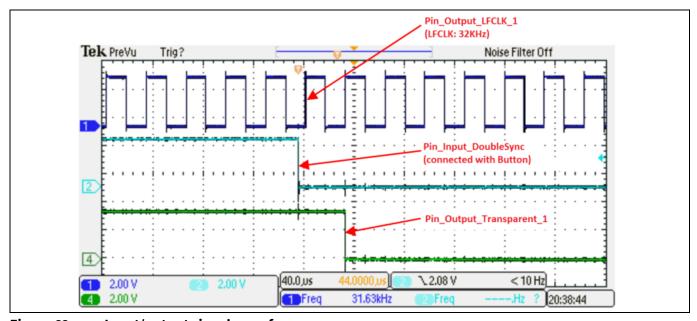

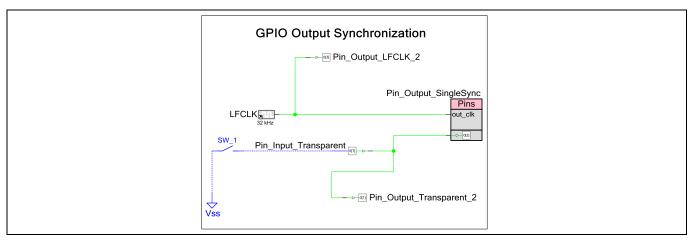

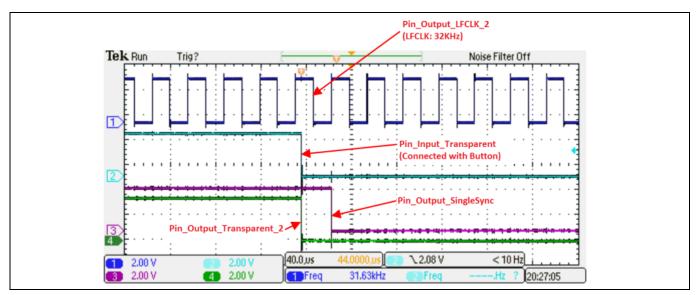

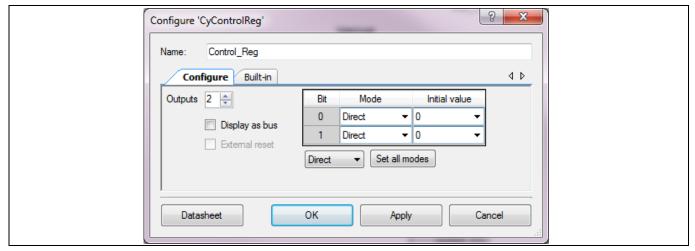

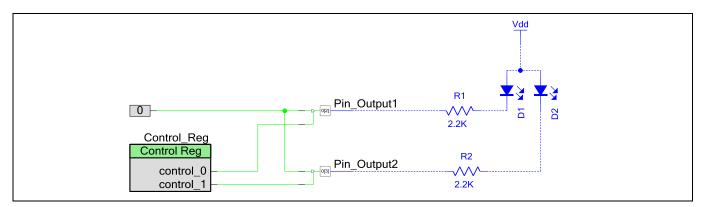

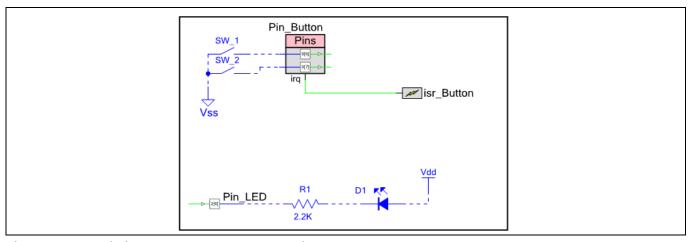

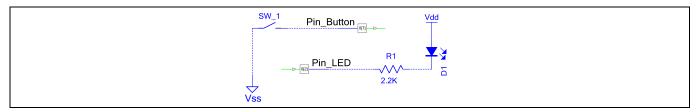

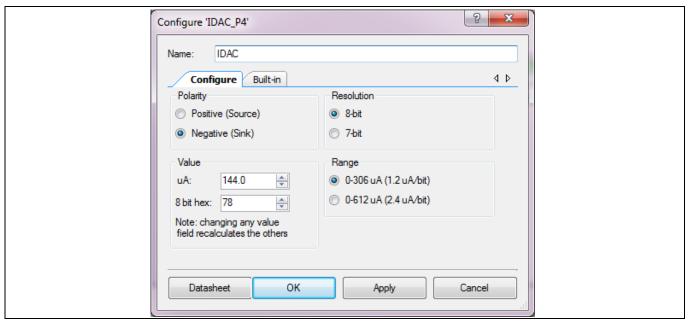

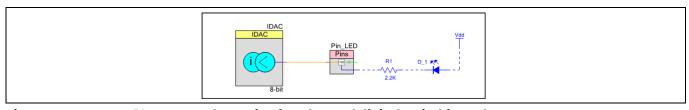

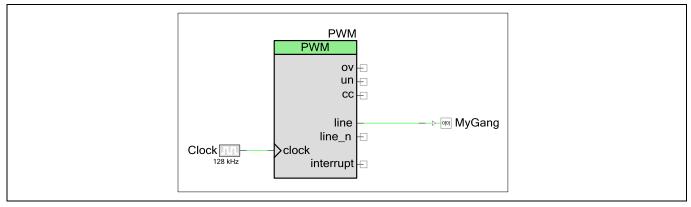

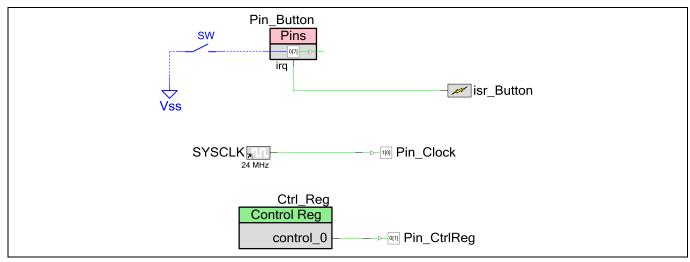

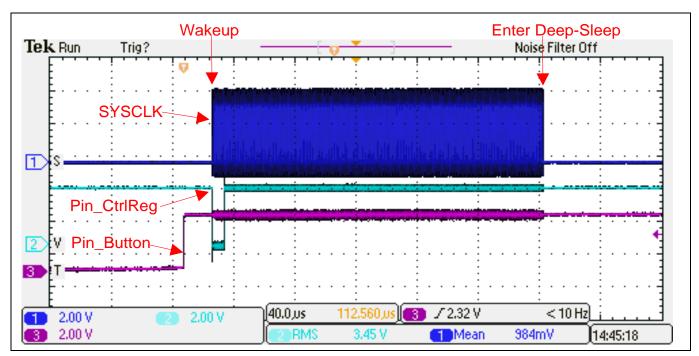

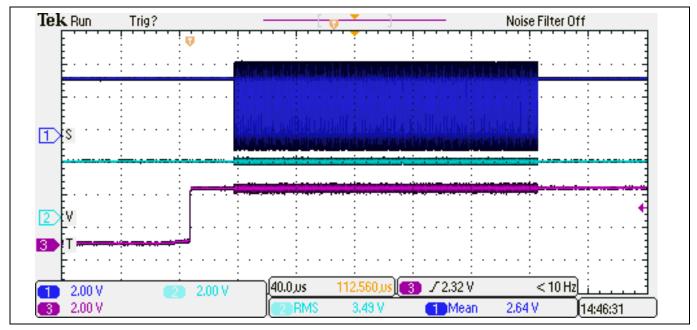

| 12 | Control register handling in Deep Sleep         |                                                                        |                                               | ✓                                                    |