#### AN84810

# PSoC® 3 and PSoC 5LP Advanced DMA Topics

Author: Ranjith M

**Associated Project: Yes**

Associated Part Family: All PSoC® 3 and PSoC 5LP parts

Software Version: PSoC Creator™ 3.0 SP2 Related Application Notes: AN52705, AN61102

AN84810 discusses several advanced PSoC® 3 and PSoC 5LP direct memory access (DMA) topics and design challenges. This application note builds upon the fundamental concepts introduced in AN52705 – Getting Started with DMA. Topics covered include indexed transfers, timing and bandwidth considerations, data alignment, and DMA debugging tips.

#### **Contents**

| 1 | Intro | duction1                                   | (  | 6.1 | Indexed DMA                          | 27 |

|---|-------|--------------------------------------------|----|-----|--------------------------------------|----|

| 2 | PSo   | C Resources2                               | (  | 6.2 | Nested DMA                           | 28 |

|   | 2.1   | PSoC Creator2                              | 7  | Deb | ougging DMA                          | 29 |

|   | 2.2   | Code Examples4                             | -  | 7.1 | Common Issues                        | 29 |

|   | 2.3   | PSoC Creator Help5                         | -  | 7.2 | Debugging Methods                    | 31 |

|   | 2.4   | Technical Support5                         | 8  | Pro | jects                                | 32 |

| 3 | DMA   | A Considerations6                          | 8  | 8.1 | Parallel to Serial Converter Project | 32 |

|   | 3.1   | DMA Terms and Definitions6                 | 8  | 8.2 | Nested DMA Project                   | 32 |

|   | 3.2   | DMA Timing7                                | 9  | Sur | nmary                                | 33 |

|   | 3.3   | DMA Channel Priority Handling10            | 10 | App | pendix A: Memory Maps                | 34 |

|   | 3.4   | Terminating a TD Chain11                   | 11 | App | pendix B: Termination Request Signal | 36 |

| 4 | Mult  | i-Byte Data Alignment12                    | 12 | App | pendix C: DMA Channel Arbitration    |    |

| 5 | Writi | ing to Standard Registers and Components18 |    | Flo | w Diagram                            | 39 |

| 6 | Mod   | lifying a TD Dynamically 27                | 13 | App | pendix D: Misaligned Data Transfers  | 40 |

#### 1 Introduction

Direct memory access (DMA) controllers transfer data between peripherals and memory without CPU intervention. The DMA controller (DMAC) in PSoC<sup>®</sup> 3 and PSoC 5LP features 24 channels and 128 transaction descriptors (TDs), making it very versatile for a wide variety of applications. PSoC Creator™, the development environment for PSoC, has tools including a DMA wizard and component APIs that make it easy to design complex DMA functions.

This application note teaches you advanced methods to get maximum performance from the PSoC DMAC. The topics covered include DMA timing, DMA channel priority handling, multi-byte data alignment, and methods to modify a TD dynamically.

This application note assumes that you are already familiar with the topics discussed in the basic DMA application note, AN52705 – Getting Started with DMA. It also assumes that you are familiar with developing applications using PSoC Creator for PSoC 3 or PSoC 5LP. If you are new to these products, you can find introductions in AN54181 – Getting Started with PSoC 3 and AN77759 – Getting Started with PSoC 5LP. If you are new to PSoC Creator, see the PSoC Creator home page.

### 2 PSoC Resources

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. The following is an abbreviated list for PSoC 4:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP. In addition, PSoC Creator includes a device selection tool.

- Datasheets: Describe and provide electrical specifications for the PSoC 4000, PSoC 4100, and PSoC 4200, PSoC 4xx7 BLE, PSoC 4200-M device families

- CapSense Design Guide: Learn how to design capacitive touch-sensing applications with the PSoC 4 family of devices.

- Application Notes and Code Examples:

Cover a broad range of topics, from basic to advanced level. Many of the application notes include code examples. PSoC Creator provides additional code examples see Code Examples.

Technical Reference Manuals (TRM):

Provide detailed descriptions of the architecture and registers in each PSoC 4 device family.

#### • Development Kits:

- CY8CKIT-040, CY8CKIT-042, and CY8CKIT-044 PSoC 4 Pioneer Kits are easy-to-use and inexpensive development platforms. These kits include connectors for Arduino™ compatible shields and Digilent® Pmod™ daughter cards.

- CY8CKIT-049 is a very low-cost prototyping platform for sampling PSoC 4 devices.

- CY8CKIT-001 is a common development platform for all PSoC family devices.

- The MiniProg3 device provides an interface for flash programming and debug.

#### 2.1 PSoC Creator

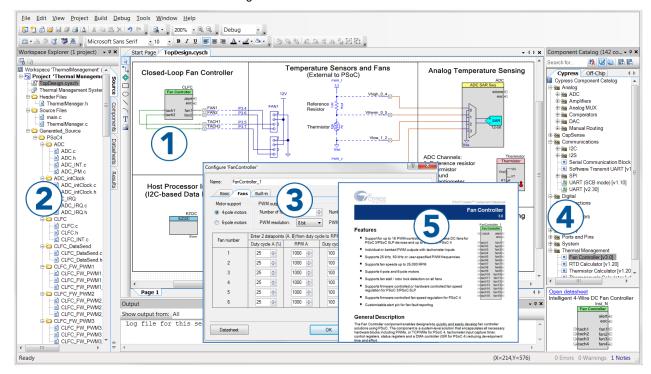

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of systems based on PSoC 3, PSoC 4, and PSoC 5LP. See Figure 1 – with PSoC Creator, you can:

- Drag and drop Components to build your hardware system design in the main design workspace

- Codesign your application firmware with the PSoC hardware

- Configure Components using configuration tools

- 4. Explore the library of 100+ Components

- 5. Review Component datasheets

Figure 1. PSoC Creator Features

#### 2.2 Code Examples

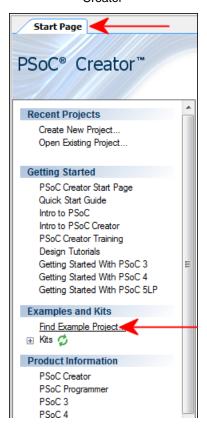

PSoC Creator includes a large number of code example projects. These projects are available from the PSoC Creator Start Page, as Figure 2 shows.

Example projects can speed up your design process by starting you off with a complete design, instead of a blank page. The example projects also show how PSoC Creator Components can be used for various applications. Code examples and datasheets are included, as Figure 3 shows.

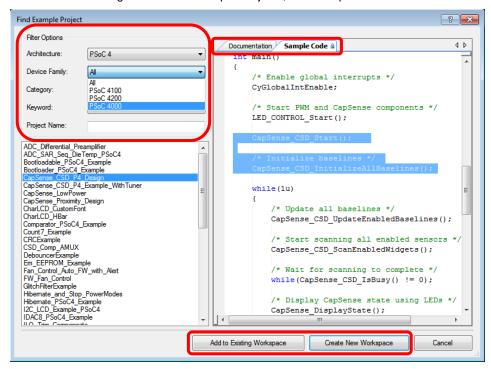

In the Find Example Project dialog shown in Figure 3, you have several options:

- Filter for examples based on architecture or device family, i.e., PSoC 3, PSoC 4 or PSoC 5LP; category; or keyword

- Select from the menu of examples offered based on the Filter Options

- Review the datasheet for the selection (on the Documentation tab)

- Review the code example for the selection. You can copy and paste code from this window to your project, which can help speed up code development, or

- Create a new project (and a new workspace if needed) based on the selection. This can speed up your design process by starting you off with a complete, basic design. You can then adapt that design to your application.

Figure 2. Code Examples in PSoC Creator

Figure 3. Code Example Projects, with Sample Code

#### 2.3 PSoC Creator Help

Visit the PSoC Creator home page to download the latest version of PSoC Creator. Then, launch PSoC Creator and navigate to the following items:

- Quick Start Guide: Choose Help > Documentation > Quick Start Guide. This guide gives you the basics for developing PSoC Creator projects.

- Simple Component example projects: Choose File > Open > Example projects. These example projects demonstrate how to configure and use PSoC Creator Components.

- Starter designs: Choose File > New > Project > PSoC 4 Starter Designs. These starter designs demonstrate the unique features of PSoC 4.

- System Reference Guide: Choose Help > System Reference > System Reference Guide. This guide lists and describes the system functions provided by PSoC Creator.

- Component datasheets: Right-click a Component and select "Open Datasheet." Visit the PSoC 4 Component Datasheets page for a list of all PSoC 4 Component datasheets.

- **Document Manager**: PSoC Creator provides a document manager to help you to easily find and review document resources. To open the document manager, choose the menu item **Help** > **Document Manager**.

#### 2.4 Technical Support

If you have any questions, our technical support team is happy to assist you. You can create a support request on the Cypress Technical Support page.

If you are in the United States, you can talk to our technical support team by calling our toll-free number: +1-800-541-4736. Select option 8 at the prompt.

You can also use the following support resources if you need quick assistance.

- Self-help

- Local Sales Office Locations

### 3 DMA Considerations

The DMAC is one of the most useful components in PSoC 3 and PSoC 5LP. However, it also exposes a whole new set of design considerations with which you may not be familiar. Here are some points to consider when designing a system with DMA.

#### 3.1 DMA Terms and Definitions

Following is a list of terms and definitions that are used in this application note. These terms are described in detail in AN52705 – Getting Started with DMA but are included here for clarity.

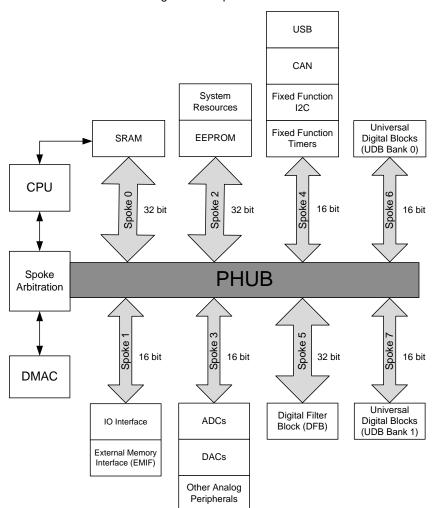

**Peripheral HUB (PHUB)**: The PHUB is the central hub that has data buses connected between the CPU, DMAC, and on-chip peripherals and memory.

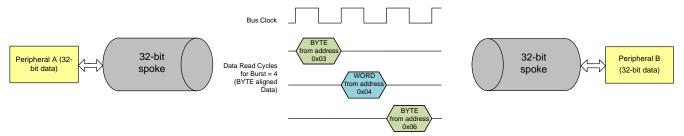

**Spoke**: Spokes are data buses that branch out from the PHUB to peripherals. Spoke widths can be 16 or 32 bits; see the device datasheet and Technical Reference Manual (TRM) for details. Figure 4 shows the PHUB and spoke connections.

**Channel**: DMA channels use the PHUB to transfer data. A channel fetches transaction descriptors, accesses the PHUB spokes for the source and the destination, and transfers data.

**Transaction descriptor**: A TD stores all information required for a data transfer, including the source and destination addresses and the number of bytes to transfer. Multiple chained TDs can be allocated to a single DMA channel.

Figure 4. Peripheral HUB

#### 3.2 DMA Timing

This section describes how to calculate the best-case timing for a DMA channel. Many factors can cause the DMA to deviate from this best-case timing; those factors are also discussed here.

The PSoC DMAC operates at the same frequency as the CPU, which is the bus clock frequency. Most PSoC family members run at a bus clock frequency as high as 67 MHz. DMA data transfers are either intra-spoke (within the same PHUB spoke) or inter-spoke (between different PHUB spokes).

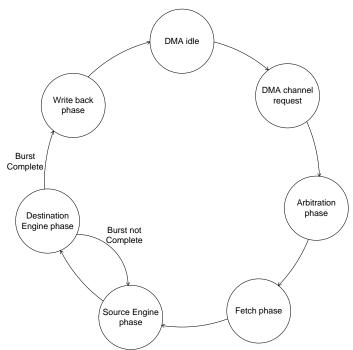

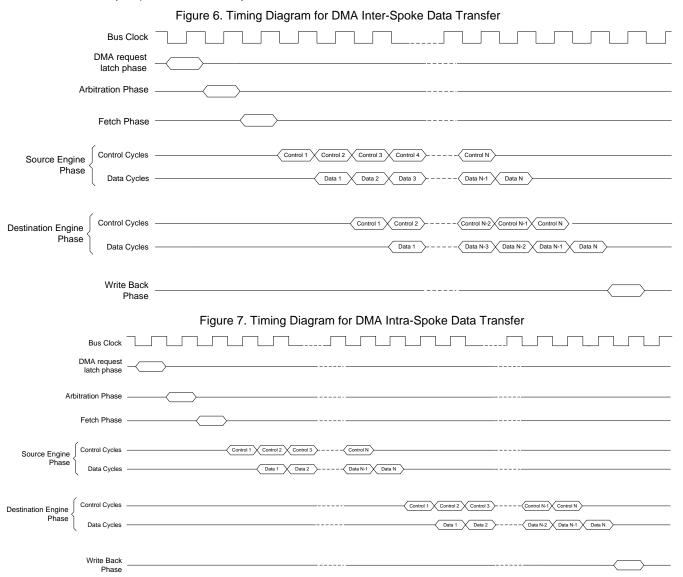

For each data transfer, the DMA implements a set of phases, as Figure 5, Figure 6, and Figure 7 show:

- DMA request (DRQ) latch phase: It takes one clock cycle for the DMA request to be latched into the DMAC.

- Arbitration phase: This phase is used to arbitrate between simultaneous requests from multiple DMA channels. One clock cycle is required for this phase. If a channel loses arbitration, it reenters the queue and waits for the next arbitration cycle.

- Fetch phase: This phase is used fetch the TD and configuration information for the channel. One clock cycle is required.

- Source engine phase: This phase is used to select the spoke to which the source memory or peripheral is connected. If the spoke is being used by another bus master, that is, the CPU, data transfer from the source is delayed until the spoke is available. The source engine phase initially consists of a bus control cycle followed by a data cycle. Then the control and data cycles are pipelined in parallel.

- Destination engine phase: This phase selects the spoke to which the destination peripheral is connected. The data collected in the source engine phase is transferred to the destination peripheral as soon as the spoke is available. The destination engine phase initially consists of a bus control cycle followed by a data cycle. Then the control and data cycles are pipelined in parallel.

- Write back phase: In this phase, the TD and DMA channel configurations are updated after the data transfer. This phase requires one clock cycle.

Figure 5 shows a simple state diagram for a DMA transfer. Figure 6 and Figure 7 on page 8 show the actual timing for an inter-spoke and an intra-spoke data transfer.

Figure 5. DMA Data Transfer State Diagram

The number of clock cycles required for the source engine and destination engine phases is the same for an interspoke and an intra-spoke data transfer. However, the two phases can happen in parallel for an inter-spoke transfer, which usually requires fewer clock cycles.

When calculating DMA timing, start with the ideal conditions, as follows:

- Only one DMA channel is active, and there is no arbitration between multiple DMA channels.

- There is no arbitration between the DMAC and the CPU. Note that the CPU and the DMAC can access different spokes simultaneously.

- The source and the destination spokes are available when the transfer is to be done.

- The source and destination spoke widths are the same.

- The data length is an even multiple of the spoke width, in bytes.

- The source and destination start addresses are on a spoke width boundary.

The number of bursts required for a DMA transfer N is defined as follows:

Number of bursts

$$[N] = \frac{(Transfer\ Count)}{(Spoke\ Width)}$$

(1)

where transfer count and spoke width are in bytes. See AN52705 for details on DMA burst transfers.

If the ideal conditions are met, the number of clock cycles required for an inter-spoke data transfer is calculated as follows:

C = 1 clock cycle to latch the drq signal +

$C = N + 7 \tag{2}$

1 clock cycle for arbitration phase +

1 clock cycle for fetch phase +

(N + 3) clock cycles for source and destination engine phases +

1 clock cycle for write back phase

The number of clock cycles required for an intra-spoke data transfer is calculated as follows:

C = 1 clock cycle to assert the drq signal +

$C = 2N + 6 \tag{3}$

1 clock cycle for arbitration phase + 1 clock cycle for fetch phase +

(N + 1) clock cycles for source engine phase +

(N + 1) clock cycles for destination engine phase +

1 clock cycle for write back phase

The exact number of clock cycles required for a DMA transaction under non-ideal conditions varies depending on the conditions. Use the following tips to calculate the clock cycles required for a non-ideal DMA transaction:

- The clock cycle to assert the drq signal is not required for continuous DMA transfers. For example, if the transfer length is set to 100 and the request per burst is set to 0 (complete transfer in a single request), the latching of the request is required only for the first DMA transfer.

- 2. The arbitration between multiple DMA channels takes only one clock cycle. If the DMAC is already performing a data transfer, arbitration is performed in parallel with the data transfer, and this clock cycle is hidden.

- 3. If the CPU is competing with the DMAC for a spoke, the DMAC must wait until the CPU releases the spoke if the CPU is assigned a higher priority than the DMAC. The priority of the CPU over the DMAC is controlled using the spk\_cpu\_pri[6:0] bits in the PHUB\_CFG register. See the "PHUB" section in the PSoC Registers TRM for details.

- 4. If the source or destination start address is not on a spoke width boundary, the number of clock cycles required for the DMA transfer varies depending upon the spoke width and the addresses. The formulas in Equations (1) and (2) for inter-spoke and intra-spoke transfers can also be used in this case, with a change in the value of N as calculated by Equation (3).

- If the source and destination widths are 32 bits, N is unchanged if the source and destination addresses are 32-bit DWORD aligned. N is multiplied by 2 if the source and destination are WORD aligned, and N is multiplied by 3 if the source and destination are BYTE aligned. See the section Multi-Byte Data Alignment for details.

- 5. If endian swapping is enabled for an inter-spoke DMA transaction, the destination transfer cannot occur until the last source byte has been put into the DMAC FIFO. The DMAC must write the last source byte to the first location of the destination to do the endian swap. The effective value of N in this case is calculated as (N calculated with Source spoke width) + (N calculated with Destination spoke width) 1.

- 6. If the source and destination peripherals have unequal spoke widths, the number of clock cycles required for a transfer is governed by the narrower spoke width. In this case, N = (Transfer Count) / (Narrower Spoke Width).

Table 1 shows the number of clock cycles required for a DMA transfer in different scenarios to transfer N bursts of data.

Table 1. Number of Clock Cycles for DMA Transfer between PSoC Resources

| Use Case                   | Number of Clock Cycles |

|----------------------------|------------------------|

| Flash to SRAM              | N + 7                  |

| SRAM to SRAM               | 2N + 6                 |

| SRAM to peripherals        | N + 7                  |

| Peripherals to SRAM        | N + 7                  |

| Peripherals to peripherals | 2N + 6                 |

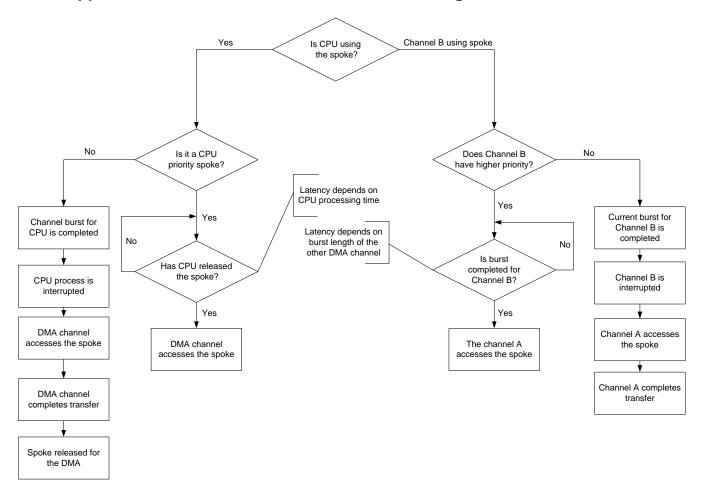

Appendix C: DMA Channel Arbitration Flow Diagram provides a flow diagram for DMA channel arbitration.

### 3.3 DMA Channel Priority Handling

Each of the 24 DMA channels is assigned a priority value ranging from 0 to 7, with 0 being the highest priority and 7 being the lowest. Since there are only 8 different priorities and 24 DMA channels, multiple channels may have the same priority.

For channels having the same priority, two methods are used to decide which channel gets priority:

- 1. Simple priority: The lowest channel number has a higher priority. This is enabled by default.

- 2. Round robin: Round robin priority ensures that all channels get an equal opportunity to access the PHUB. This is disabled by default and is set using the API function CyDmaChRoundRobinEnable().

For channels with different priorities, two rules are applied to determine which channel gets priority:

- 1. Simple priority: The channel with the lowest priority number gets priority.

- 2. Grant allocation fairness algorithm: The grant allocation fairness algorithm is designed such that even the lowest priority channels get access once in a while. With this method, channels with priorities 0 and 1 always have 100 percent access and are not interrupted, with the exception that 0 is higher priority than 1. The channels with priorities 2 to 7 are given access according to Table 2.

Table 2. Channel Priority Distribution

| Channel Priority | Bandwidth (%) |

|------------------|---------------|

| 2                | 50            |

| 3                | 25            |

| 4                | 12.5          |

| 5                | 6.25          |

| 6                | 3             |

| 7                | 1.5           |

The grant allocation fairness algorithm is enabled by default. You can disable it by setting the simple priority bit (bit 23) in the PHUB\_CFG register. See the "PHUB" section of the PSoC 3 Registers TRM and PSoC 5LP Registers TRM for details.

Note that Table 2 applies only if DMA channels with all the priorities are requesting simultaneously. Otherwise, the DMA channel with a higher priority is given more access than Table 2 shows.

Figure 8 shows a channel priority wheel that describes how the next 63 requests are handled if all channels with priorities 2 to 7 are requesting simultaneously.

Figure 8. DMA Channel Priority Wheel

The bandwidth utilization of the DMA channel can be defined as the number of clock cycles utilized by the DMA channel for the data transfer as a percentage of the total number of available clock cycles across sustained DMA requests of burst length N.

For inter-spoke data transfers:  $BW = \frac{N}{(N+7)} \times 100$  (4)

For intra-spoke data transfers:  $BW = \frac{2N}{(2N+6)} \times 100$  (5)

If a channel with priority 2 to 7 is **not** requesting, the slots of the missing channel priority are used by the channel with the highest priority. In that case, channels with a higher priority get more access than Figure 8 shows.

#### 3.4 Terminating a TD Chain

In some cases, a TD must be terminated before data transfer is completed. This is called non-count termination. There are three methods to terminate a TD and abort a DMA transaction:

- API function call to terminate the current TD [CyDmaChSetRequest(channel, CPU\_TERM\_TD)]

- API function call to terminate the current TD chain [CyDmaChSetRequest(channel, CPU\_TERM\_CHAIN)]

- Hardware trq signal

Use the API function CyDmaChSetRequest() to terminate either the current TD or the entire TD chain. This API function disables the DMA channel and terminates the chain of TDs if the second parameter is set to CPU\_TERM\_CHAIN. This API terminates the current TD but does not disable the DMA channel if the second parameter is set to CPU\_TERM\_TD.

When one of these methods is used, the DMA channel is reconfigured as if the current transaction has completed normally. If enabled, the nrq signal is activated; see the DMA Component datasheet for details.

**Note:** The DMA channel completes any ongoing transaction before terminating, so termination may require some cycles for the final transaction to be complete. The DMAC may transfer more data bytes before terminating the TD. You should be extremely careful while accessing these memory locations after a terminate TD API request as the function is not blocking and may return before the data transfer has been actually terminated.

#### 3.4.1 Using the Hardware trq Signal

You can also use the hardware signal trq, or termination request. This signal, when asserted during the source engine phase of a transaction, stops the DMA transaction.

This is an effective way to terminate a TD using a hardware signal when the transfer count is set to zero. If the transfer count parameter of a TD is set to zero, the TD runs indefinitely unless it is terminated by a non-count termination. See Appendix B: Termination Request Signal for an example of how to use the trg signal.

**Note:** The trq signal is used only when the DMA is trying to transfer data. A positive edge on this line is ignored at all other times.

## 4 Multi-Byte Data Alignment

One feature of the DMAC is that it can transfer more than one byte in a single bus cycle. This allows more efficient and faster data transfers.

The section DMA Timing introduced the concept of N:  $Number\ of\ bursts\ [N]\ =\ \frac{(Transfer\ Count)}{(Spoke\ Width)} \tag{6}$

Here are some examples:

For Transfer Count = 2; Spoke Width = 2: N = 1For Transfer Count = 4; Spoke Width = 2: N = 2

For Transfer Count = 3; Spoke Width = 2: N = 2 (always round up to the next integer)

For Transfer Count = 4; Spoke Width = 4: N = 1

All of these calculations assume that the source and destination addresses are aligned. There are three possible ways for addresses to be aligned: BYTE, WORD, and DWORD, as Figure 9 shows:

- BYTE = All addresses

- WORD = Even or 16-bit addresses: 0x00, 0x02, 0x04, 0x06, 0x08, 0x0A, 0x0C, 0x0E, and so on

- DWORD = 32-bit addresses: 0x00, 0x04, 0x08, 0x0C, and so on

Figure 9. Notation to Represent Possible Data Alignments in the Memory

|   | 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05 | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|---|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|   |      | DW   | ORD  |      |      | DWC  | ORD  |      |      | DWG  | ORD  |      |      | DWC  | ORD  |      |

| Ī | WC   | RD   | WO   | RD   | wo   | RD   | WC   | RD   | WC   | RD   | WO   | RD   | wo   | RD   | wo   | RD   |

|   | BYTE |

To reduce the number of clock cycles needed for a data transfer, align the source and destination addresses with the spoke width boundaries. An address is aligned with a 32-bit spoke width boundary if the address is DWORD aligned. An address is aligned with a 16-bit wide spoke if the address is WORD aligned. BYTE-aligned addresses are never aligned with any spoke width boundary.

**Note:** In some cases, if the addresses are not aligned with the spoke width boundaries, the DMAC may fetch incorrect data from the source or write incorrect data to the destination address. Appendix D: Misaligned Data Transfers details the results of misaligned data transfers.

You can avoid incorrect data transfers by using one of the following methods:

- 1. Enable the increment source address or increment destination address option in the TD configuration.

- 2. Force the source and destination addresses to the spoke width boundaries.

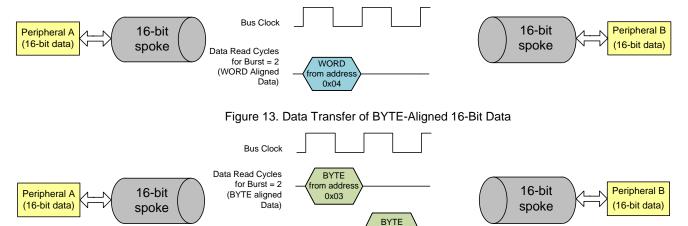

Figure 10 and Figure 11 show WORD-aligned and BYTE-aligned arrangements for 16-bit data, respectively.

Figure 10. WORD-Aligned Arrangement of 16-Bit Data

| 0x00 | 0x01 | 0x02 | 0x03 | 0x04   | 0x05  | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|------|------|------|------|--------|-------|------|------|------|------|------|------|------|------|------|------|

|      |      |      |      | DATA ' | VALUE |      |      |      |      |      |      |      |      |      |      |

| WORD |      | WO   | RD   | WC     | RD    | WC   | RD   | WC   | RD   | WC   | RD   | wc   | RD   | WC   | RD   |

Figure 11. BYTE-Aligned Arrangement of 16-Bit Data

| 0x00 | 0x01 | 0x02 | 0x03 | 0x04  | 0x05 | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|

|      |      |      | DATA | VALUE |      |      |      |      |      |      |      |      |      |      |      |

| BYTE | BYTE | BYTE | BYTE | BYTE  | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE | BYTE |

A data transfer from address location "n" is carried out in a single clock cycle if the data at the source is aligned with the spoke boundary, as Figure 12 shows. When the data is BYTE aligned, data transfer takes two clock cycles, as Figure 13 shows.

Figure 12. Data Transfer of WORD-Aligned 16-Bit Data

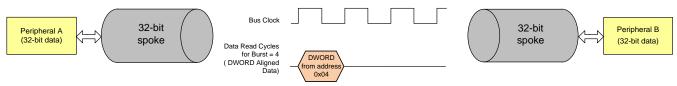

Figure 14, Figure 15, and Figure 16 show the DWORD-aligned, WORD-aligned, and BYTE-aligned arrangements for a 32-bit data transfer, respectively.

from address 0x04

Figure 14. DWORD-Aligned Arrangement of 32-Bit Data

|   | 0x00  | 0x01 | 0x02 | 0x03 | 0x04 | 0x05   | 0x06  | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|---|-------|------|------|------|------|--------|-------|------|------|------|------|------|------|------|------|------|

|   |       |      |      |      |      | DATA ' | VALUE |      |      |      |      |      |      |      |      |      |

| Ī | DWORD |      |      |      |      | DW     | ORD   |      |      | DWC  | ORD  |      |      | DWC  | ORD  |      |

Figure 15. WORD-Aligned Arrangement of 32-Bit Data

| 0x00 | ones ones  |    | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |    |    |    |

|------|------------|----|------|------|------|------|------|------|------|------|------|------|----|----|----|

|      | DATA VALUE |    |      |      |      |      |      |      |      |      |      |      |    |    |    |

| WORD |            | WO | RD   | WC   | RD   | WO   | RD   | WC   | RD   | WC   | RD   | WC   | RD | wo | RD |

Figure 16. BYTE-Aligned Arrangement of 32-Bit Data

| 0x00 | 0x01 | 0x02 | 0x03 | 0x04   | 0x05  | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

|------|------|------|------|--------|-------|------|------|------|------|------|------|------|------|------|------|

|      |      |      |      | DATA ' | VALUE |      |      |      |      |      |      |      |      |      |      |

| BYTE | BYTE | BYTE | BYTE | wo     | RD    | BYTE |

The data transfer from address location "n" is carried out in a single clock cycle if the data at the source is aligned with the spoke boundary, as Figure 17 shows. When the data is WORD aligned, the data transfer takes two clock cycles, and when the data is BYTE aligned, data transfer takes three clock cycles, as Figure 18 and Figure 19 show.

Figure 17. Data Transfer of DWORD-Aligned 32-Bit Data

Figure 18. Data Transfer of WORD-Aligned 32-Bit Data

Figure 19. Data Transfer of BYTE-Aligned 32-Bit Data

**Note:** If the transfer count is odd, the number of cycles is different. For example a 3-byte burst on a 32-bit spoke takes two clock cycles, even if the addresses are DWORD aligned: one cycle to transfer two bytes, and another to transfer the third byte. Also, if increment source and destination address are not enabled in the TD configuration, only the first two bytes are transferred.

For the Keil compiler, use the keyword \_at\_ to force variables into absolute address locations in SRAM. This ensures that variables are aligned with even address boundaries, for example:

```

uint8 myVariable _at_ 0x1000;

```

Note: Variables forced to absolute memory locations cannot be initialized.

For the GCC compiler, use the keyword <u>\_\_attribute\_\_</u> to force variables to 16-bit or 32-bit address boundaries. For example:

```

uint32 var __attribute__ ((aligned(32)));

```

You can replace the number 32 in the previous format with 16 to align the variables with 16-bit address boundaries. You must use the appropriate keywords to align the data with the spoke width boundaries, depending upon your compiler.

#### 4.1.1 Aligning UDBs

You can do DMA transfers to and from the registers in UDB-based PSoC Creator Components, though enabling the increment source or destination address is not always a viable option. To work around this, you may need to force the Component to be aligned with an address boundary. You can use PSoC Creator directives to force a UDB-based Component to start at a specific address.

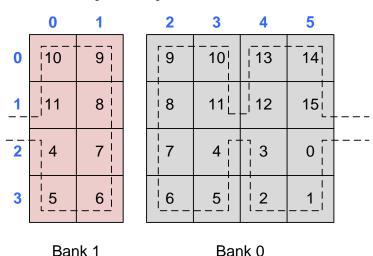

There are as many as 24 UDBs in a PSoC device, and each set of UDB registers has a particular base address. The base addresses for the UDBs are provided in the PSoC 3 Registers TRM and PSoC 5LP Registers TRM. The UDBs are distributed in the form of two banks and are numbered in a specific fashion, as Figure 20 shows. The dashed line represents how UDBs are chained.

Figure 20. Organization of PSoC UDBs

The numbers in blue on the top and left of the diagram are the indices that PSoC Creator uses to address each of the UDBs. The numbers inside the squares indicate the UDB number. For example, UDB0 is addressed as U(2,5). To find out where PSoC Creator places a Component in the UDB array, follow these steps:

1. Place a 16-bit UDB-based Counter Component in the TopDesign, as Figure 21 shows, and build the project.

Counter

Counter

Counter

tc

comp

count

count

clock

12 MHz

16-bit (UDB)

Figure 21. Counter Component

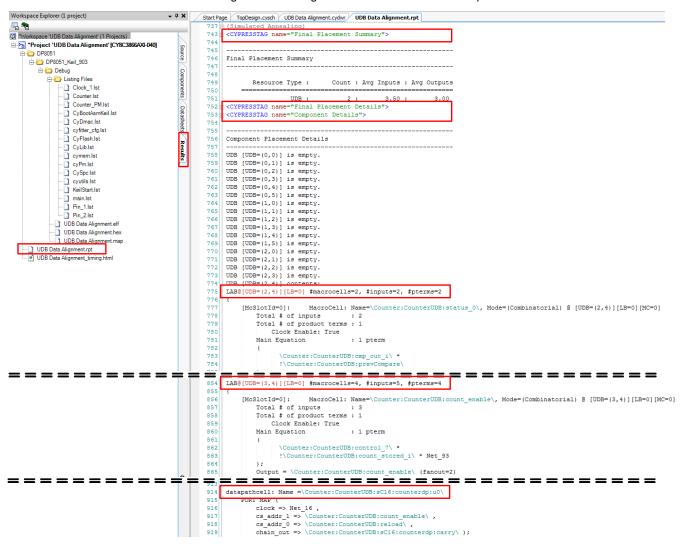

2. Examine the .rpt file to find the location where PSoC Creator has placed the Component, as Figure 22 shows.

Figure 22. Finding the UDB Location of the Component

Figure 22 shows that PSoC Creator has placed the Component in UDBs U(2,4) and U(3,4) or UDB3 and UDB2. The LSB data path of the Component is located in UDB2. In the Registers TRM, the FIFO 0 (F0) address for UDB2 is 0x6442, which is a WORD-aligned address. Note that the UDB register space is on a 16-bit spoke, and the DMAC can transfer two bytes, or one word, in one clock cycle on this spoke.

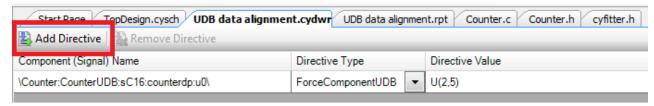

If the Component placement was unaligned for some reason, follow these steps to align the counter FIFO 0 addresses with a word address boundary:

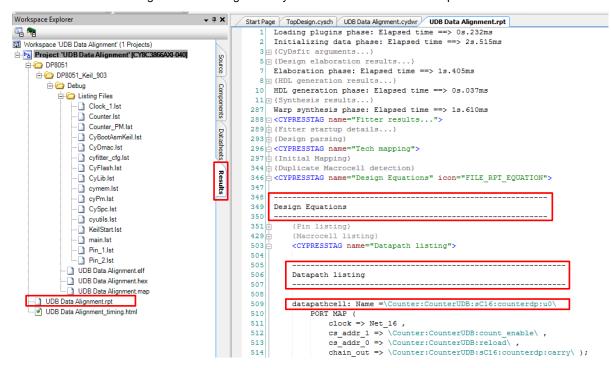

1. Open the .rpt file and locate the line "Design Equations," as Figure 23 shows. Expand the list by clicking on the [+] symbol left of the line. Locate the line "Datapath listing" to find the fully elaborated name of the Component.

Figure 23. Locating the Fully Elaborated Name of the Component

Open the .cydwr file, go to the Directives tab, and add a directive using the Add Directive button, as Figure 24 shows. In the column "Component (Signal) Name," type the fully elaborated Component name obtained from the .rpt file. Select "ForceComponentUDB" as the directive type. Enter the required UDB location as mentioned previously. To force the Counter to UDB0, where the FIFO 0 address is 0x6440, which is WORD aligned, enter U(2,5).

Figure 24. Adding the Directive

3. Rebuild the project, and then check the .rpt file again to confirm that the counter was placed in UDB(2,5).

## 5 Writing to Standard Registers and Components

The DMAC can transfer data to and from almost any memory or register location in PSoC. This includes the memory, UDBs, and registers of any PSoC Creator Component. However, the DMA Wizard provided with PSoC Creator supports data transfer between only a few Components.

To use DMA to transfer data between Components that are not supported by the DMA Wizard, you must find the addresses of the Components' registers. To do so, use the PSoC register maps in the PSoC 3 Registers TRM and PSoC 5LP Registers TRM.

For example, the following steps show how to transfer a byte of data from a GPIO port to an SRAM location.

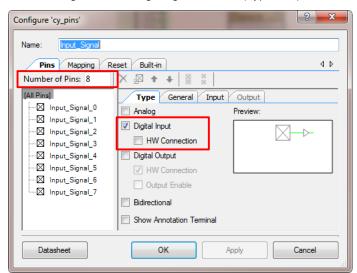

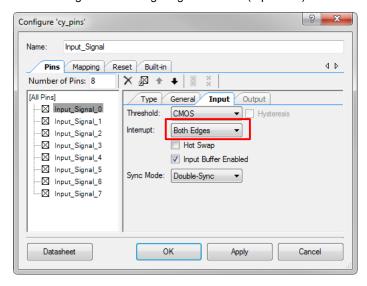

- 1. Place a Pins Component in the TopDesign and change the number of pins to 8, as Figure 25 shows. Deselect the option hardware connection (HW Connection).

- Enable the port interrupt control unit (PICU) interrupt, as Figure 26 shows. The PICU interrupt is used to trigger the DMA channel to initiate a data transfer.

Figure 25. Configuring GPIO Pins (Type Tab)

Figure 26. Configuring GPIO Pins (Input Tab)

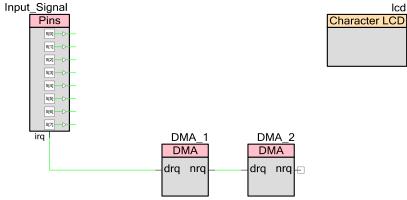

3. Place two DMA Components and a Character LCD Component in the TopDesign. Wire the Components as Figure 27 shows.

Figure 27. Completed TopDesign

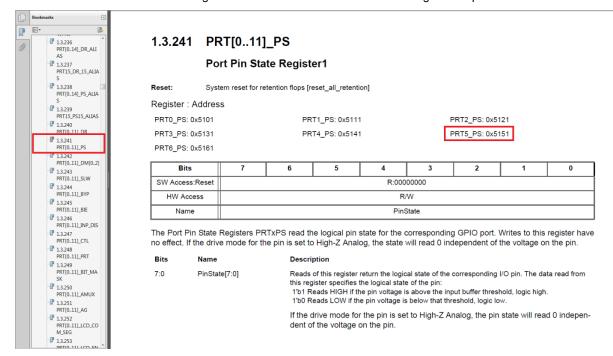

4. Assign a suitable port for the GPIO using the .cydwr file. Then, if you selected port 5, for example, locate the address of port 5 in the register map, as Figure 28 shows.

Figure 28. Locate the Address From the Register Map

5. You can use either the absolute address (0x5151) or the alias (Input\_Signal\_PS) in your code to address the port pin state register.

You can find out the alias names for the Component registers from the ".h" generated file of the Component. These files are automatically generated by PSoC Creator when you build the project. In this case, the alias name Input\_Signal\_PS is defined in the file *Input\_Signal.h*.

- 6. The PICU interrupt must be cleared each time it is triggered. All interrupts from the port are masked until the interrupt is cleared. The PICU interrupt is cleared by reading the interrupt status register of the port.

- 7. This example uses two DMA channels: one to transfer the GPIO input value to SRAM and the other to clear the PICU interrupt.

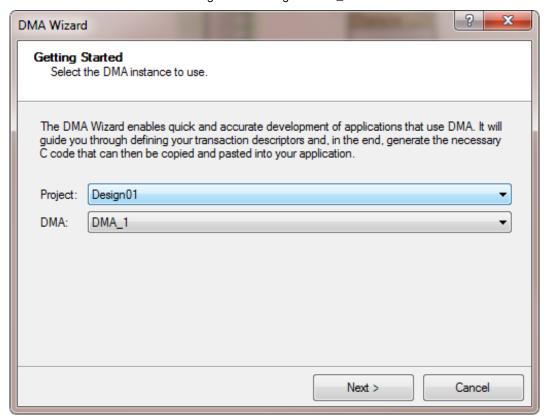

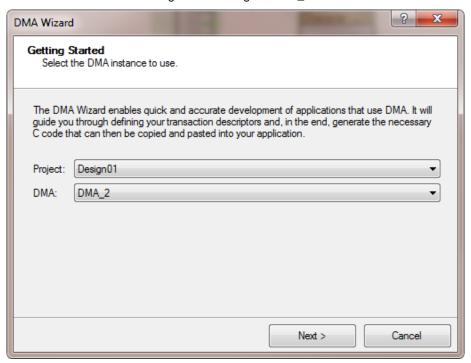

- 8. Open the DMA Wizard from the PSoC Creator menu via Tools > DMA Wizard, as Figure 29 shows.

Figure 29. Configure DMA\_1

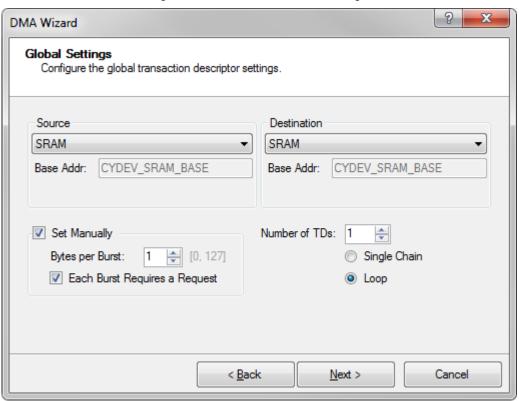

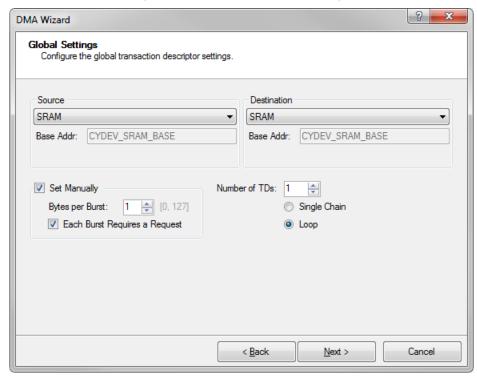

- 9. Configure the options as Figure 30 shows, and click Next.

- 10. Leave the source and destination at the default values (SRAM) for now. The DMA Wizard supports only a specific set of Components by default. You must edit the source value in the code later to suit your requirement. The SRAM location should be updated each time the value on the GPIO pins changes. This requires only a single TD that runs when a DMA request is received.

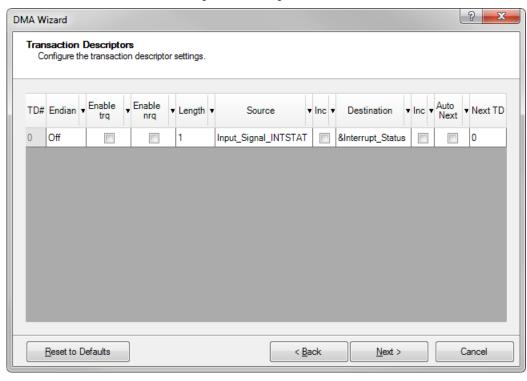

Figure 30. DMA Channel Global Settings

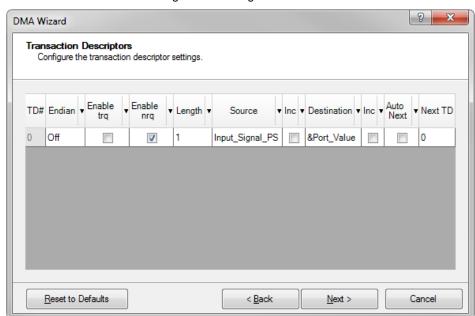

11. Enable the nrq signal. The nrq signal of DMA\_1 is used to trigger DMA\_2. Set the source address value as described in step 5. The destination is the address of the SRAM location to which the data from the GPIO pins is stored. Figure 31 shows the TD configuration window after setting these values.

Figure 31. Configure the TDs

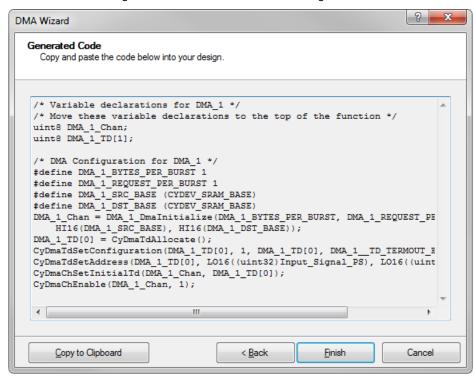

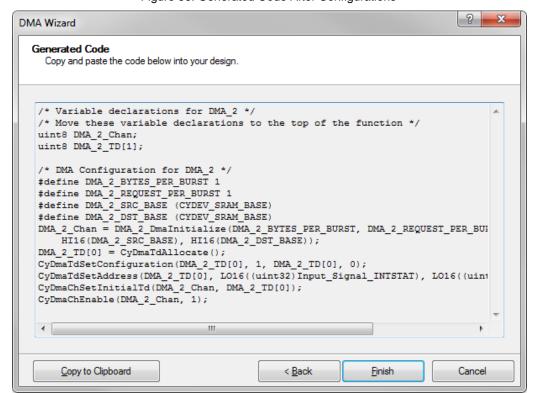

12. Copy the generated code, as Figure 32 shows, into the clipboard, and paste it into the main.c file.

Figure 32. Generated Code After Configurations

13. Configure the second DMA channel similarly, as Figure 33 through Figure 36 show.

Figure 33. Configure DMA\_2

Figure 34. DMA Channel Global Settings

Figure 35. Configure the TD

Figure 36. Generated Code After Configurations

- 14. Edit *main.c.* In the #define statements, change DMA\_1\_SRC\_BASE and DMA\_2\_SRC\_BASE to CYDEV\_PERIPH\_BASE, since the GPIO is a peripheral. Add code to start the Character LCD Component. The resulting code is similar to Code 1.

- 15. You can verify the functionality of the project by changing the data input to the GPIO pins. The character LCD displays the decimal value of the data input applied to the GPIO pins.

This procedure is similar for any other standard Component, or for PSoC registers. Be sure to edit the generated code appropriately so that the base address for the source and the destination is correct. The base addresses for different sources and destinations are available in the PSoC Creator generated file *cydevice\_trm.h* after building a project. Table 3 shows a list of commonly used base addresses.

Table 3. Commonly Used Base Addresses

| Source/Destination | PSoC 3            | PSoC 5LP              |

|--------------------|-------------------|-----------------------|

| Flash              | CYDEV_FLS_BASE    | CYDEV_FLASH_BASE      |

| SRAM               | CYDEV_SRAM_BASE   | CYDEV_SRAM_DATA_MBASE |

| Peripherals        | CYDEV_PERIPH_BASE | CYDEV_PERIPH_BASE     |

#### Code 1. Completed Code for Transferring Data Bytes from GPIO Pins to SRAM

```

#include <device.h>

/* DMA Configuration for DMA 1 */

#define DMA 1 BYTES PER BURST 1

#define DMA 1 REQUEST PER BURST 1

#define DMA 1 SRC BASE (CYDEV PERIPH BASE)

#define DMA 1 DST BASE (CYDEV SRAM BASE)

/* DMA Configuration for DMA \frac{1}{2} */

#define DMA 2 BYTES PER BURST 1

#define DMA 2 REQUEST PER BURST 1

#define DMA 2 SRC BASE (CYDEV PERIPH BASE)

#define DMA 2 DST BASE (CYDEV SRAM BASE)

uint8 Port Value;

uint8 Interrupt_Status;

void main()

uint8 DMA 1 Chan;

uint8 DMA 1 TD[1];

uint8 DMA_2 Chan;

uint8 DMA_2_TD[1];

DMA 1 Chan = DMA 1 DmaInitialize(DMA 1 BYTES PER BURST, DMA 1 REQUEST PER BURST,

HI16(DMA 1 SRC BASE), HI16(DMA 1 DST BASE));

DMA 1 TD[0] = CyDmaTdAllocate();

CyDmaTdSetAddress(DMA_1_TD[0], LO16((uint32)&Input_Signal_PS), LO16((uint32)&Value));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable (DMA 1 Chan, 1);

DMA 2 Chan = DMA 2 DmaInitialize(DMA 2 BYTES PER BURST, DMA 2 REQUEST PER BURST,

HI16 (DMA 2 SRC BASE), HI16 (DMA 2 DST BASE));

DMA 2 TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_2_TD[0], 1, DMA_2_TD[0], 0);

CyDmaTdSetAddress(DMA 2 TD[0], LO16((uint32)&Input Signal INTSTAT),

LO16((uint32)&Interrupt_Status)); /* Read the interrupt status register

* to clear the PICU interrupt */

CyDmaChSetInitialTd(DMA 2 Chan, DMA 2 TD[0]);

CyDmaChEnable (DMA 2 Chan, 1);

CyGlobalIntEnable;

lcd Start();

for(;;)

lcd Position(0,0);

lcd PrintNumber(Port Value);

CyDelay(20);

lcd_ClearDisplay();

}

```

## 6 Modifying a TD Dynamically

The PSoC DMAC can access its own registers. This allows a TD to dynamically alter the properties of another TD. Two examples of DMA transfers that use this technique are indexed DMA and nested DMA.

#### 6.1 Indexed DMA

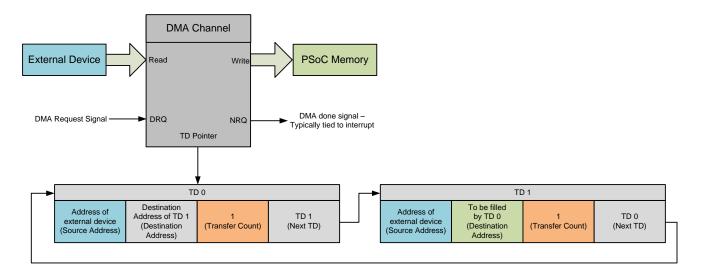

With indexed DMA, you can access PSoC memory and register addresses, for example, from an external device using a communication port. You use two TDs to do so. The first TD acts as an address fetch—it writes the destination address of the second TD. Then the second TD is called to carry out the actual data transfer. The external device can then access the PSoC memory locations as if those locations were shared memory. For example, if the actual memory space of the external device is only 256 bytes (0x00 to 0xFF), it can be extended to 512 bytes by using the PSoC memory locations with indexed DMA.

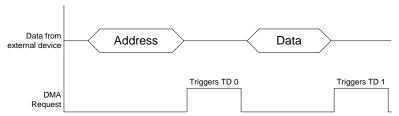

You can configure a DMA channel in the PSoC device for this purpose, as Figure 37 shows. If the external device wants to write to the PSoC memory, it should pass the address of the location followed by the data to be written to the PSoC memory. An interrupt associated with the peripheral through which the external master is connected to the PSoC device can be used to generate a DMA channel request.

Figure 38 shows the timing diagram for an indexed data transfer in this case.

Figure 37. Block Diagram for Indexed DMA Transfer

Figure 38. Timing Diagram for an Indexed DMA Transfer

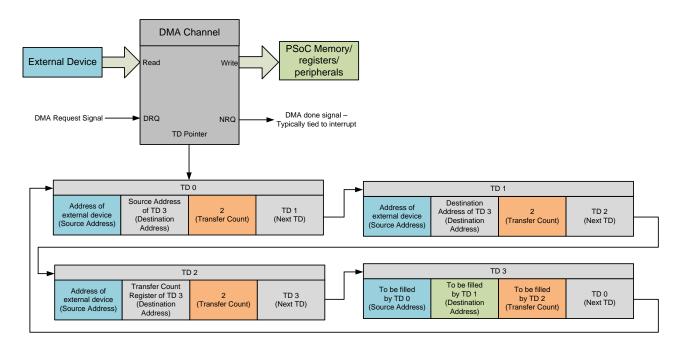

### 6.2 Nested DMA

Nested DMA is similar to indexed DMA, except that it involves multiple TDs to configure any parameters of the TD that does the actual data transfer. These parameters include source address, destination address, and transfer count.

Figure 39 shows the block diagram for a nested DMA data transfer.

Figure 39. Block Diagram for a Nested DMA Transfer

**Note:** If the upper 16 bits of source or destination address are different for TD 3, different DMA channels should be used for updating the TD configuration and actual data transfer.

An example project provided with this application note demonstrates the nested DMA feature.

# 7 Debugging DMA

This section explains some common issues that you may encounter while working with DMA, and some debugging techniques.

#### 7.1 Common Issues

#### 7.1.1 Base Address Differences

The 8-bit PSoC 3, the 32-bit PSoC 5LP, and the DMAC that exists in both families all have different addressing schemes. It is important to be aware of these differences, especially when porting DMA designs between the PSoC families.

To start, note that the DMAC uses 32-bit addresses (source and destination), stored in separate 16-bit registers. The upper halves of the addresses are specified in a DMA channel:

```

DMA DmaInitialize(..., upperSrcAddr, upperDestAddr)

```

And the lower halves of the addresses are specified in the TDs allocated to a DMA channel:

```

CyDmaTdSetAddress(..., lowerSrcAddr, lowerDestAddr)

```

For PSoC 5LP, you can easily obtain the upper and lower halves of an address from a (4-byte) pointer variable, by using the HI16 or LO16 macros, defined in the *cytypes.h* file:

```

upperSrcAddr = HI16(srcArray);

lowerSrcAddr = LO16(srcArray);

```

For PSoC 3, the contents of a pointer variable cannot be used because the Keil 8051 compiler uses a 3-byte pointer. It contains a 16-bit absolute address and a third byte for the memory space used (see Appendix A). Instead, use one of the following code snippets to obtain the upper half of the address:

Source or destination in SRAM or peripheral register:

```

upperSrcAddr = 0;

Source in flash:

upperSrcAddr = (CYDEV_FLS_BASE) >> 16

```

A list of commonly used base addresses is provided in Table 3 on page 25.

Conditional compilation can be used:

```

#if (defined(__C51__))

upperSrcAddr = 0;

lowerSrcAddr = srcArray;

#else /* PSoC 5 */

upperSrcAddr = HI16(srcArray);

lowerSrcAddr = LO16(srcArray);

#endif

```

#### 7.1.2 Endian Formats

Endian format refers to how multi-byte variables are stored in a byte-wide memory. In big endian format, the most significant byte is stored in the first byte (lowest address). In little endian format, the least significant byte is stored in the lowest address.

For PSoC 3, the Keil 8051 compiler uses big endian format. The PSoC 5LP Cortex-M3 and all its compilers use little endian format. Both PSoC 3 and PSoC 5LP multi-byte peripheral registers use little endian format.

DMA TDs can be programmed to have bytes swapped while transferring data. The swap size is set to 2 bytes for 16-bit transfers or 4 bytes for 32-bit transfers. The following examples handle 2- and 4-byte swaps:

```

CyDmaTdSetConfiguration(myTd, 2, myTd, (TD_TERMOUT0_EN | TD_SWAP_EN));

CyDmaTdSetConfiguration(myTd, 4, myTd, (TD TERMOUT0 EN | TD SWAP EN | TD SWAP SIZE4));

```

DMA byte swapping is required only in PSoC 3, when transferring multi-byte parameters between peripherals and variables in memory. It must be disabled for all other uses, including all PSoC 5LP uses.

**Note:** If the transfer count is not an integer multiple of the swap size, incorrect data is transferred to the destination.

#### 7.1.3 Preserving TD Configuration

You can set the preserve the TD configuration using the API function CyDmaChEnable(). If the TDs are preserved, the TD whose number is the same as the channel number becomes RESERVED and is used as the working register for the channel. For example, if you are using DMA channel 6 and the TD is preserved, you are not allowed to use TD 6. This TD is now used by the DMA engine for its private use.

If a TD is preserved, the TD is copied into the working register of the channel each time it is executed. The TD updates the source address, destination address, and transfer count only in the working register during the data transfer. If the channel is triggered again, the TD reloads its values to the working register from the original configuration registers.

If the TD is not preserved, the original TD settings are changed during the transfer. The transfer count value is decremented and finally reaches zero when the TD has been completed. An infinite data transfer begins if the TD is triggered again, since the transfer count is set to zero. If the source or destination address for the TD is configured for incrementing during the transfer, it results in erroneous data transfers.

**Note:** Take extra precautions when using the hardware request (drq) option when not preserving TD, as you may be requesting the wrong data.

#### 7.1.4 Address Alignment

If some data bytes are not transferred, a likely reason may be misaligned source and data addresses. Make sure that the source and destination addresses are aligned with spoke width boundaries. Doing so also increases transfer efficiency. A detailed discussion of the methods to align source and destination addresses with even address boundaries appears in the section Multi-Byte Data Alignment.

#### 7.2 Debugging Methods

Some methods to debug a DMA transfer are the following:

- Observe the drq and nrq signals on a scope: If you are using a hardware signal to trigger the DMA Component, observe the drq terminal to make sure that the DMA Component is being triggered correctly. If the termout signal is enabled for the DMA Component, at the completion of a data transfer the DMA Component produces a pulse at the nrq terminal that is two bus clocks wide.

- View critical DMA registers: The source address, destination address, and DMA configuration registers can be used to debug DMA transfers. Enter debug mode, navigate to the corresponding register location, and make sure that all registers have the expected values. The DMA registers inform the current status of DMA transfer, such as the number of bytes transferred, the TD that is being executed currently, and the status of DMA. The details of these registers are available in the PSoC 3 and PSoC 5LP Registers TRMs.

- 3. Use the correct method to trigger the DMA: Make sure that the correct trigger option is set for the drq terminal, that is, level or edge. Setting an incorrect trigger method can result in situations in which DMA requests are missed or are generated unnecessarily.

- The choice of trigger method depends on the source that generates the trigger signal. The trigger option is generally set to level when the DMA is used to transfer data from a FIFO. For example, the level option is used if you are transferring data from a UART Component to SRAM. This ensures that the DMA begins a transfer as soon as the UART buffer is not empty. The trigger option is set to edge if the data transfer follows the occurrence of an event such as ADC conversion complete.

- 4. Check the allocation and deallocation of TDs. The TDs of a DMA channel define the behavior of the DMA channel. A TD specifies the source address, destination address, number of bytes to be transferred (transfer count), and the next TD to be executed. Multiple TDs can be allocated to a channel. See the DMA Component datasheet for details.

Always disable a DMA channel before allocating or deallocating a TD for that channel. Otherwise the channel may behave indeterminately and write to random memory or peripheral addresses, which can be very difficult to debug. The following paragraphs explain the reason that this happens.

Two parameters are used to keep track of the allocation and deallocation of the TDs. One is CyDmaTdFreeIndex, which points to the next unallocated TD. The other one is CyDmaTdCurrentNumber, which stores the number of free TDs currently available. Byte 0 of the register (PHUB\_TDMEM[xxx]\_ORIG\_TD0), pointed by CyDmaTdFreeIndex has the next free TD number available after the current free TD is allocated. This acts like a linked list to keep track of the available TDs.

If a TD is being used, PHUB\_TDMEM[xxx]\_ORIG\_TD0 holds the eight lower bits of the transfer count (XFRCNT). This is normally loaded during TD configuration with the total number of bytes to be transferred by that TD. It is updated by the TD after every burst transfer with a new transfer count value (remaining bytes to be transferred). When a new TD is allocated using the API CyDmaTdAllocate(), CyDmaTdFreeIndex is updated with the value in PHUB\_TDMEM[CyDmaTdFreeIndex]\_ORIG\_TD0.

Now consider that the TDs are allocated using the API CyDmaTdAllocate() and freed using CyDmaTdFree(). When TDs are released with CyDmaTdFree(), the general DMA configuration itself is not changed, but instead CyDmaTdFreeIndex is updated with the value of the released TD number. If the TD number released using CyDmaTdFree() is Freed\_TD\_Number, the PUHB\_TDMEM[Freed\_TD\_Number]\_ORIG\_TD0 configuration register is updated with the previous value of CyDmaTdFreeIndex.

If a DMA channel request occurs after the TD is freed but with the DMA channel enabled, the TDMEM.TD0 value that points to the next free TD is corrupted since that value is taken as the transfer count. Now if another TD is allocated, the newly allocated TD may be a TD that is already in use. This TD could now transfer data incorrectly, causing system-wide issues.

**Note:** The DMAC latches a channel request even if the channel is disabled. This latched request is executed as soon as the channel is enabled again. This may cause the DMA Component to transfer incorrect data when the device wakes from sleep or the channel is re-enabled if a channel request occurs when the channel is inactive.

# 8 Projects

Two projects are provided with this application note to help you understand the concepts introduced in this application note.

#### 8.1 Parallel to Serial Converter Project

This project uses a DMA channel to convert a parallel stream of 8-bit data from a GPIO port to serial data. The data is shifted out at a constant rate through another GPIO pin.

This project shows you how to use DMA to transfer data between standard components that are not supported by the DMA Wizard. This project also demonstrates the method to force UDB Components to required locations.

Figure 40 shows the test setup for the parallel to serial converter project.

V<sub>DD</sub>

PIN4\_0

PIN4\_1

PIN4\_2

PIN4\_3

PSoC

PIN4\_4

PIN4\_5

PIN4\_5

PIN4\_6

PIN4\_7

Vss

Figure 40. Project Setup for Parallel to Serial Converter Project

#### 8.2 Nested DMA Project

This project demonstrates the method to dynamically modify a TD using another TD.

The project allows an external master with UART transmit capability to transfer variable amounts of data to different locations in the PSoC SRAM. The number of data bytes and the address to which these data bytes are to be written can be changed dynamically.

The first byte of the data stream received by the PSoC device specifies the SRAM address, and the second byte specifies the number of bytes to follow. The remaining bytes in the data stream are written to the SRAM.

Figure 41 shows the test setup for the nested DMA project.

Hyperterminal

Serial UART

Port of port of computer DVK

VDD

RX

GND

PSoC

GND

VSS

TOTAL TOTAL

Figure 41. Project Setup for Nested DMA Project

# 9 Summary

The PSoC 3 and PSoC 5LP DMA controller allows you to significantly offload the CPU and to transfer data between memory and peripherals. The DMA is powerful enough to modify itself dynamically, which makes this Component unique.

This application note explained some advanced concepts regarding the PSoC DMA and offered projects as examples.

### **About the Author**

Name: Ranjith M

Title: Applications Engineer

Background: Ranjith graduated from Government Engineering College, Thrissur with a Bachelor's Degree in

Electronics and Communications Engineering.

# 10 Appendix A: Memory Maps

The PSoC 3 and PSoC 5LP memory maps are different due to the architecture of their respective CPUs.

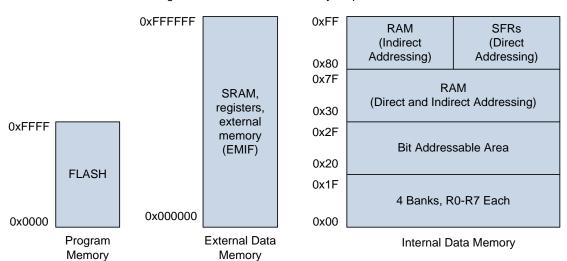

The PSoC 3 8051 memory map consists of three distinct memory spaces, as Figure 42 shows.

- Program memory: This space is 64 KB and is occupied solely by flash memory. The 8051 executes instructions from this space.

- External data memory: This space is "external" to the 8051 core but is "internal" to the PSoC 3 device. All SRAM, registers and EMIF addresses are mapped into this space. Flash memory is also mapped into this space, mainly for DMA data access. This space is 16 MB and requires a 24-bit address to access it.

- 8051 internal data memory: This space is part of the 8051 core. It contains 256 bytes of RAM and several special function registers (SFRs). The 8051 uses fast register and bit instructions to access portions of this space. The 8051 hardware stack also occupies this space; the stack size can be at most 256 bytes.

Note: This address space is not included in the PSoC 3 memory map and is not available for DMA access.

For more details, see any PSoC 3 datasheet or the application note AN60630 - PSoC 3 8051 Code and Memory Optimization.

Figure 42. PSoC 3 8051 Memory Map

The PSoC 5LP ARM Cortex-M3 architecture is simpler. It uses a single 32-bit linear memory map, as Figure 43 shows. The SRAM in the PSoC 5LP occupies the addresses 0x1FFF8000 to 0x20007FFF, centered on the boundary between the Cortex-M3 code and SRAM spaces. The remainder of the code space is occupied solely by flash, starting at address 0. The PSoC 5LP registers occupy the Cortex-M3 peripheral space.

Figure 43. PSoC 5LP Cortex-M3 Memory Map

| Vendor-specific                   | 0xFFFFFFF                              |

|-----------------------------------|----------------------------------------|

| Private peripheral bus - External | 0xE0100000<br>0xE00FFFFF               |

| Private peripheral bus - Internal | 0xE0040000<br>0xE003FFFF<br>0xE0000000 |

| External device 1.0GB             | 0xDFFFFFFF 0xA0000000                  |

| External RAM 1.0GB                | 0x9FFFFFFF 0x60000000                  |

| Peripheral 0.5GB                  | 0x5FFFFFF<br>0x40000000                |

| SRAM 0.5GB                        | 0x30000000<br>0x20000000               |

| Code 0.5GB                        | 0x1FFFFFFF<br>0x00000000               |

# 11 Appendix B: Termination Request Signal

To see how the trq input of the DMA operates, set the transfer count to zero to start an infinite data transfer and then trigger the DMA channel. A positive edge on the trq terminal stops the data transfer by a non-count termination.

The following steps explain a scenario where the trq terminal is used for a non-count termination:

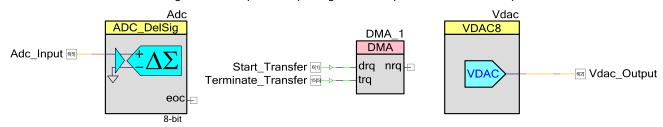

1. A DMA channel is used to transfer an 8-bit data output from the ADC to a VDAC. Figure 44 shows the TopDesign schematic.

Figure 44. Completed TopDesign for the trq Demonstration Example

- 2. Connect a variable voltage source to the Adc\_Input and an oscilloscope or an LED to the Vdac\_Output. Connect two switches to the pins Start\_Transfer and Terminate\_Transfer.

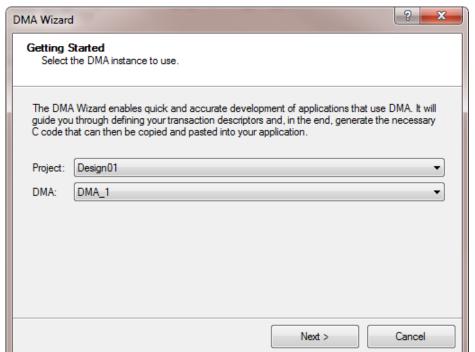

- Open the PSoC Creator DMA Wizard from the menu Tools > DMA Wizard, as Figure 45 shows. Select the DMA Component from your design and click Next.

Figure 45. Selecting the DMA Channel

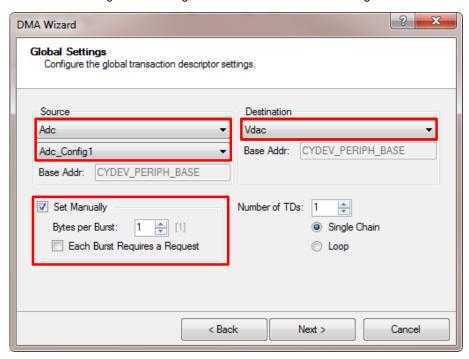

4. In the next window, set the configurations as Figure 46 shows, and click Next.

Figure 46. Configure General DMA Channel Settings

5. In the next window, select the option "Term In" and set the "Length" field (the transfer length) to zero, as Figure 47 shows. This initiates an infinite transfer. Click **Next**.

< Back

Next >

Cancel

Figure 47. Configure the TDs

Reset to Defaults

- In the final window, click Copy to Clipboard to copy the resultant code. Paste this code into your project main.c file.

- 7. Add code to main.c to start the ADC and VDAC Components, and start ADC conversion, as Code 2 shows.

Program the PSoC device and run the code. Press the Start\_Transfer switch to transfer ADC output to the VDAC. Similarly, press the Terminate\_Transfer switch to terminate data transfer to the VDAC.

Code 2. Code in the File main.c

```

#include <device.h>

/* DMA Configuration for DMA 1 */

#define DMA_1_BYTES_PER_BURST 1

#define DMA_1_REQUEST_PER_BURST 0

#define DMA_1_SRC_BASE (CYDEV_PERIPH_BASE)

#define DMA 1 DST BASE (CYDEV PERIPH BASE)

void main()

uint8 DMA 1 Chan;

uint8 DMA 1 TD[1];

DMA_1_Chan = DMA_1_DmaInitialize(

DMA 1 BYTES PER BURST,

DMA 1 REQUEST PER BURST,

HI16 (DMA 1 SRC BASE),

HI16(DMA 1 DST BASE));

DMA 1 TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA 1 TD[0], 0,

DMA_INVALID_TD, TD_TERMIN_EN);

CyDmaTdSetAddress(DMA_1_TD[0],

LO16((uint32)Adc DEC SAMP PTR),

LO16((uint32) Vdac Data PTR));

CyDmaChSetInitialTd(DMA 1 Chan,

DMA 1 TD[0]);

CyDmaChEnable(DMA_1_Chan, 1);

Adc Start();

Adc StartConvert();

Vdac Start();

for(;;)

{

```

# 12 Appendix C: DMA Channel Arbitration Flow Diagram

# 13 Appendix D: Misaligned Data Transfers

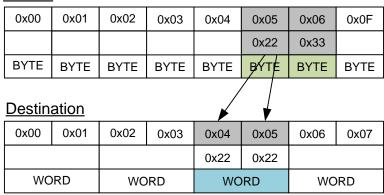

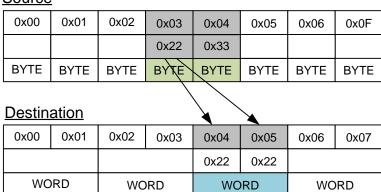

The DMAC performs incorrect data transfers if the source or destination addresses are misaligned and the increment source address and increment destination address are not enabled. Figure 48 shows a valid DMA transfer when the source and destination addresses are aligned. Figure 49 through Figure 54 illustrate different scenarios where misaligned data results in incorrect DMA transactions for 16-bit data.

Figure 48. Aligned Source and Destination Addresses - Valid DMA Transfer

#### Source 0x01 0x00 0x02 0x03 0x04 0x05 0x06 0x07 0x22 0x33 WORD WORD WORD WORD **Destination** 0x00 0x01 0x02 0x03 0x04 0x05 0x07 0x06 0x22 0x33 WORD WORD WORD WORD

Figure 49. Misaligned Destination Address – Destination Data Overwrite

#### **Source** 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x33 ⁄0x22 WORD WORD WORD WORD **Destination** 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x0F 0x22 0x33 **BYTE** BYTE **BYTE BYTE BYTE BYTE BYTE BYTE**

Figure 50. Misaligned Destination Address – Destination Data Overwrite

#### Source 5 4 1 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x22 0x33 WORD WORD WORD WORD Destination 0x02 0x00 0x01 0x03 0x04 0x05 0x06 0x0F 0x22 0x33 **BYTE BYTE BYTE BYTE BYTE BYTE BYTE BYTE**

Figure 51. Misaligned Source Address – Destination Data Duplicate

### Source

Figure 52. Misaligned Source Address – Destination Data Duplicate

### **Source**

Figure 53. Misaligned Source Address and Destination Address – Single-Byte Transfer

### **Source**

| 0x00    | 0x01  | 0x02 | 0x03     | 0x04 | 0x05 | 0x06 | 0x0F |

|---------|-------|------|----------|------|------|------|------|

|         |       |      | 0x22     | 0x33 |      |      |      |

| BYTE    | BYTE  | BYTE | ВУТЕ     | BYTE | BYTE | BYTE | BYTE |

| Destina | ation |      | <b>\</b> |      |      |      |      |

| 0x00    | 0x01  | 0x02 | 0x03     | 0x04 | 0x05 | 0x06 | 0x0F |

|         |       |      |          |      |      |      |      |

|         |       |      | 0x22     |      |      |      |      |

Figure 54. Misaligned Source Address and Destination Address – Single-Byte Transfer

# **Source**

| 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05 | 0x06 | 0x0F |

|------|------|------|------|------|------|------|------|

|      |      |      |      |      | 0x22 | 0x33 |      |

| BYTE |

# **Destination**

| 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05 | 0x06 | 0x0F |

|------|------|------|------|------|------|------|------|

|      |      |      | 0x22 |      | 0x22 |      |      |

| BYTE |

# **Document History**

Document Title: AN84810 - PSoC® 3 and PSoC 5LP Advanced DMA Topics

Document Number: 001-84810

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                               |

|----------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| **       | 4015646 | RNJT               | 05/30/2013         | New Application Note.                                                                                                               |

| *A       | 4602407 | RNJT               | 12/19/2014         | Added Table 1 with the number of clock cycles required for DMA transfer between PSoC resources.  Updated the section Debugging DMA. |

| *B       | 4800612 | RNJT               | 06/25/2015         | Updated Figure 28, Figure 29, Figure 32, and Figure 33 Corrected a typo in Code 1 Updated template Sunset Review                    |

| *C       | 5740149 | AESATP12           | 05/17/2017         | Updated logo and copyright.                                                                                                         |

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

#### **PSoC® Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

# **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Videos | Blogs | Training | Components

## **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2013-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.