# PSoC<sup>®</sup> 3, PSoC 4, and PSoC 5LP Mixed-Signal Circuit Board Layout Considerations

Author: Mark Hastings Associated Part Family: All PSoC 3, PSoC 4, and PSoC 5LP parts Related Application Notes: None To get the latest version of this application note, or the associated project file, please visit http://www.cypress.com/go/AN57821.

AN57821 introduces basic PCB layout practices to achieve 12- to 20-bit performance for the PSoC<sup>®</sup> 3, PSoC 4, and PSoC 5LP families of devices. The design practices covered in this application note are good rules to use in any mixed-signal design for any accuracy.

## Contents

| 1 | Introduction1                  |                                  |    |  |

|---|--------------------------------|----------------------------------|----|--|

| 2 | Trace Resistance Does Matter2  |                                  |    |  |

| 3 | Sha                            | ared Return Paths                | 4  |  |

|   | 3.1                            | Beware of the Hidden Killer      | 5  |  |

| 4 | Rou                            | iting Analog and Digital Signals | 6  |  |

|   | 4.1                            | What is Crosstalk?               | 6  |  |

|   | 4.2                            | 3-W Rule                         | 7  |  |

| 5 | Mul                            | tiple Power Domains              | 8  |  |

| 6 | Gro                            | und Planes                       | 8  |  |

| 7 | Bypass Capacitors10            |                                  |    |  |

|   | 7.1 PSoC 3 and PSoC 5LP10      |                                  |    |  |

|   | 7.2                            | PSoC 4                           | 10 |  |

|   | 7.3                            | Capacitor Selection              | 12 |  |

| 8 | All Capacitors Are Not Equal13 |                                  |    |  |

PRFS

| 9        | Mixed-Signal PCB Rules Summary13     |    |  |  |  |

|----------|--------------------------------------|----|--|--|--|

| 10       | PCB Layout and Auto Routing Tools    | 14 |  |  |  |

| 11       | Summary                              | 14 |  |  |  |

| A        | Appendix A: Layout Examples          | 15 |  |  |  |

|          | A.1 PSoC 3 and PSoC 5LP SSOP, QFN, a |    |  |  |  |

|          | A.2 PSoC 4 QFN and SSOP Packages     |    |  |  |  |

| Docu     | ument History                        | 17 |  |  |  |

| Worl     | Norldwide Sales and Design Support18 |    |  |  |  |

| Products |                                      |    |  |  |  |

| PSo      | C <sup>®</sup> Solutions             | 18 |  |  |  |

| Cypr     | Cypress Developer Community18        |    |  |  |  |

| Tech     | hnical Support                       | 18 |  |  |  |

|          |                                      |    |  |  |  |

AN57821

## 1 Introduction

To better understand the problems that may arise when using ADCs with a resolution of 12 bits or above, it is helpful to know how small a voltage an ADC can resolve. An 8-bit ADC with a range of 2 V detects a minimum value of 2 V/256 = 0.008 V or about 8 mV. Although 8 mV seems small, compare it to ADCs with higher resolutions. Table 1 compares ADCs with an input range of  $\pm 1 V$  and resolutions between 8 and 20 bits.

| Range ± 1.024 Volts |            |       |  |  |

|---------------------|------------|-------|--|--|

| Bits                | Resolution | Units |  |  |

| 8                   | 8.000      | mV    |  |  |

| 9                   | 4.000      | mV    |  |  |

| 10                  | 2.000      | mV    |  |  |

| 11                  | 1.000      | mV    |  |  |

| 12                  | 500        | μV    |  |  |

| 13                  | 250        | μV    |  |  |

#### Table 1. ADC Resolution

| Range ± 1.024 Volts |            |       |  |  |

|---------------------|------------|-------|--|--|

| Bits                | Resolution | Units |  |  |

| 14                  | 125.0      | μV    |  |  |

| 15                  | 62.5       | μV    |  |  |

| 16                  | 31.3       | μV    |  |  |

| 17                  | 15.6       | μV    |  |  |

| 18                  | 7.8        | μV    |  |  |

| 19                  | 3.9        | μV    |  |  |

| 20                  | 2.0        | μV    |  |  |

When the resolution is 20 bits, an ADC resolves down to 2 µV. Add a little gain and you can resolve voltages less than a single microvolt. Also, do not forget that a system with a low-resolution ADC and a narrow input range (high ADC gain) may resolve voltages in the microvolt range as well.

Offsets and noise sources below 1 mV, which were insignificant with a low-resolution ADC, are now significant when using a 12- to 20-bit ADC. These errors can easily be overlooked by designers who are not used to sensitive analog circuits. Today's electronics are smaller than ever, and the small circuit board geometries alone are enough to cause many problems.

## 2 Trace Resistance Does Matter

As PCBs get smaller, trace widths continue to get narrower and closer. Six-mil (0.006-inch) or less trace widths and spaces between traces are common in today's electronics. Even if you specify 6-mil traces, they can easily be overetched down to 4 or 5 mils.

So, why do you care about traces getting smaller? One problem is that as traces get narrower the trace resistance increases. The standard equation for trace resistance is provided in Equation 1.

Resistance = Resistivity

$$\times \frac{Length}{(Width \times Thickness)}$$

Where,

Resistivity for copper is about 6.787 ×  $10^{-7}$  Ω/inch.

Thickness of copper for a 1-oz copper PCB equals 1.378 mils.

A one-inch trace 8 mils wide, on a 1-oz copper PCB is about 0.062  $\Omega$ . Table 2 shows the calculated resistance values for several combinations of trace lengths and widths.

| Trace Resistance in $\Omega$ |                       |        |        |        |  |

|------------------------------|-----------------------|--------|--------|--------|--|

| Width                        | Trace Length (inches) |        |        |        |  |

| (mils)                       | 0.1"                  | 0.5"   | 1"     | 2"     |  |

| 15                           | 0.0033                | 0.0164 | 0.0328 | 0.0657 |  |

| 10                           | 10 0.0049             |        | 0.0493 | 0.0985 |  |

| 8                            | 0.0062                | 0.0308 | 0.0616 | 0.1231 |  |

| 6                            | 0.0082                | 0.0410 | 0.0821 | 0.1642 |  |

| 4                            | 0.0123                | 0.0616 | 0.1231 | 0.2463 |  |

| Table 2 | 2. Trace | Resistance |

|---------|----------|------------|

|---------|----------|------------|

As shown in Table 2, all combinations are well under an ohm. That does not sound too bad, but it all depends on where it is with respect to the circuit. If it is the trace to the input of a high-impedance amplifier, it may not matter, but in other cases, you may not be so lucky. Now take this same table and pass a 5-mA current through each trace combination. Although 5 mA is not much current and trace resistances less than an ohm seem small, the combined offsets are significant when using a high-resolution ADC, as shown in Table 3.

| Offset Due to 5 mA Current (microvolts) |                       |        |        |         |  |

|-----------------------------------------|-----------------------|--------|--------|---------|--|

| Width                                   | Trace Length (inches) |        |        |         |  |

| (mils)                                  | 0.1"                  | 0.5"   | 1"     | 2"      |  |

| 15                                      | 16.42                 | 82.10  | 164.20 | 328.40  |  |

| 10                                      | 24.63                 | 123.13 | 246.25 | 492.50  |  |

| 8                                       | 30.79                 | 153.93 | 307.85 | 615.70  |  |

| 6                                       | 41.05                 | 205.23 | 410.45 | 820.90  |  |

| 4                                       | 61.57                 | 307.83 | 615.65 | 1231.30 |  |

Table 3. Trace Voltage Offset

In this table, if 5 mA flows through a 2-inch-long trace that is 6 mils wide, the voltage drop is about 820  $\mu$ V or 0.82 mV. In Table 1, note that this voltage drop does not become significant until your system is using a 12-bit or higher resolution ADC. The cells shaded in green are conditions that affect a 16-bit ADC by at least half of the least significant bit or more. The cells shaded in yellow are conditions that can cause the same error in a 12-bit or higher ADC. This assumes that both the 12- and 16-bit ADC have an input range of 2 volts (+/- 1 volt).

An example application where this magnitude of offset causes significant error is measuring temperature with a thermocouple. With a K-type thermocouple, the output is about 40  $\mu$ V per degree centigrade. The 410- $\mu$ V offset equates to an error in excess of 10 °C. If the same trace is over-etched to 4 mils, the error is 50 percent higher. From this example, you can see how important it is to evaluate every PCB trace in your signal path. Although at first this does not sound too bad for a 12-bit ADC, if you add a gain of 16 in front of the ADC, you have the equivalent voltage resolution of a 16-bit ADC.

## 3 Shared Return Paths

When designing a circuit board with mixed signals or high-precision ADCs, you should know where current is flowing in the PCB. Trace currents of just a few milliamperes can be enough to cause significant problems.

Trace resistance usually causes a problem when a sensitive analog signal's return path is shared by a digital or high-current analog device. In these cases, high current does not mean amperes, but instead milliamperes. In the previous example, the thermocouple shared the same return path as a 5-mA load. If you reduce that load to 0.5 mA, the error remains 1 °C. Therefore, even currents in the hundreds of microamperes are significant.

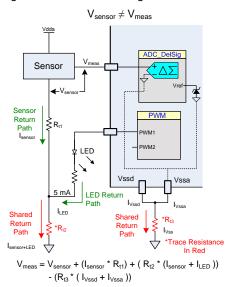

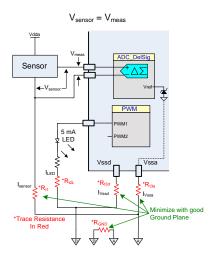

Figure 1 shows an example where return current paths are shared between the analog and digital grounds, and between a sensor and an LED. Both these shared paths can cause problems that may appear as system offsets or gain errors.

Figure 1. Resistance in Signal Return Path

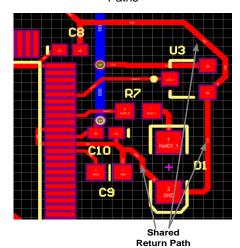

When the ADC in this example measures the output of the sensor, it also measures the voltage across the trace resistance. Depending on the length of the trace between the common ground point and the place where the sensor and LED currents combine, a significant voltage offset error may occur. How significant depends on the desired accuracy of the system, the voltage gain of the sensor, and the magnitude of the offset error voltage. An example of the PCB layout is shown in Figure 2.

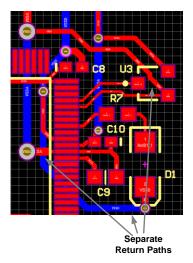

Figure 2. Example Layout with Shared Return Paths

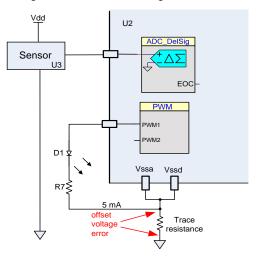

The analog ground (V<sub>SSA</sub>) is as important as any of the signals you are measuring. The trace between the PSoC V<sub>SSA</sub> pin and the system ground must be as short and low impedance as possible. Sharing this path with any component that uses even a few hundred microamperes can cause problems when measuring sub-millivolt signals. An offset can translate into a measurement offset when using single-ended measurements. In Figure 3, the LED's current flows in the same path back to the supply, but the sensor has its own path. The internal bandgap reference is also connected to V<sub>SSA</sub>. Any voltage induced by sharing the return path with the LED causes the ADC's reference to fluctuate by the I\*R drop. This offset between the reference and V<sub>SSA</sub> causes an ADC gain error.

Figure 3. Current in Analog Ground Path

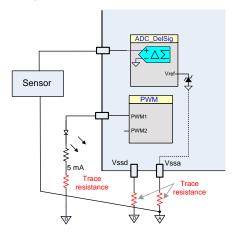

By providing separate ground paths for the digital ground ( $V_{SSD}$ ), analog ground ( $V_{SSA}$ ), sensor, and LED, there are no shared return paths (Figure 4). The sensor, ADC, and reference are at the same analog ground reference, so changing current in the LED has little or no effect on the sensor's output. Also note in the figure that the sensor and  $V_{SSA}$  connect to the analog ground at the same location. This can physically be the same point or to a very low impedance plane.

Figure 4. Good Ground Connections

Using a differential ADC connection to the sensor helps eliminate common mode voltage offsets caused by sharing a sensor return with a high current path (see Figure 1). A common voltage is an offset common to both the sensor  $V_{SS}$  and the sensor output. However, a differential connection to the sensor does not help errors caused by shared ground paths with  $V_{SSA}$  (Figure 3). See Figure 5.

Figure 5. Differential ADC and Separate Return Paths

An example of an improved routing that maintains separate return paths, separate analog and digital supplies, and a differential connection to the sensor is shown in Figure 6.

Figure 6. Example Layout with Separate Return Paths

# 3.1 Beware of the Hidden Killer

When sharing return paths with sensors or the V<sub>SSA</sub> pin with a modulated load, such as a LED driven by a PWM, errors may not always be apparent at first. If the load is modulated in perfect sync with the ADC, the errors induced may be large or insignificant. If synchronization does not cause measurable errors on the bench, then no problem may be seen in the initial development and testing. The problem is that with a change in either the ADC sample rate or the PWM frequency in this case, the error or noise can change significantly. This can be hard to test because in many applications, the change in the load modulation can vary due to environmental or software changes. So a board design that appears to be working at one time may fail at others. This is why it is imperative to follow good design rules even if a design appears to be working properly.

# 4 Routing Analog and Digital Signals

Ideally, analog and digital signals should be kept on opposite sides of the board, but this is usually impractical. Many designs require both analog and digital signals in the same area. Unfortunately, running relatively high-impedance analog signals in the same area as digital signals can cause unwanted crosstalk, which can add excessive noise to the analog signal.

#### 4.1 What is Crosstalk?

Crosstalk occurs when one signal affects another signal without being directly connected. This is most common when a digital signal with fast rise and fall times affects an analog signal with much high impedance. Digital signals are not immune to crosstalk either. High-speed digital signals can easily affect other digital signals. Crosstalk between signals is usually one of three types: conductive, capacitive, or inductive. In all cases, increasing the distance between signals and decreasing the parallel length between signals will help to reduce the problem.

Conductive crosstalk is usually not a problem and is an issue only when signals have very high impedance, such as more than 10 M $\Omega$ . It usually occurs when foreign materials such as dirt, oil, salt, or other liquids contaminate a PCB and cause the PCB material between traces to become more conductive. This decrease in resistance may cause enough crosstalk to adversely affect circuit operation. A solder mask can protect the PCB in some cases, but there are always areas, such as where components are attached to the PCB, that are exposed. Measures should be taken to isolate the PCB from these materials if they are found in the environment where the product is used. If it is impossible to insulate the PCB from foreign materials, a conformal coating can be applied to the PCB, but with added cost.

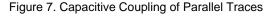

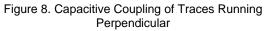

Capacitive coupling may occur when one trace is directly above the other on a different layer. A capacitor is formed between the copper traces. The more the overlap of the copper between these traces, the higher the capacitance. Decreasing the overlapping area between the signals will decrease the capacitance and therefore decrease the coupling. In some situations, especially with only two-layer boards, it may be impossible to eliminate instances where a sensitive analog signal crosses over a fast digital signal. In these cases, the signals should cross at 90° angles to minimize the capacitance formed between these signals. If you are using multilayer boards with more than two layers, make sure a power plane is between the two signals where they intersect to minimize coupling. Notice in Figure 7 that a capacitor is formed between the two traces, which is directly proportional to the overlapping area.

If a multilayer board is used, make sure the analog and digital traces intersect at a  $90^{\circ}$  angle. This way, the overlapping area is much less and therefore creates less capacitive coupling between the signals. See Figure 8 for an example.

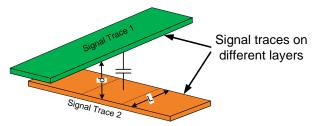

Figure 9 shows an example PCB layout where the analog traces (red) must cross over the digital (blue) traces. Notice the  $90^{\circ}$  angles between the analog and digital traces.

Figure 9. Digital Traces Cross Analog Traces at 90°

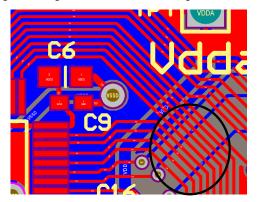

Traces that run next to each other on the same or a near layer may be coupled magnetically. This is referred to as inductive coupling. Inductive coupling is a function of three mechanical features: the separation between traces, the distance that the two traces are parallel, and the distance between the trace and the nearest power plane. The distance between the signals and between the signals and the ground plane are the biggest contributors, as shown in the simplified Equation 2 and Figure 10.

Equation 2

$$Crosstalk \cong \frac{1}{1 + (\frac{d}{h})}$$

As you can see, the height the trace is above the ground plane is a huge factor. By reducing this distance, the crosstalk is reduced by the square of the height. If you need to run digital and analog traces near each other, keeping them close to the ground plane may be the best option to reduce crosstalk.

## 4.2 3-W Rule

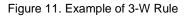

The 3-W rule states that the separation between logic traces (center to center) should be three times the width of the traces. For example, if the traces on a PCB are 0.008 inches wide, the distance between the trace's centers would be 0.024 inches (0.008 inches x 3), and the distance between trace edges would be 0.016 inches (0.008 inches x 2). This puts each trace outside the 70 percent magnetic flux boundary of the other trace. To be outside the 98 percent flux boundary, the spacing between the traces. Of course, all of this is dependent on the impedance of the traces and the rise time of the signals. See Figure 11.

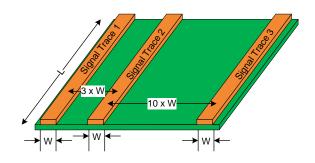

Another option to reduce coupling between signals that must run near each other and on the same side of the board is to use a guard trace connected to ground between the signals. This helps to reduce the capacitive coupling between the signals. See Figure 12.

**Guard Trace**

In multilayer boards, some layers are closer to some layers than others. For example, with a common 4-layer 0.062-inch-thick board, layers 1 and 2 are closer together than layers 2 and 3. When routing analog and digital signals in the same area, separate the traces on non-adjacent layers to ensure maximum separation.

## 5 Multiple Power Domains

Sensitive analog systems make it desirable to maintain separate analog and digital power supplies. The PSoC 3, PSoC 4, and PSoC 5LP families provide separate power and ground pins for the analog and digital blocks. The PSoC 3 and PSoC 5LP GPIOs are also divided into four groups, but this is mainly to provide multiple logic levels to external components. A summary of the power supply connections follows.

- V<sub>SSD</sub> Ground for all digital logic and I/O pins.

- V<sub>DDD</sub> Supply for all digital peripherals and digital core regulator. V<sub>DDD</sub> must be less than or equal to V<sub>DDA</sub>.

- V<sub>SSA</sub> Ground for all analog peripherals.

- V<sub>DDA</sub> Supply for all analog peripherals and analog core regulator. V<sub>DDA</sub> must be the highest voltage present on the device. All other supply pins must be less than or equal to V<sub>DDA</sub>.

- V<sub>CCD</sub> Output of digital core regulator and input to digital core. Requires a 1-µF cap to V<sub>SSD</sub>. Regulator output not for external use.

- V<sub>CCA</sub> (PSoC 3 and 5LP only) Output of analog core regulator and input to analog core. Requires a 1-µF cap to V<sub>SSA</sub>. Regulator output not for external use.

- V<sub>DDIO</sub> Supplies for I/O pins. For PSoC 3 and 5LP, there are four V<sub>DDIO</sub> pins. The GPIOs are grouped into four groups, each with its own power pin. V<sub>DDIO</sub> must be less than or equal to V<sub>DDA</sub>.

Depending on the product family and part number, a PSoC device may have all or a subset of these pins. For details, refer to the datasheet of the part you are using.

The use of separate external analog and digital regulators is always a good idea. If the cost of an additional regulator is prohibitive and the digital section of your design does not contain high-speed or high-current switching, it is possible to use a single regulator. One important note is always to wire your design as if you have separate regulators. Separate both power and ground signals for the analog ( $V_{DDA}$ ,  $V_{SSA}$ ) and digital supplies ( $V_{DDD}$ ,  $V_{SSD}$ ). Make the connection between these two supplies (analog and digital) as close to the power supply source as possible. Usually the output impedance of the power supply is low, and with such a connection, the digital supply has less of an effect on the analog supply.

The PSoC 4 parts that are available in the 28-pin SSOP package have the V<sub>SSD</sub> and V<sub>SSA</sub> supply pins combined into a single V<sub>SS</sub> pin to save pins. Also, the V<sub>DDA</sub> and V<sub>DDD</sub> pins are combined into a single V<sub>DD</sub> pin. This 28-pin SSOP package should be avoided when the maximum analog performance is required when several GPIO pins are used to drive fast low-impedance loads.

## 6 Ground Planes

Ground planes are always beneficial in a mixed-signal design, but additional layers may be expensive for a given design. Even with two-layer boards, it is possible to provide partial planes under sensitive analog sections of the design. Whether you use ground planes or not, make sure the return paths are as direct to the power supply as possible. Remember, ground planes may not improve your design if the path to the supply is not low impedance, or the plane is too fragmented. On two-sided boards, do not rely only on using fill; it can lead to narrow, high-resistance paths that are not obvious without careful inspection. Route the ground with traces and supplement with fill.

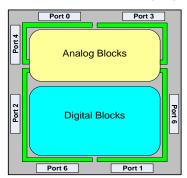

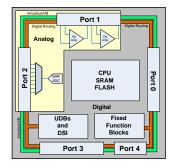

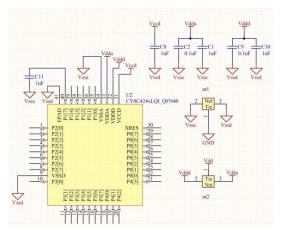

If care is taken when selecting pins, the board layout can be much easier and enable partial analog and digital power planes. Figure 13 shows how the analog and digital sections of the chip are placed in the PSoC 3 and PSoC 5LP device with respect to the I/O ports.

#### Figure 13. PSoC 3/PSoC 5LP Analog/Digital Layout

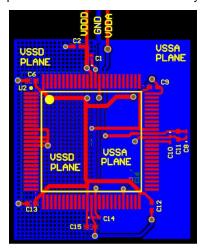

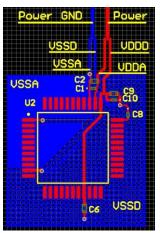

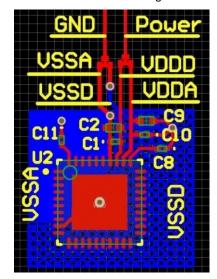

Figure 14 is an example of a two-layer board layout. The PSoC device is rotated  $90^{\circ}$  clockwise with respect to the image in Figure 13. The blue is the bottom layer, and the red is the top layer. Notice that there is adequate room to route the signals away from the PSoC device on the top layer even with all power supply pins connected and good power grounds on the bottom layer. The V<sub>SSD</sub> plan was hatched intentionally so that it is easy to distinguish between the V<sub>SSD</sub> and V<sub>SSA</sub> power planes. Normally, it is recommended to make your power planes solid, unless there is a special case, such as CapSense<sup>®</sup> buttons and controls.

If separate analog and digital ground planes can be used in your design, they should be connected at a single point in most cases. This single point should be between the power supply source and the PSoC device itself.

With a single regulator, it is possible to use a single ground plane, but only if the analog and digital components are well isolated from one another.

See Appendix A for example layouts for QFN, and SSOP packages.

# 7 Bypass Capacitors

#### 7.1 PSoC 3 and PSoC 5LP

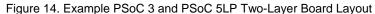

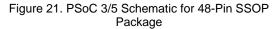

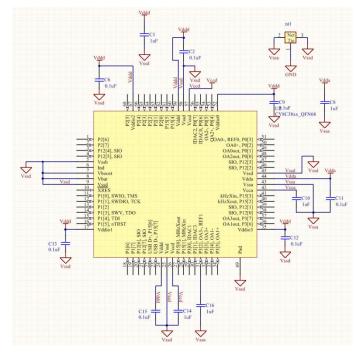

As mentioned previously, there are several power domains with the PSoC 3 and PSoC 5LP parts. Each of these domains has individual bypass capacitor requirements. Table 4 summarizes these requirements, and Figure 15 shows an example schematic with the capacitors in place.

| Power Supply                                                                                                                                       | Bypass Capacitors                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DDD} - V_{SSD}$                                                                                                                                | 0.1-µF ceramic capacitor at each pin plus a 4.7-µF to 10-µF bulk capacitor (C1, C2, C15).                                                                                                                                                                                                                                                                     |

| V <sub>DDA</sub> – V <sub>SSA</sub> 0.1-μF ceramic capacitor at pin (C11). Additional 1-μF to 10-μF bulk capacitor (C8) if more from power supply. |                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDIO</sub> 0,1,2,3 –<br>V <sub>SSD</sub>                                                                                                    | 0.1- $\mu$ F ceramic capacitor at each V <sub>DDIO</sub> pin. Additional 1- $\mu$ F bulk capacitor if several pins are switching 5 to 10 mA. (C9, C13, C6, C12)                                                                                                                                                                                               |

| $V_{CCA} - V_{SSA}$                                                                                                                                | $1-\mu F$ capacitor (C9) at the V <sub>SSA</sub> pin.                                                                                                                                                                                                                                                                                                         |

| $V_{CCD} - V_{SSD}$                                                                                                                                | $1-\mu F$ ceramic capacitor (C14) at one of the two V <sub>CCD</sub> pins. The V <sub>CCD</sub> pins should be connected together.                                                                                                                                                                                                                            |

| V <sub>REF</sub> – V <sub>SSA</sub><br>(optional)                                                                                                  | The internal bandgap may be bypassed at pin P3[2] or P0[3] with a 1- $\mu$ F to 10- $\mu$ F capacitor (C16).<br>For PSoC 5LP, reference bypass capacitors should be used for each of the SAR ADCs if operating above 100 ksps. A 1- $\mu$ F to 10- $\mu$ F capacitor should be placed on pins P0[2] and/or P0[4], depending on which SAR ADCs are being used. |

Table 4. PSoC 3 and PSoC 5LP Bypass Capacitor Connection Summary

Figure 15. Example PSoC 3 and PSoC 5LP Schematic of Power Connections

#### 7.2 PSoC 4

Since the PSoC 4 family is not intended to achieve the accuracy and resolution possible with both PSoC 3 and PSoC 5, board layout is not as critical either. That said, it is still always important to adhere to good board layout practices. In the example PSoC 4200 series device shown in Figure 16, notice that there are two analog sensitive areas near Port 1 and Port 2. Port 2 is the preferred port to route signals directly to the SAR ADC, although an AMUXBUS can be used to route all signals to the SAR ADC, but with a higher resistive path. Port 1 contains two generalpurpose opamps, which can be used to buffer input signals to the ADC or to operate totally independent of the SAR ADC. If these two ports are used for analog signaling, it is a good practice to keep digital signals routed away from this area.

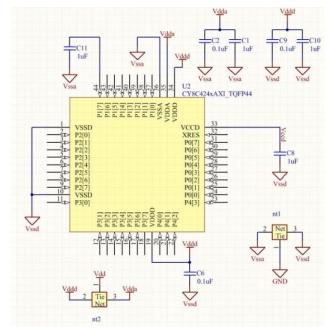

Figure 16. PSoC 4200 Block Layout Diagram

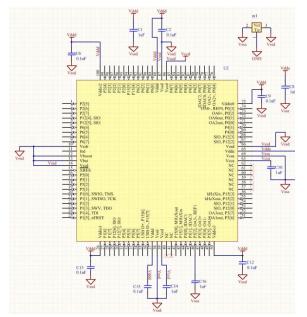

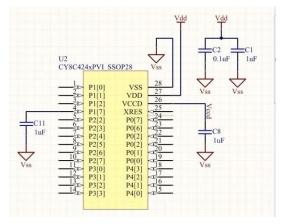

Figure 17 shows an example schematic for the PSoC 4200 series TQFP 44-pin package. Notice that there are much fewer power supply pins than are used for PSoC 3 and PSoC 5LP. There are several reasons for this, including that it is a Table 5 summarizes the PSoC 4 power connections and the bypass capacitors for each pin.

Figure 18 shows an example layout for PSoC 4 in the 44-pin TQFP package. The  $V_{SSD}$  digital ground plane is shown hatched so it is easy to tell the difference between the two analog and digital ground planes. This is just one example of the many ways in which to lay out a two-layer PCB. Appendix A: Layout Examples gives sample schematics and PCB layouts for the QFN and SSOP packages as well. significantly smaller device and it does not contain a high-performance 16- to 20-bit Delta-Sigma ADC as do the PSoC 3 and PSoC 5LP devices.

#### Figure 17. PSoC 4 TQFP 44 Example Schematic

| Table 5. PSoC 4 Bypass  | Canacitor Connection | Summary |

|-------------------------|----------------------|---------|

| Table 5. 1 000 + Dypass |                      | Summary |

| Power Supply                                                                                     | Bypass Capacitors                                                                                                   |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| V <sub>DDD</sub> – V <sub>SSD</sub>                                                              | 0.1- $\mu$ F ceramic capacitor at each pin plus a 1- $\mu$ F to 10- $\mu$ F bulk capacitor (C9, C10).               |

| V <sub>DDA</sub> – V <sub>SSA</sub>                                                              | 0.1- $\mu$ F ceramic capacitor at pin (C2). Additional 1- $\mu$ F to 10- $\mu$ F bulk capacitor (C1).               |

| $V_{CCD} - V_{SSD}$                                                                              | 1- $\mu$ F ceramic capacitor at the V <sub>CCD</sub> pin (C8)                                                       |

| V <sub>REF</sub> - V <sub>SSA</sub> (optional)                                                   | The internal bandgap may be bypassed with a 1- $\mu$ F to 10- $\mu$ F capacitor at P1[7]. (C11)                     |

| V <sub>DDIO</sub> – V <sub>SSA</sub><br>(V <sub>DDIO</sub> is not present in all PSoC 4 devices) | 0.1- $\mu$ F ceramic capacitor and an additional 1- $\mu$ F to 10- $\mu$ F bulk capacitor (not shown in the image). |

| $V_{DD}$ – $V_{SS}$<br>(these pins are not present in all PSoC 4 devices)                        | 0.1- $\mu$ F ceramic capacitor and an additional 1- $\mu$ F to 10- $\mu$ F bulk capacitor (not shown in the image). |

#### Figure 18. PSoC 4 TQFP 44-Pin Layout

#### 7.3 Capacitor Selection

There are two types of capacitors used for power supply stability: bypass and bulk. Bulk capacitors are sometimes referred to as reservoir capacitors as well. The bypass capacitors must be placed near the power supply pins of the component. Bypass capacitors help to eliminate high-frequency noise and supply current for short transients. These capacitors are usually between 0.001  $\mu$ F and 0.1  $\mu$ F. Capacitors with a dielectric of NPO, X5R, and X7R make excellent bypass capacitors and are available in values from hundreds of picofarads to several microfarads.

The reservoir capacitors are usually placed near the regulators. They are also spread around the board if it is more than a few square inches in size and contains several active components. The capacitors are used to supply power for longer periods and filter low-frequency noise. Reservoir capacitors range in size between 1  $\mu$ F and 100  $\mu$ F or even larger for boards with high current signals or power supplies. X5R, tantalum, and some surface mount electrolytic capacitors work well for this purpose.

Often the  $0.01-\mu$ F or  $0.1-\mu$ F capacitor is sufficient for a bypass capacitor. For reservoir capacitors, it is recommended to do some simple calculations to make sure you have the optimum value. Too big and you are spending more than you need. Too little and your power supply ripple may be excessive and cause noise. Start with the equation:

$$I = C * \frac{dV}{dT}$$

1....

$$C = I * \frac{dt}{dV}$$

dt = Clock or highest frequency component (fclk \*  $\pi$ ) I = Average current

dV = Acceptable ripple voltage

$$C = \frac{I_{ave}}{(f_{clk} * \pi * dV)}$$

# 8 All Capacitors Are Not Equal

When selecting a capacitor for any application, even a simple bypass cap, it is very important to look at its specifications. The voltage and temperature coefficients are two of the most ignored capacitor specifications, but they can greatly affect the device capacitance under normal operating conditions.

As devices become increasingly smaller, tradeoffs are made between performance and size. A capacitor that is rated at 1  $\mu$ F and a max voltage of 6.3 may be less than 0.1  $\mu$ F at 5 volts. So you really do need to pay attention to the voltage coefficient. Also, do not assume that the coefficient is the same for an entire family of parts. The voltage and temperature coefficient can vary greatly between packages. A 0805 package may have a better voltage coefficient than a 0603 package, or the other way around. So read the datasheet. If you cannot get temperature and voltage coefficients for a capacitor, consider using a capacitor from a different manufacturer.

# 9 Mixed-Signal PCB Rules Summary

The following is a list of rules to keep in mind when designing mixed-signal boards:

- 1. Consider separate analog and digital supplies.

- 2. Understand all return paths.

- 3. Use four-layer boards with power planes if possible, although they are not always affordable.

- 4. Do not run analog signals parallel to clocks or fast digital signals.

- 5. If analog and digital signals must cross, make the intersection at 90° to keep the coupling capacitance to a minimum.

- 6. Use power planes in similar areas. For example, only run analog signals over analog power planes.

- 7. Keep bypass capacitors as close to ICs as possible. Also make sure bypass connections to power signals are low impedance.

- 8. Separate analog and digital signals and components on the board, if possible. Designate "analog" and "digital" areas of the PCB.

- 9. Avoid long traces into a high-impedance input. These act as antennas.

- 10. Keep power traces as wide (low impedance) as possible.

- 11. Keep analog signals close to the ground plane to minimize inductive crosstalk.

- 12. Use large or multiple vias when connecting power signals between planes to reduce impedance.

- 13. Minimize the digital rise and fall times of digital signals.

- 14. Use guard traces to isolate analog and digital signals.

# **10 PCB Layout and Auto Routing Tools**

PCB layout tools have come a long way in the last 20 years. Many of these tools allow signals to be grouped and create different rules for trace widths and distance between traces. These rules keep you from inadvertently making mistakes. Auto routers have also become more powerful, and many common tools follow the same rules as when you route by hand. A skilled PCB layout designer can use these rules to enhance the quality of the auto router. Although these tools are very powerful, be careful how they route analog and digital signals. You may find it worthwhile to hand route the sensitive part of your board and then let the auto router complete the least critical section of the board. Either way, make sure you review the final routing.

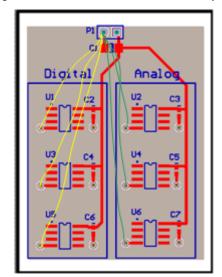

Placing the parts in optimal locations can also greatly aid in either hand routing or auto routing. After the parts placement and board layout is complete, a simple test can be used to validate if shared return paths could cause a problem. Print out your board layout and draw the most direct path between your power supply and each of the components. Use one color for analog parts and another for digital parts. If the different colors cross, you may want to re-evaluate your design. See Figure 19.

Figure 19. Draw Return Paths on PCB Layout

# 11 Summary

The design tips discussed in this application note help you grasp the following concepts:

- Understand your signal return path and do not share analog and digital return paths, if possible.

- Trace resistance does matter, and it is as simple as Ohms law to determine just how much.

- There is always coupling between any two adjacent traces, so keep digital signals away from analog signals.

## About the Author

| Name:       | Mark Hastings                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title:      | Applications Engineer MTS                                                                                                                                                                                                                           |

| Background: | Mark Hastings graduated from Washington State University in 1984. For most of the last 25 years, he has been involved in embedded and mixed-signal designs. Most of his free time is spent hiking and climbing in the North Cascades of Washington. |

# A Appendix A: Layout Examples

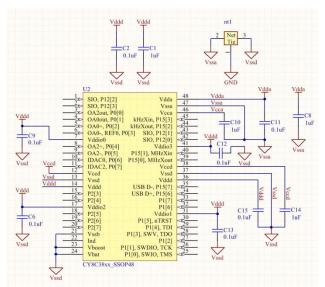

## A.1 PSoC 3 and PSoC 5LP SSOP, QFN, and TFQP Packages

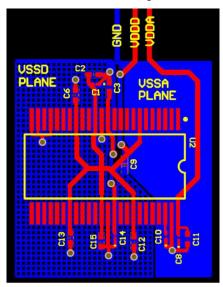

Figure 20. Example Layout for 48-Pin SSOP Package

For more examples including schematic, layout and gerber files, see CY8CKIT-030 and CY8CKIT-050 development kit web pages. Also refer to PSoC 3 and PSoC 5LP CAD resources web pages.

Figure 22. Example PSoC 3/5 Layout for 68-Pin QFN Package

Figure 23. Schematic for 68-Pin QFN Package

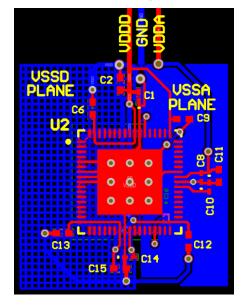

## A.2 PSoC 4 QFN and SSOP Packages

Figure 24. Example Layout for PSoC 4 QFN 40-Pin Package

Uss Vdd

Figure 26. Example Layout for PSoC 4 SSOP 28-

Pin Package

Figure 27. Example Schematic for PSoC 4 SSOP 28-Pin Package

For more examples including schematic, layout and gerber files, see CY8CKIT-044, CY8CKIT-042, and CY8CKIT-040 development kit web pages. Also, refer to PSoC 4 CAD resources web page.

Figure 25. Example Schematic for PSoC 4 QFN 40-Pin Package

# **Document History**

Document Title: AN57821 - PSoC<sup>®</sup> 3, PSoC 4, and PSoC 5LP Mixed-Signal Circuit Board Layout Considerations

Document Number: 001-57821

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                   |

|----------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 2818833 | MEH                | 12/01/2009         | New application note                                                                                                                                                                                                    |

| *A       | 2896385 | MEH                | 03/19/2010         | Changed connection to Vboost from $V_{\mbox{\scriptsize DDD}}$ to $V_{\mbox{\scriptsize SSD}}$                                                                                                                          |

| *В       | 2991511 | SRIH               | 07/22/2010         | Fixed branding discrepancies                                                                                                                                                                                            |

| *C       | 3095205 | MEH                | 11/25/2010         | Changed the title, updated abstract, and fixed a few minor typos.                                                                                                                                                       |

| *D       | 3460049 | MEH                | 12/09/2011         | Changed Title<br>Updated Figures 1, 3, 4, and 5, and Tables 2 and 3<br>Several minor changes throughout document<br>Changed abstract<br>Updated template                                                                |

| *E       | 3656888 | MEH                | 6/26/2012          | Updated <b>Error! Not a valid result for table.</b> .<br>Updated Ground Planes <b>Error! Not a valid result for table.</b> .<br>Added Appendix A.<br>Updated in new template.                                           |

| *F       | 3719890 | MEH                | 8/23/2012          | Updated capacitor designators to match the schematic changes in rev *E.                                                                                                                                                 |

| *G       | 3811577 | MEH                | 11/15/2012         | Updated Associated Part Family as "All PSoC 3 and PSoC 5LP parts".<br>Replaced PSoC 5 with PSoC 5LP in all instances across the document.                                                                               |

| *H       | 3940231 | MEH                | 4/08/2013          | Fixed wiring error with SSOP 48-pin package. Added PSoC 4 information.                                                                                                                                                  |

| *I       | 4494203 | MEH                | 9/05/2014          | Added the section "All Capacitors Are Not Equal".Error! Not a valid result for table.                                                                                                                                   |

| *J       | 4573117 | MEH                | 11/18/2014         | Sunset Update                                                                                                                                                                                                           |

| *K       | 4776263 | NIDH               | 06/03/2015         | Updated the following for PSoC 4-M series:<br>Updated Multiple Power Domains.<br>Updated Table 5.<br>Added links to kit web pages for additional schematic/layout details.<br>Updated the document as per new template. |

| *L       | 5687787 | AESATMP7           | 04/18/2017         | Updated Cypress Logo and Copyright.                                                                                                                                                                                     |

# Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

# Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

# **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

# **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Videos | Blogs | Training | Components

## **Technical Support**

cypress.com/go/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2009-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress prevey grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under thes claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.