# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# THIS SPEC IS OBSOLETE

Spec No: 001-14799

# Spec Title: INTERFACING CYPRESS MOBL(R) ASYNCHRONOUS DUAL-PORT TO TI OMAP1710 MULTIMEDIA PROCESSOR - AN5036

Sunset Owner: PRAJITH CHEERAKKODA (PRJI)

Replaced by: NONE

# AN5036

## Interfacing Cypress MoBL(R) Asynchronous Dual-Port to TI OMAP1710 Multimedia Processor

Author: Hingkwan Huen Associated Project: Yes Associated Part Family: MoBL® Dual Port Software Version: NA Related Application Notes: AN5055, AN5074, AN5056

If you have a question, or need help with this application note, contact the author at hkh@cypress.com

Systems using a TI OMAP1710 Multimedia Processor can easily benefit from the performance and flexibility of a Cypress Dual-Port. As one of the industry's lowest power consuming Dual-Ports, designing in the Cypress MoBL Dual-Port allows the customer to interconnect multiple processors in a system, where power is of the most concern, and without having to compromise in performance.

### Introduction

The Texas Instruments OMAP1710 Multimedia Processor is a low-power, highly-integrated hardware and software platform designed to meet the application processing needs of next-generation embedded devices.

The OMAP<sup>™</sup> platform enables OEMs and ODMs to quickly bring to market devices featuring rich user interfaces, high-processing performance, and long battery life through the maximum flexibility of a fully-integrated mixed-processor solution.

The OMAP1710 is primarily targeted at mobile communications applications using WLAN802.11x, Bluetooth, GSM, GPRS, EDGE, CDMA and other proprietary wireless standards. The processor provides video and image processing (MPEG, JPEG, etc.), advanced speech/audio processing, graphics and video acceleration, generalized web access and data processing.

The OMAP1710 Multimedia Processor supports External Memory Interface (EMIF) that readily connects to Cypress asynchronous Dual-Ports. This application note describes the wiring, EMIF register settings, and other design considerations for connecting the OMAP1710 Multimedia Processor to the 1/4-Mb Cypress MoBL® Dual-Port (CYDM256A16-55). The same design can be used in interfacing the OMAP1710 Multimedia Processor to other Cypress MoBL Dual-Ports in the x16 configuration, such as the CYDM128A16 and CYDM064A16.

### TI External Memory Interface (EMIF)

The Texas Instruments OMAP1710 Multimedia Processor supports two types of external memory interfaces: EMIFF and EMIFS. EMIFF is primarily used to gluelessly interface the processor with SDRAMs, while the EMIFS is used to interface to asynchronous and synchronous burst memories, such as NAND/NOR flashes and asynchronous SRAM. The EMIFS is a 16-bit memory interface, and it can be configured to gluelessly interface to Cypress's lowpower MoBL Dual-Ports.

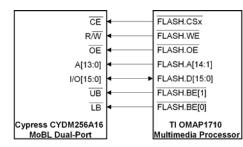

The Cypress MoBL Dual-Port CYDM256A16 has a standard asynchronous SRAM interface. Table 1 lists the signal connections between the OMAP1710's EMIFS and Cypress MoBL Dual-Port CYDM256A16. This is a 1.8 V LVCMOS interface.

#### Table 1. EMIFS & CYDM256A16 Signal Equivalents

| OMAP1710 EMIFS<br>Signal (I/O)   |     | CYDM256A1<br>6<br>Signal (I/O) |     | Function             |  |

|----------------------------------|-----|--------------------------------|-----|----------------------|--|

| FLASH.CSx                        | 0   | CE                             | Т   | Chip select          |  |

| FLASH.WE                         | 0   | R/W                            | I   | Write enable         |  |

| FLASH.OE                         | 0   | OE                             | 1   | Output enable        |  |

| FLASH.A[14:1                     | 0   | A[13:0]                        | T   | Address              |  |

| FLAS <mark>H.D</mark> [15:0<br>] | 1/0 | 1/0[15:0]                      | 1/0 | Data                 |  |

| FLASH.BE[1]                      | 0   | UB                             |     | Upper byte<br>enable |  |

| FLASH.BE[0]                      | 0   | LB                             | 1   | Lower byte<br>enable |  |

## Wiring Diagram

Figure 1 below shows the physical wiring between the OMAP1710 Multimedia Processor and the MoBL Dual-Port CYDM256A16. Either port of the Dual-Port may be used.

# Figure 1. Wiring Diagram of OMAP1710 to CYDM256A16

Table 2 shows the list of EMIF and MoBL Dual-Port pins that are not required for the memory interface (optional).

#### Table 2. Default Signal

| CYDM256A16<br>Signal |                 | OMAP1710 EMII<br>Signal | FS       |

|----------------------|-----------------|-------------------------|----------|

| SEM                  | $V_{\text{DD}}$ | FLASH.A[25:15]          | NC       |

| INT                  | NC              | FLASH.CLK               | NC       |

| BUSY                 | NC              | FLASH.RDY               | $V_{DD}$ |

| IRR[1:0]             | V <sub>SS</sub> | FLASH.ADV               | NC       |

| ODR[4:0]             | NC              | FLASH.BAA               | NC       |

| SFEN                 | $V_{\text{DD}}$ | FLASH.RP                | NC       |

| M/S                  | $V_{\text{DD}}$ | FLASH.WP                | NC       |

To setup the EMIFS to properly interface to the Cypress MoBL Dual-Port, the following EMIFS registers need to be configured, while the rest of the register settings can be left in their default states. EMIFS Register Settings shows the required EMIFS register settings.

#### Table 3.EMIFS Register Settings

| Field                                               | Value | Description                                                    |

|-----------------------------------------------------|-------|----------------------------------------------------------------|

| EMIFS_CCSx: Chip-Select Configuration Register      |       |                                                                |

| BTWST                                               | 0000b | tdle cycle # for bus turnaround and CS high-pulse-width timing |

| MAD                                                 | Ob    | Non-multiplexed protocol                                       |

| BW                                                  | 0b    | Data bus is 16 bits wide                                       |

| RDMODE                                              | 000b  | Read mode setting - async.                                     |

| WELEN                                               | 0010b | Pulse length during write access                               |

| WRWST                                               | 0000b | Wait states cycle number for write                             |

| RDWST                                               | 0011b | Wait states cycle number for read                              |

| FCLKDIV                                             | 01b   | TC_CK divider for REF_CLK<br>(REF_CLK ≤ 50MHz)                 |

| EMIFS_DWS: Dynamic                                  |       | Wait States Control Register                                   |

| WRRDYMAS<br>K_CSx                                   | 1b    | FLASH.RDY signal is masked                                     |

| Full<br>handshake<br>enable for<br>CSx              | 1b    | Non-full-handshaking                                           |

| EMIFS_ACSx: Adv. Chip-Select Configuration Register |       |                                                                |

| OEHOLD                                              | 0000b | # of cycles from OE to CS (high)                               |

| OESETUP                                             | 0000b | # of cycles from CS to OE (low)                                |

To arrive at the register settings shown above, assume the system clock TC\_CK runs at 100 MHz; a 50-MHz REF\_CLK is derived by dividing the system clock by two (FCLKDIV = 01b). Please note that this setting may vary depending on the speed of the desired memory interface as well as the speed of the system clock. Given most timing parameters of the OMAP processor are specified with a range of guaranteed values, the timing analysis below will use the worst case values, and the register settings takes into account the timing margin required for successful operations. The following section provides a brief explanation for each of the register settings.

# EMIFS\_CCSx - Chip-Select Configuration Register

*BTWST*—No wait states are needed to interface to the Cypress MoBL Dual-Port family.

*MAD*—Cypress MoBL Dual-Ports do not support multiplexed address and data bus; therefore, this field needs to be disabled.

*BW*—The memory interface to CYDM256A16 is 16-bit wide.

*RDMODE*—The Cypress MoBL Dual-Port family supports asynchronous reads.

*WELEN*—With a REF\_CLK period of 20 ns, and referring to Figure 2-13 in the TI OMAP1710 Technical Reference Manual, the write pulse is given by  $P = (WELEN + 1)*REF_CLK$ . In order to fulfill the data setup time of the Cypress MoBL Dual-Port, WELEN needs to be 2 to provide enough margin for a successful write.

*WRWST*—Similar to WELEN, referring to Figure 2-13 in the TI OMAP1710 Technical Reference Manual, the duration of N = (WRWST + 1)\*REF\_CLK. In order to satisfy the timing requirement, setting WRWST to 0 can provide enough timing margin for a successful write.

*RDWST*—Refer to Figure 2-3 of the Technical Reference Manual, the duration of the chip select assertion  $N = (RDWST + 2)*REF_CLK$ . RDWST = 3 is required to provide enough margin for a successful read.

*FCLKDIV*—The EMIFS reference clock REF\_CLK runs up to 50MHz. Assuming the system clock TC\_CK runs at 100MHz, and for the sake of demonstrating a timing analysis, FCLKDIV needs to be 01b, which divides the frequency of TC\_CK by two.

# EMIFS\_DWS - Dynamic Wait States Control Register

WRRDYMASK\_CSx—Since full-handshaking mode is not supported by the Cypress MoBL Dual-Port family, FLASH.RDY is masked and not monitored by the processor.

Full handshake enable for CSx—Since full-handshaking mode is not supported by the Cypress MoBL Dual-Port family, this feature needs to be disabled.

### EMIFS\_ACSx - Adv. Chip-Select Configuration Register

*OEHOLD*—Initiating proper read operations with Cypress MoBL Dual-Ports requires OEHOLD to be 0b.

OESETUP—Initiating proper read operations with Cypress MoBL Dual-Ports requires OESETUP to be 0b.

EMIFS control and configurations can be done dynamically. EMIFS ensures that a new CS configuration takes effect only when no access is requested (CS idle). To prevent inconsistency and critical behavior, the EMIFS configuration must be done by MPU software while other masters are inactive.

For more information about EMIFS register settings, please see OMAP1710 *Multimedia Processor Technical*

*Reference Manual*, TI literature number SWPU071B, September 2004.

### **Timing Considerations**

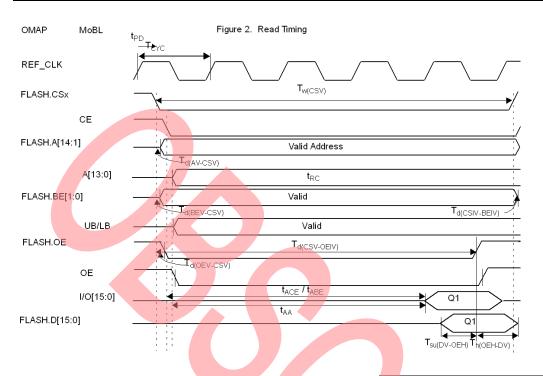

This section of the application note provides a sample timing analysis of read and write operations with the OMAP1710 Multimedia Processor and MoBL Dual-Port CYDM256A16-55.

## **Read Operation**

With an internal reference clock of 50 MHz (20-ns period), the register setting required to initiate proper read operation is shown in EMIFS Register Settings. RDWST, which defines the number of waitstates inserted, needs to be 3 REF\_CLK cycle. This essentially extends the chip select enable duration to 5 x REF\_CLK = 100 ns. shows the timing details of a read operation between the OMAP1710 and MoBL Dual-Port.

The signal names for the OMAP processor and the MoBL Dual-Port are shown on the left. Timing parameters for the OMAP1710 are shown with an uppercase T while parameters for the MoBL Dual-Port are shown with a lowercase t. Please refer to for timing parameter definitions.

| Symbol                    | Part | Description                                     | Min<br>(ns) | Max<br>(ns) |

|---------------------------|------|-------------------------------------------------|-------------|-------------|

| t <sub>PD</sub>           | PCB  | Board propagation delay                         |             | 1           |

| T <sub>CYC</sub>          | OMAP | REF_CLK period                                  | 2           | 0           |

| T <sub>W(CSV)</sub>       | OMAP | FLASH.CSx low duration                          | 98          | 102         |

| $T_{d(AV-CSV)}$           | OMAP | Delay, Address valid to<br>FLASH.CSx low        | -4          | 6           |

| T <sub>d(BEV-CSV)</sub>   | OMAP | Delay, FLASH.BEx valid to<br>FLASH.CSx low      | -5          | 2           |

| T <sub>d(CSIV-BEIV)</sub> | OMAP | Delay, FLASH.CSx high to<br>FLASH.BEx invalid   | -2          | 5           |

| T <sub>d(OEV-CSV)</sub>   | OMAP | Delay, FLASH.OE low to<br>FLASH.CSx low         | -1          | 5           |

| T <sub>d(CSV-OEIV)</sub>  | OMAP | Delay, FLASH.CSx low to<br>FLASH.OE high        | 95          | 98          |

| T <sub>su(DV-OEH)</sub>   | OMAP | Set-up, read data valid<br>before FLASH.OE high | 15          | -           |

| T <sub>h(OEH-DV)</sub>    | OMAP | Hold, read data valid after<br>FLASH.OE high    | -14         | -           |

#### Table 4. Read Timing Parameters

| t <sub>RC</sub>  | DP | Read cycle time                 | 55 | -  |

|------------------|----|---------------------------------|----|----|

| t <sub>ABE</sub> | DP | Bye enable access time          | -  | 55 |

| t <sub>ACE</sub> | DP | CE low to data valid            | -  | 55 |

| t <sub>AA</sub>  | DP | Address to data value           | -  | 55 |

| t <sub>OHA</sub> | DP | Output hold from address change | 5  | -  |

The following timing analysis is based on the timing parameters for the OMAP1710 EMIFS running at 50 MHz and Cypress MoBL Dual-Port CYDM256A16-55.

#### Propagation Delay

Propagation delay ( $t_{PD}$ ) is the board flight time between the OMAP1710 Multimedia Processor and the MoBL Dual-Port. This delay is important to take into account. A 3-inch FR-4 strip-line generates 0.528-ns delay (176-ps/inch delay) between the OMAP and the Dual-Port. The board propagation delay will vary for different board designs, and as a conservative assumption, 1 ns is used for this application note. Assume all signals going from OMAP1710 to the MoBL Dual-Port to have the same trace length and thus the same propagation delay. The only propagation delay that will be added is for the data coming back from the Dual-Port to the OMAP processor during a read operation.

#### Interfacing Cypress MoBL(R) Asynchronous Dual-Port to TI OMAP1710 Multimedia Processor

#### Worst Case Analysis

Since most timing parameters are specified with a range of guaranteed values, it is possible to perform a worst case timing analysis using the tightest timing budget provided by the data sheets of the two devices. Referring to Figure 2, the worst parameters are shown in Table 5.

#### Table 5. Worst Case Timing Parameters for Read

| Symbol                    | Worst Case (ns) | Explanation               |

|---------------------------|-----------------|---------------------------|

| T <sub>W(CSV)</sub>       | 98              | Shortest CE period        |

| $T_{d(AV-CSV)}$           | -4              | Slowest address assertion |

| T <sub>d(BEV-CSV)</sub>   | -5              | Slowest BE assertion      |

| T <sub>d(CSIV-BEIV)</sub> | -2              | Shortest BE assertion     |

| T <sub>d(OEV-CSV)</sub>   | -1              | Slowest OE assertion      |

| T <sub>d(CSV-OEIV)</sub>  | 95              | Shortest OE assertion     |

| T <sub>su(DV-OEH)</sub>   | 15              | Minimum set-up            |

| T <sub>h(OEH-DV)</sub>    | -14             | Minimum hold              |

| t <sub>RC</sub>           | 55              | Minimum read cycle        |

| t <sub>ABE</sub>          | 55              | Slowest access time       |

| t <sub>ACE</sub>          | 55              | Slowest access time       |

| t <sub>AA</sub>  | 55 | Slowest access time |

|------------------|----|---------------------|

| t <sub>она</sub> | 5  | Minimum hold time   |

#### Address

The read cycle timing window needs to be at least  $t_{RC}$  as required by the MoBL Dual-Port, meaning the address needs to be valid for at least 55 ns. Since all control signals are asserted with reference to FLASH.CSx of the OMAP processor, the worst case valid address assertion happens  $T_{d(AV-CSV)}$  (4 ns) after FLASH.CSx assertion. According to the OMAP documentations, the address line does not get deasserted until after the FLASH.CSx gets deasserted, thus a valid address will hold for at least  $T_{w(CSV)} + T_{d(AV-CSV)} = 98$  ns - 4 ns = 94 ns, which satisfies the 55-ns requirement of the MoBL Dual-Port.

#### Byte Enables and Output Enable

Similar to the address assertion, the byte and output enables are both asserted by the OMAP processor with reference to the FLASH.CSx signal. The worse case here is when byte enables are asserted  $T_{d(BEV-CSV)}$  (5 ns) after the assertion of the FLASH.CSx signal. Applying the same concept, output enable becomes available  $T_{d(OEV-CSV)}$  (1 ns) after the assertion of the FLASH.CSx signal. This satisfies timing as the data is read out from the Dual-Port at a much later time and the margin is sufficient for the given timing window

#### Data

The data is read from the MoBL Dual-Port with a certain access time after the address  $(t_{AA})$ , output enable  $(t_{DOE})$ , and chip or byte enables (t<sub>ACE</sub> or t<sub>ABE</sub>) become valid. In this case, since the chip enable signal acts as a reference to all other control signals driven by the OMAP processor, and  $t_{AA} = t_{ABE} = t_{ACE}$  (55 ns), the slowest control signals to become valid are the byte enables. Thus, the MoBL Dual-Port will provide the data  $T_{d(BEV-CSV)} + t_{ABE} = 5 \text{ ns} + 55 \text{ ns} =$ 60 ns after the assertion of FLASH.CSx. The data will propagate back to the OMAP processor and this incurs another 2 ns of propagation delay to the overall timing. That is, the data will arrive at the OMAP1710 processor 62 ns after the initial assertion of FLASH.CSx ( $t_{PD} \times 2 = 2$  ns, because data needs to propagate back to the OMAP1710). This data will then hold for t<sub>OHA</sub> (5 ns) after the address change

The minimum read data set-up time required by OMAP1710 is defined by  $T_{su(DV-OEH)}$ , which references to the time before FLASH.OE is deasserted. According to the worst case parameters, the FLASH.OE signal will be asserted for at least 95 ns after the assertion of FLASH.CSx. With the data coming back to the OMAP1710 62 ns after FLASH.CSx asserts low,  $T_{su(DV-OEH)} + 62$  ns = 15 ns + 62 ns = 77 ns  $\leq$  95 ns, which satisfies the 15-ns minimum set-up time. In terms of hold time, data needs to hold for  $T_{h(OEH-DV)}$  after the deassertion of FLASH.OE (–14 ns). Since the Dual-Port data is held valid for t<sub>OHA</sub> (5 ns) after the address change (same time as the deassertion of FLASH.CSx), the data hold time is easily satisfied.

#### Write Operation

Similar to the read operation, the write operation runs on the same internal EMIFS reference clock of 50 MHz. Please note that all write operations initiated by the OMAP1710 processor will be R/W (FLASH.WE) controlled, since the deassertion of the FLASH.WE signal happens  $T_{d(WEIV-CSIV)}$  before the deassertion of FLASH.CSx.

The register setting required to initiate proper write operation is shown in EMIFS Register Settings. WRWST is set to 0b, as no wait state is required. On the other hand, WELEN is set to 2b to satisfy the minimum write pulse length of  $t_{PWE}$  (40 ns). Table 6 shows the timing details of a write operation between the OMAP1710 and MoBL Dual-Port

The timing diagram in Table 6 demonstrates a write operation between the OMAP1710 Multimedia Processor and the MoBL Dual-Port. The following analysis is based on the timing parameters for the Cypress CYDM256A16-55 Dual-Port. Table 6 lists the parameters as specified by the data sheets of the two devices.

#### **Table 6. Write Timing Parameters**

| Symbol                    | Part | Description                                   | Min<br>(ns) | Max<br>(ns) |

|---------------------------|------|-----------------------------------------------|-------------|-------------|

| t <sub>PD</sub>           | PCB  | Board propagation delay                       |             | 1           |

| T <sub>CYC</sub>          | OMAP | REF_CLK period                                | 2           | :0          |

| T <sub>W(CSV)</sub>       | OMAP | FLASH.CSx low duration                        | 94          | 106         |

| $T_{d(\text{AV-CSV})}$    | OMAP | Delay, Address valid to<br>FLASH.CSx low      | -4          | 6           |

| $T_{d(\text{BEV-CSV})}$   | OMAP | Delay, FLASH.BEx valid to<br>FLASH.CSx low    | -5          | 2           |

| $T_{d(CSIV\text{-}BEIV)}$ | OMAP | Delay, FLASH.CSx high to<br>FLASH.BEx invalid | -2          | 5           |

| Td(CSV-WEV)               | OMAP | Delay, FLASH.CSx low to<br>FLASH.WE low       | 16          | 22          |

| T <sub>d(WEIV-CSIV)</sub> | OMAP | Delay, FLASH.WE high to<br>FLASH.CSx high     | 16          | 23          |

| T <sub>d(DV-CSV)</sub>    | OMAP | Delay, data bus valid to<br>FLASH.CSx low     | 1           | 9           |

| T <sub>d(DIV-CSIV)</sub>  | OMAP | Delay, data bus invalid to<br>FLASH.CSx high  | 0           | 9           |

| twc                       | DP   | Write cycle time                              | 55          | -           |

| t <sub>AW</sub>           | DP   | Address valid to write end                    | 45          | -           |

| t <sub>PWE</sub>          | DP   | Write pulse width                             | 40          | -           |

| t <sub>SD</sub>           | DP   | Data set-up to write end                      | 30          | -           |

| t <sub>HD</sub>           | DP   | Data hold from write end                      | 0           | -           |

The following sample timing analysis is based on the timing parameters for the OMAP1710 EMIFS running at 50 MHz and Cypress MoBL Dual-Port CYDM256A16-55.

#### Worst Case Analysis

Similar to the read operation, the same type of analysis is performed for the write operation. The worst case parameters are shown in Table 7.

| Symbol                    | Worst Case<br>(ns) | Explanation                         |

|---------------------------|--------------------|-------------------------------------|

| T <sub>W(CSV)</sub>       | 94                 | Shortest CE period                  |

| T <sub>d(AV-CSV)</sub>    | -4                 | Slowest address assertion           |

| T <sub>d(BEV-CSV)</sub>   | -5                 | Slowest BE assertion                |

| T <sub>d(CSIV-BEIV)</sub> | -2                 | Shortest BE assertion               |

| T <sub>d(CSV-WEV)</sub>   | 22                 | Slowest WE assertion                |

| T <sub>d(WEIV-CSIV)</sub> | 23                 | Shortest WE period                  |

| T <sub>d(DV-CSV)</sub>    | 1                  | Slowest data valid                  |

| T <sub>d(DIV-CSIV)</sub>  | 9                  | Shortest data valid period          |

| t <sub>wc</sub>           | 55                 | Minimum write cycle                 |

| t <sub>AW</sub>           | 45                 | Minimum address enable to write end |

| t <sub>PWE</sub>          | 40                 | Minimum write pulse width           |

| t <sub>SD</sub>           | 30                 | Minimum data setup time             |

| t <sub>HD</sub>           | 0                  | Minimum data hold time              |

#### Address

The write cycle timing window needs to be at least t<sub>WC</sub> as required by the MoBL Dual-Port, meaning the address needs to be valid for at least 55 ns. Since all control signals are asserted with reference to FLASH.CSx of the OMAP processor, the worst case valid address assertion happens T<sub>d(AV-CSV)</sub> (4 ns) after FLASH.CSx assertion. According to the OMAP documentations, the address line does not get deasserted until after the FLASH.CSx gets deasserted, thus a valid address will hold for at least T<sub>w(CSV)</sub> + T<sub>d(AV-CSV)</sub> = 94 ns - 4 ns = 90 ns, which satisfies the 55-ns requirement of the MoBL Dual-Port.

#### Byte Enables

Similar to the address assertion, the byte enables are asserted by the OMAP processor with reference to the FLASH.CSx signal. The worst case is when the byte enables are asserted  $T_{d(BEV-CSV)}$  (5 ns) after the assertion of the FLASH.CSx signal. This; however, does not impact the write operation, as the data is written into the Dual-Port at a much later time (when FLASH.WE is deasserted).

#### Data

The data is written into the MoBL Dual-Port on the rising edge of the R/W signal, and this needs to satisfy both the minimum address valid to R/W deassertion time (t<sub>AW</sub>) and the minimum write pulse width (t<sub>PWE</sub>) requirements. The minimum t<sub>AW</sub> required from the Dual-Port is 45 ns and the EMIFS supplies  $T_{W(CSV)} - T_{d(WEIV-CSIV)} = 94$  ns - 23 ns = 71 ns, which satisfies the 45-ns requirement. On the other hand, the minimum pulse width is satisfied, because  $T_{W(CSV)} - T_{d(WEIV-CSIV)} = 94$  ns - 23 ns - 22 ns = 49 ns, which also satisfies the minimum t<sub>PWE</sub> of 40 ns.

The minimum write set-up and hold time required by the MoBL Dual-Port is defined by  $t_{SD}$  and  $t_{HD}$ , respectively. These parameters are in reference to the time before and after the deassertion of the R/W signal. According to the worst case parameters, the data will be valid  $T_{d(DV-CSV)}$  with reference to the assertion of FLASH.CSx and becomes invalid  $T_{d(DIV-CSIV)}$  with reference to the deassertion of FLASH.CSx. This satisfies the  $t_{SD}$  set-up time, as the available set-up time is  $T_{W(CSV)} - T_{d(WEIV-CSIV)} = 94$  ns – 23 ns = 71 ns  $\geq$  30 ns, and the available hold time is  $T_{d(WEIV-CSIV)} = 23$  ns  $\geq$  0 ns.

# Conclusion

Systems using a TI OMAP1710 Multimedia Processor can easily benefit from the performance and flexibility of a Cypress Dual-Port. As one of the industry's lowest power consuming Dual-Ports, designing in the Cypress MoBL Dual-Port allows the customer to interconnect multiple processors in a system, where power is of the most concern, and without having to compromise in performance. In addition, as this application note has shown, the interface between the TI OMAP1710 and Cypress MoBL Dual-Ports does not require any glue logic, which will save valuable board spaces

For further information, please visit the Cypress web site at www.cypress.com. The web site also provides the latest data sheets, models, and any related documentation.

## References

- Cypress Semiconductor, CYDM256A16, CYDM128A16, CYDM064A16, CYDM128A08, CYDM064A08 1.8V 4K/8K/16K x16 and 8K/16K x8 MoBL<sup>®</sup> Dual-Port Static RAM Data sheet, January 2005.

- Texas Instruments, OMAP1710 Multimedia Processor Data Manual, Literature Number SWPS015, March 2004.

- Texas Instruments, OMAP1710 Multimedia Processor Technical Reference Manual, Literature Number SWPU071B, September 2004.

## **Additional Resources**

- a. Interfacing Cypress MoBL(R) Dual-Port to TI OMAP5912 Application Processor - AN5055.

- b. Interfacing Cypress MoBL(R) Asynchronous Dual-Port to TI OMAP2420 Multimedia Processor -AN5056.

- c. Implementing Interprocessor Using Cypress MoBL(R) Dual-ports and the Milbox Register -AN5074.

## About the Author

| Name:    | Hingkwan Huen             |

|----------|---------------------------|

| Title:   | Systems Engineer Sr Staff |

| Contact: | hkh@cypress.com           |

# **Document History**

Document Title: Interfacing Cypress MoBL(R) Asynchronous Dual-Port to TI OMAP1710 Multimedia Processor - AN5036 Document Number: 001-14799

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date        | Description of Change                                                                                                                              |

|----------|---------|--------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 483207  | ODC                | 04/25/2007                | New Spec.                                                                                                                                          |

| *A       | 3164700 | ODC                | 02/07/2011                | Updated as per template<br>Added Additional Resources heading and provided links to application notes.<br>Added Document History Page              |

| *В       | 3243575 | ODC                | 05/06/2011                | Hyperlink added to AN5055, AN5074, and AN5056.<br>Layout Guidelines section renames as Wiring Diagram<br>Additional Resources information updated. |

| *C       | 3607156 | AASI               | 05/02 <mark>/201</mark> 2 | Converted from FrameMaker to docx.                                                                                                                 |

| *D       | 4460895 | RSKV               | 07/30/2014                | Obsolete document.                                                                                                                                 |

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

# Products

| Automotive                 | cypress.com/go/automotive                      |

|----------------------------|------------------------------------------------|

| Clocks & Buffers           | cypress.com/go/clocks                          |

| Interface                  | cypress.com/go/interface                       |

| Lighting & Power Control   | cypress.com/go/powerpsoc<br>cypress.com/go/plc |

| Memory                     | cypress.com/go/memory                          |

| Optical Navigation Sensors | cypress.com/go/ons                             |

| PSoC                       | cypress.com/go/psoc                            |

| Touch Sensing              | cypress.com/go/touch                           |

| USB Controllers            | cypress.com/go/usb                             |

| Wireless/RF                | cypress.com/go/wireless                        |

|                            |                                                |

# **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/go/support

xx and xx are registered trademarks of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

© Cypress Semiconductor Corporation, 2007-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.