### **About this document**

### **Scope and purpose**

This application note describes how to set up the various clock sources in XMC7000 family MCUs and provides examples including configuring PLL/FLL and calibrating the ILO.

### **Intended audience**

This document is intended for anyone using XMC7000 family MCUs.

### **Associated part family**

XMC7000 family of XMC<sup>™</sup> industrial microcontrollers.

# Table of contents

# **Table of contents**

|         | it this document                     |                   |

|---------|--------------------------------------|-------------------|

| Table   | e of contents                        | 2                 |

| 1       | Introduction                         | 4                 |

| 2       | Clock system for XMC7000 family MCUs | 5                 |

| 2.1     | Overview                             | 5                 |

| 2.2     | Clock resources                      | 5                 |

| 2.3     | Clock system functions               | 6                 |

| 2.4     | Basic clock system settings          | 12                |

| 3       | Configuring the clock resources      | 13                |

| 3.1     | ECO configuration                    | 13                |

| 3.1.1   | Use case                             | 13                |

| 3.1.2   | Code preview                         | 15                |

| 3.2     | WCO configuration                    | 16                |

| 3.2.1   | Overview                             | 16                |

| 3.3     | Setting the IMO                      | 17                |

| 3.4     | Setting ILO0/ILO1                    | 17                |

| 4       | FLL and PLL configuration            | 18                |

| 4.1     | Setting the FLL                      | 18                |

| 4.1.1   | Overview                             | 18                |

| 4.1.2   | Use case                             | 18                |

| 4.1.3   | Code preview                         | 19                |

| 4.2     | Setting the PLL                      | 20                |

| 4.2.1   | Overview                             | 20                |

| 4.2.2   | Use case                             | 20                |

| 4.2.3   | Code preview                         | 22                |

| 5       | Internal clock configuration         | 24                |

| 5.1     | Configuring CLK_PATHx                | 24                |

| 5.1.1   | Code preview                         | 25                |

| 5.2     | Configuring CLK_HFx                  | 26                |

| 5.2.1   | Code preview                         | 27                |

| 5.3     | Configuring CLK_LF                   |                   |

| 5.4     | Configuring CLK_FAST_0/CLK_FAST_1    | 28                |

| 5.5     | Configuring CLK_MEM                  |                   |

| 5.6     | Configuring CLK_PERI                 | 28                |

| 5.7     | Configuring CLK_SLOW                 |                   |

| 5.8     | Configuring CLK_GR                   |                   |

| 5.9     | Configuring PCLK                     |                   |

| 5.9.1   | PCLK configuration example           |                   |

| 5.9.1.  |                                      |                   |

| 5.9.1.  | 8                                    |                   |

| 5.9.2   | Code preview                         |                   |

| 5.10    | Configuring the ECO Prescaler        |                   |

| 5.10.1  |                                      |                   |

| 6       | Supplementary information            |                   |

| 6.1     | Input clocks in peripheral functions |                   |

| 6.2     | Clock calibration counter function   |                   |

| 6.2.1   | Overview                             |                   |

| Applica | cation note 2                        | 002-34253 Rev. *C |

# Table of contents

| 6.2.2     | Use case                                                                             | 25 |

|-----------|--------------------------------------------------------------------------------------|----|

|           |                                                                                      |    |

| 6.2.3     | Configuration                                                                        | 35 |

| 6.2.3.1   | Sample code for initial configuration of clock calibration counter with ILO0 and ECO | 36 |

| 6.3       | CSV diagram and relationship of monitored clock and reference clock                  | 37 |

| Glossary  |                                                                                      | 39 |

| Reference | es                                                                                   | 40 |

| Revision  | history                                                                              | 41 |

|           | ·<br>!r                                                                              |    |

Introduction

# 1 Introduction

XMC7000 family MCUs are targeted at industrial systems. These products enable a secure computing platform and incorporate Infineon low-power flash memory along with multiple high-performance analog and digital functions.

XMC7000 family clock system supports high-speed and low-speed clocks using both internal and external clock sources. One of the typical use cases for clock input is for internal real-time clock (RTC). XMC7000 family supports phase-locked loop (PLL) and frequency-locked loop (FLL) to generate clocks that operate the internal circuit at a high speed. XMC7000 family also supports a function to monitor the clock operation and to measure the clock difference of each clock with reference to a known clock.

To understand more on the functionality described and terminology used in this application note, see the "Clocking System" chapter in the XMC7000 MCU family architecture reference manual.

**Clock system for XMC7000 family MCUs**

# 2 Clock system for XMC7000 family MCUs

### 2.1 Overview

The clock system in this series of MCUs is divided into two blocks. One selects the clock resources (such as external oscillator and internal oscillator) and multiplies the clock (using FLL and PLL). The other distributes and divides clocks to the CPU cores and other peripheral functions. However, there are some exceptions such as RTC that can connect directly to a clock resource.

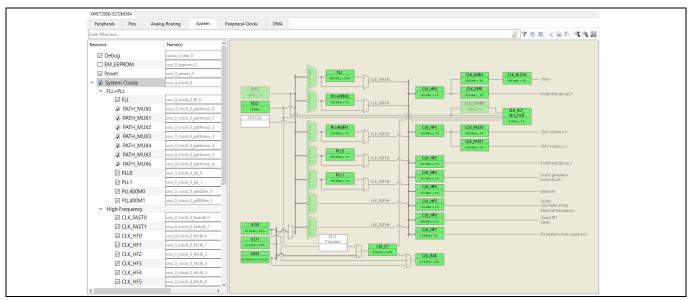

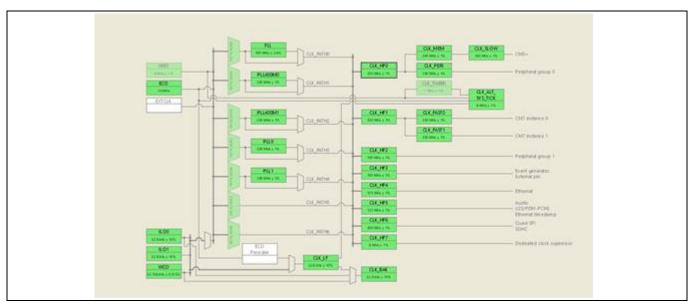

Figure 1 shows the overview of the clock system.

Figure 1 Clock system structure

### 2.2 Clock resources

The MCU supports two types of resource inputs – internal and external. Each of these internally supports three types of clocks, respectively.

- Internal clock sources (all clocks are enabled by default):

- Internal main oscillator (IMO): Built-in clock with a frequency of 8 MHz (Typical)

- Internal low-speed oscillator 0 (ILO0): Built-in clock with a frequency of 32.768 kHz (Typical)

- Internal low-speed oscillator 1 (ILO1): Has the same function as ILO0, but ILO1 can monitor the clock of ILO0

- External clock sources (all clocks are disabled by default):

- External crystal oscillator (ECO): Uses an external oscillator whose input frequency range is between 8 and 33.34 MHz

- Watch crystal oscillator (WCO): Uses an external oscillator whose frequency is stable 32.768 kHz, mainly used by the RTC module

- External clock (EXT\_CLK): The EXT\_CLK is a 0.25 MHz to 80 MHz range clock that can be sourced from a signal on a designed I/O pin. This clock can be used as the source clock for either PLL or FLL or can be used directly by the high-frequency clocks.

For more details on functions such as IMO, PLL, and so on, and numerical values such as frequency, see the XMC7000 MCU family architecture reference manual and the datasheet.

**Clock system for XMC7000 family MCUs**

# 2.3 Clock system functions

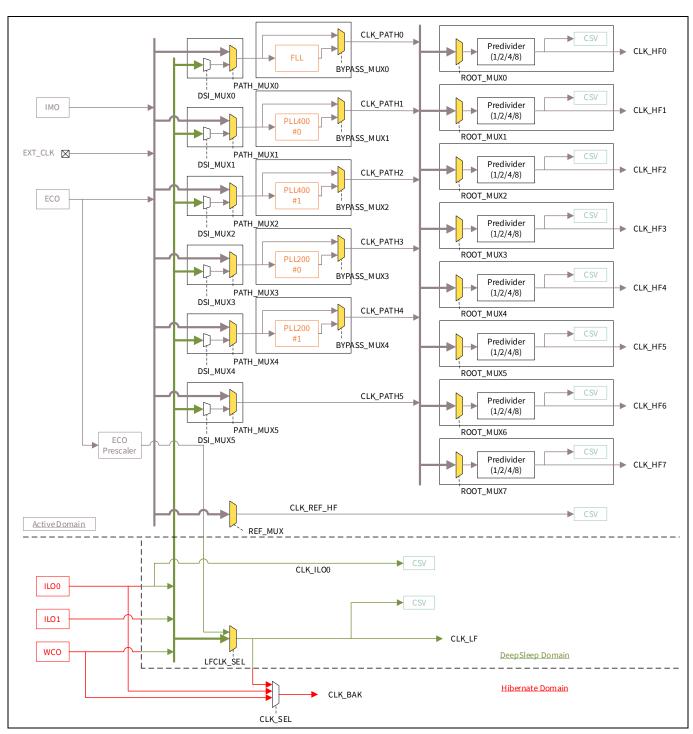

Figure 2 shows the details of the clock selection and multiplier block. This block generates root frequency clocks CLK\_HF0 to CLK\_HF7 from the clock resources. This block has the capability to select one of the supported clock resources – FLL and PLL to generate the required high-speed clock. This MCU supports two types of PLLs: PLL without spread spectrum clock generation (SSCG) and fractional operation (PLL200#x), and PLL with SSCG and fractional operation (PLL400#x).

Figure 2 Clock system block diagram

# Clock system for XMC7000 family MCUs

| Domain/block        | Description                                                                                                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active domain       | Region of operation only in Active power mode                                                                                                                  |

| DeepSleep<br>domain | Region of operation in Active and DeepSleep power modes                                                                                                        |

| Hibernate domain    | Region of operation in the All Power mode                                                                                                                      |

| ECO prescaler       | Divides the ECO and creates a clock that can be used with the CLK_LF clock. The division function has a 10-bit integer divider and an 8-bit fractional divider |

| DSI_MUX             | Selects a clock from ILO0, ILO1, and WCO                                                                                                                       |

| PATH_MUX            | Selects a clock from IMO, ECO, EXT_CLK, and DSI_MUX output                                                                                                     |

| CLK_PATH            | CLK_PATHs 0 through 5 are used as the input sources for high-frequency clocks                                                                                  |

| CLK_HF              | CLK_HFs 0 through 7 are recognized as high-frequency clocks                                                                                                    |

| FLL                 | Generates the high-frequency clock                                                                                                                             |

| PLL                 | Generates the high-frequency clock. There are two kinds of PLL:                                                                                                |

|                     | - PLL200: Without SSCG and fractional operation                                                                                                                |

|                     | - PLL400: With SSCG and fractional operation                                                                                                                   |

| BYPASS_MUX          | Selects the clock to be output to CLK_PATH. In case of FLL, the clock that can be selected is either the FLL output or clock input to FLL.                     |

| ROOT_MUX            | Selects the clock source of CLK_HFx. The clocks that can be selected are CLK_PATHs 0 through 5.                                                                |

| Predivider          | Predivider (divided by 1, 2, 4, or 8) is available to divide the selected CLK_PATH.                                                                            |

| REF_MUX             | Selects the CLK_REF_HF clock source                                                                                                                            |

| CLK_REF_HF          | Used to monitor CSV of CLK_HF                                                                                                                                  |

| LFCLK_SEL           | Selects the CLK_LF clock source                                                                                                                                |

| CLK_LF              | MCWDT source clock                                                                                                                                             |

| CLK_SEL             | Selects the clock to be input to the RTC                                                                                                                       |

| CLK_BAK             | Mainly input to the RTC                                                                                                                                        |

| CSV                 | Clock supervision to monitor the clock operation                                                                                                               |

Note:

The clock configuration is done one time via the ModusToolbox $^{\mathsf{TM}}$  Device Configurator; the settings code is auto generated.

# **Clock system for XMC7000 family MCUs**

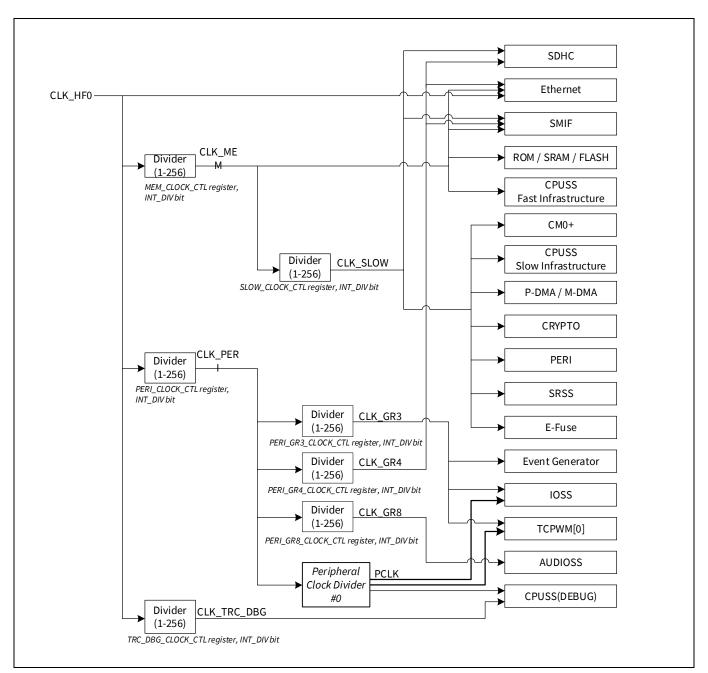

Figure 3 shows the distribution of CLK\_HF0.

CLK\_HF0 is the root clock for the CPU subsystem (CPUSS) and peripheral clock dividers. For more details on Figure 3, see the XMC7000 MCU family architecture reference manual and the datasheet.

Figure 3 CLK\_HF0 block diagram

### **Clock system for XMC7000 family MCUs**

| Clock input | Description                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_MEM     | Clock input to the CPUSS of Fast Infrastructure, Ethernet, and Serial Memory Interface (SMIF)                                                            |

| CLK_PERI    | Clock source for CLK_GR and peripheral clock divider                                                                                                     |

| CLK_SLOW    | Clock input to the CPUSS of Cortex®-M0+ and Slow Infrastructure, SDHC, and SMIF                                                                          |

| CLK_GR      | Clock input to peripheral functions. CLK_GR is grouped by the clock gater. CLK_GR has six groups.                                                        |

| PCLK        | Peripheral clock used in peripheral functions. PCLK can be configured for each channel of IPs independently; it can select one divider to generate PCLK. |

| CLK_TRC_DBG | Clock input to CPUSS(DEBUG)                                                                                                                              |

| Divider     | Divider has a function to divide each clock. It can be configured from 1 division to 256 divisions.                                                      |

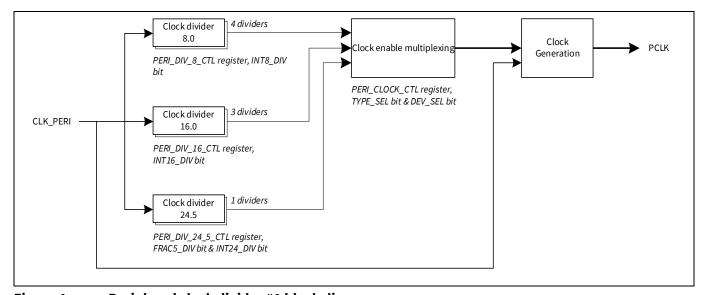

Figure 4 shows details of the peripheral clock divider #0.

This MCU needs a clock to each peripheral unit (the serial communication block (SCB), the Timer, Counter, and PWM (TCPWM), etc.) and its respective channel. The clocks are controlled by their respective dividers.

This peripheral clock divider #0 has many peripheral clock dividers to generate the peripheral clock (PCLK). See the datasheet for the number of dividers. The output of any of these dividers can be routed to any peripheral. Note that the dividers already in use cannot be used for other peripherals or channels.

Figure 4 Peripheral clock divider #0 block diagram

| Block                     | Description                                  |

|---------------------------|----------------------------------------------|

| Clock divider8.0          | Divides a clock by 8                         |

| Clock divider16.0         | Divides a clock by 16                        |

| Clock divider24.5         | Divides a clock by 24.5                      |

| Clock Enable Multiplexing | Enables the signal output from clock divider |

| Clock Generator           | Divides CLK_PERI based on clock divider      |

# **Clock system for XMC7000 family MCUs**

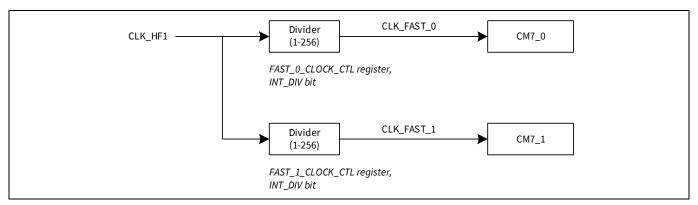

Figure 5 shows the distribution of CLK\_HF1.

CLK\_HF1 is a clock source for CLK\_FAST\_0 and CLK\_FAST\_1. The clock distribution of CLK\_HF1 is shown in Figure 5. CLK\_FAST\_0 and CLK\_FAST\_1 are the input sources for the CM7\_0 and CM7\_1 respectively.

CLK\_HF1 block diagram Figure 5

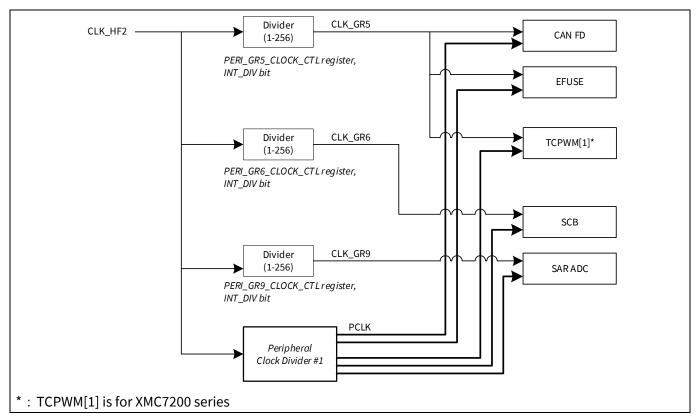

Figure 6 shows the distribution of CLK\_HF2.

CLK\_HF2 is a clock source for CLK\_GR and PCLK. The clock distribution of CLK\_HF2 is shown in Figure 6.

Figure 6 CLK\_HF2 block diagram

### **Clock system for XMC7000 family MCUs**

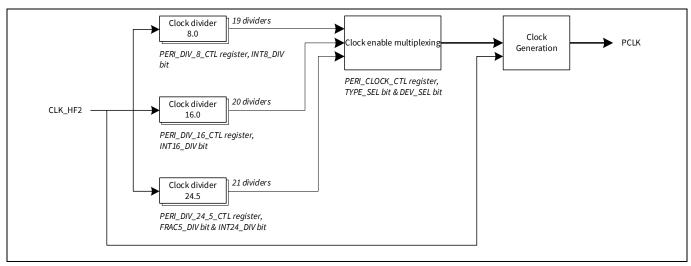

Figure 7 shows details of peripheral clock divider #1.

Peripheral clock divider #1 has many peripheral clock dividers to generate PCLK. See the datasheet for the number of each divider. The output of any of these dividers can be routed to any peripheral. Note that dividers already in use cannot be used for other peripherals or channels.

Figure 7 Peripheral clock divider #1 block diagram

| Block                     | Description                                      |

|---------------------------|--------------------------------------------------|

| Clock divider8.0          | Divides a clock by 8                             |

| Clock divider16.0         | Divides a clock by 16                            |

| Clock divider24.5         | Divides a clock by 24.5                          |

| Clock Enable Multiplexing | Enables the signal output from the clock divider |

| Clock Generator           | Divides CLK_PERI based on the clock divider      |

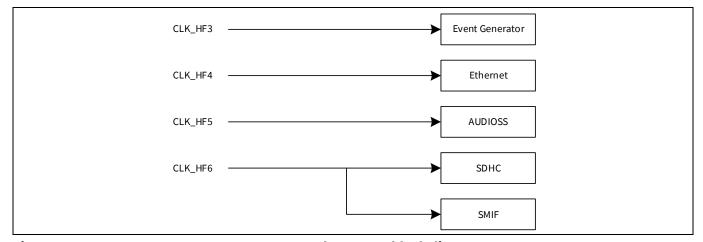

Figure 8 shows the distribution of CLK\_HF3, CLK\_HF4, CLK\_HF5, and CLK\_HF6. For more details on these functions in Figure 8, see the XMC7000 MCU family architecture reference manual.

Figure 8 CLK\_HF3, CLK\_HF4, CLK\_HF5, and CLK\_HF6 block diagram

CLK\_HF7 is dedicated to CSV. See the XMC7000 MCU family architecture reference manual for CSV description.

**Clock system for XMC7000 family MCUs**

# 2.4 Basic clock system settings

This section displays the configuration of the clock system in the Device Configurator of ModusToolbox $^{\text{\tiny TM}}$  software.

You can configure the clock system according to your system in the Device Configurator as follows:

Figure 9 Basic clock system setting

**Configuring the clock resources**

# 3 Configuring the clock resources

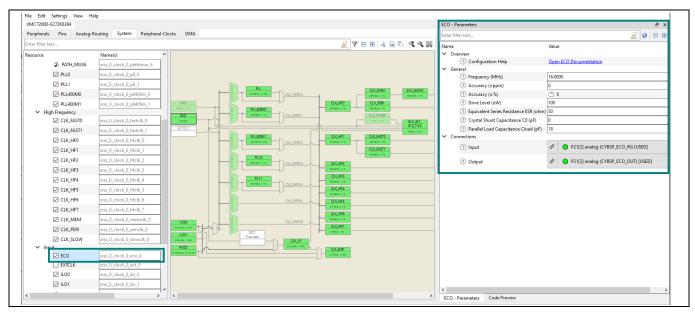

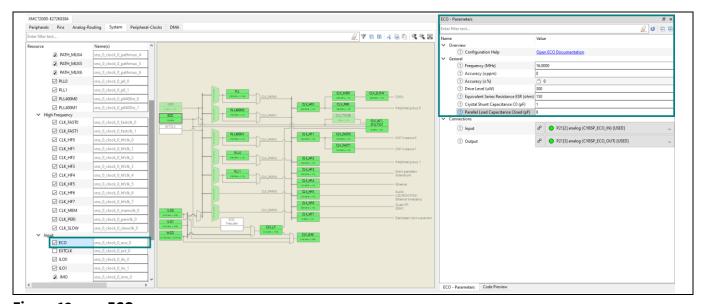

# 3.1 ECO configuration

The ECO is disabled by default and needs to be enabled for usage. Also, trimming is necessary to use the ECO. This device can set the trimming parameters that control the oscillator according to the crystal unit and ceramic resonator. The method to determine the parameters differs between the crystal unit and ceramic resonator.

You can configure these parameters in the **System** tab of the ModusToolbox™ Device Configurator. ModusToolbox™ software will automatically generate the corresponding code.

Figure 10 ECO configuration

### 3.1.1 Use case

| Oscillator to use                                              | Crystal unit |

|----------------------------------------------------------------|--------------|

| Fundamental frequency                                          | 16 MHz       |

| Maximum drive level                                            | 300.0 μW     |

| Equivalent series resistance                                   | 150.0 ohm    |

| Shunt capacitance                                              | 0.530 pF     |

| Parallel load capacitance                                      | 8.000 pF     |

| Crystal unit vendor's recommended value of negative resistance | 1500 ohm     |

| Automatic gain control                                         | OFF          |

Note: These values are decided in consultation with the crystal unit vendor.

You can configure these parameters in the **System** tab of the Device Configurator; based on these, ModusToolbox™ software automatically generates the corresponding code.

# **Configuring the clock resources**

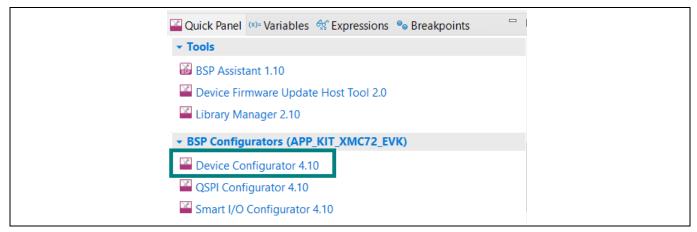

### Double-click the **Device Configurator on the left Quick Panel.**

(you can also double-click design.modus to open the Device Configurator in your project,\bsps\TARGET\_APP\_KIT\_XMC72\_EVK\config\design.modus)

Figure 11 **Quick Panel**

Figure 12 **ECO** use case

**Configuring the clock resources**

# 3.1.2 Code preview

This code is auto generated after configuration in the Device Configurator.

```

#include "cy_gpio.h"

#include "cy_sysclk.h"

#define CY_CFG_SYSCLK_ECO_ENABLED 1

#define CY CFG SYSCLK ECO FREQ 16000000UL

#define CY_CFG_SYSCLK_ECO_GPIO_IN_PRT GPIO_PRT21

#define CY_CFG_SYSCLK_ECO_GPIO_IN_PIN 2

#define CY_CFG_SYSCLK_ECO_GPIO_OUT_PRT GPIO_PRT21

#define CY_CFG_SYSCLK_ECO_GPIO_OUT_PIN 3

#define CY_CFG_SYSCLK_ECO_CLOAD 8UL

#define CY_CFG_SYSCLK_ECO_ESR 150UL

#define CY_CFG_SYSCLK_ECO_DRIVE_LEVEL 300UL

#if (!defined(CY_DEVICE_SECURE))

STATIC_INLINE void Cy_SysClk_EcoInit()

(void) Cy_GPIO_Pin_FastInit(GPIO_PRT21, 2, CY_GPIO_DM_ANALOG, OUL, HSIOM_SEL_GPIO);

(void) Cy GPIO Pin FastInit (GPIO PRT21, 3, CY GPIO DM ANALOG, OUL, HSIOM SEL GPIO);

if (CY_SYSCLK_BAD_PARAM == Cy_SysClk_EcoConfigure(CY_CFG_SYSCLK_ECO_FREQ, 9UL, 150UL, 300UL))

cycfg_ClockStartupError(CY_CFG_SYSCLK_ECO_ERROR);

if (CY_SYSCLK_TIMEOUT == Cy_SysClk_EcoEnable(3000UL))

cycfg_ClockStartupError(CY_CFG_SYSCLK_ECO_ERROR);

#endif //(!defined(CY_DEVICE_SECURE))

```

Figure 13 Code preview

**Configuring the clock resources**

# 3.2 WCO configuration

### 3.2.1 Overview

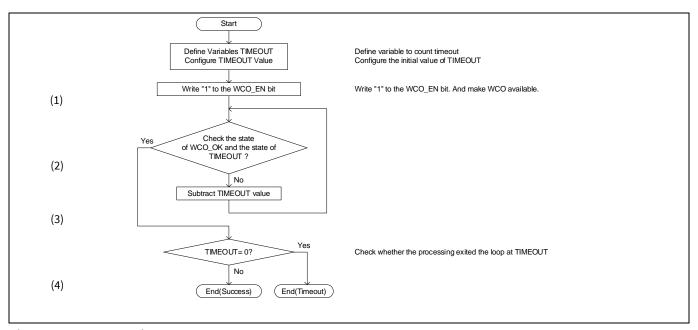

The WCO is disabled by default. Accordingly, WCO cannot be used unless it is enabled. Figure 14 shows how to configure the registers for enabling the WCO.

To disable the WCO, write '0' to the WCO\_EN bit of the BACKUP\_CTL register.

Figure 14 Enabling the WCO

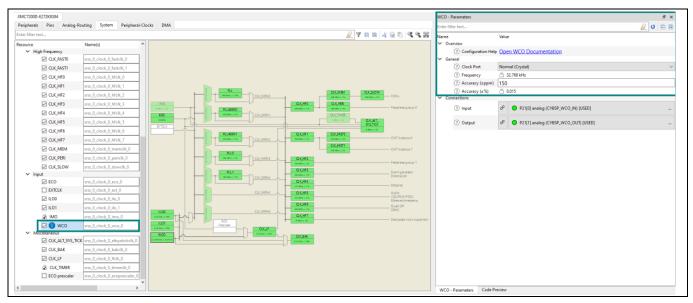

You can enable the WCO in the **System** tab of the Device Configurator. ModusToolbox™ software automatically generates the corresponding code.

Figure 15 WCO Configuration

### **Configuring the clock resources**

This code is auto generated after configuration in the Device Configurator.

```

#include "cy_gpio.h"

#include "cy sysclk.h"

#define CY_CFG_SYSCLK_WCO_ENABLED 1

#define CY_CFG_SYSCLK_WCO_IN_PRT GPIO_PRT21

#define CY_CFG_SYSCLK_WCO_IN_PIN OU

#define CY_CFG_SYSCLK_WCO_OUT_PRT GPIO_PRT21

#define CY CFG SYSCLK WCO OUT PIN 1U

#define CY_CFG_SYSCLK_WCO_BYPASS CY_SYSCLK_WCO_NOT_BYPASSED

#if ((!CY_CPU_CORTEX_M4) || (!defined(CY_DEVICE_SECURE)))

___STATIC_INLINE void Cy_SysClk_WcoInit()

(void)Cy_GPIO_Pin_FastInit(GPIO_PRT21, OU, 0x00U, 0x00U, HSIOM_SEL_GPIO);

(void) Cy GPIO Pin FastInit (GPIO PRT21, 1U, 0x00U, 0x00U, HSIOM SEL GPIO);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_WcoEnable(1000000UL))

cycfg_ClockStartupError(CY_CFG_SYSCLK_WCO_ERROR);

#endif //((!CY_CPU_CORTEX_M4) || (!defined(CY_DEVICE_SECURE)))

```

Figure 16 **Code preview**

#### **Setting the IMO** 3.3

The IMO is enabled by default so that all functions operate properly. The IMO will automatically be disabled during DeepSleep, Hibernate, and XRES modes. Therefore, it is not required to set IMO explicitly.

#### 3.4 **Setting ILO0/ILO1**

ILO0 and ILO1 are enabled by default.

Note:

ILO0 is used as the operating clock of the watchdog timer (WDT). Therefore, if ILO0 is disabled, you should disable the WDT. To disable ILO0, write '0b01' to the WDT\_LOCK bit of the WDT\_CTL register, and then write '0b00' to the ENABLE bit of the CLK\_ILO0\_CONFIG register.

### **FLL and PLL configuration**

# 4 FLL and PLL configuration

This section shows the configuration of FLL and PLL in the clock system.

# 4.1 Setting the FLL

### 4.1.1 Overview

The FLL must be configured before it is used. The FLL has a current-controlled oscillator (CCO); the output frequency of this CCO is controlled by adjusting the trim of the CCO.

### **4.1.2** Use case

| Input clock frequency  | 16 MHz  |

|------------------------|---------|

| Output clock frequency | 100 MHz |

You can configure these parameters in the **System** tab of the Device Configurator; based on these, ModusToolbox™ software automatically generates the corresponding code.

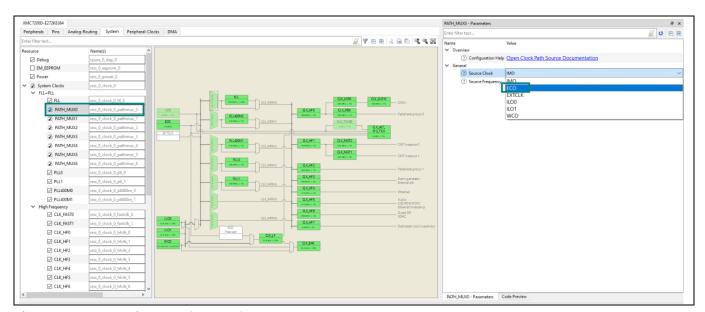

- 1. In the Device Configurator, select PATH\_MUX0.

- 2. On the PATH\_MUX Parameters pane, select ECO (16 MHz) as the source clock.

Figure 17 Setting ECO (16 MHz) as the source clock

### **FLL and PLL configuration**

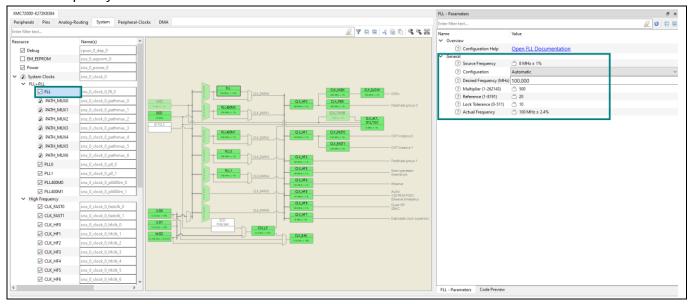

Select FLL, and in the FLL – Parameters pane, under General, enter the **Desired Frequency (MHz)** as 100.000 to set the frequency as 100 MHz.

Figure 18 Setting output clock frequency as 100.000 MHz

# 4.1.3 Code preview

Figure 19 Code preview

**FLL and PLL configuration**

#### **Setting the PLL** 4.2

#### 4.2.1 **Overview**

You must configure the PLL before using it.

You can configure these parameters in the System tab of the Device Configurator; based on these, ModusToolbox™ software automatically generates the corresponding code.

#### 4.2.2 **Use case**

| Parameter              | Value                   |

|------------------------|-------------------------|

| Input clock frequency  | 8.000 MHz               |

| Output clock frequency | 350.000 MHz (PLL400 #0) |

|                        | 250 MHz (PLL400 #1)     |

|                        | 200.000 MHz (PLL200 #0) |

|                        | 100.000 MHz (PLL200 #1) |

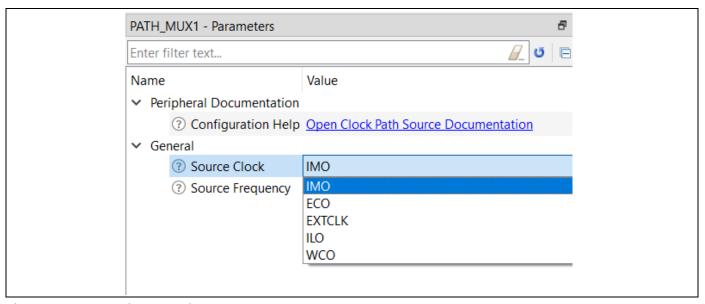

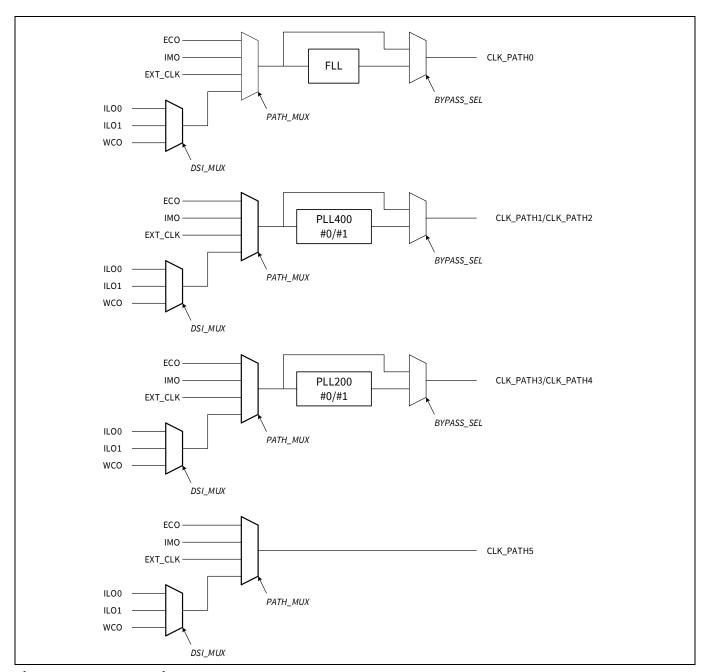

First, select the source clock for PLL400M#0/PLL400M#1/PLL200M#0/PLL200M#1 in PATH\_MUX1/PATH\_MUX2/PATH\_MUX3/PATH\_MUX4.

Figure 20 Setting 'IMO' in 'Parameters'

### **FLL and PLL configuration**

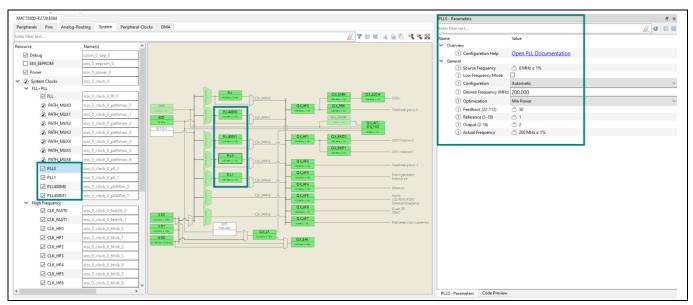

Configure the corresponding desired frequency as follows:

Figure 21 Configuring output frequency in 'Parameters'

Figure 22 Configuring output frequency in 'Parameters'

### **FLL and PLL configuration**

# 4.2.3 Code preview

```

#include "cy_sysclk.h"

#define CY_CFG_SYSCLK_PLL2_ENABLED 1

#define CY_CFG_SYSCLK_PLL2_FEEDBACK_DIV 50

#define CY_CFG_SYSCLK_PLL2_REFERENCE_DIV 1

#define CY_CFG_SYSCLK_PLL2_OUTPUT_DIV 2

#define CY_CFG_SYSCLK_PLL2_LF_MODE_false

#define CY_CFG_SYSCLK_PLL2_OUTPUT_MODE_CY_SYSCLK_FLLPLL_OUTPUT_AUTO

#define CY_CFG_SYSCLK_PLL2_OUTPUT_FREQ 200000000

#if (!defined(CY_DEVICE_SECURE))

static const cy_stc_pll_manual_config_t srss_0_clock_0_pll_0_pllConfig =

.feedbackDiv = 50,

.referenceDiv = 1,

.outputDiv = 2,

.lfMode = false,

.outputMode = CY_SYSCLK_FLLPLL_OUTPUT_AUTO,

#endif //(!defined(CY_DEVICE_SECURE))

_STATIC_INLINE void Cy_SysClk_P112Init()

Cy_SysClk_PllDisable(SRSS_PLL_200M_0_PATH_NUM);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllManualConfigure(SRSS_PLL_200M_0_PATH_NUM, &srss_0_clock_0_pll_0_pllConfig))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllEnable(SRSS_PLL_200M_0_PATH_NUM, 10000u))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

```

Figure 23 Code preview for PLL200M#0 configuration

```

#include "cy_sysclk.h"

#define CY CFG SYSCLK PLL3 ENABLED 1

#define CY_CFG_SYSCLK_PLL3_FEEDBACK_DIV 25

#define CY_CFG_SYSCLK_PLL3_REFERENCE_DIV 1

#define CY_CFG_SYSCLK_PLL3_OUTPUT_DIV 2

#define CY_CFG_SYSCLK_PLL3_LF_MODE false

#define CY_CFG_SYSCLK_PLL3_OUTPUT_MODE CY_SYSCLK_FLLPLL_OUTPUT_AUTO

#define CY_CFG_SYSCLK_PLL3_OUTPUT_FREQ 100000000

#if (!defined(CY_DEVICE_SECURE))

static const cy_stc_pll_manual_config_t srss_0_clock_0_pll_1_pllConfig =

.feedbackDiv = 25.

.referenceDiv = 1,

.outputDiv = 2,

.lfMode = false,

.outputMode = CY_SYSCLK_FLLPLL_OUTPUT_AUTO,

#endif //(!defined(CY_DEVICE_SECURE))

_STATIC_INLINE void Cy_SysClk_P113Init()

Cy_SysClk_PllDisable(SRSS_PLL_200M_1_PATH_NUM);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllManualConfigure(SRSS_PLL_200M_1_PATH_NUM, &srss_0_clock_0_pl1_1_pllConfig))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllEnable(SRSS_PLL_200M_1_PATH_NUM, 10000u))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

```

Figure 24 Code preview for PLL200M#1 configuration

### **FLL and PLL configuration**

```

#include "cy_sysclk.h"

#define CY_CFG_SYSCLK_PLL0_ENABLED 1

#define CY_CFG_SYSCLK_PLL0_FEEDBACK_DIV 87

#define CY_CFG_SYSCLK_PLL0_REFERENCE_DIV 1

#define CY_CFG_SYSCLK_PLL0_OUTPUT_DIV 2

#define CY_CFG_SYSCLK_PLL0_FRAC_DIV 8388608

#define CY_CFG_SYSCLK_PLL0_FRAC_DITHER_EN false

#define CY_CFG_SYSCLK_PLL0_FRAC_EN true

#define CY_CFG_SYSCLK_PLL0_LF_MODE false

#define CY_CFG_SYSCLK_PLL0_OUTPUT_MODE CY_SYSCLK_FLLPLL_OUTPUT_AUTO

#define CY_CFG_SYSCLK_PLL0_OUTPUT_FREQ 350000000

static const cy_stc_pll_manual_config_t srss_0_clock_0_pl1400m_0_pl1Config =

.feedbackDiv = 87.

.referenceDiv = 1,

.outputDiv = 2,

.lfMode = false

.outputMode = CY_SYSCLK_FLLPLL_OUTPUT_AUTO,

.fracDiv = 8388608,

.fracDitherEn = false,

.fracEn = true,

1:

_STATIC_INLINE void Cy_SysClk_P110Init()

Cy_SysClk_PllDisable(SRSS_PLL_400M_0_PATH_NUM);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllManualConfigure(SRSS_PLL_400M_0_PATH_NUM, &srss_0_clock_0_pll400m_0_pllConfig))

cycfg ClockStartupError(CY CFG SYSCLK PLL ERROR);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllEnable(SRSS_PLL_400M_0_PATH_NUM, 10000u))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

```

Figure 25 Code preview for PLL400M#0 configuration

```

#include "cy_sysclk.h"

#define CY_CFG_SYSCLK_PLL1_ENABLED 1

#define CY_CFG_SYSCLK_PLL1_FEEDBACK_DIV 62

#define CY_CFG_SYSCLK_PLL1_REFERENCE_DIV 1

#define CY CFG SYSCLK PLL1 OUTPUT DIV 2

#define CY_CFG_SYSCLK_PLL1_FRAC_DIV 8388608

#define CY_CFG_SYSCLK_PLL1_FRAC_DITHER_EN false

#define CY_CFG_SYSCLK_PLL1_FRAC_EN true

#define CY_CFG_SYSCLK_PLL1_LF_MODE false

#define CY_CFG_SYSCLK_PLL1_OUTPUT_MODE CY_SYSCLK_FLLPLL_OUTPUT_AUTO

#define CY_CFG_SYSCLK_PLL1_OUTPUT_FREQ 250000000

static const cy_stc_pll_manual_config_t srss_0_clock_0_pl1400m_l_pl1Config =

.feedbackDiv = 62,

.referenceDiv = 1,

.outputDiv = 2,

.lfMode = false

.fracDitherEn = false,

.fracEn = true,

_STATIC_INLINE void Cy_SysClk_PlllInit()

Cy_SysClk_PllDisable(SRSS_PLL_400M_1_PATH_NUM);

if (CY_SYSCLK_SUCCESS != CY_SysClk_PllManualConfigure(SRSS_PLL_400M_1_PATH_NUM, &srss_0_clock_0_pll400m_1_pllConfig))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

if (CY_SYSCLK_SUCCESS != Cy_SysClk_PllEnable(SRSS_PLL_400M_1_PATH_NUM, 10000u))

cycfg_ClockStartupError(CY_CFG_SYSCLK_PLL_ERROR);

}

```

Code preview for PLL400M#1 configuration Figure 26

**Internal clock configuration**

#### Internal clock configuration 5

#### 5.1 **Configuring CLK\_PATHx**

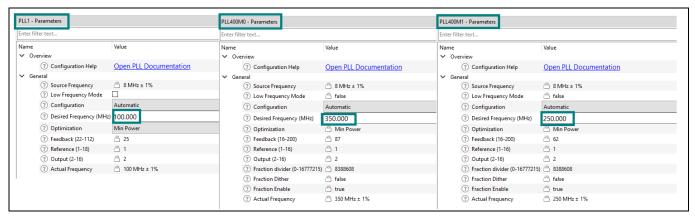

CLK\_PATHx is used as the input source for root clocks CLK\_HFx. CLK\_PATHx can select all clock resources including the FLL and PLL using DSI\_MUX and PATH\_MUX. CLK\_PATH5 cannot select the FLL and PLL, but other clock resources can be selected.

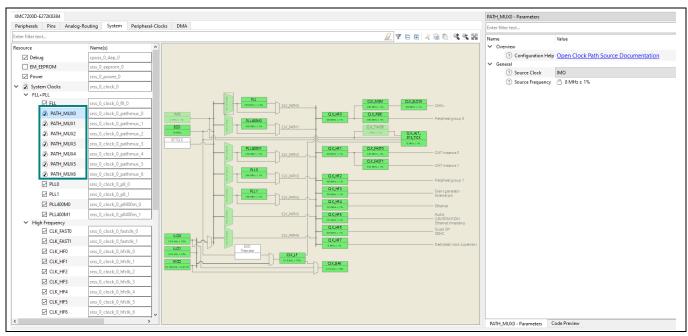

Figure 27 shows the generation diagram for CLK\_PATHx.

**Generating CLK\_PATHx** Figure 27

### **Internal clock configuration**

You can configure CLK\_PATHx in the **System** tab of the Device Configurator. ModusToolbox™ software automatically generates the corresponding code.

Figure 28 **CLK\_PATHx** configuration

#### **Code preview** 5.1.1

```

#include "cy_sysclk.h"

#if defined (CY_USING_HAL)

#include "cyhal_hwmgr.h"

#endif //defined (CY_USING_HAL)

#define CY_CFG_SYSCLK_CLKPATH0_ENABLED 1

#define CY CFG SYSCLK CLKPATHO SOURCE CY SYSCLK CLKPATH IN ECO

#define CY_CFG_SYSCLK_CLKPATH0_SOURCE_NUM 1UL

#if defined (CY_USING_HAL)

const cyhal_resource_inst_t srss_0_clock_0_pathmux_0_obj =

.type = CYHAL_RSC_CLKPATH,

.block_num = 0U,

.channel_num = 0U,

#endif //defined (CY_USING_HAL)

STATIC_INLINE void Cy_SysClk_ClkPath0Init()

Cy_SysClk_ClkPathSetSource(OU, CY_CFG_SYSCLK_CLKPATHO_SOURCE);

void init_cycfg_system(void)

#if defined (CY_USING_HAL)

cyhal_hwmgr_reserve(&srss_0

pendif //defined (CY_USING_HAL)

_0_clock_0_pathmux_0_obj);

```

Figure 29 Code preview for CLK\_PATHx configuration

**Internal clock configuration**

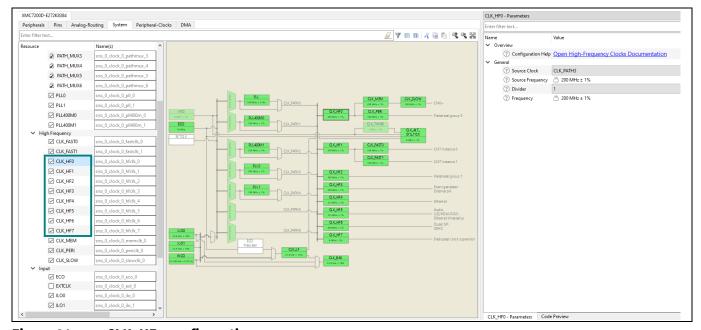

# 5.2 Configuring CLK\_HFx

CLK\_HFx (x=0,1,2,3,4,5,6,7) can be selected from any CLK\_PATHy (y=0,1,2,3,4,5). A predivider is available to divide the selected CLK\_PATHx. CLK\_HF0 is always enabled because it is the source clock for the CPU cores. CLK\_HFx can be disabled.

To enable CLK\_HFx, write '1' to the ENABLE bit of each CLK\_ROOT\_SELECT register. To disable CLK\_HFx, write '0' to the ENABLE bit of each CLK\_ROOT\_SELECT register.

The ROOT\_DIV bit of the CLK\_ROOT register sets the predivider values from the options: No division, divide by 2, by 4, and by 8.

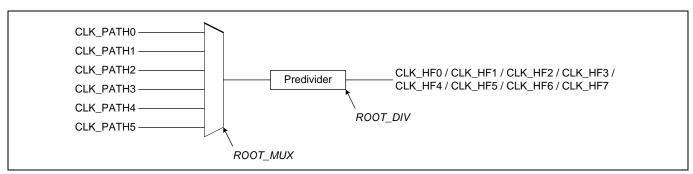

Figure 30 shows the details of ROOT\_MUX and the predivider.

Figure 30 ROOT\_MUX and predivider

You can configure CLK\_HFx in the **System** tab of the Device Configurator. ModusToolbox™ software automatically generates the corresponding code.

Figure 31 CLK\_HFx configuration

**Internal clock configuration**

# 5.2.1 Code preview

```

#include "cy_sysclk.h"

#define CY_CFG_SYSCLK_CLKHF0_ENABLED 1

#define CY_CFG_SYSCLK_CLKHF0_DIVIDER CY_SYSCLK_CLKHF_NO_DIVIDE

#define CY_CFG_SYSCLK_CLKHF0_OUL

#define CY_CFG_SYSCLK_CLKHF0_FREQ_MHZ_200UL

#define CY_CFG_SYSCLK_CLKHF0_CLKPATH CY_SYSCLK_CLKHF_IN_CLKPATH3

#define CY_CFG_SYSCLK_CLKHF0_CLKPATH_NUM_3UL

__STATIC_INLINE void Cy_SysClk_ClkHf0Init()

{

Cy_SysClk_ClkHfSetSource(OU, CY_CFG_SYSCLK_CLKHF0_CLKPATH);

Cy_SysClk_ClkHfSetDivider(OU, CY_SYSCLK_CLKHF0_DIVIDE);

Cy_SysClk_ClkHfDirectSel(CY_CFG_SYSCLK_CLKHF0, false);

}

```

Figure 32 Code preview for CLK\_HFx configuration

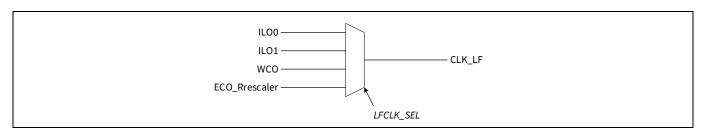

# 5.3 Configuring CLK\_LF

CLK\_LF can be selected from one of the possible sources: WCO, ILO0, ILO1, and ECO\_Prescaler. CLK\_LF cannot be set when the WDT\_LOCK bit in the WDT\_CTL register is disabled because CLK\_LF can select ILO0 that is input clock for the WDT.

Figure 33 shows the details of LFCLK\_SEL that CLK\_LF is configured.

Figure 33 LFCLK\_SEL

Table 1 shows the required registers for CLK\_LF. See the XMC7000 MCU family architecture reference manual for more details.

Table 1 Configuring of CLK\_LF

| Register name | Bit name       | Value | Selected item         |

|---------------|----------------|-------|-----------------------|

| CLK_SELECT    | LFCLK_SEL[2:0] | 0     | ILO0                  |

|               |                | 1     | WCO                   |

|               |                | 5     | ILO1                  |

|               |                | 6     | ECO_Prescaler         |

|               |                | Other | Reserved. Do not use. |

**Internal clock configuration**

# 5.4 Configuring CLK\_FAST\_0/CLK\_FAST\_1

CLK\_FAST\_0 and CLK\_FAST\_1 are generated by dividing CLK\_HF1 by (x+1). When configuring CLK\_FAST\_0 and CLK\_FAST\_1, configure a value (x = 0..255) divided by the FRAC\_DIV bit and INT\_DIV bit of the CPUSS\_FAST\_0\_CLOCK\_CTL register and CPUSS\_FAST\_1\_CLOCK\_CTL register.

### 5.5 Configuring CLK\_MEM

CLK\_MEM is generated by dividing CLK\_HF0; its frequency is configured by the value obtained by dividing CLK\_HF0 by (x+1). When configuring CLK\_MEM, configure a value (x = 0..255) divided by the INT\_DIV bit of the CPUSS\_MEM\_CLOCK\_CTL register.

# 5.6 Configuring CLK\_PERI

CLK\_PERI is the clock input to the peripheral clock divider and CLK\_GR. CLK\_PERI is generated by dividing CLK\_HF0; its frequency is configured by the value obtained by dividing CLK\_HF0 by (x+1). When configuring CLK\_PERI, configure a value (x = 0..255) divided by the INT\_DIV bit of the CPUSS\_PERI\_CLOCK\_CTL register.

# 5.7 Configuring CLK\_SLOW

CLK\_SLOW is generated by dividing CLK\_MEM; its frequency is configured by the value obtained by dividing CLK\_MEM by (x+1). After configuring CLK\_MEM, configure a value divided (x = 0..255) by the INT\_DIV bit of the CPUSS\_SLOW\_CLOCK\_CTL register.

# 5.8 Configuring CLK\_GR

The clock source of CLK\_GP is CLK\_PERI in Group 3, 4, 8, and CLK\_HF2 in Group 5, 6, and 9. Groups 3, 4, and 8 are clocks divided by CLK\_PERI. To generate CLK\_GR3, CLK\_GR4, and CLK\_GR8, write the division value (from 1 to 255) to divide the INT8\_DIV bit of the CPUSS\_PERI\_GRX\_CLOCK\_CTL register.

# 5.9 Configuring PCLK

PCLK is a clock that activates each peripheral function. Peripheral Clock Dividers have a function to divide CLK\_PERI and generate a clock to be supplied to each peripheral function. For assignment of the peripheral clocks, see the "Peripheral Clocks" section in the datasheet.

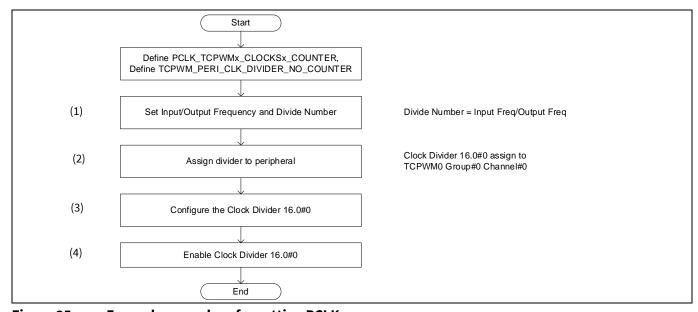

Figure 34 shows the flow to set peripheral clock dividers. See the XMC7000 MCU family architecture reference manual for more details.

### **Internal clock configuration**

Figure 34 Procedure to generate PCLK

Internal clock configuration

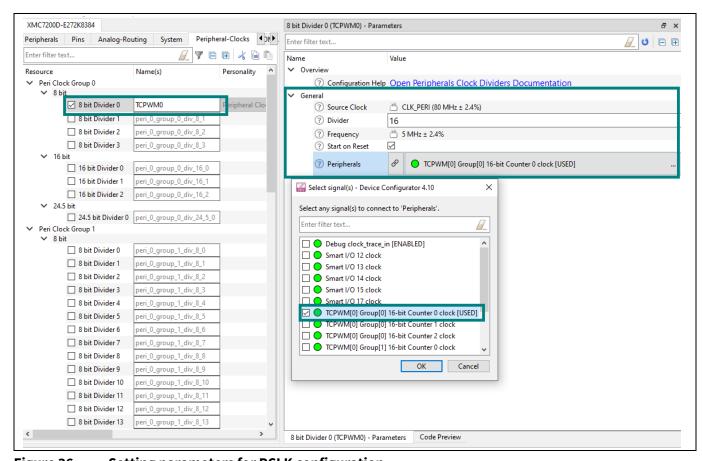

# **5.9.1** PCLK configuration example

### 5.9.1.1 Use case

| Parameter                      | Value                           |

|--------------------------------|---------------------------------|

| Input clock frequency          | 80 MHz                          |

| Output clock frequency         | 2 MHz                           |

| Divider type                   | Clock divider 16.0              |

| Used divider                   | Clock divider 16.0#0            |

| Peripheral clock output number | 31 (TCPWM0, Group#0, Counter#0) |

Figure 35 Example procedure for setting PCLK

**Internal clock configuration**

# 5.9.1.2 Configuration

You can configure these parameters in the **Peripheral-Clocks** tab of the Device Configurator; based on these, ModusToolbox™ software automatically generates the corresponding code.

- 1. In the Device Configurator, select the **System** tab.

- 2. Select FLL, and in the FLL Parameters pane, under General, enter the Desired Frequency (MHz) as 80.000 to set the frequency as 80 MHz.

- 3. Select CLK\_HF0 and select CLK\_PATH0 in Source Clock

- 4. Select CLK\_PERI, under General, enter '1' in Divider

- 5. In **Peripheral-Clocks** tab, set the parameters as follows:

Figure 36 Setting parameters for PCLK configuration

**Internal clock configuration**

# 5.9.2 Code preview

```

/st NOTE: This is a preview only. It combines elements of the

* cycfg_clocks.c and cycfg_clocks.h files located in the folder

* C:/PSVP/bsp_csp/source/bsps/catlc/KIT_XMC72_EVK/config/GeneratedSource.

#include "cy_sysclk.h"

#if defined (CY_USING_HAL)

#include "cyhal_hwmgr.h"

#define TCPWM0_HW CYHAL_CLOCK_BLOCK_PERIPHERAL0_8BIT

#endif //defined (CY_USING_HAL)

#if !defined (CY USING HAL)

#define TCPWM0_HW CY_SYSCLK_DIV_8_BIT

#endif //!defined (CY_USING_HAL)

#define TCPWM0_NUM OU

#define TCPWM0_GRP_NUM (OU << PERI_PCLK_GR_NUM_Pos)

#if defined (CY_USING_HAL)

const cyhal_resource_inst_t TCPWM0_obj =

.type = CYHAL_RSC_CLOCK,

.block_num = TCPWM0_HW,

.channel_num = TCPWM0_NUM,

1;

#endif //defined (CY_USING_HAL)

void init_cycfg_clocks(void)

Cy_SysClk_PeriPclkDisableDivider((en_clk_dst_t)TCPWM0_GRP_NUM, CY_SYSCLK_DIV_8_BIT, 0U);

Cy_SysClk_PeriPclkSetDivider((en_clk_dst_t)TCPWM0_GRP_NUM, CY_SYSCLK_DIV_8_BIT, 0U, 15U);

Cy_SysClk_PeriPclkEnableDivider((en_clk_dst_t)TCPWM0_GRP_NUM, CY_SYSCLK_DIV_8_BIT, 0U);

void reserve_cycfg_clocks(void)

#if defined (CY_USING_HAL)

cyhal_hwmgr_reserve(&TCPWM0_obj);

#endif //defined (CY_USING_HAL)

```

Figure 37 Code preview for PCLK configuration

**Internal clock configuration**

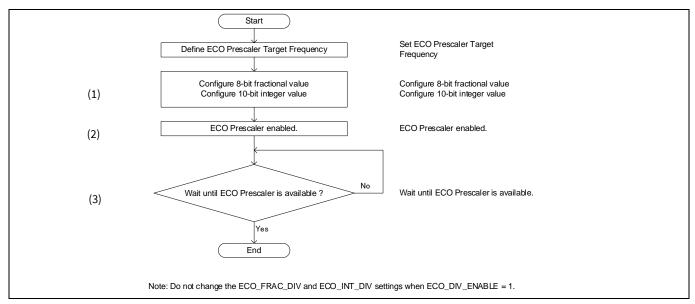

# 5.10 Configuring the ECO Prescaler

### 5.10.1 Overview

The ECO\_Prescaler divides the ECO and creates a clock that can be used with CLK\_LF. The division function has a 10-bit integer divider and an 8-bit fractional divider.

Figure 38 shows the steps to enable ECO\_Prescaler. For details on the ECO\_Prescaler, see XMC7000 MCU family architecture reference manual.

Figure 38 Enabling the ECO\_Prescaler

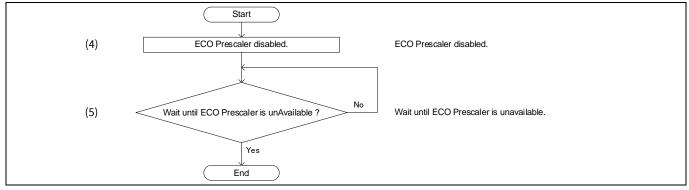

Figure 39 shows the steps to disable the ECO\_Prescalar. For details on the ECO\_Prescaler, see XMC7000 MCU family architecture reference manual.

Figure 39 Disabling the ECO\_Prescaler

**Supplementary information**

# **6** Supplementary information

# 6.1 Input clocks in peripheral functions

You can view the clock inputs for each peripheral function in the **System** tab of the Device Configurator.

For detailed values of PCLK, see the "Peripheral Clocks" section of the datasheet.

Figure 40 Clock inputs

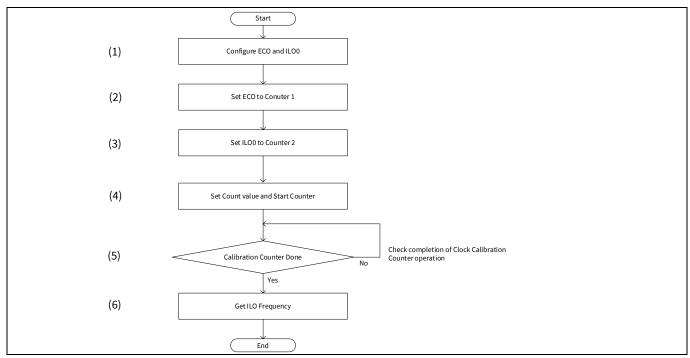

### 6.2 Clock calibration counter function

### 6.2.1 Overview

The clock calibration counter has two counters that can be used to compare the frequency of two clock sources. All clock sources are available as a source for these two clocks.

- 1. Calibration Counter1 counts clock pulses from Calibration Clock1 (the high-accuracy clock used as the reference clock). Counter1 counts in decreasing order.

- 2. Calibration Counter2 counts clock pulses from Calibration Clock2 (measurement clock). This counter counts in increasing order.

- 3. When Calibration Counter1 reaches 0, Calibration Counter2 stops counting, and its value can be read.

- 4. The frequency of Calibration Counter2 can be obtained by using the value and the following equation:

$$CalibrationClock2 = \frac{Counter2value}{Counter1value} \times CalibrationClock1$$

Figure 41 shows an example of the clock calibration counter function when ILO0 and ECO are used. ILO0 and ECO must be enabled. See ILO0 and ECO for 3.4 Setting ILO0/ILO1 and 3.1 ECO.

### **Supplementary information**

Figure 41 Example of clock calibration counter with ILO0 and ECO

### **6.2.2** Use case

| Parameter                   | Value                           |

|-----------------------------|---------------------------------|

| Measurement clock           | ILO0 clock frequency 32.768 kHz |

| Reference clock             | ECO clock frequency 16 MHz      |

| Reference clock count value | 40000ul                         |

# 6.2.3 Configuration

Table 2 lists the parameters and Table 3 lists the functions of the configuration part in ModusToolbox™ CAT1 Peripheral Driver Library for Clock Calibration Counter with ILO0 and ECO settings.

Table 2 Configuration parameters for Clock calibration counter with ILO0 and ECO

| Parameters                       | Description                              | Value                            |

|----------------------------------|------------------------------------------|----------------------------------|

| ITO_0                            | Define the ILO_0 configuration parameter | Oul                              |

| ILO_1                            | Define the ILO_1 configuration parameter | 1ul                              |

| ILONo                            | Define the measurement clock             | ILO_0                            |

| clockMeasuredInfo[].name         | Measurement clock                        | CY_SYSCLK_MEAS_CLK_ILO0<br>= 1ul |

| clockMeasuredInfo[].measuredFreq | Store the measurement clock frequency    | -                                |

| counter1                         | Reference clock count value              | 40000ul                          |

| CLK_FREQ_ECO                     | ECO clock frequency                      | 16000000ul (16 MHz)              |

### **Supplementary information**

Table 3 Functions for clock calibration counter with ILO0 and ECO

| Functions                                                                 | Description                                      | Value                                                      |

|---------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------|

| GetILOClockFreq()                                                         | Get the ILO 0 Frequency                          | -                                                          |

| Cy_SysClk_StartClk MeasurementCounters (clk1, count1, clk2)               | Set and start calibration Clk1: Reference clock  | [Set the counter]  clk1 = CY_SYSCLK_MEAS_CLK_ECO = 0x101ul |

|                                                                           | Count1: Measurement period                       | count1 = counter1                                          |

|                                                                           | Clk2: Measurement clock                          | clk2 = clockMeasuredInfo[].name                            |

| <pre>Cy_SysClk_ClkMeasurement CountersDone()</pre>                        | Check if counter measurement is done             | -                                                          |

| Cy_SysClk_ClkMeasurement<br>CountersGetFreq<br>(MesauredFreq, refClkFreq) | Get the measurement clock frequency              |                                                            |

|                                                                           | MesauredFreq: Stored measurement clock frequency | MesauredFreq = clockMeasuredInfo[].measuredFreq            |

|                                                                           | refClkFreq: Reference clock frequency            | refClkFreq = CLK_FREQ_ECO                                  |

# 6.2.3.1 Sample code for initial configuration of clock calibration counter with ILOO and ECO

The following is the sample code:

```

/* Scenario: ILO frequency may be drifting. Measure the ILO frequency

using

the clock measurement counters, with the IMO as the

reference. */

#define EC0 FREQ

1600000UL /* 16 MHz ECO */

/* 32.768 kHz ILO */

32768UL

#define ILO NOMINAL

/\star Start the ILO clock measurement using the ECO \star/

(void) Cy SysClk StartClkMeasurementCounters (CY SYSCLK MEAS CLK ILO,

/* Counter 1 clock = ILO */

0x7FUL,

/* Counter 1 period = 128 */

CY SYSCLK MEAS CLK ECO);

/* Counter 2 clock = IMO */

/* Wait for counter 1 to reach 0 */

while(!Cy SysClk ClkMeasurementCountersDone()){}

/* Measure clock 1 with the ECO clock cycles (counter 2) */

uint32 t measuredFreq = Cy SysClk ClkMeasurementCountersGetFreq(false,

ECO FREQ);

if (measuredFreq != ILO NOMINAL)

/* Take appropriate action such as trimming the ILO or changing the

LFCLK source */

```

### **Supplementary information**

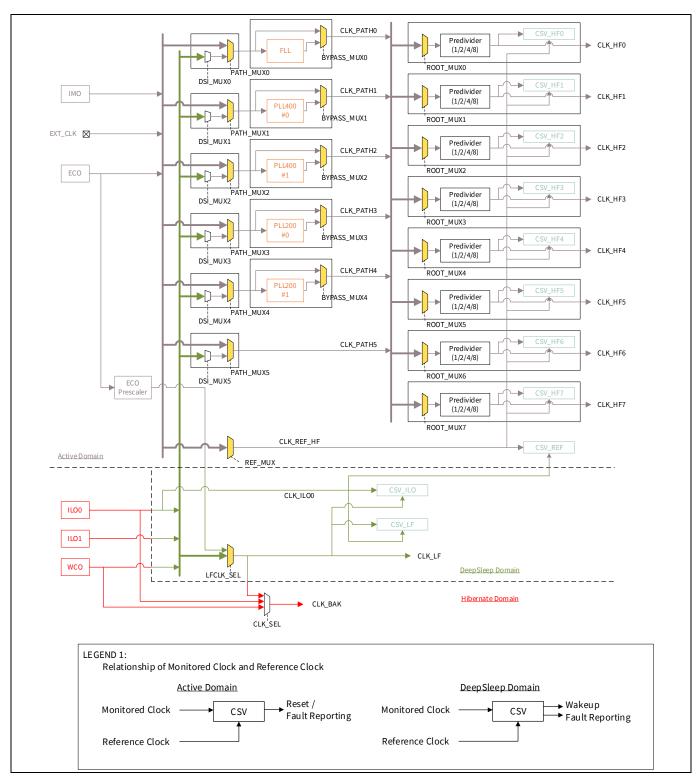

# 6.3 CSV diagram and relationship of monitored clock and reference clock

Figure 42 shows the clock diagram with monitored clock and reference clock for CSV. Table 4 shows the relationship between monitored clock and reference clock.

Figure 42 CSV diagram

# **Supplementary information**

Table 4 Monitored clock and reference clock

| <b>CSV</b> components | Monitor clock      | Reference clock    | Notes                                                     |

|-----------------------|--------------------|--------------------|-----------------------------------------------------------|

| CSV_HF0               | CSV_HF0            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF1               | CLK_HF1            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF2               | CLK_HF2            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF3               | CLK_HF3            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF4               | CLK_HF4            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF5               | CLK_HF5            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF6               | CLK_HF6            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_HF7               | CLK_HF7            | CLK_REF_HF         | CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. |

| CSV_REF               | CLK_REF_HF         | ILO0<br>(CLK_ILO0) | -                                                         |

| CSV_ILO               | ILO0<br>(CLK_ILO0) | CLK_LF             | CLK_LF is selected from WCO, ILO1, or ECO Prescaler.      |

| CSV_LF                | CLK_LF             | ILO0<br>(CLK_ILO0) | _                                                         |

Glossary

# Glossary

### Table 5 Glossary

| Terms                     | Description                                                                                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUDIOSS                   | Audio Subsystem. See the "Audio Subsystem" chapter of the XMC7000 MCU family architecture reference manual for details.                                                                     |

| CAN FD                    | CAN FD is the CAN with Flexible Data rate, and CAN is the Controller Area Network. See the "CAN FD Controller" chapter of the XMC7000 MCU family architecture reference manual for details. |

| CLK_FAST_0                | Fast lock. CLK_FAST is used for the CM7 and CPUSS Fast Infrastructure.                                                                                                                      |

| CLK_FAST_1                | Fast clock. CLK_FAST is used for the CM7 and CPUSS Fast Infrastructure.                                                                                                                     |

| CLK_HF                    | High-frequency clock. Both CLK_FAST and CLK_SLOW are derived from CLK_HF. CLK_HF, CLK_FAST and CLK_SLOW are synchronous to each other.                                                      |

| CLK_GR                    | Group clock. CLK_GR is the clock input to peripheral functions.                                                                                                                             |

| CLK_MEM                   | Memory clock. CLK_MEM clocks the CPUSS fast infrastructure.                                                                                                                                 |

| CLK_PERI                  | Peripheral clock. CLK_PERI is the clock source for CLK_SLOW, CLK_GR and peripheral clock divider.                                                                                           |

| CLK_SLOW                  | Slow clock. CLK_FAST is used for the CM0+ and CPUSS slow Infrastructure.                                                                                                                    |

| Clock calibration counter | Clock calibration counter has a function to calibrate the clock using two clocks.                                                                                                           |

| CSV                       | Clock supervision                                                                                                                                                                           |

| ECO                       | External crystal oscillator                                                                                                                                                                 |

| EXT_CLK                   | External clock                                                                                                                                                                              |

| FLL                       | Frequency-locked loop                                                                                                                                                                       |

| ILO                       | Internal low-speed oscillator                                                                                                                                                               |

| IMO                       | Internal main oscillator                                                                                                                                                                    |

| Peripheral Clock Divider  | Peripheral clock divider derives a clock for the use of each peripheral function.                                                                                                           |

| PLL200                    | Phase-locked loop. This PLL is not implemented for SSCG and fractional operation.                                                                                                           |

| PLL400                    | Phase-locked Loop. This PLL is implemented for SSCG and fractional operation.                                                                                                               |

| SAR ADC                   | Successive approximation register analog-to-digital converter. See the "SAR ADC" chapter of the XMC7000 MCU family architecture reference manual for details.                               |

| SCB                       | Serial communication block. See the "Serial Communication Block (SCB)" chapter of the XMC7000 MCU family manual for details.                                                                |

| SDHC                      | Secure Digital High-Capacity Host Controller. See the "SDHC Host Controller" chapter of the XMC7000 MCU family architecture reference manual for details.                                   |

| SMIF                      | Serial Memory Interface. See the "Serial Memory Interface" chapter of the XMC7000 MCU family architecture reference manual for details.                                                     |

| TCPWM                     | Timer, counter, and pulse width modulator. See the "Timer, Counter, and PWM" chapter of the XMC7000 MCU family architecture reference manual for details.                                   |

| WCO                       | Watch crystal oscillator                                                                                                                                                                    |

### References

### References

- [1] Datasheet

- XMC7100 XMC7000 microcontroller 32-bit Arm® Cortex®-M7

- XMC7200 XMC7000 microcontroller 32-bit Arm® Cortex®-M7

- [2] Architecture reference manual

- XMC7000 MCU family architecture reference manual

- [3] Registers reference manual

Note: Contact Technical support to obtain these documents.

- 002-33817: XMC7100 registers reference manual

- 002-33812: XMC7200 registers reference manual

# **Revision history**

# **Revision history**

| Document revision | Date       | Description of changes                     |

|-------------------|------------|--------------------------------------------|

| **                | 2021-12-13 | Initial release                            |

| *A                | 2022-05-06 | Updated 5.9 Configuring PCLK               |

|                   |            | Updated 5.10 Configuring the ECO Prescaler |

|                   |            | Updated Supplementary information          |

| *B                | 2023-01-09 | Updated 3.1.1 Use case                     |

| *C                | 2023-11-08 | Updated 2.2 Clock resources                |

|                   |            | Updated 2.4 Basic clock system settings    |

|                   |            | Updated 3.1.1 Use case and 3.2.1 Overview  |

|                   |            | Updated 4.1.2 Use case and 4.2.2 Use case  |

|                   |            | Updated 5.9.1 PCLK configuration example   |

|                   |            | Added Associated part family               |

|                   |            | Updated the References section             |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2023-11-08 Published by

Infineon Technologies AG 81726 Munich, Germany

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference 002-34253 Rev. \*C

#### Important notice

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Narnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.