#### About this document

#### Scope and purpose

This application note describes the method for creating an *nvram.txt* file, which is then used to test a new board design, optimize NVRAM values, and program the one-time programmable (OTP) nonvolatile memory in the AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip device using the PCIe or SDIO host interface for WLAN.

#### **Intended audience**

This document is intended for design and applications engineers, and includes information on:

- NVRAM content development and OTP memory programming flow

- Customizing the nvram.txt file

- OTP memory programming procedure

#### **Table of contents**

| Abou  | ut this document                                        | 1  |

|-------|---------------------------------------------------------|----|

| Table | e of contents                                           |    |

| 1     | Introduction                                            | 2  |

| 1.1   | IoT resources                                           | 2  |

| 2     | OTP memory programming considerations                   |    |

| 3     | NVRAM content development and memory programming flow   | 4  |

| 4     | Customizing the nvram.txt file                          | 6  |

| 4.1   | Using the nvram.txt file template                       |    |

| 4.2   | Editing the nvram.txt file                              | 16 |

| 4.3   | Finalizing the nvram.txt file                           |    |

| 5     | Programming the OTP memory                              | 18 |

| 5.1   | Programming the basic parameters into the OTP memory    | 18 |

| 5.2   | Creating and editing the OTP binary map                 | 26 |

| 6     | Programming the CYW5459x OTP memory using Gigabyte Brix |    |

| 6.1   | Programming the OTP memory                              | 33 |

| 7     | Programming the CYW5459x OTP BD address                 |    |

| Revis | sion history                                            |    |

Introduction

# 1 Introduction

The AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip is a single-chip IEEE 802.11 ac 2x2 MIMO/RSDB WLAN + Bluetooth<sup>®</sup> 5.0 device for embedded applications. One-time programmable (OTP) nonvolatile memory is included in the WLAN section of the device to store board-specific information such as PCIe header, product ID, manufacturer ID, and MAC address. Excluding the internal header information, up to 1150 bytes of useraccessible OTP memory is available on the CYW5459x for WLAN information. The application note provides OTP programming information for both PCIe and SDIO host interfaces.

The OTP memory content, along with an editable NVRAM file (*nvram.txt* file), provides all configuration information used by the WLAN device driver to initialize and configure the CYW5459x device.

#### 1.1 IoT resources

The wealth of data available **here** will help you to select the right IoT device for your design, and quickly and effectively integrate the device into your design. You can access a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates. You can acquire technical documentation and software from the **Support Community website**.

OTP memory programming considerations

## 2 OTP memory programming considerations

In embedded designs where the host and device are permanently connected, which is typically done using a hardwired PCIe or SDIO interface is the only mandatory entry to be programmed into OTP memory is the PCIe or SDIO header. This is because there are certain PCIe or SDIO function settings (such as L1 sub-state for low power) which are read before the firmware and NVRAM are downloaded. To properly set these settings, the PCIe or SDIO header must be programmed into their OTP memory.

Other than the PCIe or SDIO header, all other NVRAM parameters can be stored in the host's nonvolatile memory rather than in OTP memory. For non-embedded devices that may be installed on different hosts, the OTP memory can be programmed to protect the unique MAC address and prevent end-users from altering the power control parameters such as maximum output power.

The initial state of all OTP bits in an unprogrammed device is 0. Individual bits can be set to 1, but once set, the bits can never be reset to 0. The entire OTP array can be programmed in a single-write cycle using the w1 commands provided with the PCIe or SDIO driver. As an alternative, multiple write cycles can be used to selectively program specific fields. However, only the bits that are still in the 0 state can be set to the 1 state during each programming cycle.

The OTP programming process is irreversible, so it is recommended that you finalize all NVRAM parameters before programming any of the parameter into the OTP memory. Test the boards and modules using only the editable *nvram.txt* file.

The driver loads the parameters stored in the *nvram.txt* file onto on-chip RAM, allowing the chip to be tested even if the OTP memory has only been programmed with the PCIe or SDIO header. This method allows you to tune the RF components and alter critical parameters using different versions of the *nvram.txt file* while testing boards. Optionally, a few basic parameters, such as the board type and MAC address, can be programmed into the OTP memory prior to board testing during development.

- *Note:* If a parameter is present in both the on-chip OTP memory and the nvram.txt file, the value in the OTP memory takes priority over the value in the nvram.txt file.

- Note: The programming process of an OTP memory is irreversible. Infineon strongly recommends conducting development on boards using the parameters provided in the editable nvram.txt file. Do not program the OTP memory until the contents of the nvram.txt file have been verified and the file has been finalized for production use. The one exception to this is the PCIe or SDIO header, which must be programmed into OTP memory for full PCIe or SDIO functionality.

NVRAM content development and memory programming flow

#### 3 NVRAM content development and memory programming flow

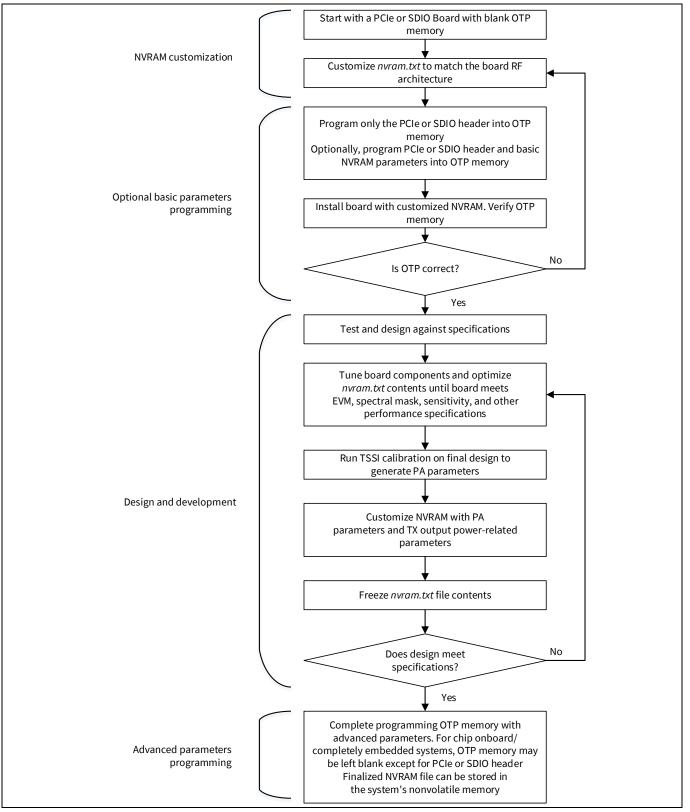

**Figure 1** shows the *nvram.txt* file content development and the OTP memory programming flow. Parameters in the *nvram.txt* file can be divided into basic and advanced categories.

Note: Conduct the NVRAM development and OTP programming flow shown in **Figure 1** on fewer boards/modules during the product development stage. Once this process is complete and the production version of the nvram.txt file and OTP memory file is approved for production use, programming can begin for high volume mass production as defined by each manufacturer.

#### OTP memory programming and NVRAM development - AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip

#### NVRAM content development and memory programming flow

Figure 1 NVRAM development and programming flow of OTP memory

Customizing the nvram.txt file

# 4 Customizing the nvram.txt file

This section describes customizing, editing, and finalizing the *nvram.txt* file for OTP memory programming.

#### 4.1 Using the nvram.txt file template

For each reference board design, Infineon provides an *nvram.txt* file for the specific board design. Typically, the file is named in accordance with the board it supports (for example, *cyw5459xwliparef.txt*).

The *nvram.txt* file might be included with the reference board design package or the driver release. The latest version of the file can be downloaded from the **Developer Community**.

**Table 1** provides a list of parameters in a typical *nvram.txt* file that are common to dual-band 802.11ac 2x2MIMO PCIe or SDIO reference design boards.

Parameters in the *nvram.txt* file need not be entered in any specific order.

The parameters listed in **Table 1** are used and specified by Infineon and should only be changed by Infineon. It is important that a customer's design is reviewed by Infineon early in the development process. Some of the parameters in **Table 1** may need to be changed by Infineon to accommodate differences in the RF front end between the customer's design and the Infineon reference design from which it was derived.

| NVRAM parameter | Example data | Description                                                                                        |

|-----------------|--------------|----------------------------------------------------------------------------------------------------|

| sromrev         | 11           | SROM revision for 802.11ac chips                                                                   |

| boardtype       | 0x084e       | This is a critical parameter that should be copied from a similar Infineon reference board design. |

| tssipos2g       | 1            | This represents if TSSI has positive slope for 2.4 GHz. For CYW5459x, set the value to 1.          |

| tssipos5g       | 1            | This represents if TSSI has positive slope for 5 GHz. For CYW5459x, set the value to 1.            |

| rxchain         | 3            | This specifies the number of rx paths (bit mask). For CYW5459x, set the value to 3.                |

| txchain         | 3            | This specifies the number of tx paths (bit mask). For CYW5459x, set the value to 3.                |

| antswitch       | 0            | <ul><li>This enables switch-based diversity:</li><li>0: disable</li><li>1: enable</li></ul>        |

| vendid          | 0x14e4       | PCIe vendor ID                                                                                     |

|                 | 0x4416       | PCIe device ID, CYW54590                                                                           |

| devid           | 0x4417       | PCIe device ID, CYW54591                                                                           |

|                 | 0x441a       | PCIe device ID, CYW54594                                                                           |

| manfid          | 0x02d0       | Manufacturer ID                                                                                    |

| vendid          | 0x04b4       | SDIO vendor ID                                                                                     |

|                 | 0xbd3a       | SDIO device ID, CYW54590                                                                           |

| devid           | 0xbd3b       | SDIO device ID, CYW54591                                                                           |

|                 | 0xbd3c       | SDIO device ID, CYW54594                                                                           |

| nocrc           | 1            | Check for CRC errors when loading firmware                                                         |

Table 1

Infineon-specific NVRAM parameters

#### Customizing the nvram.txt file

| NVRAM parameter                                      | Example data                                          | Description                                                                                                                                                                                                           |

|------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| boardflags<br>boardflags2<br>boardflags3             | 0x00480201<br>0x00800000<br>0x48700186                | Board configuration flag that defines the power topology, external components (iPA, eLNA), and so on                                                                                                                  |

| tworangetssi2g<br>tworangetssi5g                     | 0<br>0                                                | 2.4-GHz and 5-GHz TSSI dual power range flag, which iPA chips support                                                                                                                                                 |

| xtalfreq                                             | 37400                                                 | Describes the reference oscillator frequency in kHz. '37400' stands for 37.4 MHz.                                                                                                                                     |

| extpagain2g                                          | 2                                                     | Supports 5-GHz external PA. Use '2' for iPA boards, and use '0' for ePA boards.                                                                                                                                       |

| extpagain5g                                          | 2                                                     | Supports 5-GHz external PA. Use '2' for iPA boards, and use '0' for ePA boards.                                                                                                                                       |

| aa2g, aa5g                                           | 3                                                     | <ul> <li>Number of antennas available for the 2.4-GHz and 5-GHz bands, respectively, in bit-mapped binary format:</li> <li>1 = 01b for one antenna</li> <li>3 = 11b for two antennas (applies to CYW5459x)</li> </ul> |

| subband5gver                                         | 0x4                                                   | Defines 5-GHz sub-band allocation                                                                                                                                                                                     |

| tempthresh                                           | 255                                                   | Infineon internal use only                                                                                                                                                                                            |

| tempoffset                                           | 255                                                   | Infineon internal use only                                                                                                                                                                                            |

| rawtempsense                                         | 0x1ff                                                 | Infineon internal use only <i>Note: Do not modify.</i>                                                                                                                                                                |

| phycal_tempdelta                                     | 15                                                    | Infineon internal use only                                                                                                                                                                                            |

| temps_period                                         | 15                                                    | Infineon internal use only                                                                                                                                                                                            |

| temps_hysteresis                                     | 15                                                    | Infineon internal use only                                                                                                                                                                                            |

| AvVmid_c0, AvVmid_c1                                 | 2, 140, 2, 145, 2,<br>145, 2, 145, 2,<br>145          | Infineon internal use only <i>Note: Do not modify.</i>                                                                                                                                                                |

| swctrlmap_2g,<br>swctrlmap_5g,<br>swctrlmapext_2g/5g | 0x02020202,<br>0x05050404,<br>0x04040000,<br>0x000000 | Describes how to control the external 2.4-GHz and 5-GHz<br>FEM (front-end module) or TR-SW.                                                                                                                           |

Review the design variables listed in **Table 2** prior to beginning board or module testing. During the development phase, start with the default power amplifier (PA) parameters contained in the provided *nvram.txt* file. The PA parameters are eventually optimized using Infineon transmit signal strength indicator (TSSI) calibration tools.

The parameters in **Table 2** typically require tuning for each specific-board or module design. This is not an exhaustive list. Additional parameters may be added by Infineon at any time to control the RF performance-related attributes of the driver. Always check with Infineon for the latest version of the *nvram.txt* file for the reference design before starting for any board customization efforts.

#### Customizing the nvram.txt file

Note:

To avoid unexpected operating results, contact a technical support representative before attempting to add NVRAM parameters.

| NVRAM parameter                                 | Example data | Description                                                                                                                                                                                                                                                              |

|-------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 |              | Board revision used by the WLAN driver.                                                                                                                                                                                                                                  |

|                                                 |              | Examples:                                                                                                                                                                                                                                                                |

| boardrev                                        | 0x1102       | 0x1102 converts to P102                                                                                                                                                                                                                                                  |

|                                                 |              | 0x1210 converts to P210                                                                                                                                                                                                                                                  |

|                                                 |              | Country code for regulatory. Specifies which regulatory tables are to be loaded.                                                                                                                                                                                         |

| Ccode                                           | 0            | Note: Together, the ccode and regrev parameters<br>set the power and other limitations necessary<br>to meet the country-specific regulatory<br>requirements.                                                                                                             |

| Regrev                                          | 0            | The regulatory revision code for regulatory use, and<br>specifies which regulatory tables are to be loaded.<br>Note: Together, the ccode and regrev parameters set the<br>power and other limitations necessary to meet the<br>country-specific regulatory requirements. |

| rxgains2gtrelnabypa0,<br>rxgains2gtrelnabypa1   | 1            | This variable defines the isolation that 5 GHz eLNA<br>provides when put in bypass mode.<br>'a0' and 'a1' apply for Core 0 and Core 1, respectively, and<br>to low sub-band.                                                                                             |

| rxgains5gmtrelnabypa0,<br>rxgains5gmtrelnabypa1 | 1            | This variable defines the isolation that 5 GHz eLNA<br>provides when put in bypass mode.<br>'a0' and 'a1' apply for Core 0 and Core 1, respectively, and<br>to mid sub-band.                                                                                             |

| rxgains5ghtrelnabypa0,<br>rxgains5ghtrelnabypa1 | 1            | This variable defines the isolation that 5 GHz eLNA<br>provides when put in bypass mode.<br>'a0' and 'a1' apply for Core 0 and Core 1, respectively, and<br>to high/X1 sub-band.                                                                                         |

| rxgains2gelnagaina0,<br>rxgains2gelnagaina1     | 1            | This variable defines the 2.4-GHz eLNA gain in dB.<br>'a0' and 'a1' apply to Core 0 and Core 1, respectively.                                                                                                                                                            |

| rxgains2gtrisoa0,<br>rxgains2gtrisoa1           | 7            | This variable defines the 2.4-GHz isolation that TR switch provides when in "T" mode.<br>'a0' and 'a1' apply to Core 0 and Core 1, respectively.                                                                                                                         |

| rxgains5gelnagaina0,<br>rxgains5gelnagaina1     | 3            | This variable defines the 5-GHz eLNA gain in dB.<br>'a0' and 'a1' apply to Core 0 and Core 1, respectively.<br>Applies to low sub-band.                                                                                                                                  |

| rxgains5gtrisoa0,<br>rxgains5gtrisoa1           | 6            | This variable defines the 5-GHz isolation that TR switch<br>provides when in "T" mode.<br>'a0' and 'a1' apply to Core 0 and Core 1, respectively.                                                                                                                        |

#### Table 2 NVRAM parameters that require customization

# OTP memory programming and NVRAM development - AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip

| NVRAM parameter                         | Example data           | Description                                                                                                                                                                   |

|-----------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |                        | Applies to low sub-band.                                                                                                                                                      |

| ······                                  |                        | This variable defines the 5-GHz eLNA gain in dB.                                                                                                                              |

| rxgains5gmelnagaina0,                   | 3                      | 'a0' and 'a1' apply to Core 0 and Core 1, respectively.                                                                                                                       |

| rxgains5gmelnagaina1                    |                        | Applies to mid sub-band.                                                                                                                                                      |

| rxgains5gmtrisoa0,<br>rxgains5gmtrisoa1 | 6                      | This variable defines the 5-GHz isolation that TR switch<br>provides when in "T" mode. 'a0' and 'a1' apply to Core 0<br>and Core 1, respectively.<br>Applies to mid sub-band. |

|                                         |                        | This variable defines the 5-GHz eLNA gain in dB.                                                                                                                              |

| rxgains5ghelnagaina0,                   | 3                      | 'a0' and 'a1' apply to Core 0 and Core 1, respectively.                                                                                                                       |

| rxgains5ghelnagaina1                    |                        | Applies to high/X1 sub-band.                                                                                                                                                  |

| rxgains5ghtrisoa0,                      | C                      | This variable defines the 5-GHz isolation that TR switch provides when in "T" mode.                                                                                           |

| rxgains5ghtrisoa1                       | 6                      | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                                                                                      |

|                                         |                        | Applies to high/X1 sub-band.                                                                                                                                                  |

|                                         |                        | Antenna gain (in dBi) defined by converting hexadecimal to<br>8-bit binary: (agba0: 2.4-GHz antenna gain, aga0: 5-GHz<br>antenna gain)                                        |

|                                         |                        | • Lower 0–5 bits = signed 2s complement in units of dB.                                                                                                                       |

| agbg0, aga0, agbg1, aga1                | 0x7f                   | <ul> <li>Higher 6–7 bits = unsigned number in units of quarter<br/>dB.</li> </ul>                                                                                             |

|                                         |                        | Suffices '0' and '1' apply for Core 0 and Core 1,                                                                                                                             |

|                                         |                        | respectively.                                                                                                                                                                 |

|                                         |                        | Examples:                                                                                                                                                                     |

|                                         |                        | $0x82 = 2.5 \text{ dB} (2 + 2 \times 0.25)$                                                                                                                                   |

|                                         |                        | $0x7f = -0.75 \text{ dB} (-1 + 1 \times 0.25)$                                                                                                                                |

|                                         |                        | PA parameters for the 2.4-GHz band based on TSSI                                                                                                                              |

| pa2ga0, pa2ga1,                         | -148, 5828, -679       | calibration.                                                                                                                                                                  |

| pa2gccka0, pa2gccka1                    |                        | pa2ga0/a1 – OFDM / pa2gccka0/a1- CCK.                                                                                                                                         |

|                                         |                        | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                                                                                      |

|                                         |                        | PA parameters for the 5-GHz band based on TSSI calibration                                                                                                                    |

|                                         | 83, 6045, -553,<br>57, | (Low / Mid / High / X1). Sub-band frequency range.<br>Channel Range:                                                                                                          |

| pa5ga0, pa5ga1                          | 5940, -566, 12,        | <ul> <li>Low 5180 to 5240 36-48</li> </ul>                                                                                                                                    |

| μασβάν, μασβάτ                          | 5919, -605, -17,       | <ul> <li>Mid 5260 to 5320 52-64</li> </ul>                                                                                                                                    |

|                                         | 5899, -640             | <ul> <li>High 5500 to 5700 100-140, X1 5745 to 5825 149-165<br/>(pa5ga0/a1)</li> </ul>                                                                                        |

|                                         |                        | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                                                                                      |

|                                         | -152, 8169, -994,      | Core 0 PA parameters for 5G (Low / Mid / High / X1).                                                                                                                          |

|                                         | -150, 8190, -999,      | (subband5gver=4), for 40 MHz/80 MHz BW                                                                                                                                        |

| pa5gbw4080a0                            | -138, 8514, -          | Sub-band frequency range.                                                                                                                                                     |

|                                         | 1034,                  | Channel Range:                                                                                                                                                                |

# OTP memory programming and NVRAM development - AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip

| NVRAM parameter            | Example data      | Description                                                                                             |

|----------------------------|-------------------|---------------------------------------------------------------------------------------------------------|

|                            | -130, 8806, -1058 | • Low 5180 to 5240 36-48                                                                                |

|                            |                   | • Mid 5260 to 5320 52-64                                                                                |

|                            |                   | • High 5500 to 5700 100-140                                                                             |

|                            |                   | X1 5745 to 5825 149-165.                                                                                |

|                            |                   | Core 1 PA parameters for 5G (Low / Mid / High / X1).                                                    |

|                            |                   | (subband5gver=4), for 40 MHz/80 MHz BW                                                                  |

|                            | -169, 7695, -945, | Sub-band frequency range.                                                                               |

|                            | -156, 8053, -980, | Channel Range:                                                                                          |

| pa5gbw4080a1               | -160, 8075, -984, | • Low 5180 to 5240 36-48                                                                                |

|                            | -158, 8219, -997  | • Mid 5260 to 5320 52-64                                                                                |

|                            |                   | • High 5500 to 5700 100-1-40                                                                            |

|                            |                   | X1 5745 to 5825 149-165.                                                                                |

|                            |                   | 5 GHz, 40 MHz BW PD offset (1/4 dB steps) in 2's                                                        |

| pdoffset40ma0,             | 0x0000            | complement format 4 bits for each sub-band.                                                             |

| pdoffset40ma1              |                   | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                |

| pdoffset80ma0,             |                   | 5 GHz, 80 MHz BW PD offset (1/4 dB steps) in 2's                                                        |

| pdoffset80ma1              | 0x0000            | complement format 4 bits for each sub-band.                                                             |

| puolisetoolilai            |                   | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                |

|                            |                   | Maximum output power for the 2.4 GHz band in                                                            |

|                            | 0x46              | hexadecimal format. Units of 0.25 dB. This applies to all                                               |

|                            |                   | complementary code keying (CCK) rates as measured at                                                    |

|                            |                   | antenna port. The nominal target power in dBm for CCK packets is (0.25 × maxp2ga0 in decimal) – 1.5 dB. |

| ກວນກິສວ0, ກວນກິສວ <b>1</b> |                   | The value can be entered in either hexadecimal or decimal                                               |

| maxp2ga0, maxp2ga1         | 0840              | formats.                                                                                                |

|                            |                   | In the example shown for 0 x 46, the maximum output                                                     |

|                            |                   | power is $(16 \times 4 + 6)/4 = 17.5$ dBm, and the nominal power                                        |

|                            |                   | is 17.5 – 1.5 = 16.0 dBm.                                                                               |

|                            |                   | 'a0' and 'a1' apply for Core 0 and Core 1, respectively.                                                |

| cckbw202gpo                | 0x0000            | CCK power offsets for 20 MHz rates (11, 5.5, 2, 1 Mbps)                                                 |

| cckbw20ul2gpo              | 0x0000            | CCK power offsets for 20 U/L rates (11, 5.5, 2, 1 Mbps)                                                 |

|                            |                   | Core 0 2g CCK PD offset (1/4 dB steps) in 2's complement                                                |

| cckpwroffset0              | 0x4               | format - For example, if 1dB reduction is required then the                                             |

| cckpwionseto               | 0,4               | value is 0x4, but if 1dB higher offset is required then it is                                           |

|                            |                   | 0xc.                                                                                                    |

|                            |                   | Core 1 2g CCK PD offset (1/4 dB steps) in 2's complement                                                |

| cckpwroffset1              | 0x4               | format – For example, if 1dB reduction is required then the                                             |

| cenpwronset                |                   | value is 0x4, but if 1dB higher offset is required then it is                                           |

|                            |                   | 0xc.                                                                                                    |

| dot11agofdmhrbw202gpo      | 0x6666            | OFDM power offset. Specified in half dBm units – 54, 48, 36,                                            |

|                            |                   | and 24 Mbps.                                                                                            |

| ofdmlrbw202gpo             | 0x0033            | OFDM 2.4 GHz power offset. Specified in half dBm units:                                                 |

| οιαιπιτοννΖυΖεμυ           |                   | MCS1 and MCS2: 11n and 11ac 40 MHz BW                                                                   |

| NVRAM parameter    | Example data                 | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                              | MCS1 and MCS2: 11n and 11ac 20 MHz BW                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |                              | • 12 and 18 Mbps: 11g                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |                              | • 6 and 9 Mbps: 11g                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                              | 11n/ac MCS0/1/2, 3-7, C8, C9 2.4 MHz power offset.<br>Specified                                                                                                                                                                                                                                                                                                                                                         |

| mcsbw202gpo        | 0xAA886664                   | in half dBm units – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                          |

| 1163511202600      |                              | (If separate control of MCS1 and MCS2 is required, then use                                                                                                                                                                                                                                                                                                                                                             |

|                    |                              | ofdmlrbw202gpo).                                                                                                                                                                                                                                                                                                                                                                                                        |

| maxp5ga0, maxp5ga1 | 0x4A, 0x4A,<br>0x4A,<br>0x4A | Maximum output power for the 5 GHz band in hexadecimal<br>format. Units of 0.25 dB. This applies to all legacy<br>orthogonal frequency division multiplexing (OFDM) rates<br>as measured at antenna port. The nominal target power in<br>dBm is (0.25 × maxp5ga0 in decimal) – 1.5 dB. The value<br>can be entered in either hexadecimal or decimal format.<br>'a0' and 'a1' apply for Core 0 and Core 1, respectively. |

|                    |                              | 5 GHz band low sub-band 12/18 & M1/M2:                                                                                                                                                                                                                                                                                                                                                                                  |

|                    |                              | <ul> <li>(0) 20 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| mcslr5glpo         | 0x0000                       | • (1) 40 MHz                                                                                                                                                                                                                                                                                                                                                                                                            |

| incsitogipo        | 0x0000                       | • (2) 80 MHz                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                              | • (3) 160 MHz                                                                                                                                                                                                                                                                                                                                                                                                           |

| mcsbw205glpo       | 0xAA886662                   | 5 GHz low band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset                                                                                                                                                                                                                                                                                                                                                               |

|                    | 0744000002                   | for 20 MHz BW – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                              |

| mcsbw405glpo       | 0xAA886664                   | 5 GHz low band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset                                                                                                                                                                                                                                                                                                                                                               |

|                    |                              | for 40 MHz BW – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                              |

| mcsbw805glpo       | 0xAA886664                   | 5 GHz low band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset                                                                                                                                                                                                                                                                                                                                                               |

|                    |                              | for 80 MHz BW – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                              |

|                    |                              | 5 GHz band mid sub-band 11ag/11n/11ac QPSK power<br>offset with respect to BPSK - mcs 1/2 with respect to mcs 0/<br>1/2 and 12/18 Mbps with respect to 6/9 Mbps. LSB to MSB<br>nibble:                                                                                                                                                                                                                                  |

| mcslr5gmpo         | 0x0000                       | • (0) 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                              | • (1) 40 MHz                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                              | • (2) 80 MHz                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                              | • (3) 160 MHz                                                                                                                                                                                                                                                                                                                                                                                                           |

| mcsbw20Eampa       | 0xAA886664                   | 5 GHz mid band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset                                                                                                                                                                                                                                                                                                                                                               |

| mcsbw205gmpo       | 0XAA886664                   | for 20 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                                 |

| mcsbw405gmpo       | 0xAA886664                   | 5 GHz mid band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset<br>for 40 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                    |

|                    | 0                            | 5 GHz mid band 11n/ac MCS0/ 1/2, 3-7, C8, C9 power offset                                                                                                                                                                                                                                                                                                                                                               |

| mcsbw805gmpo       | 0xAA886664                   | for 80 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2.                                                                                                                                                                                                                                                                                                                                                                                 |

| mcslr5ghpo         | 0x0000                       | 5 GHz band high/X1 sub-band 11ag/11n/11ac QPSK power                                                                                                                                                                                                                                                                                                                                                                    |

| NVRAM parameter                  | Example data | Description                                                                                                                                                                 |

|----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |              | offset with respect to BPSK - mcs 1/2 with respect to mcs 0/1/2 and 12/18 Mbps with respect to 6/9 Mbps. LSB to MSB nibble:                                                 |

|                                  |              | • (0) 20 MHz                                                                                                                                                                |

|                                  |              | • (1) 40 MHz                                                                                                                                                                |

|                                  |              | • (2) 80 MHz                                                                                                                                                                |

|                                  |              | • (3) 160 MHz                                                                                                                                                               |

| mcsbw205ghpo                     | 0xAA886664   | 5 GHz high/X1 band 11n/ac MCS0/1/2,3-7, C8, C9 power offset for 20 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2                                                                          |

| mcsbw405ghpo                     | 0xAA886664   | 5 GHz high/X1 band 11n/ac MCS0/1/2,3-7, C8, C9 power<br>offset for 40 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2                                                                       |

| mcsbw805ghpo                     | 0xAA886664   | 5 GHz high/X1 band 11n/ac MCS0/1/2,3-7, C8, C9 power offset for 80 MHz – C9/C8/M7/M6/M5/M4/M3/M0-2                                                                          |

|                                  |              | 20in40 OFDM signed power offsets with respect to 20in20 for 64 QAM and above. LSB nibble to MSB nibble:                                                                     |

|                                  |              | • (0) 2.4 GHz band                                                                                                                                                          |

| sb20in40hrpo                     | 0            | • (1) 5 GHz low sub-band                                                                                                                                                    |

|                                  |              | • (2) 5 GHz mid sub-band                                                                                                                                                    |

|                                  |              | • (3) 5 GHz high/X1 sub-band                                                                                                                                                |

|                                  |              | <ul> <li>20in40 OFDM signed power offsets with respect to 20in20 for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 2.4 GHz band</li> </ul>                       |

| sb20in80and160hr5glpo            | 0            | <ul> <li>(1) 5 GHz low sub-band</li> </ul>                                                                                                                                  |

|                                  |              | <ul> <li>(2) 5 GHz mid sub-band</li> </ul>                                                                                                                                  |

|                                  |              | <ul> <li>(3) 5 GHz high/X1 sub-band</li> </ul>                                                                                                                              |

|                                  |              | <ul> <li>5 GHz low sub-band 20in80, 20in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 20in80 with respect to 20in20</li> </ul> |

| ab 20: n 00 and 1 C 0 by E al na |              | <ul> <li>(0) 20in160 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> </ul>                                                                          |

| sb20in80and160hr5glpo            | 0            | <ul> <li>(1) 201100 with respect to 201120</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> </ul>                                                                 |

|                                  |              | <ul> <li>(2) 201100 - 20LL/00 with respect to 20L0/0L</li> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160 sub-bands</li> </ul>                                   |

|                                  |              | 5 GHz low sub-band 40in80, 40in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:                                                                |

|                                  |              | • (0) 40in80 with respect to 40in40                                                                                                                                         |

| sb40and80hr5glpo                 | 0            | • (1) 40in160 with respect to 40in40                                                                                                                                        |

|                                  |              | • (2) 80in160 with respect to 80in80                                                                                                                                        |

|                                  |              | • (3) 40in160 -40LL/UU with respect to 40LU/UL                                                                                                                              |

| sb20in80and160hr5gmpo            | 0            | 5 GHz mid sub-band 20in80, 20in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:                                                                |

| σστοιπουαπατουπισεμιμο           | U            | • (0) 20in80 with respect to 20in20                                                                                                                                         |

|                                  |              | • (1) 20in160 with respect to 20in20                                                                                                                                        |

| NVRAM parameter       | Example data | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |              | • (2) 20in80 - 20LL/UU with respect to 20LU/UL                                                                                                                                                                                                                                                                                                                         |

|                       |              | <ul> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160<br/>sub-bands</li> </ul>                                                                                                                                                                                                                                                                                |

| sb40and80hr5gmpo      | 0            | <ul> <li>5 GHz mid sub-band 40in80, 40in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 40in80 with respect to 40in40</li> <li>(1) 40in160 with respect to 40in40</li> <li>(2) 80in160 with respect to 80in80</li> <li>(3) 40in160 -40LL/UU with respect to 40LU/UL</li> </ul>                                              |

| sb20in80and160hr5ghpo | 0            | <ul> <li>5 GHz high/X1 sub-band 20in80, 20in160 OFDM signed<br/>power offsets for 64 QAM and above. LSB nibble to MSB<br/>nibble:</li> <li>(0) 20in80 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160<br/>sub-bands</li> </ul> |

| sb40and80hr5ghpo      | 0            | <ul> <li>5 GHz high/X1 sub-band 40in80, 40in160 OFDM signed<br/>power offsets for 64 QAM and above. LSB nibble to MSB<br/>nibble:</li> <li>(0) 40in80 with respect to 40in40</li> <li>(1) 40in160 with respect to 40in40</li> <li>(2) 80in160 with respect to 80in80</li> <li>(3) 40in160 -40LL/UU with respect to 40LU/UL</li> </ul>                                  |

| sb20in40lrpo          | 0            | <ul> <li>20in40 OFDM signed power offsets with respect to 20in20 for 16 QAM and below. LSB nibble to MSB nibble:</li> <li>(0) 2.4 GHz band</li> <li>(1) 5 GHz low sub-band</li> <li>(2) 5 GHz mid sub-band</li> <li>(3) 5 GHz high/X1 sub-band</li> </ul>                                                                                                              |

| sb20in80and160lr5glpo | 0            | <ul> <li>5 GHz low sub-band 20in80, 20in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:</li> <li>(0) 20in80 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160 sub-bands</li> </ul>                 |

| sb40and80lr5glpo      | 0            | <ul> <li>5 GHz mid sub-band 20in80, 20in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 20in80 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> </ul>                                                                                          |

# OTP memory programming and NVRAM development - AIROC<sup>™</sup> CYW5459x Wi-Fi & Bluetooth<sup>®</sup> combo chip

| NVRAM parameter       | Example data | Description                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       |              | <ul> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160<br/>sub-bands</li> </ul>                                                                                                                                                                                                                                                                    |  |

| sb40and80hr5gmpo      | 0            | <ul> <li>5 GHz mid sub-band 40in80, 40in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 40in80 with respect to 40in40</li> <li>(1) 40in160 with respect to 40in40</li> <li>(2) 80in160 with respect to 80in80</li> <li>(3) 40in160 -40LL/UU with respect to 40LU/UL</li> </ul>                                  |  |

| sb20in80and160hr5ghpo | 0            | <ul> <li>5 GHz high/X1 sub-band 20in80, 20in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 20in80 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160 sub-bands</li> </ul> |  |

| sb40and80hr5ghpo      | 0            | <ul> <li>5 GHz high/X1 sub-band 40in80, 40in160 OFDM signed power offsets for 64 QAM and above. LSB nibble to MSB nibble:</li> <li>(0) 40in80 with respect to 40in40</li> <li>(1) 40in160 with respect to 40in40</li> <li>(2) 80in160 with respect to 80in80</li> <li>(3) 40in160 -40LL/UU with respect to 40LU/UL</li> </ul>                              |  |

| sb20in40lrpo          | 0            | <ul> <li>20in40 OFDM signed power offsets with respect to 20in20 for 16 QAM and below. LSB nibble to MSB nibble:</li> <li>(0) 2.4 GHz band</li> <li>(1) 5 GHz low sub-band</li> <li>(2) 5 GHz mid sub-band</li> <li>(3) 5 GHz high/X1 sub-band</li> </ul>                                                                                                  |  |

| sb20in80and160lr5glpo | 0            | <ul> <li>5 GHz low sub-band 20in80, 20in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:</li> <li>(0) 20in80 with respect to 20in20</li> <li>(1) 20in160 with respect to 20in20</li> <li>(2) 20in80 - 20LL/UU with respect to 20LU/UL</li> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160 sub-bands</li> </ul>     |  |

| sb40and80lr5glpo      | 0            | <ul> <li>5 GHz low sub-band 40in80, 40in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:</li> <li>(0) 40in80 with respect to 40in40</li> <li>(1) 40in160 with respect to 40in40</li> <li>(2) 80in160 with respect to 80in80</li> <li>(3) 40in160 -40LL/UU with respect to 40LU/UL</li> </ul>                                  |  |

| NVRAM parameter Example data |   | Description                                                                                                                                                                                                                                                                             |  |

|------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              |   | 5 GHz mid sub-band 20in80, 20in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:                                                                                                                                                                            |  |

|                              |   | • (0) 20in80 with respect to 20in20                                                                                                                                                                                                                                                     |  |

| sb20in80and160lr5gmpo        | 0 | • (1) 20in160 with respect to 20in20                                                                                                                                                                                                                                                    |  |

|                              |   | • (2) 20in80 - 20LL/UU with respect to 20LU/UL                                                                                                                                                                                                                                          |  |

|                              |   | <ul> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160<br/>sub-bands</li> </ul>                                                                                                                                                                                                 |  |

|                              |   | 5 GHz mid sub-band 40in80, 40in160 OFDM signed power                                                                                                                                                                                                                                    |  |

|                              |   | offsets for 16 QAM and below. LSB nibble to MSB nibble:                                                                                                                                                                                                                                 |  |

|                              |   | • (0) 40in80 with respect to 40in40                                                                                                                                                                                                                                                     |  |

| sb40and80lr5gmpo             | 0 | • (1) 40in160 with respect to 40in40                                                                                                                                                                                                                                                    |  |

|                              |   | • (2) 80in160 with respect to 80in80                                                                                                                                                                                                                                                    |  |

|                              |   | • (3) 40in160 -40LL/UU with respect to 40LU/UL                                                                                                                                                                                                                                          |  |

|                              |   | 5 GHz high/X1 sub-band 20in80, 20in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:                                                                                                                                                                        |  |

|                              |   | • (0) 20in80 with respect to 20in20                                                                                                                                                                                                                                                     |  |

| sb20in80and160lr5ghpo        | 0 | • (1) 20in160 with respect to 20in20                                                                                                                                                                                                                                                    |  |

|                              |   | • (2) 20in80 - 20LL/UU with respect to 20LU/UL                                                                                                                                                                                                                                          |  |

|                              |   | <ul> <li>(3) 20in160 - 20LLL/UUU with respect to other 20in160<br/>sub-bands</li> </ul>                                                                                                                                                                                                 |  |

|                              |   | 5 GHz high/X1 sub-band 40in80, 40in160 OFDM signed power offsets for 16 QAM and below. LSB nibble to MSB nibble:                                                                                                                                                                        |  |

| sb40and80lr5ghpo             | 0 | • (0) 40in80 with respect to 40in40                                                                                                                                                                                                                                                     |  |

| on roundoorrogripo           | 0 | • (1) 40in160 with respect to 40in40                                                                                                                                                                                                                                                    |  |

|                              |   | • (2) 80in160 with respect to 80in80                                                                                                                                                                                                                                                    |  |

|                              |   | • (3) 40in160 - 40LL/UU with respect to 40LU/UL                                                                                                                                                                                                                                         |  |

| dot11agduphrpo               | 0 | 11a/g duplicate mode signed power offsets for 64 QAM.<br>Common power offset for Dup40, Dup40in80, and<br>Dup40in160 with respect to 40in40 11n/11ac, Quad80 and<br>Quad80in160 with respect to 11ac 80in80, Oct160 with<br>respect to 11ac 160in160. LSB to MSB nibble:                |  |

| astrra Parkinko              | ľ | • (0) 2.4 GHz band                                                                                                                                                                                                                                                                      |  |

|                              |   | • (1) 5 GHz low sub-band                                                                                                                                                                                                                                                                |  |

|                              |   | • (2) 5 GHz mid sub-band                                                                                                                                                                                                                                                                |  |

|                              |   | • (3) 5 GHz high/X1 sub-band                                                                                                                                                                                                                                                            |  |

| dot11agduplrpo               | 0 | Bits 11a/g duplicate mode signed power offsets for 16 QAM<br>and below. Common power offset for Dup40, Dup40in80,<br>and Dup40in160 with respect to 40in40 11n/11ac, Quad80<br>and Quad80in160 with respect to 11ac 80in80, Oct160 with<br>respect to 11ac 160in160. LSB to MSB nibble: |  |

#### Customizing the nvram.txt file

| NVRAM parameter   | Example data              | Description                                                            |

|-------------------|---------------------------|------------------------------------------------------------------------|

|                   |                           | • (0) 2.4 GHz band                                                     |

|                   |                           | • (1) 5 GHz low sub-band                                               |

|                   |                           | • (2) 5 GHz mid sub-band                                               |

|                   |                           | • (3) 5 GHz high/X1 sub-band                                           |