# Failure analysis process in TRAVEO™ T2G devices

# About this document

#### Scope and purpose

This application note describes the failure analysis flow in TRAVEO<sup>™</sup> T2G automotive microcontroller devices. It provides a comprehensive description of how the customer should handle a failing sample and how the device must be prepared to allow the regular failure analysis procedure at Infineon. It covers also the 'No Trouble Found' (NTF) process after all standard tests have passed.

#### **Intended audience**

This document is intended for anyone who uses the TRAVEO<sup>™</sup> T2G microcontrollers to configure a secured system and to prepare and apply to a failure analysis process for any kind of claim.

#### Associated part family

TRAVEO<sup>™</sup> T2G family

# Table of contents

# **Table of contents**

| 2.3.2Reporting schedules73General information of TRAVEO <sup>TM</sup> T2G security concept113.1Lifecycle stages.113.1.1"NORMAL_PROVISIONED"123.1.2"SECURE"123.1.3"SECURE"123.1.4"RMA"123.1.5CORRUPTED133.2Authentication133.3Access restrictions143.3.1Debug access port (DAP) configuration143.3.2Access restrictions to internal components153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2.2Step 3: definition of the certificate and signature224.2.1Step 3: definition of system call data in related locations in the SRAM244.3Required hardware274.4Rest sources275Restrictions on performing the standard FA flow286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done31                                                                                                                                                                                                                 | Abou  | t this document                                                   | . 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------|-----|

| 2       Overview of the standard FA flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table | of contents                                                       | . 2 |

| 2.1       Minimum information to be provided to Infineon       6         2.2       Procedure at Infineon       6         2.3       Reporting       7         2.3.1       Reporting schedules       7         3.2       Reporting schedules       7         3.3       Reporting schedules       7         3.4       Reporting schedules       7         3.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE"       12         3.1.3       "SECURE"       12         3.1.4       "RMA"       12         3.1.5       CORUPTED       13         3.2       Authentication       13         3.3       Access restrictions to internal components       15         3.3.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.2       Access to debug interface (DAP)       17         3.4       Lifecycle stage transition to "RMA"       18         3.5       Authenticated debugger techniques       20         4       Reuse a sample in the NTF process       21         4.1       Flash programming and application execution in the "RM                                                                                                   | 1     | Introduction                                                      | . 4 |

| 2.2       Procedure at Infineon       6         2.3       Reporting       7         2.3.1       Reporting schedules       7         7       2.3.2       Reporting schedules       7         3       General information of TRAVEO"* T2G security concept       11         3.1.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE"       12         3.1.3       "SECURE"       12         3.1.4       "RMA"       12         3.1.5       CORRUPTED       13         3.2       Authentication       13         3.4       ccess restrictions       14         3.3.1       Debug access port (DAP) configuration       14         3.3.1       Debug access rost iclash, efves, SRAM, and MMIO       16         3.3.2.1       Access restrictions to flash, efves, SRAM, and MMIO       16         3.3.2.2       Access restrictions to flash, efves, SRAM, and MMIO       16         3.3.2.1       Access restrictions to flash, efves, SRAM, and MMIO       16         3.3.2.2       Access restrictions to flash, efves, SRAM, and MMIO       16         3.3.2.1       Access restrictions to effash, efves, SRAM, and MMIO       16         3.4       Llécycle stage transition to "RMA" <th>2</th> <th>Overview of the standard FA flow</th> <th>. 5</th> | 2     | Overview of the standard FA flow                                  | . 5 |

| 2.3Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.1   | Minimum information to be provided to Infineon                    | 6   |

| 2.3.1       Reporting tool       7         2.3.2       Reporting schedules       7         3       General information of TRAVEO" T2G security concept       11         3.1       Lifecycle stages       11         3.1.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE"       12         3.1.3       "SECURE W_DEBUG"       12         3.1.4       "RMA"       12         3.1.5       CORRUPTED       13         3.2       Authentication       13         3.3       Access restrictions       14         3.1       Debug access port (DAP) configuration       14         3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.2.2       Access restrict                                                       | 2.2   | Procedure at Infineon                                             | 6   |

| 2.3.2Reporting schedules73General information of TRAVEO"* T2G security concept113.1Lifecycle stages113.1.1"NORMAL PROVISIONED"123.1.2"SECURE"123.1.3"SECURE W_DEBUG"123.14"RMA"123.15CORRUPTED133.2Authentication133.3Access restrictions143.4Secure CORPONENT143.2Authentication133.3Access restrictions to internal components153.3.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.3Step 3: execution of the certificate and signature234.2.4Verification of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA system call275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations285.1 <t< td=""><td>2.3</td><td>Reporting</td><td>7</td></t<>                                                                                                                      | 2.3   | Reporting                                                         | 7   |

| 3       General information of TRAVEO" T2G security concept       11         3.1       Lifecycle stages       11         3.1.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE"       12         3.1.3       "SECURE"       12         3.1.4       "RMA"       12         3.1.5       CORRUPTED       13         3.2       Authentication       13         3.3       Access restrictions       14         3.3.1       Debug access port (DAP) configuration       14         3.3.2       Access restrictions to internal components       15         3.3.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.3       System call drace (DAP)       17         3.4       Lifecycle stage transition to "RMA"       18         3.4       Lifecycle stage transition to "RMA"       18         3.5       Authenticated debugger techniques       20         4.1       Flash programming and application executi                                                       | 2.3.1 | Reporting tool                                                    | 7   |

| 3.1       Lifecycle stages.       11         3.1.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE.W_DEBUG"       12         3.1.3       "SECURE.W_DEBUG"       12         3.1.4       "RMA".       12         3.1.5       CORRUPTED.       13         3.2       Authentication.       14         3.3.1       Debug access port (DAP) configuration       14         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO.       16         3.3.2.2       Access restrictions to flash, eFuse, SRAM, and MMIO.       16         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO.       16         3.3.2.2       Access restrictions to "RMA".       18         3.4       Lifecycle stage transition to "RMA".       18         3.5       Authenticated debugger techniques.       20         4       Reuse a sample in the NTF process       21         4.1       Flash programming and application execution in the "RMA" lifecycl                                                                                                   | 2.3.2 | Reporting schedules                                               | 7   |

| 3.1.1       "NORMAL_PROVISIONED"       12         3.1.2       "SECURE"       12         3.1.3       "SECURE"       12         3.1.4       "RMA"       12         3.1.5       CORRUPTED       13         3.2       Authentication       13         3.3       Access restrictions       14         3.1.1       Debug access port (DAP) configuration       14         3.2.1       Access restrictions to internal components       15         3.3.2.1       Access restrictions to flash, eFuse, SRAM, and MMIO       16         3.3.2.2       Access to debug interface (DAP)       17         3.3.3       System call requirements       17         3.4       Lifecycle stage transition to "RMA"       18         3.5       Authenticated debugger techniques       20         4       Ruse a sample in the NTF process       21         4.1       Flash programming and application execution in the "RMA" lifecycle stage       21         4.2       OpenRMA procedure       22         4.2.1       Step 1: preparation of the certificate and signature       23         4.2.2       Step 3: execution of the OpenRMA script       26         4.2.4       Verification of a succesful OpenRMA script                                                                 | 3     | General information of TRAVEO <sup>™</sup> T2G security concept   | 11  |

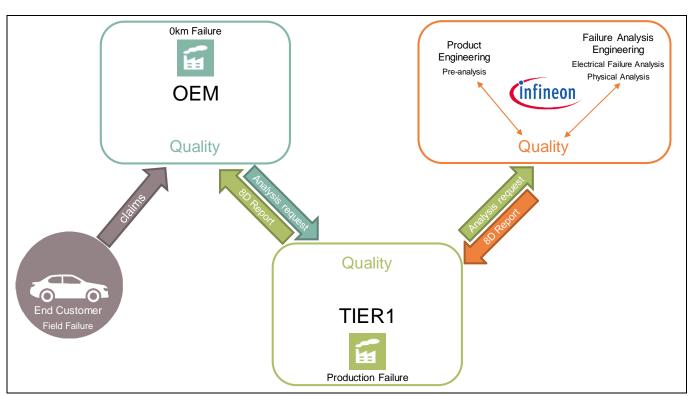

| 3.1.2"SECURE"123.1.3"SECURE_W_DEBUG".123.1.4"RMA".123.1.4"RMA".123.1.5CORRUPTED133.2Authentication133.3Access restrictions.143.1.1Debug access port (DAP) configuration143.2Access restrictions to internal components.153.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access to debug interface (DAP)173.3System call requirements.173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques.204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 3: execution of the OpenRMA script264.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.4Reset sources.275.1Matrix of possible security combinations.285.1Matrix of possible security comb                                                                                                                                                                                | 3.1   | Lifecycle stages                                                  | 11  |

| 3.1.3"SECURE_W_DEBUG".123.1.4"RMA"123.1.5CORRUPTED133.2Authentication133.3Access restrictions143.1.1Debug access port (DAP) configuration143.2Access restrictions to internal components.153.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.2.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access restrictions to RMA"173.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations285.1Matrix of possible security combinations285.1Matrix of possible security combinations285.1Matrix of possible security combinations337.2Debugger d                                                                                                                                            | 3.1.1 | "NORMAL_PROVISIONED"                                              | 12  |

| 3.1.4"RMA"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1.2 | "SECURE"                                                          | 12  |

| 3.1.5CORRUPTED133.2Authentication133.3Access restrictions143.3.1Debug access port (DAP) configuration143.3.2Access restrictions to internal components153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access to debug interface (DAP)173.3.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.2Step 1: preparation of the certificate and signature234.2.3Step 3: execution of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA337.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary338Glossary34                                                                                                                                                                                            | 3.1.3 | "SECURE_W_DEBUG"                                                  | 12  |

| 3.2Authentication133.3Access restrictions143.3.1Debug access port (DAP) configuration143.3.2Access restrictions to internal components153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access to debug interface (DAP)173.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process204.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.4Resit sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307.1Minimum requirements for a system call initiated by a debugger317.3Port pin detection method337.4Debug gcript for transition to "RMA"338Glossary348Glossary34                                                                                                                                                                                         | 3.1.4 |                                                                   |     |

| 3.3Access restrictions.143.3.1Debug access port (DAP) configuration143.3.2Access restrictions to internal components.153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO.163.3.2.2Access to debug interface (DAP)173.3.3System call requirements.173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques.204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage.214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.4Required hardware.275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations.286Preparations before sending a device for FA.337.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.4Debug script for transition to "RMA" lifecycle stage cannot be done337.4Debug script for transition to "RMA"338Glossary33348Glossary3334                                                                                                                                                                           | 3.1.5 | CORRUPTED                                                         | 13  |

| 3.3.1Debug access port (DAP) configuration143.3.2Access restrictions to internal components.153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO.163.3.2.2Access to debug interface (DAP)173.3System call requirements.173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques.204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware275Restrictions on performing the standard FA flow286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debug ger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary348References35                                                                                                                                                                         | 3.2   |                                                                   |     |

| 3.3.2Access restrictions to internal components.153.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access to debug interface (DAP)173.3.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware275Restrictions on performing the standard FA flow286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary348References35                                                                                                                                                                                                                       |       |                                                                   |     |

| 3.3.2.1Access restrictions to flash, eFuse, SRAM, and MMIO163.3.2.2Access to debug interface (DAP)173.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Becosary338Glossary348References35                                                                                                                                                                                                                                                          | 3.3.1 |                                                                   |     |

| 3.3.2.2Access to debug interface (DAP)173.3.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step 1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34                                                                                                                                                                                                                                                                                                     |       |                                                                   |     |

| 3.3.3System call requirements173.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary348References35                                                                                                                                                                                                                                                                                                                                                                 |       |                                                                   |     |

| 3.4Lifecycle stage transition to "RMA"183.5Authenticated debugger techniques204Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method337.3Port pin detection method337.4Bebug script for transition to "RMA"338Glossary348References35                                                                                                                                                                                                                                                                                                                                             |       |                                                                   |     |

| 3.5Authenticated debugger techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                                   |     |

| 4Reuse a sample in the NTF process214.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM.244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware.274.4Reset sources.275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations.286Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method337.3Port pin detection method337.4Restrictions to "RMA"338Glossary348References35                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                                   |     |

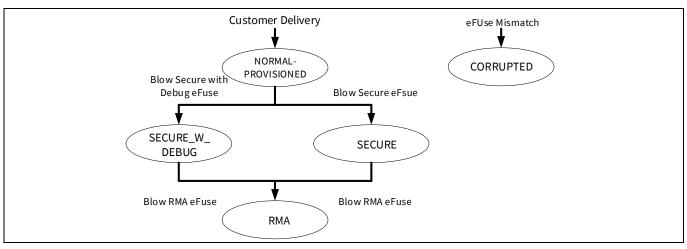

| 4.1Flash programming and application execution in the "RMA" lifecycle stage214.2OpenRMA procedure224.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.5   | Authenticated debugger techniques                                 | 20  |

| 4.2OpenRMA procedure224.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary338References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4     | • •                                                               |     |

| 4.2.1Step1: preparation of the certificate and signature234.2.2Step 2: definition of system call data in related locations in the SRAM244.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary348References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.1   |                                                                   |     |

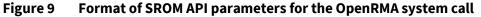

| 4.2.2Step 2: definition of system call data in related locations in the SRAM.244.2.3Step 3: execution of the OpenRMA script.264.2.4Verification of a successful OpenRMA system call.274.3Required hardware.274.4Reset sources.275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations.286Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method.337.4Debug script for transition to "RMA"348Glossary348References.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2   |                                                                   |     |

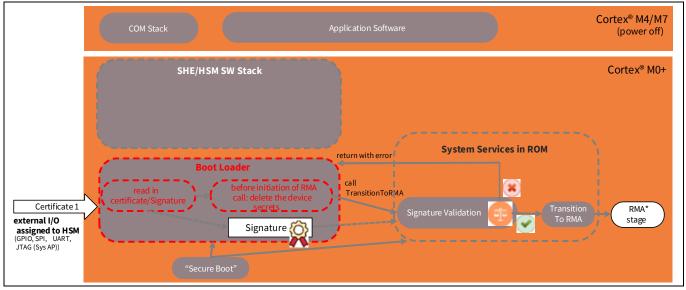

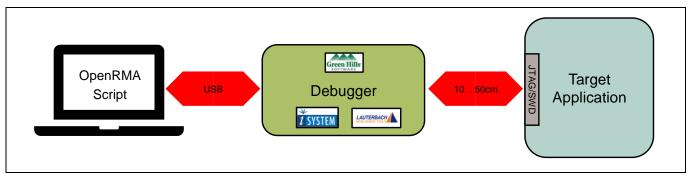

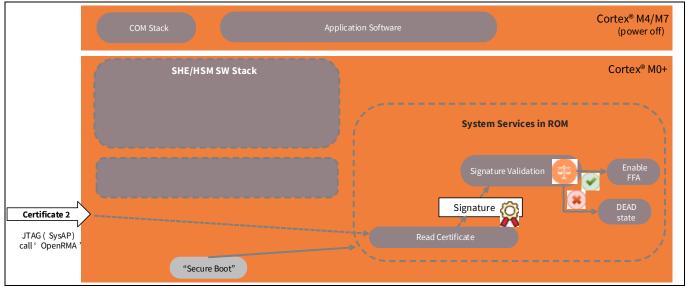

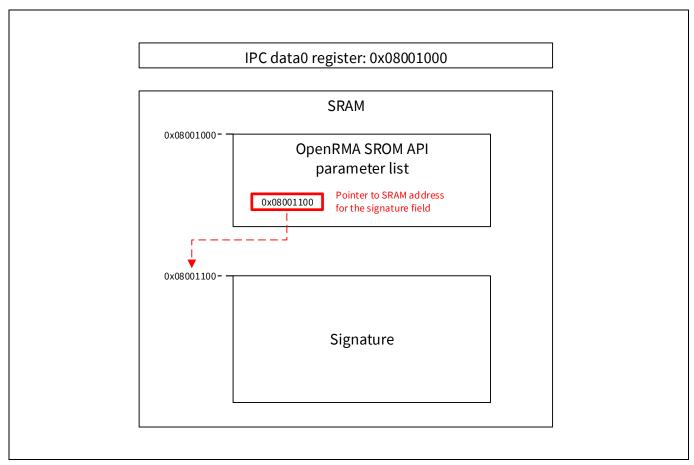

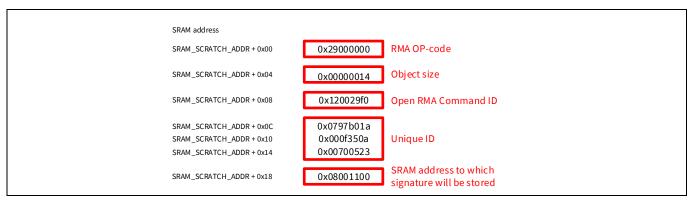

| 4.2.3Step 3: execution of the OpenRMA script264.2.4Verification of a successful OpenRMA system call274.3Required hardware275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"348Glossary34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                                   |     |

| 4.2.4Verification of a successful OpenRMA system call274.3Required hardware274.4Reset sources275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                                   |     |

| 4.3Required hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                                   |     |

| 4.4Reset sources.275Restrictions on performing the standard FA flow285.1Matrix of possible security combinations.286Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method.337.4Debug script for transition to "RMA"338Glossary.34References.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                   |     |

| 5Restrictions on performing the standard FA flow285.1Matrix of possible security combinations286Preparations before sending a device for FA307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger327.2Debugger detection method337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | •                                                                 |     |

| 5.1Matrix of possible security combinations.286Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.4   | Reset sources                                                     | 27  |

| 6Preparations before sending a device for FA.307Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary.34References.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5     | Restrictions on performing the standard FA flow                   | 28  |

| 7Procedure when transition to "RMA" lifecycle stage cannot be done317.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary.34References.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.1   | Matrix of possible security combinations                          | 28  |

| 7.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6     | Preparations before sending a device for FA                       | 30  |

| 7.1Minimum requirements for a system call initiated by a debugger.327.2Debugger detection method.337.3Port pin detection method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7     | Procedure when transition to "RMA" lifecycle stage cannot be done | 31  |

| 7.2Debugger detection method.337.3Port pin detection method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                   |     |

| 7.3Port pin detection method337.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7.2   |                                                                   |     |

| 7.4Debug script for transition to "RMA"338Glossary34References35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.3   |                                                                   |     |

| 8 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.4   |                                                                   |     |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8     |                                                                   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                                   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                                   |     |

# Table of contents

| evision history | 38 |

|-----------------|----|

| visclaimers     | 39 |

#### Introduction

# 1 Introduction

This application note describes how to properly handle devices which failed in the field at the end customer, during production at the OEM as a '0km failure', or during production at TIER1.

Infineon strives for getting a 0-ppm failure rate of its automotive products. To reach the highest standard of automotive quality, each failing device must be analyzed systematically with various analysis techniques to solve manufacturing defects, material imperfections, or design errors.

The ownership of all activities during the whole failure analysis (FA) procedure is associated with Infineon's quality division (QA) who is responsible for interacting with customers and internal departments such as Product Engineering, Failure Analysis Engineering, and Product Design. Each case is managed in the "My Cases" in the SFDC system where all interactions are collected and distributed to all collaborators attending to the case. During the whole process, Infineon provides regular intermediate reports which include the latest results of failure investigation, which in turn defines new steps along with respective schedules. A case will be closed with a final 8D-report after the root cause was identified and correction actions are defined. If all standard tests have passed, the claimed sample will be returned to the customer with the result as "No Trouble Found" (NTF).

TRAVEO<sup>™</sup> T2G devices include an efficient and reliable security mechanism which supports state-of-the-art safety and security standards for the automotive industry.

The protection state of a TRAVEO<sup>™</sup> T2G device is determined by irreversible burning of eFuses. Apart from different configuration parameters and hash values, nonvolatile lifecycle stages are also defined by eFuses. These describe a protection status in which the device is running. A transition from one lifecycle stage to the next is irreversible. The focus in this application note is on the transition to "RMA" lifecycle stage and what the customer must consider to allow the standard FA flow and how the sample can be reused during the NTF process.

This application note refers to AN228680 – Secure system configuration in TRAVEO<sup>™</sup> T2G family, which provides detailed information on handling of security and debugging. Review this document carefully to develop a secured system in your application which allows the device to be fully testable during the FA process.

Overview of the standard FA flow

2

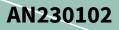

Figure 1 Standard FA flow for automotive microcontrollers

During the lifetime of a TRAVEO<sup>™</sup> T2G product, the device can fail in various stages, in the production facilities, or in the final product. Figure 1 shows the standard FA flow for how the customer can claim a defective device. Basically, the TIER1 customer is the direct client of Infineon, and there is no different process depending on where the device failed. For each analysis request, the device will follow a strict analysis procedure which ends with a final 8D-report which summarizes the analysis results; if a defect was found it will explain the root cause in detail. Table 1 summarizes the different failure stages along with the responsibilities to perform a proper FA flow.

| Case | Failure stage          | Description                                               | Actions                                                                        | Responsibility |

|------|------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|----------------|

| 1    | TIER1<br>production    | The TRAVEO™ T2G<br>device failed during<br>TIER1 EOL test | Perform a swap test to identify if the failure moves with the microcontroller. | TIER1          |

|      | plant                  |                                                           | Perform initial failure analysis                                               | TIER1          |

|      | (production            |                                                           | Create a failure report                                                        | TIER1          |

|      | failure)               |                                                           | Define a clear and comprehensive failure description                           | TIER1          |

|      |                        |                                                           | QA of TIER1 contacts regional quality                                          | TIER1 /        |

|      |                        |                                                           | partner at Infineon to hand over all                                           | Infineon       |

|      |                        |                                                           | required information (see section 2.1)                                         |                |

|      |                        |                                                           | Infineon creates a new FA case in                                              | Infineon       |

|      |                        |                                                           | salesforce.com                                                                 |                |

|      |                        |                                                           | TIER1 sends the sample to Infineon                                             | TIER1          |

|      |                        |                                                           | Steps followed are described in Failure<br>analysis procedure at Infineon      | Infineon       |

| 2    | OEM<br>production      | TIER1 application<br>including TRAVEO™                    | OEM identifies an issue on the TIER application unit                           | OEM            |

|      | plant (0km<br>failure) | T2G device failed<br>during OEM EOL test                  | Same procedure as in Case 1                                                    | -              |

| 3    | Final product          | TIER1 application                                         | End-consumer claims the product (e.g.,                                         | End-customer/  |

|      | T2G device             | ) including TRAVEO™<br>T2G device failed in               | vehicle) at the dealership                                                     | dealership     |

|      |                        | the final product in the                                  | Same procedure as in Case 2                                                    | -              |

#### Table 1 Life stages where a TRAVEO<sup>™</sup> T2G product can fail and how the FA flow is handled

# 2.1 Minimum information to be provided to Infineon

To ensure a fully qualified and fast support process, all needed information must be provided directly during the first contact with Infineon.

See Customer request handout for the complete list of required information. It can be used as a blueprint to hand in support requests.

# 2.2 Procedure at Infineon

All external examinations, electrical characterizations, and other non-destructive tests must be completed before device decapsulation or performing other destructive tests.

Expendable control samples should be used to test "risky" analysis procedures before attempting them on the devices under evaluation. They have must be used while verifying test setups and electrical failures.

| Responsible Tasks                 |                                                                                                                                                                                   |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quality assurance (QA)            | New claim                                                                                                                                                                         |

|                                   | Open new case in the MyCases system                                                                                                                                               |

|                                   | Provide the LOT history                                                                                                                                                           |

| Product engineering (PE)          | Pre-analysis                                                                                                                                                                      |

|                                   | Visual inspection                                                                                                                                                                 |

|                                   | Cleaning                                                                                                                                                                          |

|                                   | Pin alignment                                                                                                                                                                     |

|                                   | <ul> <li>Pre-analysis on an eval board (check lifecycle stage<sup>1</sup>, perform<br/>OpenRMA command<sup>2</sup>, perform standard RAM march and galloping<br/>test)</li> </ul> |

|                                   | Provide first intermediate report                                                                                                                                                 |

| Failure analysis engineering (FA) | Electrical failure analysis (EFA)                                                                                                                                                 |

|                                   | Standard outgoing test on ATE tester                                                                                                                                              |

|                                   | DC test                                                                                                                                                                           |

|                                   | Flash test                                                                                                                                                                        |

|                                   | Operation margin tests                                                                                                                                                            |

|                                   | Provide intermediate 8D report                                                                                                                                                    |

|                                   | Provide final 8D report                                                                                                                                                           |

| Failure analysis engineering      | Physical failure analysis (PFA)                                                                                                                                                   |

|                                   | Provide final 8D report                                                                                                                                                           |

#### Table 2 Failure analysis procedure at Infineon

# 2.3 Reporting

# 2.3.1 Reporting tool

For each claim, a dedicated FA case must be opened in the 'MyCases' system at Salesforce.com. It is the customer relationship management tool used to track customer returns and communicate with the customer. It includes the history of communication between the customer and Infineon and collaborators who are involved in the FA process. The ownership of each case is assigned to a customer related QA representative.

# 2.3.2 Reporting schedules

The case closure target is 35 days (case opened to case closed). The target analysis stage cycle time to achieve this target is shown in Table 3.

These targets are general guidelines to help manage the analysis cycle time. The exact time at each stage will vary depending on the complexity from case to case.

<sup>&</sup>lt;sup>1</sup> Customer should have ideally transitioned the device to "RMA" lifecycle stage before sending to Infineon. See section 3.4.

<sup>&</sup>lt;sup>2</sup> OpenRMA command must to be performed after the lifecycle stage has been transitioned to "RMA". See section 4.2.

Application note

# **Overview of the standard FA flow**

| Stage                         | Target cycle | Stage          | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | time (days)  | owner          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRIAGE/SHIPPING               | 3            | Regional<br>QA | This stage includes the initial contact with the customer,<br>understanding the customer issue, and the assignment of a<br>shipping address. Monitoring of the shipping time of the units<br>to Infineon is the responsibility of the customer quality<br>engineer (CQE).<br>If the return does not arrive or the customer does not provide<br>a shipment tracking number within five days, the case may be<br>put on pending status for four additional days. If no units or a<br>tracking number are received after nine days, the case may be<br>cancelled after notification to the customer.                                                                                                                                                                                                  |

| RECEIVING                     | 1            | FA             | This stage includes receiving the units at Infineon and the<br>initial non-destructive analysis such as visual inspection<br>(ensure the part(s) received match the MPN / part marking<br>provided in the SFDC case), X-ray, CSAM, and/or lead<br>conditioning. This stage is owned by the failure analysis<br>group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pre-analysis                  | 1            | PE             | Pre-analysis is done in case the MCU is not directly sent to<br>Infineon's backend to Failure analysis engineering to perform<br>EOL test. It includes some basic tests which are dependent on<br>debug access restriction settings. If possible, standard RAM<br>(March, Galloping) tests can be done. At the minimum, the<br>sample is checked whether the provided unlocking codes<br>(certificate along with the signature) can be used for the<br>OpenRMA command which is required to test the device on<br>the ATE. It will also check whether the device is in DEAD state.<br>Note that this stage might be skipped if the device is directly<br>sent to Infineon's Failure analysis engineering where the<br>device is tested against the test specification in a dedicated<br>test mode. |