# Multi core handling in TRAVEO<sup>™</sup> T2G family

# About this document

#### Scope and purpose

This application note provides useful information for multi-core (multi-CPU) handling in TRAVEO<sup>™</sup> T2G MCUs. A TRAVEO<sup>™</sup> T2G MCU can have up to three Arm<sup>®</sup> Cortex<sup>®</sup>-M CPUs. Multi-CPU architecture helps in improving system performance and efficiency. This document describes how to perform exclusive control, synchronization, and pass data between the different CPUs. In addition, the document provides an overview of cache coherency issues that occur between CPUs with cache and other masters, and suggests methods to avoid the issue in different scenarios.

#### Associated part family

TRAVEO<sup>™</sup> T2G family

#### **Intended** audience

This document is intended for anyone using TRAVEO<sup>™</sup> T2G family.

# **Table of contents**

|       | About this document                                                 |

|-------|---------------------------------------------------------------------|

|       | Table of contents    1                                              |

| 1     | Introduction                                                        |

| 2     | <b>Considerations for CPU startup</b>                               |

| 2.1   | Example of step-up CPU clock frequency 5                            |

| 2.1.1 | Configuration                                                       |

| 3     | Considerations for resource access                                  |

| 4     | <b>Consideration for write buffer in CPU and bus infrastructure</b> |

| 5     | Communicating between CPUs 11                                       |

| 5.1   | CPU synchronization                                                 |

| 5.1.1 | Implementation example operation of synchronization between CPUs    |

| 5.1.2 | Use case                                                            |

| 5.1.3 | Configuration                                                       |

| 5.2   | Mutual exclusion operation                                          |

| 5.2.1 | Implementation example of mutual exclusion                          |

| 5.2.2 | Use case                                                            |

| 5.2.3 | Configuration                                                       |

| 5.3   | Data passing                                                        |

| 5.3.1 | Implementation example of passing small data (up to 64 bits)        |

| 5.3.2 | Use case                                                            |

| 5.3.3 | Configuration                                                       |

| 5.3.4 | Implementation example of passing large data (more than 64 bits)    |

| 5.3.5 | Use case                                                            |

| 5.3.6 | Configuration                                                       |

# Table of contents

| 6       | Consideration for cache coherency issue                               |

|---------|-----------------------------------------------------------------------|

| 6.1     | Cache coherency                                                       |

| 6.2     | Cache memory overview                                                 |

| 6.2.1   | Cache memory placement                                                |

| 6.2.2   | I-cache and D-cache operation 48                                      |

| 6.2.2.1 | Cache memory behavior                                                 |

| 6.2.2.2 | Cache memory configuration                                            |

| 6.2.2.3 | Cache maintenance operation                                           |

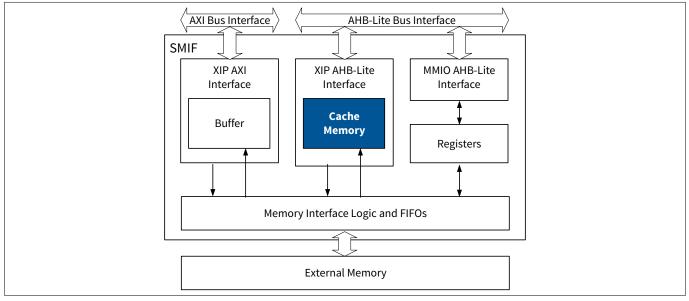

| 6.2.3   | Cache memory operation in flash memory (Code and Work)                |

| 6.2.4   | Cache memory operation in SMIF53                                      |

| 6.3     | Cache coherency handling                                              |

| 6.3.1   | Cache disable                                                         |

| 6.3.2   | Cache invalidate                                                      |

| 6.3.3   | Cache clean                                                           |

| 6.3.4   | Cache configuration sets to write-through                             |

| 6.3.5   | Use TCM as shared memory 55                                           |

| 6.4     | Cache coherency issue scenarios55                                     |

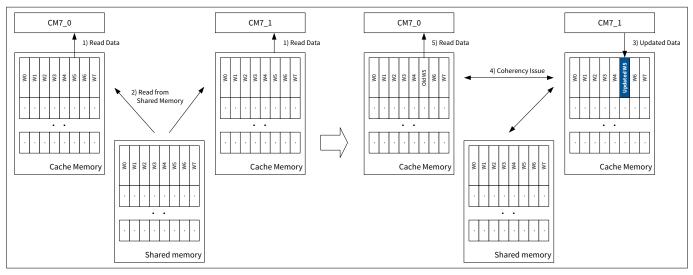

| 6.4.1   | Cache coherency issue between CM7 CPUs55                              |

| 6.4.1.1 | Scenario and solution between CM7 CPUs55                              |

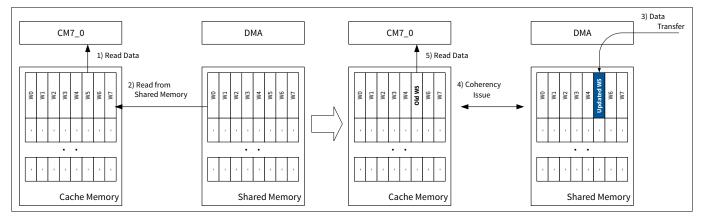

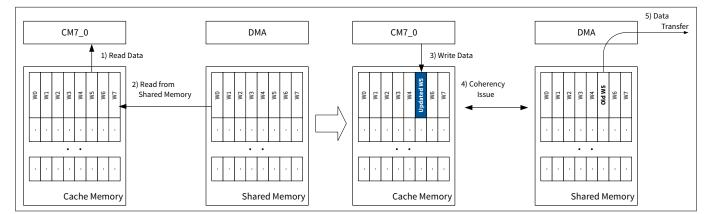

| 6.4.2   | Cache coherency issue between CM7 CPU and other masters               |

| 6.4.2.1 | Scenario and solution for CM7 CPU read and other master write         |

| 6.4.2.2 | Scenario and solution for CM7 CPU write and other master read         |

| 6.4.3   | Cache coherency issue for flash memory access                         |

| 6.4.4   | Cache coherency issue for SMIF access 59                              |

| 6.4.4.1 | Scenario and solution for CM7 access (CM0+ writes and CM7_0 reads)    |

| 6.4.4.2 | Scenario and solution for CM7 access (CM0+ reads and CM7_0 writes)    |

| 6.4.5   | Cache coherency issue for using SROM APIs63                           |

| 6.4.5.1 | Scenario and solution when using SROM API (CM0+ API parameter read)   |

| 6.4.5.2 | Scenario and solution when using SROM API (CM7 execution result read) |

| 6.5     | Additional cache issue scenarios64                                    |

| 6.5.1   | Cache issue for protection attribute switching65                      |

| 6.5.1.1 | Scenario and solution for protection attribute switching              |

| 7       | <b>Glossary</b>                                                       |

| 8       | Related documents                                                     |

| 9       | Other references                                                      |

|         | Revision history                                                      |

|         | Disclaimer                                                            |

## 1 Introduction

# 1 Introduction

TRAVEO<sup>™</sup> T2G family MCUs include Arm<sup>®</sup> Cortex<sup>®</sup>-M CPUs with SRAM, and flash memories, hardware-based Cryptography (eSHE/HSM support), communication peripherals (CAN FD and LIN), digital peripherals (Timer, Counter, and Pulse Width Modulator (PWM)), and analog peripherals (SAR ADC) in a single chip.

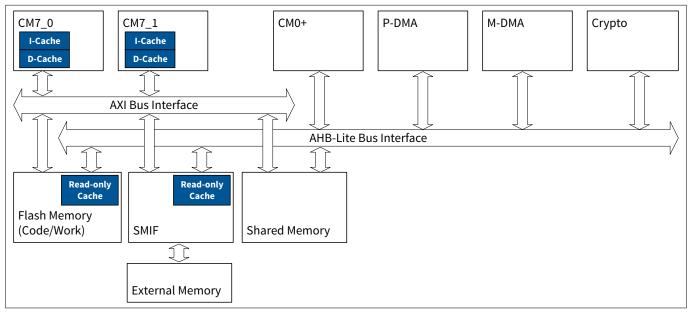

The CPU subsystem (CPUSS) of the TRAVEO<sup>™</sup> T2G MCU consists of multiple bus masters, multiple CPUs, two types of DMA controllers (P-DMA and M-DMA), and a hardware cryptography block (Crypto). The CPUSS also has an Inter-Processor communication (IPC) block that can be used for exclusive control, synchronization, and data passing between CPUs.

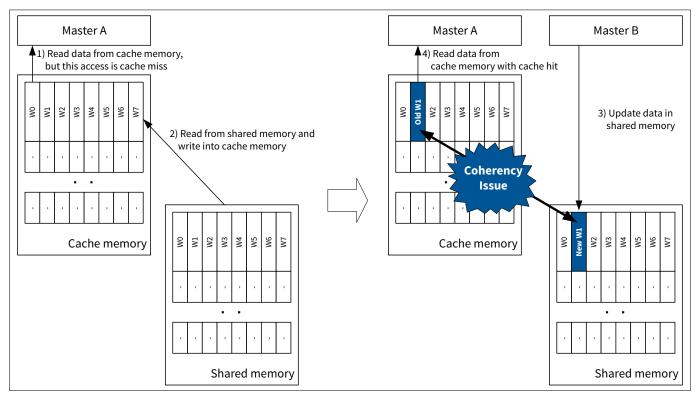

TRAVEO<sup>™</sup> T2G MCUs have cache memory on some peripherals. In addition, the CYT3, CYT4, and CYT6 series have cache memory on the CPU. A cache memory is a low-latency memory, and helps to improve the performance. However, the cache memory can cause coherency issues between memories. Therefore, use of the cache memory requires careful handling.

In addition, this application note describes example code with the Sample Driver Library (SDL). The code snippets in this application note are part of the SDL. See <u>Other references</u> for the SDL.

The SDL consists of a configuration, and a driver associated with the peripheral driver. The configuration helps to set the chosen parameter values for the desired operation, whereas the peripheral driver configures each register based on the parameter values in the configuration. You can adapt the configuration according to your system.

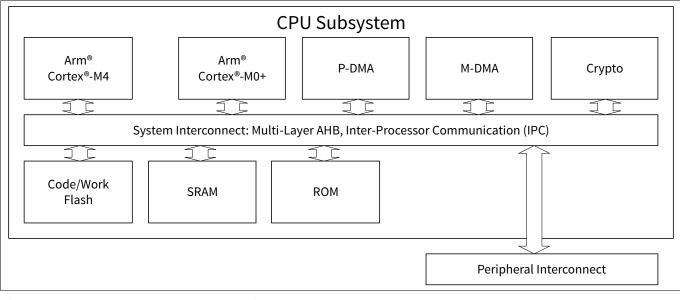

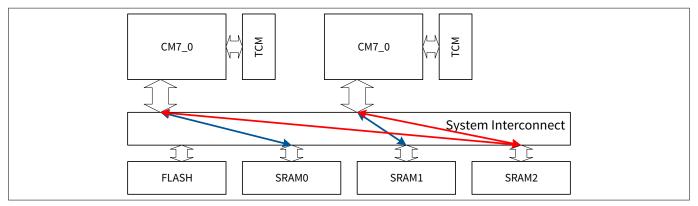

Figure 1 shows block diagram of CPUSS for the CYT2B series, and Figure 2 shows block diagram for the CYT4B series.

Figure 1

CPUSS for CYT2B series

# Multi core handling in TRAVEO<sup>™</sup> T2G family

## 1 Introduction

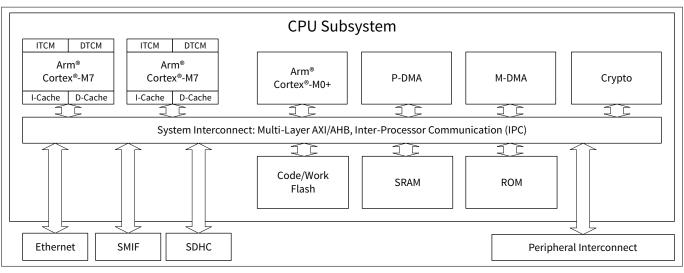

#### Figure 2

#### **CPUSS for CYT4B series**

The CYT2 series MCUs have an Arm<sup>®</sup> Cortex<sup>®</sup>-M4F-based CPU (CM4) and a Cortex<sup>®</sup>-M0+-based CPU (CM0+). The CYT4 series have two Arm<sup>®</sup> Cortex<sup>®</sup>-M7-based CPUs (CM7) and one CM0+. The CYT3 series have one Arm<sup>®</sup> Cortex<sup>®</sup>-M7-based CPU (CM7) and one CM0+. The CYT6B series has four Arm<sup>®</sup> Cortex<sup>®</sup>-M7-based CPUs (CM7) and one CM0+. CM7 CPUs have Instruction/Data cache (I-cache/D-cache) and Instruction/Data Tightly-Coupled Memories (ITCM/DTCM). The CPUSS of TRAVEO<sup>™</sup> T2G MCUs have bus masters for P-DMA, M-DMA, and Crypto. In addition, CYT6B, CYT4B, and CYT3B series MCUs have SDHC and Ethernet as the bus master. CYT4D series MCU has Ethernet, JPEG decoder, VIDEO subsystem, and AXI M-DMA as the bus master. CYT3D series MCU has Ethernet and VIDEO subsystem as the bus master.

See the Arm<sup>®</sup> documentation sets for CM7, CM4, and CM0+, and the TRAVEO<sup>™</sup> T2G architecture technical reference Manual (TRM) for more information.

*Note:* The contents of the block diagram may vary depending on the device. See the device datasheet for device specific details and bus masters.

All memories and peripherals are shared by all bus masters. Shared resources are accessed through standard Arm<sup>®</sup> multi-layer bus arbitration. Exclusive accesses are supported by an IPC block.

A CPUSS with multi-CPU architecture presents unique opportunities for system-level design and performance optimization in a single MCU. The CPUSS with multi-CPU, you can allocate:

- Tasks to different CPUs so that multiple functions may be done at the same time

- Resources to CPUs so that a CPU may be dedicated to managing those resources, thus improving efficiency

### 2 Considerations for CPU startup

# 2 Considerations for CPU startup

Generally, when a user application software is started, the CPU uses the PLL to switch to high-speed operation. However, sudden changes in CPU clock may cause the external or internal supply voltage to drop. If the voltage drops below a defined voltage, the internal brown-out detect (BOD) circuit will trigger a low-voltage detection reset. To avoid a low-voltage detection reset, it is recommended to step up CPU clock in stages to make sure it does not go below the voltage defined by the BOD. See the specific device datasheet for BOD detection voltage. This is especially important for the CYT4 and CYT6 series, which have multiple CM7s.

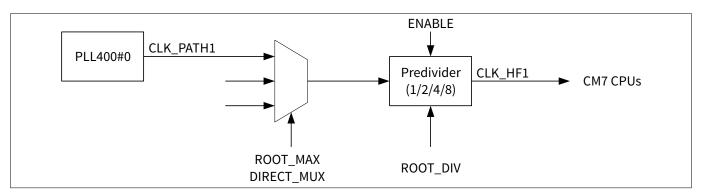

Here is an example of stepping up the CPU clock frequency in stages for the CYT4B series. Figure 3 shows the CM7 CPUs' clock connection in this example. This example uses CLK\_PATH1 with PLL400#0 as the root clock for CLK\_HF1, which is the CM7 CPUs' clock.

#### Figure 3 CM7 CPU's clock connection

# 2.1 Example of step-up CPU clock frequency

This section describes how to step up the CPU clock frequency in stages. This is an example for the CYT4B series.

# 2.1.1 Configuration

Table 1 and Table 2 list the parameters and functions in the SDL for stepping up the CPU clock frequency.

Table 1

Clock configuration parameters

| Parameters                          | Description                      | Value |

|-------------------------------------|----------------------------------|-------|

| WAIT_CYCLE_WHILE_DISTRIBUTING_CLOCK | Rising time adjustment           | 50 ul |

| SRSS_NUM_HFROOT                     | Number of HF clocks              | 8 ul  |

| clkHfSetting.targetDiv              | Set target CLK_HF division       | -     |

| clkHfSetting.source                 | Selection of target CLK_HF root. | -     |

| Functions                       | Description            | Remarks |

|---------------------------------|------------------------|---------|

| Cy_SysTick_DelayCoreCycle(wait) | Delay input core cycle | -       |

The following code shows an example of stepping up the clock frequency:

SRSS->unCLK\_ROOT\_SELECT[x].stcField.u4ROOT\_MUX is the ROOT\_MUX field in the SRSS\_CLK\_ROOT\_SELECT[x] register mentioned in the registers TRM. Other registers are also described in the same manner."x" signifies the register suffix number.

See *cyip\_srss\_v3.h* under hdr/rev\_x/ip for more information on the union and structure representation.

#### 2 Considerations for CPU startup

#### Code Listing 1 Example of stepping up the CPU clock frequency

```

#define WAIT CYCLE WHILE DISTRIBUTING CLOCK (50ul)

#define SRSS_NUM_HFROOT

8u1

typedef enum

{

CY SYSCLK HFCLK NO DIVIDE = \Thetau,

/**< don't divide hf_clk. */</pre>

CY_SYSCLK_HFCLK_DIVIDE_BY_2 = 1u, /**< divide hf_clk by 2 */

CY_SYSCLK_HFCLK_DIVIDE_BY_4 = 2u, /**< divide hf_clk by 4 */

CY_SYSCLK_HFCLK_DIVIDE_BY_8 = 3u

/**< divide hf_clk by 8 */

} cy_en_hf_clk_dividers_t;

typedef enum

{

CY_SYSCLK_HFCLK_IN_CLKPATH0 = 0u, /**< hf_clk input is Clock Path 0 */

CY_SYSCLK_HFCLK_IN_CLKPATH1 = 1u, /**< hf_clk input is Clock Path 1 */

CY_SYSCLK_HFCLK_IN_CLKPATH2 = 2u, /**< hf_clk input is Clock Path 2 */

CY_SYSCLK_HFCLK_IN_CLKPATH3 = 3u, /**< hf_clk input is Clock Path 3 */

CY_SYSCLK_HFCLK_IN_CLKPATH4 = 4u, /**< hf_clk input is Clock Path 4 */

CY_SYSCLK_HFCLK_IN_CLKPATH5 = 5u, /**< hf_clk input is Clock Path 5 */

:

CY SYSCLK HFCLK IN CLKIMO = 0xFFu, /**< hf_clk input is directly connected to IMO */

} cy_en_hf_clk_sources_t;

void SystemInit (void)

{

/***

PLL setting and enabling

***/ /* Set PLL here. */

:

/*** Setting for each clk hf

***/

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH3}, //

setting for clk_hf0

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH1}, //

setting for clk_hf1

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH4}, //

setting for clk_hf2

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH1}, //

setting for clk hf3

{ .targetDiv = CY_SYSCLK_HFCLK_DIVIDE_BY_4, .source = CY_SYSCLK_HFCLK_IN_CLKPATH3}, //

setting for clk_hf4

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH2}, //

setting for clk_hf5

{ .targetDiv = CY SYSCLK HFCLK NO DIVIDE, .source = CY SYSCLK HFCLK IN CLKPATH3}, //

setting for clk_hf6

{ .targetDiv = CY_SYSCLK_HFCLK_NO_DIVIDE, .source = CY_SYSCLK_HFCLK_IN_CLKPATH5}, //

setting for clk_hf7

};

for(int8_t i_clkHfNo = @ul; i_clkHfNo < SRSS_NUM_HFROOT; i_clkHfNo++)</pre>

{

```

#### 2 Considerations for CPU startup

```

SRSS->unCLK_ROOT_SELECT[i_clkHfNo].stcField.u4ROOT_MUX

=

clkHfSetting[i clkHfNo].source; /* CLK_HF configuration */

SRSS->unCLK_ROOT_SELECT[i_clkHfNo].stcField.u2ROOT_DIV

=

CY_SYSCLK_HFCLK_DIVIDE_BY_8; /* CLK_HF configuration */

SRSS->unCLK_ROOT_SELECT[i_clkHfNo].stcField.u1DIRECT_MUX = 1u; /* Select ROOT_MUX */

/* CLK_HF configuration */

SRSS->unCLK_ROOT_SELECT[i_clkHfNo].stcField.u1ENABLE = 1u; /* 1 = enable */ /*

CLK_HF configuration */

/* Gradually decrease the current root clock divider until the target divider is

reached */ /* Step up CPU Clock frequency */

for(int8_t i_divRegValue = 2; i_divRegValue >= clkHfSetting[i_clkHfNo].targetDiv;

i_divRegValue--)

{

Cy_SysTick_DelayCoreCycle(WAIT_CYCLE_WHILE_DISTRIBUTING_CLOCK);

SRSS->unCLK_ROOT_SELECT[i_clkHfNo].stcField.u2ROOT_DIV = i_divRegValue;

}

Cy_SysTick_DelayCoreCycle(WAIT_CYCLE_WHILE_DISTRIBUTING_CLOCK);

}

•

}

```

In this example, the CPU clock frequency is stepped up using the CLK\_HF clock divider in steps from 8 division to target division using the CLK\_HF clock divider. The call to the Cy\_SysTick\_DelayCoreCycle() API provides the required delay between each successive step. See the "Clocking System" chapter in the architecture TRM and application note for PLL and CLK\_HF configuration.

#### **3** Considerations for resource access

# **3 Considerations for resource access**

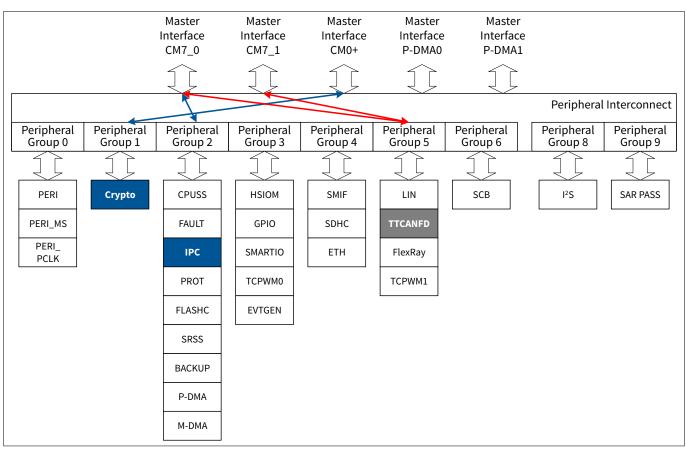

As mentioned above, all memory and peripherals are accessed through standard Arm<sup>®</sup> multi-layer bus architecture by all bus masters. Therefore, each master can start accessing the bus at the same time. However, the multiple bus masters can access different memory or peripheral groups at the same time, but cannot access the same memory or peripheral group at same time.

Figure 4 shows resource connection for CYT4BF series. IPC (blue box) access of CM7\_0 and Crypto (blue box) access of CM0+ can be performed at same time (indicated by blue arrows). However, CM7\_0 and CM7\_1 cannot access TTCAN FD (grey box) at the same time (indicated by red arrows).

#### Figure 4 Resource connection (CYT4BF series)

To improve performance, you need to consider CPU resource allocation in system design, so that the CPU may be dedicated to managing those resources. In this case, dedicating either CM7\_0 or CM7\_1 to TTCAN FD management will improve performance.

A similar case occurs for memory access. For example, SRAM0 access of CM7\_0 and SRAM1 access of CM7\_1 can be performed at same time (blue arrow). CM7\_0 and CM7\_1 cannot access same SRAM at the same time even if the addresses are different within the SRAM (red arrow).

### **3** Considerations for resource access

#### Figure 5 Memory connection (CYT4BF series)

In such cases, you can improve performance by assigning dedicated SRAM for each CPU or using TCM dedicated to each CPU.

*Note:* The connection of resources and memory may vary depending on the device. See the device datasheet for device specific details.

4 Consideration for write buffer in CPU and bus infrastructure

4

# Consideration for write buffer in CPU and bus infrastructure

TRAVEO<sup>™</sup> T2G has write buffers in CPU and bus infrastructure. A write buffer increases the execution performance, because subsequent instructions can be executed without waiting for the write complition. However, this means that the application cannot assume the impact of a register write in a timely way. Therefore, it might require extra steps to ensure the correctness of the program operation.

For the write buffer in the CPU, you can use memory barrier instructions to support the sequencing between memory accesses, or between memory accesses and other operations.

For the write buffer in bus infrastructure, if the MPU region is set to the device type for the concerned register, the CPU will continue the execution and not wait for the register write. The writing to register is ensured, but the timing may differ. For example, the timing depends on the following conditions:

- Write buffer in the CPU

- Clock ratio between the CPU and the register clock

- Buffers in the bus infrastructure

- Other masters accessing and occupying the bus system (arbitration)

A readback of a register is necessary when you want to ensure that the changes in the registers are effective before proceeding with the code execution. A readback operation reads the data from the concerned register after writing register the write buffer data.

For example, when leaving an interrupt handler, clear the interrupt flag in the peripheral register and execute a readback to ensure that the flag is cleared in the peripheral register before clearing the flag in the NVIC. As a result, it can prevent an immediate resetting of the flag in the NVIC.

See the Arm<sup>®</sup> Cortex<sup>®</sup>-M Programming Guide to Memory Barrier Instructions in Related documents[6] for more details.

5

# Communicating between CPUs

Architectures with multiple CPUs often require exclusive control, synchronization, and data passing between CPUs, TRAVEO<sup>™</sup> T2G can use IPC for such control. IPC has support for mutual exclusion (mutex), message passing, and event/release notification.

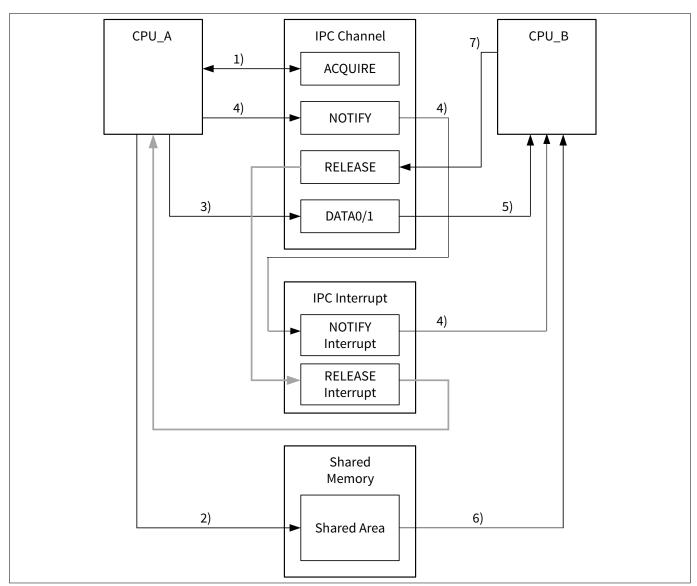

The IPC hardware contains register structures for IPC channel and IPC interrupt. IPC channel registers implement lock/release mechanisms, and messaging. IPC interrupt structure registers generate interrupts to each CPU for messaging events and lock/release events.

The IPC channel structure ACQUIRE register provides lock feature and IPC\_STRUCTx\_LOCK\_STATUS indicates lock status. The IPC\_STRUCTx\_NOTIFY register generates notification event, the IPC\_STRUCTx\_RELEASE register releases IPC channel structure and generates release event. IPC\_STRUCTx\_DATA0/1 register can pass a message up to 64 bits.

TRAVEO<sup>™</sup> T2G devices have a supervisory ROM that contains the boot ROM code and SROM APIs. The SROM APIs are designed to be used with Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ (CM0+). The specific IPC channel structures and interrupt structures are used to activate the APIs. See the "Nonvolatile memory programming" chapter in the architecture TRM for more information.

Note: LDREX/STREX and other exclusive access instructions are not supported by the TRAVEO<sup>™</sup> T2G devices. Therefore, implementation inter-process communication in system of multiple CPUs and shared memory needs to use IPC.

# 5.1 CPU synchronization

This section describes how to synchronize CPUs using IPC. In a multi-CPU architecture, the order in which tasks are executed by each CPU needs to be carefully managed.

As an example, consider two CPUs (CPU\_A and CPU\_B), where the CPU\_A initializes resources and then CPU\_B uses the initialized resources. In this case, however, if CPU\_B uses the resource before CPU\_A initializes the resource (wrong order of execution), it causes an unintended operation.

IPC has two solutions for this issue. One solution is to use the IPC\_STRUCTx\_DATA0/1 register. Another solution is to use the IPC\_STRUCTx\_NOTIFY register. The solution using IPC\_STRUCTx\_DATA0/1 register is easy to implement. CPU\_A writes a specific value to the IPC\_STRUCTx\_DATA0 register when initialization is completed. CPU\_B polls the IPC\_STRUCTx\_DATA0 register and does not start execution until it reads that specific value from the IPC\_STRUCTx\_DATA0 register.

Synchronization using IPC\_STRUCTx\_NOTIFY register uses a notification event interrupt. Table 3 lists the registers associated with the notification event. IPC\_STRUCTx\_NOTIFY register is used to generate an IPC notify event and IPC\_STRUCTx\_RELEASE is used to generate an IPC release event.

| Structure       | Register name       | Bit name           | Description                                                                                                                                                                    |

|-----------------|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPCx<br>channel | IPC_STRUCTx_NOTIFY  | INTR_NOTIFY[15:0]  | This field allows for the generation of<br>notification events to the IPC<br>interrupt structures.<br>SW always reads a '0' from this field.                                   |

|                 | IPC_STRUCTx_RELEASE | INTR_RELEASE[15:0] | This field allows for the generation of<br>release events to the IPC interrupt<br>structures, but only when the lock is<br>acquired.<br>SW always reads a '0' from this field. |

## Table 3Notify event registers

(table continues...)

| Structure         | Register name                | Bit name      | Description                                                                               |

|-------------------|------------------------------|---------------|-------------------------------------------------------------------------------------------|

| IPCx<br>interrupt | IPC_INTR_STRUCTx_INTR        | NOTIFY[31:16] | These interrupts cause fields to be activated when an IPC notification event is detected. |

|                   |                              |               | SW writes '1' to these fields to clear the interrupt cause.                               |

|                   |                              | RELEASE[15:0] | These interrupts cause fields to be activated when an IPC release event is detected.      |

|                   |                              |               | SW writes '1' to these fields to clear the interrupt cause.                               |

|                   | IPC_INTR_STRUCTx_INTR_SET    | NOTIFY[31:16] | SW writes '1' to this field to set the corresponding field in the INTR register.          |

|                   |                              | RELEASE[15:0] | SW writes '1' to this field to set the corresponding field in the INTR register.          |

|                   | IPC_INTR_STRUCTx_INTR_MASK   | NOTIFY[31:16] | Mask bit for corresponding field in the INTR register                                     |

|                   |                              | RELEASE[15:0] | Mask bit for corresponding field in the INTR register                                     |

|                   | IPC_INTR_STRUCTx_INTR_MASKED | NOTIFY[31:16] | Logical and of corresponding request and mask bits                                        |

|                   |                              | RELEASE[15:0] | Logical and of corresponding INTR and INTR_MASK fields                                    |

## Table 3 (continued) Notify event registers

"x" indicates channel number for each IPC structure.

Each bit in the IPC\_STRUCTx\_NOTIFY and IPC\_STRUCTx\_RELEASE registers corresponds to the channel number of IPC interrupt structure, and each bit in the IPC\_INTR\_STRUCTx\_INTR, IPC\_INTR\_STRUCTx\_INTR\_SET, IPC\_INTR\_STRUCTx\_INTR\_MASK, and IPC\_INTR\_STRUCTx\_INTR\_MASKED registers corresponds to channel number of IPC channel structures. NOTIFY [31:16] corresponds to channel numbers 15 to 0 of IPC channel structure. See the registers TRM for more information.

*Note:* The channel number of IPC channel structure and IPC interrupt structure may vary depending on the device. See the device datasheet for device specific details.

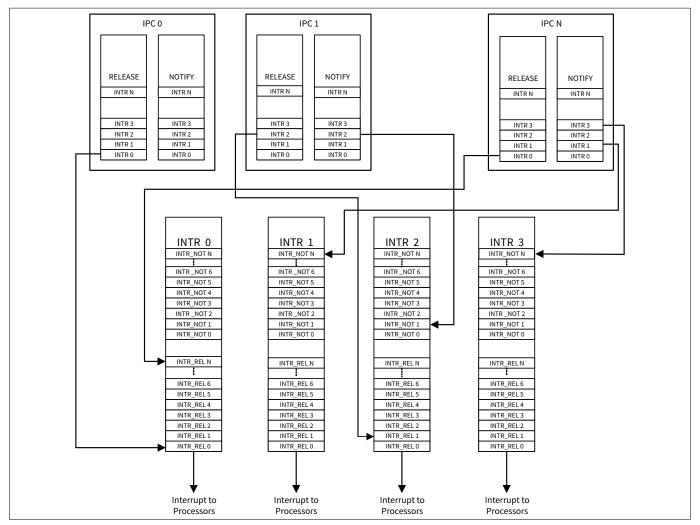

Figure 6 shows the relation between the IPC channel structures and the IPC interrupt structures. An IPC interrupt structure can be triggered from any of the IPC channel structures, and the event generated from an IPC channel structure can trigger any or multiple interrupts in an IPC interrupt structure.

Figure 6 IPC channel structures and interrupt structures

In the example shown in Figure 6, IPC 0 channel structure can trigger the RELEASE event of INTR 0 and IPC 1 channel structure can trigger the NOTIFY and RELEASE event of INTR 2. IPC N channel structure can trigger the NOTIFY event of INTR 1 and INTR 3, and the RELEASE event of INTR 0.

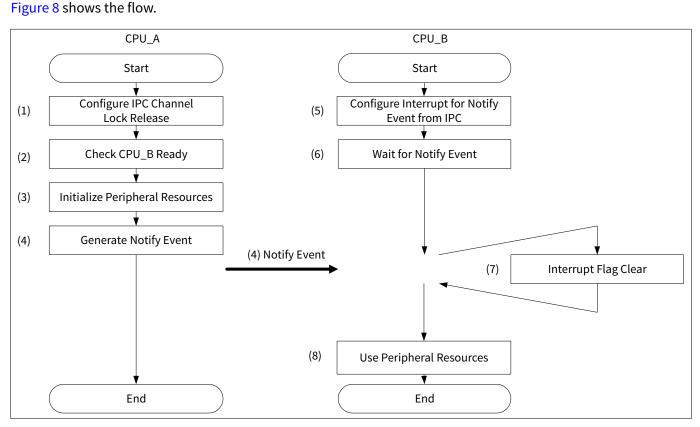

# 5.1.1 Implementation example operation of synchronization between CPUs

The section describes how to synchronize using the IPC\_STRUCTx\_NOTIFY register. In this use case, when CPU\_A completes initialization of resources, CPU\_A notifies interrupt to CPU\_B using the IPC\_STRUCTx\_NOTIFY register. CPU\_B waits to execute until it receives the notify interrupt in the following example.

# 5.1.2 Use case

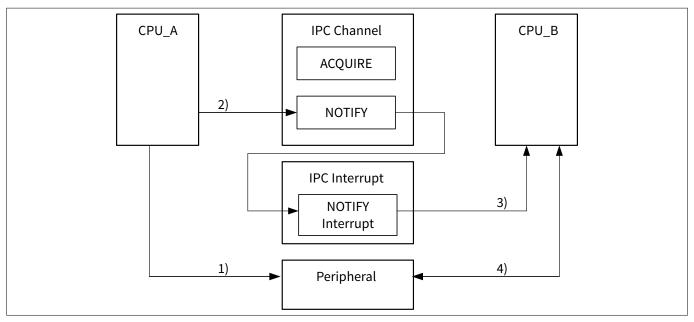

Figure 7 shows an implementation example of CPU synchronization using IPC.

# Multi core handling in TRAVEO<sup>™</sup> T2G family

#### 5 Communicating between CPUs

#### Figure 7 CPU synchronization using IPC

- **1.** CPU\_A initializes the peripheral.

- 2. After completing peripheral initialization, CPU\_A generates a notify interrupt to CPU\_B.

- **3.** Then, a notify interrupt occurs in CPU\_B.

- **4.** CPU\_B can start running the operation using the peripheral (initialized by CPU\_A) after returning from the interrupt routine.

#### Figure 8 CPU synchronization operation

The following is the structure of the sample code.

- IPC channel structure: 6

- IPC interrupt structure: 5

See the "Interrupts" chapter in the architecture TRM and AN219842 - How to use interrupt in TRAVEO<sup>™</sup> T2G for interrupt configuration details.

# 5.1.3 Configuration

Table 4 and Table 5 list the parameters and functions in SDL for CPU synchronization using IPC. This is example for CYT2B series. Here, it assumes that CPU\_A is CM4 and CPU\_B is CM0+.

#### Table 4 Configuration parameters for CPU synchronization

| Parameter              | Description                                                             | Value                                     |

|------------------------|-------------------------------------------------------------------------|-------------------------------------------|

| IPC_NOTIFY_INT_NUMBER  | Defines using IPC interrupt<br>structure number for the notify<br>event | 5ul (IPC5 interrupt structure)            |

| IPC_CHANNEL_NUMBER     | Defines using the IPC channel structure number                          | 6ul (IPC6 channel structure)              |

| CY_IPC_NO_NOTIFICATION | Defines a value to indicate that no notification events are needed      | 0x00000000ul                              |

| waitFlag               | Indicates whether peripheral initialization is complete                 | 0: Completed<br>1: Not complete (Default) |

#### Table 5Configuration functions for CPU synchronization

| Function                                       | Description                                                        | Remarks |

|------------------------------------------------|--------------------------------------------------------------------|---------|

| Cy_IPC_Drv_GetIpcBaseAddress(ipcIndex)         | Gets the base address of the IPC channel structure.                | -       |

|                                                | ipcIndex: IPC channel structure number                             |         |

| Cy_IPC_Drv_LockRelease(base, releaseEventIntr) | Releases the IPC channel lock.                                     | -       |

|                                                | base: Base address of the IPC channel to operate                   |         |

|                                                | releaseEventIntr: Specifies the release event                      |         |

| Cy_IPC_Drv_GetIntrBaseAddr(ipcIntrIndex)       | Gets the base address of the IPC interrupt structure.              | -       |

|                                                | ipcIndex: IPC interrupt structure number                           |         |

|                                                | Gets the value of INTR_MASK register.                              | -       |

|                                                | base: Base address of the<br>IPC interrupt structure to<br>operate |         |

#### (table continues...)

| Table 5       (continued) Configuration functions for CPU synchronization |                                                                    |         |  |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------|---------|--|--|

| Function                                                                  | Description                                                        | Remarks |  |  |

| Cy_IPC_Drv_ExtractAcquireMask(intMask)                                    | Gets the value of the NOTIFY field in INTR_MASK.                   | -       |  |  |

|                                                                           | intMask: Value of<br>INTR_MASK                                     |         |  |  |

| Cy_IPC_Drv_AcquireNotify(base, notifyEventIntr)                           | Sets the notify event to the NOTIFY register.                      | -       |  |  |

|                                                                           | base: Base address of the IPC channel structure                    |         |  |  |

|                                                                           | notifyEventIntr: Value of the notify event setting                 |         |  |  |

|                                                                           | Checks whether the lock is acquired                                | -       |  |  |

|                                                                           | base: Base address of the<br>IPC channel structure to<br>operate   |         |  |  |

| Cy_IPC_Drv_ReleaseNotify(base, notifyEventIntr)                           | Sets the release event to the RELEASE register.                    | -       |  |  |

|                                                                           | base: Base address of the IPC channel structure                    |         |  |  |

|                                                                           | notifyEventIntr: Value of the release event setting                |         |  |  |

| Cy_IPC_Drv_SetInterruptMask(base, ipcReleaseMask, ipcNotifyMask)          | Sets interrupt to the INTR_MASK register.                          | -       |  |  |

|                                                                           | base: Base address of the<br>IPC interrupt structure<br>number     |         |  |  |

|                                                                           | ipcReleaseMask: Value of the release event setting                 |         |  |  |

|                                                                           | ipcNotifyMask: Value of the notify event setting                   |         |  |  |

| Cy_IPC_Drv_GetInterruptStatusMasked(base)                                 | Gets the value of INTR_MASKD register.                             | -       |  |  |

|                                                                           | base: Base address of the<br>IPC interrupt structure to<br>operate |         |  |  |

|                                                                           | Clears the interrupt flag.                                         | -       |  |  |

| ipcNotifyMask)                                                            | base: Base address of the<br>IPC interrupt structure to<br>operate |         |  |  |

|                                                                           | ipcReleaseMask: Clears<br>data for the release event               |         |  |  |

|                                                                           | ipcNotifyMask: Clears data<br>for the notify event                 |         |  |  |

#### Table 5(continued) Configuration functions for CPU synchronization

The following code shows an example of CPU synchronization using IPC.

- Base signifies the pointer to the IPC register base address.

- **base**->unNOTIFY.u32Register is the IPC\_STRUCTx\_NOTIFY register mentioned in the registers TRM . Other registers are also described in the same manner. "**x**" signifies the register suffix number.

- To improve the register setting performance, the SDL writes a complete 32-bit data to the register. Each bit field is generated and written to the register as the final 32-bit data.

```

un_IPC_INTR_STRUCT_INTR_t reg = { 0 };

reg.stcField.u16NOTIFY = ipcNotifyMask;

reg.stcField.u16RELEASE = ipcReleaseMask;

base->unINTR.u32Register = reg.u32Register;

```

See *cyip\_ipc.h* under *hdr/rev\_x/ip* for more information on the union and structure representation of registers.

#### Code Listing 2 Example of CPU synchronization for CM4

```

#define IPC_NOTIFY_INT_NUMBER 5ul /* Notify interrupt number */ /* Define number of IPC

interrupt for notify event. */

#define IPC_CHANNEL_NUMBER 6ul /* IPC number which is used in this example */ /* Define

IPC channel number */

#define CY_IPC_NO_NOTIFICATION

(uint32_t)(0x0000000ul) /* Define Lock release data

without release event */

#define _FLD2VAL(field, value) (((uint32_t)(value) & field ## _Msk) >> field ## _Pos)

int main(void)

{

•

/* At first force release the lock state. */

volatile stc_IPC_STRUCT_t* ipcBase = Cy_IPC_Drv_GetIpcBaseAddress(IPC_CHANNEL_NUMBER); /*

Get base address of IPC channel structure. See Code Listing 3. */

(void)Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* IPC_channel

initialization (Release a lock).See Code Listing 4.

*/

/* Wait until the CMO+ IPC server is started */

/* Note:

* After the CMO+ IPC server is started, the corresponding number of the INTR MASK is set.

* So in this case CM4 can recognize whether the server has started or not by the INTR_MASK

status.

*/

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER); /* Get base address of IPC interrupt

structure. See Code Listing 5. */

uint32_t intrMask;

uint32_t notifyMask;

do

{

intrMask = Cy_IPC_Drv_GetInterruptMask(ipcIntrStrBase); /* Get value of IPC.INTR_MASK.

See Code Listing 6. */

notifyMask = Cy_IPC_Drv_ExtractAcquireMask(intrMask); /* Get value of notify mask. See

Code Listing 7. */

} while((notifyMask & (1ul << IPC_CHANNEL_NUMBER)) == 0); /* (2) Check if CMO+ ready. *</pre>

```

/\* Initialize peripherals \*/ /\* (3) Initialize peripherals. \*/

```

/* Generate a notify interrupt */

Cy_IPC_Drv_AcquireNotify(ipcBase, (1ul << IPC_NOTIFY_INT_NUMBER)); /* Generate notify

interrupt. See Code Listing 8. */

for(;;)

{

}

}</pre>

```

#### Code Listing 3 Cy\_IPC\_Drv\_GetIpcBaseAddress () function

```

__STATIC_INLINE volatile stc_IPC_STRUCT_t* Cy_IPC_Drv_GetIpcBaseAddress (uint32_t ipcIndex)

{

CY_ASSERT((uint32_t)CPUSS_IPC_IPC_NR > ipcIndex);

return ( (volatile stc_IPC_STRUCT_t*) ( &IPC->STRUCT[ipcIndex] ) );

}

```

#### Code Listing 4 Cy\_IPC\_Drv\_LockRelease() function

```

cy_en_ipcdrv_status_t Cy_IPC_Drv_LockRelease (volatile stc_IPC_STRUCT_t* base, uint32_t

releaseEventIntr)

{

cy_en_ipcdrv_status_t retStatus;

/* Check to make sure the IPC is Acquired */

if( Cy_IPC_Drv_IsLockAcquired(base) ) /* Check if the lock is acquired. See Code Listing 9.

*/

{

/* The IPC was acquired, release the IPC channel */

Cy_IPC_Drv_ReleaseNotify(base, releaseEventIntr); /* Release the IPC channel. See Code

Listing 10. */

retStatus = CY_IPC_DRV_SUCCESS;

}

else /* The IPC channel was already released (not acquired) */

{

retStatus = CY_IPC_DRV_ERROR;

}

return(retStatus);

}

```

#### Code Listing 5 Cy\_IPC\_Drv\_GetIntrBaseAddr() function

```

__STATIC_INLINE volatile stc_IPC_INTR_STRUCT_t* Cy_IPC_Drv_GetIntrBaseAddr (uint32_t

ipcIntrIndex)

{

CY_ASSERT((uint32_t)CPUSS_IPC_IPC_IRQ_NR > ipcIntrIndex);

return ( (volatile stc_IPC_INTR_STRUCT_t*) ( &IPC->INTR_STRUCT[ipcIntrIndex] ) ); /* Get

base address of IPC interrupt structure. */

}

```

#### Code Listing 6 Cy\_IPC\_Drv\_GetInterruptMask() function

```

__STATIC_INLINE uint32_t Cy_IPC_Drv_GetInterruptMask(volatile stc_IPC_INTR_STRUCT_t const *

base)

{

return (base->unINTR_MASK.u32Register); /* Get value of the INTR_MASK. */

}

```

#### Code Listing 7 Cy\_IPC\_Drv\_ExtractAcquireMask() function

```

__STATIC_INLINE uint32_t Cy_IPC_Drv_ExtractAcquireMask (uint32_t intMask)

{

return _FLD2VAL(IPC_INTR_STRUCT_INTR_MASK_NOTIFY, intMask); /* Get value of

INTR_MASK.NOTIFY value. */

}

```

#### Code Listing 8 Cy\_IPC\_Drv\_ExtractAcquireMask() function

```

__STATIC_INLINE void Cy_IPC_Drv_AcquireNotify (volatile stc_IPC_STRUCT_t* base, uint32_t

notifyEventIntr)

{

un_IPC_STRUCT_NOTIFY_t reg = { 0 };

reg.stcField.u16INTR_NOTIFY = notifyEventIntr;

base->unNOTIFY.u32Register = reg.u32Register; /* (4) Generate Notify event. */

}

```

#### Code Listing 9 Cy\_IPC\_Drv\_IsLockAcquired() function

```

__STATIC_INLINE bool Cy_IPC_Drv_IsLockAcquired (volatile stc_IPC_STRUCT_t const * base)

{

return ( @u != base->unLOCK_STATUS.stcField.u1ACQUIRED ); /* Read value of IPC channel

structure acquired*/

}

```

#### Code Listing 10 Cy\_IPC\_Drv\_ReleaseNotify() function

```

__STATIC_INLINE void Cy_IPC_Drv_ReleaseNotify (volatile stc_IPC_STRUCT_t* base, uint32_t

notifyEventIntr)

{

un_IPC_STRUCT_RELEASE_t reg = { 0 };

reg.stcField.u16INTR_RELEASE = notifyEventIntr;

base->unRELEASE.u32Register = reg.u32Register; /* (1) Write to RELEASE register for

releasing the IPC channel structure. */

}

```

#### Code Listing 11 Example of CPU synchronization for CM0+

```

#define IPC_NOTIFY_INT_NUMBER 5ul /* Notify interrupt number */ /* Define number of IPC

interrupt for release event. */

#define IPC CHANNEL NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel */

#define CY IPC NO NOTIFICATION

(uint32 t)(0x000000000)

cy_stc_sysint_irq_t irq_cfg = /* Configure IPC interrupt. */

{

.sysIntSrc = (cy_en_intr_t)(cpuss_interrupts_ipc_0_IRQn + IPC_NOTIFY_INT_NUMBER),

.intIdx

= CPUIntIdx2 IRQn,

.isEnabled = true,

};

/* Configure IPC interrupt. */

uint8_t waitFlag = 1ul;

int main(void)

{

:

/* Enable application core CM4.

* CY_CORTEX_M4_APPL_ADDR must be updated if CM4 memory layout is changed.

*/

Cy_SysEnableApplCore(CY_CORTEX_M4_APPL_ADDR); /* Activate CM4 */

/* Enable IPC interrupt mask */

volatile stc IPC INTR STRUCT t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER); /* Get base address of IPC interrupt

structure. See Code Listing 5. */

uint32_t releaseMask = CY_IPC_NO_NOTIFICATION;

uint32_t notifyMask = (1ul << IPC_CHANNEL_NUMBER);</pre>

Cy_IPC_Drv_SetInterruptMask(ipcIntrStrBase, releaseMask, notifyMask); /* (5)-1 Enable IPC

notify event. See Code Listing 13. */

/* Interrupt setting */ /* (5)-2 Configure interrupt for IPC notify event */

Cy_SysInt_InitIRQ(&irq_cfg);

Cy_SysInt_SetSystemIrqVector(irq_cfg.sysIntSrc, IpcIntHandler);

/* Set the Interrupt Priority & Enable the Interrupt */

NVIC_SetPriority(CPUIntIdx2 IRQn, 0ul);

NVIC_EnableIRQ(CPUIntIdx2_IRQn);

/* (5)-2 Configure interrupt for IPC notify event */

/* Wait until IPC interrupt is generated */

while(waitFlag == 1ul); /* (6) Wait for interrupt */

for(;;)

{

/* (8) CMO+ can use peripheral. */

:

}

}

```

#### Code Listing 12 Notify interrupt handler for CM0+

```

void IpcIntHandler(void)

{

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER); /* Get base address of IPC interrupt

structure. See Code Listing 5. */

= Cy_IPC_Drv_GetInterruptStatusMasked(ipcIntrStrBase);

uint32 t intrMasked

uint32_t releaseMasked = CY_IPC_NO_NOTIFICATION; /* Do not care */ /* Get value of

INTR_MASKD. See Code Listing 14. */

uint32_t notifyMasked = Cy_IPC_Drv_ExtractAcquireMask(intrMasked); /* Get value of notify

mask. See Code Listing 7. */

/* Check if the interrupt is caused by the notifier channel */

if (notifyMasked & (1ul << IPC_CHANNEL_NUMBER)) /* Check if interrupts are valid. */

{

/* Clear IPC interrupt */

Cy_IPC_Drv_ClearInterrupt(ipcIntrStrBase, releaseMasked, notifyMasked); /* Clear

Interrupt flag. See Code Listing 15. */

/* Clear wait flag */

waitFlag = Oul;

}

}

```

#### Code Listing 13 Cy\_IPC\_Drv\_SetInterruptMask() function

#### Code Listing 14 Cy\_IPC\_Drv\_GetInterruptStatusMasked() function

```

__STATIC_INLINE uint32_t Cy_IPC_Drv_GetInterruptStatusMasked (volatile stc_IPC_INTR_STRUCT_t

const * base)

{

return (base->unINTR_MASKED.u32Register); /* Get value of INTR_MASKD. */

}

```

#### Code Listing 15 Cy\_IPC\_Drv\_ClearInterrupt() function

```

__STATIC_INLINE void Cy_IPC_Drv_ClearInterrupt(volatile stc_IPC_INTR_STRUCT_t* base, uint32_t

ipcReleaseMask, uint32_t ipcNotifyMask)

{

un_IPC_INTR_STRUCT_INTR_t reg = { 0 };

reg.stcField.u16NOTIFY = ipcNotifyMask;

reg.stcField.u16RELEASE = ipcReleaseMask;

base->unINTR.u32Register = reg.u32Register; /* (7) Clear interrupt flag */

(void)base->unINTR.u32Register; /* Read the register to flush the cache */ /* Read back */

}

```

# 5.2 Mutual exclusion operation

This section describes how to mutually exclude shared resource access between CPUs using IPC. In a multi-CPU architecture, each CPU may share memory and peripherals, such as data exchange or external serial communication.

As an example, consider the situation where two CPUs (CPU\_A and CPU\_B) share the memory. CPU\_A is supposed to read and update the memory data. Then, CPU\_B is supposed to read and update the same memory data, but only after CPU A completes the operation. However, if CPU\_A reads memory data, but CPU\_B updates the memory data before CPU\_A updates the memory data, there will be a mismatch between the actual memory data and the expected memory data because CPU\_B is supposed to update the data written by CPU\_A.

To avoid this issue, CPU\_B should not be allowed to access the memory while CPU\_A is reading and updating the data.

IPC in TRAVEO<sup>™</sup> T2G MCUs can easily implement exclusive access using the IPC\_STRUCTx\_ACQUIRE register. This register has a lock feature for the IPC channel structure. A lock of the IPC channel structure is acquired by reading this register. Table 6 shows the result of the ACQUIRE register read operation.

| Result of read access | IPC channel structure status           |

|-----------------------|----------------------------------------|

| 0                     | IPC channel structure lock failed.     |

| 1                     | IPC channel structure lock successful. |

Table 6IPC\_STRUCTx\_ACQUIRE register operation

If the register is already in an acquired state, another master cannot acquire it. The acquired state of the IPC channel structure is provided by the IPC\_STRUCTx\_LOCK\_STATUS register. The acquired state of the IPC channel structure is released by writing any value into the IPC\_STRUCTx\_RELEASE register; this allows for the generation of release events to the IPC interrupt structure.

# 5.2.1 Implementation example of mutual exclusion

This section describes an example of mutual exclusion access. This use case assumes that CPU\_A and CPU\_B access a common peripheral resource. An IPC channel structure is associated with a common peripheral resource; when accessing the common peripheral resource, each CPU must acquire a lock on the associated IPC channel structure. Therefore, the CPU that cannot acquire the IPC channel structure lock is not allowed to access the common peripheral.

# 5.2.2 Use case

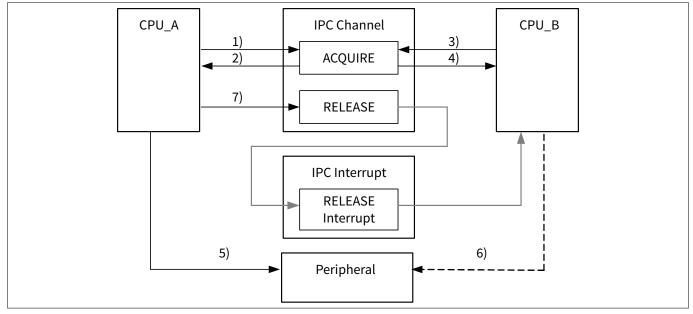

Figure 9 shows an implementation example of common peripheral exclusive access using IPC.

## Figure 9 Example of exclusive access

The following shows an example of exclusive control implementation:

- **1.** CPU\_A reads the IPC\_STRUCTx\_ACQUIRE register before CPU\_A accesses the common peripheral.

- 2. When CPU\_A reads "1" from the IPC\_STRUCTx\_ACQUIRE register, CPU\_A is successful in acquiring the IPC channel structure lock.

- **3.** CPU\_B reads the IPC\_STRUCTx\_ACQUIRE register for accessing the common peripheral after CPU\_A has acquired the IPC channel structure lock.

- **4.** CPU\_B reads "0" from the IPC\_STRUCTx\_ACQUIRE register. This indicates that CPU\_B cannot acquire the IPC channel structure lock.

- 5. CPU\_A reads and writes to the common peripheral.

- 6. CPU\_B, which could not acquire the IPC channel structure lock, is not allowed to access the common peripheral.

- 7. CPU\_A releases the IPC channel structure lock by writing to the IPC\_STRUCTx\_RELEASE register when the write to the common peripheral is complete. If the IPC interrupt structure is set to generate a release interrupt by the IPC\_STRUCTx\_RELEASE register write, the IPC interrupt structure notifies the release interrupt to CPU\_B.

- *Note:* IPC has no hardware to restrict resource access. Therefore, software must have strict rules not to access shared memory if it cannot acquire the lock.

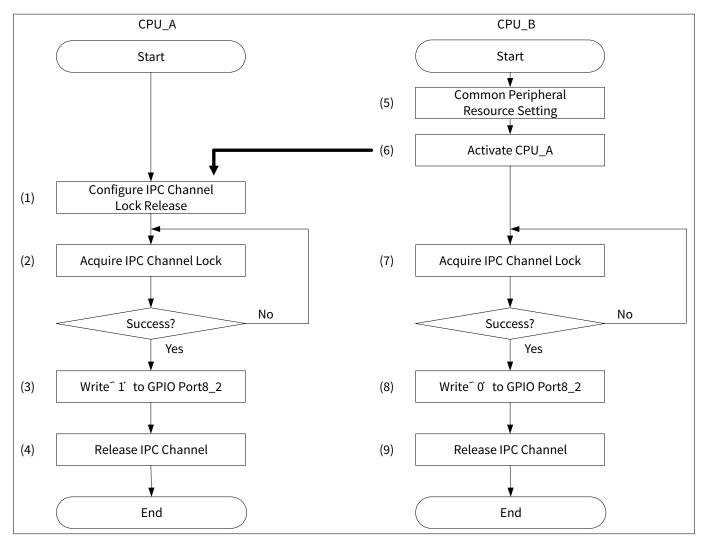

Figure 10 shows the example flow for mutual exclusion.

#### Figure 10 Mutual exclusion flow

The following shows the structure of the sample code.

- IPC channel structure: 6

- Common peripheral: Port8 (2pin)

See the "I/O System" chapter in the architecture TRM and AN220193 - GPIO usage setup in TRAVEO<sup>™</sup> T2G family for GPIO configuration details.

# 5.2.3 Configuration

Table 7 and Table 8 list the parameters and functions in the SDL for mutual exclusion using IPC. This example uses CYT2B series. In this case, it is assumed that CPU\_A is CM4 and CPU\_B is CM0+.

| Table 7 | Configuration parameters for mutual exclusion |

|---------|-----------------------------------------------|

|---------|-----------------------------------------------|

| Parameters         | Description                                   | Value                        |

|--------------------|-----------------------------------------------|------------------------------|

| IPC_CHANNEL_NUMBER | Define using the IPC channel structure number | 6ul (IPC6 channel structure) |

| CY_CB_LED_PORT     | Define the I/O port number                    | GPIO_PRT8                    |

|                    |                                               | (Assign to port 8)           |

#### (table continues...)

## Table 7 (continued) Configuration parameters for mutual exclusion

| Parameters                 | Description                                                                                                                       | Value                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| CY_CB_LED_PIN              | Define the I/O pin                                                                                                                | 2ul                                    |

| CY_IPC_NO_NOTIFICATION     | Defines a value to indicate that no notification events are needed                                                                | 0x000000000000000000000000000000000000 |

| user_led_port_pin_cfg.xxxx | I/O port configuration<br>See AN220193 - GPIO usage setup<br>in TRAVEO <sup>™</sup> T2G family for GPIO<br>configuration details. | -                                      |

## Table 8 Configuration functions for mutual exclusion

| Function                     | Description                                  | Remark |

|------------------------------|----------------------------------------------|--------|

| Cy_IPC_Drv_LockAcquire(base) | Acquire the IPC channel lock.                | -      |

|                              | base: Base address of IPC channel to operate |        |

Code Listing 16 shows an example of mutual exclusion using IPC.

#### Code Listing 16 Example of mutual exclusion for CM4

```

#define IPC_CHANNEL_NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel number */

/* Define port and pin Number */

#define CY CB LED PORT

GPIO PRT8

#define CY_CB_LED_PIN

2ul

/* Define port and pin Number */

#define CY_IPC_NO_NOTIFICATION

(uint32_t)(0x00000000ul)

int main(void)

{

:

/* At first force release the lock state. */

volatile stc_IPC_STRUCT_t* ipcBase = Cy_IPC_Drv_GetIpcBaseAddress(IPC_CHANNEL_NUMBER); /*

Get base address of IPC channel structure. See Code Listing 3. */

(void)Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (1) IPC channel

initialization (Release a lock). See Code Listing 4.*/

/* Lock IPC channnel */

for(;;)

{

if(CY_IPC_DRV_SUCCESS == Cy_IPC_Drv_LockAcquire(ipcBase)) /* Acquire lock of IPC

channel. See Code Listing 17. */

{

/* Set IO port to 1 */

Cy_GPIO_Write(CY_CB_LED_PORT, CY_CB_LED_PIN, 1ul); /* (3) Set IO Port to 1. */

/* Release the lock state */

Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (4) Release IPC

channel without release event. See Code Listing 4. */

break;

}

}

for(;;)

{

}

}

```

#### Code Listing 17 Cy\_IPC\_Drv\_LockAcquire() function

```

cy_en_ipcdrv_status_t Cy_IPC_Drv_LockAcquire (volatile stc_IPC_STRUCT_t const * base)

{

cy_en_ipcdrv_status_t retStatus;

if( 0ul != base->unACQUIRE.stcField.u1SUCCESS ) /* (2) Acquire lock of IPC channel */

{

retStatus = CY_IPC_DRV_SUCCESS;

}

else

{

retStatus = CY_IPC_DRV_ERROR;

}

return(retStatus);

}

```

#### Code Listing 18 Example of mutual exclusion for CM0+

```

#define IPC CHANNEL NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel number */

static cy_stc_gpio_pin_config_t user_led_port_pin_cfg = /* Configure IO Port. */

{

.outVal

= 0ul,

.driveMode = CY_GPI0_DM_STRONG_IN_OFF,

= CY_CB_LED_PIN_MUX,

.hsiom

.intEdge = Oul,

.intMask = Oul,

.vtrip

= 0ul.

.slewRate = Oul,

.driveSel = Oul,

};

int main(void)

{

:

/* Initialize the port pin for LED */

Cy_GPIO_Pin_Init(CY_CB_LED_PORT, CY_CB_LED_PIN, &user_led_port_pin_cfg); /* (5) Initialize

IO Port. */

/* Enable application core CM4.

* CY_CORTEX_M4_APPL_ADDR must be updated if CM4 memory layout is changed.

*/

Cy_SysEnableApplCore(CY CORTEX M4 APPL ADDR); /* (6) Activate CM4 */

volatile stc_IPC_STRUCT_t* ipcBase = Cy_IPC_Drv_GetIpcBaseAddress(IPC_CHANNEL_NUMBER); /*

Get base address of IPC channel structure. See Code Listing 3. */

for(;;)

{

if(CY IPC DRV SUCCESS == Cy_IPC_Drv_LockAcquire(ipcBase)) /* (7) Acquire lock of IPC

channel. See Code Listing 17. */

{

/* Set IO port to 0 */ /* (8) Set IO Port to 0. */

Cy_GPI0_Write(CY_CB_LED_PORT, CY_CB_LED_PIN, 0ul);

/* Release the lock state */

Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (9) Release IPC

channel without release event. See Code Listing 4. */

break;

}

}

for(;;)

{

```

}

# 5.3 Data passing

This section describes how to pass data between CPUs using IPC. In a multi-CPU architecture, each CPU may pass a message to the other CPUs. In this case, IPC can be used.

# 5.3.1 Implementation example of passing small data (up to 64 bits)

This section describes passing data of 64 bits or less. If the message data is 64 bits or less, IPC\_STRUCTx\_DATA0/1 can be used for data passing. IPC\_STRUCTx\_DATA0/1 has two 32-bit registers. A message of up to 64 bits can be written to these registers to be sent to other CPUs.

# 5.3.2 Use case

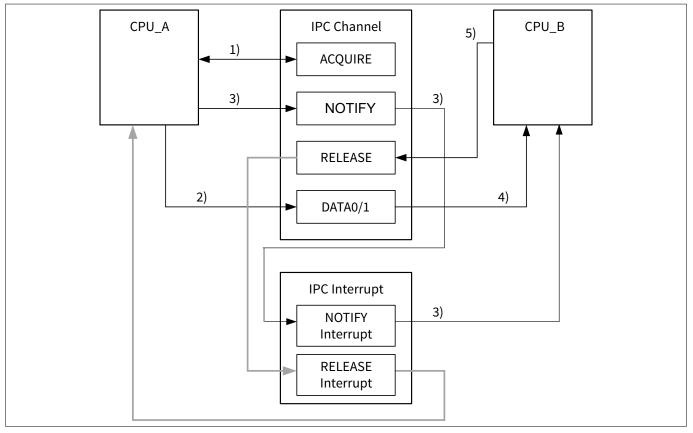

Figure 11 shows an implementation example of small message communication using IPC. In this example, CPU\_A passes the message to CPU\_B.

#### Figure 11 Example of passing a small message

The following shows an example of passing data up to 64 bits:

- 1. CPU\_A reads the IPC\_STRUCTx\_ACQUIRE register. When CPU\_A reads "1" from the IPC\_STRUCTx\_ACQUIRE register, CPU\_A is successful in acquiring the IPC channel structure lock.

- 2. After the IPC channel structure is locked, CPU\_A places the message data up to 64 bits in the IPC\_STRUCTx\_DATA0/1 registers.

- **3.** Now that the message is placed in the IPC channel, CPU\_A generates a notify event to CPU\_B by setting the corresponding bit in the IPC\_STRUCTx\_NOTIFY register.

- **4.** When CPU\_B accepts the notify interrupt, CPU\_B can read the IPC\_INTR\_STRUCTx\_INTR\_MASKED register to know which IPC channel triggered the notify event. Based on this, CPU\_B identifies the channel to read and reads from the IPC\_STRUCTx\_DATA0/1 registers.

- 5. After receiving the message, CPU\_B releases the IPC channel structure so that other processors/ processes can use it. It also optionally generates a release event to CPU\_A. This will generate a release event interrupt to CPU\_A, when the corresponding bit of IPC\_INTR\_STRUCTx\_INTR\_MASK was not masked.

- *Note:* IPC has no hardware to restrict resource access. Therefore, CPU\_B software must have strict rules not to access IPC\_STRUCTx\_DATA0/1 if it does not receive notify interrupt.

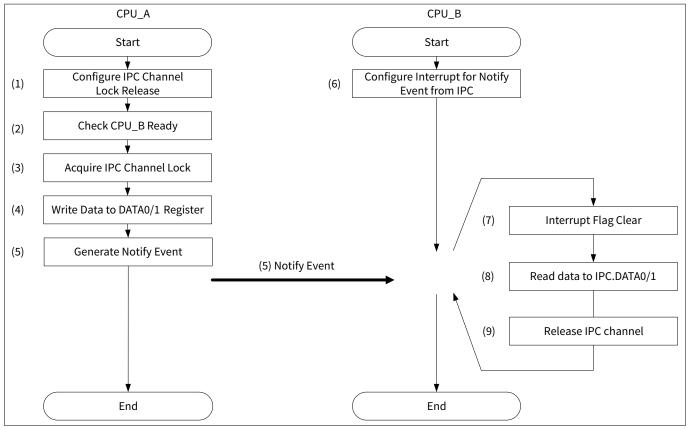

Figure 12 shows the example flow for data passing (up to 64 bit).

Figure 12 Data passing (up to 64 bits) flow

The following shows the structure of the sample code.

- IPC channel structure: 6

- IPC interrupt structure: 5

See the "Interrupts" chapter in the architecture TRM and AN219842 - How to use interrupt in TRAVEO<sup>™</sup> T2G for interrupt configuration details.

# 5.3.3 Configuration

Table 9 and Table 10 list the parameters and functions in the SDL for data passing of 64 bits or less using IPC. This example uses CYT2B series. In this case, it is assumed that CPU\_A is CM4 and CPU\_B is CM0+.

| Parameters             | Description                                                                | Value                                  |

|------------------------|----------------------------------------------------------------------------|----------------------------------------|

| IPC_NOTIFY_INT_NUMBER  | Define using the IPC interrupt<br>structure number for the notify<br>event | 5ul (IPC5 interrupt structure)         |

| IPC_CHANNEL_NUMBER     | Define using the IPC channel structure number                              | 6ul (IPC6 channel structure)           |

| IPC_DATA               | Define passing data 0                                                      | 0x5A5A5A5Aul                           |

| IPC_DATA2              | Define passing data 1                                                      | 0x12345678ul                           |

| CY_IPC_NO_NOTIFICATION | Defines a value to indicate that no notification events are needed         | 0x000000000000000000000000000000000000 |

# Table 9Configuration parameters

# Table 10Configuration functions

| Functions                                                             | Description                                             | Remarks                                                      |

|-----------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|

| Cy_IPC_Drv_SendMsgWord_2(base,<br>notifyEventIntr, message, message2) | Set the DATA0/1 register of the IPC channel structure.  | It has function of acquire lock and notify event generation. |

|                                                                       | base: Base address of the IPC channel to operate        |                                                              |

|                                                                       | notifyEventIntr: Value of then<br>notify event setting  |                                                              |

|                                                                       | message: Write data to<br>IPC.DATA0                     |                                                              |

|                                                                       | message2: Write data to<br>IPC.DATA1                    |                                                              |

|                                                                       | Write data to the DATA0 register.                       | -                                                            |

| dataValue)                                                            | base: Base address of the IPC channel to operate        |                                                              |

|                                                                       | dataValue: Write data                                   |                                                              |

| Cy_IPC_Drv_WriteData1Value(base,                                      | Write data to the DATA1 register.                       | -                                                            |

| dataValue)                                                            | base: Base address of the IPC channel to operate        |                                                              |

|                                                                       | dataValue: Write data                                   |                                                              |

| Cy_IPC_Drv_ReadMsgWord_2(base, message, message)                      | Read the DATA0/1 register of the IPC channel structure. | -                                                            |

|                                                                       | base: Base address of the IPC channel to operate        |                                                              |

|                                                                       | message: Stored address for IPC.DATA0                   |                                                              |

|                                                                       | message2: Stored address for IPC.DATA0                  |                                                              |

|                                                                       | Read the DATA0 register.                                | -                                                            |

|                                                                       | base: Base address of the IPC channel to operate        |                                                              |

#### (table continues...)

# Table 10 (continued) Configuration functions

| Functions                       | Description                                      | Remarks |

|---------------------------------|--------------------------------------------------|---------|

| Cy_IPC_Drv_ReadData1Value(base) | Read the DATA1 register.                         | -       |

|                                 | base: Base address of the IPC channel to operate |         |

Code Listing 19 shows an example of data passing of 64 bits or less using IPC.

#### Code Listing 19 Example of data passing (up to 64 bits) for CM4

```

#define IPC NOTIFY INT NUMBER 5ul /* Notify interrupt number */ /* Define number of IPC

interrupt for notify event. */

#define IPC_CHANNEL_NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel number */

#define IPC_DATA

0x5A5A5A5Aul /* Define send message data */

0x12345678ul /* Define send message data */

#define IPC DATA2

#define CY_IPC_NO_NOTIFICATION

(uint32_t)(0x0000000ul) /* Define Lock release data

without release event */

int main(void)

{

:

/* At first force release the lock state. */ /* Get base address of IPC channel structure.

See Code Listing 3. */

volatile stc_IPC_STRUCT_t* ipcBase = Cy_IPCs_Drv_GetIpcBaseAddress(IPC_CHANNEL_NUMBER);

(void)Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (1) IPC channel

initialization (Release a lock). See Code Listing 4. */

/* Wait until the CMO+ IPC server is started */

/* Note:

* After the CMO+ IPC server is started, the corresponding number of the INTR_MASK is set.

* So in this case CM4 can recognize whether the server has started or not by the INTR_MASK

status.

*/

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER); /* Get base address of IPC interrupt

structure. See Code Listing 5. */

uint32_t intrMask;

uint32_t notifyMask;

do

{

intrMask = Cy_IPC_Drv_GetInterruptMask(ipcIntrStrBase); /* Get value of IPC.INTR_MASK.

See Code Listing 6. */

notifyMask = Cy_IPC_Drv_ExtractAcquireMask(intrMask); /* Get value of notify mask. See

Code Listing 7. */

} while((notifyMask & (1ul << IPC_CHANNEL_NUMBER)) == 0); /* (2) Check if CMO+ ready. */</pre>

/* Send the message to the MO+ through IPC */

Cy_IPC_Drv_SendMsgWord_2(ipcBase, (1ul << IPC_NOTIFY_INT_NUMBER), (uint32_t)IPC_DATA,

(uint32 t)IPC DATA2); /* Write Data to DATA0/1 register. See Code Listing 22. */

```

```

for(;;)

{

}

}

```

#### Code Listing 20 Cy\_IPC\_Drv\_SendMsgWord\_2() function

```

cy_en_ipcdrv_status_t Cy_IPC_Drv_SendMsgWord_2 (volatile stc_IPC_STRUCT_t* base, uint32_t

notifyEventIntr, uint32_t message, uint32_t message2)

{

cy_en_ipcdrv_status_t retStatus;

if( CY_IPC_DRV_SUCCESS == Cy_IPC_Drv_LockAcquire(base) ) /* (3) Acquire lock of IPC

channel. See Code Listing 17. */

{

/* If the channel was acquired, send the message. */

Cy_IPC_Drv_WriteDataValue(base, message); /* Set passing data. See Code Listing 23. */

Cy_IPC_Drv_WriteData1Value(base, message2); /* Set passing data. See Code Listing 23.

*/

Cy_IPC_Drv_AcquireNotify(base, notifyEventIntr); /* (5) Generate notify interrupt. See

Code Listing 8. */

retStatus = CY_IPC_DRV_SUCCESS;

}

else

{

/* Channel was already acquired, return Error */

retStatus = CY IPC DRV ERROR;

}

return(retStatus);

}

```

#### Code Listing 21 Cy\_IPC\_Drv\_WriteDataValue() and Cy\_IPC\_Drv\_WriteData1Value() functions

```

__STATIC_INLINE void Cy_IPC_Drv_WriteDataValue (volatile stc_IPC_STRUCT_t* base, uint32_t

dataValue)

{

base->unDATA0.u32Register = dataValue; /* (4) Set IPC.DATA0 register */

}

__STATIC_INLINE void Cy_IPC_Drv_WriteData1Value (volatile stc_IPC_STRUCT_t* base, uint32_t

dataValue)

{

base->unDATA1.u32Register = dataValue; /*( (4) Set IPC.DATA1 register */

}

```

#### Code Listing 22 Example of data passing (up to 64 bits) for CM0+

```

#define IPC_NOTIFY_INT_NUMBER 5ul /* Notify interrupt number */ /* Define number of IPC

interrupt for notify event. */

#define IPC_CHANNEL_NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel */

/* Configure notify interrupt */

cy_stc_sysint_irq_t irq_cfg =

{

.sysIntSrc = (cy_en_intr_t)(cpuss_interrupts_ipc_0_IRQn + IPC_NOTIFY_INT_NUMBER),

.intIdx

= CPUIntIdx2 IRQn,

.isEnabled = true,

};

/* Configure notify interrupt */

int main(void)

{

:

/* Enable IPC interrupt mask */ /* (6)-1 Enable IPC release event. */

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER);

uint32_t releaseMask = CY_IPC_NO_NOTIFICATION;

uint32_t notifyMask = (1ul << IPC_CHANNEL_NUMBER);</pre>

Cy_IPC_Drv_SetInterruptMask(ipcIntrStrBase, releaseMask, notifyMask);

/* (6)-1 Enable IPC release event. */

/* Interrupt setting */ /* (6)-2 Configure interrupt for IPC notify event */

Cy_SysInt_InitIRQ(&irq_cfg);

Cy_SysInt_SetSystemIrqVector(irq_cfg.sysIntSrc, IpcNotifyInt_ISR);

/* Set the Interrupt Priority & Enable the Interrupt */

NVIC_SetPriority(CPUIntIdx2_IRQn, 0ul);

NVIC_EnableIRQ(CPUIntIdx2_IRQn);

/* (6)-2 Configure interrupt for IPC notify event */

for(;;)

{

}

}

```

#### Code Listing 23 Notify interrupt handler

```

void IpcNotifyInt ISR(void)

{

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER);

= Cy_IPC_Drv_GetInterruptStatusMasked(ipcIntrStrBase);

uint32_t intrMasked

uint32 t releaseMasked = CY IPC NO NOTIFICATION; /* Do not care */

uint32_t notifyMasked = Cy_IPC_Drv_ExtractAcquireMask(intrMasked); /* Get value of notify

mask. See Code Listing 12. */

/* Check if the interrupt is caused by the notifier channel */

if (notifyMasked & (1ul << IPC_CHANNEL_NUMBER)) /* Check if interrupts are valid. */

{

/* Clear the interrupt */

Cy_IPC_Drv_ClearInterrupt(ipcIntrStrBase, releaseMasked, notifyMasked); /* (7) Clear

Interrupt flag. See Code Listing 15. */

/* Read DATA */

uint32_t Data;

uint32_t Data2;

volatile stc_IPC_STRUCT_t* ipcBase = Cy_IPC_Drv_GetIpcBaseAddress(IPC_CHANNEL_NUMBER);

Cy_IPC_Drv_ReadMsgWord_2(ipcBase, &Data, &Data2); /* Read passing data. See Code

Listing 26. */

/* Finally relase the lock */

Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (9) Release the IPC

channel. See Code Listing 4. */

}

}

```

#### Code Listing 24 Cy\_IPC\_Drv\_ReadMsgWord\_2() function

```

cy_en_ipcdrv_status_t Cy_IPC_Drv_ReadMsgWord_2 (volatile stc_IPC_STRUCT_t const * base,

uint32_t * message, uint32_t* message2)

{

cy_en_ipcdrv_status_t retStatus;

if ( Cy_IPC_Drv_IsLockAcquired(base) ) /* Check if the lock is acquired. See Code Listing

9. */

{

/* The channel is locked; message is valid. */

*message = Cy_IPC_Drv_ReadDataValue(base); /* Read passing data. See Code Listing 27.

*/

*message2 = Cy_IPC_Drv_ReadData1Value(base); /* Read passing data. See Code Listing

27. */

retStatus = CY_IPC_DRV_SUCCESS;

}

else

{

/* The channel is not locked so channel is invalid. */

retStatus = CY_IPC_DRV_ERROR;

}

return(retStatus);

}

```

# Code Listing 25 Cy\_IPC\_Drv\_ReadDataValue() and Cy\_IPC\_Drv\_ReadData1Value() function

```

__STATIC_INLINE uint32_t Cy_IPC_Drv_ReadDataValue (volatile stc_IPC_STRUCT_t const * base)

{

return (base->unDATA0.u32Register); /* (8) Read IPC.DATA0 register */

}

__STATIC_INLINE uint32_t Cy_IPC_Drv_ReadData1Value (volatile stc_IPC_STRUCT_t const * base)

{

return (base->unDATA1.u32Register); /* (8) Read IPC.DATA1 register */

}

```

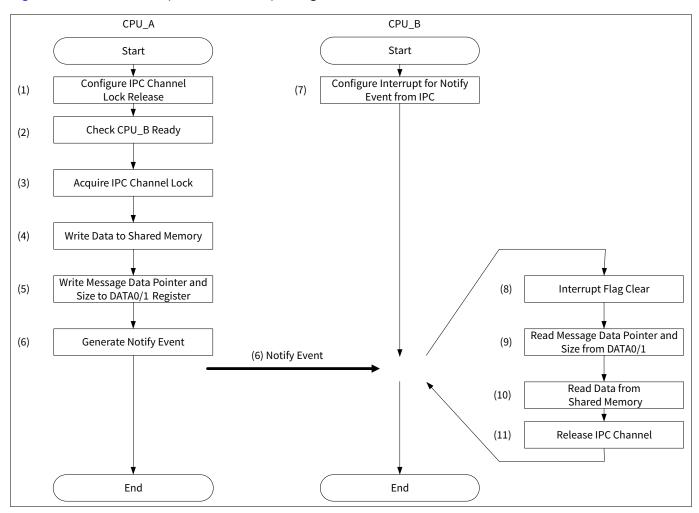

# 5.3.4 Implementation example of passing large data (more than 64 bits)

This section describes passing of a large message. Larger messages can be sent as pointers. CPU\_A can allocate a larger message structure in the shared memory and use the 32-bit IPC\_STRUCTx\_DATA0/1 registers to pass the pointer and size on which the message is placed to CPU\_B.

*Note:* This section describes an implementation example using the shared memory. This case can cause cache coherency issue. See Consideration for cache coherency issue for more details.

# 5.3.5 Use case

Figure 13 shows an implementation example of large message communication using IPC.

# Figure 13 Example of passing a large messageData passing (more than 64 bits) flow

The following shows an example of passing data more than 64 bits:

- **1.** CPU\_A reads the IPC\_STRUCTx\_ACQUIRE register. When CPU\_A reads "1" from the

- IPC\_STRUCTx\_ACQUIRE register, CPU\_A is successful in acquiring the IPC channel structure lock.

- **2.** After the IPC channel structure is locked, CPU\_A places message data in the shared memory.

- **3.** Then, CPU\_A places the message data pointer and size of the shared memory in the IPC\_STRUCTx\_DATA0/1 registers.

- **4.** Now that the message and pointer are placed, CPU\_A generates a notify event to CPU\_B by setting the corresponding bit in the IPC\_STRUCTx\_NOTIFY register.

- **5.** When CPU\_B accepts the notify interrupt, CPU\_B can read the IPC\_INTR\_STRUCTx\_INTR\_MASKED register to know which IPC channel had triggered the notify event. Based on this, CPU\_B identifies the channel to read and reads pointer and size from IPC\_STRUCTx\_DATA0/1 registers.

- 6. CPU\_B reads the message data of the specified size from the address indicated by the pointer.

- 7. After receiving the message, CPU\_B releases the IPC channel structure so that other processors/ processes can use it. It also optionally generates a release event to CPU\_A. This will generate a release

event interrupt to the CPU\_A, when the corresponding bit of IPC\_INTR\_STRUCTx\_INTR\_MASK was not masked.

*Note:* IPC has no hardware to restrict resource access. Therefore, CPU\_A and CPU\_B software must have strict rules not to access IPC\_STRUCTx\_DATA0/1 and message data in shared memory if it does not receive notify interrupt.

Figure 14 shows the example flow for data passing (More than 64 bits).

#### Figure 14

# Data passing (more than 64 bits) flow

The following shows the structure of the sample code.

- IPC channel structure: 6

- IPC interrupt structure: 5

- Shared memory: SRAM

- Data size: 4 word (16 bytes)

# 5.3.6 Configuration

Table 11 lists the parameters and functions in the SDL for data passing of more than 64 bits using IPC. This is example in CYT2B series. In this case, it is assumed that CPU\_A is CM4 and CPU\_B is CM0+.

| Parameters             | Description                                                        | Value                                                        |  |

|------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|--|

| IPC_NOTIFY_INT_NUMBER  | Define using the IPC interrupt structure number for notify event   | 5ul (IPC5 interrupt structure)                               |  |

| IPC_CHANNEL_NUMBER     | Define using the IPC channel structure number                      | 6ul (IPC6 channel structure)                                 |  |

| DATA_SIZE              | Define the passing data size                                       | 4ul (4 word)                                                 |  |

| sharedData[]           | Shared memory area on the SRAM -                                   |                                                              |  |

| ipc_data[]             | Passing data                                                       | 0x12345678ul, 0x87654321ul,<br>0x12345678ul,<br>0x87654321ul |  |

| CY_IPC_NO_NOTIFICATION | Defines a value to indicate that no notification events are needed | 0x000000000000000000000000000000000000                       |  |

#### Table 11Configuration parameters

Code Listing 26 shows an example of data passing of more than 64 bits using IPC.

#### Code Listing 26 Example of data passing (more than 64 bits) for CM4

```

#define IPC NOTIFY INT NUMBER 5ul /* Notify interrupt number */ /* Define number of IPC

interrupt for notify event. */

#define IPC_CHANNEL_NUMBER

6ul /* IPC number which is used in this example */ /* Define

IPC channel */

#define DATA_SIZE

4ul /* Word */ /* Define passing data size */

/* Use shared memory(.bss_share) defined in the "linker_directives.ld" file */

#pragma ghs section bss=".bss_share"

uint32_t sharedData[DATA_SIZE]; /* Shared area reserved on SRAM. */

#pragma ghs section bss=default

uint32 t ipc data[DATA SIZE] = {0x12345678ul, 0x87654321ul, 0x12345678ul, 0x87654321ul}; /*

Define passing data */

#define CY_IPC_NO_NOTIFICATION

(uint32_t)(0x00000000ul)

int main(void)

{

•

/* At first force release the lock state. */

volatile stc IPC STRUCT t* ipcBase = Cy IPC Drv GetIpcBaseAddress(IPC CHANNEL NUMBER); /*

Get base address of IPC channel structure. See Code Listing 3. */

(void)Cy_IPC_Drv_LockRelease(ipcBase, CY_IPC_NO_NOTIFICATION); /* (1) IPC channel

initialization (Release a lock). See Code Listing 4. */

/* Wait until the CMO+ IPC server is started */

/* Note:

* After the CMO+ IPC server is started, the corresponding number of the INTR_MASK is set.

* So in this case CM4 can recognize whether the server has started or not by the INTR_MASK

status.

*/

volatile stc_IPC_INTR_STRUCT_t* ipcIntrStrBase =

Cy_IPC_Drv_GetIntrBaseAddr(IPC_NOTIFY_INT_NUMBER); /* Get base address of IPC interrupt

structure. See Code Listing 5. */

uint32_t intrMask;

uint32_t notifyMask;

do

{

intrMask = Cy_IPC_Drv_GetInterruptMask(ipcIntrStrBase); /* Get value of IPC.INTR_MASK.

See Code Listing 6. */

notifyMask = Cy_IPC_Drv_ExtractAcquireMask(intrMask); /* Get value of notify mask. See

Code Listing 7. */

} while((notifyMask & (1ul << IPC_CHANNEL_NUMBER)) == 0); /* (2) Check if CMO+ ready. */</pre>

```

```

if(CY_IPC_DRV_SUCCESS == Cy_IPC_Drv_LockAcquire(ipcBase)) /* (3) Acquire lock of IPC

channel. See Code Listing 17. */

{

/* Write to Shared momory */

for(uint32_t i = @ul; i < DATA_SIZE; i++ )</pre>

{

sharedData[i] = ipc_data[i]; /* (4) Write a message to the shared area on SRAM. */

}

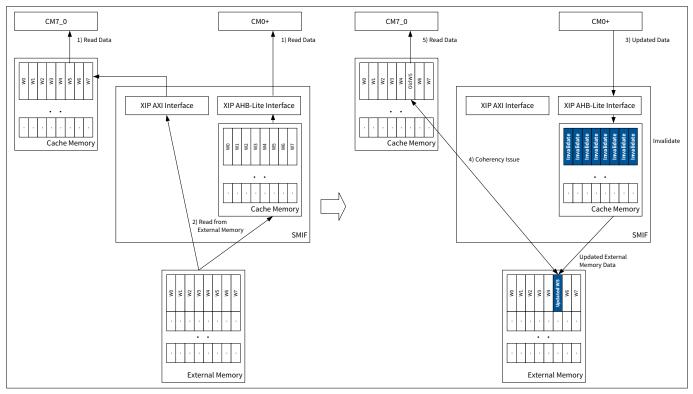

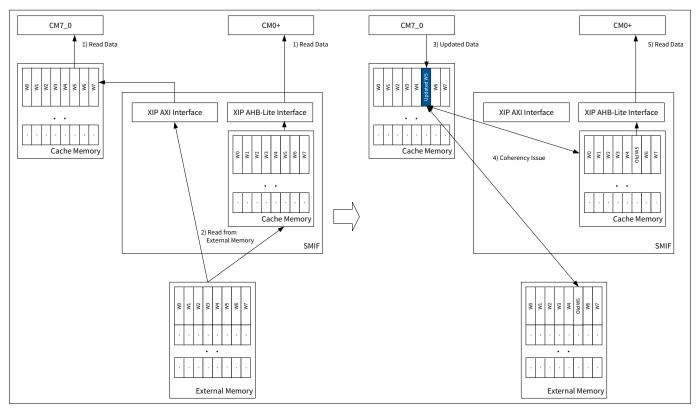

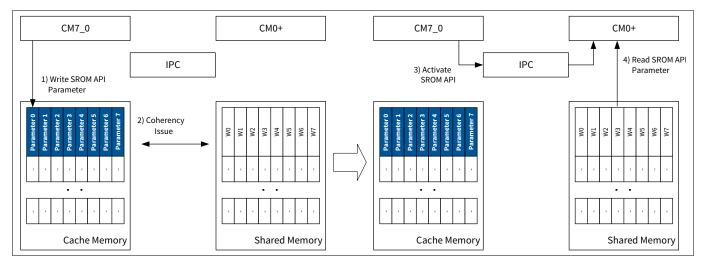

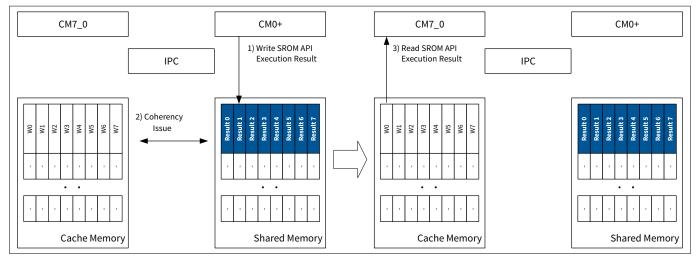

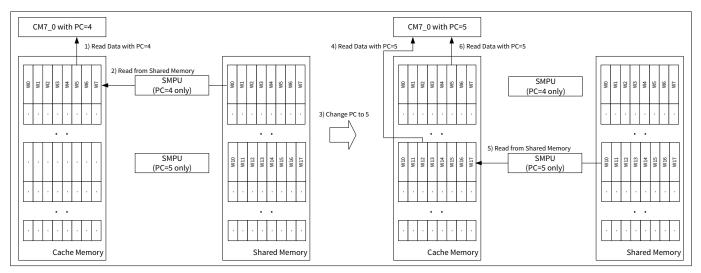

/* Send message */