### About this document

#### **Associated Part Family**

CYPD212x, CYPD3125, CYPD4x25, CYPD5x25, CYPD5126, CYPD612X, CYPD622X

#### Scope and purpose

AN210403 provides hardware design and PCB layout guidelines for designing a Dual Role Power (DRP) application (for example, a notebook with a Type-C port) using EZ-PD<sup>™</sup> CCG2, CCG3, CCG4, CCG5, CCG5C, CCG6, CCG6F, CCG6SF, and CCG6DF USB Type-C controllers. The application note also demonstrates DRP application examples using Cypress evaluation kits as reference.]

#### Abbreviations

| bus, an Arm <sup>®</sup> data |

|-------------------------------|

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

| Abbreviation     | Description                                         |                   |

|------------------|-----------------------------------------------------|-------------------|

| DC               | direct current                                      |                   |

| DFP              | Downstream Facing Port                              |                   |

| DI               | digital or data input                               |                   |

| DMA              | direct memory access                                |                   |

| DNL              | differential nonlinearity                           |                   |

| DO               | digital or data output                              |                   |

| DRP              | Dual Role Power                                     |                   |

| DSI              | digital signal interface                            |                   |

| DSM              | deep-sleep mode                                     |                   |

| ECO              | external crystal oscillator                         |                   |

| EEPROM           | electrically erasable programmable read only memory |                   |

| EMCA             | Electronically Marked Cable Assembly                |                   |

| EMIF             | external memory interface                           |                   |

| FB               | Feedback                                            |                   |

| FIFO             | first in first out                                  |                   |

| FSR              | full scale range                                    |                   |

| GPIO             | general purpose I/O                                 |                   |

| НСІ              | host-controller interface                           |                   |

| HFCLK            | high-frequency clock                                |                   |

| I <sup>2</sup> C | inter-integrated circuit                            |                   |

| IDE              | integrated development environment                  |                   |

| ILO              | internal low-speed oscillator                       |                   |

| ІМО              | internal main oscillator                            |                   |

| INL              | integral nonlinearity                               |                   |

| I/O              | input/output                                        |                   |

| IOR              | I/O read                                            |                   |

| IOW              | I/O write                                           |                   |

| IRES             | initial power on reset                              |                   |

| IRA              | interrupt request acknowledge                       |                   |

| IRQ              | interrupt request                                   |                   |

| ISR              | interrupt service routine                           |                   |

| IVR              | interrupt vector read                               |                   |

| LRb              | last received bit                                   |                   |

| LRB              | last received byte                                  |                   |

| LSb              | least significant bit                               |                   |

| LSB              | least significant byte                              |                   |

| LUT              | lookup table                                        |                   |

| MISO             | master-in-slave-out                                 |                   |

| MMIO             | memory mapped input/output                          |                   |

| MOSI             | master-out-slave-in                                 |                   |

| Application Note | 2 of 98                                             | 002-10403 Rev. *G |

| Abbreviation     | Description                           |

|------------------|---------------------------------------|

| MSb              | most significant bit                  |

| MSB              | most significant byte                 |

| PC               | program counter                       |

| РСН              | program counter high                  |

| PCL              | program counter low                   |

| PD               | power down                            |

| PGA              | programmable gain amplifier           |

| PM               | power management                      |

| РМА              | CCG4 memory arbiter                   |

| POR              | power-on reset                        |

| PPOR             | precision power-on reset              |

| PRS              | pseudo random sequence                |

| PSRR             | power supply rejection ratio          |

| PSSDC            | power system sleep duty cycle         |

| PWM              | pulse width modulator                 |

| RAM              | random-access memory                  |

| RCP              | Reverse Current Protection            |

| RETI             | return from interrupt                 |

| RF               | radio frequency                       |

| ROM              | read only memory                      |

| RW               | read/write                            |

| SAR              | successive approximation register     |

| SC               | switched capacitor                    |

| SCB              | serial communication block            |

| SCP              | Short Circuit Protection              |

| SIE              | serial interface engine               |

| SIO              | special I/O                           |

| SE0              | single-ended zero                     |

| SNR              | signal-to-noise ratio                 |

| SOF              | start of frame                        |

| SOI              | start of instruction                  |

| SOP              | Start of Packet                       |

| SP               | stack pointer                         |

| SPD              | sequential phase detector             |

| SPI              | serial peripheral interconnect        |

| SPIM             | serial peripheral interconnect master |

| SPIS             | serial peripheral interconnect slave  |

| SRAM             | static random-access memory           |

| SROM             | supervisory read only memory          |

| SSADC            | single slope ADC                      |

| Application Note | 2 of 09 002 10402 Pov *C              |

| Description                                 |

|---------------------------------------------|

| supervisory system call                     |

| system clock                                |

| serial wire debug                           |

| terminal count                              |

| transaction descriptors                     |

| True Random Number Generator                |

| universal asynchronous receiver/transmitter |

| Upstream Facing Port                        |

| universal serial bus                        |

| USB I/O                                     |

| USB Power Delivery                          |

| watch crystal oscillator                    |

| watchdog timer                              |

| watchdog reset                              |

|                                             |

Table of contents

### Table of contents

| Abou  | t this document                                            | . 1 |

|-------|------------------------------------------------------------|-----|

| Table | of contents                                                | . 5 |

| 1     | Introduction                                               | . 8 |

| 2     | USB Power Delivery Specification                           | 12  |

| 2.1   | Type-C Signal Definition                                   |     |

| 2.2   | Type-C Ports                                               |     |

| 2.2.1 | Downstream Facing Port and Upstream Facing Port            |     |

| 2.2.2 | USB PD Dual Role Power                                     |     |

| 3     | CCGx Devices Overview                                      | 16  |

| 3.1   | Type-C PD Controller Power Subsystem                       |     |

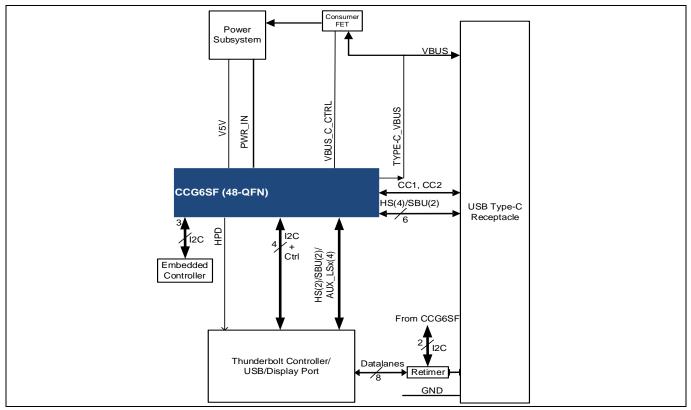

| 4     | Single Type-C Port DRP Application using CCG6SF controller | 20  |

| 4.1   | Power Supply Design                                        |     |

| 4.1.1 | Reset and Clock                                            |     |

| 4.1.2 | Noise Suppression of Supply Voltages                       | 21  |

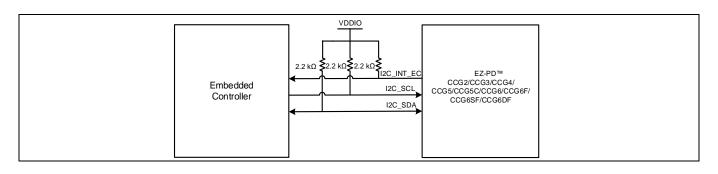

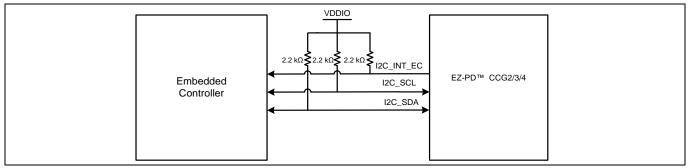

| 4.2   | I <sup>2</sup> C Communication with Embedded Controller    |     |

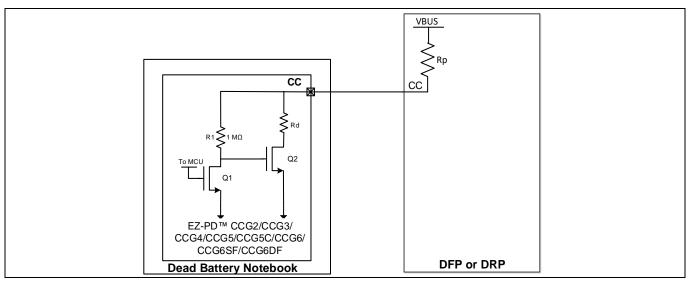

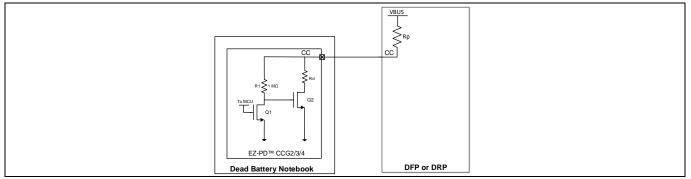

| 4.3   | Dead Battery Charging                                      |     |

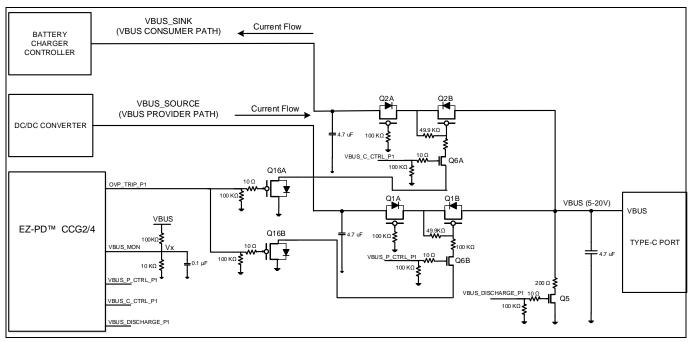

| 4.4   | Power Provider/Consumer Role                               | 22  |

| 4.4.1 | Control of VBUS Provider Path and VBUS Consumer Path       | 22  |

| 4.4.2 | Fault Protection Modes                                     | 22  |

| 4.4.3 | Control of VBUS Discharge Path                             | 22  |

| 5     | Dual Type-C Port DRP Application Using CCG6DF              | 23  |

| 5.1   | Power Supply Design                                        | 23  |

| 5.1.1 | Reset and Clock                                            | 24  |

| 5.1.2 | Noise Suppression of Supply Voltages                       | 24  |

| 5.2   | I <sup>2</sup> C Communication with Embedded Controller    | 24  |

| 5.3   | Dead Battery Charging                                      | 24  |

| 5.4   | Power Provider/Consumer Role                               | 25  |

| 5.4.1 | Control of VBUS Provider Path and VBUS Consumer Path       |     |

| 5.4.2 | Fault Protection Modes                                     | 25  |

| 5.4.3 | Control of VBUS Discharge Path                             | 25  |

| 6     | Single Type-C Port DRP Application using CCG6 and CCG6F    | 26  |

| 6.1   | Electrical Design Considerations                           | 27  |

| 6.2   | Power Supply Design                                        | 27  |

| 6.2.1 | Reset and Clock                                            |     |

| 6.2.2 | Noise Suppression of Supply Voltages                       |     |

| 6.3   | I <sup>2</sup> C Communication with Embedded Controller    | 28  |

| 6.4   | Dead Battery Charging                                      |     |

| 6.5   | Power Provider/Consumer Role                               |     |

| 6.5.1 | Control of VBUS Provider Path and VBUS Consumer Path       |     |

| 6.5.2 | Reverse Current Protection and Short Circuit Protection    |     |

| 6.5.3 | Control of VBUS Discharge Path                             |     |

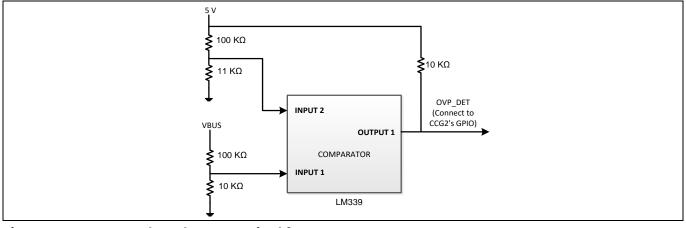

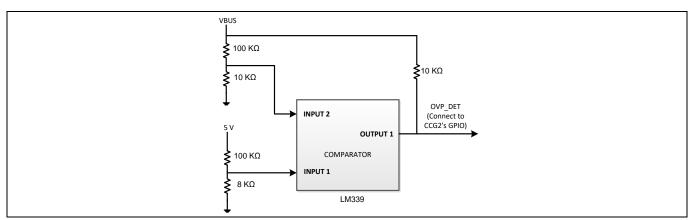

| 6.5.4 | Overvoltage Protection (OVP) for VBUS                      |     |

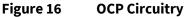

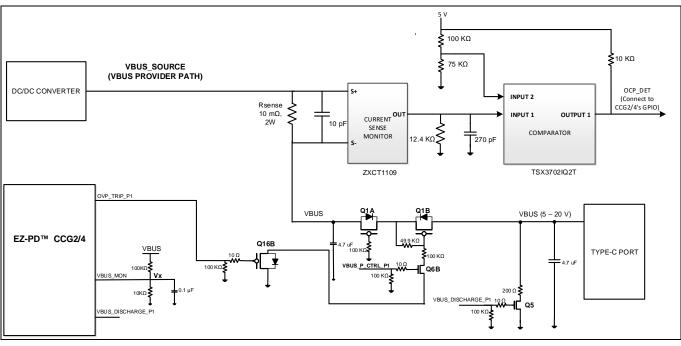

| 6.5.5 | Overcurrent Protection (OCP) for VBUS                      |     |

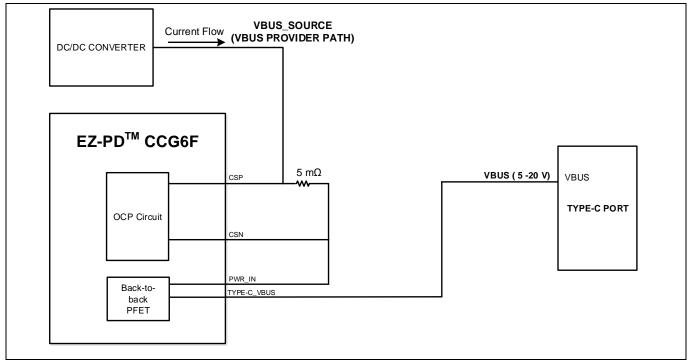

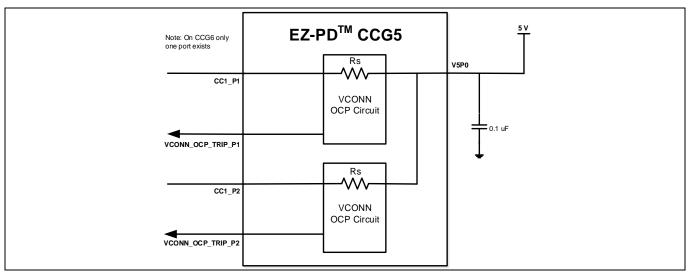

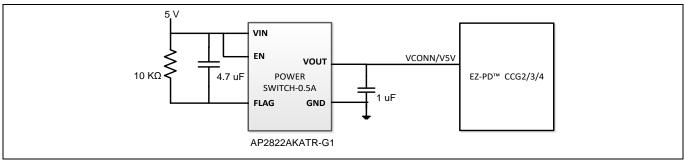

| 6.5.6 | Overcurrent Protection (OCP) for VCONN                     |     |

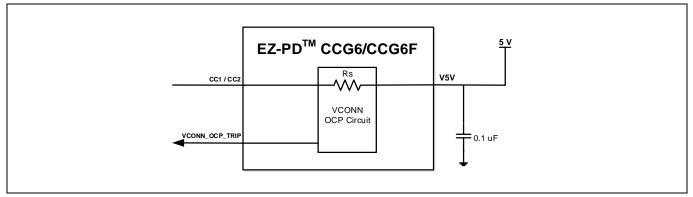

| 7     | Single Type-C Port DRP Application Using CCG5C             |     |

| 7.1   | Power Supply Design                                        |     |

| 7.1.1 | Reset and Clock                                            | 36  |

|       |                                                            |     |

#### Table of contents

| 7.1.2             | Noise Suppression of Supply Voltages                            |                   |

|-------------------|-----------------------------------------------------------------|-------------------|

| 7.2               | I <sup>2</sup> C Communication with Embedded Controller         |                   |

| 7.3               | Dead Battery Charging                                           |                   |

| 7.4               | Power Provider/Consumer Role                                    |                   |

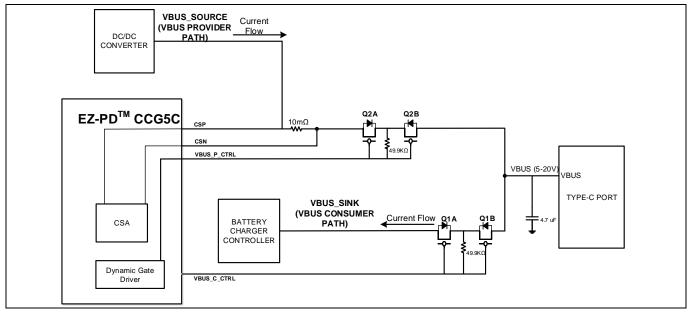

| 7.4.1             | Control of VBUS Provider Path and VBUS Consumer Path            |                   |

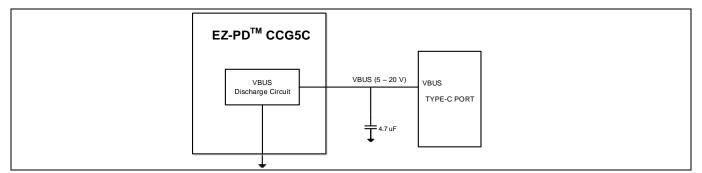

| 7.4.2             | Control of VBUS Discharge Path                                  |                   |

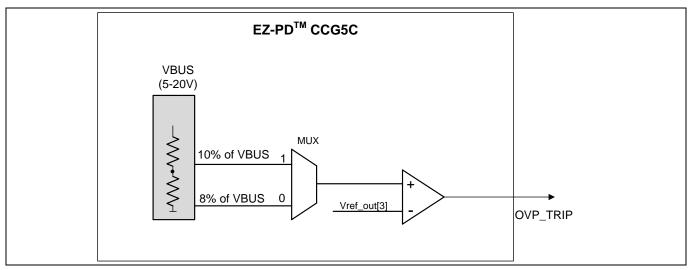

| 7.4.3             | Overvoltage Protection (OVP) for VBUS                           |                   |

| 7.4.4             | Overcurrent Protection (OCP) for VBUS                           |                   |

| 7.4.5             | Overcurrent Protection (OCP) for VCONN                          |                   |

| 8                 | Dual Type-C Port DRP Application Using CCG5                     | 41                |

| 8.1               | Power Supply Design                                             |                   |

| 8.1.1             | Reset and Clock                                                 |                   |

| 8.1.2             | Power supply Noise Suppression                                  |                   |

| 8.2               | I <sup>2</sup> C Communication with Embedded Controller         |                   |

| 8.3               | Dead Battery Charging                                           |                   |

| 8.4               | Power Provider/Consumer Role                                    |                   |

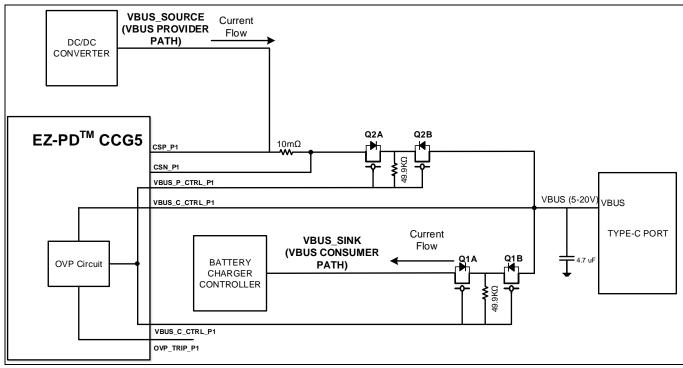

| 8.4.1             | Control of VBUS Provider Path and VBUS Consumer Path            |                   |

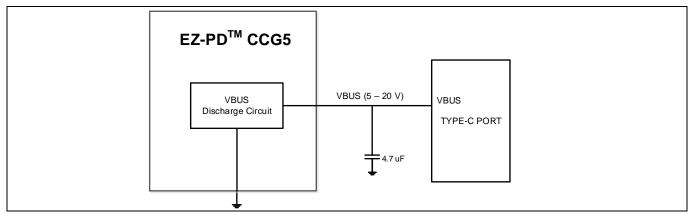

| 8.4.2             | Control of VBUS Discharge Path                                  |                   |

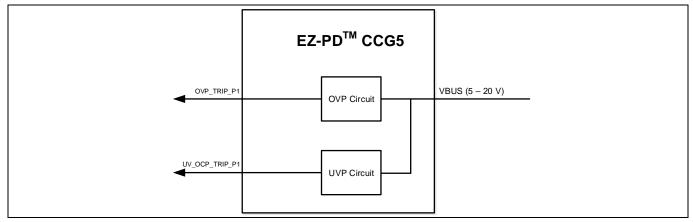

| 8.4.3             | Overvoltage Protection (OVP) for VBUS                           |                   |

| 8.4.4             | Undervoltage Protection (UVP) for VBUS                          |                   |

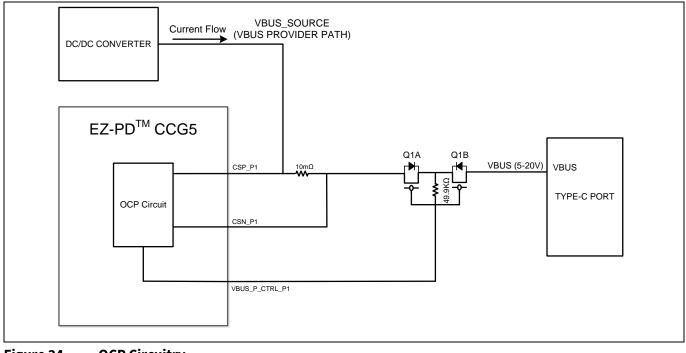

| 8.4.5             | Overcurrent Protection (OCP) for VBUS                           |                   |

| 8.4.6             | Overcurrent Protection (OCP) for VCONN                          |                   |

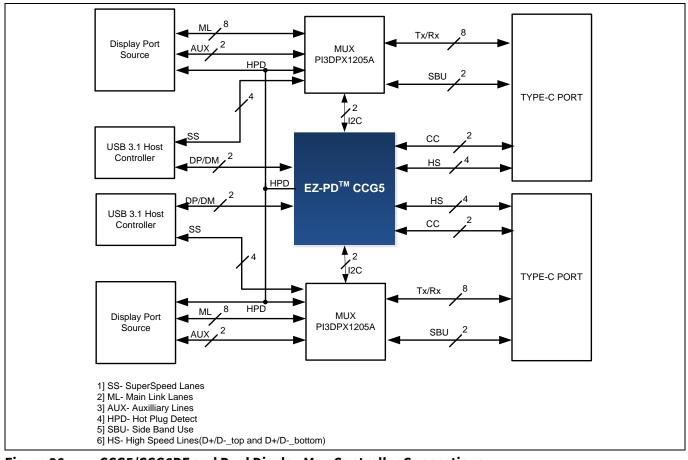

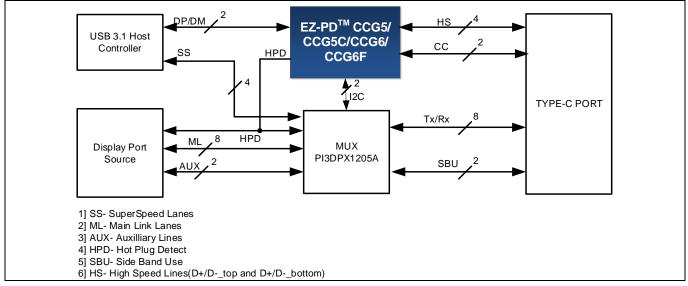

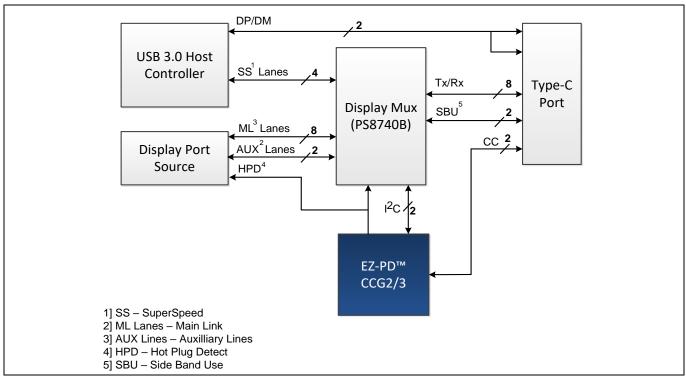

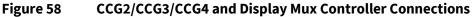

| 8.5               | DisplayPort Connections                                         |                   |

| 8.6               | Electrical Design Considerations                                |                   |

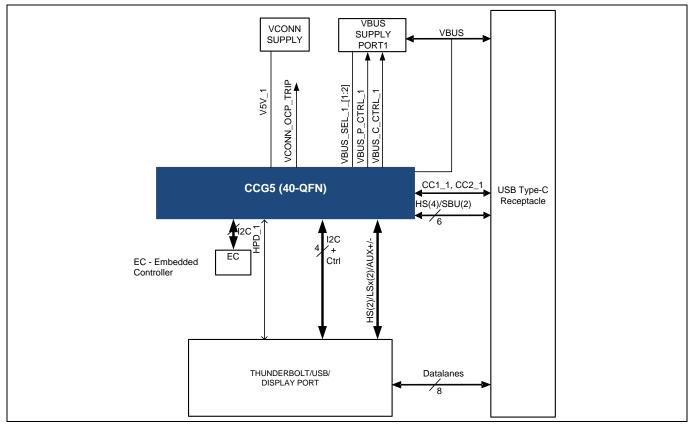

| 9                 | Single Type-C Port DRP Application Using CCG5                   |                   |

| 9.1               | Power Supply Design                                             |                   |

| 9.2               | I <sup>2</sup> C Communication with Embedded Controller         |                   |

| 9.3               | Dead Battery Charging                                           |                   |

| 9.4               | Power Provider/Consumer Role                                    |                   |

| 9.5               | DisplayPort Connections                                         |                   |

| 9.6               | Electrical Design Considerations                                |                   |

|                   | Dual Type-C Port DRP Application Using CCG4                     |                   |

| <b>10</b><br>10.1 |                                                                 |                   |

| 10.1              | Power Supply Design<br>Decoupling Capacitors in Power Subsystem |                   |

| 10.1.1            |                                                                 |                   |

| 10.1.2            | I <sup>2</sup> C Communication with Embedded Controller         |                   |

| 10.2              | Dead Battery Charging                                           |                   |

| 10.5              | Power Provider/Consumer Role                                    |                   |

| 10.4              |                                                                 |                   |

| 10.4.1            |                                                                 |                   |

| 10.4.2            | 6                                                               |                   |

| 10.4.3            |                                                                 |                   |

| 10.4.3            |                                                                 |                   |

| 10.4.4            |                                                                 |                   |

| 10.4.4            |                                                                 |                   |

| 10.4.4            |                                                                 |                   |

| 10.4.5            |                                                                 |                   |

| 10.4.6            |                                                                 |                   |

| 10.4.0            | DisplayPort Connections                                         |                   |

| 10.5              | Electrical Design Considerations                                |                   |

|                   | ition Note 6 of 98                                              | 002-10403 Rev. *G |

| 1.17.1.50         |                                                                 | 2021-03-14        |

### Table of contents

| 11     | Single Type-C Port DRP Application Using CCG4                                        | .72  |

|--------|--------------------------------------------------------------------------------------|------|

| 11.1   | Power Supply Design                                                                  | .73  |

| 11.2   | I <sup>2</sup> C Communication with Embedded Controller                              | .73  |

| 11.3   | Dead Battery Charging                                                                | .73  |

| 11.4   | Power Provider/Consumer Role                                                         | .73  |

| 11.5   | DisplayPort Connections                                                              | .73  |

| 11.6   | Electrical Design Considerations                                                     | .74  |

| 11.7   | Power Supply Design                                                                  |      |

| 11.7.1 | · · · · · · · · · · · · · · · · · · ·                                                |      |

| 11.7.2 |                                                                                      |      |

| 11.8   | I <sup>2</sup> C Communication with Embedded Controller                              | .77  |

| 11.9   | Dead Battery Charging                                                                | .77  |

| 11.10  | Power Provider/Consumer Role                                                         |      |

| 11.10  |                                                                                      |      |

| 11.10  | · · · · · · · · · · · · · · · · · · ·                                                |      |

| 11.10  | 8                                                                                    |      |

| 11.10  |                                                                                      |      |

| 11.10  |                                                                                      |      |

| 11.11  | DisplayPort Connections                                                              |      |

| 11.12  | Electrical Design Considerations                                                     | 79   |

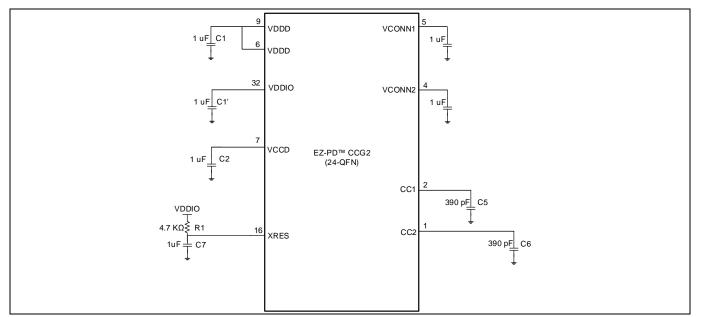

| 12     | Single Type-C Port DRP Application Using CCG2                                        | .80  |

| 12.1   | Power Supply Design                                                                  | .81  |

| 12.1.1 |                                                                                      |      |

| 12.1.2 | Reset and Clock Circuit                                                              | . 82 |

| 12.2   | I <sup>2</sup> C Communication with Embedded Controller                              | .82  |

| 12.3   | Dead Battery Charging                                                                | .82  |

| 12.4   | Power Provider/Consumer Role                                                         | . 82 |

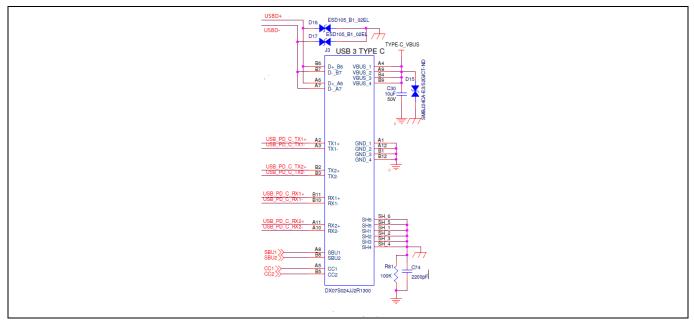

| 12.5   | DisplayPort Connections                                                              | .82  |

| 12.6   | Electrical Design Considerations                                                     | .82  |

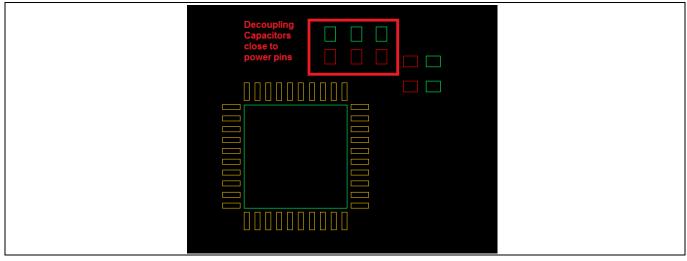

| 13     | Electrical Design Considerations                                                     | .83  |

| 13.1   | ESD and EMI/EMC Protection                                                           | .83  |

| 13.1.1 | Power Domain                                                                         | .83  |

| 13.1.2 | Routing of Type-C (USB Data and CC) Lines                                            | .85  |

| 13.1.3 | Routing of CSP and CSN Lines on CCG5, CCG5C, CCG6, CCG6F, CCG6SF, and CCG6DF Devices | .86  |

| 13.1.4 |                                                                                      |      |

| 13.1.5 | Typical 32-mil, Six-Layer PCB Example for DRP Application                            | .87  |

| 13.1.6 |                                                                                      |      |

| 13.1.7 | 0                                                                                    |      |

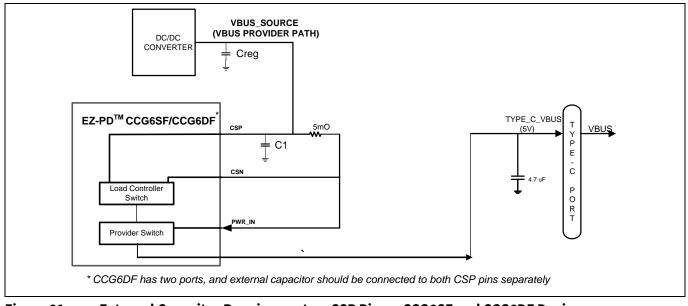

| 13.1.8 | CAP Recommendation on CSP Pin for CCG6F, CCG6SF, and CCG6DF Notebook Designs         | .90  |

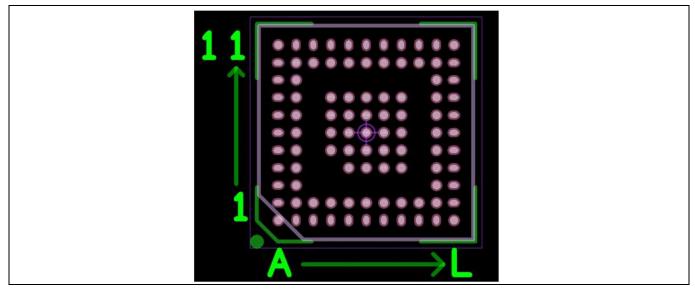

| 14     | Layout Design Guidelines for BGA Packages-CCG6DF                                     | .92  |

| 15     | Schematic and Layout Review Checklist                                                |      |

| 16     | Cypress Design Resources                                                             |      |

| Revis  | ion history                                                                          | .97  |

Introduction

## 1 Introduction

The **USB Power Delivery (PD) Specification Revision 3.0, Version 2.0** defines power delivery up to 100 W (20 V at 5 A) over existing USB standards. The **USB Type-C Cable and Connector Specification Revision 2.0** details a new reversible and sub-3-mm slim connector design that supports 100 W of power along with USB and non-USB signals such as DisplayPort.

Cypress provides a portfolio of USB Type-C and PD controllers, including EZ-PD CCG1, EZ-PD CCG2, EZ-PD CCG3, EZ-PD CCG4, EZ-PD CCG5, EZ-PD CCG5C, EZ-PD CCG6, EZ-PD CCG6F, EZ-PD CCG6SF, and CCG6DF.

CCG1 is Cypress' first-generation Type-C and PD controller, which supports up to two USB ports with PD. CCG1 has 32 KB flash and 4 KB SRAM memory. CCG1 is a fixed-function part and the functionality is implemented in the CCG1 device's firmware. CCG1 provides a USB Type-C and Power Delivery solution for notebooks, monitors, docking stations, power adapters, and USB Type-C cables.

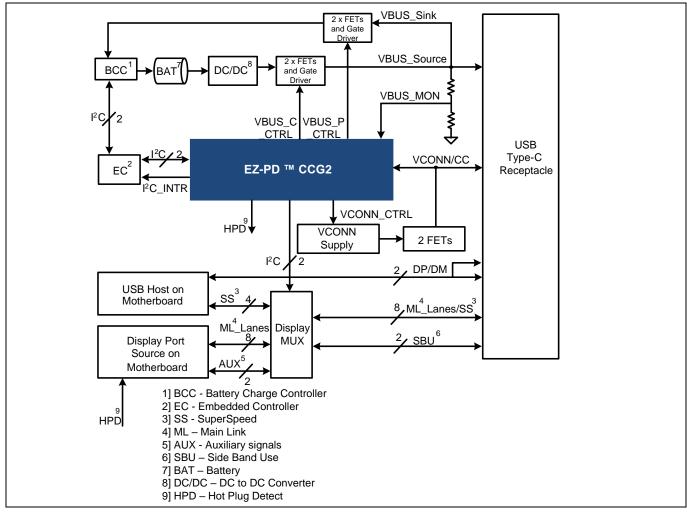

CCG2 is Cypress' second-generation Type-C and PD controller, integrating one Type-C transceiver and termination resistors Rp, Rd, and Ra. CCG2 has 32 KB of flash and 4 KB of SRAM memory. It provides a complete USB Type-C and Power Delivery solution for Type-C notebook and cable designs.

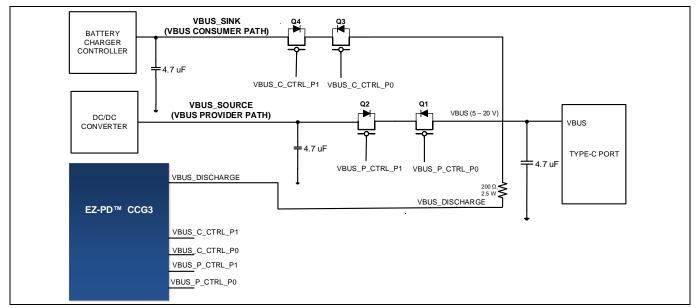

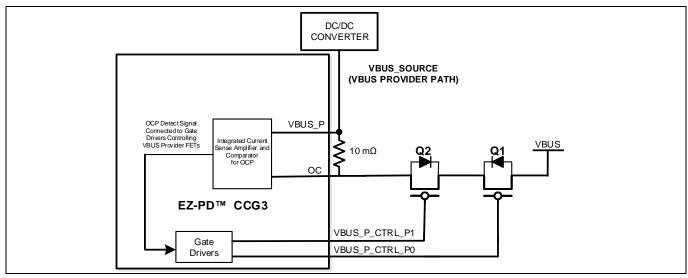

CCG3 is Cypress' third-generation USB Type-C and PD controller, integrating one Type-C transceiver and termination resistors Rp, Rd, and Ra. CCG3 provides additional features such as a crypto engine for authentication, two integrated pairs of gate drivers to control the VBUS provider and consumer path, integrated VCONN and VBUS discharge FETs, integrated overvoltage and overcurrent protection, and USB 2.0 Billboard support. In addition, CCG3 has 128 KB of flash and 8 KB of SRAM memory.

CCG4 is Cypress' fourth-generation Type-C and PD controller, which includes two Type-C transceivers and termination resistors Rp and Rd. CCG4 has integrated VCONN FETs, 128 KB of flash, and 8 KB of SRAM memory. CCG4 provides a complete solution for dual Type-C port notebook and power adapter designs.

CCG5 is Cypress' fifth-generation Type-C and PD controller, which includes two Type-C transceivers and termination resistors Rp and Rd. CCG5 is an enhancement to CCG4 with integrated (Side Band Usage) SBU muxes, HS (High Speed) muxes, 20-V VBUS regulator and High-side current sense amplifier. CC and SBU pins are made high-voltage-tolerant to withstand VBUS to CC line-short faults. CCG5 provides a complete solution for dual Type-C port notebook and dock station designs. CCG5C is enhanced version of CCG5 which supports single port Type-C and PD control. CCG5C is pin-compatible to the CCG5 controller 40-pin QFN package.

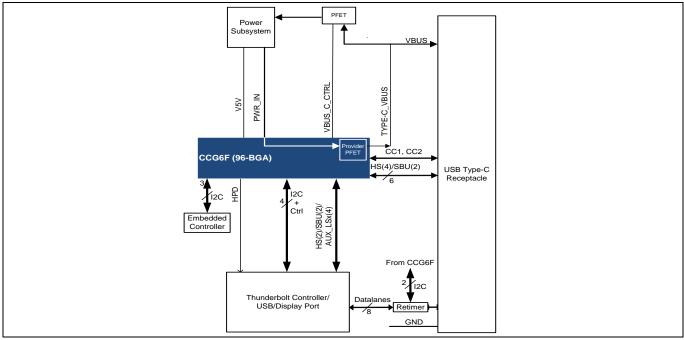

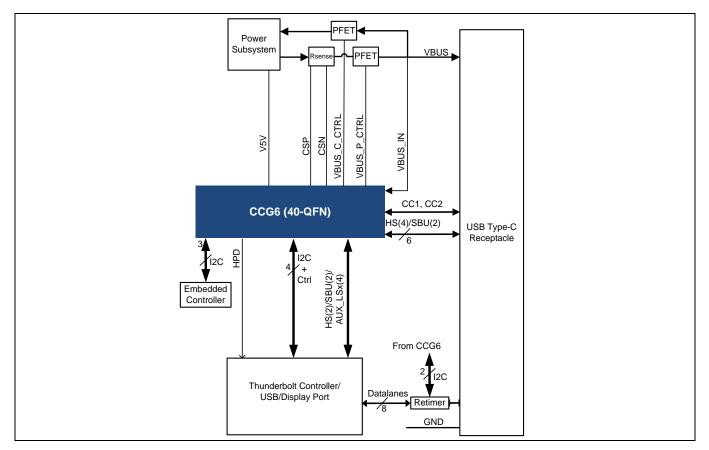

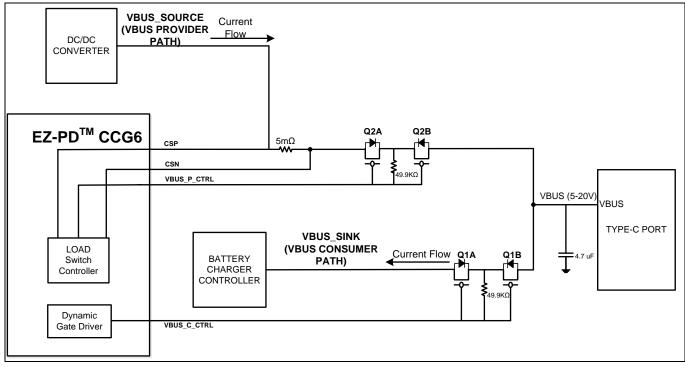

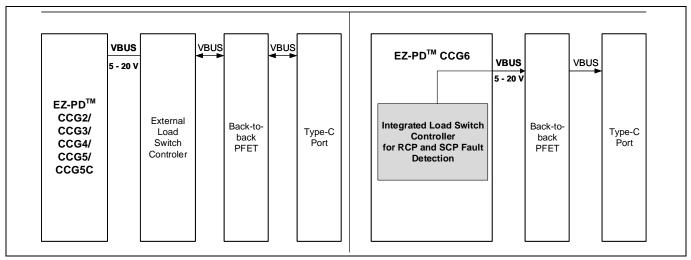

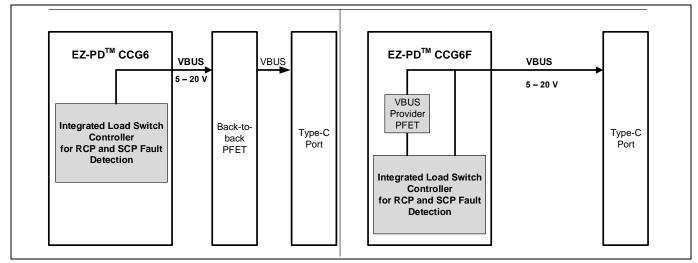

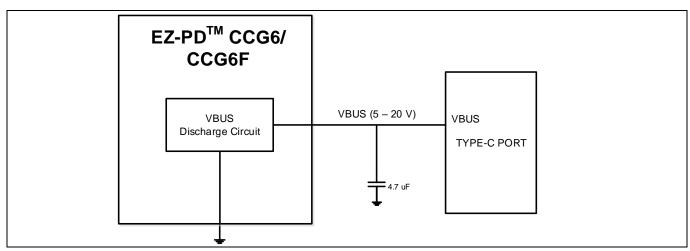

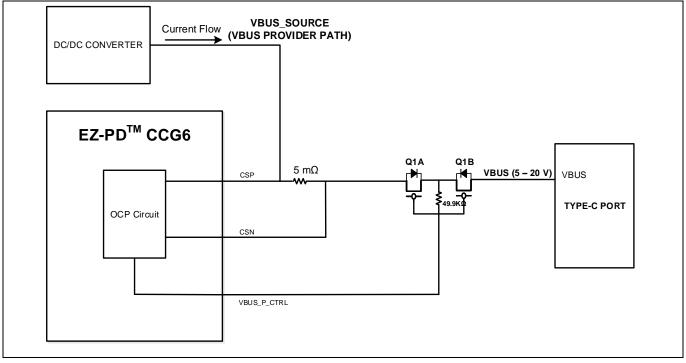

CCG6 is Cypress' sixth-generation Type-C and PD controller, which includes a single Type-C transceiver and termination resistors Rp and Rd. CCG6 has an integrated Load Switch Controller in the VBUS provider path, which can protect the system from reverse current and short circuit faults. CCG6 also supports true random number generator for firmware authentication. CCG6F is an enhancement of CCG6 as it has an integrated PFET in the VBUS provider path. CCG6F controller supports Thermal Shutdown.

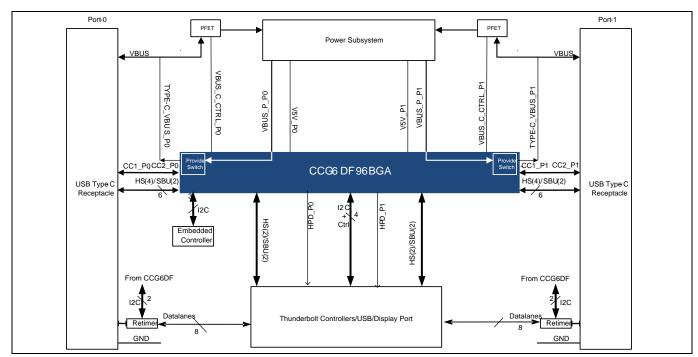

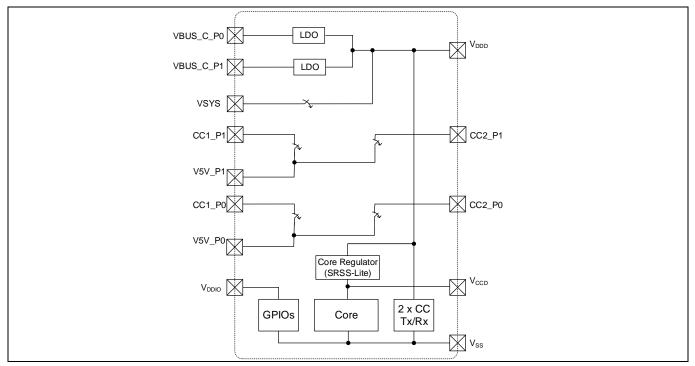

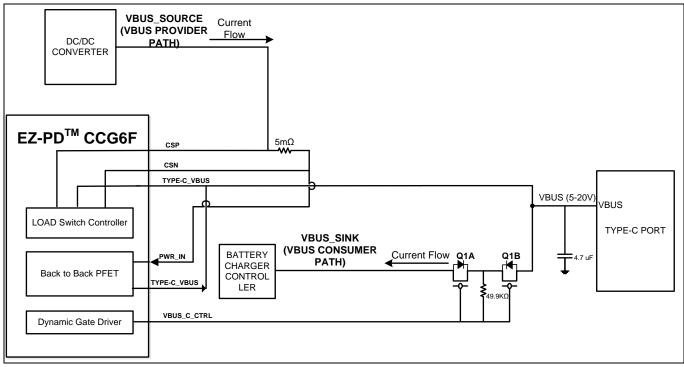

CCG6DF and CCG6SF are Cypress' sixth-generation Type-C and PD controllers for Thunderbolt and Non-Thunderbolt platforms. CCG6DF includes two Type-C transceivers and termination resistors Rp and Rd while CCG6SF includes a single Type-C transceiver and termination resistors Rp and Rd. CCG6DF and CCG6SF have been enhanced from CCG6 by including the VBUS provider path load switch (5 V/3 A) on each port, which will reduce the system Bill-of-Material (BOM) cost. CCG6SF and CCG6DF controllers support Thermal Shutdown.

These Type-C and PD controllers are fully compliant with the USB PD and Type-C standards. **Table 1** summarizes the differences among them.

## Introduction

| Features                                                                                                         | CCG1           | CCG2                | CCG3                | CCG4             | CCG5/5C                                                                   | CCG6/<br>CCG6F      | CCG6SF/<br>CCG6DF                  |

|------------------------------------------------------------------------------------------------------------------|----------------|---------------------|---------------------|------------------|---------------------------------------------------------------------------|---------------------|------------------------------------|

| Number of Type-C and<br>PD Ports                                                                                 | 1              | 1                   | 1                   | 2                | 2/1                                                                       | 1                   | 1/2                                |

| Integrated Arm <sup>®</sup> Cortex <sup>®</sup> -<br>M0 MCU at 48 MHz                                            | Yes            | Yes                 | Yes                 | Yes              | Yes                                                                       | Yes                 | Yes                                |

| Memory (Flash, SRAM)                                                                                             | 32 KB, 4<br>KB | 32 KB, 4 KB         | 128 KB, 8<br>KB     | 128 KB,<br>8 KB  | 128 KB,<br>12 KB                                                          | 128<br>KB, 12<br>KB | 64 KB, 16<br>KB                    |

| Integrated Type-C<br>Transceiver (Number)                                                                        | Yes (1)        | Yes (1)             | Yes (1)             | Yes (2)          | Yes (2) / Yes<br>(1)                                                      | Yes (1)             | Yes (1) /<br>Yes (2)               |

| Integrated Type-C<br>Resistors                                                                                   | No             | Yes (Ra, Rp,<br>Rd) | Yes (Ra,<br>Rp, Rd) | Yes (Rp,<br>Rd)  | Yes (Rp, Rd)                                                              | Yes<br>(Rp,<br>Rd)  | Yes (Rp,<br>Rd)                    |

| Number of GPIOs                                                                                                  | Up to 30       | Up to 14            | Up to 20            | Up to<br>30      | Up to 38 / Up<br>to 15                                                    | Up to<br>17         | Up to 20 /<br>Up to 23             |

| Number of Serial<br>Communication Blocks<br>(I²C/SPI/UART)                                                       | 1              | 2                   | 4                   | 4                | 4                                                                         | 4                   | 4                                  |

| Number of TCPWM<br>Blocks<br>(Each block can be<br>configured as timer,<br>counter, or pulse width<br>modulator) | 2              | 6                   | 4                   | 4                | 2                                                                         | 2                   | 2                                  |

| Integrated USB<br>Billboard Device Class<br>Full Speed USB 2.0<br>Device                                         | No             | No                  | Yes                 | No               | No                                                                        | No                  | No                                 |

| Hardware<br>Authentication Block<br>(Crypto)                                                                     | No             | No                  | Yes                 | No               | No                                                                        | Yes<br>TRNG<br>only | Yes<br>TRNG<br>only                |

| Integrated VCONN FETs                                                                                            | No             | No                  | Yes (1<br>pair)     | Yes (2<br>pairs) | Yes (2 pairs)/<br>Yes (1 pair)<br>With VCONN<br>Overcurrent<br>Protection | Yes (1<br>pair)     | Yes (1<br>pair) / Yes<br>(2 pairs) |

| Integrated VBUS<br>Discharge FETs                                                                                | No             | No                  | Yes                 | No               | Yes                                                                       | Yes                 | Yes                                |

| Integrated 20-V VBUS<br>NFET/PFET Gate Drivers                                                                   | No             | No                  | Yes (2<br>pairs)    | No               | No                                                                        | No                  | No                                 |

| Integrated SBU/AUX<br>Analog Switch                                                                              | No             | No                  | Yes                 | No               | Yes                                                                       | Yes                 | Yes                                |

Table 1Feature Comparison of Cypress' USB Type-C and PD Controllers

| Features                                                                                                         | CCG1                                                | CCG2                                                                                   | CCG3                                                                                         | CCG4                                                                              | CCG5/5C                                                                                 | CCG6/<br>CCG6F                              | CCG6SF/<br>CCG6DF                       |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|

| Supply Voltage                                                                                                   | 1.8 V –<br>5.5 V                                    | 2.7 V –<br>5.5 V                                                                       | 2.7 V –<br>21.5 V                                                                            | 2.7 V –<br>5.5 V                                                                  | 2.7 V –<br>21.5 V/<br>2.75 V–<br>21.5 V for<br>CCG5C                                    | 2.75 V<br>-<br>21.5 V                       | 2.75 V –<br>21.5 V                      |

| VBUS Overvoltage<br>Protection (OVP),<br>Undervoltage<br>Protection (UVP) and<br>Overcurrent Protection<br>(OCP) | Yes<br>(Using<br>external<br>hardware<br>circuitry) | Yes<br>(Using<br>external<br>hardware<br>circuitry)                                    | Yes<br>(Integrat<br>ed)                                                                      | Yes<br>(Using<br>external<br>hardwa<br>re<br>circuitry<br>)                       | Yes<br>(Integrated)                                                                     | Yes<br>(Integr<br>ated)                     | Yes<br>(Integrat<br>ed)                 |

| Integrated ADCs for<br>OVP, UVP, OCP<br>Detection and Other<br>Voltage or Current<br>Measurements                | 1 channel<br>(12-bit<br>SAR)                        | 1 channel<br>(8-bit SAR)                                                               | 2<br>channels<br>(8-bit<br>SAR)                                                              | 4<br>channel<br>s<br>(8-bit<br>SAR)                                               | 4 channels /<br>1-channel<br>(8-bit SAR)                                                | 1<br>chann<br>el<br>(8-bit<br>SAR)          | 1 channel<br>(8-bit<br>SAR)             |

| Load Switch Controller<br>for RCP and SCP                                                                        | No                                                  | No                                                                                     | No                                                                                           | No                                                                                | No                                                                                      | Yes                                         | Yes                                     |

| Integrated 20 V VBUS<br>PFET                                                                                     | No                                                  | No                                                                                     | No                                                                                           | No                                                                                | No                                                                                      | Includ<br>ed in<br>CCG6F<br>Only            | No                                      |

| Integrated VBUS<br>Provider Switch                                                                               | No                                                  | No                                                                                     | No                                                                                           | No                                                                                | No                                                                                      | Yes<br>(CCG6<br>F only)                     | Yes<br>(5 V/3 A)                        |

| Thermal Shutdown                                                                                                 | No                                                  | No                                                                                     | No                                                                                           | No                                                                                | No                                                                                      | Includ<br>ed in<br>CCCG<br>6F<br>only       | Yes                                     |

| USB Battery Charger<br>(BC) Revision 1.2 and<br>Legacy Apple Charger<br>Detection and<br>Emulation               | No                                                  | No                                                                                     | Yes                                                                                          | No                                                                                | Yes                                                                                     | Yes                                         | Yes                                     |

| ESD Protection                                                                                                   | Yes<br>(Up-to<br>2.2 kV)                            | Yes<br>(Up-to ± 8-<br>kV contact<br>discharge<br>and up-to<br>±15-kV air<br>discharge) | Yes<br>(Up-to ±<br>8-kV<br>contact<br>discharge<br>and up-to<br>±15-kV air<br>discharge<br>) | Yes<br>(Up-to ±<br>8-kV<br>contact<br>dischar<br>ge and<br>up-to<br>±15-kV<br>air | Yes<br>(Up to ± 8-kV<br>contact<br>discharge<br>and up to<br>±15-kV air<br>discharge) / | Yes<br>(Hum<br>an<br>Body<br>Model<br>Only) | Yes<br>(Human<br>Body<br>Model<br>Only) |

#### Introduction

| Features | CCG1                          | CCG2                         | CCG3                          | CCG4           | CCG5/5C                               | CCG6/<br>CCG6F            | CCG6SF/<br>CCG6DF |

|----------|-------------------------------|------------------------------|-------------------------------|----------------|---------------------------------------|---------------------------|-------------------|

|          |                               |                              |                               | dischar<br>ge) | Human Body<br>Model only<br>for CCG5C |                           |                   |

| Packages | 40-QFN,<br>16-SOIC,<br>35-CSP | 24-QFN,<br>14-DFN,<br>20-CSP | 40-QFN,<br>42-CSP,<br>16-SOIC | 40-QFN         | 40-QFN<br>96-BGA/<br>40-QFN           | 40-<br>QFN/<br>96-<br>BGA | 48-QFN<br>96-BGA  |

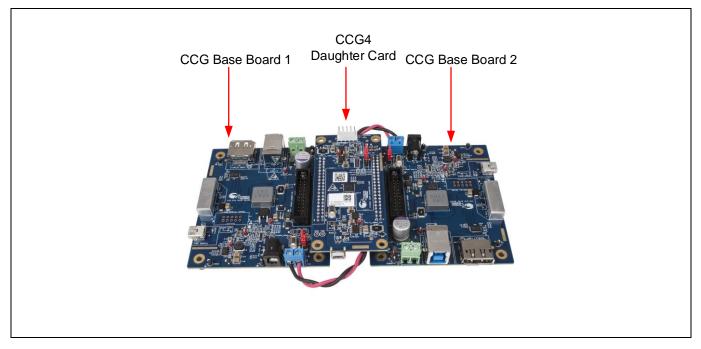

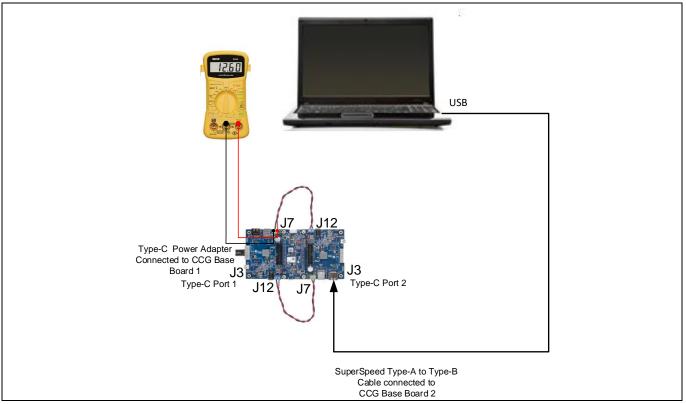

This application note provides information on designing USB Type-C DRP applications using CCG2, CCG3, CCG4 CCG5, CCG5C, CCG6, CCG6F, CCG6SF, and CCG6DF. CCG2, CCG3, CCG4, CCG5, CCG5C, CCG6, CCG6SF, and CCG6DF controllers have more integrated features as compared to CCG1, which help to reduce the BOM cost of DRP application design. See **AN96527 – Designing USB Type-C Products Using Cypress' CCG1 Controllers** for detailed information on USB Type-C designs using CCG1. This application note gives a brief overview of CCG2, CCG3, CCG4, CCG5, CCG5C, CCG6, CCG6SF, and CCG6DF, and explains the power subsystem required to kick start the design. It provides hardware guidelines for a successful notebook design with a single or dual Type-C port using Cypress' Type-C and PD controllers. The application note provides information on how to use the CCG4 Evaluation Kit (see **Table 2** for Type-C PD controller evaluation kits) to demonstrate the DRP application.

#### Table 2 Type-C and PD Controller Evaluation Kits

| Type-C PD Controller | <b>Type-C PD Controller Evaluation Kit</b> |

|----------------------|--------------------------------------------|

| CCG2                 | CY4521 EZ-PD CCG3 Evaluation Kit           |

| CCG3                 | CY4531 EZ-PD CCG3 Evaluation Kit           |

| CCG4                 | CY4541 EZ-PD CCG4 Evaluation Kit           |

This application note references the **CY4541 EZ-PD CCG4 Evaluation Kit** and is intended as supplemental information to the respective kit guide.

**USB** Power Delivery Specification

## 2 USB Power Delivery Specification

This section reviews the basics of USB power delivery. The **USB PD specification** defines how a PD-enabled USB port can get the required power from VBUS by negotiating with external power sources (such as wall warts).

A USB port providing power is known as a source, and a USB port consuming power is known as a sink. There is only one source port and one sink port in each PD connection. In the legacy USB specification, the USB port on host computer (such as a notebook or a PC) was always a source and the USB peripheral device was always a sink. The USB PD specification allows the source and sink to interchange their roles so that a USB peripheral device (such as an external self-powered hard disk or monitor) can supply power to a USB Host. These new power roles are independent of the USB data transfer roles between the USB Host and USB device. An example is a self-powered USB peripheral such as a monitor that can charge the battery of a notebook or PC, which is a USB Host.

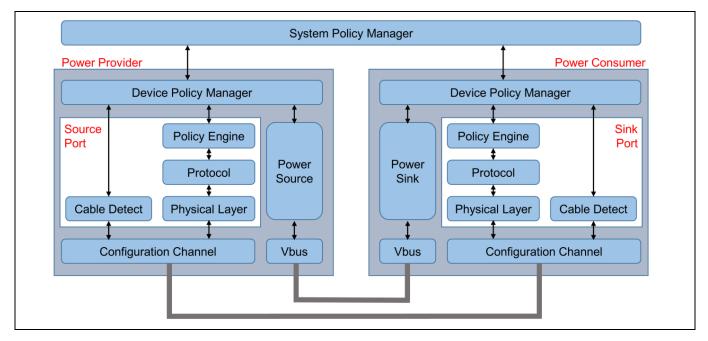

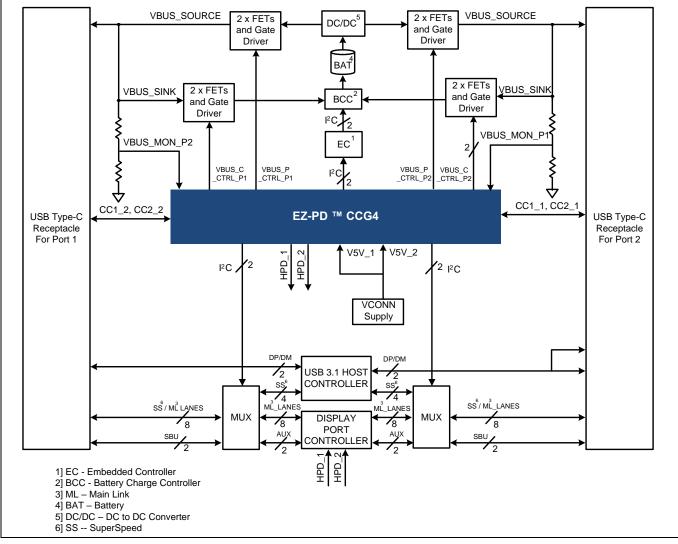

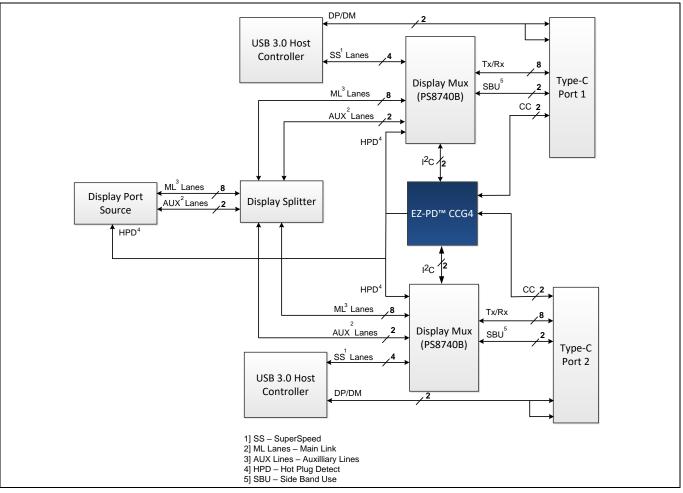

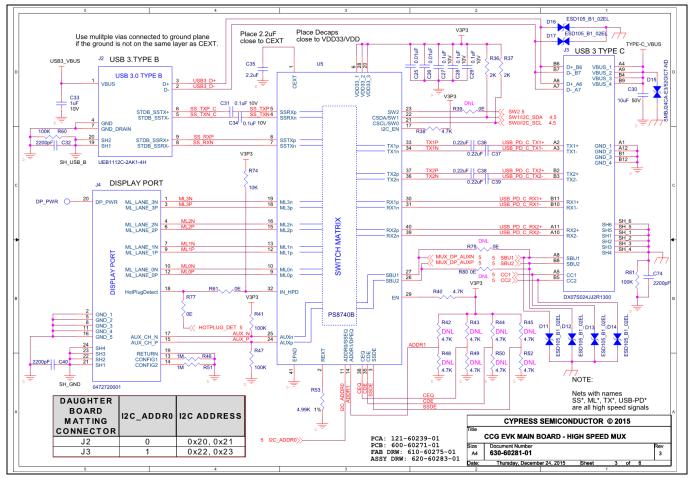

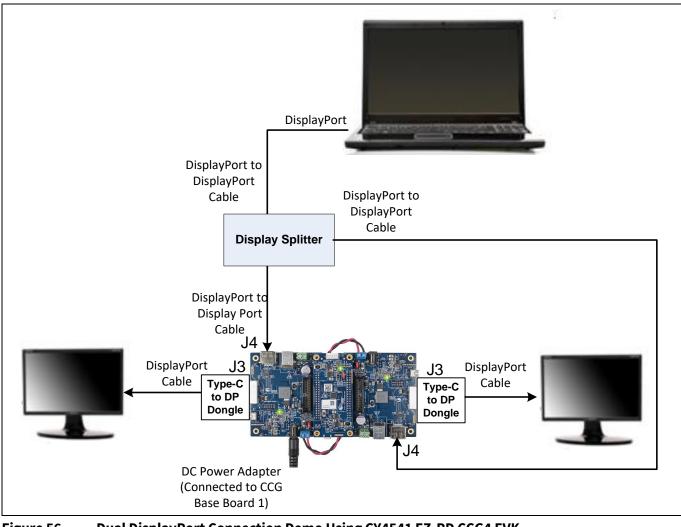

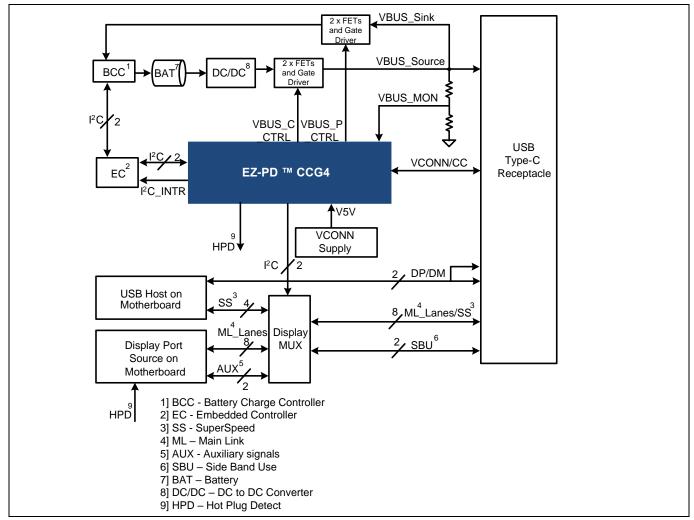

**0** shows logical block diagram of the Type-C and PD architecture.

Type-C and PD Architecture for Dual Role Power Applications

**System Policy Manager:** The PD Specification defines a System Policy Manager that is implemented on the USB Host running as an operating system stack. For more details of System Policy, see the **PD Specification**.

- **Device Policy Manager:** The Device Policy Manager is the module running in the Power Provider or Power Consumer, which applies a Local Policy to each Port in the device via the Policy Engine.

- **Source Port:** The Source Port is the power provider port, which supplies power over VBUS. It is, by default, a USB port on the Host or Hub.

- **Sink Port:** The Sink Port is the USB power consumer port, which consumes power over VBUS. It is, by default, a USB port on a device.

- **Policy Engine:** The Policy Engine interprets the Device Policy Manager's input to implement the Policy for the port. It also directs the Protocol Layer to send messages.

- **Protocol:** The Protocol Layer creates the messages for communication between Port Partners.

- **Physical Layer:** The Physical Layer sends and receives messages over either VBUS or the configuration channel (CC) between Port Pairs.

#### **USB** Power Delivery Specification

- **Power Source:** The ability of a Power Delivery (PD) port to source power over VBUS. This refers to a Type-C port with Rp asserted on CC.

- **Power Sink:** The ability of a Power Delivery (PD) port to sink power from VBUS. This refers to a Type-C port with Rd asserted on CC.

- **Cable Detection Module:** The Cable Detection Module detects the presence of an Electronically Marked Cable Assembly (EMCA) cable attached to a Type-C port.

Dual-role devices can be developed by combining both provider and consumer elements in a single device.

When a USB Host and USB device are interconnected, they form a USB link pair, and each link partner has a configuration channel (CC) controller. Messages are then logically exchanged among Device Policy Managers within each PD controller. These messages are physically transferred over the CC, and a PD contract is set up between the link pair, and then power is delivered over VBUS.

The CC is a new signal pair in the Type-C signal definition—see **Type-C Signal Definition**.

### 2.1 Type-C Signal Definition

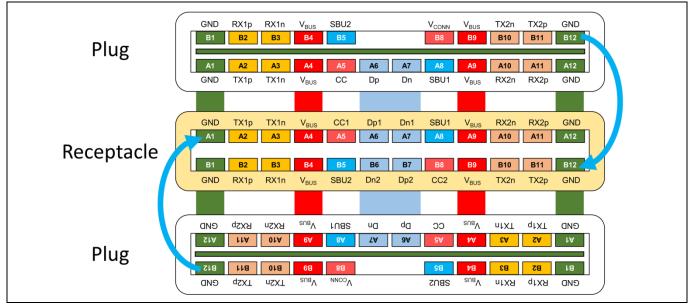

**Figure 1** shows the USB Type-C Receptacle, Plug, and Flipped-Plug signals. **Table 3**, **Figure 2**, and **Table 4** show the signals used on the USB Type-C receptacle and plug.

| Figure 1 USB Type-C Plug, Receptacle, and Flipped-P |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Table 3 | <b>USB Type-C R</b> | eceptacle Signals |

|---------|---------------------|-------------------|

|         |                     |                   |

| Signal Group | Signal                                                  | Description                                                                                                                                                                                                                         |

|--------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB 3.1      | TX1p, TX1n,<br>RX1p, RX1n,<br>TX2p, TX2n,<br>RX2p, RX2n | The SuperSpeed USB serial data interface defines a differential transmit pair and a differential receive pair. On a USB Type-C receptacle, two pairs of SuperSpeed USB signal pins are defined to enable the plug-flipping feature. |

| USB 2.0      | Dp1, Dn1<br>Dp2, Dn2                                    | The USB 2.0 serial data interface defines a differential pair. On a USB Type-C receptacle, two sets of USB 2.0 signal pins are defined to enable plug-flipping.                                                                     |

#### **USB Power Delivery Specification**

| Signal Group             | Signal     | Description                                                                                       |

|--------------------------|------------|---------------------------------------------------------------------------------------------------|

| Configuration<br>Channel | CC1, CC2   | The CC in the receptacle detects the signal orientation and channel configuration.                |

| Auxiliary signals        | SBU1, SBU2 | Sideband use. See the USB Type-C Cable and Connector Specification Revision 1.3 for more details. |

| Power                    | VBUS       | USB cable bus power                                                                               |

|                          | GND        | USB cable return current path                                                                     |

#### Table 4USB Type-C Plug Signals

| Signal Group             | Signal                                               | Description                                                                                                                                                                                                                   |

|--------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB 3.1                  | TX1p, TX1n<br>RX1p, RX1n<br>TX2p, TX2n<br>RX2p, RX2n | The SuperSpeed USB serial data interface defines a differential transmit pair and a differential receive pair. On a USB Type-C plug, two pairs of SuperSpeed USB signal pins are defined to enable the plug-flipping feature. |

| USB 2.0                  | Dp, Dn                                               | On a USB Type-C plug, the USB 2.0 serial data interface defines differential pair.                                                                                                                                            |

| Configuration<br>Channel | СС                                                   | The CC in the plug is used for connection detection and interface configuration.                                                                                                                                              |

| Auxiliary signals        | SBU1, SBU2                                           | Sideband use. See the USB Type-C Cable and Connector Specification Revision 1.3 for more details.                                                                                                                             |

| Power                    | VBUS                                                 | USB cable bus power                                                                                                                                                                                                           |

|                          | VCONN                                                | Type-C cable plug power                                                                                                                                                                                                       |

|                          | GND                                                  | USB cable return current path                                                                                                                                                                                                 |

As shown in **Figure 1**, the USB Type-C receptacle has USB 3.1 (TX and RX pairs) and USB 2.0 (Dp and Dn) data buses, USB power (VBUS), ground (GND), CC signals (CC1 and CC2), and two sideband use (SBU) signal pins. As listed in **Table 3** and **Table 4**, the descriptions of the USB Type-C plug and receptacle signals are the same, except for the CC and VCONN signals. The two sets of USB 2.0 and USB 3.1 signal locations in this layout facilitate the mapping of the USB signals independent of the plug orientation in the receptacle.

When a cable with the Type-C plug is inserted into the receptacle, one CC pin is used to establish signal orientation, and the other CC pin is repurposed as VCONN for powering the electronics in the USB Type-C cable (plug).

**USB Power Delivery Specification**

### 2.2 Type-C Ports

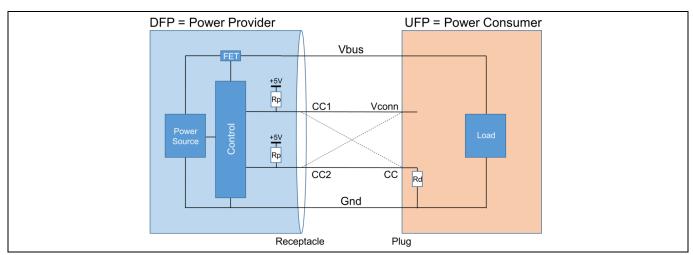

### 2.2.1 Downstream Facing Port and Upstream Facing Port

A Type-C downstream facing port (DFP) is by default a USB Host and a power source, whereas a Type-C upstream facing port (UFP) is by default a USB Device and a power sink. A DFP exposes Rp terminations on its CC pins (CC1 and CC2), while a UFP exposes Rd terminations on its CC pin, as shown in **Figure 2**.

Figure 2 Direct Connection of a Downstream Facing Port and Upstream Facing Port

DFPs, specifically those associated with the flow of data in a USB connection, are typically the USB ports on a Host such as a PC or a hub. In its default state, the DFP sources VBUS and VCONN. On the other hand, UFP sinks VBUS.

### 2.2.2 USB PD Dual Role Power

PD-enabled USB products (such as a notebook with a Type-C port) operate as a power provider and a power consumer. The USB PD specification refers to such USB Type-C port as Dual Role Power (DRPs).

DRP devices have the capability to detect the presence of the Rp and Rd resistors on the CC lines. A typical DRP device can perform the roles listed in **Table 5**.

| No.      | Data Port Role<br>(USB Host or Device) | Power Port Role<br>(Power Provider or Power Consumer) |

|----------|----------------------------------------|-------------------------------------------------------|

| -        | DFP                                    | Source (Power Provider, Connect Rp and disconnect Rd) |

| <u>)</u> | DFP                                    | Sink (Power Consumer, Disconnect Rp and connect Rd)   |

| 5        | UFP                                    | Source (Power Provider, Connect Rp and disconnect Rd) |

| 1        | UFP                                    | Sink (Power Consumer, Disconnect Rp and connect Rd)   |

Table 5Roles of DRP Device

**CCGx Devices Overview**

#### **CCGx Devices Overview** 3

Table 6 lists the available part numbers for CCG2, CCG3, CCG4, CCG5, CCG5C, CCG6, CCG6F, CCG6SF, and CCG6DF Type-C and PD controllers with their respective applications.

| Type-C PD<br>Controller | Manufacturing Part<br>Number  | Role            | Application                                       | Package     |

|-------------------------|-------------------------------|-----------------|---------------------------------------------------|-------------|

| CCG2                    | CYPD2122-24LQXIT              | DRP             | Notebooks                                         | 24-pin QFN  |

|                         | CYPD2122-20FNXIT              | DRP             | Tablets                                           | 20-ball CSP |

|                         | CYPD2121-24LQXIT              | DRP             | Dock/Monitor Upstream Port                        | 24-pin QFN  |

|                         | CYPD2134-24LQXIT              | DFP             | Power Adapter                                     | 24-pin QFN  |

|                         | CYPD2125-24LQXIT              | DFP             | Dock/Monitor Downstream Port                      | 24-pin QFN  |

|                         | CYPD2103-20FNXIT              | Cable           | Cable                                             | 20-ball CSP |

|                         | CYPD2119-24LQXIT              | C-DP            | UFP                                               | 24-pin QFN  |

|                         | CYPD2120-24LQXIT              | C-HDMI          | UFP                                               | 24-pin QFN  |

|                         | CYPD2103-14LHXIT              | Cable           | Cable                                             | 14-pin DFN  |

|                         | CYPD2105-20FNXIT              | Active<br>Cable | Active Cable                                      | 20-ball CSP |

|                         | CYPD2104-20FNXIT              | Accessory       | Accessory                                         | 20-ball CSP |

| CCG3                    | CYPD3125-40LQXIT              | DRP             | Notebooks                                         | 40-pin QFN  |

|                         | CYPD3121-40LQXIT              | DFP             | Monitor/Dock                                      | 40-pin QFN  |

|                         | CYPD3135-40LQXIT              | DFP             | Power Adapter                                     | 40-pin QFN  |

|                         | CYPD3122-40LQXIT              | UFP             | Monitor/Dock                                      | 40-pin QFN  |

|                         | CYPD3120-40LQXIT              | UFP             | Dongle                                            | 40-pin QFN  |

|                         | CYPD3105-42FNXIT              | Cable           | Thunderbolt Active Cable                          | 42-pin CSP  |

| CCG4                    | CYPD4225-40LQXIT              | DRP             | Dual Type-C Port Notebooks,<br>Docking Stations   | 40-pin QFN  |

|                         | CYPD4125-40LQXIT              | DRP             | Single Type-C Port Notebooks,<br>Docking Stations | 40-pin QFN  |

|                         | CYPD4126-40LQXIT              | DRP             | Notebooks, desktops                               | 40-pin QFN  |

|                         | CYPD4226-40LQXIT              | DRP             | Notebooks, desktops                               | 40-pin QFN  |

|                         | CYPD4236-40LQXIT              | DRP             | Docking station                                   | 40-pin QFN  |

|                         | CYPD4126-24LQXIT              | DRP             | Notebooks, desktops                               | 24-pin QFN  |

|                         | CYPD4136-24LQXIT              | DRP             | Docking station                                   | 24-pin QFN  |

| CCG5                    | CYPD5125-40LQXIT <sup>1</sup> | DRP             | Notebooks                                         | 40-pin QFN  |

|                         | CYPD5225-96BZXIT              | DRP             | Notebooks, Docking Station                        | 96-ball BGA |

| CCG5C                   | CYPD5126-40LQXIT              | DRP             | Notebooks, Desktops                               | 40-pin QFN  |

|                         | CYPD5137-40LQXIT              | DRP             | Docking Stations                                  | 40-pin QFN  |

| CCG6                    | CYPD6125-40LQXIT              | DRP             | Notebooks and Desktops                            | 40-pin QFN  |

Table 6 **Type-C PD Controller MPNs and Applications**

<sup>&</sup>lt;sup>1</sup> Not recommended for new designs (NRND). See the CCG5C datasheet for pin-to-pin compatible replacement part. **Application Note** 16 of 98

**CCGx Devices Overview**

| Type-C PD<br>Controller | Manufacturing Part<br>Number | Role | Application            | Package     |

|-------------------------|------------------------------|------|------------------------|-------------|

|                         | CYPD6137-40LQXIT             | DRP  | Docking Station        | 40-pin QFN  |

| CCG6F                   | CYPD6126-96BZXI              | DRP  | Notebooks and Desktops | 96-ball BGA |

|                         | CYPD6126-96BZXIT             | DRP  | Notebooks and Desktops | 96-ball BGA |

| CCG6SF                  | CYPD6127-48LQXI              | DRP  | Notebooks and Desktops | 48-pin QFN  |

| CCG6DF                  | CYPD6227-96BZXI              | DRP  | Notebooks and Desktops | 96-ball BGA |

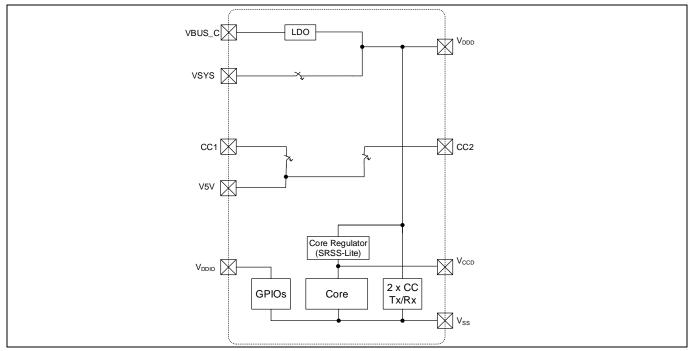

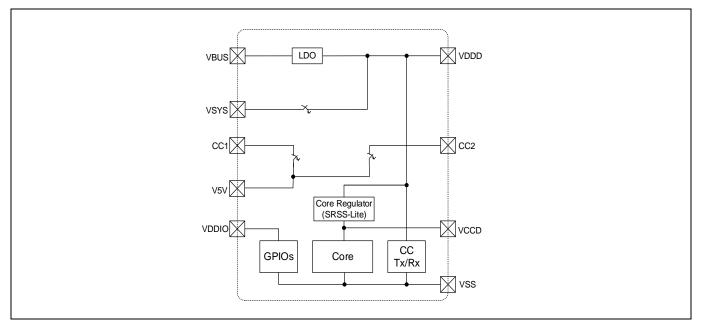

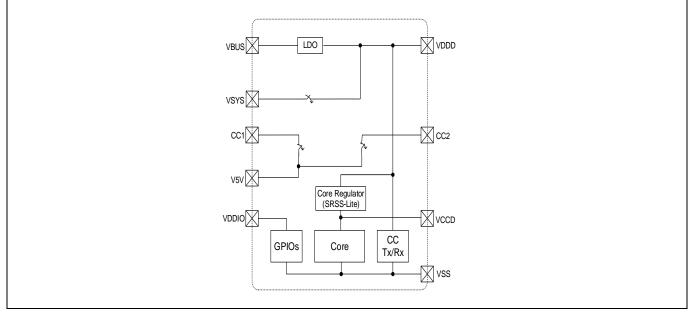

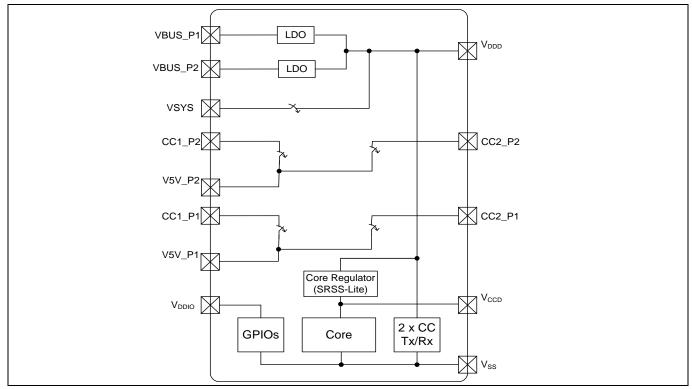

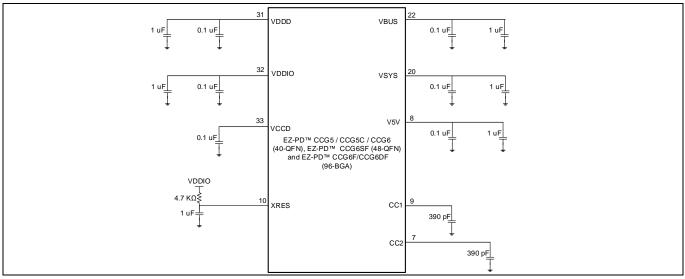

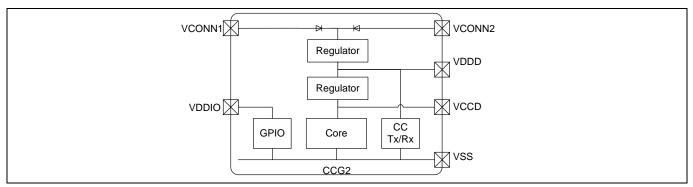

### 3.1 Type-C PD Controller Power Subsystem

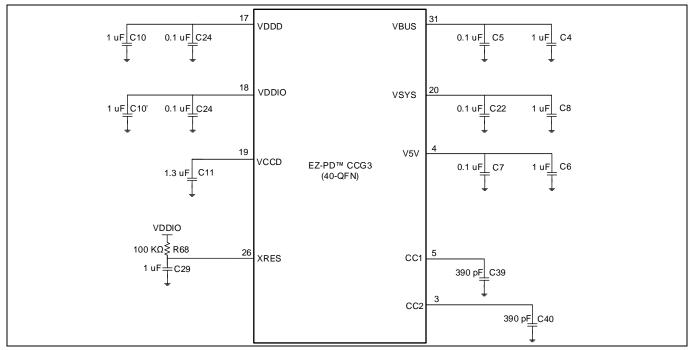

**Table 7** provides the power domain details of Type-C and PD controllers and the recommended values of bypass capacitors to be used on the respective power supply pins.

| Type-C and PD<br>Controller | Power<br>Supply Pin     | Power Supply Domain                                                                                                                                                                                | Role                                                                                          | Valid Input Voltage<br>Level | Value of Bypass<br>Capacitor to GND |

|-----------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------|-------------------------------------|

| CCG2                        | VDDD                    | Supply to the core                                                                                                                                                                                 | DRP                                                                                           | 3.0 V to 5.5 V               | 1μF                                 |

|                             |                         |                                                                                                                                                                                                    | DFP                                                                                           | 3.0 V to 5.5 V               |                                     |

|                             |                         |                                                                                                                                                                                                    | UFP                                                                                           | 2.7 V to 5.5 V               |                                     |

|                             | VDDIO                   | Supply to I/Os                                                                                                                                                                                     | DRP                                                                                           | 1.71 V to VDDD               | 1μF                                 |

|                             |                         |                                                                                                                                                                                                    | DFP                                                                                           |                              |                                     |

|                             |                         |                                                                                                                                                                                                    | UFP                                                                                           |                              |                                     |

|                             | VCCD                    | The core voltage of the device is brought out to the pin. This<br>pin cannot be used as a voltage source and is intended to<br>connect only a decoupling capacitor.<br>NA (This is an output pin.) |                                                                                               |                              | 1μF                                 |

|                             | VCONN1<br>and<br>VCONN2 | Supply to power VCONN<br>FETs                                                                                                                                                                      | DRP                                                                                           | 4.0 V to 5.5 V               | NA                                  |

|                             |                         |                                                                                                                                                                                                    | DFP                                                                                           |                              | NA                                  |

|                             |                         |                                                                                                                                                                                                    | UFP                                                                                           |                              | NA                                  |

|                             |                         |                                                                                                                                                                                                    | Cable                                                                                         | 4.0 V to 5.5 V               | 1μF                                 |

| CCG3                        | VBUS                    | Supply to the core                                                                                                                                                                                 | DRP                                                                                           | 4.0 V to 21.5 V              | 1μF                                 |

|                             |                         | Note: Either VBUS or VSYS can be provided.                                                                                                                                                         | DFP                                                                                           |                              |                                     |

|                             |                         |                                                                                                                                                                                                    | UFP                                                                                           |                              |                                     |

|                             | VSYS                    | Supply to the core                                                                                                                                                                                 | DRP                                                                                           | 2.7 V to 5.5 V               | 1 μF                                |

|                             |                         | Note: Either VBUS or VSYS                                                                                                                                                                          | DFP                                                                                           |                              |                                     |

|                             |                         | can be provided.                                                                                                                                                                                   | UFP                                                                                           |                              |                                     |

|                             | VDDD                    | Supply to the analog blocks                                                                                                                                                                        | DRP                                                                                           | VDDD is an output            | 1μF                                 |

|                             |                         | in chip                                                                                                                                                                                            | DFP                                                                                           | pin, which is                |                                     |

|                             |                         | UFP                                                                                                                                                                                                | intelligently<br>switched between<br>output of the VBUS<br>regulator and<br>unregulated VSYS. |                              |                                     |

|                             | VDDIO                   | Supply to the I/Os                                                                                                                                                                                 | DRP                                                                                           | 1.71 V to VDDD               | 1μF                                 |

Table 7

Type-C and PD Controller Power Subsystem

**CCGx Devices Overview**

| Type-C and PD<br>Controller | Power<br>Supply Pin     | Power Supply Domain                                                                                                                                                 | Role              | Valid Input Voltage<br>Level                           | Value of Bypass<br>Capacitor to GND |

|-----------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------|-------------------------------------|

|                             |                         |                                                                                                                                                                     | DFP<br>UFP        | Note that, VDDIO<br>pin can be shorted<br>to VDDD pin. |                                     |

|                             | VCCD                    | The core voltage of the devic<br>pin cannot be used as a volta<br>connect only a decoupling ca                                                                      | 1μF               |                                                        |                                     |

|                             | V5V                     | Supply to power VCONN<br>FETs                                                                                                                                       | DRP<br>DFP<br>UFP | 2.7 V to 5.5 V                                         | 1μF                                 |

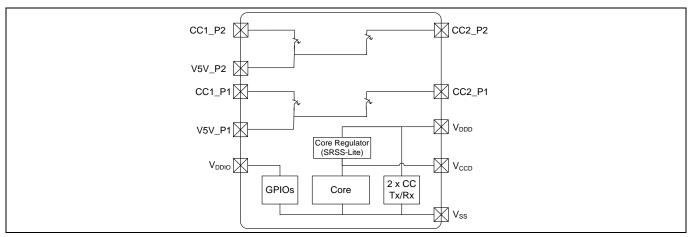

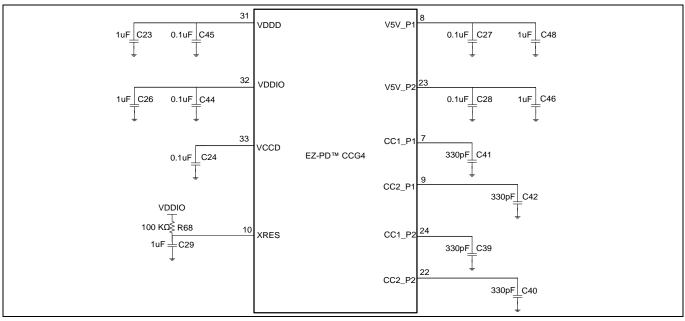

| CCG4                        | VDDD                    | Supply to the core                                                                                                                                                  | DRP<br>DFP<br>UFP | 3.0 V to 5.5 V<br>3.0 V to 5.5 V<br>2.7 V to 5.5 V     | 1μF                                 |

| \<br>\<br>{                 | VDDIO                   | Supply to I/Os                                                                                                                                                      | DRP<br>DFP<br>UFP | 1.71 V to VDDD                                         | 1μF                                 |

|                             | VCCD                    | The core voltage of the device is brought out to the pin. This<br>pin cannot be used as a voltage source and is intended to<br>connect only a decoupling capacitor. |                   |                                                        | 0.1 μF                              |

|                             | V5V_P1<br>and<br>V5V_P2 | Supply to power VCONN<br>FETs                                                                                                                                       | DRP<br>DFP<br>UFP | 4.85 V to 5.5 V                                        | 0.1 μF                              |

| CCG5                        | VBUS                    | Supply to the core<br>Note: Either VBUS or VSYS<br>can be provided                                                                                                  | DRP<br>DFP<br>UFP | 4.0 V to 21.5 V                                        | 1μF                                 |

|                             | VSYS                    | Supply to the core<br>Note: Either VBUS or VSYS<br>can be provided.                                                                                                 | DRP<br>DFP<br>UFP | 3 V to 5.5 V                                           | 1μF                                 |

|                             | VDDD                    | Supply Input                                                                                                                                                        | DRP<br>DFP<br>UFP | 3.0 V to 5.5 V<br>3.0 V to 5.5 V<br>2.7 V to 5.5 V     | 1μF                                 |

| VDD                         | VDDIO                   | Supply to I/Os                                                                                                                                                      | DRP<br>DFP<br>UFP | 1.71 V to VDDD                                         | 0.1 μF                              |

|                             | VCCD                    | The core voltage of the device is brought out to the pin. This<br>pin cannot be used as a voltage source and is intended to<br>connect only a decoupling capacitor. |                   |                                                        | 0.1 μF                              |

|                             | V5V_P1<br>and<br>V5V_P2 | Supply to power VCONN<br>FETs                                                                                                                                       | DRP<br>DFP<br>UFP | 4.85 V to 5.5 V                                        | 1μF                                 |

**CCGx Devices Overview**

| Type-C and PD<br>Controller | Power<br>Supply Pin                                        | Power Supply Domain                                                                                                                                                 | Role   | Valid Input Voltage<br>Level | Value of Bypass<br>Capacitor to GND |

|-----------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------|-------------------------------------|

| CCG5C / CCG6                | VBUS                                                       | Supply to the core                                                                                                                                                  | DRP    | 4.0 V to 21.5 V              | 1μF                                 |

| / CCG6F                     |                                                            | Note: Either VBUS or VSYS                                                                                                                                           | DFP    |                              |                                     |

|                             |                                                            | can be provided                                                                                                                                                     | UFP    |                              |                                     |

|                             | VSYS                                                       | Supply to the core                                                                                                                                                  | DRP    | 3V to 5.5 V                  | 1μF                                 |

|                             |                                                            | Note: Either VBUS or VSYS                                                                                                                                           | DFP    | 3V to 5.5V                   |                                     |

|                             |                                                            | can be provided.                                                                                                                                                    | UFP    | 2.75 V to 5.5V               |                                     |

|                             | VDDD                                                       | Supply Input                                                                                                                                                        | DRP    | 3.0 V to 5.5 V               | 1 μF                                |

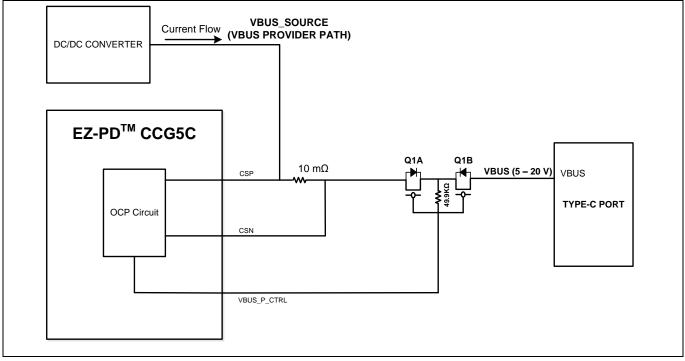

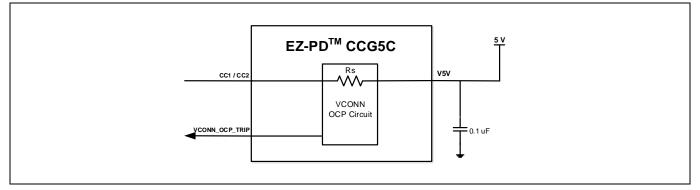

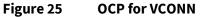

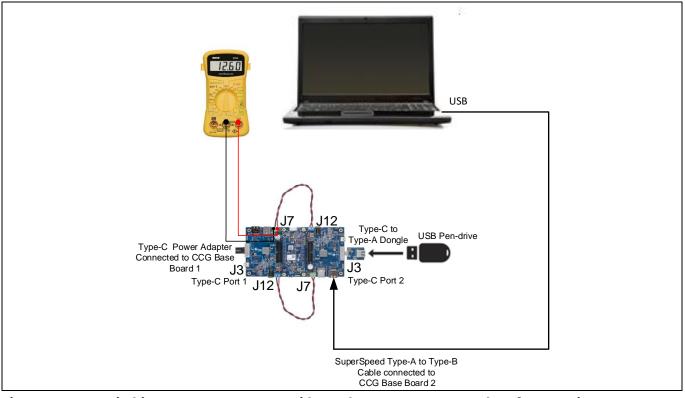

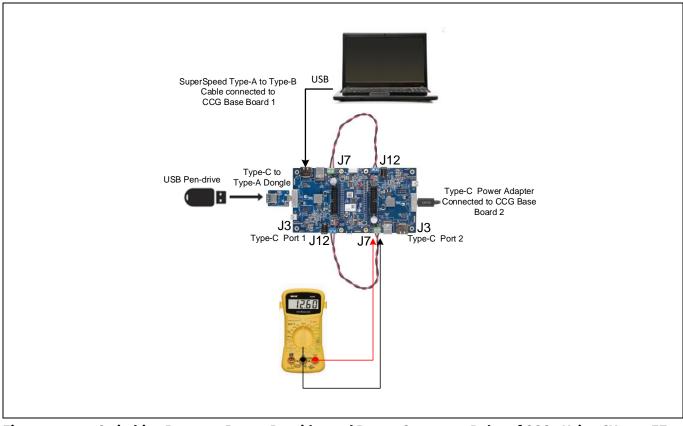

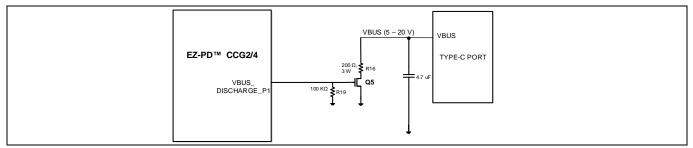

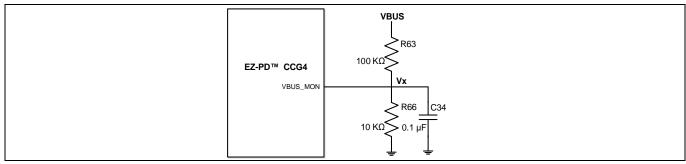

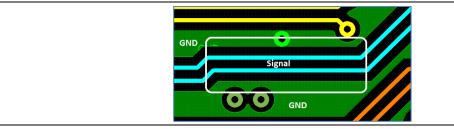

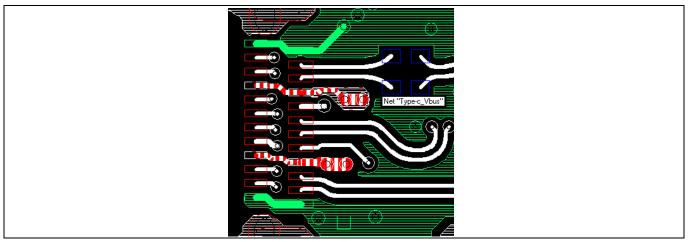

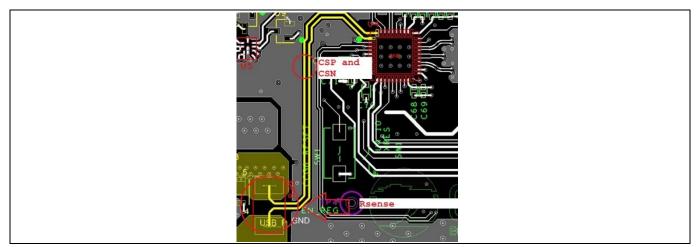

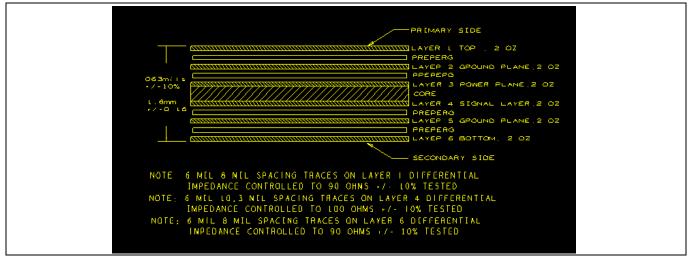

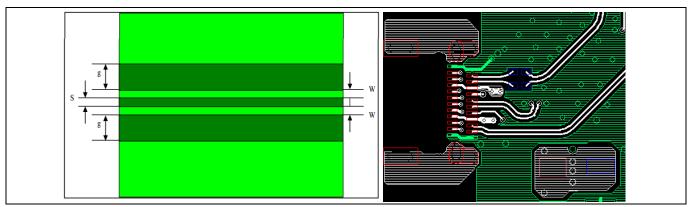

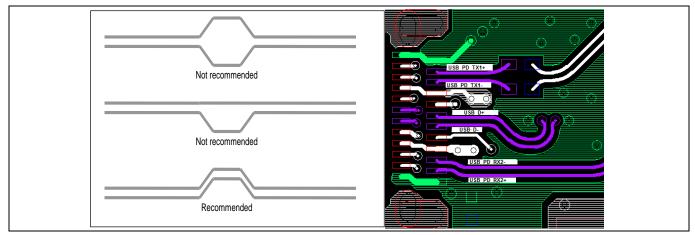

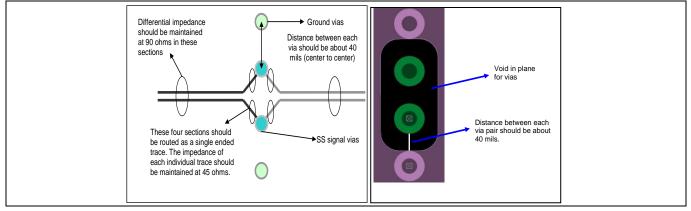

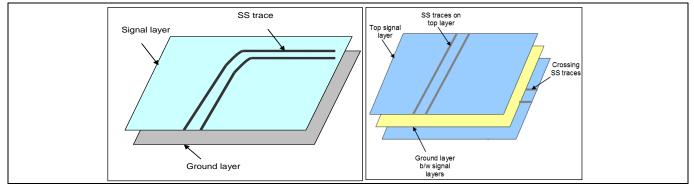

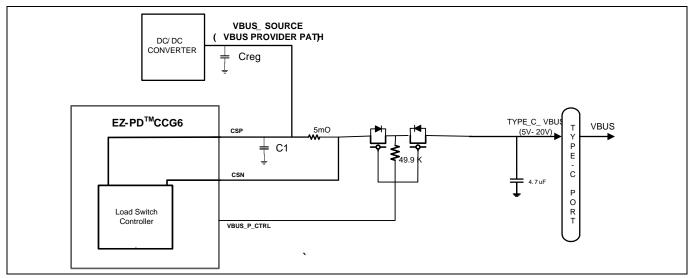

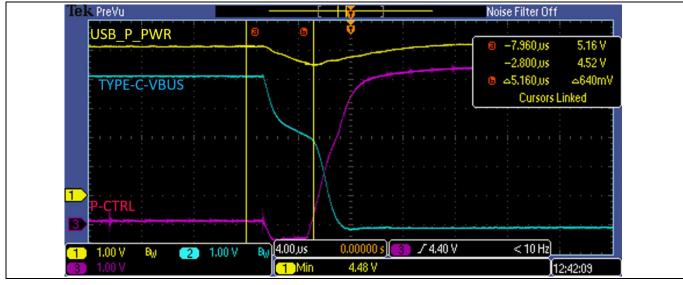

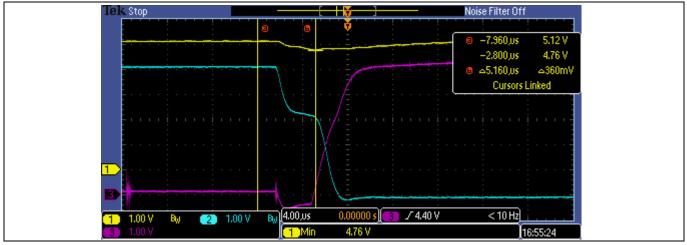

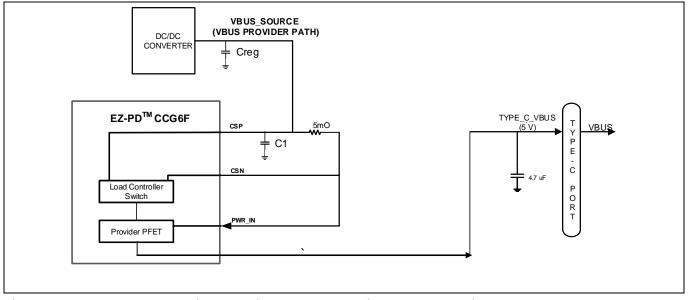

|                             |                                                            |                                                                                                                                                                     | DFP    | 3.0 V to 5.5 V               |                                     |