# **Technical Information**

**Bipolar Semiconductors**

## **Products and Innovations**

The goal of highest reliability and efficiency in a core technology is always a moving target; therefore we understand that continuous improvement is essential. On this basis we have established comprehensive standards with our technologies and our products, in the power classes ranging from around 10kW to over 30MW per component. These include for example:

- PowerBLOCK modules in press-pack technology with currents up to 1100 Ampere

- Diodes and thyristors with a silicon diameter up to six inches and blocking voltages up to 9500 Volts

- Light-triggered thyristors with integrated protection functions

- Freewheeling diodes for the highest requirements in fast switching applications such as with IGBTs or IGCTs

## Contents

| 1. Introduction                                                                                                                                                          | 6        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1 Diode                                                                                                                                                                | 6        |

| 1.2 Thyristor                                                                                                                                                            | 7        |

| 2. Type and polarity designation                                                                                                                                         | 9        |

| 2.1 Designation of the terminals                                                                                                                                         | 9        |

| 2.2 Constructions                                                                                                                                                        | 9        |

| 2.2.1 General                                                                                                                                                            | 9        |

| 2.2.2 Disc cells                                                                                                                                                         | 9        |

| 2.2.3 PowerBLOCK-Module                                                                                                                                                  | 9        |

| 2.2.4 Stud type and flat case constructions                                                                                                                              | 10       |

| 3. Electrical properties                                                                                                                                                 | 11       |

| 3.1 Forward direction                                                                                                                                                    | 11       |

| 3.1.1 Forward off-state current i <sub>D</sub>                                                                                                                           | 12       |

| 3.1.2 Forward off-state voltage $v_D$                                                                                                                                    | 12       |

| 3.1.2.1 Repetitive peak forward off-state voltage V <sub>DRM</sub>                                                                                                       | 12       |

| 3.1.2.2 Non-repetitive peak forward off-state voltage V <sub>DSM</sub>                                                                                                   | 13       |

| 3.1.2.3 Forward direct off-state voltage V <sub>D (DC)</sub>                                                                                                             | 13       |

| 3.1.3 Forward breakover voltage V <sub>(BO)</sub>                                                                                                                        | 13       |

| 3.1.4 Open gate forward breakover voltage V <sub>(BO)0</sub>                                                                                                             | 13       |

| 3.1.5 Holding current l                                                                                                                                                  | 13<br>13 |

| 3.1.6 Latching current I <sub>L</sub> 3.1.7 On-state current i <sub>T</sub> , I <sub>TAV</sub> , I <sub>TRMS</sub> i <sub>F</sub> , I <sub>FAV</sub> , I <sub>FRMS</sub> | 13       |

| 3.1.8 On-state voltage $v_T$ , $v_F$                                                                                                                                     | 14       |

| 3.1.9 On-state characteristic                                                                                                                                            | 14       |

| 3.1.10 Equivalent line approximation with $V_{T(TO)}$ , $V_{F(TO)}$ and $r_T$                                                                                            | 14       |

| 3.1.11 Maximum average on-state current I <sub>TAVM</sub> , I <sub>FAVM</sub>                                                                                            | 15       |

| 3.1.12 Maximum RMS on-state current I <sub>TRMSM</sub> , I <sub>FRMSM</sub>                                                                                              | 15       |

| 3.1.13 Overload on-state current I <sub>T(OV)</sub> , I <sub>F(OV)</sub>                                                                                                 | 15       |

| 3.1.14 Maximum overload on-state current I <sub>T(OV)M</sub> , I <sub>F(OV)M</sub>                                                                                       | 15       |

| 3.1.15 Surge on-state current I <sub>TSM</sub> , I <sub>FSM</sub>                                                                                                        | 17       |

| 3.1.16 Maximum rated value ʃi²dt                                                                                                                                         | 17       |

| 3.2 Reverse direction                                                                                                                                                    | 18       |

| 3.2.1 Reverse current i <sub>R</sub>                                                                                                                                     | 18       |

| 3.2.2 Reverse voltage v <sub>R</sub>                                                                                                                                     | 18       |

| 3.2.2.1 Repetitive peak reverse voltage V <sub>RRM</sub>                                                                                                                 | 18       |

| 3.2.2.2 Non-repetitive peak reverse voltage V <sub>RSM</sub> 3.2.2.3 Direct reverse voltage V <sub>R(DC)</sub>                                                           | 18<br>18 |

| T (DC)                                                                                                                                                                   |          |

| 3.3 Control properties of thyristors                                                                                                                                     | 19       |

| 3.3.1 Positive gate control                                                                                                                                              | 19       |

| 3.3.1.1 Gate current i <sub>G</sub><br>3.3.1.2 Gate voltage V <sub>G</sub>                                                                                               | 19<br>19 |

| 3.3.1.3 Gate voltage $V_G$                                                                                                                                               | 19       |

| 3.3.1.4 Gate trigger voltage V <sub>GT</sub>                                                                                    | 19        |

|---------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.3.1.5 Gate non-trigger current I <sub>GD</sub>                                                                                | 19        |

| 3.3.1.6 Gate non-trigger voltage V <sub>GD</sub>                                                                                | 19        |

| 3.3.1.7 Control characteristic                                                                                                  | 20        |

| 3.3.1.8 Control circuit                                                                                                         | 20        |

| 3.3.1.9 Minimum duration of the trigger pulse t <sub>gmin</sub>                                                                 | 23        |

| 3.3.1.10 Maximum permissible peak trigger current                                                                               | 23        |

| 3.4 Carrier storage effect and switching characteristics                                                                        | 24        |

| 3.4.1 Turn-on                                                                                                                   | 24        |

| 3.4.1.1 Diode                                                                                                                   | 24        |

| 3.4.1.1.1 Peak value of the forward recovery voltage V <sub>FRM</sub>                                                           | 25        |

| 3.4.1.1.2 On-state recovery time t <sub>fr</sub>                                                                                | 25        |

| $3.4.1.2$ Thyristor $3.4.1.2.1$ Gate controlled delay time $t_ed$                                                               | 25<br>26  |

| 3.4.1.2.2 Critical rate of rise of the on-state current (di/dt) <sub>cr</sub>                                                   | 26        |

| 3.4.1.2.3 Repetitive turn-on current I <sub>T(RC)M</sub>                                                                        | 27        |

| 3.4.1.2.4 Critical rate of rise of off-state voltage (dv/dt)cr                                                                  | 27        |

| 3.4.2 Turn-off                                                                                                                  | 27        |

| 3.4.2.1 Recovery charge Q <sub>r</sub>                                                                                          | 27        |

| 3.4.2.2 Peak reverse recovery current I <sub>RM</sub>                                                                           | 29        |

| 3.4.2.3 Reverse recovery time $t_{rr}$<br>3.4.2.4 Turn-off time $t_{\alpha}$                                                    | 30<br>30  |

| ' .                                                                                                                             | <b>33</b> |

| 3.5 Power dissipation (losses)                                                                                                  |           |

| 3.5.1 Total power dissipation P <sub>tot</sub>                                                                                  | 33        |

| 3.5.2 Off-state losses P <sub>D</sub> , P <sub>R</sub>                                                                          | 33<br>33  |

| 3.5.3 On-state losses P <sub>T</sub> , P <sub>F</sub> 3.5.4 Switching losses P <sub>TT</sub> , P <sub>FT</sub> +P <sub>RO</sub> | 34        |

| 3.5.4.1 Turn-on losses $P_{TT}$ , $P_{FT}$                                                                                      | 34        |

| 3.5.4.2 Turn-off losses $P_{RO}$                                                                                                | 35        |

| 3.5.5 Gate dissipation $P_{G}$                                                                                                  | 35        |

| 3.6 Insulation test voltage V <sub>ISOL</sub>                                                                                   | 35        |

|                                                                                                                                 |           |

| 4. Thermal properties                                                                                                           | 36        |

| 4.1 Temperatures                                                                                                                | 36        |

| 4.1.1 Junction temperature T <sub>vj</sub> , T <sub>vj max</sub>                                                                | 36        |

| 4.1.2 Case temperature T <sub>C</sub>                                                                                           | 36        |

| 4.1.3 Heatsink temperature T <sub>H</sub>                                                                                       | 37        |

| 4.1.4 Cooling medium temperature T <sub>A</sub>                                                                                 | 37        |

| 4.1.5 Junction operating temperature range T <sub>cop</sub>                                                                     | 37        |

| 4.1.6 Storage temperature range T <sub>stg</sub>                                                                                | 37        |

| 4.2 Thermal resistances                                                                                                         | 37        |

| 4.2.1 Internal thermal resistance R <sub>thJC</sub>                                                                             | 37        |

| 4.2.2 Thermal transfer resistance R <sub>thCH</sub>                                                                             | 37        |

| 4.2.3 Heatsink thermal resistance R <sub>thCA</sub>                                                                             | 38        |

| 4.2.4 Total thermal resistance R <sub>thJA</sub>                                                                                | 38        |

| 4.2.5 Transient internal thermal resistance Z <sub>thJC</sub>                                                                   | 38        |

| 4.2.6 Transient heatsink thermal resistance Z <sub>thCA</sub>                                                                   | 38        |

| 4.2.7 Total transient thermal resistance Z <sub>thJA</sub>                                                                      | 39        |

| 4.3 Cooling                                                                                                                                    | 39              |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 4.3.1 Natural air cooling                                                                                                                      | 39              |

| 4.3.2 Forced air cooling                                                                                                                       | 39              |

| 4.3.3 Water cooling                                                                                                                            | 39              |

| 4.3.4 Oil cooling                                                                                                                              | 39              |

| 5. 5. Mechanical properties                                                                                                                    | 40              |

| 5.1 Tightening torque                                                                                                                          | 40              |

| 5.2 Clamping force                                                                                                                             | 40              |

| 5.3 Creepage distance                                                                                                                          | 40              |

| 5.4 Humidity classification                                                                                                                    | 40              |

| 5.5 Vibration                                                                                                                                  | 40              |

| 5.6 UL-registration                                                                                                                            | 40              |

| 6. Notes for applications                                                                                                                      | 41              |

| 6.1 Case non-rupture current                                                                                                                   | 41              |

| 6.2 Thermal load cycling                                                                                                                       | 41              |

| 6.3 Parallel connection                                                                                                                        | 42              |

| 6.4 Series connection                                                                                                                          | 44              |

| 6.5 Pulsed Power                                                                                                                               | 46              |

| 6.5.1 Applications with DC                                                                                                                     | 46              |

| 6.5.2 Current rise time at turn-on                                                                                                             | 46              |

| <ul><li>6.5.3 Zero crossing of current and voltage during turn-on</li><li>6.5.4 Turn-off with a high di/dt versus a negative voltage</li></ul> | 47<br>47        |

| 7. Protection                                                                                                                                  | 49              |

| 7.1 Overvoltage protection                                                                                                                     | 49              |

| 7.1.1 Individual snubbering (RC-snubber)                                                                                                       | <b>49</b>       |

| 7.1.2 Input snubbering for AC-controllers                                                                                                      | 52              |

| 7.1.3 Supply snubbers for line commutated converters                                                                                           | 53              |

| 7.1.4 Additional options for protection versus energy intensive overvoltages                                                                   | 55              |

| 7.2 Overcurrent protection                                                                                                                     | 56              |

| 7.2.1 Short-term protection with superfast semiconductor fuses                                                                                 | 56              |

| 7.2.1.1 Selection of fuses 7.2.2 Further protection concepts: short-term protection of high power semiconductors                               | 56<br>59        |

| 7.2.2.1 High speed DC-circuit breakers                                                                                                         | 59              |

| 7.2.2.2 Crowbar (electronic short circuit)                                                                                                     | 59              |

| 7.2.2.3 Line side circuit breaker                                                                                                              | 59              |

| 7.2.2.4 Blocking of trigger pulses                                                                                                             | 59              |

| 7.2.3 Long-term protection                                                                                                                     | 59              |

| 7.2.4 Fully rated protection 7.3 Dynamic current limiting with inductors in the load circuit                                                   | 59<br><b>60</b> |

| 7.4 Reduction of interference pulses in the gate circuit                                                                                       | 61              |

| 7.4 Reduction of interference pulses in the gate circuit                                                                                       | OI              |

| 8. Mounting                           | 62  |

|---------------------------------------|-----|

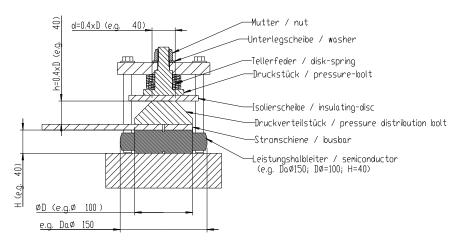

| 8.1 Disc cases                        | 62  |

| 8.1.1 Mounting of disc cells          | 62  |

| 8.1.2 Positioning the heatsinks       | 66  |

| 8.1.3 Connection of busbars           | 66  |

| 8.1.4 Connection of the control leads | 67  |

| 8.2 Stud cases                        | 67  |

| 8.2.1 Mounting stud cases             | 67  |

| 8.2.2 Positioning the heatsinks       | 67  |

| 8.2.3 Connection of busbars           | 68  |

| 8.2.4 Connection of the control leads | 68  |

| 8.3 Flat base cases                   | 68  |

| 8.3.1 Mounting flat base devices      | 68  |

| 8.3.2 Positioning the heatsinks       | 69  |

| 8.3.3 Connection of busbars           | 69  |

| 8.3.4 Connection of the control leads | 69  |

| 8.4 PowerBLOCK-Modules                | 69  |

| 8.4.1 Mounting PowerBLOCK-modules     | 69  |

| 8.4.2 Positioning the heatsinks       | 69  |

| 8.4.3 Connection of busbars           | 70  |

| 8.4.4 Connection of the control leads | 70  |

| 9. Maintenance                        | 70  |

| 10. Storage                           | 70  |

| 11. Type designation                  | 71  |

| 12. Circuit topologies                | 72  |

| A1. Abbreviations                     | 74  |

| A2. List of Figures                   | 76  |

| A3. List of tables                    | 78  |

|                                       | , - |

| A4. Conditions of use                 | 79  |

## **Preface**

Power semiconductors are the central components in converters technology. Due to constant advancement these components find further use in ever new and more complex applications.

Based on the suggestions and questions we have been approached with we compiled this Technical Information (TI) as a reference document.

This Technical Information describes all essential technical terms for bipolar power semiconductors (diodes and thyristors) and thus provides assistance in working and designing as well as a reference document for the development and projection of inverter circuitry with bipolar components.

It is aimed at the relevant specialists in industry, research, development and training.

General information regarding converters, their circuits and specialties can be found in the pertinent literature.

At this point we refer to the appropriate standards which always need to be regarded in their latest version.

The current technical data of Infineon power semiconductors can be down-loaded from www.Infineon.com.

This Technical Information is meant to assist in better understanding the terms and the application of data sheet specifications of bipolar power semiconductors.

Definitions and abbreviations used are mainly in accordance with DIN / IEC / EN.

Please note that no guaranty can be given that circuits, appliances and processes described here are free of patent rights.

## 1. Introduction

This TI is to give detailed definitions to specifications used in the data sheets. Further, the user is to be assisted to transfer the data sheet specifications correctly in his application.

The following information is generally valid for all Infineon pressure contact components (disc cells and PowerBLOCK-Modules). Exceptions are individually marked. Information given here is valid in accordance with the currently valid norms and standards.

#### 1.1 Diode

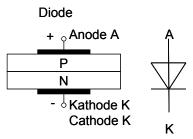

A diode is a component with one P and one N conducting semiconductor zone. The PN-junction is responsible for the elementary features of this semiconductor (see Figure 1).

Figure 1: Schematic construction of a diode

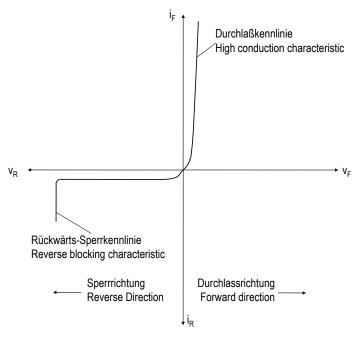

The characteristic of a diode is depicted in Figure 2. It consists of two sections: the blocking characteristic and on-state characteristic.

Figure 2 Characteristics of a diode

When a voltage up to several kV is applied in reverse direction, reverse currents in the range of mA will flow via the main terminals anode and cathode.

When a voltage is applied in forward direction, currents up to several kA will flow via the main terminals anode and cathode.

### 1.2 Thyristor

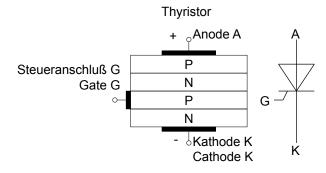

A thyristor is a component with a total of four alternating P and N conducting semiconductor zones. These will thus form three PN-junctions (see Figure 3).

Figure 3: Schematic construction of a thyristor

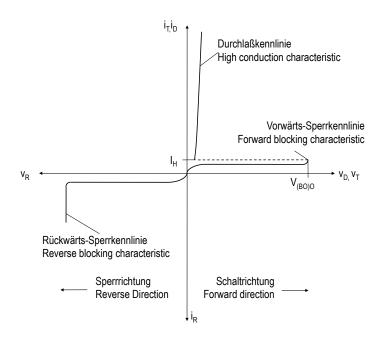

The characteristics of a conventional (reverse blocking) thyristor are depicted in Figure 4. They consist of three sections: The blocking and the on-state characteristic in forward direction and the blocking characteristic in reverse direction.

Figure 4 Characteristics of a thyristor

As can be seen from the characteristics, the thyristor is initially blocked in forward and reverse directions. Generally the blocking capability is approximately the same in both directions.

When voltages up to several kV are applied in forward or reverse direction, only small blocking currents will flow via the main terminals anode and cathode. An additional control current  $I_G$  between control terminal (gate) and cathode

will trigger the thyristor when a forward voltage  $v_D$  is present, i.e. it turns on to the on-state characteristic. However, it may not be turned off via the control terminal. Only when the forward current by changes in the load circuit drops below the holding current  $I_H$ , the thyristor will once again block.

Fast thyristors are available in 2 basic versions:

■ Symmetrically blocking thyristors (SCR → Silicon Controlled Rectifier)

These thyristors show approximately equal blocking capability in both directions. Individual types are differentiated by their blocking capability, their current carrying capability, their turn-off time and the gate-cathode structure.

■ Asymmetrically blocking thyristors

(ASCR — Asymmetric Silicon Controlled Rectifier)

These thyristors provide full blocking capability in forward direction and little blocking capability in reverse. Here the reverse blocking PN-junction is replaced by a stop layer which allows a significant reduction of the silicon height.

The advantages compared to symmetrically blocking thyristor are a shorter turn-off time for the same on-state voltage or a lower on-state voltage for the same turn-off time.

## 2. Type and polarity designation

## 2.1 Designation of the terminals

Figure 5 Designation of the terminals

#### 2.2 Constructions

#### 2.2.1 General

The semiconductor element (pellet) is built into a case and thus protected from adverse influences of the external environment.

All semiconductors described here are constructed in pressure contact technology.

The pressure contact technology is known for:

- very high load cycling capability

- very good over-load capability

#### 2.2.2 Disc cells

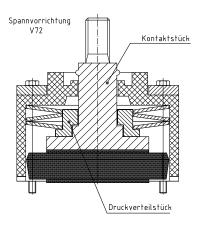

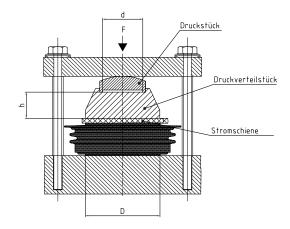

When mounting disc cells the pressure for the components has to be applied from the exterior. Double sided cooling allows the heat generated through the losses to be dissipated in the best possible way from the disc cells. They are thus used for applications with highest power requirements.

#### 2.2.3 PowerBLOCK-Module

The PowerBLOCK-Module is a case concept which in itself provides sufficient pressure to the semiconductor element. In addition, defined isolation against the base plate is provided. This simplifies the application of the modules significantly, as a complete rectifier for example may be constructed on a common heatsink. Due to the single sided cooling and the limits of the isolation voltage, possibilities of its application in the high power area are limited.

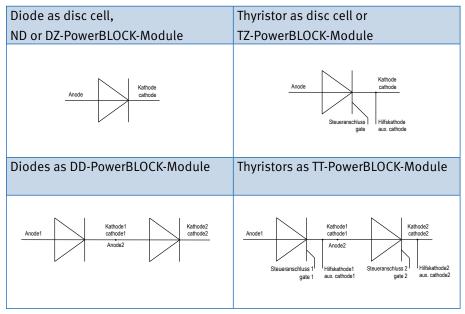

Figure 6 Construction concepts of pressure contact components

#### 2.2.4 Stud type and flat case constructions

In stud (screw) type and flat case constructions the semiconductor element is already pressed correctly. These case types are now out-dated and mostly replaced by the more powerful PowerBLOCK-Module.

## 3. Electrical properties

The electrical properties of diodes and thyristors are temperature dependent and therefore valid only in conjunction with a temperature specification.

All values mentioned in the data sheets are applicable to mains frequency 40 to 60Hz if not otherwise specified.

Maximum values are those values given by the manufacture as the absolute limits which generally even for short times may not be exceeded as this may lead to a functional deterioration or destruction of the components. Characteristic values are ranges of data distribution at defined conditions and may form the basis of incoming inspection.

#### 3.1 Forward direction

For diodes

the forward direction is the direction between the main terminals in which the diode has reached conduction mode even at a low voltage of just a few volts (see Figure 1, direction anode-cathode).

#### For thyristors

the forward direction is the direction between the main terminals in which the thyristor may operate in two stable modes – the on- and the off-state - (see Figure 3, direction anode-cathode).

Addition of the words "positive" or "forward" is used to expressly distinguish currents and voltages in forward direction from those in reverse direction.

The forward characteristic of the thyristor consists of an off-state and an on-state region (see Figure 4).

The forward off-state characteristic is that part of the forward characteristic of a thyristor which illustrates the instantaneous values of the forward off-state current and the forward off-state voltage.

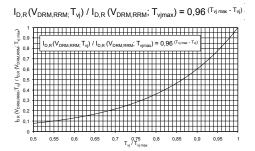

**Figure 7** Typical dependence of the off-state current  $i_{D,R}(V_{DRM,RRM})$  referenced to  $I_{D,R}(V_{DRM,RRM}; T_{vj\;max})$  on the junction temperature  $T_{vj}$  referenced to  $T_{vj\;max}$

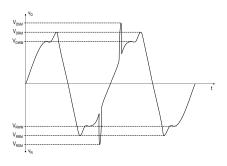

**Figure 8** Definition of the off-state voltage occurrences

### 3.1.1 Forward off-state current i<sub>D</sub>

$i_D$  is the current which flows in forward direction through the main terminals in the off-state condition of the thyristor. In the data sheet it is specified for the voltage  $V_{DRM}$  and the maximum junction temperature  $T_{v_{j\,max}}$ .

This current depends on the junction temperature  $T_{vi}$  (see Figure 7).

#### 3.1.2 Forward off-state voltage v<sub>D</sub>

$v_{\text{D}}$  is the voltage which is applied across the main terminals in forward direction during the off-state condition of the thyristor.

## 3.1.2.1 Repetitive peak forward off-state voltage $V_{\text{DRM}}$

$V_{\text{DRM}}$  is the maximum value of repetitive voltages in the forward off-state direction including all repetitive peak voltages.

In DC applications a reduction to  $V_{D\ (DC)}$  is necessary. See also section 3.1.2.3. In view of transient voltages occurring in operation, thyristors are usually operated at supply voltages of which the peak value is equal to the maximum rated repetitive peak off-state voltage divided by a safety factor of between 1.5 and 2.5.

$$\hat{\mathbf{V}}_{line} = \mathbf{V}_{DWM,RWM} \frac{\mathbf{V}_{DRM}^{bzw.} \mathbf{V}_{RRM}}{1,5...2,5}$$

A low safety factor is used where the transient voltages mostly known. These are generally self commutated converters with large energy storage. For converters supplied from mains with unknown transient levels a safety voltage margin of 2.0 to 2.5 is preferable.

If transient voltages are likely to occur in operation, which exceed the maximum permissible repetitive peak off-state voltage, a suitable transient voltage protection network has to be provided (see 7.1).

#### 3.1.2.2 Non-repetitive peak forward off-state voltage V<sub>DSM</sub>

$V_{\text{DSM}}$  is the maximum rated non-repetitive peak value of a voltage in forward direction on the thyristor which must not be exceeded.

#### 3.1.2.3 Forward direct off-state voltage V<sub>D (DC)</sub>

$V_{D (DC)}$  is the permanently allowable direct voltage in forward direction in off-state mode. For the semiconductors described here the value is rated at approximately half repetitive peak off-state voltage. This is valid for a failure probability of approximately 100 fit (failure in time; 1fit = 1\*10.9 failures per hour, i.e. one failure in 109 operating hours of the device). Probabilities of failure to be expected for varying DC-voltages are available on request.

#### 3.1.3 Forward breakover voltage $V_{(BO)}$

$V_{(BO)}$  is the value of the off-state voltage in forward direction at which for a given gate current the thyristor switches from the off-state to the on-state.

*Exception:* For light triggered thyristors (LTT's) with integrated breakover diode (BOD)  $V_{(BO)}$  is the minimum voltage at which protective triggering of the thyristor occurs

#### 3.1.4 Open gate forward breakover voltage V<sub>(BO)0</sub>

$V_{(BO)0}$  is the breakover voltage at zero gate current. Triggering the thyristor by exceeding the  $V_{(BO)0}$  may cause destruction of the device.

Exception: Light triggered thyristors are protected by an integrated breakover diode (BOD).

#### 3.1.5 Holding current I<sub>H</sub>

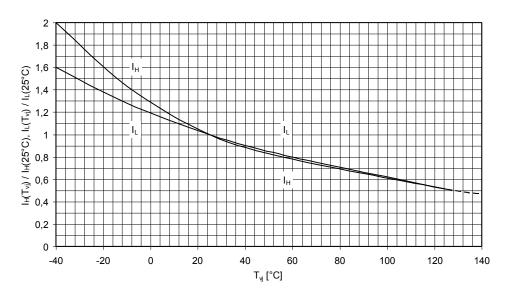

$I_H$  is the minimum value of on-state current required to maintain the thyristor in on-state.  $I_H$  drops with raising junction temperature (see Figure 9).

Light triggered thyristors show a significantly lower holding current than comparable electrically triggered thyristors.

#### 3.1.6 Latching current I

$I_L$  is the on-state current required to maintain the thyristor in the on-state once the gate current has decayed. It depends on the rate of change, peak and duration of the gate current as well as on the junction temperature (see Figure 9).

*Exception:* Light triggered thyristors show a significantly lower latching current than comparable electrically triggered thyristors.

#### 3.1.7 On-state current i<sub>T</sub>, I<sub>TAV</sub>, I<sub>TRMS</sub> i<sub>F</sub>, I<sub>FAV</sub>, I<sub>FRMS</sub>

The on-state current is the current which flows via the main terminals in the on-state of the thyristor ( $i_T$ ,  $I_{TAV}$ ,  $I_{TRMS}$ ) or the diode ( $i_F$ ,  $I_{FAV}$ ,  $I_{FRMS}$ ). It is differentiated in:

$i_T$ ,  $i_F$  = instantaneous value

$I_{TAV}$ ,  $I_{FAV}$  = average value

$I_{TRMS}$ ,  $I_{FRMS} = RMS$  (route mean square)

Figure 9 Typical dependence of the latching current  $I_L$  and holding current  $I_H$  normalized to  $T_{vj}$ =25°C of the junction temperature  $T_{vi}$

#### 3.1.8 On-state voltage $v_T$ , $v_F$

$v_T$ ,  $v_F$  is the voltage across the main terminals at the defined on-state current. It depends on the junction temperature. Values given in the data sheet are valid for the completely turned on thyristor  $(v_T)$  or for the diode  $(v_F)$ .

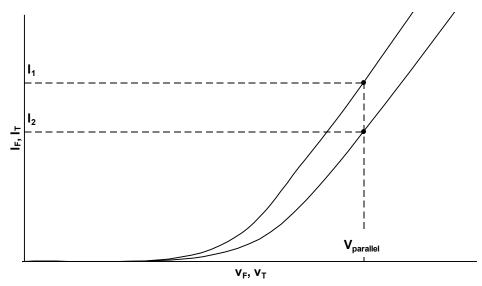

#### 3.1.9 On-state characteristic

The on-state characteristic is the relation of the instantaneous values of on-state current and on-state voltage for the diode or for the completely turned on thyristor at a defined junction temperature.

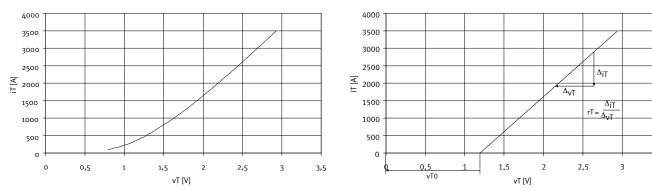

#### 3.1.10 Equivalent line approximation with $V_{T(TO)}$ , $V_{F(TO)}$ and $r_T$

The equivalent line is an approximation to the on-state characteristic of a thyristor  $(V_{T(TO)}, r_T)$  or of a diode  $(V_{F(TO)}, r_T)$  to calculate the on-state power dissipation. Given are:

$V_{T(TO)}$ ,  $V_{F(TO)}$  = threshold voltage

$r_T$  = differential resistance or slope resistance

The value of  $V_{T(TO)}$ ,  $V_{F(TO)}$  results from the intersection of the equivalent line approximation and the voltage axis, the value of  $r_T$  is calculated from the rate of raise of the equivalent line. Depending on the cooling it may be necessary to adapt the equivalent lines shown in the data sheet to the application. In some data sheets there may hence be an additional low level value for  $V_{T(TO)}$ ,  $V_{F(TO)}$  and  $r_T$ .

For components with high blocking voltages (T...1N, T...3N, D...1N) equivalent lines are shown in addition as an approximation to a typical on-state characteristic which describes approx. the 50% value in the statistical distribution. In applications in which many equal components are used the conduction losses of the entire installation can be calculated using the typical equivalent line approximation.

Figure 10 Example of an on-state characteristic and the matching equivalent line approximation

#### 3.1.11 Maximum average on-state current I<sub>TAVM</sub>, I<sub>FAVM</sub>

$I_{TAVM}$ ,  $I_{FAVM}$  is the maximum permissible continuous average value of the on-state current in a single phase half-wave resistive load circuit according to DIN VDE 0558, part 1 rated at a defined case temperature  $T_{C}$  and a frequency of 40 to 60Hz.

A diagram is given in the data sheets of the thyristors or diodes with low blocking voltages which shows the maximum average on-state current versus the maximum allowable case temperature  $T_C$  for various current conduction angles.

This diagram takes only the conduction losses into account. For components with high blocking voltages (>2200V) additional turn-off losses and to some degree blocking and turn-on losses need to be considered. For components with very high blocking voltages (>4kV) this diagram is, therefore, omitted in the data sheet.

## 3.1.12 Maximum RMS on-state current $I_{TRMSM}$ , $I_{FRMSM}$

$I_{TRMSM}$ ,  $I_{FRMSM}$  is the maximum value of RMS on-state current permissible considering electrical and thermal stresses of all assembly parts of the device. This current must not be exceeded for flat base and stud type cases and modules even under the best cooling conditions of the thyristor ( $I_{TRMSM}$ ) or the diode ( $I_{FRMSM}$ ).

## 3.1.13 Overload on-state current $I_{T(OV)}$ , $I_{F(OV)}$

$I_{T(OV)}$ ,  $I_{F(OV)}$  is the maximum allowable value of on-state current that the thyristor ( $I_{T(OV)}$ ) or the diode ( $I_{F(OV)}$ ) may conduct in short time operation without losing its control property. In the diagram for overload on-state current it is given as the peak value at 50Hz sinusoidal half-waves for different preloads versus time t.

This illustration does not take into account increased blocking or turn-off losses as they occur for devices with high blocking voltages. For components with very high blocking voltages (>4kV) this diagram is, therefore, omitted in the data sheet.

#### 3.1.14 Maximum overload on-state current I<sub>T(OV)M</sub>, I<sub>F(OV)M</sub>

$I_{T(OV)M}$ ,  $I_{F(OV)M}$  is the value of on-state current at which the device must be turned off in order not to destroyed the thyristor ( $I_{T(OV)M}$ ) or the diode ( $I_{F(OV)M}$ ). These values are intended for the design of the protection networks. The thyristor may temporarily lose its forward blocking capability when the current flowing through it reaches this value and may temporarily lose its control properties.

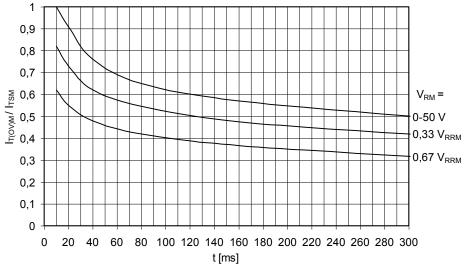

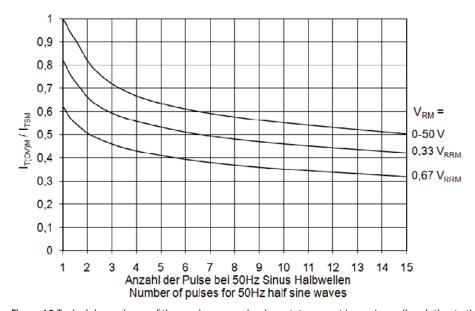

The maximum overload on-state current characteristic shows this value as the peak value of a 50Hz sinusoidal half-wave versus time t. Two conditions are differentiated: no load operation preceding and operation with maximum average on-state currents preceding.

3,5

The maximum overload on-state current characteristics given in the individual data sheet applies to a reverse blocking voltage of 80% of the repetitive peak reverse voltage. In cases where the actual reverse voltage is lower, a higher maximum overload on-state current is allowable which is shown in Figure 11 and Figure 12 for a preceding continuous maximum overload on-state current I<sub>TAVM</sub>. The conditions for a device without preceding load can not be determined from this.

This illustration does not take into account increased blocking or turn-off losses as they occur for devices with high blocking voltages. For components with very high blocking voltages (>4kV) this diagram is, therefore, omitted in the data sheet. The protection concepts for these devices are described in chapter 7.2.

Figure 11 Typical dependence of the maximum overload on-state current  $I_{T(OV)M}$ ,  $I_{F(OV)M}$  (in relation to the surge current  $I_{TSM}$  or  $I_{FSM}$  for 10ms and  $T_{v_j \text{ max}}$ ) on the number of half-sinewaves at 50Hz.

Parameter: reverse blocking voltage  $V_{RM}$

Figure 12 Typical dependence of the maximum overload on-state current  $I_{T(OV)M}$ ,  $I_{F(OV)M}$  (in relation to the surge current  $I_{TSM}$  or  $I_{FSM}$  for 10ms and  $T_{v_j \; max}$ ) on the time t for a number of half-sinewaves at 50Hz. Parameter: reverse blocking voltage  $V_{RM}$

### 3.1.15 Surge on-state current I<sub>TSM</sub>, I<sub>FSM</sub>

$I_{TSM}$ ,  $I_{FSM}$  is the maximum permissible peak value of a single half sine-wave 50Hz current pulse. It is specified at 25°C (equates to a short circuit from no load condition) or at

turn-on at maximum permissible junction temperature (equates short circuit after

permanent load with maximum permissible current). When stressing a semiconductor with the surge on-state current, the device loses its blocking capability. Therefore, no negative voltage shall subsequently be applied. This stress may be repeated during fault conditions in a non-periodic way provided the junction temperature has dropped to

values within the permissible operating temperature area.

When exceeding the maximum permissible value destruction of the device is risked (for details please see chapter 7.2 over current protection).

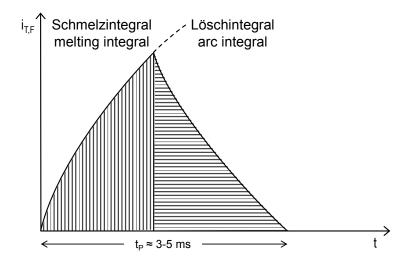

#### 3.1.16 Maximum rated value si2dt

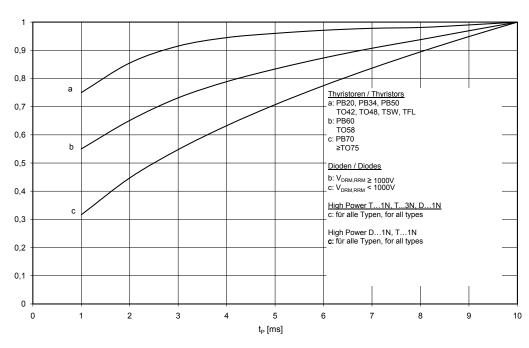

si<sup>2</sup>dt is the square of the surge on-state current integrated over time.

The maximum rated si²dt-value serves to determine the short-circuit protection (see 7.2).

For half-sinewaves with periods shorter than 10ms the maximum rated  $\int_{0}^{2} dt$ -value is shown in Figure 13. Regarding voltage stress and repetition the same applies as for the surge on-state current. When exceeding the maximum permissible value, destruction of the device is risked. In addition, in particular for large diameter thyristors, it has to be observed that the permissible critical turn-on current rate of change  $(di/dt)_{cr}$  may not be exceeded.

Figure 13 Typical dependence of the  $\delta i^2$  dt normalized to the value  $\delta i^2$  dt (10ms) on the half-sinewave duration  $t_p$

#### 3.2 Reverse direction

The reverse direction is the direction from one main terminal to the other in which the thyristor and diode is in a stable high resistance state of operation (direction cathode-anode).

If values (voltages and currents) and data in reverse direction are to be distinguished from those in forward direction, then the term "reverse" or "negative" is used.

The reverse blocking characteristic of a thyristor or a diode represents the instantaneous values of reverse current and reverse voltage.

#### 3.2.1 Reverse current i<sub>R</sub>

$i_R$  is the current flowing in reverse direction through the main terminal of the thyristor or diode. The reverse current depends on the reverse voltage and the junction temperature  $T_{vi}$  (Figure 7)

#### 3.2.2 Reverse voltage V<sub>R</sub>

$V_R$  is the voltage applied across the main terminals of the thyristor or diode in reverse direction.

#### 3.2.2.1 Repetitive peak reverse voltage V<sub>RRM</sub>

$V_{RRM}$  is the maximum permissible instantaneous value of repetitive voltages in reverse direction including all repetitive peak voltages.

In DC applications a reduction to  $V_{R (DC)}$  is necessary.

See also section 3.2.2.3.

For supply voltage see section 3.1.2.1.

#### 3.2.2.2 Non-repetitive peak reverse voltage V<sub>RSM</sub>

$V_{\text{RSM}}$  is the maximum allowable non-repetitive peak value of a transient voltage in reverse direction which must not be exceeded even for the shortest duration. The value resulting is:

For blocking voltages < 800V:

$$V_{RSM} = V_{RRM} + 50V \text{ (at } T_{vi} = 25^{\circ}\text{C ... } T_{vi \text{ max}})$$

For blocking voltages ≥ 800V:

$$V_{RSM} = V_{RRM} + 100V \text{ (at } T_{vi} = 25^{\circ}\text{C ... } T_{vi \text{ max}})$$

#### 3.2.2.3 Direct reverse voltage $V_{R(DC)}$

$V_R$  (DC) is the permanently allowable direct voltage in reverse direction, analogous to forward direct off-state voltage 3.1.2.3.

## 3.3 Control properties of thyristors

#### 3.3.1 Positive gate control

#### 3.3.1.1 Gate current i<sub>G</sub>

$i_G$  is the current flowing through the control path (terminals G – HK).

Thyristors shall only be pulse triggered during the forward off-state phase.

Positive trigger pulses during the reverse off-state phase will lead to significantly increased off-state losses due to the transistor effects caused. These losses adversely affect the functionality and may lead to destruction. Exception: For light triggered thyristors control pulses during the reverse off-state phase are permissible.

#### 3.3.1.2 Gate voltage V<sub>G</sub>

$V_G$  is the positive voltage across the gate terminal (G) and the cathode (K) or auxiliary cathode (HK).

#### 3.3.1.3 Gate trigger current I<sub>GT</sub>

$I_{GT}$  is the minimum value of gate current which causes the thyristor to trigger. It depends on the voltage across the main terminals and the junction temperature. At the given value of the gate trigger current all thyristors of a given type will trigger. The gate trigger current increases with lower junction temperature and is thus specified at 25°C.

The trigger pulse generator has to safely exceed the data sheet value I<sub>GTmax</sub> (see also 3.3.1.8).

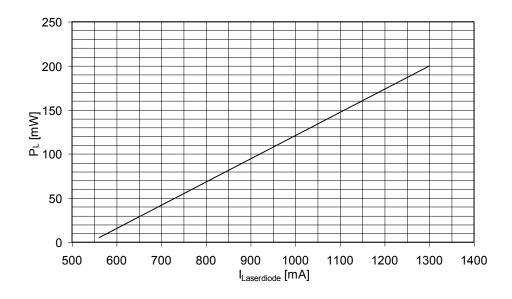

Exception: For light triggered thyristors the minimum light power  $P_L$  is specified which causes all thyristors of a given type to trigger.

#### 3.3.1.4 Gate trigger voltage V<sub>GT</sub>

$V_{GT}$  is the voltage which occurs across gate terminal and cathode when the gate trigger current  $I_{GT}$  flows. It depends on the voltage across the main terminals and the junction temperature. At the given value of the gate trigger voltage all thyristors of a given type will trigger. The gate trigger voltage drops with increasing junction temperature and is thus specified at 25°C.  $V_{GT}$  is measured when a specified load current flows.

#### 3.3.1.5 Gate non-trigger current I<sub>GD</sub>

$I_{GD}$  is the value of the gate current which does just not cause the thyristor to trigger. It depends on the voltage across the main terminals and the junction temperature. At the given maximum value no thyristor of a given type triggers. The gate non-trigger current decreases with increasing junction temperature and is thus specified at  $T_{vi\,max}$ .

#### 3.3.1.6 Gate non-trigger voltage V<sub>GD</sub>

V<sub>GD</sub> is the value of the gate voltage which does just not cause the thyristor to trigger.

It depends on the voltage across the main terminals and the junction temperature. At the given maximum value no thyristor of a given type triggers. The gate non-trigger voltage decreases with increasing junction temperature and is thus specified at  $T_{vi max}$ .

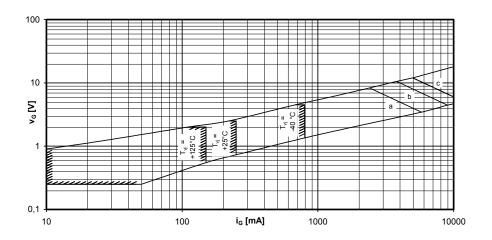

Figure 14 Example for control characteristic  $v_G = f(i_G)$  with trigger area for  $V_D = 12 \text{ V}$

#### 3.3.1.7 Control characteristic

It shows the limits of statistical distribution of the input characteristics of a thyristor type. Within the distribution of the input characteristics the temperature dependent trigger areas are detailed as well as the curves of the maximum permissible gate power dissipation  $P_{\text{GM}}$  (a - 20W / 10ms, b - 40W / 1ms, c - 60W / 0.5ms).

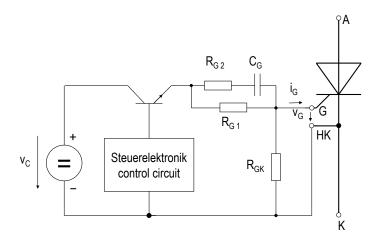

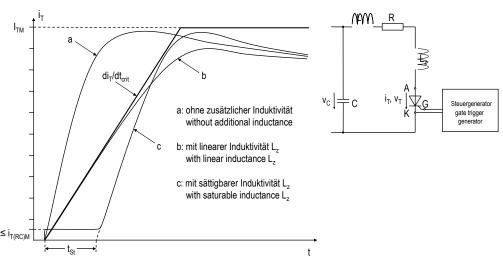

#### 3.3.1.8 Control circuit

In a normal application the design of the control circuit should be done in accordance with the control data which are detailed in connection with the critical rise time of the on-state current, the gate control delay time and the latching current (see Figure 15). The minimum control data given in 3.3.1.3 and 3.3.1.4 are valid only for applications with low requirements with regard to critical current rise time and gate control delay time. In reality overdriving  $I_{\rm GT}$  specified in the data sheet 4- to 5-fold assures safe operation even with high requirements for current rise time and gate control delay time.

Terms used in this context are:

$di_G/dt = gate current slew rate$

i<sub>GM</sub> = peak gate current

$t_G$  = duration of the trigger pulse

$V_1$  = open circuit voltage of the control circuit

With increasing slew rate of the on-state current  $di_T/dt$  as well as repetitive turn-on current  $I_{T(RC)M}$  from the snubber an effect from the load circuit to the gate current  $i_G$  is notable (see 3.4.1.2 and Figure 21).

Figure 15 Concept of a trigger circuit for thyristors

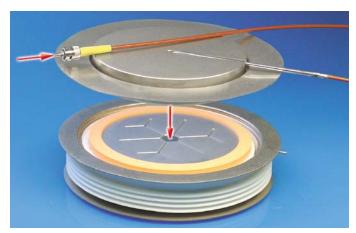

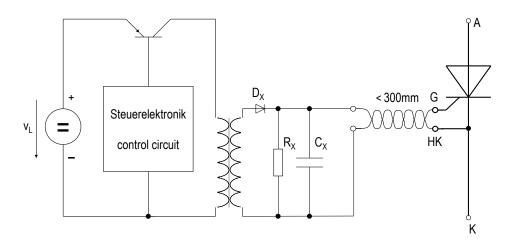

Initially there is only a small area around the gate area on the pellet conductive during turn-on of the thyristor which leads to high current density and increased voltage. Due to internal coupling this voltage also appears at the control terminals and, therefore, leads to an intermediate drop of the gate trigger current. In order to avoid the possible destruction of the thyristor,  $i_G$  should not drop below the value of the gate trigger current  $I_{GT}$ . To prevent the gate pulse from dropping too low, a compensation by means of a higher open circuit voltage  $V_C$  of the trigger circuit may be necessary. For parallel or series connection of thyristors high, steep rising and synchronous trigger pulses are necessary in order to achieve equalised turn-on. See also distribution of gate control delay time values (3.4.1.2.1). Exception: To control light triggered thyristors, laser diodes emitting light in the region of 900 to 1000nm are required. Minimum values for light power  $P_C$  are given which in conjunction with the given turn-on voltage will assure safe triggering of the thyristors. The light power is specified at the output of the fibre optic cable. With regard to even turn-on here too overdriving is recommended in particular for parallel and series connection with high di/dt requirements.

Infineon recommends the application of the laser diodes SPL PL90 aligned in the appropriate fitting (see Figure 16) and offers these together with suitable fibre optic cables as ancillary equipment.

Figure 16 LTT with fibre optic cable

The laser diodes SPL PL 90 comply with the following laser classes: If the laser diode is correctly terminated with the fibre optic cable the control system complies with laser class 1. No operational hazard.

With open operation of the laser diode or in case of a broken fibre optic cable, the system equates to the laser class 3b according to IEC 60825–1. In this case hazard of operation exists due to invisible radiation. Direct or indirect exposure to the eyes or skin is to be avoided.

Figure 17 Laser diode SPL PL 90 typical dependence of the light power on the control current

To control light-triggered thyristors, we recommend a current pulse for the laser diode SPL PL90 as in Figure 18. As the laser diode SPL PL90 is not suitable for long-term control, we recommend controlling the laser diode with a frequency of approximately 6kHz, while using the pulse in Figure 18.

Figure 18 Recommended current pulse for laserdiode SPL PL 90

## 3.3.1.9 Minimum duration of the trigger pulse $t_{\rm gmin}$

The trigger pulse has to be applied at least until the latching current of the thyristor (3.1.6) has been exceeded, as otherwise the thyristor will return to its off-state. The gate trigger current of the thyristor must remain at least at its rated value until the end of the trigger pulse.

In applications with very low current rise times or low load currents often a trigger profile with multiple pulses is used (e.g. with a frequency of repetition of 6kHz).

For light triggered thyristors make sure that when using multiple pulses the laser diode does not heat up inadmissibly. The light power of a current controlled laser diode drops with increasing temperature.

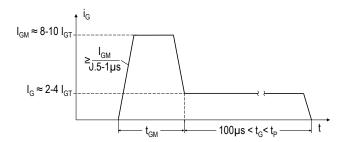

#### 3.3.1.10 Maximum permissible peak trigger current

In applications with a high rate of rise of current  $i_{GT}$  may be overdriven even harder than described in 3.3.1.8. For this the gate current should be increased for a time  $t_{GM} \approx 10\text{-}20\mu\text{s}$  to the 8- to 10-fold value of  $I_{GT}$  and than continue for a sufficient time  $t_G$  with a reduced amplitude. The open circuit voltage of the trigger circuit should at least apply 30V in order to assure a high reactionless gate current.

Figure 19 Safe overdrive of the gate trigger current

## 3.4 Carrier storage effect and switching characteristics

When the state of operation changes in power semiconductors, the stationary values of current and voltage do not change immediately due to the carrier storage effect. Additionally, in thyristors only small areas around the gate structure become conductive when triggered. The switching losses resulting from this have to be dissipated as heat from the semiconductor.

#### 3.4.1 Turn-on

#### 3.4.1.1 Diode

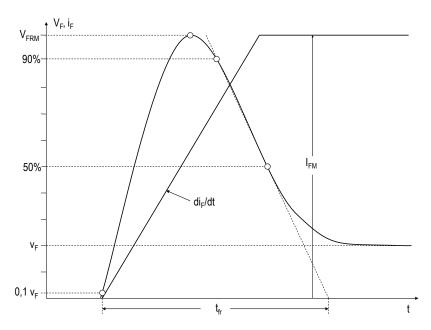

When passing from a non-conducting or blocked state to a conducting state, voltage peaks occur at the diode due to the carrier storage effect (see Figure 20).

Figure 20 Schematic representation of a diode turn-on process

#### 3.4.1.1.1 Peak value of the forward recovery voltage V<sub>FRM</sub>

$V_{\text{FRM}}$  is the highest voltage value occurring during the forward recovery time (see Figure 20). It increases with rising junction temperature and current slew rate.

In mains operation (50 / 60Hz) with its moderate current slew rates  $V_{FRM}$  is negligible. In self-commutated converters with fast switches di/dt>1000A/us (IGBT's, GTO's and IGCT's), however, it may reach values up to several hundred volts. Although the forward recovery voltage exists for just a few microseconds and thus does not contribute to the sum of losses of the diodes in a significant way, its effect on the switching semiconductor has to be considered when designing the converter.

In diagrams for diodes optimized for these applications data is included which details the forward recovery voltage as a function of the current slew rate.

#### 3.4.1.1.2 On-state recovery time $t_{fr}$

According to DIN IEC 60747-2  $t_{fr}$  is the time the diode needs to become fully conducting and a static on-state voltage  $v_{F}$  appears, when suddenly switched from zero to a defined on-state (see Figure 20).

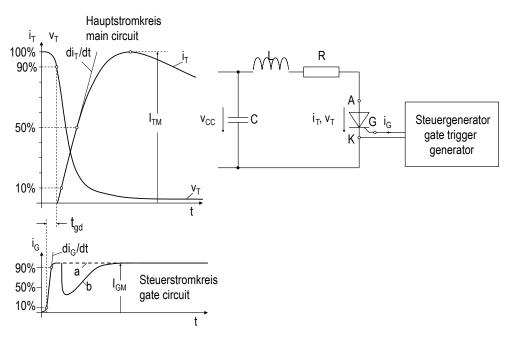

#### 3.4.1.2 Thyristor

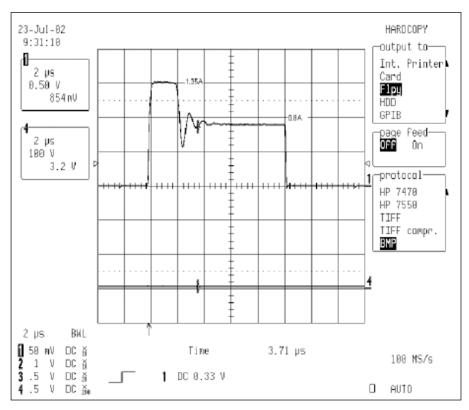

The turn-on process is initiated at forward off-state voltage  $v_D$  by a gate current with a slew rate  $di_G/dt$  and a magnitude  $i_{GM}$ . For light triggered thyristors this applies to an equally specified trigger pulse on the laser diode. During the gate controlled delay time  $t_{gd}$  the blocking voltage across the thyristor drops to 90% (see Figure 21). As initially only a small area around the gate structure becomes conductive, the initial current density and thus the critical rate of rise of on-state current  $(di/dt)_{cr}$  is a gauge for the robustness of the thyristor during turn-on.

Figure 21 Schematic representation of a thyristor turn-on process

- a gate current with turned off load circuit

- b gate current with steeply rising on-state current (see also 3.3.1.8)

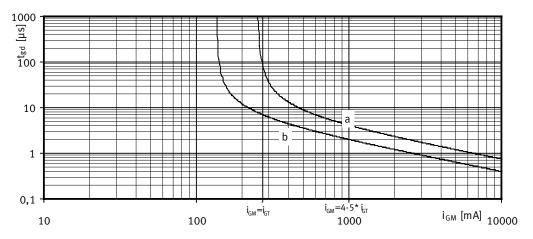

Figure 22 Typical dependence of the gate controlled delay time  $t_{gd}$  and the maximum gate current  $i_{GM}$  a) maximum value b) typical value

#### 3.4.1.2.1 Gate controlled delay time $t_{gd}$

$t_{gd}$  is the period between the gate current reaching 10% of its maximum value  $I_{GM}$  and the time when the anode-cathode voltage drops below 90% of the applied forward off-state voltage  $v_D$  (see Figure 21).

It reduces significantly with increasing gate current (light power for LTTs) (see Figure 22). In high power thyristors the  $t_{\rm gd}$  depends also on  $v_{\rm D}$ .

The value given in the data sheet is defined according to DIN IEC 60747 – 6 and is valid for  $T_{vi} = 25$ °C and specified trigger pulse.

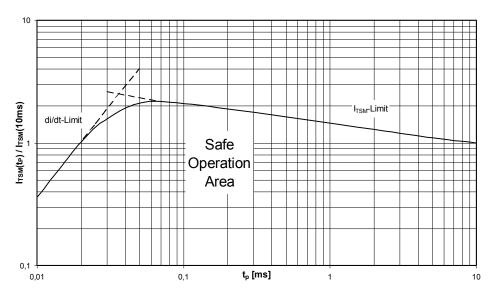

#### 3.4.1.2.2 Critical rate of rise of the on-state current (di/dt)<sub>cr</sub>

Once the voltage has collapsed due to the thyristor triggering a small area of the cathode around the gate structure begins to conduct on-state current. This current conducting area then spreads out depending on the current density with a speed of typically  $0.1 \text{mm/}\mu\text{s}$ . The current carrying capability of the system is therefore limited in the beginning. Damage or destruction of the thyristor is impossible, however, when the value given in the data sheet for the critical current slew rate is not exceeded. For S-thyristors and thyristors with large square sections the gate is distributed (finger structure). Therefore, these types show a higher  $(\text{di/dt})_{cr}$ .

According to DIN IEC 60747 - 6 the critical current rise time  $(di/dt)_{cr}$  refers to loading with on-state current over the period of a dampened half sine-wave. It is defined as the angle of a straight line through the 10% and 50% points of the rising on-state current (see Figure 21, Figure 47) whilst the following conditions apply:

Junction temperature  $T_{vj} = T_{vj \text{ max}}$ Forward off-state voltage  $v_D = 0.67 \text{ V}_{DRM}$ , Peak current value  $i_{TM} = 2 \text{ I}_{TAVM}$ Frequency of repetition  $f_0 = 50 \text{ Hz}$  The trigger pulse is defined in the individual data sheets (see also 3.3.1.8).

Exception: Light triggered thyristors are tested with a forward off-state voltage of  $v_D = V_{DRM}$ .

#### 3.4.1.2.3 Repetitive turn-on current $I_{T(RC)M}$

$I_{T(RC)M}$  is the maximum permissible peak value of the on-state current immediately after turn-on with undefined rate of rise. In general this turn-on current is caused by the discharge of the RC-snubber network. The maximum permissible repetitive turn-on current also applies to the following steep current rise up to the critical rate of rise of the on-state current (di/dt)<sub>cr</sub>.

For Infineon components the following values apply

$I_{T(RC)M} = 100A$

Exception: Component with the type designation T...1N or T...3N

$I_{T(RC)M} = 150A$

For applications above 60Hz the values for both the critical current rise time  $(di/dt)_{cr}$  as well as the repetitive turn-on current  $I_{T(RC)M}$  have to be reduced. Further details for particular conditions on request.

#### 3.4.1.2.4 Critical rate of rise of off-state voltage (dv/dt)cr

$(dv/dt)_{cr}$  is the maximum value for the rate of rise of a voltage applied in forward direction running almost linearly from 0% to 67% of  $V_{DRM}$  at which a thyristor will not switch to the on-state.

For an exponential rate of voltage rise it is a line which crosses the exponential function starting from 0% to 63% of the maximum value.

It applies for open trigger circuit and maximum permissible junction temperature. Exceeding  $(dv/dt)_{cr}$  may cause destruction.

Exception: Aside from the over-voltage protection (BOD) light triggered thyristors have an integrated dv/dt protection. This causes the thyristors to trigger safely over the entire gate structure when the dv/dt gets to high.

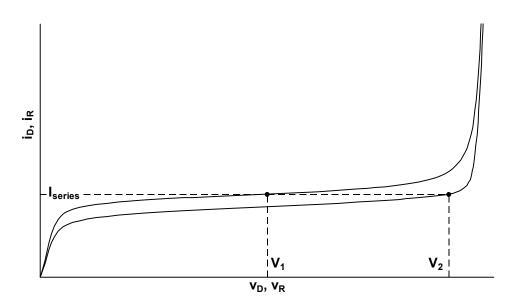

#### 3.4.2 Turn-off

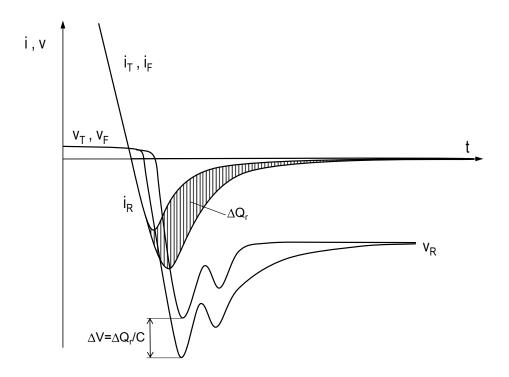

Turning off is usually started by application of a reverse voltage. The load current of the thyristor or the diode does not cease at the zero crossing but continues to flow briefly in reverse direction as reverse recovery current until the carriers have left the junction region.

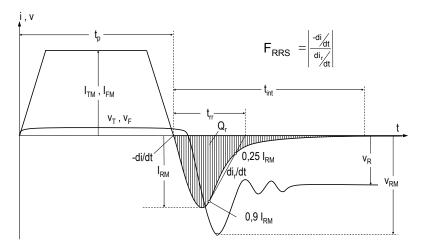

The softness factor F<sub>RRS</sub> describes the relation of the rates of rise of the currents during the turn-off process.

#### 3.4.2.1 Recovery charge Q<sub>r</sub>

$Q_r$  is the total amount of charge flowing out of the semiconductor after switching from on-state to reverse off-state. It increases with rising junction temperature as well as magnitude and fall time of the on-state current. If not otherwise specified, the given values are valid for  $v_R = 0.5V_{RRM}$  and  $v_{RM} = 0.8V_{RRM}$  and are not exceeded by 95% of the individual types of thyristors or diodes. For this an appropriately designed RC-snubber network is specified. For components with the type designation T...1N, T...3N and D...1N the given values in the data sheet are maximum values which are 100% tested in production.

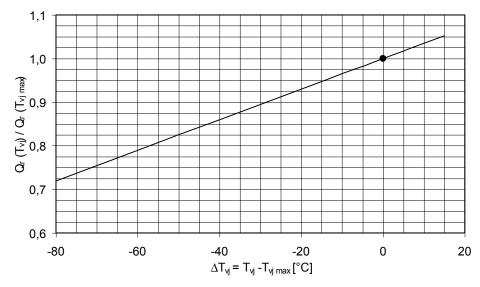

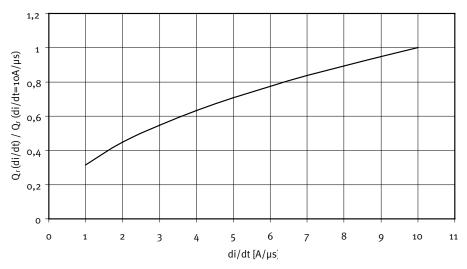

The recovery charge  $Q_r$  is mainly dependent on the junction temperature  $T_{vj}$  and on the rate of fall of the decaying current (see Figure 24 and Figure 25).

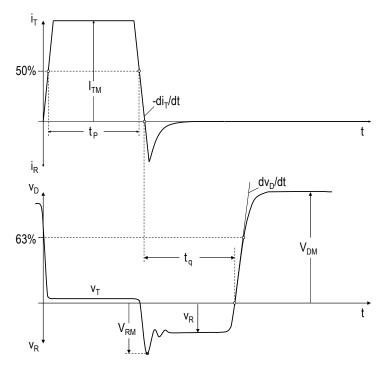

Figure 23 Schematic representation of the thyristor and diode turn-off process

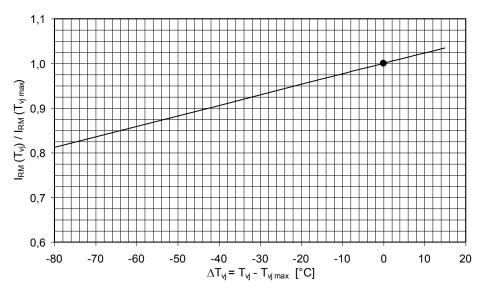

$\textbf{Figure 24} \ \text{Typical} \ T_{vj} \text{-} dependence of the recovery charge} \ Q_r \ normalized \ to \ Q_r (T_{vj \ max})$

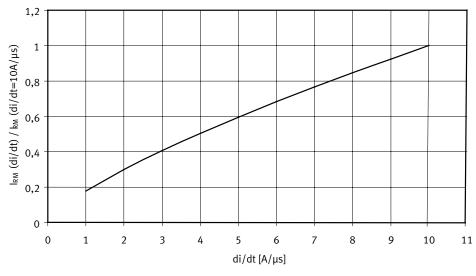

Figure 25 Typical di/dt-dependence of the recovery charge  $Q_r$  normalized to  $Q_r$  (di/dt=10A/ $\mu$ s)

#### 3.4.2.2 Peak reverse recovery current I<sub>RM</sub>

$I_{RM}$  is the maximum value of the reverse recovery current. The dependences and operating conditions given for  $Q_r$  also apply. If  $I_{RM}$  is not shown in the diagrams, its value may be approximately determined as follows:

$$I_{RM} \approx \sqrt{\frac{\left|-\frac{di}{dt}\right| \cdot Q_r}{1...1, 3}}$$

For components with the type designation T...1N, T...3N and D...1N the given values in the data sheet are maximum values which are 100% tested in production.

The peak reverse recovery current  $I_{RM}$  is mainly dependent on the junction temperature  $T_{vj}$  and on the rate of fall of the decaying current (see Figure 26 and Figure 27).

Figure 26 Typical  $T_{vj}$ -dependence of the peak reverse recovery current  $I_{RM}$  normalized to  $I_{RM}$  ( $T_{vj \ max}$ )

$\textbf{Figure 27} \ \textit{Typical di/dt-dependence of the peak reverse recovery current I}_{RM} \ \textit{normalized to I}_{RM} \ (\textit{di/dt=10/\mu s})$

#### 3.4.2.3 Reverse recovery time t<sub>rr</sub>

$t_{rr}$  is the time interval between the zero crossing of the current and the time at which a straight line through the 90% and 25% points of the decaying reverse recovery current crosses the zero line (see Figure 23). Should  $t_{rr}$  not be specified, its value may be approximately calculated with the following formula:

$$t_{rr} \approx \frac{2 \cdot Q_r}{I_{RM}}$$

#### 3.4.2.4 Turn-off time $t_a$

$t_{\rm q}$  is the time interval between the zero crossing of the current commutated in reverse direction and the reapplication of forward off-state voltage at which a thyristor does not turn-on without a control pulse.

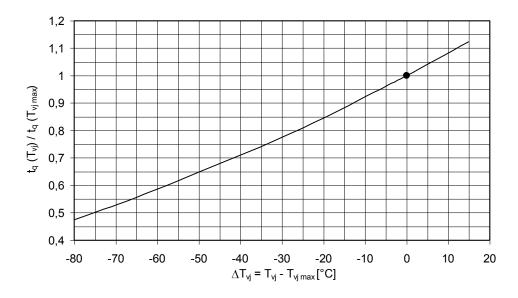

The actual pause time realised in the application before the forward off-state voltage reoccurs is called hold-off time. This time must always be greater than the turn-off time. The turn-off time mainly depends on the fall time of the on-state current, the rate of rise of the forward off-state voltage and the junction temperature (see Figure 29 - Figure 31). To determine  $t_q$  the duration  $t_p$  of the forward current has to be chosen long enough so that the thyristor at the point of commutation is completely turned on (see Figure 28). The values given in the data sheets are valid for following conditions:

| Junction temperature                          | $T_{vj} = T_{vj max}$   |

|-----------------------------------------------|-------------------------|

| Magnitude of on-state current                 | $i_{TM} \ge I_{TAVM}$   |

| Fall rate of the on-state current             | $-di_T/dt = 10 A/\mu s$ |

| Reverse voltage                               | $V_{RM} = 100V$         |

| Rate of rise of the forward off-state voltage | $dv_D/dt = 20V/\mu s$   |

| Forward off-state voltage                     | $V_{DM} = 0.67 V_{DRM}$ |

Exception: Fast thyristors were commutated off with a current rate of fall of  $-di/dt=20A/\mu s$ . The  $dv_D/dt$  may vary here and is specified by the 5th letter in the type designation (see section 2.3).

For phase controlled thyristors usually typical values for the turn-off time are given as they are mainly employed in line commutated converters. In these applications the hold-off time is generally much longer than the turn-off time of the thyristor. If the hold-off time is shorter than the turn-off time, the thyristor will once again turn-on with rising forward off-state voltage without application of a trigger pulse and destruction may be caused ( $t_q$ -limit values on request if necessary).

If the thyristor is operated together with an inverse diode (for example free wheeling diode), much longer turn-off times have to be taken into consideration due to the low commutation voltage (typically 30% longer). Additionally, in such applications the inductance of the free wheeling circuit should be minimised as otherwise the turn-off time may increase to significantly higher values.

Figure 28 Schematic representation of the turn-off behaviour of a thyristor

Figure 29 Typical dependence of the turn-off time  $t_q$  normalized to  $T_{v_j max}$  on the junction temperature  $T_{v_j}$

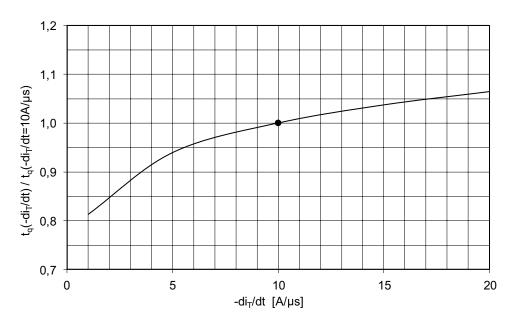

$\textbf{Figure 30} \ \text{Typical dependence of the turn-off time } \ t_q \ \text{normalized to the -di}_T / dt_{\text{norm}} \ \text{on the off-commutating rate of fall -di}_T / dt$

Figure 31 Typical dependence of the turn-off time  $t_q$  normalized to the  $dv_D/dt = 20V/\mu s$  on the rate of rise of off-state voltage  $dv_D/dt$

### 3.5 Power dissipation (losses)

For thyristor and diode the dissipation (or losses) are classified as off-state, on-state, turn-on and turn-off losses. The thyristor also shows control losses. Under given cooling conditions their sum determines the current loading capability.

For mains operation up to 60Hz with its moderate dynamic requirements the dimensioning can be exclusively done based on the on-state losses, as the sum of the others is comparatively negligible.

For semiconductors with high blocking voltages (> 2200V) or large square sections with a pellet  $\emptyset \ge 80$ mm even for mains operation the turn-off losses should be regarded in the calculation.

#### 3.5.1 Total power dissipation P<sub>tot</sub>

$\mathbf{P}_{\text{tot}}$  is the average value of the sum of the individual losses.

#### 3.5.2 Off-state losses $P_D$ , $P_R$

$P_D$ ,  $P_R$  are the losses caused by off-state current and off-state voltage in forward direction ( $P_D$ ) and in reverse direction ( $P_R$ ).

#### 3.5.3 On-state losses $P_T$ , $P_F$

$P_T$ ,  $P_F$  is the electric power converted to heat when only the conducting state in forward direction is considered. The average value of the on-state loss  $P_{TAV}$  or  $P_{FAV}$  is calculated with the values of the equivalent straight line according to the following formula:

$$\begin{split} &P_{TAV} = V_{T(TO)} \bullet I_{TAV} + r_{T} \bullet I^{2}_{TRMS} = V_{T(TO)} \bullet I_{TAV} + r_{T} \bullet I^{2}_{TAV} \bullet F^{2} \text{ (for thyristors)} \\ &P_{FAV} = V_{F(TO)} \bullet I_{FAV} + r_{T} \bullet I^{2}_{FRMS} = V_{F(TO)} \bullet I_{FAV} + r_{T} \bullet I^{2}_{FAV} \bullet F^{2} \text{ (for diodes)} \end{split}$$

For formfactors F refer to Table 1

The diagrams in the data sheets show the relation of the average value of on-state dissipation power and on-state current for various shapes of current.

Instead of calculating the on-state losses with  $v_{T0}$ ,  $v_{F0}$  and  $r_{T}$ , alternatively the on-state voltage can be calculated with a more precise approximation with the following relation:

$$v_T = A + B \cdot i_T + C \cdot Ln(i_T + 1) + D \cdot \sqrt{i_T}$$

The factors A, B, C and D are listed in the datasheets.

Exception: PowerBLOCK-Modules are not listed with the ABCD coefficients.

| Stromform        | Scheitelfaktor                | Mittelfaktor                 | Formfaktor                   | Formfaktor <sup>2</sup>  |

|------------------|-------------------------------|------------------------------|------------------------------|--------------------------|

| Current waveform | peak factor                   | average factor               | form factor                  | form factor <sup>2</sup> |

|                  | $S = \frac{\hat{i}}{I_{RMS}}$ | $M = \frac{\hat{i}}{I_{AV}}$ | $F = \frac{I_{RMS}}{I_{AV}}$ | F <sup>2</sup>           |

| 0 180°           |                               |                              |                              |                          |

| sinus 180° el    | 2                             | $\pi = 3,14$                 | $\pi / 2 = 1,57$             | 2,47                     |

| sinus 120° el    | 2,23                          | 4,18                         | 1,875                        | 3,52                     |

| sinus 90° el     | 2,83                          | 6,29                         | 2,22                         | 4,93                     |

| sinus 60° el     | 3,88                          | 10,9                         | 2,77                         | 7,66                     |

| sinus 30° el     | 5,88                          | 23,42                        | 3,98                         | 15,8                     |

| DC               | 1                             | 1                            | 1                            | 1                        |

| 0° 0 180°        |                               |                              |                              |                          |

| rect 180° el     | $\sqrt{2} = 1,41$             | 2                            | $\sqrt{2} = 1,41$            | 2                        |

| rect 120° el     | $\sqrt{3} = 1,73$             | 3                            | $\sqrt{3} = 1,73$            | 3                        |

| rect 90° el      | $\sqrt{4} = 2$                | 4                            | $\sqrt{4} = 2$               | 4                        |

| rect 60° el      | $\sqrt{6} = 2,45$             | 6                            | $\sqrt{6} = 2,45$            | 6                        |

| rect 30° el      | $\sqrt{12} = 3,46$            | 12                           | $\sqrt{12} = 3,46$           | 12                       |

Table 1 Form factors for phase angle control conditions

### 3.5.4 Switching losses $P_{TT}$ , $P_{FT} + P_{RO}$

$P_{TT}$ ,  $P_{FT}$ + $P_{RQ}$  are the portions of electric power converted to heat when turning on ( $P_{TT}$  for thyristors,  $P_{FT}$  for diodes) and turning off ( $P_{RQ}$ ). The average switching losses increase with increasing rates of rise and fall of the on-state current at turn-on and turn-off as well as with the frequency of repetition. Up to medium size thyristors and diodes with blocking voltages up to 2200V and applications at mains frequencies of up to 60Hz the switching losses are mostly negligible compared to the on-state losses.

For semiconductors with high blocking voltages > 2200V or large square sections with a pellet  $\emptyset \ge 80$ mm even for mains operation the turn-off losses should be regarded in the calculation (on request if necessary).

The turn-off losses of diodes, however, are generally still negligible.

#### 3.5.4.1 Turn-on losses P<sub>TT</sub>, P<sub>FT</sub>

$P_{TT}$ ,  $P_{FT}$  is that dissipative portion which exceeds the on-state loss  $P_{T}$  (for thyristors) or  $P_{F}$  (for diodes) during turn-on. It is caused on the one hand by the carrier storage effect and on the other hand by the delayed propagation of the current carrying area.

To be able to turn on with the greatest possible square section many thyristors are equipped with trigger amplification. This consist of one or several amplifying gates (= auxiliary thyristors). In thyristors with large square sections the amplifying gate is branched (finger structure). This causes a wider area to become conductive at the time of triggering and thus reduces the turn-on losses.

The sum of turn-on and on-state losses  $P_{TT}$ ,  $P_{FT}$  +  $P_{T}$ ,  $P_{F}$  important for the dissipation calculation may be drawn from the progression of the on-state current and the on-state voltage during and after turning on.

$$P_{TT} + P_{T} = \frac{1}{t_{T}} \int_{0}^{t_{T}} i_{T}(t) \cdot v_{T}(t) dt \qquad (for thyristors)$$

$$P_{FT} + P_{F} = \frac{1}{t_{T}} \int_{0}^{t_{T}} i_{F}(t) \cdot v_{F}(t) dt$$

(for diodes)

In practice the turn-on losses are generally neglected.

#### 3.5.4.2 Turn-off losses P<sub>RO</sub>

Turn-off losses occur due to the carrier storage effect. They depend on the progression of the reverse delay current as well as on the magnitude and rate of rise of the reverse off-state voltage and may therefore be influenced by the snubber (see Figure 23).

$$P_{RQ} = \frac{1}{t_{int}} \int_{0}^{t_{int}} i_{R}(t) \cdot v_{R}(t) dt$$

For the time period  $t_{int}$  to be determined by integration the turn-off losses are calculated as follows: An approximation of the turn-off losses may be calculated as follows:

$$P_{RQ} = E_{RQ} * f \approx Q_r * v_R * 0.4 * f$$

for the on-state limit characteristic  $P_{RO} = E_{RO} * f \approx Q_r * v_R * 0.5 * f$  for the typical on-state characteristic

$E_{RO}$  = turn-off loss energy

f = frequency

Q<sub>r</sub> = maximum recovery charge

$v_R$  = (reverse voltage) driving voltage after commutation

### 3.5.5 Gate dissipation P<sub>G</sub>

$P_G$  is the electrical power converted into heat due the gate current flowing between gate terminal and cathode. This is distinguished into peak gate dissipation  $P_{GM}$  (product of the peak values of gate current and gate voltage) and average gate dissipation  $P_{GAV}$  (average value of gate dissipation referenced to the cycle duration).

## 3.6 Insulation test voltage $V_{\text{ISOL}}$

The insulation test voltage  $V_{ISOL}$  is the RMS-value of a sinewave voltage between the base plate and the terminal of thyristor or diode modules. For DC-requirements  $V_{ISOL\,DC}$  is equal to the peak value of the specified RMS-value (i.e.  $1.41*V_{ISOL}$ ). During the test all terminals are connected with each other and  $V_{ISOL}$  is applied versus the base plate.

# 4. Thermal properties

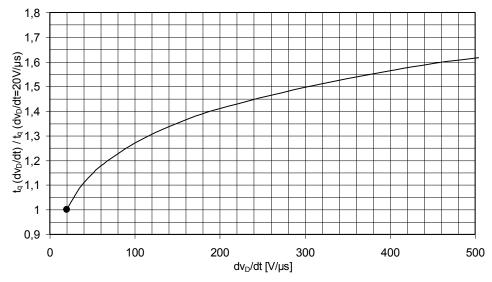

In order to maintain the thermal equilibrium the electric power loss converted to heat in the semiconductors has to be dissipated. For this purpose heatsinks with defined cooling properties are available. To describe this function thermal equivalent circuits, by analogy to electrical ciruits, according to Figure 32 are used.

Figure 32 Thermal equivalent circuits for diodes and thyristors

$R_{th IC}$ = steady state thermal resistance junction - case

$R_{th CH}$ = steady state transfer thermal resistance case - heatsink

$R_{th HA}$ = steady state thermal resistance heatsink

a - single sided cooling

b - double sided cooling

## 4.1 Temperatures

## 4.1.1 Junction temperature $T_{vj}$ , $T_{vj max}$

The junction temperature is the most important reference for all fundamental electrical properties. It represents a mean spatial temperature within the semiconductor systems and is, therefore, known more precisely as the equivalent junction temperature or virtual junction temperature.

To observe the maximum permissible junction temperature  $T_{vj max}$  is important for the function and reliability of the device. To exceed this maximum value may change the properties of the semiconductor irreversibly and destroy it.

#### 4.1.2 Case temperature T<sub>C</sub>

$T_{\rm C}$  is the maximum temperature at the contact area of the thyristor or diode case of a disc cell or the base plate of a PowerBLOCK-module.

#### 4.1.3 Heatsink temperature T<sub>H</sub>

$T_{\rm H}$  is the temperature of the heatsink resulting from the semiconductor through the contact area of the heatsink and its surrounding cooling media.

The heatsinks offered by Infineon have been tested and specified with components mounted. The heatsink data given, therefore, include the thermal transfer resistance  $R_{thCH}$  between device and heatsink. This value can, therefore, be disregarded in the calculation.

#### 4.1.4 Cooling medium temperature T<sub>A</sub>

$T_A$  is the temperature of the cooling medium prior to entering the heatsink. For air cooling this is defined at the inlet side of the heatsink. For fluid cooling it is defined at the inlet of the heatsink.

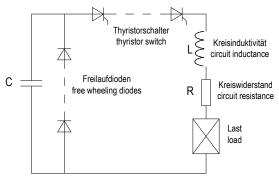

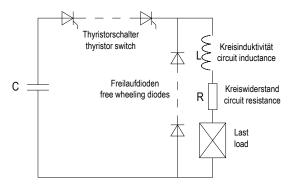

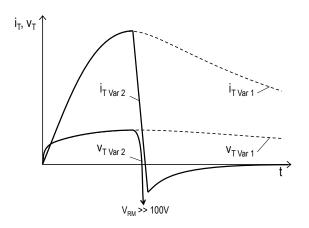

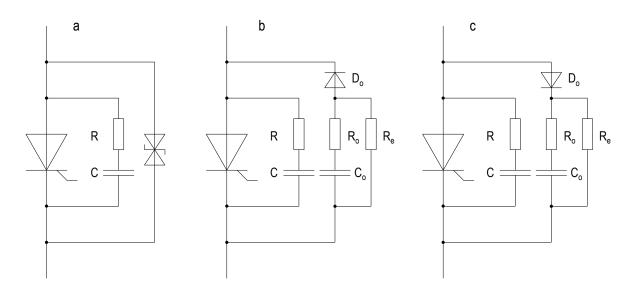

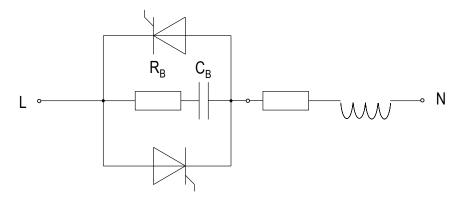

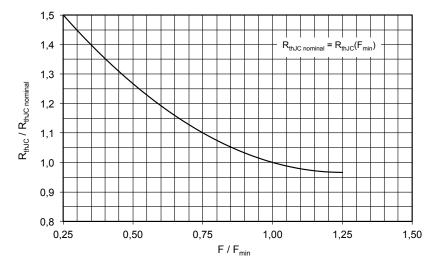

#### 4.1.5 Junction operating temperature range T<sub>cop</sub>