# Thermal design recommendation and guideline for SMD packages

## **About this document**

#### Scope and purpose

This application note analyzes the thermal performance of 1700 V CoolSiC™ MOSFETs in TO-263 packages. These MOSFETs were soldered on the following printed circuit board (PCB) boards: 2-layer board with 1 oz. copper, 2-layer board with 2 oz. copper, 4-layer board with 1 oz. copper and 4-layer board with 2 oz. copper. The design of via matrix, diameters of vias, and the assembly of heat sinks were varied in each design. In this way, the temperature rises of SiC MOSFETs were tested. This investigation aimed to determine the best arrangement of MOSFETs on the PCBs for maintaining low temperature in the packages. The size and cost of the PCB were also considered. This application note allows customers and engineers to design their systems effectively taking advantage of the precise heat dissipation features presented in the experimental data.

#### Intended audience

Electronic engineers dealing with PCBs or other system designs.

### **Table of contents**

| Abou  | ıt this document                            | 1  |

|-------|---------------------------------------------|----|

| Table | e of contents                               | 1  |

| 1     | Introduction                                | 3  |

| 1.1   | Aim                                         | 3  |

| 1.2   | Independent variables                       | 3  |

| 1.2.1 | PCB layers                                  | 3  |

| 1.2.2 | Copper thickness                            | 3  |

| 1.2.3 | Via size                                    | 4  |

| 1.2.4 | Number of vias                              | 4  |

| 1.2.5 | Heat sink                                   | 4  |

| 2     | Thermal measurement set-up                  | 6  |

| 2.1   | Measurement of power dissipation            | 6  |

| 2.2   | Measurement of temperature rise             | 6  |

| 2.3   | Temperature measurement point               | 7  |

| 3     | Measurement parameters                      | 8  |

| 3.1   | Number of PCB layers and copper thickness   | 8  |

| 3.2   | Through-hole technology (THT) vias diameter | 8  |

| 3.3   | Via matrix size                             | 8  |

| 3.4   | Heat sink                                   | 9  |

| 3.5   | Existence of solder mask                    | 9  |

| 3.6   | Current                                     | 10 |

| 4     | Test result and interpretation              | 11 |

| 4.1   | The influence of different types of PCB     | 11 |

| 4.2   | The influence of different current          |    |

| 4.3   | The influence of solder mask                | 14 |

| 4.4   | The influence of THT vias diameter          | 16 |

# Introduction

| 4.4.1 Test on 2L1OZ / 2L2OZ at 0.3A | 16 |

|-------------------------------------|----|

| ·                                   |    |

| 4.5 The influence of heat sink      |    |

| 4.6 Whether a heat sink is needed   | 20 |

| 5 Conclusions                       | 22 |

| 6 References                        | 23 |

| Appendix: PCBs                      | 23 |

| Revision history                    |    |

## Thermal design recommendation and guideline for SMD package

# 1 Introduction

Heat dissipation is a significant aspect of circuit design, especially in printed circuit board (PCB) layout. The interaction between transistors, packages and PCBs must be carefully designed to optimize heat dissipation. Heat sinks are not necessary for 1700 V CoolSiC™ MOSFETs in a surface-mount device (SMD) TO-263 package, which has reduced system complexity and cooling efforts in the PCB design. Therefore, using 1700 V CoolSiC™ MOSFET will save space and lower the cost of the PCB

Generally, the capability of the SMD to dissipate heat is weaker than the though-hole device, so customers may be concerned about the thermal transmission properties of this product. Hence, its thermal performance is investigated and evaluated in this application note.

### 1.1 Aim

In the following experiment, the temperature increases of a 1700 V SiC MOSFET in a TO-263 package were detected by studying different cases of PCB heat dissipation. From the test data, the effects of copper thickness, MOSEFT current, via diameters, via matrix size, and the existence of solder mask and heat sinks were analyzed. The investigation intended to determine the most suitable heat dissipation method under different constraints for customers and engineers.

# 1.2 Independent variables

This section introduces the important factors that influence the thermal performance of the MOSFET.

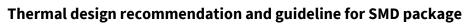

# 1.2.1 PCB layers

The thermal dissipation ability can be improved by the addition of PCB layers, as this increases the amount of copper placed on a board. In PCB design, the number of layers is an important parameter that needs to be considered. Using more layers also helps to minimize the electromagnetic interference between layers. So, the interference between signals decreases, and the life cycle of the PCB is extended. Additionally, the multilayer PCBs reduce the layout difficulty for complex circuits. On the other hand, building more layers will increase the cost of production.

Figure 1 Vias in PCB layers

# 1.2.2 Copper thickness

The thickness of copper also influences the thermal transmission. It is measured using the unit ounce (oz.). An ounce (oz.) is a unit of weight that can be converted into grams (g) as follows: 1 oz.  $\approx$ 28.35 g.

In the PCB industry, 1 oz. represents the thickness of copper, spread out evenly over an area of 1 square foot (FT<sup>2</sup>). It is the weight per unit area to represent the average thickness of the copper foil.

# Thermal design recommendation and guideline for SMD package

V2.0

#### Introduction

$$1 \text{FT}^2 = 0.09290304 m^2; \ \rho_{Cu} = 8.9 \ \frac{g}{cm^3}$$

thickness(t) =

$$\frac{mass(m)}{area(S) \cdot density(\rho)} = \frac{28.35 g}{0.09290304 m^2 \cdot 8.9 \ \frac{g}{cm^3}} \approx 35 \mu\text{m}$$

So, 1 oz. represents 35 μm copper thickness, 2 oz. represent 70 μm copper thickness.

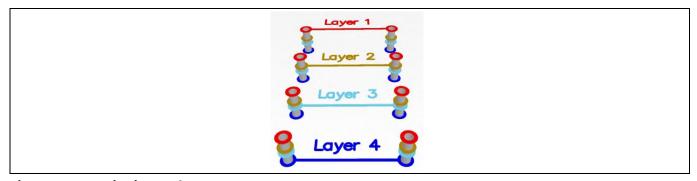

#### Via size 1.2.3

Moreover, another critical factor is the diameter of the through-hole via on the board. As the size of the through-hole via increases, the effect of heat dissipation becomes more significant. However, the solder climbing problem may occur in the reflow welding process when the diameter is too large.

As shown in Figure 2 below, there are two groups of through-hole vias in the test: the via under the pad (solder joint of device) and the via around the pad (solder joint of device).

Via matrix number Figure 2

#### **Number of vias** 1.2.4

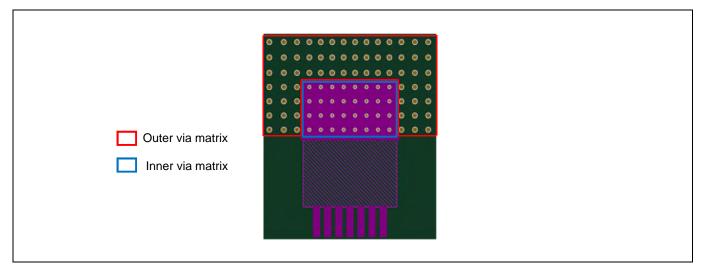

Additionally, as vias help to transmit heat, increasing the number of vias will improve the performance. The via matrixs under the pad was kept the same in all measurement set-ups, while the number of outer vias was varied. Figure 2 displays an example of two different arrangements. The via pitch size is 1.3 mm in both cases. Apparently, the via matrix on the right side occupies a larger area. The area of copper around the pad increases as the via matrix grows, which causes the total copper size at the drain increases. If the area of copper under the pad is represented by S (67.45 mm<sup>2</sup>), the total drain copper size of a 10x5 via matrix will be 1.6 S (112.52 mm<sup>2</sup>). In comparison, a 14 x 7 via matrix uses 3.4 S (229.35 mm<sup>2</sup>) area.

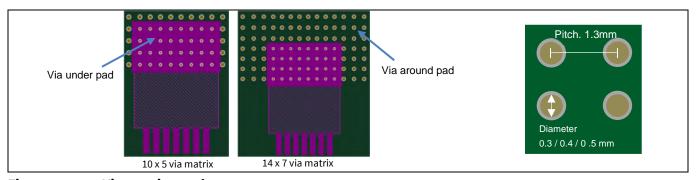

#### 1.2.5 **Heat sink**

A heat sink is a device that transfers heat from heat-prone electronic components in electrical appliances to another medium, such as air. It can be made of aluminum alloy, brass or bronze in the form of plates, sheets, etc.

Figure 3 A variety of heat sinks on the market

# Thermal design recommendation and guideline for SMD package

#### Introduction

The efficiency of heat sinks depends on the thermal conductivity, k, of the materials. It measures the ability of heat conductance of a material. Table 1 lists the thermal conductivity of a range of materials. While silver has relatively high thermal conductivity and dissipates heat fast, using silver heat sinks will be expensive. Therefore, copper is commonly the best choice due to its reasonable price. Aluminum is also used when the requirements for thermal dissipation is not a priority, as its conductivity is much lower than with copper.

The thermal conductivity of common materials Table 1

| Material | k [W/(m⋅K)] | Material | k [W/(m⋅K)] | Material             | k [W/(m·K)] |

|----------|-------------|----------|-------------|----------------------|-------------|

| Si       | 150         | Cu       | 401         | Sn                   | 64          |

| SiO2     | 1.6         | Brass    | 70-183      | Pb                   | 35          |

| SiC      | 490         | bronze   | 32-153      | ABS                  | 0.25        |

| GaAs     | 46          | Al       | 237         | Glass                | 0.5-1.0     |

| Au       | 317         | Al203    | 45          | FR4                  | 0.2         |

| Ag       | 429         | AlN      | 150         | Phenolic epoxy resin | 0.2         |

| Ni       | 90          | Fe       | 80          | air                  | 0.01-0.04   |

# Thermal design recommendation and guideline for SMD package

Thermal measurement set-up

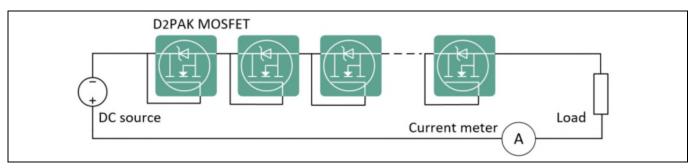

#### Thermal measurement set-up 2

#### 2.1 Measurement of power dissipation

Figure 4 **Measurement schematics**

The circuit used for thermal measurements is shown in Figure 4. In the test, the following devices are used:

- DC Power Supply TPR3005-2DF

- DC Load Chroma 63110A

- Agilent Data Logger 34970A

- Digital Multimeter 34450A.

By using electronic loads, the current in the circuit was kept constant. The voltage drop of the volume diode was measured by the voltage meter. So, the power dissipation could be derived from the product of voltage and current.

#### 2.2 Measurement of temperature rise

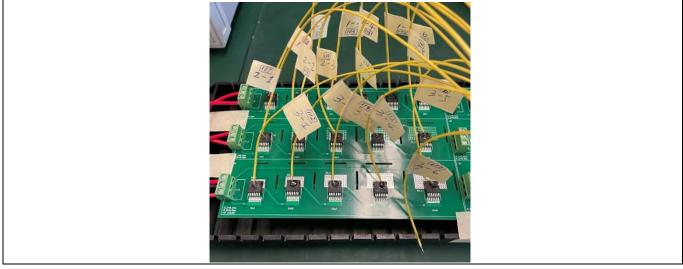

The temperature rise was measured using thermocouples and data acquisition instruments Figure 5 demonstrates the experimental set-up for temperature measurement.

Figure 5 **Temperature measurement set-up**

# Thermal design recommendation and guideline for SMD package

#### Thermal measurement set-up

The J-type thermocouple used has high sensitivity, linearity and stability. The temperature range of the coverage measurement of a J-type thermocouple is -200 ~ 1200 °C, although 0 ~ 750 °C is normally used. The tolerance is around 2°C.

To begin with, the open circuit temperature T<sub>a</sub> was measured. Then, the circuit was closed and the temperature started to rise. 30 minutes later, the temperature T<sub>c</sub> was recorded again when the heat dissipation was stabilized. The temperature rise was obtained from:

$$\Delta T_{c-a} = T_c - T_a$$

.

Airflow reduces the accuracy of the measurement data, so the test platform was equipped with a windproof carton to get rid of this effect.

#### 2.3 Temperature measurement point

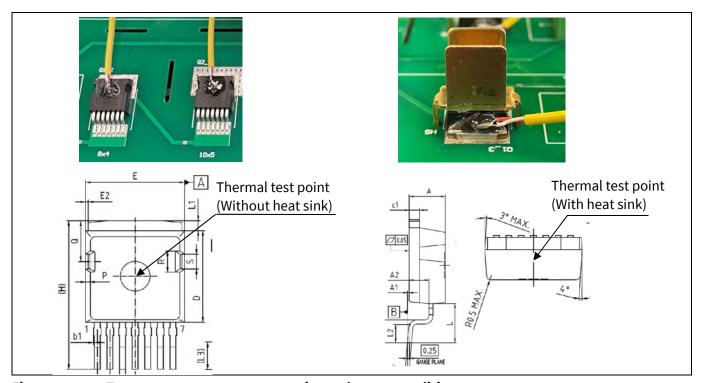

Figure 6 Temperature measurement point under two conditions

As shown in Figure 6, the measurement points are different in the two cases. The temperature is measured from the top of the packages without heat sinks attached. When a heat sink was presented, the measurement point was located at the side of the package.

# Thermal design recommendation and guideline for SMD package

**Measurement parameters**

#### 3 **Measurement parameters**

#### 3.1 Number of PCB layers and copper thickness

The difference between the four PCBs used in measurement are listed below:

- 2 layers with 1 oz. copper (2L10Z)

- 2 layers with 2 oz. copper (2L2OZ)

- 4 layers with 1 oz. copper (4L1OZ)

- 4 layers with 2 oz. copper (4L2OZ)

#### Through-hole technology (THT) vias diameter 3.2

The diameters of the vias used in the experiment were 0.3 mm, 0.4 mm and 0.5 mm.

#### Via matrix size 3.3

Figure 7 Outer and inner via matrix

Figure 7 above displays the boundary between the inner via matrix and outer via matrix. In order to check both the impact of the arrangement and diameters of the vias on the temperature change, the combinations of different sizes of outer via matrix and different diameters of inner vias were tested accordingly. The testing conditions are listed in Table 2, Table 3 and Table 4.

Table 2 Via matrix 1 (0.3 mm vias under the pad)

| Via variants             | 1                     | 2                      | 3                      | 4                      | 5                      |

|--------------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|

| Via matrix inner 8x4 8x4 |                       | 8x4                    | 8x4                    | 8x4                    | 8x4                    |

| Diameter inner           | 0.3 mm                | 0.3 mm                 | 0.3 mm                 | 0.3 mm                 | 0.3 mm                 |

| Via matrix total         | 8x4                   | 10x5                   | 12x6                   | 14x7                   | 16x8                   |

| Diameter outer           | n.a                   | 0.5 mm                 | 0.5 mm                 | 0.5 mm                 | 0.5 mm                 |

| Via pitch                | 1.3 mm                | 1.3 mm                 | 1.3 mm                 | 1.3 mm                 | 1.3 mm                 |

| Total drain              | 67.45 mm <sup>2</sup> | 112.52 mm <sup>2</sup> | 163.94 mm <sup>2</sup> | 229.35 mm <sup>2</sup> | 309.92 mm <sup>2</sup> |

| copper size              |                       |                        |                        |                        |                        |

| Related ratio            | S                     | 1.67 S                 | 2.43 S                 | 3.4 S                  | 4.6 S                  |

# Thermal design recommendation and guideline for SMD package

**Measurement parameters**

Table 3 Via matrix 2 (0.4 mm vias under the pad)

| Via variants         | 1                     | 2                      | 3                      | 4                      |

|----------------------|-----------------------|------------------------|------------------------|------------------------|

| Via matrix inner 8x4 |                       | 8x4                    | 8x4                    | 8x4                    |

| Diameter inner       | 0.4 mm                | 0.4 mm                 | 0.4 mm                 | 0.4 mm                 |

| Via matrix total     | 8x4                   | 12x6                   | 14x7                   | 16x8                   |

| Diameter outer       | n.a.                  | 0.5 mm                 | 0.5 mm                 | 0.5 mm                 |

| Via pitch            | 1.3 mm                | 1.3 mm                 | 1.3 mm                 | 1.3 mm                 |

| Total drain copper   | 67.45 mm <sup>2</sup> | 163.94 mm <sup>2</sup> | 229.35 mm <sup>2</sup> | 309.92 mm <sup>2</sup> |

| size                 |                       |                        |                        |                        |

| Related ratio        | S                     | 2.43 S                 | 3.4 S                  | 4.6 S                  |

Table 4 Via matrix 3 (0.5 mm vias under the pad)

| Via variants            | 1                     | 2                      | 3                      | 4                      |

|-------------------------|-----------------------|------------------------|------------------------|------------------------|

| Via matrix inner        | 8x4                   | 8x4                    | 8x4                    | 8x4                    |

| Diameter inner          | 0.5 mm                | 0.5 mm                 | 0.5 mm                 | 0.5 mm                 |

| Via matrix total        | 8x4                   | 12x6                   | 14x7                   | 16x8                   |

| Diameter outer          | n.a.                  | 0.5 mm                 | 0.5 mm                 | 0.5 mm                 |

| Via pitch               | 1.3 mm                | 1.3 mm                 | 1.3 mm                 | 1.3 mm                 |

| Total drain copper size | 67.45 mm <sup>2</sup> | 163.94 mm <sup>2</sup> | 229.35 mm <sup>2</sup> | 309.92 mm <sup>2</sup> |

| Related ratio           | S                     | 2.43 S                 | 3.4 S                  | 4.6 S                  |

## 3.4 Heat sink

Two kinds of heat sinks were tested as shown in Table 5 below.

Table 5 Two kinds of heat sink

| Heat sink | HS1                                            | HS2                                    |

|-----------|------------------------------------------------|----------------------------------------|

|           |                                                |                                        |

| Material  | copper                                         | Aluminum                               |

| Size (mm) | 17 x 14.5 x 10 x 0.8                           | 8.8 x 8.8 x 5                          |

| URL links | https://item.taobao.com/item.htm?spm=a230r.1.1 | https://item.taobao.com/item.htm?spm=a |

|           | 4.33.5a7c54dap97EQn&id=543677256194&ns=1&a     | 1z10.3-c.w4002-                        |

|           | bbucket=20#detail                              | 21214618245.49.36155473n100vU&id=5819  |

|           |                                                | 76481584                               |

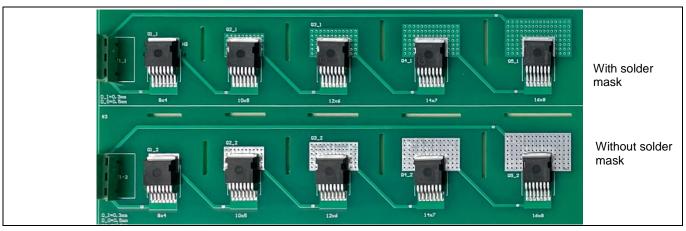

## 3.5 Existence of solder mask

The thermal conductivity of solder mask is around 0.2 according to Table 1 above. As the thickness of solder mask was only 20  $\mu$ m, it is not certain to what extent the solder mask influences the thermal dissipation. So, the thermal impact of it must be checked through the configuration shown in Figure 8 below.

# Thermal design recommendation and guideline for SMD package

## **Measurement parameters**

Figure 8 Thermal copper with and without solder mask

The diameter of the inner vias was 0.3 mm, and that of the outer vias was 0.5 mm.

Table 6 Parameters of inner and outer vias

| Via variants     | 1                     | 2                      | 3                      | 4                      | 5                      |

|------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|

| Via matrix inner | 8x4                   | 8x4                    | 8x4                    | 8x4                    | 8x4                    |

| Diameter inner   | ter inner 0.3 mm 0.3  |                        | 0.3 mm                 | 0.3 mm                 | 0.3 mm                 |

| Via matrix total | 8x4                   | 10x5                   | 12x6                   | 14x7                   | 16x8                   |

| Diameter outer   | n.a.                  | 0.5 mm                 | 0.5mm                  | 0.5 mm                 | 0.5 mm                 |

| Via pitch        | 1.3 mm                | 1.3 mm                 | 1.3mm                  | 1.3 mm                 | 1.3 mm                 |

| Total drain      | 67.45 mm <sup>2</sup> | 112.52 mm <sup>2</sup> | 163.94 mm <sup>2</sup> | 229.35 mm <sup>2</sup> | 309.92 mm <sup>2</sup> |

| copper size      |                       |                        |                        |                        |                        |

| Related ratio    | S                     | 1.67 S                 | 2.43 S                 | 3.4 S                  | 4.6 S                  |

## 3.6 Current

The current across the MOSFET body diode were set to the following values:

- 0.1 A

- 0.2 A

- 0.3 A

- 0.4 A

- 0.5 A

# Thermal design recommendation and guideline for SMD package

**Test result and interpretation**

# 4 Test result and interpretation

The results are presented by charts in this chapter, based on the measurement plan described in the previous chapter. Then, conclusions are drawn from the test data.

# 4.1 The influence of different types of PCB

This first test measured the temperature rise of the PCBs with different via matrixes and currents. The trend of the temperature rise with different current was the same, so the data resulted from 0.3 A current was selected to be analyzed here. The diameter of the inner via was 0.3 mm, while the diameter of the outer via was 0.5 mm.

Table 7 Temperature rise ΔT of PCBs with different layers and via matrix at 0.3 A

| Current is 0.3 A | Via matrix |        |        |        |        |  |  |  |  |

|------------------|------------|--------|--------|--------|--------|--|--|--|--|

| PCB variant      | 8X4        | 10X5   | 12X6   | 14X7   | 16X8   |  |  |  |  |

| 2L1OZ            | 46.84℃     | 42.06℃ | 36.71℃ | 35.03℃ | 29.37℃ |  |  |  |  |

| 2L2OZ            | 43.63℃     | 39.23℃ | 34.92℃ | 32.54℃ | 29.09℃ |  |  |  |  |

| 4L10Z            | 40.25℃     | 35.46℃ | 33.09℃ | 30.70℃ | 28.78℃ |  |  |  |  |

| 4L2OZ            | 37.23℃     | 32.89℃ | 31.26℃ | 29.55℃ | 28.56℃ |  |  |  |  |

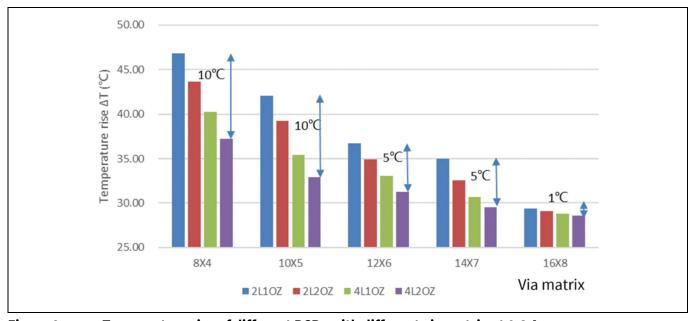

It is observed from Table 7 that there is a rising trend in  $\Delta T$  in different via matrixes: 2L10Z > 2L20Z > 4L10Z > 4L20Z. As the size of the via matrix grows, the gap of  $\Delta T$  between the 4 PCBs narrows. With the via matrix 8 x 4, the temperature rise of 4L20Z is about  $10^{\circ}$ C lower than that of 2L10Z. With the via matrix 16x8, the temperature rise of 4 PCBs is almost the same.

Figure 9 Temperature rise of different PCBs with different via matrix at 0.3 A

The reason for this is that the thickness of copper increases with the number of layers. As more copper is used in the PCB, the heat dissipation rate increases accordingly. When there are fewer vias presented, the copper is the main heat dissipation pathway. Due to the increase of the size of via matrix, the vias become the dominant heat dissipation pathway.

# Thermal design recommendation and guideline for SMD package

### Test result and interpretation

Therefore, when the via matrix is small, the heat dissipation can be increased by selecting the PCB with more layers or with greater copper thickness. But when the via matrix is large, increasing the number of PCB layers and copper thickness no longer produces a significant effect.

**Conclusion 1** concerning PCB layer, copper thickness and number of vias

- When the total drain copper size is smaller than 3S (202.35 mm<sup>2</sup>), adding PCB layers and copper thickness will improve thermal performance significantly. Also, adding PCB layers is more effective than increasing copper thickness.

- Otherwise, when the total drain copper size is greater than 3S (202.35 mm<sup>2</sup>), the impacts of PCB layer and copper thickness is weakened. 1 oz. and 2 layers should be sufficient for cooling.

So, the top layer is very important. When the copper size is large enough, most of the heat is conducted by the top layer. Otherwise, we have to increase the number of PCB layers and copper thickness.

# Thermal design recommendation and guideline for SMD package

**Test result and interpretation**

# 4.2 The influence of different current

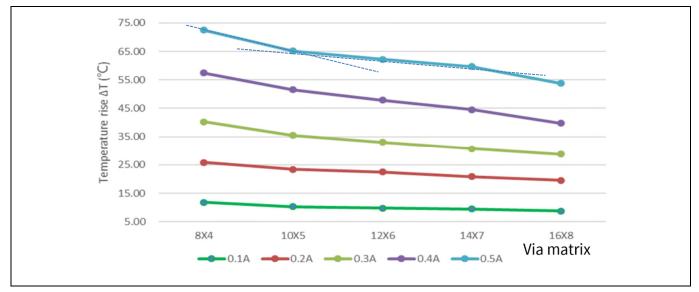

This test measured the temperature rise under the current of 0.1 A to 0.5 A with different via matrixes. Because the trend was the same, the result of 4L1OZ PCB was selected for analysis here. The diameter of the inner via was 0.3 mm, while the diameter of the outer via was 0.5 mm. The data recorded in Table 8 below is displayed in Figure 10 below.

Table 8 Temperature rise under the current of 0.1 A to 0.5 A with different via matrixes on 2L1OZ PCB

| PCB is 2L10Z | Via matrix (℃) |       |       |       |       |  |  |  |  |

|--------------|----------------|-------|-------|-------|-------|--|--|--|--|

| Current      | 8X4            | 10X5  | 12X6  | 14X7  | 16X8  |  |  |  |  |

| 0.1 A        | 14.64          | 13.08 | 11.67 | 10.68 | 9.47  |  |  |  |  |

| 0.2 A        | 29.62          | 26.83 | 24.33 | 22.65 | 19.49 |  |  |  |  |

| 0.3 A        | 46.84          | 42.06 | 36.71 | 35.03 | 29.37 |  |  |  |  |

| 0.4 A        | 59.67          | 52.24 | 46.31 | 43.24 | 37.82 |  |  |  |  |

| 0.5 A        | 73.14          | 65.88 | 59.96 | 56.68 | 50.69 |  |  |  |  |

Figure 10 Temperature rise under the current of 0.1 A to 0.5 A with different via matrixes on a 2L1OZ PCB

It can be observed from the chart that if the current increases (which means the power increases),  $\Delta T$  will increase. When the current is small, the difference between the temperature rises of various via matrixes is negligible. When the current is large, the difference is also large.

For a 2L1OZ PCB, at 0.1 A, the temperature rises with these 5 via matrixes are within 12 +/- 3  $^{\circ}$ C. But at 0.5 A, the temperature change with an 8x4 via matrix is about 23  $^{\circ}$ C higher than 16x8. In other words,  $\Delta$ T of 2L1OZ PCB is affected greater by the current, as the slope is steeper.

Therefore, when the current is small, the number of THT vias has little influence on the temperature rise. When the current increases, the number of THT vias has a greater influence on the temperature rise. It can also be seen from Figure 10 above that the temperature rise decreases with the growth of the via matrix at different currents.

# Thermal design recommendation and guideline for SMD package

Test result and interpretation

### Conclusion2 concerning current/power impact on the temperature rising:

Generally, power/current changing will not influence the total thermal resistance, as normally  $\Delta T$  increases linearly with current.

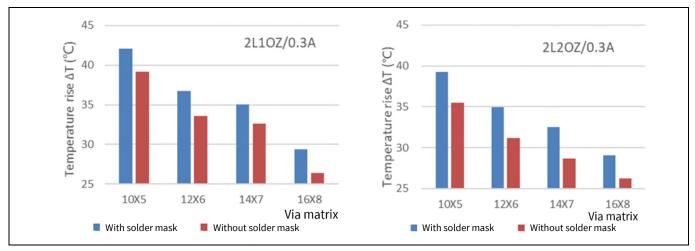

# 4.3 The influence of solder mask

Solder mask affects the heat dissipation in some cases. This test measured and compared the temperature rise of different via matrixes on 4 types of PCB with/without solder mask. The diameter of the inner via was 0.3 mm, while the diameter of the outer via was 0.5 mm. The current was set to 0.3 A.

Table 9 Temperature rise in 2L1OZ/2OZ PCBs with/without solder mask at 0.3 A

| . <u>.</u>                 | 2L10Z |       |       |       |       | 2L2   | 2 <b>0</b> Z |       |

|----------------------------|-------|-------|-------|-------|-------|-------|--------------|-------|

| Via matrix                 | 10X5  | 12X6  | 14X7  | 16X8  | 10X5  | 12X6  | 14X7         | 16X8  |

| With solder mask (℃)       | 42.06 | 36.71 | 35.03 | 29.37 | 39.23 | 34.92 | 32.54        | 29.09 |

| Without solder mask (℃)    | 39.16 | 33.61 | 32.63 | 26.41 | 35.46 | 31.15 | 28.66        | 26.24 |

| Temperature difference (℃) | 2.90  | 3.10  | 2.40  | 2.96  | 3.77  | 3.77  | 3.88         | 2.85  |

The data in Table 9 above could be transferred to the Figure 11 below. The average temperature improvement was about 3 ~4℃.

Figure 11 Temperature rise in 2L10Z/20Z PCBs with/without solder mask

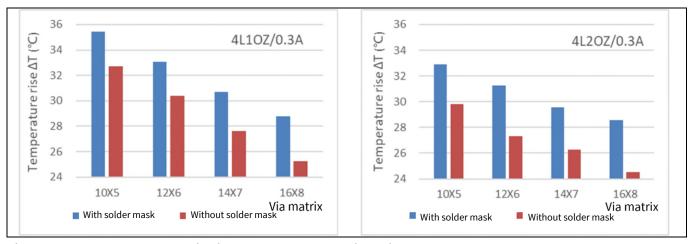

The test results of 4L10Z/4L2OZ PCBs are shown in Table 10 below.

Table 10 Temperature rise in 4L10Z/20Z PCBs with/without solder mask at 0.3A

|                                        |       | 4L10Z |       |       |       | 4L2   | 2 <b>0</b> Z |       |

|----------------------------------------|-------|-------|-------|-------|-------|-------|--------------|-------|

| Via matrix                             | 10X5  | 12X6  | 14X7  | 16X8  | 10X5  | 12X6  | 14X7         | 16X8  |

| With solder mask (°C)                  | 35.46 | 33.09 | 30.70 | 28.78 | 32.89 | 31.26 | 29.55        | 28.56 |

| Without solder mask (℃)                | 32.71 | 30.41 | 27.64 | 25.25 | 29.82 | 27.34 | 26.25        | 24.53 |

| Temperature difference ( $^{\circ}$ C) | 2.75  | 2.68  | 3.06  | 3.53  | 3.07  | 3.92  | 3.30         | 4.03  |

# Thermal design recommendation and guideline for SMD package

### **Test result and interpretation**

Figure 12 Temperature rise in 4L10Z/20Z PCBs with/without solder mask

The above charts show that the solder mask affects temperature rise. The temperature rise without solder mask is about 3-4  $^{\circ}$ C lower.

Table 11 Temperature rise in 4L1OZ PCB with/without solder mask at different currents

| PCB type is 4L10Z       | 0.1 A |      |      | 0.3 A |       |       |       | 0.5 A |       |       |       |       |

|-------------------------|-------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                         | 10X5  | 12X6 | 14X7 | 16X8  | 10X5  | 12X6  | 14X7  | 16X8  | 10X5  | 12X6  | 14X7  | 16X8  |

| With solder mask (°C)   | 10.22 | 9.79 | 9.40 | 9.17  | 35.46 | 33.09 | 30.70 | 28.78 | 65.18 | 62.20 | 60.65 | 53.76 |

| Without solder mask (℃) | 9.13  | 9.02 | 7.88 | 7.78  | 32.71 | 30.41 | 27.64 | 25.25 | 60.30 | 57.47 | 54.81 | 48.45 |

| Temp. difference (°C)   | 1.09  | 0.77 | 1.52 | 1.39  | 2.75  | 2.68  | 3.06  | 3.53  | 4.88  | 4.55  | 5.84  | 5.31  |

| Average (°C)            |       | 1.2  |      | 3     |       |       |       | 5.1   |       |       |       |       |

Table 11 illustrates that the minimum difference between temperature rises with and without solder mask was about 1°C. The maximum difference was about 5°C.

Assuming the forward voltage was  $V_f$ =2.5 V, the total power at 0.3 A was  $P = V_f X I_f = 2.5 V X 0.3 A = 0.75 W$ . The temperature difference was  $\Delta T = 3^{\circ}C$ , the thermal resistance difference was  $\Delta R th_{ia} = \Delta T/P = 3^{\circ}C/0.75 W = 4^{\circ}C/W$ .

# Conclusion 3 concerning with / without solder mask

If the solder mask on the copper around the D2PAK device is removed, the total thermal resistance Rth<sub>ia</sub> will decrease  $4 \, ^{\circ}\text{C/W}$ .

# Thermal design recommendation and guideline for SMD package

Test result and interpretation

#### The influence of THT vias diameter 4.4

This part tested and analyzed the temperature rises with different diameters of THT vias on different kinds of PCB and with different currents.

The diameters of the inner vias were 0.3 mm, 0.4 mm and 0.5 mm, and the diameters of the outer vias were 0.5 mm. The current range was 0.1 A to 0.5 A.

At first, the temperature rises with different diameters of THT vias at 0.3 A current were analyzed.

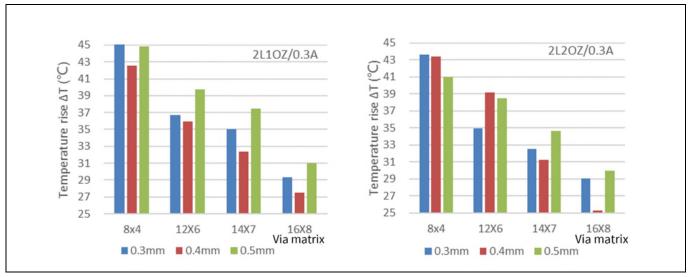

#### 4.4.1 Test on 2L1OZ / 2L2OZ at 0.3A

Table 12 Temperature rise in 2L1OZ/2L2OZ PCB at 0.3 A for different inner via diameters

| Current at 0.3 A          |       | 2L10Z ( | OZ (Unit: ℃) 2L2OZ (Unit |       |       |       |       |       |

|---------------------------|-------|---------|--------------------------|-------|-------|-------|-------|-------|

| Via matrix                | 8x4   | 12X6    | 14X7                     | 16X8  | 8x4   | 12X6  | 14X7  | 16X8  |

| Inner via diameter 0.3 mm | 46.84 | 36.71   | 35.03                    | 29.37 | 43.63 | 34.92 | 32.54 | 29.09 |

| Inner via diameter 0.4 mm | 42.59 | 35.97   | 32.35                    | 30.51 | 43.43 | 39.18 | 31.29 | 25.27 |

| Inner via diameter 0.5 mm | 44.85 | 39.76   | 37.44                    | 31.04 | 40.98 | 38.53 | 34.66 | 29.95 |

The test results in Table 12 above could be transferred to Figure 13 below.

Temperature rise in 2L10Z/2L20Z PCB at 0.3 A Figure 13

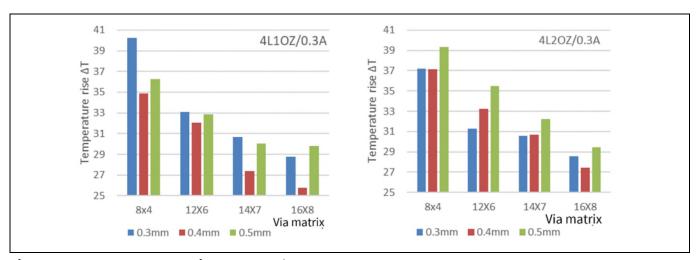

#### 4.4.2 Test on 4L10Z / 4L20Z at 0.3 A

Similar thermal tests were carried out on the 4l1OZ and 4L2OZ to check their performance. The data is recorded in Table 13 below.

Table 13 Temperature rise in 4L10Z/20Z PCB at 0.3 A

| Current 0.3 A             |       | 4L10Z ( | Unit: ℃) |       | 4L2OZ (Unit: ℃) |       |       |       |  |

|---------------------------|-------|---------|----------|-------|-----------------|-------|-------|-------|--|

| Via rray                  | 8x4   | 12X6    | 14X7     | 16X8  | 8x4             | 12X6  | 14X7  | 16X8  |  |

| Inner via diameter 0.3 mm | 40.25 | 33.09   | 30.70    | 28.78 | 37.23           | 31.26 | 29.55 | 28.56 |  |

| Inner via diameter 0.4 mm | 34.90 | 32.08   | 27.40    | 25.79 | 37.15           | 33.23 | 30.69 | 27.41 |  |

| Inner via diameter 0.5 mm | 36.29 | 32.87   | 30.06    | 29.82 | 39.33           | 35.47 | 32.26 | 29.43 |  |

The test results from Table 13 above could be transferred to Figure 14 below.

# Thermal design recommendation and guideline for SMD package

### **Test result and interpretation**

Figure 14 Temperature rise on 4L1OZ/2OZ PCB at 0.3 A

It can be observed from the above four figures that almost all via matrixes with a via diameter of 0.4 mm result in the lowest temperature rise on different PCBs. They have the most significant effect on the PCBs with 1 oz. copper thickness.

It should be noted that when the via matrix was small and a 2 oz. copper thickness PCB was applied, the 0.3 mm via diameter also had an advantage in heat dissipation. Sometimes it has better performance than the 0.4 mm one (for example, with the via matrix 12x6 on a 2 oz. copper PCB).

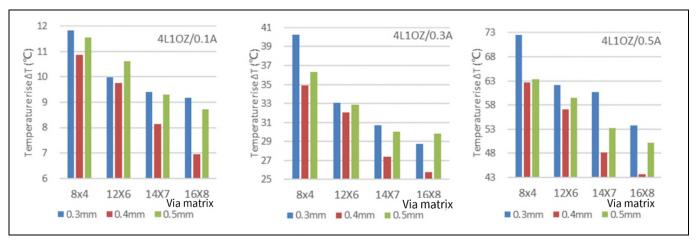

Moreover, the temperature rises with different diameters of THT vias under different currents are analyzed. Let us take a 4L1OZ PCB as an example:

Table 14 Temperature rise with 0.3, 0.4 and 0.5 mm inner via diameters at 0.1, 0.3 and 0.5 A on 4L1OZ

| <b>4L10Z</b> (Unit: °C) | 0.1 A |       |      |      | 0.3 A |       |       |       | 0.5 A |       |       |       |

|-------------------------|-------|-------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

|                         | 8x4   | 12X6  | 14X7 | 16X8 | 8x4   | 12X6  | 14X7  | 16X8  | 8x4   | 12X6  | 14X7  | 16X8  |

| Inner via 0.3 mm        | 11.81 | 9.99  | 9.40 | 9.17 | 40.25 | 33.09 | 30.70 | 28.78 | 72.50 | 62.20 | 60.65 | 53.76 |

| Inner via 0.4 mm        | 10.87 | 9.75  | 8.14 | 6.95 | 34.90 | 32.08 | 27.40 | 25.79 | 62.73 | 57.04 | 48.21 | 43.65 |

| Inner via 0.5 mm        | 11.55 | 10.61 | 9.30 | 8.72 | 36.29 | 32.87 | 30.06 | 29.82 | 63.30 | 59.45 | 53.18 | 50.12 |

Table 14 further illustrates that under different current conditions, the 0.4 mm diameter had the advantage in heat dissipation. In other words, the temperature rises with the 0.4 mm via matrixes is lower. It is worth mentioning that this advantage is more significant in the case of high current.

# Thermal design recommendation and guideline for SMD package

### Test result and interpretation

Figure 15 Temperature rise with 0.3, 0.4 and 0.5 mm diameters at 0.1, 0.3 and 0.5 A

According to the test result, we could conclude that 0.4 mm diameter produces the best thermal performance compared with 0.3 mm and 0.5 mm. It indicated that top-layer copper is very important for heat transmission, while the air inside the thermal vias is an inefficient thermal conductor. Hence, there is a trade-off between increasing the amount of copper and the volume of air through the vias.

# **Conclusion 4 concerning inner via diameters**

0.4 mm inner via diameter results in the lowest temperature rise compared to 0.3 mm and 0.5 mm.

# Thermal design recommendation and guideline for SMD package

**Test result and interpretation**

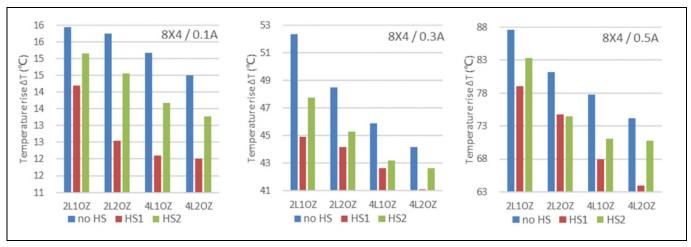

# 4.5 The influence of heat sink

Finally, the influence of the heat sink on temperature rise is considered. The experimental data is compared with the situation without a heat sink. The via matrix used in this test is 8 x 4, with no via matrix surrounding the pad. The diameter of the THT via was 0.4 mm. Figure 6 above and Table 5 above describe the heat sink assembly on the board. The measurement point was located at the side of the package in this test.

Table 15 Temperature rise of different heat sinks on 2L1OZ/2OZ and 4L1OZ/2OZ PCB at 0.1, 0.3 and 0.5 A

| PCB type and current   | 0.1 A |       |       |       | 0.3 A |       |       |       | 0.5 A |       |       |       |

|------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                        | 2L10Z | 2L20Z | 4L10Z | 4L20Z | 2L10Z | 2L20Z | 4L10Z | 4L20Z | 2L10Z | 2L20Z | 4L10Z | 4L20Z |

| Without heat sink (°C) | 15.94 | 15.74 | 15.17 | 14.50 | 52.34 | 48.49 | 45.87 | 44.16 | 87.56 | 81.22 | 77.75 | 74.18 |

| With heat sink HS1(°C) | 14.19 | 12.54 | 12.10 | 12.01 | 44.94 | 44.18 | 42.67 | 41.09 | 79.02 | 74.75 | 67.93 | 64.00 |

| With heat sink HS2(°C) | 15.15 | 14.57 | 13.68 | 13.27 | 47.76 | 45.29 | 43.21 | 42.66 | 83.33 | 74.47 | 71.08 | 70.80 |

The test data in Table 15 above could be transferred to Figure 16 below.

Figure 16 Temperature rise of different heat sinks at 0.1, 0.3 and 0.5 A

From the above chart, it is clear that heat sinks produce a positive effect on heat dissipation. Under large currents, adding a heat sink reduced the temperature rise by about  $10^{\circ}$ C.

Additionally, HS1 had better performance than HS2 in heat dissipation, since HS1 was made of copper while HS2 was made of aluminum.

Conclusion 5 concerning the selection of heat sink

Copper heat sinks help the heat dissipation to the largest extent.

# Thermal design recommendation and guideline for SMD package

Test result and interpretation

#### Whether a heat sink is needed 4.6

This test compares the change of temperature rise under the two situations: increasing heat dissipation area and installation of heat sink. Finally, suggestions are made according to the heat dissipation requirements. Whether to increase the heat dissipation area or to install heat sinks can be justified by customers.

Take the 4L1OZ PCB as an example. A heat sink was installed on Group1. Via matrixes were modified in Group2. The diameter of the inner vias for both groups was 0.4 mm. The diameter of the outer vias in the Group 2 was 0.5 mm.

The temperature rises of the two groups cannot be compared directly because the measurement points of the two sets of data are different. So, we used the 4L1OZ PCB without outer via matrix and heat sink as a benchmark to compare the two groups of data. Th second column of Table 16 and Table 17 shows the temperature measured from the side and the center of the package on the same PCB layout.

Table 16 Temperature rise under the current of 0.1 A 0.3 A and 0.5 A with different heat sinks on 4L1OZ PCB

| PCB type: 4L10Z |         |         | Heat sink  |         |           |

|-----------------|---------|---------|------------|---------|-----------|

| current         | No HS   | Н       | <b>S1</b>  | HS2     | 2         |

| 0.1 A           | 15.17℃  | 12.10°C | ΔT= 3.07°C | 13.68°C | ΔT=1.49°C |

| 0.3 A           | 45.87°C | 42.67°C | ΔT= 3.2°C  | 43.21℃  | ΔT=2.66°C |

| 0.5 A           | 77.75℃  | 67.93°C | ΔT= 9.82°C | 71.08°C | ΔT=6.67°C |

Table 17 Temperature rise under the current of 0.1 A 0.3 A and 0.5 A with different via matrixes on 4L1OZ PCB

| PCB type: 4L10Z | Via matrixes    |               |            |                   |            |                                |            |  |

|-----------------|-----------------|---------------|------------|-------------------|------------|--------------------------------|------------|--|

| Via matrix      | 8X4 (67.45 mm2) | 12X6 (16      | 33.94 mm²) | 14X7 (229.35 mm²) |            | 16X8 (309.92 mm <sup>2</sup> ) |            |  |

| 0.1 A           | 10.87℃          | 9.75 <b>℃</b> | ΔT=1.12°C  | 8.14°C            | ΔT=2.73°C  | 6.95 ℃                         | ΔT=3.92°C  |  |

| 0.3 A           | 34.90°C         | 32.08°C       | ΔT=2.82°C  | 27.40°C           | ΔT=7.5°C   | 25.79 ℃                        | ΔT=9.11°C  |  |

| 0.5 A           | 62.73℃          | 57.04°C       | ΔT=5.69°C  | 48.21°C           | ΔT=14.52°C | 43.65 °C                       | ΔT=19.08°C |  |

By subtracting the value of the 12x6, 14x7 and 16x8 via matrixes with 8x4 via matrix, the effect of increasing heat dissipation area on temperature rise can be found. In the same way, by subtracting the value of HS1 and HS2 with the value No HS, the effect of the heat sink on temperature rise can be found.

Based on the above analysis, the new data are as follows:

Firstly, the temperature of the 8x4 via matrix and the no-heat sink version was set to 0 ℃ for easier comparison. The negative number represents the amount of temperature decrease compared with '8x4 via matrix' or 'No HS.'

From the above tables, it can be concluded that the effect of installing the heat sink is greater than small heat dissipation area at 0.1, 0.3 and 0.5 A current. When the heat dissipation area increases, the heat dissipation will be better than the installation of heat sinks.

# Thermal design recommendation and guideline for SMD package

### **Test result and interpretation**

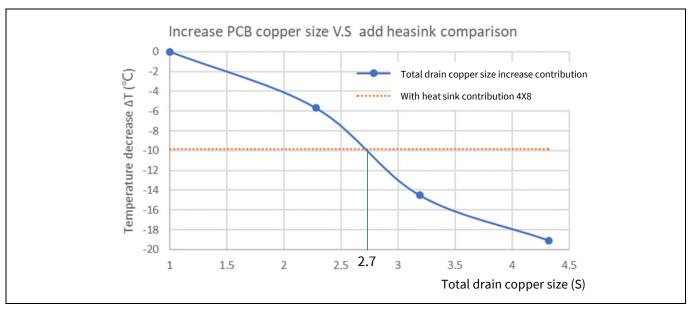

Figure 17 Thermal performance comparison of PCB copper size and HS1 at 0.5 A current

From the above figure, it can be seen more accurately that when the area is less than 2.7 S, the heat sink method is better. On the other hand, when the heat dissipation area increases, the more heat dissipation is better.

In other words, it is more effective to adopt the strategy of increasing the heat dissipation area in order to improve the heat dissipation greatly, when the heat dissipation area is large enough.

### Conclusion 6 whether a heat sink is needed

Only when the total drain copper size is smaller than 2.7S (182.12 mm<sup>2</sup>), it is necessary to consider adding a heat sink.

# Thermal design recommendation and guideline for SMD package

**Conclusions**

#### 5 **Conclusions**

After testing the thermal behavior of a 1700 V SiC MOSFET in a TO-263 package under various conditions, we have summarized the key aspects for achieving the optimal cooling performance on PCBs. The test results show that the 4L2OZ board has a better cooling effect than the 2L1OZ board. However, the influence of the board type is less critical when the total drain copper area is greater than three times the copper area under the pad (≥200 mm²). Also, it was found that 0.4 mm thermal vias under and around the pad led to lower temperature changes. The soldering mask around the pad increases the total thermal resistance R<sub>thia</sub> by about 4°C/W. Moreover, a heat sink improves the thermal performance when the total drain copper area is limited to 2.7 times the copper area under the pad (< 182 mm<sup>2</sup>). In this case, a copper heat sink is a better choice than an aluminum heat sink. The data shows that the MOSFET has excellent heat performance even without a heat sink, so the engineers should consider abandoning heat sinks in their design when the via matrix size is large.

# Thermal design recommendation and guideline for SMD package

#### **References**

#### 6 References

- Datasheet: Infineon-IMBF170R1K0M1-DataSheet-v02\_01-EN

- Application note: AN201708-Thermal Performance of surface mount semiconductor packages

- General Recommendations for **Assembly** of Infineon **Packages** [Online]. Available: [3] https://www.infineon.com/dgdl/Infineon-General\_Recommendations\_for\_Assembly\_of\_Infineon\_Packages-P-v04\_00-EN.pdf?fileId=5546d4625cc9456a015ccaf4a1fe3a32

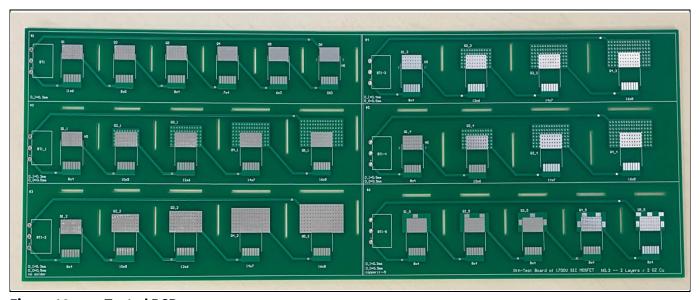

# **Appendix: PCBs**

Figure 18 **Tested PCBs**

# Thermal design recommendation and guideline for SMD package

**Revision history**

# **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| V1.0             | 2021/02/19      | Initial creation       |

| V1.1             | 2021/04/20      | Updated                |

| V2.0             | 2021/05/03      | Updated                |

### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021/05/03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AN-2021-02

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.