ADC\_Filtering\_1

for KIT\_AURIX\_TC375\_LK

ADC filtering

AURIX™ TC3xx Microcontroller Training V1.0.0

### Scope of work

# Four EVADC channels are used to convert the same analog signal with different filters enabled.

The Enhanced Versatile Analog-to-Digital Converter (EVADC) module is configured to convert four channels. The data resulting from the conversions of three channels is automatically modified: one channel computes an average on 4 results, another channel applies a 3<sup>rd</sup> order Finite Impulse Response (FIR) filter and another channel applies a 1<sup>st</sup> order Infinite Impulse Response (IIR) filter. Finally, the last channel measures the same signal without Data Modification. The channels are continuously converted and, for each of them, the maximum and minimum values are stored, which are then sent through UART in order to be compared.

#### Introduction

- The Enhanced Versatile Analog-to-Digital Converter module (EVADC) of the AURIX™ TC37x comprises 8 independent analog to digital converters (EVADC groups) with up to 16 analog input channels each.

- Each channel can convert analog inputs with a resolution of up to 12-bit.

- Analog/Digital conversions can be requested by several request sources:

- Queued request source, specific to a single group

- Synchronization source, synchronized conversion request from another ADC master kernel

- A queued request source provides several buffer stages building a queue and can handle application-specific arbitrary conversion sequences up to the queue size.

- The trigger for the conversion can be sent:

- Once (by another external module)

- On a regular time base (by an external timer)

- Permanently (by using the refill option)

# infineon

#### Introduction

- > The data resulting from conversions can be automatically modified before being used by an application to reduce the required CPU/DMA load to process the conversion.

- Three types of data modification are supported:

- Standard Data Reduction Mode

- Result Filtering Mode

- Difference Mode

- With Standard Data Reduction Mode, the EVADC accumulates up to 16 values before generating a result interrupt. This mode can be used on any result register of any group GxRES0..GxRES15, where x is the number of the group.

- When **Result Filtering Mode** is enabled, depending on the configuration, the EVADC can apply either a 3<sup>rd</sup> order Finite Impulse Response (FIR) filter with selectable coefficients, or a 1<sup>st</sup> order Infinite Impulse Response (IIR) filter with selectable coefficients to the conversion results. This mode can be applied on the result registers GxRES7 and GxRES15 of any group, where x is the number of the group.

- > The **Difference Mode** subtracts the content of the result register GxRES0 from the conversion results. This mode can be used on the result registers GxRES1..GxRES15 of any group, where x is the number of the group.

### Hardware setup

This code example has been developed for the board KIT\_A2G\_TC375\_LITE.

In this example, the pins AN36, AN37, AN38 and AN39 are used, connected to a voltage source.

| 7201 | ,    |         |

|------|------|---------|

| 6    | AN25 | (P40.1) |

| 5    | AN24 | (P40.0) |

| 4    | AN36 | (P40.6) |

| 3    | AN37 | (P40.7) |

| 2    | AN38 | (P40.8) |

| 1    | AN39 | (P40.9) |

**Note**: The channels can be HW filtered by the board, depending on which capacitor/resistors couples are soldered. Consult the AURIX<sup>™</sup> TC375 lite Kit's User Manual to check which channels are filtered by HW.

**Note**: The reference voltage (VAREF) of the EVADC on the board KIT\_A2G\_TC375\_LITE is 3.3 V.

#### Configuration of the EVADC

The configuration of the EVADC is done in the *initADC()* function in four different steps:

- Configuration of the EVADC module

- Configuration of the EVADC group

- Configuration of the EVADC channels

- Configuration of the data modification

#### Configuration of the EVADC module

The default configuration of the EVADC module, given by the iLLDs, can be used for this example.

This is done by initializing an instance of the *IfxEvadc\_Adc\_Config* structure and applying default values to its fields through the function *IfxEvadc\_Adc\_initModuleConfig()*.

Then, the configuration can be applied to the EVADC module with the function IfxEvadc\_Adc\_initModule().

#### Configuration of the EVADC group

The configuration of the EVADC group is done by initializing an instance of the *IfxEvadc\_Adc\_GroupConfig* structure with default values through the function *IfxEvadc\_Adc\_initGroupConfig()* and modifying the following fields:

- arbiter a structure that represents the enabled request sources, which can be one of the three queue sources. In this example, arbiter.requestSlotQueue0Enabled is set to TRUE, thus enabling the request queue 0.

- > queueRequest[0] a structure that allows to configure the queue request source 0 by setting:

- triggerConfig a parameter that specifies the trigger configuration

- **master** to indicate which converter is the master

- groupld to select which converter to configure

The configuration is applied through the function <code>IfxEvadc\_Adc\_initGroup()</code>.

#### Configuration of the EVADC channels

The configuration of each channel is done by initializing an instance of the *IfxEvadc\_Adc\_ChannelConfig* structure with default values through the function *IfxEvadc\_Adc\_initChannelConfig()* and modifying the following fields:

- > channelld to select the channel to configure

- resultRegister to indicate the register where the A/D conversion value is stored

Then, the configuration is applied with the function *IfxEvadc\_Adc\_initChannel()* and the channel is added to the queue through the function *IfxEvadc\_Adc\_addToQueue()*.

Finally, the result registers used for storing the conversion results can be configured to use data modification, in order to enable the filtering.

#### Configuration of the data modification

The data modification is configured in the *applyFiltering()* function.

To support the EVADC data modification it is needed to directly modify the Group Result Control Registers (GxRCRy, with x indicating the Group number and y indicating the result register where to apply the filtering).

#### Configuration of the data modification

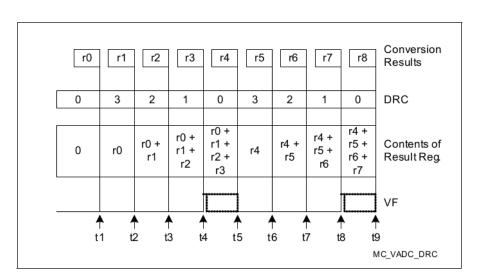

To enable the **Standard Data Reduction Mode** on a specific result register, the Data Modification Mode (DMM) bit field of the associated GxRCRy register must be set to **IfxEvadc\_DataModificationMode\_standardDataReduction** (00<sub>B</sub>) and the Data Reduction Control (DRCTR) bit field of the same register can be set to one of the values presented in <u>table 1</u>.

When the conversion is ready, depending on the configuration of the DRCTR bit field, the result register contains the sum of up to 16 result values, thus it is needed to divide the content of the result register GxRESy by the number of the accumulated values in order to obtain an average of the measurements.

**Note:** Using Standard Data Reduction Mode, the final result must be read before the next data reduction sequence starts (before t5 or t9 in the example), otherwise the Valid Flag (**VF**) bitfield **will not be cleared**.

In order to read a correct measurement, VF must be 1 and Data Reduction Counter (DRC) bitfield must be 0.

#### **Configuration of the data modification: Table 1**

| DMM             | DRCTR                                                           | Filter coefficients         |

|-----------------|-----------------------------------------------------------------|-----------------------------|

| 00 <sub>B</sub> | 0000 <sub>B</sub> = IfxEvadc_DataReductionControlMode_0         | Data Reduction disabled     |

| 00 <sub>B</sub> | 0001 <sub>B</sub> = IfxEvadc_DataReductionControlMode_1         | Accumulate 2 result values  |

| 00 <sub>B</sub> | 0010 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_2</i>  | Accumulate 3 result values  |

| 00 <sub>B</sub> | 0011 <sub>B</sub> = IfxEvadc_DataReductionControlMode_3         | Accumulate 4 result values  |

| 00 <sub>B</sub> | 0100 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_4</i>  | Accumulate 5 result values  |

| 00 <sub>B</sub> | 0101 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_5</i>  | Accumulate 6 result values  |

| 00 <sub>B</sub> | 0110 <sub>B</sub> = IfxEvadc_DataReductionControlMode_6         | Accumulate 7 result values  |

| 00 <sub>B</sub> | 0111 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_7</i>  | Accumulate 8 result values  |

| 00 <sub>B</sub> | 1000 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_8</i>  | Accumulate 9 result values  |

| 00 <sub>B</sub> | 1001 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_9</i>  | Accumulate 10 result values |

| 00 <sub>B</sub> | 1010 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_10</i> | Accumulate 11 result values |

| 00 <sub>B</sub> | 1011 <sub>B</sub> = IfxEvadc_DataReductionControlMode_11        | Accumulate 12 result values |

| 00 <sub>B</sub> | 1100 <sub>B</sub> = IfxEvadc_DataReductionControlMode_12        | Accumulate 13 result values |

| 00 <sub>B</sub> | 1101 <sub>B</sub> = IfxEvadc_DataReductionControlMode_13        | Accumulate 14 result values |

| 00 <sub>B</sub> | 1110 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_14</i> | Accumulate 15 result values |

| 00 <sub>B</sub> | 1111 <sub>B</sub> = IfxEvadc_DataReductionControlMode_15        | Accumulate 16 result values |

#### Configuration of the data modification

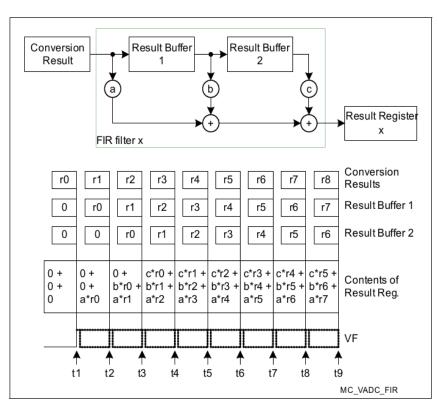

To enable the **Result Filtering Mode** on a specific result register, the Data Modification Mode (DMM) bit field of the associated GxRCRy register must be set to *IfxEvadc\_DataModificationMode\_resultFilteringMode* (01<sub>B</sub>) and the Data Reduction Control (DRCTR) bit field of the same register can be set to enable either a 3<sup>rd</sup> order Finite Impulse Response (FIR) filter or a 1<sup>st</sup> order Infinite Impulse Response (IIR) filter, both with selectable coefficients, according to the values in <u>table 2</u>.

When a **FIR filter** is enabled, depending on the selected coefficients, a gain of 3 or 4 (the DC gain of a FIR filter is equal to the sum of its coefficients) is applied to the ADC result, producing a 14-bit value.

Therefore, in order to obtain the filtered measurement, it is needed to divide the content of the result register by the sum of the selected coefficients.

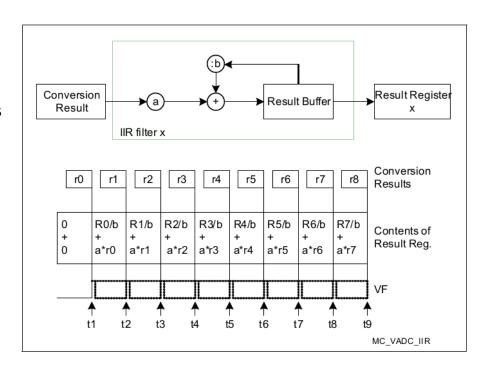

#### Configuration of the data modification

The selectable coefficients for an **IIR filter** lead to a gain of 4 to the ADC result, producing a 14-bit value. Consequently, in order to obtain the filtered measurement, the content of the result register needs to be divided by 4.

All the measurement's divisions are carried out in the *Cpu0\_main.c* file, after reading the conversion result from the result register.

The FIR and IIR filters needs to be initialized, otherwise the first values are incorrect (see the figures for the two filters).

**Note:** In this example, a delay before starting to read the conversion results is needed. This ensures that incorrect values are not read due to the filters not being yet at full speed.

#### Available coefficients for FIR and IIR filters: Table 2

| DMM             | DRCTR                                                           | Filter coefficients       |

|-----------------|-----------------------------------------------------------------|---------------------------|

| 01 <sub>B</sub> | 0000 <sub>B</sub> = IfxEvadc_DataReductionControlMode_0         | FIR filter: a=2, b=1, c=0 |

| 01 <sub>B</sub> | 0001 <sub>B</sub> = IfxEvadc_DataReductionControlMode_1         | FIR filter: a=1, b=2, c=0 |

| 01 <sub>B</sub> | 0010 <sub>B</sub> = IfxEvadc_DataReductionControlMode_2         | FIR filter: a=2, b=0, c=1 |

| 01 <sub>B</sub> | 0011 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_3</i>  | FIR filter: a=1, b=1, c=1 |

| 01 <sub>B</sub> | 0100 <sub>B</sub> = IfxEvadc_DataReductionControlMode_4         | FIR filter: a=1, b=0, c=2 |

| 01 <sub>B</sub> | 0101 <sub>B</sub> = IfxEvadc_DataReductionControlMode_5         | FIR filter: a=3, b=1, c=0 |

| 01 <sub>B</sub> | 0110 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_6</i>  | FIR filter: a=2, b=2, c=0 |

| 01 <sub>B</sub> | 0111 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_7</i>  | FIR filter: a=1, b=3, c=0 |

| 01 <sub>B</sub> | 1000 <sub>B</sub> = IfxEvadc_DataReductionControlMode_8         | FIR filter: a=3, b=0, c=1 |

| 01 <sub>B</sub> | 1001 <sub>B</sub> = IfxEvadc_DataReductionControlMode_9         | FIR filter: a=2, b=1, c=1 |

| 01 <sub>B</sub> | 1010 <sub>B</sub> = IfxEvadc_DataReductionControlMode_10        | FIR filter: a=1, b=2, c=1 |

| 01 <sub>B</sub> | 1011 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_11</i> | FIR filter: a=2, b=0, c=2 |

| 01 <sub>B</sub> | 1100 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_12</i> | FIR filter: a=1, b=1, c=2 |

| 01 <sub>B</sub> | 1101 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_13</i> | FIR filter: a=1, b=0, c=3 |

| 01 <sub>B</sub> | 1110 <sub>B</sub> = IfxEvadc_DataReductionControlMode_14        | IIR filter: a=2, b=2      |

| 01 <sub>B</sub> | 1111 <sub>B</sub> = <i>IfxEvadc_DataReductionControlMode_15</i> | IIR filter: a=3, b=4      |

#### Configuration of the data modification

In this example, the converted channels are configured as it follows:

Table 3

| Channel | Data Modification Mode enabled    |

|---------|-----------------------------------|

| AN39    | Standard Data Reduction Mode      |

| AN38    | Result Filtering Mode: IIR filter |

| AN37    | Result Filtering Mode: FIR filter |

| AN36    | No Data Modification Mode enabled |

The channel AN36 has no data modification enabled in order to use it as a comparison.

#### **Configuration of the EVADC**

When the EVADC module, its group and channels are configured together with the Data Modification registers, the scan sequence is started with the function *IfxEvadc\_Adc\_startQueue()*.

#### Read the EVADC measurements

Finally, to read a conversion, the function *readADCValue()* is used, which calls the *IfxEvadc\_Adc\_getResult()* function from iLLDs until a new measurement is returned (a new measurement is considered correct only when both the Valid Flag and the Data Reduction Counter bitfield are set to 1 and respectively 0, the latter is needed because the Standard Data Reduction Mode is enabled on the AN39 pin).

All the functions used to get a conversion and configuring the EVADC module, its group and channels can be found in the iLLD header *IfxEvadc\_Adc.h*.

#### Configuration of the UART

In this example, the UART connection is used to make the debugging more convenient and easier to understand. The configured EVADC channels are continuously read, but the maximum and minimum values, together with the computed  $V_{DD}$  are printed using UART communication only when the user requests them.

The initUART() function initializes the UART communication.

The iLLD function *IfxAsclin\_Asc\_initModuleConfig()* fills the configuration structure *ascConf* with default values. Then, the parameters used to configure the module are set, depending on the needed connection: baudrate, Tx and Rx buffers, Tx and Rx pin configuration etc.

Finally, *IfxAsclin\_Asc\_initModule()* initializes the module with the user configuration and *IfxAsclin\_Asc\_stdlfDPipeInit()* initializes the standard interface to use the ASCLIN module.

The functions *isDataAvailable()* and *receiveData()* are used to interface with the ASCLIN module to check if new data is available through the function *IfxAsclin\_Asc\_getReadCount()* and, respectively, to receive data over the UART communication through the function *IfxAsclin\_Asc\_read()*.

The function *IfxStdIf\_DPipe\_print()* is used to print the stored processed values.

The functions used to interface and initialize the ASCLIN module can be found in the iLLD header *lfxAsclin\_Asc.h*, while the latter can be found in the iLLD header *lfxStdlf\_DPipe.h*.

### Run and Test

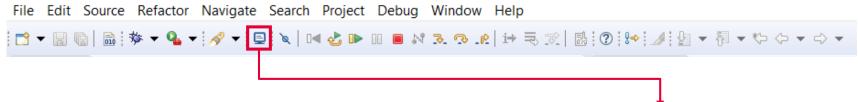

> For this training, a serial monitor is required for visualizing the values. The monitor can be opened inside the AURIX™ Development Studio using the following icon:

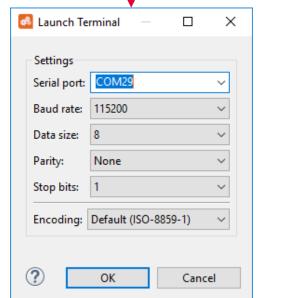

- The serial monitor must be configured with the following parameters to enable the communication between the board and the PC:

- Speed (baud): 115200

- Data bits: 8

- Stop bit: 1

### Run and Test

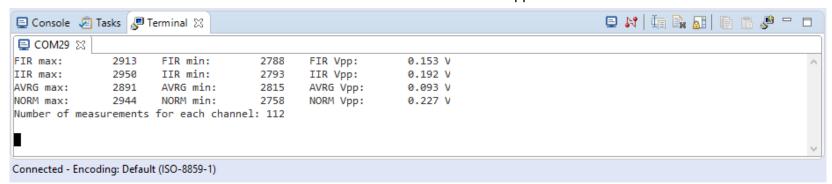

After code compilation and flashing the device, perform the following steps:

- Connect the channels AN39, AN38, AN37 and AN36 to any DC signal between 0 and 3.3V

- Open the serial monitor and start the serial communication, linked with the appropriate COMx port (this can be checked in the Device Manager)

- After a few seconds, send the character "1" to print the maximum and minimum values read by the channels, together with the computed V<sub>pp</sub>

The maximum and minimum values are expressed as a 12-bits integer value, in decimal format (0 - 4095 range), while the  $V_{pp}$  is expressed in Volts

It can be noticed that for this signal, the filter applying an average is the most effective one to reduce the  $V_{\text{pp}}$  range.

### References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference ADC\_Filtering\_1\_KIT\_TC375\_LK

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.