## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

---

本ドキュメントは Cypress (サイプレス) 製品に関する情報が記載されております。本ドキュメントには、「MB」から始まるシリーズ名、品名およびオーダ型格が記載されておりますが、これらはすべて「CY」から始まるシリーズ名、品名およびオーダ型格として、新規および既存のお客様に引き続き提供してまいります。

#### オーダ型格の調べ方について

1. [www.cypress.com/pcn](http://www.cypress.com/pcn)にアクセスしてください。

2. SEARCH PCNS フィールドに、オーダ型格などのキーワードを入力し、「Apply」をクリックしてください。

3. 該当するタイトル>Title)をクリックしてください。

4. 「Affected Parts List」ファイルを開いてください。

当該ファイルに記載されている各種変更情報をご利用ください。

#### 詳しいお問い合わせ先

Cypress 製品およびそのソリューションの詳細につきましては、お近くの営業所へお問い合わせください。

#### サイプレスについて

サイプレスは、世界で最も革新的な車載や産業機器、スマート家電、民生機器および医療機器製品向けに、最先端の組み込みシステム ソリューションを提供するリーディング カンパニーです。サイプレスのマイクロコントローラーや、アナログ IC、ワイヤレスおよび USB ベースのコネクティビティ ソリューション、高い信頼性と高性能を提供するメモリ製品は、各種機器メーカーの差異化製品の開発と早期市場参入を支援します。サイプレスは、ベストクラスのサポートと開発リソースをグローバルに提供することで、彼らが従来市場を破壊しまったく新しい製品カテゴリを歴史的なスピードで市場投入できるよう支援します。詳細はサイプレスのウェブサイト ([japan.cypress.com](http://japan.cypress.com)) をご覧ください。

# 32 ビット・マイクロコントローラ FM3 ファミリ Peripheral Manual Ethernet 編

Doc. No. 002-04783 Rev. \*B

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

<http://www.cypress.com>

© Cypress Semiconductor Corporation, 2011-2017. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下、「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア又はファームウェア（以下、「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき、Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、また、本段落で特に記載されているものを除き、Cypress の特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾していない。本ソフトウェアにライセンス契約書が伴っておらず、かつ、あなたが Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意をしていない場合、Cypress は、あなたに対して、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、(直接又は再販売者及び販売代理店を介して間接のいずれかで) エンドユーザーに対して、バイナリーコード形式で本ソフトウェアを外部に配布すること、並びに (2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）に抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サブライセンスの権利を除く）を付与する。本書面のその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェアに関するても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。** 適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のあるいかなる製品又は回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためにのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計し、プログラムし、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分として用いるため、又はシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせることになるその他の使用（以下、「本目的外使用」という。）のためには、設計、意図又は承認されていない。重要な構成部分とは、装置又はシステムのその構成部分の不具合が、その装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できる、機器又はシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ、あなたは Cypress をそれら一切から免除するものとし、本書により免除する。あなたは、Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から Cypress を免責補償する。

Cypress、Cypress のロゴ、Spansion、Spansion のロゴ及びこれらの組み合わせ、WICED、PSoC、CapsSense、EZ-USB、F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress の商標のより完全なリストは、cypress.com を参照のこと。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries.

# はじめに

Cypress(サイプレス) 製品につきまして、平素より格別のご愛顧を賜り厚くお礼申し上げます。

本ファミリをご利用になる前に、『ペリフェラルマニュアル』およびご使用する製品の『データシート』をご一読ください。

なお本書は、ペリフェラルマニュアルから Ethernet に関する内容を抜きだした別冊として定義しております。

## 本書の目的と対象読者

本書は、実際に本ファミリを使用して製品を開発される技術者を対象に、本ファミリの機能や動作、使い方について解説しています。

### ＜注意事項＞

本マニュアルは周辺機能の構成および動作を説明するものであり、各デバイスの仕様を説明するものではありません。

デバイス仕様の詳細については、それぞれのデータシートを参照してください。

### 商標

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries.

その他の社名および製品名は各社の商標もしくは登録商標です。

## サンプルプログラムおよび開発環境

FM3 ファミリの周辺機能を動作させるためのサンプルプログラムを無償で提供しております。また、本ファミリで使用する開発環境も掲載しています。当社マイコンの動作仕様や使用方法の確認などにお役立てください。

## マイコンサポート情報

<http://www.spansion.com/jp/support/microcontrollers/>

### ＜注意事項＞

サンプルプログラムは、予告なしに変更することがあります。また、サンプルプログラムは標準的な動作や使い方を示したものですので、お客様のシステム上でご使用の際は十分評価された上でご使用ください。また、サンプルプログラムの使用に起因し生じた損害については、当社は一切その責任を負いません。

## 関連マニュアル

本ファミリに関連するマニュアルを示します。状況に応じて必要なマニュアルを参照してください。

本書に記載したマニュアルの内容は予告なく変更することがあります。最新版をお問い合わせください。

### ペリフェラルマニュアル

FM3 ファミリ ペリフェラルマニュアル (002-04744)

以降、『ペリフェラルマニュアル』とよびます。

FM3 ファミリ ペリフェラルマニュアル タイマ編 (002-04837)

以降、『タイマ編』とよびます。

FM3 ファミリ ペリフェラルマニュアル アナログマクロ編 (002-4841)

以降、『アナログマクロ編』とよびます。

FM3 ファミリ ペリフェラルマニュアル 通信マクロ編 (002-04845)

以降、『通信マクロ編』とよびます。

FM3 ファミリ ペリフェラルマニュアル Ethernet 編 (本書)

以降、『Ethernet 編』とよびます。

### データシート

デバイス仕様、電気的特性、外形寸法、オーダ型格などの詳細は以下を参照してください。

32 ビット FM3 ファミリ データシート

### <注意事項>

データシートはシリーズごとに用意されています。

ご使用する製品のデータシートを参照してください。

### CPU プログラミングマニュアル

ARM Cortex-M3 コアの詳細は <http://www.arm.com/> から入手できる以下を参照してください。

Cortex-M3 テクニカルリファレンスマニュアル

ARMv7-M アーキテクチャ アプリケーション レベル リファレンス マニュアル

### フラッシュプログラミングマニュアル

内蔵されているフラッシュメモリの機能や動作の詳細は以下を参照してください。

FM3 ファミリ フラッシュプログラミングマニュアル

### <注意事項>

フラッシュプログラミングマニュアルはシリーズごとに用意されています。

ご使用する製品のフラッシュプログラミングマニュアルを参照してください。

## 本書の使い方

### 機能の探し方

本書では次の方法で、使いたい機能の説明を探すことができます。

目次から探す

本書の内容を記載順に示します。

### 章について

本書では、Ethernetについて説明しています。

### 用語について

本書で使用している用語について示します。

| 用語     | 説明                   |

|--------|----------------------|

| ワード    | 32 ビット単位でのアクセスを指します。 |

| ハーフワード | 16 ビット単位でのアクセスを指します。 |

| バイト    | 8 ビット単位でのアクセスを指します。  |

### 表記について

本書のレジスタ説明中のビット構成図では以下のように表記しています。

|        |                |

|--------|----------------|

| bit:   | ビット番号          |

| Field: | ビットフィールド名      |

| 属性:    | 各ビットのリード、ライト属性 |

| R:     | リードオンリ         |

| W:     | ライトオンリ         |

| R/W:   | リード・ライト可能      |

| -:     | 未定義            |

| 初期値:   | リセット直後のレジスタ初期値 |

| 0:     | 初期値"0"         |

| 1:     | 初期値"1"         |

| X:     | 初期値不定          |

本書では、複数のビットを以下のように表記しています。

例: bit7 から bit0 の場合は bit7:0

本書では、アドレスなどの数値を以下のように表記しています。

16進数: プレフィックス(接頭辞)として"0x"を付けて表記しています(例 : 0xFFFF)。

2進数: プレフィックス(接頭辞)として"0b"を付けて表記しています(例 : 0b1111)。

10進数: 数値だけで表記しています(例 : 1000)。

## 本マニュアルにおける対象製品

Table 1 対象製品一覧

| シリーズ名         | 型格                                                                     |

|---------------|------------------------------------------------------------------------|

| MB9BD10T シリーズ | MB9BFD18S, MB9BFD18T,<br>MB9BFD17S, MB9BFD17T,<br>MB9BFD16S, MB9BFD16T |

| MB9B610T シリーズ | MB9BF618S, MB9BF618T,<br>MB9BF617S, MB9BF617T,<br>MB9BF616S, MB9BF616T |

| MB9B210T シリーズ | MB9BF218S, MB9BF218T,<br>MB9BF217S, MB9BF217T,<br>MB9BF216S, MB9BF216T |

# Contents

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>CHAPTER 1: Ethernet .....</b>                                      | <b>9</b>  |

| 1. 概要 .....                                                           | 10        |

| 2. Ethernet の入出力信号 .....                                              | 13        |

| 3. Ethernet-MAC セットアップ制御手順 .....                                      | 17        |

| 4. Ethernet システム制御部レジスタ .....                                         | 18        |

| 4.1. モード選択レジスタ (ETH_MODE) .....                                       | 19        |

| 4.2. クロックゲーティングレジスタ (ETH_CLKG) .....                                  | 21        |

| <b>CHAPTER 2: Ethernet-MAC .....</b>                                  | <b>23</b> |

| 1. 概要 .....                                                           | 24        |

| 2. ブロック構成 .....                                                       | 25        |

| 3. アーキテクチャ .....                                                      | 26        |

| 3.1. 端子機能 .....                                                       | 27        |

| 3.2. AHB アプリケーション・ホスト・インターフェース .....                                  | 29        |

| 3.3. DMA コントローラ .....                                                 | 30        |

| 3.4. チェックサムエンジン .....                                                 | 42        |

| 3.5. Energy Efficient Ethernet .....                                  | 45        |

| 3.6. MAC マネジメントカウンタ .....                                             | 48        |

| 3.7. Station Management Agent .....                                   | 50        |

| 3.8. IEEE1588 .....                                                   | 52        |

| 4. レジスタ .....                                                         | 61        |

| 4.1. GMAC Register 0 (MCR) .....                                      | 71        |

| 4.2. GMAC Register 1 (MFFR) .....                                     | 75        |

| 4.3. GMAC Register 2, 3 (MHTRH, MHTRL) .....                          | 80        |

| 4.4. GMAC Register 4 (GAR) .....                                      | 81        |

| 4.5. GMAC Register 5 (GDR) .....                                      | 83        |

| 4.6. GMAC Register 6 (FCR) .....                                      | 84        |

| 4.7. GMAC Register 7 (VTR) .....                                      | 86        |

| 4.8. GMAC Register 10 (RWFFR) .....                                   | 88        |

| 4.9. GMAC Register 11 (PMTR) .....                                    | 90        |

| 4.10. GMAC Register 12 (LPICSR) .....                                 | 92        |

| 4.11. GMAC Register 13 (LPITCR) .....                                 | 94        |

| 4.12. GMAC Register 14 (ISR) .....                                    | 95        |

| 4.13. GMAC Register 15 (IMR) .....                                    | 97        |

| 4.14. GMAC Register 16 (MAR0H) .....                                  | 98        |

| 4.15. GMAC Register 17 (MAR0L) .....                                  | 100       |

| 4.16. GMAC Register 18,20,22,..., 542)( MAR1H, 2H, 3H,..., 31H) ..... | 101       |

| 4.17. GMAC Register 19,21,23,..., 543 ( MAR1L, 2L, 3L,..., 31L) ..... | 103       |

| 4.18. GMAC Register 54 (RGSR) .....                                   | 104       |

| 4.19. GMAC Register 448 (TSCR) .....                                  | 105       |

| 4.20. GMAC Register 449 (SSIR) .....                                  | 108       |

| 4.21. GMAC Register 450 (STSIR) .....                                 | 109       |

| 4.22. GMAC Register 451 (STNIR) .....                                 | 110       |

| 4.23. GMAC Register 452 (STSUR) .....                                 | 111       |

| 4.24. GMAC Register 453 (STNUR) .....                                 | 112       |

| 4.25. GMAC Register 454 (TSAR) .....                                  | 113       |

## Contents

|                                                      |     |

|------------------------------------------------------|-----|

| 4.26. GMAC Register 455 (TTSR) .....                 | 114 |

| 4.27. GMAC Register 456 (TTNR) .....                 | 115 |

| 4.28. GMAC Register 457 (STHWSR) .....               | 116 |

| 4.29. GMAC Register 458 (TSR).....                   | 117 |

| 4.30. GMAC Register 459 (PPSCR) .....                | 119 |

| 4.31. GMAC Register 460 (ATNR) .....                 | 121 |

| 4.32. GMAC Register 461 (ATSR) .....                 | 122 |

| 4.33. DMA Register 0 (BMR).....                      | 123 |

| 4.34. DMA Register 1 (TPDR).....                     | 126 |

| 4.35. DMA Register 2 (RPDR) .....                    | 127 |

| 4.36. DMA Register 3 (RDLAR) .....                   | 128 |

| 4.37. DMA Register 4 (TDLAR).....                    | 129 |

| 4.38. DMA Register 5 (SR).....                       | 130 |

| 4.39. DMA Register 6 (OMR) .....                     | 134 |

| 4.40. DMA Register 7 (IER).....                      | 137 |

| 4.41. DMA Register 8 (MFBOCR) .....                  | 140 |

| 4.42. DMA Register 9 (RIWTR).....                    | 142 |

| 4.43. DMA Register 11 (AHBSR) .....                  | 143 |

| 4.44. DMA Register 18 (CHTDR) .....                  | 144 |

| 4.45. DMA Register 19 (CHRDR).....                   | 145 |

| 4.46. DMA Register 20 (CHTBAR).....                  | 146 |

| 4.47. DMA Register 21 (CHRBAR) .....                 | 147 |

| 4.48. MMC Register list.....                         | 148 |

| 4.49. GMAC Register.64 (mmc_cntl) .....              | 155 |

| 4.50. GMAC Register.65 (mmc_intr_rx) .....           | 156 |

| 4.51. GMAC Register.66 (mmc_intr_tx) .....           | 158 |

| 4.52. GMAC register.67 (mmc_intr_mask_rx) .....      | 160 |

| 4.53. GMAC Register.68 (mmc_ipc_intr_tx) .....       | 162 |

| 4.54. GMAC Register.128 (mmc_ipc_intr_mask_rx) ..... | 164 |

| 4.55. GMAC Register.130 (mmc_ipc_intr_rx).....       | 166 |

| 5. ディスクリプタ .....                                     | 168 |

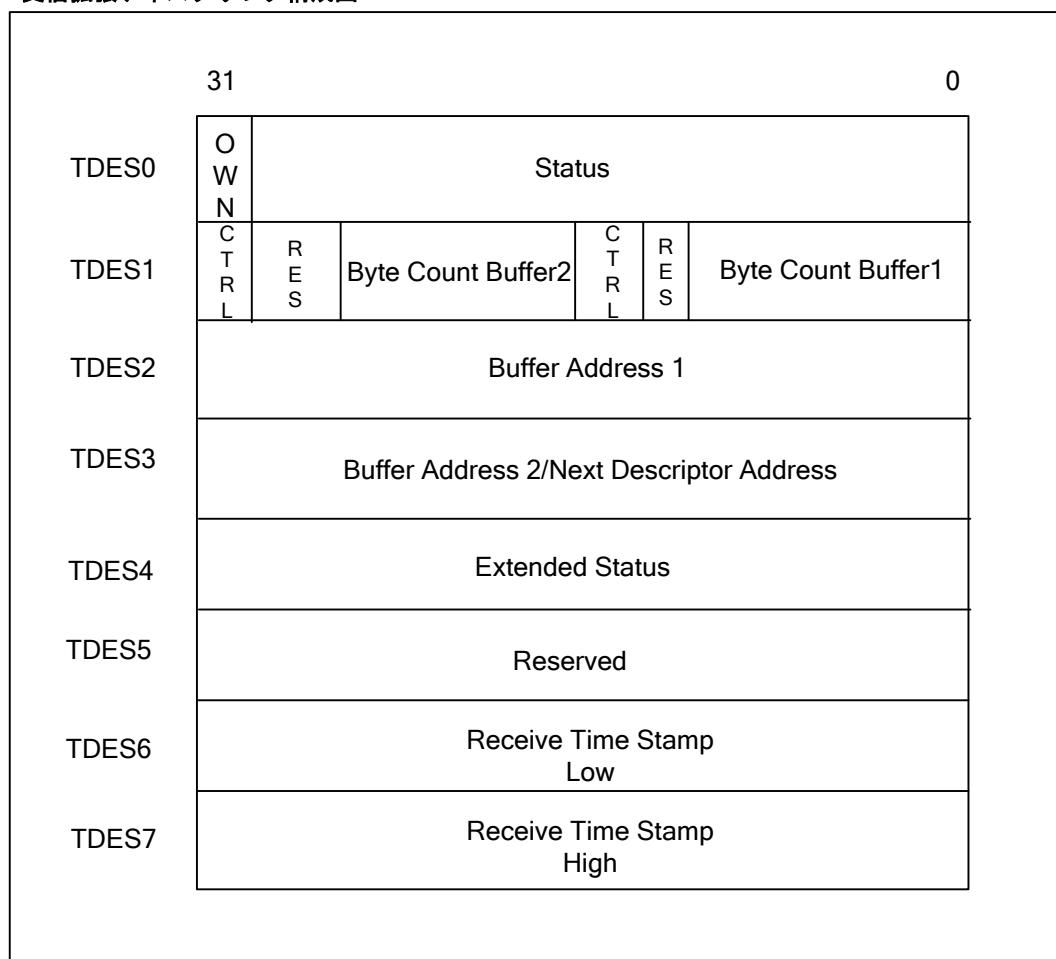

| 5.1. 送信拡張ディスクリプタ .....                               | 169 |

| 5.1.1. Transmit Enhanced Descriptor 0 (TDES0).....   | 170 |

| 5.1.2. Transmit Enhanced Descriptor 1 (TDES1).....   | 174 |

| 5.1.3. Transmit Enhanced Descriptor 2 (TDES2).....   | 175 |

| 5.1.4. Transmit Enhanced Descriptor 3 (TDES3).....   | 176 |

| 5.1.5. Transmit Enhanced Descriptor 6 (TDES6).....   | 177 |

| 5.1.6. Transmit Enhanced Descriptor 7 (TDES7).....   | 178 |

| 5.2. 受信拡張ディスクリプタ .....                               | 179 |

| 5.2.1. Receive Enhanced Descriptor 0 (RDES0) .....   | 180 |

| 5.2.2. Receive Enhanced Descriptor 1 (RDES1) .....   | 183 |

| 5.2.3. Receive Enhanced Descriptor 2 (RDES2) .....   | 184 |

| 5.2.4. Receive Enhanced Descriptor 3 (RDES3) .....   | 185 |

| 5.2.5. Receive Enhanced Descriptor 4 (RDES4) .....   | 186 |

| 5.2.6. Receive Enhanced Descriptor 6 (RDES6) .....   | 188 |

| 5.2.7. Receive Enhanced Descriptor 7 (RDES7) .....   | 189 |

| 6. プログラミングガイド.....                                   | 190 |

| 主な変更内容.....                                          | 195 |

| 改訂履歴.....                                            | 197 |

# CHAPTER 1: Ethernet

---

Ethernet 関連ブロックの構成について説明します。

---

1. 概要

2. Ethernet の入出力信号

3. Ethernet-MAC セットアップ制御手順

4. Ethernet システム制御部レジスタ

## 1. 概要

Ethernet 機能の概要と Ethernet-MAC セットアップ制御手順について説明します。

### ■ 概要

本ファミリの Ethernet 機能は、Ethernet-MAC 部と、その周辺回路から構成されます。本章では、Ethernet-MAC 周辺回路の説明と、Ethernet-MAC セットアップ制御手順について説明します。

### ■ ブロックダイヤグラム

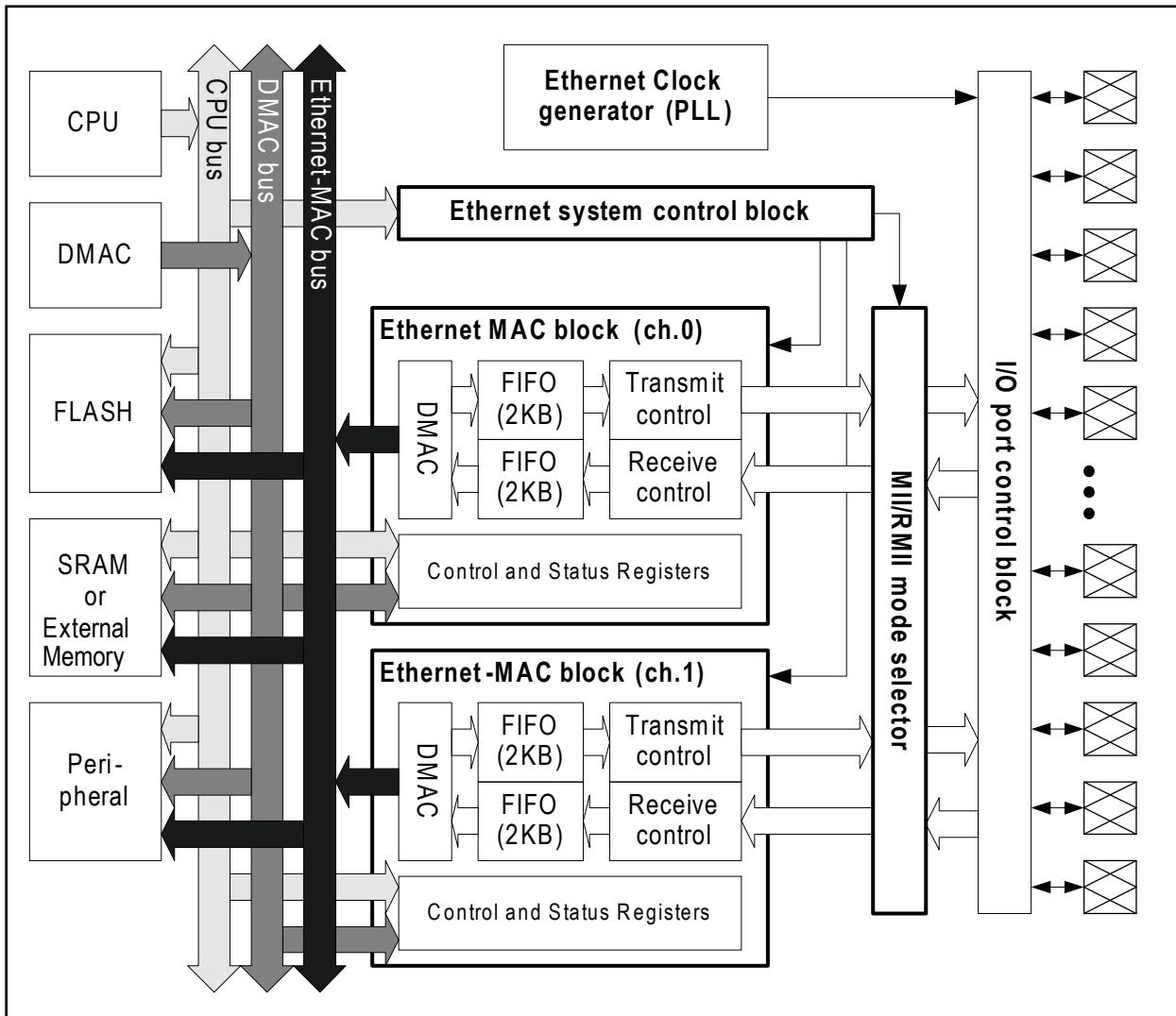

Ethernet-MAC と周辺回路の構成図を Figure 1-1 に示します。

Figure 1-1 Ethernet-MAC と周辺回路の構成図

## ■ 各ブロックの説明

### ● Ethernet-MAC 部

Ethernet-MAC は、Ethernet 通信プロトコル制御を行うブロックです。ブロックダイヤグラムには ch.0 と ch.1 の 2 個の Ethernet-MAC が記載されていますが、ch.0 の 1 個のみ搭載している品種と、ch.0 と ch.1 の 2 個搭載している品種があります。1 個搭載品種の場合、ch.1 側は使用できません。2 個搭載品種は、両方の Ethernet-MAC を独立して使用できます。

各 Ethernet-MAC は、送信制御部、受信制御部、FIFO メモリ、専用 DMAC から構成されています。CPU からの制御レジスタ部 (Control and Status Registers) への指示により動作の制御を行います。専用 DMAC は、CPU により形成されたメモリ上のディスクリプタを使用し、送受信データの転送処理を行います。Ethernet-MAC に関する詳細は、『Ethernet-MAC』の章を参照してください。

各 Ethernet-MAC を動作させる場合、あらかじめ、Ethernet システム制御部へのレジスタ書き込みにより、以下の手順で Ethernet-MAC セットアップをしてください。

1. 各 Ethernet-MAC に対するクロック供給を開始する。

2. MII/RMII モードを選択する。

3. 各 Ethernet-MAC へハードウェアリセットを発行し、Ethernet-MAC を再起動する。

上記については、「3. Ethernet-MAC セットアップ制御手順」を参照してください。

各 Ethernet-MAC は、上記のセットアップのハードウェアリセット解除後に、初期設定を行い、動作開始を指示します。各 Ethernet-MAC の内部レジスタには、MII/RMII モードの選択を行う箇所がありますが、これらは上記セットアップ手順とは別に設定を行います。

Figure 1-1 に示すように、Ethernet-MAC のうち DMAC は、CPU およびマイコンの DMAC とは独立した専用システムバス (AHB) を持っており、CPU、マイコン DMAC と同時動作が可能です。

### ● Ethernet-システム制御部 (Ethernet system control block)

Ethernet システム制御部は、Ethernet-MAC の周辺回路の制御を行い、各 Ethernet-MAC のセットアップ制御を行います。「3. Ethernet-MAC セットアップ制御手順」に、セットアップ制御手順を記載しています。また、「4. Ethernet システム制御部レジスタ」に、Ethernet システム制御部のレジスタ機能を記載しています。

各 Ethernet-MAC を動作させない場合、クロック信号の供給を停止しておくことで、マイコンの低消費電力化を行うことができます。

### ● MII/RMII モード選択部 (MII/RMII mode selector)

MII/RMII モード選択部は、Ethernet-MAC の外部 PHY インタフェース信号を I/O ポート制御部と接続するセレクタブロックです。Ethernet システム制御部のレジスタ設定に基づき、使用するインターフェース (MII/RMII) モードを選択します。

### ● I/O port 制御部 (I/O port control block)

マイコンの外部端子は、GPIO など、Ethernet 以外の周辺機能ブロックの端子と端子機能が兼用されています。マイコンの外部端子を Ethernet の外部 PHY インタフェース端子として使用するために、I/O ポート部の制御レジスタの設定が必要になります。

マイコンが低消費電力モード (STOP モード、タイマモード) の状態にあるとき、外部 PHY からの Wakeup パケットを受信するためには、PHY インタフェース端子の入出力信号を有効とする状態 (直前保持状態とよびます) にしておく必要があります。

I/O ポート制御部に関する詳細は、『ペリフェラルマニュアル』の『I/O ポート』の章を参照してください。

## ● Ethernet クロック生成部 (Ethernet clock generator block)

Ethernet クロック生成部から出力されるクロック信号を、マイコン外部端子へ出力できます。このクロック信号出力を一般的な外部 PHY デバイスの入力クロックに使う場合、PLL を使用せず、メイン発振器の出力を Ethernet クロック生成部でスルーして供給するようにしてください。PLL を使用してクロック出力信号を生成した場合、一般的な PHY デバイスに要求される入力クロック発振精度を保証できません。Ethernet クロック生成部に関する詳細は、『FM3 ファミリ ペリフェラルマニュアル 通信マクロ編』の『USB/Ethernet クロック生成部』の章を参照してください。

## 2. Ethernet の入出力信号

Ethernet 機能に関連する入出力信号の接続を説明します。

### ■ マイコン外部端子

#### ● 外部 PHY インタフェース信号

外部端子は、Ethernet-MAC の ch.0, ch.1 および MII/RMII の PHY インタフェース信号端子の機能が兼用されています。Ethernet システム制御部のセットアップ制御時に、どのインターフェース信号を用いるかが決定されます。Ethernet-MAC 1 個搭載品と、2 個搭載品のそれぞれの外部端子名と各 Ethernet-MAC の PHY インタフェース信号の対応関係の一覧を Table 2-1 に示します。

Table 2-1 外部端子名と PHY インタフェース信号の対応関係

| 外部端子名           |                    | MII<br>(ch.0 使用) | RMII<br>(ch.0 使用) | RMII<br>(ch.0, ch.1 使用)      | 備考 |

|-----------------|--------------------|------------------|-------------------|------------------------------|----|

| ch.0 のみ<br>搭載品種 | ch.0, ch.1<br>搭載品種 |                  |                   |                              |    |

| E_RXCK_REFCK    | E_RXCK0_REFCK      | ch.0 RX_CLK      | ch.0 REF_CLK      | ch.0 REF_CLK<br>ch.1 REF_CLK | *1 |

| E_RX00          | E_RX00             | ch.0 RXD[0]      | ch.0 RXD[0]       | ch.0 RXD[0]                  |    |

| E_RX01          | E_RX01             | ch.0 RXD[1]      | ch.0 RXD[1]       | ch.0 RXD[1]                  |    |

| E_RX02          | E_RX02_RX10        | ch.0 RXD[2]      | 使用しない             | ch.1 RXD[0]                  |    |

| E_RX03          | E_RX03_RX11        | ch.0 RXD[3]      | 使用しない             | ch.1 RXD[1]                  |    |

| E_RXDV          | E_RXDV0            | ch.0 RX_DV       | ch.0 CRS_DV       | ch.0 CRS_DV                  |    |

| E_RXER          | E_RXER0_RXDV1      | ch.0 RX_ER       | 使用しない             | ch.1 CRS_DV                  | *2 |

| E_TCK           | E_TCK0_MDC1        | ch.0 TX_CLK      | 使用しない             | ch.1 MDC                     |    |

| E_TX00          | E_TX00             | ch.0 TXD[0]      | ch.0 TXD[0]       | ch.0 TXD[0]                  |    |

| E_TX01          | E_TX01             | ch.0 TXD[1]      | ch.0 TXD[1]       | ch.0 TXD[1]                  |    |

| E_TX02          | E_TX02_TX10        | ch.0 TXD[2]      | 使用しない             | ch.1 TXD[0]                  |    |

| E_TX03          | E_TX03_TX11        | ch.0 TXD[3]      | 使用しない             | ch.1 TXD[1]                  |    |

| E_TXEN          | E_TXEN0            | ch.0 TX_EN       | ch.0 TX_EN        | ch.0 TX_EN                   |    |

| E_TXER          | E_TXER0_TXEN1      | ch.0 TX_ER       | 使用しない             | ch.1 TX_EN                   | *3 |

| E_CRS           | E_CRS0             | ch.0 CRS         | 使用しない             | 使用しない                        |    |

| E_COL           | E_COL0             | ch.0 COL         | 使用しない             | 使用しない                        |    |

| E_MDC           | E_MDC0             | ch.0 MDC         | ch.0 MDC          | ch.0 MDC                     |    |

| E_MDIO          | E_MDIO0            | ch.0 MDIO        | ch.0 MDIO         | ch.0 MDIO                    |    |

| -               | E_MDIO1            | 使用しない            | 使用しない             | ch.1 MDIO                    |    |

\*1：この端子は、MII の場合、RX\_CLK 入力として使用します。RMII の場合、REF\_CLK 入力として使用します。Ethernet-MAC を ch.0, ch.1 の両方を使用する場合、両チャネル共通の入力です。

\*2：RMII の場合、外部 PHY からの RX\_ER 入力は使用しないため、接続する必要はありません。

\*3：MII の場合、TX\_ER 出力は、EEE (Energy Efficient Ethernet) における LPI モード時のみ "H" レベル出力を行います。EEE を使用しない場合、PHY との接続は不要です。

Ethernet-MAC の ch.0, ch.1 両方を使用する場合、MII は選択できません。

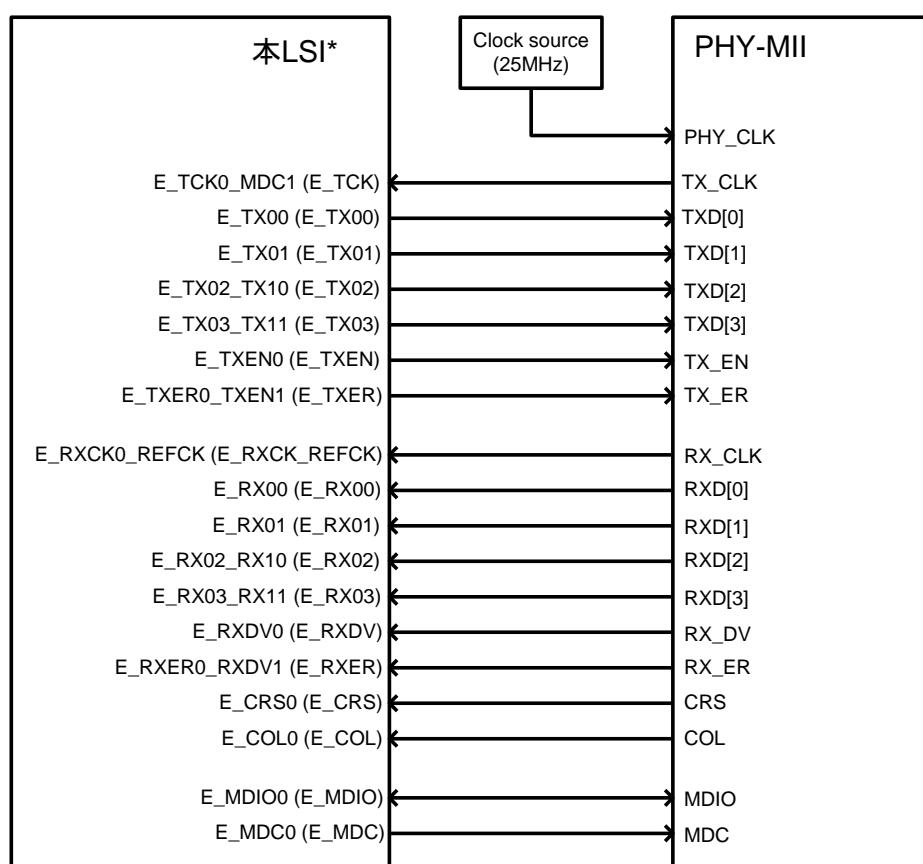

## ● 外部 PHY 接続例

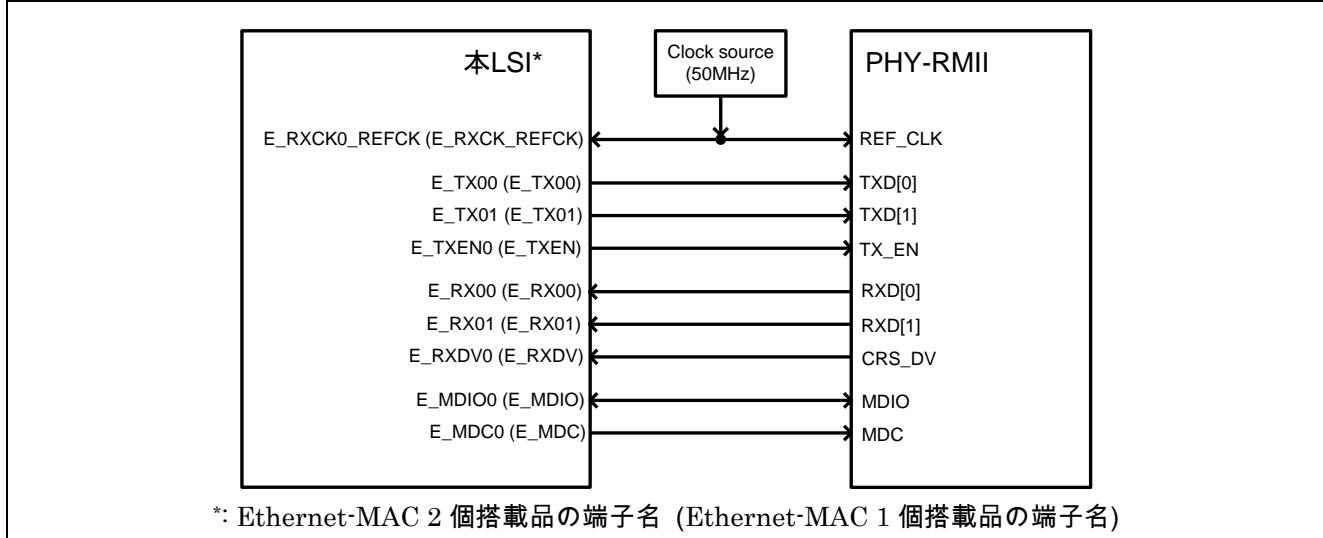

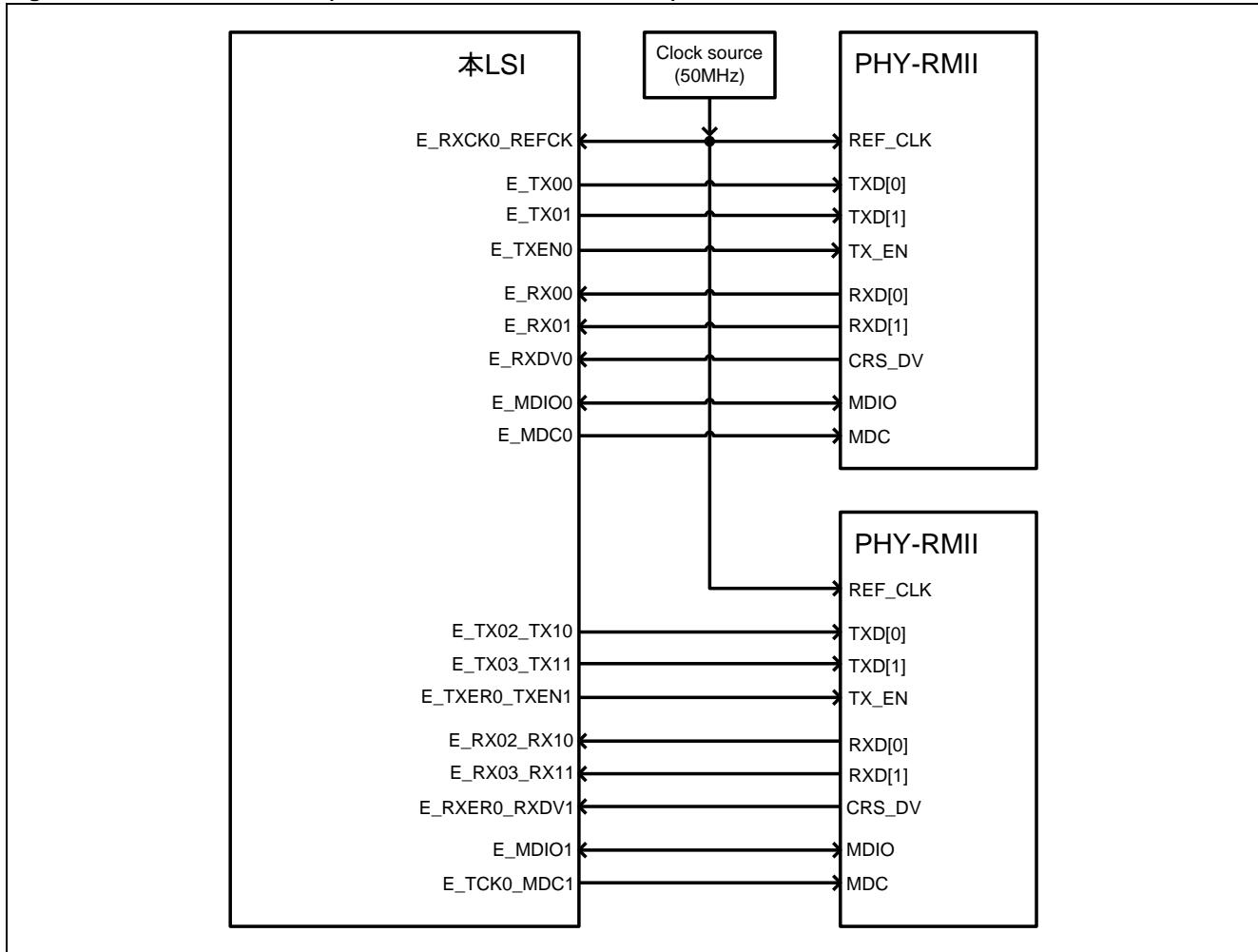

以下に外部 PHY デバイスとの接続例を示します。

Figure 2-1～Figure 2-3 に記載していませんが、MDIO 信号はプルアップすることを推奨します。

Ethernet-MAC (ch.0)を使用し、MII モードで PHY と接続 (Figure 2-1)

Ethernet-MAC (ch.0)を使用し、RMII モードで PHY と接続 (Figure 2-2)

Ethernet-MAC (ch.0, ch.1)を使用し、RMII モードで 2 個の PHY と接続 (Figure 2-3)

**Figure 2-1 MII モード接続図 (Ethernet-MAC ch.0 を使用)**

\*: Ethernet-MAC 2 個搭載品の端子名 (Ethernet-MAC 1 個搭載品の端子名)

Figure 2-2 RMII モード接続図 (Ethernet-MAC ch.0 を使用)

Figure 2-3 RMII モード接続図 (Ethernet-MAC ch.0, ch.1 を使用)

## ● その他の外部端子

Table 2-1 に示す以外で、Ethernet 機能に関連する外部端子を Table 2-2 に示します。

**Table 2-2 その他の外部端子**

| 外部端子名         | 機能                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------|

| E_PPS0_PPS1 * | Ethernet-MAC 部から、PTP 機能のシステム・タイム・カウンタの 1 秒ごとのパルスを出力します。ETH_MODE.PPSSEL レジスタにて、ch.0, ch.1 のどちらの出力を選択するか決定できます。 |

| E_COUT        | Ethernet クロック生成部で生成したクロック信号を出力する端子です。                                                                         |

\* : Ethernet-MAC を 1 個搭載の品種は、E\_PPS 端子です。ch.1 の出力は選択できません。

## ■ 内部接続端子

### ● システムクロック信号および AHB バスインターフェース

各 Ethernet-MAC は、AHB バスを経由して CPU, メモリに接続します。各 Ethernet-MAC を使用する際、AHB クロック (HCLK) を 25 MHz 以上に設定してください。

各 Ethernet-MAC のシステム・タイム・カウンタのソースクロック (PTP\_CLK) には、AHB クロック (HCLK) が接続されます。

### ● 割込み信号インターフェース

各 Ethernet-MAC 部から出力される割込み信号を Table 2-3 に示します。これらの割込みは、NVIC に接続されています。割込みについては、『ペリフェラルマニュアル』の『割込み』の章を参照してください。

**Table 2-3 Ethernet-MAC からの割込み信号**

| 割込み信号名       | 機能                                       |

|--------------|------------------------------------------|

| MAC0_INT_SBD | Ethernet-MAC ch.0 の割込みです。                |

| MAC0_INT_PMT | Ethernet-MAC ch.0 の WAKE-UP フレーム受信割込みです。 |

| MAC0_INT_LPI | Ethernet-MAC ch.0 の LPI ステート終了通知の割込みです。  |

| MAC1_INT_SBD | Ethernet-MAC ch.1 の割込みです。                |

| MAC1_INT_PMT | Ethernet-MAC ch.1 の WAKE-UP フレーム受信割込みです。 |

Ethernet-MAC ch.1 は、MII モードを持たないため、LPI 割込みを発生しません。

### 3. Ethernet-MAC セットアップ制御手順

Ethernet-MAC セットアップ制御手順について説明します。

#### ■ セットアップについて

マイコンに対する電源投入などにより、AHB バス上にリセットが発生した場合は、以下のセットアップ制御を実施してください。

I/O ポート部の選択を行った後、以下手順を実施し、各 Ethernet-MAC のセットアップを行います。各 Ethernet-MAC へのクロック供給、MII/RMII のモードの選択、各 Ethernet-MAC へのハードウェアリセット発行および解除を行います。セットアップ完了後、各 Ethernet-MAC の初期設定を行い、動作を開始させます。

#### ■ MII モード選択時の手順

1. ETH\_CLKGMACEN[1:0]=01 を書き込みます。Ethernet-MAC(ch.0)にクロック供給を開始します。

2. ETH\_MODE.IFMODE=0, ETH\_MODE.RST0=1, ETH\_MODE.RST1=0 を書き込みます。 MII を選択し、Ethernet-MAC(ch.0)にハードウェアリセットを発行します。

3. この時点で、外部 PHY からクロック信号 (RX\_CLK, TX\_CLK) が入力されている必要があります。クロック信号が入力されていない場合、入力されるまで待ちます。

4. ETH\_MODE.IFMODE=0, ETH\_MODE.RST0=0, ETH\_MODE.RST1=0 を書き込みます。 MII を選択し、Ethernet-MAC(ch.0)のハードウェアリセットを解除します。

#### ■ RMII モード (ch.0 のみ使用) 選択時の手順

1. ETH\_CLKGMACEN[1:0]=01 を書き込みます。Ethernet-MAC(ch.0)にクロック供給を開始します。

2. ETH\_MODE.IFMODE=1, ETH\_MODE.RST0=1, ETH\_MODE.RST1=0 を書き込みます。 RMII を選択し、Ethernet-MAC(ch.0)にハードウェアリセットを発行します。

3. この時点で、外部 PHY からクロック信号 (REF\_CLK) が入力されている必要があります。クロック信号が入力されていない場合、入力されるまで待ちます。

4. ETH\_MODE.IFMODE=1, ETH\_MODE.RST0=0, ETH\_MODE.RST1=0 を書き込みます。 RMII を選択し、Ethernet-MAC(ch.0)のハードウェアリセットを解除します。

#### ■ RMII モード (ch.0, ch.1 両方使用) 選択時の手順

1. ETH\_CLKGMACEN[1:0]=11 を書き込みます。Ethernet-MAC(ch.0, ch.1)にクロック供給を開始します。

2. ETH\_MODE.IFMODE=1, ETH\_MODE.RST0=1, ETH\_MODE.RST1=1 を書き込みます。 RMII を選択し、Ethernet-MAC(ch.0, ch.1)にハードウェアリセットを発行します。

3. この時点で、外部 PHY からクロック信号 (REF\_CLK) が入力されている必要があります。クロック信号が入力されていない場合、入力されるまで待ちます。

4. ETH\_MODE.IFMODE=1, ETH\_MODE.RST0=0, ETH\_MODE.RST1=0 を書き込みます。 RMII を選択し、Ethernet-MAC(ch.0, ch.1)のハードウェアリセットを解除します。

※ETH\_MODE.PTPSEL は、出力する PTP 信号のチャネルに合わせて任意の選択が可能です。

## 4. Ethernet システム制御部レジスタ

Ethernet システム制御部のレジスタについて説明します。

Ethernet システム制御部のレジスター一覧を Table 4-1 に示します。

Table 4-1 Ethernet システム制御部レジスター一覧

| オフセットアドレス | レジスタ略称   | レジスタ名          | 参照先 |

|-----------|----------|----------------|-----|

| 0x00      | ETH_MODE | モード選択レジスタ      | 4.1 |

| 0x08      | ETH_CLKG | クロックゲーティングレジスタ | 4.2 |

Ethernet システム制御部ベースアドレス : 0x40066000

## 4.1. モード選択レジスタ (ETH\_MODE)

ETH\_MODE は、Ethernet の外部インターフェースモードを制御します。

### ■ レジスタ構成

| bit   | 31 | 30 | 29 | 28     | 27 | 26 | 25   | 24     |

|-------|----|----|----|--------|----|----|------|--------|

| Field |    | 予約 |    | PPSSEL |    |    | 予約   |        |

| 属性    | R  | R  | R  | R/W    | R  | R  | R    | R      |

| 初期値   | 0  | 0  | 0  | 0      | 0  | 0  | 0    | 0      |

| bit   | 23 | 22 | 21 | 20     | 19 | 18 | 17   | 16     |

| Field |    |    |    | 予約     |    |    |      |        |

| 属性    | R  | R  | R  | R      | R  | R  | R    | R      |

| 初期値   | 0  | 0  | 0  | 0      | 0  | 0  | 0    | 0      |

| bit   | 15 | 14 | 13 | 12     | 11 | 10 | 9    | 8      |

| Field |    |    | 予約 |        |    |    | RST1 | RST0   |

| 属性    | R  | R  | R  | R      | R  | R  | R/W  | R/W    |

| 初期値   | 0  | 0  | 0  | 0      | 0  | 0  | 0    | 0      |

| bit   | 7  | 6  | 5  | 4      | 3  | 2  | 1    | 0      |

| Field |    |    | 予約 |        |    |    |      | IFMODE |

| 属性    | R  | R  | R  | R      | R  | R  | R    | R/W    |

| 初期値   | 0  | 0  | 0  | 0      | 0  | 0  | 0    | 0      |

### ■ レジスタ機能

#### [bit31:29] 予約

書き込み時は"0"を書き込んでください。読み出時は"0"が読み出されます。

#### [bit28] PPSSEL

各 Ethernet-MAC の PTP 機能のシステム・タイム・カウンタ・パルス出力のうち、どちらを E\_PPS0\_PPS1 端子に出力するかを選択します。

| bit     | 動作                        |

|---------|---------------------------|

| 書き込み時 0 | Ethernet-MAC(ch.0)を選択します。 |

| 書き込み時 1 | Ethernet-MAC(ch.1)を選択します。 |

| 読み出し時   | レジスタ設定値を読み出します。           |

#### [bit27:10] 予約

書き込み時は"0"を書き込んでください。読み出時は"0"が読み出されます。

[bit9] RST1

Ethernet-MAC(ch.1) に対するハードウェアリセット信号を制御します。

| bit     | 動作                                       |

|---------|------------------------------------------|

| 書き込み時 0 | Ethernet-MAC(ch.1) に対するハードウェアリセットを解除します。 |

| 書き込み時 1 | Ethernet-MAC(ch.1) に対するハードウェアリセットを発行します。 |

| 読み出し時   | レジスタ設定値を読み出します。                          |

[bit8] RST0

Ethernet-MAC (ch.0) に対するハードウェアリセット信号を制御します。

| bit     | 動作                                       |

|---------|------------------------------------------|

| 書き込み時 0 | Ethernet-MAC(ch.0) に対するハードウェアリセットを解除します。 |

| 書き込み時 1 | Ethernet-MAC(ch.0) に対するハードウェアリセットを発行します。 |

| 読み出し時   | レジスタ設定値を読み出します。                          |

[bit7:1] 予約

書き込み時は"0"を書き込んでください。読み出し時は"0"が読み出されます。

[bit0] IFMODE

MII/RMII モードセレクタの接続を選択します。

| bit     | 動作              |

|---------|-----------------|

| 書き込み時 0 | MII を選択します。     |

| 書き込み時 1 | RMII を選択します。    |

| 読み出し時   | レジスタ設定値を読み出します。 |

## 4.2. クロックゲーティングレジスタ (ETH\_CLKG)

ETH\_CLKG は、各 Ethernet-MAC へのクロック供給を制御します。

### ■ レジスタ構成

| bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25         | 24  |

|-------|----|----|----|----|----|----|------------|-----|

| Field | 予約 |    |    |    |    |    |            |     |

| 属性    | R  | R  | R  | R  | R  | R  | R          | R   |

| 初期値   | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0   |

| bit   | 23 | 22 | 21 | 20 | 19 | 18 | 17         | 16  |

| Field | 予約 |    |    |    |    |    |            |     |

| 属性    | R  | R  | R  | R  | R  | R  | R          | R   |

| 初期値   | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0   |

| bit   | 15 | 14 | 13 | 12 | 11 | 10 | 9          | 8   |

| Field | 予約 |    |    |    |    |    |            |     |

| 属性    | R  | R  | R  | R  | R  | R  | R          | R   |

| 初期値   | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0   |

| bit   | 7  | 6  | 5  | 4  | 3  | 2  | 1          | 0   |

| Field | 予約 |    |    |    |    |    | MACEN[1:0] |     |

| 属性    | R  | R  | R  | R  | R  | R  | R/W        | R/W |

| 初期値   | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0   |

### ■ レジスタ機能

#### [bit31:2] 予約

書き込み時は"0"を書き込んでください。読み出し時は"0"が読み出されます。

#### [bit1:0] MACEN[1:0]

Ethernet-MAC へのシステムクロック供給を選択します。

| bit1:0   | Ethernet-MAC 1 個搭載品種         | Ethernet-MAC 2 個搭載品種                                       |

|----------|------------------------------|------------------------------------------------------------|

| 書き込み時 00 | Ethernet-MAC(ch.0) へクロック供給停止 | Ethernet-MAC(ch.0, ch.1)へクロック供給停止                          |

| 書き込み時 01 | Ethernet-MAC (ch.0)へクロック供給開始 | Ethernet-MAC(ch.0)へクロック供給開始<br>Ethernet-MAC(ch.1)へクロック供給停止 |

| 書き込み時 11 | 設定禁止                         | Ethernet-MAC(ch.0, ch.1)へクロック供給開始                          |

| 書き込み時 10 | 設定禁止                         | 設定禁止                                                       |

| 読み出し時    | レジスタ設定値を読み出します。              | レジスタ設定値を読み出します。                                            |

## CHAPTER 1: Ethernet

## CHAPTER 2: Ethernet-MAC

---

Ethernet-MAC の機能と動作の説明を行います。

---

1. 概要

2. ブロック構成

3. アーキテクチャ

4. レジスタ

5. ディスクリプタ

6. プログラミングガイド

## 1. 概要

Ethernet-MAC は、以下の 4 つのブロックで構成されています。各ブロックの主な機能を説明します。

### ■ GMAC : Ethernet Media Access Controller

- IEEE802.3-2005 準拠

- 10/100Mbps のデータ転送速度に対応

- IEEE802.3 準拠の MII インタフェース

- 10/100 Mbps において全二重と半二重動作に対応

- 半二重動作で CSMA/CD プロトコルに対応

- 半二重モードでバックプレッシャに対応

- 全二重動作で IEEE 802.3x フローコントロールに対応

- CRC およびデータパディングの自動生成

- ジャンボフレーム対応

- 種々のフレキシブル・アドレスフィルタリングモードに対応

- MII 上のデバッグ用内部ループバックに対応

- IEEE802.3Q VLAN パケットに対応

- Wake-On-LAN (Remote Wake-Up, Magic Packet)に対応

- Checksum Offload に対応

- Energy Efficient Ethernet (EEE)用の IEEE 802.3-az-2010 に対応

- RMII インタフェースに対応

- IEEE1588-2008 準拠

- MAC Management Counter をサポート

### ■ MTL : MAC Transaction Layer

- 送信 FIFO 2K バイト, 受信 FIFO 2K バイト

- コリジョンフレームの自動再送信処理

- レイトコリジョン, アンダーラン・フレームの廃棄

### ■ DMA : DMA Controller

- ディスクリプタ方式 DMA

- 送信および受信データバスはリトルエンディアンに対応

### ■ AHB : AHB Interface

- AMBA Specification Rev.2.0 準拠

- 32 ビット幅のアドレスおよびデータ

- マルチレイヤ・バス対応

## 2. ブロック構成

Ethernet-MAC のブロック構成を説明します。

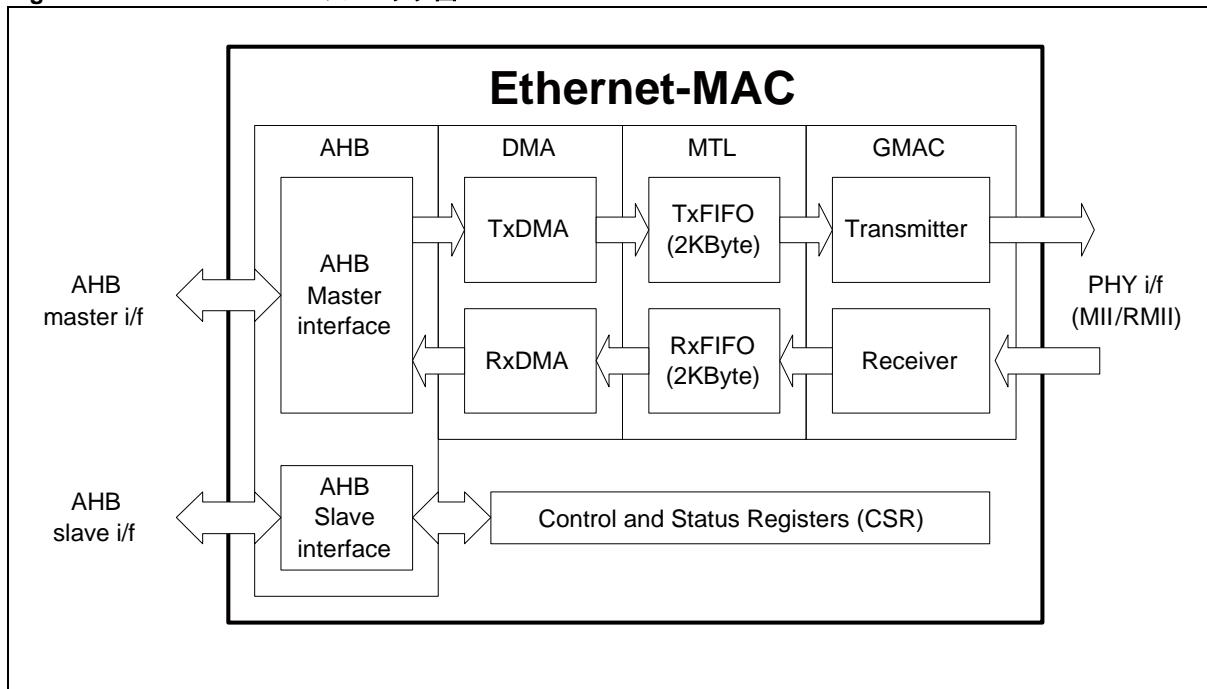

Figure 2-1 Ethernet-MAC のブロック図

Figure 2-1 に、Ethernet-MAC のブロック図を示します。以下に各機能ブロックの説明を行います。

### ● AHB : AHB Interface

システムバス (AHB) とのインターフェースを制御する機能ブロックです。内部 DMA は、AHB マスタ・インターフェースを持ち、システムバス経由でホストメモリに直接アクセスできます。AHB スレーブ・インターフェースは、ホスト CPU と Control Status Registers (CSR)とのインターフェースを行います。

### ● DMA : DMA Controller

送信 DMA (TxDMA) と受信 DMA (RxDMA) が独立に動作できる構成です。DMA はホストメモリに構築されたディスクリプタテーブルの内容に従い、データ転送処理を行います。

### ● MTL : MAC Transaction Layer

送信データ、受信データのバッファリング用にそれぞれ 2K バイトの FIFO メモリを搭載しています。MTL は FIFO の制御を行う機能ブロックで、自動再送信、フレームの破棄処理などを行います。

### ● GMAC : Ethernet Media Access Controller

Ethernet の通信プロトコルを実現する機能ブロックです。PHY インタフェースは、MII/RMII をサポートしています。

## 3. アーキテクチャ

---

Ethernet-MAC のアーキテクチャについて説明します。

---

- 3.1 端子機能

- 3.2 AHB アプリケーション・ホスト・インターフェース

- 3.3 DMA コントローラ

- 3.4 チェックサムエンジン

- 3.5 Energy Efficient Ethernet

- 3.6 MAC マネジメントカウンタ

- 3.7 Station Management Agent

- 3.8 IEEE1588

### 3.1. 端子機能

Ethernet-MAC の端子機能について説明します。

#### ■ PHY インタフェース端子

Table 3-1 に PHY インタフェース端子を示します。GMAC は、MII/RMII の両方のインターフェースをサポートします。表中の MII/RMII の列で○が付いている端子を PHY に接続する必要があります。

Table 3-1 PHY インタフェース端子

| 信号端子名   | I/O | 機能           | MII | RMII | 備考                                         |

|---------|-----|--------------|-----|------|--------------------------------------------|

| RX_CLK  | IN  | 受信クロック       | ○   | ×    | 100 Mbps 時 : 25 MHz<br>10 Mbps 時 : 2.5 MHz |

| RXD[0]  | IN  | 受信データ 0      | ○   | ○    |                                            |

| RXD[1]  | IN  | 受信データ 1      | ○   | ○    |                                            |

| RXD[2]  | IN  | 受信データ 2      | ○   | ×    |                                            |

| RXD[3]  | IN  | 受信データ 3      | ○   | ×    |                                            |

| RX_DV   | IN  | 受信データ有効      | ○   | ×    |                                            |

| RX_ER   | IN  | 受信エラー検出      | ○   | ×    | RMII 時接続不要                                 |

| TX_CLK  | IN  | 送信クロック       | ○   | ×    | 100 Mbps 時 : 25 MHz<br>10 Mbps 時 : 2.5 MHz |

| TXD[0]  | OUT | 送信データ 0      | ○   | ○    |                                            |

| TXD[1]  | OUT | 送信データ 1      | ○   | ○    |                                            |

| TXD[2]  | OUT | 送信データ 2      | ○   | ×    |                                            |

| TXD[3]  | OUT | 送信データ 3      | ○   | ×    |                                            |

| TX_EN   | OUT | 送信データ有効      | ○   | ○    |                                            |

| TX_ER   | OUT | 送信エラー        | ○   | ×    | Energy Efficient Ethernet<br>対応 PHY にのみ接続  |

| CRS     | IN  | キャリア検出       | ○   | ×    |                                            |

| COL     | IN  | 衝突検出         | ○   | ×    |                                            |

| MDC     | OUT | マネジメントクロック   | ○   | ○    | SYS_CLK 入力を分周して生成します。                      |

| MDIO    | IO  | マネジメントデータ    | ○   | ○    | 外部端子にて双方向制御されます。プルアップすることを推奨します。           |

| REF_CLK | IN  | リファレンスクロック   | ×   | ○    | 50 MHz クロック入力                              |

| CRS_DV  | IN  | キャリア検出/データ有効 | ×   | ○    |                                            |

## ■ ホスト・インターフェース、その他の端子

Table 3-2 にホスト・インターフェース端子、その他の端子を示します。本回路の動作、機能を説明するに必要な端子に限定しています。

**Table 3-2 ホスト・インターフェース、その他の端子**

| 端子名     | I/O | 機能               | 説明                                                                                                                                                                                                          |

|---------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_CLK | IN  | システムクロック         | <ul style="list-style-type: none"> <li>AHB バス上のクロック (HCLK) が、接続されています。</li> <li>DMA の転送動作の基準クロックとなります。</li> <li>マネジメントインターフェースの MDC は、SYS_CLK を分周して生成します。</li> <li>必ず、25 MHz 以上の HCLK を供給してください。</li> </ul> |

| PTP_CLK | IN  | PTP クロック         | <ul style="list-style-type: none"> <li>PTP システムカウンタモジュールの基準クロック入力です。</li> <li>マイコン上の AHB クロック (HCLK) が接続されています。</li> </ul>                                                                                  |

| INT_SBD | OUT | Ethernet-MAC 割込み | <ul style="list-style-type: none"> <li>Ethernet-MAC からの様々なイベントを通知する割込み信号です。</li> <li>マイコンの NVIC に接続されます。</li> </ul>                                                                                         |

| INT_PMT | OUT | WakeUp 割込み       | <ul style="list-style-type: none"> <li>GMAC レシーバが、PHY から WakeUp パケットを受信したイベントを通知する割込み信号です。</li> <li>マイコンをスタンバイモードから復帰させることができます。</li> </ul>                                                                 |

| INT_LPI | OUT | LPI 割込み          | <ul style="list-style-type: none"> <li>GMAC レシーバが、PHY から LPI (Low Power Idle) 状態を抜けた通知を受けたイベントを通知する割込み信号です。</li> <li>マイコンをスタンバイモードから復帰させることができます。</li> </ul>                                                |

| PTPPPS  | OUT | 秒カウント出力          | <ul style="list-style-type: none"> <li>PTP システムタイムカウンタモジュールの秒カウント出力です。</li> <li>マイコンの外部端子へ出力できます。詳細は、「4.30. GMAC Register 459 (PPSCR)」を参照してください。</li> </ul>                                                 |

## 3.2. AHB アプリケーション・ホスト・インターフェース

Ethernet-MAC の AHB インタフェースについて、説明します。AHB マスタ・インターフェースは、内部 DMA 要求サイクルを AHB サイクルに変換し、データの転送を制御します。AHB スレーブ・インターフェースは、ホスト CPU からの GMAC と DMA の CSR (Control and Status Register) スペースへのアクセスを提供します。AHB スレーブ・インターフェースへのアクセス中に、AHB マスタ・インターフェースの動作が可能です。

### ■ AHB マスタ・インターフェース

- DMA Bus Mode レジスタの FB または MB ビットをプログラミングすることによって、固定長バースト・モード(SINGLE, INCR4, INCR8, INCR16)または、不定長バースト・モード(SINGLE, INCR)転送、またはその混合を選択できます。

- 固定長バースト・モードを選択した場合、AHB マスタは常に SINGLE, INCR4, INCR8 または INCR16 タイプのバーストを開始します。固定長バースト・モードでは、DMA が INCR4/8/16 でないバースト転送を要求した場合、AHB ホスト・インターフェースは転送を複数のバースト・トランザクションに分割します。例えば、DMA が 15 ビートのバースト転送を要求した場合、AHB インタフェースはそれを INCR8 と INCR4 と 3 つの SINGLE トランザクションに分割します。

- 不定長バースト・モードでは、AHB マスタは常に INCR で転送を開始し、DMA によって要求されたバーストを 1 つの転送で完了します。

- 混合バースト・モードでは、AHB マスタは DMA が 16 ビート以下のサイズの転送を要求したとき、固定長バースト(INCRx)を開始します。DMA が 17 ビート以上の長さのバーストを要求したとき、AHB マスタは不定長バースト (INCR) で転送を開始し、バーストを 1 つの転送で完了します。

- AHB マスタからアクセスできないメモリ領域 (メモリが存在しない領域) へのアクセスが発生した場合、バスエラーが発生します。この場合、DMA はすべてのトランザクションを停止し、CSR および割込みを通じてエラーが致命的であることを知らせます。動作を再開するには、アプリケーションは、ソフトリセットを実行しなければなりません。

- AHB マスタからの転送は、常に 32 ビット (4byte) アドレス境界にアライメントされます。

- DMA コントローラは、送信 FIFO にバーストデータを完全に受け入れられるスペースがあるときにだけ、AHB バーストリード転送を要求します。

- DMA コントローラは、受信 FIFO に十分なバーストデータがあるときにだけ、AHB バーストライト転送を要求します。AHB マスタ・インターフェースは常に、AHB バスにプッシュするデータが利用可能であることを前提としています。しかし、DMA はバースト中に、完了前に end-of-valid data (有効なデータの終わり) を示すことがあります(Ethernet フレームの end-of-frame の送信のため)。固定長バースト・モードでは、AHB マスタ・インターフェースは指定された長さの転送が完了するまでダミーデータを使ってバーストを継続します。INCR モードでは、バースト転送を完了前に終了するステップを実行します。

### ■ AHB スレーブ・インターフェース

- シングルおよびバースト転送をサポート

- CSR との間の 32 ビット, 16 ビット, 8 ビットのライト/リード転送をサポートしています。ただし、ソフトウェア同期の問題を避けるため、CSR へのアクセスは、32 ビット・アクセスが推奨されます。

- OKAY 応答のみを生成し、ERROR 応答を生成しません。

### 3.3. DMA コントローラ

Ethernet-MAC 内部の DMA コントローラについて説明します。Ethernet-MAC は、独立した送信 DMA エンジンと受信 DMA エンジン、および CSR (Control and Status Registers) スペースを備えています。送信エンジンはデータをシステムメモリからデバイスポート(MTL)へ転送し、受信エンジンはデータをシステムメモリへ転送します。DMA コントローラはディスクリプタを利用することによってデータを転送元から転送先へ効率的に移動し、ホスト CPU の介入を最小限にします。DMA は Ethernet のフレームのようなパケット方式のデータ転送のために設計されています。DMA コントローラは、フレームの送受信完了、その他正常/エラー条件でホスト CPU に割込みを発生させるようにプログラムできます。

#### ■ ディスクリプタ構造

DMA とホストドライバは、下記の 2 つのデータ構造で通信します。

- Control and Status registers (CSR)

- ディスクリプタリストおよびデータバッファ

コントロール・ステータスレジスタについては「4.レジスタ」のセクションで詳細に説明しています。ディスクリプタについては「5.ディスクリプタ」のセクションで詳細に説明しています。

DMA は GMAC から受信したデータフレームをホストメモリの受信バッファへ転送し、ホストメモリの送信バッファからの送信データフレームを送信します。ホストメモリに常駐するディスクリプタはこれらのバッファのポインタとして機能します。

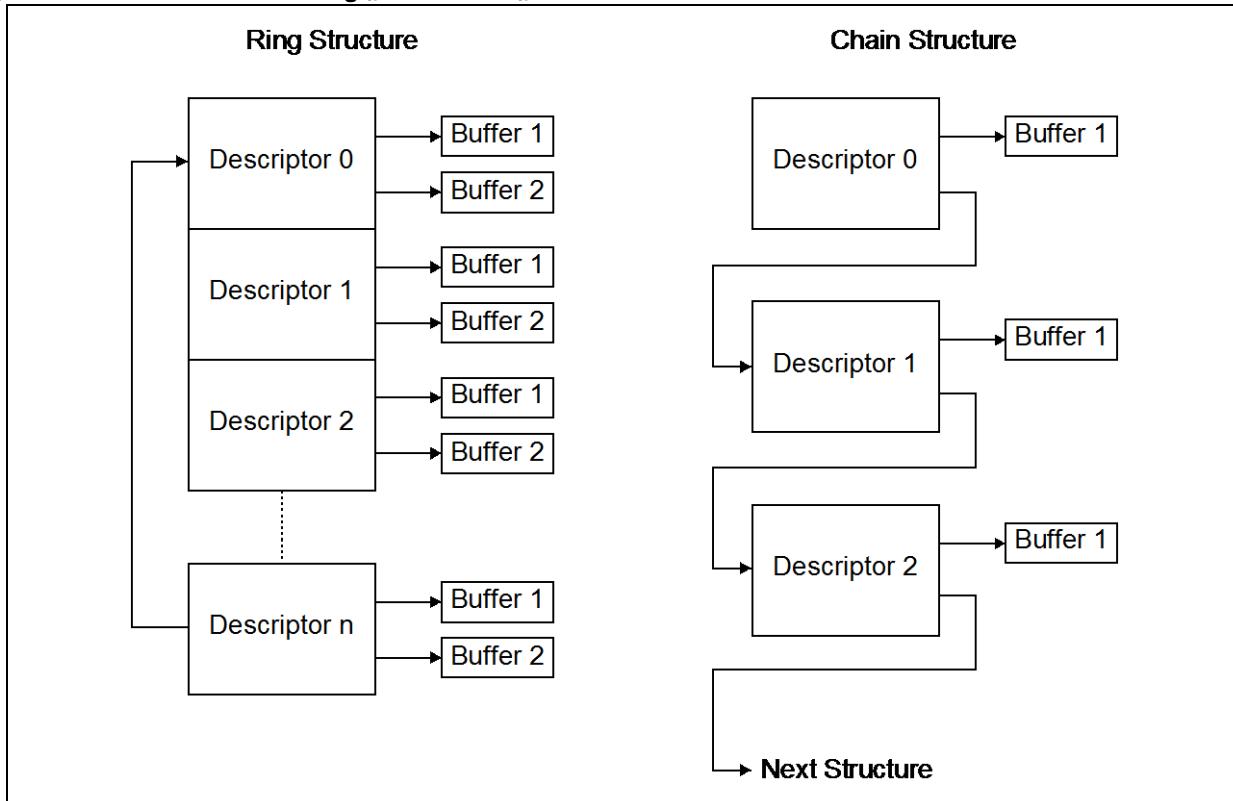

Figure 3-1 ディスクリプタの Ring 構造と Chain 構造

ディスクリプタは、受信用と送信用の2つがあります。各リストのベースアドレスをそれぞれ DMA Registers 3 および 4 へ書き込みます。ディスクリプタリストは(暗黙または明示的に)フォワードリンクされます。最後のディスクリプタが最初のエントリに戻り、Ring 構造を生成できます。ディスクリプタを明示的に Chain 化するには、受信および送信ディスクリプタの両方の2番目のアドレスを Chain 化します。Figure 3-1 に、ディスクリプタの Ring 構造および Chain 構造を示します。

ディスクリプタリストは、ホストメモリースペースに常駐します。各ディスクリプタは、最大2つのバッファをポイントできます。これによって2つのバッファを、メモリ内の連続するバッファとして使用するのではなく、物理アドレスを指定して使用できます。

データバッファはホストメモリースペースに常駐し、フレーム全体または一部によって構成されますが、1つのフレームを超えることはできません。バッファはデータのみを含み、ステータスはディスクリプタに保存されます。データの Chain 化では複数のデータバッファにわたるフレームを参照します。しかし、1つのディスクリプタは複数のフレームにわたることはできません。DMA は end-of-frame が検出されたとき、次のフレーム・バッファへスキップします。データの Chain 化を許可または禁止できます。

## ■ DMA コントローラの初期化

Ethernet-MAC の初期化は以下のように行います。

1. GMAC Register 0 に書込みを行い、動作モードを構成し、送信動作をイネーブルします。PS および DM ビットをオート・ネゴシエーションされた結果(PHY からリードされる)を元に設定します。

2. DMA Register 0 に書込みを行い、ホストのバスアクセス・パラメータをセットします。

3. DMA Register 7 に書込みを行い、不要な割込み原因をマスクします。

4. ソフトウェアドライバは、送信および受信ディスクリプタリストを作成します。次に、DMA Register 3 と DMA Register 4 の両方に書き込み、DMA に各リストの開始アドレスを供給します。

5. GMAC Registers 1, 2, 3 に書込みを行い、フィルタ・オプションを指定します。

6. DMA Register 6 の bit13 と bit1 をセットし、送信 DMA, 受信 DMA の動作を開始します。

7. GMAC Register 0 に書込みを行い、受信動作を許可します。(Receiver Enable: bit2)。

送信および受信エンジンは Running ステートに入り、それぞれのディスクリプタリストからディスクリプタを取得しようとします。次に受信および送信エンジンは、受信および送信動作の処理を開始します。送信および受信プロセスは相互に独立しており、別々に開始または停止できます。

## ● ホスト・バス・バーストアクセス

DMA は、AHB マスタ・インターフェース上での固定長バーストを行うように構成されている場合(DMA Register 0 の FB ビット)、それを実行します。最大バースト長は PBL フィールド(DMA Register 0[13:8])によって指定および制限されます。16 バイトの読み出しのために、受信および送信ディスクリプタは常に可能な最大のバーストサイズ(PBL によって制限されるか、または  $16 * 8/\text{バス幅}$ )でアクセスされます。

送信 DMA は、MTL 送信 FIFO に構成されたバースト、または(構成されたバーストよりもサイズが小さい場合は)end of frame までのバイト数を受け入れる十分なスペースがある場合にのみデータ転送を開始します。DMA は AHB マスタ・インターフェースに開始アドレスと要求される転送の数を指示します。AHB インタフェースが固定長バースト・モードに構成されている場合、DMA は INCR4/8/16 および SINGLE トランザクションの最適の組合せを使ってデータを転送します。そうでない場合(固定長バーストを使用しない)は、INCR(不定長)と SINGLE トランザクションを使ってデータを転送します。

受信 DMA は、MTL 受信 FIFO に構成されたバーストを受け入れる十分なスペースがある場合、または(構成されたバーストよりもサイズが小さい場合)受信 FIFO で end of frame が検出された場合にのみデータ転送を開始します。DMA は AHB マスタ・インターフェースに開始アドレスと要求される転送の数を指示します。AHB インタフェースが固定長バースト・モードに構成されている場合、DMA は INCR4/8/16 および SINGLE トランザクションの最適の組合せを使ってデータを転送します。そうでない場合(DMA Register 0 の FB ビットがリセットされている)は、INCR(不定長)と SINGLE トランザクションを使ってデータを転送します。

## ● ホスト・データバッファ・アライメント

フレームの先頭の送信および受信データバッファの開始アドレスにアライメントに関する制約はありません。例えば、32ビット・メモリを備えたシステムでは、バッファの開始アドレスは4つのバイトのどれにでもアライメントできます。しかしDMAは常に32ビット幅にアライメントされたアドレスに、必要でないバイトレーンはダミーデータを使って、転送を行います。これは一般的には、Ethernetフレームの始まりまたは終わりの転送の際に行われます。

### <Example 3-1 バッファリード>

送信バッファアドレスが0x0FF2で、15バイトを送信する場合、DMAはアドレス0x0FF0から5つ32ビットデータをリードします。データをMTL送信 FIFOへ転送するとき、余分のバイト(最初の2バイト)はドロップされ無視します。同様に、最後の転送の最後の3バイトも無視します。DMAは常に、end-of-frameでない限り完全な32ビットデータをMTL送信 FIFOへ転送することを保証します。

### <Example 3-2 バッファライト>

受信バッファアドレスが0x0FF2で、16バイトの受信フレームを転送する必要がある場合、DMAはアドレス0x0FF0から5個の32ビットデータを書き込みます。最初の転送の最初の2バイト、および5番目の転送の最後の2バイトにはダミーデータを書き込みます。

## ● バッファサイズの計算

DMAは送信および受信ディスクリプタのサイズ・フィールドを更新しません。DMAはディスクリプタのステータスフィールド(RDESおよびTDES)だけを更新します。ドライバはサイズ計算を実行しなければなりません。

送信 DMAは正確な数のバイト(TDES1のバッファサイズフィールドで指定されています)を GMACへ転送します。ディスクリプタが firstとマークされている場合(TDES0のFSビットがセットされている)、DMAはバッファからの最初の転送に start of frame のマークを付けます。ディスクリプタが lastとマークされている場合(TDES0のLSビットがセットされている)、DMAはそのデータバッファからの最後の転送に end-of frame to the MTL のマークを付けます。

受信 DMAは、バッファがフルになるまで、またはMTLから end-of frame を受信するまで、バッファへデータを転送します。ディスクリプタに lastのマーク(RDES0の LSビット)が付いていない場合、そのディスクリプタの対応するバッファはフルであり、バッファ内の有効なデータの量はバッファサイズフィールドで指定されているサイズから、そのディスクリプタの FSビットがセットされているときのデータバッファポインタオフセットを引いた量によって正確に示されます。データバッファポインタがデータバス幅にアライメントされているとき、オフセットは0です。ディスクリプタが lastとマークされている場合、バッファはフルでないことがあります(RDES1のバッファサイズで示されます)。この最後のバッファの有効なデータの量を計算するには、ドライバはフレーム長をリードし(RDES0[29:16]の FLビット)、このフレームの先行フレームのバッファサイズの合計を引く必要があります。受信 DMAは常に、次のフレームを新しいディスクリプタを使って転送します。

### <注意事項>

受信バッファの開始アドレスがシステムバスのデータ幅にアライメントされていない場合、システムはシステムバス幅にアライメントされたサイズの受信バッファを割り当てなければなりません。例えば、システムがアドレス0x1000から1024バイト(1KB)の受信バッファを割り当てる場合、ソフトウェアは受信ディスクリプタの中のバッファ開始アドレスに0x1002のオフセットを含めるようにプログラムできます。受信DMAはこのバッファにフレームを書き込むとき、最初の2つの位置(0x1000および0x1001)にダミーデータを挿入します。実際のフレームは位置0x1002から書き込まれます。したがって、バッファサイズが1024とプログラミングされている場合でも、開始アドレスオフセットのため、このバッファの実際の有効なスペースは1022バイトとなります。

## ● DMA アービター

DMA モジュール内のアービターは、送信および受信チャネル間の AHB マスター・インターフェースへのアクセスのアービトリエーションを実行します。round-robin と fixed-priority の 2 つのタイプのアービトリエーションが可能です。DMA Register 0 の DA=0 の場合、round-robin アービトリエーションが選択され、PR, TXPR の設定により、プライオリティが選択されます。DA=1 の場合、fixed-priority アービトリエーションが選択され、TXPR の設定により、プライオリティが選択されます。詳細は、DMA Register 0 の「4.33. DMA Register 0 (BMR)」を参照してください。

## ■ 送信動作

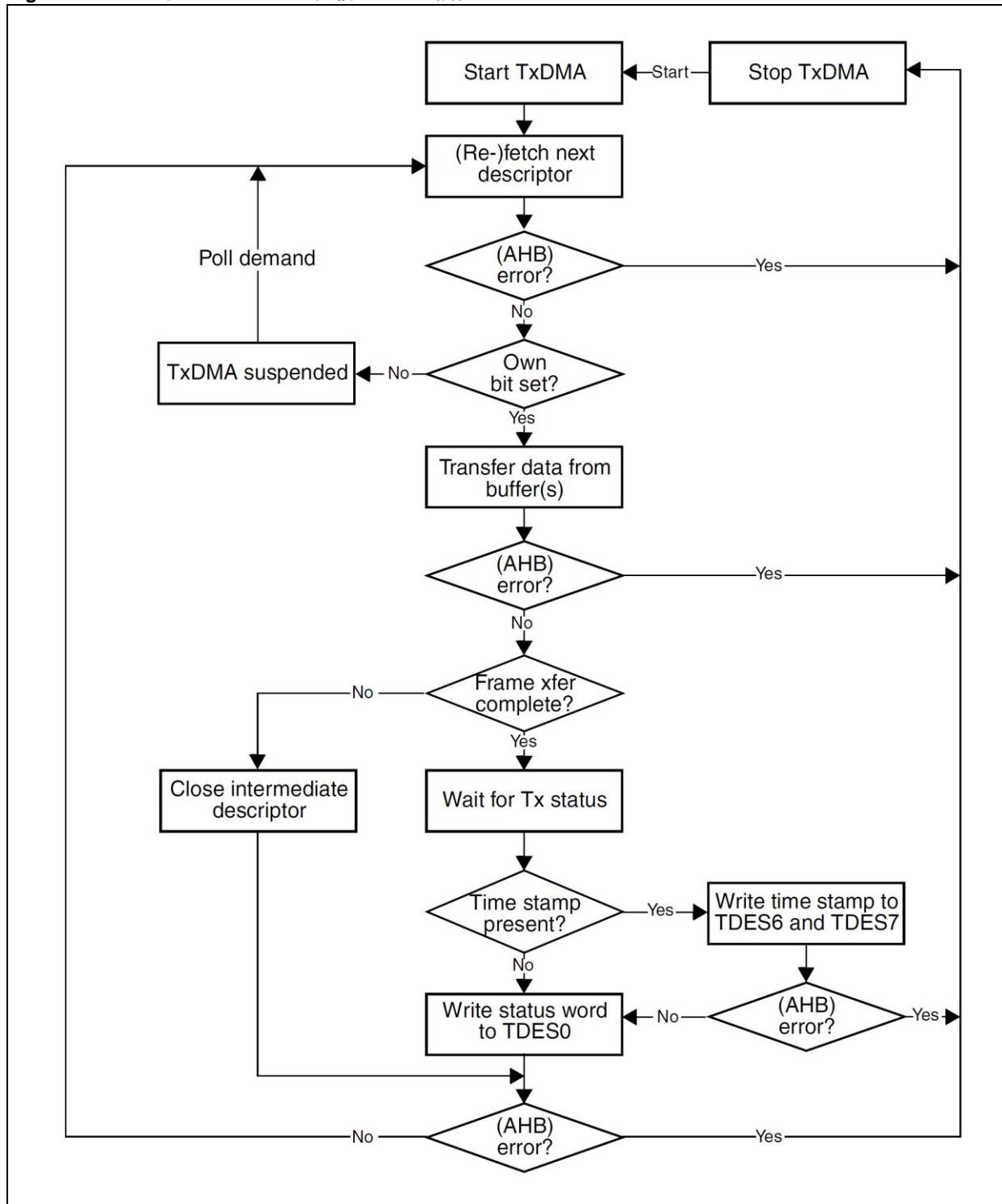

### ● 送信 DMA 動作: デフォルト(Non-OSF)モード

送信 DMA エンジンは、デフォルトモードでは以下のようないくつかの処理を行います。デフォルトモードでの送信 DMA 送信フローを Figure 3-2 に示します。

1. ホストは、送信ディスクリプタ(TDES0-TDES3)をセットアップし、対応するデータバッファを Ethernet フレームデータによってセットアップした後、OWN ビット(TDES0[31])をセットします。

2. ST ビット(DMA Register 6[13])をセットした後、DMA は Run ステートに入ります。

3. Run ステートのとき、DMA は、送信を要求しているフレームの送信ディスクリプタリストをポーリングします。ポーリング開始後、後続の Ring オーダ、Chain オーダのいずれかのディスクリプタを読み出します。DMA が、ホストによって所有されたフラグ付きディスクリプタを検出したとき、またはエラー条件が発生したとき、送信が一時停止され、Transmit Buffer Unavailable (DMA Register 5[2])および Normal Interrupt Summary (DMA Register 5[16])ビットの両方がセットされます。送信エンジンはステップ 9 に進みます。

4. 取得したディスクリプタに DMA の所有フラグがセットされている場合 (TDES0[31] = 1)、DMA は取得したディスクリプタから、送信データバッファアドレスをデコードします。

5. DMA はホストメモリから送信データを取得し、そのデータを送信のために MTL へ転送します。

6. Ethernet フレームが複数のディスクリプタのデータバッファに格納されている場合、DMA は中間のディスクリプタをクローズして、次のディスクリプタを取得します。end-of-Ethernet-frame データが MTL へ転送されるまでステップ 3, 4, 5 が繰り返されます。

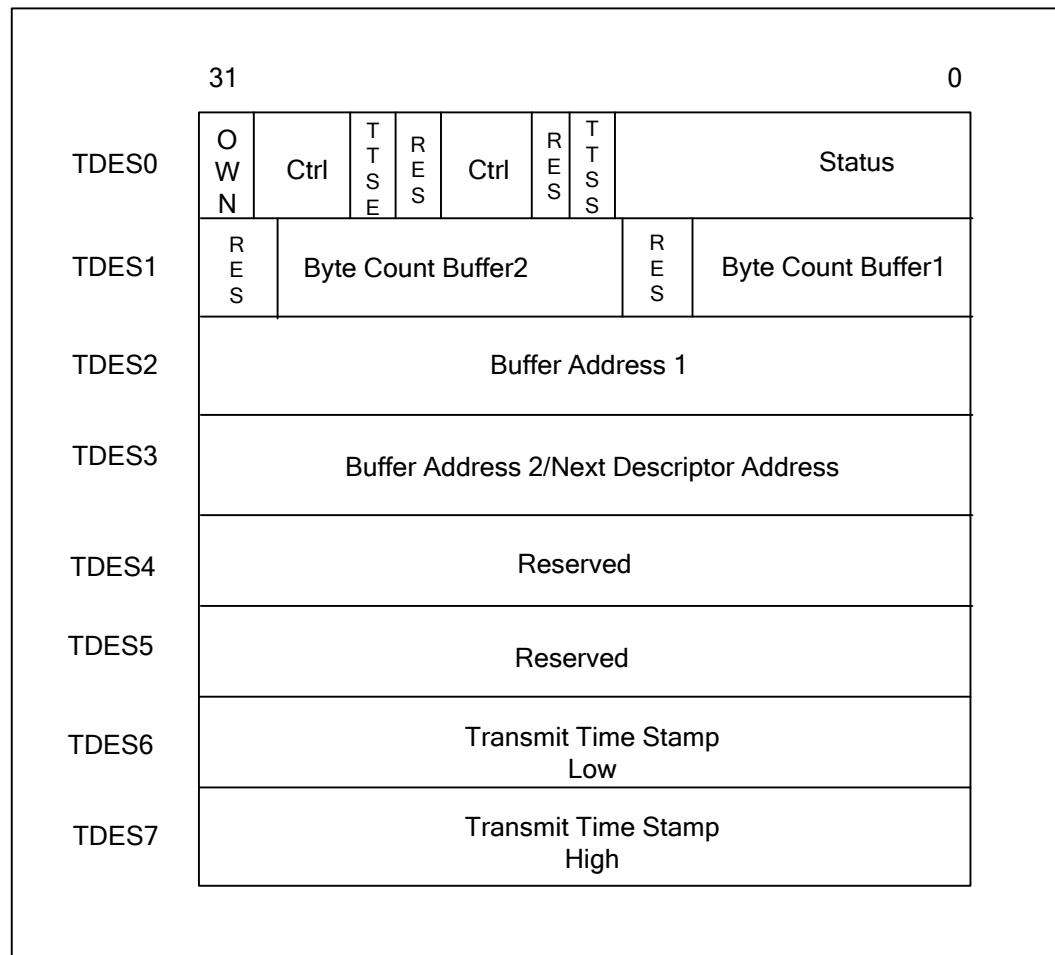

7. フレーム送信が完了したとき、そのフレームの IEEE 1588 タイムスタンプ生成がイネーブルされている場合 (送信ステータスによって示される)、MTL から取得したタイムスタンプ値が、end-of-frame バッファを含んでいる送信ディスクリプタ(TDES6 および TDES7)に書き込まれます。次に、ステータス情報がこの送信ディスクリプタ(TDES0)に書き込まれます。このステップ中に OWN ビットがクリアされるので、ホストがこのディスクリプタを所有することになります。このフレームにタイムスタンプ生成がイネーブルされていない場合、DMA は TDES6 および TDES7 の内容を変更しません。

8. 最後のディスクリプタの Interrupt on Completion (TDES0[30])がセットされているフレームの転送が完了した後、送信割込み(DMA Register 5[0])がセットされます。このとき、DMA エンジンはステップ 3 に戻ります。

9. Suspend ステートのとき、転送ポーリング要求を受信し、Underflow Interrupt Status ビットがクリアされると、DMA はディスクリプタの再取得を試みます(その後、ステップ 3 に戻ります)。

Figure 3-2 デフォルトモードでの送信 DMA の動作

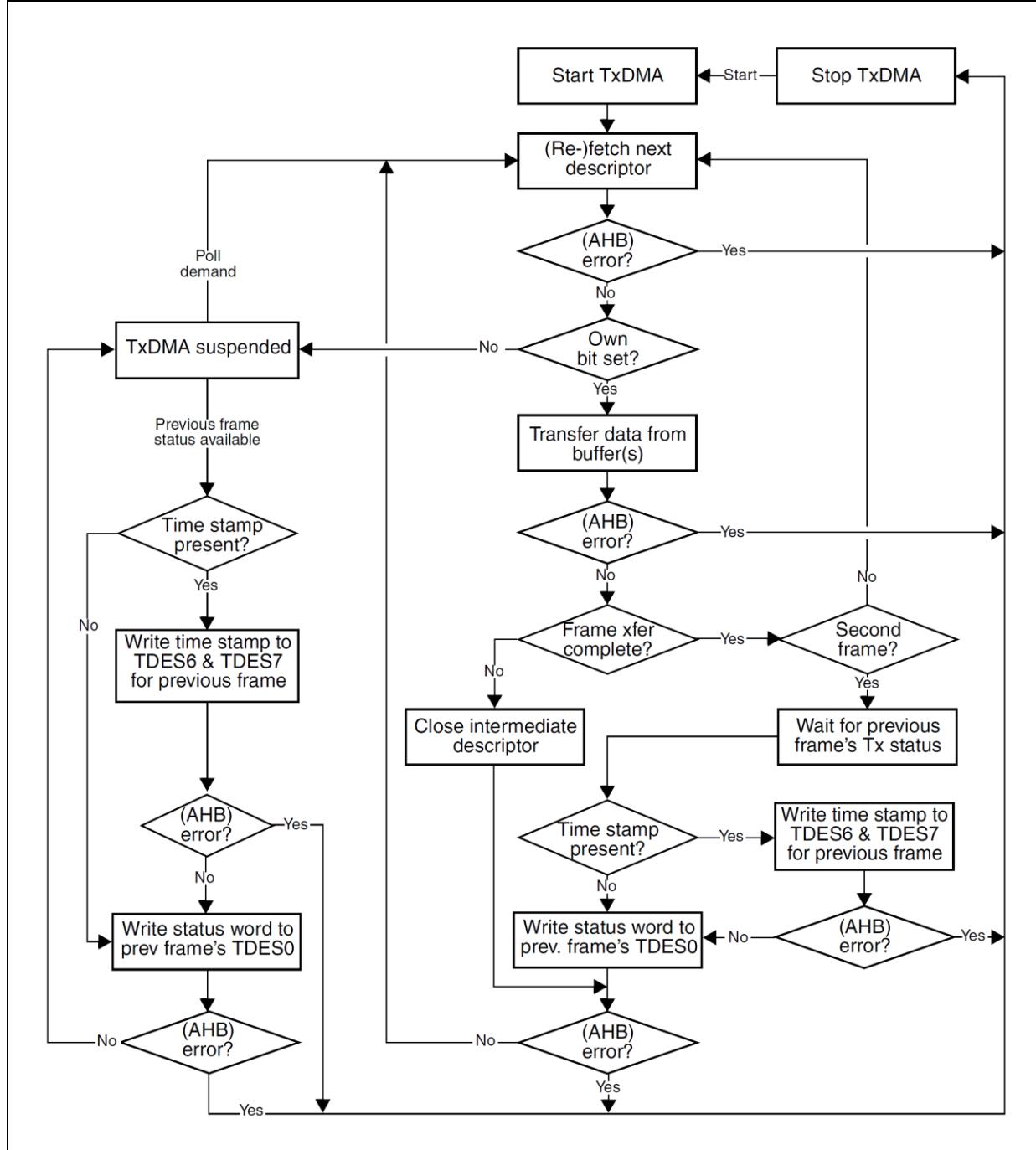

## ● 送信 DMA の動作: OSF モード

DMA Register 6[2]の OSF (Operate on Second Frame) ビットがセットされている場合、Run ステートで、送信処理は、最初のフレームのステータス・ディスクリプタをクローズすることなく 2つのフレームを同時に取得できます。送信プロセスは、最初の送信が終了すると、即座に 2番目のフレームの送信ディスクリプタリストをポーリングします。2番目のフレームが有効である場合、送信プロセスは最初のフレームのステータス情報を書き込む前にこのフレームを転送します。

OSF モードでは、Run ステートの送信 DMA は以下の順序で動作します。フローを Figure 3-3 に示します。

1. DMA は送信 DMA(デフォルトモード)のステップ 1-6 に示すように動作します。

2. DMA は、前のフレームの最後のディスクリプタをクローズすることなしに次のディスクリプタを取り込みます。

3. DMA が取得したディスクリプタを所有する場合、DMA はこのディスクリプタ内の送信バッファアドレスをデコードします。DMA がディスクリプタを所有しない場合、DMA は Suspend モードに入り、ステップ 7へスキップします。

4. DMA はホストメモリから送信フレームを取り込み、End-of-Frame データが転送されるまで MTL へフレームを転送し、このフレームが複数のディスクリプタにわたる場合は中間のディスクリプタをクローズします。

5. DMA は前のフレームのフレーム送信ステータスおよびタイムスタンプを待ちます。ステータスが入手でき、(ステータスピットによって示される)タイムスタンプが取得された場合、DMA はそのタイムスタンプを TDES6 および TDES7 に書き込みます。次に DMA は、OWN ビットをクリアしたステータスを対応する TDES0 へ書き込み、それによってディスクリプタをクローズします。前のフレームでタイムスタンプの生成がイネーブルされていない場合、DMA は TDES6 および TDES7 の内容を変更しません。

6. 送信割込みがイネーブルされていれば、送信割込みをセットします。DMA は次のディスクリプタを取り込み、ステップ 3 に進みます(ステータスが正常の場合)。前の送信のステータスがアンダフローエラーを示す場合、DMA は Suspend モードに入ります(ステップ 7)。

7. Suspend モードでは、MTL から保留中のステータスおよびタイムスタンプを受信した場合、DMA はタイムスタンプ(現在のフレームでイネーブルされている場合)を TDES6 および TDES7 に書き込み、次にステータスを対応する TDES0 に書き込みます。その後に、関連する割込みをセットし、Suspend モードに戻ります。

8. DMA は送信ポーリング要求(DMA Register 1)を受信した後でのみ、Suspend モードを終了して Run ステートに入ることができます(保留中のステータスに応じてステップ 1 またはステップ 2 へ進みます)。

---

### <注意事項>

DMA は現在のディスクリプタをクローズする前に次のディスクリプタを取り込むため、ディスクリプタ Chain が正しく、適切に処理されるためには 3つ以上の異なるディスクリプタが必要です。

---

Figure 3-3 OSF モードの送信 DMA の動作

## ● 送信フレーム処理

送信 DMA はデータバッファがプリアンブル、パッドバイト、FCS フィールドを除いた完全な Ethernet フレームを含んでいると想定します。DA, SA, Type/Len フィールドは有効なデータを含んでいる必要があります。送信ディスクリプタによって、CRC, PAD の挿入をディセーブルするよう指示されている場合、バッファは CRC バイトを含む完全な Ethernet フレーム(プリアンブルを除く)を含んでいなければなりません。フレームはデータの Chain 化が可能で、複数のバッファも使用できます。フレームは FS(TDES0[28]) と LS(TDES0[29]) によって区切らなければなりません。送信を開始するとき、最初のディスクリプタの FS(TDES0[28]) はセットされていなければなりません。このとき、フレームデータがホストのバッファから MTL 送信 FIFO へ転送されます。同時に、そのフレームの LS(TDES0[29]) がクリアされている場合、送信プロセスは次のディスクリプタの取得を試みます。送信プロセスはこのディスクリプタの FS(TDES0[28]) がクリアされていると想定します。LS(TDES0[29]) がクリアされていれば、それは中間バッファを表します。LS(TDES0[29]) がセットされていれば、それはフレームの最後のバッファを表します。フレームの最後のバッファが送信された後、DMA はステータス情報を、LS(TDES0[29]) がセットされているディスクリプタの TDES0 ワードに書き戻します。このとき、Interrupt on Completion (TDES0[30]) がセットされている場合、Transmit Interrupt (DMA Register 5[0]) がセットされ、新規ディスクリプタが取り込まれ、このプロセスが繰り返されます。実際のフレーム送信は、MTL 送信 FIFO がプログラム可能な送信しきい値(DMA Register 6[16:14])に到達した、または完全なフレームが FIFO に入った後 (Store and Forward Mode (DMA Register 6[21]) のオプション) に開始されます。PHY インタフェースからフレームの送出が終了したとき、最後のディスクリプタが開放されます(OWN ビット TDES0[31] がクリアされます)。

## ● 送信ポーリング一時停止

以下のいずれかの条件で、送信ポーリングが一時停止されます。

- ・ DMA がホストによって所有されるディスクリプタ(TDES0[31]=0)を検出したとき。再開するにはドライバはディスクリプタの所有権を DMA に渡し、Poll Demand コマンドを発行しなければなりません。

- ・ アンダフローによる送信エラーが検出されたため、フレーム送信がアボートされたとき。適切な Transmit Descriptor 0 (TDES0) ビットがセットされます。

上の2番目の条件が発生したとき、Abnormal Interrupt Summary (DMA Register 5[15]) と Transmit Underflow ビット (DMA Register 5 [5]) の両方がセットされ、その情報が Transmit Descriptor 0 に書き込まれ、一時停止になります。1番目の条件で DMA が Suspend ステートに入った場合、Normal Interrupt Summary (DMA Register 5 [16]) と Transmit Buffer Unavailable (DMA Register 5 [2]) がセットされます。

いずれの場合も、送信リスト内での位置は保持されます。保持される位置は、最後に DMA によってクローズされたディスクリプタの位置です。ドライバは一時停止の原因を是正した後、明示的に Transmit Poll Demand コマンドを発行しなければなりません。

## ■ 受信動作

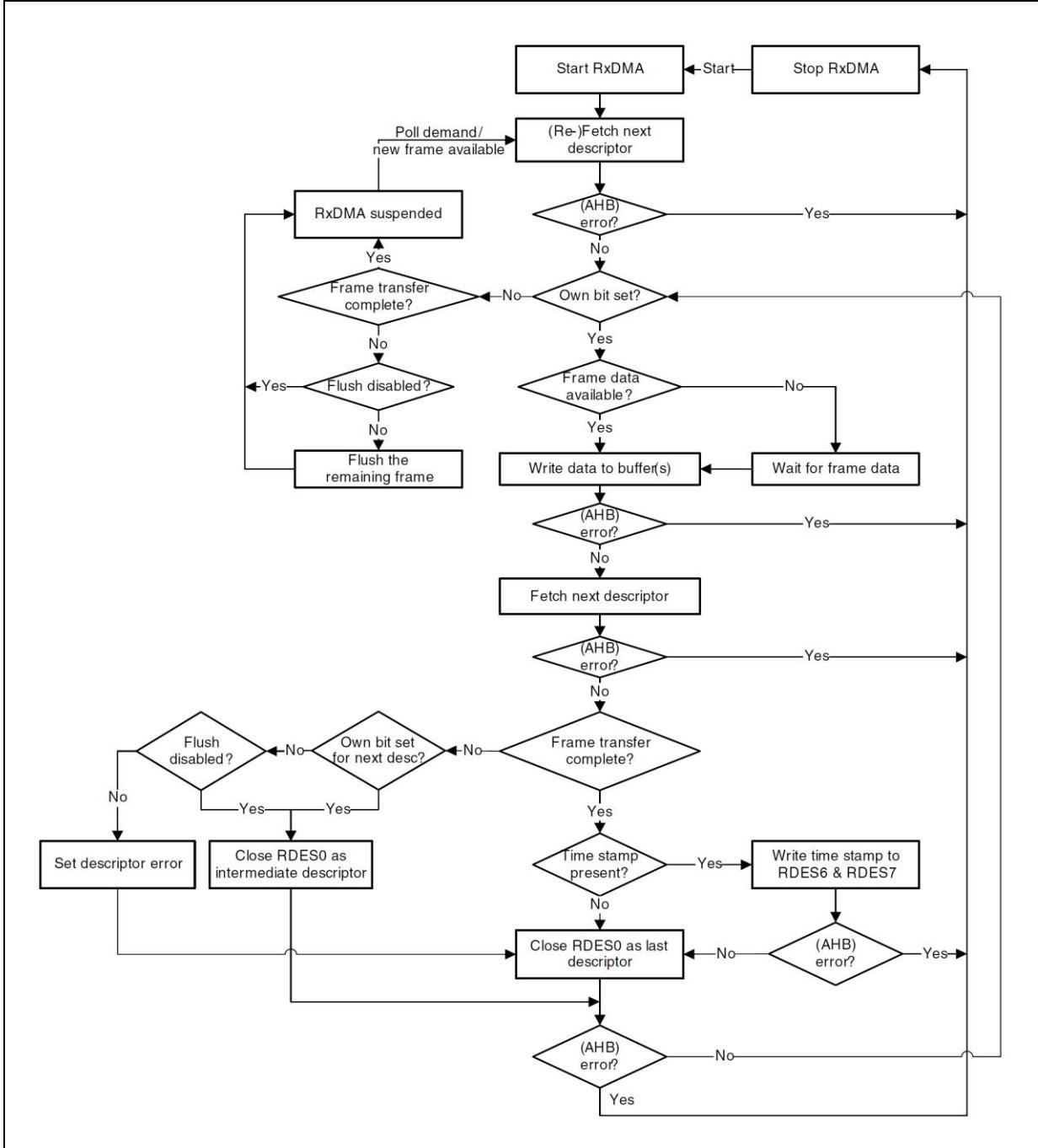

受信 DMA エンジンの受信シーケンスを Figure 3-4 および以下に手順を示します。

1. ホストは受信ディスクリプタ(RDES0-RDES3)をセットアップし、OWN ビット(RDES0[31])をセットします。

2. SR (DMA Register 6[1]) ビットがセットされると、DMA は Run ステートに入ります。Run ステートでは DMA は受信ディスクリプタリストをポーリングし、使用可能なディスクリプタの取得を試みます。取り込んだディスクリプタが使用可能でない(ホストによって所有されている)場合、DMA は Suspend ステートに入り、ステップ 9 にジャンプします。

3. DMA は取得されたディスクリプタからの受信データバッファアドレスをデコードします。

4. 着信フレームが処理され、取得したディスクリプタのデータバッファに入れられます。

5. バッファがフルになるかフレーム転送が完了したとき、受信エンジンは次のディスクリプタを取り込みます。

6. 現在のフレーム転送が完了している場合、DMA はステップ 7 に進みます。DMA が次に取り込まれるディスクリプタを所有しておらず、フレーム転送が完了していない(EOF がまだ転送されていない)場合、DMA は RDES0 の Descriptor Error ビットをセットします(フラッシュがディセーブルされていない場合)。DMA は現在のディスクリプタをクローズし(OWN ビットをクリアします)、RDES0 の Last Segment (LS) ビットをクリアすることによって中間ディスクリプタとしてマークし(フラッシュがディセーブルされていない場合は Last Descriptor としてマークし)、ステップ 8 へ進みます。DMA が次のディスクリプタを所有しているが、現在のフレーム転送が完全でない場合、DMA は現在のディスクリプタを中間ディスクリプタとしてクローズし、ステップ 4 に戻ります。

7. IEEE 1588 タイムスタンプ生成がイネーブルされている場合、DMA はタイムスタンプ(利用可能な場合)を現在のディスクリプタの RDES6 および RDES7 に書き込みます。次に DMA は、MTL から受信フレームのステータスを取得し、ステータスワードを現在のディスクリプタの RDES0 に書き込み、OWN ビットをクリアし Last Segment ビットをセットします。

8. 受信エンジンは最新のディスクリプタの OWN ビットをチェックします。ホストがディスクリプタを所有している場合(OWN ビットが 0)、Receive Buffer Unavailable ビット(Register 5[7])がセットされ、DMA 受信エンジンは Suspended ステートに入ります(ステップ 9)。DMA がディスクリプタを所有する場合、エンジンはステップ 4 に戻り、次のフレームを待ちます。

9. Receive エンジンが Suspend ステートに入る前に、受信 FIFO から部分的なフレームがフラッシュされます(DMA Register 6 の bit24 を使用してフラッシュをコントロールできます)。

10. Receive Poll 要求が発行されるか、MTL 受信 FIFO からの次のフレームの転送開始が可能になったとき、受信 DMA は Suspend ステートを終了します。受信エンジンはステップ 2 へ進み、次のディスクリプタを再び取り込みます。

DMA は、タイムスタンプの書戻しを完了し、ディスクリプタへのステータスの書戻しを実行する準備ができるまで MTL からのステータスの受信をアクノリッジしません。

ソフトウェアが CSR を通じたタイムスタンプ生成をイネーブルしている場合、フレームの有効なタイムスタンプ値が入手不能であるとき(例えば、タイムスタンプを書き込むことができるようになる前に受信 FIFO がフルになつたため)、DMA は RDES6 および RDES7 にオール 1 を書き込みます。そうでない場合(タイムスタンプがイネーブルされていない場合)、RDES6 および RDES7 は変更されません。

Figure 3-4 受信 DMA の動作

## ● 受信ディスクリプタの取得

受信エンジンは常に、着信フレームを予測して余分のディスクリプタを取得しようとします。以下のいずれかの条件が満たされると、ディスクリプタを取得しようとします。

- Receive Start/Stop ビット(DMA Register 6[1])がセットされ、Run ステートに入った直後。

- 現在のフレームの転送を終了する前に、ディスクリプタのデータバッファがフルになった。

- フレーム受信を完了しているが、現在の受信ディスクリプタがまだクローズしていない。

- ホストが所有するバッファ(RDES0[31]=0)により、受信プロセスが一時停止されている状態で、新規フレームを受信した。

- 受信 Poll Demand コマンドが発行された。

## ● 受信フレーム処理

GMAC は、受信フレームがアドレスフィルタを通過し、フレームサイズが MTL 受信 FIFO のしきい値バイト数より大きいか等しいとき、または完全なフレームが Store-and-Forward モードで FIFO に書き込まれたときにのみ、受信フレームをホストメモリに転送します。

フレームがアドレスフィルタを通過しなかった場合、GMAC ブロックの中で破棄されます(GMAC Register 1 [31]:Receive All ビットがセットされていない場合)。衝突や終了が未完了のために 64 バイト未満になっているフレームを MTL 受信 FIFO からページできます。

64 バイト(構成可能なしきい値)が受信された後、MTL ブロックは DMA ブロックに対してフレームデータを現在のディスクリプタによって指定されている受信バッファへ転送するよう要求します。DMA は、AHB Interface がデータ転送の準備完了状態になった後(DMA がホストからの送信データを取り込んでいない場合)、フレームを区切るために First Descriptor (RDES0[9])をセットします。

ディスクリプタは、データバッファがフルになるか、またはフレームの最後のセグメントが受信バッファへ転送されて OWN (RDES[31])ビットが 0 にリセットされたときに開放されます。

フレームが 1 つのディスクリプタに収まっている場合、LS (RDES0[8])と FS (RDES0[9])の両方をセットします。DMA は次のディスクリプタを取り込み、LS (RDES0[8])ビットをセットし、前のフレームディスクリプタの RDES0 ステータスビットを開放します。次に DMA は Receive Interrupt (DMA Register 5[6])をセットします。DMA がホストによって所有されていることを示すフラグが付いているディスクリプタを検出するまで、同じプロセスが繰り返されます。このようなディスクリプタが検出されたとき、受信プロセスは Receive Buffer Unavailable (DMA Register 5[7])をセットし、Suspend ステートに入ります。受信リスト内の位置は保持されます。

## ● 受信プロセスの一時停止

受信プロセスが Suspend ステートのときに新しい受信フレームが到着した場合、DMA はホストメモリの現在のディスクリプタを再び取り込みます。ディスクリプタが現在 DMA によって所有されている場合、受信プロセスは再び Run ステートに入り、フレームの受信を開始します。ディスクリプタが依然としてホストによって所有されている場合、デフォルトでは DMA は現在のフレームを MTL 受信 FIFO の最上位で廃棄し、受信されなかったフレームカウンタを増分します。MTL 受信 FIFO に 2 つ以上のフレームが格納されている場合、このプロセスが繰り返されます。Operation Mode レジストの bit24 (DFF)をセットすることによって、MTL 受信 FIFO の最上位のフレームの廃棄またはフラッシュを防止できます。このとき、受信プロセスは Receive Buffer Unavailable ステータスをセットし、Suspend ステートに戻ります。

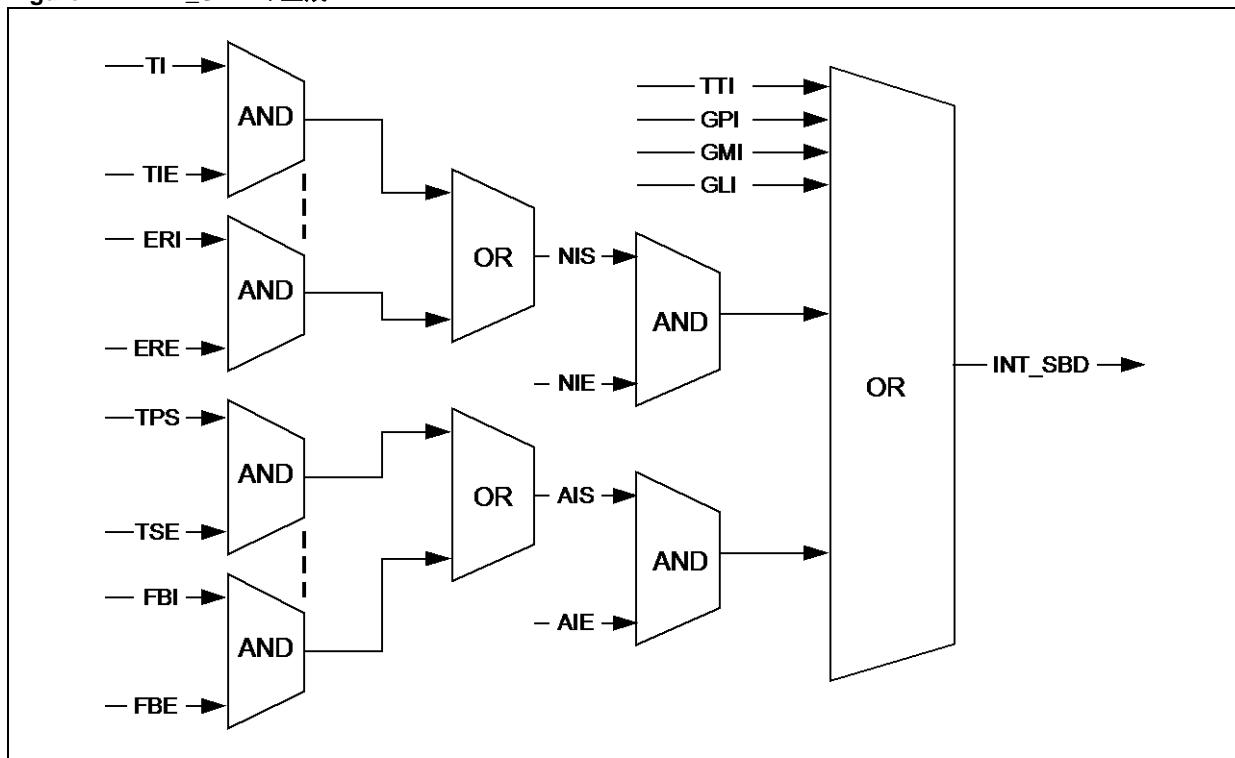

## ■ 割込み

割込みは種々のイベントにより発生します。DMA Register 5 は、割込みの原因になるすべてのビットを含んでいます。DMA Register 7 は、割込みの原因になる各イベントのイネーブルビットを含んでいます。DMA Register 5 で記述されているように、割込みには正常割込みと異常割込みの 2 つの種類があります。割込みは、対応するビット位置に 1 を書き込むことによってクリアされます。グループ内のすべてのイネーブルされているビットがクリアされたとき、対応するサマリビットがクリアされます。両方のサマリビットがクリアされたとき、割込み信号 INT\_SBD がデアサートされます。Ethernet-MAC が割込みをアサートした原因である場合、DMA Register 5 の GLI, GMI, GPI のいずれかのビットが 1 にセットされています。

### ＜注意事項＞

DMA Register 5 は(割込み)ステータスレジスタです。割込み信号(INT\_SBD)がこのステータスレジスタの何らかのイベントによってアサートされるのは、DMA Register 7 で対応するイネーブルビットがセットされている場合だけです。

割込みは待ち行列制御を行いません。ドライバが応答する前に別の割込みイベントが発生した場合に、追加の割込みは発生しません。例えば、Receive Interrupt (DMA Register 5[6]) は、1つ以上のフレームがホストバッファへ転送されたことを示します。ドライバは DMA によって所有されるすべてのディスクリプタを、最後の記録位置から最初の記録位置までスキヤンしなければなりません。

同時に複数の割込みイベントが発生した場合でも割込みは1回だけ生成されます。ドライバは割込みの原因を調べるために DMA Register 5 をスキヤンしなければなりません。ドライバが DMA Register 5 の該当ビットをクリアした後は、新しい割込みイベントが発生するまで、割込みが再度生成されることはありません。例えば、コントローラが Receive Interrupt (DMA Register 5[6]) を生成し、ドライバが DMA Register 5 のリードを開始します。次に Receive Buffer Unavailable (DMA Register 5[7]) が発生します。ドライバは Receive Interrupt をクリアします。この時点でも、Receive Buffer Unavailable 割込みがアクティブまたは保留中であるために INT\_SBD 信号はデアサートされません。

Receive Interrupt (DMA register 5[6]) の柔軟なコントロールのために、割込みタイマ ("4.42. DMA Register 9 (RIWTR)" を参照) が提供されています。この割込みタイマは、非 0 値にプログラムされていて、DMA Register 7 で対応する受信割込みがイネーブルされていて、対応する DIC(RDES1[31]) で割込みがディセーブルされている場合、受信 DMA が受信フレームのシステムメモリへの転送を完了したとき、受信割込みをアサートさせず、カウントを開始します。このタイマがタイムアウトすると、RI ビットがセットされ割込みがアサートされます。このタイマは、そのディスクリプタに対して DIC(RDES1[31]) で割込みがイネーブルされている場合は、フレームがメモリへ転送されても、カウントを開始せず停止したままで、割込みを発生させます。

## ■ DMA へのエラー応答

DMA チャネルによって開始されるすべてのデータ転送で、バスエラーが発生した場合、その DMA はすべての動作を停止し、エラービットと Status register (DMA Register 5) の Fatal Bus Error ビットを更新します。その場合、DMA コントローラにソフトリセットまたはハードリセットを行い、DMA が再初期化された後にのみ、動作を再開できます。

## ■ CRC

DMA は、Ethernet フレームの FCS フィールドの CRC を生成します。DMA は Ethernet フレームの FCS フィールドの 32 ビット CRC を計算します。エンコードは下記の生成多項式によって定義されます。

$$G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$$

## 3.4. チェックサムエンジン

TCP や UDP などの通信プロトコルはチェックサムフィールドを導入しており、それを使ってネットワーク上で送信されるデータの完全性が判定されます。Ethernet の最も広範な利用方法は、IP データグラム上で TCP および UDP をカプセル化することであるため、GMAC は、オプションの Checksum Offload Engine (COE)を導入し、チェックサム計算、送信パスへの挿入、受信パスでのエラー検出をサポートしています。

### ■ 送信チェックサムオフロードエンジン

送信チェックサムオフロードエンジン (COE) は 2 つのタイプのチェックサム計算と挿入をサポートします。CIC ビット (TDES0[23:22])をセットすることによって、各フレームについてこのチェックサムエンジンをコントロールできます。

#### ● IP ヘッダチェックサムエンジン

IPv4 データグラムでは、ヘッダフィールドの完全性は 16 ビットのヘッダチェックサムフィールド(IPv4 データグラムの 11, 12 番目のバイト)によって示されます。COE は Ethernet フレームの Type フィールドの値が 0x0800 で、IP データグラムの Version フィールドの値が 0x4 のときに IPv4 データグラムを検出します。送信時、フレームのチェックサムフィールドは、計算時は無視され、計算値に置換されます。IPv6 ヘッダにはチェックサムフィールドがないため、COE は IPv6 ヘッダフィールドを変更しません。この IP ヘッダチェックサム計算の結果は送信ステータスの IP Header Error ステータスピット(TDES0[16])によって示されます。このステータスピットは、Ethernet フレームの Type フィールドと IP ヘッダの Version フィールドの値が一致しないとき、または Ethernet フレームに IP header Length フィールドで指定されている十分なデータがないときにセットされます。つまり、このビットは以下のいずれかの状況で IP ヘッダエラーがアサートされているときセットされます。

IPv4 データグラム :

- Ethernet type が 0x0800 で、IP ヘッダの Version フィールドが 0x4 でない

- IPv4 Header Length フィールドが、0x5 (20 バイト)未満の値を示す

- 合計フレーム長が IPv4 Header Length フィールドで指定されている値より小さい

IPv6 データグラム :

- Ethernet タイプが 0x86DD で、IP header Version フィールドが 0x6 でない

- IPv6 ヘッダ(40 バイト)または拡張ヘッダ(拡張ヘッダの対応する Header Length フィールドで指定されています)が完全に受信される前にフレームが終了した。

COE は、このような IP ヘッダエラーを検出したときでも、Ethernet フレームの Type フィールドが IPv4 ペイロードを示している場合は IPv4 ヘッダチェックサムを挿入します。

## ● TCP/UDP/ICMP チェックサムエンジン

TCP/UDP/ICMP チェックサムエンジンは、IPv4 または IPv6 ヘッダ(拡張ヘッダを含む)を処理し、カプセル化されたペイロードが TCP, UDP, ICMP のいずれかを判定します。

### ＜注意事項＞

TCP, UDP, ICMP/ICMPv6 以外のペイロードについては、このチェックサムエンジンはバイパスされ、フレームでそれ以上の変更は行われません。

断片化された IP フレーム(IPv4 または IPv6)とセキュリティ機能を備えた IP フレーム(認証ヘッダ、カプセル化されたセキュリティペイロードなど)は、このエンジンでは処理されないため、バイパスしなければなりません。つまり、このようなフレームではペイロードチェックサムの挿入をイネーブルしてはいけません。

IPv6 認証ヘッダを使用する Ethernet 環境下では、チェックサムエンジンはイネーブルできません。送信拡張ディスクリプタ 0 の CIC フィールドは、00 または 01 にしてください。

TCP, UDP または ICMP ペイロードのチェックサムが計算され、ヘッダ内の対応するビットに挿入されます。このエンジンは下記の 2 つのモードで動作できます。

- 最初のモードは、TCP, UDP または ICMPv6 擬似ヘッダに対するチェックサム計算を行わず、入力フレームの Checksum フィールドに(その計算結果が)存在すると見なします。エンジンは、Checksum フィールドの値を含めてチェックサム計算を行い、Checksum フィールドを最終的なチェックサムで更新します。

- 2 番目のモードは、エンジンは Checksum フィールドを無視します。TCP, UDP または ICMPv6 擬似ヘッダデータをチェックサム計算に含め、Checksum フィールドを最終的なチェックサムによって上書きします。

### ＜注意事項＞

IPv4 上の ICMP 上のパケットは、擬似ヘッダは定義されないため、ICMP パケットの Checksum フィールドはどちらのモードでも常に 0x0000 でなければなりません。この値が 0x0000 でない場合、正しくないチェックサムがパケットに挿入されることがあります。

この操作の結果は、TDES0[12]の IP Payload Error ビットによって示されます。このエンジンは、フレームが Store-and-Forward モードで GMAC トランスマッタに転送され、end-of-frame が FIFO に書き込まれていないことを検出したとき、または IP ヘッダの Payload Length フィールドで指定されているバイト数を受信する前にパケットが終了したときに、IP Payload Error をセットします。パケットが指定されているペイロードの長さより長い場合、COE はそれらを埋め込みバイトとして無視し、エラーを報告しません。このエンジンは、最初のタイプのエラーを検出したときには TCP, UDP または ICMP ヘッダを変更しません。2 番目のエラー・タイプでは、計算によって得られたチェックサムを対応するヘッダフィールドへ挿入します。

### ＜注意事項＞

TCP, UDP, ICMP のチェックサムは完全なフレームについて計算され、次にその対応するヘッダフィールドに挿入されます。この要件のため、この機能は送信 FIFO が Store-and-Forward モードに構成されている場合(DMA Register 6 TSF=1)にのみイネーブルされます。GMAC が Threshold (cut-through) モードに構成されている場合、送信 COE はバイパスされます。

Store-and-Forward モードであっても、TCP, UDP, ICMP のチェックサムを挿入する際は、下記のバイト数の条件を満たすフレームに対してだけイネーブルする必要があります。

フレーム長 (Byte) < 2036 (Byte) は、下記のバイト数の条件を満たす PBL は、DMA Register 0 で指定する送信時のバースト長になります。送信時、PBL するの設定可能最大値は、512 のため、通常の Ethernet フレームであれば問題はありません。しかしこの条件を満たさないフレーム長の場合、チェックサム挿入エンジンは失敗し、その結果、不適切なリカバリのために先行するすべてのフレームが破損する可能性があります。

## ■ 受信チェックサムオフロードエンジン

受信 Ethernet フレームの中の IPv4 フレームと IPv6 フレームの両方が検出され、データの完全性チェックを行います。このモジュールは GMAC Configuration レジスタの IPC ビットをセットすることで有効になります。

GMAC レシーバは、受信 Ethernet フレームの Type フィールドの値 0x0800 または 0x86DD をチェックし、それぞれ IPv4 または IPv6 フレームを識別します。この識別は VLAN タグ付フレームにも適用されます。受信チェックサムオフロードエンジンは、IPv4 ヘッダチェックサムを計算し、それが受信 IPv4 ヘッダのチェックサムと一致することをチェックします。指定されたペイロードタイプ(Ethernet Type フィールド)と IP ヘッダバージョンが一致しない、または受信したフレームに IPv4 ヘッダの Length フィールドで指定されている十分なバイト数がない(または IPv4 または IPv6 ヘッダのバイト数が 20 未満である)ときに IP Header Error ビットがセットされます。また、受信 IP データグラム(IPv4 または IPv6)の中の TCP, UDP または ICMP ペイロードを識別し、TCP, UDP または ICMP 仕様で定義されている方法でそのペイロードのチェックサムを適切に計算します。このエンジンは、チェックサム計算のための TCP/UDP/ICMPv6 擬似ヘッダバイトを含んでおり、受信した Checksum フィールドが計算値と一致することをチェックします。この演算の結果は受信ステータスワードの Payload Checksum Error ビットに示されます。また、このステータスピットは TCP, UDP または ICMP のペイロード長が IP ヘッダで指定されている想定ペイロード長と一致しない場合にもセットされます。

"TCP/UDP/ICMP チェックサムエンジン"で記述しているように、このエンジンは、断片化された IP データグラム、セキュリティ機能を備えた IP データグラム、および TCP, UDP, ICMP 以外のペイロードをバイパスします。この情報は(チェックサムエンジンがバイパスされるかどうかに関わりなく)受信ステータスで与えられます。

---

### <注意事項>

GMAC が IPv6 Routing 拡張ヘッダの Segment Left フィールドに 0 以外の値を持ったパケットを受信した場合、チェックサムエンジンは、受信パケットをバイパスし、無視します。

IPv6 認証ヘッダを使用する Ethernet 環境下では、チェックサムエンジンはイネーブルできません。GMAC Register0(MCR) の IPC(bit10) は、0 にしてください。

---

## 3.5. Energy Efficient Ethernet

Energy Efficient Ethernet (EEE)は、IEEE 802.3 Media Access Control (MAC)サブレイヤと物理レイヤを Low-Power Idle (LPI)モードで動作することを可能にするオプションの動作モードです。

LPI モードでは、送受信するデータがないときに通信装置の機能の一部をオフに切り換えることによって電力の消費を削減できます。リンクの両側のシステムで、リンク利用率が低い時間に一部の機能をディセーブルすることによって消費電力を削減できます。GMAC はシステムが LPI モードに入るか LPI モードを終了するかをコントロールし、それを PHY に知らせます。

EEE は、リンクパートナーが EEE をサポートするかどうかを決定するネゴシエーション方法を規定し、次に両方の装置に共通のパラメータセットを選択します。

LPI モードは、GMAC が MII を使い、全二重モードでのみサポートされます。

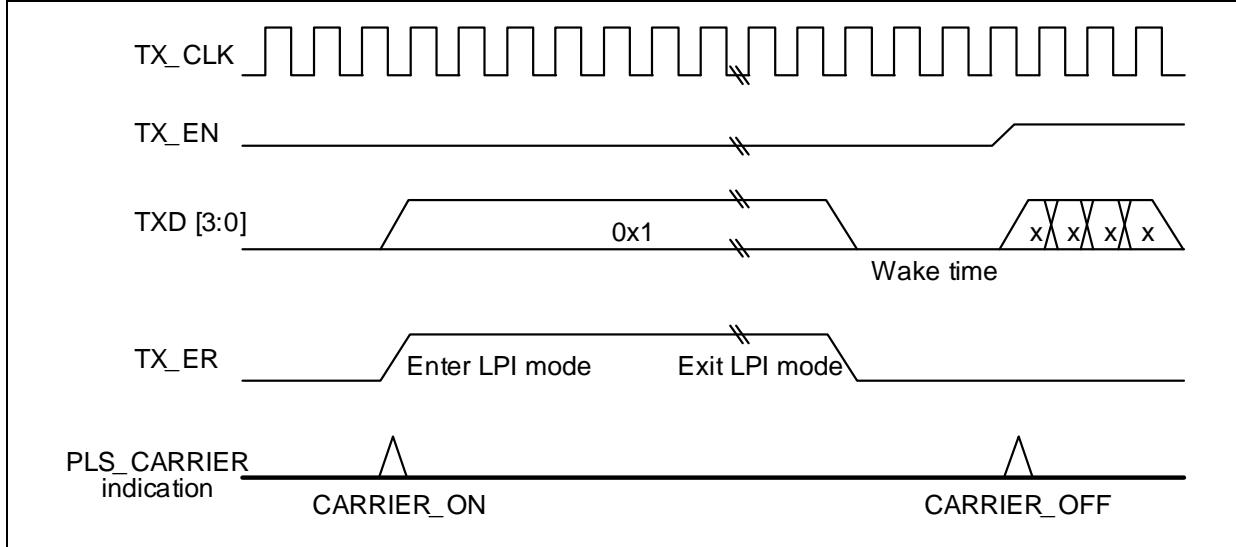

### ■ 送信バス機能

送信バスで、ソフトウェアは、GMAC Register 12 (LPI Control and Status Register) の bit16 (LPIEN) をセットすることによって、GMAC に対して送信を停止し、LPI プロトコルを開始するよう指示しなければなりません。GMAC は進行中の送信を完了し、送信ステータスを生成します。次に、Interframe gap (IFG) の間、IDLE パターンの代わりに LPI パターンの送信を開始します。

PHY を LPI ステートにするため、GMAC は以下のタスクを実行します。

1. TX\_EN をディアサートします。

2. TX\_ER をアサートします。

3. TXD[3:0] を 0x1 (100 Mbps の場合) にセットします。

GMAC は PHY が LPI ステートに入っている全期間にわたって TX\_EN, TX\_ER, TXD 信号を同じ状態に維持します。

4. GMAC Register 12 (LPI Control and Status Register) の bit0 を更新し、割込みを生成します。

PHY の LPI ステートを終了する、つまりソフトウェアが LPIEN ビットをリセットすると、GMAC は以下のタスクを実行します。

5. LPI パターンの送信を停止し、IDLE パターンの送信を開始します。

6. LPI TW TIMER をスタートします。

GMAC は、PHY のウェイクアップ時間が経過するまで送信を開始できません。オート・ネゴシエーション・ウェイクアップ間隔は、GMAC Register 13 (LPI Timers Control Register) の bit[15:0] (TWT: LPI TW TIMER) にプログラムされます。

7. LPI 終了ステータス GMAC Register 12 (LPI Control and Status Register) の bit1 を更新し、割込みを生成します。

### <注意事項>

- ・ LPI モード中に TX\_CLK の供給が停止される場合、GMAC Register 12 (LPI Control and Status Register) の bit19 (LPITXA) を使用できません。Energy Efficient Ethernet 標準(802.3az)によると、PHY は MII(10 Mbps/100 Mbps) モードで LPI ステートの間、TXCLK クロックを停止できません。

- ・ GMAC が送信 LPI モードで、TX\_CLK の供給が停止しているとき、アプリケーションは TX\_CLK ドメインに同期されている CSR レジスタに書き込んではいけません。

- ・ GMAC が LPI モードで、ホストがソフトリセットまたはハードリセットを発行したとき、GMAC トランスマッタは LPI モードを終了します。

Figure 3-5 に、LPI モード遷移中の TX\_EN, TX\_ER および TXD[3:0] 信号の動作を示します。

**Figure 3-5 LPI の遷移(送信)**

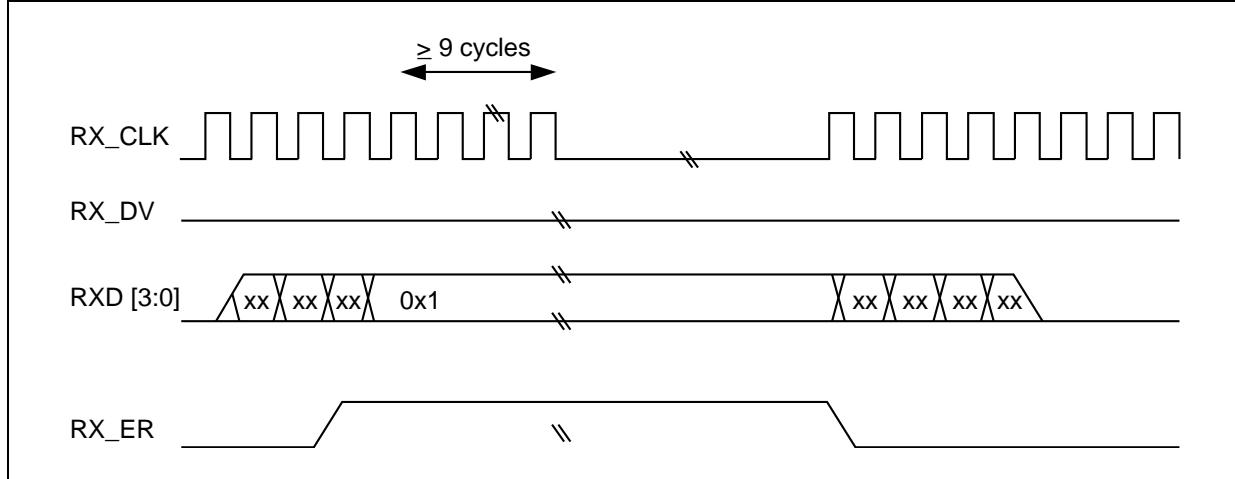

## ■ 受信バス機能

受信バスでは、PHY がリンクパートナーから LPI ステートに入る信号を受信したとき、PHY および GMAC は以下のタスクを実行します。

1. PHY が RX\_ER をアサートします。

2. PHY が RXD[3:0] を 0x1 にセットします。

3. PHY が RX\_DV をデアサートします。

PHY は LPI ステートに入っている全期間、RX\_ER, RXD, RX\_DV 信号を同じステートに保持します。

4. GMAC が、GMAC Register 12 (LPI Control and Status Register) の bit2 (RLPIEN) を更新し、即座に割込みを生成します。

PHY がリンクパートナーから LPI ステートを終了する信号を受信したとき、PHY および GMAC は以下のタスクを実行します。

1. PHY が RX\_ER をデアサートし、通常のフレーム間ステートに戻ります。

2. GMAC が、GMAC Register 12 (LPI Control and Status Register) の bit3 (RLPIEX) を更新し、割込みを生成します。この場合、割込み信号 INT\_LPI (synchronous to Rx clock) もアサートされます。

Figure 3-6 に、LPI モード遷移中の RX\_ER, RX\_DV および RXD[3:0] 信号の動作を示します。

### ＜注意事項＞

MDIO を通じて書き込まれる PHY レジスタの RX\_CLK\_stoppable ビットがアサートされている場合、Figure 3-6 に示すように、PHY が GMAC に LPI を指示しているとき、PHY は LPI ステートの開始から 9 クロックサイクル以上後に、随時 RX\_CLK の供給を停止できます。

GMAC が LPI モードのときに、ホストがソフトリセットまたはハードリセットを発行した場合、GMAC レシーバは、リセット中に LPI モードを終了します。リセットがデアサートされた後にまだ LPI パターンが受信される場合、GMAC レシーバは再び LPI ステートに入ります。

受信 LPI モードで RX クロックが停止した場合、ホストは RX クロックドメインに同期されている CSR レジスタへの書き込みを行うことはできません。

Figure 3-6 LPI 遷移(受信)

## ■ LPI タイマ

GMAC トランスマッタは、下記の 2 つのタイマを動作させます。タイマには GMAC Register 13 (LPI Timers Control Register)からそれぞれの値がロードされます。

### · LPI LS TIMER :

LPI LS TIMER は、リンクステータスが Up になって以降の経過時間(ms 単位)をカウントします。このタイマは、リンクが Down になるたびにクリアされ、リンクが Up になると、ソフトウェアによってプログラムされているターミナルカウントに到達するまで、再びインクリメントします。PHY インタフェースは、ターミナルカウントに到達しない限り LPI パターンをアサートしません。これによって、リモートステーションとのリンクが確立されてから LPI パターンがアサートされるまでの最小限の時間が確保されます。この時間は IEEE standard 802.3-az-2010 によって 1 秒と規定されています。LPI LS TIMER は 10 ビット幅です。したがってソフトウェアは最大 1023 ms までプログラミングできます。

### · LPI TW TIMER :

LPI TW TIMER は LPI がデアサートされて以降の経過時間(μs 単位)をカウントします。このタイマのターミナルカウントは、Transmit TW を確保するための値で、オート・ネゴシエーション後、GMAC が通常の送信動作を再開できるまでの時間です。GMAC は LPI TW TIMER をマイクロ秒単位でサポートします。LPI TW TIMER は 16 ビット幅です。したがってソフトウェアは最大 65535 μs までプログラミングできます。

PHY からの TX\_CLK 供給が停止する場合は、GMAC Register 12 (LPI Control and Status Register) の bit17 (PLS) を 0 にプログラムします。それによって内部タイマがリセットされます。LPI LS TIMER または LPI TW TIMER がカウント中に、TX\_CLK 周波数が変化すると、不適切なタイムアウトが発生することがあります。

## 3.6. MAC マネジメントカウンタ

MAC マネジメントカウンタ (MMC)は、受信および送信フレームに関する統計収集のためレジスタのセットです。レジスタは、レジスタの動作をコントロールするためのコントロールレジスタ、収集された割込みを表示する3つの32ビットレジスタ、割込みをマスクする3つの32ビットレジスタおよび統計カウンタレジスタで構成されています。

### ■ MMC の動作

MMC モジュール内のレジスタは AHB スレーブ・インターフェースを通じてアプリケーションからアクセスできます。各レジスタは、32ビット幅です。ワードアクセス(32ビット幅)のアクセスのみが許容されます。それぞれの統計カウンタの機能(カウントする内容)を「4.48. MMC Register list の Table 4-5 MMC レジスタマップ」にて、説明しています。

受信 MMC カウンタは、Address Filter (AFM) ブロックによってフレームが渡されたときに更新されます。AFM モジュールによって破棄されたフレームの統計は、それらのフレームが 6 バイト未満の小さなフレーム(DA バイトが完全には受信されない)でない限り更新されません。受信 IPC カウンタは、送信先アドレスフィルタを通過したフレームに対してのみ更新されます。受信 IPC カウンタは、受信 Ethernet フレーム内のカプセル化された IPv4, IPv6, TCP, UDP, または ICMP ペイロードに関する統計を収集します。

MMC コントロールレジスタにより、マネジメントカウンタのオペレーションモードを設定できます。カウンタが規定値に達するイベントにより、割込みを発生させることができます。MMC 受信割込みレジスタ, MMC 送信割込みレジスタ, MMC 受信チェックサムオフロード割込みレジスタにより、割込みの状態を確認できます。MMC 受信割込みマスクレジスタ, MMC 送信割込みマスクレジスタ, MMC 受信チェックサムオフロード割込みマスクレジスタにより、各割込みを個別にマスクできます。

MMC レジスタの命名規則は以下のとおりです。

- tx:送信に関連付けられたカウンタを示す接頭辞または接尾辞

- rx:受信に関連付けられたカウンタを示す接頭辞または接尾辞

- \_g:正常なフレームのみをカウントするレジスタを示す接尾辞

- \_gb:フレームが正常か不良かに関わりなくフレームをカウントするレジスタを示す接尾辞

送信が正常に完了した場合、送信されたフレームは「正常」と見なされます。つまり、以下のいずれかのエラーのためにフレーム送信が中止された場合以外は、送信フレームは正常なフレームです。

- Jabber Timeout

- No Carrier/Loss of Carrier

- Late Collision

- Frame Underflow

- Excessive Deferral

- Excessive Collision

受信フレームは、以下のどのエラーも存在しない場合、「正常な」フレームと見なされます。

- CRC error

- Runt Frame (64 バイト未満)

- Alignment error (10/100 Mbps のみ)

- Length error (Type フレーム以外)

- Out of Range (Type フレームのみ、最大サイズより長い)

- MII\_RXER Input error

最大フレームサイズは以下のようにフレームの種類により異なります。

- Untagged frame maxsize = 1518

- VLAN Frame maxsize = 1522

- Jumbo Frame maxsize = 9018

- JumboVLAN Frame maxsize = 9022

## 3.7. Station Management Agent

Station Management Agent (SMA) モジュールは、2 ワイヤ Station Management Interface を通じて任意の PHY レジスタにアクセスできるようにします。このインターフェースは、最大 32 個の PHY のアクセスをサポートします。アプリケーションは 32 個の PHY から 1 つの PHY と、その PHY 内の 32 個のレジスタから 1 つのレジスタを選択し、コントロールデータの送信、またはステータス情報の受信ができます。

### ■ 機能

マネジメント動作で使用する MDC クロック信号は、SYS\_CLK からの分周クロックです。分周比は GMAC Register 4 の MDC クロック範囲の設定で決定されます。SYS\_CLK の周波数に基づき、MDC クロックを Table 3-3 のように設定します。

Table 3-3 MDC の生成

| GMAC Register 4 の CR[3:0] | SYS_CLK           | MDC クロック    |

|---------------------------|-------------------|-------------|

| 0000                      | 60 MHz ~ 100 MHz  | SYS_CLK/42  |

| 0001                      | 100 MHz ~ 150 MHz | SYS_CLK/62  |

| 0010                      | 20 MHz ~ 35 MHz   | SYS_CLK/16  |

| 0011                      | 35 MHz ~ 60 MHz   | SYS_CLK/26  |

| 0100                      | 150 MHz ~ 250 MHz | SYS_CLK/102 |

| 0101                      | 250 MHz ~ 300 MHz | SYS_CLK/124 |

| 0110, 0111                | 予約                |             |

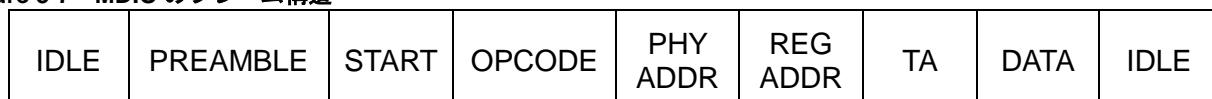

マネジメント動作の入出力データは、MDIO 信号に入出力されます。MDIO のフレーム構造を Figure 3-7 に示します。

Figure 3-7 MDIO のフレーム構造

- IDLE : Hi-Z 状態になります。 (MDC 上にクロックはありません)

- PREAMBLE : 32 ビットの連續した 1

- START : フレームの開始は 01

- OPCODE : 読出しでは 10, 書込みでは 01

- PHY ADDR : 32 個の PHY から 1 つを選択する 5 ビットアドレス

- REG ADDR : 選択した PHY 内のレジスタアドレス

- TA : 書込み時、Ethernet-MAC が 10 をドライブします。

: 読出し時、1 ビット目は Hi-Z 状態、2 ビット目は PHY が 0 をドライブします。

- DATA : 書込み時、Ethernet-MAC がライトデータをドライブします。

: 読出し時、PHY がリードデータをドライブします。

## ■ マネジメントライト動作

ユーザが GMII Write ビット(GW)および Busy ビット(GB)(「4.4. GMAC Register 4 (GAR)」を参照)をセットすると、SMA モジュールは、PHY アドレス、PHY 内のレジスタアドレス、およびライトデータを使用し、PHY レジスタへのライト動作を開始します。トランザクションの進行中にアプリケーションは GMII アドレスレジスタの内容および GMII データレジスタを変更できません。ライト動作が完了した後、Busy ビット(GB)がリセットされます。

SMA モジュールは、SYS\_CLK をプログラムされたクロック分周比(GMII アドレスレジスタの CR ビット)によって分周し、このインターフェースの MDC クロックを生成します。GMAC はフレームの持続時間全体にわたって MDIO ラインをドライブします。ライト動作のフレームフォーマットを Figure 3-8 に示します。

Figure 3-8 ライト時のフレームフォーマット

| IDLE | PREAMBLE  | START | OPCODE | PHY ADDR | REG ADDR | TA | DATA      | IDLE |

|------|-----------|-------|--------|----------|----------|----|-----------|------|

| Z    | 1111...11 | 01    | 01     | AAAAAA   | RRRRR    | 01 | DDD...DDD | Z    |

## ■ マネジメントリード動作

ユーザが GMII Busy ビット(GB)(「4.4. GMAC Register 4 (GAR)」を参照)をセットし、GMII Write ビットが 0 のとき、SMA モジュールは、PHY アドレスおよび PHY 内のレジスタアドレスを使用して、PHY レジスタのリード動作を開始します。トランザクションが進行中にアプリケーションは GMII アドレスレジスタの内容および GMII データレジスタを変更できません。リード動作が完了した後、Busy ビットがリセットされます。さらに、PHY から読み出されたデータによって GMII データレジスタが更新されます。リード時のフレームフォーマットを Figure 3-9 に示します。

Figure 3-9 リード時のフレームフォーマット

| IDLE | PREAMBLE  | START | OPCODE | PHY ADDR | REG ADDR | TA | DATA      | IDLE |

|------|-----------|-------|--------|----------|----------|----|-----------|------|

| Z    | 1111...11 | 01    | 10     | AAAAAA   | RRRRR    | Z0 | DDD...DDD | Z    |

## 3.8. IEEE1588

IEEE1588 機能について説明します。

### ■ IEEE1588 の概要

IEEE 1588 標準は、ネットワーク通信、ローカル・コンピューティング、分散オブジェクトなどの技術を活用する計測および制御システムにおけるクロックの正確な同期を可能にするプロトコルを定義しています。このプロトコルは、Ethernet またはそのほかの、マルチキャスト・メッセージングをサポートするローカルエリアネットワークによって通信するシステムに適用されます。このプロトコルは精度、分解能、安定性が異なる種々のクロックを含む異種システムの同期を可能にします。このプロトコルは、最小限のネットワークおよびローカルのクロック・コンピューティング・リソースを使って、システム全体にわたってマイクロ秒以下の同期精度をサポートします。

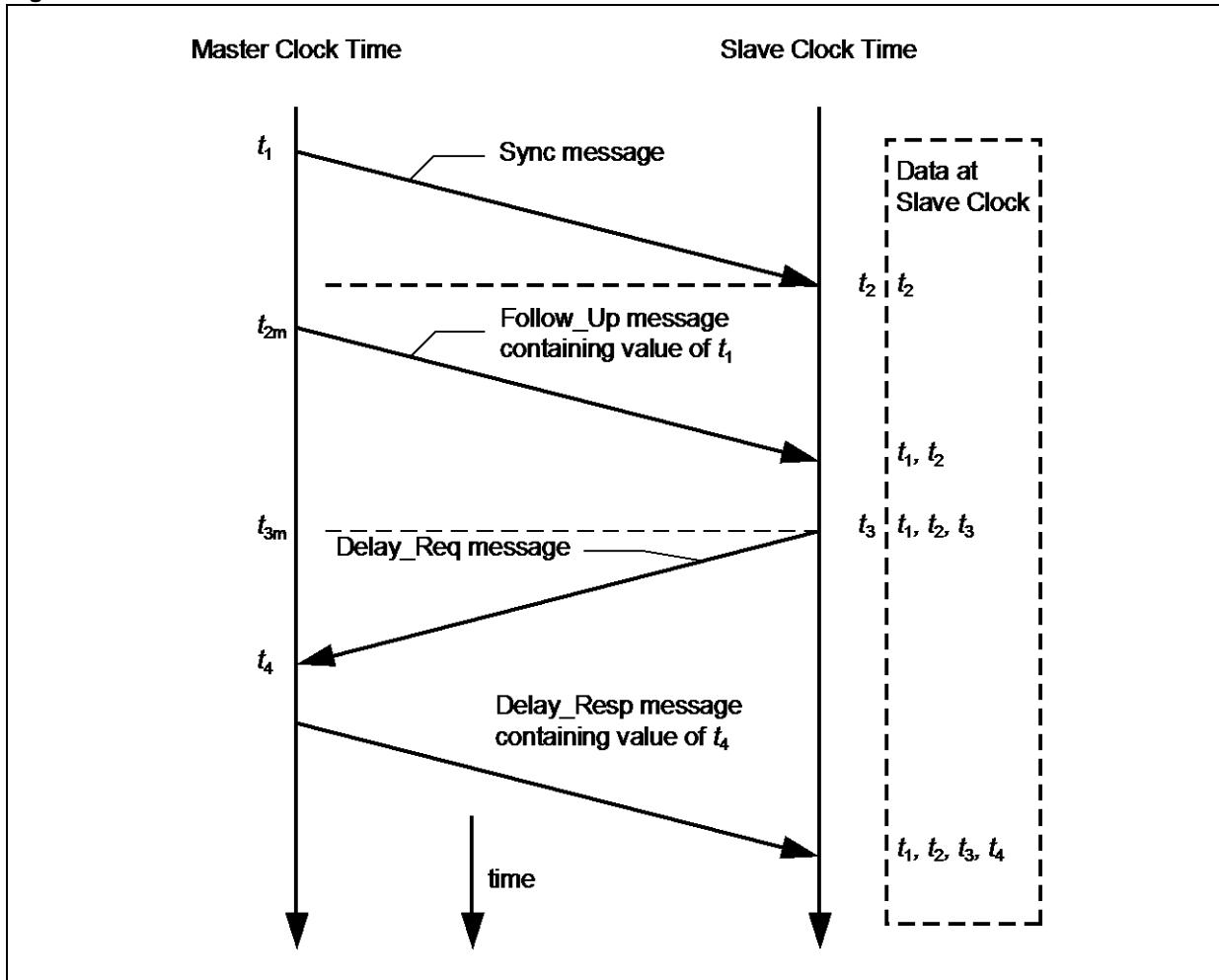

Precision Time Protocol (PTP) と呼ばれるメッセージベースのプロトコルが UDP/IP 上で転送されます。タイミング/クロック情報の分配においては、システムまたはネットワークはマスタノードとスレーブノードに分類されます。このプロトコルで PTP メッセージを交換することによってスレーブノードをマスタノードに同期する技術を Figure 3-10 に示しています。

Figure 3-10 ネットワークの時間同期

1. マスタは PTP Sync メッセージをすべてのノードにブロードキャストします。Sync メッセージにはマスタのリファレンス時間情報が含まれます。このメッセージがマスタのシステムを出る時刻は t1 で、これは Ethernet ポートのために PHY インタフェースでキャプチャされなければなりません。

2. スレーブは Sync メッセージを受信し、そのタイミングリファレンスを使って正確な時刻 t2 をキャプチャします。

3. 次にマスタはスレーブに t1 情報を含む Follow\_up メッセージを送信します(この情報は後で使用されます)。

4. スレーブはマスタに、このフレームが MII を出る正確な時刻 t3 を記載した Delay\_Req メッセージを送信します。

5. マスタはこのメッセージを受信し、それがシステムに入る正確な時刻 t4 をキャプチャします。

6. マスタは t4 情報を Delay\_Resp メッセージに入れてスレーブに送信します。

7. スレーブは t1, t2, t3, t4 の 4 つの値を使ってそのローカル・タイミングリファレンスをマスタのタイミングリファレンスに同期します。

プロトコルの実装の大部分はソフトウェアで、UDP の上のレイヤで行われます。しかし、上記のように、特定の PTP パケットが Ethernet ポートに入る、またはそのポートを出る正確な時刻をキャプチャするためにハードウェア・サポートが必要とされます。高精度の PTP を適切に実装するには、このタイミング情報がキャプチャされ、ソフトウェアへ返されなければなりません。

## ■ リファレンスタイミング・ソース

Ethernet-MAC は、リファレンスクロックを入力として、内部的にリファレンス時間(「システム時間」とも呼ばれます)を生成し、それを使ってタイムスタンプをキャプチャします。システム時間の生成、更新、変更については「■システム時間レジスタモジュール」を参照してください。

時間のナップショットを生成するために、64 ビット形式のリファレンスタイムを必要とします(2 つの 32 ビット・チャネルに分割され、上位 32 ビットが秒単位の時間、下位 32 ビットが ns 単位の時間を示します)。IEEE 1588-2008 標準は時間の上位フィールドを 48 ビット幅と定義しています。タイムスタンプのフィールドは下記のとおりです。

- UIInteger48-seconds フィールド

- UIInteger32-nanoseconds フィールド

"seconds" フィールドはタイムスタンプの整数部で、秒単位です。"nanoseconds" フィールドはタイムスタンプの小数部で、ns 単位です。例 : 2.000000001 秒は secondsField = 0x0000\_0000\_0002, nanoSeconds = 0x0000\_0001 で表されます。したがって、この形式での nanoseconds フィールドの最大値は 0x3B9A\_C9FF((10e9-1) ns) となります。これはデジタルロールオーバ動作モードとして定義されます。また、値 0x7FFF\_FFFF の後 nano-seconds フィールドがロールオーバし、seconds フィールドを増分するレガシーモードもサポートされます(精度は最大 0.466ns/ビット)。これはバイナリ・ロールオーバ・モードとして定義されます。これらのモードは、Time Stamp Control レジスタ "TSDB: Time Stamp Digital or Binary rollover control" ビットを使ってコントロールされます。

Ethernet-MAC に保持される時間は 64 ビット幅です。なぜなら、seconds レジスタの上位 16 ビットへのオーバフローは、130 年に 1 回しか発生しないからです。seconds フィールドの上位 16 ビットの値は GMAC レジスタからのみ取得できます。32 ビットの "seconds" フィールドでオーバフローが発生したときにそれを知らせるステータスピットが提供されています。

また、1 秒のインターバル(デフォルト)を示すために pulse-per-second 出力も供給されます。インターバルを変更するオプションも提供されています。詳細については「4.30. GMAC Register 459 (PPSCR)」を参照してください。

## ■ 送信パス機能

フレームの SFD が PHY インタフェースに出力されたときに、タイムスタンプがキャプチャされます。フレー

ムのタイムスタンプをキャプチャする必要があるか否かはフレームごとに制御可能です。つまり、各送信フレームにタイムスタンプをキャプチャする必要があるか否かを示すマークを付けることができます。

PTP フレームを識別するための処理は実行されません。フレーム単位のコントロールは、送信ディスクリプタのコントロールビットを通じて実行されます。

キャプチャされたタイムスタンプは、フレームのステータスが供給されるのと同様の方法で、アプリケーションに返されます。タイムスタンプとフレームの送信ステータスが供給されます。タイムスタンプは対応する送信ディスクリプタによってソフトウェアに返され、それによってタイムスタンプが自動的に特定の PTP フレームにコネクトされます。64 ビットのタイムスタンプ情報が TDES6 および TDES7 フィールドに書き戻され、TDES6 がタイムスタンプの下位 32 ビットを保持します。

## ■ 受信パス機能

Ethernet-MAC は、対応する受信ディスクリプタによってタイムスタンプをソフトウェアに返します。64 ビットのタイムスタンプ情報が RDES6 および RDES7 フィールドに書き戻され、RDES6 がタイムスタンプの下位 32 ビットを保持します。タイムスタンプは、Last Descriptor ステータスフィールドが 1 (EOF マーク) にセットされている受信ディスクリプタにのみ書き込まれます。タイムスタンプが生成できない場合(例えば、受信 FIFO オーバフローのため)、ディスクリプタ(RDES6 および RDES7)には"オール 1"パターンが書き込まれ、タイムスタンプが正しくないことを示します。ソフトウェアがコントロールレジスタ・ビットを使ってタイムスタンプをディセーブルしている場合、DMA は RDES6 および RDES7 を変更しません。

## ■ タイムスタンプ・エラー・マージン

IEEE 1588 仕様によると、タイムスタンプは PHY インタフェースで送信および受信フレームの SFD でキャプチャされなければなりません。リファレンスタイミング・ソースが PHY インタフェースのクロックと異なるため、非同期クロックドメイン間の情報転送によって小さなエラー・マージンが発生します。

送信パスではキャプチャおよびレポートされるタイムスタンプの最大エラー・マージンは 2 PTP クロックです。つまり、キャプチャされるタイムスタンプには、PHY インタフェース上で SFD が送信されてから 2 クロック以内のリファレンスタイム・ソースの値が与えられます。同様に、受信パスでは、エラー・マージンは 3 PHY インタフェースクロックと最大 2 PTP クロックの和となります。SFD データが PHY インタフェースに到達する前に 3 PHY インタフェースクロックに起因するエラー・マージンがシステム(またはリンク)に存在していたと想定すれば、この固定の遅延は無視できます。

## ■ リファレンスタイミングクロックの周波数範囲

クロックドメイン間のタイムスタンプ情報の転送には非同期ロジックが関係するため、2 つの連続するタイムスタンプ・キャプチャの間に最小限の遅延が必要とされます。この遅延は PHY インタフェースおよび PTP クロックの両方の 3 クロックサイクルです。間隔がこれより短いと、Ethernet-MAC は 2 番目のフレームのタイムスタンプスナップショットを生成しません。

最大 PTP クロック周波数は、リファレンスタイムの最大分解能(1GHz では 1ns)と PTP クロック上で動作するロジックで利用できるタイミング抑制によって制限されます。考慮すべきもう 1 つの要因は、リファレンスタイム・ソースの分解能(または「粒度」)が同期の精度を決定するということです。そのため、PTP クロックの周波数を高くするとシステムパフォーマンスが向上します。最小 PTP クロック周波数は 2 つの連続する SFD バイトの間で要求される時間に依存します。PHY インタフェースクロック周波数は IEEE 仕様によって固定されるため、適切な動作のために要求される最小 PTP クロック周波数は Ethernet-MAC の動作モードおよび動作速度に依存します。100 Mbps 全二重動作では 2 つの SFD の間の最小間隔は 160 PHY インタフェースクロックです。(64 バイト・フレームのための 128 クロックと、最小 IFG のための 24 クロック、およびプリアンブルのための 8 クロック) この例では、 $(3 \times \text{PTP}) + (3 \times \text{PHY}) \leq 160 \times \text{PHY}$  です。したがって、最小 PTP クロック周波数は約 0.5MHz ( $(160 - 3) \times 40\text{ns} \div 3 = 2093\text{ns}$ ) です。

## ■ システム時間レジスタモジュール

64 ビットの時間はこのモジュールに保持され、入力リファレンスクロック(PTP\_CLK)(注 : FM3 ファミリ マイ

この Ethernet-MAC は、入力リファレンスクロック(PTP\_CLK)に AHB のシステムバスロック : HCLK が接続されています。)を使って更新されます。この時間は送信または受信している Ethernet フレームのスナップショット(タイムスタンプ)を生成するためのソースとなります。

System Time カウンタは、Coarse correction(粗修正)方法を使って初期化または修正できます。この方法では、初期値またはオフセット値が Time Stamp Update レジスタに書き込まれます。初期化の場合は System Time カウンタに Time Stamp Update レジスタの値が書き込まれ、システム時間修正の場合はシステム時間にオフセット値が加算または減算されます。

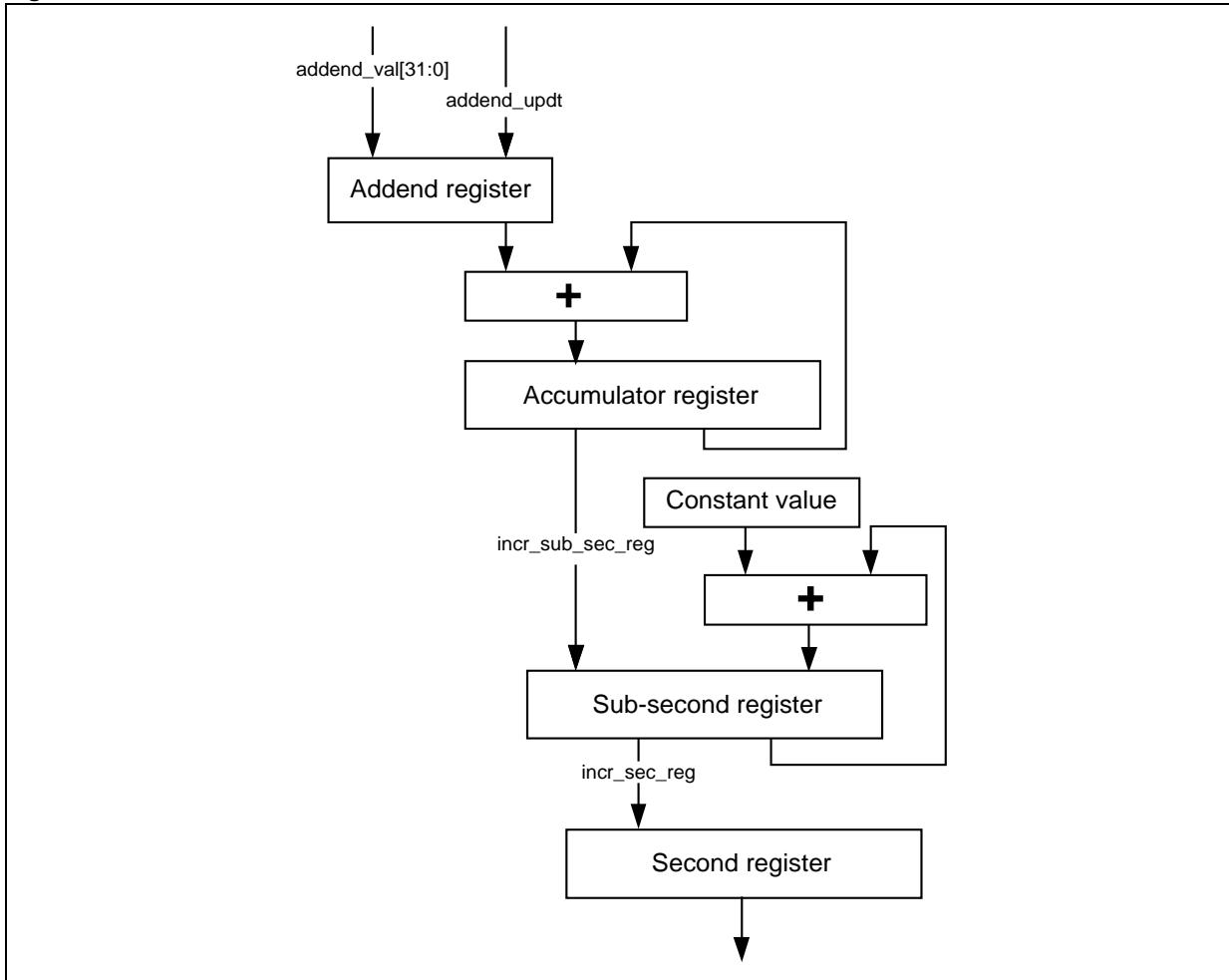

Fine correction(微修正)方法では、スレーブクロック(PTP\_CLK)のマスタクロックに対する周波数ドリフト(IEEE 1588 で定義されています)が、粗修正の場合のように 1 クロック内ではなく一定時間の間に修正されます。これは直線的な時間を維持するのに役立ち、PTP Sync メッセージ間隔間でリファレンス時間が大幅に変動する(ジッタを大きくする)ことはありません。このメソッドでは、アキュムレータは Figure 3-11 に示すように Addend レジスタの内容を集計します。アキュムレータが生成する算術的繰上げがシステムタイムカウンタを増分するためのパルスとして使われます。アキュムレータと Addend は 32 ビットレジスタです。したがって、アキュム

レータは高精度周波数乗算器または除算器として動作します。このアルゴリズムを Figure 3-11 に示します。

**Figure 3-11 微修正メソッドによるシステム時間の更新**

System Time Update ロジックは 20ns の精度を実現するために 50 MHz のクロック周波数を必要とします。周波数

分割はリファレンスクロック周波数の、要求されるクロック周波数に対する比です。したがって、例えばリファレンスクロック(PTP\_CLK)が 66 MHz のとき、この比は  $66\text{MHz}/50\text{MHz} = 1.32$  となります。その結果、レジスタでセットするデフォルトの Addend 値は  $2^{32}/1.32$  または 0xC1F07C1F です。

リファレンスクロックが低い値にドリフトする場合、例えば 65 MHz の場合、この比は  $65 / 50$ 、つまり 1.3 となり、Addend レジスタで設定される値は  $2^{32}/1.30$  または 0xC4EC4EC4 です。クロックが高い値にドリフトする場合、例えば 67 MHz の場合、Addend レジスタは 0xBF0B7672 にセットされなければなりません。クロックのドリフトが 0 である場合、デフォルトの Addend の値 0xC1F07C1F ( $2^{32}/1.32$ ) をプログラムしなければなりません。

ソフトウェアは、Sync メッセージを元にして周波数のドリフトを計算し、それに基づいて Addend レジスタを更新しなければなりません。

最初に、スレーブクロックは、Addend レジスタに FreqCompensationValue0 をセットします。この値は以下のとおりです。

$$\text{FreqCompensationValue0} = 2^{32} / \text{FreqDivisionRatio}$$

最初は、MasterToSlaveDelay が後続の Sync メッセージと同じであると想定し、下記のアルゴリズムを適用しなければなりません。いくつかの Sync サイクルの後に、周波数がロックします。このとき、スレーブクロックは正確な MasterToSlaveDelay 値を決定し、新しい値を使ってマスタと再同期できます。

このアルゴリズムは以下のとおりです。

- MasterSyncTimen の時刻にマスタはスレーブクロックに Sync メッセージを送信します。スレーブは、そのローカルクロックが SlaveClockTimen のときにこのメッセージを受信し、次のように MasterClockTimen を計算します。

$$\text{MasterClockTimen} = \text{MasterSyncTimen} + \text{MasterToSlaveDelay}$$

- マスタクロックは現在の Sync サイクルをカウントします。MasterClockCountn は次の式によって求められます。

$$\text{MasterClockCountn} = \text{MasterClockTimen} - \text{MasterClockTimenn-1} \quad (\text{Sync サイクル } n \text{ と } n - 1 \text{ で MasterToSlaveDelay が同じと想定します})$$

- スレーブクロックは現在の Sync サイクルをカウントします。SlaveClockCountn は次のように求められます。

$$\text{SlaveClockCountn} = \text{SlaveClockTimen} - \text{SlaveClockTimenn-1}$$

- 現在の Sync サイクルのマスタとスレーブのクロック・カウントの差 (ClockDiffCountn) は次の式によって求められます。

$$\text{ClockDiffCountn} = \text{MasterClockCountn} - \text{SlaveClockCountn}$$

- スレーブクロックの周波数スケーリング係数 (FreqScaleFactorn) は次の式によって求められます。

$$\text{FreqScaleFactorn} = (\text{MasterClockCountn} + \text{ClockDiffCountn}) / \text{SlaveClockCountn}$$

- Addend レジスタの周波数補正值 (FreqCompensationValuen) は次の式によって求められます。

$$\text{FreqCompensationValuen} = \text{FreqScaleFactorn} * \text{FreqCompensationValuen} - 1$$

理論的には、このアルゴリズムによって 1 つの Sync サイクルでロックが得られますが、ネットワーク伝搬遅延や動作条件の変動のために、いくつかのサイクルを必要とする場合があります。

このアルゴリズムは自動修正型です。何らかの理由でスレーブクロックの初期値が間違ったマスタからの値にセットされている場合、このアルゴリズムは、さらにいくつかの Sync サイクルを使ってそれを修正します。

## ■ PTP の処理およびコントロール

PTP メッセージの共通メッセージヘッダを Table 3-4 に示しています。この形式は IEEE 標準 1588-2008 に準拠しています。

Table 3-4 IEEE 1588-2008 で定義されているメッセージ形式

| ビット               |                    | オクテット | オフセット |

|-------------------|--------------------|-------|-------|

| transportSpecific | messageType        | 1     | 0     |

| 予約                | versionPTP         | 1     | 1     |

|                   | messageLength      | 2     | 2     |

|                   | domainNumber       | 1     | 4     |

| 予約                |                    | 1     | 5     |

|                   | flagField          | 2     | 6     |

|                   | correctionField    | 8     | 8     |

| 予約                |                    | 4     | 16    |

|                   | sourcePortIdentity | 10    | 20    |

|                   | sequenceId         | 2     | 30    |

|                   | messageType field  | 1     | 32    |

|                   | logMessageInterva  | 1     | 33    |

PTP フレームの一部のフィールドは、タイプを検出し、生成するスナップショットをコントロールするために使用されます。これは Ethernet 上で直接に送信される PTP フレーム、UDP / IPv4 上で送信される PTP フレーム、UDP / IPv6 上で送信される PTP フレームで異なります。「IPv4 上の PTP フレーム」では、スナップショットの生成をコントロールするために使用するフィールドに関する情報を示します。

## ■ IPv4 上の PTP フレーム

Table 3-5 は、IEEE 1588 version 1 および 2 に対応する UDP over IPv4 上で送信される PTP パケットのスナップショットをコントロールするために照合されるフィールドに関する情報を示しています。タグ・フレームのオクテット位置のオフセットは 4 です。これは IEEE 1588-2008 標準の Annex D および Table 3-4 で定義されているメッセージ形式をベースとしています。

Table 3-5 コントロールとステータスのために要求される IPv4-UDP PTP フレームのフィールド

| 対応するフィールド                                  | オクテット位置        | 対応する値                                                                       | 説明                                                                                                                                                                                                    |

|--------------------------------------------|----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|