## Version 1.0, September 2001

# **Design Note**

**DN-SMPS Singlestage**

## **Cool**SET<sup>™</sup>

Design of 30W Off-Line SMPS using CoolSET ICE2B265

Authors: Yew Ming Lik

**Junyang Luo**

**Meng Kiat Jeoh**

Published by Infineon Technologies AG http://www.infineon.com

# **Power Management & Supply**

## **Contents:**

| 1. Introduction                                                               | 3  |

|-------------------------------------------------------------------------------|----|

| 2. BLOCK DIAGRAM                                                              | 3  |

| 3. POWER MANAGEMENT.                                                          | 4  |

| 4. Start-up delay                                                             | 4  |

| 5. IMPROVED CURRENT MODE.                                                     | 5  |

| 6. Soft-Start                                                                 | 6  |

| 7. OSCILLATOR AND FREQUENCY REDUCTION                                         | 7  |

| 8. Current Limiting                                                           | 8  |

| 9. Leading Edge Blanking                                                      | 8  |

| 10. Propagation Delay Compensation                                            | 8  |

| 11. Protection Unit                                                           | 9  |

| 12. OVERLOAD + OPEN LOOP WITH NORMAL LOAD AND AUTO RESTART MODE               | 9  |

| 13. OVERVOLTAGE DUE TO OPEN LOOP WITH NO LOAD                                 | 10 |

| 14. 30W DEMO POWER SUPPLY BOARD                                               | 11 |

| 15. DESIGN OF THE POWER SUPPLY                                                | 12 |

| 15.1. Determine input capacitor $C_3$ and minimum DC input voltage $V_{IMIN}$ | 12 |

| 15.2 Transformer Calculation                                                  | 12 |

| 15.3 Current Sense Resistor                                                   | 15 |

| 15.4 Soft-start capacitor C <sub>7</sub>                                      | 15 |

| 15.5 Capacitor at V <sub>CC</sub> C <sub>6</sub>                              | 15 |

| 15.6 Start-up Resistor $R_2$ and $R_3$                                        | 16 |

| 15.6 Control Loop Design                                                      | 16 |

| 16. Summary                                                                   | 18 |

| References                                                                    | 20 |

Yew ming lik, Junyang Luo and Meng Kiat Jeoh

Infineon Technologies Asia Pacific Pte. Ltd. 168 Kallang Way, Singapore 349253

Email: minglik.Yew@infineon.com, Junyang.Luo@infineon.com,

MengKiat.Jeoh@infineon.com

#### 1. Introduction

The CoolSET ICE2B265 is an integrated pulse width modulator with built in CoolMOS. It is an inexpensive controller combined with the CoolMOS power switch with which designers can obtain all the stringent requirements imposed on the present modern Switched Mode Power Supply (SMPS) like very low standby power, few external components count and minimized PCB size. This application note provides beside functional description of the ICE2B265, it presents also the design of simple low cost and high efficient 30W Flyback SMPS circuit.

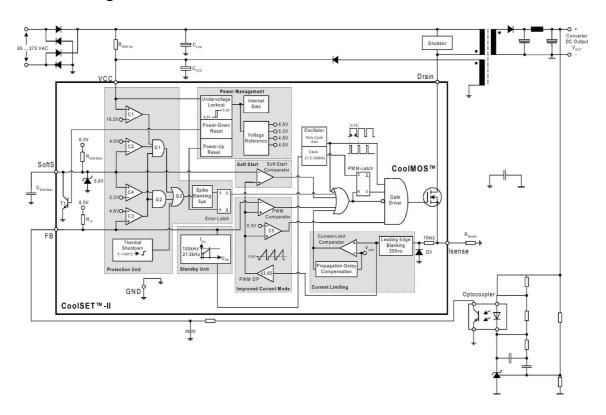

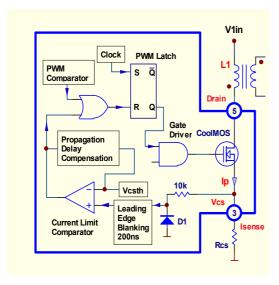

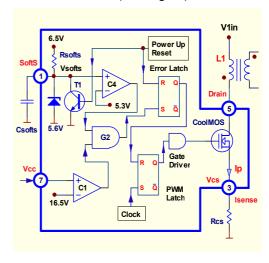

### 2. Block Diagram

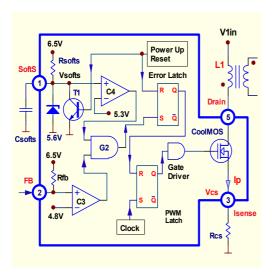

Fig.1. Block diagram of ICE2B265P

The control section of the CoolSET provides several special enhancements to satisfy the needs for low power standby and protection features. It consists of 5 main units, the Power Management, the

Softstart, the Improved Current Mode, the Current Limiting, the Standby and the Protection Unit. The Standby Unit enables the frequency reduction to lower the power consumption in standby mode. The

frequency reduction is limited to 21kHz to avoid audible noise. In case of failure modes like open loop, overvoltage or overload due to short circuit the device switches into Auto Restart Mode, which is control by the Protection Unit. With the patented Propagation Delay Compensation circuit integrated in the Current Limiting Unit, the peak current limitation can be controlled precisely. It leads to more cost efficient dimension of the transformer and the secondary diode.

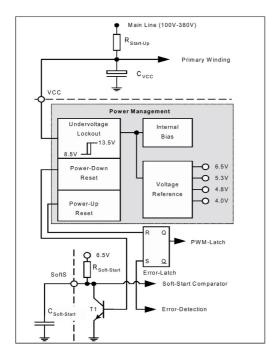

## 3. Power Management

Fig.2. Power Management Unit

Fig.2 shows the Power Management Unit of the IC. The external supply voltage  $V_{\rm CC}$  is monitored by the Undervoltage Lockout. The external capacitor  $C_{\rm VCC}$  is charged up by the current through the  $R_{\rm START-UP}$ , when the SMPS is plugged to the main line. The IC remains inactive before  $V_{\rm VCC}$  reaches the on-threshold  $V_{\rm CCON}$ =13.5V. The current consumption of the IC at this moment is max. 55uA. When the on-threshold is exceeded, the IC is activated:

- □ The internal bandgap generates a reference voltage V<sub>REF</sub>=6.5V to supply the internal circuit.

- The internal Error-latch in the protection unit is reset by the Power Up Reset. The Error-latch flip-flop is

- then ready to shut down the gate drive if the Protection Unit is activated.

- ☐ The soft-start transistor switch T₁ is released by the Power-Down Reset. The current through R<sub>SOFT-START</sub> starts to charge the external soft-start capacitor C<sub>SOFT-START</sub>. The soft-start is then activated.

To avoid uncontrolled ringing at switch-on a hystersis at the Undervoltage Lockout is implemented which means that switch-off is only after active mode when  $V_{\text{CC}}$  falls below 8.5V.

When  $V_{\text{CC}}$  falls below the off-threshold  $V_{\text{CCOFF}}$ =8.5V the internal reference is switched off and the Power Down Reset let the transistor switch T1 to discharge the soft-start capacitor  $C_{\text{SOFT-START.}}$  Thus it is ensured that the soft-start is always activated at every switch-on.

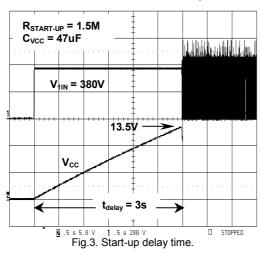

## 4. Start-up delay

During startup,  $C_{VCC}$  is charged by the current through  $R_{START-UP}$ . The IC is activated only when the  $V_{CC}$  reaches the on-threshold of  $V_{CCON}$ =13.5V. Because of the very low IC current consumption before activation, high value startup resistor can be used to minimize power loss in start-up resistor. The value of  $R_{START-UP}$  and  $C_{VCC}$  will effect the startup delay time, which can be estimated by using equation as follow:

$$t_{delay} = \frac{C_{VCC} \times V_{CCON}}{\frac{V_{1lN}}{R_{START-UP}} - I_{VCC1}}$$

(1)

t<sub>delay</sub> is the duration of the startup time from the moment the SMPS is plugged to the main line until the IC is activated. V<sub>1IN</sub> is the rectified line input voltage and I<sub>VCC1</sub> is the current consumption of the IC before activation. Fig.3 shows the t<sub>start delay</sub> of the actual SMPS with  $R_{START-UP} = 2 \times 470 k\Omega$ ,  $C_{VCC}$ =47 $\mu F$  and  $V_{1IN}$  =380V. (1) indicates that the start-up delay time depends not only on the main input voltage but also mainly on the value of  $R_{START-UP}$  and  $C_{VCC}$ . The t<sub>delay</sub> can be shorten by reducing the  $R_{\mbox{\scriptsize START-UP}}$  value. However, the loss at R<sub>START-UP</sub> will increase. It has to be compromised between shorter startup delay time and loss at startup resistor.

Startup circuit with transistor switch can be implemented to achieve startup without losses and constant shorter delay time.

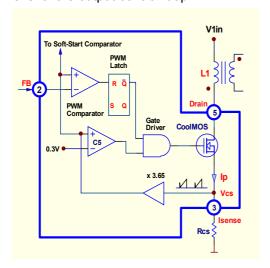

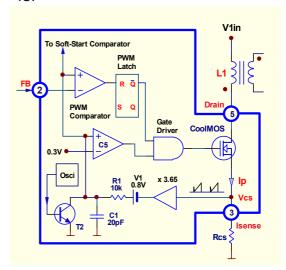

#### 5. Improved Current Mode

In Current Mode the primary current is sensed by the sense resistor  $R_{\rm CS}$  (Fig. 4). The sense voltage  $V_{\rm CS}$  is amplified 3.65 times for comparison with FB signal by the PWM Comparator. The current flow is terminated by resetting the PWM-Latch, when the sense voltage reaches the level of the FB signal, which is the program level of the output control loop.

Fig.4. Current Mode Control

Thus, the turn-on time of the power MOSFET as well as the peak primary current is well defined by the level of the FB signal. For flyback converter with discontinuous current operation the power stored in the primary inductor is represented by the equation

$$P = \frac{1}{2} \times L \times f \times i_{P}^{2}$$

(2)

Where P is the power stored in the primary inductor, L is the primary inductor, f is the swiching frequency and  $I_P$  is the peak primary current.

As can be seen, the line-input voltage does not appear in (2). One of the advantages of the Current Mode is that the line variation does not influence the regulation of the output voltage. However, the Current Mode is extremely susceptible to noise on the sense voltage. A noise spike is generated each time the power Mosfet switch is turned on which might turn off the driver immediately especially when the power is small and the FB signal is low.

To improve the Current Mode during light load, a voltage ramp is implemented in the IC.

Fig.5. Improved Current Mode

The amplified current sense voltage  $v_{CS}$  is superimposed on the voltage ramp, which is built by the switch  $T_2$ , the voltage source  $V_1$  and  $1^{st}$  order low pass filter composed of  $R_1$  and  $C_1$  (see Fig.5).

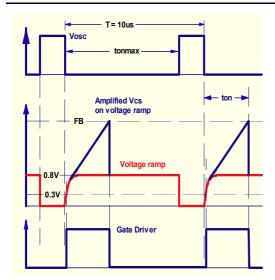

Fig.6. Normal Load Condition

Fig.6 shows the effect of the Voltage Ramp in normal load condition. The switch  $T_2$  is opened at the falling slope of the oscillator. It enables the Voltage Ramp to rise. The Gate Driver turns on the power MOSFET when the Voltage Ramp reaches 0.3V. The primary current starts to flow and is sensed by  $R_{CS}$ . The current sense voltage  $V_{CS}$  is amplified 3.65 times by the PWM OP, which is then superimposed on the Voltage Ramp. The current flow is terminated when the amplified sense voltage on the Voltage Ramp reaches the FB voltage level.

In case of light load (see Fig.7) or no load, the current sense voltage  $V_{\text{CS}}$  is so small that only the Voltage Ramp remains as a well defined signal for the comparison with the FB-signal.

Fig.7. Light Load Conditions

The slope of the Voltage Ramp then controls the turn-on time of the Gate

Driver. The Gate Driver is turned on only when the Voltage Ramp exceeds 0.3V due to the Comparator  $C_5$ . The turn-on time can then be continuously reduced to zero by decreasing  $V_{\text{FB}}$  below that threshold.

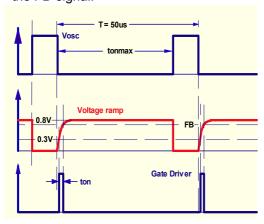

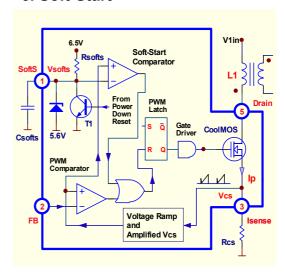

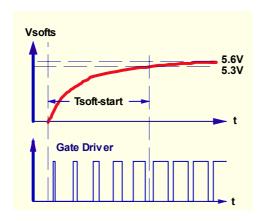

#### 6. Soft-Start

Fig.8. Soft-Start

The Soft-Start voltage  $V_{SOFTS}$  is generated by charging the external capacitor  $C_{SOFTS}$  through the internal pullup resistor  $R_{SOFTS}$  (see Fig.8). The Soft-Start comparator compares the Soft-Start voltage  $V_{SOFTS}$  at the negative input with the ramp voltage of the superimposed Voltage Ramp at the positive input. In Soft-Start phase  $V_{SOFTS}$  is always smaller than the Feedback Voltage  $V_{FB}$ . In this case  $V_{SOFTS}$  defines the pulse width of the Gate Driver through the Soft-Start Comparator by resetting the PWM-Latch. The Soft-Start phase is completed when  $V_{SOFTS}$  reaches 5.3V (Fig.9). The Soft-Start time is then defined by

$$T_{SOFT-START} = 1.69 \times R_{SOFTS} \times C_{SOFTS}$$

(3)

The transistor switch  $T_1$  at Soft-Start is controlled by the Power Down Reset. It is to ensure that the Soft-Start is always activated at the restart of the IC after power down or in Auto Restart mode.

Fig.9. Soft-Start Phase

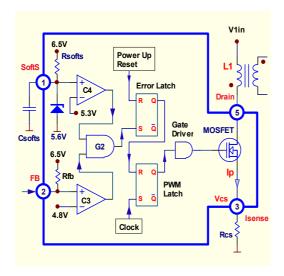

The Soft-Start voltage  $V_{\text{SOFTS}}$  is used not only for minimization of current and voltage stresses on the external power MOSFET switch during start-up, it is also used for activation of the Protection Unit (Fig.10).

Fig.10. Activation of Protection Unit

When the Soft-Start phase is over ( $V_{SOFTS} > 5.3V$ ), the Error Latch will be activated by Comparator  $C_4$  if the feedback voltage  $V_{FB}$  does not drop below 4.8V, which means that the output voltage  $V_{OUT}$  at the secondary side of the SMPS does not reaches its nominal level. To ensure proper start-up of the SMPS, the duration of the Soft-Start phase has to be long enough to enable  $V_{OUT}$  to rise to its nominal value. This will cause the control

loop to pull down the level of the feedback signal V<sub>FR</sub> below 4.8V (see Fig.11).

Fig.11. Start-up Phase

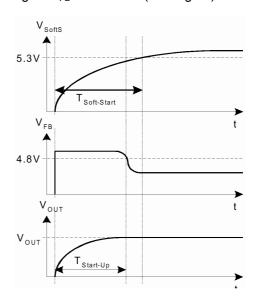

# 7. Oscillator and Frequency Reduction

The oscillator, which generates the switching frequency F=67kHz, is integrated in the IC. The oscillator is adjusted so that the Gate driver pulse can reach a maximum duty cycle of  $D_{MAX} = 0.72$ .

The frequency of the oscillator can be influenced by the feedback voltage  $V_{FB}$  as shown in Fig.12. This feature allows a SMPS to operate at lower frequency at light loads thus lowering the switching losses while maintaining good cross regulation performance and low output ripple. The power consumption of the whole SMPS can be reduced very effectively at light load. The minimal reachable frequency is limited to 20kHz to avoid audible noise in any case.

Fig.12. Frequency Reduction vs V<sub>FB</sub>

## 8. Current Limiting

Fig.13. Current Limiting

The cycle by cycle current limiting is performed by the Current Limit Comparator (see Fig.13). The primary current I<sub>P</sub> is converted into a sense voltage V<sub>CS</sub> by an external sense resistor R<sub>CS</sub>. The sense voltage  $V_{\text{CS}}$  goes through the 200ns Leading Edge Blanking before reaching the Current Limit Comparator. When V<sub>CS</sub> exceeds the internal threshold voltage V<sub>CSTH</sub>, the Current Limit Comparator immediately turns off the Gate Driver via the PWM Latch. A Propagation Delay Compensation is added to the Current Limiting circuit to avoid excessive primary overshoot of the current. especially at the high line voltage (refer to Propagation chapter 10 Delay Compensation).

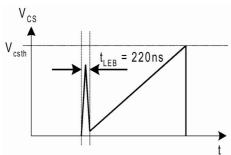

#### 9. Leading Edge Blanking

Fig.14. Leading Edge Blanking

Each time when the CoolMOS is switched on a leading spike is generated due to the

primary-side capacitance and secondary-side rectifier reverse recovery time (Fig. 14). This spike causes a premature turn-off of the Gate Driver if it exceeds the threshold voltage  $V_{\text{CSTH}}$ . To avoid it, the spike is blanked out with a time constant of  $t_{\text{LEB}}$  = 220ns. During the blanking time the Gate Driver can not be switched off by the Current Limit Comparator.

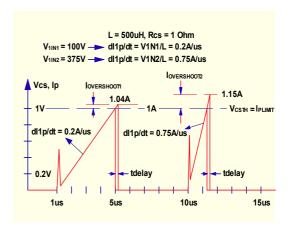

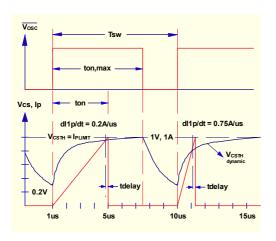

# 10. Propagation Delay Compensation

In case of overcurrent detection, that is when the sense voltage V<sub>CS</sub> reaches the threshold voltage of the Current Limit Comparator  $V_{\text{CSTH}}$ , the shut down of the internal CoolMOS is delayed due to the propagation delay of the circuit between the current sense input I<sub>SENSE</sub> and the Gate Driver output. This delay causes an overshoot of the peak primary current overshoot is  $I_{PPEAK}$ . The particularly at high input line voltage. Fig.15 shows an example of different current overshoots at two different line voltages. The example assumes that the primary inductance is 500µH, the current sense resistor  $R_{SENSE}$ =1 $\Omega$ , the propagation delay time t<sub>PROP DELAY</sub>=200ns and the input line voltages after rectification are V<sub>1IN1</sub>= 100V and  $V_{1IN2} = 370V$ .

Fig.15. Current overshoot

The result of the example obviously shows that if the current sense threshold  $V_{CSTH}$  is set at a constant level  $V_{CSTH} = 1V$ , the current overshoot  $I_{OVERSHOOT2}$  at high line input voltage of  $V_{IN2} = 375V$  and at  $t_{DELAY} = 200$ ns is 15% higher than the actual current limit  $I_{PLIMIT}$ .

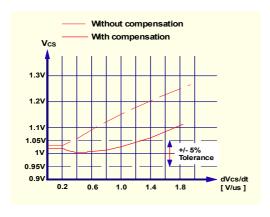

The Propagation Delay Compensation which is done by means of a dynamic volatge threhold  $V_{\text{CSTH}}$  as shown in Fig.16 is integrated in the IC to minimize the overshoot.

Fig.16. Dynamic Voltage Threshold V<sub>CSTH</sub>

At high line input voltage, when the slope of the current sense voltage  $V_{CS}$  is steeper, the Gate Driver is switched off earlier due to the lower  $V_{CSTH}$ . The effect of the overshoot is then compensated.

The Propagation Delay Compensation in the IC is designed so that the tolerance of the internal current limiting is at +/- 5%. The propagation delay time is compensated over temperature within a range of at least

$$0 \le R_{CS} \times \frac{dI_P}{dt} \le 1 \frac{dV_{CS}}{dt}$$

(4)

In this way, the IC is able to accurately limit the overcurrent (see Fig.17).

Fig.17. Overcurrent Shutdown

#### 11. Protection Unit

An overload, open loop, overvoltage detection and a thermal shutdown are integrated within the Protection Unit (see Fig.1, Block Diagram). If the Protection Unit is activated, the Error Latch is set that disables the external power MOSFET after a blanking time of  $5\mu s$ . The blanking is used to avoid mistriggering of the Error Latch by voltage spikes during normal operation mode.

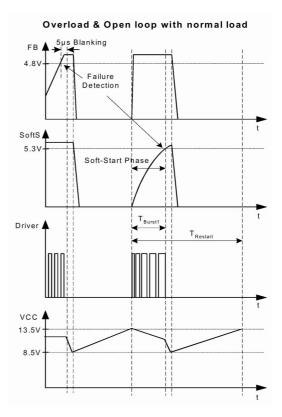

# 12. Overload + Open Loop with normal load and Auto Restart Mode

Fig.18. Auto Restart Mode

Fig.18 shows the Auto Restart Mode in case of overload or open loop with normal load. The detection of open loop or overload is provided by the Comparator C3, C4 and the AND-gate G2 (see Fig.19).

During operation at normal load the supply voltage of the IC  $V_{CC}$  is in the range of

8.5V and 13.5V, the Soft-Start voltage  $V_{\text{SOFTS}}$  is above 5.3V and the

Fig.19. FB-Detection

feedback voltage V<sub>FB</sub> stays lower than 4.8V. At this time the Comparator C<sub>4</sub> has released one of the input of the AND-gate G<sub>2</sub>. The comparator C<sub>3</sub> is now able to set the Error-Latch in case of open loop or overload, which leads the feedback voltage  $V_{FB}$  to rise above 4.8V. 5 $\mu$ s after the V<sub>FB</sub> reaches the threshold voltage of 4.8V, the Gate Driver is terminated. The SMPS stops to operate which causes the supply voltage of the IC V<sub>CC</sub> to drop. The IC is turned off when  $V_{CC}$  falls to  $V_{CCoff}$  = 8.5V. At this time the external soft-start capacitor  $C_{\text{SOFTS}}$  is discharged by the internal switch T<sub>1</sub> due to the Power Down Reset and the consumption current of the IC is reduced to maximum 55μA. The SMPS then goes into Auto Restart Mode. The V<sub>CC</sub> increases again by charging the capacitor C<sub>VCC</sub> through the Start-up Resistor R<sub>START-UP</sub> during the IC is inactive. When it reaches the turn-on threshold  $V_{CCon}$  =13.5V, the IC is turned on again. The Error Latch is then reset by the Power Up Reset and the internal pull-up resistor R<sub>SOFTS</sub> starts to charge the external Soft-Start capacitor C<sub>SOFTS</sub> to start the Soft-Start Phase. During Soft-Start Phase the detection of overload and open loop by C<sub>3</sub> and G<sub>2</sub> is disabled by the Comparator C<sub>4</sub>. The Soft-Start Phase ends with the Soft-Start voltage  $V_{SOFTS} \ge 5.3V$ . If the overload or open loop failure is not removed after the Soft-Start Phase, the Error Latch is activated and the SMPS goes into Auto Restart Mode again.

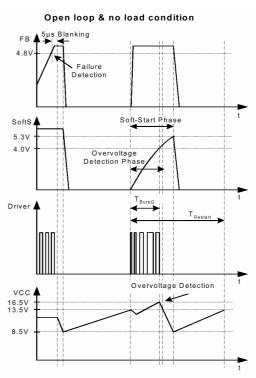

# 13. Overvoltage due to open loop with no load

Fig.20. Auto Restart Mode

Fig.20 shows the Auto Restart Mode for open loop and no load condition. In case of this failure mode the SMPS output voltage as well as the  $V_{CC}$  increases. Additional comparators  $C_1$ ,  $C_2$  and the AND-gate  $G_1$  are implemented to detect this failure mode (see Fig.21).

Fig.21. Overvoltage Detection

The overvotage detection is provided by Comparator C1 only when the Soft-Start voltage  $V_{\text{SOFTS}}$  is below the threshold of the Comparator  $C_2$  at 4.0V and the voltage at pin FB is above 4.8V. During this overvoltage detection phase Comparator C1 can set the Error Latch and terminates the Burst Phase earlier during Auto Restart Mode when  $V_{\text{CC}}$  exceeds 16.5V. Once the Soft-Start phase is over, which means that the  $V_{\text{SOFTS}}$  is above 4.0V, the overvoltage detection by  $C_1$  is disabled. This will enable the  $V_{\text{CC}}$  to vary in the range of 8.5V to 21V caused by output load changes at normal operating mode.

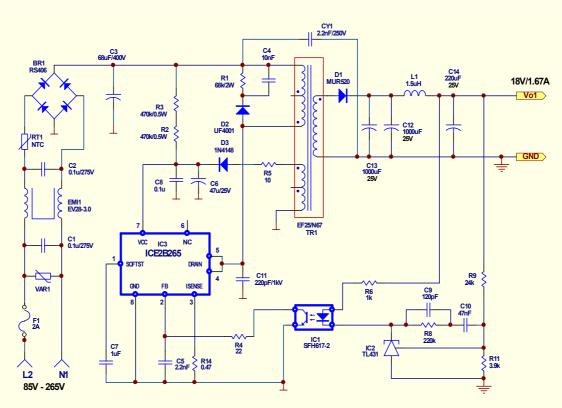

# 14. 30W Demo Power Supply Board

Fig.22 shows a very simple and low cost 30W switching power supply circuitry utilizing the ICE2B265P. It is designed for used as the power supply of a Digital Photo Printer.

#### The specification of the circuits:

#### Input voltage range

85 - 265 V<sub>AC</sub> 50/60Hz

#### **Output**

18V/1.67A

#### Maximum output power

P<sub>OMAX</sub> =30W

#### Input power at standby mode

$P_{\text{IN}} \le 0.5 \text{W}$  at  $P_{\text{O}}$  = 0W and  $V_{\text{IN}}$  = 240Vac

#### **Efficiency**

η ≥ 80%

Fig.22. 30W SMPS Demoboard using CoolSET ICE2B265 011005 - M.K.leoh

### 15. Design of the Power Supply

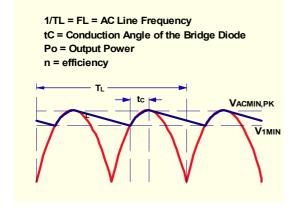

# 15.1. Determine input capacitor $C_3$ and minimum DC input voltage $V_{1MIN}$

To choose the value of the input capacitor  $C_5$  the following rule of thumb is applied:

$C_5$  = 2 to 3  $\mu F$  per W for 100/115V<sub>AC</sub> or universal input.

$C_5 = 1 \mu F$  per Watt for 230 $V_{AC}$ .

$C_5$  = 68uF is selected for this design. The minimum DC input voltage  $V_{1MIN}$  (see Fig.24) at the lowest line voltage of 85V is a very important parameter for the calculation of the transformer. It can be obtained with good approximation by the following equations:

$$V_{1MIN} = \sqrt{V_{ACMIN,PK}^2 - \frac{2 \times W_{IN}}{C_5}}$$

(5)

$V_{\text{ACMIN,PK}}$  is the minimum peak input voltage, whereas  $W_{\text{IN}}$  is the energy which is discharged out of  $C_5$ .

$$V_{ACMIN.PK} = V_{ACMIN} \times \sqrt{2}$$

(6)

The discharged energy  $W_{\text{IN}}$  is equivalent to the required peak output power  $P_{\text{OPK}}$  for the duration of the discharge time  $T_{\text{L}}/2-t_{\text{C}}$ .

$$W_{IN} = \frac{P_{OPK}}{n} \times (\frac{T_L}{2} - t_C)$$

(7)

Fig.23 Input Voltage Ripple

Assuming that the conduction time of the bridge rectifier diodes is about 3 ms and substitute the specified values in (5), (6) and (7), we obtain:

$$V_{ACMIN,PK} = 85V \times \sqrt{2} = 120V \tag{8}$$

$$W_{IN} = \frac{30W}{0.8} \times (\frac{20ms}{2} - 3ms)$$

(9)  $W_{IN} = 0.26Ws$

$$V_{1MIN} = \sqrt{(120V)^2 - \frac{2 \times 0.26Ws}{68uF}}$$

(10)  $V_{1MIN} = 82V$

Taking the voltage drop at the bridge rectifier into consideration, the  $V_{1MIN}$  should then be:

$V_{1MIN} = 80V.$

#### 15.2 Transformer Calculation

#### 15.2.1. Maximum Duty Cycle

The transformer is designed so that the SMPS is operated in discontinuous current mode for the whole operating range.

The maximum duty cycle  $d_{MAX}$  at minimum input voltage  $V_{1MIN}$  is chosen as

$$d_{MAX} = 0.5 \tag{11}$$

#### 15.2.2 Reflected Output Voltage

The reflected output voltage  $V_{\text{R}}$  is the reflected value of the secondary voltage across the primary winding. It can be obtained by the equation

$$V_{R} = \frac{d_{MAX}}{1 - d_{MAX}} \times (V_{1MIN} - V_{DS})$$

(12)

The Drain-Source voltage  $V_{DS}$  of the internal CoolMOS is negligible due to the smaller  $R_{DSON}$ .  $V_R$  is then:

$$V_{R} = \frac{0.5}{1 - 0.5} \times 80V = 80V \tag{13}$$

## 15.2.3 Maximum Primary Peak and RMS Current

The maximum primary peak current  $I_{1PKMAX}$  is propotional to the maximum output power. It can be derived as follow:

$$I_{1PKMAX} = \frac{2 \times P_{OMAX}}{\eta \times V_{1MIN} \times d_{MAX}}$$

(14)

Substitute the known values of  $P_{OMAX}$ ,  $V_{1MIN}$ ,  $d_{MAX}$  and the efficiency  $\eta$  into (14),  $I_{1PK}$  becomes:

$$I_{1PKMAX} = \frac{2 \times 30W}{0.8 \times 80V \times 0.5} = 1.875A$$

(15)

The maximum primary RMS current can be calculated from  $I_{1PK,MAX}$  and  $d_{MAX}$ :

$$I_{1RMS,MAX} = I_{1PK,MAX} \sqrt{\frac{d_{MAX}}{3}}$$

(16)

$$I_{IRMS,MAX} = 1.875 A \sqrt{\frac{0.5}{3}} = 0.77 A$$

(17)

#### 15.2.4 Primary Inductance L<sub>1</sub>

Primary inductance can be determined by the energy equation of the flyback transformer defined below:

$$L_1 = \frac{2P_{OMAX}}{\eta \, I_{IPK,MAX}^2 f} \tag{18}$$

f is the switching frequency of the SMPS which is around 67kHz.

$$L_1 = \frac{2 \times 30W}{0.8 \times 1.875^2 A \times 67 kHz} \approx 320 \mu H$$

(19)

#### 15.2.5 Number of Primary turns

For this design, core size of EF25 is recommended due to its low cost and easy availability. For 67kHz operation, Epcos N67 material is a good choice.

In the discontinuous current mode operation, at switching frequency of 67kHz, the maximum flux density in the core  $B_{MAX}$  is usually limited by the core loss. To keep the loss in the core at acceptable level (see Epcos datasheet,

N67 Core loss vs frequency),  $B_{MAX} = 0.2T$  is chosen for the calculation of the number of primary turns  $N_1$ .

$$N_1 = \frac{L_1 \times I_{1PK,MAX}}{B_{MAX} \times A_{MIN}}$$

(20)

$A_{MIN}$  is the minimum cross sectional area of the core. For EF25,  $A_{MIN}$  = 51.5mm<sup>2</sup>.

$$N_1 = \frac{320 \times 2}{0.2 \times 51.5} \approx 60 \tag{21}$$

The required core gap  $L_{\text{GAP}}$  to achieve the primary inductance  $L_1$  with the number of primary turns  $N_1$  can be calculated by using the equation given in Epcos data book for "Ferrites and Accessories"

$$L_{GAP} = \left(\frac{L_1}{N_1^2 \times K1}\right)^{\frac{1}{K2}}$$

(22)

K1 and K2 are the core-specific constants. For EF25, K1=90, K2=-0.731 are specified in the datasheet. In the calculation  $L_1/N_1^2$  has to be in the dimension of nH. The needed core air gap is then

$$L_{GAP} = \left(\frac{320 \times 10^{3}}{60^{2} \times 90}\right)^{\frac{1}{-0.731}} mm$$

$$L_{GAP} = 1.02mm$$

(23)

#### 15.2.6 Number of Secondary Turn

The number of turn for the secondary output can be derived from the reflected output voltage  $V_R$  in (13) and the number of primary turns  $N_1$ . During the flyback time all windings will have the same volt per turn  $V_T$ :

$$V_T = \frac{V_R}{N_1} = \frac{80V}{60 \text{ turns}} = 1.33 \frac{V}{\text{turn}}$$

(24)

The number of turns  $N_{\text{O1}}$  for 18V-output  $V_{\text{O1}}$  is then:

$$N_{O1} = \frac{V_{O1} + V_{D}}{V_{T}} \tag{25}$$

$V_{\text{D}}$  is the output diode forward voltage drop, which is typically about 1V.

$$N_{O1} = \frac{18+1}{1.33} \approx 14 \tag{26}$$

The bias voltage for the  $V_{\text{CC}}$  should be around 15V. The number of turn for the bias winding is then:

$$N_{BIAS} = \frac{V_{BIAS} + V_{D}}{V_{T}} = \frac{16}{1.33} \approx 12$$

(27)

#### 15.2.7 Output Rectifier Diodes

To select the proper output rectifier diode, the maximum peak inverse voltage across the diode  $V_{D1,PK}$  has to be defined.  $V_{D1,PK}$  can be obtained by the equation defined below:

$$V_{D1,PK} = V_{O1} + \left(\frac{N_{O1}}{N_1} \times V_{1MAX}\right)$$

(28)

whereas  $V_{1MAX}$  is the maximum DC input voltage. The calculation result is:

$$V_{D1,PK} = 18V + (\frac{14}{60} \times 375V)$$

The reverse voltage rating of the selected diode  $V_{DR}$  should be greater than 1.25x  $V_{DPK}$  and the rated DC current has to be at least 3 times the maximum output current. MUR520 is chosen for used in this design.

# 15.2.8 Maximum Secondary Peak and RMS Current

The maximum secondary peak and RMS currents are propotional to the maximum DC output current as follows:

$$I_{OPK,MAX} = \frac{2 I_{OMAX}}{1 - d_{MAX}}$$

(29)

$$I_{ORMS,MAX} = I_{OPK,MAX} \times \sqrt{\frac{1 - d_{MAX}}{3}}$$

(30)

$I_{\text{OMAX}}$  is the maximum DC output current,  $I_{\text{OPK,MAX}}$  is the maximum peak output current and  $I_{\text{ORMS,MAX}}$  is the maximum RMS

output current. The results of the calculation is listed in Table 1.

| Secondary | Max. Peak                     | Max. RMS                       |

|-----------|-------------------------------|--------------------------------|

| Output    | Current                       | Current                        |

| 18V/1.67A | I <sub>O1PK,MAX</sub> = 6.68A | I <sub>O1RMS,MAX</sub> = 2.73A |

Table 1. Max. Peak and RMS Output Current

#### 15.2.9. Output Capacitors

Output capacitor selection is dominated by the  $R_{\text{ESR}}$  (equivalent series resistance) and the ripple current rating of the capacitor. The ripple current, which flows through the output capacitor, can be calculated as follows:

$$I_{O,RIPPLE} = \sqrt{I_{ORMS,MAX}^2 - I_{OMAX}^2}$$

(31)

The ripple current in the output capacitor of the 18V/1.67A will then be:

$$I_{O1,RIPPLE} = \sqrt{2.73^2 - 1.67^2} A$$

$$I_{O1,RIPPLE} = 2.16A$$

(32)

The Epcos datasheet of her B41858-series aluminum electrolytic capacitor shows that the rms current rating of a  $1000\mu\text{F}/25\text{V}$  capacitor at 100kHz switching frequency and  $105^{\circ}\text{C}$  ambient is 1.69A.2 pieces of this capactors (Fig.22) have to be used to accommodate the required ripple current of  $V_{\text{O1}}$ . The  $R_{\text{ESR}}$  of these capacitors are specified as  $0.034\Omega$ . The output ripple voltage caused by the parallel of these two  $R_{\text{ESR}}$ , which is  $R_{\text{ESRTOT}} = 0.017\Omega$ , is then:

$$V_{O1,RP} = I_{O1PK,MAX} \times R_{ESRTOT}$$

$V_{O1,RP} = 6.68 A \times 0.017 \Omega = 0.11 V$  (36)

This switching ripple voltage is further reduced by the additional L-C filter ( $L_3$  and  $C_{14}$  in Fig.22). The 220 $\mu$ F/25V with  $R_{ESR}$  = 0.12 $\Omega$  is chosen for  $C_{14}$ . To eliminate the pole in the control loop caused by the  $L_1$ - $C_{14}$  filter,  $L_1$  has to be around 1.5 $\mu$ H. With this  $L_1$ - $C_{14}$  values combination,  $V_{O1,RP}$  is reduced to:

$$\dot{V_{O1,RP}} = V_{O1,RP} \times \frac{R_{ESR}}{2 \pi f L_4 + R_{ESR}}$$

$$= 0.11 \times \frac{0.12}{2 \pi 67 \times 1.5 \times 10^{-3} + 0.12} V$$

$$\approx 18 mV$$

(34)

The switching ripple voltage V'<sub>O1,RP</sub> appears at the output terminal has been attenuated to around 18mV.

#### 15.3 Current Sense Resistor

The current sense resistor ( $R_{14}$  in Fig.22) is defined by the maximum primary peak current and the minimum threshold voltage of the Current Limiting  $V_{\text{CSTHMIN}}$ .

$$R_{14} = \frac{V_{CSTHMIN}}{I_{1PK,MAX}} = \frac{0.95V}{2A} \approx 0.45\Omega \tag{35}$$

Since the maximum loss occurred in R<sub>14</sub> can be:

$$P_{R14MAX} = I_{IRMS,MAX}^2 R_{14}$$

$$P_{R14MAX} = 0.765^2 \times 0.45W = 0.26W$$

(36)

a 1W low inductance resistor is recommended.

#### 15.4 Soft-start capacitor C<sub>7</sub>

As mentioned in chapter 6 "Soft-Start" on page 4 and 5, the duration of the soft-start phase  $T_{\rm SOFT-START}$  has to be long enough to ensure proper start-up of the SMPS. That means  $V_{\rm O1}$  has to be at 18V before  $V_{\rm SOFTS}$  reaches 5.3V (see Fig.11 on page 5,  $T_{\rm SOFT-START} > T_{\rm START-UP}$ ).

To estimate the  $T_{\text{START-UP}}$ , the available power during the soft-start phase, which charges the output capacitors, has to be defined. The total value of all capacitors at the output is:

$$C'_{01} = C_{12} + C_{13} + C_{14} = 2220 \mu F$$

(37)

In case of hard-start (if soft-start does not exists), the power which will charge C'<sub>O1</sub> is:

$$\dot{P_{O1}} = \eta \times \frac{1}{2} \times L_1 \times f \times \left(\frac{V_{CSTHMIN}}{R_{14}}\right)^2$$

(38)

$$P'_{O1} = 0.8 \times \frac{1}{2} \times 320 \times 67 \times 10^{-3} \times \left(\frac{0.95}{0.45}\right)^2 W$$

$P'_{O1} = 38.2W$

Assuming that the charge-up power to the  $C'_{O1}$  rises linearly during the soft-start phase, the charge power is then only half of 38.2W.  $T_{START-UP}$ , which is needed to raise the voltage  $V_{O1}$  to 18V, can then be estimated:

$$T_{START-UP} = \frac{1}{2} x \frac{V_{O1}^2 \times C_{O1}^{'}}{0.5 P_{O1}^{'}}$$

(39)

$$T_{START-UP} = \frac{18^2 \times 2220}{38.2} \mu s \approx 18.8 ms$$

In the application circuit of Fig.22, the external soft-start capacitor  $C_7$  =  $1\mu F$  is recommended. The internal soft-start resistor  $R_{SOFTS}$  =  $50k\Omega$  is specified on the datasheet of the IC. The soft-start time  $T_{SOFT-START}$  can then be calculated using (3):

$$T_{SOFT-START} = 1.69 \times 50 \times 1 \text{ ms} = 84.5 \text{ms}$$

(40)

In this case,  $T_{SOFT-START} > T_{START-UP}$  and the start-up of the SMPS is secured.

### 15.5 Capacitor at V<sub>CC</sub> C<sub>6</sub>

The  $V_{\text{CC}}$  capacitor  $C_6$  ( $C_{\text{VCC}}$  in Fig.22) needs to ensure the power supply of the IC until the power can be provided by the auxiliary bias winding. Regardless the current transfer from the start-up resistor  $R_1$  and the auxiliary winding during start-up time  $T_{\text{START-UP}}$ , the capacitance value  $C_6$  can be estimated as below:

$$C_6 = \frac{I_{VCC3} T_{START-UP}}{V_{CCHY}}$$

(41)

$I_{VCC3}$  is the IC supply current with active gate-drive. Its maximum value is 8mA as specified on the datasheet.  $V_{CCHY}$  = 5V is the turn-on/off hysteresis of the IC supply voltage  $V_{CC}$ . Based on the estimated value of  $T_{START-UP}$  in (39),  $C_6$  should then be:

$$C_6 = \frac{8mA \times 18.8ms}{5V} \approx 30 \mu F \tag{42}$$

$C_6$  = 47 $\mu$ F is selected to sustain the Vcc.

15.6 Start-up Resistor R2 and R3

The start-up resistor  $R_{START-UP}$  consists of  $R_2$  and  $R_3$ , which is connected in series as shown in Fig.22. By using (1) on page 2, the longest start-up delay time, which happens at the lowest line- input voltage  $V_{ACMIN}$  = 85V can be estimated:

$$t_{START-DELAY} = \frac{C_6 V_{CCON}}{\frac{V_{ACMIN}\sqrt{2}}{R_{START-UP}} - I_{VCC1}}$$

(43)

$$t_{START-DELAY} = \frac{47 \mu F \times 13.5 V}{\frac{85 V \sqrt{2}}{2 \times 470 k \Omega} - 55 \mu A} \approx 8.7 s$$

In worst case, the IC is turned on only in 8.7s after the SMPS is plugged to the main line. The maximum loss occurs in  $R_{\text{START-UP}}$  is roughly:

$$P_{ST-LOSS} \approx \frac{\left(V_{ACMAX}\sqrt{2}\right)^2}{R_{START-UP}} \tag{44}$$

$$P_{ST-LOSS} = \frac{\left(265V\sqrt{2}\right)^2}{2\times470k\Omega} \approx 0.15W$$

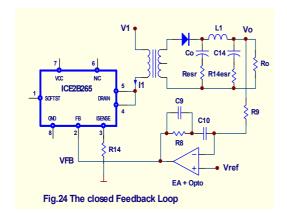

#### 15.6 Control Loop Design

#### 15.6.1 Power Stage Transfer Function

Fig. 24 shows the essential elements of the control loop.

Following equations are used to define the DC or low frequency gain of the feedback loop of the power stage (from the control voltage  $v_{FB}$  at the feedback-input pin2 to the output voltage node  $v_{O}$ ):

$$P_{O} = \frac{1}{2} \times l_{1}^{2} \times L_{1} \times f \times \eta$$

(45)

$$P_O = \frac{v_O^2}{R_O} \tag{46}$$

$$\frac{I_1}{v_{FB}} = \frac{V_{CSTH}}{R_{14} \times A_v} \tag{47}$$

Substitute  $P_O$  and  $I_1$  in (45) with (46) and (47) and rearrange the equation in term of  $v_O/v_{FB}$ , we obtain

$$G_{PS} = \frac{v_O}{v_{FB}} = \frac{V_{CSTH}}{R_{14} \times A_v} \times \sqrt{\frac{\eta L_1 R_O f}{2}}$$

(48)

$A_{\rm v}$  is the PWM-OP gain, which is equal to 3.65 as specified in the datasheet of ICE2B265. Equation (48) shows that the DC or low frequency gain  $G_{\rm PS}$  of the power stage is proportional to the square root of the output load  $R_{\rm O}$  and independent of the input voltage variation due to the current mode control. For  $R_{\rm OMIN}$  = 10.8 $\Omega$  (at  $P_{\rm OMAX}$  = 30W), the minimum gain is

$$\begin{aligned} G_{PS,MIN} &= \frac{0.95}{0.45 \times 3.65} \times \sqrt{\frac{0.8 \times 320 \times 10.8 \times 67 \times 10^{-3}}{2}} \\ G_{PS,MIN} &= 5.6 \\ G_{PS,MIN} &= 14.9 \text{ dB}. \end{aligned} \tag{49}$$

In case of  $P_{OMIN}$  = 0.5W, the output load will be  $R_{OMAX}$  = 648 $\Omega$ , the maximum power stage gain will then be

$$\begin{split} G_{PS,MAX} &= \frac{0.95}{0.45 \times 3.65} \times \sqrt{\frac{0.8 \times 320 \times 648 \times 67 \times 10^{-3}}{2}} \\ G_{PS,MAX} &= 43 \\ G_{PS,MAX} &= 32.7 \text{ dB} \end{split} \tag{50}$$

The small signal transfer function of the power stage with its pole and ESR-zero is shown below:

$$G_{PS}(s) = G_{PS} \times \left[ \frac{1 + sR_{ESR}C_{O}}{1 + s\frac{R_{O}}{2}C_{O}} \right]$$

(51)

Co consists of  $C_{12}$  and  $C_{13}$  ( see Fig.22) with the total value of  $2000\mu F$  and  $R_{ESR}$  is the ESR values (see page 12) of both capacitor in parallel, Thus  $R_{ESR} = 0.017\Omega$ . The poles and zero at minimum and at maximun power are listed in Table 2 below:

| Output Power                           | Poles $F_p = 1/\pi R_0 C_0$ | Zeros<br>$F_z = 1/2\pi R_{ESR}Co$ |

|----------------------------------------|-----------------------------|-----------------------------------|

| $P_{OMAX} = 30W$<br>$R_O = 10.8\Omega$ | F <sub>PH</sub> = 14.7Hz    | F <sub>z</sub> = 4.68kHz          |

| $P_{OMIN} = 0.5W$<br>$R_O = 648\Omega$ | F <sub>PL</sub> = 0.24Hz    | F <sub>z</sub> = 4.68kHz          |

Table 2. Poles and zero

The transfer function of the output filter  $L_{1}$ - $C_{14}$  can be expressed as follows:

$$G_{LC} = \frac{1 + \frac{1}{sC_{14}R_{14ESR}}}{1 + s\left(\frac{L_1}{R_{14ESR}} - \frac{1}{\omega^2 C_{14}R_{14ESR}}\right)}$$

(52)

$C_{14}$  and  $L_1$  have to be selected so that the pole of the filter  $F_{PLC}$  is located far a way from the crossover frequency  $F_{CO}$  to avoid its influence in the control loop. The control loop bandwidth can only be kept high with high  $F_{PLC},$  which is desirable. The L-C filter has a -2 gain slope with rapid changes of phase shift, which could induce instability in the control loop. To prevent it, the pole has to be compensated by the zero as mentioned on page 12. Based on this consideration, Epcos Alcapacitor B41858-series of  $C_{14}=220\mu F/35V$  with  $R_{14ESR}=0.084\Omega$  is selected. The zero frequency is then at:

$$F_{Z14} = \frac{1}{2\pi R_{14FSR} C_{14}} = 8.6 \text{kHz}$$

(53)

Set the pole equal to zero and solve for the inductance  $L_1$ :

$R_6$ =1k $\Omega$  is chosen to limit the maximum current that flows into TL431. In order to achieve larger bandwidth and at the same time to get the overall gain response with -1 slope, the crossover frequency  $F_C$  = 3kHz is selected. The gain of the power stage at  $F_C$  and at full load can then be derived from (51)

$$\frac{1}{2\pi\sqrt{L_1C_{14}}} = 8.6kHz$$

(54)

#### $L_1 = 1.55 \mu H$

With this combination of  $L_1$  and  $C_{14}$ , the influence of the filter on the contol loop can thus be neglected; the small signal transfer function of the power stage is then dominated only by (51).

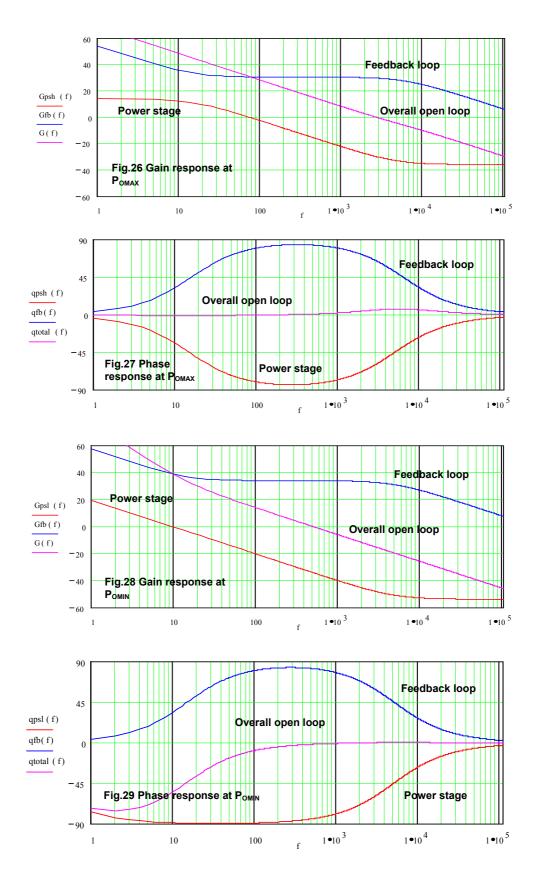

The open loop gain and phase responses of the transfer function for the minimum and maximum output power are shown in Fig.26 and in Fig.27.

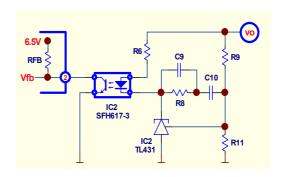

To close the loop, the feedback loop circuitry as shown in Fig.25 is added. It consists of a compensation network (TL431,  $R_6-R_{11}$ ,  $C_9$  and  $C_{10}$ ) and the optocoupler IC<sub>2</sub>.

Fig.25 Feedback Loop Circuitry

## The transfer function of the feedback loop is

$$G_{FB}(s) = \frac{v_{FB}(s)}{v_{O}(s)} = \frac{G_{C}R_{FB}}{R_{6}} \cdot \frac{1 + s(C_{9} + C_{10})R_{8}}{sC_{10}R_{9}(1 + sC_{9}R_{8})} \quad \text{(55)}$$

, where  $G_C$  is the current transfer ratio of the optocoupler. For SFH617-3,  $G_C$  = 100%. The internal pull-up resistor at FB (pin2) is specified as  $R_{FB}$  = 3.7k $\Omega$ .

$$\left|G_{PSH}(s)\right| = G_{PSMIN} \times \sqrt{\frac{1 + \left(\frac{F_{C}}{F_{Z}}\right)^{2}}{1 + \left(\frac{F_{C}}{F_{PH}}\right)^{2}}}$$

(56)

$$\left|G_{PSH}(s)\right| = 5.2 \times \sqrt{\frac{1 + \left(\frac{3 \text{kHz}}{4.68 \text{kHz}}\right)^2}{1 + \left(\frac{3 \text{kHz}}{14.7 \text{Hz}}\right)^2}} = 0.03$$

$$G_{PSH}(F_C) = -30.4dB$$

The feedback loop gain with TL431 has to be 30.4dB at  $F_{\rm C}$  and must have zero slop response. For further calculation,  $R_9$  has to be defined first.  $R_{11}$  determines the bias current of the resistor divider  $R_9-R_{11}$ . If  $R_{11}=3.9k\Omega$  is selected,  $R_9$  can be calculated by

$$R_9 = R_{11} \left( \frac{V_0}{V_{REF}} - 1 \right)$$

(57)

$$R_9 = 3.9k\Omega \times \left(\frac{18}{2.5} - 1\right) = 24k\Omega .$$

$V_{\text{REF}}$  is the reference voltage of TL431. To calculate the feedback loop gain at  $F_{\text{C}}$ , (55) can be simplified as below:

$$\left|G_{FB}(F_C)\right| = \frac{G_C R_{FB}}{R_6} \frac{R_8}{R_9} \tag{58}$$

Since  $[G_{FB}(F_C)] = 30.4dB$ ,

$$R_8 = R_9 \times 10^{\frac{30.4}{20}} \times \frac{R_6}{G_C R_{FB}} \approx 200 k\Omega \tag{59} \label{eq:R8}$$

$C_9$  is obtained by placing the pole at  $F_{PFB}$  = 2 x  $F_C$ .

$$C_9 = \frac{1}{2\pi R_8 F_{PFB}} = 133 pF$$

(60)

In order to have sufficient phase margin, especially at light load, the zero is placed at  $F_{ZFB}$  = 20Hz. The value of  $C_{10}$  is then

$$C_{10} = \frac{1}{2\pi R_8 F_{ZFB}} - C_9 = 39nH \tag{61}$$

Based on above calculation, the values of the feedback network components are selected as follows:

$R_8 = 220k\Omega$

$R_9 = 24k\Omega$

$$C_{10} = 47nF$$

$$F_{ZFB} = 15.4Hz$$

,  $F_{PFB} = 6kHz$

Fig.26 and Fig.28 also illustrate the responses of the feedback loop circuitry and the total open loop, whereas Fig.27 and Fig.29 show its respective phase responses.

### 16. Summary

This application note introduced briefly the features and functions of the CoolSET<sup>TM</sup>, the new integrated product that includes PWM control IC and the CoolMOS<sup>TM</sup>, the new generation Power MOSFET. A low cost 30W SMPS demo-board circuit is developed and its operation is analyzed is detail. The detail explanation of the board and the experiment results are described in the application note "30W Off-line SMPS Demoboard using CoolSET<sup>TM</sup> ICE2B265".

#### References

- Harald Zoellinger and Rainer Kling, "CoolSET™ ICE2AXXX for Off-line Switch Mode Power Supply", Infineon Technologies Application Note, AN-SMPS-ICE2AXXX-1, version 1.0, January 2001.

Infineon Technologies, "CoolSET™-II Off-Line SMPS Current Mode Controller with 650V/800V CoolMOS™ on Board, Infineon Technologies Datasheet, version 2.2, Exhibitary 2001

- February 2001.

| Revision History                                             |         |                                     |  |  |  |  |

|--------------------------------------------------------------|---------|-------------------------------------|--|--|--|--|

| Application Note AN-SMPS-ICE2B265-1                          |         |                                     |  |  |  |  |

| Actual Release: V1.0 Date: 25.09.2001 Previous Release: V1.0 |         |                                     |  |  |  |  |

| Page of                                                      | Page of | Subjects changed since last release |  |  |  |  |

| actual                                                       | prev.   |                                     |  |  |  |  |

| Rel.                                                         | Rel.    |                                     |  |  |  |  |

| 22                                                           |         | First Issue                         |  |  |  |  |

|                                                              |         |                                     |  |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see the address list on the last page or our webpage at

http://www.infineon.com

**CoolMOS™** and **CoolSET™** are trademarks of Infineon Technologies AG.

We listen to Your Comments

Any information within this dokument that you feel is wrong, unclear or missing at all? Your feedback will help us to continously improve the quality of this dokument. Please send your proposal (including a reference to this dokument) to: mcdoku.comment@infineon.com

Edition 2001-03-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München

© Infineon Technologies AG 2000. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics. Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Siemens AG Österreich

Erdberger Lände 26 A-1031 Wien

T (+43)1-17 07-3 56 11

Fax (+43)1-17 07-5 59 73

885 Mountain Highway

## Design of 30W Off-Line SMPS using CoolSET ICE2B265

## Infineon Technologies AG sales offices worldwide – partly represented by Siemens AG

Bayswater. Victoria 3153 T (+61)3-97 21 21 11 Fax (+61)3-97 21 72 75 Siemens Electronic Components Charleroisesteenweg 116/ Chaussée de Charleroi 116 B-1060 Brussel/Bruxelles T (+32)2-5 36 69 05 Fax (+32)2-5 36 28 57 Email:components@siemens.nl Siemens Ltda. Semiconductores Avenida Mutinga,3800-Pirituba 05110-901 São Paulo-SP T (+55)11-39 08 25 64 Fax (+55)11-39 08 27 28 Infineon Technologies Corporation 320 March Road, Suite 604 Canada, Ontario K2K 2E2 T (+1)6 13-5 91 63 86 Fax (+1)6 13-5 91 63 89 Siemens Schweiz AG Bauelemente Freilagerstrasse 40 CH-8047 Zürich T (+41)1-4 953065 Fax (+41)1-4 955050 Infineon Technologies AG Völklinger Str.2 D-40219 Düsseldorf T (+49)2 11-3 99 29 30 Fax (+49)2 11-3 99 14 81 Infineon Technologies AG Werner-von-Siemens-Platz 1 D-30880 Laatzen (Hannover) T (+49)5 11-8 77 22 22 Fax (+49)5 11-8 77 15 20 Infineon Technologies AG Von-der-Tann-Straße 30 D-90439 Nürnberg T (+49)9 11-6 54 76 99 Fax (+49)9 11-6 54 76 24 Infineon Technologies AG Weissacher Straße 11 D-70499 Stuttgart T (+49)7 11-1 37 33 14 Fax (+49)7 11-1 37 24 48 Infineon Technologies AG Halbleiter Distribution Richard-Strauss-Straße 76 D-81679 München T (+49)89-92 21 40 86 Fax (+49)89-92 21 20 71 Siemens A/S Borupyang 3 DK-2750 Ballerup T (+45)44 77-44 77 Fax (+45)44 77-40 17 Siemens S.A. Dpto.Componentes Ronda de Europa,5 E-28760 Tres Cantos-Madrid T (+34)91-5 14 71 51 Fax (+34)91-5 14 70 13

Infineon Technologies France, 39/47,Bd.Ornano F-93527 Saint-Denis CEDEX2 T (+33)1-49 22 31 00 Fax (+33)1-49 22 28 01 Siemens Components Scandinavia P.O .Bo x 6 0 FIN-02601 Espoo (Helsinki) T (+3 58)10-5 11 51 51 Fax (+3 58)10-5 11 24 95 scs@components.siemens.se Infineon Technologies Siemens House Oldbury GB-Bracknell.Berkshire RG12 8FZ T (+44)13 44-39 66 18 Fax (+44)13 44-39 66 32 Simacomp Kft. Lajos u.103 H-1036 Budanest T (+36)1-4 57 16 90 Fax (+36)1-4 57 16 92 Infineon Technologies Hong Kong Ltd. Suite 302,Level 3, Festival Walk, 80 Tat Chee Avenue, Yam Yat Tsuen, **Kowloon Tong** Hong Kong T (+8 52)28 32 05 00 Fax (+8 52)28 27 97 62 Siemens S..A. Semiconductor Sales Via Piero e Alberto Pirelli,10 I-20126 Milano T (+39)02-66 76 -1 Fax (+39)02-66 76 43 95 Siemens Ltd. **Components Division** No.84 Keonics Electronic City Hosur Road Bangalore 561 229 T (+91)80-8 52 11 22 Fax (+91)80-8 52 11 80 Siemens Ltd. CMP Div.5th Floor 4A Ring Road,IP Estate New Delhi 110 002 T (+91)11-3 31 99 12 Fax (+91)11-3 31 96 04 Siemens Ltd. CMP Div.4th Floor 130,Pandurang Budhkar Marg, Worli Mumbai 400 018 T (+91)22-4 96 21 99 Fax (+91)22-4 96 22 01 Siemens Ltd. Electronic Components Division 8,Raglan Road IRL-Dublin 4 T (+3 53)1-2 16 23 42 Fax (+3 53)1-2 16 23 49 Nisko Ltd. 2A, Habarzel St. P.O.Box 58151 61580 Tel Aviv -Isreal T (+9 72)3 -7 65 73 00

Fax (+9 72)3 -7 65 73 33

Siemens Components K.K. Talanawa Park Tower 12F &17F 3-20-14,Higashi-Gotanda, Shinagawa-ku T (+81)3-54 49 64 11 Fax (+81)3 -54 49 64 01 Infineon Technologies AG Sdn Bhd **Bayan Lepas Free Industrial Zone1** 11900 Penang T (+60)4 -6 44 99 75 Fax (+60)4 -6 41 48 72 Siemens Components Scandinavia Østre Aker vei 24 Postboks 10.Veitvet N-0518 Oslo T (+47)22-63 30 00 Fax (+47)22-68 49 13 scs@components.siemens.se Siemens Electronic Components Postbus 16068 NI -2500 BB Den Haag T (+31)70-3 33 20 65 Fax (+31)70-3 33 28 15 Email:components@siemens.nl Siemens Auckland 300 Great South Road Greenland Auckland T (+64)9-5 20 30 33 Fax (+64)9-5 20 15 56 Siemens S.A. an Componentes Electronicos R.Irmaos Siemens,1 Alfragide P-2720-093 Amadora T (+351)1-4 17 85 90 Fax (+351)1-4 17 80 83 Siemens Pakistan Engineering Co.Ltd. PO Box 1129,Islamabad 44000 23 West Jinnah Ave Islamahad T (+92)51-21 22 00 Fax (+92)51-21 16 10 Siemens SP.z.o.o. ul.Zupnicza 11 PL-03-821 Warszawa T (+48)22-8 70 91 50 Fax (+48)22-8 70 91 59 Siemens Ltd. Asia Tower,10th Floor 726 Yeoksam-dong,Kang-nam Ku **CPO Box 3001** Seoul 135-080 T (+82)2-5 27 77 00 Fax (+82)2-5 27 77 79 INTECH electronics ul.Smolnaya,24/1203 RUS-125 445 Moskva T (+7)0 95 -4 51 97 37 Fax (+7)0 95 -4 51 86 08 Siemens Components Scandinavia Österögatan 1,Box 46 S-164 93 Kista T (+46)8-7 03 35 00 Fax (+46)8-7 03 35 01 Email: scs@components.siemens.se

Infineon Technologies Asia Pacific Pte.Ltd. Taiwan Branch 10F,No.136 Nan King East Road Section 23, Taipei T (+8 86)2-27 73 66 06 Fax (+8 86)2-27 71 20 76 Infineon Technologies Asia Pacific,Pte.Ltd. 168 Kallang Way Singapore 349 253 T (+65)8 40 06 10 Fax (+65)7 42 62 39 Infineon Technologies Corporation 1730 North First Street San Jose,CA 95112 T (+1)4 08-5 01 60 00 Fax (+1)4 08-5 01 24 24 Siemens Components,Inc. Optoelectronics Division 19000 Homestead Road Cupertino CA 95014 T (+1)4 08-2 57 79 10 Fax (+1)4 08-7 25 34 39 Siemens Components,Inc. Special Products Division 186 Wood Avenue South Iselin N.I 08830-2770 T (+1)7 32-9 06 43 00 Fax (+1)7 32-6 32 28 30 Infineon Technologies Hong Kong Ltd. Beijing Office Room 2106,Building A Vantone New World Plaza No.2 Fu Cheng Men Wai Da Jie 100037 Beijing T (+86)10 -68 57 90 -06,-07 Fax (+86)10 -68 57 90 08 Infineon Technologies Hong Kong Ltd. Chengdu Office Room14J1,Jinyang Mansion 58 Tidu Street Chengdu, Sichuan Province 610 016 T (+86)28-6 61 54 46 /79 51 Fax (+86)28 -6 61 01 59 Infineon Technologies Hong Kong Ltd. Shanghai Office Room1101,Lucky Target Square No.500 Chengdu Road North Shanghai 200003 T (+86)21-63 6126 18 /19 Fax (+86)21-63 61 11 67 Infineon Technologies Hong Kong Ltd. Shenzhen Office Room 1502,Block A Tian An International Building Renim South Road Shenzhen 518 005 T (+86)7 55 -2 28 91 04 Fax (+86)7 55-2 28 02 17 Siemens Ltd. Components Division P.O.B.3438 Halfway House 1685 T (+27)11-6 52 -27 02 Fax (+27)11-6 52 20 42