## **About this document**

This application note provides information on how to get started with security on the PSOC<sup>™</sup> Control C3 MCU out of the box. It contains guidance on how to provision and program a secure application. It introduces the security architecture of the PSOC<sup>™</sup> Control MCU, consisting of an Arm<sup>®</sup> Trust Zone-enabled Cortex<sup>®</sup>-M33. This document provides a brief overview of the security features available on the device.

### **Intended audience**

This document is intended for customers who want to start with enabling secured boot and explore security feature implementation on PSOC™ Control MCU devices.

### **Table of contents**

## **Table of contents**

|         | About this document                                           | 1  |

|---------|---------------------------------------------------------------|----|

|         | Table of contents                                             | 2  |

| 1       | Overview of PSOC™ Control C3 MCU                              | 4  |

| 2       | Ease of development                                           | 5  |

| 2.1     | Device lifecycle stages (LCS)                                 | 5  |

| 2.1.1   | Development LCS                                               | 6  |

| 2.1.2   | Production LCS                                                | 6  |

| 2.1.3   | RMA LCS                                                       | 6  |

| 2.2     | Boot policy update                                            | 7  |

| 2.3     | Development flow                                              | 8  |

| 2.3.1   | Getting started                                               | 8  |

| 2.3.1.1 | Initialize the application directory                          |    |

| 2.3.1.2 | Key generation                                                | 10 |

| 3       | Application structure                                         | 11 |

| 3.1     | Basic application structure                                   | 12 |

| 4       | Boot flow                                                     | 13 |

| 4.1     | Boot sequence                                                 | 13 |

| 4.2     | BOOT_SIMPLE_APP                                               | 15 |

| 4.3     | Secure boot                                                   | 15 |

| 4.3.1   | BOOT_ONE_SLOT                                                 | 16 |

| 4.3.2   | BOOT_TWO_SLOTS                                                | 17 |

| 4.3.3   | BOOT_THREE_SLOTS                                              | 18 |

| 4.4     | Dual bank application                                         | 19 |

| 5       | Code signing and verification                                 | 20 |

| 5.1     | Code signing                                                  | 20 |

| 5.2     | Code validation                                               | 20 |

| 6       | Edge Protect Tools                                            | 22 |

| 6.1     | Overview                                                      | 22 |

| 6.2     | Device communication                                          | 23 |

| 6.3     | Packaged assets                                               | 24 |

| 6.4     | Edge Protect Tools package for PSOC™ Control C3               | 24 |

| 7       | Processing, memory, and peripheral isolation                  | 26 |

| 7.1     | Memory isolation                                              | 27 |

| 7.2     | Peripheral isolation                                          | 32 |

| 7.2.1   | Security aware peripheral protection controller (PPC) regions | 33 |

| 8       | Firmware upgrade                                              | 34 |

| 8.1     | BootROM DFU serial interface                                  | 34 |

### **Table of contents**

| 8.2     | User application (DFU MW) serial interface  | 35 |

|---------|---------------------------------------------|----|

| 8.3     | Firmware upgrade sequence                   | 38 |

| 8.4     | Live firmware update                        | 39 |

| 8.4.1   | OEM provisioning parameters                 | 41 |

| 8.4.2   | Firmware upgrade sequence                   | 42 |

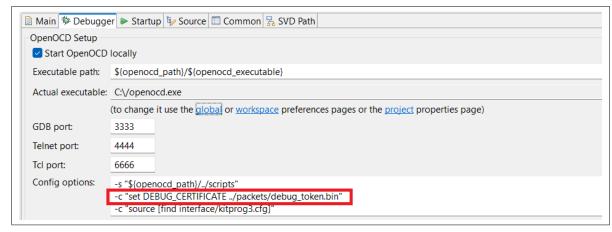

| 9       | Debug token                                 | 43 |

| 9.1     | Debug token use cases                       | 43 |

| 9.2     | Generating a debug certificate              | 44 |

| 9.3     | Generating RMA certificate                  | 46 |

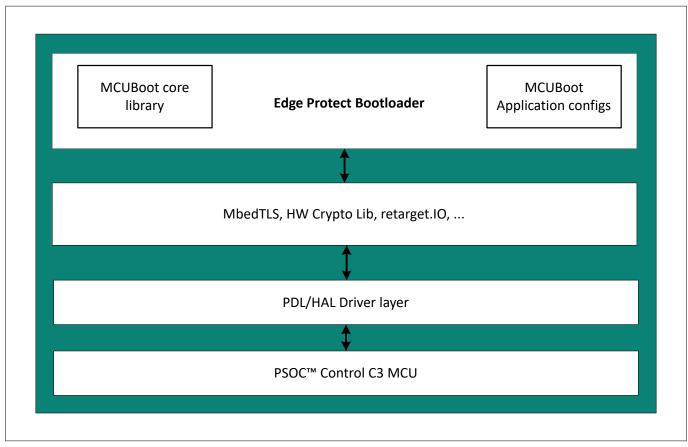

| 10      | Edge Protect Bootloader                     | 48 |

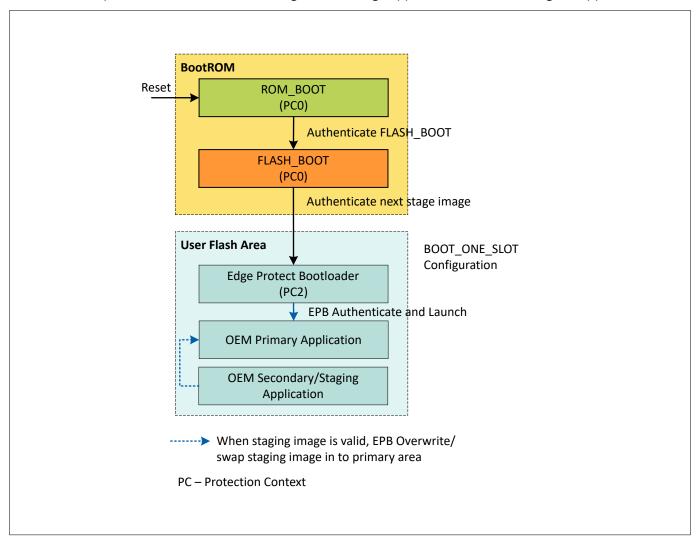

| 10.1    | Boot flow                                   | 48 |

| 10.2    | Architecture                                | 48 |

| 10.3    | Edge Protect Bootloader features            | 49 |

| 10.3.1  | Power fail-safe update                      | 50 |

| 10.3.2  | Multi image authentication                  | 50 |

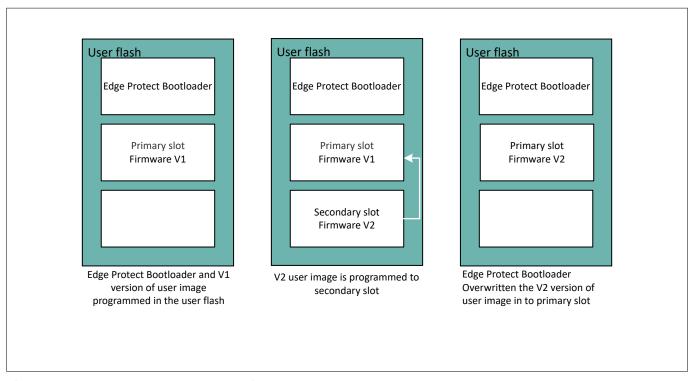

| 10.3.3  | Upgrade by overwrite                        | 54 |

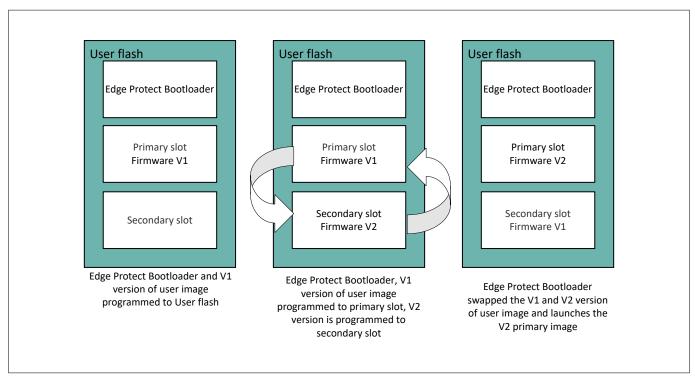

| 10.3.4  | Upgrade by swap                             | 55 |

| 10.3.5  | Secure boot                                 | 56 |

| 10.3.6  | Secure firmware update                      | 57 |

| 10.3.7  | Image encryption                            | 57 |

| 10.3.8  | Downgrade prevention                        | 60 |

| 10.3.9  | Dependency check                            | 61 |

| 10.3.10 | Fault injection hardening                   | 61 |

| 10.3.11 | Serial logging                              | 62 |

| 11      | Policy file                                 | 63 |

| Α       | Appendix A. Default OEM provisioning policy | 65 |

|         | References                                  | 71 |

|         | Glossary                                    | 72 |

|         | Revision history                            | 74 |

|         | Disslaimer                                  | 75 |

### 1 Overview of PSOC™ Control C3 MCU

### 1 Overview of PSOC™ Control C3 MCU

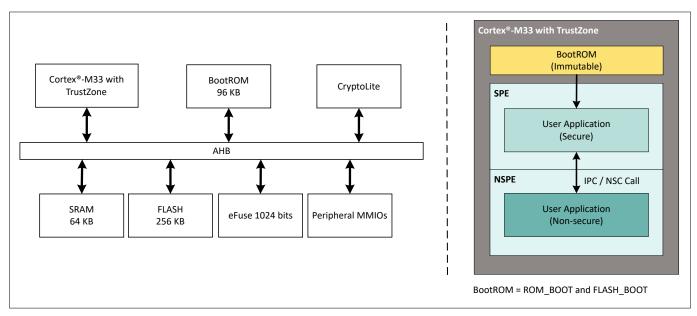

The PSOC™ Control C3 MCU is a single core device that contains Arm® TrustZone enabled Cortex® M33, SONOS flash, a range of peripherals, including high-performance programmable analog subsystem (HPPASS), coordinate rotation digital computer (CORDIC), ADC, UART, SPI, I2C, CAN FD, crypto accelerators, and several other blocks. The CM33 allows for both a secure programming environment (SPE) and a non-secure programming environment (NSPE). Although a single CPU is used, individual SPE and NSPE projects can be created. The BootROM is responsible for the initial secure boot and the root of trust (RoT). The main function of the BootROM is to configure the system information, authenticate the application, and transfer control to the application. Figure 1 shows the basic hardware cores and boot flow of the PSOC™ Control C3 MCU.

Figure 1 Basic hardware blocks and boot flow

## Table 1 Security features of PSOC™ Control C3 MCU parts

| Sl. No. | Security features            | Comments                                                                                                                                                                       |  |

|---------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | Secure boot                  | The chain of trust includes up to the first Original Equipment Manufacturer (OEM) code. The policy file parameter determines if secure boot is extended to the first OEM code. |  |

| 2       | Secured debug                | Yes. supported                                                                                                                                                                 |  |

| 3       | Secured firmware upgrade     | Yes, BootROM supports an in-built device firmware update (DFU) serial interface                                                                                                |  |

| 4       | OEM policies                 | Yes, supported                                                                                                                                                                 |  |

| 5       | Transition to production LCS | Yes                                                                                                                                                                            |  |

| 6       | Transition to RMA LCS        | Yes, with authentication                                                                                                                                                       |  |

| 7       | OpenRMA with debug token     | Yes, and signed by Infineon                                                                                                                                                    |  |

| 8       | OEM RoT keys (pub keys)      | Yes, it supports initial and alternate keys in case of key revocation is required                                                                                              |  |

### 2 Ease of development

## 2 Ease of development

## 2.1 Device lifecycle stages (LCS)

Devices are shipped in the development stage, which allows the device to be provisioned and programmed as many times as needed to develop the final application. Devices are shipped with a default policy that defines all debug ports as open and allow application execution without code authorization. This allows you to program, evaluate, and debug the parts prior to any knowledge about security or code signing.

During the development stage, the OEM can take ownership of the part, allowing it to replace the default policy file with a custom policy. All aspects of the production stage can be simulated, including locking down the CPU access ports, which will lock out any attempt to connect the debugger to the part. The only difference between the development and production stages from a code operation point of view is that the SYS\_AP (system access port) cannot be disabled in the development stage. This ensures that the developer cannot be locked out of the part and can, at any time, recover from a device configuration error and even return the device to its original state. When the firmware is ready for production, the device can be advanced to the production stage.

The production stage locks down the device owner, meaning that the key used to authenticate the firmware can no longer be changed from what was programmed into the device. The debug ports, including SYS\_AP, can all be disabled or left enabled as per your requirement. Devices can be advanced to the production stage after receiving them from Infineon. This is the typical model once the OEM starts to ship their product. There is no need to transfer ownership in the development stage; instead, you can take ownership and advance the device to the production stage in a single step as part of provisioning the device.

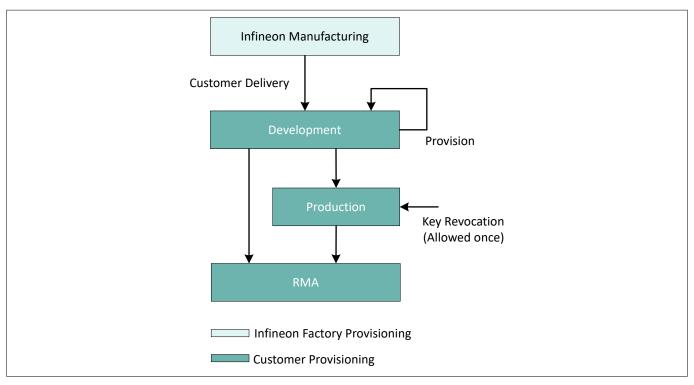

The RMA stage is only used in the event that a problem is found in the hardware and the device must be shipped back to Infineon for failure analysis (FA). Figure 2 shows the flow from development to RMA.

**Note**: Blowing eFuses to change LCS requires VDDIO0 to be 2.5 V. See the datasheet for more details.

BootROM execution flow depends on the lifecycle stage at which the MCU is running. LCS is dictated by blowing eFuse bit values in to the device. During provisioning, the LCS can be moved for the device. Infineon signed RAM applications are used to provision the assets into the device and change the device LCS. RAM applications and the associated input parameters are loaded into the device SRAM through a SWD or DFU serial interface. RAM applications are authenticated by BootROM before it execute from device SRAM. The LCS is sequential and cannot be reverted back to the previous stage, since the LCS is maintained in the eFuse memory. Device DAP access restriction shall be based on a deployed policy, which will be applicable for both production and development LCS. Figure 2 shows the LCS transition in the PSOC™ Control C3 device.

### 2 Ease of development

Figure 2 LCS transition

## 2.1.1 Development LCS

- Device shipped to customer in development LCS by default

- OEM policy assets will be provisioned in this LCS

- Transition allowed in this stage is production or RMA

- cyapp\_prov\_oem RAM application will be used to do the device LCS transition from development to production

- Device can be provisioned again until the prov\_oem\_complete parameter is false. See the policy\_oem\_provisioning.json file

### 2.1.2 Production LCS

- This is a lifecycle stage of a secured device

- OEM policy assets (example, SECURE\_HASH) will be provisioned prior moving to this LCS

- Device will launch the customer application only when authentication is success

- Production LCS is mandated for a secured device and it protects the customer application from tampering

- The only transition allowed in this stage is production to RMA LCS

- After the device transition to production LCS, the protection state is set to SECURE

### 2.1.3 RMA LCS

- RMA LCS allows Infineon to do failure analysis (FA)

- For FA, customer transitions the device LCS to RMA and ship the device to Infineon

- RMA transition is allowed only when the device is in production LCS

- RMA transition in production LCS requires a certificate signed with the OEM\_ROT\_KEY

### 2 Ease of development

- cyapp\_to\_rma RMA application will be used to transition the device in to RMA LCS

- During the RMA transition, the following list of assets will be cleared from the device

- HUK

- IAK

- MPN\_KEY and MPN\_ROT\_KEY\_01\_HASH

- OEM policies

- All user flash contents

- PROT FW policy

- Infineon policies

- After the device moved to RMA state, the device will not boot the OEM application

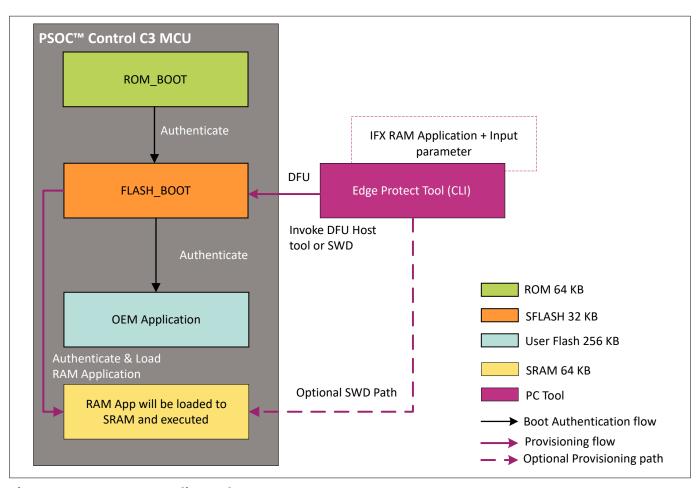

## 2.2 Boot policy update

- Boot policy is one of the input parameters for the RAM application, which is used to provision the device

- The RAM applications are signed by Infineon and the input parameters are not, but it is bundled as a downloadable module (DLM) packet using a provisioning tool

- The RAM application bundle can be sent to the device SRAM location via DFU serial interface or SWD using the Edge Protect Tools

**Note**: Edge Protect Tools support only SWD or DFU serial interface (UART, I2C, SPI) for provisioning the device

These SWD/ DFU ports are invoked by a provisioning tool

**Note**: BootROM has a built-in DFU-supported serial interface to receive RAM application

- After the RAM application is moved to SRAM, the BootROM authenticates the RAM application and gives control to the RAM application

- Further, the RAM application will provision the device. At the end of the RAM application, the device will go reset and the BootROM will execute/branch based on the boot policy configured

### 2 Ease of development

Figure 3 **Boot policy update**

#### 2.3 **Development flow**

The typical development flow for a PSOC™ Control C3 device is the same work flow as most other systems.

- 1. Provision the device

- 2. Design, develop, and modify the project code

- 3. Compile/link

- 4. Program the device

- Run/debug on the device 5.

#### 2.3.1 **Getting started**

Infineon ships the device with development LCS and provisioned with BOOT\_SIMPLE\_APP configuration, which the BootROM can expect the first user application to be in raw format and launches the application without authentication.

General application development instructions are available in the Application development instructions section of the Getting started with PSOC™ Control C3 MCU on ModusToolbox™ software document. Once you are ready to provision the device with a secure boot configuration, do the following:

- Initialize application directory

- Generate two key pairs (private/public optional)

- Edit policy file

- Provision the device

### 2 Ease of development

Infineon's Edge Protect Tools is a set of command-line tools used to perform the needed functions for key signing, key generation, provisioning the device, and so on. These tools are executed from inside a shell tool. It is recommended to use the modus-shell, which is installed along with Edge Protect Suite. Before using these tools, change the directory to the top level of your application folder, the same level as the application project directories.

**Note**: Ensure that the KitProg3/MiniProg4 on your PSOC<sup>™</sup> Control C3 device is updated to firmware version 2.60.1412 or later.

For more information about the KitProg3, see the Getting started with PSOC™ Control C3 MCU on ModusToolbox™ software document.

## 2.3.1.1 Initialize the application directory

When initializing the application folder for using Infineon's Edge Protect Tools, several folders will be created in your application directory. The following is a list of these folders and their contents.

- **keys:** Any keys that you create with the Edge Protect Tools will be placed in this directory. If you prefer to create your own keys, you must place the keys in this directory

- **logs:** Each time you run the Edge Protect Tools, creates a time and date log files. These files can assist in debugging any problems with the tools that can occur. This directory is created for the first time that you execute an Edge Protect Tools command after initialization

- **packets:** Some commands generate JSON-formatted packets that are downloaded into the device or will be used by another command. These files are placed in this folder

- **policy:** Contains some sample policy files that can be modified or copied as required. Eventually, each one will have a custom policy file that fits their application

The following command will initialize the application directory and prepare it for all the following Edge Protect Tools commands, it will be executed once per application.

edgeprotecttools -t psoc\_c3 init

Execute the following command once per session to configure the connection between the tool and a MiniProg4 or kit SWD port.

edgeprotecttools set-ocd --name openocd --path <openocd\_path>

Replace copenocd\_path> with the path to the openocd directory installed when the Early Access Pack is installed. Typically, will be in the C:/Users/username/ModusToolbox/packs/ModusToolbox-PSOC-C3-Early-Access-Pack/tools/openocd. Replace the username with the equivalent on your system.

**Note**: If you are using modus-shell on a macOS system, the recommended usage for EdgeProtectTool is as follows:

arch -arm64 edgeprotecttools <command>

### 2 Ease of development

## 2.3.1.2 Key generation

You need to create two key pairs that are private and public keys. The second key pair is useful if you need to revoke the first key due to a private key security breach. The following two commands generate two keys that will be placed in the key's directory.

edgeprotecttools create-key --key-type ECDSA-P256 --output keys/oem\_private\_key\_0.pem keys/oem\_public\_key\_0.pem

edgeprotecttools create-key --key-type ECDSA-P256 --output keys/oem\_private\_key\_1.pem keys/oem\_public\_key\_1.pem

The keys generated are 256-bit ECC keys and the output is in the .pem format. This is a common ASCII format compatible with many public-domain tools.

### 3 Application structure

## **3** Application structure

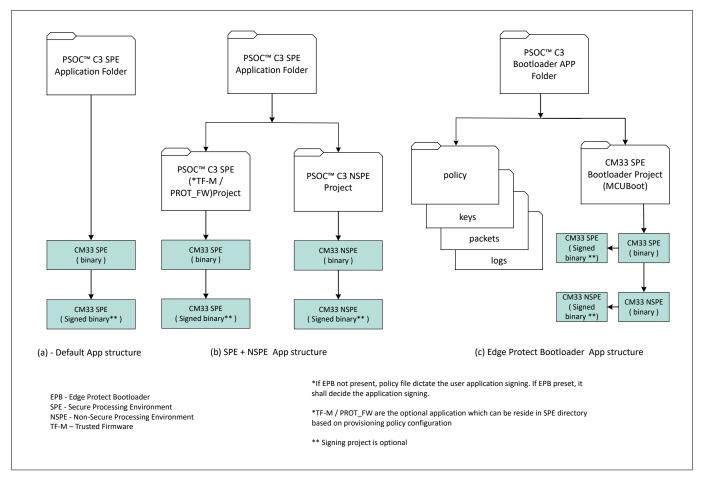

This section shows a typical folder structure for an application. The term "application" refers to one or more projects that run on this CPU. Although the CM33 is a single CPU, it includes TrustZone, so there will be two projects associated with it as follows:

- A Secure Processing Environment (SPE)

- Non-Secure Processing Environment (NSPE) project

It is an option to support NSPE project if required. Each application can contain four additional folders that are generated when the Edge Protect Tools that are used to initialize the application for provisioning. These folders include:

- policy

- keys

- packets

- logs

They contain the default policy files, the generated or stored keys, packets generated by the tools, and log files generated each time you execute the Edge Protect Tools. See the Getting started for more details about Edge Protect Tools and these folders.

Figure 4 File structure

### 3 Application structure

## 3.1 Basic application structure

In the default application structure, only one SPE project will be created and presented, this default structure can be used if you need only an SPE-based project, see Figure 4 (a). Additionally, you can add an NSPE project if needed, see Figure 4 (b).

The first application will be authenticated by BootROM and the application must be signed if the boot configuration is BOOT\_ONE\_SLOT, BOOT\_TWO\_SLOTS, BOOT\_THREE\_SLOTS, and BOOT\_IDLE configurations. Signing the first application is a mandate for production LCS.

If the Edge Protect Bootloader (EPB) is used, it will be viewed as a separate application within ModusToolbox™ 3.3 and it will be compiled, linked, and programmed separately from the main application, see Figure 4 (c). The main application will contain the CM33 SPE and CM33 NSPE project. Note that in this configuration, only the EPB application directory includes the four folders required when provisioning the device. This is because when the device boots up, the secure boot sequence only extends the chain of trust to the next application. In this case, the next application is the EPB. EPB is responsible for extending the chain of trust to the next application by authenticating the code. Provisioning and the policy file only directly affect the first OEM application that is the EPB. Keys used to authenticate the main application can have been loaded into the device during provisioning or can be stored in the EPB; this is up to you and the application requirements.

### 4 Boot flow

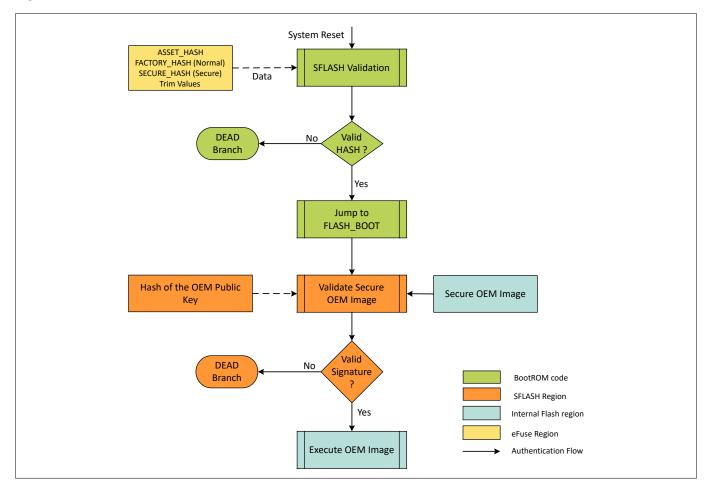

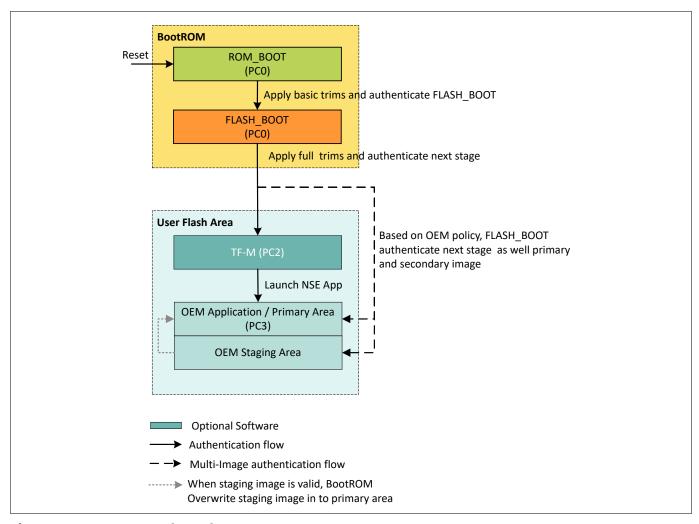

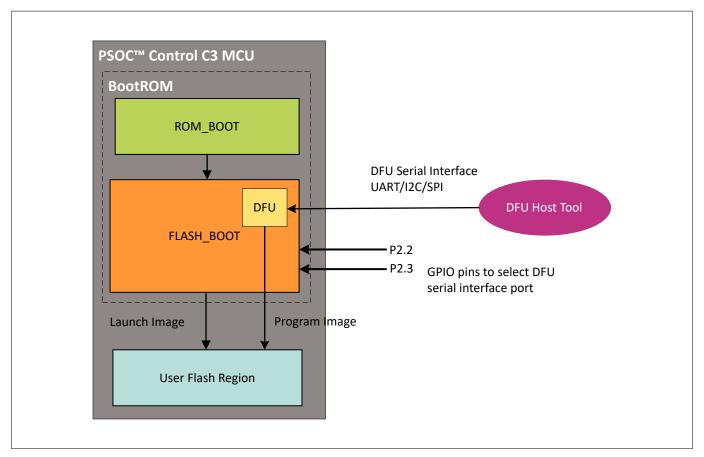

BootROM executes the code from the beginning of power-on reset (POR) until the launch of an OEM application. The main functionality of BootROM is to authenticate and launch the next stage application. BootROM consists of ROM\_BOOT and FLASH\_BOOT.

## 4.1 Boot sequence

- After reset, the ROM\_BOOT applies basic trim, configures clocks, and validates the SFLASH

- ROM\_BOOT execution jumps to FLASH\_BOOT on successful validation

- FLASH\_BOOT authenticates the next stage application (OEM)

- FLASH\_BOOT prepares to launch the application on successful authentication

- If authentication fails, the device will go to the DEAD branch

Figure 5 shows the steps involved in the BootROM root of trust.

Figure 5 Root of trust

Table 2 shows the elements used to validate each stage of BootROM validation.

Table 2 Elements used for each stage of validation

| Step | Element    | Checked by    | Using         |

|------|------------|---------------|---------------|

| 1    | ROM        | N/A immutable | N/A immutable |

| 2    | ASSET_HASH | ROM_BOOT      | eFUSE zeroes  |

(table continues...)

### 4 Boot flow

### Table 2 (continued) Elements used for each stage of validation

| Step | Element          | Checked by       | Using       |

|------|------------------|------------------|-------------|

| 3    | SFLASH_BOOT code | ROM_BOOT         | ASSET_HASH  |

| 4    | OEM_ROT_KEY      | SFLASH_BOOT code | eFUSE_HASH  |

| 5    | OEM Application  | SFLASH_BOOT code | OEM_ROT_KEY |

The device internal user flash region can have multiple images based on the BOOT\_CFG\_ID parameter present in the boot policy. The boot policy will be configured during device provisioning.

BOOT\_CONFIG\_ID parameter will have the following allowed configuration.

- BOOT\_SIMPLE\_APP

- BOOT\_ONE\_SLOT

- BOOT\_TWO\_SLOTS

- BOOT\_THREE\_SLOTS

- BOOT\_IDLE

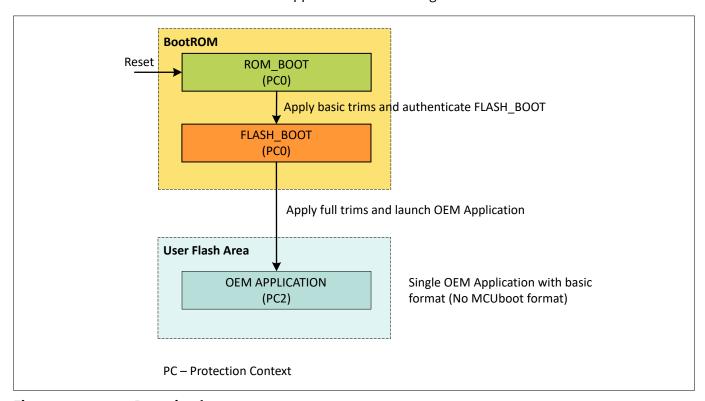

## 4.2 BOOT\_SIMPLE\_APP

- Simple OEM application is a default BootROM configuration

- One OEM application will be present in the user flash region with basic application format (interrupt table and code, no MCUboot format)

- OEM application start address is the start of internal flash

- BootROM will not authenticate the OEM application in this configuration

Figure 6 Boot simple app

### 4.3 Secure boot

The process of verifying and validating the integrity and authenticity of firmware as a prerequisite to their execution. At each stage of the boot process checks that code is authorized to run before execution. PSOC™ Control C3 BootROM authenticates user application based on boot configuration.

Table 3 Secure boot configuration

| boot_cfg_id      | Description                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| BOOT_ONE_SLOT    | BootROM authenticates the first OEM application present in the use flash.                                                     |

| BOOT_TWO_SLOTS   | BootROM authenticates the two (primary, staging) OEM application present in the use flash and launch the primary application. |

| BOOT_THREE_SLOTS | BootROM authenticates the three OEM application present in the use flash and launch the first OEM application.                |

### 4 Boot flow

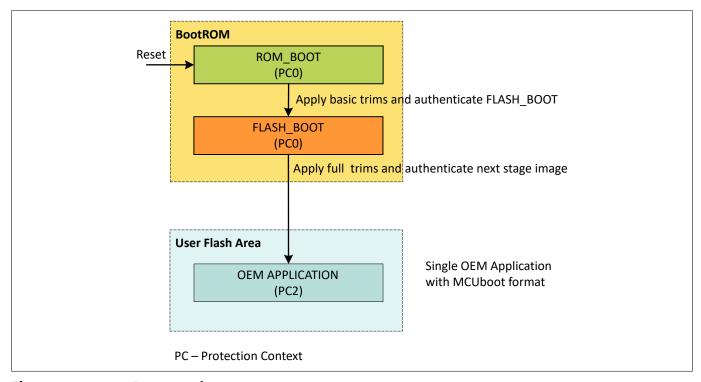

## 4.3.1 BOOT\_ONE\_SLOT

- One OEM application can be present in the user flash region with the MCUboot format

- BOOT\_APP\_LAYOUT[0] contains start address and size for the application

- BootROM will authenticate and launch the OEM application

Figure 7 Boot one slot

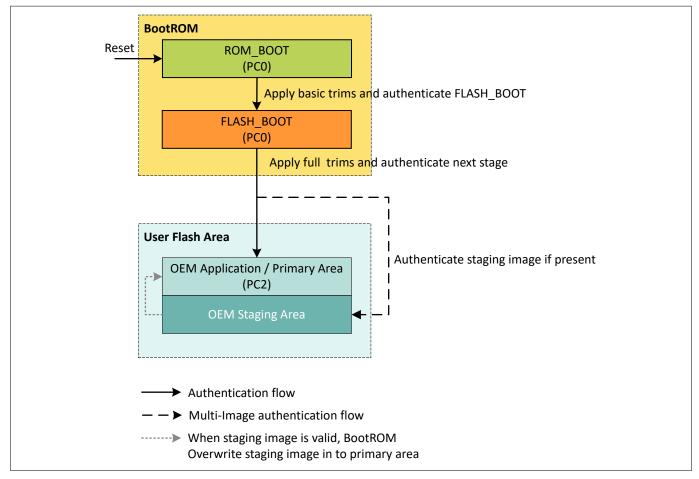

## 4.3.2 BOOT\_TWO\_SLOTS

- Two OEM applications can be present in the user flash region

- BOOT\_APP\_LAYOUT[0 to 1] contain the start address and size for the primary and secondary/staging images

- Primary slot is for boot and the secondary slot is for update the image

- BootROM will authenticate a secondary image and update it in to the primary slot on successful authentication

- Further BootROM launches OEM application from primary location

Figure 8 Boot two slots

### 4.3.3 BOOT\_THREE\_SLOTS

- Three OEM applications can be present in the user flash region

- BOOT\_APP\_LAYOUT[0 to 2] contain the start address and size correspondingly for the first application (Example: TF-M) application, second application (OEM App) primary slot, and secondary slot

- Here the first application can be either TF-M software or EdgeProtectBootloader based OEM bootloader or protected firmware

- Using the multi-image authentication feature, the BootROM will authenticate each stage of the application and launch the primary image

- If the first image is invalid or both of the primary and secondary images are invalid, the device will go to dead branch

Figure 9 Boot three slots

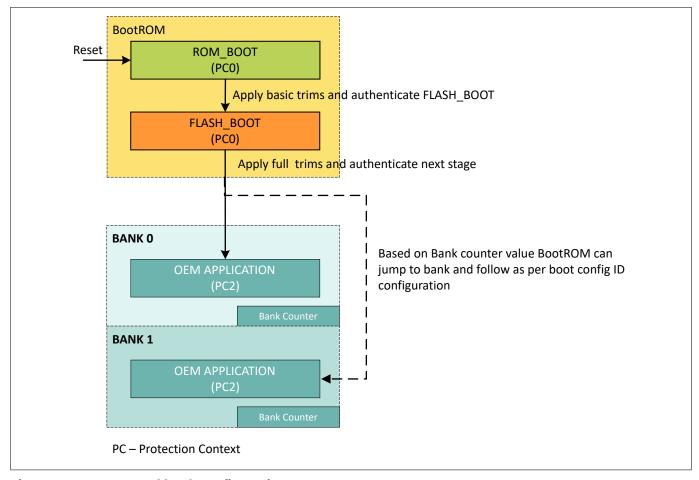

## 4.4 Dual bank application

- The user flash regions can be split into two equal regions. Both regions will have dual bank counter offset and an OEM application

- BootROM can read the dual bank counter offset value and identify the active bank region

- BootROM will then authenticate the active bank region and execute the application

Figure 10 Dual bank configuration

### 5 Code signing and verification

#### **Code signing and verification** 5

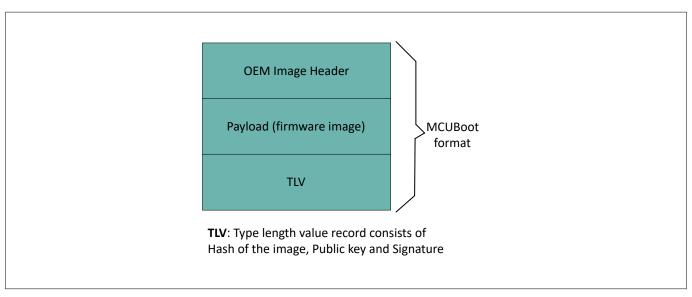

Code signing and verification must for secure boot configuration. In other words, the user application must be signed for BOOT\_ONE\_SLOT, BOOT\_TWO\_SLOTS, and BOOT\_THREE\_SLOTS configurations.

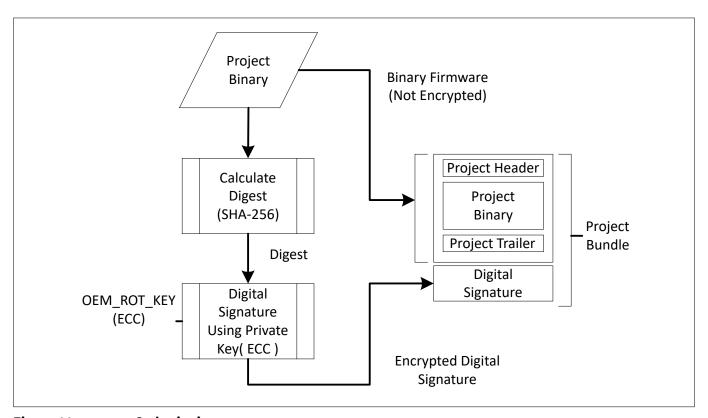

#### 5.1 **Code signing**

To verify the user application, create a digital signature and append it to the end of the project binary during build time. The user code is not encrypted, but the digital signature is the encrypted digest one. The digital signature is generated by encrypting the digest with the ECDSA private key. In this case, it is the OEM ROT PRIVATE KEY. The digest is generated by running the user project binary through an SHA-256 hash function. This method guarantees that a third party without access to the OEM's private key cannot properly sign the application code, which is therefore only created and signed by the OEM.

Note: The MCUboot-based Project Header consists of image attributes and Project Trailer consists of image trailer TLV information.

Figure 11 **Code signing**

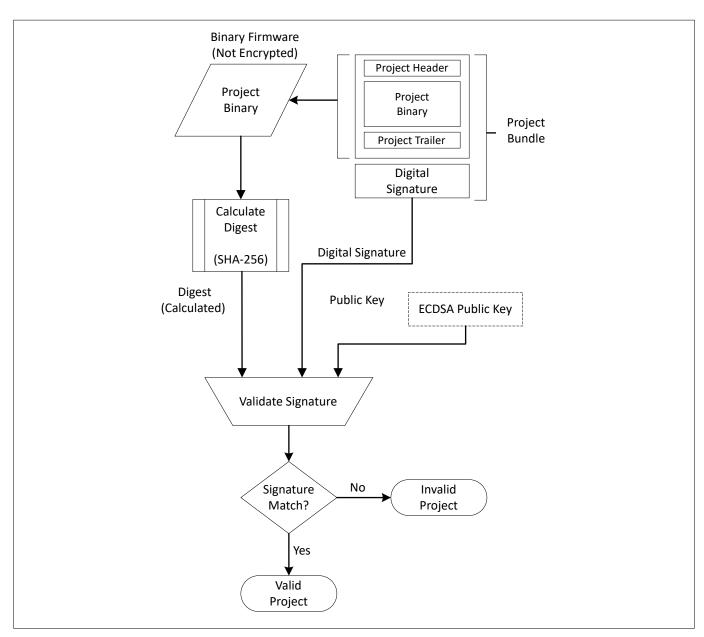

#### **Code validation** 5.2

When secured boot is enabled through provisioning, whether the device is in production or development LCS, the BootROM must verify the OEM code prior to execution. The project binary image must be signed by the OEM\_ROT\_PRIVATE\_KEY before loaded into the device. BootROM verifies the OEM code by first calculating the hash of the project binary image. It then uses the calculated hash, the project digital signature that is appended to the end of the code, and the OEM\_ROT\_PUBLIC\_KEY to verify if the OEM code is authentic. If the code fails verification, the BootROM will not jump to the user code but will wait in an endless loop until the device has been reset. Figure 12 shows a graphical representation of this process.

### 5 Code signing and verification

Figure 12 ECDSA code verification

### **6 Edge Protect Tools**

#### **Edge Protect Tools** 6

#### **Overview** 6.1

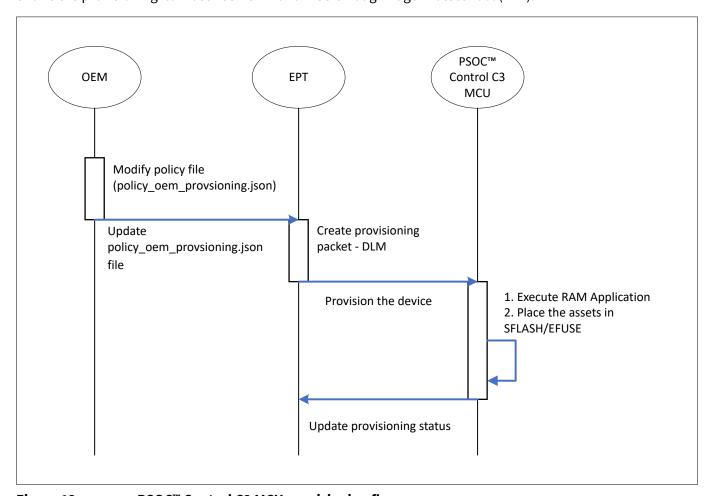

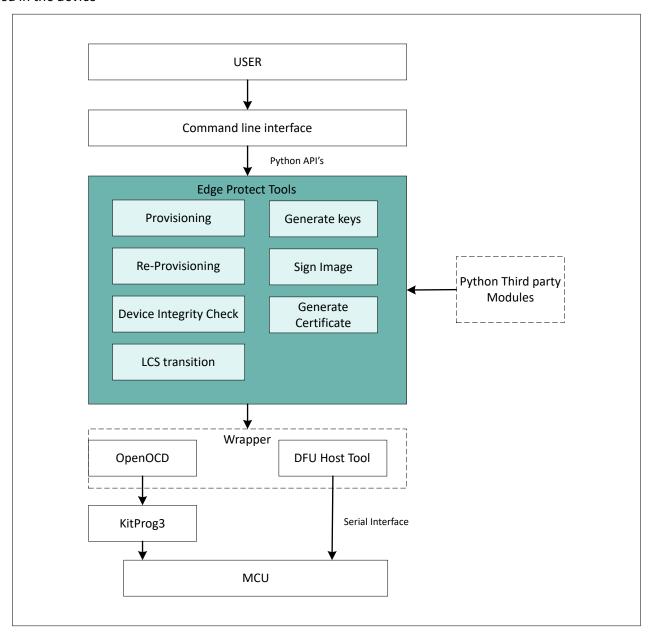

Edge Protect Tools is a comprehensive security tools package built on Python, offering a command-line interface to interact with MCUs for various purposes. These purposes include: provisioning, device integrity checks, RMA transition, and more. The tools are developed using the Python programming language and leverage several third-party Python modules to handle different tasks. For instance, these modules are used to manage configuration files in JSON format, object files in ELF format, and perform cryptographic operations. Use any shell command-line tool to interact with Edge Protect Tools. However, Infineon recommends using modus-shell, which comes bundled with the ModusToolbox™ installation package for a seamless interaction experience. When executing commands that require interaction with the MCU, such as provisioning, the tools prepare the necessary provisioning packets and communicate with the device using programming tools like OpenOCD via the SWD interface or the DFU Host Tool via serial interfaces like I2C, SPI, and UART. Figure 13 shows the provisioning flow between OEM and MCU through Edge Protect Tool (EPT).

Figure 13 **PSOC™ Control C3 MCU provisioning flow**

The Edge Protect Tools package supports a range of operations that cater to various security-related needs. Some of the key operations supported by the tools include:

- Provisioning, which involves injecting keys and policy into the device, ensuring a secure setup

- Re-provisioning allows for modifying certain configurations post-provisioning and providing flexibility in device management

- Enables a Device Integrity Exam, which verifies the authenticity of the device and ensures it is in a known state, thereby preventing any potential security breaches

### **6 Edge Protect Tools**

- In addition, the Edge Protect Tools facilitate key pair generation, creating key pairs that can be utilized for provisioning, and image signing purposes. Certificate generation is another supported operation, which generates certificates that can be used for debugging and RMA transition

- The tools support signing images with the OEM key, ensuring the integrity and authenticity of the images used in the device

Figure 14 Edge Protect Tools design flow

### 6.2 Device communication

The Edge Protect Tools package supports communication with the device using programming tools such as the OpenOCD tool via the SWD interface on the device, or by utilizing the DFU Host Tool via serial interfaces like I2C, SPI, UART, or USB. The Edge Protect Tools package does not directly call the programming tool commands, but instead utilizes a wrapper mechanism to interface with the programming tools. This model has the potential to be further extendible to other programming tools, although this is currently outside the scope of the tool's current version.

### **6 Edge Protect Tools**

#### 6.3 **Packaged assets**

OEM policy - The OEM policy (policy\_oem\_provisioning.json) file can be used to configure the device policy configurations, which is located in the policy folder as part of the Edge Protect Tools package.

#### Edge Protect Tools package for PSOC™ Control C3 6.4

The Edge Protect Tools is packaged as a part of the Edge Protect Security Suite for the PSOC™ Control C3 device. Follow these steps to setup Edge Protect Security Suite.

- Download and install the Infineon Developer Center Launcher

- 2. Login using your Infineon credentials

- 3. Download and install the "ModusToolbox™ Edge Protect Security Suite" from Developer Center Launcher

Note:

The default installation directory of the Edge Protect Security Suite in Windows operating system is C:/ Users/<USER>/Infineon/Tools. After installing the Edge Protect Security Suite, add the Edge protect tools executable to system PATH variable (/ModusToolbox-Edge-Protect-Security-Suite-<version>/ tools/edgeprotecttools/bin)

To utilize the executable file, find the executable file in the ./bin directory, which is compatible with Windows, Linux, and macOS. To use it directly, add the executable path to your system's environment variable PATH.

Note:

You need to install Python separately. The Edge Protect Tools support Python versions ranging from 3.8 to 3.12.

Once you have installed the Edge Protect Tools package, initialize it for a specific target device. For example, to initialize it for the PSOC™ Control C3 device, navigate to your working directory and execute the following command in a shell CLI:

```

edgeprotecttools.exe -t psoc_c3 init

```

After that, set up the OpenOCD path to be used by the tools. Run the following command:

```

edgeprotecttools.exe set-ocd --name openocd --path <openocd path>

```

replacing <openocd path> with the actual path to the OpenOCD tool on your system. After initialization, a specific folder structure will be created in your working directory.

To provision the device, execute a specific command using the Edge Protect Tools utility. The basic command is as follows:

```

edgeprotecttools -t psoc_c3 provision-device -p policy/policy_oem_provisioning.json

```

However, if you are using an external MiniProg, specify the probe ID in the command. To find the probe ID, run the following command:

```

~/ModusToolbox/tools_3.3/fw-loader/bin/fw-loader.exe --device-list

```

### **6 Edge Protect Tools**

This will provide you with a connected device, including their respective probe IDs. If you have multiple MiniProgs connected to your system, specify the correct probe ID in the provision-device command. For example,

```

edgeprotecttools -t psoc_c3 provision-device -p policy/policy_oem_provisioning.json --probe-id

061003B803260400

```

If you want to lock in the policy parameters and prevent any further modifications to the configuration, you can set the prov\_oem\_complete parameter to true in the policy\_oem\_provisioning.json file and provision the device. Once this parameter is set to true, the device is essentially "locked" and cannot be provisioned again in normal provisioned LCS. This ensures that the configured policy parameters remain unchanged and secure.

### **Code Listing 6**

```

"prov_oem_complete": {

"description": "Indicates OEM assets are finalized in SFLASH",

"warning": "Once the 'prov_oem_complete' parameter value is set to true, it cannot be

changed! No further updates to SFLASH are allowed",

"value": true

},

```

To transition a device to the production LCS, set the target\_lcs parameter to SECURE and provision the device. Once the device is moved to the secure LCS, it is locked into this stage and cannot be provisioned again. Additionally, it is mandatory that the user application be in MCUboot format, as the device will only launch authenticated applications during the secure LCS. This ensures that only trusted and verified applications can run on the device.

### Code Listing 7

```

"device_policy": {

"target_lcs": {

"description": "The LCS to which the transition should be done",

"applicable_conf": "NORMAL_PROVISIONED, SECURE",

"value": "SECURE"

},

```

Note:

The terms NORMAL\_PROVISIONED LCS and DEVELOPMENT LCS are interchangeable, and similarly, SECURE LCS is equivalent to PRODUCTION LCS. The key distinction between DEVELOPMENT LCS and PRODUCTION LCS remain in the requirement for secure boot. In DEVELOPMENT LCS, secure boot is not mandatory, whereas in PRODUCTION LCS, secure boot is a requirement.

### 7 Processing, memory, and peripheral isolation

# 7 Processing, memory, and peripheral isolation

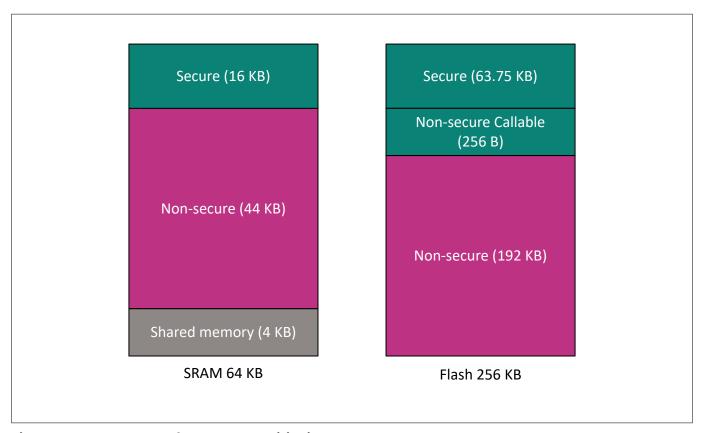

The Cortex M33 CPU of PSOC Control C3 MCU has the Arm TrustZone-M security extension enabled. The extension allows partitioning of the system's resources into two worlds: Secure and Non-secure. Additionally, the extension introduces Secure and Non-secure states to the CPU. In the Secure state, the CPU has access to all the resources on the MCU while in the Non-secure state the CPU has access only to the Non-secure resources. The TrustZone extension adds new access restrictions which isolates resources into Secure and Non-secure worlds at the hardware level.

The TrustZone-M security extension enables you to create an isolated execution environment and execute Secure and Non-secure software on the same M33 CPU. Since the Secure and Non-secure worlds are isolated at a hardware level, there is no information leakage from Secure to Non-secure software. Typically the software, such as bootloader, cryptography service, secure storage service, etc. are executed in the Secure world. The Non-secure software handle communication with the external world and other user tasks. If the Non-secure software requires some service from Secure software, the TrustZone allows it to create Secure entry points to call Secure software from Non-secure software.

The isolation provided by TrustZone is address space based. The memory and peripherals are aliased into two regions in the address space, i.e., same memory/peripheral is mapped in multiple regions in the 4 GB address space. The aliasing is done using the bit 28 of the address. If bit 28 = 0, the address is Non-secure and if bit 28 = 1, the address is Secure. The CPU in Secure state must use the Secure alias for code execution and peripheral access, while in Non-secure state, the CPU must use the Non-secure alias. Table 4 shows how the 256 KB flash, 64 KB RAM, and peripherals of the MCU are mapped to multiple address ranges.

Table 4 PSOC™ Control C3 memory and peripheral address mapping

| Memory/peripheral | Address range                                             | Alias      |

|-------------------|-----------------------------------------------------------|------------|

| Flash             | 0x0200_0000 -0x0203_FFFF /<br>0x2200_0000 - 0x2203_FFFF   | Non-secure |

|                   | 0x1200_0000 - 0x1203_FFFF /<br>0x3200_0000 - 0x3203_FFFF  | Secure     |

| RAM               | 0x0400_0000 - 0x0400_FFFF /<br>0x2400_0000 - 0x24200_FFFF | Non-secure |

|                   | 0x1400_0000 - 0x1400_FFFF /<br>0x3400_0000 - 0x3400_FFFF  | Secure     |

| Peripherals       | 0x4200_0000 - 0x43FF_FFFF                                 | Non-secure |

|                   | 0x5200_0000 - 0x53FF_FFFF                                 | Secure     |

On top of TrustZone, protection context (PC) is implemented in PSOC™ Control C3 MCU for additional security. Protection context is a protection mechanism, which provides the ability to restrict memory and peripheral resources between multiple masters or from the same master executing multiple applications. Protection context adds an additional attribute to bus masters on top of the Non-Secure (NS) and Privilege attribute. This additional attribute is used for isolating resources by memory protection controller (MPC) and peripheral protection controller (PPC).

After reset, the M33 CPU starts in Secure state and the BootROM executes in Secure state. The BootROM later transfers the control to the user application. The BootROM does not change the CPU state. The CPU continues to run in a Secure state, therefore, it is required that the first user application must be a Secure application. Depending on the use case, you can build the entire application as Secure software or it can be split into Secure and Non-secure software. If the application is split into Secure and Non-secure software, then ensure that the memory and peripherals are partitioned such that the Non-secure software has access to its resources. The next section describes how the memory is partitioned to enable Non-secure software execution.

### 7 Processing, memory, and peripheral isolation

The majority of the code example for PSOC™ Control C3 are demonstrated as "secure software". Note:

See the "TrustZone" and "Protection units" sections from PSOC™ Control C3 architecture reference manual for more information about TrustZone and protection context and its isolation capabilities.

#### 7.1 **Memory isolation**

Memory isolation (partitioning) in PSOC™ C3 MCU is controlled with implementation-defined attribution unit (IDAU), secure attribution unit (SAU), and memory protection controller (MPC). The memory can be partitioned into Secure, Non-secure, or Non-secure callable (NSC: A special type of Secure region is used for calling Secure software from Non-secure software) regions by configuring these protection units.

IDAU: It provides a fixed (non-configurable) implementation to indicate whether an address is Secure or Nonsecure. It indicates an address as Secure if the 28th bit of address is '1' else, it is marked as Non-secure. The security attribute indication by IDAU is aligned with the address aliasing scheme shown in Table 4.

SAU: It has eight programmable regions to indicate certain address ranges as Secure, Non-secure, or Nonsecure callable. CMSIS provides the necessary assets (APIs and device headers) required to program SAU. SAU and IDAU are implemented as part of TrustZone extension and the attribution units work together to indicate whether an address is Secure or Non-secure, the higher security among the two is used as indication.

MPC: It divides the flash and SRAM on to smaller blocks of 2 KB and configures Non-secure (NS), Read (R), and Write (W) attributes of each memory block for each protection context. If a memory block is marked as Secure, then it can be accessed by Secure alias address and if a memory block is marked as Non-secure, it can be accessed using Non-secure alias address. MPC configuration is stored in the MCU during the device provisioning process through the OEM policy.

The BootROM reads the OEM policy during device initialization and configures the SAU and MPC. After device initialization, the MPC configuration cannot be updated in the run time, the device must be re-provisioned to change it. SAU can be reconfigured in run time by Secure privileged software. Ensure that SAU and MPC configuration are aligned, that is they mark the same set of address range as Secure or Non-secure. In case of conflicting configuration, the program execution can end up in fault.

Depending on the application's needs, you can choose the isolation level required between Secure and Nonsecure software. You can either rely only on TrustZone or use the additional isolation capability of protection context on top of TrustZone. If the context switching latency between Non-secure and Secure is critical, then it is recommended to use TrustZone isolation, as the protection context switching adds an additional overhead, which cannot be desired in certain applications. If security is the utmost priority, then use the additional protection context isolation.

Taking an example to demonstrate how the device memory can be partitioned by configuring SAU and MPC. Assume that a use case requires both Secure (PC2) and Non-secure (PC3) projects and the memory requirements for this application are as shown in Figure 15.

### 7 Processing, memory, and peripheral isolation

Figure 15 **Example memory partitioning**

By default, TrustZone marks the entire memory as secure. SAU registers must be programmed with CMSIS to configure Non-secure and Non-secure callable regions. On Arm® TrustZone technology, see the Armv8-M architecture reference manual and see how SAU registers are configured to create Non-secure and Non-secure callable regions.

This section focuses on how to configure MPC memory access restrictions via the OEM policy.

**Secure memory:** Secure memory uses Secure software in the Secure alias range. Out of reset, all the memory is marked as Secure with read/write access for all PCs that is Non-secure access to the memory is not allowed. Therefore, it is not required to configure the Secure regions in the OEM policy. Non-secure callable region is a type of Secure region and should be treated as Secure region in the MPC configuration. Optionally, you can restrict the Secure access to the memory to PC0-2. To enforce such restrictions, specify the NS, R, and W attributes for each PC. MPC configuration objects must be populated in mpc\_struct\_ram and mpc\_struct\_flash in the OEM policy to configure MPC.

The following objects show how the earlier mentioned memory access restriction can be implemented to configure secure memory regions in SRAM and flash respectively.

### 7 Processing, memory, and peripheral isolation

### **Code Listing 1**

```

"description": "SRAM MPC configuration for secure region. Offset and size in KB. The values

must be multiple of 2 (e.g. 0 KB, 2 KB, 4 KB, 8 KB, ...)",

"offset": "0 KB",

"size": "16 KB",

"attr": {

"description": "The MPC attributes for this memory region",

"comment_1": "WRN allow write, read, and NS only access",

"comment_2": "-RN allow read, NS-only access",

"comment_3": "--- and --N, no access",

"comment_4": "WR- read and write access, but NS=0 only",

"value": {

"pc0": "WR-",

"pc1": "WR-",

"pc2": "WR-",

"pc3": "---"

"pc4": "---",

"pc5": "---",

"pc6": "---",

"pc7": "---"

}

}

}

```

### **Code Listing 2**

```

"description": "Flash MPC configuration for secure region. Offset and size in KB. The values

must be multiple of 2 (e.g. 0 KB, 2 KB, 4 KB, 8 KB, ...)",

"offset": "0 KB",

"size": "64 KB",

"attr": {

"description": "The MPC attributes for this memory region",

"comment_1": "WRN allow read, write, and NS only access",

"comment_2": "-RN allow read, NS-only access",

"comment_3": "--- and --N, no access",

"comment_4": "WR- read and write access, but NS=0 only",

"value": {

"pc0": "WR-",

"pc1": "WR-",

"pc2": "WR-",

"pc3": "---",

"pc4": "---",

"pc5": "---",

"pc6": "---",

"pc7": "---"

}

}

}

```

### 7 Processing, memory, and peripheral isolation

Here, you must specify the start offset of the memory region that they want to configure and the size of the region. As the MPC divides the memory in blocks of 2 KB (both flash and SRAM), both the start offset and size must be a multiple of 2 KB. After setting the offset and size, the value field must be configured. The attr object is used to set up access restrictions for each PC from 0–7. In this case, the region can be accessible by Secure software from PC0-2. So, for "pc0", "pc1", and "pc2", set the value to WR-, which means to write and read access for Secure software. For the rest of the PC that is, "pc3" to "pc7", set their value to ---, which means no access to this region by any software. As mentioned earlier, restricting access to only PC0-2 is optional. If not required, then there is no need to configure Secure regions in the policy.

Note:

The PC0 MPC restrictions configured through the OEM policy are not applied by BootROM. The BootROM executes in PC0, therefore, the PC0 configuration is locked and cannot be configured.

**Non-secure memory:** Non-secure memory is used by Non-secure software in the Non-secure alias range. If the application contains a Non-secure project, the OEM policy must be configured to create Non-secure regions. In this example, the two projects running in PC2 and PC3. The following objects show how Non-secure region can be set for PC2, 3 according to Figure 15 in SRAM and flash respectively.

### **Code Listing 3**

```

"description": "SRAM MPC configuration for non-secure region. Offset and size in KB. The

values must be multiple of 2 (e.g. 0 KB, 2 KB, 4 KB, 8 KB, ...)",

"offset": "16 KB",

"size": "44 KB",

"attr": {

"description": "The MPC attributes for this memory region",

"comment_1": "WRN allow write, read, and NS only access",

"comment 2": "-RN allow read, NS-only access",

"comment 3": "--- and --N, no access",

"comment_4": "WR- read and write access, but NS=0 only",

"value": {

"pc0": "WR-",

"pc1": "WR-",

"pc2": "WRN"

"pc3": "WRN",

"pc4": "WR-",

"pc5": "WR-",

"pc6": "WR-",

"pc7": "WR-"

}

}

}

```

### 7 Processing, memory, and peripheral isolation

### **Code Listing 4**

```

{

"description": "Flash MPC configuration for non-secure region. Offset and size in KB. The

values must be multiple of 2 (e.g. 0 KB, 2 KB, 4 KB, 8 KB, ...)",

"offset": "64 KB",

"size": "192 KB",

"attr": {

"description": "The MPC attributes for this memory region",

"comment_1": "WRN allow read, write, and NS only access",

"comment_2": "-RN allow read, NS-only access",

"comment_3": "--- and --N, no access",

"comment_4": "WR- read and write access, but NS=0 only",

"value": {

"pc0": "WR-",

"pc1": "WR-",

"pc2": "WRN",

"pc3": "WRN",

"pc4": "WR-",

"pc5": "WR-",

"pc6": "WR-",

"pc7": "WR-"

}

}

}

```

To configure memory as Non-secure, the start offset and size must be set up in the JSON objects. After that, the region's attributes can be defined in attr object. Here, the memory to be Non-secure is accessible for PC2 and 3 so, "pc2" and "pc3" must be set to WRN. The access to the rest of the PCs can either be set to WRN for Non-secure access from other PCs or set to WR- so that the memory is Secure accessible from other PCs. If required, the access to other PCs can be removed by setting --- or --N for those PCs.

Note:

Secure software can access Non-secure memory using a Non-secure alias address. For example, in this use case, the flash offset 64 KB to 256 KB is Non-secure. Secure software can access it by using flash based Non-secure address (0x2200\_0000) + 64 KB to 256 KB offset that is, 0x2201\_0000 - 0x2203\_FFFF.

**Shared memory:** It is also possible to set a certain region of memory to be Secure accessible from one PC and Non-secure accessible from another PC. A shared memory can be configured using such access restrictions. In this example use case, shared memory is set up in last 4 KB SRAM. The PC2 access must be set to wr- for Secure software access and PC3 access must be set to wrn for Non-secure access. The following configuration object shows an example configuration for such a shared memory use case.

### 7 Processing, memory, and peripheral isolation

### **Code Listing 5**

```

{

"description": "SRAM MPC configuration for shared memory. Offset and size in KB. The values

must be multiple of 2 (e.g. 0 KB, 2 KB, 4 KB, 8 KB, ...)",

"offset": "60 KB",

"size": "4 KB",

"attr": {

"description": "The MPC attributes for this memory region",

"comment_1": "WRN allow read, write, and NS only access",

"comment 2": "R-N allow read, NS-only access",

"comment_3": "--- and --N, no access",

"comment_4": "WR- read and write access, but NS=0 only",

"value": {

"pc0": "WR-",

"pc1": "WR-",

"pc2": "WR-",

"pc3": "WRN"

"pc4": "--N",

"pc5": "--N",

"pc6": "--N"

"pc7": "--N"

}

}

}

```

Non-secure callable: If the Non-secure software wish to make a call to Secure software, then it is imperative to define the NSC region where NSC veneers can be placed. An NSC veneer is an intermediate target of branch while transitioning from Non-secure to Secure state. When non-secure software makes a call to secure software, it actually branches to the NSC veneer which holds the special SG instruction that performs the security state change and then branches to the actual secure function. If an NSC region is required, use SAU to define those regions in the Secure alias range. CMSIS can be used to write such a code. Ensure that the veneers are placed in NSC regions and not in the normal Secure region. In this example use case, configure one SAU entry to mark the 0x1200\_FF00 - 0x1200\_FFF address range as NSC. On Arm® TrustZone technology, see the Armv8-M architecture reference manual for SAU programming model.

For getting started with a two project application with Secure and Non-secure projects, use the PSOC™ Control MCU: Non-secure empty app template as a starter template. The example project provides a minimal Secure application, which performs basic security configurations and transfers control to a Non-secure application. See the PSOC™ Control C3 MCU: Memory isolation code example to see how partitioned memory regions can be accessed from Secure and Non-secure perspectives.

Note:

If PC isolation is not required, that is both Secure and Non-secure applications running in PC2, the MPC configuration can be done in a similar way. In such cases, configure the Secure and Non-secure regions only for PC2.

### 7.2 Peripheral isolation

The peripherals of the PSOC™ Control C3 MCU are mapped and aliased into the 0x4200\_0000 - 0x43FF\_FFFF/ 0x5200\_0000 - 0x53FF\_FFFF address space. Similar to memory, the peripherals can be configured for Secure or Non-secure access. Partitioning using TrustZone alone is not enough because of limited SAU entries. For fine grain access control, PPC is available in the MCU. The PPC divides the peripheral address space into fixed size

### 7 Processing, memory, and peripheral isolation

smaller regions. A PPC region protects the MMIO registers of a peripheral. PPC is configurable at run time by Secure privileged software. For each PPC region, configure the NS attribute, PC\_MASK (which PCs can access the region), and privileged/unprivileged access restrictions. Secure peripherals can be accessed by Secure software using Secure alias address and Non-secure peripherals can be accessed by both Secure and Nonsecure software using Non-secure alias.

#### 7.2.1 Security aware peripheral protection controller (PPC) regions

There are certain special PPC region whose access control rules differ from the normal PPC region. If the special, aka security aware, PPC region's NS attribute is configured as Non-secure, then the PPC allows the peripheral to be accessed from both Secure and Non-secure alias. The security aware PPC regions are implemented for peripherals, which either understand the Non-secure access attribute or shared between Secure and Non-secure software.

The I/O subsystem of the PSOC™ Control C3 MCU is a security aware peripheral. The I/O subsystem (IOSS) can differentiate between Secure and Non-secure access and can take the decision whether to respond to access. Each I/O pin of the device can be configured as Secure or Non-secure. The behavior of IOSS is as follows:

- If a pin is configured as Secure, it can be accessed only with a Secure alias address

- If a pin is configured as Non-secure, it can be accessed only with a Non-secure alias

- If a Secure pin is accessed with Non-secure alias address or a Non-secure pin is accessed with Secure alias address, the pin's response is Read Zero Write Ignore (RZWI)

This behavior ensures that if Secure and Non-secure pins are configured on the same GPIO port, then a Secure access to the port does not affect the Non-secure pin and a Non-secure access does not affect the Secure pins. The PSOC™ Control MCU: Security aware GPIO code example demonstrates how the PPC can be configured for IOSS to configure a Secure and Non-secure pin on the same port. The example also demonstrates how to configure interrupts for Secure and Non-secure pins.

Security aware PPC regions are also available for Inter-Processor Communication (IPC) peripheral, which can be used for communication between Secure and Non-secure software. In such cases, an IPC channel will be shared between Secure and Non-secure worlds and it should be accessible to both the worlds.

To know more about protection units, see the "Protection units" section of the PSOC™ Control C3 architecture reference manual.

### 8 Firmware upgrade

## 8 Firmware upgrade

The PSOC™ Control C3 MCU offers firmware upgrade capabilities through its Device Firmware Update (DFU) serial interface, which can be accessed via two distinct methods.

- 1. The first method involves utilizing the BootROM DFU serial interface, which provides a direct pathway for upgrading the firmware

- 2. The second method uses the user application (DFU MW: device firmware upgrade middleware) serial interface, offering an alternative route for firmware upgrades

### 8.1 BootROM DFU serial interface

For factory programming and upgrading images with reset, the BootROM-based method is highly recommended. This approach leverages the immutable BootROM, which has built-in support for Infineon's custom serial DFU protocol, enabling firmware upgrades. The DFU serial interface is versatile, accommodating UART, I2C, and SPI ports.

The selection of the DFU serial interface port is determined by the state of two GPIO pins, specifically Port P2.2 and P2.3, which are scanned during power cycles, resets, and not during run time. When DFU is enabled through OEM policy and the P2.2 and P2.3 GPIO pins meet specific conditions, the BootROM launches DFU mode.

Connect the DFU serial interface selection GPIO pins in to pulled high (Vdd) or low (Vss) state according to the DFU port selection table.

Establish the communication between host (DFU Host Tool) and PSOC™ C3 MCU target according to serial interface pins.

Table 5 DFU serial interface selection

| DFU serial interface selection | P2.3 = Vss     | P2.2 = Vdd     | P2.3 = High-Z  |

|--------------------------------|----------------|----------------|----------------|

| P2.2 = Vss                     | Serial disable | UART           | Serial disable |

| P2.2 = Vdd                     | I2C            | SPI            | Serial disable |

| P2.2 = High-Z                  | Serial disable | Serial disable | Serial disable |

**Note**: To set the DFU select pins (P2.2, P2.3) HIGH or LOW, use external pull-up or pull-down resistors of  $1 \text{ k}\Omega$  or less.

Table 6 Serial interface pins

| Pin  | UART | SPI  | 12C |

|------|------|------|-----|

| P8.0 | _    | SS   | _   |

| P8.1 | Rx   | MOSI | SCL |

| P8.2 | _    | MISO | _   |

| P8.3 | Тх   | CLK  | SDA |

Once the image is loaded through the DFU Host Tool, the BootROM authenticates it based on the boot configuration and successfully launches the user application. Figure 16 shows the firmware upgrade process through the BootROM DFU flow.

### 8 Firmware upgrade

Figure 16 Firmware upgrade through BootROM DFU

Connect the DFU serial interface selection GPIO pins in to pulled high (Vdd) or low(Vss) state according to Table 5.

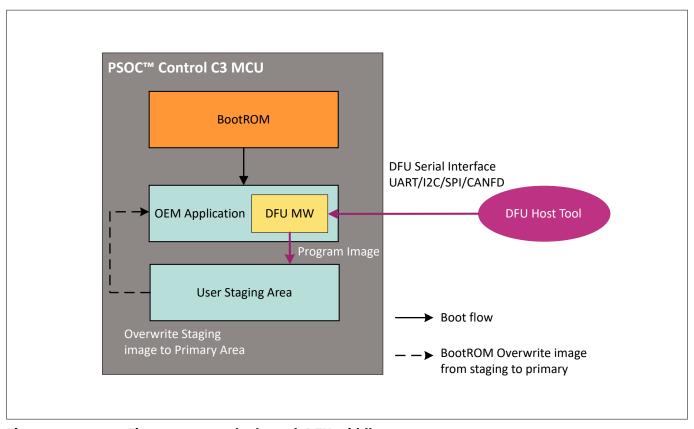

## 8.2 User application (DFU MW) serial interface

For field firmware upgrades, the user application (DFU MW) method is highly recommended. This approach allows to develop the end application using the DFU MW library, which is provided by Infineon as part of the ModusToolbox™ Library manager. Alternatively, you can create your own custom protocol to perform firmware upgrades. Figure 17 shows the firmware upgrade process through the user application using the DFU MW protocol library. Notably, the DFU MW serial interface supports a range of ports, including UART, I2C, SPI, and CAN FD.

One of the key benefits of using the DFU MW library is that it abstracts the underlying complexity of the firmware upgrade process, providing a higher-level interface to interact with. This makes it easier to integrate firmware upgrade capabilities into the user application, without requiring extensive knowledge of the underlying hardware or firmware upgrade protocols.

### 8 Firmware upgrade

Figure 17 Firmware upgrade through DFU middleware

In both the BootROM-based and user application (DFU MW) methods, the Infineon provided PC-based DFU Host tool supports transferring the firmware image to the device. The tool uses the DFU protocol format to transfer the image packet by packet, ensuring a reliable and efficient upgrade process.

The boot configuration of the device determines whether the new image should be signed or unsigned. There are four possible boot configurations: BOOT\_SIMPLE\_APPLICATION, BOOT\_ONE\_SLOT, BOOT\_TWO\_SLOTS, and BOOT\_THREE\_SLOTS.

For the BOOT\_SIMPLE\_APPLICATION configuration, the BootROM does not perform authentication of the image, and the image is expected to be in raw format. This means that the image is not encrypted or signed, and the BootROM will load it directly into the device.

In contrast, for the BOOT\_ONE\_SLOT, BOOT\_TWO\_SLOTS, and BOOT\_THREE\_SLOTS configurations, the image must be signed with the MCUboot format. This ensures that the image is authenticated and verified before it is loaded into the device. The Infineon provided EdgeProtectTool is a useful utility that supports signing the image using the MCUboot format, making it easier to create secure and authenticated firmware images.

Figure 18 shows the MCUboot image structure.

#### 8 Firmware upgrade

Figure 18 MCUboot format

Once the firmware image is prepared, it can be loaded onto the device using the DFU Host Tool via a serial interface. This interface enables the transfer of the image to the device, where it can be authenticated and loaded into memory.

For more information on the image signing process, it is recommended to see the PSOC™ Control MCU: Basic secure application code example and the Edge Protect Tools section. These resources provide detailed guidance on how to sign the image using the MCUboot format, ensuring that the firmware is secure and authenticated.

The PSOC™ Control MCU: Basic secure application code example offers a comprehensive overview of the secure boot process, including the steps involved in signing and verifying the firmware image. The Edge Protect Tools section, on the other hand, provides a detailed guide on how to use the Edge Protect Tool to sign and encrypt the firmware image.

Table 7 Boot configuration

| BOOT configuration          | BOOTROM authentication | Description                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_SIMPLE_APPLICATI<br>ON | No                     | In this configuration, the BootROM does not perform authentication of the new image. Instead, the new image is simply overwritten onto the existing firmware via the serial interface. This configuration is straightforward, but it does not provide any security features to ensure the authenticity of the firmware.                               |

| BOOT_ONE_SLOT               | Yes                    | In this configuration, the BootROM performs authentication of the new image. The one slot address is set during provisioning, and the BOOT_APP_LAYOUT[0] contains the start address and size for the application. This configuration provides a basic level of security, ensuring that the firmware is authenticated before it is loaded into memory. |

(table continues...)

### 8 Firmware upgrade

(continued) Boot configuration Table 7

| BOOT configuration | BOOTROM authentication | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_TWO_SLOTS     | Yes                    | In this configuration, the BootROM also performs authentication of the new image. The primary and staging/secondary slot addresses and sizes are set in boot_app_layout during provisioning. Additionally, the oem_provisioning_policy.json file is referenced, which contains the provisioning policy for the device. This configuration provides a higher level of security, with two separate slots for the firmware image. |

| BOOT_THREE_SLOTS   | Yes                    | In this configuration, the BootROM performs authentication of the new image, and all three slot addresses and sizes are set in boot_app_layout during provisioning. Again, the oem_provisioning_policy.json file is referenced, which contains the provisioning policy for the device. This configuration provides the highest level of security, with three separate slots for the firmware image.                            |

Table 8 shows the list of tools/packages used in firmware upgrade.

#### Table 8 **Tools and packages**

| Tool/package           | Purpose                                                                                                                                                                                                                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFU middleware package | This library provides support for the DFU protocol and enables flash read and write operations.                                                                                                                         |

| DFU Host Tool          | This is a PC-based host tool used to upload the firmware image to the device through a serial interface. The tool offers both a graphical user interface (GUI) and a command-line interface (CLI) for user convenience. |

| EdgeProtectTool        | This tool is used for signing the firmware image, ensuring its authenticity and integrity.                                                                                                                              |

#### 8.3 Firmware upgrade sequence

### **Prerequisite**

The PSOC™ Control C3 MCU must be in the development or production lifecycle stage (LCS). See the Edge Protect Tools section to provision the device.

#### **BootROM DFU serial interface**

- Develop the new firmware (PSOC™ Control MCU: Basic secure application code example) image a. according to the boot configuration and boot app layout

- b. Provision the device with the dfu enable parameter set to "true". If the device is already provisioned with the dfu\_enable flag set to true, skip this step

If using the SWD interface for provisioning, ensure that the DFU port selection pin is in Note: serial disable state. If using a serial interface for provisioning, ensure that the DFU port selection pin is in the respective serial interface enable state

Set the DFU port selection pin according to Table 5 for the selected serial interface c.

If using KitProg, UART and I2C pins are routed through KitProg for DFU communication Note: by default. For SPI upgrade, establish a hardware connection for the SPI interface. See the EVK schematic for the DFU wiring diagram

#### 8 Firmware upgrade

- **d.** Power cycle or reset the device

- **e.** The device's BootROM launches the DFU based on the selected serial interface

- **f.** Open the DFU Host Tool and select the port

- **g.** Configure the serial port parameters:

- 1. UART: Baud rate = 115200, Number of Bits = 8, Stop Bits = 1, RTS/CTS = No, Parity = None

- **2. I2C:** Speed = 400K, Mode = Slave, 7-bit addr, address = 0x35

- 3. SPI: Mode = Slave, Motorola 00 (CPHA = 0, CPOL = 0), Speed <= 12Mbps

- **h.** Select the new firmware image hex file

- i. Click the **Program** button to upload the image to the device. Monitor the firmware upgrade progress in the DFU HT Log window

- **j.** After successful image load, reconnect the serial interface selection pins to the serial disable state

- **k.** Power cycle the device. The BootROM launches the new application image successfully

### 2. Through user application (DFU MW) serial interface

- **a.** Develop the new firmware (PSOC™ Control MCU: Firmware upgrade through DFU MW code example) image according to the boot configuration and boot app layout

- **b.** Load the DFU middleware library from the ModusToolbox™ Quick panel

- **c.** Develop code with reference to mtb\_shared/dfu/release-v5.1.1/docs/html/index.html

- **d.** For more information on developing DFU MW-based code example, see the AN236282 Device Firmware Update (DFU) middleware (MW) for ModusToolbox™

- **e.** At this stage, you have a working DFU MW-based firmware code loaded on the device's primary slot through the SWD/serial interface

- **f.** Power cycle the device

- **g.** Open the DFU Host Tool and configure the serial port parameters:

- 1. UART: Baud rate = 115200, Number of Bits = 8, Stop Bits = 1, RTS/CTS = No, Parity = None

- **2. I2C:** Speed = 400K, Mode = Slave, 7-bit addr, address = 0x35

- **3. SPI:** Mode = Slave, Motorola 00 (CPHA = 0, CPOL = 0), Speed <= 12Mbps

- **h.** Select the new firmware image hex file

- i. Click the **Program** button to upload the image to the device. Monitor the firmware upgrade progress in the DFU HT Log window

- **j.** After successful image load, reconnect the serial interface selection pins to the serial disable state

- **k.** Power cycle the device. The BootROM launches the new application image successfully

### 8.4 Live firmware update

The live firmware update method enables downloading the new firmware and launching it without a device reset. This update mechanism can be employed when the device down time is critical.

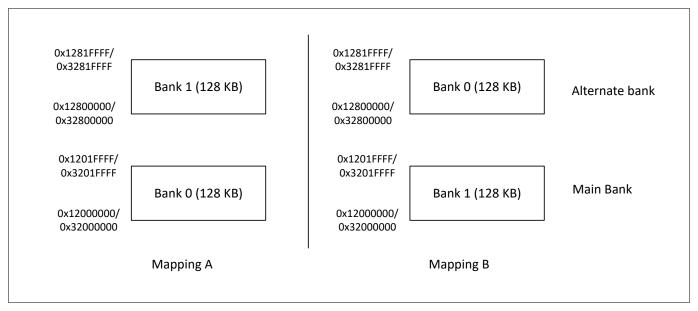

The flash in the PSOC™ Control C3 MCU support dual bank mode. The dual bank feature is key for live firmware update. In dual bank mode, the flash is divided into two equal sized banks called as bank 0 and bank 1.

Table 9 Flash address mapping in single and dual bank mode

| Flash mode | Address                   |  |

|------------|---------------------------|--|

| Single     | 0x1200_0000 - 0x1204_0000 |  |

| Dual       | 0x1200_0000 - 0x1202_0000 |  |

|            | 0x1280_0000 - 0x1282_0000 |  |

The two banks have separate address mapping and are not contiguous in address space. Two mapping modes are available in dual bank mode - mapping A and mapping B. In mapping A, the bank 0 is available at the lower address and bank 1 is at the higher address. In mapping B, the bank 0 is at the higher address and bank 1 is at

#### 8 Firmware upgrade

the lower address. The bank at the lower address is referred to as "Main Bank" and the one at the higher address is referred as "Alternate Bank".

Figure 19 Flash dual bank mode

The bank mode and mapping mode can be controlled via the OEM policy, which must be injected in the device through provisioning. The configuration provided in the policy is applied by the BootROM during the device boot process.

To perform a live firmware update, active firmware is placed and executed from the main bank while the new firmware is downloaded in an alternate bank. The new version of firmware must be downloaded in an alternate bank at the same offset as the active firmware in the main bank. For example, if the active firmware is placed at 0x1200 1000 which is at an offset of 0x1000 in the main bank, then the new firmware must be placed at the same offset in the alternate bank, which is at address 0x1280 1000. When the new firmware is downloaded and authenticated (optional) successfully, the active firmware performs a bank mapping change operation. This operation swaps the location on bank 0 and bank 1 such that the new firmware is moved to the same address from where the previous firmware was executed. Once the mapping is changed, control can be transferred to new firmware (without reset) by calling its "Reset Vector".

Note: The code required for bank mapping change should be executed from SRAM.

This change in firmware version must be conveyed to BootROM so that on the next power cycle the BootROM sets the appropriate bank mapping option such that the new firmware is available in the main bank and can be authenticated (optional) and launched. This is done by incrementing the counter value of the new firmware image. See OEM provisioning parameters for a detailed explanation. Once the bank mapping selection is finalized, the BootROM always launches firmware from a fixed address (in the main bank) specified in OEM policy, therefore, it is essential to place every new firmware at the same offset in an alternate bank so that it is moved to the same address after a bank mapping change is performed.

This method of firmware offers the following:

- 1. Lower downtime compared to other upgrade mechanisms as reset is not required for upgrade operation

- 2. Increases flash life as there is no copy operation. Bank mapping change moves the new firmware to the execution address (main bank address)

- Uses Read While Write (RWW) feature of flash. Allows for code execution during flash write on alternate 3. bank. This ensures that all critical interrupts are serviced on time

The following section describes the OEM provisioning parameters to enable dual bank mode for a live firmware update.

#### 8 Firmware upgrade

#### 8.4.1 **OEM provisioning parameters**

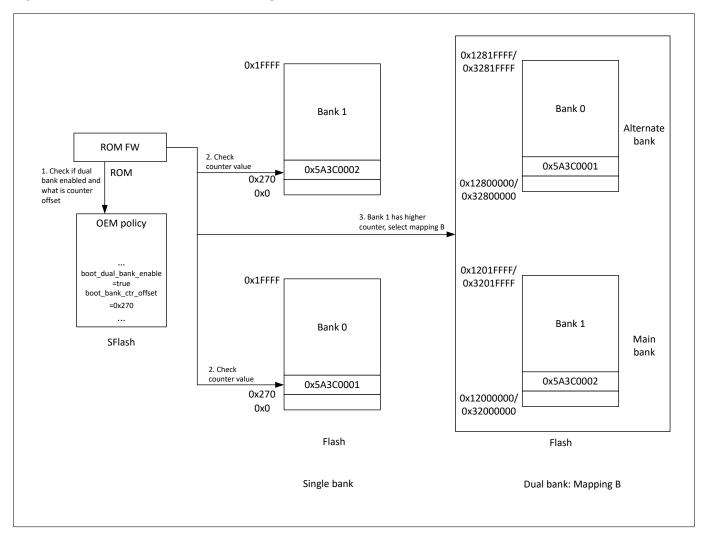

The following parameters in the OEM policy must be configured to enable dual bank mode:

- boot\_dual\_bank\_enable: Set this to "true" to enable dual bank mode during device startup 1.

- boot bank ctr offset: This parameter indicates the address of version/counter of the image. A value 2. between 0-0x1FFFF can be set. The BootROM looks for a counter value at this offset in both bank 0 and bank 1 and compares their value. If the value of the counter is greater in bank 0 than bank 1, the BootROM selects mapping A. If the value of the counter is higher in bank 1 than bank 0, the boot ROM selects mapping B

The counter is a 32-bit number. The upper 16 bits should have a tag value of 0x5A3C and the lower 16 bits for counter value. If the tag is absent/incorrect, the counter is identified as incorrect by BootROM and will not boot to that bank.

Maintaining the correct counter value is the responsibility of users. It can be implemented as part of an image or can be incremented at run time.

Figure 20 shows the flow for bank mapping selection.

Figure 20 **Bank mapping selection**

Dual bank mode works with both signed and unsigned images. To use signed images, set the following additional parameters in the OEM policy.

boot cfg id: Set this to BOOT ONE SLOT for signed images. Else set to BOOT SIMPLE APP for unsigned 1. images

#### 8 Firmware upgrade

- 2. boot\_app\_layout.address: Specify the start address of the signed image

- 3. boot app layout.size: Specify the slot size of the signed image

#### 8.4.2 Firmware upgrade sequence

#### **Prerequisite**

The PSOC™ C3 MCU should be in development or production lifecycle stage (LCS). The dual bank feature must be enabled through OEM policy provisioning. See the Edge Protect Tools section to provision the device.

### Live firmware update through user application (DFU MW) serial interface

- Develop a base version of firmware with counter value 1 using DFU middleware (for firmware download) and program in the main bank

- At this stage, you have a working DFU MW based firmware code loaded on device main bank which can 2. download new firmware through a serial interface