# **About this document**

### **Scope and purpose**

This application note provides guidance on software usage of various SoC peripherals available on CYW20829 along with its use cases.

### **Intended audience**

This document is intended for application developers of AIROC™ CYW20829 who are interested in understanding the features and peripherals of CYW20829.

# **Table of contents**

|         | About this document                  | 1  |

|---------|--------------------------------------|----|

|         | Table of contents                    | 2  |

| 1       | Overview of CYW20829                 | 6  |

| 1.1     | Features                             | 6  |

| 1.2     | Block diagram                        | 7  |

| 1.3     | Software architecture                | 8  |

| 2       | Peripheral management                | 9  |

| 2.1     | Memory                               | 9  |

| 2.1.1   | Typical memory sections of a program | 9  |

| 2.2     | Clock tree                           | 10 |

| 2.2.1   | Features                             | 10 |

| 2.2.2   | Description                          | 11 |

| 2.2.2.1 | Internal main oscillator (IMO)       | 11 |

| 2.2.2.2 | Internal low-speed oscillator (ILO)  | 11 |

| 2.2.2.3 | Precision ILO (PILO)                 | 11 |

| 2.2.2.4 | Frequency-locked loop (FLL)          | 11 |

| 2.2.2.5 | Medium frequency oscillator (MFO)    | 11 |

| 2.2.2.6 | Peripheral clock dividers (PERI)     | 11 |

| 2.2.2.7 | Internal high-speed oscillator (IHO) | 12 |

| 2.2.2.8 | Clock tree                           | 12 |

| 2.2.3   | Software usage                       | 12 |

| 2.2.3.1 | Sequence diagram                     | 12 |

| 2.2.3.2 | Device Configurator                  | 14 |

| 2.2.4   | Applications and code examples       | 15 |

| 2.3     | Serial memory interface (SMIF)       | 15 |

| 2.3.1   | Features                             | 16 |

| 2.3.2   | Description                          | 16 |

| 2.3.2.1 | Block diagram                        | 16 |

| 2.3.3   | Software usage                       | 18 |

| 2.3.3.1 | Sequence diagram                     | 19 |

| 2.3.3.2 | Device Configurator                  | 20 |

| 2.3.4   | Applications and code example        | 21 |

| 2.4     | GPIO                                 | 21 |

| 2.4.1   | Features                             | 22 |

| 2.4.2   | Description                          | 22 |

| 2.4.2.1 | Block diagram                        | 22 |

| 2.4.3   | Software usage                       | 23 |

| 2.4.3.1 | Sequence diagram                     | 23 |

| 2.4.3.2 | Device Configurator                  | 24 |

|         |                                      |    |

| 2.4.4   | Applications and code example    | 25 |

|---------|----------------------------------|----|

| 2.5     | Serial Communication Block (SCB) | 25 |

| 2.5.1   | Features                         | 25 |

| 2.5.2   | Description                      | 26 |

| 2.5.2.1 | SPI                              | 26 |

| 2.5.2.2 | UART                             | 27 |

| 2.5.2.3 | I2C                              | 28 |

| 2.5.3   | Software usage                   | 29 |

| 2.5.3.1 | Sequence diagram                 | 29 |

| 2.5.3.2 | Device Configurator              | 31 |

| 2.5.4   | Applications and code example    | 32 |

| 2.6     | TCPWM/Timer                      | 33 |

| 2.6.1   | Features                         | 33 |

| 2.6.2   | Description                      | 33 |

| 2.6.2.1 | Block diagram                    | 34 |

| 2.6.2.2 | TCPWM counters                   | 34 |

| 2.6.2.3 | TCPWM operating modes            | 35 |

| 2.6.3   | Software usage                   | 36 |

| 2.6.3.1 | Device Configurator              | 36 |

| 2.6.4   | Application and code examples    | 38 |

| 2.7     | Watchdog timer (WDT)             | 38 |

| 2.7.1   | Features                         | 38 |

| 2.7.2   | Description                      | 39 |

| 2.7.2.1 | Block diagram                    | 39 |

| 2.7.3   | Software usage                   | 40 |

| 2.7.3.1 | Sequence diagram                 | 40 |

| 2.7.3.2 | Device Configurator              | 41 |

| 2.7.4   | Applications and code examples   | 41 |

| 2.8     | MCWDT                            | 42 |

| 2.8.1   | Features                         | 42 |

| 2.8.2   | Description                      | 42 |

| 2.8.2.1 | Block diagram                    | 42 |

| 2.8.3   | Software usage                   | 43 |

| 2.8.3.1 | Sequence diagram                 | 43 |

| 2.8.3.2 | Device Configurator              | 43 |

| 2.8.4   | Applications and Code example    | 44 |

| 2.9     | Real time clock (RTC)            | 44 |

| 2.9.1   | Features                         | 45 |

| 2.9.2   | Description                      | 45 |

| 2.9.2.1 | Block diagram                    | 45 |

| 2.9.3   | Software usage                   | 46 |

| 2.9.3.1 | Sequence diagram                 | 46 |

| 2.9.3.2  | Device Configurator                 | 48 |

|----------|-------------------------------------|----|

| 2.9.4    | Applications and code examples      | 49 |

| 2.10     | Datawire                            | 49 |

| 2.10.1   | Features                            | 49 |

| 2.10.2   | Description                         | 50 |

| 2.10.2.1 | Block diagram                       | 50 |

| 2.10.2.2 | Implementation                      | 50 |

| 2.10.2.3 | Trigger Multiplexer (TrigMUX)       | 55 |

| 2.10.3   | Software usage                      | 56 |

| 2.10.3.1 | Sequence diagram                    | 56 |

| 2.10.3.2 | Device Configurator                 | 57 |

| 2.10.4   | Applications and code examples      | 58 |

| 2.11     | CAN                                 | 58 |

| 2.11.1   | Features                            | 58 |

| 2.11.2   | Description                         | 59 |

| 2.11.3   | Software usage                      | 60 |

| 2.11.3.1 | Sequence diagram                    | 61 |

| 2.11.3.2 | PDL interface                       | 61 |

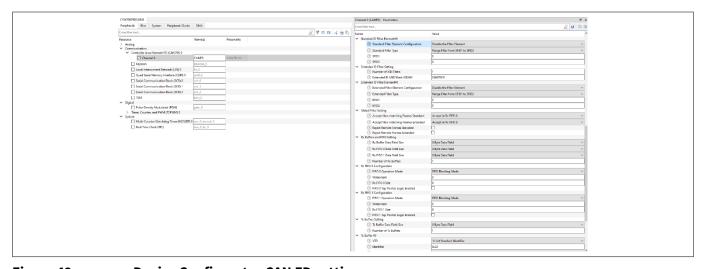

| 2.11.3.3 | Device Configurator                 | 62 |

| 2.11.4   | Applications and code example       | 63 |

| 2.12     | Smart I/O                           | 63 |

| 2.12.1   | Features                            | 63 |

| 2.12.2   | Description                         | 63 |

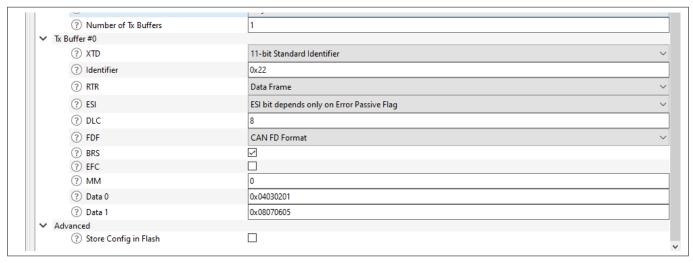

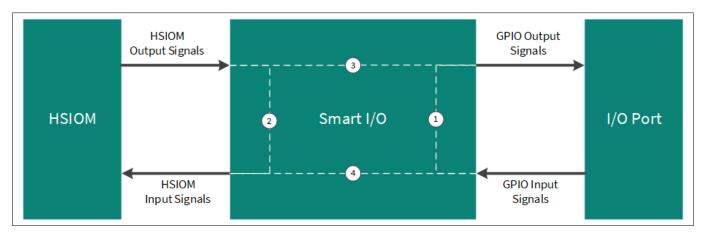

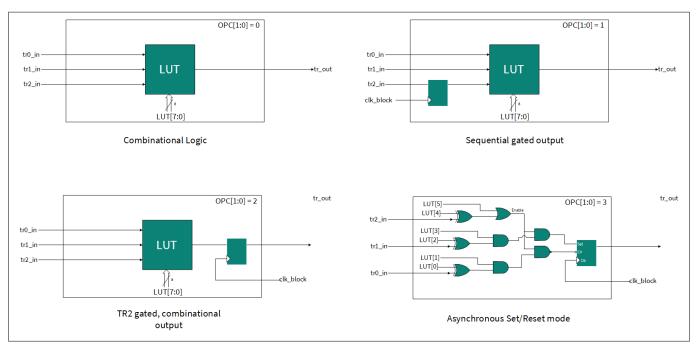

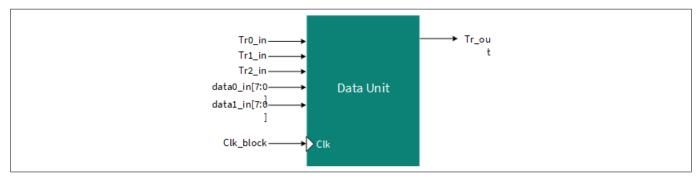

| 2.12.2.1 | Block diagram                       | 64 |

| 2.12.2.2 | Block components                    | 64 |

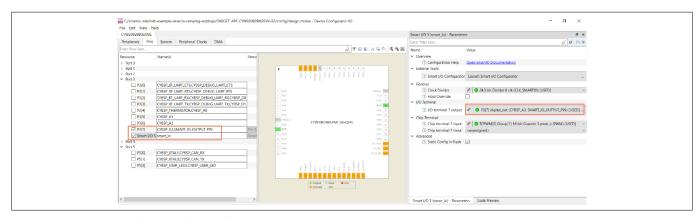

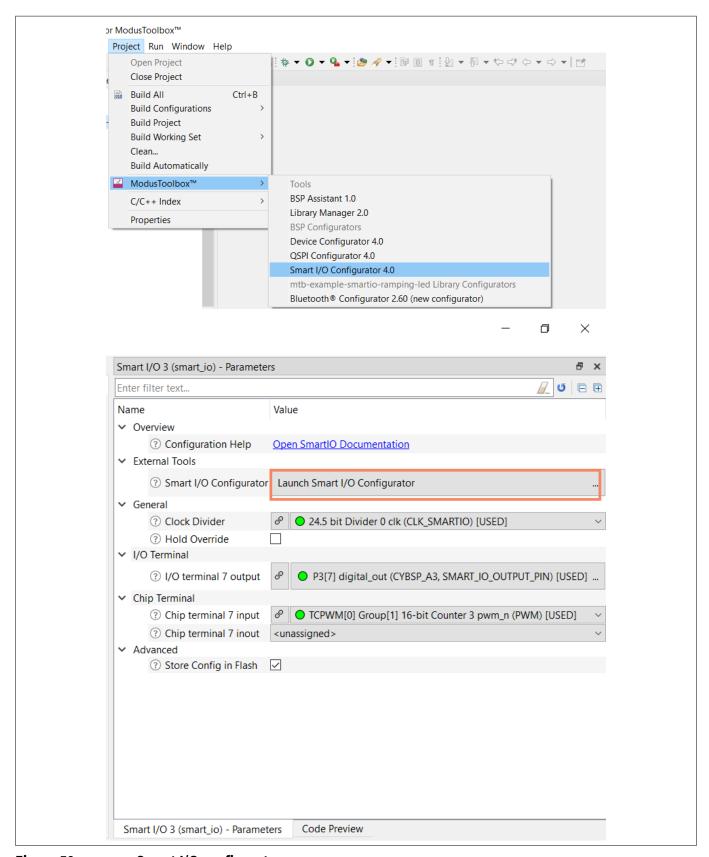

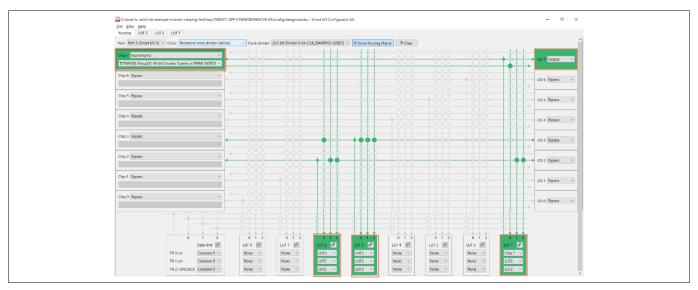

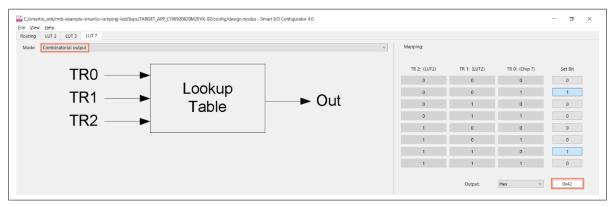

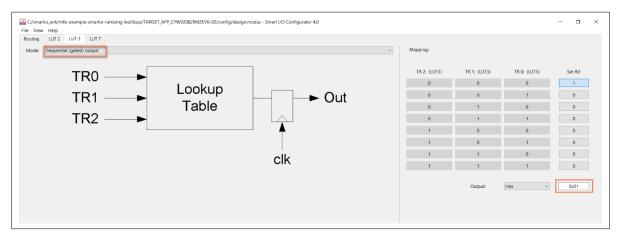

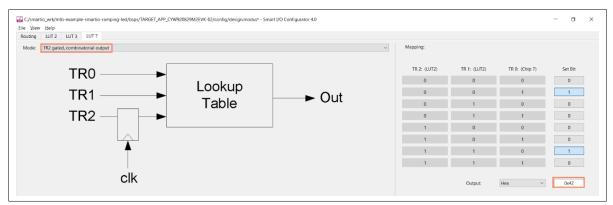

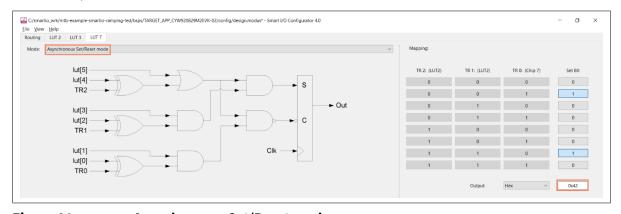

| 2.12.3   | Software usage                      | 67 |

| 2.12.3.1 | Smart I/O configuration flow        | 67 |

| 2.12.3.2 | Device Configurator                 | 67 |

| 2.12.4   | Applications and code examples      | 73 |

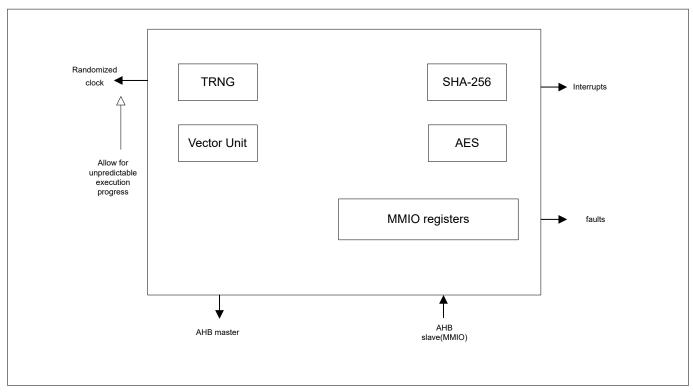

| 2.13     | Cryptolite                          | 74 |

| 2.13.1   | Introduction                        | 74 |

| 2.13.2   | Features                            | 74 |

| 2.13.3   | Description                         | 74 |

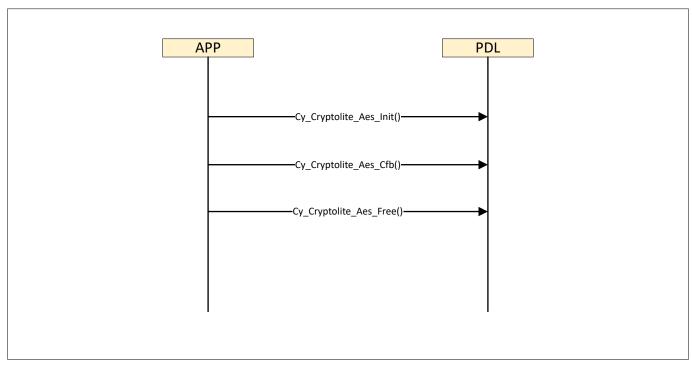

| 2.13.3.1 | Advanced encryption standard (AES)  | 74 |

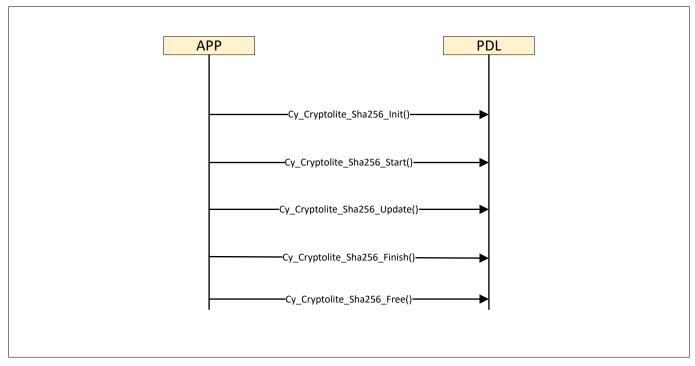

| 2.13.3.2 | Secure hash algorithm (SHA)         | 75 |

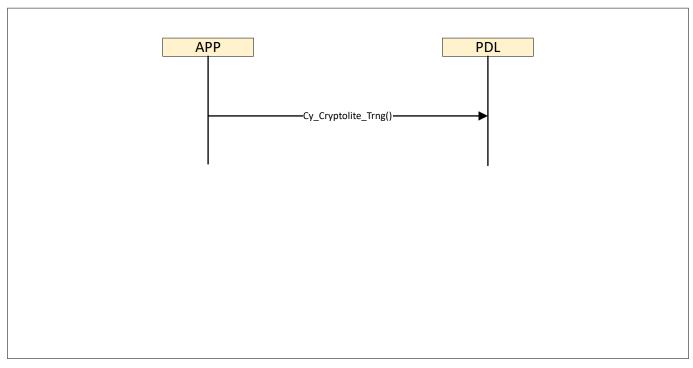

| 2.13.3.3 | True random number generator (TRNG) | 75 |

| 2.13.4   | Software usage                      | 76 |

| 2.13.4.1 | Sequence diagram                    | 77 |

| 2.13.4.2 | Device Configurator                 | 78 |

| 2.13.5   | Applications and code example       | 78 |

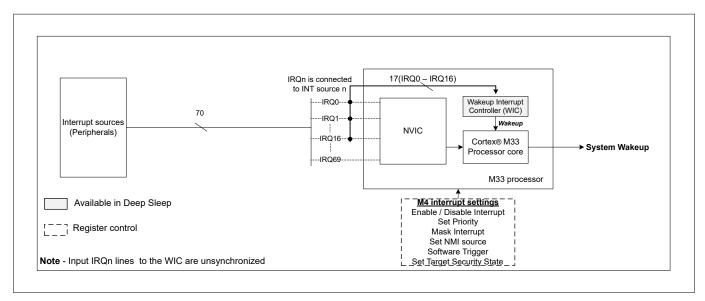

| 2.14     | Interrupts                          | 78 |

| 2.14.1   | Introduction                        | 78 |

| Features                      | 79                                                                                                                                                                                                                                           |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                   | 79                                                                                                                                                                                                                                           |

| Software usage                | 80                                                                                                                                                                                                                                           |

| Applications and code example | 80                                                                                                                                                                                                                                           |

| Trigger multiplexer           | 80                                                                                                                                                                                                                                           |

| Introduction                  | 80                                                                                                                                                                                                                                           |

| Features                      | 80                                                                                                                                                                                                                                           |

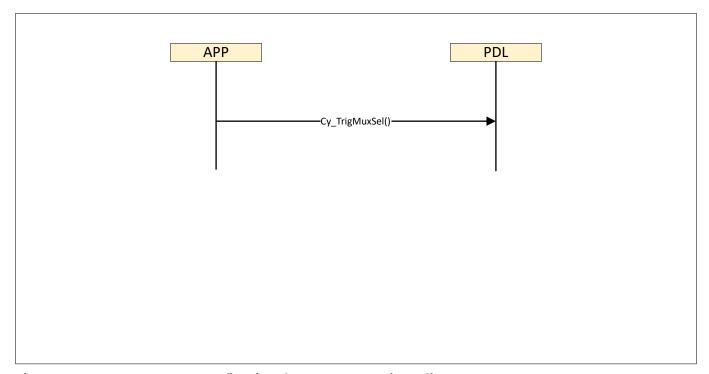

| Description                   | 81                                                                                                                                                                                                                                           |

| Software usage                | 81                                                                                                                                                                                                                                           |

| Sequence diagram              | 81                                                                                                                                                                                                                                           |

| Device Configurator           | 81                                                                                                                                                                                                                                           |

| Applications                  | 82                                                                                                                                                                                                                                           |

| References                    | 83                                                                                                                                                                                                                                           |

| Revision history              | 84                                                                                                                                                                                                                                           |

| Trademarks                    | 85                                                                                                                                                                                                                                           |

| Disclaimer                    |                                                                                                                                                                                                                                              |

|                               | Features Description Software usage Applications and code example Trigger multiplexer Introduction Features Description Software usage Sequence diagram Device Configurator Applications  References Revision history  Trademarks Disclaimer |

### 1 Overview of CYW20829

### 1 Overview of CYW20829

### 1.1 Features

- High-performance compute subsystem with Arm® Cortex® M33 core dedicated for rich real-time embedded applications

- Bluetooth® Low Energy (Bluetooth® LE) controller subsystem with Arm® Cortex® M33 with dedicated ROM and RAM for Bluetooth® operations

- CPU subsystem

- 96-MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M33 CPU

- ARMv8-M architecture

- Core logic operation at either 1.1 V or 1.0 V

- Datawire (DMA) controller with 16 channels

- 32 KB cache for greater eXecute-In-Place (XIP) performance with low power

- 256 KB SRAM with power and data retention control

- 64 KB ROM

- Bluetooth® subsystem

- 48 MHz Arm<sup>®</sup> Cortex<sup>®</sup> M33

- 2.4 GHz RF transceiver with 50 Ω antenna drive

- Configurable TX power for 0 dBm and 10 dBm

- Excellent receiver sensitivity

- LE-1 Mbps: -98 dBm

- LE-2 Mbps: –95 dBm

- Coded PHY 500 kbps (LE-LR): -101 dBm

- Coded PHY 125 kbps (LE-LR): -106 dBm

- Received signal strength indication (RSSI) with 1-dB resolution

- Link layer engine supports up to 16 connections simultaneously, four are peripheral

### 1 Overview of CYW20829

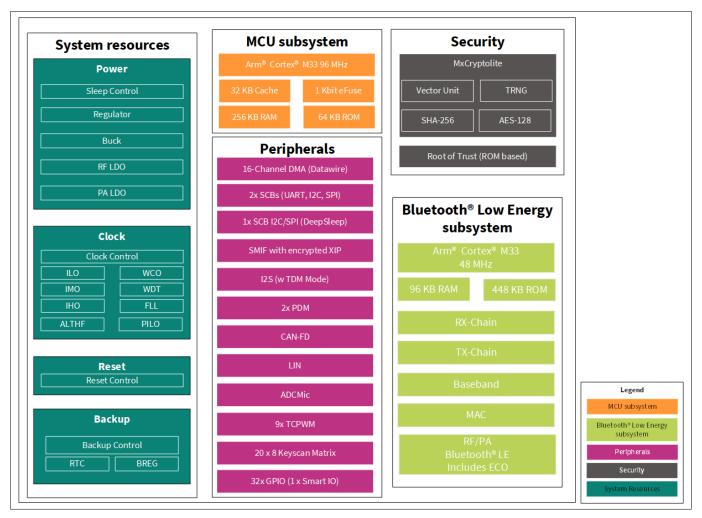

# 1.2 Block diagram

Figure 1 shows the architectural view of CYW20829.

Figure 1 Block diagram

### 1 Overview of CYW20829

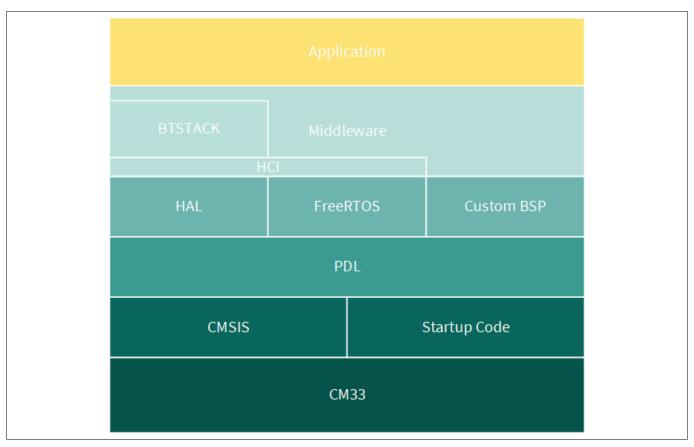

# 1.3 Software architecture

Figure 2 shows the software stack architecture of the CYW20829 CPU subsystem.

Figure 2 Software architecture

### 2 Peripheral management

# 2 Peripheral management

### 2.1 Memory

The CYW20829 follows the Arm® Cortex® M33 compatible memory design architecture. The on-chip memory is isolated across the CPU subsystem and Bluetooth® subsystem. The CPU subsystem consists of 256 KB of RAM, 32 KB of Cache. The Bluetooth® subsystem consists of 448 KB of ROM and 96 B of RAM. The access to Bluetooth® subsystem memory and 64 KB BootROM memory is restricted to user application. The user application will be loaded to external memory such as serial flash or EEPROM and the code will be executed in place. Apart from the application code, some regions of the memory range are occupied for memory mapped on-chip SoC peripherals. These regions of the SoC peripheral memory are readable, writable, non-executable, volatile, and uninitialized at power-up.

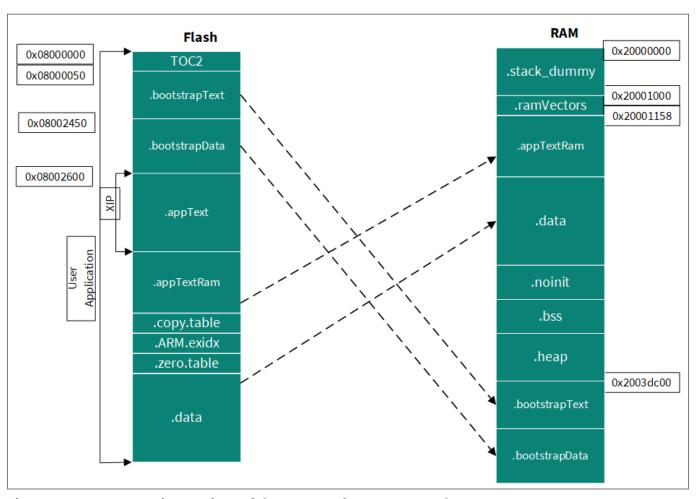

# 2.1.1 Typical memory sections of a program

By default, all the sections of the program memory (serial flash) have the following attributes:

- Readable

- Nonvolatile

Table 1 Program memory sections

| Section              | Start address | End address | Length  | Write | Execute | Initialized |

|----------------------|---------------|-------------|---------|-------|---------|-------------|

| .appText             | 0x08002600    | 0x0800a857  | 0x8258  | FALSE | TRUE    | TRUE        |

| .copy.table          | 0x0800a858    | 0x0800a86f  | 0x18    | TRUE  | FALSE   | TRUE        |

| .ARM.exidx           | 0x0800a870    | 0x0800a877  | 0x8     | FALSE | FALSE   | TRUE        |

| .zero.table          | 0x0800a878    | 0x0800a87f  | 0x8     | TRUE  | FALSE   | TRUE        |

| segment_1            | 0x20000000    | 0x20000113  | 0x114   | TRUE  | FALSE   | TRUE        |

| .ramVectors          | 0x20001000    | 0x20001157  | 0x158   | TRUE  | FALSE   | FALSE       |

| .appTextRam          | 0x20001158    | 0x20003a6f  | 0x2918  | FALSE | TRUE    | TRUE        |

| .data                | 0x20003a70    | 0x20004037  | 0x5c8   | TRUE  | FALSE   | TRUE        |

| .noinit              | 0x20004038    | 0x200040af  | 0x78    | TRUE  | FALSE   | FALSE       |

| .bss                 | 0x200040b0    | 0x2002b833  | 0x27784 | TRUE  | FALSE   | FALSE       |

| .heap                | 0x2002b834    | 0x2003dbff  | 0x123cc | TRUE  | FALSE   | FALSE       |

| .bootstrapText       | 0x2003dc00    | 0x2003f5df  | 0x19e0  | FALSE | TRUE    | TRUE        |

| .bootstrapzero.table | 0x2003f5e0    | 0x2003f5e7  | 0x8     | TRUE  | FALSE   | TRUE        |

| .bootstrapData       | 0x2003f5e8    | 0x2003f603  | 0x1c    | FALSE | FALSE   | TRUE        |

Table 1 shows the typical sections of the application code. Some sections of the program will be copied from an external memory to the RAM, as show in Figure 3.

### 2 Peripheral management

Figure 3 Copying sections of the program form an external memory

### 2.2 Clock tree

CYW20829 provides flexible clocking options with on-chip crystal oscillators, a frequency lock loop, and support for multiple external clock sources. The CYW20829 device clock system provides clocks to the subsystems that require them, and it allows switching between different clock sources.

### 2.2.1 Features

- Internal main oscillator (IMO) at a fixed 8 MHz frequency

- Internal high-speed oscillator (IHO) at a fixed 48 MHz frequency

- Precision internal low-speed oscillator (PILO) at a fixed 32.768 kHz frequency

- Internal low-speed oscillator (ILO) at a fixed 32.768 kHz frequency

- Frequency-locked loop (FLL) for logic clocking up to 96 MHz

- Medium frequency oscillator (MFO) at a fixed 2 MHz frequency

- Additional high-frequency clocks can be generated by division

- PERI Provides the peripheral support

- Watch crystal oscillator (WCO) that requires external crystal with 32.768 kHz frequency

- Enables the configurable clock

- Configurable clock frequency and divider

- Configurable clock sources

### 2 Peripheral management

## 2.2.2 Description

### 2.2.2.1 Internal main oscillator (IMO)

The IMO is the primary source of internal clocking. It is trimmed during testing to achieve the specified accuracy. The IMO default frequency is 8 MHz, and tolerance is ±2%. The IMO output can be used by the PLL or FLL to generate a wide range of high-frequency clocks, or it can be used directly by the high-frequency root clocks.

### 2.2.2.2 Internal low-speed oscillator (ILO)

The ILO operates with no external components and outputs a stable clock at 32.768 kHz nominal. The ILO is a very low-power oscillator, nominally 32 kHz, that operates in all power modes. The ILO can be calibrated against a high-accuracy clock for better accuracy. The ILO is always the source of the watchdog timer (WDT); therefore, enabling the WDT will automatically enable the ILO.

## 2.2.2.3 Precision ILO (PILO)

PILO is an additional source that has better frequency stability than ILO. It is intended to replace a watch crystal in Bluetooth<sup>®</sup> LE products while supporting delay counters that are accurate enough to meet Bluetooth<sup>®</sup> LE requirements. PILO works in Hibernate and higher modes. PILO can be configured to continue operating during XRES for RTC.

# 2.2.2.4 Frequency-locked loop (FLL)

CYW20829 contains one frequency-locked loop (FLL) that resides on clock path 0. The FLL is capable of generating a clock output in the range of 24 MHz to 96 MHz; the input frequency must be between 0.040 Hz and 96 MHz and must be at least 2.5 times less than the CCO frequency. This makes it possible to use the IMO to generate much higher clock frequencies for the rest of the system.

# 2.2.2.5 Medium frequency oscillator (MFO)

There is no actual circuit for MFO and it is generated internally by dividing IMO by 4 to generate 2 MHz clock.

# 2.2.2.6 Peripheral clock dividers (PERI)

There are multiple peripheral clock dividers that, in effect, create multiple separate peripheral clocks. The 8-bit and 16-bit dividers are integer dividers. A divider value of '1' means the output frequency matches the input frequency (that is, there is no change). Otherwise, the frequency is divided by the value of the divider. For example, if the input frequency is 50 MHz and the divider is set to '10', the output frequency is 5 MHz. The five fractional bits support further precision in 1/32nd increments. For example, a divider with an integer value of 3 and a fractional value of 4 (4/32) results in a divider of 3.125. Fractional dividers are useful when a high-precision clock is required, for example, for a UART/SPI serial interface. Integer and fractional clock dividers are provided for peripheral use and timing purposes. There are one or more:

- 8-bit clock dividers

- 16-bit integer clock dividers

- 16.5-bit fractional clock dividers

- 24.5-bit fractional clock divider

### 2 Peripheral management

# 2.2.2.7 Internal high-speed oscillator (IHO)

The IHO operates with no external components and outputs a stable clock at 48 MHz.

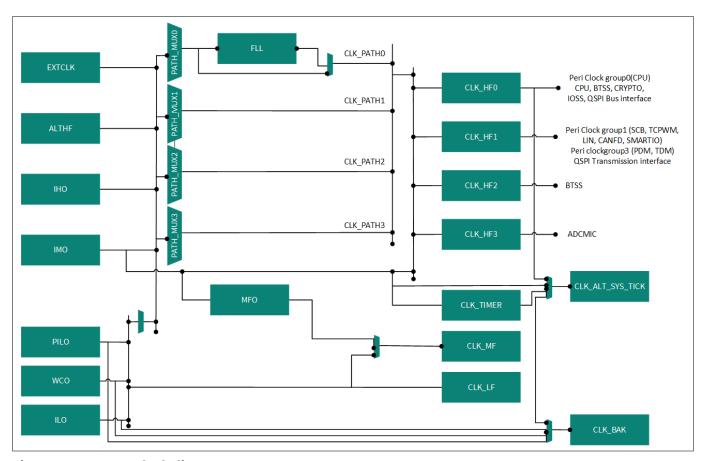

### 2.2.2.8 Clock tree

Figure 4 Block diagram

- CLK\_HF's are the Active mode clocks and it can use any clock source from the following clock sources IMO, IHO, ALTHF, and EXTCLK

- CLK\_LF is a Deep Sleep domain clock and CLK\_BAK is a Hibernate clock and both can select clock sources are from ILO, WCO, and PILO

- IMO is also available in Deep Sleep

### 2.2.3 Software usage

This section describes the software usage of clock trees using PDL APIs and device configurators. For more information, see the clock PDL APIs in clock tree PDL.

### 2.2.3.1 Sequence diagram

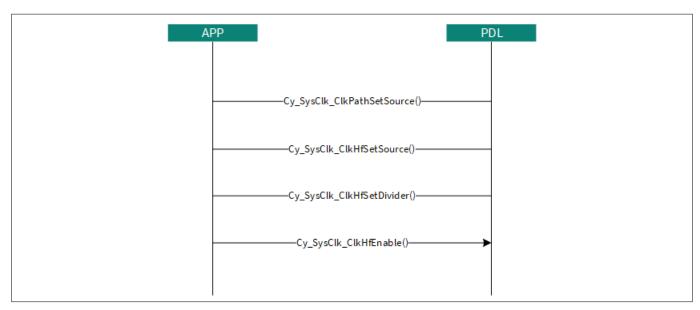

• Enable high-frequency clocks (HF1)

### 2 Peripheral management

Figure 5 Enable high-frequency clocks (HF1)

See the following code block to enable HF1 by using Path 1:

```

/* set the Source of PATH MUX 1 as IMO */

Cy_SysClk_ClkPathSetSource(1U, CY_SYSCLK_CLKPATH_IN_IMO);

/* Set Source of HF Clock as Clk path mux 1 */

Cy_SysClk_ClkHfSetSource(1U, CY_SYSCLK_CLKHF_IN_CLKPATH1);

/*Set the Divider to get the Desired HF frequency */

Cy_SysClk_ClkHfSetDivider(1U, CY_SYSCLK_CLKHF_NO_DIVIDE);

/* Enable Hf1 Clock */

Cy_SysClk_ClkHfEnable(1U);

```

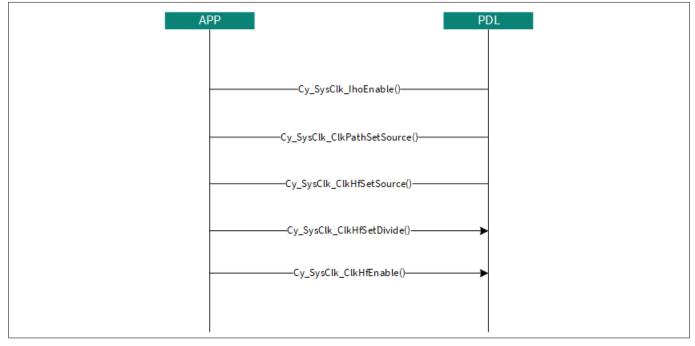

Enable HF3 by changing the source of Clk path mux 1 as IHO

Figure 6 Enable HF3 by changing the source CLK path mux 1 as IHO

### 2 Peripheral management

See the following code block to enable HF3 with the source clock path of IHO:

```

if(!Cy_SysClk_IhoIsEnabled)

{

/* Enable IHO */

Cy_SysClk_IhoEnable()

}

/* set the Source of PATH MUX 1 as IMO */

Cy_SysClk_ClkPathSetSource(1U, CY_SYSCLK_CLKPATH_IN_IHO);

/* Set Source of HF Clock as Clk path mux 1 */

Cy_SysClk_ClkHfSetSource(3U, CY_SYSCLK_CLKHF_IN_CLKPATH1);

/*Set the Divider to get the Desired HF frequency */

Cy_SysClk_ClkHfSetDivider(3U, CY_SYSCLK_CLKHF_NO_DIVIDE);

/* Enable Hf1 Clock */

Cy_SysClk_ClkHfEnable(3U);

```

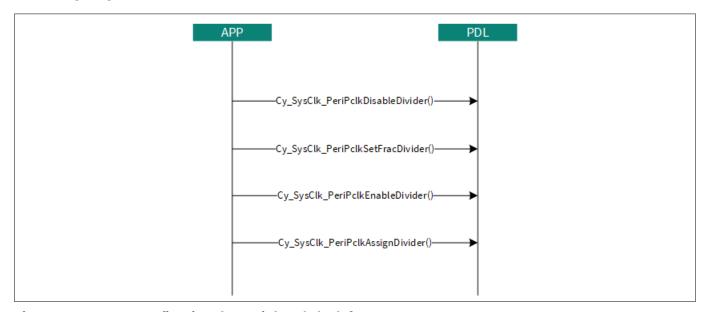

• Configuring the peripheral clock for SCB

Figure 7 Configuring the peripheral clock for SCB

See the following code block to configure the peripheral clock for SCB:

```

Cy_SysClk_PeriPclkDisableDivider(PCLK_SCB2_CLOCK_SCB_EN, CY_SYSCLK_DIV_16_5_BIT, 0U);

/* Sets one of programmable divider for SCB2 */

Cy_SysClk_PeriPclkSetFracDivider(PCLK_SCB2_CLOCK_SCB_EN, CY_SYSCLK_DIV_16_5_BIT, U, 12U, 10);

/* Enable the Selected Divider rrfrrrr */

Cy_SysClk_PeriPclkEnableDivider(PCLK_SCB2_CLOCK_SCB_EN, CY_SYSCLK_DIV_16_5_BIT, 0U);

/* Assigns the Divider to SCB2 block */

Cy_SysClk_PeriPclkAssignDivider(PCLK_SCB2_CLOCK_SCB_EN, CY_SYSCLK_DIV_16_5_BIT, 0U);

```

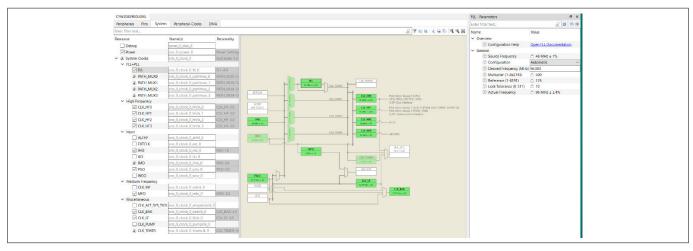

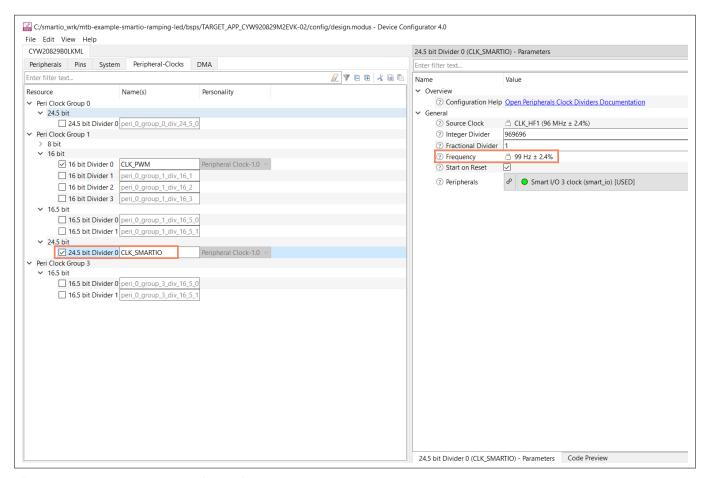

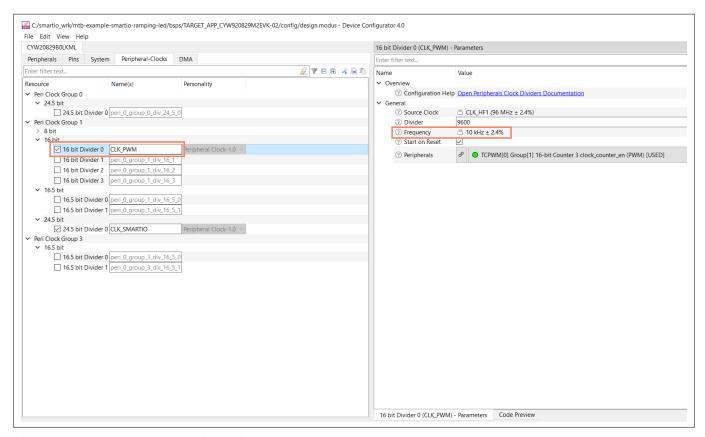

## 2.2.3.2 Device Configurator

The device configurator in ModusToolbox<sup>™</sup> lets you choose various clock sections and their parameters as well. Additionally, you can use HAL APIs to configure basic clock parameters.

### 2 Peripheral management

Figure 8 FLL parameters

Figure 9 Peripheral clock settings

# 2.2.4 Applications and code examples

Clock tree use cases are:

- System clock (systick)

- Periodic functions (Callbacks)

- Simple timer

For example, see CYW20829 clock frequency measurement, which demonstrates how a clock measurement counter can be used to measure the internal clock signal using another clock signal as a reference. Here, the IMO clock is used as a reference clock to measure internal clock signals such as the internal high-frequency clocks HFO, HF1, HF2, and HF3.

# 2.3 Serial memory interface (SMIF)

SMIF is designed to provide a convenient and efficient means of communicating with serial flash memories, enabling the CYW20829 SoC to read, write, and erase data from the memories. By using the SMIF interface, developers can easily integrate serial flash memories into their applications, allowing for more versatile and scalable memory solutions. The SMIF in CYW20829 is an IP for external serial connectivity that provides high-performance communication to the external memories. The SPI-based communication interface to the external quad SPI (QSPI) high-speed memory devices.

### 2 Peripheral management

### 2.3.1 Features

- Supports eXecute-In-Place (XIP) from external quad flash

- Supports DDR

- Supports for single, dual and quad interfaces with throughput up to 384 Mbps

- XIP mode also supports AES-128 based on-the-fly encryption and decryption, enabling secure storage and access of code and data in the external memory

## 2.3.2 Description

The SMIF IP block implements a SPI-based communication interface for interfacing external memory devices to CYW20829. The SMIF supports SPI, dual SPI (DSPI), and quad SPI (QSPI) configurations. The primary usage model for the SMIF is that of an external memory interface, and it operates at a maximum frequency of 48 MHz.

The MMIO mode is used for implementing a generic SPI/DSPI/QSPI/communication interface using the SMIF block. This interface can be used to implement special commands such as program or erase of flash, memory device configuration, sleep mode entry for memory devices, or other special commands specific to the memory device. The transfer width (SPI, DSPI, or QSPI) of a transmission is a parameter set for each transmit and receive operation. Therefore, these can be changed at run time. In a typical memory interface with flash memory, the SMIF is used in the memory mode while reading from the memory, and it switches to the normal mode when writing to flash memory. A typical memory device has multiple types of commands. The SMIF interface can be used to transmit different types of commands.

XIP is a mode of operation where read or write commands to the memory device are directed through the SMIF without any use of API function calls. In this mode, the SMIF block maps the AHB bus accesses to external memory device addresses to make it behave like internal memory. This allows the CPU to execute code directly from external memory.

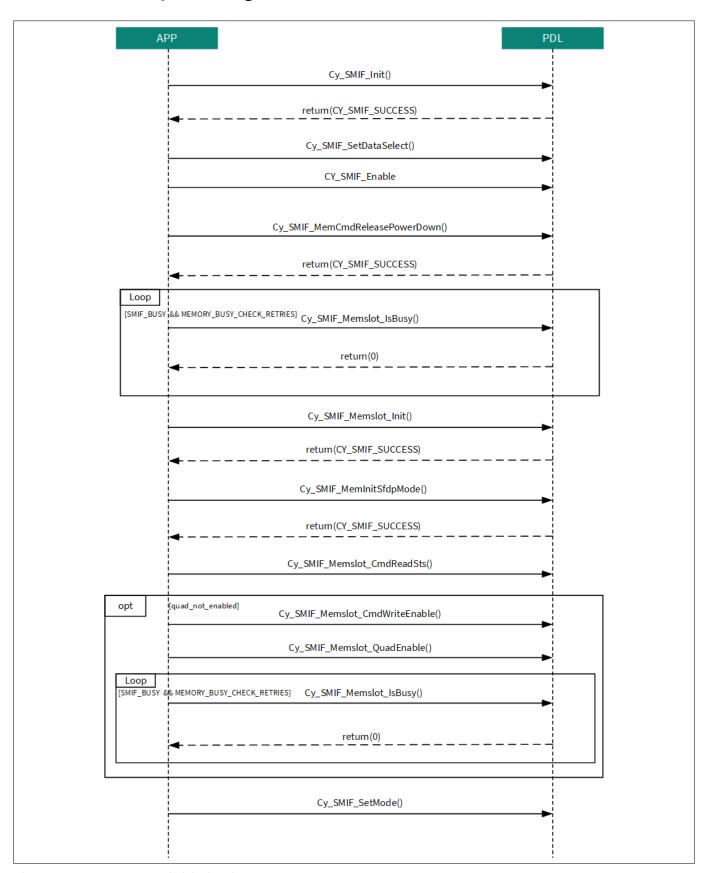

XIP mode is not limited to code and is suitable for data read and write accesses. The memory regions available for XIP address allocation are defined in a linker script file (.ld). The XIP interface is protected by MPC integrated into SMIF, along with associated interrupts and MMIO. Figure 12 shows the SMIF sequence diagram. Call the cybsp\_smif\_init() API to initialize the SMIF. Use the Cy\_SMIF\_MemCmdReleasePowerDown() API to send the release power-down command, and then use the Cy\_SMIF\_Memslot\_IsBusy() API to check if the status of the device is busy.

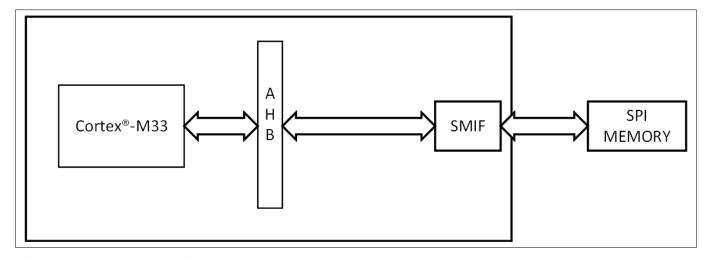

### 2.3.2.1 Block diagram

Figure 10 Block diagram

The SMIF provides the interface between the Cortex -M33 and the external memory device via AHB.

# 2 Peripheral management

The SMIF block maps the AHB bus accesses to external memory device addresses to make it behave like internal memory. This allows the CPU to execute code directly from external memory.

## Table 2 Memory interface

| Memory device     | IO signals                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------|

| Single SPI memory | SCK, CS, SI, and SO. This memory device has two data signals (SI and SO)                           |

| Dual SPI memory   | SCK, CS, IO0, and IO1. This memory device has two data signals (IO0, IO1)                          |

| Quad SPI memory   | SCK, CS, IO0, IO1, IO2, and IO3. This memory device has four data signals (IO0, IO1, IO2, and IO3) |

### 2 Peripheral management

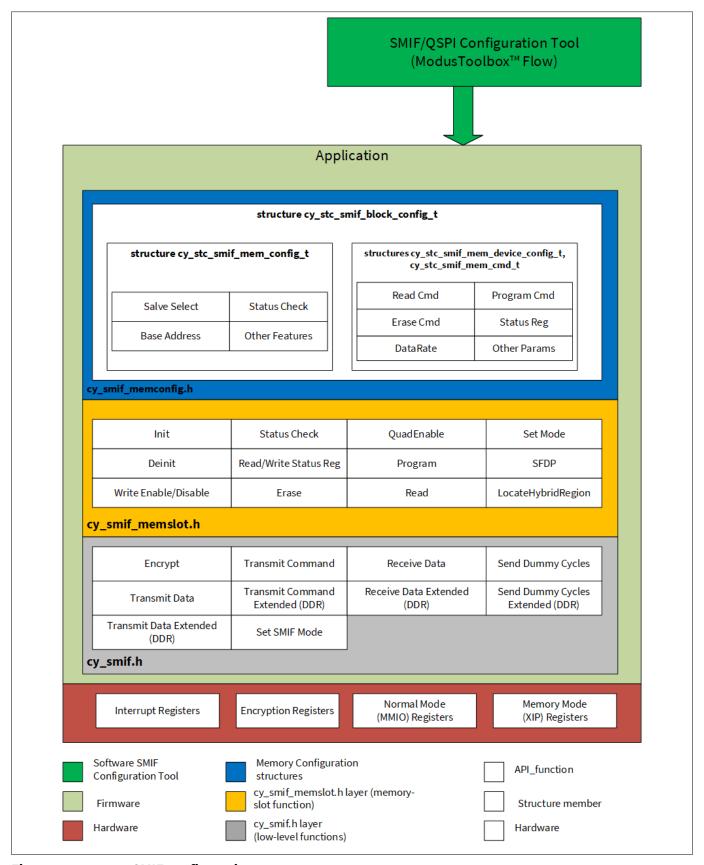

### 2.3.3 Software usage

Figure 11 SMIF configuration

### 2 Peripheral management

# 2.3.3.1 Sequence diagram

Figure 12 SMIF initialization

### 2 Peripheral management

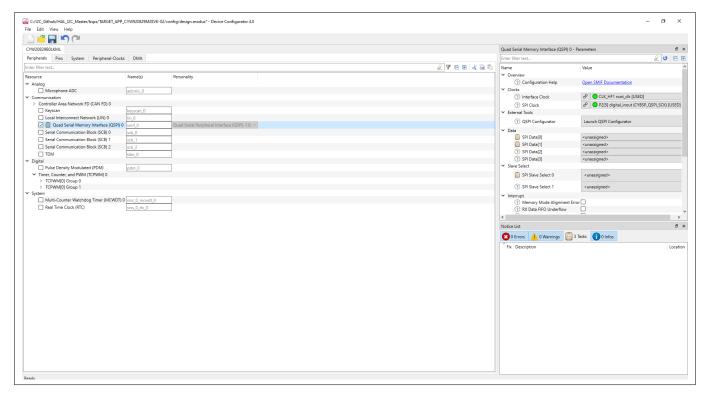

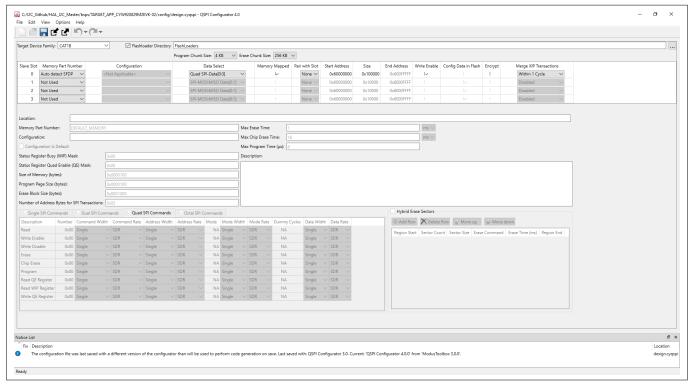

### 2.3.3.2 Device Configurator

Do the following to initialize the SMIF:

- 1. Open the Device Configurator. Navigate to the **Peripheral** tab in the Device Configurator

- 2. Select the checkbox next to the QSPI option

This generates the initialization code. On the right side of the Device Configurator window, you can configure the Interface Clock, SPI Clock, and Data Lines for the SMIF. Additionally, the Device Configurator provides a **Code Preview** window that displays the defines and functions related to the QSPI configuration.

Figure 13 Peripheral interface in the Device Configurator

Additionally, the QSPI configurator provides the flexibility to initialize the QSPI memory configuration. You can select the Memory Part number, Data Select, enable and disable the encryption, and so on.

### 2 Peripheral management

Figure 14 QSPI memory configuration in the Device Configurator

#### 2.3.4 Applications and code example

SMIF use cases are:

- To interface an external flash to the SoC

- To perform XIP ("on-the-fly" translation of read and write transfers on the XIP AHB interface to external memory SPI transfers)

For example, see the following:

- Serial flash read and write, which demonstrates interfacing an external NOR flash memory and performing read and write operations using the serial flash library

- Code example: Demonstrates how to initialize the SMIF for XIP

#### 2.4 **GPIO**

GPIO is a term used to describe a collection of pins or ports that can be found on various electronic devices, including microcontrollers, single-board computers, and embedded systems. These pins are specifically designed to offer a flexible interface for connecting and managing external devices or circuits. The GPIO pins can be configured to serve as either input or output channels, granting the device the ability to receive information from external sensors or transmit signals to control other components. When functioning as input pins, they have the capability to detect the state or voltage level of an external signal. Conversely, when operating as output pins, they can generate or produce signals with varying voltage levels. The number of GPIO pins available on a device may vary depending on the specific hardware being used. Typically, each pin is assigned a unique number or identifier, which is utilized for programmatic interaction. Developers have the ability to write software code that can read the state of input pins or set the state of output pins, enabling them to establish connections with a wide range of external components, such as buttons, sensors, LEDs, and more. The GPIO interface offers a versatile means of communication and control between a device and its external environment.

### 2 Peripheral management

#### 2.4.1 **Features**

- Separate Set, Clear, and Invert Registers for output

- Interrupt configurations on all GPIO pins, edge-triggered on rising, falling, or both edges

- Frozen mode for latching current state

- Overvoltage tolerant pins (OVT\_GPIO)

- Eight drive modes including pull-up/down, open drain drive HIGH and LOW

- Slew rate control to control speed for each GPIO

- Automatic place and route of signals to and from GPIOs

- Analog and digital input and output capability

#### 2.4.2 Description

The configuration information for I/O cells in the GPIO component is communicated through registers. In the power mode of System Deep Sleep, these registers are preserved, while in the Hibernate power mode, they are reset to their default values. In order to enable the Hibernate Interrupt feature, the configuration information of the I/O cells is preserved or frozen when transitioning into System Deep Sleep or Hibernate power modes. Consequently, the configuration signals can be directed within the system's HP (high power), LP (low power), or ULP (ultra-low power) modes.

The configuration of I/O cells encompasses various details, such as the drive mode (pull-up/pull-down) and drive strength. This configuration information may be specific to individual I/O pads, including details like drive mode, drive strength, slew control transitioning (fast or slow), input buffer mode, and more. Through the I/O port, software can access the I/Os to write output signals and read input signals. By leveraging these capabilities, software can carry out bit-banging operations. The signals for GPIO data input, data output, and data output enable in I/O cells are connected via the HSIOM functional connections. The HSIOM register fields determine the specific connection.

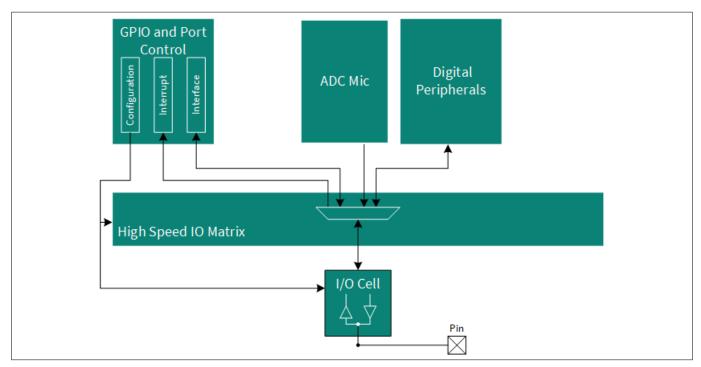

#### 2.4.2.1 **Block diagram**

The GPIO pins establish a connection with I/O cells, which are equipped with an input buffer to facilitate digital input with high input impedance as well as a driver for digital output signals. The I/O cells are linked to digital peripherals through the high-speed I/O matrix (HSIOM). Each pin's HSIOM incorporates multiplexers that establish a connection between the chosen peripheral and the pin.

### 2 Peripheral management

Figure 15 Block diagram

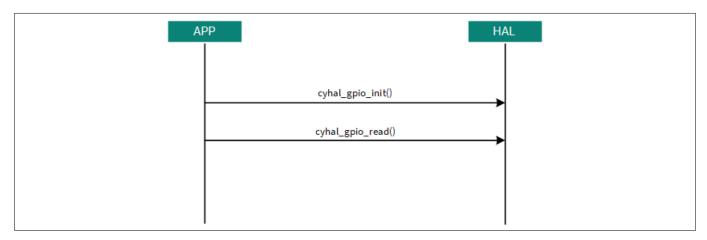

## 2.4.3 Software usage

This section describes about the software usage of GPIO using PDL and HAL APIs and device configurator. For more documentation, see the GPIO HAL APIs and PDL APIs in the following:

- Hardware Abstraction Layer (HAL)

- MTB CAT1 Peripheral Driver Library

# 2.4.3.1 Sequence diagram

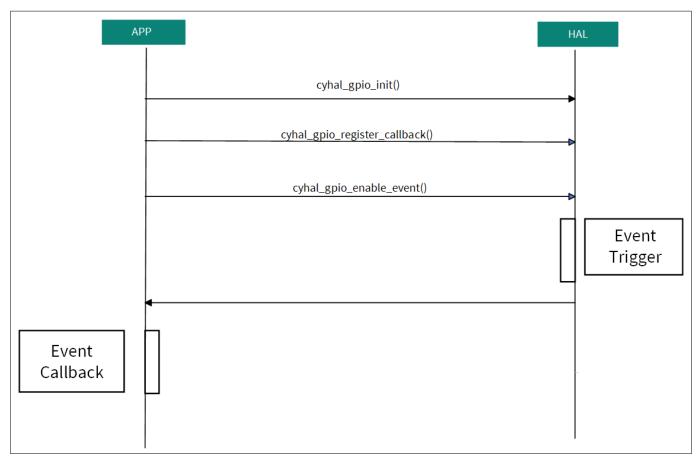

Use case 1: Figure 16 illustrates about the reading the GPIO state.

Figure 16 Reading the GPIO state

Use case 2: Figure 17 illustrates the utilization of a GPIO set as an input pin to produce interrupts.

### 2 Peripheral management

Figure 17 Utilization of GPIO set as an input pin

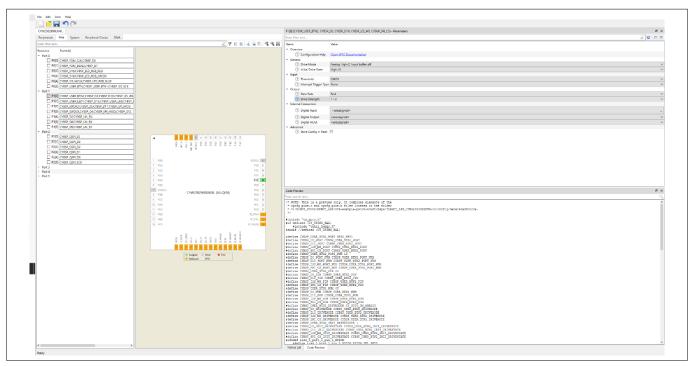

#### **Device Configurator** 2.4.3.2

Do the following to initialize the GPIO:

- Use the following methods to access the Device Configurator: 1.

- Right-click on the project and select ModusToolbox™, and then select Device Configurator Or

- Click Device Configurator in the bottom left corner of the Quick Panel of ModusToolbox™

- Navigate to the Peripheral tab in the Device Configurator 2.

- 3. Select the checkbox in the Pins section

This action generates the initialization code. On the right side of the Device Configuration window, you can configure parameters such as Drive Mode, Initial Drive State, Interrupt Trigger Type, Slew Rate, and **Drive Strength**

Go to File and click Save before closing the Device Configurator. Additionally, the Device Configurator 4. provides a Code Preview window that displays the defines and functions related to the GPIO configuration

Note: Use Device Configurator only for PDL APIs.

### 2 Peripheral management

Figure 18 Device Configurator for GPIO

# 2.4.4 Applications and code example

GPIO use cases are:

- LED Blinking with GPIO and Delay

- · LED Breathing using TCPWM

For example, HAL: GPIO interrupt demonstrates the use of a GPIO configured as an input pin to generate interrupts on an Infineon MCU. The GPIO signal interrupts the CPU and executes a user-defined interrupt service routine (ISR). The GPIO interrupt acts as a wakeup source to wake the CPU from Deep Sleep.

# 2.5 Serial Communication Block (SCB)

The SCB has the capability to support three different serial communication protocols, such as SPI, UART, and  $I^2C$ . However, note the following:

- A SCB can support only one of these protocols at any given time

- Not all SCBs are capable of supporting all three modes (SPI, UART, and I<sup>2</sup>C)

- Not all SCBs operate in Deep Sleep mode. To determine which SCBs operate in Deep Sleep and which SCB is capable of supporting which mode, see the device datasheet for specific information

### 2.5.1 Features

- Standard I<sup>2</sup>C master and slave functionality

- Trigger outputs for connection to DMA

- Each SCB has a 256-byte FIFO for receive (Rx) and transmit (Tx)

- Multiple interrupt sources to indicate status of FIFOs and transfers

### 2 Peripheral management

- Local loop-back control

- Deep Sleep-capable SCB features:

- EZ mode for SPI and I2C slaves, allows for operation without CPU intervention

- CMD\_RESP mode for SPI and I2C slaves ,allows for operation without CPU intervention

- Low-power (Deep Sleep) mode of operation for SPI and I2C slaves (using external clocking)

- Deep Sleep wakeup on I2C slave address match or SPI slave selection

## 2.5.2 Description

Every SCB is equipped with 256-byte dedicated RAM specifically designed for transmit and receive operations. This RAM can be configured in three distinct modes: FIFO mode, EZ mode, and Command-Response mode. Masters can only use FIFO mode. UART only uses FIFO mode. I2C and SPI slaves can use all three modes.

**Note**: EZ and CMD Response modes are available only on the Deep Sleep-capable SCB.

The SCB can receive clock signals from two sources: either an internal clock provided by the peripheral clock dividers or an external master clock. However, for UART, SPI master, and I2C master modes, the SCB must use clk\_scb as the clock source. SPI slave and I<sup>2</sup>C slave modes can utilize the clock from an external master; however, this capability is limited to the Deep Sleep-capable SCBs.

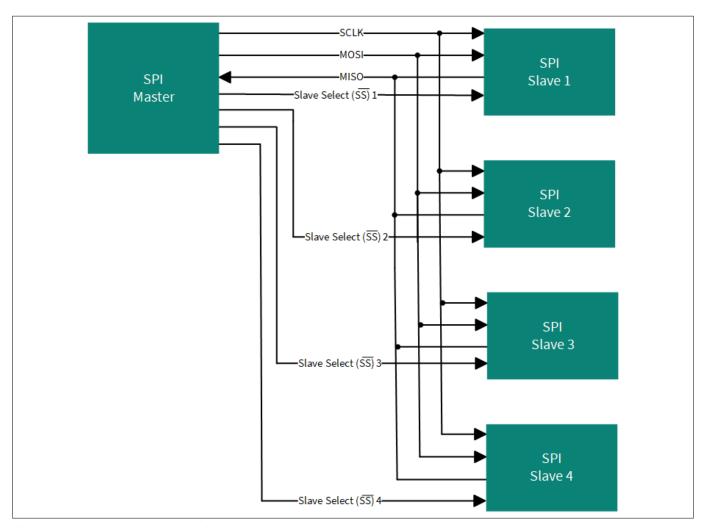

### 2.5.2.1 SPI

The SPI protocol is a synchronous serial interface protocol that allows devices to function in either master or slave mode. Data transfer initiation is the responsibility of the master device. The SCB facilitates a single-master-multiple-slaves topology for SPI communications, with multiple slaves being supported and having their individual slaves select lines. During the SPI data transfer, the master selects a slave by asserting its SS line, and subsequently, it transmits data on the MOSI line along with a clock signal on the SCLK line. Depending on the configuration, the slave captures data on the MOSI line using either the rising or falling edges of the SCLK signal while simultaneously sending data on the MISO line, which is then captured by the master. This block supports the following features.

- Support both master and slave functionality

- Activating wake-up interrupt cause upon slave selection

- Offering three modes: FIFO mode, EZ mode (for slaves only), and CMD\_RESP mode (for slaves only)

- Local loop-back control

- Support interrupts or a polling CPU interface for data handling

### **Block diagram**

A SPI interface has the following four signals:

- SCLK: Clock output from the master, input to the slave

- MOSI: Data output from the master, input to the slave

- MISO: Data input to the master, output from the slave

- Slave Select (SS): Output from the master, input to the slave

### 2 Peripheral management

Figure 19 SPI block diagram

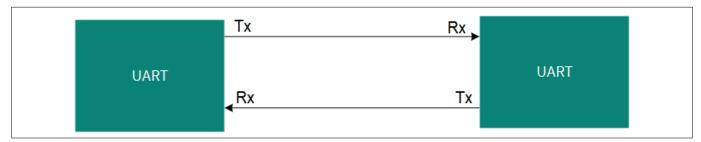

### 2.5.2.2 UART

The UART protocol is an asynchronous serial interface used for point-to-point communication. TX (Transmitter output) and RX (Receiver input) are the two main signals. For flow control in UART, the following two additional side-band signals are utilized; however, note that the flow control applies only to the TX functionality.

- Clear to Send (CTS), an input signal to the transmitter, indicating that the receiver is ready to receive data, allowing the transmitter to send the data

- Request to Send (RTS), an output signal from the receiver, which becomes active when the receiver is ready

to receive data. The RTS of one device is connected to the CTS of the other device and vice versa. Therefore,

when a device (receiver) is prepared to receive data, it activates its RTS, triggering the CTS of the other

device (transmitter), signaling it to send the data

This block supports the following features:

- Data frame size programmable from 4 to 9 bits

- Programmable amount of STOP bits

- Parity support (odd and even parity)

- · Transmitter and receiver functionality

- · Start skipping

- Hardware flow control

### **Block diagram**

### 2 Peripheral management

The UART transfer is initiated with a start bit, followed by several data bits, and optionally a parity bit, concluding with one or more stop bits. The start and stop bits serve to mark the beginning and end of data transmission. The transmitter includes the parity bit, which allows the receiver to identify single-bit errors. Due to the asynchronous nature of the interface, there is no shared clock between the transmitter and receiver. Therefore, both parties must synchronize and settle on the same baud rate for effective communication.

Figure 20 **UART block diagram**

#### I<sub>2</sub>C 2.5.2.3

Every SCB supports both I<sup>2</sup>C master and slave modes. However, only SCB[0] is accessible in system Deep Sleep power mode and permits externally-clocked operations. This section describes the software usage of SCB using PDL and HAL APIs and a device configurator. I<sup>2</sup>C is an asynchronous serial interface that supports single-master, multi-master, and multi-slave configurations. Devices can function as either a master, slave, or master/slave. In master/slave mode, a device switches between master and slave roles depending on the address it receives. During a data transfer, only one master can be active at a time, and this active master is responsible for generating the clock signal on the SCL line. This block supports the following features:

- Master, slave, and master-slave functionality

- Clock stretching

- Multi-master modes and bus arbitration

- Programmable oversampling of I2C clock signal (SCL)

- Wake up from sleep modes

### **Block diagram**

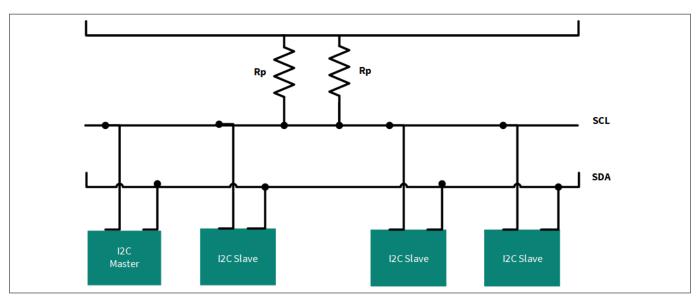

The standard I2C bus consists of two wires, namely Serial Data (SDA) and Serial Clock (SCL). I2C devices utilize open collector or open-drain output stages and are connected to these lines along with pull-up resistors (Rp). Devices in the I2C bus have a straightforward master/slave relationship, and they can function as either transmitters or receivers. Each slave device on the bus is uniquely addressable by a 7-bit address through software.

### 2 Peripheral management

Figure 21 **Block diagram**

#### 2.5.3 Software usage

This section describes the software usage of SCB (SPI, UART, and I2C) using PDL and HAL APIs and a device configurator. For more details on SCB (SPI, UART, and I2C) HAL APIs and PDL APIs, see the following:

- **SPI HAL**

- **UART HAL**

- **I2C HAL**

- **SPI PDL**

- **UART PDL**

- **I2C PDL**

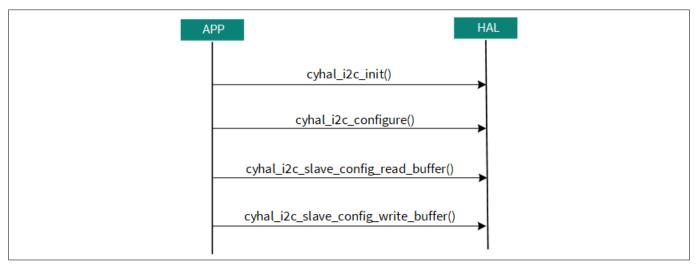

#### **Sequence diagram** 2.5.3.1

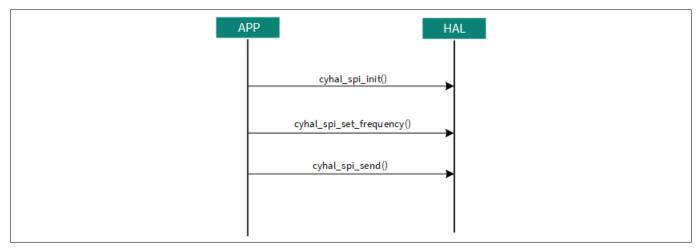

Use case 1: Configuration to send command packets by SPI master.

Figure 22 SPI master command packet transmission sequence

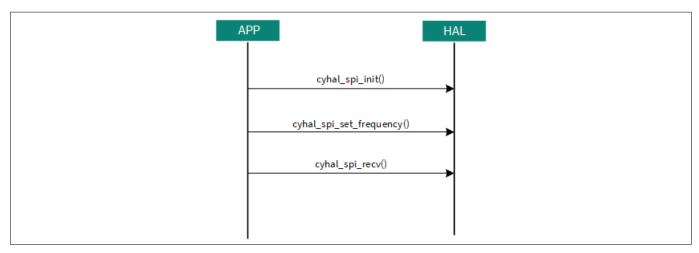

Use case 2: Configuration to receive command packets by SPI slave.

### 2 Peripheral management

Figure 23 SPI slave command packet receive sequence

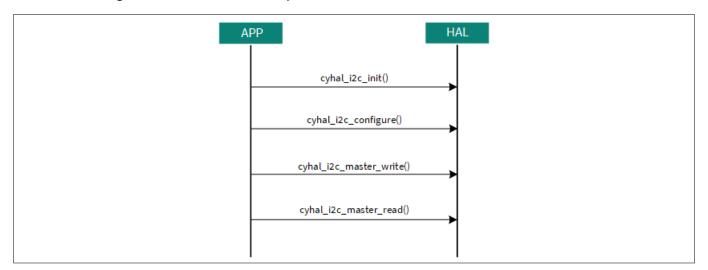

Use case 3: Configuration to read and write by I2C master.

Figure 24 I2C master read and write

Use case 4: Configuration to read and write by I2C slave.

Figure 25 I2C slave read and write

Use case 5: Simple UART communication to read.

### 2 Peripheral management

Figure 26 UART communication

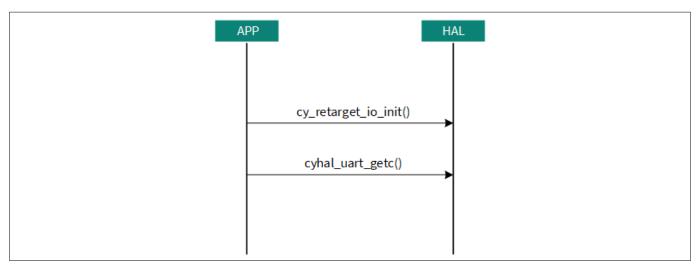

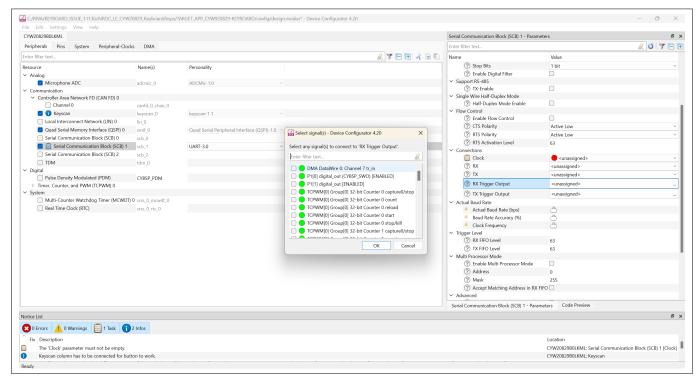

### 2.5.3.2 Device Configurator

Do the following to initialize the SCB:

- 1. Use the following methods to access the Device Configurator:

- Right-click on the project and select ModusToolbox<sup>™</sup>, and then select Device Configurator

Or

- Click Device Configurator in the bottom left corner of the Quick Panel of ModusToolbox™

- 2. Navigate to the Peripheral tab in the Device Configurator

- **3.** Select the checkbox next to the SCB option

- This action generates the initialization code. On the right side of the Device Configuration window, you can configure parameters such as Mode and Enable wakeup from Deep Sleep Mode(SCB0)

- **4.** Go to **File** and click **Save** before closing the Device Configurator. Additionally, the Device Configurator provides a Code Preview window that displays the defines and functions related to the SCB configuration

**Note**: Use Device Configurator only for PDL APIs.

### 2 Peripheral management

Figure 27 Device Configuration for SCB

# 2.5.4 Applications and code example

SCB use cases are:

- SPI

- Communication with external peripheral

- Act as a peripheral device

- Wakeup from Deep Sleep

- UART

- Debug device with a PC

- Redirect Printf to use the UART

- I2C

- Communication with external peripheral

- Act as a peripheral device

- Wakeup from Deep Sleep

For example, see the following:

• HAL: SPI master demonstrates the use of a SPI (HAL) resource in master mode. The SPI master is configured to send command packets to control a user LED on the slave

### 2 Peripheral management

- HAL: SPI slave demonstrates the use of a SPI (HAL) resource in slave mode. The SPI slave is configured to receive command packets to control a user LED on the kit

- Hardware Abstraction Layer (HAL): I2C master demonstrates the use of the I2C resource in HAL in master mode. The I2C master is configured to send command packets to control a user LED on the slave

- Hardware Abstraction Layer (HAL): I2C slave demonstrates the use of the I2C resource in HAL in slave mode. The I2C slave is configured to receive command packets to control a user LED on the kit

- HAL: Hello world demonstrates a simple UART communication by printing the "Hello world" message on a terminal and blinking an LED using a timer resource

# 2.6 TCPWM/Timer

The Timer, Counter, Pulse Width Modulator (TCPWM) block in CYW20829 uses a 16- or 32-bit counter, which can be configured as a timer, counter, pulse width modulator (PWM), or quadrature decoder.

The block can be used to:

- Measure the period and pulse width of an input signal (timer)

- Find the number of times a particular event occurs (counter)

- Generate PWM signals, or decode quadrature signals

This chapter explains the features, implementation, and operational modes of the TCPWM block. TCPWM supports operation in Active, Low power Active, Sleep and Low power Sleep power modes.

### 2.6.1 Features

- The TCPWM block supports the following operational modes:

- Timer-counter with compare

- Timer-counter with capture

- Quadrature decoding

- Pulse width modulation

- Pseudo-random PWM

- PWM with dead time

- Up, Down, and Up/Down counting modes

- Clock prescaling (division by 1, 2, 4, ... 64, and 128)

- 16- or 32-bit counter widths

- Double buffering of compare/capture and period values

- Underflow, overflow, and capture/compare output signals

- Complementary output for PWMs

- Supports interrupt on:

- Terminal count: Depends on the mode; typically occurs on overflow or underflow

- Capture/compare: The count is captured to the capture register or the counter value equals the value in the compare register

# 2.6.2 Description

To enable and disable the TCPWM block, use the TCPWM\_CTRL\_SET and TCPWM\_CTRL\_CLR register bits, respectively. Use these registers to avoid race-conditions on read-modify-write attempts to the TCPWM\_CTRL register, which controls the enable/disable fields of the counters.

### 2 Peripheral management

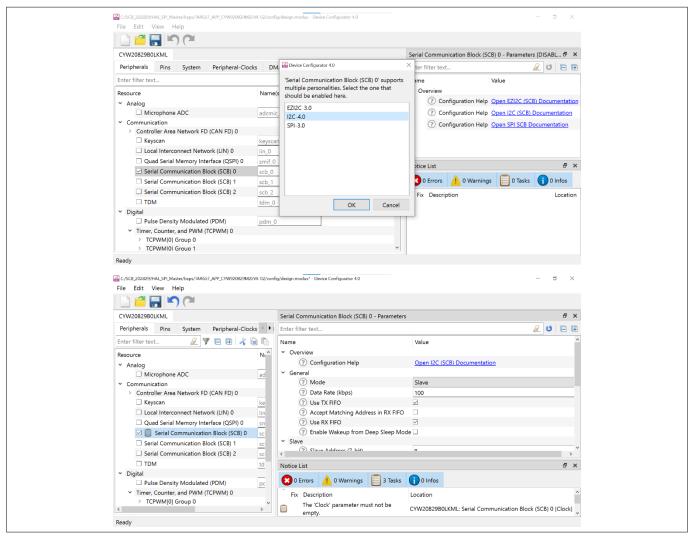

# 2.6.2.1 Block diagram

Figure 28 Block diagram

- The TCPWM block can contain up to 32 counters. Each counter can be 16- or 32-bit wide. The three main registers that control the counters are:

- TCPWM\_CNT\_CC is used to capture the counter value in CAPTURE mode. In all other modes, this value is compared to the counter value

- TCPWM\_CNT\_COUNTER holds the current counter value

- TCPWM\_CNT\_PERIOD holds the upper value of the counter. When the counter counts for n cycles, this field should be set to n-1

The number of 16- and 32-bit counters are device-specific. For more details, see the device datasheet. In this chapter, a TCPWM refers to the entire block and all the counters inside. A counter refers to the individual counter inside the TCPWM. Within a TCPWM block, the width of each counter is the same. TCPWM has following interfaces:

- I/O signal interface: Consists of input triggers (such as reload, start, stop, count, and capture) and output signals (such as pwm, pwm\_n, overflow (OV), underflow (UN), and capture/compare (CC)). All of these input signals are used to trigger an event within the counter, such as a reload trigger generating a reload event. The output signals are generated by internal events (underflow, overflow, and capture/compare) and can be connected to other peripherals to trigger events

- Interrupts: Provides interrupt request signals from each counter, based on TC or CC conditions

### 2.6.2.2 TCPWM counters

Each TCPWM counter can have its own clock source and the only source for the clock is from the configurable peripheral clock dividers generated by the clocking system. To select a clock divider for a particular counter inside a TCPWM, use the CLOCK\_CTL register from the PERI register space.

Each TCPWM block has 14 Trigger\_In signals, which come from other on-chip resources, such as other TCPWMs, SCBs, or DMA. The Trigger\_In signals are shared with all counters inside of one TCPWM block. Use the Trigger Mux registers to configure which signals get routed to the Trigger\_In for each TCPWM block. Two constant trigger inputs, '0' and '1', are available in addition to the 14 Trigger\_In. For each counter, the trigger input source

### 2 Peripheral management

is selected using the TCPWM\_CNT\_TR\_CTRL0 register. Each counter can select any of the 16 trigger signals to be the source for any of the following events:

- Reload

- Start

- · Stop/Kill

- Count

- Capture/swap

Each counter can generate three trigger output events. These trigger output events can be routed through the trigger mux to other peripherals on the device.

The three trigger outputs are:

- Overflow (OV)

- Underflow (UN)

- Compare/Capture (CC)

The TCPWM block provides a dedicated interrupt output for each counter. This interrupt can be generated for a terminal count (TC) or CC event. A TC is the logical OR of the OV and UN events.

Each counter has two outputs: pwm (line\_out) and pwm\_n (line\_compl\_out) (complementary of pwm). Note that the OV, UN, and CC conditions are used to drive pwm and pwm\_n by configuring the TCPWM\_CNT\_TR\_CTRL2 register.

The TCPWM block works in Active and Sleep modes. The TCPWM block is powered from VCCD. The configuration registers and other logic are powered in Deep Sleep mode to keep the states of configuration registers.

## 2.6.2.3 TCPWM operating modes

TCPWM supports six function modes: Timer, Capture, quadrature Decoder, Pulse Width Modulation (PWM), PWM with dead time insertion (PWMDT) and Pseudo random PWM (PWM\_PR). The TCPWM driver is structured to map these functional modes to four high-level operating modes:

### Timer/counter mode:

The timer mode is used to measure the time taken for an event or the time difference between two events. The timer functionality increments and decrements a counter between '0' and the value stored in the PERIOD register. When the counter is running, the count value stored in the COUNTER register is compared with the compare/capture register (CC). When the counter changes from a state in which COUNTER equals CC, the cc\_match event is generated

### Capture mode:

The capture functionality increments and decrements a counter between '0' and PERIOD. When the capture event is activated, the count value in the COUNTER register is copied to CC\_BUFF). The capture functionality is used to measure the pulse width (connected as one of the input triggers and used as a capture event)

### PWM:

Pulse Width Modulation mode (PWM)

The PWM can output a left, right, center, or asymmetrically-aligned PWM. Incrementing or decrementing a counter between '0' and PERIOD and comparing the counter value COUNTER with CC generates the PWM signal. When COUNTER equals CC, the cc\_match event is generated. To generate a pulse-width modulated signal, use the cc\_match event along with overflow and underflow events. Two pulse-width modulated signals, pwm and pwm\_n, are outputs from the PWM

To generate the PWM output signals, use the underflow, overflow, and cc\_match events. Each of these events can be individually set to INVERT, SET, or CLEAR pwm\_dt\_input. The PWM behavior depends on

### 2 Peripheral management

the PERIOD and CC registers. The software can update the PERIOD\_BUFF and CC\_BUFF registers without affecting the PWM behavior. This is the main rationale for double-buffering these registers

- PWM with Dead Time mode (PWMDT)

The PWMDT functionality is the same as the PWM functionality; however, the following are the differences:

- PWM\_DT supports dead time insertion; PWM does not support dead time insertion

- PWM\_DT does not support clock pre-scaling; PWM supports clock pre-scaling

- PWM Pseudo-Random mode (PWMPR)

The PWM\_PR functionality changes the counter value using the linear feedback shift register (LFSR). This results in a pseudo random number sequence. A signal similar to PWM signal is created by comparing the counter value COUNTER with CC. The generated signal has different frequency or noise characteristics than a regular PWM signal

### Quadrature decoder mode:

The Quadrature functionality increments and decrements a counter between '0' and 0xFFFF or 0xFFFFFFFF (32-bit mode). Counter updates are under the following quadrature signal input control:

- The index input is used to indicate an absolute position

- The phiA and phiB inputs are used to determine a change in position (the rate of change in position can be used to derive speed)

## 2.6.3 Software usage

This section describes the TCPWM software usage using HAL and PDL API's. Additionally, it explains the Device Configurator usage.

For more details, see the TCPWM PDL APIs in the following:

- TCPWM PDL

- Timer (Timer/Counter) HAL drivers

- PWM HAL drivers

- Quadrature Decoder HAL drivers

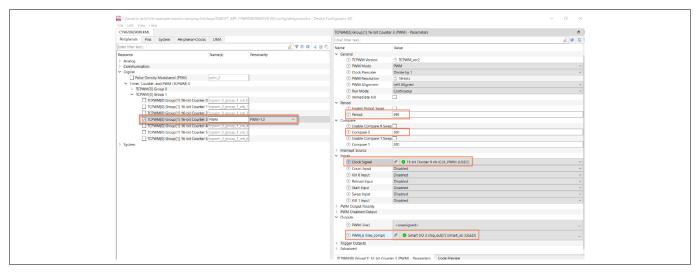

# 2.6.3.1 Device Configurator

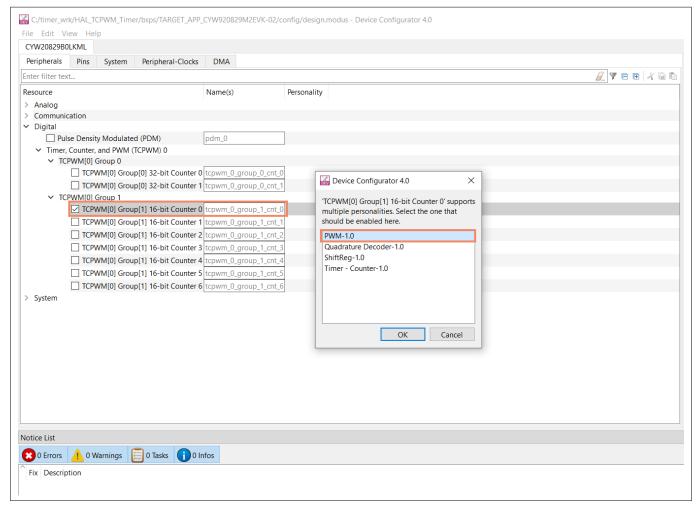

From the Device Configurator, select **32-bit counter** or **16-bit counter** (see Figure 29). TCPWM can be configured in any one of the operating mode.

#### 2 Peripheral management

Figure 29 Device Configurator enable TCPWM

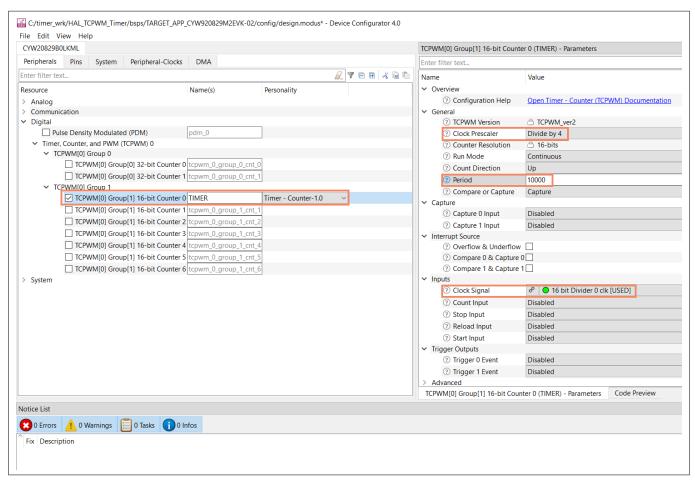

For example, configure the Timer/Counter mode using the following parameters (see Figure 30):

- TCPWM[0] Group [1] 16-bit Counter 0 = Timer and Timer Counter- 1.0

- Clock Prescaler = Divide by 4

- Period = 10000

- Clock signal = 16 bit Divider 0 clk [USED]

## 2 Peripheral management

Figure 30 Device Configurator time configuration

# 2.6.4 Application and code examples

TCPWM can be used in multiple operations anything bound with timing requirements.

The following are the typical applications:

- Timer/Counter: Used in various applications like LED blinking and Events handling

- PWM: Used in many lighting and motor control applications

- Quadrature Decoder: Used in position sensing (e.g., Mouse scroll wheel)

For more details, see the following:

- HAL: TCPWM timer

- HAL: OWM square wave

## 2.7 Watchdog timer (WDT)

The WDT driver provides a low-level interface to the WDT Hardware block. The purpose of using WDT is to recover from CPU or firmware failure by generating a device reset (WRES). It generates periodic interrupts and prevents the system from crashing by resetting the device. The WDT can be used as an interrupt source or a wakeup source in low-power modes.

#### 2.7.1 Features

The WDT component provides the following features:

#### 2 Peripheral management

- CLK LF as the input clock source

- Periodic Interrupt or wakeup generation in Active, Sleep, Deep Sleep, and Hibernate power modes

- Device reset generation if not serviced within a configurable interval

#### 2.7.2 **Description**

WDT has the capability to issue counter match interrupts and trigger a device reset in the absence of interrupt handling. WDT main purposes can be categorized into two use cases:

- The first involves utilizing the WDT to recover from a CPU or firmware failure. By configuring a timeout 1. period within the Watchdog timer, if the specified time elapses without receiving a signal, the device undergoes a reset (WRES)

- The second is used to generate periodic interrupts. Instead of performing a device reset, the WDT can 2. generate an interrupt. This interrupt can be handled by the Interrupt Service Routine (ISR) either as a periodic interrupt or as an early indication of a firmware failure, allowing the watchdog to be cleared

In CPU Active power modes, the watchdog counter has the capability to issue interrupt requests to the CPU, while in CPU Sleep and Deep Sleep power modes, it can send interrupt requests to the wakeup interrupt controller (WIC).

- Active mode: In this mode, WDT is capable of sending an interrupt to the CPU, CPU acknowledges the interrupt request and proceeds to execute the Interrupt Service Routine (ISR). The ISR is responsible for clearing the interrupt

- Sleep or Deep Sleep mode: The interrupt request from the WDT is directly transmitted to the WIC. The WIC is responsible for awakening the CPU. Once the CPU acknowledges the interrupt request, it proceeds to execute the ISR. The ISR firmware is responsible for clearing the interrupt within its operations

- Hibernate mode: Few peripherals such as the WDT remains active. Any interrupt that aims to wake up the device while in this mode will lead to a device reset. There is no specific interrupt service routine or mechanism associated with this particular mode

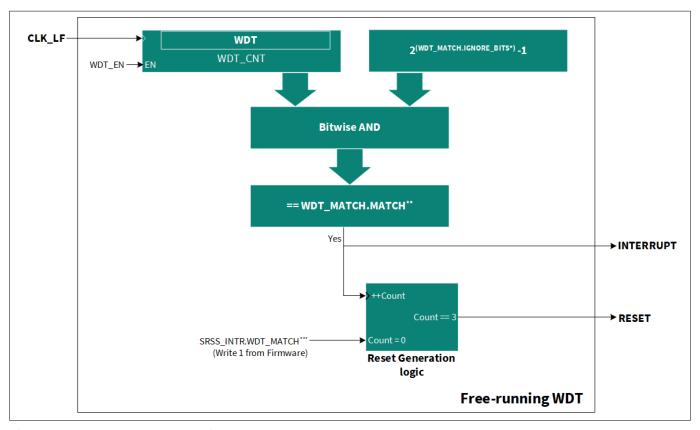

#### 2.7.2.1 **Block diagram**

This section provides an overview of the functionality of the WDT. The WDT consists of a wraparound upcounter that continuously counts. The counter is driven by the CLK\_LF clock. The timer is capable of generating an interrupt when it matches a specified value and triggering a reset event after the occurrence of the third unhandled interrupt. The number of bits utilized for the match comparison can be configured.

#### 2 Peripheral management

Figure 31 WDT block diagram

When WDT is enabled, it increments its counter with each rising edge of the CLK\_LF signal. An interrupt is generated when the counter value matches the value stored in the MATCH bits of the WDT\_MATCH register. Note that the match event does not reset the WDT counter; it continues counting until it reaches the 22-bit boundary (0x3FFFFF). At this point, it wraps around to '0' and starts counting up again. The match interrupt is generated every time the counter value equals the match value, and the WDT\_MATCH bit of the SRSS\_INTR register is set to indicate this interrupt occurrence. To clear the interrupt and reset the watchdog, a '1' must be written to the same bit (WDT\_MATCH bit of SRSS\_INTR). If the firmware fails to clear the interrupt for two consecutive occurrences, the third interrupt results in a device reset. Use the WDT\_EN bit to enable or disable the WDT. The WDT provides an option to set the number of bits to be used for comparison. Use the IGNORE\_BITS of the WDT\_MATCH register to configure the number of LSBs to ignore from the 22-bit count value while performing the match.

# 2.7.3 Software usage

This section describes the software usage of WDT using HAL APIs and PDL APIs. For more details, see the WDT HAL APIs and PDL APIs in the following:

- Hardware Abstraction Layer (HAL)

- MTB CAT1 Peripheral Driver Library

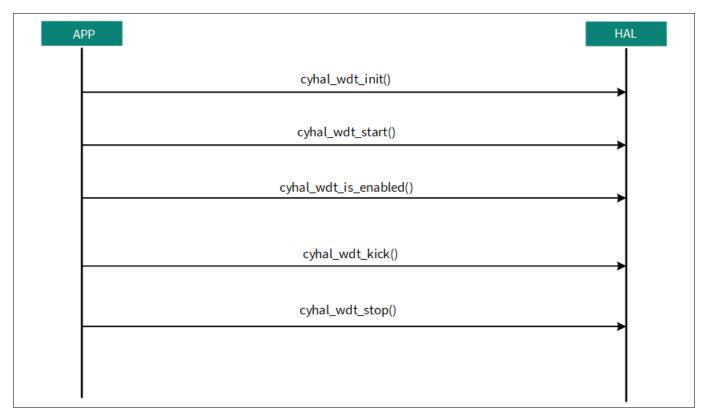

# 2.7.3.1 Sequence diagram

- **1.** Initialize the WDT using the following function:

- cyhal wdt init()

- **2.** Start (enable) the WDT using the following function:

## 2 Peripheral management

**3.** Use the following command to check whether the WDT is enabled:

```

cyhal_wdt_is-enabled()

```

**4.** Reset the device using the following function:

```

cyhal_wdt_kick()

```

This function must be called periodically to prevent the WDT from timing out and resetting the device

**5.** Disable the WDT using the following function:

cyhal\_wdt\_stop()

Figure 32 WDT sequence diagram

## 2.7.3.2 Device Configurator

WDT is not supported in Device Configurator.

# 2.7.4 Applications and code examples

WDT use cases are:

- Generate device reset

- Generate interrupts

- Generate periodic interrupts

For example, HAL: Watchdog Timer demonstrates how to set up a WDT using the WDT HAL resource. The WDT resets the device if it is not serviced or "kicked" within the configured timeout interval. This helps in recovering the program from an unintended lock up.

#### 2 Peripheral management

#### 2.8 **MCWDT**

The MCWDT component offers an interface for configuring one MCWDT hardware block. Each block consists of three counters that can be customized for different system utility functions, including a free-running counter, periodic interrupts, or watchdog reset. Note that besides the MCWDTs, each device also has a standalone watchdog (WDT) that can be utilized to generate a watchdog reset or periodic interrupts.

#### 2.8.1 **Features**

- Device reset generation if not serviced within a configurable interval

- Two 16-bit counters that can be free running, generate periodic interrupts, or generate a watchdog reset

- One 32-bit counter that can be free running or generate periodic interrupts

- Periodic interrupt/wake up generation in LP/ULP Active, LP/ULP Sleep, and Deep Sleep power modes

- All counters are clocked by CLK\_LF

#### 2.8.2 **Description**

The main purpose of MCWDT is to generate periodic CPU interrupts and function as a free-running timer. MCWDT has the capability to produce up to three periodic interrupts. Each MCWDT generates a single combined interrupt. An Interrupt Service Routine (ISR) can handle this interrupt either as a periodic interrupt or as an early indication of a firmware failure requiring the watchdog to be cleared. An alternative application of MCWDT is as a watchdog, serving to recover from CPU or firmware failures. The CLK\_LF serves as the clock source for all the counters, enabling their operation in Active, Sleep, and Deep Sleep modes. However, note that Hibernate mode is not supported for these counters.

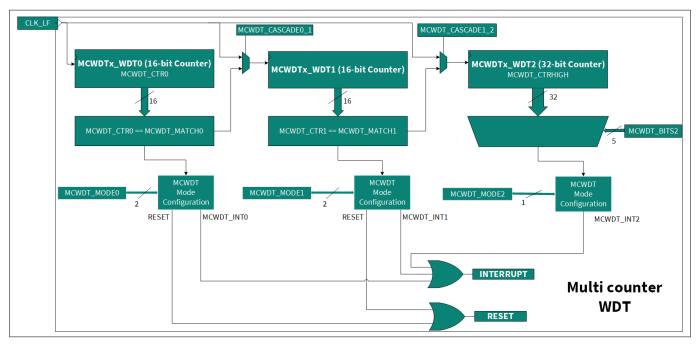

#### 2.8.2.1 **Block diagram**

The functional overview of a multi-counter WDT block in the 20829 MCU reveals the inclusion of one MCWDT (Multi-Counter Watch Dog Timers) block. This MCWDT block consists of two 16-bit counters, namely MCWDTx\_WDT0 and MCWDTx\_WDT1, along with one 32-bit counter known as MCWDTx\_WDT2. These counters can be configured to operate independently or in a cascade configuration, allowing for a maximum counter size of 64 bits. MCWDTx WDT0 and MCWDTx WDT1 are 16-bit up counters, which can be configured to be a 16-bit free-running counter or a counter with any 16-bit period. These counters can be used to generate an interrupt or reset the device. The MCWDTx\_WDT2 is a 32-bit free-running counter, which can be configured to generate an interrupt. All the counters are synchronized by CLK\_LF.

## 2 Peripheral management

Figure 33 MCWDT block diagram

## 2.8.3 Software usage

This section describes about the software usage of MCWDT using PDL APIs and device configurator. For more documentation refer the MCWDT PDL APIs provided in the below links.

PDL doxygen

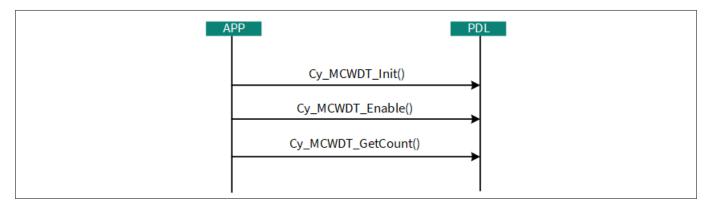

# 2.8.3.1 Sequence diagram

Using the MCWDT Peripheral Driver Library (PDL) resource, a MCWDT can report the current value of the specified counter when operating in free-running mode.

Figure 34 MCWDT sequence diagram

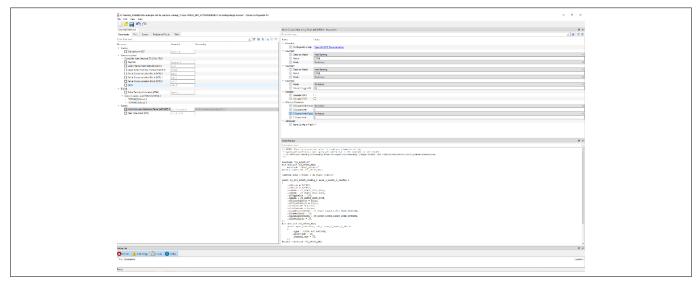

# 2.8.3.2 Device Configurator

Do the following to initialize the MCWDT:

- 1. Use the following methods to access the Device Configurator:

- Right-click on the project and select ModusToolbox™, and then select Device Configurator

## 2 Peripheral management

Or

- Click Device Configurator in the bottom left corner of the Quick Panel of ModusToolbox™

- 2. Navigate to the Peripheral tab in the Device Configurator

- **3.** Select the checkbox next to the MCWDT option.

This action generates the initialization code. On the right side of the Device Configuration window, you can configure Counter0, Counter1, and Counter2

**4.** Go to **File** and click **Save** before closing the Device Configurator. Additionally, the Device Configurator provides a Code Preview window that displays the defines and functions related to the MCWDT configuration

**Note**: Use Device Configurator only for PDL APIs.

Figure 35 Device Configurator for MCWDT

# 2.8.4 Applications and Code example

MCWDT use cases are:

- Periodic Interrupt Generation

- Reset Generation

- Interrupt Generation

- Free running timer

For example, HAL: Low-power timer demonstrates how to configure a low-power timer to measure the timing between events in free-running mode using the LPTimer HAL resource.

# 2.9 Real time clock (RTC)

RTC is a hardware component that is used to keep track of the current time and date as well as the ability to trigger a callback at a specific time. RTCs are commonly used in electronic devices such as computers, smartphones, digital cameras, microwave ovens, washing machines, clocks and other home appliances, IoT, and activity trackers where an accurate and reliable time reference is required. The RTC operates independently of the main system clock and continues to keep track of time even when the system is turned OFF or in Sleep mode. The RTC typically has a battery backup to maintain the timekeeping function; therefore, it can retain the time and date information even when the main power source is disconnected. RTC circuits usually include a crystal oscillator, a counter, and a register for storing the time and date information.

#### 2 Peripheral management

#### 2.9.1 Features

The RTC component supports the following features:

- BCD time and date format

- Configurable alarm

- Century interrupt feature

- Configurable DST

- 12-Hour/24-Hour time format

- Automatic leap year compensation

- Option to drive the RTC by an external 50-Hz or 60-Hz clock source while internal watch crystal oscillator is the default source

## 2.9.2 Description

The RTC is comprised of eight fields, namely RTC\_SEC, RTC\_MIN, RTC\_HOUR, CTRL\_12HR, RTC\_DAY, RTC\_DATE, RTC\_MON, and RTC\_YEAR, all of which are encoded in binary-coded decimal (BCD) format. BCD encoding uses four bits to represent a single decimal digit. The RTC supports both 12-hour and 24-hour time formats, with the "hours" field capable of displaying AM/PM flags. The RTC hardware automatically compensates for leap years, eliminating the need for manual adjustment. Leap years are defined as years that are divisible by 4 or 400 but not by 100.

- To Read and Write, set the READ bit and WRITE bit in the BACKUP\_RTC\_RW register

- The RTC's Alarm feature enables the generation of an interrupt that can wake up the system from Sleep, Deep Sleep, and Hibernate power modes. It consists of six fields that correspond to the RTC fields: Month/Date, Day-of-Week, and Hour: Minute: Second. This allows the RTC to generate an interrupt when the RTC time matches the time set in the ALARM registers. The RTC component physically provides two alarm functions that can trigger an SRSS backup interrupt to prompt an appropriate action on time

- The RTC component offers two modes for DST: fixed date and relative date. When DST is enabled, the

alarm2 block is reserved for executing DST start or stop actions. DST can be optionally enabled and

supports any start and end date, which can either be a fixed date such as March 24<sup>th</sup> or a relative date

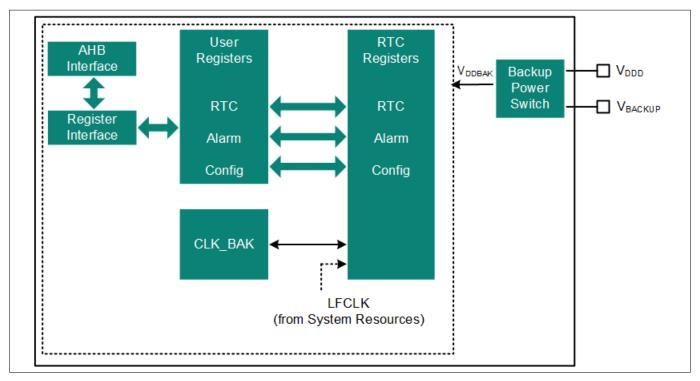

## 2.9.2.1 Block diagram

The RTC comprises two distinct blocks. The AHB RTC user registers contain all RTC settings and synchronize with the actual RTC register. However, the AHB RTC user registers do not update automatically. Instead, they are copied on-demand when a read transaction is initiated from the actual RTC register. To avoid stalling the actual RTC, you are only allowed to access the AHB RTC user register.

## 2 Peripheral management

Figure 36 Block diagram

The components of the RTC are:

- Crystal oscillator: Generates a clock signal that is used by the counter to keep track of the time and date

- Counter: Increments the values of the time and date registers accordingly

- Registers: Store the time and date information

- Battery backup: Maintain the timekeeping function even when the power source is disconnected

- Control logic: Manages the operation of the RTC circuit and interfaces with the rest of the system

- Interface: Provides a way to set the time and date, read the time and date, and configure other RTC functions

#### 2.9.3 Software usage

This section describes the software usage of RTC using PDL and HAL APIs and Device Configurator. For more details on RTC HAL APIs and PDL APIs, see the following:

- RTC HAL

- RTC PDL

## 2.9.3.1 Sequence diagram

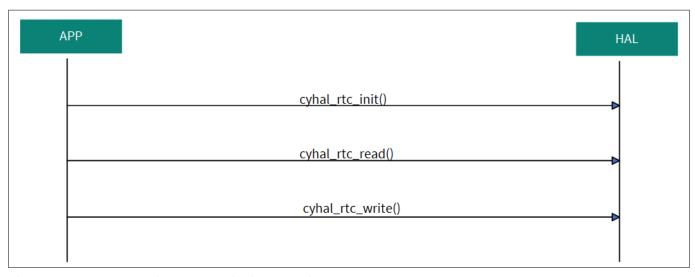

Use case 1: Receive and set the time in the RTC using the RTC HAL API.

Initialize the RTC peripheral using the following function:

cyhal\_rtc\_init()

This initialization step does not alter the RTC's state but grants access to it

• Write the specified time and date to the RTC peripheral using the following function:

cyhal\_rtc\_write()

Conversely, the following function gets the current time and date from the RTC peripheral:

cyhal\_rtc\_read()

## 2 Peripheral management

**Setting and retrieving RTC time** Figure 37

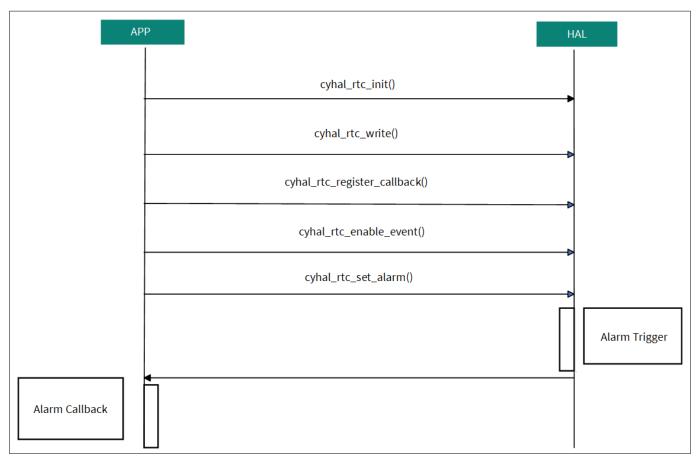

Use case 2: Set the alarm in the RTC using RTC HAL API.

Initialize the RTC peripheral using the following function:

```

cyhal_rtc_init()

```

This initialization step does not alter the RTC's state but grants access to it

Write the specified time and date to the RTC peripheral using the following function:

```

cyhal rtc write()

```

Conversely, the following function gets the current time and date from the RTC peripheral:

```

cyhal_rtc_read()

```

Register an RTC event callback handler using the following function:

```

cyhal_rtc_register_callback()

```

This enables a specific function to execute when an RTC event occurs

Configure RTC events using the following function:

```

cyhal_rtc_register_callback()

```

This allows you to define the desired behavior for different RTC events

Set an alarm (interrupt) for the specified time and date using the RTC peripheral using the following function:

```

cyhal_rtc_set_alarm()

```

This allows you to schedule an alarm that will trigger an interrupt when the specified time and date are reached

## 2 Peripheral management

Figure 38 Configuring RTC alarm

# 2.9.3.2 Device Configurator

Do the following to initialize the RTC:

- 1. Use the following methods to access the Device Configurator:

- Right-click on the project and select ModusToolbox<sup>™</sup>, and then select Device Configurator

Or

- Click Device Configurator in the bottom left corner of the Quick Panel of ModusToolbox™

- 2. Navigate to the Peripheral tab in the Device Configurator

- 3. Select the checkbox next to the RTC option

This action generates the initialization code. On the right side of the Device Configuration window, you can configure Date Format, Enable DST, Time, and Date for the RTC

**4.** Go to **File** and click **Save** before closing the Device Configurator

Additionally, the Device Configurator provides a Code Preview window that displays the defines and functions related to the RTC configuration

**Note**: Use Device Configurator only for PDL APIs.

## 2 Peripheral management

Figure 39 Device Configuration for RTC

## 2.9.4 Applications and code examples

RTC use cases are:

- RTC time keeping and time-stamping

- Set daily alarm or one time alarm

- RTC as a stopwatch

- DST adjustment

- Generate one sec interrupts

For example, see the following:

- HAL: RTC periodic wakeup demonstrates how to enter the Deep Sleep and Hibernate modes and wakeup using the RTC alarm

- HAL: Real-time clock basics demonstrates the usage of the real-time clock (RTC) in the Infineon MCU. It

shows how to get and set the time in the RTC using the RTC HAL API. The example also supports the

daylight saving time (DST) feature. A UART interface is used to input the time and configure the RTC

#### 2.10 Datawire

A Direct Memory Access (DMA) block is specifically designed for data movement and is more power efficient than the CPU for transferring large data blocks. The DMA block provides an independent data transfer engine, which offloads the CPU usage on data transfer use cases. The DMA block in CYW20829 implements a data transfer engine with different configuration options that lets the DMA block be used in different data transfer use cases. This chapter describes the different DMA configurations and use cases. The DMA engine in CYW20829 called Datawire (DW) is specifically designed for transferring small data blocks, typically between peripherals and memory, to offload the CPU from any data transfer with peripherals.

#### 2.10.1 Features

The DMA (Datawire) hardware block has the following features:

- Transfers the data between peripherals to memory without involving the CPU core

- One Datawire block (DW0) that supports up to 16 channels

- Supports multiple instances of DMA channel

## 2 Peripheral management

- Four levels of priority for each channel

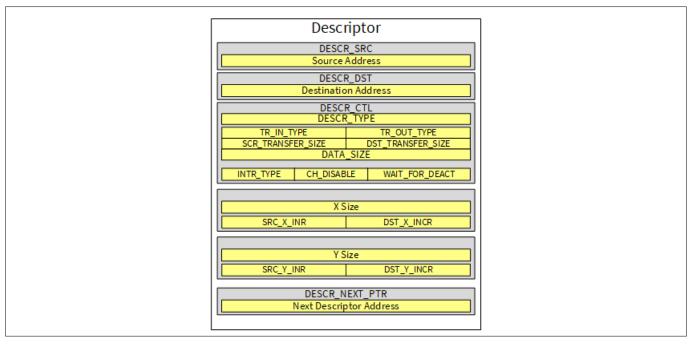

- Various attributes of DMA are configurable through software called DMA descriptors

- DMA Descriptors are defined in memory and referenced to the respective DMA channels

- Supports single-shot, one-dimensional (1-D), and two-dimensional (2-D) transfer modes using DMA descriptor

- Supports transfers up to 65536 data elements per descriptor

- Configurable source and destination address increments

- Supports 8-bit, 16-bit, and 32-bit data widths at both source and destination

- Descriptors can be chained to other descriptors in memory

- Configurable input/output trigger and interrupt generation for each descriptor

- Available in Active and Sleep power mode

## 2.10.2 Description

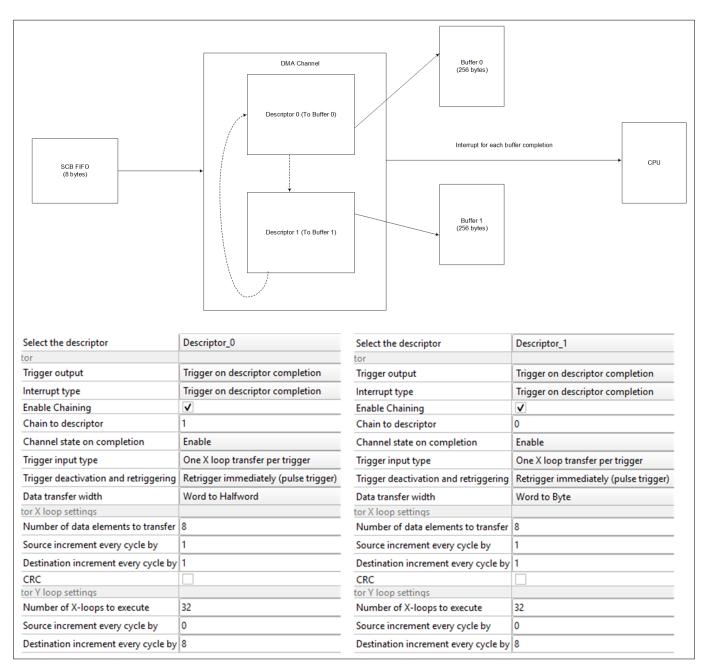

DMA transfers the data to and from the memory, peripherals, and registers. These transfers occur independently from the CPU. DMA can be configured to perform multiple independent data transfers. A channel manages all data transfers. There can be up to 32 channels in the DMA. Datawire focuses on peripheral-to-memory and memory-to-peripheral data transfers (however, it can also perform memory-to-memory data transfers). It is designed to achieve low latency for a large number of channels. It uses a single-data transfer engine that is shared by all channels.

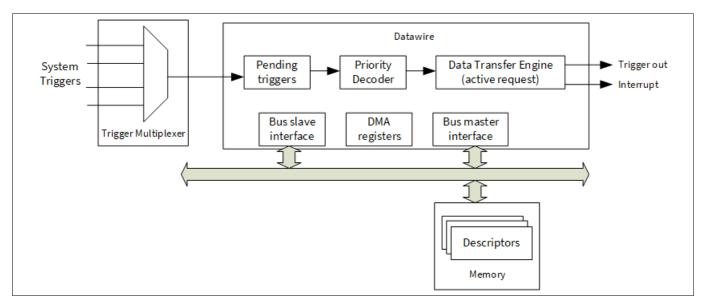

## 2.10.2.1 Block diagram

Figure 40 Block diagram

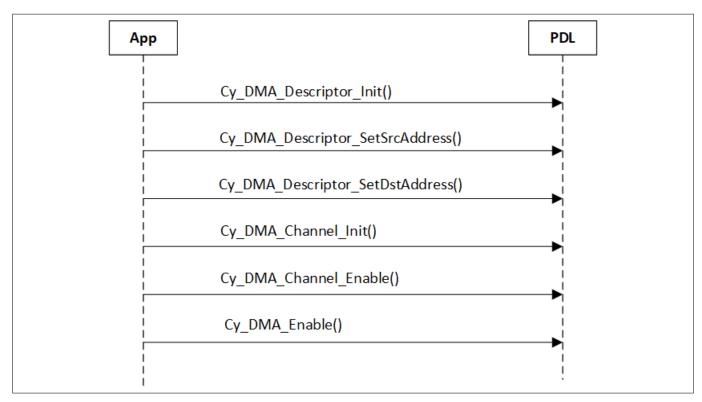

# 2.10.2.2 Implementation

DMA Channels

A single DMA hardware block can support many DMA channels that may be triggered by independent and unrelated events. CYW20829 has one DMA block that supports up to 16 channels. Each DMA channel has a trigger input, trigger output, and interrupt output line. Interrupt signals are routed to individual interrupt lines in the respective CPU. Trigger signals to and from DMA channels are routed through a trigger multiplexer block, which has a device-specific architecture. The trigger multiplexer block enables routing

#### 2 Peripheral management

of trigger signals from different peripherals to the DMA block and routing trigger outputs back to other peripherals

The DMA channels has one of the following four channel states at any given time:

- Disabled: Channel is disabled

- Blocked: Channel is enabled and is waiting for a trigger to initiate the data transfer

- Pending: The channel is enabled and has received an active trigger. In this state, the channel is ready to initiate a data transfer but waiting for it to be scheduled

- Active: The channel is enabled, has received an active trigger and has been scheduled. It is actively

performing data transfer(s). If there are multiple channels pending, the highest priority pending

channel gets scheduled

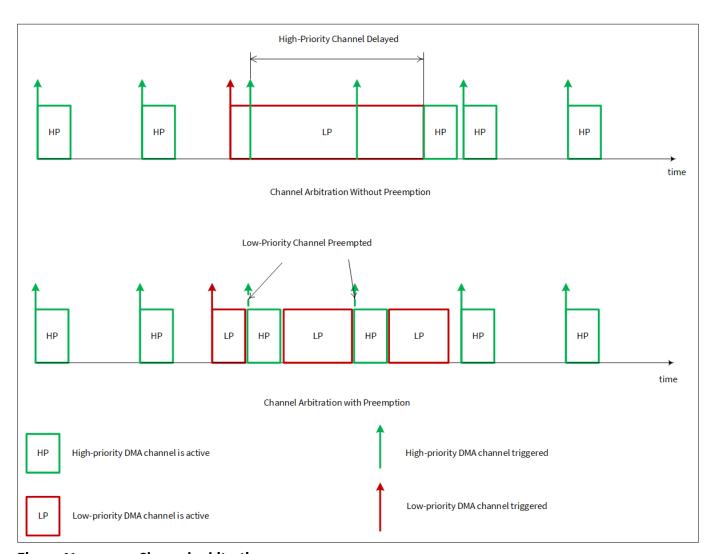

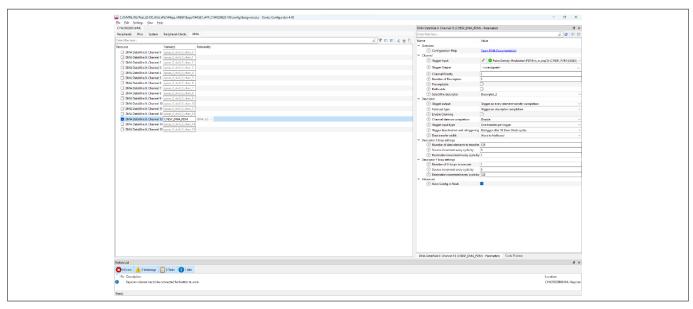

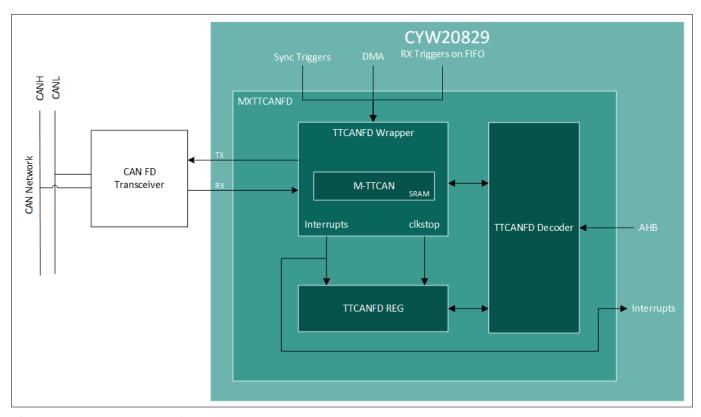

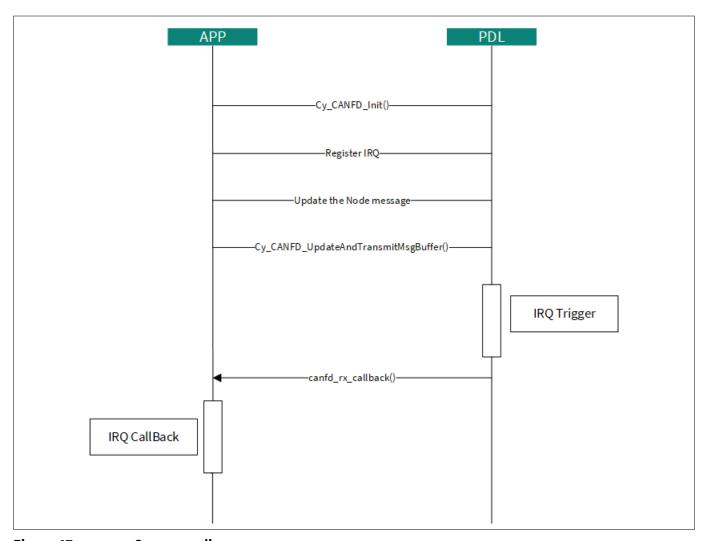

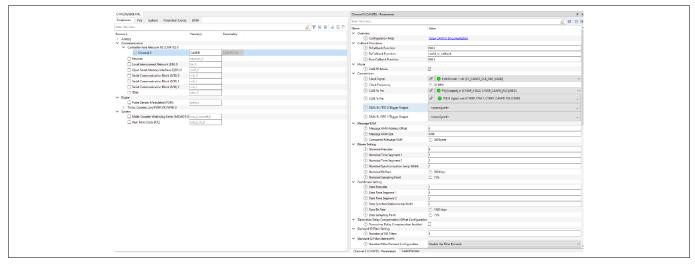

- Channel priorities and preemption