# **PSoC<sup>™</sup> 6 MCU interrupts**

## About this document

#### Scope and purpose

This application note explains the interrupt architecture in PSoC<sup>™</sup> 6 MCU and its configuration using PSoC<sup>™</sup> Creator, ModusToolbox<sup>™</sup>, and the PSoC<sup>™</sup> 6 Peripheral Driver Library (PDL) APIs. This document serves as a guide in developing projects that use interrupts. Advanced interrupt concepts such as interrupt latency, code optimization, and debug techniques are also explained.

To access an ever-growing list of hundreds of PSoC<sup>™</sup> code examples, please visit our code examples web page. You can also explore the Infineon video training library here.

### **Table of contents**

|         | About this document                                                |

|---------|--------------------------------------------------------------------|

|         | Table of contents    1                                             |

| 1       | Introduction                                                       |

| 1.1     | How to use this document                                           |

| 2       | <b>PSoC<sup>™</sup> 6 MCU interrupt architecture</b>               |

| 2.1     | CY8C61x6/7, CY8C62x6/7, and CY8C63xx interrupt architecture        |

| 2.2     | CY8C62x4, CY8C62x5, and CY8C62x8/A interrupt architecture          |

| 2.3     | Types of interrupts                                                |

| 2.3.1   | Level and pulse interrupts                                         |

| 2.4     | Interrupts and Power modes                                         |

| 2.5     | CPU sleep and wakeup                                               |

| 3       | Interrupt configuration                                            |

| 3.1     | Configuring interrupts using ModusToolbox <sup>™</sup> 10          |

| 3.1.1   | Using HAL                                                          |

| 3.1.2   | Using Device Configurator and PDL11                                |

| 3.2     | Configuring interrupts using PDL                                   |

| 3.3     | Configuring interrupts using PSoC $^{^{ m M}}$ Creator $\ldots$ 14 |

| 3.3.1   | Using the schematic (TopDesign)14                                  |

| 3.3.1.1 | Deep sleep capable                                                 |

| 3.3.1.2 | Interrupt type                                                     |

| 3.3.2   | Using the design-wide resource window (CyDWR)16                    |

| 3.3.3   | Using $PSoC^{^{ m M}}$ Creator generated code and PDL $\ldots$ 17  |

| 4       | Debugging tips                                                     |

| 5       | Advanced interrupt topics                                          |

| 5.1     | Exceptions                                                         |

| 5.2     | Interrupt latency                                                  |

| 5.3     | Nested interrupts                                                  |

| 5.4     | Code optimization                                                  |

## Table of contents

|   | <b>References</b>                                              |

|---|----------------------------------------------------------------|

| Α | <b>Appendix A. Interrupt sources in PSoC<sup>™</sup> 6 MCU</b> |

|   | Revision history                                               |

|   | <b>Disclaimer</b>                                              |

#### **1** Introduction

## 1 Introduction

An interrupt is a hardware signal or an event that transfers the execution of a program from the normal flow to an alternate set of instructions. An interrupt frees the CPU from continuously polling for a specific event, and only notifies and engages the CPU when the event occurs. The alternate program flow is referred to as an interrupt service routine or ISR. An ISR is also called an interrupt handler. After the interrupt is serviced, the program flow is reverted back to the flow that was interrupted. In system-on-chip (SoC) architectures such as PSoC<sup>™</sup>, interrupts are frequently used to communicate the status of on-chip peripherals to the CPU.

While interrupts refer to those events generated by peripherals external to the CPU such as timers, serial communication blocks, and port pin signals, an exception is an event generated by the CPU such as memory access faults and internal system timer events. PSoC<sup>™</sup> 6 MCU supports interrupts and exceptions on both its Arm<sup>°</sup> Cortex<sup>°</sup>-M4 (CM4) and Cortex<sup>°</sup>-M0+ (CM0+) CPUs.

### 1.1 How to use this document

This document assumes that you are familiar with the PSoC<sup>™</sup> 6 MCU architecture, and application development for PSoC<sup>™</sup> devices using the Infineon PSoC<sup>™</sup> Creator integrated design environment (IDE) and Peripheral Driver Library (PDL). For an introduction to PSoC<sup>™</sup> 6 MCU, see AN210781 - Getting Started with PSoC<sup>™</sup> 6 MCU with Bluetooth<sup>®</sup> Low Energy (BLE) Connectivity. If you are new to PSoC<sup>™</sup> Creator, ModusToolbox<sup>™</sup>, or PDL, see the References section for links to some of the available resources.

*Note:* Use PSoC<sup>™</sup> Creator version 4.2 or higher for PSoC 6 MCU-based designs.

This document begins with a brief explanation of the PSoC<sup>™</sup> 6 MCU interrupt architecture, with more details available in the PSoC<sup>™</sup> 6 MCU: PSoC<sup>™</sup> 63 with BLE Architecture Technical Reference Manual (TRM). To skip to an overview of writing firmware that uses interrupts, see Configuring interrupts using PDL or Configuring interrupts using PSoC<sup>™</sup> Creator or Configuring interrupts using ModusToolbox<sup>™</sup> sections respectively. Code examples that show how to use interrupts for various peripherals are listed in the References section.

The Debugging tips section provides a few tips on finding and resolving common issues encountered while using interrupts. More complex topics are covered in Advanced interrupt topics.

# 2 PSoC<sup>™</sup> 6 MCU interrupt architecture

PSoC<sup>™</sup> 6 MCU contains two CPUs: CM4 and CM0+. Interrupt signals to each CPU are handled by the respective Nested Vectored Interrupt Controller (NVIC). The NVIC enables/disables any interrupt based on the user configuration. It also resolves the interrupt priority when multiple requests occur at the same time and supports nested interrupts to allow a higher-priority interrupt to be serviced before a lower-priority ISR.

PSoC<sup>™</sup> 6 MCU also supports a wakeup interrupt controller (WIC) and multiple synchronization blocks. The WIC block allows the CPU to wake up from sleep or deep sleep low-power modes using interrupts. The WIC block remains active while the NVIC, processor core, and other device peripherals shut down. When an interrupt triggers, the WIC activates the power management system, which restores the NVIC and the processor core along with other peripherals. Each CPU has independent WIC settings.

Natively, CM4 supports up to 240 interrupts, while CM0+ supports 32 interrupts. The number of CPU interrupts available to the user varies depending on the device, see Table 1.

CM4 supports configurable interrupt priority from 0 to 7. CM0+ supports priority from 0 to 3.

There are up to 175 interrupt sources (also referred to as system interrupts) in a PSoC<sup>™</sup> 6 MCU device. System interrupts can trigger either or both CPUs.

The WIC block can wake up a CPU from deep sleep power mode. Table 2 lists the interrupt sources that can wake a CPU from deep sleep.

One or more system interrupts can be selected as the source for the CPU non-maskable interrupt (NMI), see Table 1.

| Parameter                                                                               | CY8C61x6/7,<br>CY8C62x6/7,<br>CY8C63xx | CY8C62x8/A                                                 | CY8C62x5                                                   | CY8C62x4                                                   |

|-----------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|

| Number of system<br>interrupts ("N")                                                    | 147                                    | 168                                                        | 174                                                        | 175                                                        |

| Number of deep sleep-<br>capable system interrupt<br>sources ("W")                      | 41                                     | 39                                                         | 39                                                         | 45                                                         |

| Number of CM0+ interrupt vectors available                                              | 32<br>(8 deep sleep-<br>capable)       | 8 hardware (deep<br>sleep-capable)<br>8 software triggered | 8 hardware<br>(Deep sleep-capable)<br>8 software triggered | 8 hardware<br>(Deep sleep-capable)<br>8 software triggered |

| Number of system<br>interrupts that can be<br>connected to a CM0+<br>multiplexer/vector | 1                                      | All (168)                                                  | All (174)                                                  | All (175)                                                  |

| Number of CM4 interrupt vectors available                                               | 240                                    | 240                                                        | 240                                                        | 240                                                        |

| Number of system<br>interrupts that can be<br>connected to a CM4<br>multiplexer/vector  | 1 (1:1<br>mapping)                     | 1 (1:1 mapping)                                            | 1 (1:1 mapping)                                            | 1 (1:1 mapping)                                            |

| Number of system<br>interrupts that can be<br>connected to CM0+/CM4<br>NMI interrupt    | 1                                      | 4                                                          | 4                                                          | 4                                                          |

#### Table 1 Interrupt features in PSoC<sup>™</sup> 6 MCU

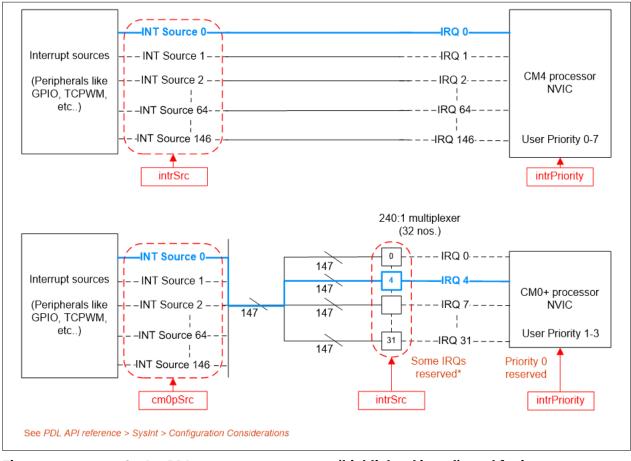

2.1

## CY8C61x6/7, CY8C62x6/7, and CY8C63xx interrupt architecture

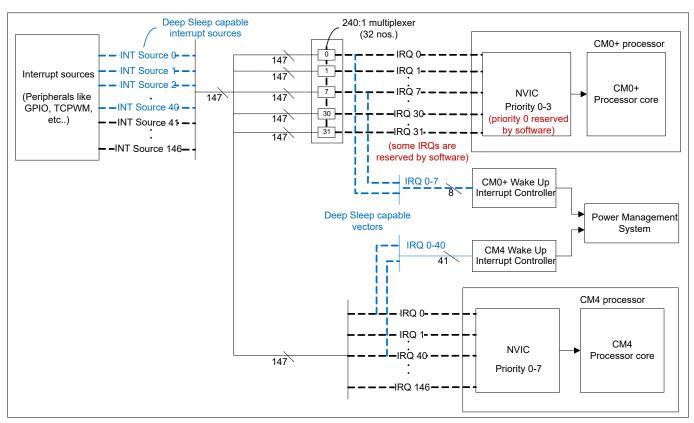

#### Figure 1 CY8C61x6/7, CY8C62x6/7, and CY8C63xx interrupt architecture

CY8C61x6/7, CY8C62x6/7, and CY8C63xx devices support up to 147 system and peripherals interrupt sources.

For CM4, the 147 interrupt sources are directly mapped to its first 147 IRQ lines, i.e., INT source n is connected to IRQ n, where 'n' = 0 to 146. For CM0+, a 240:1 multiplexer is present in front of each of 32 IRQs and redirects any of the 147 interrupts to one of CM0+ IRQ lines. This enables any interrupt source to trigger any CM0+ IRQ.

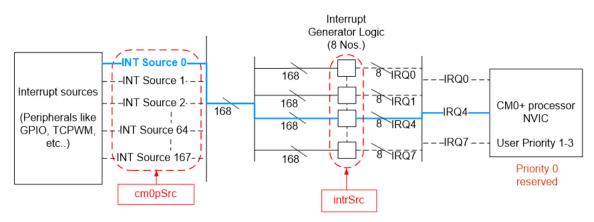

2.2

### CY8C62x4, CY8C62x5, and CY8C62x8/A interrupt architecture

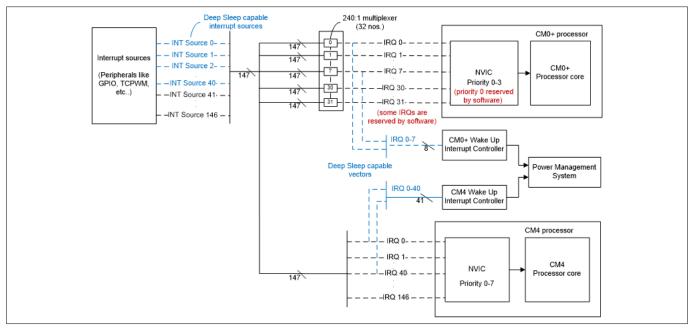

#### Figure 2 CY8C62x4, CY8C62x5, and CY8C62x8/A interrupt architecture

In CY8C62x4, CY8C62x5, and CY8C62x8/A devices, the 'N' interrupt sources are directly mapped to the first 'N' IRQ lines of the CM4. The CM0+ supports 16 interrupts, of which the first 8 interrupts (IRQ 0 – 7) can be triggered by a peripheral interrupt source; the other 8 are software-triggered interrupts. One or more system interrupts (upto 'N') can be assigned as the interrupt source for each of the IRQ 0 – 7 lines. This allows multiple interrupt sources to be connected to the same CPU interrupt simultaneously.

The WIC block supports up to 'W' interrupts that can wake up a CPU from deep sleep power mode; see "Number of deep sleep-capable system interrupt sources" in Table 1.

Table 2 lists the interrupt sources that can wake a CPU from deep sleep.

Note: When using Infineon software (PDL or PSoC<sup>™</sup> Creator), certain software restrictions apply on the number of CPU interrupts available to user and interrupt priorities. See Configuring interrupts using PDL for details.

### 2.3 Types of interrupts

There are two kinds of interrupt sources in PSoC<sup>™</sup> 6 MCU:

• Fixed-function interrupt sources

These are predefined interrupt sources from on-chip peripherals such as GPIO, TCPWM, SCB, and BLE Radio. Interrupts from fixed-function sources are generated from configurable events; for example, an interrupt on a rising for example signal on an input pin (GPIO), or an interrupt on a counter overflow (TCPWM).

Universal Digital Block (UDB) interrupt sources

UDBs consist of programmable logic devices (PLDs), datapaths, and flexible routing, which can be used to synthesize different digital functions such as Timer, PWM, UART, SPI and many more. In contrast to fixed-function interrupt sources, any digital signal generated in a UDB can trigger an interrupt. The signals are routed to the interrupt controller through the routing fabric known as Digital System Interconnect (DSI). UDB sources are available only in CY8C61x6/7, CY8C62x6/7, and CY8C63xx devices

For a complete list of interrupt sources in PSoC<sup>™</sup> 6 MCU, see Appendix A.

## 2.3.1 Level and pulse interrupts

Both CM0+ and CM4 NVICs support level and pulse signals on IRQ lines. The classification of an interrupt as level or pulse is based on the interrupt source. A fixed-function interrupt is treated as level-sensitive. For the DSI sources, which include the UDB, the interrupt can be configured as either rising-edge-triggered or level-triggered. This configuration is available only in PSoC<sup>™</sup> Creator. For more details on selecting the interrupt type, refer to the PSoC<sup>™</sup> Creator Component datasheet or PDL API reference for the interrupt source.

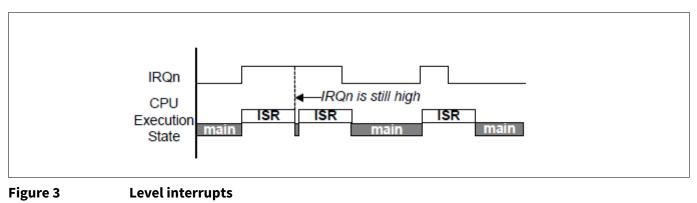

For level interrupts, if the interrupt signal is still HIGH after completing the ISR, the interrupt is still pending and the ISR is executed again. Figure 3 illustrates the timing diagram for level-triggered interrupts, where the ISR is executed if the interrupt signal is HIGH.

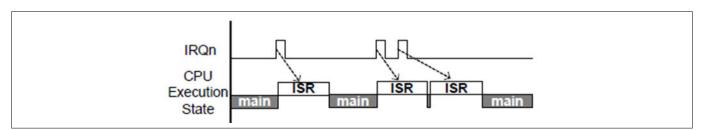

For pulse interrupts, while the ISR is being executed by the CPU, one or more rising edges of the interrupt signal are logged as a single pending request. The pending interrupt is serviced again after the current ISR execution is complete. Figure 4 illustrates the timing diagram for pulse interrupts.

#### Figure 4 Pulse interrupts

Note: The GPIO interrupt logic has additional circuitry to support interrupts on the rising edge, falling edge, and both edges. See the I/O System chapter in PSoC<sup>™</sup> 6 MCU Architecture TRM for more information.

### 2.4 Interrupts and Power modes

PSoC<sup>™</sup> 6 MCU has the following system Power modes: Low-Power (LP), Ultra-Low-Power (ULP), deep sleep, and hibernate. The Arm<sup>®</sup> CPU Power modes are active, sleep, and deep sleep; these are available in system LP and ULP Power modes.

In CPU active modes, CPUs execute code; all memory blocks and peripherals are available.

In all other Power modes (sleep, deep sleep, hibernate), CPU clocks are turned off and code execution is halted.

All peripherals available in active modes are also available in the sleep, deep sleep, and hibernate modes. Any peripheral interrupt, masked to the CPU, wakes up the CPU to Active mode.

Only a subset of peripherals operate in deep sleep mode. Interrupts from these peripherals cause a CPU to wake up to active mode. Table 2 lists these peripherals. Each CPU has a Wakeup Interrupt Controller (WIC) to wake up the CPU from its deep sleep mode. deep sleep wakeup functionality is supported only on the first 8 IRQs (0 to 7) on CM0+ and first 'W' IRQs on CM4, see Table 1.

## **PSoC<sup>™</sup> 6 MCU interrupts**

#### 2 PSoC<sup>™</sup> 6 MCU interrupt architecture

During hibernate mode, all peripherals and clocks are turned off and only certain sources like Low Power Comparator, RTC, a dedicated WAKEUP pin, or an XRES event can wake up the device. The wakeup action is a device reset instead of an interrupt to the CPU.

For more details on device Power modes CPU sleep and wakeup behavior due to interrupts, see AN219528 – PSoC<sup>™</sup> 6 MCU Low-Power Modes and Power Reduction Techniques or PSoC<sup>™</sup> 6 MCU Architecture TRM.

Table 2List of Deep Sleep Wakeup-Capable Interrupts

| Interrupt Source                                     | Interrupt Source Number |                          |                        |          |  |  |

|------------------------------------------------------|-------------------------|--------------------------|------------------------|----------|--|--|

|                                                      | CY8C63xx                | CY8C62x6/7CY<br>8C61x6/7 | CY8C62x8/<br>ACY8C62x5 | CY8C62x4 |  |  |

| GPIO Port Interrupt                                  | 0-14                    | 0-14                     | 0-14                   | 0-14     |  |  |

| GPIO All Ports                                       | 15                      | 15                       | 15                     | 15       |  |  |

| GPIO Supply Detect Interrupt                         | 16                      | 16                       | 16                     | 16       |  |  |

| Low Power Comparator Interrupt                       | 17                      | 17                       | 17                     | 17       |  |  |

| Serial Communication Block Interrupt                 | 18                      | 18                       | 18                     | 18       |  |  |

| Multi Counter Watchdog Timer                         | 19, 20                  | 19, 20                   | 19, 20                 | 19, 20   |  |  |

| Backup Domain Interrupt                              | 21                      | 21                       | 21                     | 21       |  |  |

| Other combined Interrupts for SRSS                   | 22                      | 22                       | 22                     | 22       |  |  |

| Combined Continuous Time Block<br>(CTBm) Interrupt   | 23                      | 23                       | -                      | -        |  |  |

| Bluetooth <sup>®</sup> Radio Interrupt               | 24                      | -                        | -                      | -        |  |  |

| Inter Process Communication<br>Interrupt             | 25–40                   | 25-40                    | 23-38                  | 23-38    |  |  |

| SAR ADC Interrupt                                    | -                       | -                        | -                      | 39, 40   |  |  |

| Individual Continuous Time Block<br>(CTBm) Interrupt | -                       | -                        | -                      | 41       |  |  |

| PASS Timer interrupt                                 | -                       | -                        | -                      | 42       |  |  |

| PASS FIFO Interrupt                                  | -                       | -                        | -                      | 43, 44   |  |  |

## 2.5 CPU sleep and wakeup

There are two instructions that can cause the CPU to enter its sleep modes: the "Wait-for-Interrupt" [\_\_WFI()] and "Wait-for-Event" [\_\_WFE()]. When a WFI instruction is executed, the CPU enters sleep or deep sleep (depending on the SLEEPDEEP bit of the SCR register) and wakes up on an interrupt request (with a higher priority than the current priority level) or on debug requests. The WFE instruction is like WFI but wakes up on the next interrupt or on events like Send Event (SEV instruction), external event, or debug signals. See AN219528 for more details on sleep and wakeup instructions.

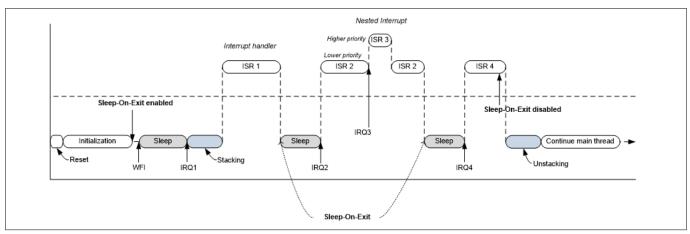

Normally, when an ISR is done executing, CPU execution returns to where it was before the ISR. PSoC<sup>™</sup> 6 MCU supports the "Sleep-on-Exit" feature where the CPU enters or returns to sleep or deep sleep (a state similar to WFI) as soon as it completes ISR execution. As seen in Figure 5, when this feature is enabled, only one WFI instruction is needed to enter a sleep mode; the CPU returns to sleep after each ISR instead of the execution returning to main. The Sleep-on-Exit feature reduces the active cycles of the CPU and reduces the energy consumed by the stacking (PUSH to stack) and unstacking (POP from stack) of processes between interrupts. Nested interrupts are also supported when Sleep-on-Exit is enabled.

## **PSoC<sup>™</sup> 6 MCU interrupts**

#### 2 PSoC<sup>™</sup> 6 MCU interrupt architecture

The Sleep-on-Exit feature is enabled by setting SLEEPONEXIT bit of the SCR register. There is also a PDL function available – Cy\_SysPm\_SleepOnExit; see Configuring interrupts using PDL for details.

**Sleep-on-Exit function**

## 3 Interrupt configuration

This section lists the steps needed to set up interrupts on a PSoC<sup>™</sup> 6 MCU device, without going into details of the software used to do them. These steps are common to both CM0+ and CM4 unless specified otherwise, and must be done for each CPU separately.

- Out of device reset, all interrupts are disabled, and interrupt priorities are set to zero

- Configure the priority level of the required IRQ in the NVIC

- Configure the interrupt path

- Choose which interrupt source is connected to the desired IRQ of the CPU. For CM0+, select the appropriate peripheral interrupt to be connected to the CPU. For CM4, this is not configurable. Interrupt source n is always connected to IRQn

- Configure the interrupt source (peripheral) and enable its interrupt

- Configure the vector table with the address of the ISR (vector). The vector table stores the entry addresses for each exception handler; see Exception Vector Table in Interrupts chapter of PSoC<sup>™</sup> 6 MCU Architecture TRM.

- Optional: Clear pending interrupt states in the NVIC

- If enabling a previously disabled interrupt, it is a good practice to clear the pending state of the NVIC before enabling the interrupt. This prevents any false trigger caused by previous interrupts that created a pending state

- Enable the interrupt in the NVIC

- Enable global interrupts. Interrupt configuration is complete

An enabled interrupt is triggered when the hardware signal from the interrupt source is active and there is no higher priority interrupt that is executing. When this happens, CPU execution jumps to the location in its vector table that corresponds to the triggered interrupt. This location contains the address of the ISR associated with that interrupt.

The ISR executes the tasks required to handle the interrupt. Typically, the first thing an ISR does is clearing the interrupt source to avoid re-entering the ISR. When the ISR terminates, the CPU returns to the address it was executing before it was interrupted. The following sections describe the software tools available for performing the steps described.

## 3.1 Configuring interrupts using ModusToolbox<sup>™</sup>

ModusToolbox<sup>™</sup> applications support both the PSoC<sup>™</sup> 6 Hardware Abstraction Layer (HAL) and Peripheral Driver Library (PDL) libraries.

### 3.1.1 Using HAL

The HAL gives an abstracted interface to configure and use various blocks on Infineon MCUs. There is no separate block for interrupts in HAL. The interrupts for different blocks are configured using the HAL APIs specific to those blocks.

For example, in the case of a GPIO Interrupt, interrupts arising from the GPIO block are configured using the GPIO HAL APIs. The steps to configure the GPIO HAL block for this example include:

- Initializing the GPIO pin: The GPIO pin, direction, drive mode, and initial value are passed to the cyhal\_gpio\_init HAL API function

- Registering the interrupt callback function: The callback function for the interrupt is registered with the GPIO pin using cyhal\_gpio\_register\_callback

- Configuring the interrupt: The interrupt settings such as the GPIO event and interrupt priority are configured using cyhal\_gpio\_enable\_event

- See the Interrupts on GPIO events code snippet in GPIO HAL API Reference Guide

For more details on HAL APIs, see PSoC<sup>™</sup> 6 HAL on GitHub.

## 3.1.2 Using Device Configurator and PDL

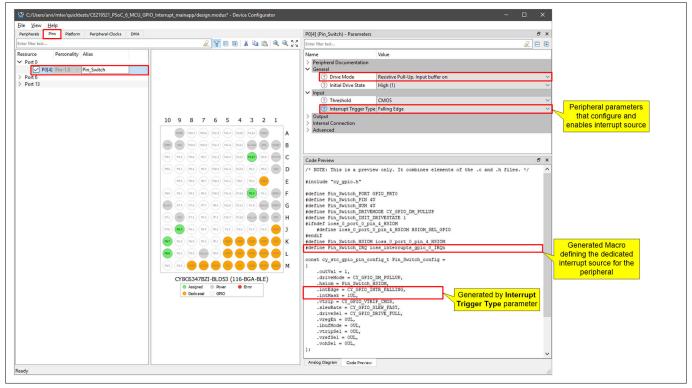

Interrupts can be configured in ModusToolbox<sup>™</sup> using the Device Configurator, the GUI-based tool used to enable and configure MCU peripherals and their interrupt parameters.

Figure 6 shows the configuration of a GPIO pin to generate interrupt on a falling edge.

### Figure 6 ModusToolbox<sup>™</sup> peripheral configuration

Based on the configuration, ModusToolbox<sup>™</sup> generates the 'C' code to achieve the desired configuration. The code generated can be viewed in the Code Preview pane; it is added to relevant cycfg\_xxx.c/h files in the TARGET\_<BSP\_name>/COMPONENT\_BSP\_DESIGN\_MODUS/GeneratedSource folder in the ModusToolbox<sup>™</sup> application. The generated code includes macros defining the interrupt source numbers and any peripheral configuration that is necessary to set up and enable the interrupt source. This simplifies the process of searching for the dedicated interrupt numbers in the device header file. The user application only needs to enable the interrupt vector on the CPU and assign an interrupt handler function as described in Configuring interrupts using PDL.

## 3.2 Configuring interrupts using PDL

The Peripheral Driver Library (PDL) simplifies software development for the PSoC<sup>™</sup> 6 MCU architecture. The PDL reduces the need to understand register usage and bit structures, so easing software development for the extensive set of peripherals available.

Note: The ModusToolbox<sup>™</sup> software version of PDL is available at the Infineon GitHub site. It is not compatible with PSoC<sup>™</sup> Creator. The ModusToolbox<sup>™</sup> version of the PDL includes support for new PSoC<sup>™</sup> 6 MCU devices and drivers. It also supports macOS and Linux hosts, as well as Windows. Developers should move to the ModusToolbox<sup>™</sup> package as projects and schedules permit. PDL v3.1 is designed for and works with PSoC<sup>™</sup> Creator. PDL v3.1 is expected to be the final PSoC<sup>™</sup> Creator-compatible release. PDL v3.0.x is installed along with the PSoC<sup>™</sup> Creator 4.2 development tools.

PDL API function calls are used to configure, initialize, enable, and use a peripheral driver. One such driver is System Interrupts (SysInt). SysInt provides structures and functions to configure and enable interrupt functionality. PDL also supports the CMSIS-Core libraries which include NVIC functions used for interrupt configuration.

The following steps use PDL and NVIC APIs to set up an interrupt to trigger on a signal from a peripheral.

- Configure the peripheral to generate the interrupt. For example, for a GPIO, configure the drive mode (pull up or pull down), interrupt signal generation on falling or rising edge, and unmask the interrupt. Refer to the PDL API reference documentation for your peripheral for this information

- Configure the interrupt using the structure provided by the SysInt API.

The structure is defined in the PDL SysInt driver file cy\_sysint.h:

```

* Initialization configuration structure for a single interrupt channel */

typedef struct {

IRQn_Type

intrSrc;

/**< Interrupt source */</pre>

#if (CY_CPU_CORTEX_M0P)

/**< (CM0+ only) Maps cm0pSrc device</pre>

cy_en_intr_t

cm0pSrc;

interrupts to intrSrc */

#endif

uint32 t

/**< Interrupt priority number (Refer to

intrPriority;

NVIC PRIO BITS) */

} cy_stc_sysint_t;

```

This structure is used to configure the following (see Figure 7 for a quick summary):

- Interrupt Source (intrSrc)

- These are the dedicated interrupt numbers as defined in the device header file (example: cy8c6247bzi\_d44.h)

- This selection depends on which CPU you want to assign the interrupt to

- For CM4, this number represents both the interrupt number of the source as well as the CPU IRQ number. Select the interrupt number of the peripheral interrupt you wish to route to the CPU. For example, to route Port 0 GPIO interrupt, assign a value of ioss\_interrupts\_gpio\_0\_IRQn (=0).

- For CM0+, this number represents one of the 32 multiplexers available for routing an interrupt to CM0+. Because each multiplexer is connected to a dedicated CM0+ IRQ line, use this to select the target CM0+ IRQ number. For example, to use multiplexer #4 (CM0+ IRQ#4), use "NvicMux4\_IRQn" (=4).

- CM0+ interrupt number (cm0pSrc)

- This parameter is applicable only for CM0+.

- This represents the interrupt number of the source, which is to be routed to the multiplexer/CM0+

interrupt generator logic, selected using the intrSrc parameter. Select the interrupt number of the

peripheral interrupt you wish to route to the CPU; for example, to route Port 0 GPIO interrupt, assign a

value of "ioss\_interrupts\_gpio\_0\_IRQn" (=0).

- Interrupt priority (intrPriority)

- Set the priority of the interrupt. For CM4, supported priorities are 0 to 7. For CM0+, supported priorities are 0 to 3

Notes:

- **1.** On CM0+, some IRQs are reserved for use by software and not available to the user. See "Configuration Considerations" under SysInt driver in PDL API reference documentation for the list of reserved IRQs

- 2. On CM0+, the interrupt priority 0 is reserved for system calls

For CY8C62x4, CY8C62x5 and CY8C62x8/A devices:

- Call Cy\_SysInt\_Init(&SysInt\_SW\_cfg\_1, ISR\_1\_handler).

- Here, SysInt\_SW\_cfg\_1 is the name of the configured structure. ISR\_1\_handler is the name of the interrupt handler that executes when the interrupt triggers. This function applies the routing and priority configuration of the interrupt but does not enable it

- Call NVIC\_ClearPendingIRQ(SysInt\_SW\_cfg\_1.intrSrc) to clear any pending interrupts

- Call NVIC\_EnableIRQ(SysInt\_SW\_cfg\_1.intrSrc) to enable the interrupt

- Call the \_enable\_irq() function to enable global interrupts. This is safe to perform as the first step, as individual CPU interrupts have not been enabled yet. You can also perform this later but interrupts are disabled at startup unless this is called

In addition to the PDL SysInt driver, the system power modes (SysPm) driver API enables the Sleep-on-Exit feature. If sleep or deep sleep mode is used in the application along with interrupts, this feature enables the firmware to keep the system in a that sleep mode almost all the time, only wake up to execute the interrupt and then immediately go back to the same sleep mode. The program does not return to the main function and stays either in the interrupt handler or in the same sleep state unless the Sleep-on-Exit feature is disabled again.

Cy\_SysPm\_SleepOnExit(true);

## 3.3 Configuring interrupts using PSoC<sup>™</sup> Creator

PSoC<sup>™</sup> Creator provides a graphical interface for routing signals from peripherals to a CPU IRQ line. PSoC<sup>™</sup> Creator provides an Interrupt (SysInt) Component. This component is a UI element on top of the SysInt PDL driver discussed in the previous section. Based on the configuration in the Component, PSoC<sup>™</sup> Creator generates code to initialize peripherals, route interrupts, and populate the interrupt configuration structure. This reduces the amount of code you must write when setting up interrupts.

The following section shows steps to use PSoC<sup>™</sup> Creator to configure an interrupt. See the References section for code examples.

## 3.3.1 Using the schematic (TopDesign)

Drag and drop a Component from the Component Catalog onto the TopDesign. Use TopDesign to place and configure peripherals that provide a source of interrupt. Consult the Component datasheet for information on the peripheral's interrupt configuration. Some peripherals provide an interrupt terminal (e.g., TCPWM). Place an instance of the SysInt Component and connect it to the interrupt terminal of the peripheral.

| Clock_1                                                         | Interrupt source                                                            | ipt compon | ent                                                                                                     | Component Catalog (120 compone → # ×<br>W W B B B %<br>Search for<br>Cypress Off-Chip 4 ▷<br>Cypress Component Catalog<br>⊕ @ Analog<br>⊕ @ CapSense                  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configure 'TCPWM_PWM_PD<br>Name: PWM_1<br>Basic Advanced        | ultin                                                                       | • f(x) ^   | 4 b<br>Type: interruptSources                                                                           | Communications     Generations     Generations     Generations     Generations     Generations     Generations     Generations                                        |

| PWM Alignment<br>Run Mode<br>Period                             | Left Aligned<br>Continuous                                                  | ▼ f(y)     | Value: 1<br>Value name: INT_ON_TC<br>Value display name:<br>Overflow/Underflow                          | PWM (TCPWM) [v1.0]     Quadrature Decoder (TCPWM)     Timer Counter (TCPWM) [v1.0]                                                                                    |

| Period 0<br>Enable Period Swap<br>Compare                       | 999                                                                         |            | Parameter: SInterruptSource<br>Description: Selects which events can<br>trigger an interrupt            | Some Counter (100 www) [v1.0]     Some Counter (100 www) [v1.0] |

| Compare 0<br>Enable Compare Swap<br>Interrupts                  | 500                                                                         |            | Counting clock (kHz): 1000<br>Period0 (kHz): 1                                                          | Sog Display     Sog Memory interfaces     Sog Ports and Pins                                                                                                          |

| Interrupt Source           period           pwm           pwm_n | Overflow/Underflow Overflow/Underflow Compare Overflow/Underflow or Compare |            | Period1 (kHz): -<br>Compare0 duty cycle: 50%<br>Compare1 duty cycle: -<br>Configure<br>Interrupt source | System     Occk [v1.0]     ODMA [v1.0]     Global Signal Reference [v2.10]     Interrupt (v1.0]     MCWDT [v1.0]                                                      |

| Datasheet                                                       | · (                                                                         | ОК         | Apply Cancel                                                                                            | Real-time clock (RTC) [v2.0]                                                                                                                                          |

#### Figure 8

#### TopDesign with interrupt componentSysInt (Interrupt) configuration

Some peripherals do not have an external interrupt terminal (e.g., SCB has interrupts built-in) or may have an option to expose it (e.g., UART).

The Interrupt Component has two configurable options as seen in Figure 9.

| Name: SysInt_1 Basic Built-in |                                                                 |             | 4 ۵                                                                      |

|-------------------------------|-----------------------------------------------------------------|-------------|--------------------------------------------------------------------------|

| Deep Sleep Capable            |                                                                 | <i>f(x)</i> | Type: IntTypeEnum<br>Value: 0                                            |

| Interrupt Type                | Auto-Select Trigger                                             |             | Value name: DERIVED                                                      |

|                               | Auto-Select Trigger<br>Rising-Edge Triggered<br>Level Triggered |             | Value display name: Auto-Select<br>Trigger<br>Parameter: \$InterruptType |

SysInt (Interrupt) configuration

## 3.3.1.1 Deep sleep capable

Enable this checkbox if you want the interrupt to be assigned to a CPU IRQ line that is deep sleep-capable. You must ensure that the interrupt source is also active and capable of providing the interrupt signal during deep sleep, failing which PSoC<sup>™</sup> Creator throws an error when the project is built. Note that this option is significant only in case the interrupt is assigned to CM0+ which has 8 (IRQ 0-7) deep sleep slots to route to. The checkbox is provided only for guidance in automatically assigning an IRQ for the interrupt and can be overridden by manual assignment from the CyDWR window. For CM4, if the interrupt source is deep sleep-capable (IRQ 0-40), disabling the checkbox has no effect on the deep sleep functionality of the interrupt.

## 3.3.1.2 Interrupt type

There are three options available for Interrupt type in the Interrupt Component configuration: Auto-Select Trigger, Rising-Edge Triggered, and Level Triggered. The selection of a particular option depends on the interrupt source (fixed-function or UDB/DSI) and the application requirements. In most cases, leave the option to Auto-Select to let PSoC<sup>™</sup> Creator derive the interrupt type from the nature of the interrupt source.

Choose only level-triggered for Fixed-function interrupt sources. Choose Level-triggered or Rising-Edge for UDB sources.

## 3.3.2 Using the design-wide resource window (CyDWR)

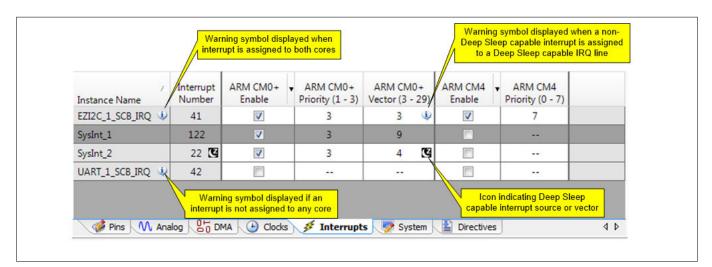

The design-wide resources window (.cydwr file) of the PSoC<sup>™</sup> Creator project has an Interrupts tab. This tab lists the instance names of all interrupts used in the TopDesign schematic along with their interrupt numbers.

Each interrupt can be allocated to either CM0+ or CM4 or both the CPUs using the 'ARM CMx Enable' checkbox. Unless specified otherwise, all interrupts are assigned to CM4 by default. **Though possible, it is not advised to assign an interrupt to both CPUs unless an application requires it. A warning icon appears in the Instance name column if both CPUs handle the same interrupt**. A tooltip description of the warning can be viewed on hovering the mouse pointer over the icon.

For CM0+, also assign a CPU IRQ line using the 'ARM CM0+ Vector' column. Note that **some CM0+ IRQs are reserved**. PSoC<sup>™</sup> Creator does not allow assigning to these IRQs and will display a warning if done so. There is no option to select the vector for CM4 as these are directly mapped to the corresponding interrupt numbers.

Once assigned to the CPU, assign the priority using the corresponding priority field. CM0+ priority is in the range of 1 to 3, (**priority 0 is reserved** for system calls). CM4 priority is in the range 0 to 7. For both CPUs, priority 0 corresponds to the highest priority and higher numbers denote lower priorities.

A deep sleep-capable interrupt source or IRQ is indicated using an icon **G**. An info icon **W** appears if a non-deep sleep-capable interrupt is assigned to a deep sleep-capable IRQ line. A build is required to refresh the interrupt numbers and icons.

#### Figure 10 Interrupts assignment in CyDWR

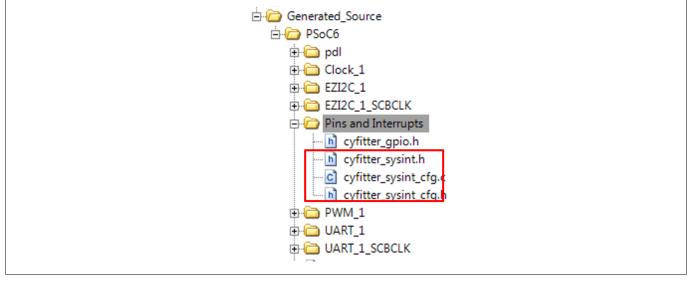

## 3.3.3 Using PSoC<sup>™</sup> Creator generated code and PDL

#### Figure 11 Generated files

Building the project generates code for use in the application. The **Pins and Interrupts** folder contains files with code generated using the information entered in the Interrupts tab in CyDWR.

Cyfitter\_sysint.h contains macros with information on interrupt number, its CPU assignment, and priority.

Cyfitter\_sysint\_cfg.c/h declares and pre-populates instances of SysInt PDL configuration structure using the CyDWR information.

The configuration structure for each interrupt is conditionally defined based on the CPU assignment. The steps to enable interrupts in firmware are similar to the ones listed in the PDL section but fewer in number.

- Call the \_\_enable\_irq() API to enable global interrupts

- Call Cy\_SysInt\_Init(&SysInt\_1\_cfg, ISR\_1\_handler)

- Where SysInt\_1\_cfg is the name of the auto-generated structure from the cyfitter\_sysint\_cfg.c file. ISR\_1\_handler is the name of the interrupt handler that executes when the interrupt triggers. The handler function can reside in the respective CPU's main.c to which the interrupt is assigned. If the

handler exists outside main.c, that file must be compiled and linked into the executable for the CPU that handles the ISR

- This step configures the interrupt (routing, priority, and interrupt handler assignment) but does not enable it

- Call NVIC\_ClearPendingIRQ(SysInt\_1\_cfg.intrSrc) to clear any pending interrupts

- Call NVIC\_EnableIRQ(SysInt\_1\_cfg.intrSrc) to enable the interrupt

You can use PSoC<sup>™</sup> Creator to generate code, and import that into a preferred IDE. AN219434 – Importing PSoC<sup>™</sup> Creator Code into an IDE for a PSoC<sup>™</sup> 6 MCU Project describes how to do that. It is recommended that you use PSoC<sup>™</sup> Creator to set up and configure interrupts in PSoC<sup>™</sup> 6 MCU, export the project to the IDE you prefer and continue developing firmware code with the IDE preferred.

## 4 Debugging tips

This section provides tips on trouble-shooting and debugging interrupts. The following are some of the frequently encountered cases:

#### Interrupt is not triggered

- Ensure that the interrupt source and global interrupt are enabled

- Ensure that the interrupt vector is initialized with correct ISR

- Check whether other interrupt sources are triggered repeatedly, so consuming the entire CPU bandwidth

#### Interrupt is triggered repeatedly

This can happen in multiple cases: Insert breakpoints in the ISR and elsewhere in the program which is expected to execute repeatedly (for example, the super-loop in the main function). If the program is not entering the main function, interrupt is triggered repeatedly

- The interrupt line from a fixed-function source

Resolution: Clear the interrupt source to resolve this behavior

- A digital output from the Component (not the interrupt line) is connected to a SysInt Component configured to level type in PSoC<sup>™</sup> Creator

- Resolution: Configure the Interrupt Component to rising for example to get one interrupt per rising edge.

#### Execution of the ISR is taking longer than expected

This can happen if other high-priority interrupts are triggered during the execution of the ISR.

Resolution: Increase the priority of the interrupt relative to other interrupt sources.

The PSoC<sup>™</sup> 6 BLE Pioneer Kit has the KitProg2 onboard programmer/debugger.

The CY8CPROTO-062-4343W PSoC<sup>™</sup> 6 Wi-Fi BT Prototyping Kit has the KitProg3 onboard programmer/debugger. This kit is supported only on ModusToolbox<sup>™</sup>.

PSoC<sup>™</sup> Creator supports debugging one CPU at a time (either CM0+ or CM4). ModusToolbox<sup>™</sup> IDE supports debugging of both CPUs simultaneously.

The debug mode is useful for checking interrupts as given below:

- To check if an interrupt is executing, add a breakpoint at one of the instructions in the ISR

- Use Breakpoint Hit Count/breakpoint condition to detect the number of times an interrupt is triggered. This is particularly useful to check if the interrupt signal has glitches causing the interrupt to trigger multiple times. To see Breakpoint Hit Count, right-click on the breakpoint, select Hit Count and observe current hit count.

- Use the Call Stack window of the debugger to check program flow to learn when a particular ISR is executed. You can also use it to check if a high-priority interrupt occurred during the execution of a low-priority ISR

- As an alternative to the debugger, you can also use a pin to do the following:

- Check if the CPU is entering the ISR

- Measure the ISR execution time. This can be done, for example, by asserting the pin in the beginning of the ISR and de-asserting the pin before returning from the ISR. The time for which the pin is HIGH can be measured using an oscilloscope to give the duration of ISR execution

# 5 Advanced interrupt topics

## 5.1 Exceptions

Exceptions are the events that cause the processor to suspend the currently executing code and branch to a handler. Interrupts are a subset of exceptions. Besides interrupts, exceptions exist for operating system applications and fault handling.

| Exception                      | Exception<br>number | Exception<br>priority | CPUs<br>supporting<br>the<br>exception | Description                                                                                                                                                                                                                                                                                                            |

|--------------------------------|---------------------|-----------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset                          | 1                   | -3                    | Both CM0+<br>and CM4                   | This exception can occur due to multiple<br>reasons, such as power-on-reset (POR),<br>external reset signal on XRES pin, or<br>watchdog reset.                                                                                                                                                                         |

|                                |                     |                       |                                        | Cortex <sup>®</sup> -M4 execution begins only after CM0+<br>de-asserts the M4 reset.                                                                                                                                                                                                                                   |

|                                |                     |                       |                                        | The reset exception address in the SRAM<br>vector table will never be used because the<br>device comes out of reset with the flash vector<br>table selected. The register configuration to<br>select the SRAM vector table can be done only<br>as part of the startup code in flash after the<br>reset is de-asserted. |

| Nonmaskable<br>Interrupt (NMI) | 2                   | -2                    | Both CM0+<br>and CM4                   | Both CPUs have their own NMI exception. NMI<br>can be triggered by the following: Any of the<br>interrupt sources, by setting NMIPENDSET bit<br>or using System Calls.<br>PSoC <sup>™</sup> 6 BLE supports routing of only one                                                                                         |

|                                |                     |                       |                                        | system interrupt as the source for NMI.<br>CY8C62x8/A supports four system interrupt<br>sources for NMI. The four selected interrupt<br>sources are logically Ored into a single CPU<br>NMI input                                                                                                                      |

|                                |                     |                       |                                        | NMI exception handler address is<br>automatically initialized to the system call<br>API located in SROM (at 0x0000000D by the<br>boot code. The value should be retained<br>by the user during vector table relocations;<br>otherwise, no system call will be executed.                                                |

| HardFault Exception            | 3                   | -1                    | Both CM0+<br>and CM4                   | HardFault exception occurs when executing an undefined instruction or accessing an invalid memory addresses.                                                                                                                                                                                                           |

| SVCall Exception               | 11                  | Configurable          | Both CM0+<br>and CM4                   | Supervisor Call (SVCall) is an always-enabled<br>exception caused when the CPU executes the<br>SVC instruction as part of the application<br>code. The SVC instruction enables the<br>application to issue a supervisor call that<br>requires privileged access to the system.                                         |

| Exception                            | Exception<br>number | Exception<br>priority | CPUs<br>supporting<br>the<br>exception | Description                                                                                                                    |

|--------------------------------------|---------------------|-----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| PendSV                               | 14                  | Configurable          | Both CM0+<br>and CM4                   | PendSV exception is normally software-<br>generated. PendSV is another supervisor call<br>related exception similar to SVCal.  |

| SysTick Exception                    | 15                  | Configurable          | Both CM0+<br>and CM4                   | SysTick is a 24-bit decrementing counter that generates periodic interrupts.                                                   |

| Memory Management<br>Fault Exception | 4                   | Configurable          | Only CM4                               | A memory management fault is an exception<br>that occurs because of a memory protection-<br>related fault.                     |

| Bus Fault Exception                  | 5                   | Configurable          | Only CM4                               | A Bus Fault is an exception that occurs<br>because of a memory-related fault for an<br>instruction or data memory transaction. |

| Usage Fault<br>Exception             | 6                   | Configurable          | Only CM4                               | A Usage Fault is an exception that occurs because of a fault related to instruction execution.                                 |

Notes:

**3.** Exception priority that are configurable can be configured from priority 0-3 for CM0+ and 0-7 for CM4.

**4.** Interrupts are also part of exceptions. Interrupt vector number 0 (i.e., IRQ 0) corresponds to the exception number 16, and so on.

### 5.2 Interrupt latency

Interrupt latency is defined as the time delay between the assertion of an interrupt and the execution of the first instruction in its ISR. CM0+ has a latency of 15 clock cycles (worst case); CM4 has a latency of 12 clock cycles (worst case). Some peripherals generate additional cycles due to synchronization circuit between the peripherals and CPUs. Table 3 provides the number of CPU clock cycle delays for various peripherals in PSoC<sup>™</sup> 6 MCU.

Table 3Synchronization delay for various peripherals

| Interrupt source                       | Synchronization delay |

|----------------------------------------|-----------------------|

| TCPWM, DMA, USB, I2S, PDM – PCM, CDS   | 0 clock cycles        |

| SCB, GPIO, LPComp, RTC, WDT, SMIF, BLE | 2 clock cycles        |

When both CPUs are in sleep/deep sleep power mode, there is a need for additional two clock cycles required for synchronization.

Context switching affects the latency and involves the following steps:

- Current instruction execution is completed

- The processor pushes the current Program Counter (PC), Link Register (LR), Program Status Register (PSR), and some of the general-purpose registers (Program and Status Register (PSR), Return Address, Link Register (LR or R14), R12, R3, R2, R1, and R0) to the stack

- The processor reads the vector address from the NVIC and updates it to the PC

- The processor updates the NVIC registers

Thus, the latency varies depending on the current instruction being executed. To make the process efficient, both CM0+ and CM4 processors implement the following two schemes:

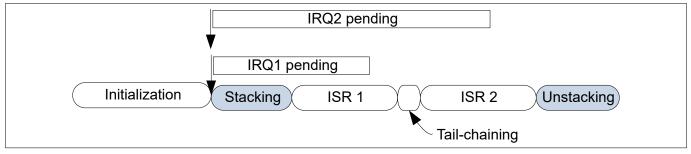

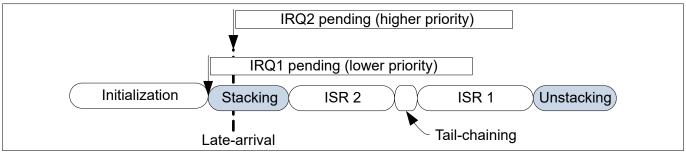

**Tail Chaining:** If an interrupt is in the pending state while the processor is executing another interrupt handler, unstacking is skipped when the execution ends for the first interrupt and the handler for the pending interrupt is immediately executed. This saves the time of restoring the registers from the stack and pushing the same registers again to stack. This is useful for nested interrupts, as seen in the following section, and for reducing the latency of low-priority interrupts.

#### Figure 12 Tail chaining

**Late Arrival:** If a higher-priority interrupt occurs during the stacking process of a lower-priority interrupt, the processor jumps to the higher-priority interrupt handler instead of a lower-priority one. The processor reads the vector address of the higher-priority interrupt at the end of the stacking process. Once the higher-priority interrupt handler is fetched and executed. This reduces the latency for a higher-priority interrupt by entering the lower priority ISR and pushing the register values to the stack.

Figure 13 Late arrival

## 5.3 Nested interrupts

NVIC automatically handles nested interrupts without any software overhead. If a higher-priority interrupt is asserted during the execution of a lower-priority interrupt handler, some of the general-purpose registers are pushed to stack, CPU reads the vector address from NVIC and jumps to the higher-priority interrupt handler. After the execution is completed, the processor restores the register values and execution resumes for the lower-priority interrupt.

## 5.4 Code optimization

An important performance requirement in interrupt-based applications is the ISR code execution time. In some applications, the critical code in the ISR must be executed within a particular time of receiving the interrupt request. Also, interrupt execution should not take too much time and stall the main code execution or other interrupts. To meet these requirements, use the following guidelines:

• Avoid calls to lengthy functions in the ISR. Functions such as Character LCD display routines or printing long strings to a UART terminal takes long time to execute, so blocking the execution of other low-priority interrupts. The recommended technique is to move non-critical function calls to the main code and just

set a flag variable in the ISR. The main code periodically checks the flag and if set, clears it and calls the function

• Assign proper priority to the interrupts. In applications with multiple interrupts, give a higher priority to more time-critical interrupts

Although AN89610 – PSoC<sup>™</sup> 4 and PSoC<sup>™</sup> 5LP ARM Cortex<sup>®</sup> Code Optimization targets a different CPU architecture, it is a useful reference for general compiler topics.

#### References

## References

For a complete and updated list of PSoC<sup>™</sup> 6 MCU code examples, visit our code examples web page . For more PSoC<sup>™</sup> 6 MCU-related documents, please visit our PSoC<sup>™</sup> 6 MCU product web page.

#### Table 4 Documents related to PSoC<sup>™</sup> 6 MCU features

| Document             | Document name                                                                                             |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| Application notes    |                                                                                                           |  |  |  |

| AN228571             | Getting Started with PSoC <sup>™</sup> 6 MCU on ModusToolbox <sup>™</sup> .                               |  |  |  |

| AN221774             | Getting Started with PSoC <sup>™</sup> 6 MCU on PSoC <sup>™</sup> Creator                                 |  |  |  |

| AN210781             | Getting Started with PSoC <sup>™</sup> 6 MCU with Bluetooth <sup>®</sup> Low<br>Energy (BLE) Connectivity |  |  |  |

| AN215656             | PSoC <sup>™</sup> 6 MCU Dual-CPU System Design                                                            |  |  |  |

| AN219434             | Importing PSoC <sup>™</sup> Creator Code into an IDE for a PSoC <sup>™</sup> 6 MCU Project                |  |  |  |

| Programmable digital |                                                                                                           |  |  |  |

| Code Examples (ModusToolbox <sup>™</sup> ) on GitHub   |                                                                                                           |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| mtb-example-psoc6-gpio-interrupt                       | PSoC <sup>™</sup> 6 MCU GPIO Interrupt                                                                    |

| mtb-example-psoc6-hello-world                          | PSoC <sup>™</sup> 6 MCU Hello World Example                                                               |

| mtb-example-psoc6-uart-transmit-receive-dma            | PSoC <sup>™</sup> 6 MCU: SCB UART Transmit and Receive with DMA                                           |

| mtb-example-psoc6-spi-master-dma                       | PSoC <sup>™</sup> 6 MCU: SCB SPI Master with DMA                                                          |

| mtb-example-psoc6-wdt                                  | PSoC <sup>™</sup> 6 MCU Watchdog Timer                                                                    |

| mtb-example-psoc6-capsense-buttons-slider              | PSoC <sup>™</sup> 6 MCU: CAPSENSE <sup>™</sup> Buttons and Slider                                         |

| mtb-example-psoc6-csdadc                               | PSoC <sup>™</sup> 6 MCU: CSD Analog-to-Digital Converter (ADC)                                            |

| mtb-example-psoc6-capsense-custom-scan                 | PSoC <sup>™</sup> 6 MCU: CAPSENSE <sup>™</sup> Custom Scan                                                |

| mtb-example-psoc6-capsense-buttons-slider-<br>freertos | PSoC <sup>™</sup> 6 MCU: CAPSENSE <sup>™</sup> Buttons and Slider (FreeRTOS)                              |

| mtb-example-psoc6-ble-findme                           | PSoC <sup>™</sup> 6 MCU with Bluetooth <sup>™</sup> Low Energy (BLE)<br>Connectivity: Find Me Application |

| mtb-example-psoc6-ble-battery-level-freertos           | PSoC <sup>™</sup> 6 MCU with BLE Connectivity: Battery Level (FreeRTOS)                                   |

| mtb-example-psoc6-ble-throughput-freertos              | PSoC <sup>™</sup> 6 MCU: BLE Throughput Measurement (FreeRTOS)                                            |

| mtb-example-psoc6-usb-audio-device-freertos            | PSoC <sup>™</sup> 6 MCU: USB Audio Device with FreeRTOS                                                   |

| mtb-example-psoc6-usb-cdc-echo                         | PSoC <sup>™</sup> 6 MCU: USB CDC Echo Application                                                         |

| mtb-example-psoc6-usb-hid-mouse                        | PSoC <sup>™</sup> 6 MCU: USB HID Mouse Application                                                        |

| mtb-example-psoc6-usb-hid-generic                      | PSoC <sup>™</sup> 6 MCU: USB HID Generic Application                                                      |

| mtb-example-psoc6-usb-msc-file-system                  | PSoC <sup>™</sup> 6 MCU: USB Mass Storage File System                                                     |

| mtb-example-psoc6-usb-msc-logger                       | PSoC <sup>™</sup> 6 MCU: USB Mass Storage Logger                                                          |

| Code Examples (PSoC <sup>™</sup> Creator)              |                                                                                                           |

| CE219521                                               | PSoC <sup>™</sup> 6 MCU - GPIO Interrupt                                                                  |

| CE216795                                               | PSoC <sup>™</sup> 6 MCU Dual-Core Basics                                                                  |

| CE218129                                               | PSoC <sup>™</sup> 6 MCU Wake up from hibernate Using Low-Power<br>Comparator                              |

#### References

| Table 4 (continued) Documents related to PSoC <sup>™</sup> 6 MCU features |                                                                                                |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|

| Document                                                                  | Document name                                                                                  |  |  |  |

| CE218542                                                                  | PSoC <sup>™</sup> 6 Custom Tick Timer Using RTC Alarm Interrupt                                |  |  |  |

| CE219339                                                                  | PSoC <sup>™</sup> 6 MCU MCWDT and RTC Interrupts (Dual Core)                                   |  |  |  |

| CE220061                                                                  | PSoC <sup>™</sup> 6 MCU Multi-Counter Watchdog Interrupts                                      |  |  |  |

| CE220607                                                                  | PSoC <sup>™</sup> 6 MCU Watchdog Timer in interrupt mode                                       |  |  |  |

| CE220169                                                                  | PSoC <sup>™</sup> 6 MCU Periodic Interrupt Using TCPWM                                         |  |  |  |

| CE212736                                                                  | PSoC <sup>™</sup> 6 MCU with Bluetooth <sup>™</sup> Low Energy (BLE)<br>Connectivity - Find Me |  |  |  |

| Software/IDE                                                              |                                                                                                |  |  |  |

| PSoC <sup>™</sup> Creator                                                 | PSoC <sup>™</sup> Creator User Guide                                                           |  |  |  |

| ModusToolbox <sup>™</sup>                                                 | ModusToolbox <sup>™</sup> User Guide                                                           |  |  |  |

| Peripheral Driver Library (PSoC <sup>™</sup> Creator)                     | PDL API Reference available on installation                                                    |  |  |  |

| Peripheral Driver Library (ModusToolbox <sup>™</sup> )                    | PDL API Reference                                                                              |  |  |  |

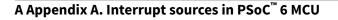

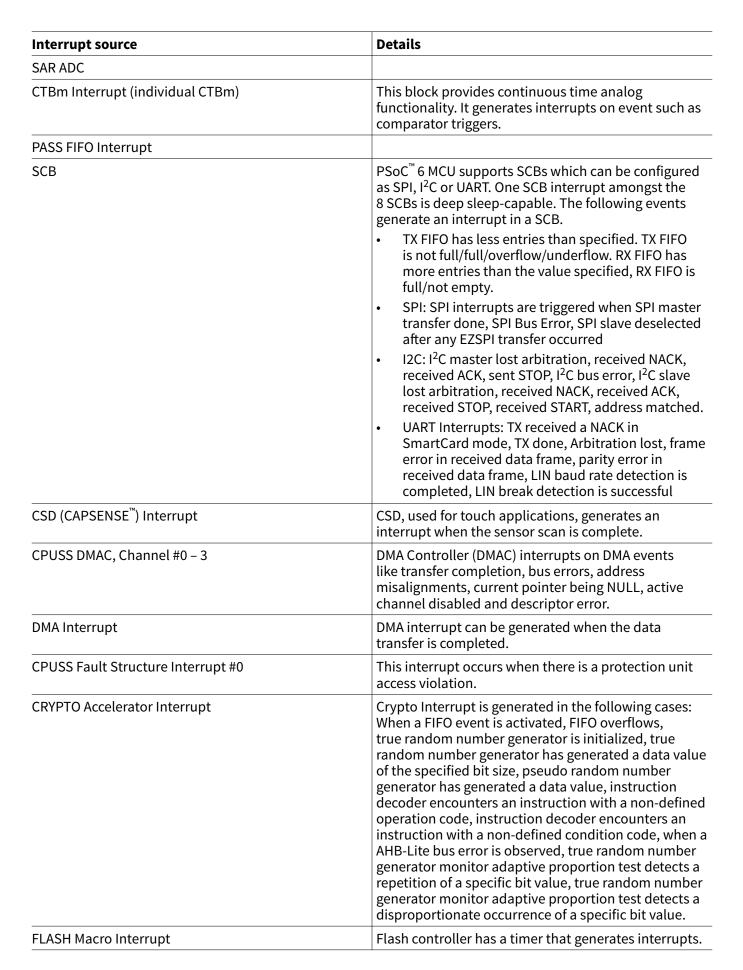

### A Appendix A. Interrupt sources in PSoC<sup>™</sup> 6 MCU

## A

## Appendix A. Interrupt sources in PSoC<sup>™</sup> 6 MCU

For information on IRQ number and applicable power mode for each interrupt, see the "Interrupts" chapter of the respective devices' technical reference manual.

| Interrupt source                               | Details                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOs                                          | Each port consists of a maximum of eight pins. Each<br>pin can generate an interrupt, but the vector address<br>is common for all pins in a port. Firmware must<br>identify the pin that caused the interrupt. PSoC <sup>™</sup> 6<br>MCU enables interrupt trigger on the rising edge,<br>falling edge, or both edges of the GPIO signal. This<br>interrupt can wake the device from sleep, deep-sleep<br>modes. |

|                                                | There is a GPIO All Ports interrupt that allows<br>combining all port interrupts into a single vector.<br>Firmware must identify the port that caused the<br>interrupt.                                                                                                                                                                                                                                           |

|                                                | There is a GPIO Supply Detect Interrupt that can be<br>used to detect the supply ramping up or ramping<br>down.                                                                                                                                                                                                                                                                                                   |

| LPComp                                         | Like GPIOs, an interrupt can be triggered on the rising<br>edge, falling edge, or both edges of the comparator<br>output signal. LPComp can also wake the device from<br>sleep, deep sleep, and hibernate power modes.                                                                                                                                                                                            |

| SCB (deep sleep)                               | SCB interrupt that can wakeup CPU/system from deep sleep                                                                                                                                                                                                                                                                                                                                                          |

| Multi Counter Watchdog Timer (MCWDT) Interrupt | MCWDT configures two 16-bit counters and one 32-<br>bit counter capable of generating periodic interrupts.<br>MCWDT can wake the CPU from deep sleep power<br>mode.                                                                                                                                                                                                                                               |

| Backup Domain Interrupt                        | Backup domain interrupt includes the RTC ALARM1,<br>RTC ALARM2, and RTC century overflow interrupt. This<br>can be used to wake the CPU from sleep, deep sleep,<br>and hibernate power modes.                                                                                                                                                                                                                     |

| Other Combined Interrupts for SRSS             | The following cases generate this interrupt: WDT<br>interrupt, Low Voltage Detect (LVD) interrupt, and<br>clock calibration interrupt. WDT interrupt occurs<br>when the watchdog counter value matches the preset<br>Counter Match value. Missing two interrupts will cause<br>a watchdog reset.<br>Low-voltage detect (LVD) interrupt when the device                                                            |

|                                                | supply voltage drops below a threshold.<br>Clock calibration interrupt is triggered when clock<br>calibration is complete.                                                                                                                                                                                                                                                                                        |

|                                                | These are capable of waking the CPU from deep sleep.                                                                                                                                                                                                                                                                                                                                                              |

| CTBm Interrupt (all CTBms)                     | This block provides continuous time analog<br>functionality. It generates interrupts on event such as<br>comparator triggers.                                                                                                                                                                                                                                                                                     |

| Bluetooth Radio Interrupt                      | Bluetooth sub-system interrupt                                                                                                                                                                                                                                                                                                                                                                                    |

| IPC Interrupt                                  | IPC interrupts could be triggered when an IPC release or notify event occurs.                                                                                                                                                                                                                                                                                                                                     |

neor

| Interrupt source                           | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating point interrupt                   | Floating Point operation fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CM0+ CTI #0                                | CTI triggers are used to communicate events between debug components.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CM4 CTI #0                                 | CTI triggers are used to communicate events between debug components.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ТСРWМ                                      | The TCPWM block can be configured to work as a 16- or 32-bit timer, counter, or PWM. It can generate interrupts on terminal count, input capture signal, or a compare true event.                                                                                                                                                                                                                                                                                                                                   |

| UDB Interrupt #0                           | Any digital signal generated in a UDB can trigger<br>an interrupt. Signals are routed to the interrupt<br>controller through the routing fabric known as Digital<br>System Interconnect (DSI).                                                                                                                                                                                                                                                                                                                      |

| I2S Audio Interrupt                        | Interrupt can be generated in the following cases. Less<br>entries in the TX FIFO than the value specified, TX FIFO<br>is not full, TX FIFO is empty, attempt to write to a<br>full TX FIFO, attempt to read from an empty TX FIFO,<br>triggers when the Tx watchdog event occurs, more<br>entries in the RX FIFO than the value specified , RX<br>FIFO is not empty, RX FIFO is full, attempt to write to a<br>full RX FIFO, attempt to read from an empty RX FIFO,<br>triggers when the Rx watchdog event occurs. |

| PDM/PCM Audio interrupt                    | More entries in the RX FIFO than the value specified,<br>RX FIFO is not empty, attempt to write to a full RX<br>FIFO, attempt to read from an empty RX FIFO                                                                                                                                                                                                                                                                                                                                                         |

| Energy Profiler Interrupt                  | This interrupt occurs on a profiling counter overflow.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Serial Memory Interface Interrupt          | This interrupt is activated when TX data FIFIO is activated, RX data FIFO is activated, alignment error, FIFIO overflow.                                                                                                                                                                                                                                                                                                                                                                                            |

| USB Interrupt                              | The USB block has a predefined set of 13 interrupt<br>trigger events that can be mapped to either one of the<br>three interrupts. Events such as USB Start of Frame<br>(SOF), USB bus reset, data endpoint events, control<br>endpoint events, Arbiter Interrupt Event, and Link<br>Power Management (LPM) event generate interrupts.                                                                                                                                                                               |