Infineon erweitert die Power-MOSFET-Familie OptiMOS™ Source-Down um einen 40-V-Baustein im PQFN-Gehäuse

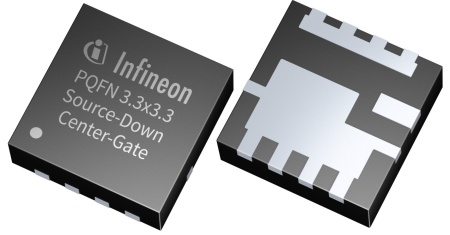

München, 29. Oktober 2020 – Moderne Systeme für die Stromversorgung erfordern eine hohe Leistungsdichte und kleine Formfaktoren, damit die Leistung auf Systemebene maximiert werden kann. Die Infineon Technologies AG (FSE: IFX / OTCQX: IFNNY) stellt sich dieser Herausforderung, indem sie auf System-Innovationen durch Verbesserungen auf Komponentenebene setzt. Zusätzlich zu dem im Februar eingeführten 25-V-Baustein bringt Infineon deshalb jetzt den Niederspannungs-Leistungs-MOSFET OptiMOS™ 40 V auf den Markt. Er ist ebenfalls im Source-Down-(SD)-PQFN-Gehäuse mit einer Grundfläche von 3,3 x 3,3 mm 2 untergebracht. Der 40 V SD MOSFET eignet sich besonders für Schaltnetzteile im Bereich Server, Telekommunikation und OR-ing sowie für Anwendung im Bereich Batterieschutz, Elektrowerkzeuge und Ladegeräte.

Das Silizium im SD-Gehäuse im Inneren des Bauteils wurde umgedreht. Dadurch wird das Source-Potenzial über das Thermal-Pad mit dem PCB verbunden anstelle des Drain-Potentials. Das führt im besten Fall zu einer deutlichen Reduzierung des R DS(on) um bis zu 25 Prozent im Vergleich zur heutigen Technologie. Auch der thermische Widerstand zwischen Junction to Case (R thJC) ist im Vergleich zu den traditionellen PQFN-Gehäusen deutlich verbessert. Der SD OptiMOS ist in der Lage, hohen Dauerströmen von bis zu 194 A standzuhalten. Zusätzlich erlauben die optimierten Layoutmöglichkeiten und die effizientere Ausnutzung der Leiterplatte eine größere Designflexibilität bei gleichzeitig höchster Leistung.

Verfügbarkeit

Der Niederspannungs-Leistungs-MOSFET OptiMOS SD 40 V ist in zwei Versionen, Standard und Center-Gate, erhältlich. Die Center-Gate-Variante ist für den Parallelbetrieb mehrerer Bausteine optimiert. Beide Varianten im PQFN-Gehäuse 3,3 x 3,3 mm 2 können ab sofort bestellt werden. Weitere Informationen sind erhältlich unter www.infineon.com/source-down.

Informationsnummer

INFPSS202010-007

Pressefotos

-

Der Niederspannungs-Leistungs-MOSFET OptiMOS™ SD 40 V ist in zwei Versionen, Standard und Center-Gate, erhältlich. Die Center-Gate-Variante ist für den Parallelbetrieb mehrerer Bausteine optimiert. Das Source-Down-(SD)-PQFN-Gehäuse mit einer Grundfläche von 3,3 x 3,3 mm² reduziert das RDS(on) um bis zu 25 Prozent und verbessert den thermischen Widerstand zwischen Junction to Case deutlich.PQFN_3_3x3_3_SDCG

Der Niederspannungs-Leistungs-MOSFET OptiMOS™ SD 40 V ist in zwei Versionen, Standard und Center-Gate, erhältlich. Die Center-Gate-Variante ist für den Parallelbetrieb mehrerer Bausteine optimiert. Das Source-Down-(SD)-PQFN-Gehäuse mit einer Grundfläche von 3,3 x 3,3 mm² reduziert das RDS(on) um bis zu 25 Prozent und verbessert den thermischen Widerstand zwischen Junction to Case deutlich.PQFN_3_3x3_3_SDCGJPG | 457 kb | 2126 x 1110 px