# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# THIS SPEC IS OBSOLETE

**Spec No**: 001-75813

Spec Title: H BRIDGE BASED MOTOR DRIVE

PROTECTION USING PSOC(R)3 - AN75813

Sunset Owner: K Sanjeev Kumar (KUK)

Replaced by: None

#### AN75813

# H Bridge Based Motor Drive Protection Using PSoC® 3

Author: Sudip Mondal Associated Project: Yes Associated Part Family: CY8C38xx Software Version: PSoC<sup>®</sup> Creator<sup>™</sup> 2.0 Related Application Notes: "For a complete list of the application notes, click here."

If you have a question, or need help with this application note, contact the author at smon@cypress.com.

AN75813 demonstrates the use of a PSoC 3 for brushed DC motor drive protection and diagnostics. The PSoC 3 protection system is optimized for the widely used H bridge, but it can easily be adapted to other DC motors. The implementation emphasizes the use of digital logic present on the PSoC 3 to free the CPU for more involved tasks such as motor control. This application note specifically addresses motor drive protection and diagnostics and does not discuss motor control.

#### **Contents**

| Introduction                                                    | 2          |

|-----------------------------------------------------------------|------------|

| Smart Drivers and their limitations                             | 2          |

| Alternate Methods to Drive H Bridges                            | 2          |

| Capacitive Pump                                                 | 3          |

| Boost Converter                                                 | 3          |

| Common Faults in H Bridge Based Motor Drives                    | 4          |

| Operation of H Bridge Based Motor Drives Of Safe Operating Area | 5          |

| Finite Set of Valid Bridge Operations                           | 6          |

| High Level Architecture of Fault Detection and System           | Protection |

| Implementation of the Fault Detection and System                |            |

| The Half Bridge Interface Block                                 |            |

| Over Current, Fault Detect and Diagnostic Blo                   |            |

| Blanking Timer                                                  |            |

| Over Current Block                                              | 14         |

| Fault Detect Block                                              | 16         |

| Diagnostic Block                                                | 18         |

| Motor Drive Signals Block                                       |            |

| Firmware Block                                                  | 24         |

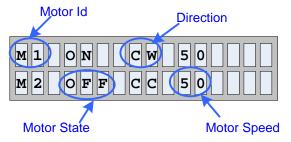

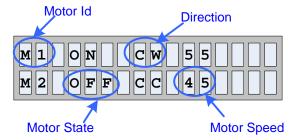

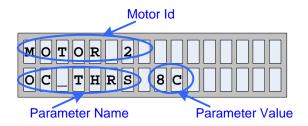

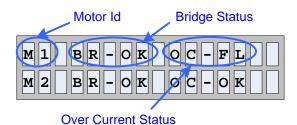

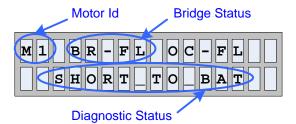

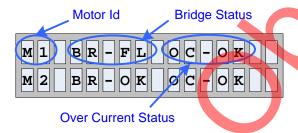

| User Interface                                                  | 28         |

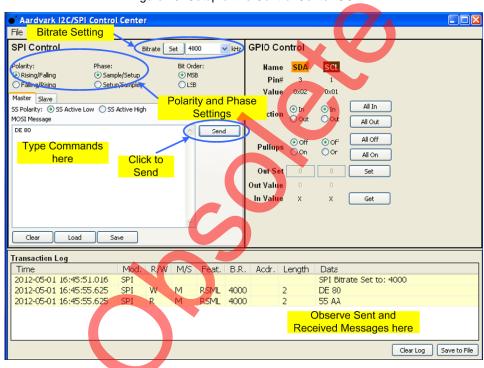

| SPI Communication                                               | 28         |

| LCD Interface                                                   | 33         |

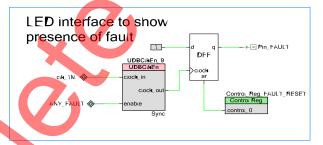

| LED Interface                                                   | 33         |

|                                                                 |            |

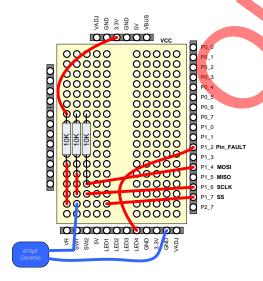

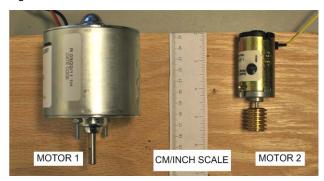

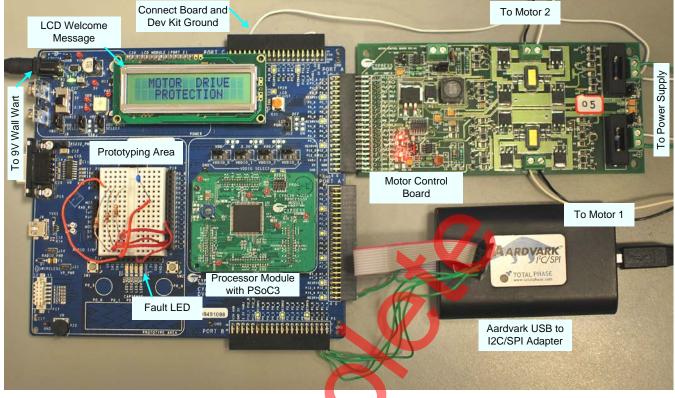

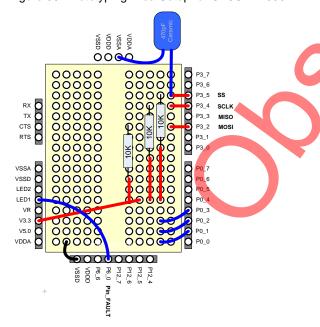

| Demonstration with CY8CKIT-001 PSoC Kit with | PSoC 3 |

|----------------------------------------------|--------|

| Processor Module, and Motor Control Board    | 34     |

| Demonstration Setup                          | 34     |

| Demonstration of Operation                   | 35     |

| Summary                                      | 40     |

| Related Application Notes                    | 40     |

| Appendix                                     | 41     |

| Setup Details for CY8CKIT-030                | 41     |

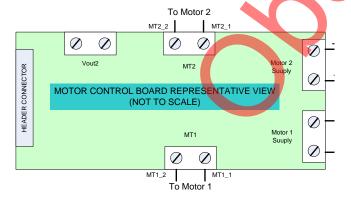

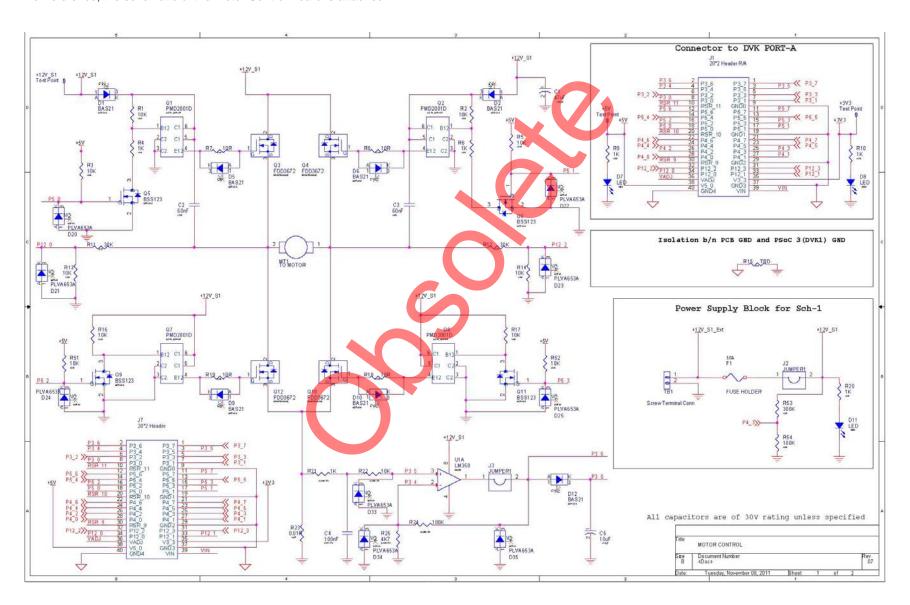

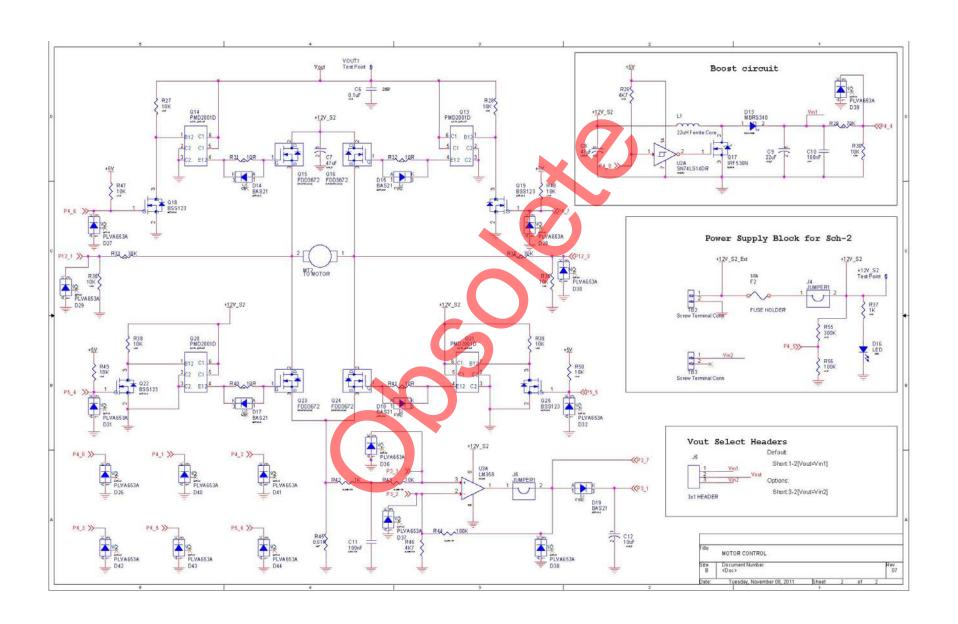

| Motor Control Board                          | 42     |

|                                              |        |

#### Introduction

DC motors are widely used in many automotive applications such as HVAC, power seats, wipers, and power windows. It is important to protect the motor drive system, because failure to do so may result in damaged components and, in some cases, hazardous conditions. Motor drive systems consist of switching elements and drivers. The switching elements (e.g. FETs, relays, IGBTs) are typically arranged in the form of an H bridge. The drivers turn the switching elements on and off according to the commands from the controller. Drivers are required, because microcontrollers typically cannot handle the voltage and current levels required to operate the switches. Fault detection, the protection mechanism, or both are often built into the switches or the drivers to signal an abnormal state such as over current or over voltage to the controlling microprocessor. These "smart" switches and drivers use different methods to report faults ranging from simple digital pins to inter-device communication channels such as SPI or I2C. When they detect a fault, they either disable the motor drive or leave that task to the controlling microprocessor.

In this application note, we discuss an alternate approach to fault detection and protection. Instead of using prepackaged motor drivers with built-in protection systems, we use basic components such as FETs and gate drivers. This method results in a larger number of available test signals and hence better determination of fault conditions. Combined with the configurability of PSoC 3 devices, this method also leads to a scalable and programmable system that can be easily shared across multiple bridges. This eliminates the need to build a fault detection system for each newly added motor. We briefly describe the limitations of smart drivers and alternate methods to drive gates. Then we discuss faults and ways to use the PSoC 3 as a fault detection and protection system.

#### **Smart Drivers and their limitations**

Drivers are necessary to interface a microcontroller with a switching device as most microcontrollers cannot handle the voltage and current levels required to control switches. Drivers with built-in, smart protection mechanisms are generally more expensive than their less smart counterparts. Smart drivers are attractive for two reasons:

- They provide the level translation required for highside gate driving.

- It is not easy to find microcontrollers with sufficient programmable analog and digital capabilities to implement a central fault detection and protection system.

However, smart drivers have limited configurability and a fixed set of fault detection abilities. The system designer has limited control over the functional definition of a fault and may have to resort to different devices for different motors. Moreover, many of the drivers can only report a fault when the motor is running. This reduces their

effectiveness for infrequently driven motors such as an HVAC flap controller motor or a seat positioning motor.

The PSoC 3 is an excellent solution in these cases. Configurable precise analog and digital blocks inside the device handle all fault detection and protection. This removes the necessity to use expensive smart drivers and switches. The system described in this application note is capable of:

- Easy and dynamic configuration of the definition of fault parameters such as over current threshold, blanking time and so on without the use of additional components

- Flexible fault reporting ranging from the presence of a fault to a detailed status of the motor driving bridge

- Continuous monitoring of inactive motors to reduce the risk of failures and hazards

Because the PSoC 3 cannot handle the voltage and current levels required for a high-side gate drive, we need alternative methods to do so. In the next section, we demonstrate two ways to implement level translation for a high-side gate drive without the use of specialized drivers.

## Alternate Methods to Drive H Bridges

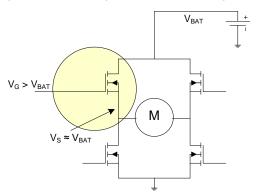

It is difficult to drive the gates of high-side N-type FETs, because the gate voltage must be higher than the available battery voltage. Figure 1 illustrates the problem.

When the highlighted switch is turned on, its source voltage  $V_S$  is close to the battery voltage  $V_{BAT}$ . Therefore, its gate voltage must sufficiently exceed the sum of the source voltage and the gate-to-source threshold. The FETs used in motor drives are designed to handle substantial current (commonly two to four amps) and often have large threshold voltages. Therefore, we need a method to generate a voltage higher than the available battery voltage. Two common methods to generate the higher voltage are:

- Use a capacitive charge pump to drive the gate voltage to almost double the battery voltage

- Use of a boost converter

Figure 1. Gate Voltage Requirement for High Side Switch

#### **Capacitive Pump**

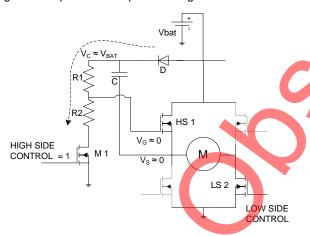

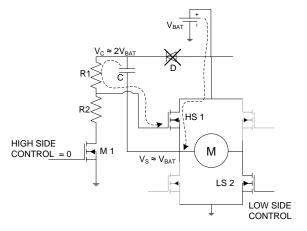

Figure 2 illustrates capacitive pumping of the voltage with an example application. It requires a PWM on the high side FET HS 1 while the low side FET LS 2 is kept ON. Low side FETs are relatively easier to drive and are not discussed in this application note. The other two switches remain inactive during the operation. We use an FET M1 with a small threshold voltage to enable direct operation by microcontroller pins.

In Figure 2.a, the microcontroller pin is high (HIGH SIDE CONTROL = 1). As the gate of M1 goes high, it is turned ON which leads to current flow through the resistors R1 and R2. The resistors R1 and R2 are appropriately sized so that the gate voltage ( $V_G$ ) is near 0, and the FET HS 1 is OFF. As a result, the source voltage of HS1 ( $V_S$ ) is close to ground. The capacitor (C) is charged to a voltage ( $V_{BAT}$ ) less one diode drop. The dashed line traces the path of the current.

When the microcontroller pin is low (HIGH SIDE CONTROL = 0). M1 turns OFF. This makes the voltage  $V_G = V_C \approx V_{BAT}$  (the gate current of FET HS 1 is negligible). The gate to source voltage exceeds the threshold voltage of the FET HS 1, and it starts to turn ON.

Figure 2. Capacitive Pump Based High-Side Gate Drive

Figure 2.a

Figure 2.b

As HS 1 turns ON, its source voltage rises. Since the voltage across the capacitor cannot change instantaneously,  $V_C$  also increases. In turn,  $V_G$  increases since the capacitor supplies the gate of HS 1. The Diode (D) becomes reverse biased and no current flows through it. This process continues until HS 1 is fully turned ON. At this point,  $V_C$  is almost equal to twice the battery voltage ( $V_{BAT}$ ), as illustrated in Figure 2.b. The cycle repeats as the controller pulls the HIGH SIDE CONTROL high again. In this manner, switch HS 1 can be cycled ON and OFF.

Extra drivers can be added in front of the FETs to supply the required gate current in cases where the size of the main FETs and the desired turn ON/turn OFF time require it. Because the capacitor (C) supplies the gate current, it must be correctly sized.

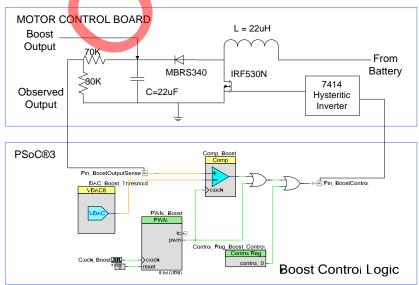

#### **Boost Converter**

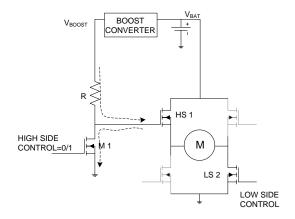

Figure 3 illustrates the use of a boost converter. A boost converter accepts the battery voltage ( $V_{BAT}$ ) as its input and produces an output voltage ( $V_{BOOST}$ ) higher than  $V_{BAT}$ . This voltage is then used to drive the high-side switch.

When HIGH SIDE CONTROL is high (1), the FET M1 is ON. This condition pulls the gate of HS 1 to ground and turns it off. When HIGH SIDE CONTROL is low, the voltage V<sub>BOOST</sub> raises the gate of HS 1 and turns it ON.

The requirement to use additional components to monitor and control the boost means that the boost converter method is used infrequently. However, this method has two advantages over the capacitive pump method:

- The boost converter does not require replication for each high side switch. This is an advantage in applications which drive several motors such as an HVAC.

- The capacitive method can be used only when the high side switch needs a PWM. The capacitor C must be periodically charged so that it can supply the gate.

The configurable analog and digital peripherals in PSoC 3 allow us to build the boost control circuit inside the device. This eliminates the need for external control components

Figure 3. Boost Converter Based High-Side Gate Drive

and makes the boost converter method particularly easy to implement.

Nevertheless, the fault detection and protection methods are not limited to any particular implementation of high side gate drive, and we demonstrate the functionality of the system with both the capacitive pump and the boost converter. We start with a discussion of the common faults that occur on an H bridge based motor drive.

## **Common Faults in H Bridge Based Motor Drives**

H bridges are commonly used in motor drives as well as many other applications. As such, the faults discussed in this section are not limited to motor drives. The major faults found with motor drives involve the switching elements (e.g. MOSFETs, IGBTs, and so on). Each switching element has its Safe Operating Area (SOA), and faults lead to operations outside the SOA. Operations outside the SOA reduce the life of the switches significantly and may lead to hazardous conditions.

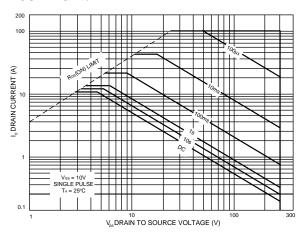

The SOA is estimated based on the junction temperature of the switch. The junction temperature depends on the ambient temperature, the power dissipation across the switch, and the thermal resistance of the junction. Device datasheets generally present a graphical representation of the SOA and mandate that the operation be restricted to the SOA. Figure 4 shows a typical example of the SOA for a MOSFET switch, as presented in the datasheet.

The figure shows that the SOA is governed by the drain to source voltage, the drain current and the duration of operation. Generally, the voltage tolerances of the switches are an order of magnitude higher than the voltages applied in practice. Also, when the switch is conducting, the voltage across the switch is close to zero. The major parameter affecting the safe operation of the switch is the current through the switch.

Current is generally measured using a low side or a high side shunt resistor (sometimes both), which converts the

Figure 4. Example of the Safe Operating Area (SOA) of a MOSFET Switch

current to a voltage signal. This voltage can then be compared against a threshold for detection of over or under current, or measured otherwise (e.g. using and ADC). With the availability of continuously configurable analog and digital hardware in PSoC 3, it becomes easy to design a configurable current monitoring and limiting system, which ensures that the switching elements operate in their SOA.

It should be noted that the SOA is specified for a particular ambient temperature (25 °C in the figure). For different ambient temperatures, the allowable period of operations become different (they decrease with increasing ambient temperature). Therefore, it is useful to be able to change the allowable ON-time with changing temperature. Most smart drivers set this time using an external component such as a resistor or a capacitor and therefore lack the ability to change it according to temperature.

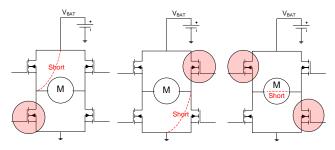

Different conditions may lead to excessive current through the switches. One of the reasons may be excessive load on the motor (a jammed motor for example). Motor resistance limits the maximum amount of current from a large load and is generally specified as the blocked rotor current for a given voltage by the motor manufacturer. Under certain circumstances, much larger currents may flow. If a motor terminal is shorted to battery or ground and a corresponding switch is turned on, hazardous shorts may be created. Similar circumstances may arise due to a shorted motor. Figure 5 shows a few examples, where the highlighted switch is turned on for a pre-specified time as part of normal operation (e.g. motor drive, active braking and so on).

Such conditions, if prolonged beyond safe limits, not only lead to operations outside the SOA, but also to dangerous conditions. It is necessary to detect and act upon such conditions immediately; it is also advantageous to be able to prevent such occurrences by periodically monitoring the H bridges when the motor is not in operation.

An open load does not lead to operation outside the SOA of the switches, as no current flows through the switches. Therefore, this fault is less critical to the electrical safety of the system. However, it leads to a functional fault (i.e. the motor can no longer perform the task it is assigned) and may be critical (e.g. in a wiper motor or door lock motor). When we account for functional safety, this is also outside the safe operating area in an extended sense. Therefore, the load also must be monitored periodically to guarantee

Figure 5. Hazardous Short Conditions on an H Bridge

functionality.

In this application note, we consider the following faults:

- Over Current

- Shorts to Battery

- Shorts to Ground

- Load Open

Because a shorted motor can be treated as a simultaneous short battery and ground, it is covered by this fault list. In the next section, we discuss the effects of the faults on electrical parameters of generic H bridge based motor drives. These parameters indicate operation outside SOA and are important for a fault detection and protection system.

# Operation of H Bridge Based Motor Drives Outside the Safe Operating Area

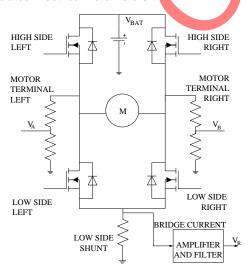

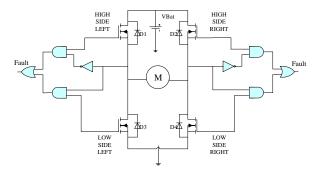

Figure 6 illustrates a generic H bridge based motor drive. The two main operation modes during which the motor spins are:

- The High Side Left and the Low Side Right switches are ON; the other two switches are OFF.

- The High Side Right and the Low Side Left switches are ON; the other two switches are OFF.

In most cases, one of the switches is not continuously ON. It is pulse width modulated for better control of the amount of current through the motor, and subsequently its speed.

The low side shunt is used to measure the instantaneous current through the motor when one high side and one low side switches are conducting. The voltage  $V_R$  is indicative

Figure 6. Generic H Bridge Based Motor Drive with Associated Electrical Parameters

of the bridge current. If one switch is suddenly turned OFF, the current through the motor diverts through one of the diodes across the switches until it drops to zero. This may or may not be registered by the low side shunt since the current may not be flowing through it, or it may reverse its direction.

The fault detection system monitors the Motor Terminal Left and Motor Terminal Right nodes. The state of the bridge can be inferred from the voltages  $V_A$  and  $V_B$ . Resistor dividers are generally used to reduce high voltages close to  $V_{BAT}$  (12 to 48 V) to a range that can be read by the electronic control and protection system (for example a microcontroller) which generally operates at a lower voltage (3 to 5 V).

Under normal operating conditions (a spinning motor),  $V_R$  is limited to a finite range. The minimum current through an unloaded motor sets the lower bound. The system designer sets the upper bound as deemed safe for a maximum allowable load. A measurement of  $V_R$  less than the lower bound indicates an open load ( $V_R$  (LOAD OPEN)). A measurement larger than the upper bound indicates over current ( $V_R$  (OVER CURRENT)).

Similarly, the signals  $V_A$  and  $V_B$  also have a normal operating range. For example, with the High Side Left FET turned ON,  $V_A$  is pulled up close to  $V_{BAT}$ . The minimum value of  $V_A$  is determined by the maximum drop across the FET, which in turn is determined by the maximum allowable current. The maximum value of  $V_A$  is actually  $V_{BAT}$  (assuming zero drop across the FET). These two voltages can be termed as  $V_A$  (NO LOAD) and  $V_A$  (FULL LOAD). With the Low Side right FET turned ON,  $V_B$  has a maximum value of  $V_B$  (FULL LOAD) and a minimum value of  $V_B$  (NO LOAD).

The definition of a faulty or hazardous condition is a state where these signals are outside normal operating ranges. Table 1 lists the various possibilities, with High Side left switch turned ON (corresponding Low Side left switch turned OFF) and Low Side right switch turned ON (corresponding High Side right switch turned OFF).

The configuration shown in Table 1 can detect the MOTOR TERMINAL LEFT shorted to ground and MOTOR TERMINAL RIGHT shorted to  $V_{BAT}$  faults. The complimentary configuration (High Side Right ON and Low Side Left ON) can detect MOTOR TERMINAL LEFT shorted to  $V_{BAT}$  and MOTOR TERMINAL RIGHT shorted to ground.

| Case   | High<br>Side<br>Left                                                                                                               | High<br>Side<br>Right | Low<br>Side<br>Left | Low<br>Side<br>Right | VA                                           | VB                                           | VR                                                                 | Inference                                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|----------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1      | 1                                                                                                                                  | 0                     | 0                   | 1                    | $V_A \ge V_{A \text{ (FULL LOAD)}}$          | $V_B \le V_{B \text{ (FULL LOAD)}}$          | $V_{R \; (LOAD \; OPEN)} \le V_{R} \le V_{R \; (OVER \; CURRENT)}$ | Normal Operation/ (V <sub>A</sub> shorted to battery and V <sub>B</sub> shorted to ground cannot be detected) |

| 2      | 1                                                                                                                                  | 0                     | 0                   | 1                    | $V_A \le V_{A \text{ (FULL LOAD)}}$          | $V_B \ge V_{B \text{ (FULL LOAD)}}$          | V <sub>R</sub> > V <sub>R (OVER CURRENT)</sub>                     | Over current condition                                                                                        |

| 3      | 1                                                                                                                                  | 0                     | 0                   | 1                    | $V_A \ll V_{A (FULL \ LOAD)}$                | $V_B \le V_{B \text{ (FULL LOAD)}}$          | X                                                                  | V <sub>A</sub> possibly shorted to ground                                                                     |

| 4      | 1                                                                                                                                  | 0                     | 0                   | 1                    | $V_A \ge V_{A \text{ (NO LOAD)}}$            | $V_B >> V_{B (FULL LOAD)}$                   | X                                                                  | V <sub>B</sub> possibly shorted to battery                                                                    |

| 5      | 1                                                                                                                                  | 0                     | 0                   | 1                    | V <sub>A</sub> << V <sub>A (FULL LOAD)</sub> | V <sub>B</sub> >> V <sub>B (FULL LOAD)</sub> | V <sub>R</sub> > V <sub>R (OVER CURRENT)</sub>                     | The load is shorted                                                                                           |

| 6      | 1                                                                                                                                  | 0                     | 0                   | 1                    | $V_A \ge V_{A \text{ (NO LOAD)}}$            | $V_B \le V_{B \text{ (NO LOAD)}}$            | V <sub>R</sub> < V <sub>R (LOAD OPEN)</sub>                        | The load is open                                                                                              |

| Simila | Similar conclusions can be drawn about the configuration High Side Left=0. High Side Right=1. Low Side Left=1 and Low Side Right=0 |                       |                     |                      |                                              |                                              |                                                                    |                                                                                                               |

Table 1. Monitor Signal States for Normal Operations and Fault Conditions

Henceforth, for ease of reading, we often abbreviate the names of the switches by the initials (High Side Left = HSL and so on). A similar table can be prepared for complimentary operation (HSL = 0, LSL =1, HSR =1 and LSR = 0).

Over Current Condition: If the voltages  $V_A$  and  $V_B$  are within normal operating range, then excess  $V_R$  can be due to over current conditions due to load malfunction, switch malfunction, or excessive load. Case 2 in Table 1illustrates an example.

**MOTOR TERMINAL LEFT Shorted to Ground:** In this case, the voltage at  $V_A$  is much lower than its lower limit of normal operation; in fact it is very close to ground. Thus, if HSL is ON and  $V_A$  is much lower than the threshold, then  $V_A$  can be assumed to be shorted to ground. Case 3 in Table 1 illustrates an example.

**MOTOR TERMINAL RIGHT Shorted to Battery:** In this case, the voltage at  $V_B$  is not close to zero, in spite of LSR being turned on. This indicates a short to battery. In such cases, heavy current flows through the sense resistor, a condition which provides additional identification. Case 4 in Table 1 illustrates an example.

**Load is Shorted:** A shorted load has its two terminals connected through a wire or a very low resistance. Both  $V_A$  and  $V_B$  are close to the mid-range voltage, and heavy current flows through the sense resistor showing large  $V_R$ . Case 5 in Table 1 illustrates an example

**Load is Open:** In this case, the voltages  $V_A$ ,  $V_B$  and  $V_R$  are all outside normal operating ranges. Case 6 in Table 1 illustrates example.

The battery voltage may drop due to excessive current during a short condition. Because voltages  $V_A$  and  $V_B$  are proportional to the battery voltage, their values might be inappropriately measured in these cases. The car battery is essentially a rather large capacitor, and therefore changes in battery voltage are slow. Therefore, if the fault detection is quick enough, we can avoid incorrect reading of the voltages. Table 1 demonstrates that the identification of the faults requires comparison of the three

monitor signals against a large number of thresholds. Completing so many comparisons in a limited amount of time requires a large number of comparators. To use an Analog to Digital Converter, voltage comparisons and corresponding corrective actions during faults must be implemented in firmware. This may result in non-deterministic timing of operations due to uncertainties in firmware execution, especially if it contains large number of interrupts. A hardware solution is preferable.

The first corrective action for all of these fault conditions is to deactivate the bridge and to suspend the current operation; this simplifies the problem. It is often sufficient to detect the existence of a fault and to deactivate the bridge, without immediate identification of the exact fault. This action requires a reduced set of observations to detect the presence of a fault and preferably consumes fewer resources than more comprehensive fault detection methods. In the next section, we describe a method to achieve that.

# Finite Set of Valid Bridge Operations

The key to quickly determine the presence of a fault is to reduce the number of possible comparisons without sacrificing the detectability of any critical fault. To do this, we group the faults into two sets:

- Faults that affect the H bridge elements, lead to hazardous condition, and so require immediate action including: shorts to battery, shorts to ground and over current condition.

- Faults that affect functionality but do not lead to hazardous condition on the H-bridge, and so do not require immediate action such as the open load fault.

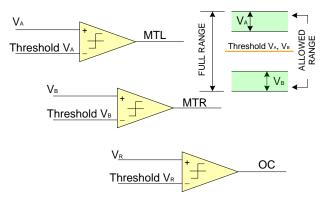

The modified detection requirements allow us to reduce the necessary comparisons to three. With a single threshold each for  $V_A$ ,  $V_B$ , and  $V_R$ , we have the simple, three-comparator implementation shown in Figure 7. The typical allowable ranges of  $V_A$  and  $V_B$  for the condition are in Table 1.

Figure 7. Three Comparator Fault Condition Detection

The MTL, MTR and OC are digital signals representative of the voltages at nodes MOTOR TERMINAL LEFT, MOTOR TERMINAL RIGHT and excessive current through the bridge respectively. Table 4 depicts their interpretations. In the presence of a fault, the deviation of the voltages  $V_{\rm A}$  and  $V_{\rm B}$  from their allowable ranges is large; this allows us to use only a single threshold for both the voltages. A current threshold should be chosen based on the motor and the allowable load. PSoC enables us to configure the thresholds dynamically and cater to different situations. For example, we can modify the current threshold during motor start to prevent false over current detection due to high inrush current.

The motor can either be driven or stationary, as required by the application. Depending on the direction of rotation of the motor, only certain combinations of these three signals are allowable as shown in Table 2. The table shows only the ON state of the switches (i.e. the OFF periods in a PWM application are ignored).

Table 1 illustrates that certain faults are undetectable for each direction of rotation. Also, it is not possible to infer the existence of a load open fault from the digital signals when the motor is running. To circumvent this difficulty, we use a special Diagnostic Sequence (Table 3) to monitor the H bridge periodically when the motor is stationary.

The Diagnostic sequence has the following characteristics:

- A high side switch and a low side switch are not simultaneously ON at any point of the sequence.

- The sequence can successfully detect and identify the presence of one fault. If the bridge suffers from multiple faults then the sequence may not correctly identify any single fault. However, it still detects at least one fault.

The Diagnostic Sequence can both detect and identify a fault. As a high side and a low side switch are never ON at the same time, there should be no current through the motor. This enables us to run this sequence whenever required without driving the motor.

Although not explicitly shown in the table, there is a state with all switches OFF inserted between two consecutive

Table 2. Allowable States of the Digital Signals Based on the Direction of Motion

| Signal | Direction 1 | Direction 2 |

|--------|-------------|-------------|

| HSL    | 1           | 0           |

| HSR    | 0           | 1           |

| LSL    | 0           | 1           |

| LSR    | 1           | 0           |

| MTL    | 1           | 0           |

| MTR    | 0           | 1           |

| ОС     | 0           | 0           |

Table 3. Diagnostic Sequence

| HSL | HSR | LSL | LSR | Target Fault              | Expected state of MTL and MTR |

|-----|-----|-----|-----|---------------------------|-------------------------------|

| 0   | 0   | 0   | 0   | Short to V <sub>BAT</sub> | MTL=0 MTR=0                   |

| 1   | 0   | 0   | 0   | Short to GND              | MTL=1 MTR=X                   |

| 0   | 0   | 1   | 1   | Neutralize bridge         | MTL=X MTR=X                   |

| 0   | (   | 0   | 0   | Short to GND              | MTL=X MTR =1                  |

| 0   | 0   | 1   | 1   | Neutralize bridge         | MTL=X MTR=X                   |

| 1   | 0   | 0   | 0   | Load open                 | MTL=1 MTR=1                   |

Table 4. Interpretation of Digital Signals

| Digital<br>Signal | Set | Indicates                                                         |

|-------------------|-----|-------------------------------------------------------------------|

| MTL               | 1   | MOTOR TERMINAL LEFT closer to the battery voltage than to ground  |

| MTL               | 0   | MOTOR TERMINAL LEFT closer to ground than to battery voltage      |

| MTR               | 1   | MOTOR TERMINAL RIGHT closer to the battery voltage than to ground |

| MTR               | 0   | MOTOR TERMINAL RIGHT closer to ground than to battery voltage     |

| ОС                | 1   | Current through the bridge higher than allowed                    |

| ОС                | 0   | Current through the bridge within safe limits                     |

steps. This ensures that an active switch is first turned OFF before activating a different switch. If there are no faults on the H bridge or the motor, both the signals MTL and MTR have the same polarity because the motor resistance is only a few ohms. When a high side switch is turned ON, the motor terminals are close to  $V_{BAT}$ , and hence MTL and MTR are both HIGH. When a low side switch is turned ON, they are both LOW. When all switches are turned OFF, the two motor terminals would start going LOW, as the resistor dividers on both sides will pull them down (Figure 6). Therefore, with all switches OFF, both MTL and MTR are LOW. Any deviations from

7

the behaviors mentioned in the table are indicative of faults. Motor terminals may have large capacitances, leading to slow transitions of MTL and MTR from HIGH to

LOW. The bridge is neutralized actively between high side switch activations to bring both the signals LOW. The sequence can be run at high speeds; in the associated project the total sequence takes 200 µs. The designer can decide how frequently the sequence needs to run based on the application. In the associated project, it is run every 2 seconds on a stationary motor.

Table 2 and Table 3 demonstrate how we can interpret a particular combination of digital signals as a fault condition. Only a few of the combinations correspond to a faultless bridge and motor. This enables us use only the digital signals to encode the state of a bridge and allows us to define the Bridge Status Word (BSW) described in Table 6.

The BSW is a snapshot of the voltage and current conditions of the H bridge converted to a single byte. It should be sampled at proper instants to obtain meaningful information. Switches take finite time to turn ON or OFF, and hence the BSW should be sampled only when switches are in defined states and not in transition. A correctly sampled BSW directly maps to either a normal operating condition or a faulty state using a lookup table; this makes fault identification straightforward. It also allows the system to "log" the bridge activity through a sequence of bytes. The system firmware may periodically store the BSW in a circular buffer, maintaining a history for a predetermined amount of time. Table 5 shows a few BSWs and their interpretation. It is by no means an exhaustive list.

If any fault condition is detected when the motor is running, then the motor is stopped and a diagnostic is performed on the motor. It is also performed periodically on stationary motors as a fault discovery mechanism.

From the above discussion, it is clear that the system needs to monitor the control signals (HSL, HSR, LSL and LSR), as well as the status signals (MTL, MTR and OC). If it detects a fault, the system communicates appropriate status to the master. It is advantageous for the system to generate the control signals, as it can take the protective action itself, rather than relying on the master to do so.

Table 5. Select BSWs and Their Interpretation

| BSW  | Meaning                                                                                    |  |  |  |

|------|--------------------------------------------------------------------------------------------|--|--|--|

| 0x4C | The motor is running with HSL and LSR turned ON.                                           |  |  |  |

| 0x4D | The motor is running with HSL and LSR turned ON. There is over current.                    |  |  |  |

| 0x48 | The motor is running with HSL and LSR turned ON. There may be a possible short to ground.  |  |  |  |

| 0x4E | The motor is running with HSL and LSR turned ON. There may be a possible short to battery. |  |  |  |

| 0x4F | Same as above.                                                                             |  |  |  |

| 0x80 | The motor is stationary. All switches are OFF. Bridge is in expected condition.            |  |  |  |

| 0x86 | The motor is stationary. All switches are OFF. There is a short to battery.                |  |  |  |

| 0xC6 | The motor is OFF. HSL is turned ON. Motor is OK                                            |  |  |  |

| 0xC4 | The motor is OFF. HSL is turned ON. Motor is open.                                         |  |  |  |

| 0xC0 | The motor is OFF. HSL is turned ON. There is a short to ground.                            |  |  |  |

This reduces the load on the master. In the next section, we present a high level architecture of a system which can:

- Communicate with a master and configure itself as requested

- Generate the control signals as per request from a master

- Generate the status signals, and the BSW

- Process the BSW to analyze and report faults

Table 6. The Bridge Status Word

| Bit Position | 7                                                                            | 6                                                                                                        | 5                                                                                                         | 4                                                                                                       | 3                                                                                                        | 2                                                                                      | 1                                                                                       | 0                                                                      |

|--------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Bit Name     | Mode                                                                         | HSL                                                                                                      | HSR                                                                                                       | LSL                                                                                                     | LSR                                                                                                      | MTL                                                                                    | MTR                                                                                     | OC                                                                     |

| Description  | 0 = The<br>motor is<br>being<br>driven.<br>1 = The<br>motor is<br>stationary | The gate of<br>the High<br>Side Left<br>transistor,<br>depicts<br>whether it is<br>ON (1) or<br>OFF (0). | The gate of<br>the High<br>Side Right<br>transistor,<br>depicts<br>whether it is<br>ON (1) or<br>OFF (0). | The gate of<br>the Low<br>Side Left<br>transistor,<br>depicts<br>whether it is<br>ON (1) or<br>OFF (0). | The gate of<br>the Low<br>Side Right<br>transistor,<br>depicts<br>whether it is<br>ON (1) or<br>OFF (0). | Depicts whether MOTOR TERMINAL LEFT is pulled to V <sub>BAT</sub> (1) or to ground (0) | Depicts whether MOTOR TERMINAL RIGHT is pulled to V <sub>BAT</sub> (1) or to ground (0) | Depicts Over Current condition. 1 = Over Current, 0 = Normal condition |

# **High Level Architecture of Fault Detection and Protection System**

The availability of a large number of analog and digital resources in the PSoC 3 allows one to easily design the fault detection and protection system. A good architecture

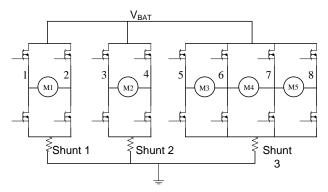

Figure 8. Example Arrangements of H Bridge and Motors

is scalable, i.e. it allows the easy addition of a new H bridge or a new motor. Also, a good architecture minimizes resource usage to enable the implementation of additional features if required.

The physical connection of the motors and the bridges significantly influences architectural choices. In many applications, H bridges are shared across motors. This is often the case where the motors need not run both simultaneously and independently as in the example shown in Figure 8.

Motors M1 and M2 can run simultaneously and independently with any speed and direction, but no two motors among M3, M4 and M5 can be driven independently at the same time. Isolated motors are those where there are no connections with all the switches off

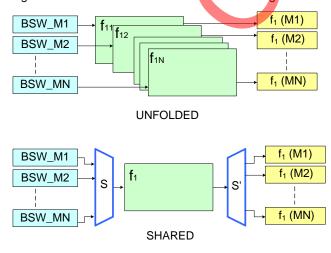

Figure 9. Dedicated vs. Shared Resource Paradigm

between the motors except through the battery or ground. In Figure 8, M1 and M2 are isolated as are M2 and M4. Connected motors are all motors which are not isolated. M3, M4 and M5 are connected and belong to a connected aroup.

The fault detection and protection system should work for both isolated and connected motors. Each motor can be uniquely identified by the two half bridges to which it connect. Therefore, it is more useful to allocate resource for each half-bridge rather than each motor, because halfbridges are shared in connected groups. Such an allocation requires a mechanism for independent access of each individual half-bridge, so that the motors can be independently accessed irrespective of the way they connect.

The next major consideration is the ability to share resources across multiple motors. The shared resource paradigm is essentially based on time multiplexing. Figure 9 compares the shared resource paradigm against the "unfolded" or dedicated resource paradigm.

The figure shows the inputs (BSW), the functional unit f1 required for the computation, the sharing mechanism (S and S'), and the outputs. The unfolded mechanism requires more functional units but requires no sharing mechanism.

The choice between the two is influenced by the following factors:

- Number of inputs N

- Resource requirement or cost of the functional unit

- Resource requirement or cost of the sharing mechanism

- Required rate of outputs

The major determinant of the architecture is the output update rate. If new outputs are required every T unit time, and the functional unit  $f_1$  requires  $f_T$  unit time to compute the output for every new input, then the maximum number of inputs which a single functional unit can process is:

$$T_{f_T}$$

where |x| denotes the greatest integer less than or equal to x. This calculation neglects any delay introduced by the sharing mechanism. This delay may become significant with a large number of inputs.

The next factor which affects the architecture is the total cost of the system. The cost of the functional units in both architectures scales linearly with the number of inputs. However, the time delay introduced by the sharing mechanism scales logarithmically with the number of inputs. Often, designers select a mixed architecture where a functional unit is allocated for every m inputs out of a total of N inputs.

One can further optimize the architecture with knowledge of connected groups. As motors in a connected group do not operate simultaneously and independently, they may not require dedicated resources.

Calculation of the optimum cost based on a given motor connection and a required output update rate is beyond the scope of this application note. It is important to carefully consider this issue when choosing a particular connection.

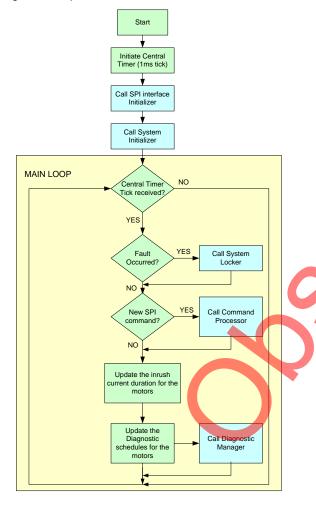

We selected the architecture used in this application note with consideration for the reusability of blocks, scalability and modularity of functions. Resources are shared wherever possible. Figure 10 depicts the architecture of our example. It consists of six major blocks:

- Bridge Interface

- Over Current

- Motor Drive Signals generation

- Fault Detect

- Diagnostic

- Firmware

These six blocks, along with the user interface, make up the complete system. The system designer can configure these blocks using APIs.

The Bridge Interface block interfaces with the physical H bridge. It configures the device pins correctly so as to transmit the control signals from the device to the bridge and the status signals from the bridge to the device. The Bridge Interface block consists of multiple half-bridge interface blocks. Each of these half-bridge interface blocks receives the H\_BRIDGE DRIVE SIGNALS from the MOTOR DRIVE SIGNALS generation system or control signals from the Diagnostic block. The Fault Detect block observes the control signals incident on the bridge, and the resultant status signal from the bridge. In case of an abnormal condition, an invalid BSW is detected. The Fault

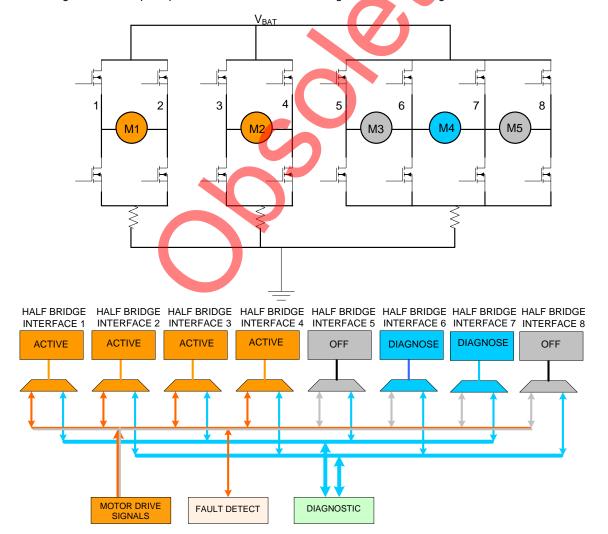

Figure 10. Example Operation of a Given Motor Configuration with the High Level Architecture

Table 7. Half-Bridge Interface Block Signals and Their Significance

| Signal Name   | Signal Type    | Significance                                                                                                                                                                                                                      |

|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable        | Digital Input  | The signal that controls the half-bridge drive signals. If this signal is 0, then the PIN_HS and PIN_LS disable the gate drivers, thus deactivating both the high side and the low side switches.                                 |

| HS_Ctrl       | Digital Input  | The signal that controls the high side switch through PIN_HS. If the bridge is enabled and HS_Ctrl is high, the switch is turned ON; otherwise the switch is turned OFF.                                                          |

| LS_Ctrl       | Digital Input  | The signal that controls the low side switch through PIN_LS. If the bridge is enabled and LS_Ctrl is high, the switch is turned ON; otherwise the switch is turned OFF.                                                           |

| PIN_HS        | Digital Output | The pin that controls the high side gate driver.                                                                                                                                                                                  |

| PIN_LS        | Digital Output | The pin that controls the low side gate driver.                                                                                                                                                                                   |

| Bridge        | Digital Output | The digital state produced by comparing V_Bridge and Threshold, as seen in Figure 11.                                                                                                                                             |

| PIN_BRIDGE    | Analog Input   | An input pin used to connect to the V_Bridge signal.                                                                                                                                                                              |

| Threshold     | Analog Input   | The signal used as the reference for digitizing the V_Bridge signal, as seen in Figure 11.                                                                                                                                        |

| PIN_ANALOG    | Analog Input   | An optional pin used to bring an analog signal into the system. In the present application, used monitor the current through the bridge.                                                                                          |

| Analog Signal | Analog Output  | An optional signal which might route into the system. It may be any analog signal deemed necessary to be monitored. In the present application, used for over current detection and hence connected to the low side shunt signal. |

Detect block identifies this as a fault, and overrides the control signals to deactivate the bridge. The Fault Detect block can observe and alter the H\_BRIDGE DRIVE SIGNALS as depicted in the diagram by the bidirectional lines between the block and the signals.

Figure 10 demonstrates an example of the architecture in operation. The Motor Drive Signals block generates signals for all motors which route to the half-bridge interface blocks. The firmware configures the routing so that each half-bridge interface block receives the correct set of signals. The figure illustrates a case where motors M1 and M2 are running, M3 and M5 are off, and M4 is being diagnosed. The color coding shows the type of signals received by each half-bridge and each motor. The Over Current block is not shown in the figure. In this scenario, it monitors motors M1 and M2.

# Implementation of the Fault Detection and Protection System

We used PSoC 3 to implement an example fault detection and protection system based on the architecture discussed in the previous section. For an introduction to design with PSoC 3, please see AN54181. We designed the system to drive, monitor and protect two isolated motors.

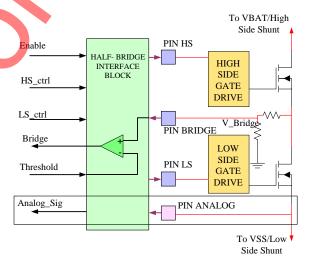

#### The Half Bridge Interface Block

#### **Conceptual Realization**

This block interfaces the system with the physical H bridge and the motors. Figure 11 illustrates the conceptual realization of the block. Table 7 lists the inputs and outputs of the Half-Bridge Interface block along with their significance.

Figure 11. Conceptual Realization of the Half-Bridge Interface Block

We discussed two ways to drive a high side gate in the section Alternate Methods to Drive H Bridges. The V\_Bridge is the resistor divided voltage at the middle of the half-bridge, i.e. at the motor terminal. In this application note, PIN ANALOG interfaces to the low side shunt, but you may choose to connect it to the high side shunt or to any other analog signal deemed necessary.

#### **PSoC 3 Implementation**

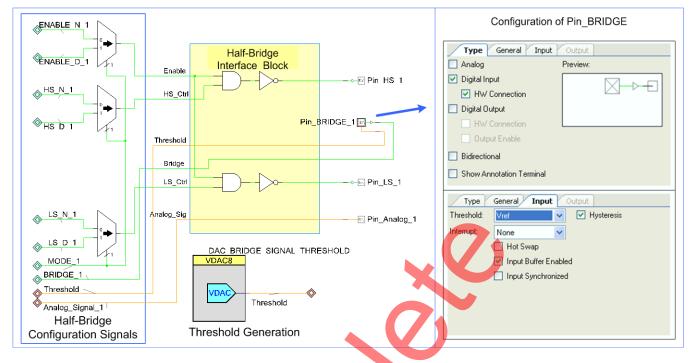

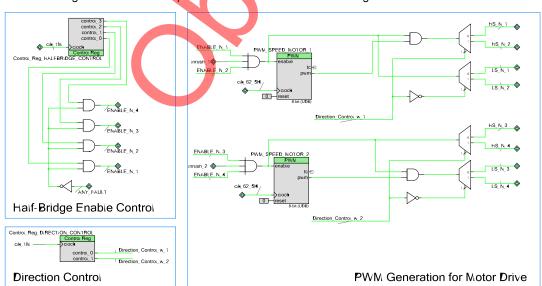

Figure 12 shows the PSoC3 implementation of the Half-Bridge Interface block and the associated configuration signals. We can drive the digital control signals (Enable, HS\_Ctrl, and LS\_Ctrl) with either the normal mode signals, marked by \_N, or the diagnostic mode signals, marked by \_D. The project uses the signal MODE to select the

Figure 12. PSoC 3 Implementation of the Half Bridge Interface Block

correct set of signals that go into the half-bridge. The project uses four instances of the Half-Bridge Interface block.

The HS\_Ctrl and LS\_Ctrl signals are logically AND'd with the Enable signal, so that they are ignored when Enable is OFF. The NOT gates are used before the pins, because the gate drivers are active low (i.e. they turn the switches ON when their inputs are LOW).

If required, you can insert an analog buffer between the Pin\_Analog and the Analog signal to prevent loading of the signal. The availability of analog buffers on PSoC 3 makes this easy to implement.

The Serial IO (SIO) pins available in PSoC 3 allow us to implement the Pin\_BRIDGE and the comparator shown in Figure 11. The SIO pin is configured as a digital input pin

Figure 13. Behavioral Differences Between Traditional and Modified Blanking Timers

with hardware connection, and its Threshold is chosen to be  $V_{REF}$ . This effectively configures the pin as a comparator, with the output as the digital state read by the pin, and the  $V_{REF}$  signal as the reference. A digital to analog converter generates this reference (the Threshold signal) to allow easy modification of the threshold. Alternately, it can be driven by another analog signal directly derived from the battery. For details on the SIO implementation, please consult the pin component datasheet and AN60580.

The block does not interact with firmware, and it does not have any APIs. The Over Current, Fault Detect and Diagnostic blocks use signals from this block.

# Over Current, Fault Detect and Diagnostic Blocks

The Over Current, Fault Detect and Diagnostic blocks are each divided into a few major parts:

- Fault Signal Detection Block: Detects the actual fault. The implementation varies according to the type of fault being identified.

- Blanking Timer: Verifies that the detected fault is a true fault and not misidentified noise. This is common to all three block types.

- Fault Latch: Ensures that once a fault is verified by the Blanking Timer, it is latched and cannot be cleared even if the fault condition goes away. The latch must be cleared in firmware and requires master intervention to ensure that the master acknowledges all faults.

- Status Register: Records the fault signals at the time of the occurrence of any fault. The firmware reads the status register to determine the source of the fault.

- Control Register: Interfaces to the firmware.

- Application Programming Interface

#### **Blanking Timer**

The Blanking Timer "blanks" or becomes zero from some non-zero starting value. Certain "events" trigger the timer. Once triggered, it starts to count down. If it "blanks" or reaches zero, then it may trigger an action. However, if it is interrupted (the triggering event does not persist, or otherwise), then it returns to the initial count and maintains the count until triggered again. A Blanking Timer ensures that a decision is made based on the occurrence of a true event, as against temporary disturbance.

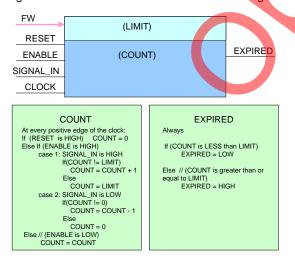

In this application note, we modified the behavior of the Blanking Timer to best suit the needs of the application. We maintain the name as the essential purpose is the same. Without loss of generality, we assume that both the modified and the traditional timers start at 0 (instead of a non-zero starting value) and count up to a pre-specified limit.

Figure 14 describes the behavior of the modified timer. The input signals RESET, ENABLE, SIGNAL\_IN and CLOCK control the timer. The output signal EXPIRED indicates a fault. The firmware sets the internal parameter LIMIT. This parameter determines the "blanking time", or the period for which the event needs to persist in order to be acknowledged as a true event. The figure shows now inputs affect the variable COUNT. It also shows COUNT, in turn, controls the output.

Figure 14. Functional Realization of the Blanking Timer

The major difference between the present realization and a traditional Blanking Timer is the symmetric movement of the internal variable COUNT between its two terminal values (0 and LIMIT). Figure 13 illustrates this point.

The COUNT variable of the modified timer is not reset to 0 as soon as the Fault signal disappears; rather, it smoothly transitions from its present value to 0. Therefore, the decision about the occurrence of the fault is not based on its continuous persistence over a period of time, but by its "average" persistence. The average persistence is better suited to the present application, as faults, though not continuously present, reduce the reliability of the H bridge and the load as a whole.

For example, imagine a case where a switch undergoes periodic fault conditions but with the period being less than LIMIT. With a traditional blanking timer, the temperature might increase slowly and eventually put the device outside its SOA. However, the modified timer expires if the fault persists more often than not. The disadvantage of the modified approach is its reduced robustness to noise as compared to the traditional realization. If noise has high average persistence then it may be recognized as a true fault.

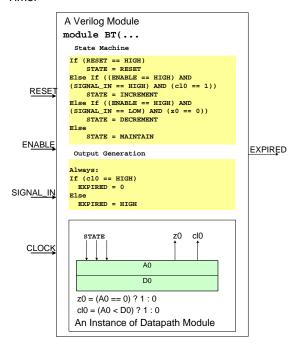

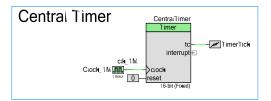

We implement the blanking timer with datapaths. Datapaths are hardware modules available in the Universal Digital Blocks (UDB) in PSoC 3. Each UDB contains one datapath element. PSoC Creator allows these modules to be instantiated inside a user defined Verilog module, as shown in Figure 15.

The datapath consists of several registers. We discuss only the registers relevant to the implementation, A0 and D0. The Datapath Configuration Tool allows eight possible operations of the datapath. At a given clock cycle, the value of STATE determines the particular operation to be performed. For more detailed information on Verilog and datapath based components, please refer to these

Figure 15. Datapath Based Implementation of the Blanking Timer

trainings (Verilog, Datapath).

The datapath operations used in this application note are:

- RESET: Loads the register A0 with value 0.

- INCREMENT: Increases the value of A0 by 1.

- DECREMENT: Decreases the value of A0 by 1.

- MAINTAIN: Maintains the value of A0.

The implementation uses two outputs from the datapath: z0 and cl0. Their significances are as follows:

- $\mathbf{z}$  0 = 1 if A0 is equal to 0; it is zero otherwise.

- cl0 = 1 if A0 is less than D0; it is zero otherwise.

Using these two values and the input signals to the Blanking Timer, a state machine is designed in Verilog which controls the datapath operation at each clock cycle. The A0 register essentially acts as the COUNT variable and the DO register acts as the LIMIT parameter. The D0 register can be written in firmware, allowing us to configure the Blanking Time.

All three fault detection blocks use a blanking timer. The Over Current, Fault Detect, and Diagnostic blocks use their associated APIs to configure their own blanking timers. There is no API particular to the blanking timers.

#### **Over Current Block**

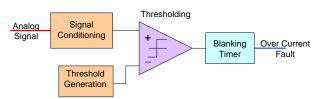

The Over Current block monitors the current through the bridge, and takes appropriate actions when the current exceeds the set threshold for a significant amount of time. A low side shunt converts the current into voltage, and hence the over current block actually monitors voltage.

#### **Conceptual Realization**

As shown in Figure 16, the Over Current block consists of three parts: the signal conditioning portion, the thresholding portion and the blanking timer.

Depending on the nature of the signal and the requirements, the analog signal from the Half-Bridge Interface block may need amplification and . It may also require differential amplifiers depending on the noise levels. The implementation in this application note uses single ended amplification.

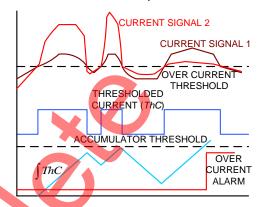

The system compares the processed against a set threshold. The result is a digital signal whose state depends on the analog signal. Figure 17 shows how the Blanking Timer accumulates the digital signal accumulates over a period of time to determine the over current fault.

The system then compares the Current Signal, which is actually the output from the Signal Processing block against the over current threshold (OC threshold) to produce the comparison result (ThC). This output accumulates or integrates until it reaches another pre-set threshold. At this point the Over Current alarm is set off. The accumulation approach has three principle advantages:

Figure 16. Conceptual Realization of the Over Current Block

Figure 17.Over Current Alarm Generation from Thresholded Current Output

- The SOA of the switch suggests that it can tolerate a specific amount of over current for a specific amount of time based on the temperature. The accumulation approach therefore leads to better use of the switch rather than instantaneous over current.

- It eliminates effect of spurious noise.

- As the Blanking Timer does the integration in the digital domain and the result compared against a digital threshold (the blanking time), it is easy to configure the system for different H bridges and motors with different over current tolerance without using external components such as capacitors.

A larger over current threshold implies that the switch can tolerate over current for a shorter time the current without violating the SOA. Therefore, the over current threshold and the accumulator threshold are related and should be set appropriately.

As seen in Figure 17, the current signal 1 and current signal 2, although indicative of different severity, produces identical effect. This is a disadvantage of the discussed approach. The current signal 2, however, is unlikely to be encountered in a practical application. A carefully chosen over current threshold, accumulator threshold, and slope of accumulation can circumvent such problems.

#### **PSoC 3 Implementation**

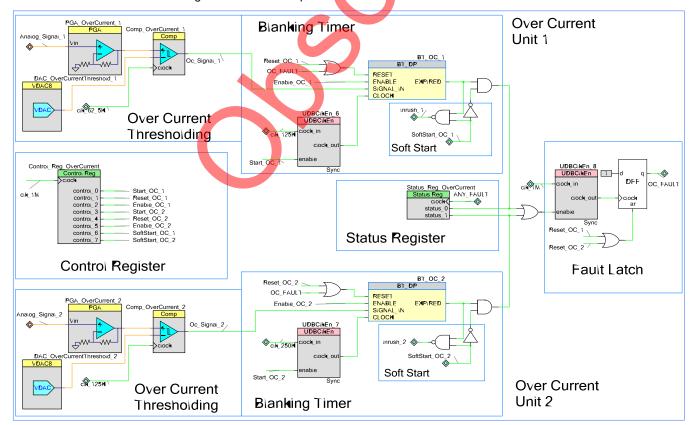

Ready availability of configurable analog blocks makes the PSoC 3 implementation of the Over Current block straightforward. Figure 18 shows the implementation of two Over Current blocks for two isolated motors. A Programmable Gain Amplifier (PGA) amplifies the voltage

14

signal which originates from the shunt resistor or from a preconditioning circuit to allow a quick gain change without change of any external components.

A voltage DAC generates the over current threshold. The firmware can modify the DAC value at runtime to change the threshold. Choose the range and value of the DAC based on the current rating of the motor and the value of the shunt resistor. As the threshold changes infrequently, a slow speed setting is sufficient.

The amplified signal goes to the positive input of a comparator, and the generated threshold to the negative input. Configure the comparator with hysteresis enabled and with non-inverting polarity (output is high when positive input is greater than negative input). Each comparator synchronizes to a clock with half the frequency of the blanking timer clock to ensure that the SIGNAL\_IN input of the blanking timer is always stable at its clock edges. For more information, see the PGA, DAC and, Comparator datasheets.

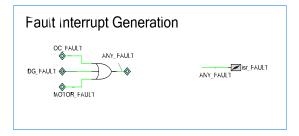

The over current signals Oc\_Signal\_1 and Oc\_Signal\_2 are input to the Blanking Timer blocks. A high signal for a sufficiently long time triggers an Over Current fault. The two EXPIRED signals from the Blanking Timers are logically OR'd to produce the resultant Over Current fault. The Fault Latch latches the fault. Once latched, only firmware can clear the fault.

When a motor starts, a large amount of inrush current flows through the motor until it reaches a stable speed. An OC Threshold set for normal operating conditions will misidentify the inrush current as an over current condition. Similarly, an OC threshold set for the inrush current may result in switches operating outside their SOA. Heavy motors with large inertia are particularly prone to this problem. A soft start strategy solves this problem. The soft starting strategy works as follows:

- Define the inrushPeriod for each motor as the duration that inrush current is most likely to.

- During this time, set the SoftStart\_OC\_x (x=1,2) to HIGH. This gates the Blanking Timer output from the Fault Latch. Instead, it feeds the output back to the motor drive signal generation unit (Inrush\_x) to turn the bridge OFF.

- The over current blanking time is set to the value STARTING\_BLANKING\_TIME which is typically much less than the normal operating conditions.

It is clear that the switches operate inside the SOA, because the threshold is the same as that for regular operating condition and the blanking time is less than the regular blanking time. The following events lead to motor start:

Figure 18. PSoC 3 Implementation of the Over Current Blocks

Table 8. API Functions of the Over Current Block

| Function                                           | Action                                                                                                                                                               |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OverCurrent_x_Start()                              | Starts and configures all the analog peripherals used by the OverCurrent _x block and resets the Blanking Timer, Fault Latch and Status Register blocks.             |

| OverCurrent_x_Stop()                               | Stops all the analog components associated with OverCurrent_x block and resets the Blanking Timer, Fault Latch, and Status Register blocks.                          |

| OverCurrent_x_SetThershold (uint8 threshold)       | Sets the Over Current threshold by modifying the DAC value with the supplied parameter threshold.                                                                    |

| <pre>uint8 OverCurrent_x_GetThreshold()</pre>      | Returns the current threshold for OverCurrent_x block.                                                                                                               |

| OverCurrent_x_SetBlankingTime (uint8 blankingTime) | Sets the blanking time for OverCurrent_x block by modifying the blanking timer D0 register according to the supplied parameter blankingTime.                         |

| <pre>uint8 OverCurrent_x_GetBlankingTime()</pre>   | Returns the current blanking time.                                                                                                                                   |

| OverCurrent_x_Enable()                             | Enables the OverCurrent_x block by enabling its blanking timer.                                                                                                      |

| OverCurrent_x_Disable()                            | Disables the blanking timer of the OverCurrent_x block from counting.                                                                                                |

| <pre>OverCurrent_x_SoftStartEnable()</pre>         | Enables the soft start function for OverCurrent_x block by setting the SoftStart_OC_x signal HIGH, and changing the blanking time value to STARTING_BLANKING_TIME_x. |

| OverCurrent_x_SoftStartDisable()                   | Disables the soft start function for OverCurrent_x block by setting the SoftStart_OC_x signal LOW, and changing the blanking time value to normal operating value.   |

- The current through the motor increases till it exceeds the OC threshold for the duration STARTING\_BLANKING\_TIME.

- The Blanking Timer expires, setting the Inrush\_x signal to high. This turns the bridge OFF.

- The current through the motor decreases, and the Blanking Timer output goes LOW. This sets Inrush x low, and the bridge turns ON again. This restarts the cycle.

In this way the motor starts without transgressing the SOA of the switches. After the inrushPeriod, the SoftStart\_OC\_x signal turns OFF, and the blanking time is set to its normal operating value.

A sudden and large increase in speed may also require large current. The user may modify the threshold and blanking time values for such events accordingly.

When the system detects any kind of fault, it sets the ANY\_FAULT signal to HIGH. On the occurrence of any faults, the status register logs the Blanking Timer output.

The Over Current control register initializes and configures the Over Current blocks. It controls the passage of the clock to the blanking timers and handles their initialization and configuration as required by the application. It is also used as an interface between the firmware and the actual hardware.

The Over Current block offers a set of APIs listed in for easy configuration of the system. The  $OverCurrent\_x$  prefix denotes that the API is particular to the Over Current unit x (x = 1 or 2).

#### Fault Detect Block

The Fault Detect block detects any abnormal bridge behavior while the motor is in operation.

#### Conceptual Realization

Table 9 lists the BSWs for particular faults. For each half-bridge, we can define the fault as a logical operation on the high-side control signal, the low-side control signal, and the state of the bridge. This enables us to easily map the BSW to a specific fault condition. Figure 19 shows the logical definition for both half-bridges.

Table 9. Abnormal Conditions and Associated BSW for Fault Conditions with Active Motors

| Signal 1 | Signal 2 | BSW(binary) | Meaning                                                                                   |

|----------|----------|-------------|-------------------------------------------------------------------------------------------|

| HSL = 1  | MTL = 0  | 01x0x0xx    | High side left FET is on, but the motor left terminal is close to ground.                 |

| LSL = 1  | MTL = 1  | 00x1x1xx    | Low side left FET is on, but the motor left terminal is close to $V_{\text{BAT}}$         |

| HSR = 1  | MTR = 0  | 0x1x0x0x    | High side right FET is on, but<br>the motor right terminal is<br>close to ground.         |

| LSR = 1  | MTR = 1  | 0x0x1x1x    | Low side right FET is on, but<br>the motor right terminal is<br>close to V <sub>BAT</sub> |

Else If ( (HS2 is HIGH) AND (BRIDGE\_2 is LOW))

FAULT = 1

Else If ( (LS2 is HIGH) AND (BRIDGE\_2 is HIGH))

FAULT = 1

17

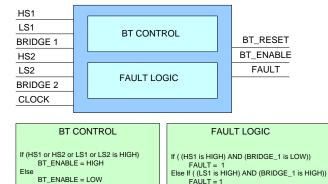

Figure 19. Logical Definition of Bridge Fault

The logical definition in Figure 19 automatically protects against turning on the high side and the low side switch of the same half-bridge simultaneously. The availability of digital logic gates on PSoC 3 makes it particularly easy to implement the above fault detection circuit.

#### **PSoC 3 Implementation**

The heart of the Fault Detect block is the FD component. We use Verilog to implement the FD component. Figure 20 describes it behavior.

The BT CONTROL portion generates the RESET and ENABLE signals for the Blanking Timer block. The system resets the Blanking Timer every time there is a transition on any of the bridge drive signals. This ensures that the system does not incorrectly detect any intermediate condition during the transition of a switch as a fault. Also, it disables the Blanking Timer unless at least one of the switches on the H bridge is ON. The Fault Logic block is the Verilog implementation of the fault definitions in Figure 19.

Figure 20. The FD Component

At every positive edge of the clock: If (HS1 or HS2 or LS1 or LS2 has changed) BT\_RESET = HIGH

BT RESET = LOW

Figure 20 shows the complete implementation of two Fault Detect blocks. During soft start, the bridge is continuously in transition; therefore, the blanking timers are held in RESET during this period. The EXPIRED signals from the Blanking Timers are logically OR'd to produce the fault signal to indicate that at least one of the H bridges sustained a fault. The Fault Latch block then latches the signal. The ANY\_FAULT signal logs the status of the two EXPIRED signals into the Status Register. The status is

Else

FAULT = 0

The Fault Detect Control Register configures the system initially and between system stalls due to any fault. The Firmware block uses this as an interface to the Fault Detect system. Table 10 lists the API functions of the Fault

used later to analyze the source of the fault.

Table 10. API Functions for the Fault Detect Block

| Function                                           | Action                                                                                                                                                                                                                                           |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FaultDetect_x_Start()                              | Starts the Fault Detect system by allowing the clock to FD_x component and the Blanking Timer BT_FD_x. Resets the Blanking Timer internal count to 0. Clears the Status Register and the Fault Latch flip-flop of any pre-existing fault status. |

| FaultDetect_x_Stop()                               | Gates the clock to the FD_x component and the Blanking Timer BT_FD_x. The Blanking Timer internal count is reset to 0. Clears the Status Register and the Fault Latch flip-flop of any pre-existing fault status.                                |

| FaultDetect_x_Enable()                             | Enables the Fault Latch functionality.                                                                                                                                                                                                           |

| FaultDetect_x_Disable()                            | Disables the Fault Latch functionality.                                                                                                                                                                                                          |

| FaultDetect_x_AssertReset()                        | Resets the Blanking Timer BT_FD_x, the Status Register and the Fault Latch flip flop. These are held in reset until released.                                                                                                                    |

| FaultDetect_x_ReleaseReset()                       | Releases the Blanking Timer BT_FD_x, the Status Register and the Fault Latch from reset condition.                                                                                                                                               |

| FaultDetect_x_SetBlankingTime (uint8 blankingTime) | Configures the blanking timer BT_FD_x so that the blanking time is equal to the provided parameter blankingTime. The Blanking Timer and the Fault Latch are also reset.                                                                          |

| <pre>uint8 FaultDetect_x_GetBlankingTime()</pre>   | Returns the current blanking time of BT_FD_x.                                                                                                                                                                                                    |

Fault Detect Unit 1 Blanking FD Component FD 1 RESET Timer cik\_FD\_1 FD\_1 HS\_N\_1 LS\_N\_1 BRIDGE\_1 HS\_N\_2 LS\_N\_2 FD 1 START RESET ENABLE SIGNAL CLOCK Control Register MOTOR\_FAULT DFF FD\_1\_START FD\_1\_RESET FD\_1\_ENABLE FD\_2\_START FD\_2\_RESET FD\_2\_ENABLE UDBCINE Status Register FD\_ FD\_1\_RESET Fault Detect Unit 2 FD 2 RESET ault Latch Blanking FD Component FD\_2\_RESE Timer FD\_2 HS1 BT DI BRIDGE1 BT RESET RESET ENABLE UDBCINEN\_1 UDBCINEN BT\_ENABLE EXPIRE FAULT CIM BRIDGE2 CLOCK iock in cih\_FD\_2 ciock or FD\_2\_START enable

Figure 21. PSoC3 implementation of the Fault Detection System

Detect\_x (x= 1,2) block.

# Diagnostic Block

The Diagnostic block:

- Periodically monitors loads which are inactive

- Diagnoses a bridge reported by the Over Current or the Fault Detect blocks.

#### **Conceptual Realization**

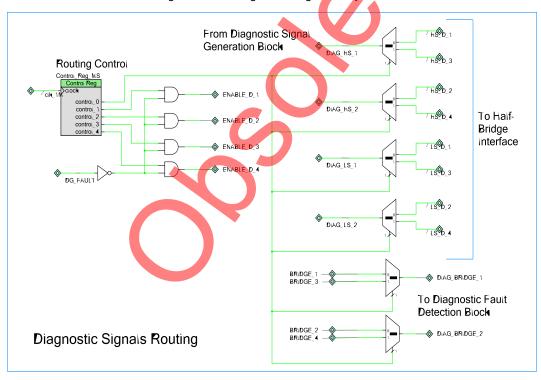

The Diagnostic block manages the sequence described in Table 3. The Diagnostic sequence excites the H bridge,

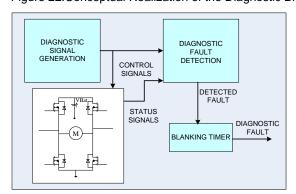

Figure 22. Conceptual Realization of the Diagnostic Block

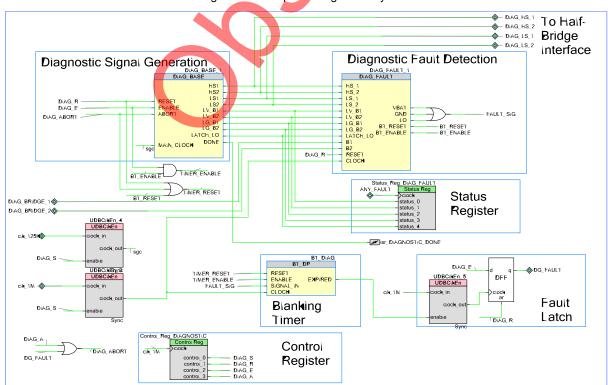

and the resulting status signals combine with the sequence to form the BSW. The BSW maps to a normal condition or a particular fault. The Diagnostic system as shown in Figure 22 consists of two parts: signal generation and BSW analysis. As usual, it uses the Blanking Timer to distinguish true faults from noise.

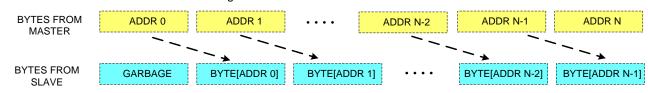

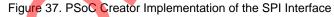

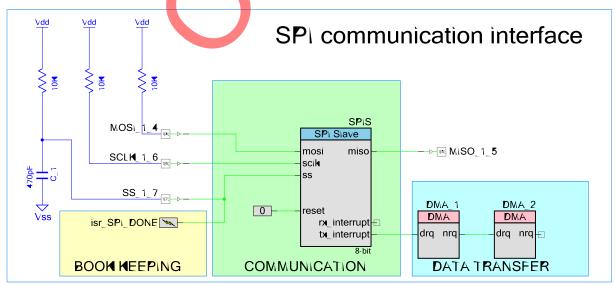

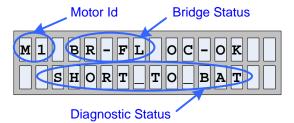

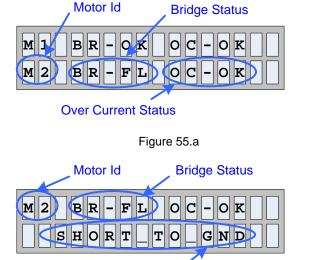

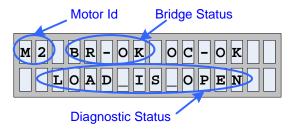

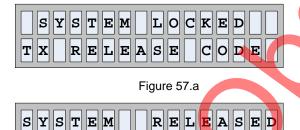

The Diagnostic Signal Generation component generates the control signals for two half-bridges: Half-bridge 1 and Half-bridge 2 as well as a few configuration signals for the Diagnostic Fault Detection component. For ease of discussion, we assume that Half-bridge 1 is the left half-bridge. Table 11 shows the inputs and outputs of the Diagnostic Signal Generation component. Figure 23 illustrates the corresponding timing diagram as well as the clock-cycles, with 0 being the first cycle after ENABLE is set high.