# 인피니언의 고전력 애플리케이션 위한 새로운 저손실 사이리스터 제품군

**New Low Loss Thyristors for High Power Applications**

이 글에서는 산업용 애플리케이션에 사용하기 위한 인피니언의 새로운 8.5kV 저손실 사이리스터 제품군에 대해서 설명하였다. 이들 제품은 새로운 기술들을 적용함으로써 8.5kV. 125°C. 50Hz/60Hz로 최대의 블로킹 성능을 달성한다.

긜/Jens Przybilla, Uwe Kellner-Werdehausen, Dr. Sebastian P. Sommer 인피니언 테크놀로지스

□ -은 경우에 산업용 드라이브나 고전압 직류(HVDC) 나 전송 같은 고전력 애플리케이션에 여전히 사이리스터를 일순위로 선택하고 있다. 석유나 가스 같은 산업용 분야에서는 펌프와 컴프레서 등에 전력대가 80MW 혹은 그 이상 이르는 산업용 드라이브를 필요로 한다. 이러한 드라이브의 요구를 충족하기 위해서는 사이리스터가최대 125℃의 최대 접합부 온도(T<sub>vj</sub>)에 이르는 넓은 온도범위로 동작하는 것이 필수 이다. 또한 동작 수명이 수십년에 달하는 극히 효율적인 고전력 드라이브를 설계하기위해서는 장기적인 안정성과 높은 서지 전류 용량을 제공해야 한다.

산업용 애플리케이션에 사용되는 이러한 드라이브는 작동 수명이 수십 년에 달하므로 사이리스터의 손실이 중요한 고려사항이다. 이와 함께 장기적인 안정성과 서지 전류 용량 또한 중요하게 고려해야 할 요소이다. 오늘날 이러한 애플리케이션에 사용되는 사이리스터는 블로킹 전압이 7kV~8kV 정도 이므로 중전압 (medium voltage, MV) 드라이브에 직렬 연결하는 소자의 수를 줄일 수 있다.

산업용 애플리케이션의 이러한 요구를 충족하기 위해서 인피니언은 온 상태 및 스위칭 시에 손실이 낮고  $T_{vi}$  = 125  $^{\circ}$  C로 높은 블로킹 전압이 가능한 새로운 8.5kV 사이리스터 제품을 출시하였다. 이와 같은 성능을 달성할 수 있게 된 것은 실리콘 디자인을 최적화하고 LTS(Low

In many cases thyristors are still the first choice for high power applications like industrial drives and high voltage direct current transmission (HVDC). Industrial drives for pumps and compressors, with power levels up to 80 MW and beyond, are needed in different markets i.e. Oil and Gas. Due to the demanding requirements of these drives, a wide operation temperature of up to  $125^{\circ}$ C maximum junction temperature ( $T_{vj}$ ) is essential for thyristors. Additionally, they have to fulfill the need for long term stability and high surge current capability for designing highly efficient, high power drives able to perform for more than several decades.

Due to the long period of operation the losses of thyristors used in industrial applications are an important factor for the design of such drives. Additionally, the long term stability and the surge current capability are also crucial issues that have to be taken into account. Today the blocking voltage of thyristors in such applications is usually 7 kV to 8 kV, this helps in reducing the number of serial devices for medium voltage (MV) drives.

To serve these needs of industrial applications Infineon Technologies Bipolar introduced a new 8.5 kV thyristor with low losses at on-state and switching with high Temperature Sintering) 와 전기 활성 비정질 탄소 패시베 이션(amorphous carbon passivation, a-C:H) 같은 검증 된 프로세스를 적용하였기 때문이다. 또한 최대 블로킹 전압을 애플리케이션 요구에 맞게 맞춤화하였다. 이 저손 실 사이리스터는 실리콘 직경은 150mm(6인치)이고 폴 피스 직경은 135mm인 패키지로 뛰어난 파라미터를 달 성한다(그림 1). 이 새로운 사이리스터는 HVDC 용으로 이미 개발된 9.5kV 6인치 사이리스터와 동일한 이점들을 제공한다[1][2]. 짧은 기간내에 100mm(4인치)나 125mm(5인치) 같은 더 작은 규격도 가능하다.

# LTS를 적용한 새로운 사이리스터

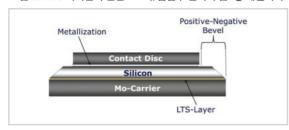

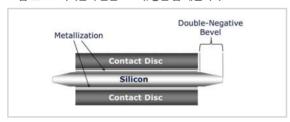

LTS 기술은 확산 접합 개념을 토대로 하며, 전체적인 영역에 걸쳐서 실리콘과 몰리브데넘 운송체 사이에 견고 한 금속 전이를 형성한다(그림 2a의 LTS 층). 그림 2b에 서 보는 자유 부유(free floating: FF) 어셈블리는 실리콘 과 몰리브데넘 사이가 건조한 계면인 것에 반해서, LTS 디자인의 열 저항은 훨씬 낮다. 뿐만 아니라 FF 어셈블리 는 튀어나온 접합부 단자 영역이 양면 음 베벨(사면)로서 2개 몰리브데넘 접촉 디스크 사이에 직접적인 열 결합이 없다. 이 점이 극히 높은 주기적 블로킹 전압  $V_{RRM}$ 과  $V_{DRM}$ 으로 최대 동작 온도를 제한할 수 있다.

그러므로 LTS 디자인은 열 소진이 더 우수하므로 최 대 125℃에 이르는 더 높은 최대 동작 온도가 가능하다. 그러면서도 서지 전류나 장기적인 블로킹 전압 안정성이 나 주기적 블로킹 전압 용량 같은 사이리스터의 주요 파 라미터로 부정적인 영향을 미치지 않는다. LTS를 적용함 으로써 높은 역 전류가 흐를 때, 특히 접합부 단자에서, 전 력 손실을 충분히 소진시킬 수 있다.

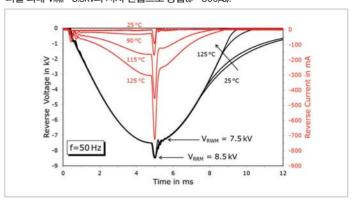

테스트를 통해서, 실리콘 웨이퍼 두께를 늘리지 않고 서도 최대 주기적 블로킹 전압  $V_{\text{RRM}}$ 과  $V_{\text{DRM}}$ 을 추가적으로 15~20퍼센트 높일 수 있는 것으로 나타났다. 이 테스트 는 사이리스터에 관한 표준 규격(IEC 60747-6)의 주기 적 전압 스트레스에 관한 규정에 따라서 실시하였다[2]. 그림 3은 전형적인 전류와 전압 특성을 보여준다. 동작 전 압  $V_{RWM}$ 과 동일한 진폭으로  $t_P = 10$ ms인 하프 사인파를 인가한다. 이 베이스 사인파는 tp=300µs의 더 짧은 간격 blocking capability at  $T_{vi} = 125$ °C. This performance was realized by the optimization of the silicon design, as well as the use of well-established

그림 1. 135mm 폴 피스를 사용한 새로운 8.5kV 6인치 전기 트리거 사이리스터

processes like Low Temperature Sintering (LTS) and an electroactive amorphous carbon passivation (a-C:H). Also, the definition of maximum blocking voltage has been tailored to application demand. The low loss thyristor features a silicon diameter of 150 mm (6-inch) with outstanding parameters in a package with 135 mm pole piece diameter (see Figure 1). This new thyristor offers the same advantages as the existing 9.5 kV 6-inch thyristors already developed for HVDC [1, 2]. The large diameter enables the adaption to smaller dimensions like 100 mm (4") and 125 mm (5") in a short period of time.

## New thyristor concept with LTS

The LTS technology is based on the concept of diffusion welding and forms a solid metallurgical transition (see LTSlayer in Fig. 2a) between Silicon and Molybdenum carrier over the entire area. In contrast to the dry interface between Silicon and Molybdenum of Free Floating assembly (FF) shown in Fig. 2b, the thermal resistance of LTS designs is significantly lower. In addition, there is no direct thermal coupling between the protruding junction termination area of FF-assembly with double-side negative bevel and the two Mo-contact discs. This may limit the maximum operating temperature at very high periodic blocking voltages  $V_{\text{RRM}}$  and  $V_{\text{DRM}}$ .

As a consequence, the better heat dissipation of LTS designs leads to a higher maximum operating temperature of up to 125°C. This has no negative effects on critical thyristor parameters like surge current or long term blocking voltage

그림 2a. LTS 디자인의 단면도로서, 접합부 단자가 음-양 베벨이다.

그림 2b. FF 디자인의 단면도로서, 양면 음 베벨이다.

표 1. 4인치 디바이스로 LTS와 FF 디자인의 주요 파라미터 비교 [3][4]

|                     | LTS<br>Current design | FF<br>Competitor |

|---------------------|-----------------------|------------------|

| Blocking capability | 9.2 kV@5°C            | 8 kV@5°C         |

| Surge current       | 65 kA@125°C           | 47.5 kA@115°C    |

| Thermal resistance  | 5.0 K/kW              | 5.7 K/kW         |

| Minimum Force       | 63 kN                 | 81 kN            |

에 더 높은 진폭으로 서지 전압  $V_{RRM}$ 에 의해 중첩된다. 이와 같이 하면 매우 높은  $V_{DRM}$  및  $V_{RRM}$ 으로 블로킹 전류가수 암페어에 이를 수 있다.

이러한 펄스 피크(Pulse Peak) 테스트를 사용해서 두 가지 향상이 가능하다:

- 첫째는 실리콘 두께는 기존 사이리스터와 같게 그대로 두고  $V_{DRM}/V_{RRM}$ 을 높이는 것이다. 이렇게 하면 직렬로 필요한 소자 수와 그에 따른 부품을 훨씬 줄이면서도 온 상태 손실은 증가하지 않는다.

- 둘째는  $V_{DRM}/V_{RRM}$ 은 그대로 두고 실리콘 두께를 기존 사이리스터와 비교해서 줄이는 것이다. 이렇게 하면 단일 사이리스터의 온 상태 전압 강하  $V_T$ 를 크게 낮출 수 있다.

이 글에서 설명하고 있는 저손실 컨셉은 두 번째 방법을 사용하고 있다. 실리콘 두께를 6퍼센트 줄임으로써 훨씬 더 낮은 온 상태 전압 강하  $V_T$ 와 동적 손실을 달성하고 있으며 그러면서도 블로킹 능력은 떨어트리지 않는다.

stability and periodic blocking voltage capability. By means of LTS the power loss during high reverse current flow, especially within junction termination, is sufficiently dissipated.

It has already been reported that maximum periodic blocking voltage,  $V_{\text{RRM}}$  and  $V_{\text{DRM}}$ , can be further increased by 15 -20 percent without increasing the silicon wafer thickness. Testing was conducted according to standards (IEC 60747-6) for thyristors subjected to periodic voltage stress [2]. Typical current and voltage characteristics are shown in **Figure 3**. The half sine with  $t_p$  = 10 ms is applied with an amplitude equal to working voltage  $V_{\text{RRM}}$ . This base sine wave is superimposed by surge voltage  $V_{\text{RRM}}$  with higher amplitude during a shorter period of  $t_p$  = 300  $\mu$ s. In this set-up the blocking current can reach values of several amps at very high voltages  $V_{\text{DRM}}$  and  $V_{\text{RRM}}$ .

By introducing this Pulse Peak test concept two improvement options are possible:

- ullet Silicon thickness is kept constant, i.e. the same as existing thyristors, and  $V_{DRM}/V_{RRM}$  is increased. This leads to a significant reduction of the number of series connected devices and corresponding components, but without increased on-state losses.

- Silicon thickness is reduced compared to existing thyristor, and  $V_{\text{DRM}}/V_{\text{RRM}}$  remains constant, but with significantly lower on-state voltage drop  $V_{\text{T}}$  of single thyristor.

For the new low loss concept described in this article the second option has been chosen reducing the silicon thickness by 6 percent in order to achieve significantly lower on-state voltage drop  $V_{\scriptscriptstyle T}$  and dynamic losses, but without negative effect on the blocking capabilities.

### **Device Performance**

Figure 3 depicts the periodic blocking test for a typical new low loss 6-inch device subjected to a periodic voltage stress at  $V_{\text{RRM}}$  = 8.5 kV and f = 50 Hz. The recorded blocking voltage and leakage current waveforms were tested at four

# 디바이스 성능

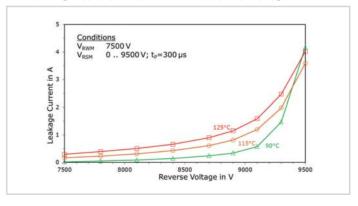

그림 3은 새로운 저손실 6인치 디바이스로 주기적 블 로킹 테스트를 한 것을 보여준다. VRRM = 8.5kV와 f = 50Hz로 주기적 전압 스트레스를 가하였다. 25℃, 90℃, 115℃, 125℃의 4개 온도로 블로킹 전압과 누설 전류 파 형을 테스트하였다. 통상적으로 각기 다른 제조업체들이 권고하는 것을 보면, 인가되는 동작 전압 V<sub>RWM</sub>이 피크 전 압 V<sub>RRM</sub>의 60~80퍼센트이다[2][5]. 하지만 이 테스트에 서 선택하고 있는 V<sub>RWA</sub>은 반복적 피크 역 블로킹 전압 V<sub>RRM</sub>의 약 90퍼센트이다.

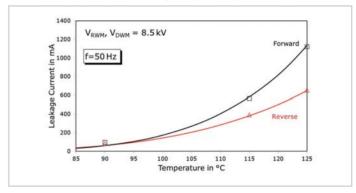

그림 4에서는 동작 온도에 대해서 누설 전류를 보여준 다. 최대 125℃의 접합부 온도와 50Hz 주파수로 이 새로 운 8.5kV 저손실 디바이스의 블로킹 성능을 측정하였다.

그림 5에서는 피크 전압 블로킹 성능을 보여준다. 125 ℃로 최대 9.5kV의 피크 블로킹 전압이 가능하다는 것을 알 수 있다. 그러므로 이 새로운 디자인의 블로킹 마진은 수십 년에 걸쳐서 장기적인 블로킹 안정성을 제공할 것임 을 알 수 있다. 이러한 마진을 달성할 수 있는 것은 LTS와 전기 활성 a-C:H 층을 사용한 베벨 패시베이션 같은 프 로세스를 적용했기 때문이다.

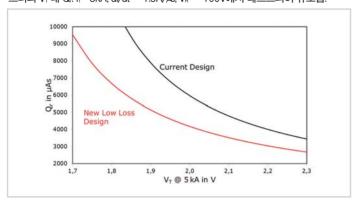

이 새로운 디바이스는 뛰어난 블로킹 성능을 달성할 뿐만 아니라, 사이리스터의 손실을 크게 낮춘다. 그림 6에 서는 150mm 실리콘 직경으로 손실 감소를 보여준다. 스 위칭 손실이 대략 30퍼센트 낮아졌다는 것을 알 수 있다. 현재 디자인과 비교해서 손실 감소는 동일한 온 상태 전 압 V<sub>T</sub>로 역 전하 Q,의 차이에 의한 것이다.

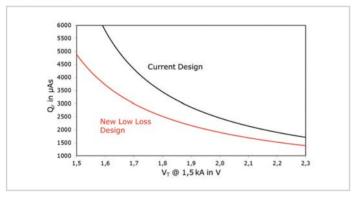

그림 7은 100mm 실리콘 직경을 사용한 새로운 저손 실 사이리스터로 계산된 데이터를 보여준다. Ir = 1.5kA.  $di/dt = -1.5A/\mu s$ ,  $V_R = -100V$ 일 때 이 더 작은 디바이스 의 블로킹 성능이 150mm 실리콘 직경 디바이스와 마찬 가지로 높을 것이라는 것을 알 수 있다.

#### 맺음말

이 글에서는 산업용 애플리케이션에 사용하기 위한 인 피니언의 새로운 8.5kV 저손실 사이리스터 제품군에 대해 서 설명하였다. 이들 제품은 새로운 기술들을 적용함으로

그림 3. 각기 다른 동작 온도로 주기적 블로킹 전압과 전류, V<sub>RMA</sub> = 7.5kV의 하프 사인 파를 최대 V<sub>RPM</sub> = 8.5kv의 서지 전압으로 중첩(t<sub>r</sub> = 300/s).

그림 4. 주기적 블로킹 전압 테스트로부터 얻은 동작 온도 대비 누설 전류. 이 새로운 디바이스로 하프 사인파를 인가해서 테스트하였다(V<sub>RMM</sub>, V<sub>DMM</sub> = 8.5kV, t₀ = 10ms).

그림 5. 각기 다른 온도 및 서지 전압(t = 300,6)으로 실시한 펄스 피크 테스트(단일 펄스)의 블로킹 전압 대 누설 전류. V<sub>RMM</sub> = 7.5kV의 하프 사인파 사용.

temperatures, 25°C, 90°C, 115°C and 125°C, respectively. Usually, the applied working voltage  $V_{RWM}$  is between 60 and 80 percent of the peak voltage  $V_{\mbox{\tiny RRM}}$  as recommended by different manufacturers [2, 5]. With the new concept, the

그림 6: 125℃ 동작 온도로 기존 사이리스터와 새로운 저손실 8.5kV 4인치 사이리 스터의 V<sub>T</sub> 대 Q<sub>r</sub>, I<sub>T</sub>=3kA, di/dt=-1.5A/µs, V<sub>R</sub>=-100V에서 테스트되어 유도됨.

그림 7. 정해진 조건 V<sub>T</sub>. I<sub>T</sub> = 1.5kA, di/dt= -1.5A/μs, V<sub>R</sub> = -100V일 때 100mm 폴 피 스를 사용한 더 작은 8.5kV 4인치 사이리스터의 역 복구 전하 Q과 온 상태 전압 강 하 V₁사이의 계산된 Trade-off

써 8.5kV, 125℃, 50Hz/60Hz로 최대의 블로킹 성능을 달 성한다. 또한 이들 제품은 뛰어난 서지 전류 용량을 달성하 고 기계적으로 설치시 힘이 작다는 것이 또 다른 장점이 다. 이러한 점은 산업용 애플리케이션에서 중요한 것이다. 이것은 현재뿐만 아니라 미래의 요구를 충족할 수 있는 뛰 어난 신뢰성을 가지고 높은 효율과 강력한 애플리케이션 이 가능하다. SN

#### 참고문헌

- [1] J. Przybilla, J. Dorn, R. Barthelmess, R. Joerke, U. Kellner-Werdehausen. "Reaching New Limits with High Power Bipolar Devices", Proceedings PCIM 2010, Nuremberg, pp. 761 ~ 766

- [2] M. Schenk, J. Przybilla, U. Kellner-Werdehausen, R. Barthelmess, J. Dorn, G. Sachs, M. Uder, S. V?lkel, ?State of the Art of Bipolar Semiconductors for Very High Power Applications", Proceedings PCIM Europe 2015, Nuremberg, pp. 930 ~ 936 [3] Datasheet "Infineon-T1901N-DS-v09\_00-en\_de", www.Infineon.com

- [4] Datasheet "5STP 20N8500\_5SYA1072-04 Dec 13",

- http://new.abb.com/semiconductors

- [5] J. Vobeck?, K. Stiegler, R. Siegrist, F. Weber, ?Low Loss High Power Thyristors for Industrial Applications", Bodo 's Power Systems, Nov. 2015, pp.18 ~ 21

selected  $V_{\text{\tiny RWM}}$  applied is about 90 percent of the repetitive peak reverse blocking voltage V<sub>ppm</sub>.

In Figure 4 the typical leakage current set against temperature behavior is shown. With this test the blocking performance of the new 8.5 kV low loss device is demonstrated for junction temperatures of up to 125°C and frequency of 50 Hz.

In addition, the peak voltage blocking performance is demonstrated in Figure 5. The device shows a capability of up to 9.5 kV peak blocking voltage at 125°C. This data highlights the blocking margin of the new design enabling a long term blocking stability over decades. The key technologies for this margin are the LTS joining process and the bevel passivation process using an electroactive a-C:H layer.

The new devices not only show an outstanding blocking capability, the losses of the thyristor have also been reduced significantly. In Figure 6 the reduction of losses are shown for a 150 mm silicon diameter amounting to approximately 30 percent lower switching losses. Compared to current designs, the reduced losses are caused by the recovery charge Q<sub>1</sub>, at the same on-state voltage V<sub>T</sub>.

In Figure 7 the calculated data for the new low loss thyristor with 100 mm silicon diameter is shown. For the defined conditions  $I_T = 1.5$  kA, di/dt = -1.5 A/µs,  $V_R = -100$  V, the blocking capability of this smaller device will be as high performing as the 150 mm silicon diameter device.

#### Conclusion

The article described a new 8.5 kV low loss thyristor family designed for industrial applications. With the new technology, full blocking capability at 50 Hz/60 Hz is achieved for 125°C at 8.5 kV. Beside these key factors, outstanding surge current capability and low mechanical installation force are additional features of these devices which are important for industrial applications. This enables highly efficient and powerful applications with superior reliability for today 's and future 's demands.