## **Table of Contents**

# **Table of Contents**

| Table of | f Contents                                               | 2  |

|----------|----------------------------------------------------------|----|

| Acronyn  | ns and Abbreviations                                     | 3  |

| 1        | Scope and Introduction                                   | 4  |

| 2        | Component Handling                                       | 6  |

| 2.1      | Moisture Sensitivity Level                               |    |

| 2.2      | Storage and Transportation Conditions                    | 7  |

| 2.3      | Packing and Automated Handling of Components             | 8  |

| 2.4      | Component Solderability                                  | 8  |

| 2.5      | ESD Protective Measures                                  | 9  |

| 3        | Surface-Mount Technology                                 | 10 |

| 3.1      | Footprint Types and Design                               | 10 |

| 3.1.1    | General Remarks                                          | 10 |

| 3.1.2    | Pad Definition and Solder Mask Layer                     | 10 |

| 3.1.3    | Pad Finishes                                             | 11 |

| 3.1.4    | Packages with Exposed Die Pads, Heat Sinks or Heat Slugs | 12 |

| 3.2      | Reflow Soldering of SMD Components                       | 14 |

| 3.2.1    | Solder Paste Composition                                 | 15 |

| 3.2.2    | Solder Paste Application                                 | 15 |

| 3.2.3    | Solder Paste Inspection                                  |    |

| 3.2.4    | Component Placement                                      |    |

| 3.2.5    | Reflow Solder Step                                       | 18 |

| 4        | Through-Hole Technology                                  | 21 |

| 4.1      | THD Component Preparation                                |    |

| 4.1.1    | Lead Cutting                                             | 21 |

| 4.1.2    | Lead Bending                                             |    |

| 4.2      | Soldering of THDs                                        |    |

| 4.2.1    | Wave and Selective Wave Soldering                        |    |

| 4.2.2    | Alternative Reflow Soldering of THD Components           |    |

| 5        | Further Soldering Techniques                             | 25 |

| 6        | Further Handling Considerations                          | 26 |

| 6.1      | Cleaning                                                 | 26 |

| 6.2      | Inspection                                               | 26 |

| 7        | Single Component Processing and Rework                   | 28 |

| 8        | Conformal Coating of Assembled PCBs                      | 30 |

| Referen  | ces                                                      | 31 |

| Revision | n History                                                | 33 |

# **Additional Information**

# **Acronyms and Abbreviations**

| 1K2    |    | special climatic condition class according to standard |

|--------|----|--------------------------------------------------------|

| AOI    |    | Automated Optical Inspection                           |

| AXI    |    | Automated X-ray Inspection                             |

| BGA    |    | Ball-Grid Array                                        |

| втс    |    | Bottom-Terminated Components                           |

| ENIG   |    | Electroless Nickel / Immersion Gold                    |

| ESD    |    | Electrostatic Discharge                                |

| HASL   |    | Hot-Air Solder Leveling                                |

| IC     |    | Integrated Circuit                                     |

| IMC    |    | Intermetallic Compound                                 |

| IR     |    | Infrared                                               |

| LGA    |    | Land-Grid Array                                        |

| LQFP   |    | Low-profile Quad Flat Package                          |

| MBB    |    | Moisture-resistant Barrier Bags                        |

| MSL    |    | Moisture-Sensitivity Level                             |

| NSMD   |    | Non-Solder Mask Defined                                |

| OSP    |    | Organic Solderability Preservatives                    |

| PCB    |    | Printed Circuit Board                                  |

| PCBA   |    | Printed Circuit Board Assembly                         |

| RH     |    | Room Humidity                                          |

| SAC    |    | tin-silver-copper solder (SnAgCu)                      |

| SMD    |    | Surface-Mounted Device                                 |

| SMD pa | ad | Solder Mask Defined pad                                |

| SMT    |    | Surface-Mount Technology                               |

| SPI    |    | Solder Paste Inspection                                |

| THD    |    | Through-Hole Device                                    |

| THT    |    | Through-Hole Technology                                |

#### **Scope and Introduction**

## 1 Scope and Introduction

This document provides a general overview of handling and processing recommendations for components made by Infineon Technologies. Throughout this document, "component" refers to electronic devices that are situated in a package with certain solderable terminals (e.g. a lead or a pad).

The document covers Surface-Mount Technology (SMT) as well as Through-Hole Technology (THT) components. The document also addresses the integration of specific package families, and some components for which no individual notes on processing are available.

Processes are described in very general terms as they are not package-specific. Therefore, the recommendations apply in the following order:

- Product specifications overrule package family-specific notes

- Package family-specific notes on processing overrule general notes

#### Surface-Mount Technology and Surface-Mounted Devices and Components

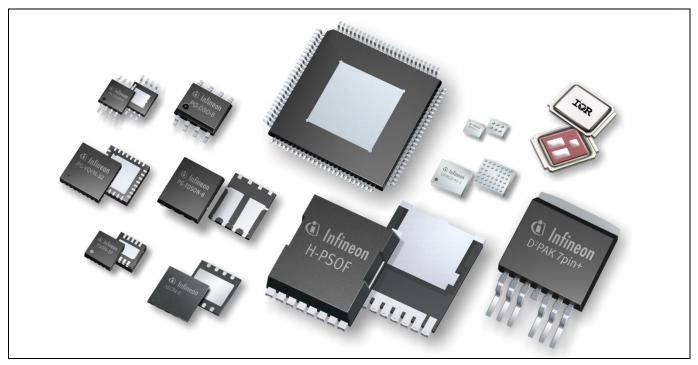

SMT refers to the mounting method used for electronic Surface-Mounted Devices (SMDs) and components that are soldered directly onto the surface of Printed Circuit Boards (PCBs). **Figure 1** shows some Infineon Technologies SMD packages.

Figure 1 Typical Infineon Technologies surface-mounted components.

#### **Scope and Introduction**

#### Through-Hole Technology and Through-Hole Devices and Components

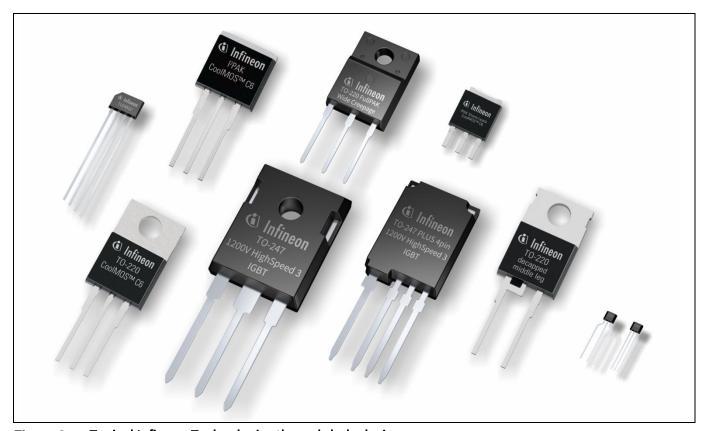

THT refers to the mounting method used for electronic Through-Hole Devices (THDs) and components whose pins are inserted into holes drilled in printed circuit boards and soldered to pads on the opposite side. The length of such pins on THDs depends on the intended application. **Figure 2** shows some Infineon Technologies THD packages.

Figure 2 Typical Infineon Technologies through-hole devices.

#### **Component Handling**

## 2 Component Handling

## 2.1 Moisture Sensitivity Level

For moisture-sensitive packages, it is necessary to control the humidity content of the component. Penetration of moisture into the package molding compound is generally caused by exposure to ambient air. Component sites with increased concentrations of moisture can cause damages to the package during the reflow process e.g. by the "popcorn effect". Thus, it is necessary to process moisture-sensitive components in a dry state, seal them in Moisture-resistant Barrier Bags (MBBs), and only remove them from the packing immediately prior to their board assembly. The Moisture-Sensitivity Level (MSL) classifies the permissible time that a component can remain outside the MBB (from opening the MBB until the final soldering process). It is a measure of the sensitivity of the component to ambient humidity. The most commonly applied standard J-STD-033\* defines eight different MSLs (Table 1). Please refer to the relevant "moisture sensitivity caution label" on the packing material [2].

The moisture sensitivity is tested with the maximum allowed reflow temperature according to J-STD-020\* [3]. Components which are MSL classified by Infineon Technologies have been tested by three reflow runs. This temperature shall not be exceeded during board assembly at the customer's facility.

Table 1 Moisture sensitivity levels according to J-STD-033\* depending on the Room Humidty (RH) [2].

| Level | Floor Life (out of bag)                                                                                             |                   |

|-------|---------------------------------------------------------------------------------------------------------------------|-------------------|

|       | Time                                                                                                                | Conditions        |

| 1     | Unlimited                                                                                                           | ≤ 30 °C / 85 % RH |

| 2     | 1 year                                                                                                              | ≤ 30 °C / 60 % RH |

| 2a    | 4 weeks                                                                                                             | ≤ 30 °C / 60 % RH |

| 3     | 168 hours                                                                                                           | ≤ 30 °C / 60 % RH |

| 4     | 72 hours                                                                                                            | ≤ 30 °C / 60 % RH |

| 5     | 48 hours                                                                                                            | ≤ 30 °C / 60 % RH |

| 5a    | 24 hours                                                                                                            | ≤ 30 °C / 60 % RH |

| 6     | Mandatory bake before use. After bake, the component must be reflowed within the time limit specified on the label. | ≤ 30 °C / 60 % RH |

The components have to be dried prior to the assembly process if one of the following situations applies:

- The moisture-sensitive components have been exposed to ambient air for longer than the specified time according to their MSL.

- The humidity indicator card indicates too much moisture after opening a MBB.

A "dry" package is reached by baking the component for 24 hours minimum at 125 +5/-0 °C according to the J-STD-020\* standard [3].

However, baking a package too often can cause solderability problems due to oxidation and/or growth of intermetallic phases. In addition, packing material (e.g. trays, tubes, reels, tapes, ...) may not withstand higher baking temperatures. Please refer to the imprints or labels on the respective packing to determine allowable maximum temperatures.

#### **Component Handling**

Note: Baking moisture-sensitive components can reduce the risk of package damage caused by absorbed water during soldering but cannot substitute for proper moisture-resistant packing.

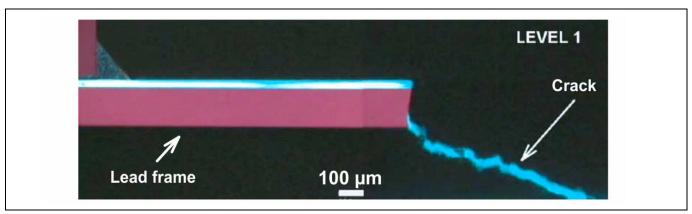

**Figure 3** shows a typical crack caused by the "popcorn effect" during soldering. The crack runs through the mold compound and results in a direct path connecting the lead frame with the package environment. Thus, it results not only in a mechanical weakening of the component but also creates a further site of potential attack by the environment.

Figure 3 Crack after solder shock caused by the so-called "popcorn" effect.

## 2.2 Storage and Transportation Conditions

Improper transportation and unsuitable storage of components can lead to a number of problems such as poor solderability, delamination, and package cracking during subsequent processing.

Accordingly, the standards IEC 60721-3-0, IEC 60721-3-1 and IEC 60721-3-2 for environmental parameters and their severities should be taken into account [9][10][11]. Detailed information concerning surface-mount technology, handling advice, and clean-room conditions can be found in the standards IEC 61760-2, IEC 62258-3 and ISO 14644-1 [12][13][14]. Table 2 gives an overview of the standards dealing with storage conditions of different products.

Table 2 Overview of general storage conditions [2][10][13].

| Product                            | Storage condition   |

|------------------------------------|---------------------|

| Component – moisture sensitive     | MBB (J-STD-033*)    |

| Component – not moisture sensitive | 1K2 (IEC 60721-3-1) |

The storage duration of the components ranges between 24 and 36 months. Please contact your local sales, application or quality engineer for further support.

7

#### **Component Handling**

## 2.3 Packing and Automated Handling of Components

Different packings and fixtures are available depending on component and customer needs. They comprise e.g. feeding components in an automatic pick & place machine (tape & reel, trays, ...) as well as surrounding bags and boxes to prevent damage during transportation or storage. Please refer to the product and packing specifications on the Infineon Technologies web page, and contact our sales department to receive information about what packing is available for a given product [1].

Generally, when dealing with device packing and automatic handling, the standards series IEC 60286-\* should be considered if applicable for a given package and packing. These standards discuss the application of continuous tapes, stick magazines and matrix trays, for example [4][5],[6]. Further information about the topic can be found in the standard ANSI/EIA-481-\* [7]. However, please be aware that the IEC and the EIA are not comparable in all topics.

Automatic or manual handling of components in or out of the component packing may cause mechanical damage to the components, the electrical contacts and/or their package bodies. In particular, unintentional bending of leads may damage the package body and result in electrical malfunction. See therefore the IEC 61340-5-\* [8].

Generally, the devices in Infineon Technologies packing are ready to use. Intentional bending is sometimes needed to prepare through-hole components prior to mounting (insertion procedure). In this case, the bending instructions in Section 4.1 have to be followed.

Any contamination to which the components or packings are exposed may cause or induce processes that (together with other factors) could lead to a damaged component. The most critical issues are:

- Solderability problems

- Corrosion

- Electrical shorts (e.g. due to conductive particles)

## 2.4 Component Solderability

Sufficiently thick and wettable metal surfaces (final plating) or solder depots/balls of the component terminals assure their good solderability, even after long periods of storage. The terminals may be post-mold plated with pure tin (Sn) or preplated with noble metals such as gold (Au) and/ or palladium (Pd) on a nickel (Ni) carrier (e.g. NiAu, NiPdAu). The composition of the terminals for components with solder balls or bumps may be either Ti-Cu or Tin-Ag-Cu based.

At Infineon Technologies, the solderability of the terminals is tested according to the standards IEC 60068-2-58:\* and J-STD-002\* [22][23]. Non-plated areas (e.g. created by device separation cutting) at the terminals are thereby ignored in any assessment of the solderability due to their non-finished surface conditions.

Further requirements for electronic-grade solder alloys and fluxes can be found in the standards J-STD-006\* and J-STD-001\* [24][26].

Note: Non-plated (e.g. cut) areas at the pins should be ignored in any assessment of the solderability due to their non-finished surface conditions.

Please contact your local sales, application or quality engineer for further support.

#### **Component Handling**

#### 2.5 ESD Protective Measures

Semiconductor devices are normally sensitive to Electrostatic Discharge (ESD), and require specific precautionary measures regarding handling and processing of their packages. The flow of electrostatic charge through e.g. an Integrated Circuit (IC) can be caused by human touch or by processing tools, resulting in high-current and/or high-voltage pulses that can damage or even destroy sensitive semiconductor structures. On the other hand, ICs may already be charged during processing. If discharging takes place too quickly ("hard" discharge), load pulses with damage potential can also be the result. ESD protective measures must therefore prevent contact of the devices with any charge source(s) over the entire fabrication path. This applies to the processing, the handling, and also the packing of the packaged devices. A few suggestions on handling and processing are provided below.

#### **Equipment for Staff**

- Dissipative/ conductive footwear or heel straps

- Suitable smocks

- Wrist straps with safety resistors

- · Gloves or finger coats which are ESD-proven (with specified volume resistivity)

#### Workplace configuration

- Standard marking of ESD protected areas

- Access controls, with wrist strap and footwear testers

- Air conditioning

- Dissipative and grounded floor

- Dissipative and grounded working and storage areas

- Dissipative chairs

- "Ground" potential bonding points for wrist straps

- Trolleys or carts with dissipative surfaces and wheels

- Suitable shipping and storage containers

- Protection against sources of electrostatic fields

#### Production installations and processing tools

- Machine and tool parts made of dissipative or metallic materials

- No materials having thin insulating layers for sliding tracks

- All parts reliably connected to ground potential

- No electric potential difference between individual machine and tool parts

- No sources of electrostatic fields

Detailed information on ESD protective measures may be obtained from the ESD specialist through the Area Sales Offices of Infineon Technologies. Our recommendations are based on the internationally applicable standards IEC 61340-5-1:\* and ANSI/ESD S20.20-\* [16][17].

#### **Surface-Mount Technology**

## 3 Surface-Mount Technology

## 3.1 Footprint Types and Design

#### 3.1.1 General Remarks

SMT is used for SMDs which are mounted by reflow soldering. The design of the pad and footprints on the PCB is a key factor for achieving high yield and reliability during board assembly. Important parameters include the size and type of the pads, the optimal thermal and electrical connections, the via design, and the board finish.

This document offers general guidelines to support our customers in board design. Studies at individual facilities may be necessary for optimization. The PCB manufacturer's capabilities, the customer's processes, and the product's specific requirements all have to be taken into account.

## 3.1.2 Pad Definition and Solder Mask Layer

The Infineon Technologies web page provides recommendations for the footprints with pad designs individually tailored towards the packages. Specific customer recommendations for certain package families are also provided [1].

The IPC-7351\* standard provides generic requirements for surface-mount design and land patterns and can be used as a basis for design [18]. However, a footprint design also affects the solder joint reliability. Modifying the generic design can therefore be beneficial. However, standard methods may sometimes not be applicable, especially for leadless packages.

Note: The footprints provided by Infineon Technologies as well as the general design rules given by the relevant standards have to be considered only as recommendations.

For reflow soldering, the size of the board pads is usually equal to or slightly larger than the package terminals or pads. Decreased board pad sizes are only used for area array packages (mainly to increase reliability) or for exposed die pads (mainly to get more space for routing). Mismatched board pad sizes could lead to:

- Swimming/ skewing (package moves parallel to the PCB plane during reflow soldering) and/or tombstoning (package lifts off during reflow soldering) caused by unbalanced and/or increased wetting forces

- Electrical opens or shorts

- Decreased reliability

A solder mask reduces the risk of solder bridging. Therefore, it should be applied between all copper pads that are expected to be electrically separated. Solder masks can also be used to divide larger copper areas into smaller wettable areas. This often improves SMT processability and creates better-balanced solder joints. Generally, two basic types of solder pads are in use.

#### Solder-Mask Defined Pads (SMD)

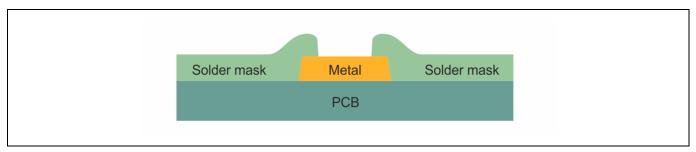

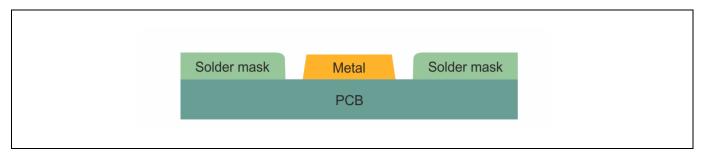

If the metal pad is larger than the solder mask opening, its extensions are solder-mask defined (**Figure 4**). The definition of solder pads by masking on the metallization allows for wider conductor lines that are especially benefical for devices that are exposed to high currents.

10

#### **Surface-Mount Technology**

Figure 4 Solder-mask defined pad.

#### Non-Solder Mask Defined Pads (NSMD)

In NSMD pads, the metal pad is surrounded by a solder mask clearance (**Figure 5**). Dimensions and tolerances of the solder mask clearance have to be specified to ensure that the mask does not overlap the solder pad. Depending on the PCB manufacturer's tolerances, 50 to 75 µm are widely used clearance values.

Figure 5 Non-solder mask defined pad.

The NSMD type is recommended especially for smaller solder pads, since the accuracy of the solder masking is generally lower than that of the copper pads. In an NSMD pad, the side walls of the copper can also be wetted. This can result in a significantly increased wettable surface for small pads and therefore increased reliability of the solder joints.

#### 3.1.3 Pad Finishes

The solder pads should easily be wetted by the liquid solder. In general, there is no recommendation for a dedicated combination of PCB pad finish and Infineon component. The quality of the finish (e.g. flatness of the surface) is particularly important for fine-pitch applications. There are several possible metal pad finishes described below.

#### Hot-Air Solder Leveling (HASL)

Solder finishes leveled by hot air have been widely used in fabrication because the appropriate methods are well known. The layer thickness is in the range of >  $5 \mu m$ . Surfaces created by this procedure are less preferred (especially for fine pitches <  $0.65 \mu m$ ) due to their relatively uneven surface profile with humps.

#### **Electroless Tin and Electroless Silver**

Solder joints on electroless tin and electroless silver are directly between copper and solder. While electroless tin finishes feature thicknesses in the range of approx. 0.3 -  $1.2~\mu m$ , the silver layers might be created with thicknesses in the range of approx. 0.2 -  $0.5~\mu m$ . The phase growth of the widely used tin-silver-copper solder alloy (SAC) on tin or silver is well understood within SMT. However, the long-term stability of these finishes,

#### **Surface-Mount Technology**

especially after baking (drying) the PCBs, may be a concern due to oxidation of the surface or acceleratedgrowth of the Intermetallic Compound (IMC) growth. The flatness of the finishes allows for small pad designs.

#### **Electroless Nickel / Immersion Gold (ENIG)**

ENIG finishes with thicknesses of 3 – 7  $\mu$ m Ni under 0.05 - 0.15  $\mu$ m Au have good solderability, flat surfaces, and high shear force values, but also more brittle solder joints of Ni and Sn containing IMC compared to Cu-Sn IMC. The solder flux is relatively low due to a lower surface solvation by the SAC solder alloy.

#### **Galvanic Gold**

Galvanic gold finish with its relatively high thicknesses of  $0.1 - 2 \mu m$  Au on  $> 3 \mu m$  Ni is typically used for connectors and not recommended for solder pads due to its low alloying tendency.

#### **Organic Solderability Preservatives (OSP)**

The protection of copper metal pads by organics is typically done with a thickness of < 1  $\mu$ m. This low cost, simple method and its possibilities for fast and automated fabrication are preferred properties of this coating. Since no additional metal is deposited on the original pad surface, the method yields very flat pads. However, the coating must be handled carefully to avoid damag. Due to its organic nature, its long-term stability is not as high as that of other coatings. Double-sided assemblies can only be created using an inert atmosphere during reflow. The intended vaporization of the layer during reflow also increases the probability of void formation in the solder joint.

Note: The wetting, alloying and therefore the overall solderability strongly depend on the surface finish of the metal pads. Since not every finish process is applicable to every pad size and pitch, the finishing technology of choice has to be carefully adapted to the targeted package solution.

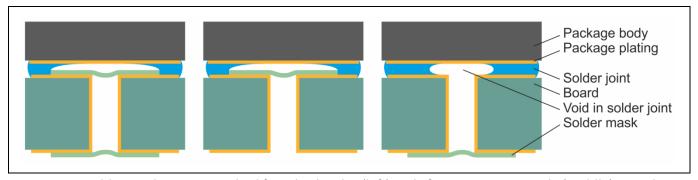

## 3.1.4 Packages with Exposed Die Pads, Heat Sinks or Heat Slugs

In most applications, the metallic die pad allows a large amount of heat to be transferred into the PCB, which increases the thermal performance of the attached device. To ensure sufficient heat transfer, the die pad should be soldered to a thermal pad on the board. For some applications and products, this can also increase the solder joint reliability and electrical performance.

Note: The connection of exposed die pads to the board requires reflow soldering. Wave soldering is not applicable.

Generally, it is possible to match the layouts of the pads on the board with the exposed pads on the components. However:

- If the exposed die pad on the component protrudes from one or more sides of the package body, it may be

helpful to increase the relevant board pad size slightly for better self-centering of the component during

reflow soldering.

- If the exposed die pad is fully hidden under the package body or even surrounded by peripheral pads, it may be helpful to decrease the board pad size to gain more space for routing and vias for these peripheral pads.

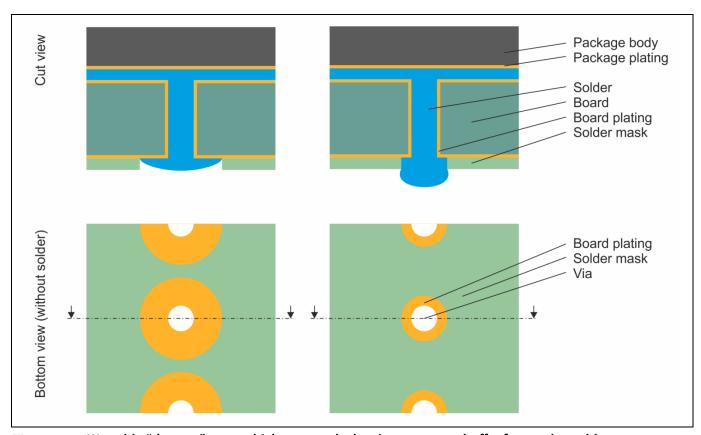

To connect the exposed die pad thermally and electrically to inner and/or bottom copper layers of the board, plated through-hole vias are generally used. They help to distribute the heat into the board area, which therefore flows from the chip over the package die pad and the solder joint to the thermal pad on the board.

A typical hole diameter of such thermal vias is 0.2 to 0.5 mm. The diameter and the number of vias in the thermal pad depend on the thermal requirements of the target product. This affects the power consumption of

#### **Surface-Mount Technology**

the product, the application requirements, the construction of the PCB, and the thermal path. Thermal and electrical analysis and/or testing are recommended to determine the minimum number of vias needed in each application.

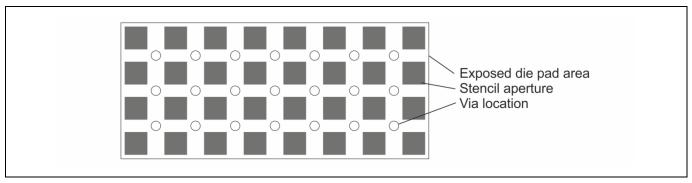

The stencil design needs to be aligned with the number and size of the vias to avoid solder paste penetrating them. Proper method is to segment the stencil apertures as shown in Figure 10 of Section 3.2.2. One of the consequences is a lower "stand-off" between the PCB and the package.

However, sometimes solder protrudes to the opposite side anyway. That may interfere with a second solder paste print process. To minimize the effect, dummy areas on the opposite side can sequester the surplus solder to avoid beading and the creation of solder balls (Figure 6).

Figure 6 Wettable "dummy" area, which surrounds the vias to act as a buffer for surplus solder.

The penetration of the vias by solder can also be avoided by plugging (e.g. filling with epoxy) and overplating the vias. If very small vias (so-called micro vias approximately 100  $\mu$ m in diameter) are used, it is generally sufficient to overplate the vias and fill them with copper. In both cases, it is necessary to specify a planar filling. However, flat dents tend to increase voiding because they serve as traps for gas aggregations formed during reflow soldering.

Another method is called tenting (Figure 7). In this case the vias are covered with a solder mask (e.g. dry-film solder mask). This cover should preferentially be applied from the package side because the voiding rate is significantly higher if tenting is applied on the opposite side. Combined with a customized solder-mask layout for the thermal pads (e.g. inserting solder mask ring around the vias), this method leads to good SMT processability and balanced solder joints.

#### **Surface-Mount Technology**

Figure 7 Solder mask tenting method from both sides (left); only from component side (middle); or only from board side (right). Note possible impacts on void formation.

To a certain extent, the open vias serve as venting holes for gas arising in the solder joint during the reflow process.

## 3.2 Reflow Soldering of SMD Components

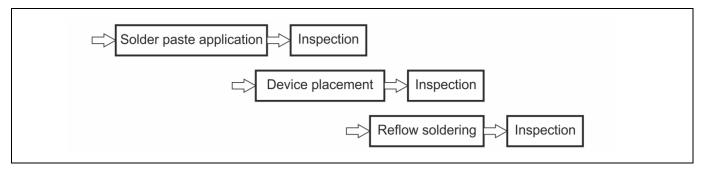

SMDs are usually mechanically and electrically connected to the board by reflow soldering. A typical process flow for single-side SMD board mounting is shown in **Figure 8**. In double-sided reflow soldering, further aspects have to be considered:

- Heavy components mounted to the top side (first reflow side) may fall off during reflow soldering of the bottom side (especially if there is heavy vibration during reflow).

- Components on the top side have to be suitable for being soldered two times at least (if classified by MSL, the components can be soldered three times [2]).

- Excessive moisture absorption between the first and the second reflow step may cause damage to moisturesensitive packages on the top side. If the maximum storage time per MSL classification of any component already mounted prior to the second reflow soldering is exceeded, suitable measures to avoid moisture soaking have to be applied (e.g. storage in moisture-barrier bags or a dry cabinet). Alternatively, a dry bake of the entire PCB may be applied (Section 2).

Figure 8 Typical process flow for single-side mounting of SMDs.

**Surface-Mount Technology**

## 3.2.1 Solder Paste Composition

Solder paste consists of a solder alloy, a flux system, and solvents. The volume is normally about 50 vol% alloy and 50 vol% flux and solvents. In terms of mass, this translates to approximately 90 wt% of alloy and 10 wt% of flux system and solvents.

The metal alloy in lead-free solder pastes generally consists of SAC alloys (SnAgCu; typically 1 - 4% Ag and < 1% Cu). The paste type (metal grain diameter in paste) selection depends on the field of application and hence the smallest stencil aperture dimensions typically used. As a starting point, Infineon Technologies recommends following the rules for "spheres per aperture" as described in Section 3.2.2.

The function of the flux system is to remove oxides and contaminants from the solder sites during the soldering process. The capability of removing oxides and contaminants depends on the activation level of the flux system that is used. A "no-clean" solder paste is preferred for all packages where cleaning underneath the component (e.g. leadless packages, packages with exposed die pads) is difficult. The residuals of no-clean pastes after reflow are intended to have no negative influences (e.g. leakage currents) on the assembled board.

The solder paste should be selected based on the requirements and components in the respective application. The paste composition affects the voiding tendency (evaporation of solvents during reflow) and the paste viscosity and therefore the printing performance. This is especially important for fine-pitch components or high-speed printing.

Generally, the solder paste is sensitive to age, temperature, and humidity. Please comply with the handling recommendations of the paste manufacturer.

## 3.2.2 Solder Paste Application

Generally, the solder paste is applied onto the PCB metal pads by stencil printing. Screen printing or dispensing is used only for special applications.

When using stencil printing, the targeted stand-off and/or solder joint volume is governed by the stencil aperture, which is defined by the stencil thickness and aperture area. The lower possible limits of these dimensions are generally defined (besides e.g. stencil material) by the maximum metal grain diameter of the solder paste.

The lateral dimensions of the stencil aperture can be estimated using the rules of "spheres per aperture" as shown in **Figure 11Figure 9**. When applying the rules, the smallest dimension of an aperture and the maximum possible grain diameter of a paste must both be taken into account. The paste-dependent metal grain diameter is given by the J-STD-005 standard [25].

For rectangular apertures:

smallest aperture dimension ≥ 5 · max. grain diameter

For circular apertures:

aperture diameter ≥ 6 · max. grain diameter

The choice of solder paste can also be driven by the lead pitch. For example, using a Type 4 paste from pitch 0.4 mm onwards is reasonable.

#### **Surface-Mount Technology**

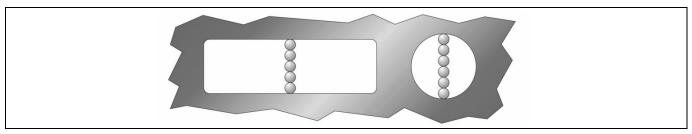

Figure 9 Rules of "spheres per aperture" for rectangular (left) and circular stencil apertures (right).

The ratio limit between the aperture area and the stencil thickness can be estimated by the following rule of thumb:

$$A_{apert} > F \cdot A_{wall}$$

A<sub>apert</sub>: Area of the aperture in the stencil e.g. for a round aperture with radius r:

$$A_{apert} = \pi \cdot r^2$$

A<sub>wall</sub>: Area of the wall of the aperture e.g. for a round aperture with radius r and stencil thickness d:

$$A_{\text{wall}} = 2\pi \cdot \mathbf{r} \cdot \mathbf{d}$$

F: Feasibility factor, which depends on the stencil and printing process quality and the solder paste (e.g. for conservative processes, F = 0.8; for advanced processes, F = 0.66)

To ensure a uniform and high solder paste transfer to the PCB, laser-cut stencils (mostly made from stainless steel) and electroformed stencils (made from nickel) are preferred. Rounding the corners of rectangular apertures (radius approx.  $50~\mu m$ ) can also support good paste releases, with a low feasibility factor of down to F = 0.66. For stencil surfaces with advanced treatment (including on aperture walls), a further reduction of the feasibility factor might be possible.

For components with leads of constant size, a typical stencil aperture is reduced to 90% of the board pad size. For components with leads of various sizes, the solder paste volumes for each pad have to be matched properly by using appropriate stencil apertures in order to avoid swimming, tilting, solder beading, or tombstoning. Especially large exposed pads in the center of the component tend to lift the component if the solder paste volume is not reduced sufficiently. This effect is caused by the tendency of molten solder to form a spherical shape (lowest surface tension). Therefore, large pads with a reduced amount of printed solder will lead to a decreased stand-off after reflow compared to smaller pads without reduction.

A typical approach for reducing the solder volume on large pads (e.g. stencil aperture edge lengths > 5 mm) is the segmentation of the stencil. Figure 10 shows such a segmentation together with the incorporation of via openings in the PCB. Placing them in the intersections of the stencil design can prevent direct and undesired printing of solder paste into these vias. Since the stand-off also depends on the wetting behavior of the board pad finish, the optimum volume has to be determined by the customer, taking into account the via technology used.

#### **Surface-Mount Technology**

Figure 10 Exemplarly design of stencil segmentation and via locations for exposed die pads.

The applied solder paste volumes and therefore the stencil thickness and apertures have to match the specifications of all components on the PCB.

Note: The solder paste volumes applied for the individual components represent a compromise among the optimal solderabilities of all components on the board.

## 3.2.3 Solder Paste Inspection

Automatic Solder Paste Inspection (SPI) systems are frequently used for inspecting the solder paste depots applied onto the boards by printing. SPI systems are either built into the printer, or are separate modules in line. Such vision systems can measure the solder paste planar coverage in x- and y-direction and the deposited solder paste volume. Adequate acceptance criteria have to be defined individually.

## 3.2.4 Component Placement

Although the self-alignment effect due to the surface tension of the liquid solder will support the formation of reliable solder joints, the components have to be placed accurately according to their geometry. Placing the components manually is possible but not recommended, especially for components with larger terminals and a wide pitch.

Generally, an automated pick-and-place machine is recommended when assembling surface mount components in order to achieve precise placement and therefore reliable solder joints. Component placement accuracies of  $\pm 50~\mu m$  are obtained with modern automatic component-placement machines using vision systems. With these systems, both the board and the component are optically measured before placing them into their programmed positions. The fiducials on the board are located either on the edge of the board for the entire board or additionally on individual mounting positions (local fiducials).

The maximum tolerable displacement of the components on the PCB is 20% of the metal pad width (for NSMD pads, see Section 3.1.2). For example, for an exposed die pad and a Low-profile Quad Flat Package (LQFP) with a 0.5 mm lead pitch, the component pad-to-board pad misalignment has to be below 50  $\mu$ m in order to assure a robust mounting process. Generally, this is achievable with a wide range of placement systems.

#### **Surface-Mount Technology**

The following general recommendations concerning component placement are important to follow:

- Especially on large boards, local fiducials close to the component can compensate for PCB tolerances.

- The lead identification capabilities of the placement system should be used instead of the outline centering. The outline centering can only be used for components in which the tolerances between pad and outline are small compared to the placement accuracy needed.

- To ensure the correct identification of the components by the vision system, adequate lighting and the correct choice of measurement modes are necessary. Accurate settings can be found in the equipment manuals.

- An unnecessary high placement force can squeeze out solder paste and cause solder joint shorts. On the

other hand, a placement force that is too low can lead to insufficient contact between component and the

solder paste and may result in insufficient sticking of the component on the solder paste. This may

furthermore lead to shifted or dropped components.

- A pick-up nozzle suitable for the component body size should be used. The nozzle should be slightly smaller

than the component body. A nozzle that is too wide may leads to an irregular force distribution, especially to

increased forces at the edges of the package body. On the other hand, a nozzle that is too small may lead to

increased force in the package center. For package bodies that are divided into different areas with different

heights, please take special care when choosing the nozzle. Nozzle shape and size are probably more critical

in these cases.

## 3.2.5 Reflow Solder Step

Reflow soldering is the most common technique to attach surface-mount components to a PCB. The soldering process typically consists of applying the solder paste, positioning the components, and melting the solder in an oven. By melting the metallic powder particles in the solder paste, the metal pads of the component and the board are joined together while creating a strong metallurgical bond after resolidification of the solder. There are usually four process zones in the conventional reflow solder process: preheatment, thermal soak, reflow, and cooling.

The optimum reflow profile of a board assembly is governed by several parameters:

- Oven design and number of zones

- Volume of the hot gas

- Board thickness and layout

- Differences in thermal mass of all components

- Maximum allowed component temperatures

- Recommended reflow profile for the solder paste

A nitrogen atmosphere will reduce oxidation and improve the solder joint quality at the typical reflow temperatures used for the lead-free process.

The temperature profile of a reflow process is divided into several sections, each with a special function. It is essential to follow the solder paste manufacturer's application notes. The single solder process parameters are influenced by various factors in addition to the device package. Additionally, most boards contain more than one package type and therefore the reflow profile has to be compatible with the requirements of all the components and materials. It is recommended to measure the solder joints' temperatures by thermocouples beneath the respective packages, taking into account the fact that components with large thermal masses do not heat up as fast as the lightweight ones. The position and the surrounding of the components on the board, as well as the boards thickness, can also influence the solder joint temperatures significantly.

#### **Surface-Mount Technology**

Note: Similar to the solder paste volumes applied on the board, the reflow temperature profile is a compromise among the optimal solderabilities of all components on the board.

During the reflow process, each solder joint has to be exposed to temperatures above the melting point of the solder (i.e. liquidus of the solder alloy) in order to reach the optimum solder joint quality in a sufficient time. On the other hand, overheating the board with its components has to be avoided as well. Please refer to the bar code label on the packing when choosing the maximum package body temperature during soldering. It is important that the maximum temperature of the package during the reflow does not exceed the specified peak temperature  $T_p$ .

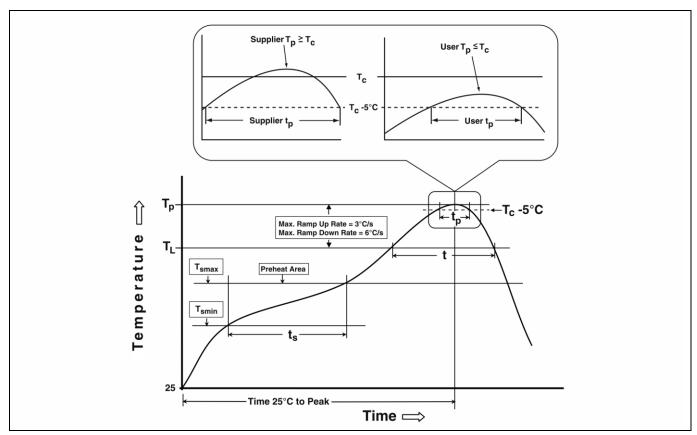

**Figure 11** shows the difference between the qualification reflow profile of the individual components and a possible process reflow profile of a component during board assembly. At Infineon Technologies the components are qualified according to the J-STD-020\* standard regarding their resistance to solder temperatures [3].

Note: The component qualifications conducted at Infineon Technologies according to the standards provide the worst-case reflow profiles a certain device and its package have to endure. They do not provide an applicable process reflow profile.

Figure 11 Qualification profile of reflow solderable electronic devices and packages with maximum endurable peak temperature  $T_p$  according to the J-STD-020\* standard. A possible process profile must have a peak temperature  $T_c$  that is below  $T_p$  [3].

#### **Surface-Mount Technology**

#### **Heating concepts**

The soldering determines the yield and quality of the Printed Circuit Board Assembly (PCBA) to a very large extent. Generally, the following heating methods are in use:

- Forced convection

- Vapor phase

- Infrared (with restrictions)

The most frequently recommended reflow type ovens used in mass production work with forced convection by blowing hot air or nitrogen at different temperatures in different zones. The boards travel through these zones on a conveyor band.

Alternative reflow oven concepts, mostly used in niche applications, are based on heat transfer by infrared or vapor phase.

When using Infrared (IR) ovens without convection, special care may be necessary to assure a sufficiently homogeneous temperature profile for all solder joints on the board, especially on large, complex boards with different thermal masses of the components. Using infrared soldering, the components are heated as a result of absorbing IR radiation. Usually the heating is done with radiators positioned on either side in order to heat or preheat the whole volume surrounding the solder joint, if possible. The temperature of the various components may vary severely since the radiation absorption mostly depends on the material and the IR wavelength, and less on the radiator temperature. The metallic terminals of the components, for example, have only a low absorption rate. In fact, they reflect IR radiation so the heat has to be supplied to the solder joints via the component itself, the similarly heated board, and the ambient air. Naturally, large and thick SMDs need longer periods than small and thin ones to reach the intended temperature. Special care has to be taken if large area array packages such as Bottom-Terminated Components (BTCs) or Land Grid Arrays (LGAs) are soldered by IR radiation, because the solder joints between the package and the board are heated up much more slowly than the environment. Precautions must be taken by empirically varying the different radiator power settings and the conveyor speed to ensure that the process does not drop below the minimum soldering temperature or exceed the maximum allowable temperature at any point. This must be ensured by specific temperature measurements.

Compared to forced convection and especially infrared soldering, a vapor-phase oven provides the least risk of overheating because it limits the temperature by using special fluids with a vapor temperature slightly above the melting point of the solder alloy. The atmosphere is free from oxygen. One disadvantage is that most vapor phase ovens are batch ovens and not conveyor-driven. This makes it difficult to implement them in mass production lines.

#### **Through-Hole Technology**

## 4 Through-Hole Technology

## 4.1 THD Component Preparation

## 4.1.1 Lead Cutting

The leads of THDs can be cut before mounting, or after mounting and soldering.

In the case of cutting after soldering, the leads are embedded in the solder joint. Severe mechanical mishandling during the cutting process could cause solder joint failure, but generally does not harm the component body. When cutting prior to mounting, the leads have to be fixed by a clamp that should be similar to a clamp used for lead bending.

## 4.1.2 Lead Bending

The through-hole devices are inserted into drilled and metallized holes in the circuit board. Prior to the insertion, the terminals of THDs may have to be bent to fit the pitch of the solder holes.

The insertion of THDs is either done with special automatic equipment or manually. Special care has to be taken to avoid damaging the package due to deformations during bending. The diameter of the drill holes in the PCB must match the tolerances of the component leads, of the drill hole position, and of the placement process. Additionally, there should be sufficient space for solder joint formation.

It is very important to comply with the following guidelines:

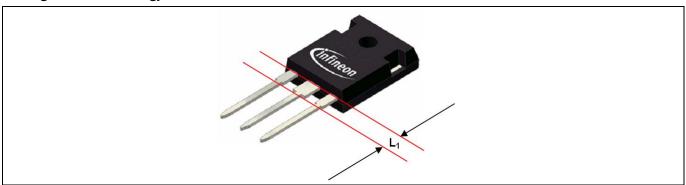

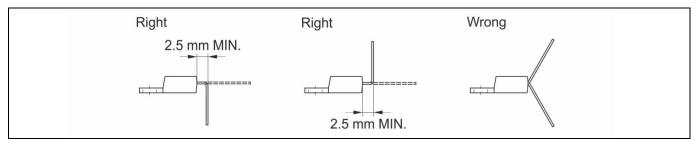

- If the package has an increased lead width next to the package body, the bending distance needs to be greater than the length of the increased lead width (L<sub>1</sub> in Figure 12).

- In other cases, the minimum distance between the package body and the first bend should be 2.5 mm. The leads must not be bent immediately adjacent to the package (Figure 13).

- The minimum bend radius needs to be 0.5 mm.

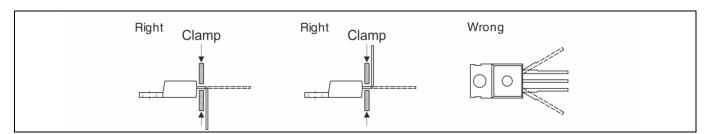

- A clamp should be used when bending to avoid excessive mechanical forces such as pulling and shearing between the leads and the package body. Between the point of bending and the package edge, tensile stress during the bending process needs to be relieved (Figure 14). Avoid slippage due to weak clamping, as well as weakening of the lead due to overly strong clamping.

- A properly designed clamping tool helps to make the bend shape reproducible.

- The maximum force applied to the leads between the clamp and the point where the bending force is applied should not exceed a certain limit. This maximum force is mainly dependent on the cross-sectional area of the lead. A typical maximum force is 20 N.

- Bending the leads parallel to the lead plane is not allowed (Figure 14).

- Bending manually is acceptable if the guidelines above are followed.

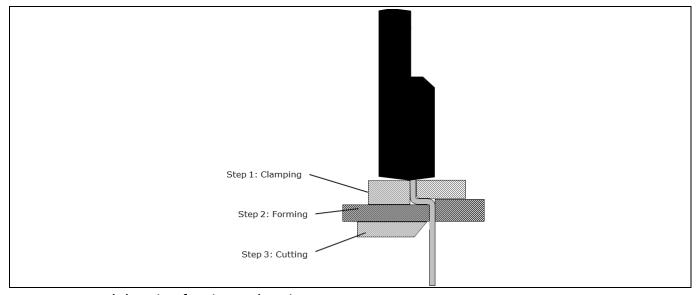

- Clamping, bending and cutting need to be done sequentially in that order; a subsequent process is not allowed to be initiated before the preceding process is finished (Figure 15).

After the insertion of the component, the protruding lead tips are occasionally bent against the PCB hole to avoid component movement during the soldering step. Please take care that this does not lead to mechanical stress which causes defects at the interface between the leads and the package body.

For details and special arrangements, please refer to the relevant product data sheet. For some package families, special notes describe bending and clamping in more detail.

#### Through-Hole Technology

Figure 12 Minimum cutting and bending distance given by the distance between package body and narrow leads.

Figure 13 Examples of bending leads of THDs.

Figure 14 Examples of lead-bending mechanisms.

Figure 15 Lead clamping, forming, and cutting process steps.

#### **Through-Hole Technology**

## 4.2 Soldering of THDs

## 4.2.1 Wave and Selective Wave Soldering

THDs are typically wave-soldered. The number of THDs on industrially produced circuit boards is steadily decreasing in many applications, making wave soldering less and less cost-effective. Therefore, the small numbers of THDs (mostly connectors and special components) are soldered with selective wave soldering.

Wave soldering is a large-scale process by which the protruding lead tips on the board side opposite to the components are soldered to a board. The name is derived from the fact that the process uses a pot to hold a quantity of molten solder. The assembled board is passed across a pumped wave or a cascade of solder. The solder wets the exposed metallic areas of the board (those not protected with solder mask), creating a reliable mechanical and electrical connection.

As already mentioned, only the lead tips of the THDs are in direct contact with the hot solder during wave soldering. The body of the package is heated through the thermal-conductive leads. This method has two consequences:

- 1. The package body is cooler than in the case of reflow soldering.

- 2. The temperature gradient between the leads and the body as well as inside the package is larger than the gradient caused by reflow soldering.

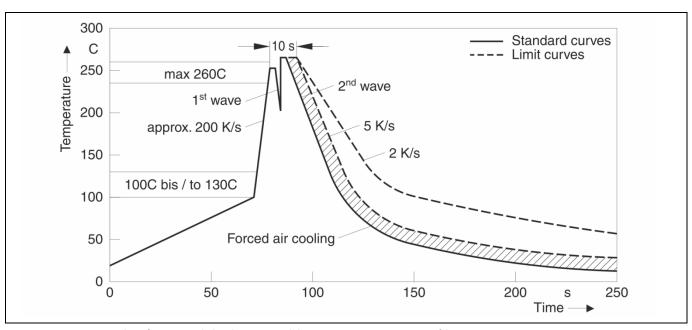

The heat resistance of wave-soldered THDs is tested according to the JESD22-B106\* and IEC60068-2-20 standards. The standards give the maximum endurable temperatures and times  $(260^{\circ}\text{C}, 10 \text{ s})$  for (selective) wave soldering. In a dual-wave process, the sum of the maximum durations of the first and second waves has to be <10 s [19],[20].

There are many types of wave-soldering machines. However, the basic components and operating principles of these machines are the same. A standard wave-solder machine has three zones: the fluxing zone, the preheating zone, and the soldering zone. An additional fourth zone, cleaning, may be used depending on the type of flux additive applied. When using lead-free solder alloys, a nitrogen atmosphere might be beneficial.

Dual-wave soldering is the most commonly used method. Figure 16 shows an example of a typical dual-wave soldering temperature profile. The peak temperatures, ramp rates, and times depend on the materials and the wave soldering equipment used.

The first wave is generated by a turbulent flow and therefore guarantees wetting of nearly all shapes of leads and board pads, but also creates some solder bridges. These solder bridges have to be removed by the second wave, which has a laminar flow.

Selective wave soldering is used when only a few THDs have to be soldered onto the board. Generally, this step takes place after the reflow soldering of the other components. The components that are not supposed to be soldered must be protected either by using special fixtures and deflectors for the board and/or by having a small wave shape that is created by using special wave-guiding tubes or covers.

#### **Through-Hole Technology**

Figure 16 Example of a typical dual-wave soldering temperature profile.

## 4.2.2 Alternative Reflow Soldering of THD Components

An alternative method to solder THDs by reflow soldering is provided by the "pin-in-paste" technique in which solder paste is printed onto a circuit board near or over the drill holes through which the leads are fed. The soldering step then takes place together with the applied SMDs.

In order to ensure reliable solder joints, it is necessary to increase the amount of solder for the leads, board pads, and drill holes compared to that of the SMDs. The amount of solder paste has to be adjusted to ensure that after reflow, the drill holes are filled to a certain amount to ensure the quality is comparable to wave-soldering quality. To achieve that, several methods are in use:

- Overprinting

- Step stencil

- Solder paste dispensing

As already mentioned earlier, the thermal load on wave-soldered THDs is not normally constant over the whole package and induced over the lead tips. Thus, a reflow-soldered THD experiences an entirely different temperature load:

- The temperature is nearly the same for the whole package compared to wave soldering.

- The duration of the peak temperature load to the package is much longer compared to wave soldering.

Therefore, the heat resistance of THDs that are reflow soldered has to be tested according to the J-STD-020\* standard similarly to the SMDs [3].

Note: Reflow soldering of Infineon Technologies THD packages is not recommended since they are qualified only for wave soldering temperature profiles.

#### **Further Soldering Techniques**

## 5 Further Soldering Techniques

Beside wave and reflow soldering, other techniques are used in special applications. These include laser welding and soldering, hot bar soldering, and manual soldering with a soldering iron or hot-air guns.

Infineon Technologies SMD products are qualified for reflow soldering while THT products are qualified for (selective) wave soldering. The approval for other soldering methods is product-specific. Please refer to the product data sheet or ask your local sales, application, or quality engineer for details.

If a soldering method different from the qualified one is required, the following remarks should be considered:

- The maximum temperature of the component body and leads must not exceed the maximum temperature allowed for the qualified soldering method.

- The maximum allowed time at high temperatures must not exceed the maximum time allowed for the qualified soldering method.

- If increased heat is applied to the leads (e.g. during iron soldering), the maximum temperatures in the package and of the package body must not exceed the maximum temperatures allowed during the qualified soldering method.

For details and special arrangements, please refer to the product data sheet and/or qualification report. For example, the given moisture sensitivity level for the given product and preconditioning permitted by J-STD-020\* shows the maximum temperatures and times for hot-air soldering [3].

In any case, mechanical or thermo-mechanical overstress during manual handling and soldering must be avoided (especially contact between the soldering iron or hot-air gun and the component package).

#### **Further Handling Considerations**

## 6 Further Handling Considerations

## 6.1 Cleaning

After the soldering process, flux residues may remain in the surroundings of the solder joints. If a "no-clean" solder paste has been used for solder paste printing, the flux residues usually do not have to be removed after the soldering process. However, in case the solder joints have to be cleaned, the cleaning method (e.g. ultrasonic, spray or vapor cleaning) and solvents have to be selected by considering the flux used (resin-based, water-soluble, etc.) and the environmental and safety aspects. Removing or drying of even small residues of the cleaning solution should also be very thorough. Please contact the flux and solder-paste manufacturer for recommended cleaning solutions.

Note: Cleaning under the package bodies of exposed die pad packages, LGAs, Ball-Grid Arrays (BGAs), or comparable packages is not likely to be complete. Some residue is likely to remain.

## 6.2 Inspection

#### **After Component Placement**

After the component placement, the status of the mounting or possible severe misplacements can be checked by a microscope or an Automated Optical Inspection (AOI). For example, the orientation of a component can also be examined by identifying the pin 1 mark.

#### **After Soldering**

A simple visual inspection of the solder joints can be done using an optical microscope. An automated visual inspection of the solder joints with conventional AOI systems is however limited to the outer solder joints, the leads and the lead frame areas that extend beyond the package body.

For several reasons, it may also be necessary to assess the joint quality with X-ray analysis and/or cross sections. These methods will allow inspection of the solder joints under the leads of SMDs, or the proper fill of metallized vias of THDs.

For packages with exposed die pads (LGAs, BGAs or comparable packages) the only reliable method for an efficient inline control is to use an Automatic X -ray Inspection (AXI) system. AXI systems are available as 2D and 3D solutions. They usually consist of an X-ray camera and the hardware and software necessary for inspection, controlling, analyzing and data transfer routines. These systems enable the user to reliably detect soldering defects such as poor soldering, bridging, unusual voiding, and missing parts.

The cross-sectioning of a soldered package as well as dye penetrant analysis can serve as tools for sample monitoring only, due to their destructive character. Nonetheless, these analysis methods must be used during the design process of new products to obtain detailed information about the solder joint quality.

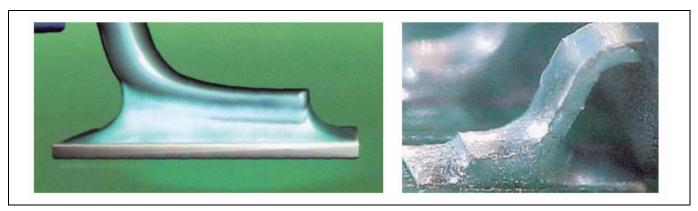

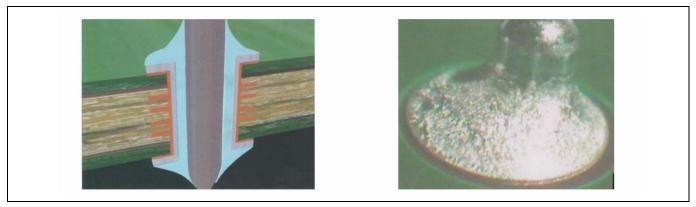

**Figure 18** and **Figure 17** show SMD and THD leads with ideal wetting according to the IPC-A-610\* standard for the acceptability of electronic assemblies [21]. The non-wetting of the punched or sawed-off lead tips is not a rejection criterion since they have no solderable finish.

26

## Further Handling Considerations

Figure 17 Example of an ideally wetted SMD lead from IPC-A-610\* [21].

Figure 18 Example of an ideally wetted THD lead from IPC-A-610\* [21].

**Single Component Processing and Rework**

## 7 Single Component Processing and Rework

If an undesired component is detected after board assembly, it can be replaced by a new one when certain aspects are taken into account. In case of simple rework processes using solder iron or hot-air gun, the repair of single solder joints is generally possible but requires special rework equipment. Especially for fine-pitch applications, it may be difficult to use soldering irons (see **Section 5**). Manual repair efforts for single solder joints of BGAs or LGAs or soldered exposed die pads are not recommended. Special tools are necessary for these types of packages.

#### Heating

The heat transfer to the component and board by hot air is strongly recommended. The temperature and the air flow for heating the component should always be controlled. With freely programmable temperature profiles (e.g. by computer controller), it is possible to adapt the profiles to different package sizes and thermal masses. Preheating from the bottom side of the board is also recommended, e.g. by using infrared techniques. However, the bottom heating should only augment the hot air flow from the upper side. Nitrogen atmosphere can be used instead of air.

During soldering, it should be assured that the package peak temperature is not higher and the temperature ramps are not steeper than for the standard assembly reflow process (Section 3.2.5).

#### Moisture

Whatever rework process is applied, do not exceed the thermal limits of the components (e.g. MSL information) and the board. If the maximum time recommended for the storage of a component outside the dry pack is exceeded after the board assembly (see label on packing material), the board should be dried prior to the rework according to the recommendations (e.g. in a dry bake). For details, please refer to Section 2.1 and the J-STD-033\* standard [2].

Note: During rework processes, comply with the temperature and moisture-sensitivity specifications of the components in the same way as during a standard reflow soldering process.

#### **Extraction**

Do not to apply excessive mechanical forces during the extraction of the component. Otherwise, a potential failure analysis of the package may provide misleading results. Furthermore, irreversible damage to the board may prohibit potential reuse. For large packages, pipettes can be used (implemented on most rework systems). For small packages, tweezers may be more practical.

#### **Component Return**

If it is intended to send the extracted component back to Infineon Technologies, please consider the following:

If the components of concern are fragile, it is especially necessary to determine if they can be electrically tested at Infineon Technologies directly after desoldering, or if these components have to be re-balled or preconditioned prior to testing. If safe removal of the suspected component is not possible or too risky, the entire board or the part of the board containing the defective component should be sent back.

If a component is suspected to be defective and has to be sent back to the supplier, please note that during the removal of this component from the board, no further defects must be introduced to the component. Additional damages may interfere with the failure analysis at the supplier's facilities. Therefore, the rules in this section have to be respected.

28

#### **Single Component Processing and Rework**

Note: Generally, components should be sent back to Infineon Technologies in their delivered state. Alternative procedures, if necessary, may be agreed upon in advance.

#### **Board Preparation**

After removing the undesired component, the pads on the board have to be cleaned to remove solder residues. This may be done by vacuum desoldering or the wicking technique. Cleaning solvents may be necessary in order to ensure sufficient removal of flux residues.

The use of any type of brushes is not recommended. Before placing a new component on the site, solder paste should be applied to each board pad by printing (special micro stencil) or dispensing. A no-clean solder paste is recommended.

#### Reassembly

After preparing the solder site, the new component can be placed onto the board. Placement accuracy and force should be comparable to the automatic pick-and-place process.

To ensure precise alignment of the package to the board, a split optic system should be utilized. The bottom side of the package as well as the corresponding footprint on the board should be observable. Microscope magnification and resolution should be appropriate for the pitch of the component. Placement accuracies better than  $\pm 100~\mu m$  are recommended. Additionally, the system should have the capability of removing solder residues from the board pads (e.g. by special vacuum tools).

29

During the soldering, it should be assured that the package peak temperature is not higher and the temperature ramps are not steeper than for the standard assembly reflow process (Section 3.2.5).

#### **Conformal Coating of Assembled PCBs**

## 8 Conformal Coating of Assembled PCBs

In some applications, conformal coatings are used to prevent damage due to external influences such as:

- Mechanical abrasion

- Vibration

- Mechanical shock

- Humidity

- Hand perspiration

- Chemicals and corrosive gases

These influences may cause:

- Electrical leakages due to humidity

- Corrosion that leads to degradation of conductor paths, solder joints, and any other metallized areas and/ or formation of electrical leakage paths. These can ultimately result in electrical shorts (electrical leakage) or open contacts.

- Mechanical damage to conductor paths, solder joints and components, leading to electrical failures

Coatings act as electrically isolating and impervious covers that adhere well to the various circuit board materials. A wide variety of different coatings is available on the market, which differ in:

- Price

- Convenience in processability (spray, dip, casting, curing, ...)

- Maintainability

- Controllability

- Homogeneity

In any case, please take into account the chemical, electrical, mechanical and thermo-mechanical interactions between the coating and the board or the components.

#### **Conformal Coating of Assembled PCBs**

#### References

- [1] Infineon Technologies: Packages. <a href="http://www.infineon.com/cms/en/product/technology/packages/">http://www.infineon.com/cms/en/product/technology/packages/</a>, last accessed: 2016-01-05 11:25 pm.

- [2] JEDEC Solid State Technology Association: IPC/JEDEC J-STD-033\*. Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices.

- [3] JEDEC Solid State Technology Association: IPC/JEDEC J-STD-020\*. Moisture/Reflow Sensitivity Classification for Nonhermetic Surface Mount Devices.

- [4] International Electrotechnical Commission: IEC 60286-3:\*. Packaging of components for automatic handling Part 3: Packaging of surface mount components on continuous tapes.

- [5] International Electrotechnical Commission: IEC 60286-4:\*. Packaging of components for automatic handling Part 4: Stick magazines for dual-in-line packages.

- [6] International Electrotechnical Commission: IEC 60286-5:\*. Packaging of components for automatic handling - Part 5: Matrix trays.

- [7] American National Standards Institute: ANSI/EIA-481-\*. 8 mm through 200 mm Embossed Carrier Taping and 8 mm & 12 mm Punched Carrier Taping of Surface Mount Components for Automatic Handling.

- [8] International Electrotechnical Commission: IEC 61340-5-\*. Electrostatics Protection of electronic devices from electrostatic phenomena.

- [9] International Electrotechnical Commission: IEC 60721-3-0. Classification of environmental conditions: Part 3: Classification of groups of environmental parameters and their severities; introduction.

- [10] International Electrotechnical Commission: IEC 60721-3-1: Classification of environmental conditions: Part 3: Classification of groups of environmental parameters and their severities; Section 1: Storage.

- [11] International Electrotechnical Commission: IEC 60721-3-2: Classification of environmental conditions: Part 3: Classification of groups of environmental parameters and their severities; Section 2: Transportation.

- [12] International Electrotechnical Commission: IEC 61760-2: Surface mounting technology Part 2: Transportation and storage conditions of surface mounting devices (SMD) Application guide.

- [13] International Electrotechnical Commission: IEC 62258-3: Semiconductor Die Products Part 3: Recommendations for good practice in handling, packing and storage.

- [14] International Organization for Standardization: ISO 14644-1. Clean rooms and associated controlled environments Part 1: Classification of airborne particulates.

- [15] Infineon Technologies: Green Products. <a href="http://www.infineon.com/cms/en/product/technology/green-products/">http://www.infineon.com/cms/en/product/technology/green-products/</a>, last accessed: 2016-01-05 14:25 pm.

- [16] International Electrotechnical Commission: IEC 61340-5-1:\*. Protection of electronic devices from electrostatic phenomena General Requirements.

- [17] American National Standards Institute: ANSI/ESD S20.20-\*. ESD Association Standard For the Development of an Electrostatic Discharge Control Program for Protection of Electrical and Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated Explosive Devices).

- [18] Association Connecting Electronics Industries: IPC-7351\*. Generic Requirements for Surface Mount Design and Land Pattern Standard.

- [19] JEDEC Solid State Technology Association: JESD22-B106\*. Resistance to Soldering Temperature for Through-Hole Mounted Devices.

#### **Conformal Coating of Assembled PCBs**

- [20] International Electrotechnical Commission IEC 60068-2-20:\*. Environmental testing Part 2-20: Tests Test T: Test methods for solderability and resistance to soldering heat of devices with leads.

- [21] Association Connecting Electronics Industries: IPC-A-610\*. Acceptability of Printed Boards Training and Certification program.

- [22] Electronic Components Industry Association, Assembly and Joining Processes and JEDEC Solid State Technology Association Committee: EIA/IPC/JEDEC J-STD-002\*. *Solderability Tests for Component Leads, Terminations, Lugs, Terminals and Wires*.

- [23] International Electrotechnical Commission: IEC 60068-2-58:\*. Environmental testing Part 2-58: Tests Test Td: Test methods for solderability, resistance to dissolution of metallization and to soldering heat of surface mounting devices (SMD).

- [24] Assembly and Joining Processes, Electronic Components Industry Association and JEDEC Solid State Technology Association Committee: IPC/EIA/JEDEC J-STD-006\*. Requirements for Electronic Grade Solder Alloys and Fluxed and Non-fluxed Solid Solders for Electronic Soldering Applications.

- [25] EIA Electronic Industries Alliance/ IPC Association Connecting Electronics Industries: J-STD-005\* Requirements for Soldering Pastes.

- [26] Assembly and Joining Processes, Electronic Components Industry Association and JEDEC Solid State Technology Association Committee: IPC/EIA/JEDEC J-STD-001\*. *Requirements for Soldered Electrical and Electronic assemblies*.

Revision **History**

# **Revision History**

## Major changes since the last revision

| Page or Reference   | Description of change                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| 2008/05 • All pages | Content update to Rev. 3                                                                                                |

| 2017/06 • All pages | <ul> <li>Content update to Rev. 4</li> <li>Complete rework of the document structure</li> <li>Content update</li> </ul> |

#### **Trademarks of Infineon Technologies AG**

HUNIC™, µIPM™, µPFC™, AU-ConvertIR™, AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, CoolDP™, CoolGaN™, COOLIR™, CoolMOS™, CoolSiC™, DAVE™, DI-POL™, DirectFET™, DrBlade™, EasyPIM™, EconoBRIDGE™, EconoPUAL™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, GaNpowiR™, HEXFET™, HITFET™, HybridPACK™, iMOTION™, IRAM™, ISOFACE™, IsoPACK™, LEDrivIR™, LITIX™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OPTIGA™, OptiMOS™, ORIGA™, PowiRaudio™, PowiRstage™, PrimePACK™, PrimeSTACK™, PROFET™, PRO-SIL™, RASIC™, REAL3™, SmartLEWIS™, SOLID FLASH™, SPOC™, StrongIRFET™, SupIRBuck™, TEMPFET™, TRENCHSTOP™, TriCore™, UHVIC™, XHP™, XMC™

Trademarks updated November 2015

#### Other Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition <2017-06-12> Published by Infineon Technologies AG 81726 Munich, Germany

© 2017 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference **Additional Information**

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer"s technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies, Products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.