## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## PSoC 4000S ファミリ

PSoC® 4 アーキテクチャ

テクニカル リファレンス マニュアル (TRM)

文書番号 : 002-15788 Rev. \*A

January 24, 2020

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

[www.cypress.com](http://www.cypress.com)

## Copyrights

© Cypress Semiconductor Corporation, 2015-2020. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリーコード形式で外部エンドユーザーに配布すること、並びに (2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属のライセンス（サブライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに關しても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参考目的のためのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapsSense, EZ-USB, F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、cypress.com を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。

# 概要

|                                          |            |

|------------------------------------------|------------|

| <b>Section A: 概要</b>                     | <b>10</b>  |

| 1. はじめに .....                            | 11         |

| 2. 開発サポート .....                          | 16         |

| 3. 文書の構成 .....                           | 17         |

| <b>Section B: CPUシステム</b>                | <b>21</b>  |

| 4. Cortex-M0+ CPU .....                  | 22         |

| 5. 割り込み .....                            | 27         |

| <b>Section C: システムリソース サブシステム (SRSS)</b> | <b>35</b>  |

| 6. I/Oシステム .....                         | 37         |

| 7. クロック供給システム .....                      | 57         |

| 8. 電源と電圧監視 .....                         | 64         |

| 9. チップ動作モード .....                        | 68         |

| 10. 消費電力モード .....                        | 69         |

| 11. ウオッчドッグ タイマー .....                   | 73         |

| 12. リセットシステム .....                       | 78         |

| 13. デバイス セキュリティ .....                    | 81         |

| <b>Section D: デジタルシステム</b>               | <b>83</b>  |

| 14. シリアル通信ブロック (SCB) .....               | 84         |

| 15. タイマー、カウンター、およびパルス幅変調器 .....          | 128        |

| <b>Section E: アナログシステム</b>               | <b>153</b> |

| 16. 低消費電力コンパレータ .....                    | 154        |

| 17. CapSense .....                       | 160        |

| 18. LCDダイレクトドライブ .....                   | 161        |

| <b>Section F: プログラムおよびデバッグ</b>           | <b>174</b> |

| 19. プログラムおよびデバッグ インターフェース .....          | 175        |

| 20. 不揮発性メモリ プログラム .....                  | 182        |

| <b>用語集</b>                               | <b>198</b> |

# 目次

|                                |           |

|--------------------------------|-----------|

| <b>Section A: 概要</b>           | <b>10</b> |

| 改訂履歴 .....                     | 10        |

| <b>1. はじめに</b>                 | <b>11</b> |

| 1.1 トップ レベル アーキテクチャ .....      | 11        |

| 1.2 特長 .....                   | 12        |

| 1.3 CPUシステム .....              | 12        |

| 1.3.1 プロセッサ .....              | 12        |

| 1.3.2 割り込みコントローラー .....        | 13        |

| 1.4 メモリ .....                  | 13        |

| 1.4.1 フラッシュ .....              | 13        |

| 1.4.2 SRAM .....               | 13        |

| 1.5 システムワイド リソース .....         | 13        |

| 1.5.1 クロック システム .....          | 13        |

| 1.5.2 電源システム .....             | 13        |

| 1.5.3 GPIO .....               | 13        |

| 1.6 固定機能デジタル .....             | 13        |

| 1.6.1 タイマー／カウンター／PWMブロック ..... | 13        |

| 1.6.2 シリアル通信ブロック .....         | 13        |

| 1.7 アナログ システム .....            | 14        |

| 1.7.1 低消費電力コンパレータ .....        | 14        |

| 1.8 特殊機能ペリフェラル .....           | 14        |

| 1.8.1 LCDセグメント駆動 .....         | 14        |

| 1.8.2 CapSense .....           | 14        |

| 1.9 プログラムおよびデバッグ .....         | 14        |

| 1.10 デバイス機能の要約 .....           | 14        |

| <b>2. 開発サポート</b>               | <b>16</b> |

| 2.1 サポート .....                 | 16        |

| 2.2 製品アップグレード .....            | 16        |

| 2.3 開発キット .....                | 16        |

| 2.4 アプリケーション ノート .....         | 16        |

| <b>3. 文書の構成</b>                | <b>17</b> |

| 3.1 主要な節 .....                 | 17        |

| 3.2 本書の表記法 .....               | 17        |

| 3.2.1 レジスタの表記法 .....           | 17        |

| 3.2.2 数値の表記法 .....             | 17        |

| 3.2.3 測定単位 .....               | 18        |

| 3.2.4 略語 .....                 | 18        |

| <b>Section B: CPUシステム</b>      | <b>21</b> |

| トップ レベル アーキテクチャ .....          | 21        |

|                                          |           |

|------------------------------------------|-----------|

| <b>4. Cortex-M0+ CPU</b>                 | <b>22</b> |

| 4.1 特長                                   | 22        |

| 4.2 ブロック図                                | 23        |

| 4.3 動作原理                                 | 23        |

| 4.4 アドレス マップ                             | 23        |

| 4.5 レジスタ                                 | 24        |

| 4.6 動作モード                                | 25        |

| 4.7 命令セット                                | 25        |

| 4.7.1 アドレス アライメント                        | 26        |

| 4.7.2 メモリ エンディアン                         | 26        |

| 4.8 Systickタイマー                          | 26        |

| 4.9 デバッグ                                 | 26        |

| <b>5. 割り込み</b>                           | <b>27</b> |

| 5.1 特長                                   | 27        |

| 5.2 動作原理                                 | 27        |

| 5.3 割り込みと例外の動作                           | 28        |

| 5.3.1 割り込み／例外の処理                         | 28        |

| 5.3.2 レベルおよびパルス割り込み                      | 28        |

| 5.3.3 例外ベクタ テーブル                         | 29        |

| 5.4 例外ソース                                | 29        |

| 5.4.1 リセット例外                             | 29        |

| 5.4.2 マスク不可能割り込み (NMI) 例外                | 30        |

| 5.4.3 HardFault例外                        | 30        |

| 5.4.4 スーパバイザ コール (SVCall) 例外             | 30        |

| 5.4.5 PendSV例外                           | 30        |

| 5.4.6 SysTick例外                          | 31        |

| 5.5 割り込みソース                              | 31        |

| 5.6 例外の優先度                               | 31        |

| 5.7 割り込みの有効と無効                           | 32        |

| 5.8 例外状態                                 | 32        |

| 5.8.1 保留中の例外                             | 33        |

| 5.9 例外のスタック使用量                           | 33        |

| 5.10 割り込みと低消費電力モード                       | 33        |

| 5.11 例外の初期化とコンフィギュレーション                  | 34        |

| 5.12 レジスタ                                | 34        |

| 5.13 関連文書                                | 34        |

| <b>Section C: システムリソース サブシステム (SRSS)</b> | <b>35</b> |

| トップ レベル アーキテクチャ                          | 36        |

| <b>6. I/Oシステム</b>                        | <b>37</b> |

| 6.1 特長                                   | 37        |

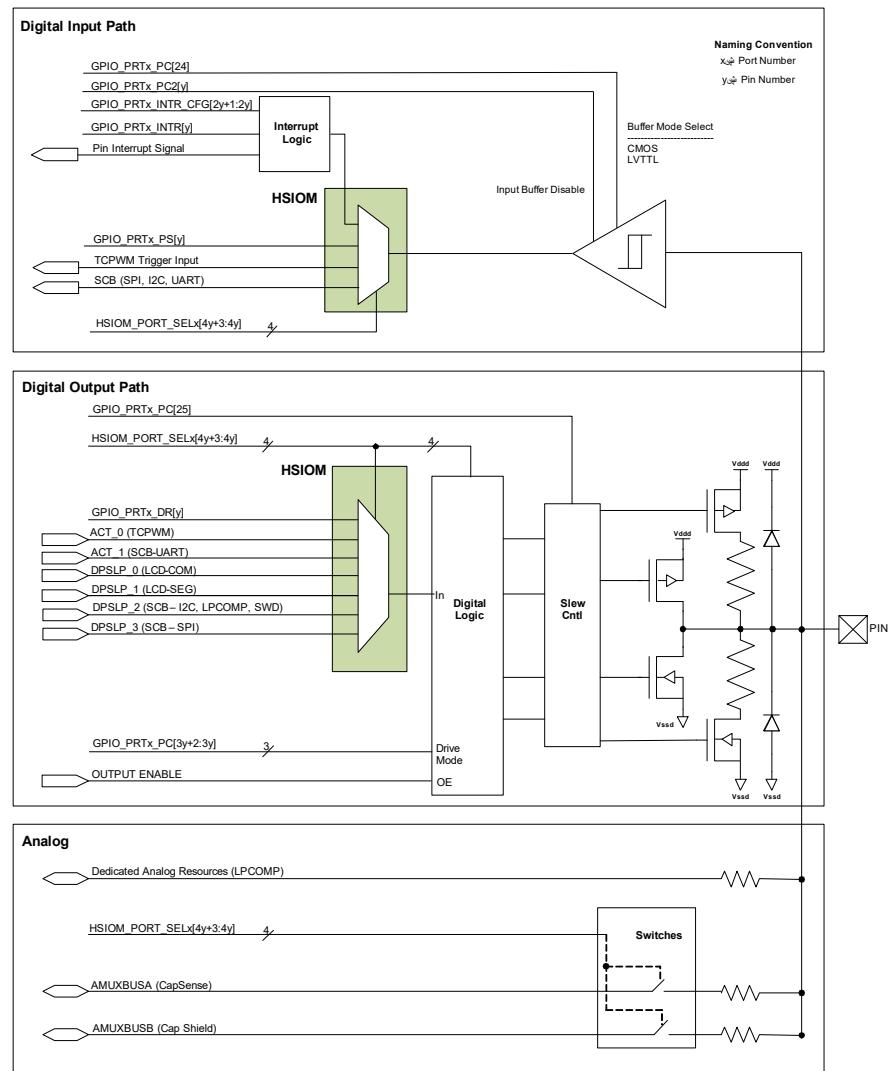

| 6.2 GPIOインターフェースの概要                      | 37        |

| 6.3 I/Oセルのアーキテクチャ                        | 38        |

| 6.3.1 デジタル入力バッファ                         | 40        |

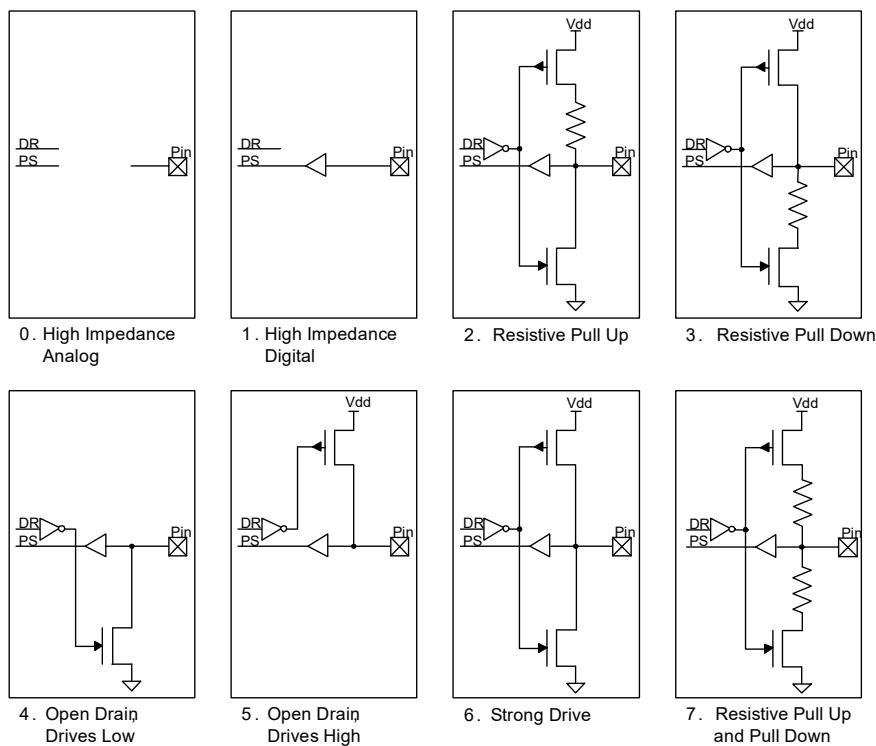

| 6.3.2 デジタル出力ドライバー                        | 40        |

| 6.4 高速I/Oマトリックス                          | 42        |

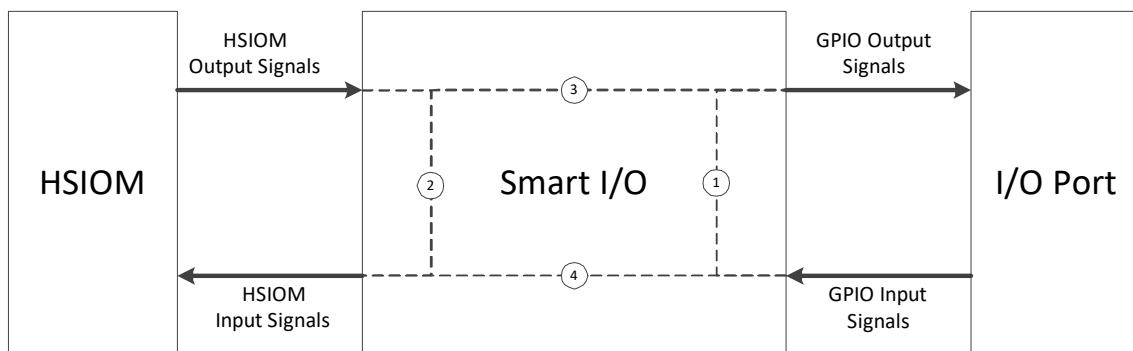

| 6.5 スマートI/O                              | 43        |

| 6.5.1 概要                                 | 43        |

| 6.5.2 ブロック コンポーネント                       | 43        |

| 6.5.3 配線                                 | 51        |

| 6.5.4 動作                                 | 51        |

|            |                                       |           |

|------------|---------------------------------------|-----------|

| 6.6        | 電源投入時のI/O状態 .....                     | 52        |

| 6.7        | 省電力モードでの動作 .....                      | 53        |

| 6.8        | 割り込み .....                            | 53        |

| 6.9        | ペリフェラルの接続 .....                       | 54        |

| 6.9.1      | ファームウェアで制御されるGPIO .....               | 54        |

| 6.9.2      | アナログI/O .....                         | 54        |

| 6.9.3      | LCD駆動 .....                           | 54        |

| 6.9.4      | CapSense .....                        | 55        |

| 6.9.5      | シリアル通信ブロック (SCB) .....                | 55        |

| 6.9.6      | タイマー／カウンター／パルス幅変調器 (TCPWM) ブロック ..... | 55        |

| 6.10       | レジスタ .....                            | 55        |

| <b>7.</b>  | <b>クロック供給システム</b>                     | <b>57</b> |

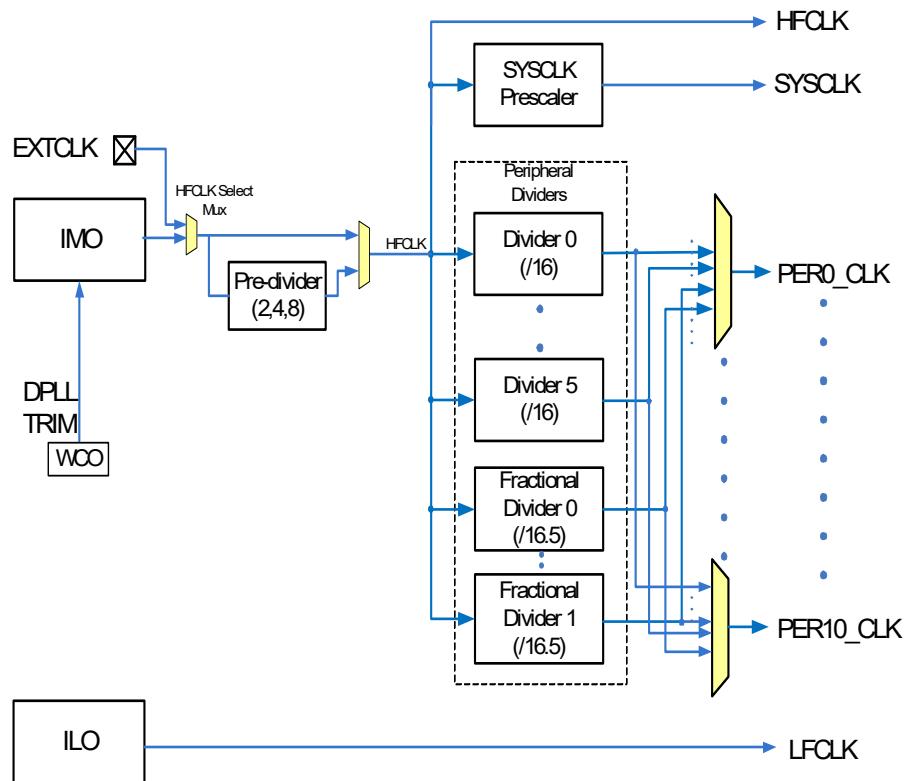

| 7.1        | ブロック図 .....                           | 57        |

| 7.2        | クロックソース .....                         | 58        |

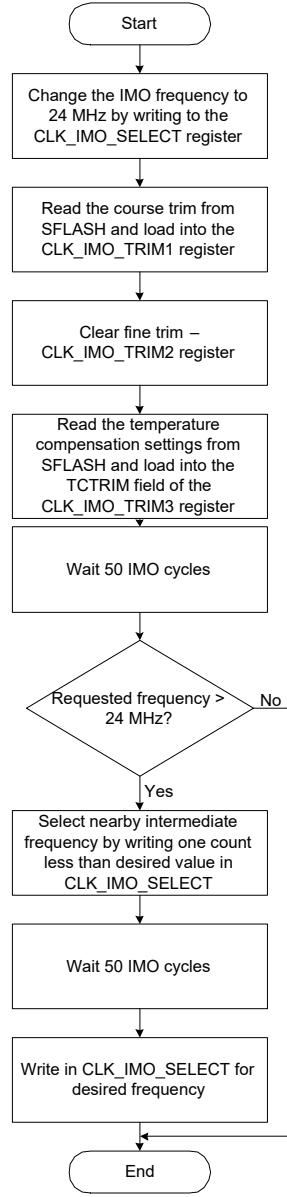

| 7.2.1      | 内部主発振器 (IMO) .....                    | 58        |

| 7.2.2      | 内部低速発振器 (ILO) .....                   | 59        |

| 7.2.3      | 外部クロック (EXTCLK) .....                 | 60        |

| 7.2.4      | 時計用水晶発振器 (WCO) .....                  | 60        |

| 7.3        | クロック分配 .....                          | 60        |

| 7.3.1      | HFCLK入力の選択 .....                      | 60        |

| 7.3.2      | LFCLK入力の選択 .....                      | 61        |

| 7.3.3      | SYSCLKプリスケーラのコンフィギュレーション .....        | 61        |

| 7.3.4      | ペリフェラル クロック分周器のコンフィギュレーション .....      | 61        |

| 7.4        | 低消費電力モード動作 .....                      | 63        |

| 7.5        | レジスター一覧 .....                         | 63        |

| <b>8.</b>  | <b>電源と電圧監視</b>                        | <b>64</b> |

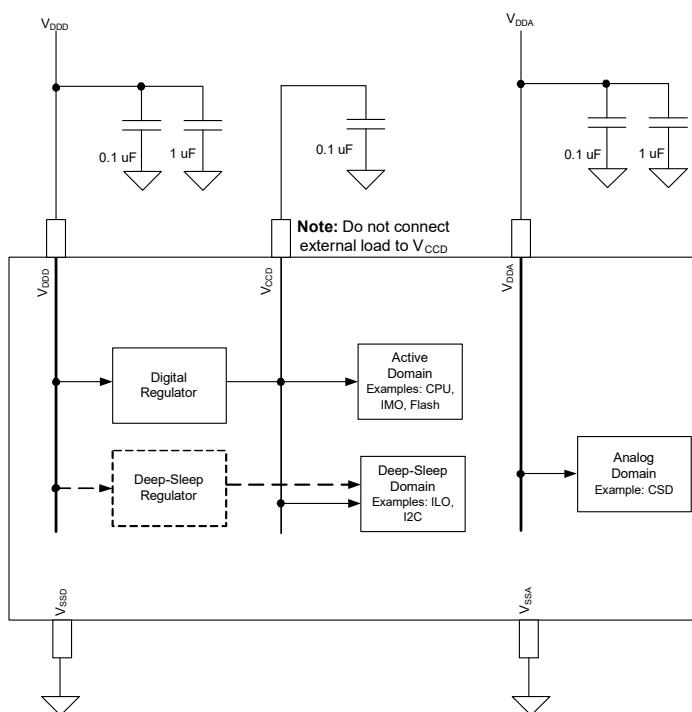

| 8.1        | ブロック図 .....                           | 64        |

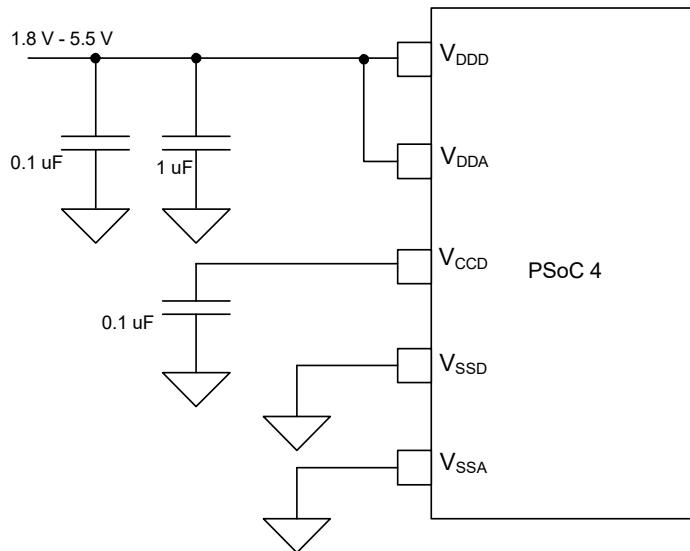

| 8.2        | 電源供給のシナリオ .....                       | 65        |

| 8.2.1      | 単一1.8V～5.5V非安定化電源 .....               | 65        |

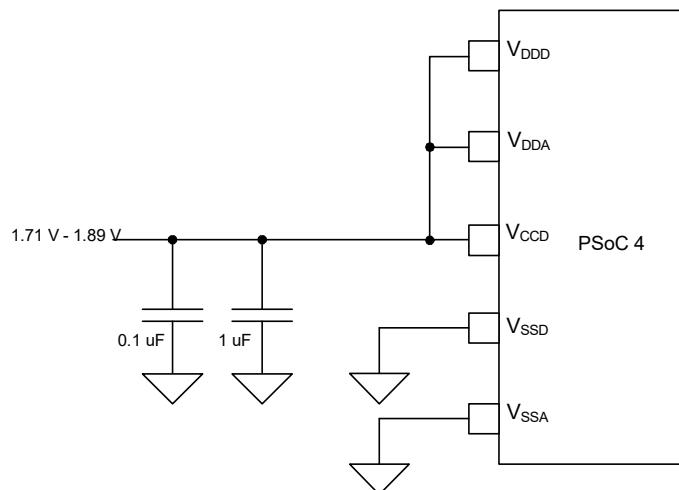

| 8.2.2      | 1.71V～1.89V安定化電源の直接接続 .....           | 65        |

| 8.3        | 動作原理 .....                            | 66        |

| 8.3.1      | レギュレータの概要 .....                       | 66        |

| 8.4        | 電圧監視 .....                            | 66        |

| 8.4.1      | パワーオンリセット (POR) .....                 | 66        |

| 8.5        | レジスター一覧 .....                         | 67        |

| <b>9.</b>  | <b>チップ動作モード</b>                       | <b>68</b> |

| 9.1        | ブート .....                             | 68        |

| 9.2        | ユーザー .....                            | 68        |

| 9.3        | 特権 .....                              | 68        |

| 9.4        | デバッグ .....                            | 68        |

| <b>10.</b> | <b>消費電力モード</b>                        | <b>69</b> |

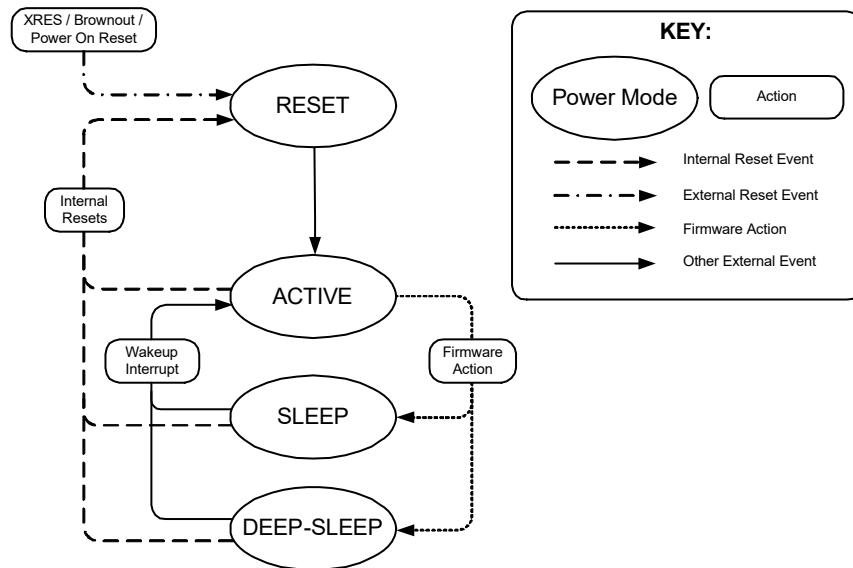

| 10.1       | アクティブ モード .....                       | 70        |

| 10.2       | スリープ モード .....                        | 70        |

| 10.3       | ディープスリープ モード .....                    | 70        |

| 10.4       | 消費電力モードの概要 .....                      | 71        |

| 10.5       | 低消費電力モードへの移行および終了 .....               | 72        |

| 10.6       | レジスター一覧 .....                         | 72        |

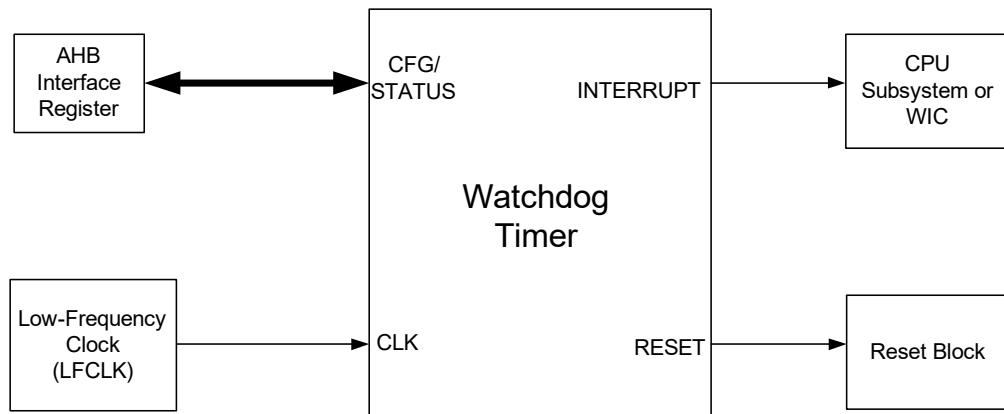

| <b>11.</b> | <b>ウォッチドッグ タイマー</b>                   | <b>73</b> |

| 11.1       | 特長 .....                              | 73        |

|                                       |           |

|---------------------------------------|-----------|

| 11.2 ブロック図 .....                      | 73        |

| 11.3 動作原理 .....                       | 73        |

| 11.3.1 WDTの有効化と無効化 .....              | 74        |

| 11.3.2 WDT割り込みと低消費電力モード .....         | 75        |

| 11.3.3 WDTリセット モード .....              | 75        |

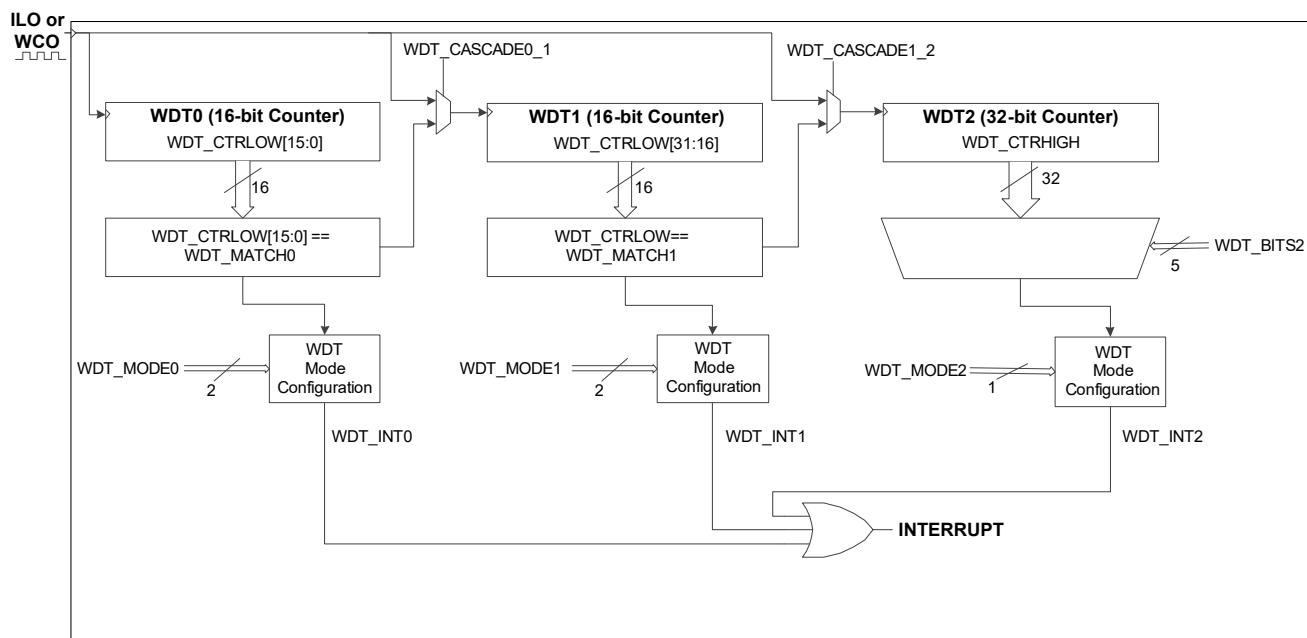

| 11.4 追加タイマー .....                     | 75        |

| 11.4.1 WDT0とWDT1 .....                | 75        |

| 11.4.2 WDT2 .....                     | 76        |

| 11.4.3 カスケード .....                    | 76        |

| 11.5 レジスター一覧 .....                    | 77        |

| <b>12. リセット システム</b>                  | <b>78</b> |

| 12.1 リセット ソース .....                   | 78        |

| 12.1.1 パワーオン リセット .....               | 78        |

| 12.1.2 電圧低下リセット .....                 | 78        |

| 12.1.3 ウオッヂドッグ リセット .....             | 78        |

| 12.1.4 ソフトウェア初期化リセット .....            | 79        |

| 12.1.5 外部リセット .....                   | 79        |

| 12.1.6 保護フォルト リセット .....              | 79        |

| 12.2 リセット ソースの識別 .....                | 79        |

| 12.3 レジスター一覧 .....                    | 80        |

| <b>13. デバイス セキュリティ</b>                | <b>81</b> |

| 13.1 特長 .....                         | 81        |

| 13.2 動作原理 .....                       | 81        |

| 13.2.1 デバイス セキュリティ .....              | 81        |

| 13.2.2 フラッシュ セキュリティ .....             | 82        |

| <b>Section D: デジタル システム</b>           | <b>83</b> |

| トップ レベル アーキテクチャ .....                 | 83        |

| <b>14. シリアル通信ブロック (SCB)</b>           | <b>84</b> |

| 14.1 特長 .....                         | 84        |

| 14.2 シリアル ペリフェラル インターフェース (SPI) ..... | 84        |

| 14.2.1 特長 .....                       | 84        |

| 14.2.2 概要 .....                       | 85        |

| 14.2.3 SPI動作モード .....                 | 86        |

| 14.2.4 スレーブへのクロック供給用のSPIマスターの使用 ..... | 91        |

| 14.2.5 イージーSPIプロトコル .....             | 91        |

| 14.2.6 SPIレジスタ .....                  | 93        |

| 14.2.7 SPI割り込み .....                  | 94        |

| 14.2.8 SPIの有効化と初期化 .....              | 94        |

| 14.2.9 内部と外部クロック供給SPI動作 .....         | 96        |

| 14.3 UART .....                       | 98        |

| 14.3.1 特長 .....                       | 98        |

| 14.3.2 概要 .....                       | 99        |

| 14.3.3 UARTの動作モード .....               | 99        |

| 14.3.4 UARTレジスタ .....                 | 107       |

| 14.3.5 UART割り込み .....                 | 107       |

| 14.3.6 UARTの有効化と初期化 .....             | 108       |

| 14.4 インター インテグレーテッド回路 (I2C) .....     | 110       |

| 14.4.1 特長 .....                       | 110       |

| 14.4.2 概要 .....                       | 110       |

| 14.4.3 用語および定義 .....                  | 111       |

|                   |                                  |            |

|-------------------|----------------------------------|------------|

| 14.4.4            | I2C動作モード .....                   | 111        |

| 14.4.5            | イージーI2C (EZI2C) プロトコル.....       | 113        |

| 14.4.6            | I2Cレジスタ .....                    | 114        |

| 14.4.7            | I2C割り込み .....                    | 116        |

| 14.4.8            | I2Cの有効化および初期化 .....              | 116        |

| 14.4.9            | I2Cにおける内部および外部クロック動作 .....       | 117        |

| 14.4.10           | スリープから復帰 .....                   | 119        |

| 14.4.11           | マスター モード転送の例 .....               | 120        |

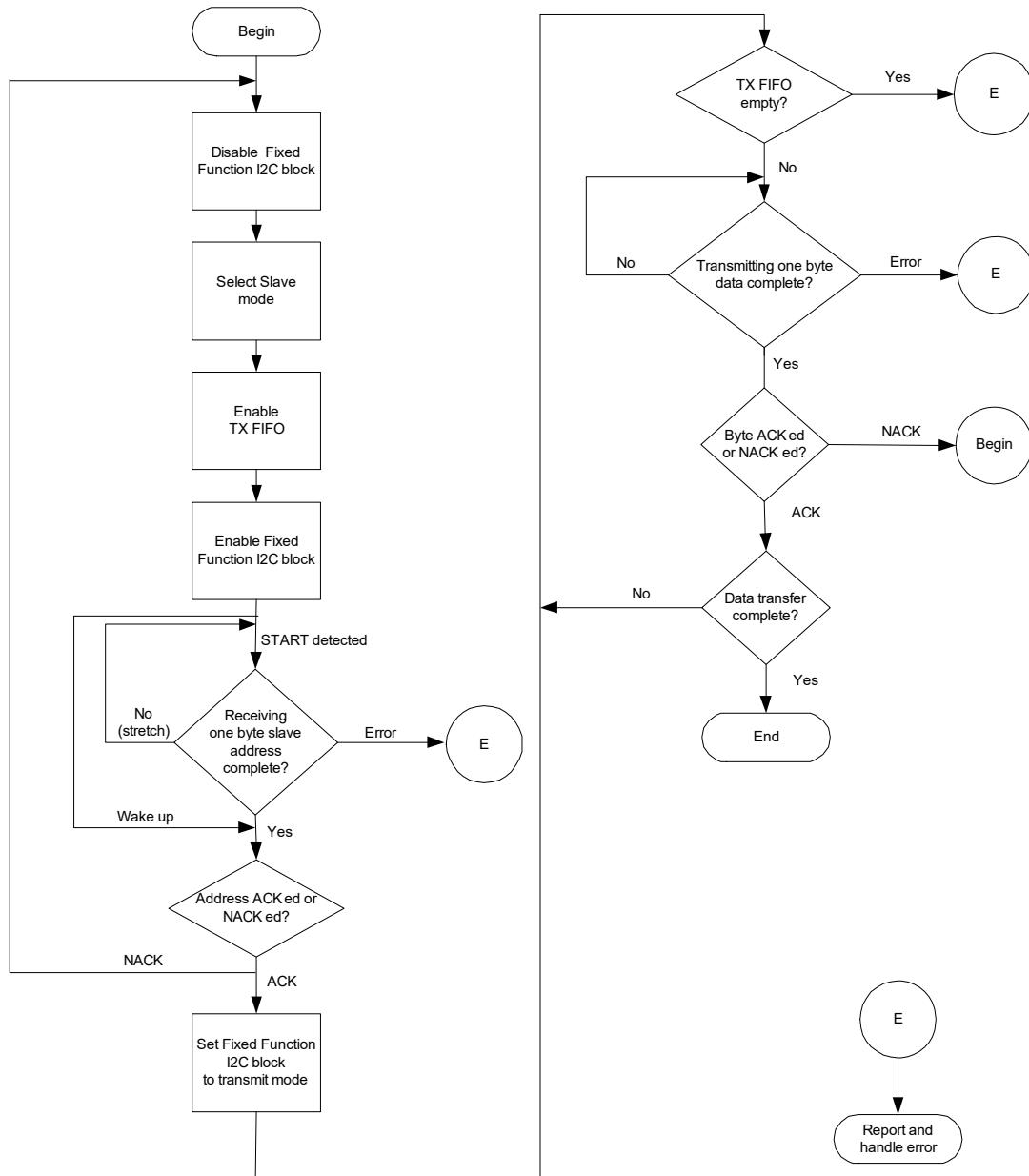

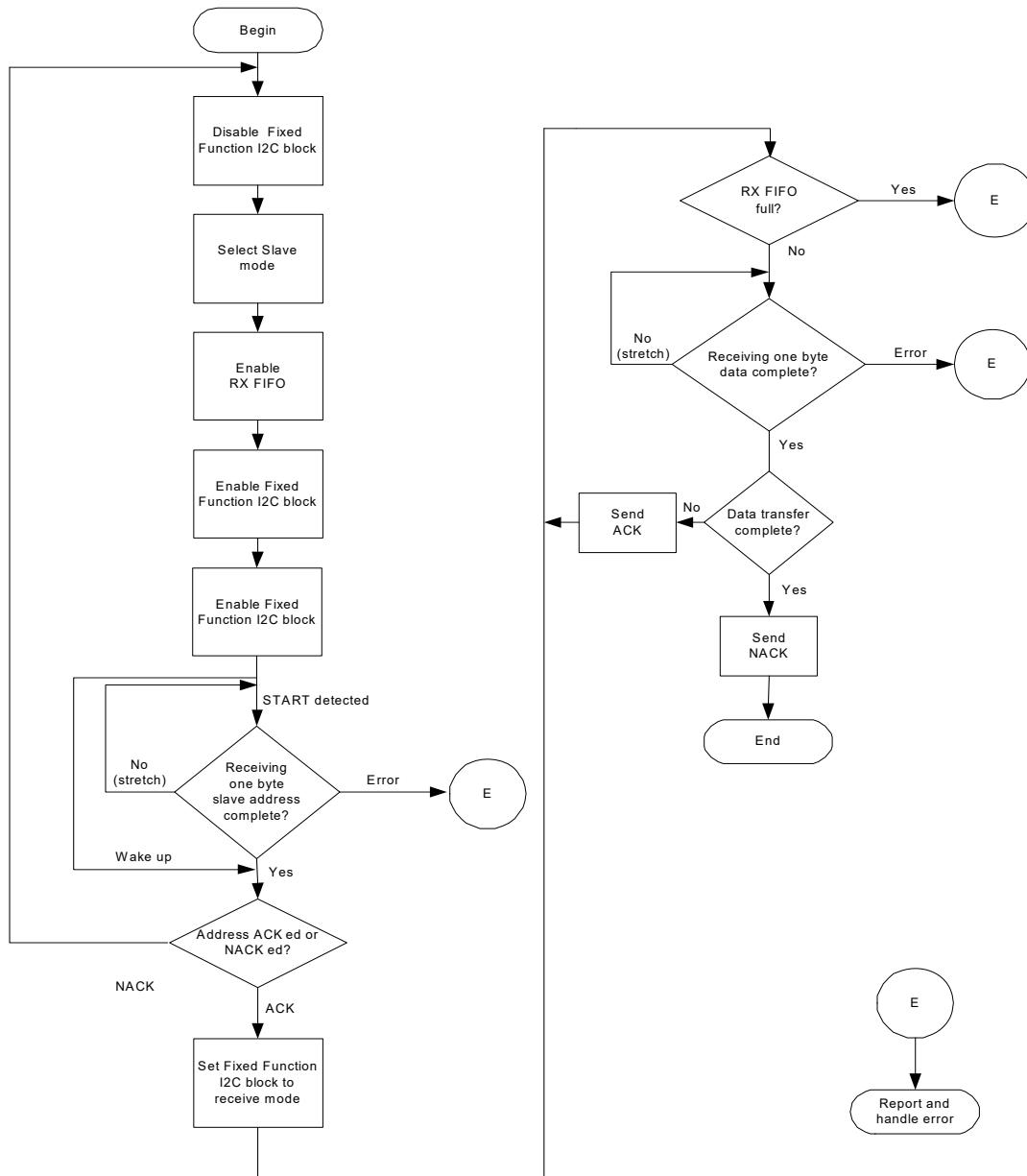

| 14.4.12           | スレーブ モード転送の例 .....               | 122        |

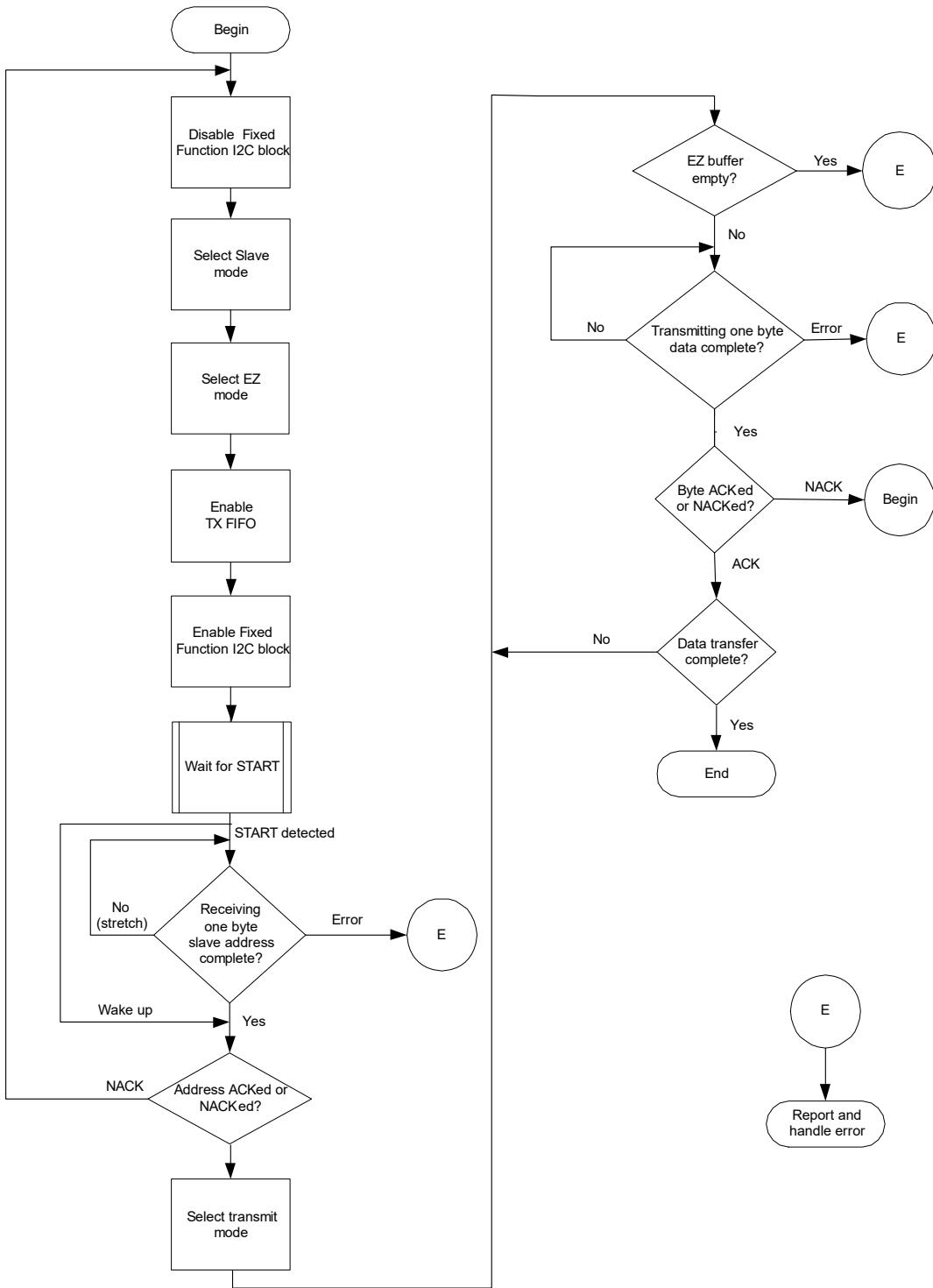

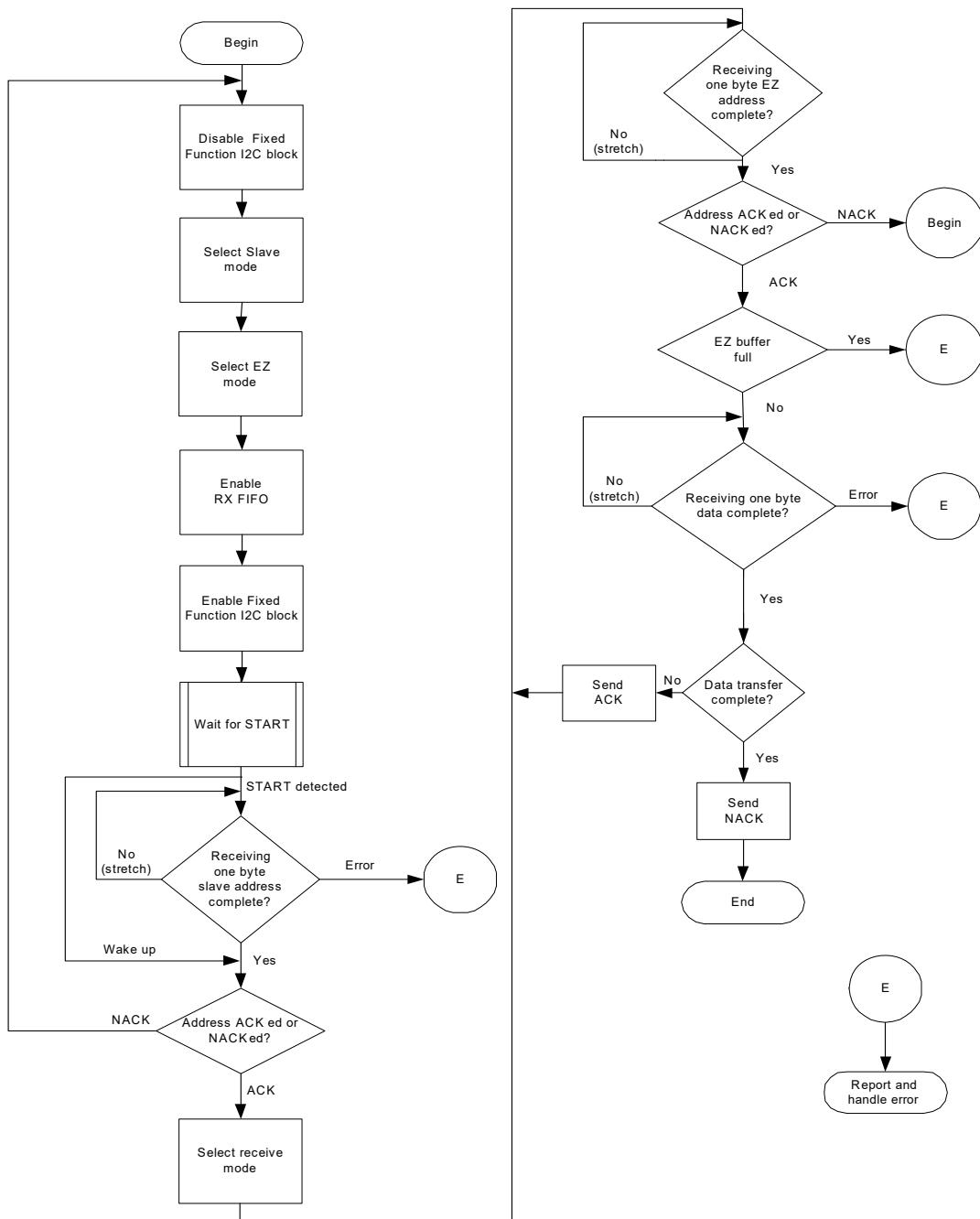

| 14.4.13           | EZスレーブ モード転送の例 .....             | 124        |

| 14.4.14           | マルチマスター モード転送の例 .....            | 126        |

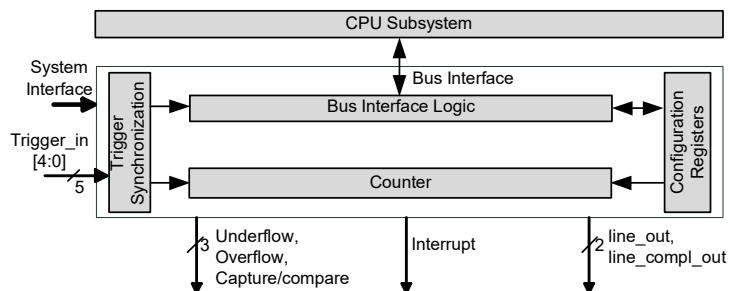

| <b>15.</b>        | <b>タイマー、カウンター、およびパルス幅変調器</b>     | <b>128</b> |

| 15.1              | 特長 .....                         | 128        |

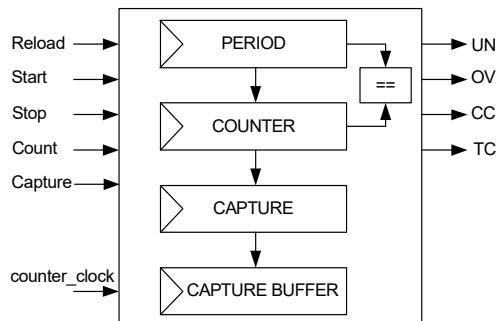

| 15.2              | ブロック図 .....                      | 129        |

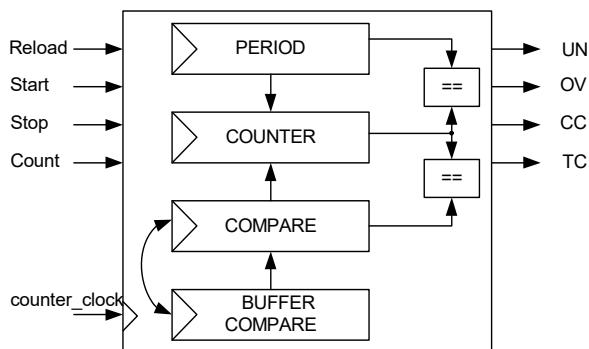

| 15.2.1            | TCPWMブロックにおけるカウンターの有効／無効 .....   | 129        |

| 15.2.2            | クロッキング .....                     | 129        |

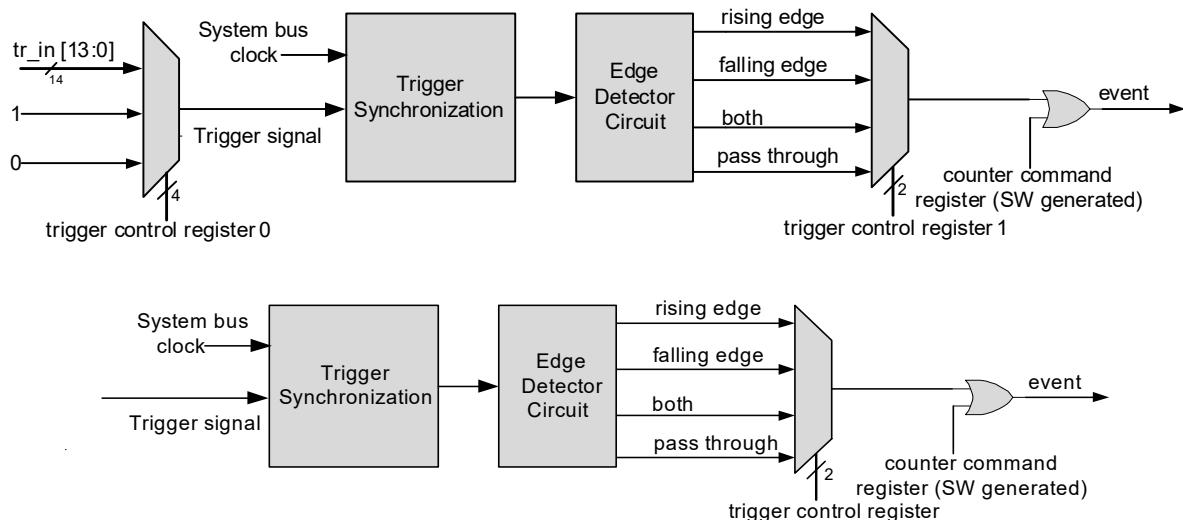

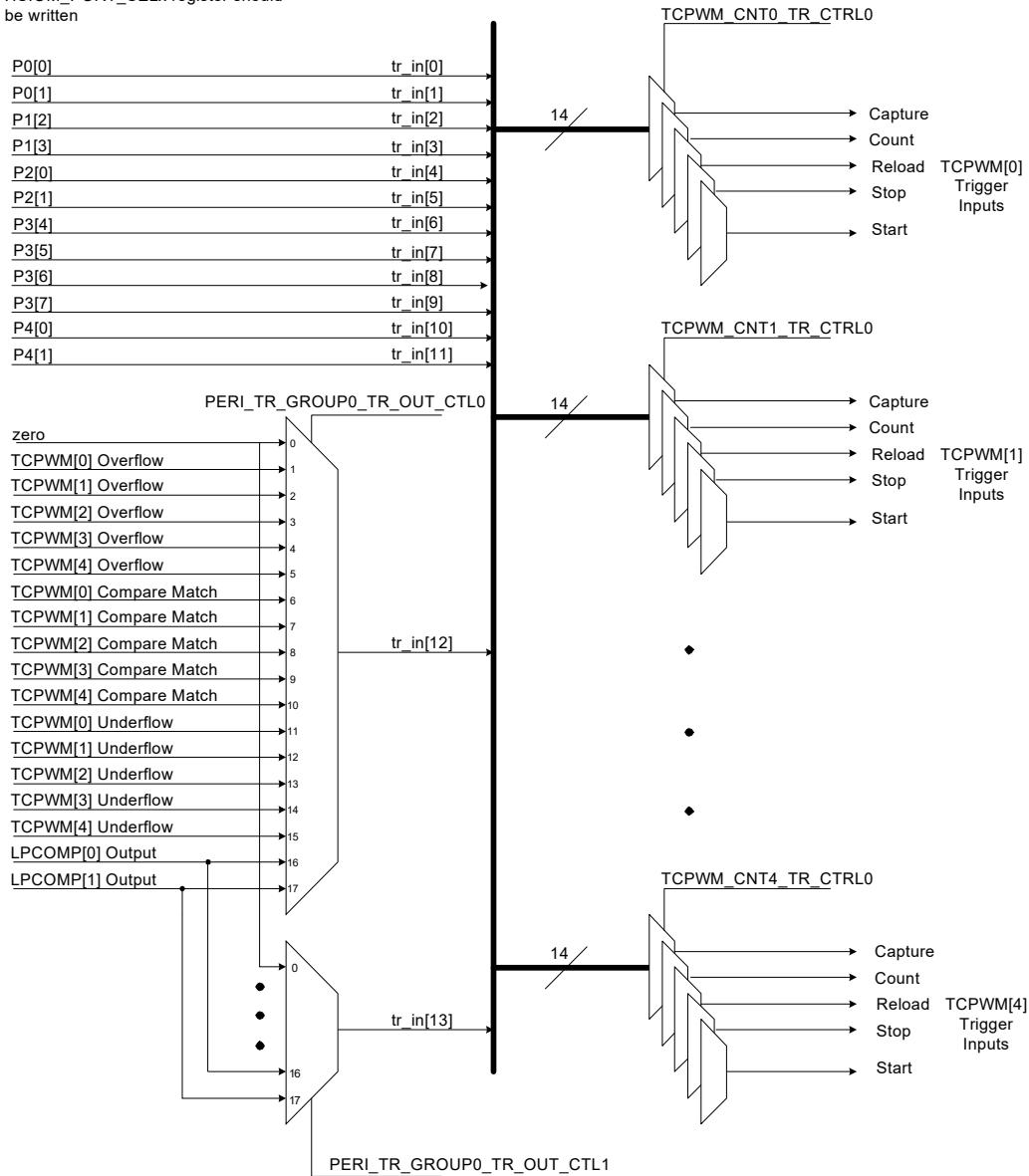

| 15.2.3            | トリガー入力に基づいたイベント .....            | 130        |

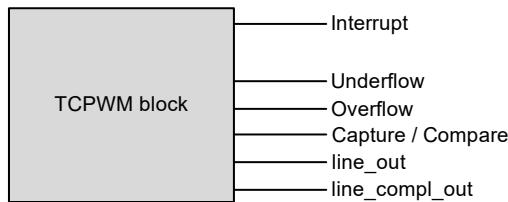

| 15.2.4            | 出力信号 .....                       | 132        |

| 15.2.5            | 電力モード .....                      | 134        |

| 15.3              | 動作モード .....                      | 134        |

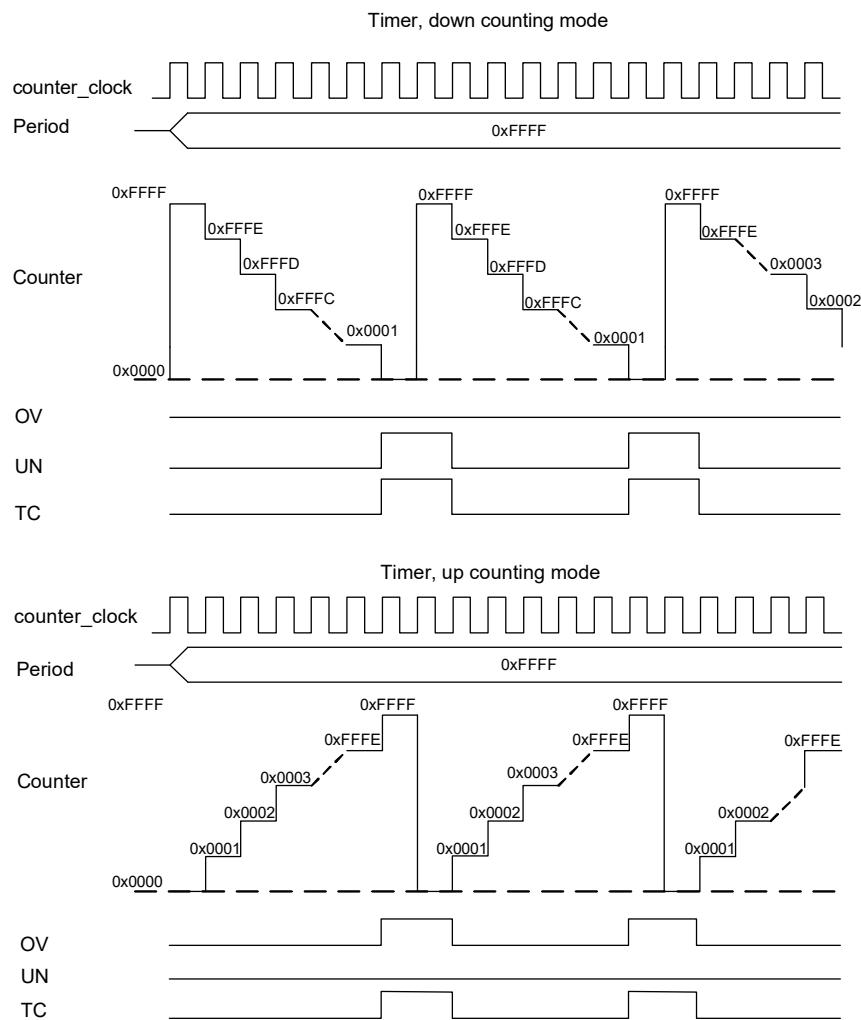

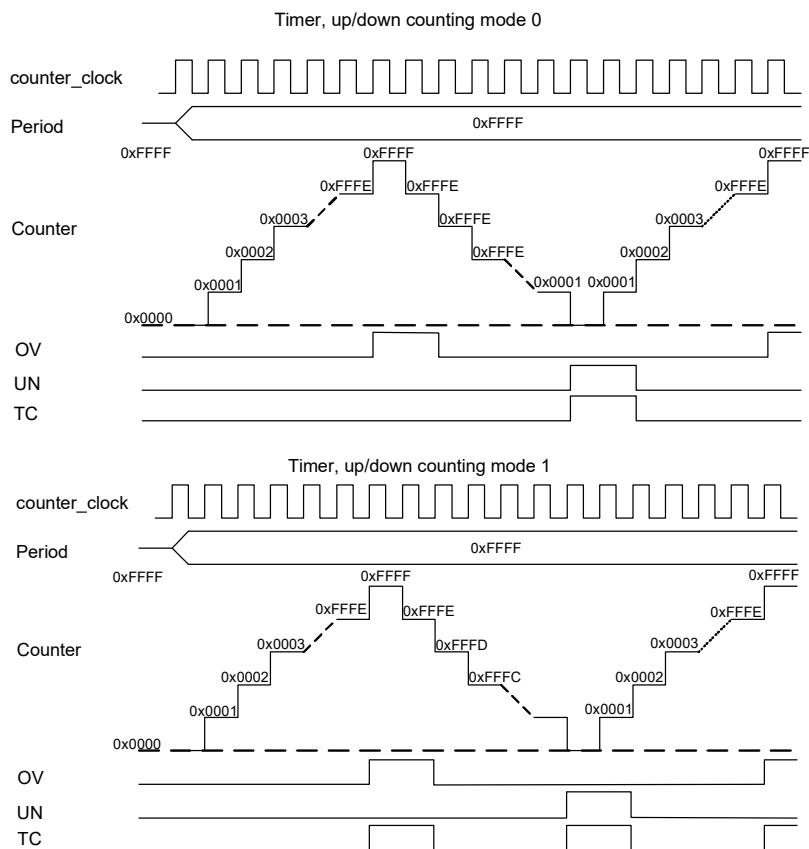

| 15.3.1            | タイマー モード .....                   | 135        |

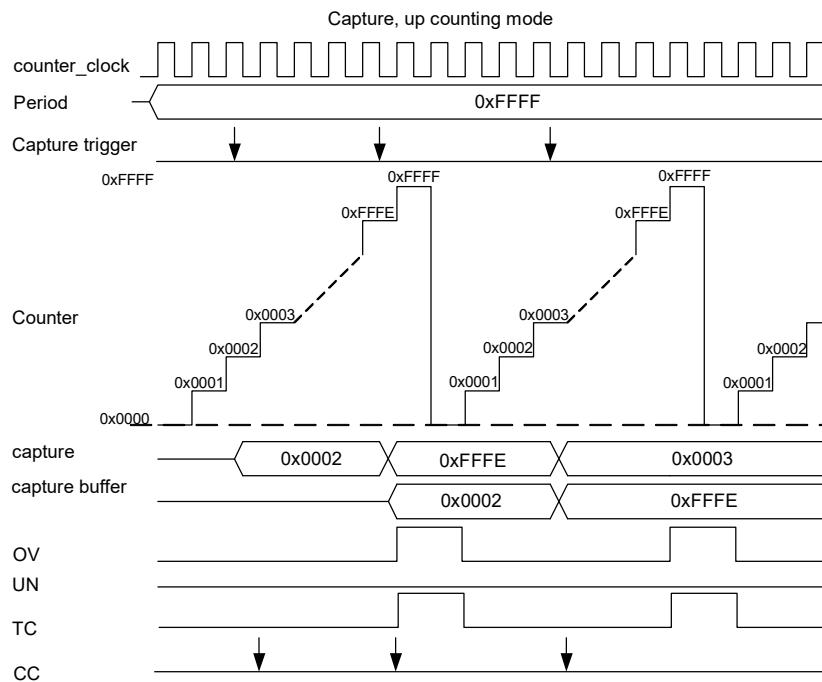

| 15.3.2            | キャプチャ モード .....                  | 138        |

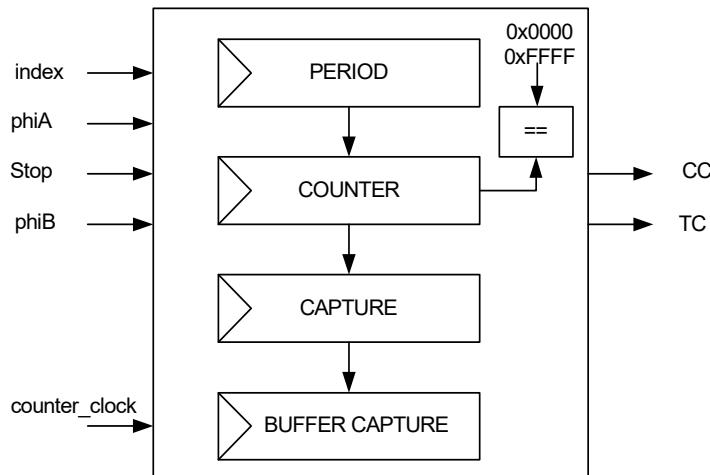

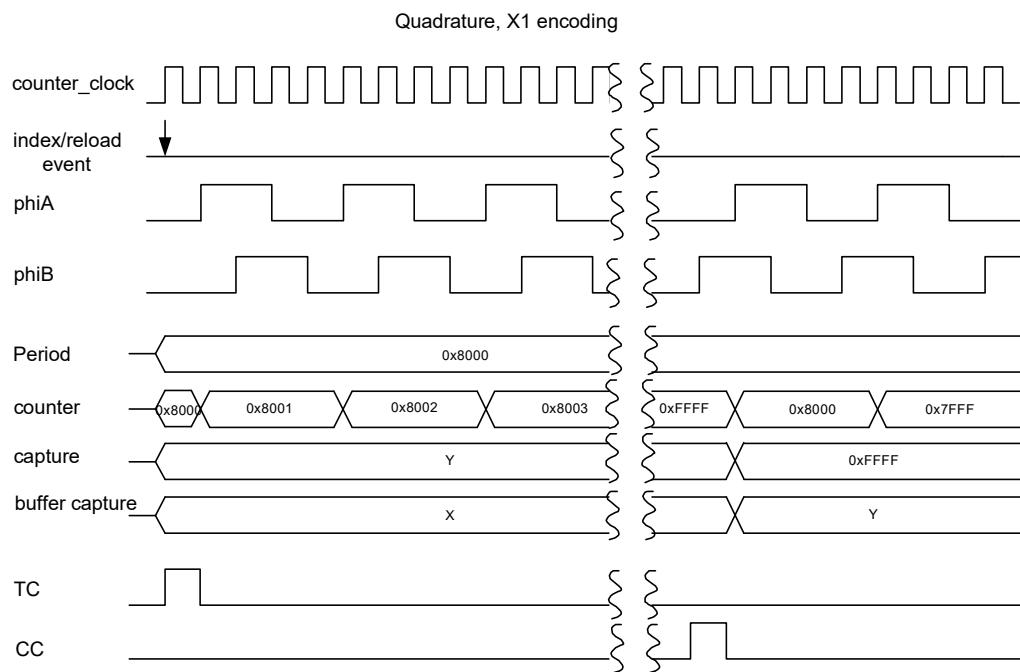

| 15.3.3            | 直交デコーダー モード .....                | 141        |

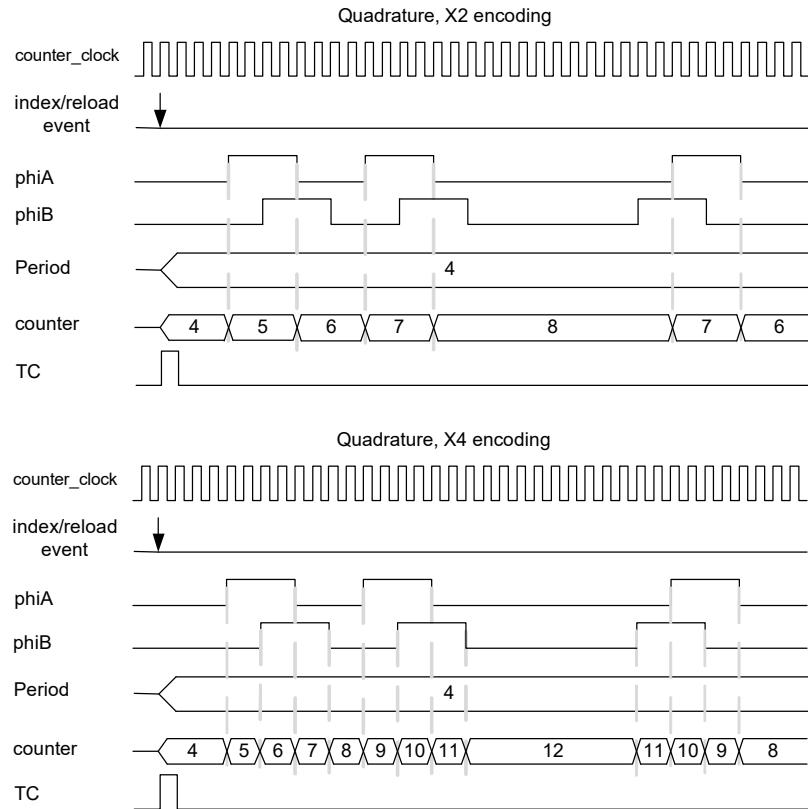

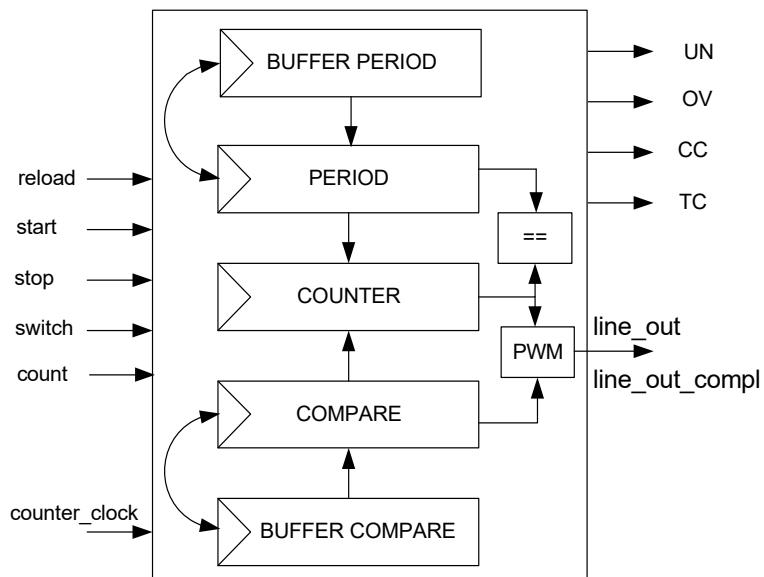

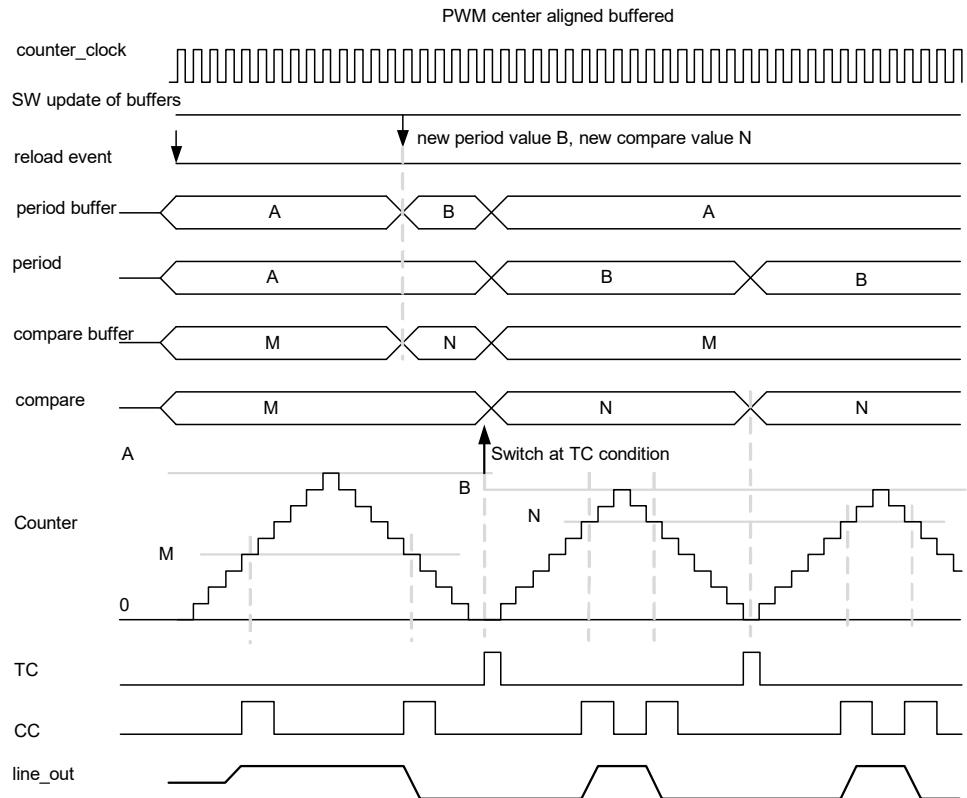

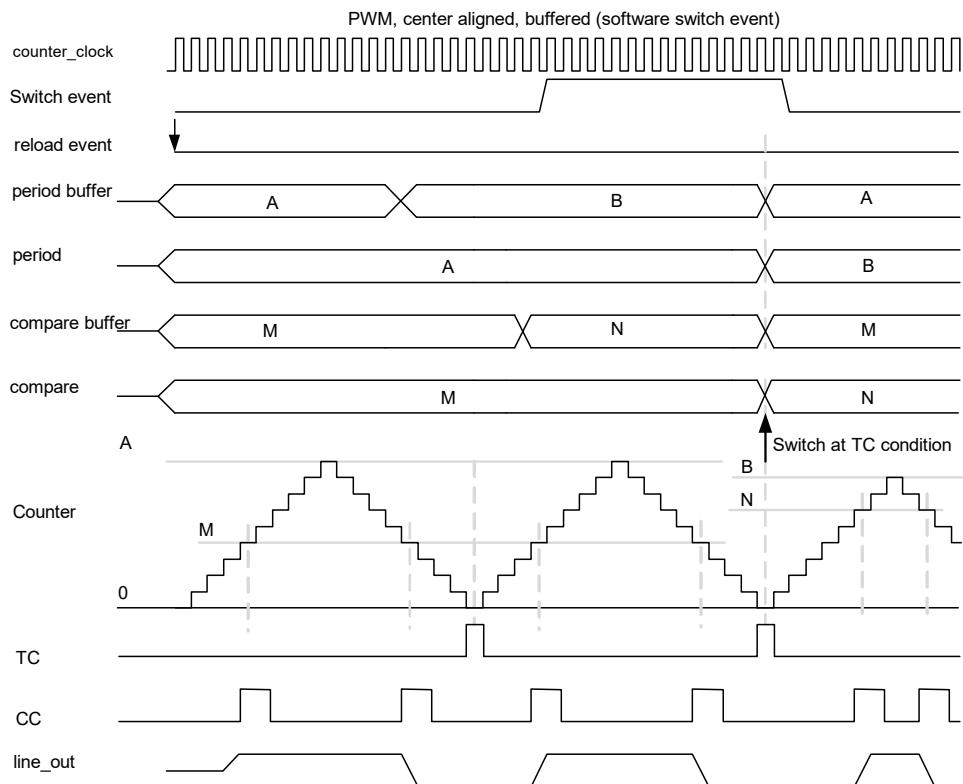

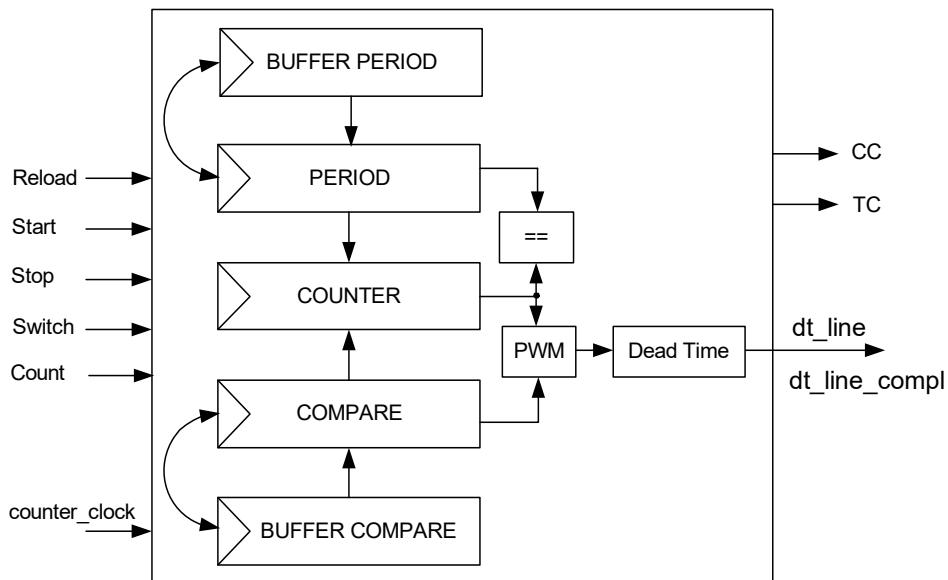

| 15.3.4            | パルス幅変調モード .....                  | 144        |

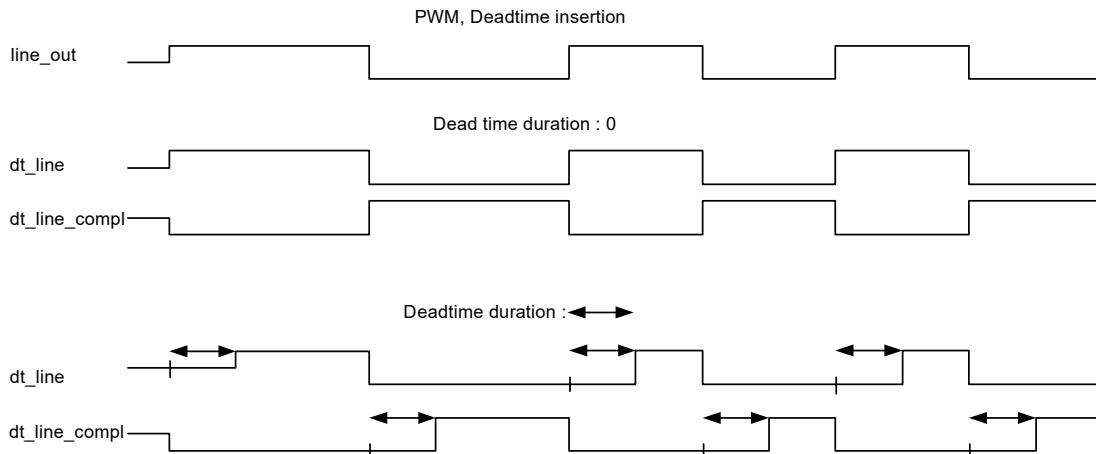

| 15.3.5            | デッドタイム付きパルス幅変調モード .....          | 148        |

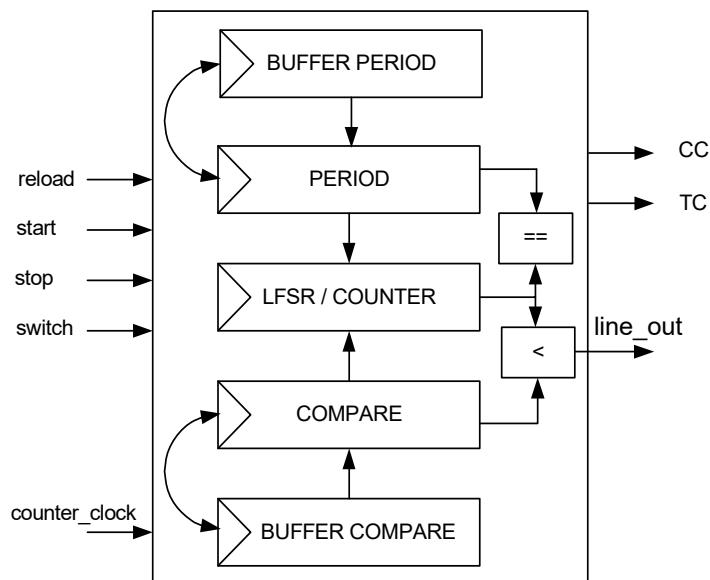

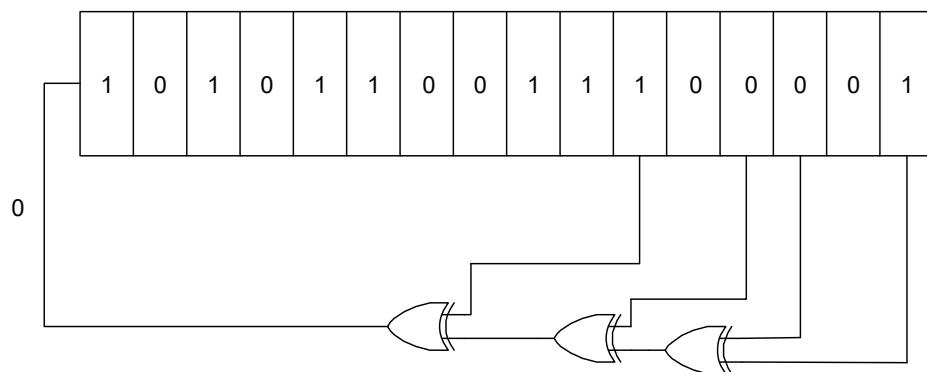

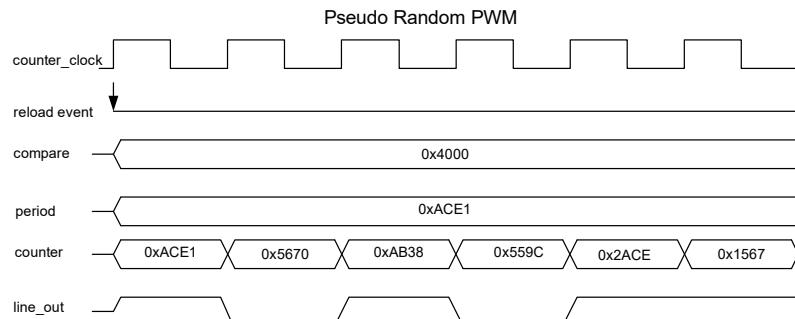

| 15.3.6            | 疑似乱数パルス幅変調モード .....              | 150        |

| 15.4              | TCPWMレジスタ .....                  | 152        |

| <b>Section E:</b> | <b>アナログ システム</b>                 | <b>153</b> |

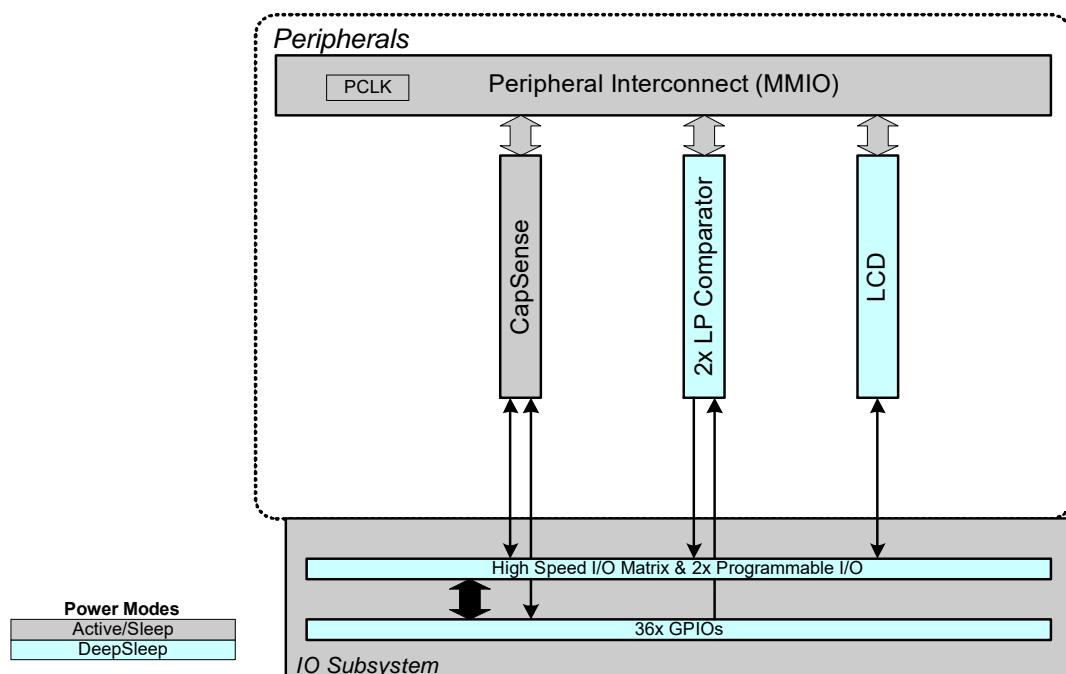

|                   | トップ レベル アーキテクチャ .....            | 153        |

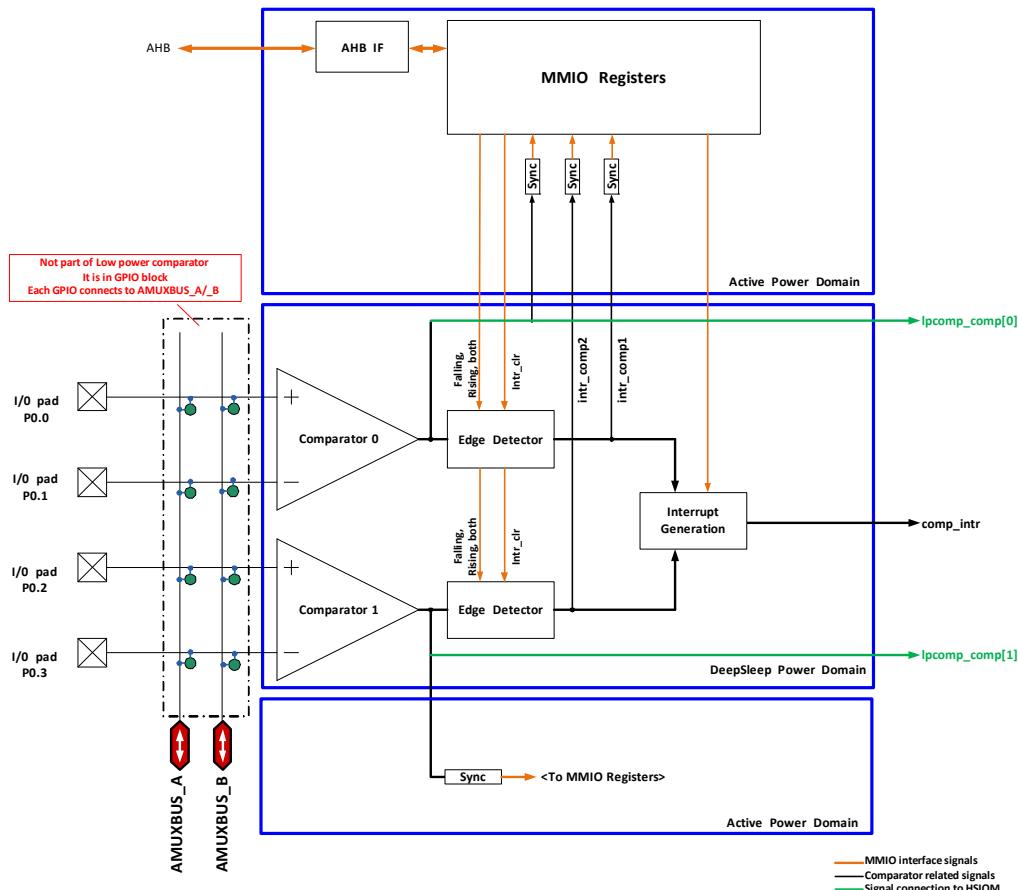

| <b>16.</b>        | <b>低消費電力コンパレータ</b>               | <b>154</b> |

| 16.1              | 特長 .....                         | 154        |

| 16.2              | ブロック図 .....                      | 154        |

| 16.3              | 動作原理 .....                       | 155        |

| 16.3.1            | 入力コンフィギュレーション .....              | 155        |

| 16.3.2            | 出力および割り込みコンフィギュレーション .....       | 156        |

| 16.3.3            | 消費電力モードおよび動作速度のコンフィギュレーション ..... | 157        |

| 16.3.4            | ヒステリシス .....                     | 157        |

| 16.3.5            | 低消費電力モードからの復帰 .....              | 158        |

| 16.3.6            | コンパレーター クロック .....               | 158        |

| 16.3.7            | オフセット調整 .....                    | 158        |

| 16.4              | レジスタ要約 .....                     | 159        |

| <b>17.</b>        | <b>CapSense</b>                  | <b>160</b> |

| <b>18.</b>        | <b>LCDダイレクト ドライブ</b>             | <b>161</b> |

| 18.1              | 特長 .....                         | 161        |

| 18.2              | LCDセグメントドライブの概要 .....            | 161        |

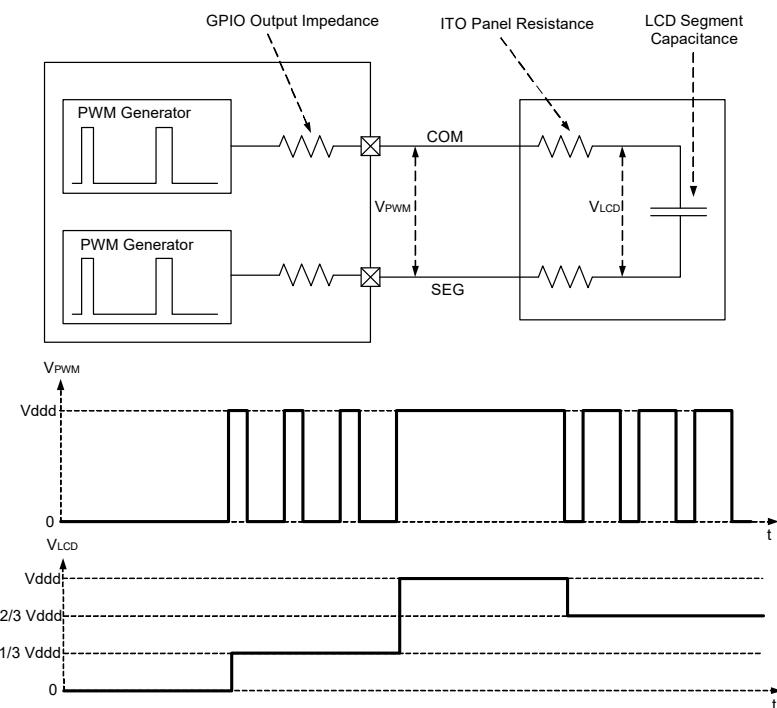

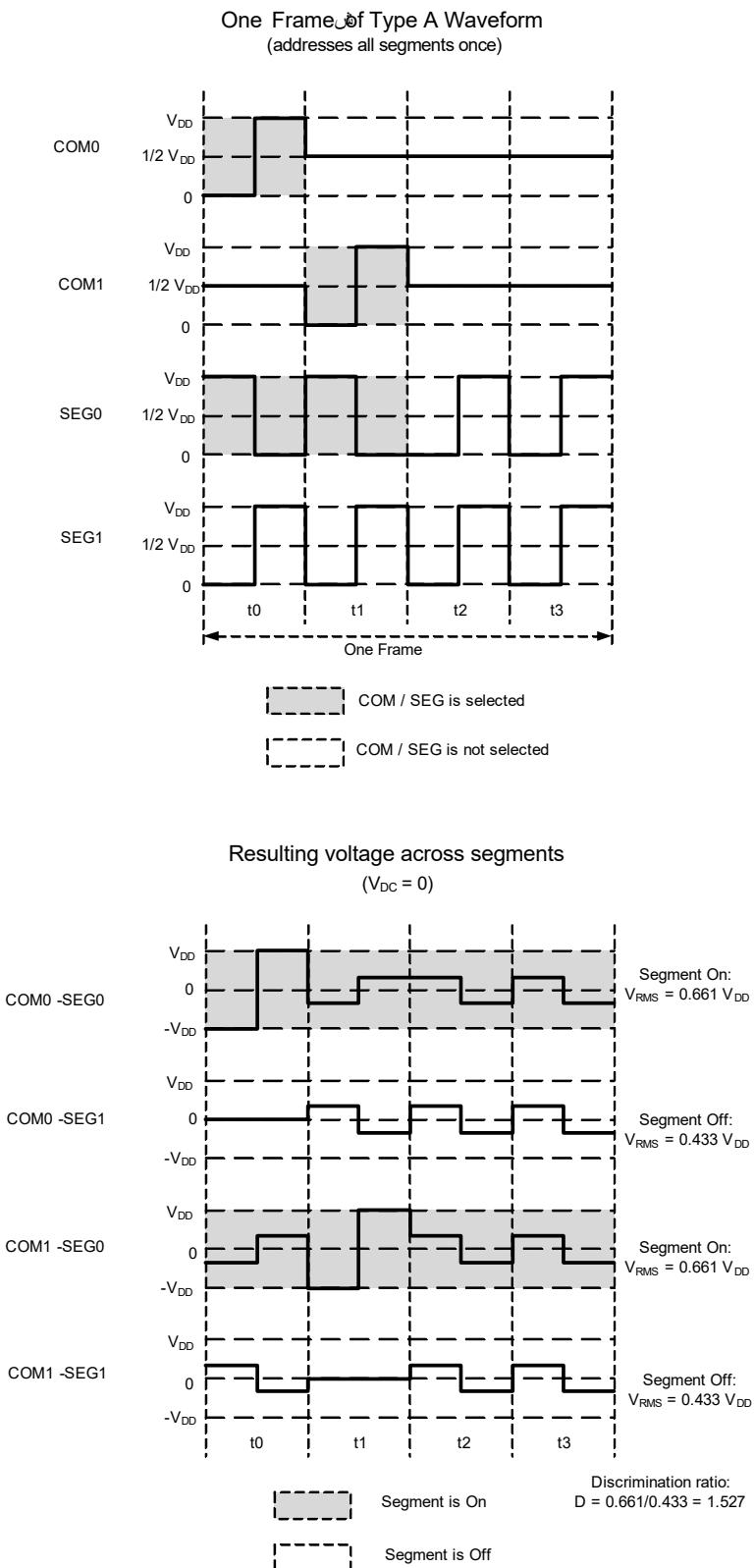

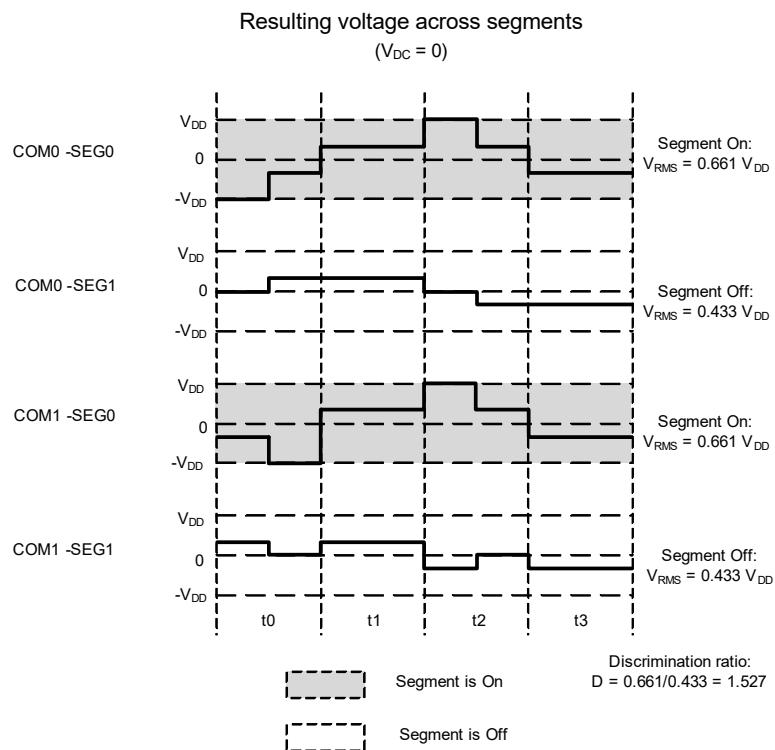

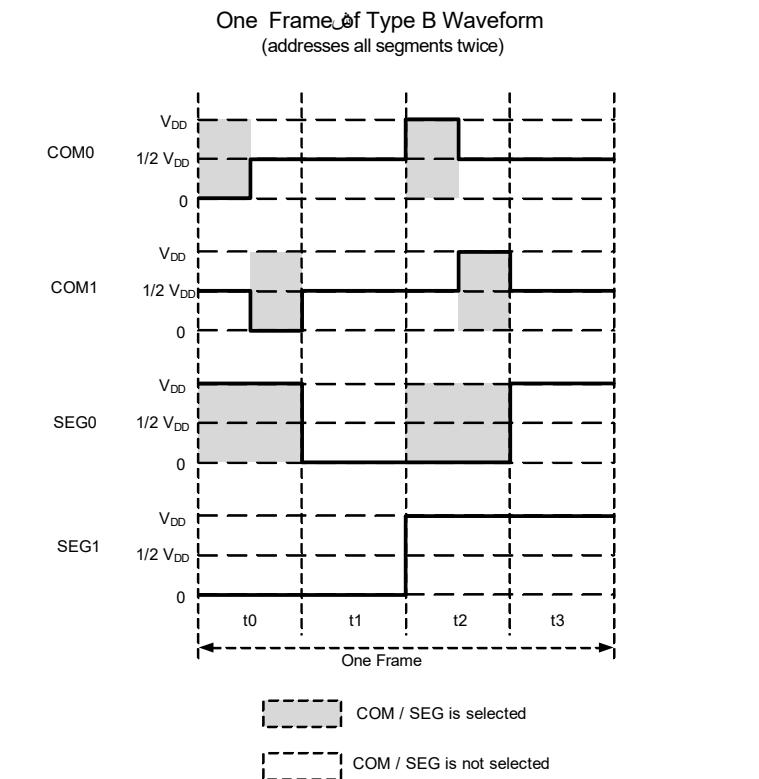

| 18.2.1            | 駆動モード .....                      | 162        |

| 18.2.2            | ドライブ モードの推奨使用方法 .....            | 170        |

| 18.2.3            | デジタル コントラスト制御 .....              | 170        |

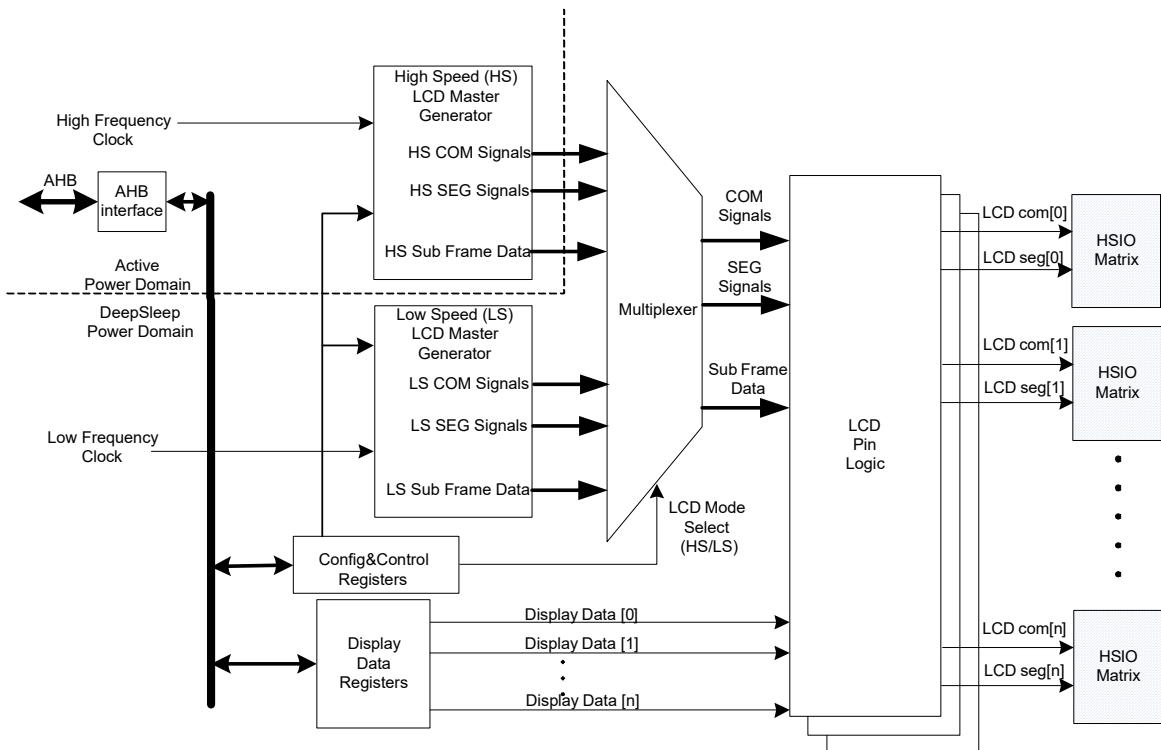

| 18.3              | ブロック図 .....                      | 171        |

|                   |                                      |            |

|-------------------|--------------------------------------|------------|

| 18.3.1            | 動作原理.....                            | 172        |

| 18.3.2            | 高速および低速のマスター信号発生器 .....              | 172        |

| 18.3.3            | マルチプレクサおよびLCDピン回路.....               | 172        |

| 18.3.4            | ディスプレイ データレジスタ.....                  | 172        |

| 18.4              | レジスター一覧 .....                        | 173        |

| <b>Section F:</b> | <b>プログラムおよびデバッグ</b>                  | <b>174</b> |

|                   | トップ レベル アーキテクチャ .....                | 174        |

| <b>19.</b>        | <b>プログラムおよびデバッグ インターフェース</b>         | <b>175</b> |

| 19.1              | 特長.....                              | 175        |

| 19.2              | 機能説明 .....                           | 175        |

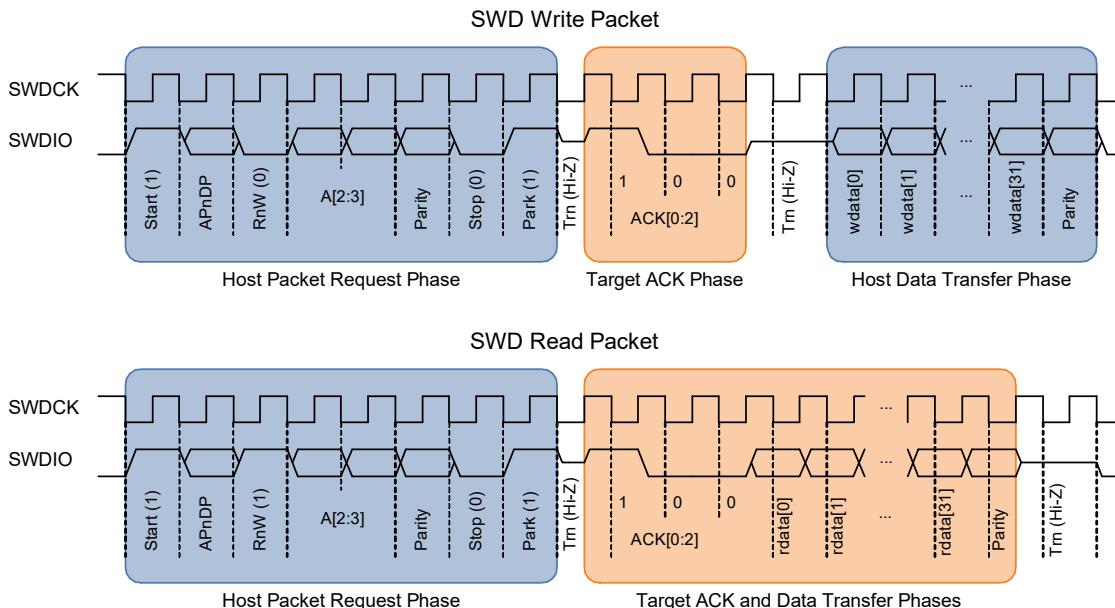

| 19.3              | シリアル ワイヤ デバッグ (SWD) インターフェース.....    | 176        |

| 19.3.1            | SWDタイミングの詳細 .....                    | 177        |

| 19.3.2            | ACK応答の詳細.....                        | 177        |

| 19.3.3            | ターンアラウンド (Trn) 期間の詳細 .....           | 177        |

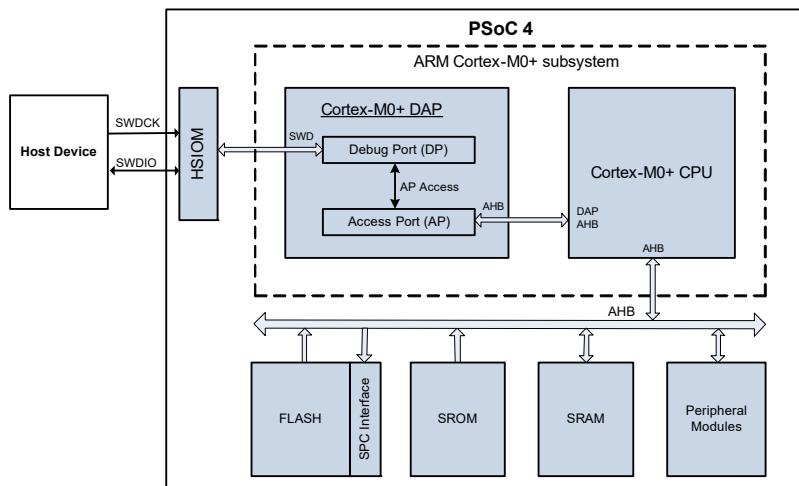

| 19.4              | Cortex-M0+デバッグおよびアクセスポート (DAP) ..... | 178        |

| 19.4.1            | デバッグポート (DP) レジスタ.....               | 178        |

| 19.4.2            | アクセスポート (AP) レジスタ.....               | 178        |

| 19.5              | PSoC 4デバイスのプログラム .....               | 179        |

| 19.5.1            | SWDポートの開通.....                       | 179        |

| 19.5.2            | SWDプログラム モードへの移行 .....               | 179        |

| 19.5.3            | SWDプログラム ルーチンの実施 .....               | 179        |

| 19.6              | PSoC 4 SWDデバッグ インターフェース .....        | 180        |

| 19.6.1            | デバッグ制御およびコンフィギュレーション レジスタ.....       | 180        |

| 19.6.2            | ブレークポイント ユニット (BPU) .....            | 180        |

| 19.6.3            | データ オッチャポイント (DWT) .....             | 180        |

| 19.6.4            | PSoC 4デバイスのデバッグ .....                | 181        |

| 19.7              | レジスタ .....                           | 181        |

| <b>20.</b>        | <b>不揮発性メモリ プログラム</b>                 | <b>182</b> |

| 20.1              | 特長.....                              | 182        |

| 20.2              | 機能説明 .....                           | 182        |

| 20.3              | システム コールの搭載 .....                    | 183        |

| 20.4              | ブロッキングと非ブロッキングのシステム コール .....        | 183        |

| 20.4.1            | システム コールの実行 .....                    | 183        |

| 20.5              | システム コール .....                       | 184        |

| 20.5.1            | シリコンID .....                         | 185        |

| 20.5.2            | クロックの設定 .....                        | 185        |

| 20.5.3            | ロード フラッシュ バイト .....                  | 186        |

| 20.5.4            | 列書き込み .....                          | 187        |

| 20.5.5            | 列プログラム .....                         | 188        |

| 20.5.6            | 全消去 .....                            | 189        |

| 20.5.7            | チェックサム .....                         | 190        |

| 20.5.8            | 書き込み保護 .....                         | 191        |

| 20.5.9            | 非ブロッキング列書き込み .....                   | 192        |

| 20.5.10           | 非ブロッキング列プログラム .....                  | 193        |

| 20.5.11           | レジューム非ブロッキング .....                   | 194        |

| 20.6              | システム コール ステータス .....                 | 195        |

| 20.7              | 非ブロッキング システム コール疑似コード .....          | 196        |

| <b>用語集</b>        |                                      | <b>198</b> |

# セクション A: 概要

このセクションは次の章を含みます:

- 11 ページのはじめに

- 16 ページの開発サポート

- 17 ページの文書の構成

## 改訂履歴

| 版  | 発行日        | 変更内容                                                     |

|----|------------|----------------------------------------------------------|

| ** | 10/17/2016 | これは英語版 002-10129 Rev. *A を翻訳した日本語版 002-15788 Rev. ** です。 |

| *A | 01/24/2020 | これは英語版 002-10129 Rev. *C を翻訳した日本語版 002-15788 Rev. *A です。 |

# 1. はじめに

PSoC® 4 は Arm® Cortex®-M0+ CPU を備えたプログラマブル組み込みシステム コントローラーです。PSoC 4000S は PSOC 4000 ファミリを改良した製品であり、PSoC 4 のより大きなメンバーと上位互換性があります。

PSoC 4 デバイスには以下の特長があります：

- 高性能、32 ビットのシングル サイクル Cortex-M0+ CPU コア

- 高性能アナログ システム

- 自己および相互静電容量式タッチ センシング (CapSense®)

- コンフィギュレーション可能なタイマー／カウンター／PWM ブロック

- コンフィギュレーション可能な通信ブロック : I<sup>2</sup>C、SPI および UART 動作モード

- 低消費電力動作モード：スリープ およびディープスリープ

本書は PSoC 4000S デバイスの各機能ブロックについて詳しく説明します。この情報は設計者がシステムレベル設計を作成するために役に立ちます。

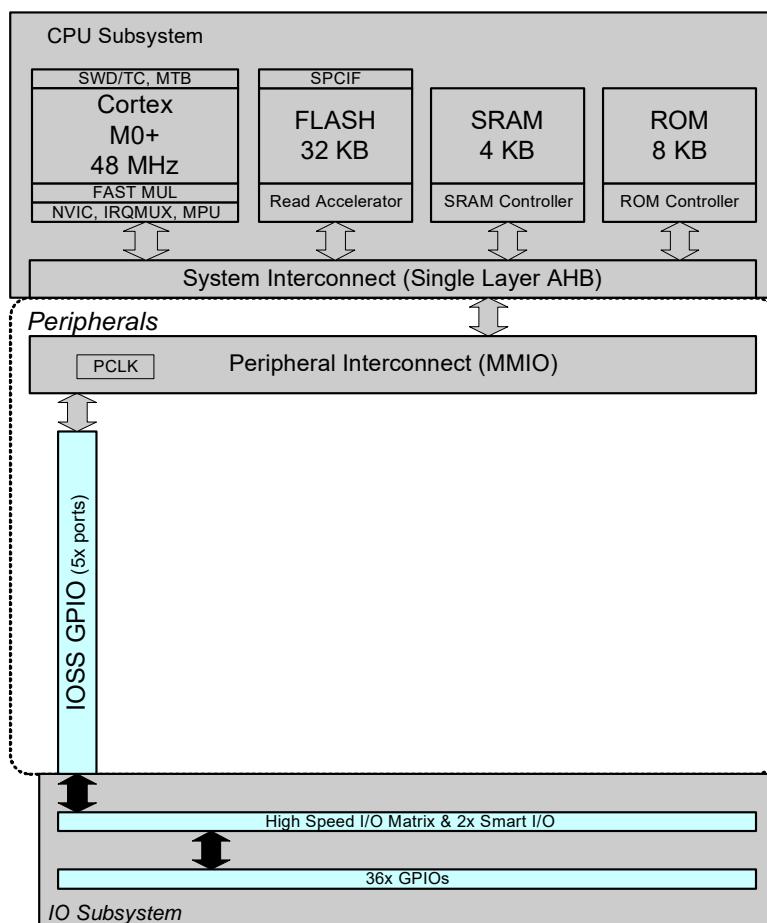

## 1.1 トップ レベル アーキテクチャ

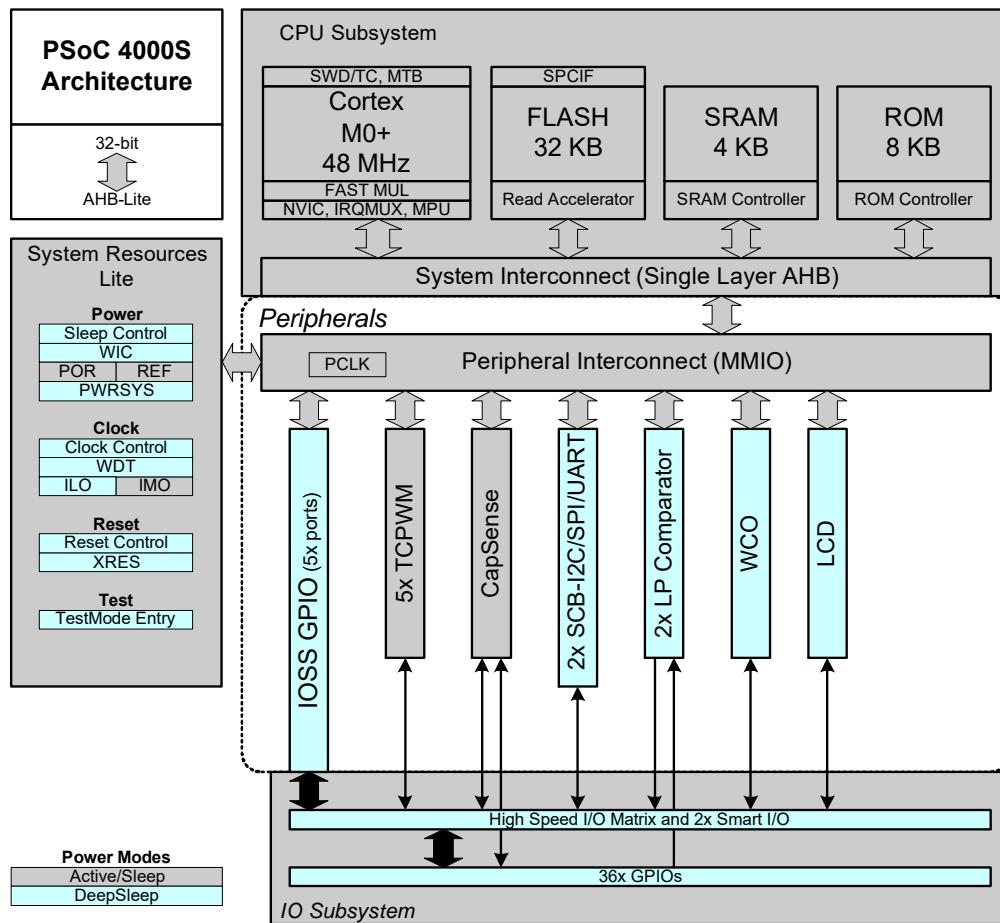

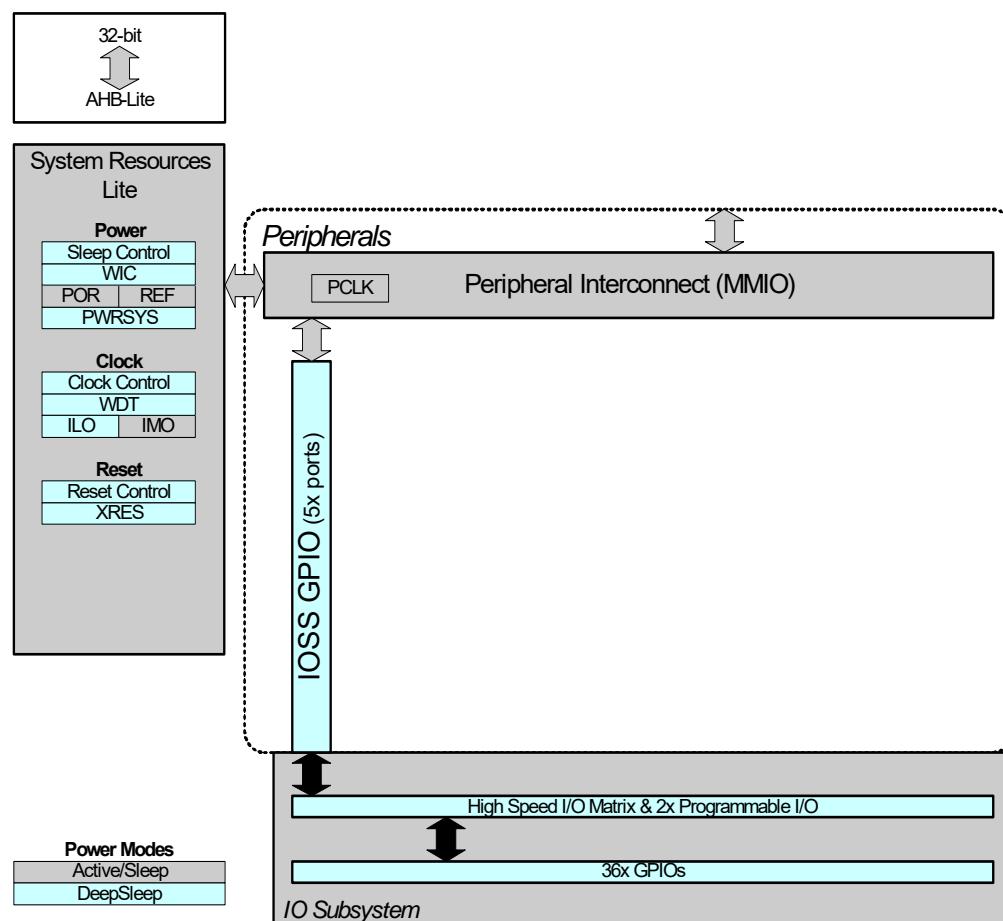

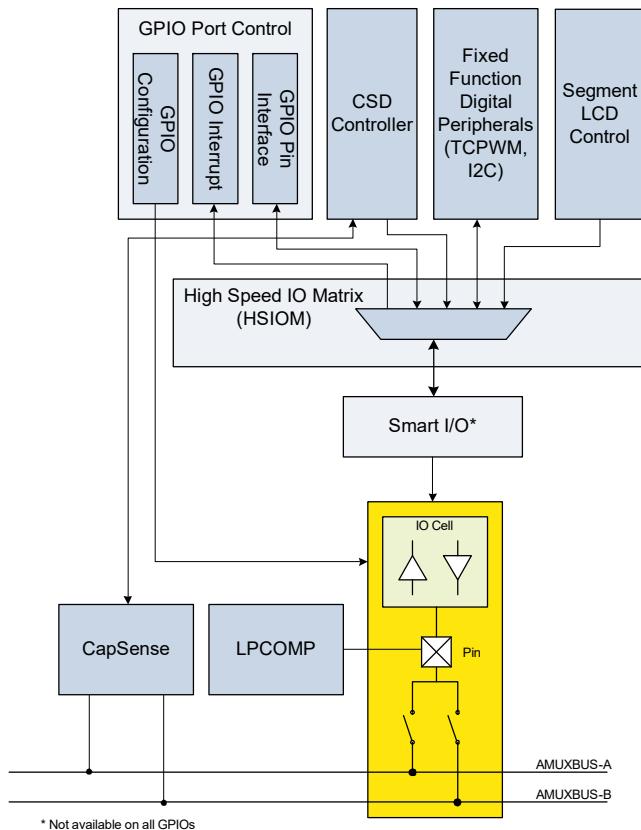

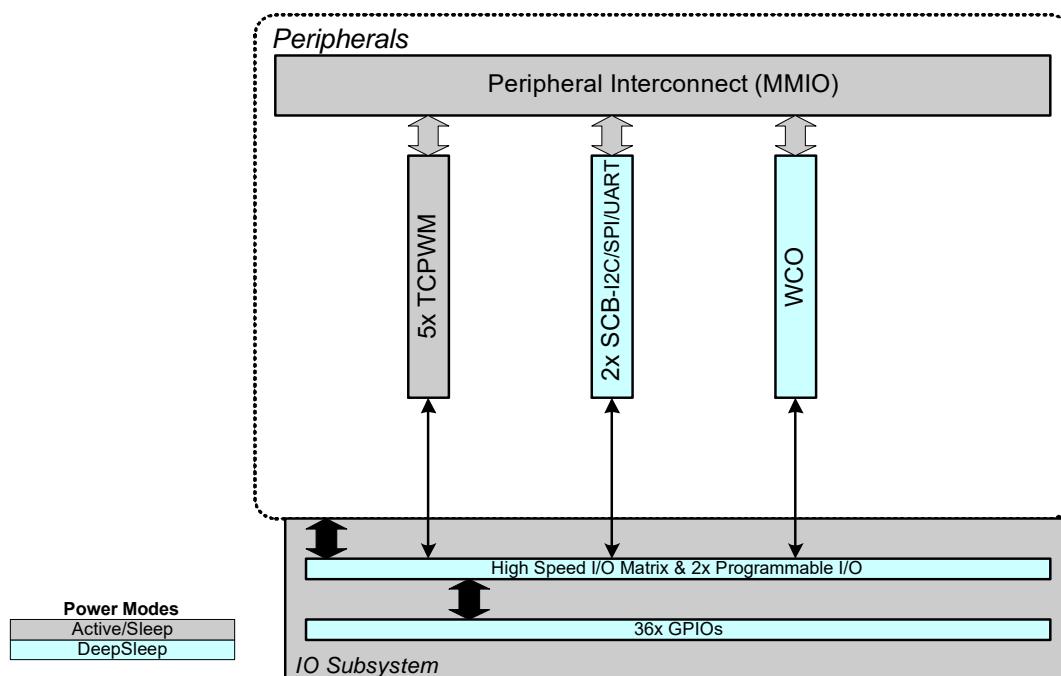

図 1-1 に PSoC 4000S アーキテクチャの主なコンポーネントを示します。

図 1-1. PSoC 4000S ファミリ ブロック図

## 1.2 特長

PSoC 4000S ファミリは以下の主なコンポーネントがあります：

- 最大 0.9DMIPS/MHz を供給するシングルサイクル乗算器を搭載した 32 ピット Cortex-M0+ CPU

- 最大 32KB フラッシュおよび 4KB SRAM

- 5 つの中央揃えパルス幅変調器 (PWM) コンプリメンタリ、デッドバンド プログラマブル出力を搭載

- 2 つの低消費電力コンパレータ

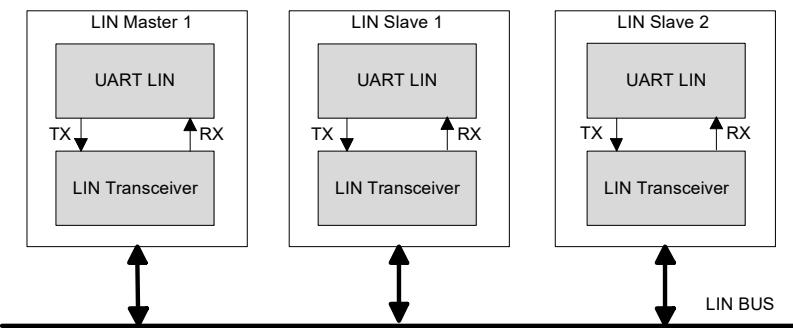

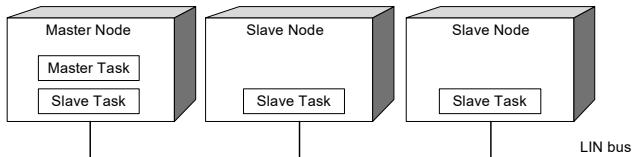

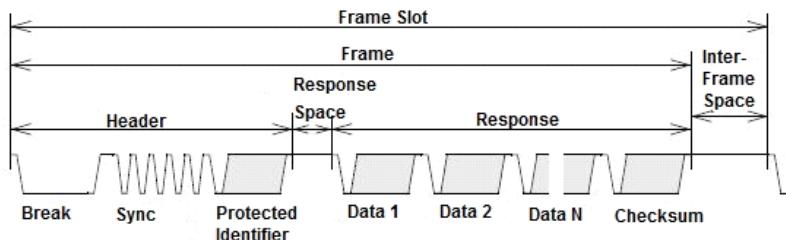

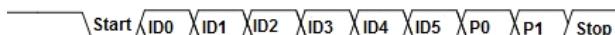

- 2 つのシリアル通信ブロック (SCB) SPI、UART、I<sup>2</sup>C およびローカル インターコネクト ネットワーク (LIN) スレーブ シリアル通信チャネルとして動作可能

- スマート I/O ブロック、I/O 信号バスでブール関数を実行可能

- CapSense

- セグメント LCD ダイレクト ドライブ

- 低消費電力動作モード：スリープ およびディープスリープ

- シリアル ワイヤ デバッグ (SWD) を介したプログラミングとデバッグ システム

- PSoC Creator™ IDE ツールによる完全サポート

## 1.3 CPU システム

### 1.3.1 プロセッサ

PSoC 4 の心臓部は 32 ビット Cortex-M0+ CPU コアです。PSoC 4000S は最大 48MHz で動作します。このプロセッサは広範なクロックゲーティングを搭載し、低消費電力動作に最適化されています。16 ビット命令を使用し、Thumb-2 命令セットを実行します。この命令セットにより、バイナリコードは完全な上位互換性があり、Cortex M3 や M4 等の高性能プロセッサに使用できます。

CPU は 1 サイクルで 32 ビット結果を出すハードウェア乗算器を搭載しています。

### 1.3.2 割り込みコントローラー

CPU サブシステムには、16 の割り込み入力を持つネスト型ベクタ割り込みコントローラー (NVIC) とプロセッサをディープスリープ モードから復帰できるウェイクアップ割り込みコントローラー (WIC) があります。

## 1.4 メモリ

PSoC 4 メモリ サブシステムはフラッシュと SRAM で構成されています。ブートおよびコンフィギュレーション ルーチンを格納する監視 ROM が提供されています。

### 1.4.1 フラッシュ

PSoC 4 はフラッシュ ブロックからの平均アクセス時間を改善する CPU に密に結合したフラッシュ アクセラレータ付きのフラッシュ モジュールを搭載しています。フラッシュ アクセラレータはシングルサイクル SRAM のアクセス性能平均の 85% を達成します。

### 1.4.2 SRAM

PSoC 4 は SRAM を提供し、これはデバイスのすべての消費電力モードでデータを保持します。

## 1.5 システムワイド リソース

### 1.5.1 クロック システム

クロック システムは内部クロックとして、内部主発振器 (IMO) および内部低速発振器 (ILO) を構成し、外部クロックおよび時計用水晶発振器 (WCO) に対応できます。

IMO は  $\pm 2\%$  の精度を持ち、デバイスの内部クロックの主要供給源です。IMO の初期設定周波数は 24MHz であり、4MHz 単位で 24MHz ~ 48MHz の間で調整できます。アプリケーションの要件を満たすために、複数のクロック周波数はメインクロック周波数から生成されます。

ILO は低消費電力ですが精度の低い発振器であり、ディープスリープ モードで周辺機能を動作させるためのクロックを生成する LFCLK の信号源として使用されます。そのクロック周波数は 40kHz で  $\pm 60$  パーセントの精度です。

1MHz ~ 48MHz の外部クロック ソースは、IMO の代わりに機能ブロック用の派生クロックを生成するために使用することができます。

### 1.5.2 電源システム

デバイスは 1.71V ~ 5.5V の単一外部電源で動作します。これは複数電源供給ドメインを提供します – デジタル セクション電源用  $V_{DDD}$  とアナログ セクション用にノイズ隔離する  $V_{DDA}$  とを外部で短絡する必要があります。

デバイスはスリープ およびディープスリープの 2 つの低消費電力モードがあり、デフォルトはアクティブ モードです。アクティブ モードでは、すべてのデジタル回路に電源が供給され CPU が動作します。スリープ モードでは、すべての他のペリフェラル機能を含めて、CPU は電源オフです。ディープスリープ モードでは、CPU、SRAM および高速ロジックはデータ保持状態に入ります；メイン システム クロックがオフにされ、低速クロックはオンで、低速ペリフェラルは動作し続けます。

各種消費電力モードで電源供給に対応するため、多数の内部レギュレータがシステムで利用可能です。

### 1.5.3 GPIO

すべての GPIO は以下の特性を持ちます：

- 8 つの駆動能力モード

- 入力と出力のディスエーブルの個別制御

- 直前の状態をラッチするための保持モード

- 選択可能なスルーレート

- 割り込み生成 – エッジトリガー

更に、デバイスはポート I/O でプル関数を実行することができる 2 つのスマート I/O ブロックがあります。スマート I/O ブロックは、低消費電力モードを含むすべてのデバイス消費電力モードで使用可能です。

ピンは 8 ビット幅のポートで構成されます。高速 I/O マトリックスは、I/O ピンに接続できる複数の信号を多重化するために使用されます。固定機能ブロックのピン位置も固定されています。

## 1.6 固定機能デジタル

### 1.6.1 タイマー／カウンター／PWM ブロック

タイマー／カウンター／PWM ブロックはユーザー プログラム可能な周期の 5 つの 16 ビット カウンターで構成されます。TCPWM ブロックはキャプチャレジスタ、周期レジスタおよび比較レジスタを持ちます。ブロックはコンプリメンタリ、デッドバンド プログラマブル出力をサポートします。これは所定の状態にする強制的な出力を行うキル入力もあります。ブロックの他の機能では中央揃え PWM、クロック プリスケール、擬似ランダム PWM および直交デコーダーの機能を含みます。

### 1.6.2 シリアル通信ブロック

デバイスは 2 つの SCB を持っています。各 SCB は I<sup>2</sup>C、UART、ローカル インターコネクト ネットワーク (LIN) スレーブ、または SPI となるシリアル通信インターフェースを搭載することができます。

各 SCB の機能を以下に示します：

- 標準 I<sup>2</sup>C マルチマスターとスレーブの機能

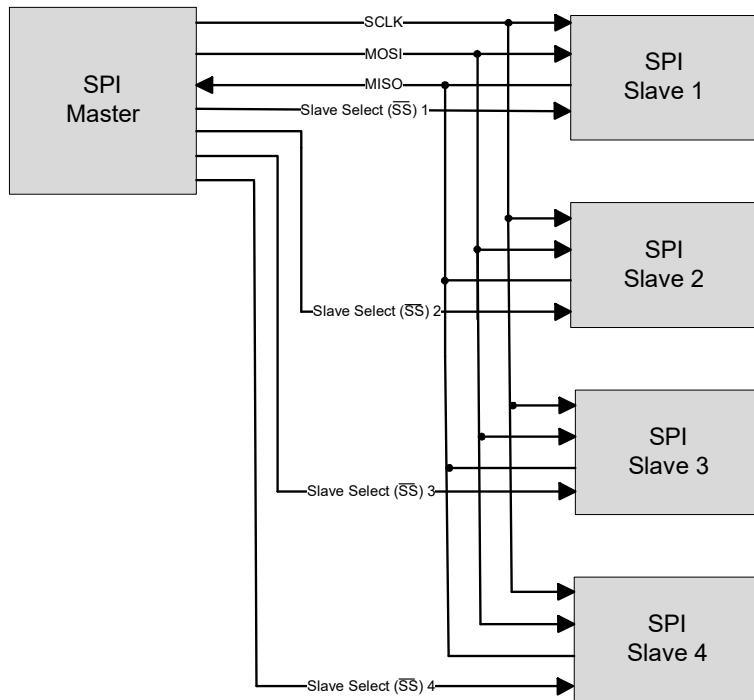

- Motorola、Texas Instruments、National Semiconductor (MicroWire) のプロトコルと互換性のある標準的な SPI マスターとスレーブの機能

- SmartCard リーダー (ISO7816)、IrDA および LIN プロトコルと互換性のある標準的な UART 送受信機能

- 標準 LIN スレーブは LIN V1.3 および LIN V2.1/2.2 仕様規格に準拠

- 32 バイト バッファを利用する EZ 機能モードのサポート

## 1.7 アナログ システム

### 1.7.1 低消費電力コンパレータ

PSoC 4 は一対の低消費電力コンパレータを持ち、これはすべてのデバイスの消費電力モードで動作することができます。この機能は、低消費電力モード時に外部電圧レベルの監視能力を保持しながら、CPU と他のシステム ブロックを無効にすることが可能です。2 つの入力電圧は、両方ともピンから配線されるか、1 つが AMUXBUS を介して内部信号から配線されます。

## 1.8 特殊機能ペリフェラル

### 1.8.1 LCD セグメント駆動

PSoC 4 は最大 8 つのコモンとそれぞれの GPIO をコモンまたはセグメントで駆動するために設定できる LCD コントローラを搭載しています。内部で LCD 電圧を生成する必要のないフル デジタル方式 (デジタル関相および PWM) を使用して LCD セグメントを駆動します。

### 1.8.2 CapSense

PSoC 4000S デバイスは第 4 世代 CapSense であり、これは以下の機能を持ちます：

## 1.10 デバイス機能の要約

表 1-1 に PSOc 4000S デバイスの要約を示します。

表 1-1. PSOc 4000S デバイスの要約

| 特長                     | PSOc 4000S |

|------------------------|------------|

| 最大 CPU 周波数             | 48MHz      |

| フラッシュ                  | 32KB       |

| SRAM                   | 4KB        |

| GPIO (最大)              | 36         |

| スマート I/O               | 2 ポート      |

| CapSense               | 使用可能       |

| LCD ドライバー              | 使用可能       |

| タイマー、カウンター、PWM (TCPWM) | 5          |

- 自己静電容量および相互静電容量ベースのタッチ センシング

- 自己静電容量および相互静電容量ベースのタッチ センシングのそれぞれはクラス最高の SNR を提供する堅牢な CapSense シグマデルタ (CSD) および CapSense クロスポイント (CSX) センシング技術

- ADC として CapSense ブロックを再構成でき、すべての GPIO ピンで ADC 入力をサポート

- プログラマブル基準電圧 (VREF) を利用する、優れた SNR

- 低EMIのためにスペクトラム拡散およびプログラマブル抵抗スイッチをサポート

- CapSense シーケンサーに初期化および構成プロセスの負荷軽減によるスキャン中の CPU オーバヘッドの削減

- シールド信号駆動を使用する耐水性 CapSense 動作

- すべての GPIO ピンでの静電容量式タッチ センシングとシールド

### 1.8.2.1 IDAC とコンパレータ

CapSense ブロックは 1 つの調整可能な基準電圧で 2 つの IDAC と 1 つのコンパレータを持ち、これらは CapSense を使用しない場合は一般目的に使用することができます。

## 1.9 プログラムおよびデバッグ

PSOc 4 デバイスはオンチップ SWD インターフェース経由で、デバイスのプログラミングとデバッグの機能をサポートします。PSOc Creator IDE は、完全に統合されたプログラミングとデバッグのサポートを提供します。SWD インターフェースは業界標準のサードパーティ製ツールとも完全互換です。

表 1-1. PSoC 4000S デバイスの要約 ( 続表 )

| 特長                   | PSoC 4000S            |

|----------------------|-----------------------|

| シリアル通信ブロック (SCB)     | 2                     |

| IDAC (CapSense 用 )   | 2                     |

| 低消費電力コンパレータ (LPCOMP) | 2                     |

| 時計用水晶発振器 (WCO)       | 使用可能                  |

| 消費電力モード              | アクティブ、スリープおよびディープスリープ |

**注意事項 :** PSoC 4100S Plus デバイスには、2 つの異なるフラッシュおよび SRAM サイズファミリがあります。データシートでは、PSoC 4100S Plus および PSoC 4100S Plus 256 KB と表記されています。PSoC 4100S Plus ファミリには、128 KB のフラッシュ、16 KB の RAM、3 つのスマート I/O ポート、および最大 57 のプログラム可能な GPIO があります。ただし、真の乱数発生器 (TRNG) およびコントローラー エリア ネットワーク (CAN) 機能はありません。他の機能と周辺機器は、PSoC 4100S Plus ファミリと同じです。

## 2. 開発サポート

### 2.1 サポート

PSoC® 4 製品の無料サポートを [www.cypress.com/psoc4](http://www.cypress.com/psoc4) からオンラインでご利用になれます。トレーニング セミナー、ディスカッション フォーラム、アプリケーション ノート、PSoC コンサルタント、CRM テクニカル サポートの電子メール、知識ベース、アプリケーション サポート エンジニアのリソースがあります。

アプリケーションについて支援が必要な場合は [www.cypress.com/support/](http://www.cypress.com/support/) をご覧になるか、1-800-541-4736 までお電話ください。

### 2.2 製品アップグレード

サイプレスは無償 PSoC Creator の予定したアップグレードと改良したバージョンを提供しています。アップグレードは DVD-ROM で代理店から入手できます。また [www.cypress.com/psoccreator](http://www.cypress.com/psoccreator) から直接ダウンロードすることもできます。システム ドキュメントの重要な更新もドキュメントのセクションで提供されます。

### 2.3 開発キット

サイプレス オンライン ストアでも開発キット、C コンパイラおよび PSoC プロジェクトを失敗なく開発するための必要なアクセサリをお求めいただけます。サイプレス オンライン ストア ウェブサイト [www.cypress.com/cypress-store](http://www.cypress.com/cypress-store) をご覧ください。製品ごとに利用可能なアイテムをご覧いただくため、**Programmable System-on-Chip** をクリックしてください。開発キットは Digi-Key、Avnet、Arrow、Future の各社より入手することも可能です。

### 2.4 アプリケーション ノート

アプリケーション ノート「[AN79953 - Getting Started with PSoC 4](#)」を参照してください。PSoC 4 デバイスの機能および PSoC Creator と PSoC 4 開発キットを使用した簡単な PSoC アプリケーションを迅速に作成する詳細情報があります。

# 3. 文書の構成

この文書は次の節を含みます：

- 21 ページのセクション B:CPU システム

- 35 ページのセクション C: システムリソース サブシステム (SRSS)

- 83 ページのセクション D: デジタル システム

- 153 ページのセクション E: アナログ システム

- 174 ページのセクション F: プログラムおよびデバッグ

## 3.1 主要な節

使い易さのため、情報はデバイスの機能によって分けられるセクションと章で構成されます。

- 節 – トップレベル アーキテクチャ、開始方法および規則と製品概要の情報を説明します。

- 章 – セクショントピックに特有の事項を個々に説明します。搭載と使用に関する詳細な情報です。

- 用語集 – テクニカル リファレンス マニュアル (TRM) で使用される専門用語を定義します。用語はボールド イタリックのフォントで表示されます。

- レジスタ テクニカル リファレンス マニュアル – テクニカル リファレンス マニュアルに、すべてのデバイス レジスタの詳細を提供します。これは追加文書です。

## 3.2 本書の表記法

本書では見出しのフォントの他に、4 つの特徴的なフォントを使用しています。

- 1 番目は文書名またはファイル名に言及する時に使用されるイタリックフォントです。

- 2 番目は本書の用語集で説明される用語に言及する時に使用されるボールド イタリックフォントです。

- 3 番目は式の例を示すために使用される Times New Roman フォントです。

- 4 番目はコード例を示すために使用される Courier New フォントです。

### 3.2.1 レジスタの表記法

レジスタ規則は、PSoC 4000S Family: PSoC 4 Registers TRM にて詳述されます。

### 3.2.2 数値の表記法

16 進数はすべて大文字で表記し、小文字の「h」を付記しています（例えば「14h」「3Ah」）。C のコーディング規則に基づき、接頭語「0x」を使用して 16 進数を表現している場合もあります。2 進数には小文字の「b」を付記しています（例えば「01010100b」や「01000011b」）。「h」も「b」も付いていない数は 10 進数です。

### 3.2.3 測定単位

次の表に本書で使用する測定単位を示します。

表 3-1. 測定単位

| 略語    | 測定単位                   |

|-------|------------------------|

| bps   | ビット毎秒                  |

| °C    | 摂氏温度                   |

| dB    | デシベル                   |

| fF    | フェムトファラッド              |

| Hz    | ヘルツ                    |

| k     | キロ、1000                |

| K     | キロ、2^10 (1024)         |

| KB    | 1024 バイトまたは約 1000 バイト  |

| Kbit  | 1024 ビット               |

| kHz   | キロヘルツ (32.000)         |

| kΩ    | キロオーム                  |

| MHz   | メガヘルツ                  |

| MΩ    | メガオーム                  |

| μA    | マイクロアンペア               |

| μF    | マイクロファラッド              |

| μs    | マイクロ秒                  |

| μV    | マイクロボルト                |

| μVrms | マイクロボルト (実効値)          |

| mA    | ミリアンペア                 |

| ms    | ミリ秒                    |

| mV    | ミリボルト                  |

| nA    | ナノアンペア                 |

| ns    | ナノ秒                    |

| nV    | ナノボルト                  |

| Ω     | オーム                    |

| pF    | ピコファラッド                |

| pp    | ピーク ツー ピーク             |

| ppm   | 100 万分の 1              |

| SPS   | サンプル数毎秒                |

| s     | シグマ : 標準偏差値を 1 単位とした表記 |

| V     | ボルト                    |

### 3.2.4 略語

次の表に本書で使用する略号を示します。

表 3-2. 略語

| 略語    | 定義                                                                 |

|-------|--------------------------------------------------------------------|

| abus  | analog output bus ( アナログ出力バス )                                     |

| AC    | alternating current ( 交流電流 )                                       |

| ADC   | analog-to-digital converter<br>( アナログ - デジタル変換器 )                  |

| AHB   | AMBA ( アドバンストマイクロコントローラーバス アーキテクチャ ) 高性能バス、Arm データ転送バスの一種          |

| API   | application programming interface ( アプリケーション プログラミング インターフェース )    |

| APOR  | analog power-on reset<br>( アナログ パワーオン リセット )                       |

| BC    | broadcast clock ( ブロードキャスト クロック )                                  |

| BOD   | brownout detect ( 電圧低下検出 )                                         |

| BOM   | bill of materials ( 部品表、員数表 )                                      |

| BR    | bit rate ( ビット レート )                                               |

| BRA   | bus request acknowledge ( バス要求認識 )                                 |

| BRQ   | bus request ( バス要求 )                                               |

| CAN   | controller area network<br>( コントローラー エリア ネットワーク )                  |

| CI    | carry in ( キャリーイン )                                                |

| CMP   | compare ( 比較 )                                                     |

| CO    | carry out ( キャリー アウト )                                             |

| COM   | LCD common signal ( LCD コモン信号 )                                    |

| CPU   | central processing unit ( 中央演算処理装置 )                               |

| CRC   | cyclic redundancy check ( 巡回冗長検査 )                                 |

| CSD   | CapSense Sigma Delta<br>( CapSense シグマ デルタ方式 )                     |

| CT    | continuous time ( 連続時間 )                                           |

| DAC   | digital-to-analog converter<br>( デジタル - アナログ 変換器 )                 |

| DAP   | debug access port ( デバッグ アクセス ポート )                                |

| DC    | direct current ( 直流 )                                              |

| DI    | digital or data input<br>( デジタル入力またはデータ入力 )                        |

| DMA   | direct memory access ( 直接メモリ アクセス )                                |

| DMIPS | Dhrystone million instructions per second<br>( ドライストーン 100 万命令毎秒 ) |

| DO    | digital or data output<br>( デジタル出力またはデータ出力 )                       |

| DSI   | digital signal interface<br>( デジタル信号インターフェース )                     |

| DSM   | deep-sleep mode ( ディープスリープ モード )                                   |

| DW    | data wire ( データ線 )                                                 |

| ECO   | external crystal oscillator ( 外部水晶発振器 )                            |

表 3-2. 略語 ( 続表 )

| 略語               | 定義                                                                             |

|------------------|--------------------------------------------------------------------------------|

| EEPROM           | electrically erasable programmable read only memory ( 電気的消去プログラム可能な読み出し専用メモリ ) |

| EMIF             | external memory interface ( 外部メモリ インターフェース )                                   |

| FB               | feedback ( フィードバック )                                                           |

| FIFO             | first in first out ( 先入れ先出しメモリ )                                               |

| FSR              | Full scale range ( フル スケール範囲 )                                                 |

| GPIO             | general purpose I/O ( 汎用 I/O )                                                 |

| HCI              | host-controller interface ( ホストコントローラー インターフェース )                              |

| HFCLK            | high-frequency clock ( 高周波クロック )                                               |

| HSIOM            | high-speed I/O matrix ( 高速 I/O マトリクス )                                         |

| I <sup>2</sup> C | inter-integrated circuit ( インターハイブ接続 )                                         |

| IDE              | integrated development environment ( 統合開発環境 )                                  |

| ILO              | internal low-speed oscillator ( 内部低速発振器 )                                      |

| ITO              | indium tin oxide ( インジウム錫酸化物 )                                                 |

| IMO              | internal main oscillator ( 内部主発振器 )                                            |

| INL              | integral nonlinearity ( 積分非直線性 )                                               |

| I/O              | input/output ( 入出力 )                                                           |

| IOR              | I/O read ( I/O 読み出し )                                                          |

| IOW              | I/O write ( I/O 書き込み )                                                         |

| IRES             | initial power on reset ( 初期パワーオン リセット )                                        |

| IRA              | interrupt request acknowledge ( 割り込み要求認識 )                                     |

| IRQ              | interrupt request ( 割り込み要求 )                                                   |

| ISR              | interrupt service routine ( 割り込みサービス ルーチン )                                    |

| IVR              | interrupt vector read ( 割り込みベクタ読み出し )                                          |

| LCD              | liquid crystal display ( 液晶ディスプレイ )                                            |

| LFCLK            | low-frequency clock ( 低周波クロック )                                                |

| LPCOMP           | low-power comparator ( 低消費電力コンパレータ )                                           |

| LRb              | last received bit ( 最後に受信したビット )                                               |

| LRB              | last received byte ( 最後に受信したバイト )                                              |

| LSb              | least significant bit ( 最下位ビット )                                               |

| LSB              | least significant byte ( 最下位バイト )                                              |

| LUT              | lookup table ( ルックアップ テーブル )                                                   |

| MISO             | master-in-slave-out ( マスターインスレーブアウト )                                          |

| MMIO             | memory mapped input/output ( メモリマップ入出力 )                                       |

| MOSI             | master-out-slave-in ( マスターアウトスレーブイン )                                          |

| MPU              | memory protection unit ( メモリ保護ユニット )                                           |

表 3-2. 略語 ( 続表 )

| 略語    | 定義                                                         |

|-------|------------------------------------------------------------|

| MSb   | most significant bit ( 最上位ビット )                            |

| MSB   | most significant byte ( 最上位バイト )                           |

| MSP   | main stack pointer ( メイン スタック ポインタ )                       |

| NMI   | non-maskable interrupt ( マスク不可割り込み )                       |

| NVIC  | nested vectored interrupt controller ( ネスト型ベクタ割り込みコントローラ ) |

| PC    | program counter ( プログラム カウンター )                            |

| PCB   | printed circuit board ( プリント回路基板 )                         |

| PCH   | program counter high ( プログラム カウンター上位バイト )                  |

| PCL   | program counter low ( プログラム カウンター下位バイト )                   |

| PD    | power down ( パワー ダウン )                                     |

| PGA   | programmable gain amplifier ( プログラマブル ゲイン アンプ )            |

| PM    | power management ( 電源管理 )                                  |

| PMA   | PSoC memory arbiter ( PSOC メモリ アービタ )                      |

| POR   | power-on reset ( パワーオン リセット )                              |

| PPOR  | precision power-on reset ( 高精度パワーオン リセット )                 |

| PRS   | pseudo random sequence ( 疑似乱数列 )                           |

| PSOC® | Programmable System-on-Chip ( プログラマブル システムオンチップ )          |

| PSP   | process stack pointer ( プロセス スタック ポインタ )                   |

| PSRR  | power supply rejection ratio ( 電源電圧変動除去比 )                 |

| PSSDC | power system sleep duty cycle ( 電源システム スリープ デューティ サイクル )   |

| PWM   | pulse width modulator ( パルス幅変調器 )                          |

| RAM   | random-access memory ( ランダム アクセス メモリ )                     |

| RETI  | return from interrupt ( 割り込みから復帰 )                         |

| RF    | radio frequency ( 無線周波数 )                                  |

| ROM   | read only memory ( 読み出し専用メモリ )                             |

| RMS   | root mean square ( 二乗平均平方根 )                               |

| RW    | read/write ( 読み出し / 書き込み )                                 |

| SAR   | successive approximation register ( 逐次比較レジスタ )             |

| SEG   | LCD segment signal ( LCD セグメント信号 )                         |

| SC    | switched capacitor ( スイッチド キャパシタ )                         |

| SCB   | serial communication block ( シリアル通信ブロック )                  |

| SIE   | serial interface engine ( シリアル インターフェース エンジン )             |

| SIO   | special I/O ( 特殊 I/O )                                     |

| SE0   | single-ended zero ( シングルエンド ゼロ )                           |

表 3-2. 略語 ( 続表 )

| 略語     | 定義                                                                    |

|--------|-----------------------------------------------------------------------|

| SNR    | signal-to-noise ratio ( 信号対雑音比 )                                      |

| SOF    | start of frame ( フレームの開始 )                                            |

| SOI    | start of instruction ( 命令の開始 )                                        |

| SP     | stack pointer ( スタック ポインタ )                                           |

| SPD    | sequential phase detector ( 順次位相検出器 )                                 |

| SPI    | serial peripheral interconnect<br>( シリアル ペリフェラル インターコネクト )            |

| SPI-M  | serial peripheral interconnect master ( シリアル ペリフェラル インターコネクト マスター )   |

| SPIS   | serial peripheral interconnect slave ( シリアル ペリフェラル インターコネクト スレーブ )    |

| SRAM   | static random access memory<br>( スタティック ランダム アクセス メモリ )               |

| SROM   | supervisory read only memory<br>( 監視用読み出し専用メモリ )                      |

| SSADC  | single slope ADC ( シングル スロープ ADC )                                    |

| SSC    | supervisory system call<br>( スーパバイザ システム コール )                        |

| SYCLK  | system clock ( システム クロック )                                            |

| SWD    | single wire debug ( シングル ワイヤ デバッグ )                                   |

| TC     | terminal count ( ターミナル カウント )                                         |

| TCPWM  | timer、counter、PWM<br>( タイマー／カウンター／PWM)                                |

| TD     | transaction descriptors<br>( トランザクション記述子 )                            |

| TIA    | trans-impedance amplifier<br>( トランスインピーダンス アンプ )                      |

| UART   | universal asynchronous receiver/transmitter<br>( 汎用非同期レシーバー／トランスマッタ ) |

| UDB    | universal digital block ( 汎用デジタル ブロック )                               |

| USB    | universal serial bus<br>( ユニバーサル シリアル バス )                            |

| USBIO  | USB I/O (USB 入出力 )                                                    |

| VTOR   | vector table offset register<br>( ベクタ テーブル オフセット レジスタ )               |

| WCO    | watch crystal oscillator ( 時計用水晶発振器 )                                 |

| WDT    | watchdog timer ( ウオッチドッグ タイマー )                                       |

| WDR    | watchdog reset ( ウオッチドッグ リセット )                                       |

| XRES   | external reset ( 外部リセット )                                             |

| XRES_N | external reset、active low<br>( 外部リセット、アクティブ LOW )                     |

# セクション B: CPU システム

このセクションは次の章を含みます。

- 22 ページの Cortex-M0+ CPU の章

- 27 ページの割り込みの章

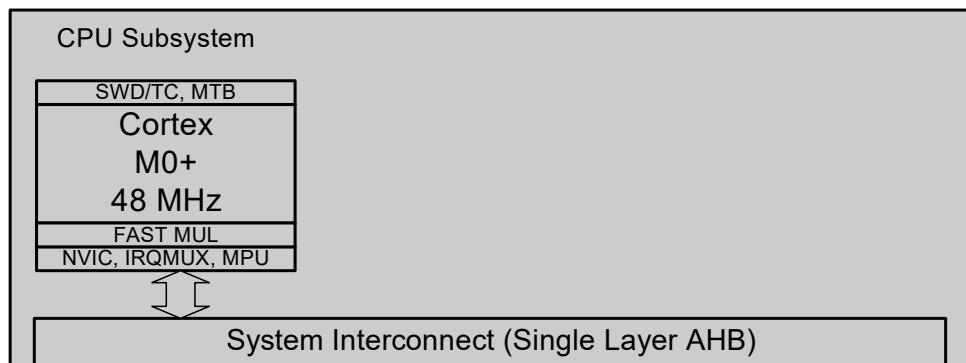

## トップ レベル アーキテクチャ

CPU システム ブロック図

## 4. Cortex-M0+ CPU

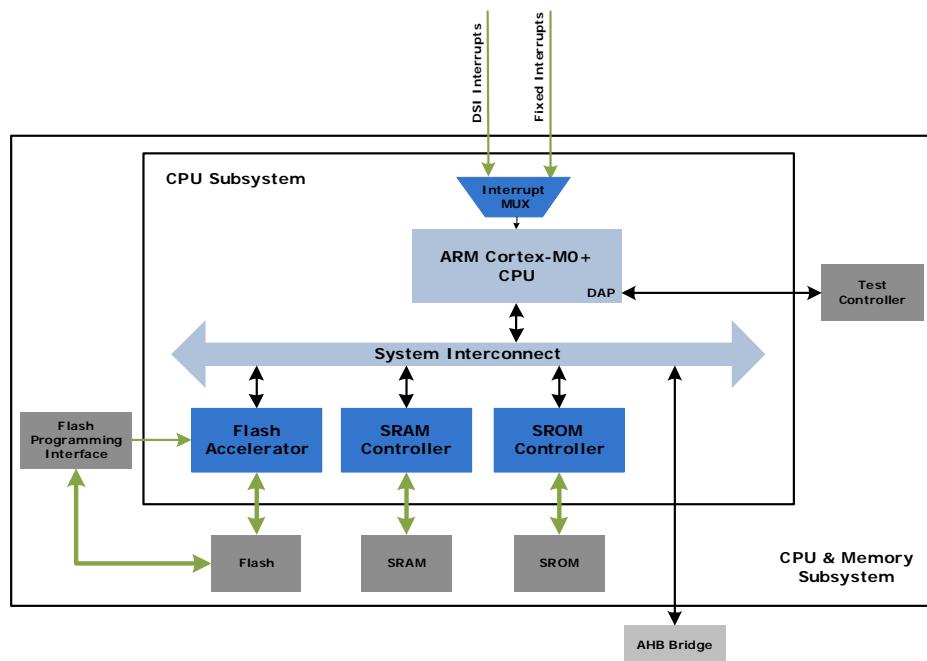

PSoC® 4 Arm Cortex-M0+ コアは低消費電力動作に最適化された 32 ビット CPU です。高効率の 2 段パイプラインおよび固定 4GB メモリ マップがあり、Armv6-M Thumb 命令セットに対応します。Cortex-M0+ は 32 ビットのシングル サイクル乗算命令およびレイテンシの短い割り込み処理にも対応します。CPU コアに密接にリンクされるその他のサブシステムはネスト型ベクタ割り込みコントローラー (NVIC)、SYSTICK タイマー、およびデバッグ機能を含みます。

この節では Cortex-M0+ プロセッサの概要を説明します。詳細については [www.arm.com](http://www.arm.com) に掲載されている Arm Cortex-M0+ のユーザー ガイドまたは、テクニカル リファレンス マニュアルを参照してください。

### 4.1 特長

PSoC 4 Cortex-M0+ は以下の特徴があります：

- プログラムとデバッグが容易であり、8 ビット／16 ビットプロセッサからの移行がより簡単

- 最大 0.9DMIPS/MHz で動作します。これは実行速度の向上、消費電力の低減に役立つ

- コード密度を高める Thumb 命令セットに対応し、メモリの効率的な使用を確保

- NVIC ユニットは突発的で確定的な割り込みと例外に対応

- 設計時、コンフィギュレーション可能なメモリ保護ユニット (MPU) を実装

- 非特権モードおよび特権モードの実行をサポート

- 任意のベクタ テーブル オフセット レジスタ (VTOR) をサポート

- 機能強化されたデバッグ機能：

- SWD ポート

- ブレークポイント

- ウオッチポイント

## 4.2 ブロック図

図 4-1. CPU サブシステム ブロック図

## 4.3 動作原理

Cortex-M0+ は 32 ビットのデータバス、32 ビットのレジスタおよび 32 ビットのメモリ インターフェースを持つ 32 ビットのプロセッサです。Thumb 命令セットのほとんどの 16 ビット命令と Thumb 2 命令セットの一部の 32 ビット命令に対応します。

プロセッサは 2 つの動作モードに対応します ([25 ページの動作モード](#) を参照してください)。シングル サイクル 32 ビット乗算命令があります。

## 4.4 アドレス マップ

Arm Cortex-M0+ には固定アドレス マップがあります。これを使用すると、簡単なメモリ アクセス命令でメモリとペリフェラルにアクセスできます。32 ビット (4GB) のアドレス空間は [表 4-1](#) に示す領域に分けられています。コードと SRAM の領域からコードを実行することができることにご注意ください。

表 4-1. Cortex-M0+ アドレス マップ

| アドレス範囲                  | 名称     | 用途                                              |

|-------------------------|--------|-------------------------------------------------|

| 0x00000000 ~ 0x1FFFFFFF | コード    | プログラム コード領域。データも配置可能。アドレス 0 から始まる例外ベクタ テーブルを保持。 |

| 0x20000000 ~ 0x3FFFFFFF | SRAM   | データ領域。この領域からのコードを実行することもできる                     |

| 0x40000000 ~ 0x5FFFFFFF | ペリフェラル | すべてのペリフェラル レジスタ。この領域からのコードを実行することができない。         |

| 0x60000000 ~ 0xDFFFFFFF |        | 未使用。                                            |

| 0xE0000000 ~ 0xE00FFFFF | PPB    | CPU コア内のペリフェラル レジスタ                             |

| 0xE0100000 ~ 0xFFFFFFFF | デバイス   | PSoC 4 固有の実装                                    |

## 4.5 レジスタ

表 4-2 に示すように、Cortex-M0+ は 16 の 32 ビット レジスタがあります：

- R0 ~ R12: 汎用レジスタ。すべての命令で R0 ~ R7 にアクセスでき、サブセットの命令で他のレジスタにアクセスできます。

- R13: スタック ポインタ (SP)。スタック ポインタは 2 つあり、1 度に 1 つのみ使用可能です。スレッド モードでは、CONTROL レジスタが主スタック ポインタまたはプロセス スタック ポインタ、どちらを使用するかを示します

- R14: リンク レジスタ。関数呼び出し中、戻りプログラム カウンターを保存します。

- R15: プログラム カウンター。このレジスタは制御プログラム フローに書き込むことが可能です。

表 4-2. Cortex-M0+ レジスタ

| 名称        | タイプ <sup>a</sup> | リセット値          | 説明                                                                                                                                                                                  |

|-----------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0 ~ R12  | RW               | 未定義            | R0 ~ R12 はデータ操作用の 32 ビットの汎用レジスタ                                                                                                                                                     |

| MSP (R13) | RW               | 0x00000000     | スタック ポインタ (SP) はレジスタ R13。スレッド モードでは、コントロール レジスタのビット 1 は使用するスタック ポインタを示す：<br>0 = 主スタック ポインタ (MSP)。これはリセット値<br>1 = プロセス スタック ポインタ (PSP)<br>リセット時、プロセッサはアドレス 0x00000000 からの値で MSP をロード |

| PSP (R13) |                  |                |                                                                                                                                                                                     |

| LR (R14)  | RW               | 未定義            | リンク レジスタ (LR) はレジスタ R14。サブルーチンと関数呼び出し、例外のために返し情報を保存                                                                                                                                 |

| PC (R15)  | RW               | [0x00000004]   | プログラム カウンター (PC) はレジスタ R15。現在のプログラム アドレスを保持。リセット時、プロセッサはアドレス 0x00000004 からの値で PC をロード。ビット 0 はリセット時 EPSR T ビットにロードされ、1 でなければならぬ                                                      |

| PSR       | RW               | 未定義            | プログラム ステータス レジスタ (PSR) は以下を含む：<br>アプリケーション プログラム ステータス レジスタ (APSR)<br>実行プログラム ステータス レジスタ (EPSR)<br>割り込みプログラム ステータス レジスタ (IPSR)                                                      |

| APSR      | RW               | 未定義            | APSR は直前の命令を実行後の条件フラグの状態を保持                                                                                                                                                         |

| EPSR      | RO               | [0x00000004].0 | リセット時、EPSR にレジスタ [0x00000004] のビット 0 の値がロードされる                                                                                                                                      |

| IPSR      | RO               | 0              | IPSR は現在の ISR の例外番号を保持する                                                                                                                                                            |

| PRIMASK   | RW               | 0              | PRIMASK レジスタは優先順位を設定することですべての例外が有効になることを防止する                                                                                                                                        |

| CONTROL   | RW               | 0              | コントロール レジスタはプロセッサがスレッド モードの時に、使用したスタックを制御する                                                                                                                                         |

a. スレッド モードとハンドラ モードのプログラム実行中のアクセス タイプです。デバッグ アクセスは異なることがあります。

表 4-3 に PSR ビットの割り当て方法を示します。

表 4-3. Cortex-M0+ PSR ビット割り当て

| ビット | PSR レジスタ | 名称 | 使用法            |

|-----|----------|----|----------------|

| 31  | APSR     | N  | 負のフラグ          |

| 30  | APSR     | Z  | ゼロ フラグ         |

| 29  | APSR     | C  | キャリーまたはボロー フラグ |

| 28  | APSR     | V  | オーバーフロー フラグ    |

表 4-3. Cortex-M0+ PSR ビット割り当て

| ビット     | PSR レジスタ | 名称   | 使用法                                                                                                                                                                               |

|---------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 ~ 25 | -        | -    | 予約済み                                                                                                                                                                              |

| 24      | EPSR     | T    | Thumb 状態のビット。常に 1 でなければならない。T ビットが 0 である時の命令実行は HardFault 例外になる                                                                                                                   |

| 23 ~ 6  | -        | -    | 予約済み                                                                                                                                                                              |

| 5 ~ 0   | IPSR     | 該当なし | 現在の ISR 例外番号：<br>0 = スレッド モード<br>1 = 予約<br>2 = NMI<br>3 = ハード フォルト<br>4 ~ 10 = 予約<br>11 = スーパバイザ コール<br>12, 13 = 予約<br>14 = PendSV<br>15 = SysTick<br>16 = IRQ0<br>...<br>47 = 32 |

MSR または CPS 命令を使用して、PRIMASK レジスタのビット 0 をセットあるいはクリアします。ビットが 0 であると例外は有効になります。ビットが 1 であると、設定された優先順位の例外、つまり HardFault、NMI、リセットを除く例外は無効になります。例外一覧については [27 ページの割り込みの章](#) を参照してください。

## 4.6 動作モード

Cortex-M0+ プロセッサは以下の 2 つの動作モードに対応します：

- **スレッド モード**：通常のアプリケーションはこれを使用します。このモードでは MSP または PSP を使用することができます。CONTROL レジスタ ビット 1 は使用するスタック ポインタを決定します。

- 0 = MSP は現在のスタック ポインタ。

- 1 = PSP は現在のスタック ポインタ。

- **ハンドラ モード**：これで例外のハンドラを実行します。MSP は常に使用されます。

スレッド モードでは、MSR 命令を使用して、CONTROL レジスタのスタック ポインタ ビットを設定します。スタック ポインタを交換する時、MSR 命令の後は直ちに ISB 命令を使用します。この動作で ISB 以後の命令に新しいスタック ポインタが確保されます。

ハンドラ モードでは MSP が常に使用されるので、CONTROL レジスタへの明示的な書き込みは無視されます。例外のエントリと戻りメカニズムは CONTROL レジスタを自動的に更新します。

## 4.7 命令セット

Cortex-M0+ は表 4-4 に示すように、Thumb 命令セットのバージョンを備えています。詳細については Cortex-M0+ の全般的なユーザー ガイドを参照してください。

命令オペランドとして定数、その他の命令固有のパラメーター、Arm レジスタを取ります。命令はオペランドに作用し、結果を転送先レジスタに保存します。PC または SP をオペランド、転送先レジスタとして使用することは多くの命令でできないか或いは制限があります。

表 4-4. Thumb 命令セット

| ニーモニック              | 概要                  |

|---------------------|---------------------|

| ADCS                | キャリー付き加算            |

| ADD{S} <sup>a</sup> | 加算                  |

| ADR                 | PC 相対アドレスからレジスタまで   |

| ANDS                | ビット単位 AND           |

| ASRS                | 算術右シフト              |

| B{cc}               | ブランチ { 条件付き }       |

| BICS                | ビット クリア             |

| BKPT                | ブレークポイント            |

| BL                  | リンク付きブランチ           |

| BLX                 | リンク付きブランチ インダイレクト   |

| BX                  | ブランチ インダイレクト        |

| CMN                 | 比較否定                |

| CMP                 | 比較                  |

| CPSID               | プロセッサ状態を変更、割り込みを無効化 |

| CPSIE               | プロセッサ状態を変更、割り込みを有効化 |

| DMB                 | データ メモリ バリア         |

表 4-4. Thumb 命令セット

| ニーモニック              | 概要                      |

|---------------------|-------------------------|

| DSB                 | データ同期化パリア               |

| EORS                | 排他的 OR                  |

| ISB                 | 命令同期化パリア                |

| LDM                 | 複数レジスタをロード、インクリメント アフター |

| LDR                 | PC 相対アドレスからレジスタをロード     |

| LDRB                | ワード単位でレジスタをロード          |

| LDRH                | ハーフワード単位でレジスタをロード       |

| LDRSB               | 符号付きバイト単位でレジスタをロード      |

| LDRSH               | 符号付きハーフワード単位でレジスタをロード   |

| LSLS                | 論理左シフト                  |

| LSRS                | 論理右シフト                  |

| MOV{S} <sup>a</sup> | 移動                      |

| MRS                 | 特殊レジスタから汎用レジスタに移動       |

| MSR                 | 汎用レジスタから特殊レジスタに移動       |

| MULS                | 乗算、32 ビット出力             |

| MVNS                | ビット単位 NOT               |

| NOP                 | なにもしない                  |

| ORRS                | 論理 OR                   |

| POP                 | スタックからレジスタのポップ          |

| PUSH                | スタックにレジスタのプッシュ          |

| REV                 | バイト逆ワード                 |

| REV16               | バイト逆パック ハーフワード          |

| REVSH               | バイト逆符号付きハーフワード          |

| RORS                | 右ローテート                  |

| RSBS                | 逆減算                     |

| SBCS                | キャリー付き減算                |

| SEV                 | イベント送信                  |

| STM                 | 複数レジスタの保存、インクリメント アフター  |

| STR                 | ワード単位レジスタ保存             |

| STRB                | バイト単位レジスタ保存             |

| STRH                | ハーフワード単位レジスタ保存          |

| SUB{S} <sup>a</sup> | 減算                      |

| SVC                 | 監視プログラム呼び出し             |

| SXTB                | 符号拡張バイト                 |

| SXTH                | 符号拡張ハーフワード              |

| TST                 | 論理 AND でテスト             |

| UXTB                | 1 バイトのゼロ拡張              |

| UXTH                | 1 ハーフワードのゼロ拡張           |

| WFE                 | イベントの待機                 |

| WFI                 | 割り込みの待機                 |

a. 「S」修飾子により、ADD、SUB または MOV 命令が APSR 条件フラグを更新します。

#### 4.7.1 アドレス アライメント

アラインされたアクセスとは、ワード アライン アドレスがワード アクセスに、ハーフワード アライン アドレスがハーフワード アクセスに使用される動作です。バイト アクセスは常にアラインされます。

Cortex-M0+ プロセッサはアラインされていないアクセスに対応しません。アラインされていないメモリ アクセス動作の実行は HardFault の例外になります。

#### 4.7.2 メモリ エンディアン

Cortex-M0+ は、ワードの最下位バイトが最下位アドレスに保存され、最上位バイトが最上位アドレスに保存されるリトルエンディアン フォーマットを使用します。

### 4.8 Systick タイマー

Systick タイマーは NVIC と統合され、SYSTICK 割り込みを生成します。この割り込みはリアルタイム システムのタスク管理に使用することができます。タイマーにはカウントダウン値として使用可能な 24 ビットのリロード レジスタがあります。Systick タイマーは Cortex-M0+ 内部クロックまたは低周波数クロック (LF\_CLK) のいずれかを信号源として使用します。

### 4.9 デバッグ

PSoC 4 は SWD に基づくデバッグ インターフェースを持ちます。4 つのブレークポイント (アドレス) コンパレーターおよび 2 つのウォッチポイント (データ) コンパレーターを備えています。

# 5. 割り込み

PSoC® 4 の Arm Cortex-M0+ (CM0+) CPU は割り込みと例外をサポートしています。割り込みとは、タイマー、シリアル通信ブロック、ポートピン信号などの CPU の外部ペリフェラルによって生成されるイベントのことです。例外とは、メモリアクセス フォルトと内部システム タイマー イベントなどの CPU によって生成されるイベントのことです。割り込みと例外が発生すると、いずれも現時点のプログラム実行が停止され、例外ハンドラーまたは割り込みサービス ルーチン (ISR) が CPU によって実行されます。デバイスは割り込みハンドラー／ISR と例外ハンドラーの両方が統合された例外ベクタ テーブルを持っています。

## 5.1 特長

PSoC 4 が対応する割り込み機能は次の通り：

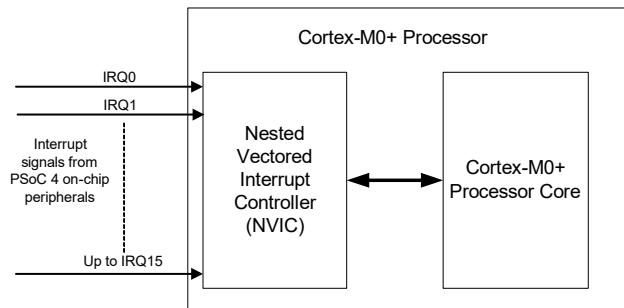

- 16 個の割り込みをサポート

- ネスト型ベクタ割り込みコントローラー (NVIC) が CPU コアに統合され、低い割り込みレイテンシの実現

- ベクタ テーブルは、フラッシュまたは SRAM のいずれかに配置することが可能

- 各割り込みに 0 から 3 までの優先度を設定可能

- レベル トリガーおよびパルス トリガー割り込み信号

## 5.2 動作原理

図 5-1. PSoC 4 割り込みブロック図

図 5-1 に割り込み信号と Cortex-M0+ CPU との関係を示します。PSoC 4 は 16 個の割り込みがあり、これらの割り込み信号は NVIC によって処理されます。NVIC は個々の割り込みの有効／無効の制御、優先度管理、CPU コアとの通信を担当します。CPU の外部周辺機器によって生成される割り込みと違い、例外は CM0+ のコアで生成されるイベントの一部であるため、図 5-1 に表示されていません。

## 5.3 割り込みと例外の動作

### 5.3.1 割り込み／例外の処理

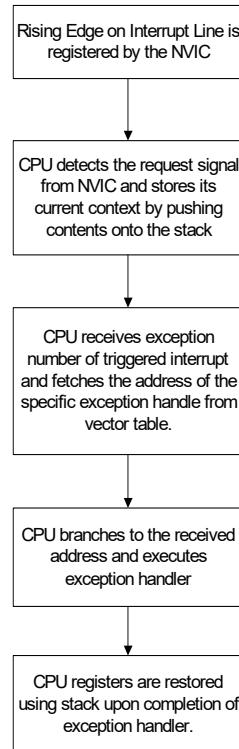

割り込みまたは例外のイベントがトリガーされると、以下の一連のイベントが発生します：

1. すべての割り込み信号がアイドルまたは非アクティブの状態であり、プロセッサがメインコードを実行している状態で、いずれかの割り込みラインが立ち上がったことが NVIC に認識されます。割り込みラインは CPU の処理を待機し、保留状態にします。

2. NVIC からの割り込み要求信号を検出する際に、CPU はスタック上に CPU レジスタの内容をプッシュすることで現在のコンテキストを保存します。

3. また、CPU はトリガーされた割り込みの例外番号を NVIC から受け取ります。**表 5-1** に示すように、すべての割り込みと例外は固有の例外番号を持っています。この例外番号を使用することで CPU は具体的な例外ハンドラー アドレスをベクターテーブルからフェッチします。

4. CPU はこのアドレスへ分岐し、あとに続く例外ハンドラーを実行します。

5. 例外ハンドラーが終了すると、CPU レジスタはスタック ポップ動作を行い元の状態に復元されます。CPU はメインコードの実行を再開します。

図 5-2. トリガーされた割り込みの処理

NVIC が割り込みの処理中に別の割り込み要求を受ける場合、または複数の割り込み要求を同時に受ける場合、これらのすべての割り込み優先度を評価し、CPU に最も高い優先度の割り込みの例外番号を送信します。従って、優先度の高い割り込みは優先度の低い ISR の実行をいつでもブロックすることができます。

例外は割り込みが処理される場合と同じ方法で処理されます。各イベントには固有の例外番号があり、その番号は適切な例外ハンドラーを実行するために CPU で使用されます。

### 5.3.2 レベルおよびパルス割り込み

NVIC は、割り込みライン (IRQ0 ~ IRQ15) で、レベルとパルス信号の両方に対応します。割り込みソースに応じてレベルおよびパルスのどちらかに分類されます。

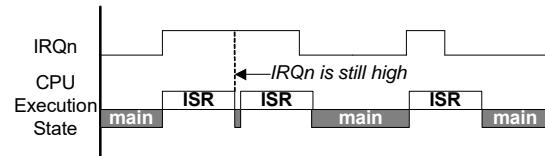

図 5-3. レベル割り込み

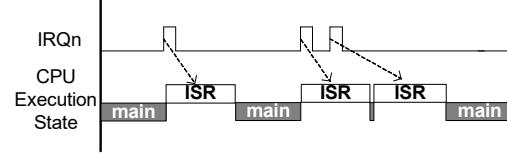

図 5-4. パルス割り込み

図 5-3 と 図 5-4 はレベルとパルス割り込みの動作を示しています。以下のイベントシーケンスは、割り込みラインが最初に非アクティブ（論理 LOW）であるとして、レベルとパルス割り込みの処理を示しています。

1. 割り込み信号の立ち上がりエッジで、NVIC は割り込み要求を登録します。割り込みは保留状態になります。その割り込み要求が CPU で未処理であることを意味します。

2. NVIC は割り込み要求信号とともに例外番号を CPU に送信します。CPU が ISR の実行を開始すると、割り込みの保留状態がクリアされます。

3. ISR が CPU によって実行されている間に割り込み信号の立ち上がりエッジが検出されると、それは 1 つの保留された割り込み要求として記録されます。現在の ISR の実行が完了すると保留中の割り込みが処理されます（パルス割り込みについては図 5-4 を参照してください）。

4. ISR の完了後に割り込み信号がまだ HIGH である場合、一度保留された後、続いて ISR が実行されます。図 5-3 は割り込み信号が HIGH である限り ISR が実行されるレベルトリガーハードウェア割り込みを示しています。

### 5.3.3 例外ベクタ テーブル

例外ベクタ テーブル ( 表 5-1 ) はすべての例外ハンドラーに対応するエントリ ポイント アドレスを格納します。CPU は例外番号に基づき、適切なアドレスをフェッチします。

表 5-1. 例外ベクタ テーブル

| 例外番号  | 例外                       | 例外の優先度                | ベクタ アドレス                                                               |

|-------|--------------------------|-----------------------|------------------------------------------------------------------------|

| -     | 初期スタック ポインタの値            | 該当なし (NA)             | Base_Address - 0x00000000 ( フラッシュ メモリの開始 ) または 0x20000000 ( SRAM の開始 ) |

| 1     | リセット                     | -3、最優先                | Base_Address + 0x0C                                                    |

| 2     | マスク不可能割り込み (NMI)         | -2                    | Base_Address + 0x08                                                    |

| 3     | HardFault                | -1                    | Base_Address + 0x0C                                                    |

| 4-10  | 予約済み                     | 該当なし                  | Base_Address + 0x10 to Base_Address + 0x28                             |

| 11    | スーパバイザ コール (SVCall)      | コンフィギュレーション可能 (0 ~ 3) | Base_Address + 0x2C                                                    |

| 12-13 | 予約済み                     | 該当なし                  | Base_Address + 0x30 to Base_Address + 0x34                             |

| 14    | PendSupervisory (PendSV) | コンフィギュレーション可能 (0 ~ 3) | Base_Address + 0x38                                                    |

| 15    | システム タイマー (SysTick)      | コンフィギュレーション可能 (0 ~ 3) | Base_Address + 0x3C                                                    |

| 16    | 外部割り込み (IRQ0)            | コンフィギュレーション可能 (0 ~ 3) | Base_Address + 0x40                                                    |

| ...   | ...                      | コンフィギュレーション可能 (0 ~ 3) | ...                                                                    |

| 31    | 外部割り込み (IRQ15)           | コンフィギュレーション可能 (0 ~ 3) | Base_Address + 0x7C                                                    |

表 5-1 では最初のワード (4 バイト) を例外番号 0 として記載していません。例外テーブルの最初のワードは、メイン スタック ポインタ (MSP) の値をデバイスリセットで初期化するために使用されるためです。例外とみなされません。ベクターテーブルは、ベクターテーブル オフセットレジスタ (VTOR) を変更することにより、メモリマップ ( フラッシュ または SRAM ) の任意の場所に配置できます。このレジスタは、0xE000ED08 にある CM0+ のシステム制御空間の一部です。このレジスタは、ベクターテーブル アドレスのビット 31:8 を取ります。ビット 7:0 は予約済みです。したがって、ベクターテーブルのアドレスは 256 バイトに揃える必要があります。SRAM にベクタ テーブルを移動させる利点は、SRAM ベクタ テーブルの内容を変更することにより例外ハンドラーのアドレスを動的に変更することができるのです。しかし、不揮発性フラッシュ メモリのベクタ テーブルをフラッシュ メモリ書き込みによって変更する必要があります。

CPUSS\_SYSREQ レジスタの DIS\_RESET\_VECT\_REL ビットが設定されていない限り、スタックポインタを取り出し、ベクタをリセットするために、フラッシュアドレス 0x00000000 および 0x00000004 の読み出しが SROM の最初の 8 バイトにリダイレクトされます。リセット時のこのビットのデフォルト値は 0 で、リセットベクタが常に SROM から取り出されるようにします。アドレス 0x00000000 および 0x00000004 からのフラッシュ読み取りを許可するためには、DIS\_RESET\_VECT\_REL ビットを「1」に設定する必要があります。スタック ポインタのベクタは、スタック ポインタがリセット時にロードされるアドレスを保持します。リセット ベクタはブート シーケンスのアドレスを保持します。このマッピングは、デバイス リセットが解除される時

に SROM からのスタック ポインタおよびリセット ベクタのデフォルト アドレスを使用するために行われます。リセットのために、まず SROM 内のブート コードを実行し、その後 CPU がフラッシュにハンドラーを実行するためにフラッシュの 0x00000004 アドレスにジャンプします。SRAM ベクタテーブルのリセット例外アドレスは使用されません。

また、CPUSS\_SYSREQ レジスタの SYSREQ ビットがセットの場合、0x00000008 フラッシュ アドレスの読み出しが、NMI ベクタ アドレスを取り出すために、フラッシュの代わりに SROM にリダイレクトされます。0x00000008 アドレスでフラッシュを読み出すために CPUSS\_SYSREQ をリセットします。

例外ソース (1 ~ 15 までの例外番号) は 5.4 例外ソースで説明します。表 5-1 で予約としてマークされている例外は、使用されていませんが、ベクタ テーブルにそれらのための予約アドレスを持っています。例外ソース (16 ~ 31 までの例外番号) は 5.5 割り込みソースで説明します。

## 5.4 例外ソース

この節では表 5-1 に記載されている ( 例外番号 1 ~ 15 ) 例外ソースについて説明します。

### 5.4.1 リセット例外

デバイス リセットは PSoC 4 で例外として扱われます。最も優先度の高い例外である -3 の優先度に常に有効にされています。デバイス リセットは、パワーオンリセット (POR)、XRES ピンによる外部リセット信号またはウォッチドッグ

リセットなど複数の原因で発生する可能性があります。デバイスがリセットされると、デバイスコンフィグレーションのための初期ブートコードが監視読み出し専用メモリ(SROM)から実行されます。SROMメモリのブートコードやその他のデータはサイプレスによってプログラムされ、外部ユーザーは読み書きできません。SROMのブートシーケンスが完了した後、CPUのコード実行はフラッシュメモリへジャンプします。フラッシュメモリアドレス0x00000004(表5-1例外#1)はフラッシュメモリ内の起動コードの位置を格納します。CPUはこのアドレスからのコードの実行を開始します。リセット解除時点でデバイスはフラッシュベクタテーブルが選択された状態となるため、SRAMベクタテーブルのリセット例外アドレスが使用されることはないことにご注意ください。リセットがアサート解除された後、SRAMベクタテーブルを選択するためのレジスタコンフィギュレーションはフラッシュの起動コードの一部として実行されます。

#### 5.4.2 マスク不可能割り込み(NMI)例外

マスク不可能な割り込み(NMI)はリセットに次いで最も優先度の高い例外です。これは-2の固定優先度によって常に有効にされています。デバイスでNMI例外をトリガーするものは2つあります：

- **NMIPENDSETビット(ユーザーNMI例外)をセットすることによるNMI例外**: NMI例外は割り込み制御状態レジスタ(CM0P\_ICSRレジスタ)にNMIPENDSETビットを立てることにより、ソフトウェアでトリガーすることができます。このビットを立てることでアクティブなベクタテーブル(フラッシュまたはSRAMベクタテーブル)に示されたNMIハンドラーが実行されます。

- **システムコールNMI例外**: フラッシュ書き込み動作とフラッシュチェックサム動作などの不揮発プログラム動作のために使用されます。CPUSS\_SYSREQレジスタにSYSCALL\_REQビットを立てることによってトリガーされます。SYSCALL\_REQビットによってトリガーされたNMI例外は、SROM内蔵されたNMI例外ハンドラーのコードを常に実行します。フラッシュまたはSRAM例外ベクタテーブルはシステムコールNMI例外のために使用されません。SROMのNMIハンドラーコードは、ユーザーによって変更されてはならない不揮発性プログラミングルーチンが含まれているため、読み出し／書き込みのアクセスができません。

#### 5.4.3 HardFault例外

HardFaultは、通常または例外処理中のエラーが原因で発生する常に有効な例外です。HardFaultは-1の優先度を持ち、優先度が設定できる他の例外よりも高い優先度を持っています。HardFault例外は、異なる種類のフォルト条件(未定義命令の実行や無効なメモリアドレスへのアクセスなど)のためのキャッチオール例外です。CM0+CPUは、HardFault例外ハンドラーにフォルトステータス情報を提供していません。ただし、ソフトウェアがフォルト状態から回復す

る能力を有している場合、ハンドラーに例外からの復帰と実行の継続ができるようにしています。

#### 5.4.4 スーパバイザコール(SVCall)例外

スーパバイザコール(SVCall)はCPUがSVC命令をアプリケーションコードの一部として実行することにより発生する常に有効な例外です。アプリケーションソフトウェアはSVC命令を使用して、オペレーティングシステムへの呼び出しを行い、サービスを提供させます。これはスーパバイザコールとして知られています。SVC命令はアプリケーションがシステムへの特権アクセスを要求するスーパバイザコールを発行することを可能にします。PSoC4のCM0+がシステム呼び出しNMI例外に対してSVCall例外に関連しない特権モードを使用することにご注意ください。(特権モードの詳細は[68ページのチップ動作モードの章](#)を参照してください)。デバイスではアーキテクチャレベルでSVCallをサポートする他の特権モードはありません。アプリケーション開発者は、エンドアプリケーションの要件に応じてSVCall例外ハンドラーを定義する必要があります。

SVCall例外の優先度は、システムハンドラー優先度レジスタ2(SHPR2)の2ビットフィールドPRI\_11[31:30]に書き込むことによって、0と3の間の値に設定することができます。SVC命令が実行された時、SVCall例外が保留状態に入り、CPUによる処理を待ちます。システムハンドラー制御および状態レジスタ(SHCSR)のSVCALLPENDEDビットは、SVCall例外の保留状態を確認、変更に使用することができます。

#### 5.4.5 PendSV例外

PendSVはSVCallに類似するスーパバイザコールの例外です。通常ソフトウェアで生成されます。PendSVは常に有効であり、その優先度を設定できます。PendSV例外は、割り込み制御状態レジスタであるCM0P\_ICSRのPENDSVSETビットをセットすることでトリガーされます。このビットをセットすると、PendSV例外が保留状態に入り、CPUによる処理を待ちます。PendSV例外の保留状態は、割り込み制御状態レジスタであるCM0P\_ICSRのPENDSVCLRビットを立てることによりクリアすることができます。PendSV例外の優先度は、システムハンドラー優先度レジスタ3(CM0P\_SHPR3)の2ビットフィールドPRI\_14[23:22]に値を書き込むことによって、0と3の間に設定できます。詳細については[Arm v6-M Architecture Reference Manual](#)を参照してください。

## 5.4.6 SysTick 例外

PSoC 4 の CM0+ CPU は、SysTick と呼ばれるシステム タイマーをその内部アーキテクチャの一部として搭載しています。SysTick は、RTOS ティック タイマー、高速アラーム タイマー、単純なカウンターなどの様々な時間管理の目的のために簡単な24ビット デクリメントのカウンターを提供しています。SysTick タイマーはそのカウントがゼロに達した時に割り込みを生成するよう設定することができ、その割り込みを SysTick 例外と呼びます。この例外は、SysTick 制御 およびステータスレジスタ (CM0P\_SYST\_CSR) の TICK-INT ビットをセットすることで有効になります。SysTick 例外の優先度は、システム ハンドラー 優先度 レジスタ 3 (CM0\_SHPR3) の 2 ビット フィールド PRI\_15[31:30] に値を書き込むことによって、0 と 3 の間に設定できます。SysTick 例外は割り込み制御状態レジスタ CM0P\_ICSR の PENDSTSETb ビットに 1 を書き込むことによって、どの瞬間ににおいても常にソフトウェアで生成することができます。同様に、SysTick 例外の保留状態は、割り込み制御状態レジスタである CM0P\_ICSR の PENDSTCLR ビットをセットすることによってクリアすることができます。

表 5-2. PSoC 4 割り込みソースの一覧

| 割り込み  | Cortex-M0+ 例外番号 | 割り込みソース                     |

|-------|-----------------|-----------------------------|

| NMI   | 2               | SYS_REQ                     |

| IRQ0  | 16              | GPIO 割り込み - ポート 0           |

| IRQ1  | 17              | GPIO 割り込み - ポート 1           |

| IRQ2  | 18              | GPIO 割り込み - ポート 2           |

| IRQ3  | 19              | GPIO 割り込み - ポート 3           |

| IRQ4  | 20              | GPIO 割り込み - すべてのポート         |

| IRQ5  | 21              | LPCOMP ( 低消費電力コンパレータ )      |

| IRQ6  | 22              | WDT ( ウオッチドッグ タイマー )        |

| IRQ7  | 23              | SCB0 ( シリアル通信ブロック 0 )       |

| IRQ8  | 24              | SCB1 ( シリアル通信ブロック 1 )       |

| IRQ9  | 25              | SPCIF 割り込み                  |

| IRQ10 | 26              | CSD (CapSense)              |

| IRQ11 | 27              | TCPWM0 ( タイマー／カウンター／PWM 0 ) |

| IRQ12 | 28              | TCPWM1 ( タイマー／カウンター／PWM 1 ) |

| IRQ13 | 29              | TCPWM2 ( タイマー／カウンター／PWM 2 ) |

| IRQ14 | 30              | TCPWM3 ( タイマー／カウンター／PWM 3 ) |

| IRQ15 | 31              | TCPWM4 ( タイマー／カウンター／PWM 4 ) |

## 5.6 例外の優先度

CPU によって処理される必要がある複数の例外がある時、例外の優先度は例外裁定に用いられます。PSoC 4 は異なる例外に優先度を設定することを柔軟に行えます。リセット、NMI および HardFault 以外のすべての例外に優先度を割り当てる

## 5.5 割り込みソース

PSoC 4 は、周辺機器からの 16 個の割り込み (IRQ0 ~ IRQ15 または例外番号 16 ~ 31) に対応しています。各割り込みのソースは表 5-3 に記載されています。PSoC 4 は割り込みラインそれぞれのための柔軟な選択機構を提供しています。割り込みは、TCPWM およびシリアル通信ブロックなどのオンチップ周辺機器からの標準の割り込みを含みます。生成された割り込みは、通常異なるペリフェラル ステートとの論理 OR です。ペリフェラル ステータス レジスタは、割り込みを生成した条件を検出するために ISR で読み出されます。割り込みは通常、ペリフェラル ステータス レジスタが割り込みのクリアのために ISR で読み出されることを必要とするレベル割り込みです。ステータス レジスタが ISR で読み出されないと、割り込みがアサートされたままとなり、ISR が継続して実行されます。

GPIO 割り込みの詳細については 37 ページの [I/O システムの章](#) をご覧ください。

ことができます。リセット、NMI および HardFault 例外はそれぞれ -3、-2、-1 の固定された優先度を持っています。PSoC 4 では優先度番号が小さい方がより高い優先度を表します。よってリセット、NMI、HardFault の例外は最上位優先度になります。他の例外は優先度 0 ~ 3 を割り当てることができます。

PSoC 4 は優先度の高い例外が現在アクティブな例外andlerを阻止(割り込み)可能なネスト例外をサポートします。後から発生した例外の優先度がアクティブな例外と同じであれば、このブリエンプションは発生しません。CPU は優先度の高い例外を処理した後、優先度の低い例外andlerの実行を再開します。PSoC 4 の CM0+ CPU は最大 4 つの例外ネストを可能にします。CPU は同じ優先度の複数の例外要求を受信した場合、最小の例外番号のものが最初に処理されます。

1 から 15 までの例外番号の優先度を設定するためのレジスタは [29 ページの「例外ソース」](#) に説明されています。

割り込み優先順位レジスタ (CM0P\_IPR) に書き込むことによって、16 個の割り込み (IRQ0 ~ IRQ15) の優先度を設定することができます。[表 5-3](#) に示すように、これは 32 ビットレジスタのグループであり、各レジスタは 4 つの割り込みの優先度を格納します。レジスタの他のビットフィールドは使用されません。

表 5-3. 割り込み優先度レジスタのビット定義

| ビット   | 名称     | 説明              |

|-------|--------|-----------------|

| 7:6   | PRI_N0 | 割り込み番号 N の優先度   |

| 15:14 | PRI_N1 | 割り込み番号 N+1 の優先度 |

| 23:22 | PRI_N2 | 割り込み番号 N+2 の優先度 |

| 31:30 | PRI_N3 | 割り込み番号 N+3 の優先度 |

## 5.7 割り込みの有効と無効

NVIC はソフトウェアで 16 個の割り込みを個別に有効／無効にするためのレジスタを提供します。割り込みが有効にされない場合、NVIC はその割り込みラインの割り込み要求を処理しません。割り込み有効セット レジスタ (CM0P\_ISER) と割り込み有効クリア レジスタ (CM0P\_ICER) はそれぞれの割り込みを有効／無効にするために使用されます。これらは 32 ビット幅のレジスタで、各ビットは同じ番号の割り込みに対応しています。また、これらの割り込みのイネーブルステータスを取得するために、レジスタをソフトウェアで読み出すことができます。[表 5-4](#) はこの 2 つのレジスタのためのレジスタアクセス プロパティを示します。これらのレジスタにゼロを書き込んでも影響がないことにご注意ください。

表 5-4. 割り込みイネーブル／ディスエーブル レジスタ

| レジスタ                              | 動作   | ビット値 | 説明         |

|-----------------------------------|------|------|------------|

| 割り込みイネーブル セット レジスタ<br>(CM0P_ISER) | 書き込み | 1    | 割り込みを有効にする |

|                                   |      | 0    | 何もしない      |

|                                   | 読み出し | 1    | 割り込みが有効    |

|                                   |      | 0    | 割り込みが無効    |

| 割り込みイネーブル クリア レジスタ<br>(CM0P_ICER) | 書き込み | 1    | 割り込みを無効にする |

|                                   |      | 0    | 何もしない      |

|                                   | 読み出し | 1    | 割り込みが有効    |

|                                   |      | 0    | 割り込みが無効    |

CM0P\_ISER と CM0P\_ICER レジスタは割り込み (IRQ0 ~ IRQ15) のみに適用可能です。これらのレジスタは例外番号 1 ~ 11 までを有効／無効にするためには使用できません。[29 ページの「例外ソース」](#) で説明されているように、15 個の例外は別の手段で有効／無効にされます。

有効にされているかどうかに関わらず、Cortex-M0+ (CM0+) CPU の PRIMASK レジスタは優先度を設定できる例外をマスクするためのグローバルイネーブル レジスタとして使用されます。優先度を設定できる例外は [表 5-1](#) に記載されているリセット、NMI、HardFault を除くすべての例外を含みます。これらは優先度を 0 から 3 に設定することができ、0 が最高の優先度で、3 が最低の優先度です。PRIMASK レジスタの PM ビット (ビット 0) がセットされると、優先度を設定できる例外のいずれも CPU によって処理されながありませんが、PM ビットがクリアされた後、それらは CPU によって処理待ちの保留状態になります。

## 5.8 例外状態

各例外は以下のいずれかの状態にあります。

表 5-5. 例外状態

| 例外状態     | 意味                                                                                        |

|----------|-------------------------------------------------------------------------------------------|

| 非アクティブ   | 例外は非アクティブまたは保留中。例外が無効になっているか、有効な例外はトリガーされていない                                             |

| 保留中      | 例外要求が CPU/NVIC によって受信されており、例外が CPU による処理を待機中                                              |

| アクティブ    | CPU で処理されているが、例外andlerの実行が完了していない例外。優先度の高い例外は、優先度の低い例外の実行に割り込むことができる。この場合両方の例外がアクティブ状態になる |

| アクティブ・保留 | 例外がプロセッサによって処理されているが、その例外andlerの実行中に、同じソースからの保留中の要求がある                                    |

割り込み制御状態レジスタ (CM0P\_ICSR) はさまざまな例外状態を説明するステータス ビットが含まれています。

- CM0P\_ICSR の VECTACTIVE ビット ([8:0]) は現在実行中の例外番号を格納します。CPU が例外andlerを (CPU はスレッド モードにある) を実行していない場合、この値はゼロです。VECTACTIVE ビット フィールドが、アクティブ例外番号を格納するために使用される割り込みプログラム ステータス レジスタ (IPSR) のビット [8:0] の値と同じであることにご注意ください。

- CM0P\_ICSR の VECTPENDING ビット ([20:12]) は最上位優先度の保留中の例外の例外番号を格納します。保留中の例外が存在しない場合、この値はゼロです。

- CM0P\_ICSR の ISRPENDING ビット (ビット 22) は NVIC が生成した割り込み (IRQ0 ~ IRQ15) が保留状態にあることを示します。

### 5.8.1 保留中の例外

周辺装置が NVIC へ割り込み要求信号を生成するが、または例外イベントが発生する時、対応する例外は保留状態に入ります。CPU は対応する例外ハンドラー ルーチンの実行を開始すると、例外が保留状態からアクティブ状態へ変更されます。

割り込みの保留状態を設定またはクリアするための異なるレジスタビットを提供することにより、NVIC は 16 個の割り込みラインのソフトウェア保留を可能にします。割り込み保留セットレジスタ (CM0P\_ISPR) と割り込み保留クリアレジスタ (CM0P\_ICPR) は割り込みラインの保留状態をセットまたはクリアするために使用されます。これらは 32 ビット幅のレジスタで、各ビットは同じ番号の割り込みに対応しています。[表 5-6](#) にこの 2 つのレジスタのためのレジスタアクセスプロパティを示します。これらのレジスタにゼロを書き込んでも影響がないことにご注意ください。

表 5-6. 割り込み保留セット／クリア レジスタ

| レジスタ                          | 動作   | ビット値 | 説明           |

|-------------------------------|------|------|--------------|

| 割り込み保留セットレジスタ<br>(CM0P_ISPR)  | 書き込み | 1    | 割り込みを保留状態にする |

|                               |      | 0    | 何もしない        |

|                               | 読み出し | 1    | 割り込みが保留中     |

|                               |      | 0    | 割り込みが保留中でない  |

| 割り込み保留クリア レジスタ<br>(CM0P_ICPR) | 書き込み | 1    | 保留の割り込みをクリア  |

|                               |      | 0    | 何もしない        |

|                               | 読み出し | 1    | 割り込みが保留中     |

|                               |      | 0    | 割り込みが保留中でない  |

既にセットされているビットに保留ビットを設定しても結果は 1 つのみの ISR の実行です。対応する割り込みが有効になっているかどうかに関わらず、保留ビットの更新は可能です。割り込みが有効にされていない場合、割り込みラインが CM0P\_ISER レジスタに書き込んで有効化されるまで、保留状態に移行しません。

CM0P\_ISPR と CM0P\_ICPR レジスタは 16 個のペリフェラル割り込み (16 ~ 31 の例外番号) のみに使用されることにご注意ください。これらのレジスタは例外番号 1 ~ 11 までを保留するためには利用できません。[29 ページの「例外ソース」](#) で説明されているように、15 個の例外は別の手段で保留されます。

## 5.9 例外のスタック使用量

CPU はメイン コード (スレッド モードで) を実行し、例外要求が発生すると、CPU は汎用レジスタの状態をスタックに格納します。次に対応する例外ハンドラーの実行 (ハンドラー モード) を開始します。CPU は 8 個の 32 ビットの内部レジスタをスタックにプッシュします。これらのレジス

タはプログラムステータスレジスタ (PSR)、戻りアドレス、リンクレジスタ (LR または R14)、R12、R3、R2、R1 および R0 です。Cortex-M0+ には MSP と PSP の二種類のスタックポインタがあります。一度にアクティブにできるのは 1 種類のスタックポインタのみです。スレッド モードでは、制御レジスタのアクティブ スタックポインタビットが現在のアクティブ スタックポインタを定義するために使用されます。ハンドラー モードでは、MSP は常にスタックポインタとして使用されます。Cortex-M0+ のスタックポインタは常に下向きに進み、最後にプッシュされたデータを持つアドレスを示します。

CPU がスレッド モードにあり、例外要求が発生した場合、CPU は汎用レジスタの内容を格納するために制御レジスタで定義されたスタックポインタを使用します。スタック プッシュの動作後、例外ハンドラーの実行をするために、CPU はハンドラー モードになります。現在の例外の実行中に別の優先度の高い例外が発生すると、CPU がハンドラー モード中であるため、MSP はスタックのプッシュ／ポップ動作に使用されます。詳細は [22 ページの Cortex-M0+ CPU の章](#) をご覧ください。

Cortex-M0+ はサービス割り込みにおける待ち時間を削減するためにテールチェーンと後着の 2 つの技術を使用しています。これらの技術は外部ユーザーには見えず、内部プロセッサーアーキテクチャの一部です。テール チェインと後着のメカニズムの詳細については [Arm Infocenter](#) をご覧ください。

## 5.10 割り込みと低消費電力モード

特定の周辺割り込み要求が生成された時に PSoC 4 は、低消費電力モードからのデバイス復帰を可能にします。ウェイクアップ割り込みコントローラー (WIC) ブロックは、1 つまたは複数のウェイクアップ ソースが割り込み信号を生成した時に、デバイスがアクティブ モードに移行するために、ウェイクアップ信号を生成します。アクティブ モードに入った後、周辺割り込みの ISR が実行されます。

CM0+ CPU で実行される割り込み待機 (WFI) 命令は、スリープ および ディープスリープ モードへの遷移をトリガします。異なる低消費電力モードに入るシーケンスの詳細は [69 ページの消費電力モードの章](#) を参照してください。チップ低消費電力モードは固定機能割り込みソースの 2 つの分類があります：

- ディープスリープおよびハイバネート モードのみで使用可能な固定機能の割り込みソース (ウォッチドッグタイマー割り込み、)

- アクティブ モードのみで使用可能な固定機能の割り込みソース (他のすべての固定機能割り込み)

## 5.11 例外の初期化とコンフィギュレーション

この節は PSoC 4 での例外の初期化とコンフィギュレーションに関するさまざまなステップを説明します。

1. 例外ベクタ テーブル位置のコンフィギュレーション：例外を使用する最初のステップは要求に基づき、フラッシュ メモリまたは SRAM のいずれかにベクタ テーブルを配置することです。このコンフィギュレーションは、VTOR レジスタのビット 31:28 に、ベクタ テーブルが存在するフラッシュまたは SRAM アドレスの値を書き込むことによって行われます。このレジスタ書き込みはデバイスの初期化コードの一部として実行されます。

アプリケーションがベクタ アドレスを動的に変更する必要がある場合、ベクタ テーブルが SRAM で利用できるようにすることをお勧めします。テーブルがフラッシュに配置されている場合には、フラッシュ書き込み動作でベクタ テーブルの内容を変更する必要があります。PSoC Creator IDE はデフォルトで SRAM にベクタ テーブルを配置しています。

2. 個別例外のコンフィギュレーション：次のステップはアプリケーションに必要な個別の例外を設定することです。

- a. 例外または割り込みソースのコンフィギュレーションについては、割り込みの発生条件の設定が含まれています。レジスタ コンフィギュレーションは要求された具体的な例外に依存します。

- b. 例外ハンドラー機能を定義し、例外ベクタ テーブルへ機能のアドレスを書き込みます。[表 5-1](#) に例外ベクタ テーブル形式を示します。例外ハンドラーのアドレスがテーブル内の適切な例外番号エントリに書き込まれる必要があります。

- c. [31 ページ の「例外の優先度」](#) で説明したように例外の優先度を設定します。

- d. [32 ページ の「割り込みの有効と無効」](#) で説明したように例外を有効にします。

## 5.12 レジスタ

表 5-7. レジスター一覧

| レジスタ名         | 説明                          |

|---------------|-----------------------------|

| CM0P_ISET     | 割り込みイネーブル セット レジスタ          |

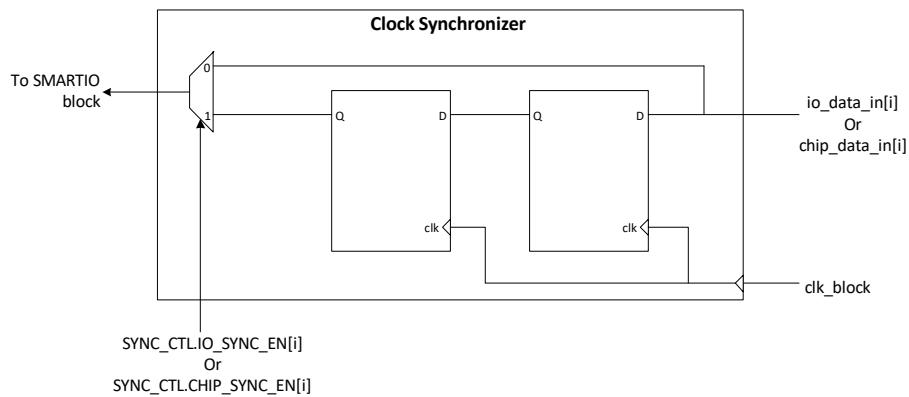

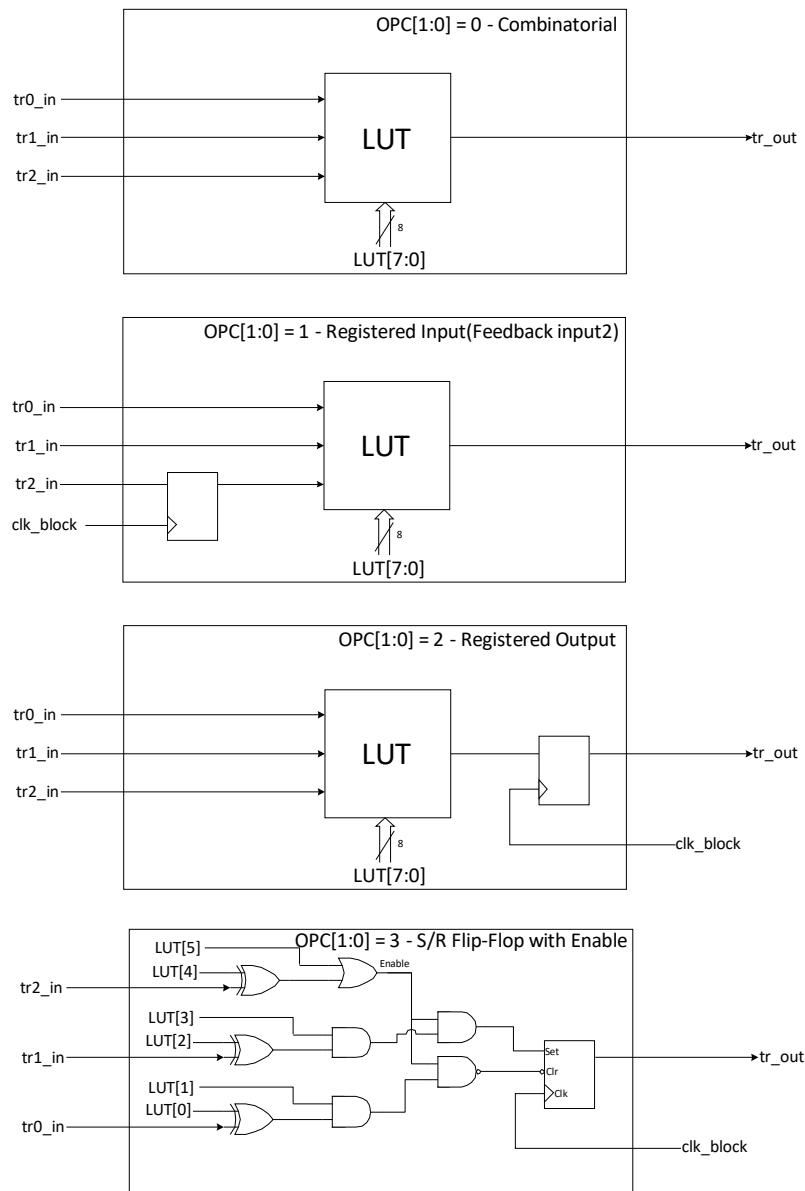

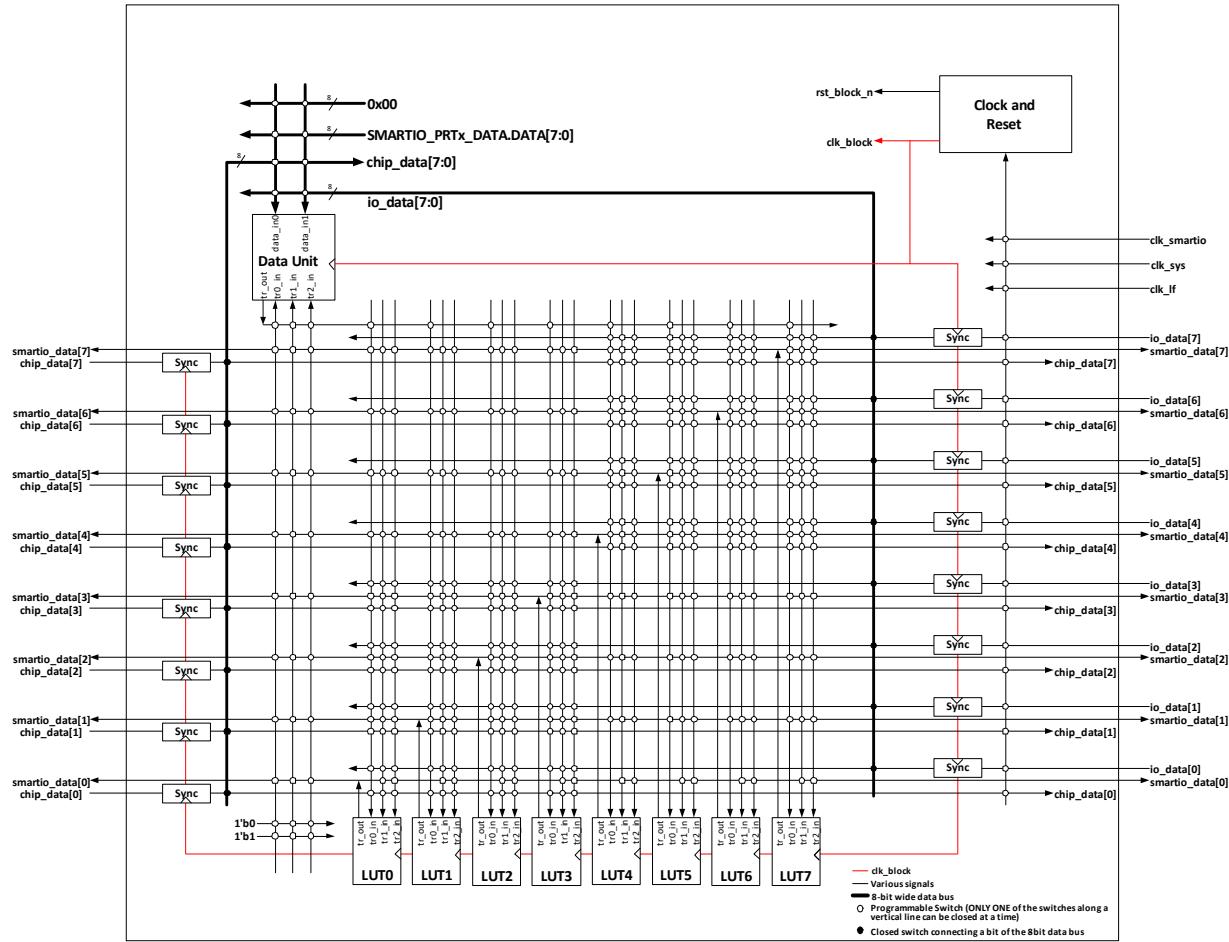

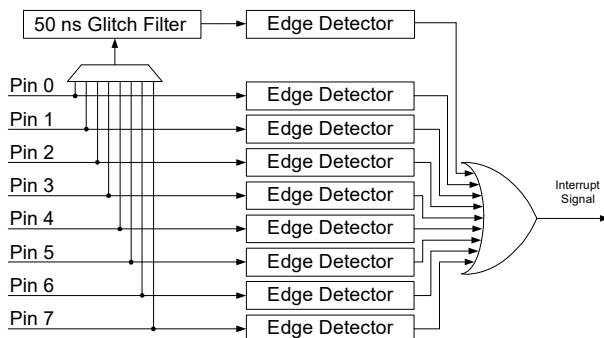

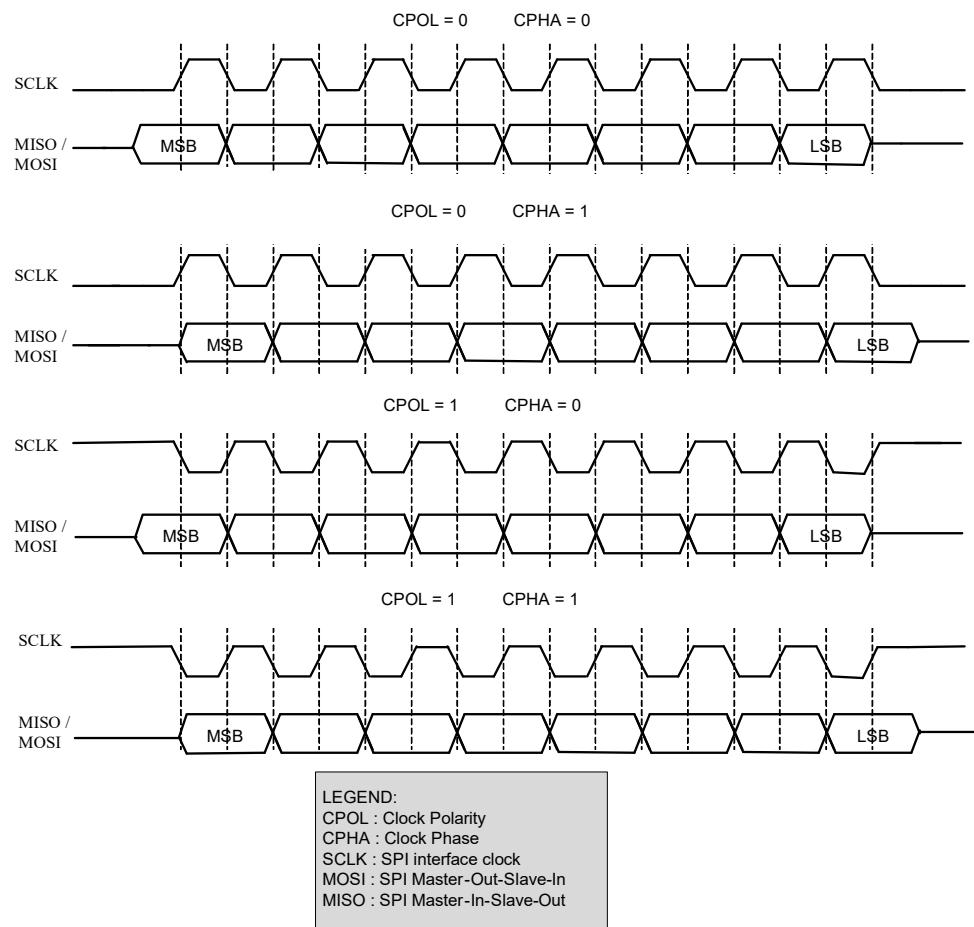

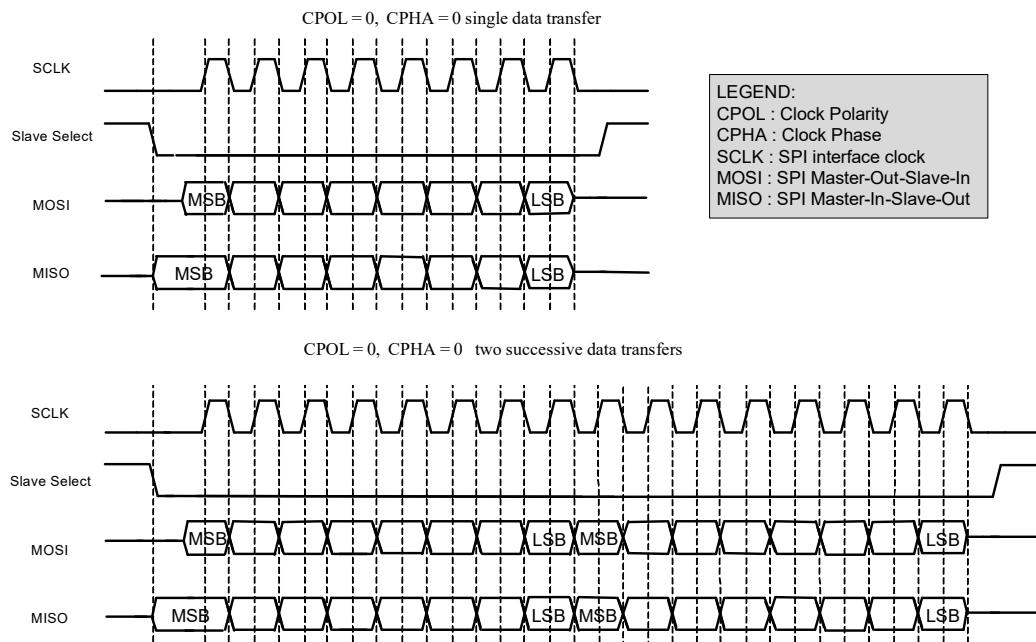

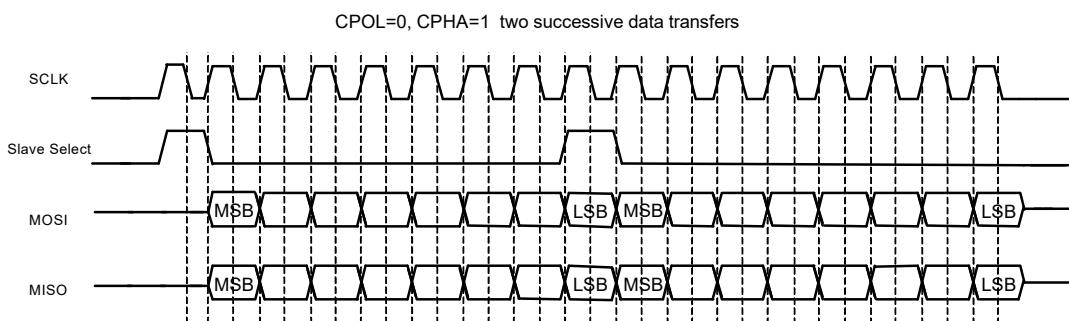

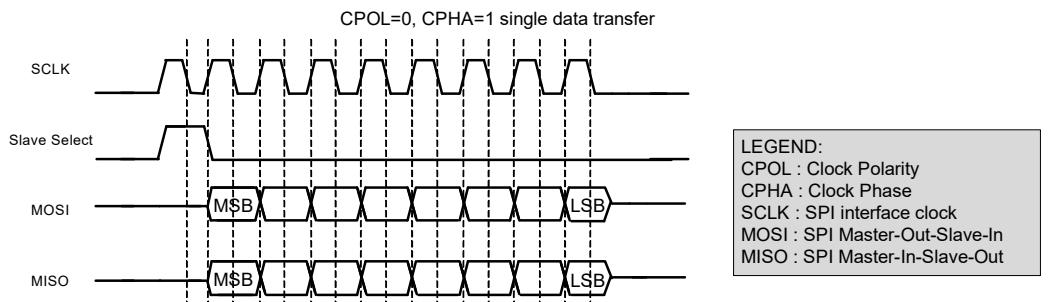

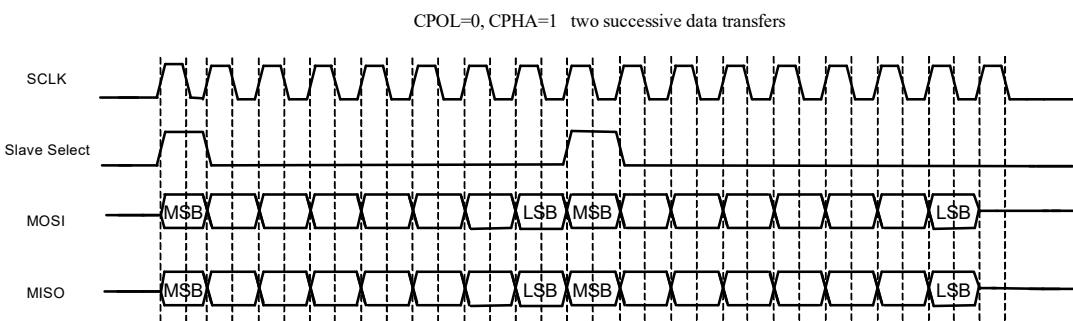

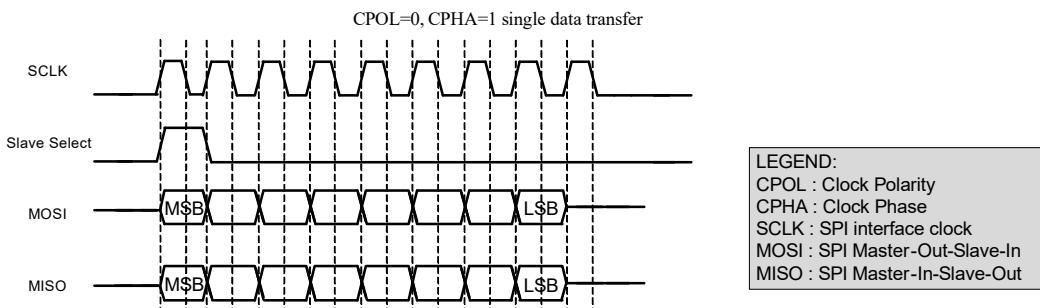

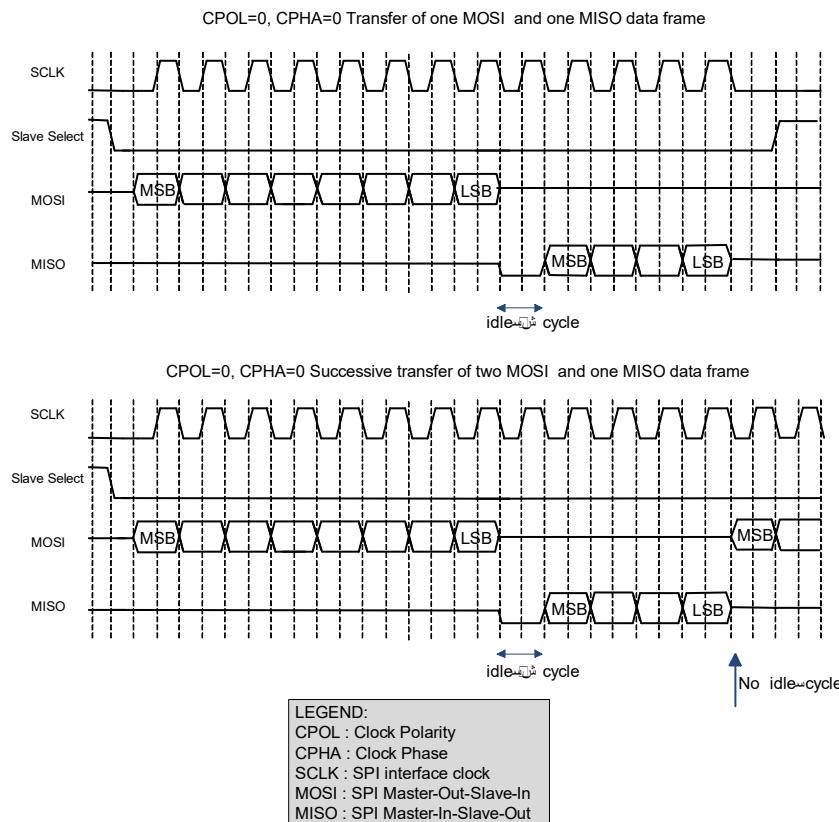

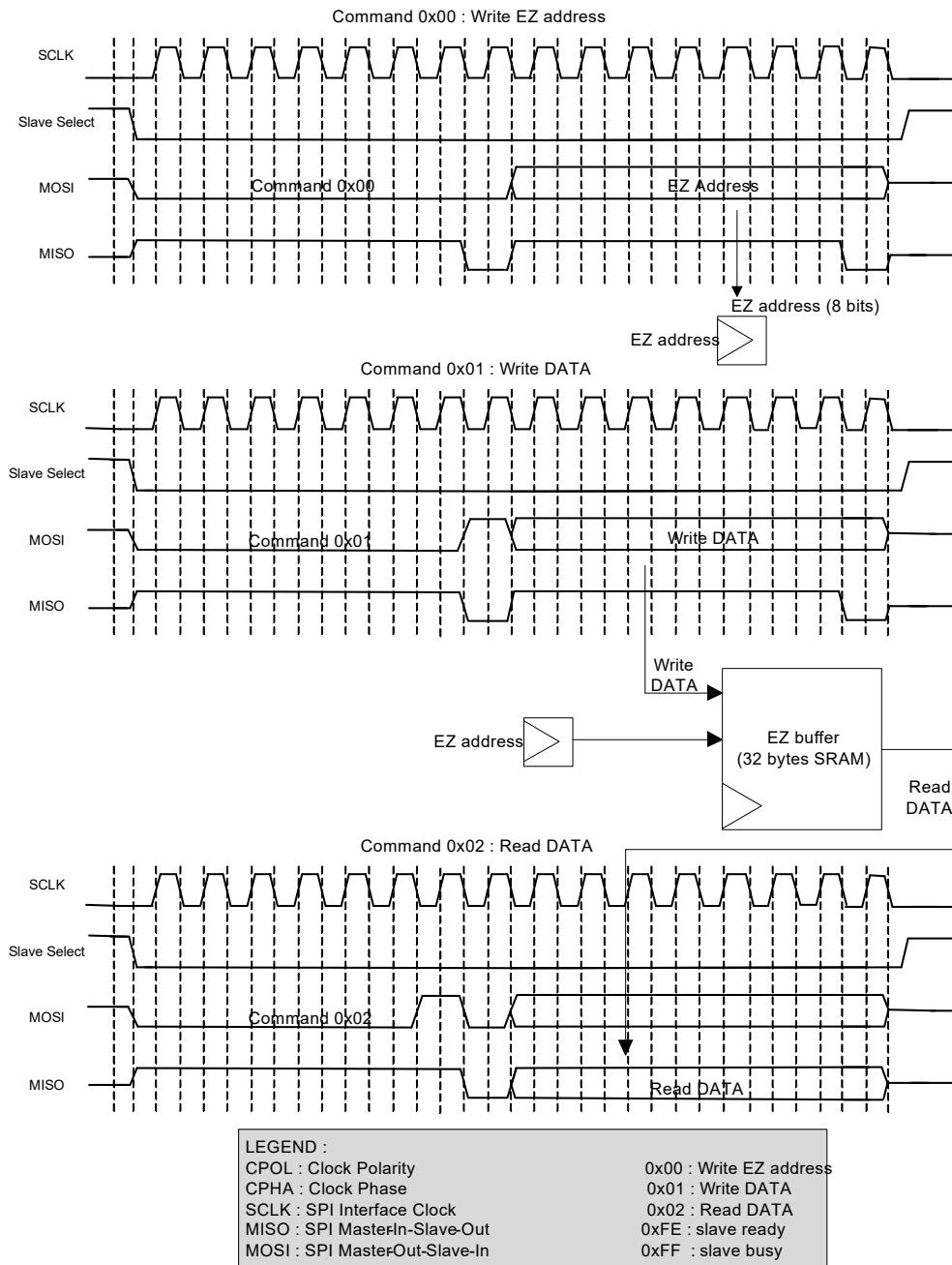

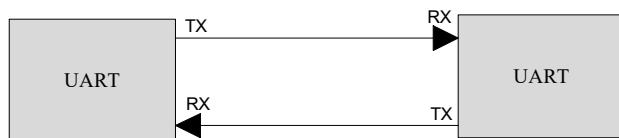

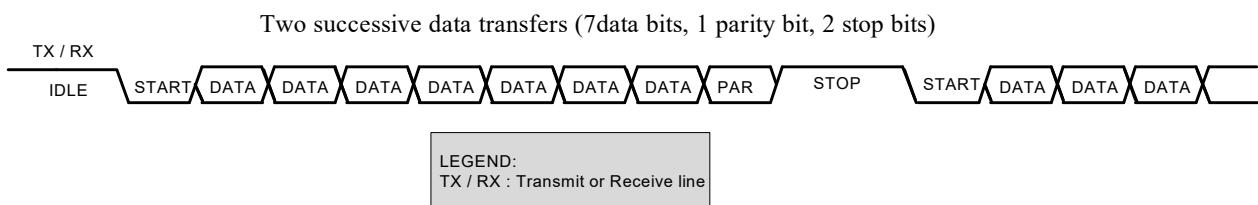

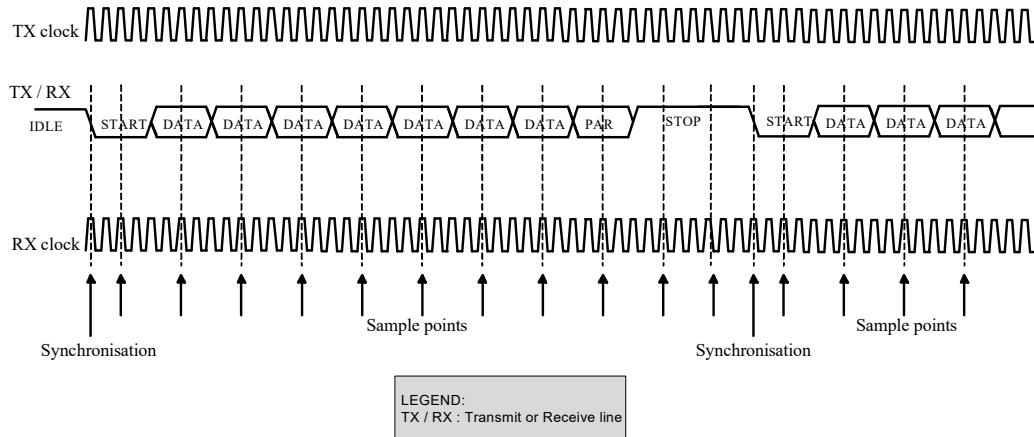

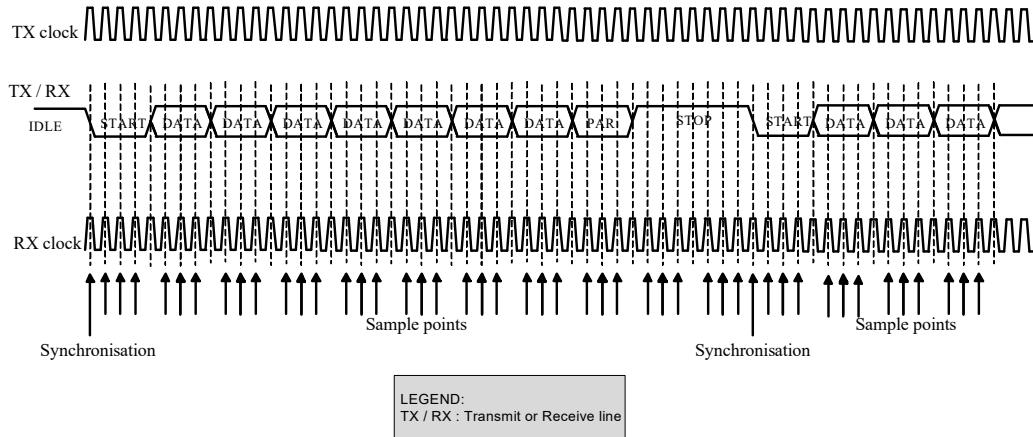

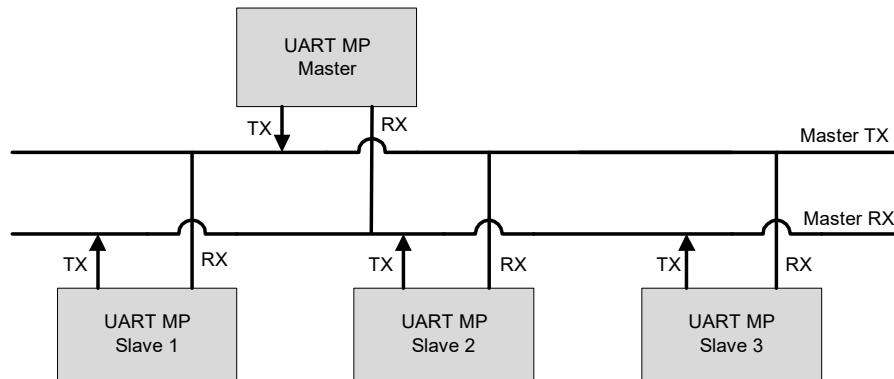

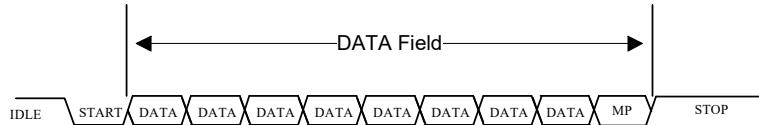

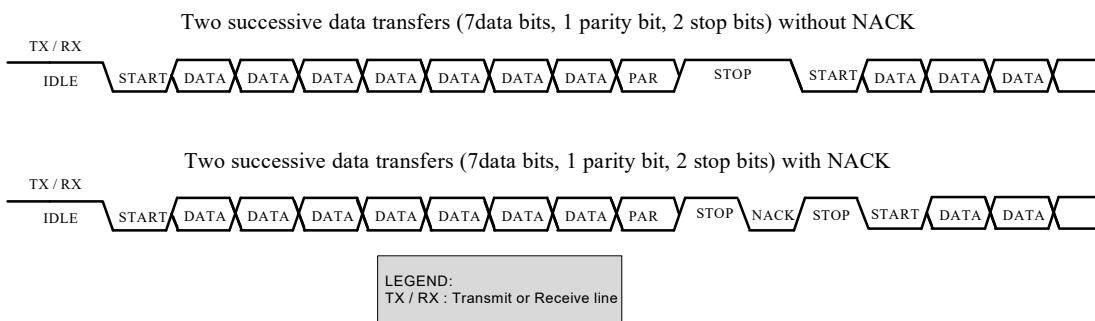

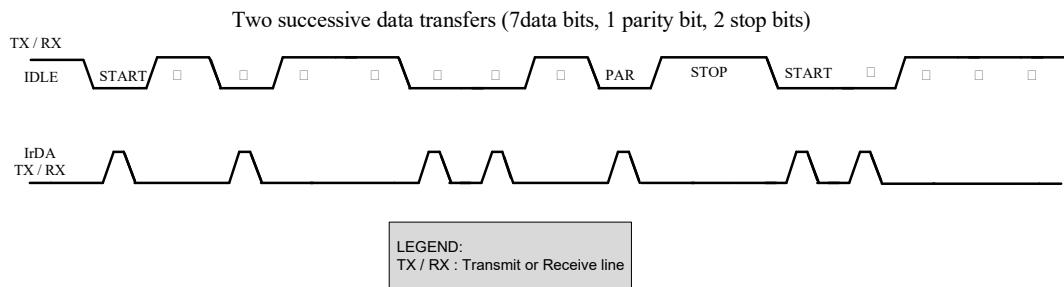

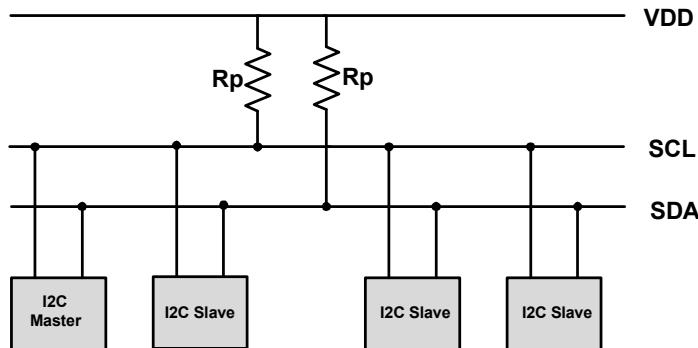

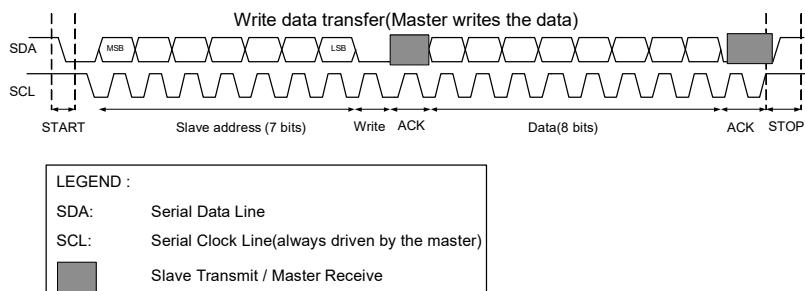

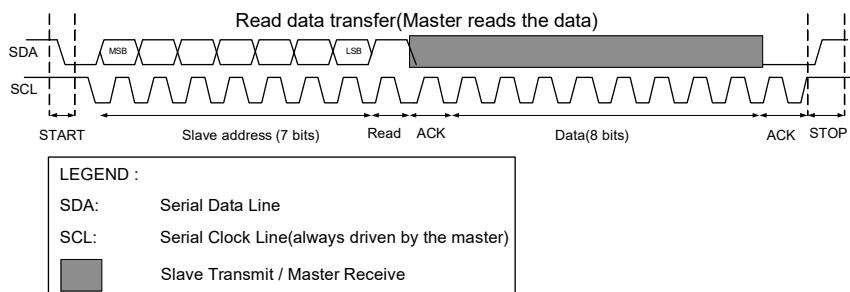

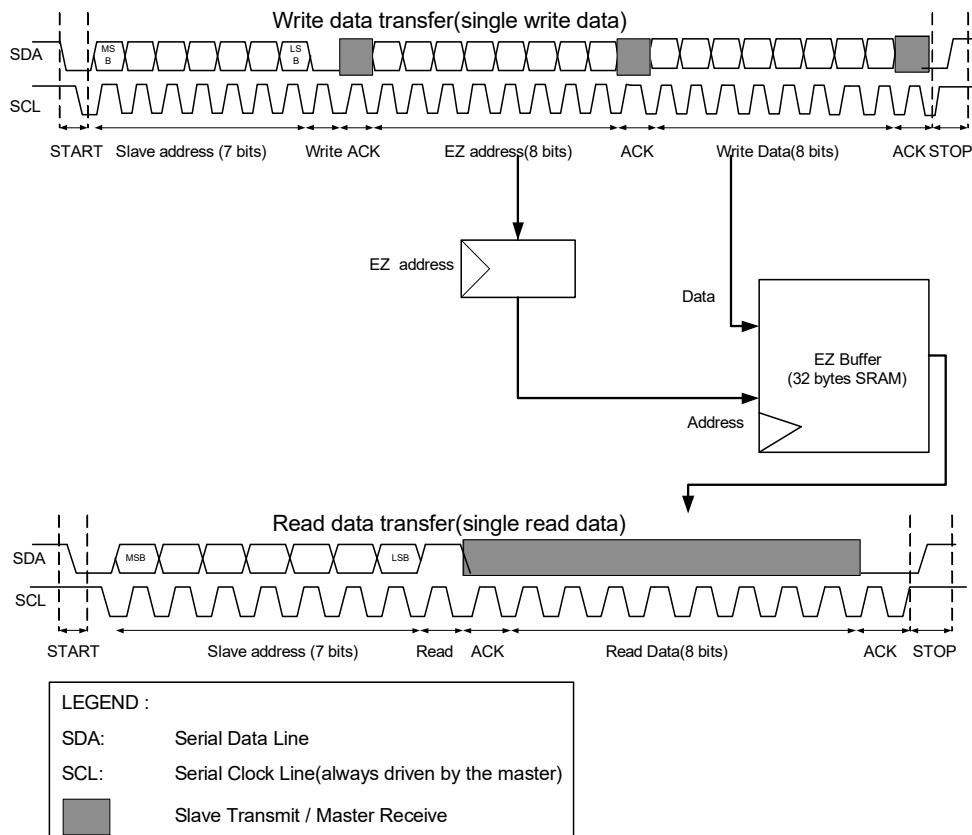

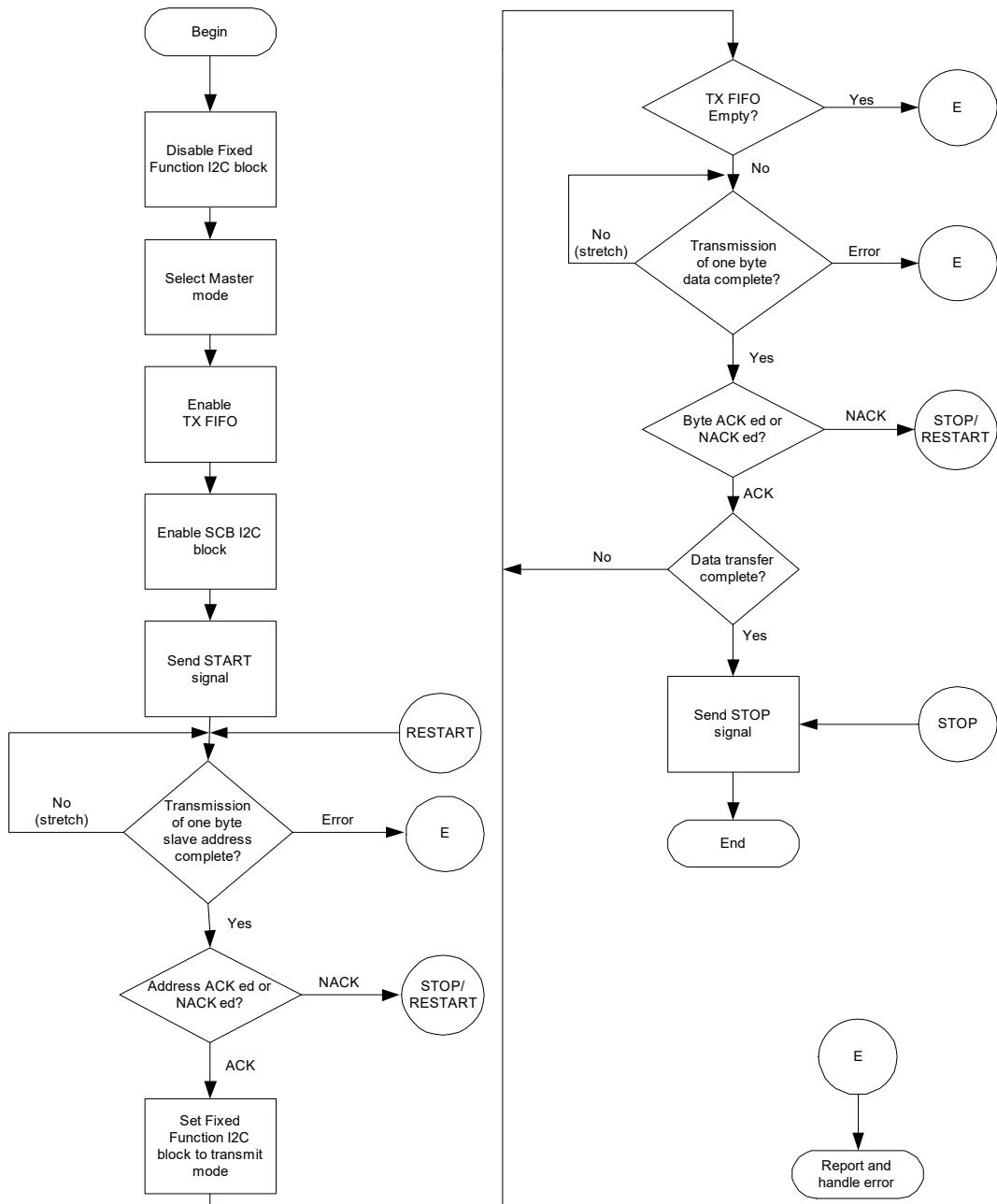

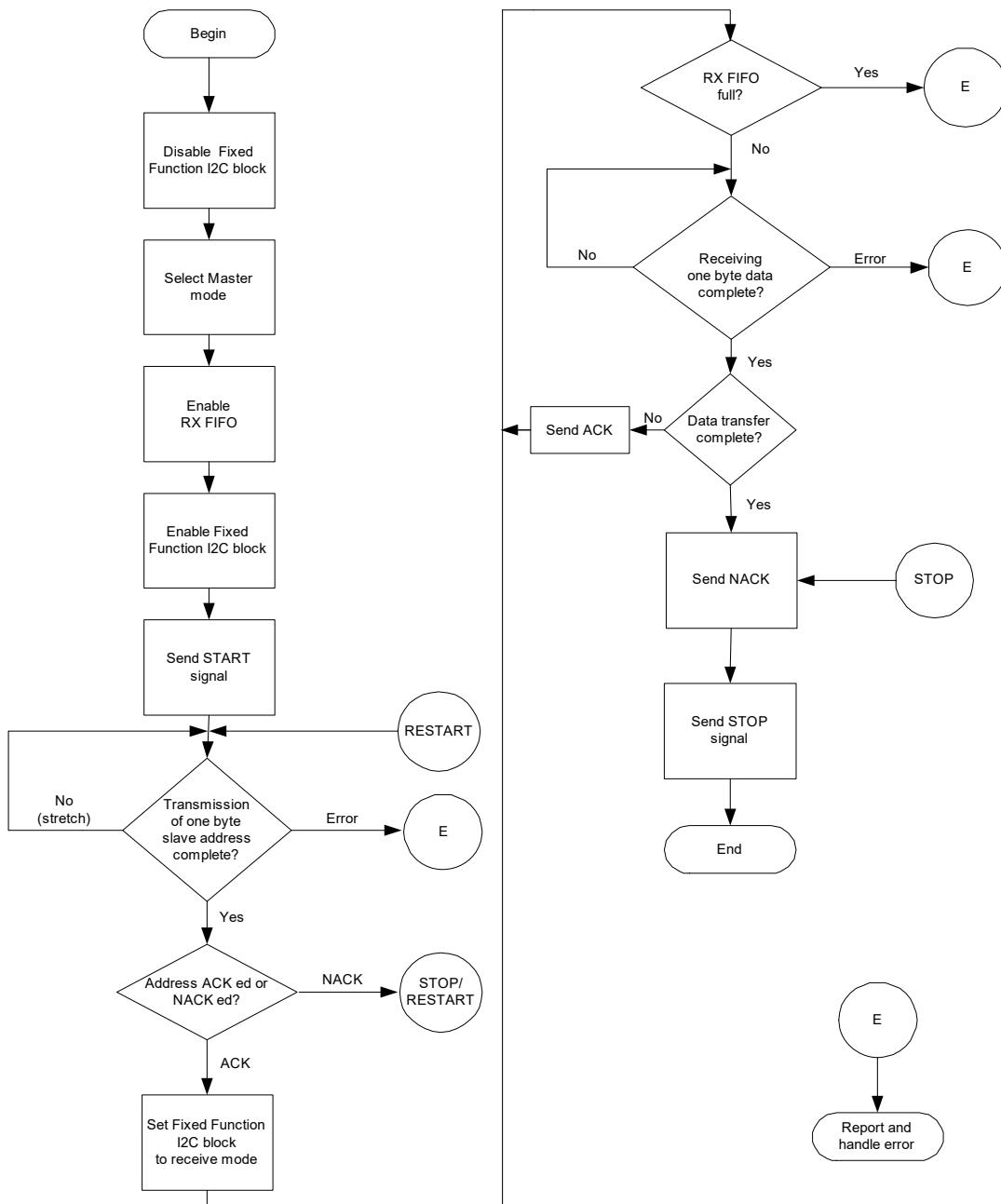

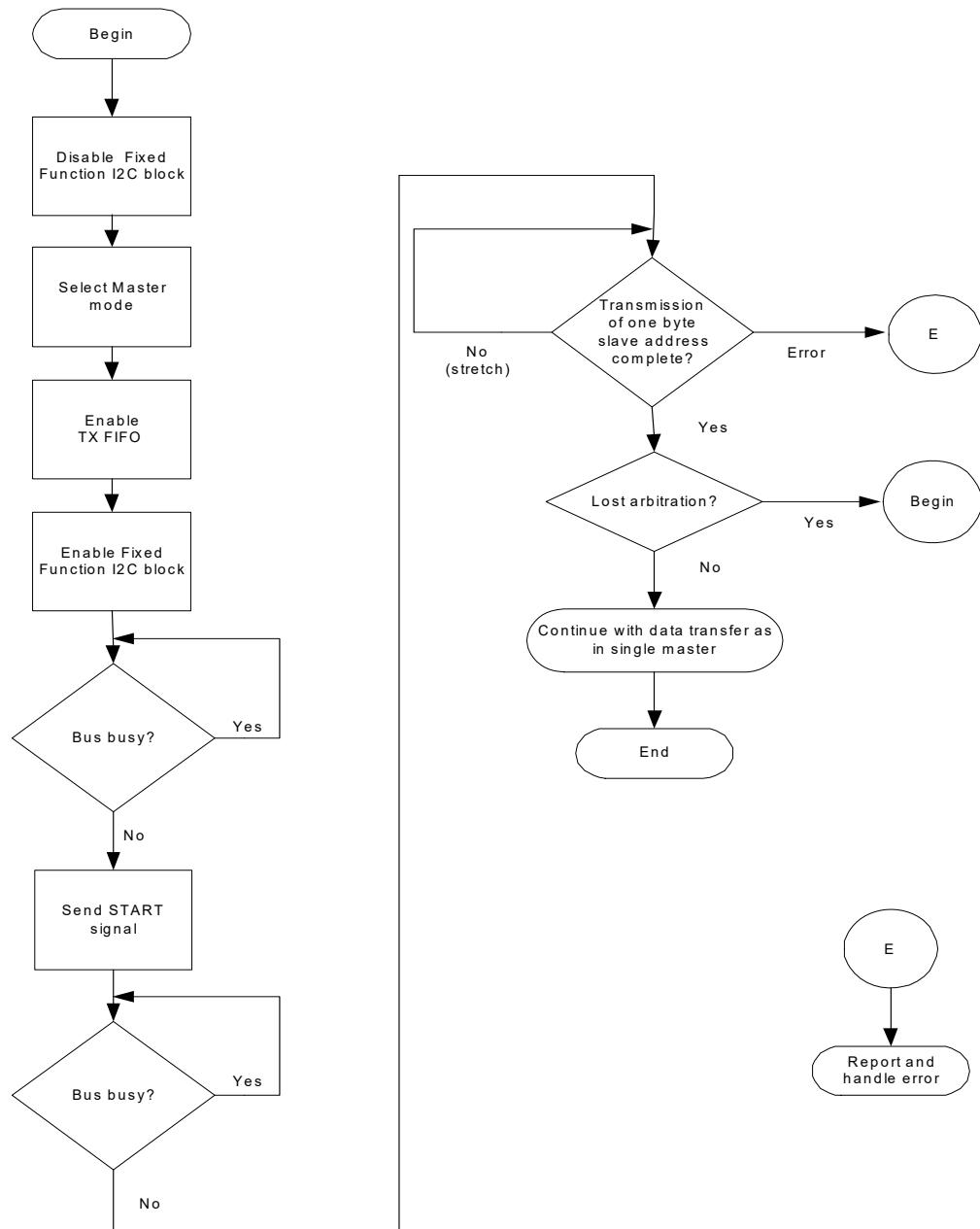

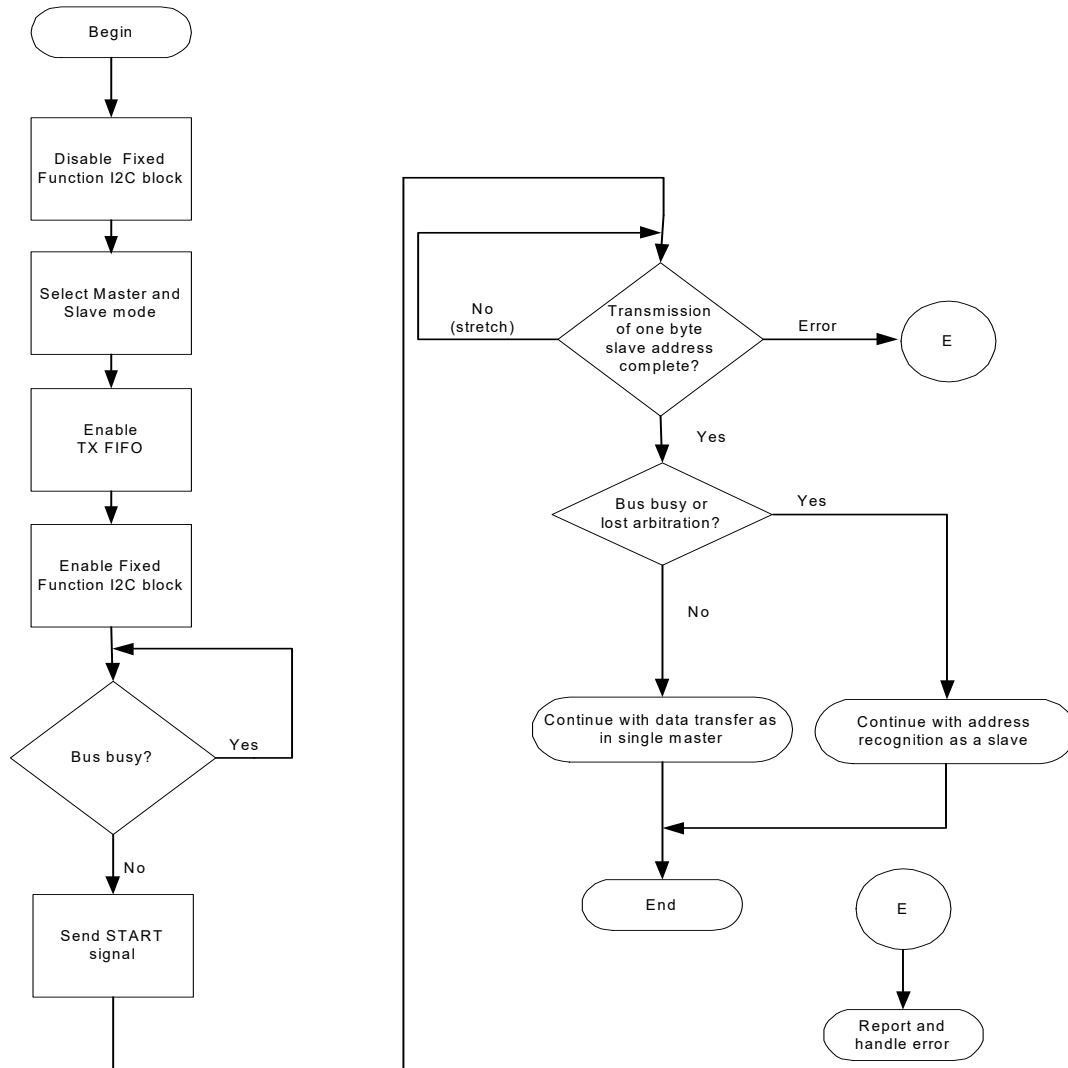

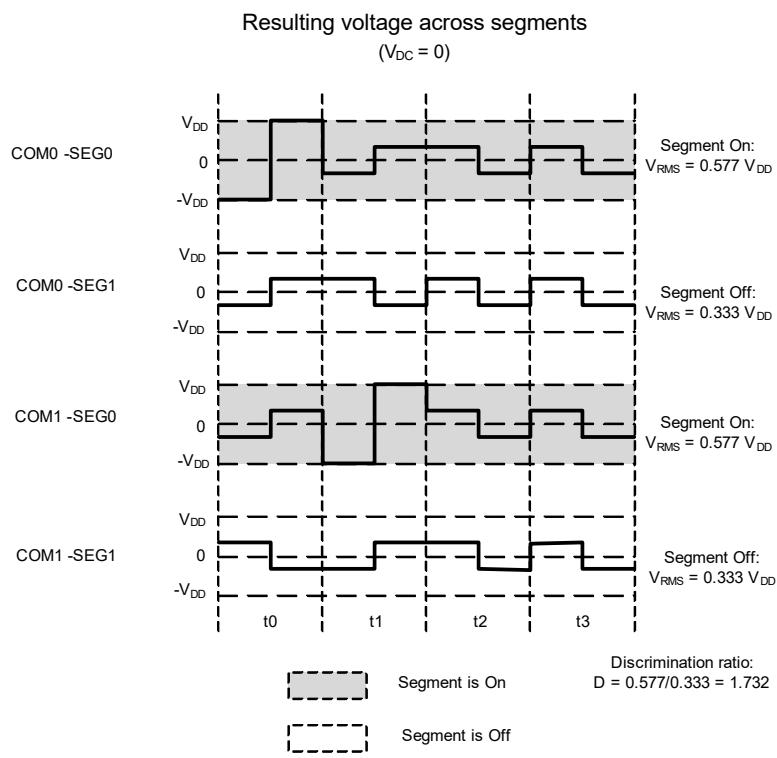

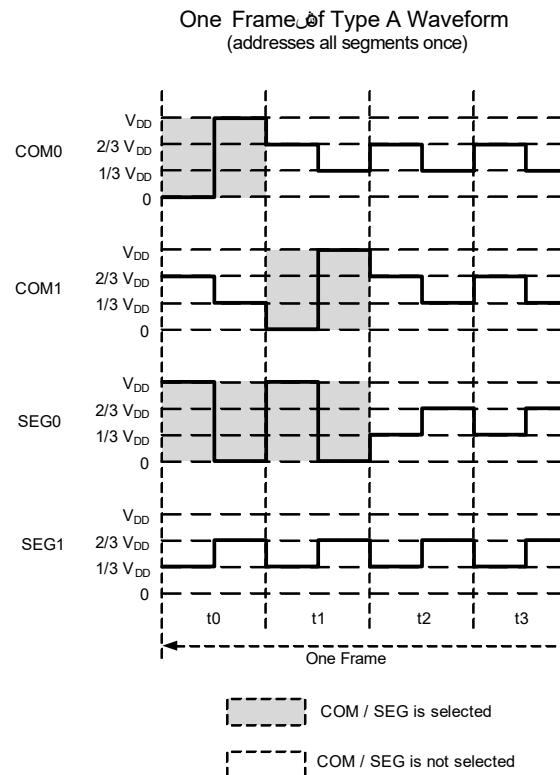

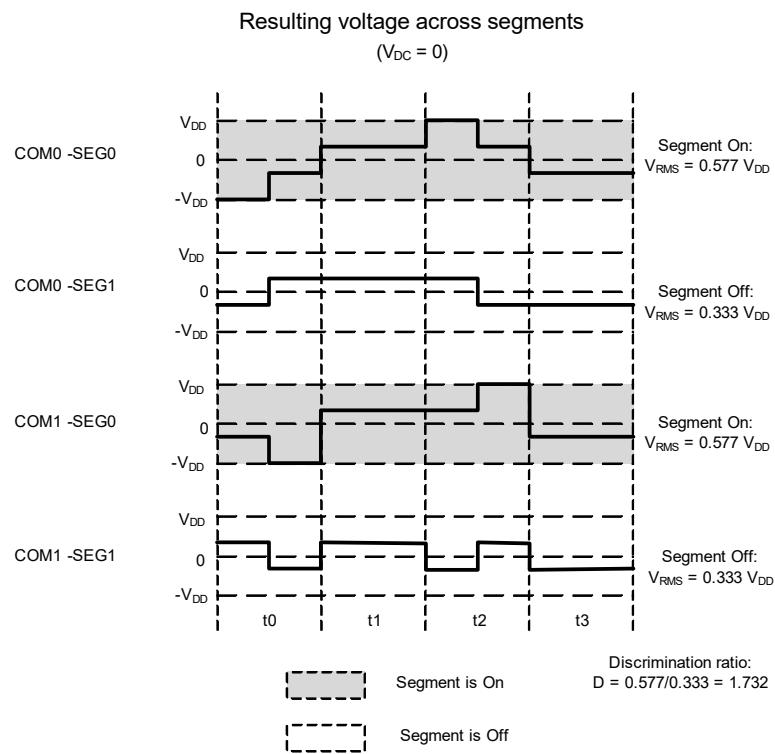

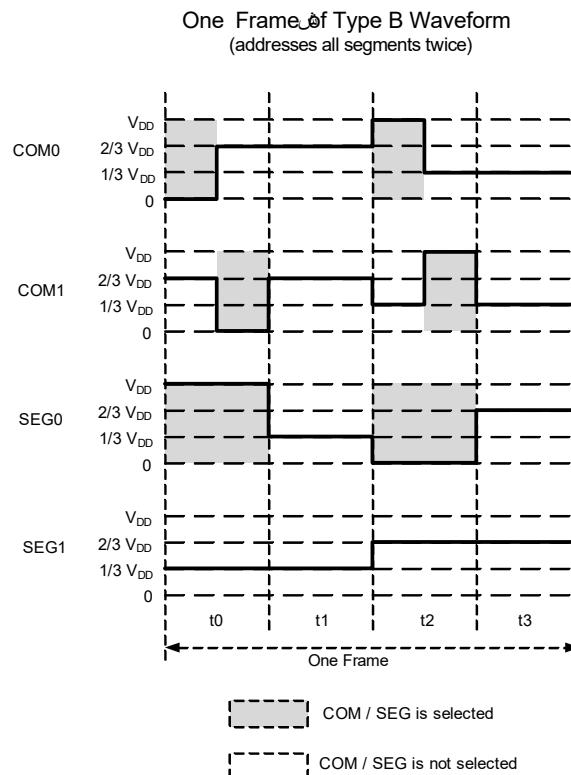

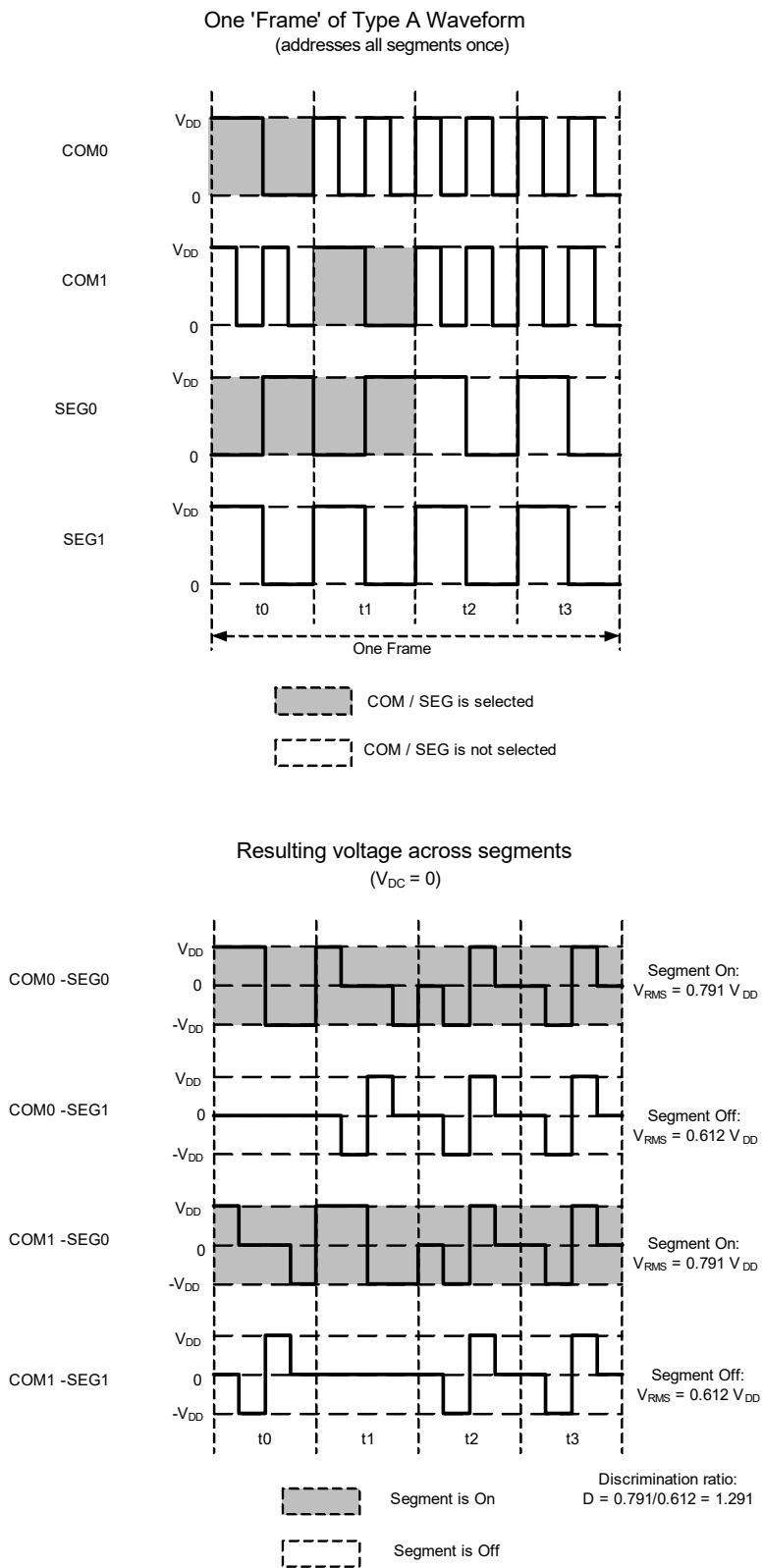

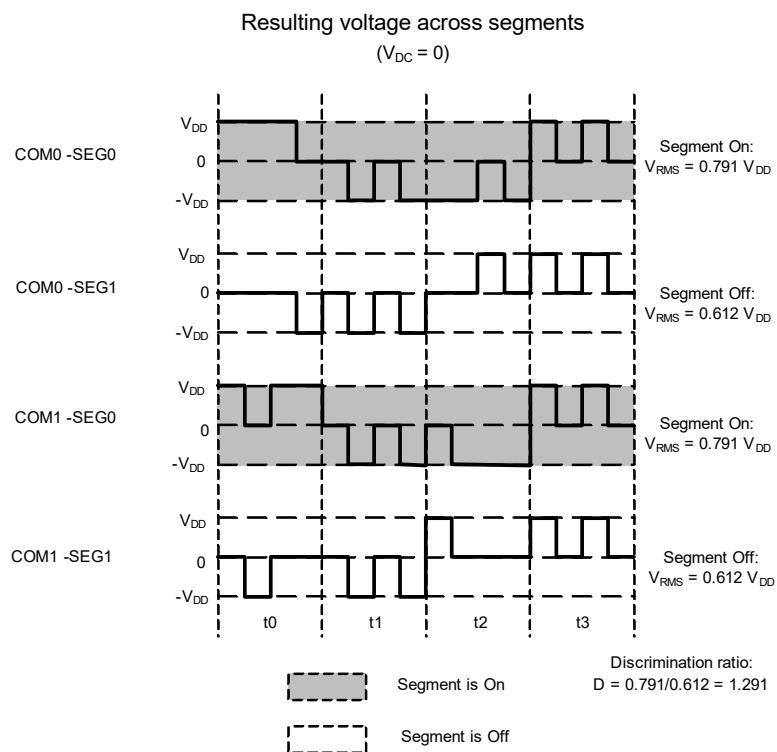

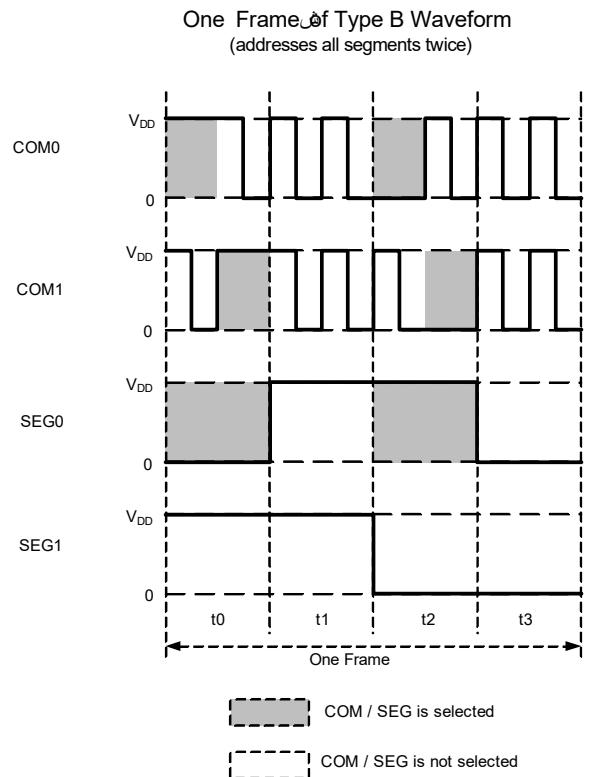

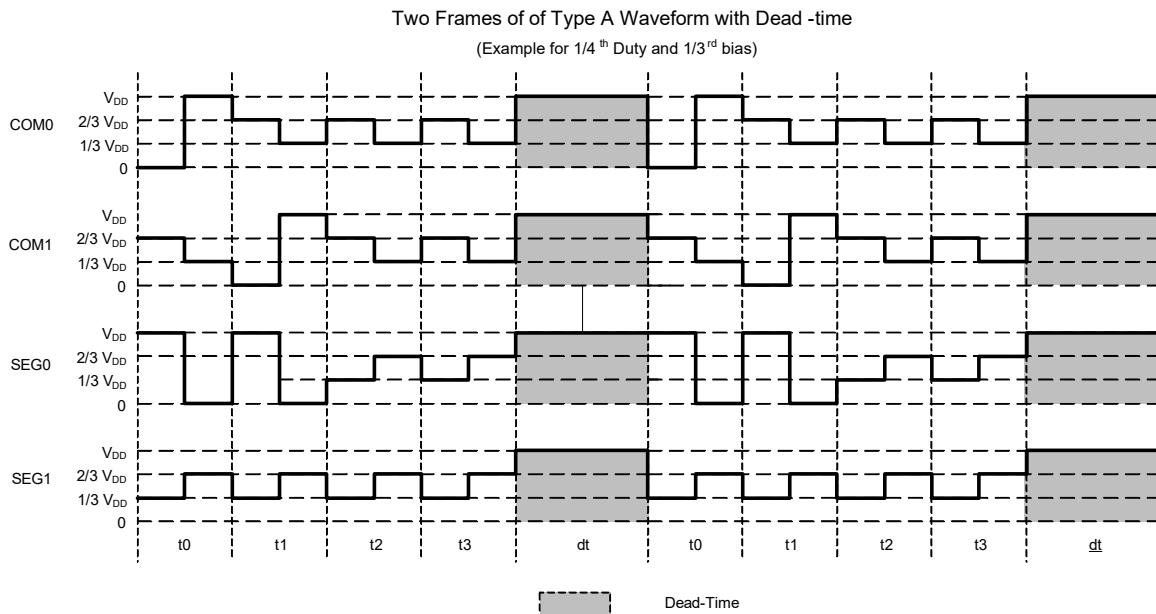

| CM0P_ICER     | 割り込みイネーブル クリア レジスタ          |