---

The following document contains information on Cypress products. The document has the ordering part numbering with the prefix "S". Cypress will offer these products to new and existing customers with the updated ordering part number (updated last digit).

#### **How to Check the Ordering Part Number**

1. Go to [www.cypress.com/pcn](http://www.cypress.com/pcn).

2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

3. Click the corresponding title from the search results.

4. Download the Affected Parts List file, which has details of all changes

#### **For More Information**

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to [www.cypress.com](http://www.cypress.com).

S6E1C1 Series

## 基于32位ARM® Cortex®-M0+ FM0+ Microcontroller

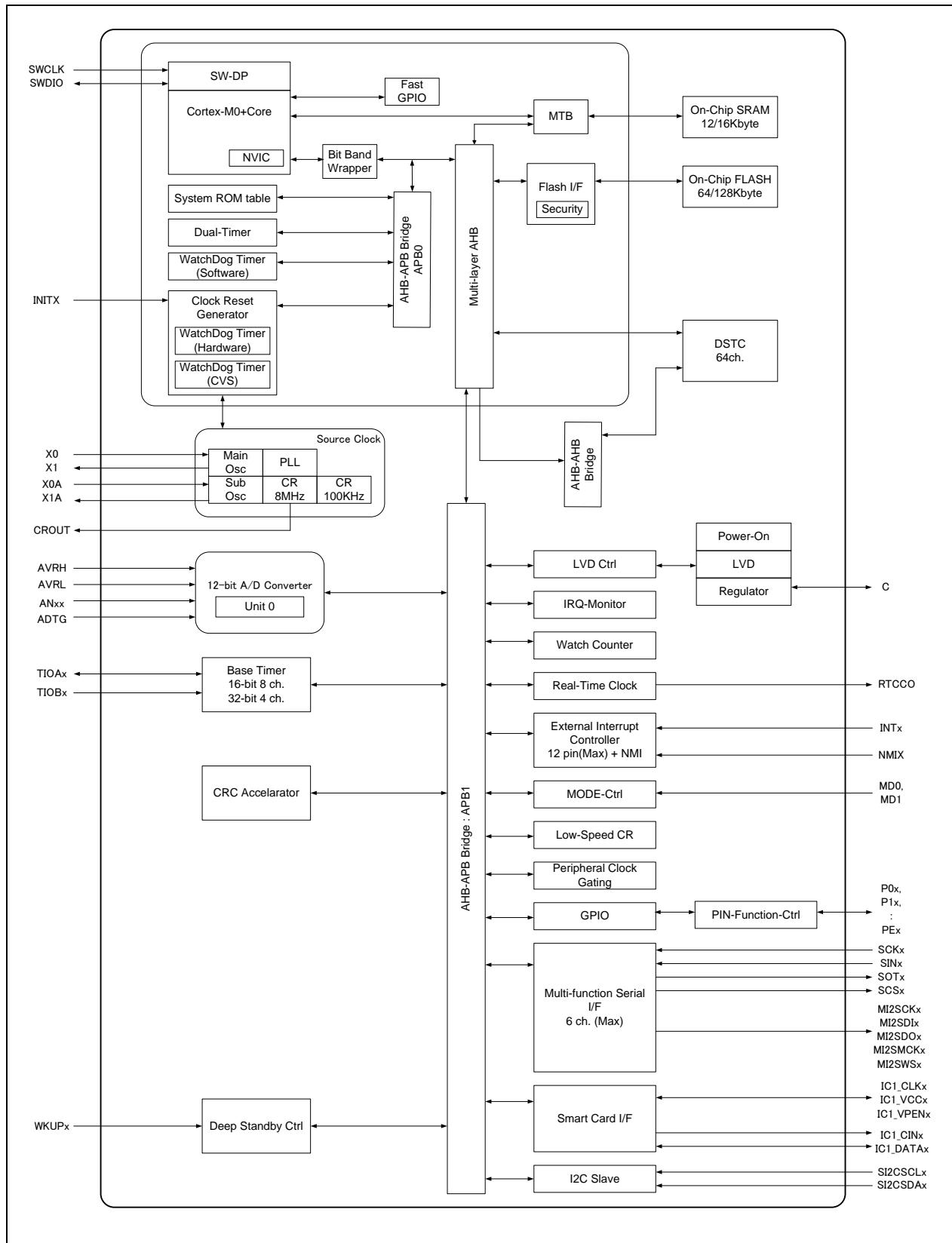

S6E1C1 系列是针对低电耗和低成本应用而设计的高集成度 32 位嵌入式微控制器。本系列有搭载片上闪存和 SRAM 的 ARM Cortex-M0+ 处理器，还包含了各种定时器、ADC 和各种通信接口（UART、CSIO (SPI)、I<sup>2</sup>C、I<sup>2</sup>S、智能卡）等在内的外设功能。“FM0+ 系列外设手册”中该数据手册记载的产品归类于 TYPE3-M0+ 产品。

### 特征

#### 32 位 ARM Cortex-M0+ 内核

- 处理器版本 : r0p1

- 最高工作频率 : 40.8 MHz

- 嵌套向量中断控制器 (NVIC) : 支持 1 通道 NMI (非屏蔽中断) 和可设定 4 个中断优先级的 24 通道的外设中断。

- 24 位系统定时器 (Sys Tick) : 该系统定时器用于管理操作系统任务

#### 位带操作

与 Cortex-M3 位带操作兼容。

#### 片上存储器

- 闪存

- 最大 128 千字节

- 读周期 : 0 等待周期

- 保护代码的加密功能

#### ■ SRAM

本系列的片上 SRAM 具有一个独立的 SRAM。

- 最大 SRAM : 16 千字节

- 4 千字节 : 在深度待机模式中可保存值

#### 多功能串口 (最多 6 通道)

- 其中 3 个通道含有 64 字节深度的 FIFO (通道 4, 6, 7); 另外三个通道不含有 FIFO (通道 0, 1, 3)

#### ■ 可从以下选择每路通道的运行模式。

- UART

- CSIO (CSIO 被许多客户称为 SPI)

- I<sup>2</sup>C

#### ■ UART

- 全双工双缓冲器

- 可选择奇偶校验的有/无。

- 内置专用波特率发生器

- 外部时钟可用作串行时钟

- 硬件流速控制; 通过 CTS/RTS 握手信号自动控制传输 (只限通道 4)

\* S6E1C12B0A/S6E1C11B0A 和 S6E1C12C0A/S6E1C11C0A 不支持硬件流速控制

- 丰富的错误检测功能 (奇偶校验错误、帧错误及溢出错误)

#### ■ CSIO (又称 SPI)

- 全双工双缓冲器

- 内置专用波特率发生器

- 溢出错误检测功能

- 串行芯片选择功能 (仅 ch1 和 ch6)

□ 数据长度 : 5 ~ 16 位

#### ■ I<sup>2</sup>C

- 支持标准模式 (最快 100kbps)/高速模式 (最快 400kbps)。

#### ■ I<sup>2</sup>S (MFS-I2S)

- 使用 CSIO (最多两通道: ch.4、ch.6) 和 I<sup>2</sup>S 时钟发生器

- 支持两种传输协议

- I<sup>2</sup>S

- MSB 对齐

- 仅主控模式

#### I<sup>2</sup>C 从机

- I<sup>2</sup>C 从机支持 I<sup>2</sup>C 的从机功能，并且支持 MCU 待机模式下唤醒。

#### 广义系统数据传输控制器 (DSTC) (64 通道)

- DSTC 可不经 CPU 高速传输数据。DSTC 采用的是广义系统，且可通过已构建在存储器中的广义系统指定内容直接访问存储器/外围设备，进行数据传输。

- 支持软件激活、硬件激活、以及链式激活功能。

#### A/D 转换器 (最多 8 通道)

- 12 位 A/D 转换器

- 逐次比较型

- 转换时间 : 2.0μs@2.7V ~ 3.6V

- 可进行优先级转换 (2 个优先级)

- 扫描转换模式

- 内置存储转换数据的 FIFO (用于扫描转换 : 16 段；用于优先级转换 : 4 段)

#### 基本定时器 (最多 8 通道)

可从以下选择每路通道的运行模式。

- 16 位 PWM 定时器

- 16 位 PPG 定时器

- 16/32 位重载定时器

- 16/32 位 PWC 定时器

#### 通用 I/O 端口

本系列的引脚不用作外部总线或者外设功能时，可用作通用 I/O 口。所有端口都可设定为快速通用 I/O 口或慢速通用 I/O 口。另外，搭载的端口重定位功能可设定哪一个 I/O 口配置外设功能。

■所有端口都为可在 1 个周期内访问的快速 GPIO

■可上拉控制各个引脚

■可直接读出引脚电平

■具有端口重定位功能

■最多 54 个高速通用 I/O 口 @64 针封装

■部分端口耐 5V。

相关引脚详情，参见“4. 引脚功能一览表”以及“5. I/O 电路类型”。

### 双定时器 (32/16 位逐减计数器)

双定时器由两个可编程的 32/16 位逐减计数器组成。可从以下选择定时器每路通道的运行模式。

■自由运行模式

■周期模式 (=重载模式)

■单次触发模式

### 实时时钟

实时时钟记录从 00 年至 99 年间的年/月/日/小时/分钟/秒/星期。

■RTC 可在指定时间 (年/月/日/小时/分钟/秒/星期) 生成中断，也可在指定年、月、日、小时或分钟生成中断。

■具有在指定时间或指定时间间隔生成中断的定时器中断功能。

■可在修改时间之时保持计数。

■可自动计数闰年。

### 计时计数器

计时计数器可把微控制器从低功耗模式中唤醒。可选择的时钟源包括主时钟、副时钟、内部高速 CR 时钟或内部低速 CR 时钟。

间隔定时器：最大间隔时间 64s (副时钟：32.768kHz)

### 外部中断控制单元

■最多 12 个外部中断输入引脚

■不可屏蔽中断 (NMI) 输入引脚：1 个

### 监视定时器 (2 通道)

达到超时值时，监视定时器生成中断或复位。

本系列有两种不同的监视，硬件监视和软件监视。

硬件监视定时器使用内置低速 CR 振荡器。因此，硬件监视定时器在任何低功耗模式下都可以工作，RTC、停止、深度待机 RTC 和深度待机停止模式除外。

### CRC (循环冗余校验) 加速器

CRC 加速器进行软件处理负荷高的 CRC 计算，以减轻数据接收及存储完整性确认的处理负荷。

■支持 CCITT CRC16 和 IEEE-802.3 CRC32。

□CCITT CRC16 生成多项式 : 0x1021

□IEEE-802.3 CRC32 生成多项式 : 0x04C11DB7

### HDMI-CEC/遥控接收器 (最多 2 通道)

■HDMI-CEC 发送器

□头块通过判断无信号自动传输

□通过检测仲裁丧失生成状态中断

□通过设置 1 字节数据自动生成 START、EOM、AC 来输出 CEC 传输

□发送 1 个块 (1 字节数据和 EOM/ACK) 时，生成传输状态中断

■HDMI-CEC 接收器

□具有自动 ACK 回复功能

□具有线误差检测功能

■遥控接收器

□4 字节接收缓冲

□具有重复码检测功能

### 智能卡接口 (最多 1 通道)

■符合 ISO7816-3 规格

■仅读卡器/仅 B 级卡

■支持协议

□发送器 : 8E2、8O2、8N2

□接收器 : 8E1、8O1、8N2、8N1、9N1

□反转模式

■TX/RX FIFO 集成 (RX : 16 字节, TX : 16 字节)

### 时钟和复位

■时钟

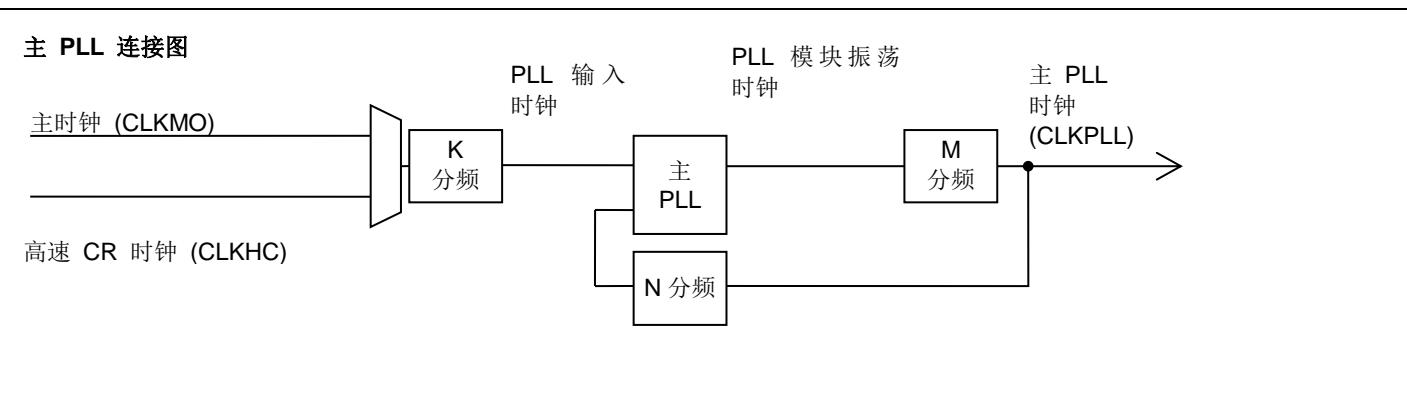

可选择 5 种时钟源 (2 种外部振荡、2 种内部 CR 振荡、主 PLL)。

□主时钟 : 8MHz ~ 48MHz

32.768kHz

□内部高速 CR 时钟 : 8MHz

100kHz

□内部低速 CR 时钟 : 8MHz ~ 16MHz(输入)

75MHz ~ 150MHz(输出)

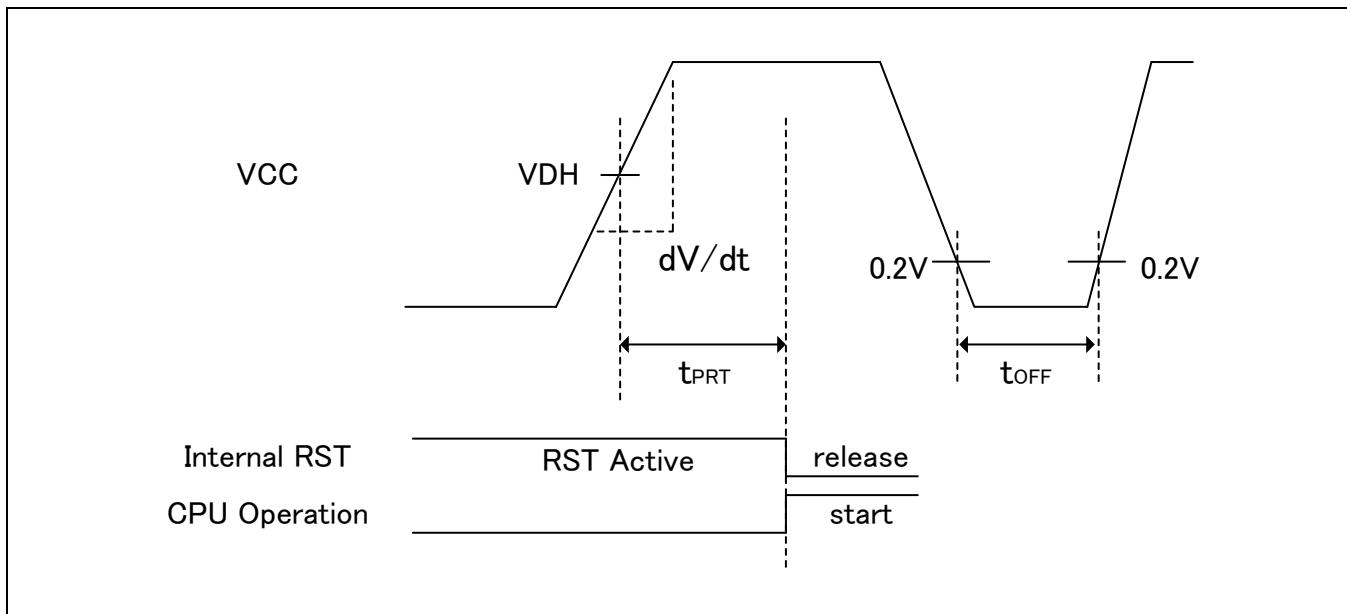

■复位

□INITX 引脚的复位请求

□上电复位

□软件复位

□监视定时器复位

□低压检测复位

□时钟监视器复位

### 时钟监视功能 (CSV)

时钟监视功能根据内置 CR 振荡器生成的时钟来监视外部时钟的异常。

■检测出外部时钟故障 (时钟停止) 时，复位有效。

■检测出外部频率异常时，中断或复位有效。

### 低压检测功能 (LVD)

本系列可在 2 个阶段监视 VCC 引脚的电压。VCC 引脚的电压比设定的电压低时，低压检测功能生成中断或复位。

■LVD1 : 监视 Vcc 和使用中断报告错误

■LVD2 : 自动复位操作

**低功耗模式**

本系列有 6 种低功耗模式。

- 休眠

- 定时器

- RTC

- 停止

- 深度待机 RTC (可选是否保持 RAM 值)

- 深度待机停止 (可选是否保持 RAM 值)

**外设时钟门控**

本系统通过对无需使用的外设进行时钟门控来降低整个系统的电流消耗。

**调试**

- 串行线调试端口 (SW-DP)

- 微型跟踪缓冲区 (MTB)

**唯一 ID**

已为设备设置 41 位的唯一识别码。

**电源**

- 支持大范围电压： VCC=1.65V~ 3.6V

## 目录

|                                                        |    |

|--------------------------------------------------------|----|

| <b>特征</b>                                              | 1  |

| 1. 产品阵容                                                | 6  |

| 2. 封装                                                  | 7  |

| 3. 引脚配置图                                               | 8  |

| 4. 引脚功能一览表                                             | 14 |

| 5. I/O 电路类型                                            | 26 |

| 6. 芯片处理注意事项                                            | 31 |

| 6.1 产品设计注意事项                                           | 31 |

| 6.2 封装焊接注意事项                                           | 31 |

| 6.3 使用环境注意事项                                           | 32 |

| 7. 芯片使用注意事项                                            | 34 |

| 8. 框图                                                  | 36 |

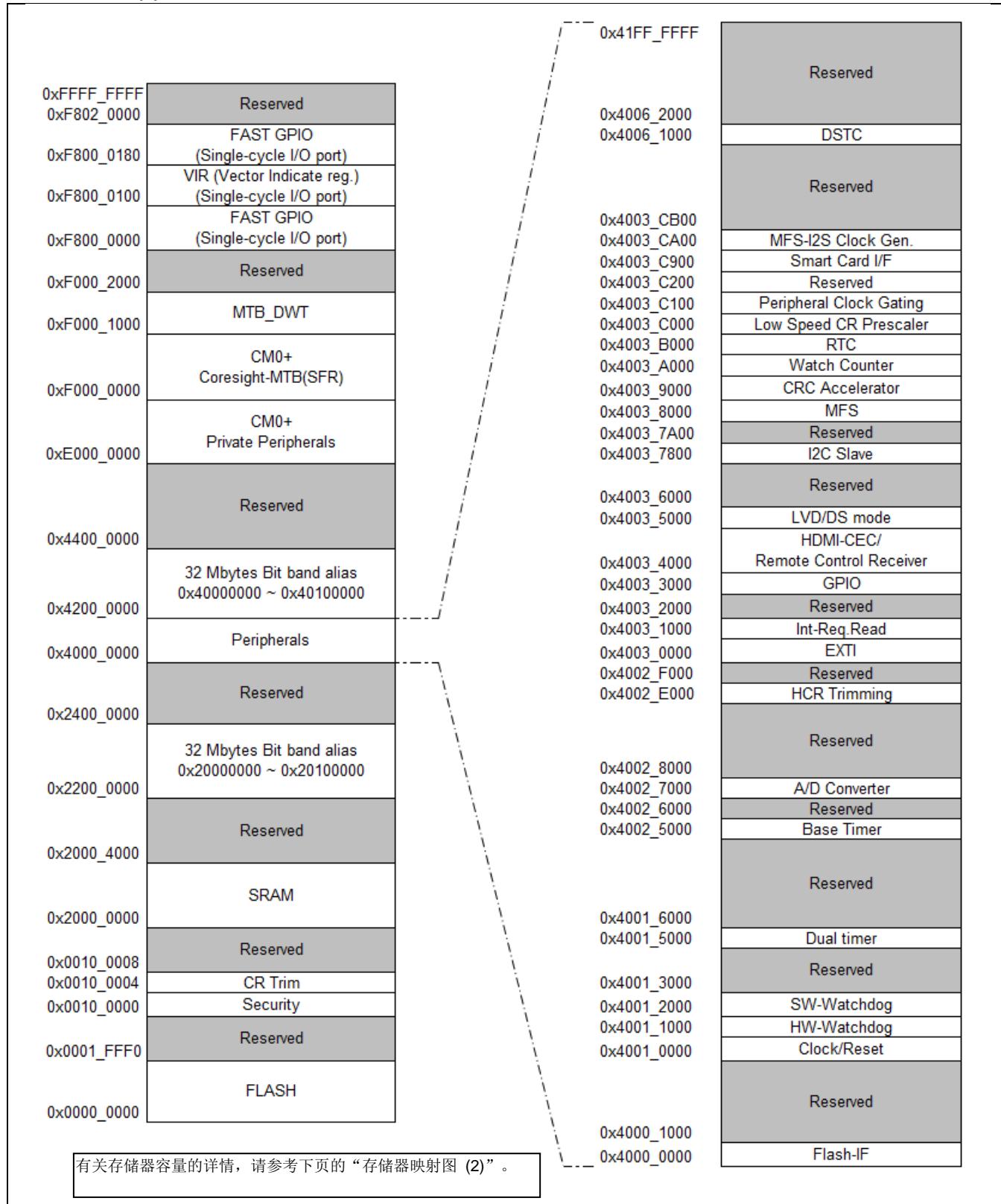

| 9. 存储器映射                                               | 37 |

| 10. 各 CPU 状态下的引脚状态                                     | 40 |

| 11. 电气特性                                               | 43 |

| 11.1 绝对最大额定值                                           | 43 |

| 11.2 推荐工作条件                                            | 44 |

| 11.3 DC 特性                                             | 45 |

| 11.3.1 额定电流                                            | 45 |

| 11.3.2 引脚特性                                            | 49 |

| 11.4 AC 特性                                             | 50 |

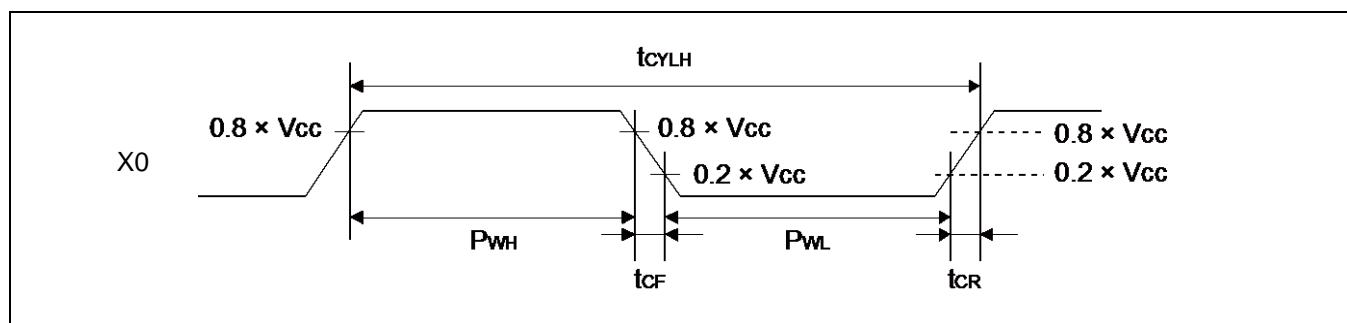

| 11.4.1 主时钟输入特性                                         | 50 |

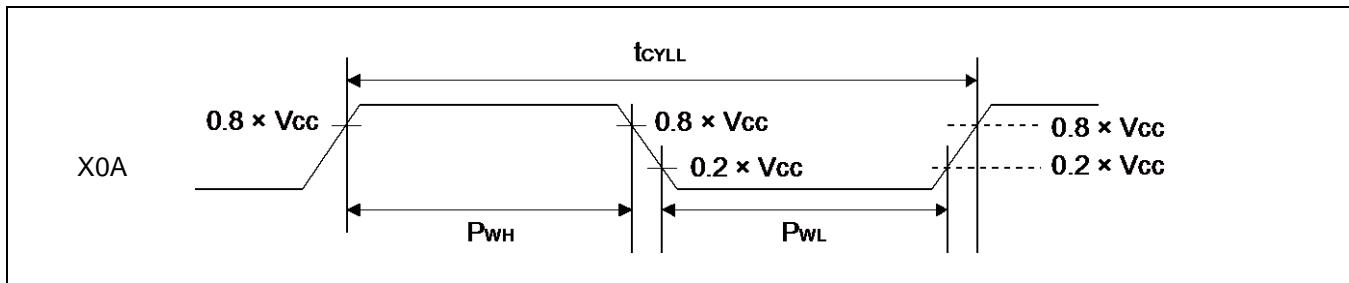

| 11.4.2 副时钟输入特性                                         | 51 |

| 11.4.3 内置 CR 振荡特性                                      | 52 |

| 11.4.4 主 PLL 的工作条件（主时钟用作 PLL 的输入时钟）                    | 53 |

| 11.4.5 主 PLL 的工作条件（内置高速 CR 时钟用作主 PLL 的输入时钟）            | 53 |

| 11.4.6 复位输入特性                                          | 54 |

| 11.4.7 上电复位时序                                          | 54 |

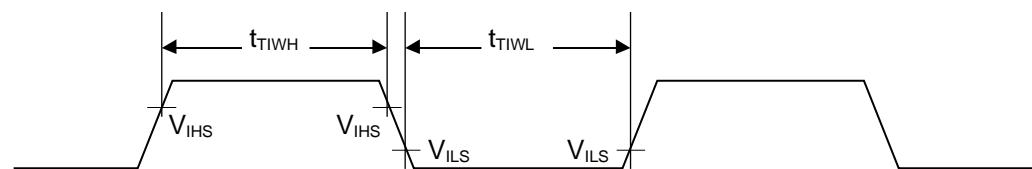

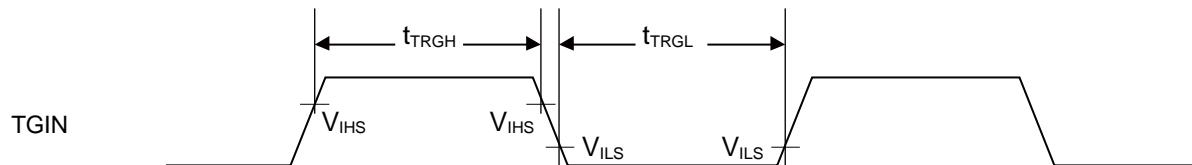

| 11.4.8 基本定时器输入时序                                       | 55 |

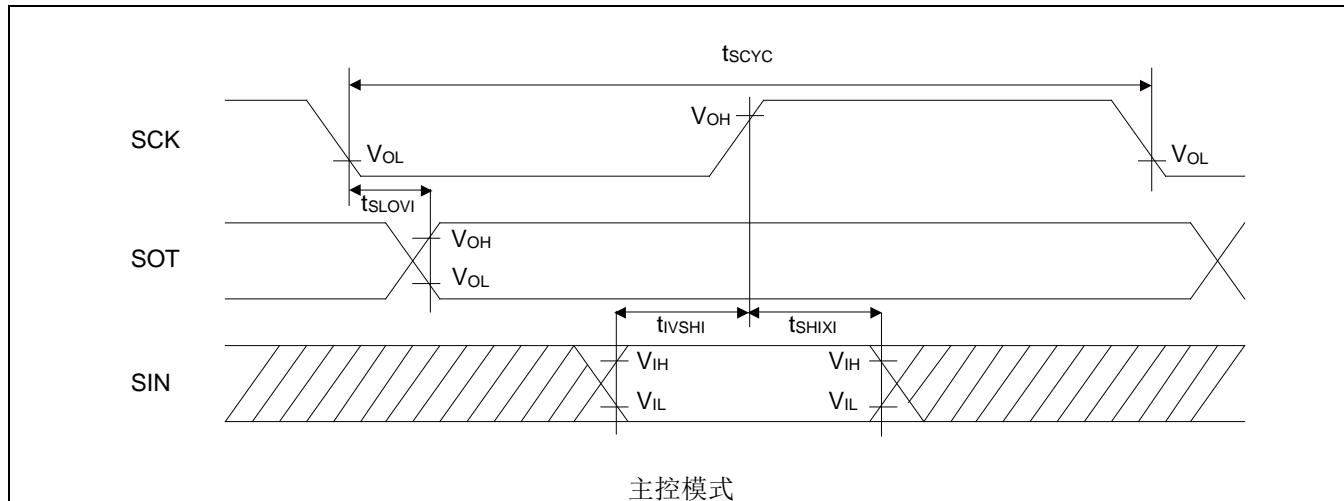

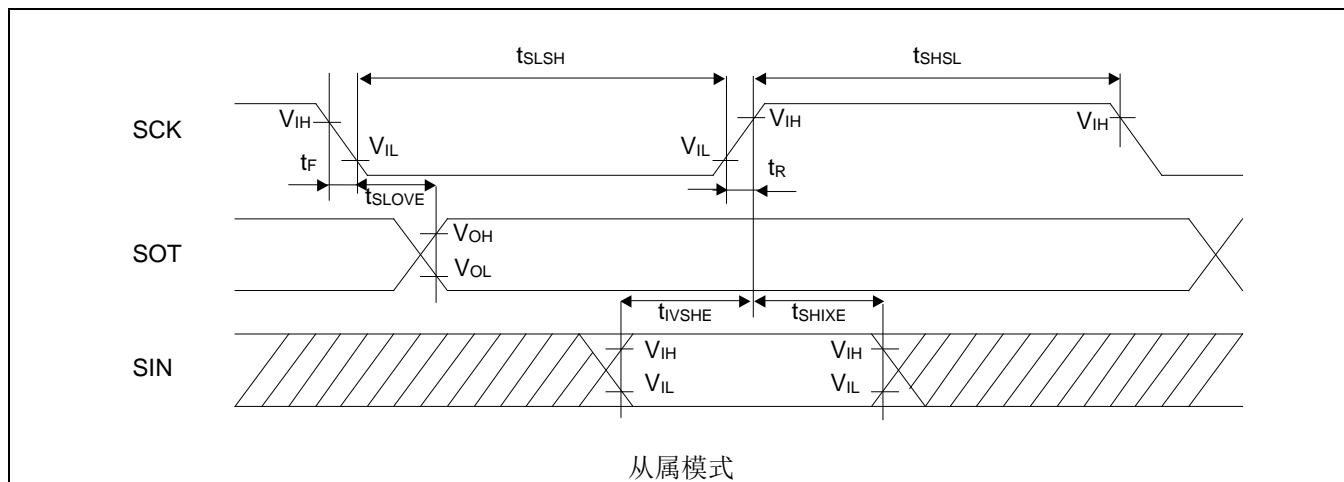

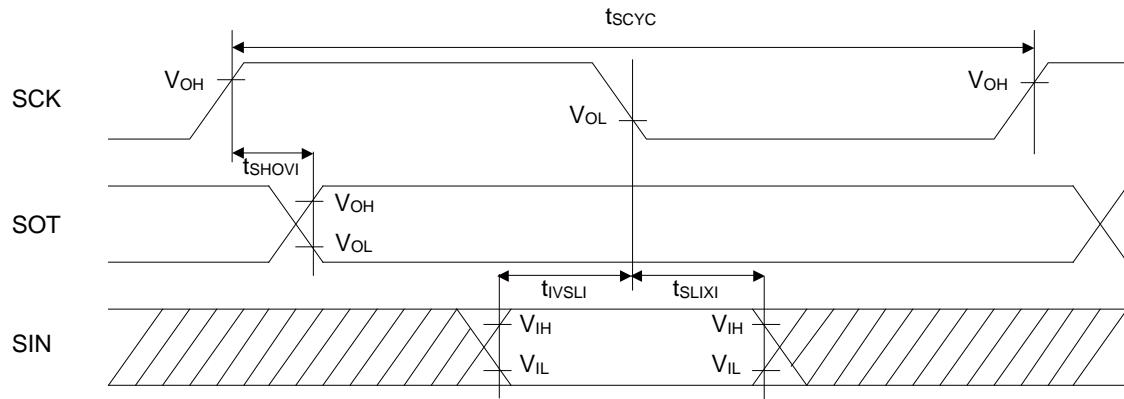

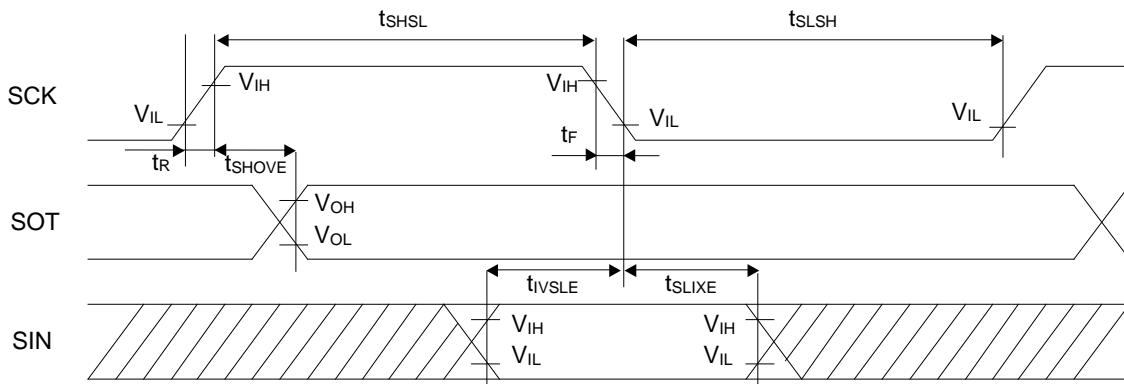

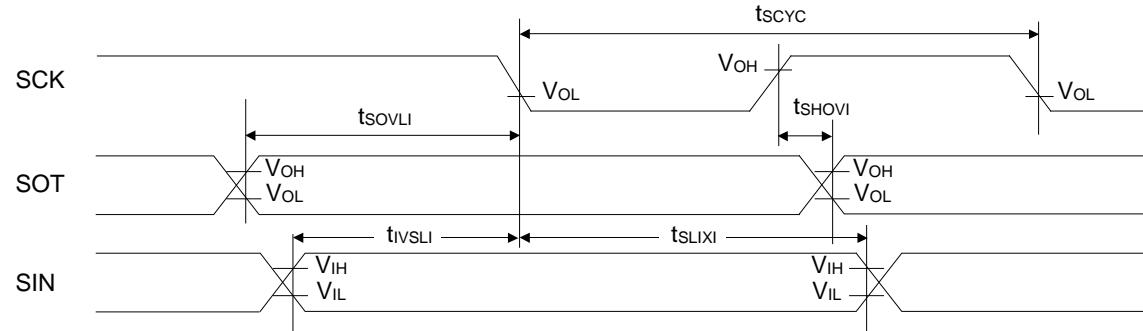

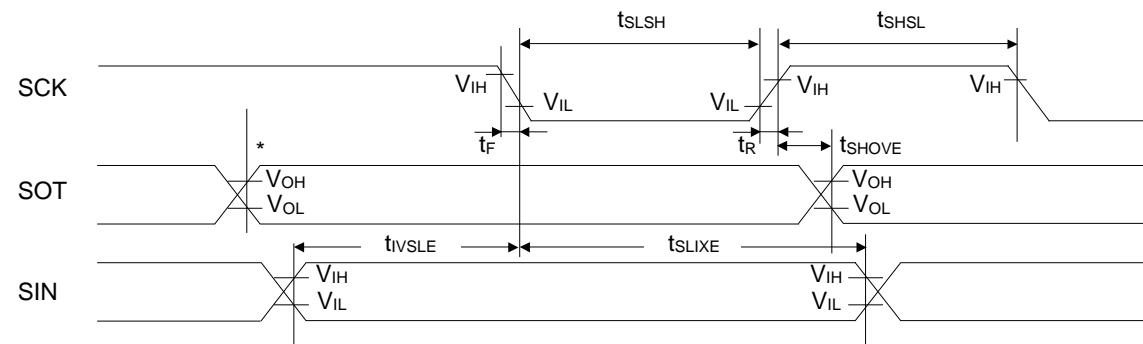

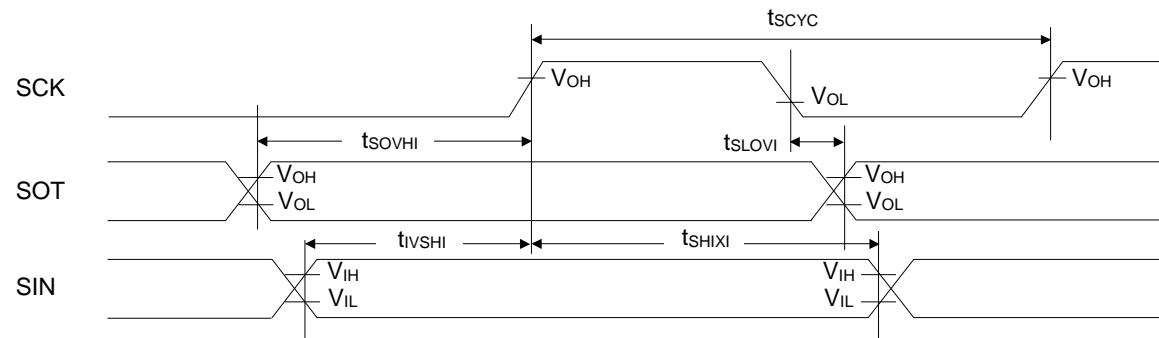

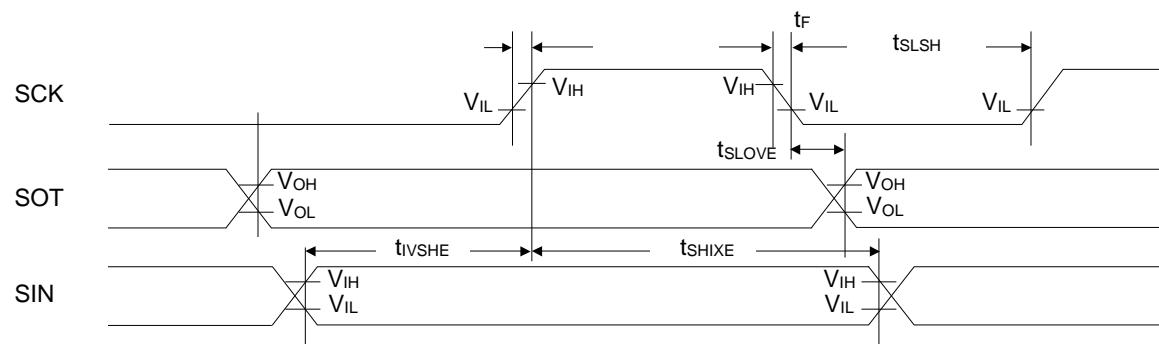

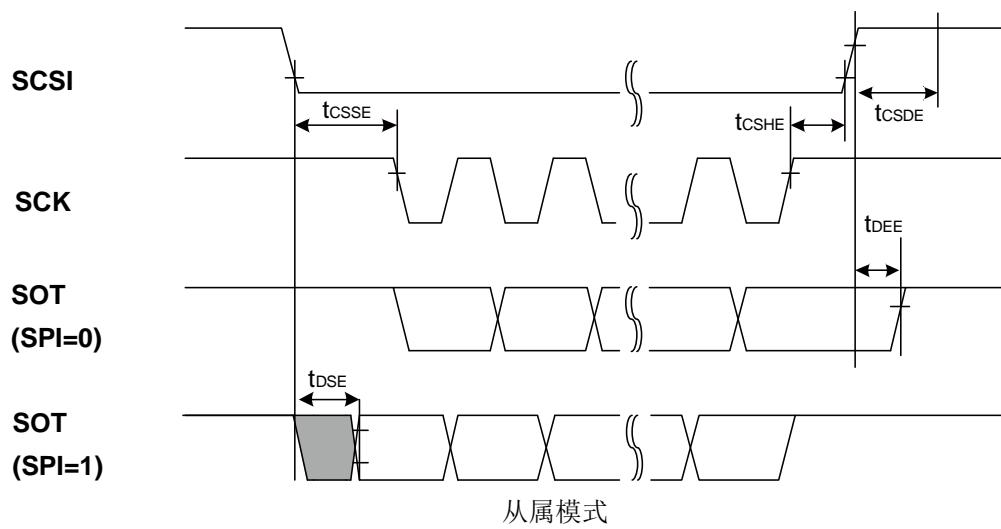

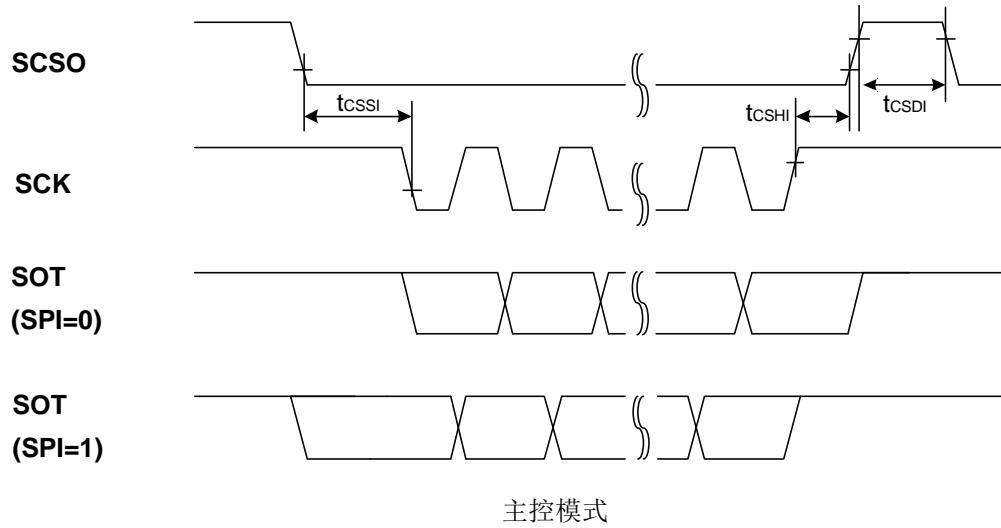

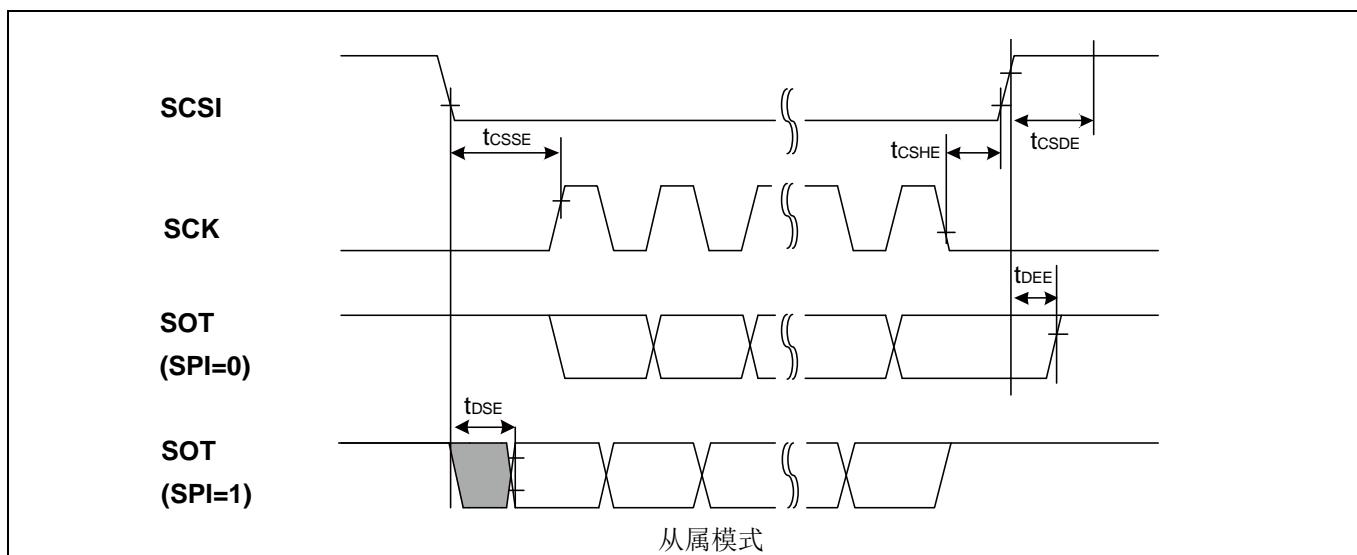

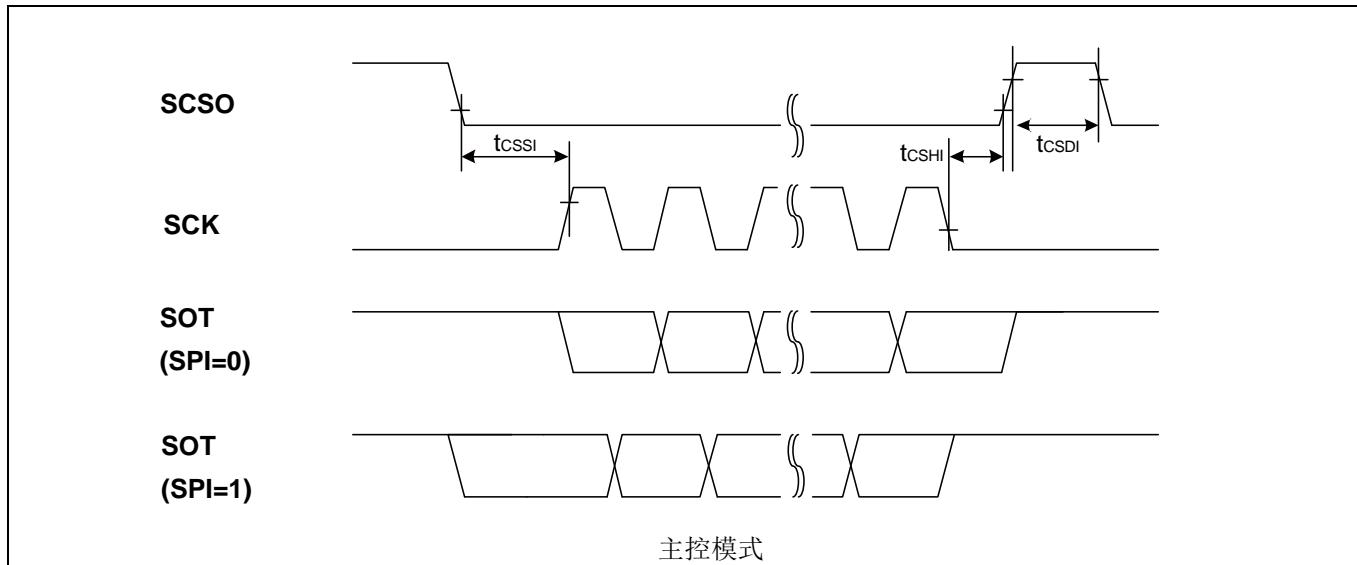

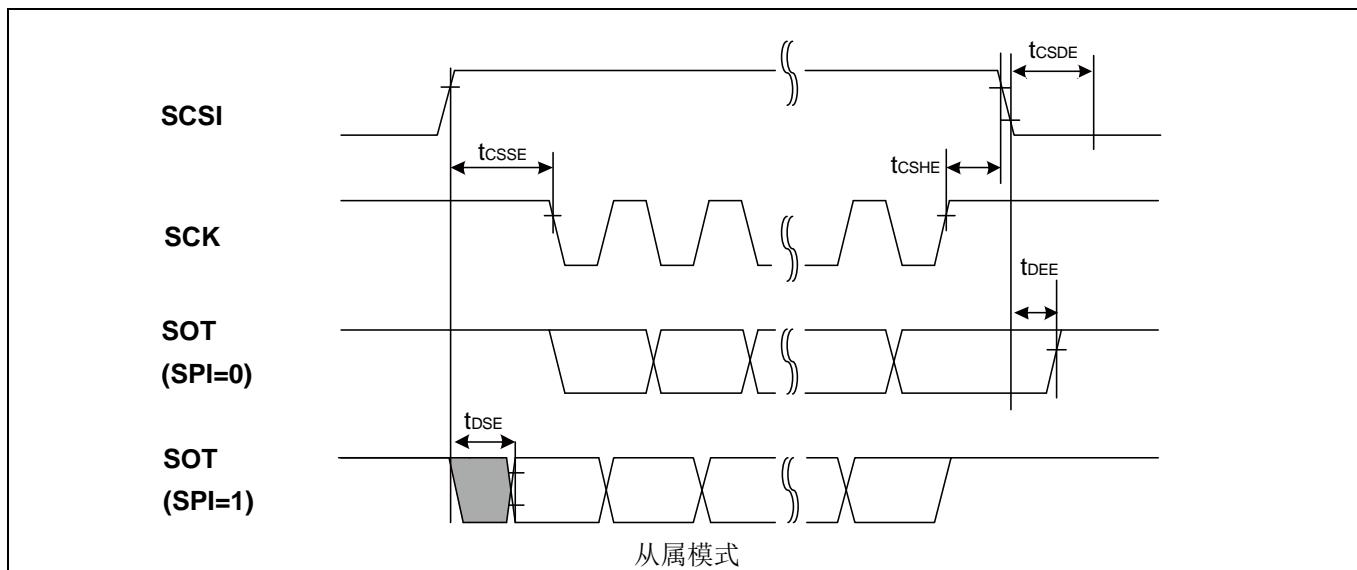

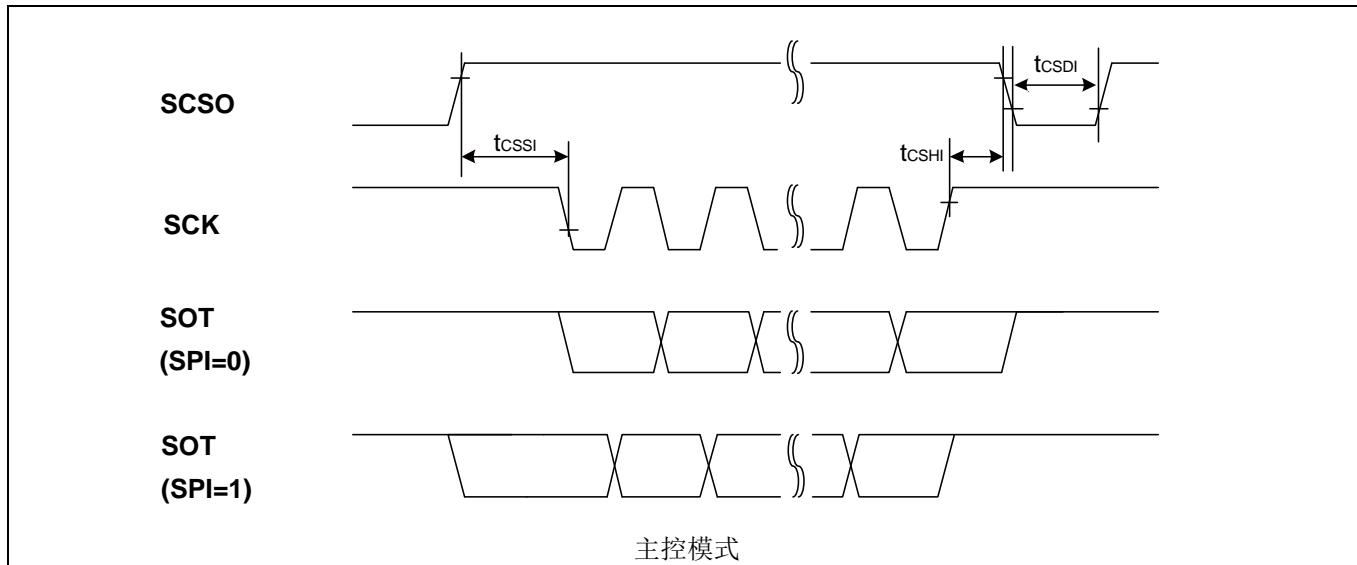

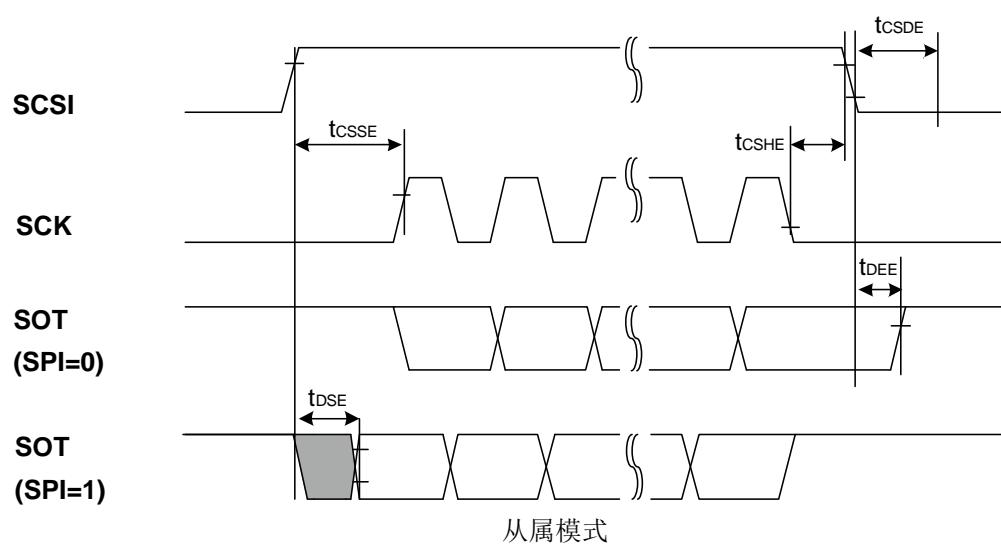

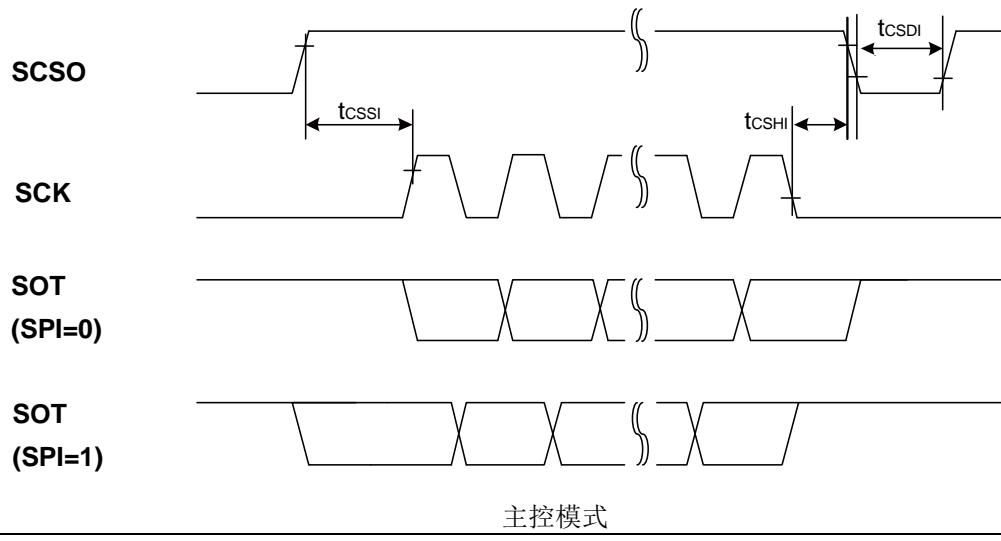

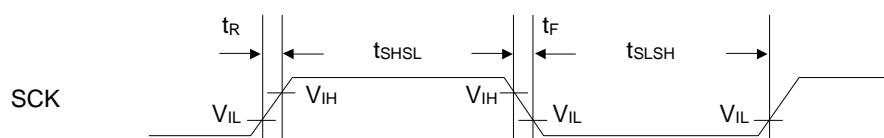

| 11.4.9 CSIO/SPI/UART 时序                                | 56 |

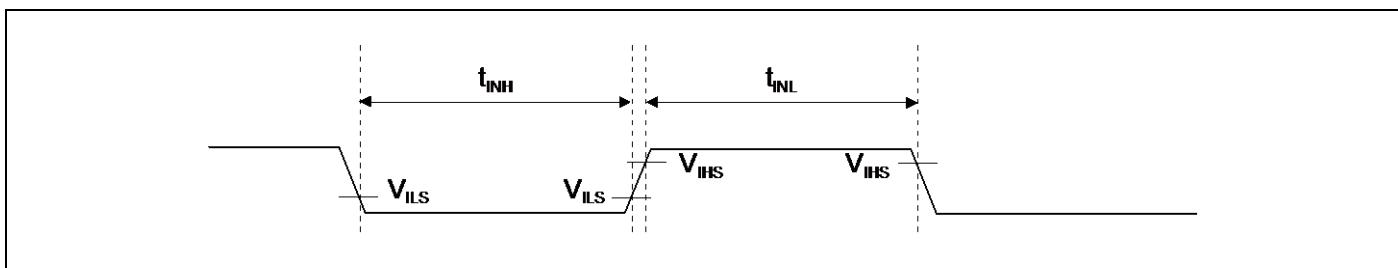

| 11.4.10 外部输入时序                                         | 73 |

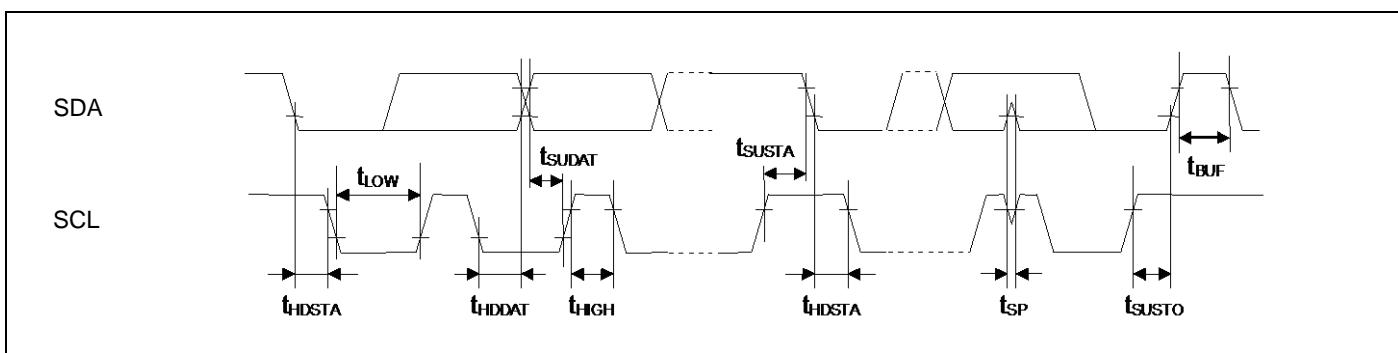

| 11.4.11 I <sup>2</sup> C 时序/I <sup>2</sup> C 从机时序      | 74 |

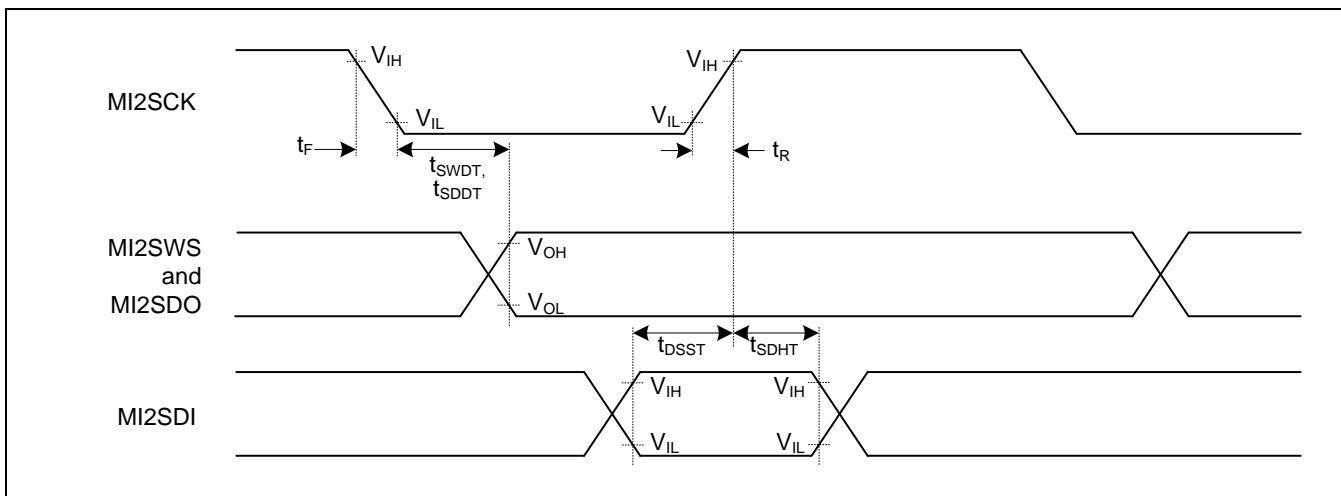

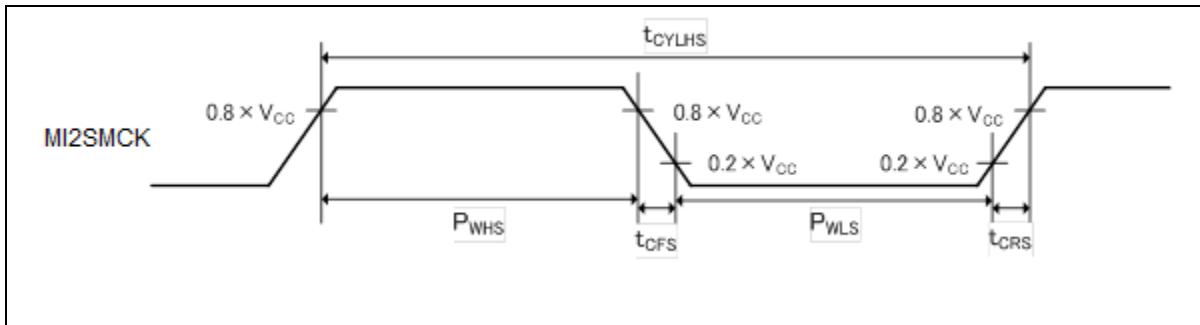

| 11.4.12 I <sup>2</sup> S 时序（多功能串口-I <sup>2</sup> S 时序） | 75 |

| 11.4.13 智能卡接口特性                                        | 77 |

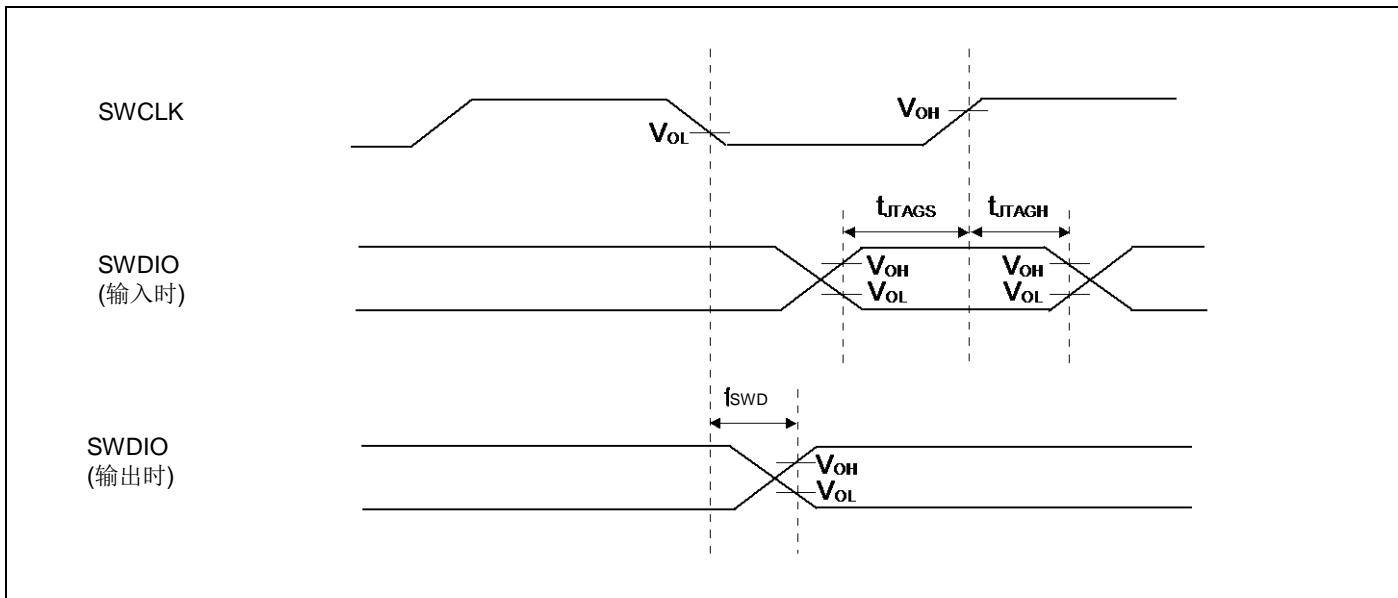

| 11.4.14 SW-DP 时序                                       | 78 |

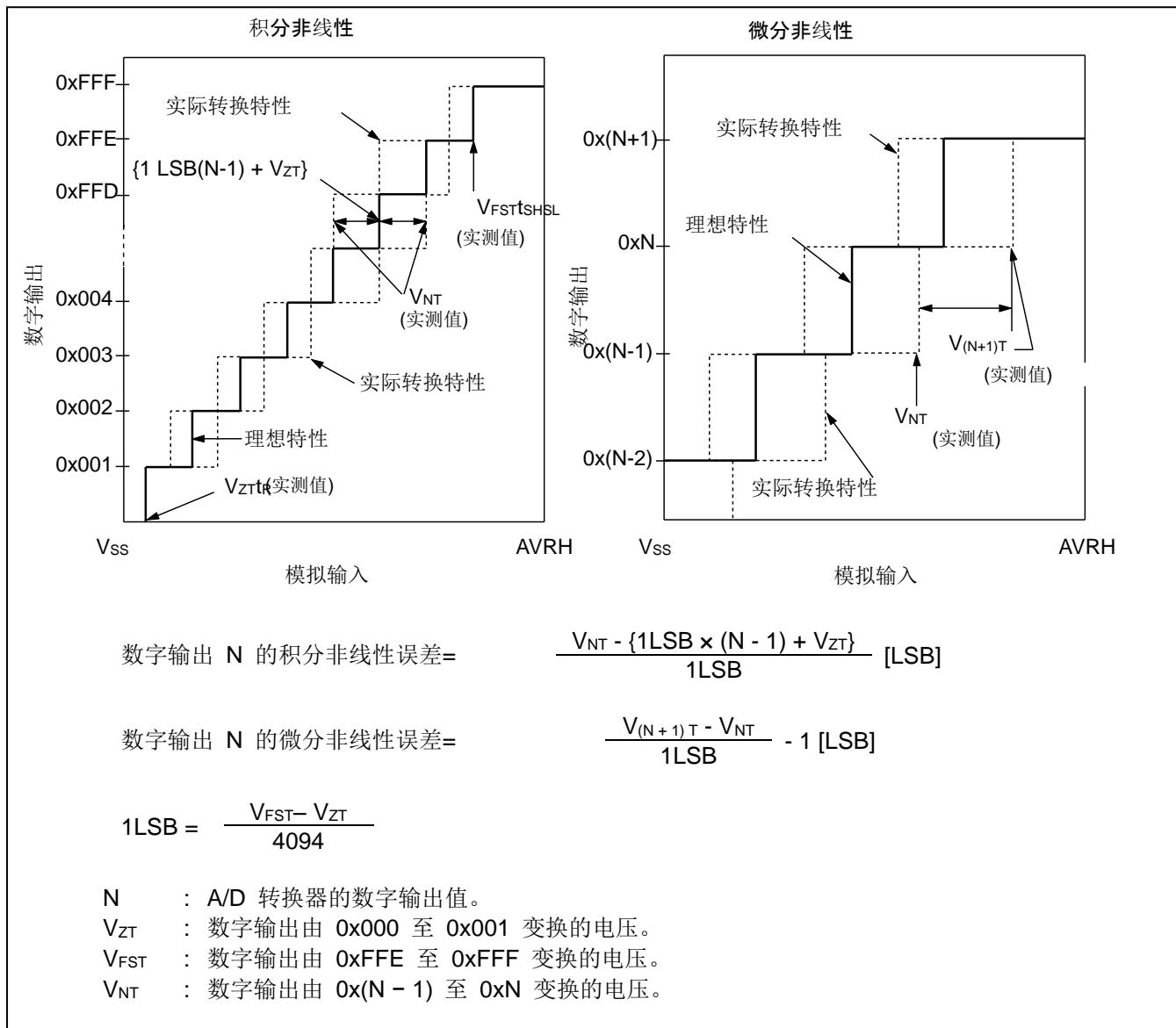

| 11.5 12 位 A/D 转换器                                      | 79 |

| 11.6 低压检测特性                                            | 82 |

| 11.6.1 低压检测复位                                          | 82 |

| 11.6.2 低压检测中断                                          | 83 |

| 11.7 闪存写入/擦除特性                                         | 84 |

| 11.8 低功耗模式唤醒时间                                         | 85 |

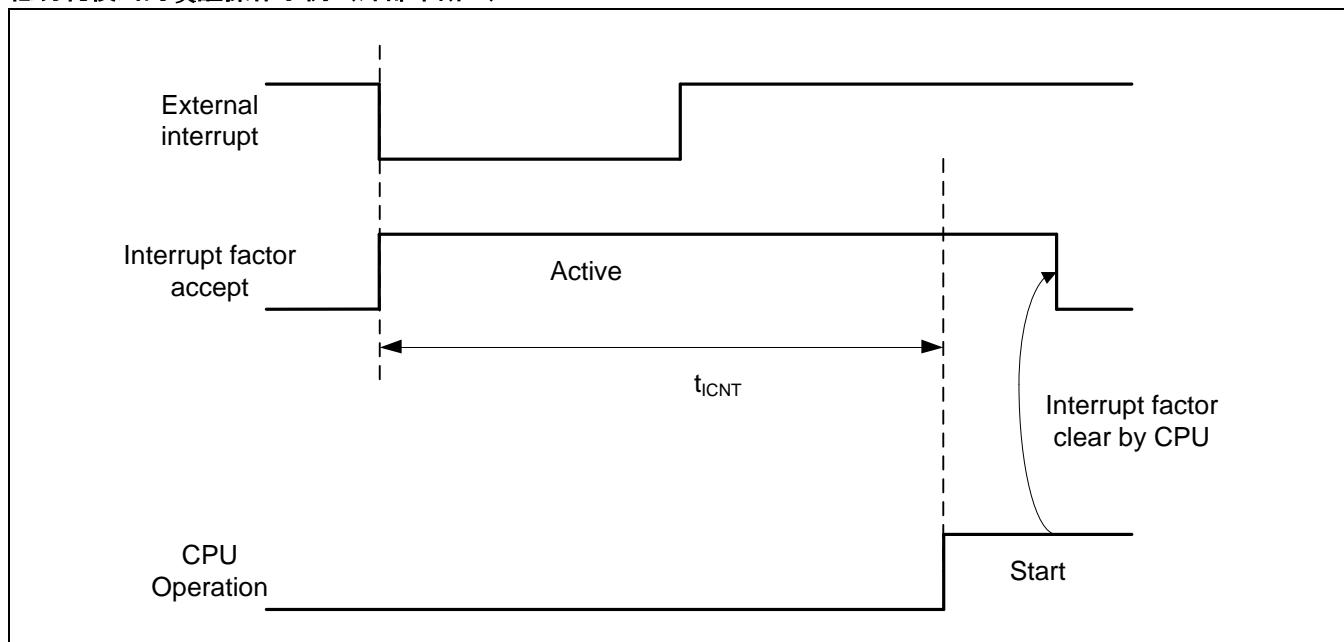

| 11.8.1 唤醒因素：中断/唤醒                                      | 85 |

| 11.8.2 唤醒因素：复位                                         | 87 |

| 12. 订购信息                                               | 89 |

| 13. 封装尺寸                                               | 90 |

| 14. Errata                                             | 96 |

| 14.1 受影响的部件                                            | 96 |

| 14.2 合格状态                                              | 96 |

---

|                     |    |

|---------------------|----|

| 14.3 Errata 总结..... | 96 |

| 文档历史 .....          | 97 |

| 销售、解决方案以及法律信息.....  | 98 |

## 1. 产品阵容

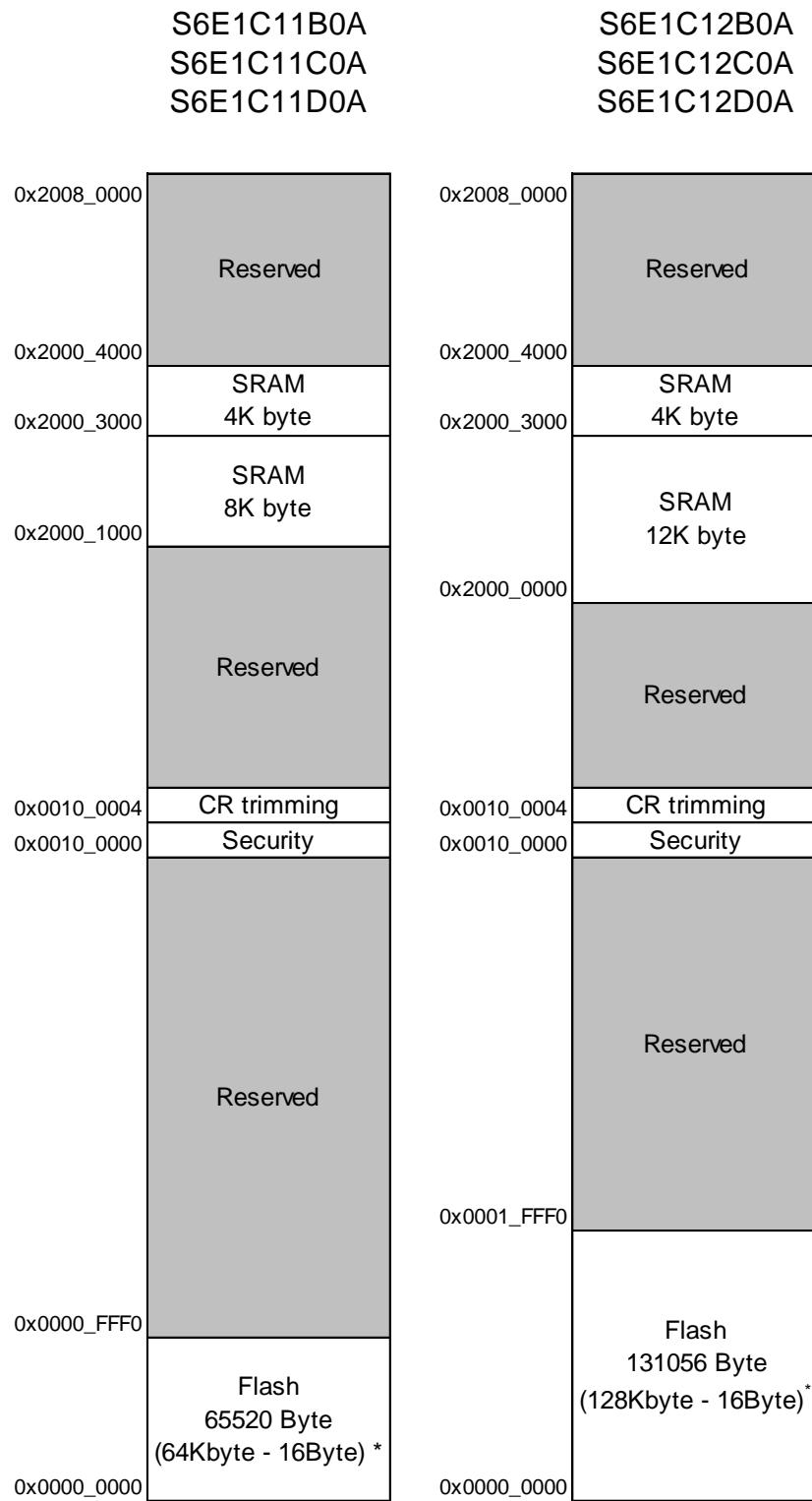

### 存储器容量

| 产品名称    | S6E1C11B0A/<br>S6E1C11C0A/<br>S6E1C11D0A | S6E1C12B0A/<br>S6E1C12C0A/<br>S6E1C12D0A |

|---------|------------------------------------------|------------------------------------------|

| 片上闪存    | 64 Kbytes                                | 128 Kbytes                               |

| 片上 SRAM | 12 Kbytes                                | 16 Kbytes                                |

### 功能

| 产品名称                                                   | S6E1C12B0A/<br>S6E1C11B0A                      | S6E1C12C0A/<br>S6E1C12C0A                         | S6E1C11D0A/<br>S6E1C12D0A                         |

|--------------------------------------------------------|------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| 引脚数                                                    | 32                                             | 48                                                | 64                                                |

| CPU                                                    | Cortex-M0+                                     | 40.8 MHz                                          |                                                   |

| 电源电压范围                                                 |                                                | 1.65 V to 3.6 V                                   |                                                   |

| DSTC                                                   |                                                | 64 ch.                                            |                                                   |

| 多功能串口<br>(UART/CSIO/I <sup>2</sup> C/I <sup>2</sup> S) | 4 ch. (最大)<br>Ch.0/1/3 不带 FIFO<br>Ch. 6 带 FIFO | 6 ch. (最大)<br>Ch.0/1/3 不带 FIFO<br>Ch.4/6/7 带 FIFO | 6 ch. (最大)<br>Ch.0/1/3 不带 FIFO<br>Ch.4/6/7 带 FIFO |

|                                                        | I <sup>2</sup> S : 无                           | I <sup>2</sup> S : 1 ch (最大)<br>Ch. 6 带 FIFO      | I <sup>2</sup> S : 2 ch (最大)<br>Ch. 4/6 带 FIFO    |

| 基本定时器<br>(PWC/重载定时器/PWM/PPG)                           |                                                | 8 ch. (最大)                                        |                                                   |

| 双定时器                                                   |                                                | 1 unit                                            |                                                   |

| HDMI-CEC/遥控接收器                                         | 1 ch.(最大)<br>Ch.1                              | 2 ch (最大)<br>Ch.0/1                               |                                                   |

| I <sup>2</sup> C 从机                                    |                                                | 1 ch (最大)                                         |                                                   |

| 智能卡接口                                                  |                                                | 无                                                 | 1 ch (最大)                                         |

| 实时时钟                                                   |                                                | 1 unit                                            |                                                   |

| 计时计数器                                                  |                                                | 1 unit                                            |                                                   |

| CRC 加速器                                                |                                                | 有                                                 |                                                   |

| 监视定时器                                                  |                                                | 1 ch. (SW) + 1 ch. (HW)                           |                                                   |

| 外部中断                                                   | 7 pins (最大),<br>NMI x 1                        | 9 pins (最大),<br>NMI x 1                           | 12 pins (最大),<br>NMI x 1                          |

| I/O 口                                                  | 24 pins (最大)                                   | 38 pins (最大)                                      | 54 pins (最大)                                      |

| 12 位 A/D 转换器                                           | 6 ch. (1 unit)                                 | 8 ch. (1 unit)                                    | 8 ch. (1 unit)                                    |

| CSV (时钟监视功能)                                           |                                                | 有                                                 |                                                   |

| LVD (低压检测)                                             |                                                | 2 ch.                                             |                                                   |

| 内置 CR                                                  | 高速                                             | 8 MHz (Typ)                                       |                                                   |

|                                                        | 低速                                             | 100 kHz (Typ)                                     |                                                   |

| 调试功能                                                   |                                                | SW-DP                                             |                                                   |

| 唯一 ID                                                  |                                                | 有                                                 |                                                   |

### 注意事项：

- 受封装引脚的限制，未配置各产品搭载的外设功能的全部信号。需要某种功能时，使用 I/O 口的端口重定位功能进行再配置。

有关内置 CR 的精确度，参见“11. 电气特性 11.4 AC 特性 11.4.3 内置 CR 振荡特性”。

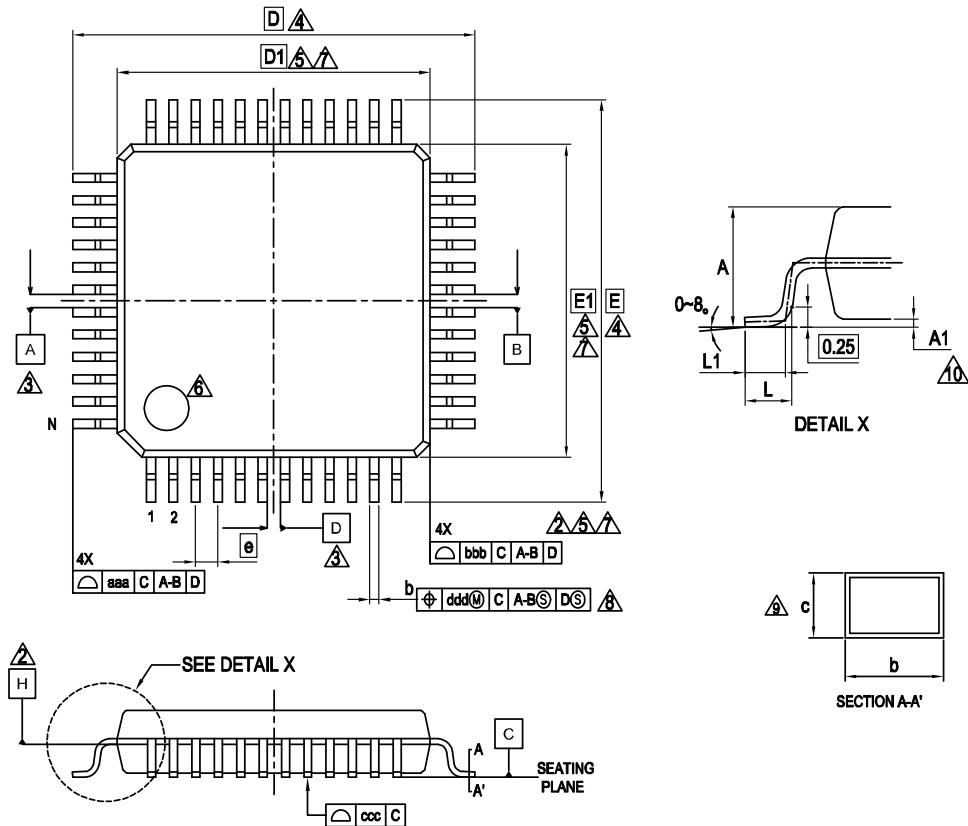

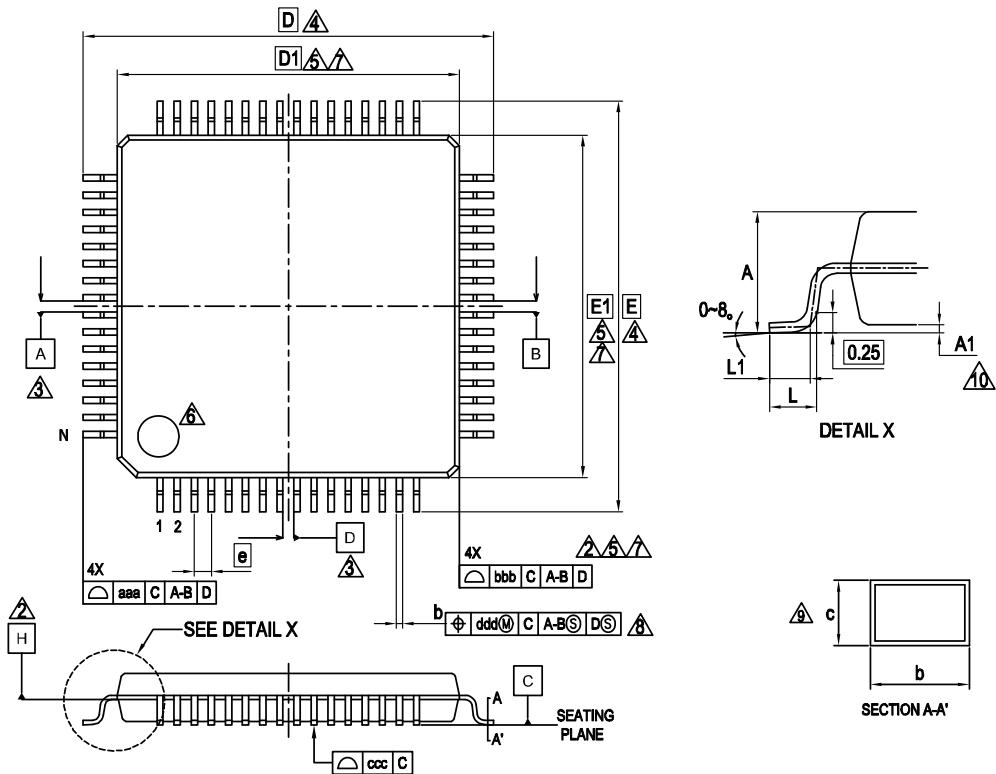

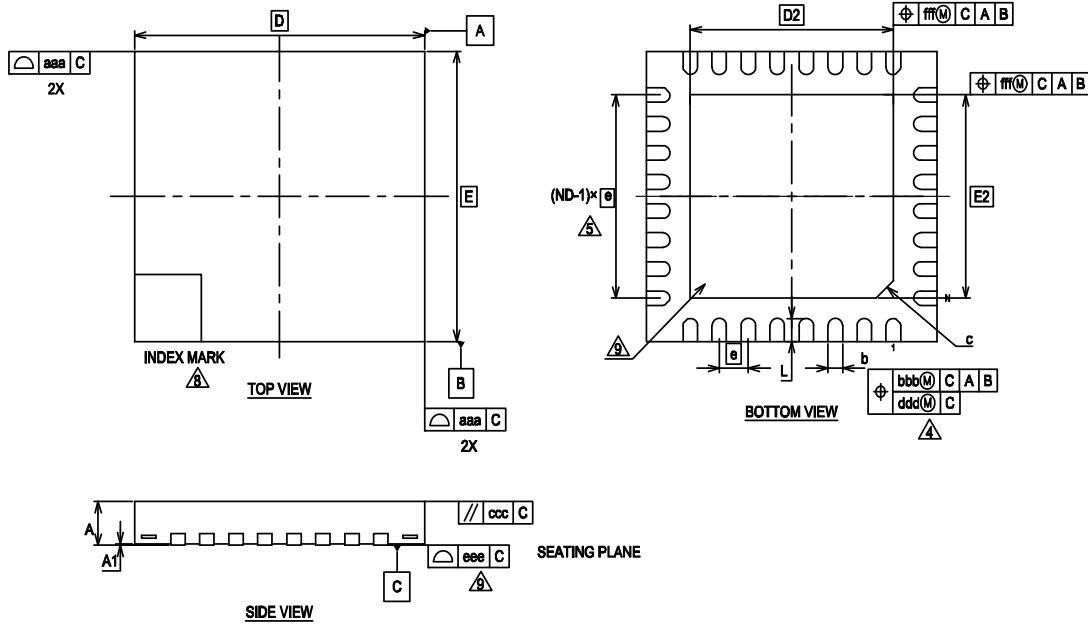

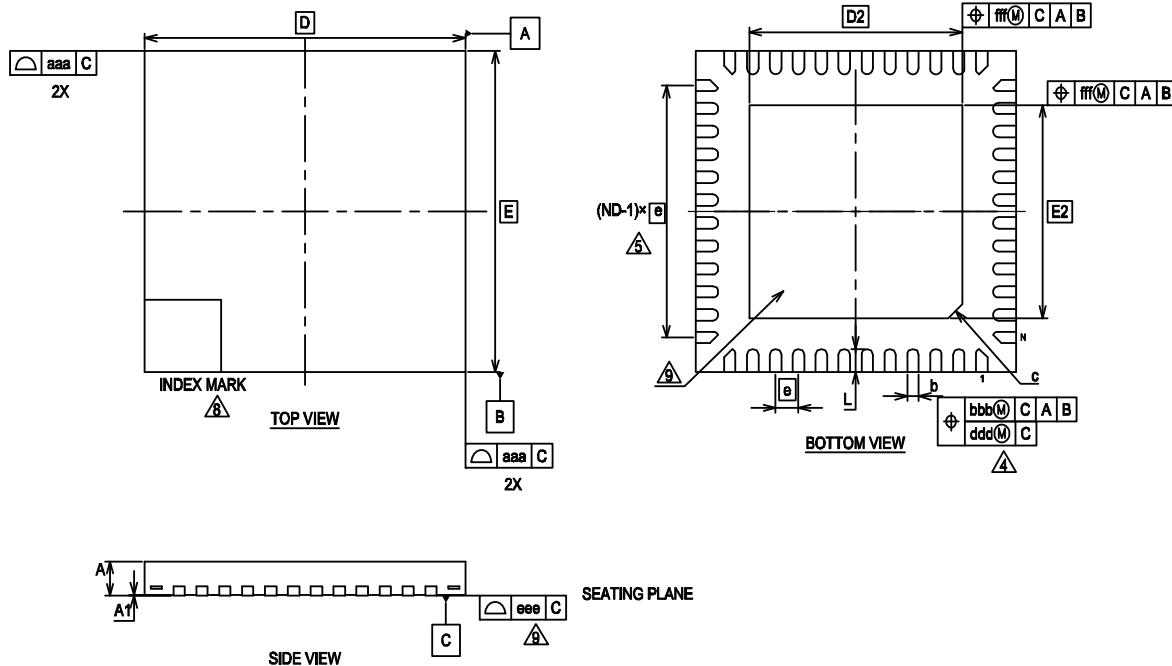

## 2. 封装

| 封装                           | 产品名称 | S6E1C12B0A/<br>S6E1C11B0A | S6E1C12C0A/<br>S6E1C11C0A | S6E1C12D0A/<br>S6E1C11D0A |

|------------------------------|------|---------------------------|---------------------------|---------------------------|

| LQFP: LQB032 (0.80 mm 间距)    | ○    | -                         | -                         |                           |

| QFN: WNU032 (0.50 mm 间距)     | ○    | -                         | -                         |                           |

| LQFP: LQA048-02 (0.50 mm 间距) | -    | ○                         | -                         |                           |

| QFN: WNY048 (0.50 mm 间距)     | -    | ○                         | -                         |                           |

| LQFP: LQD064-02 (0.50 mm 间距) | -    | -                         | ○                         |                           |

| QFN: WNS064 (0.50 mm 间距)     | -    | -                         | ○                         |                           |

○: 支持

### 注意事项：

- 各封装的详情，参见“13. 封装尺寸”。

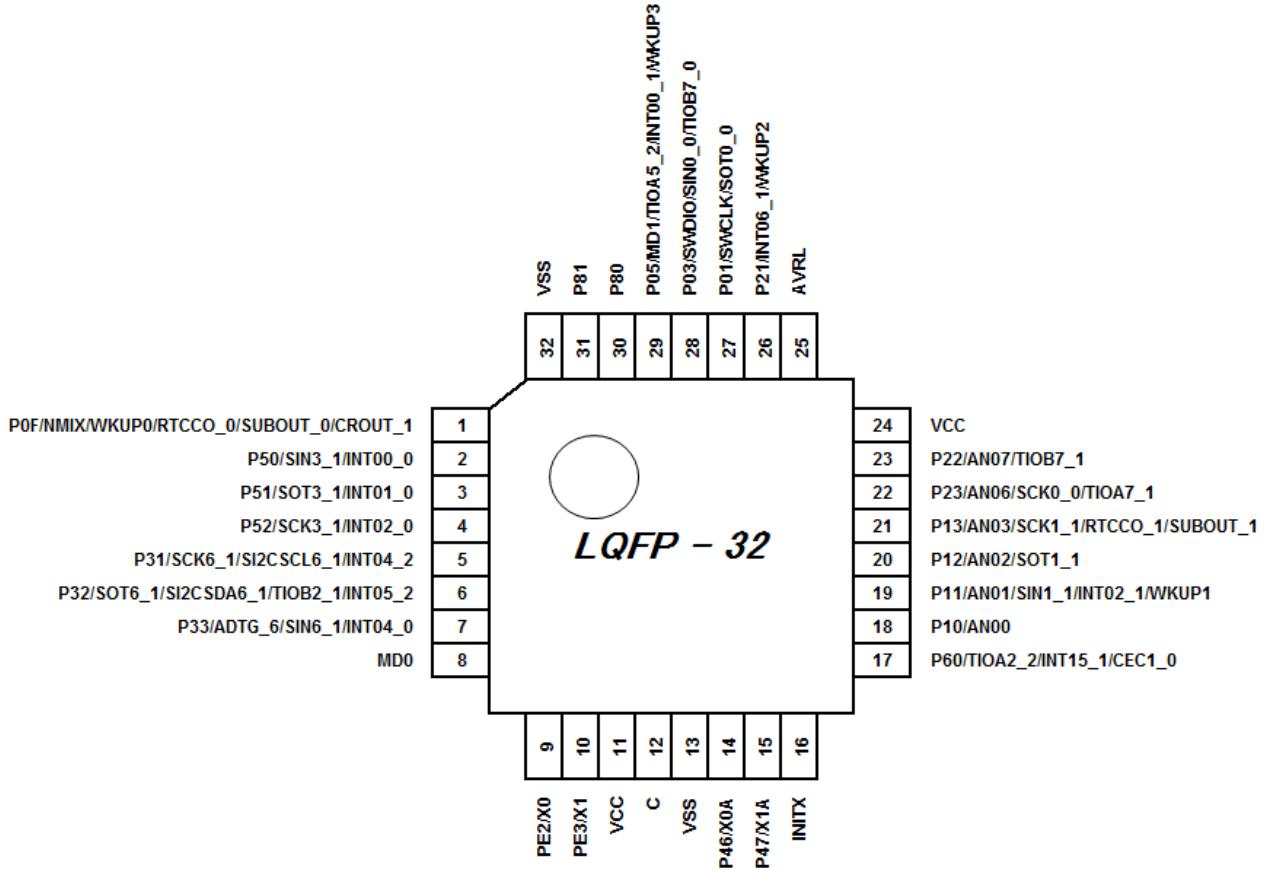

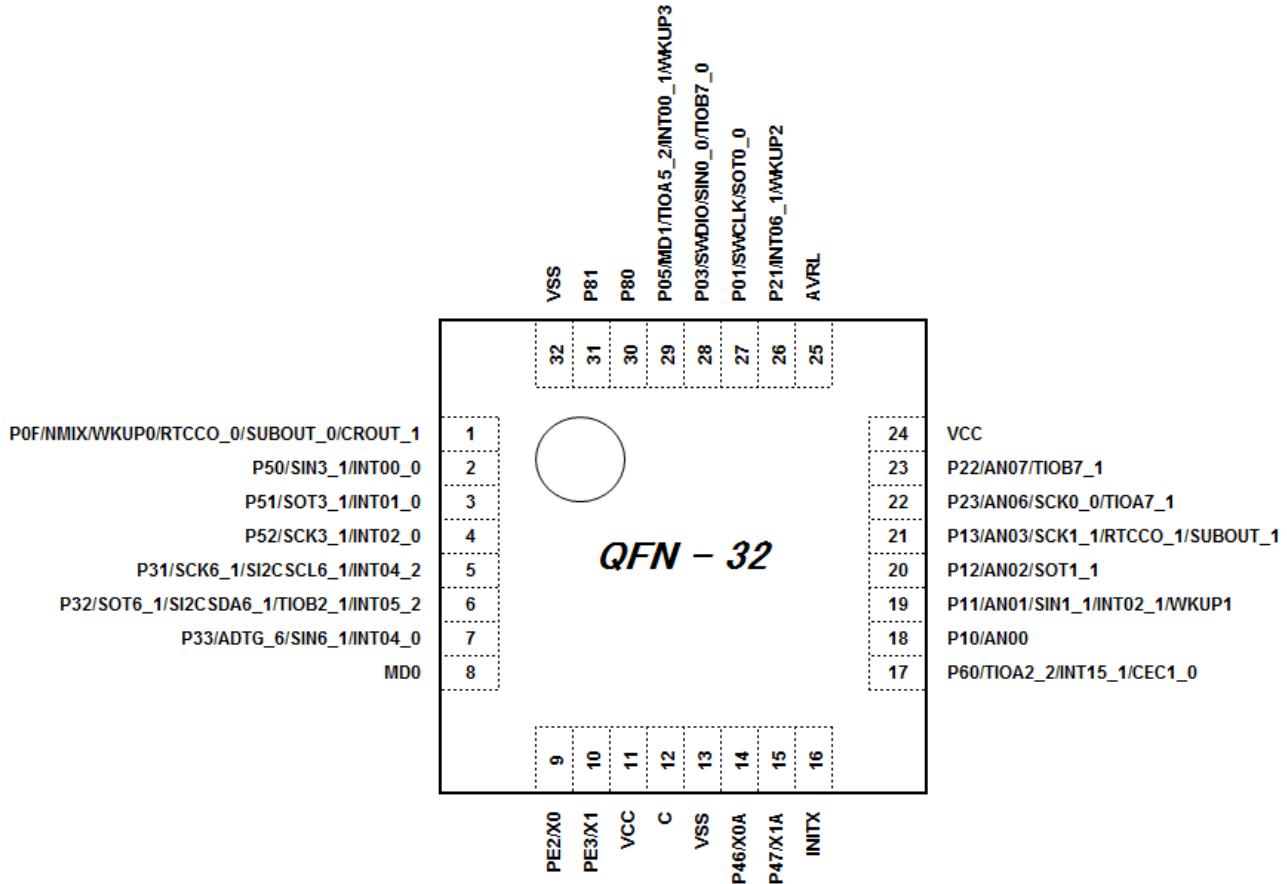

### 3. 引脚配置图

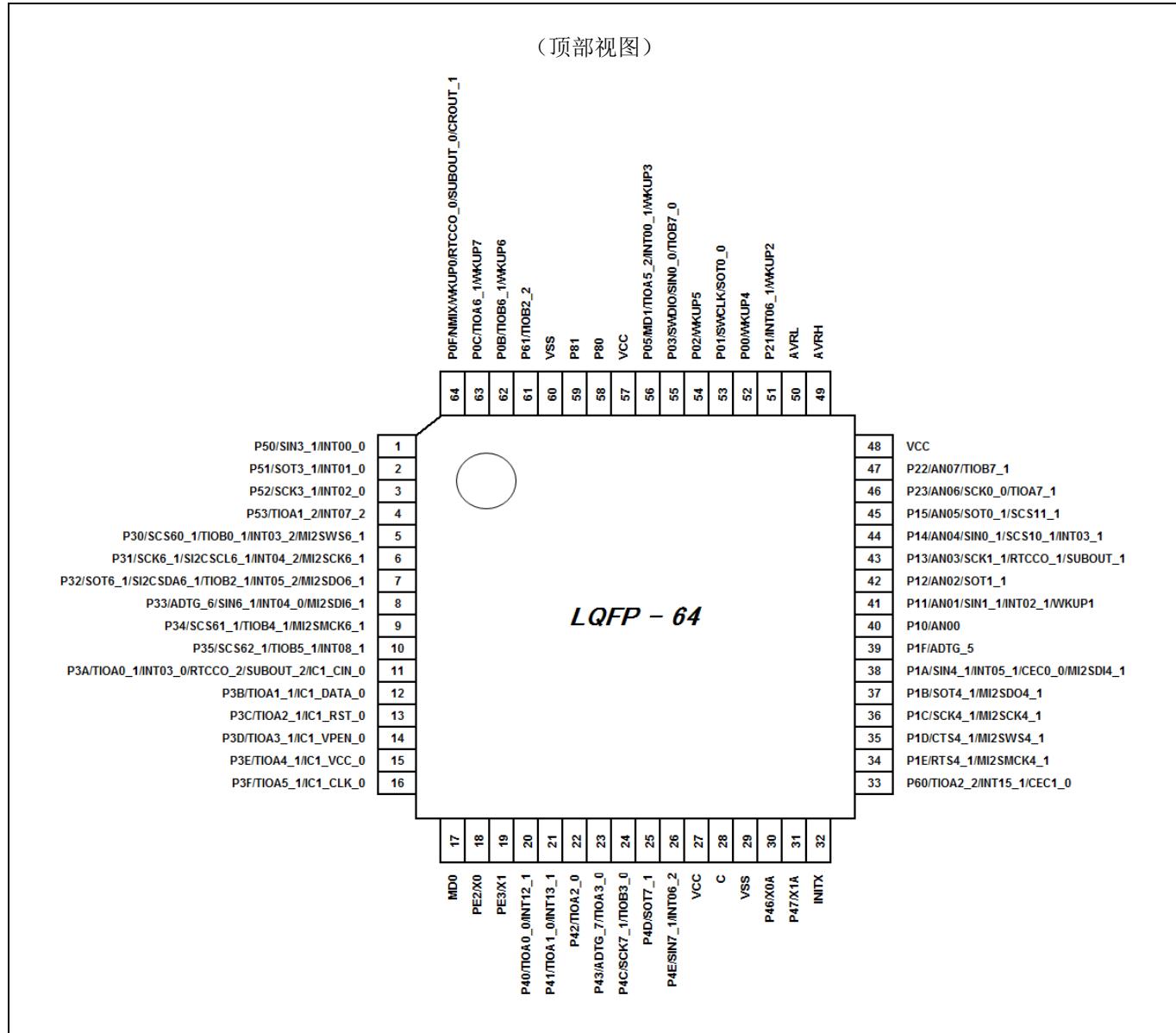

LQD064-02

#### 注意事项：

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器 (EPFR) 选择引脚。

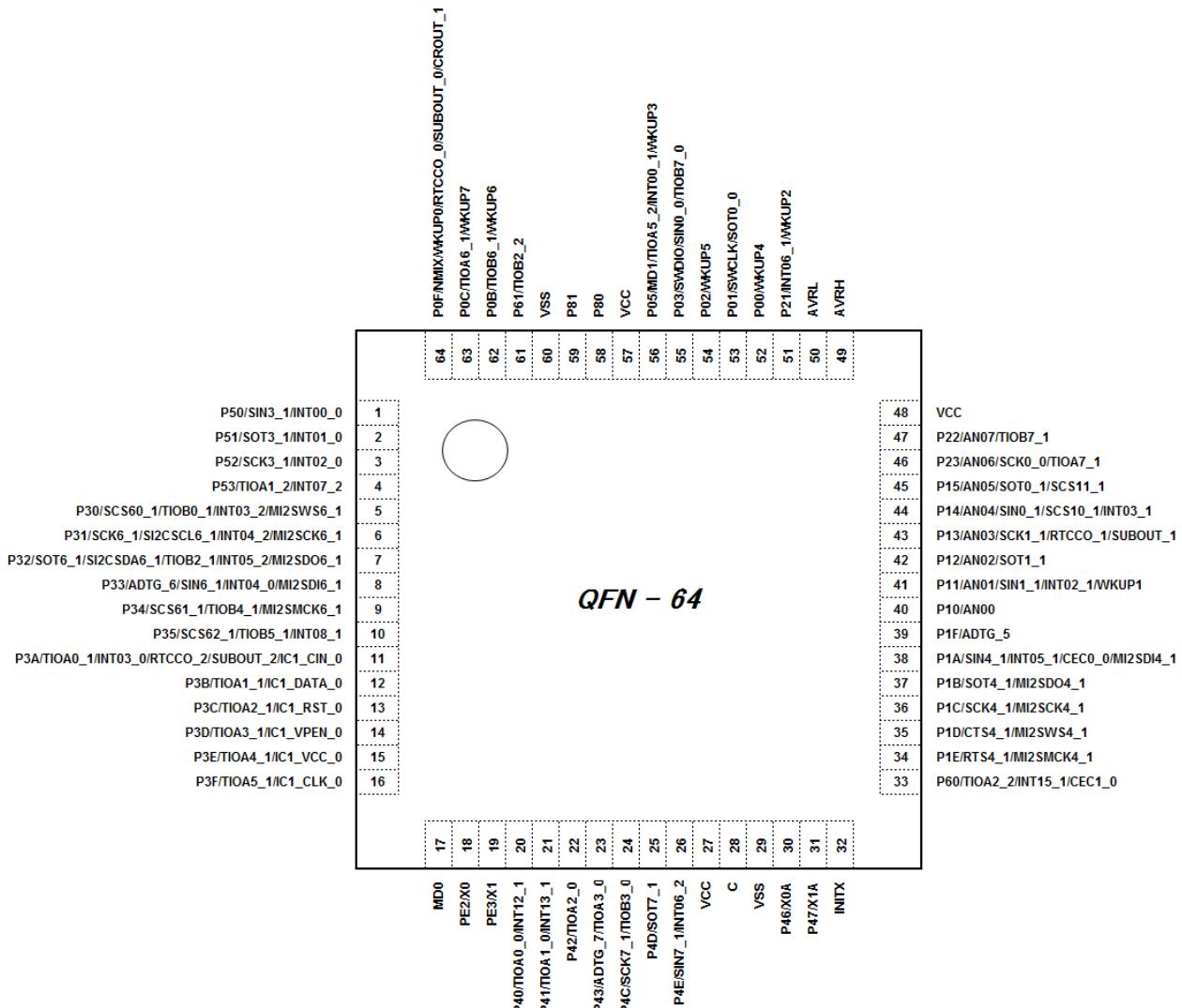

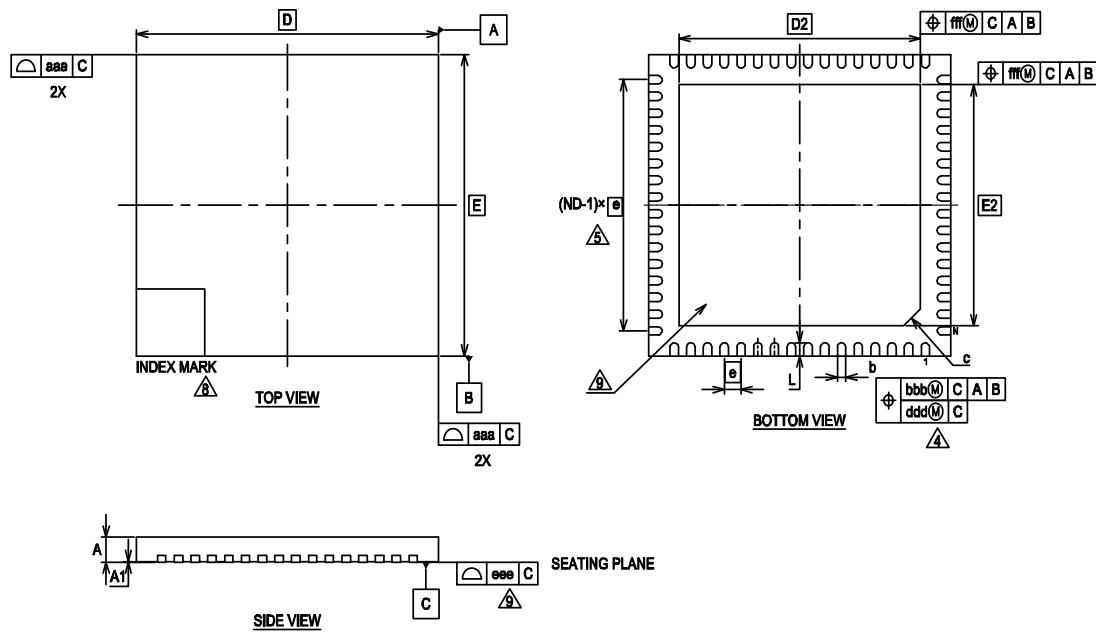

**WNS064**

(顶部视图)

**注意事项：**

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器（EPFR）选择引脚。

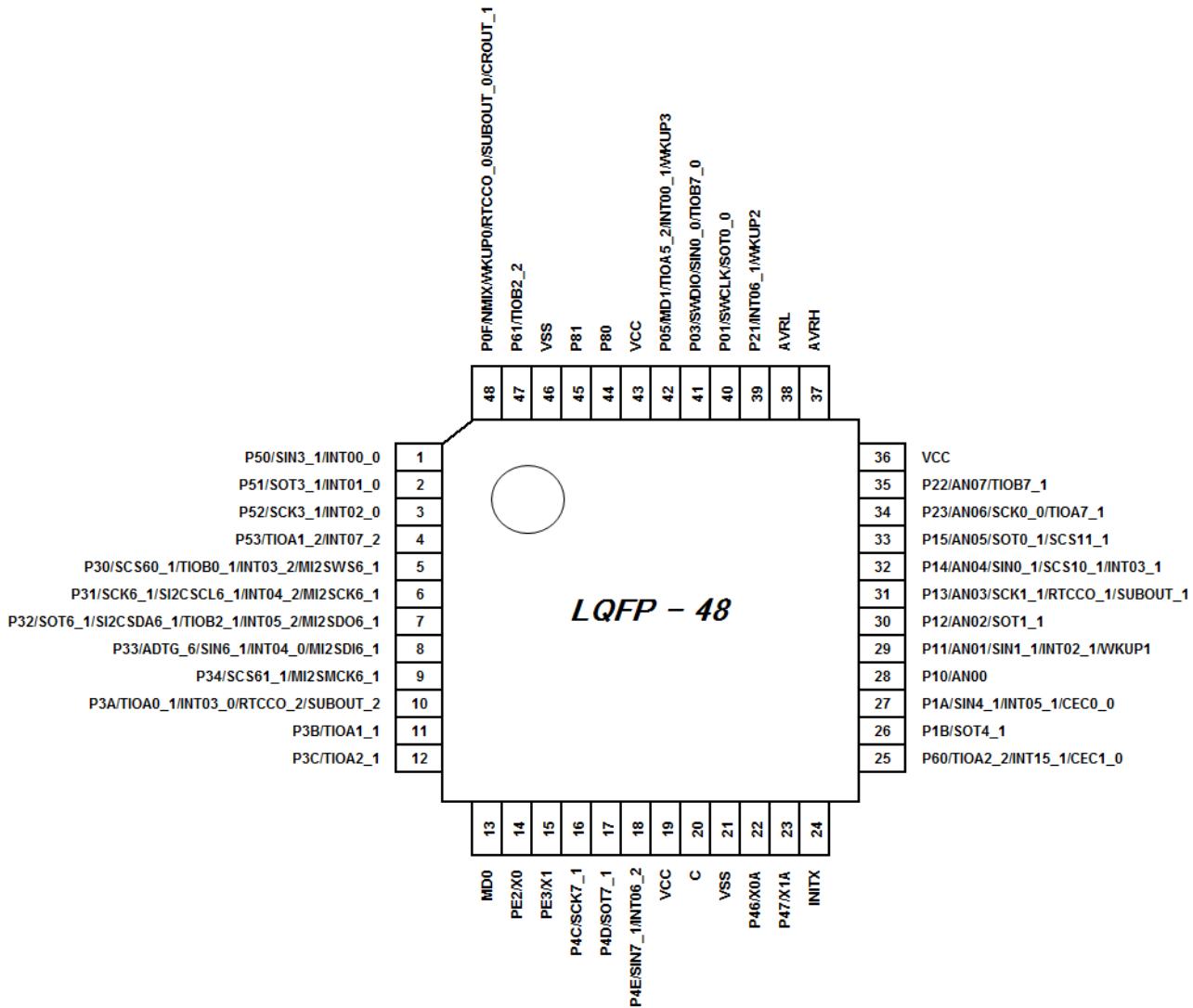

**LQA048-02**

(顶部视图)

**注意事项：**

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。

使用扩展端口功能寄存器 (EPFR) 选择引脚。

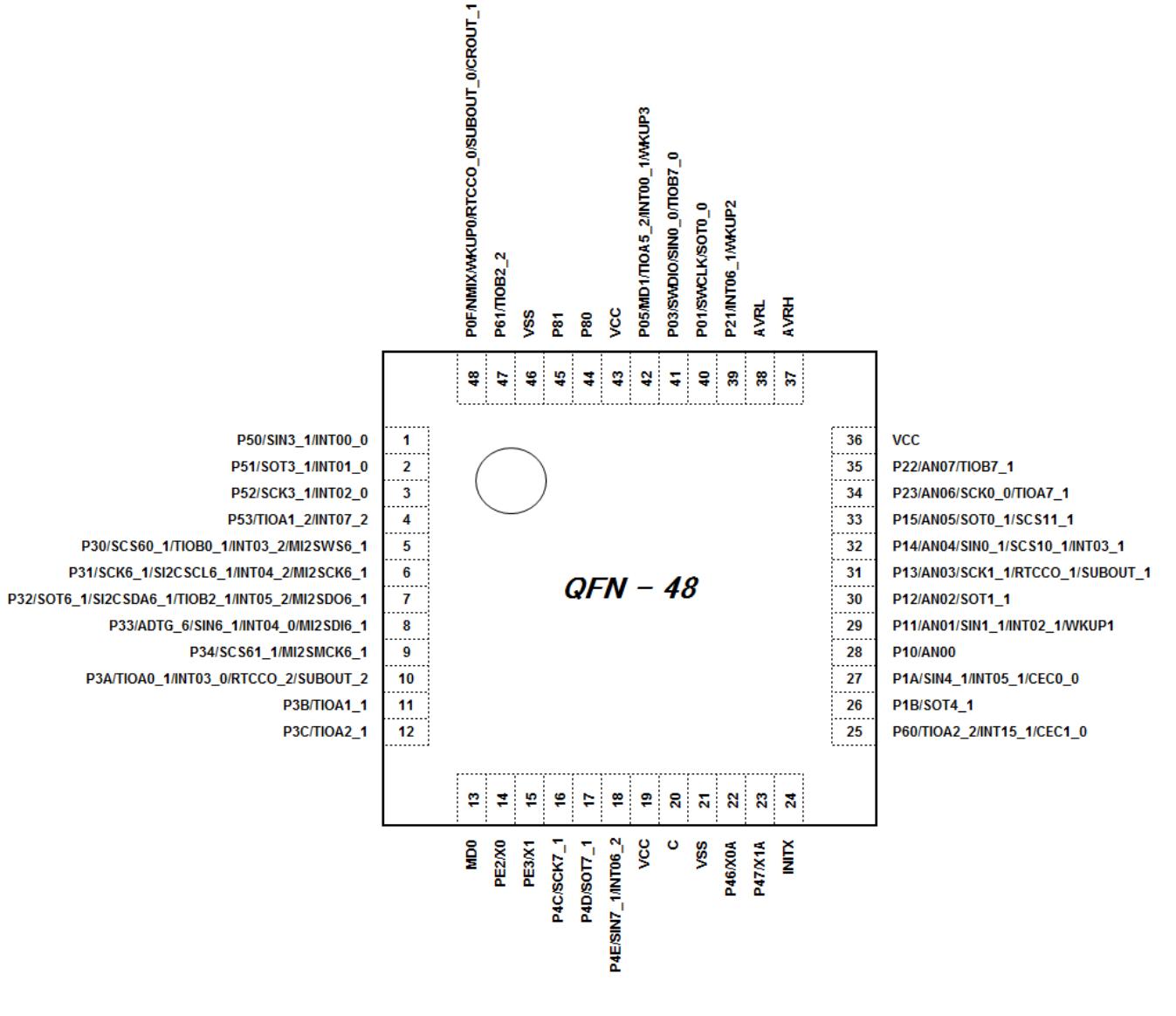

**WNY048**

(顶部视图)

**注意事项：**

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器（EPFR）选择引脚。

**LQB032**

(顶部视图)

**注意事项：**

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器（EPFR）选择引脚。

**WNU032**

(顶部视图)

**注意事项：**

- 引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。

使用扩展端口功能寄存器（EPFR）选择引脚。

## 4. 引脚功能一览表

### 引脚号一览表

引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器（EPFR）选择引脚。

| 引脚号               |                   |                   | 引脚名称       | 电路类型 | 引脚状态<br>类型 |

|-------------------|-------------------|-------------------|------------|------|------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |            |      |            |

| 1                 | 1                 | 2                 | P50        | D    | K          |

|                   |                   |                   | SIN3_1     |      |            |

|                   |                   |                   | INT00_0    |      |            |

| 2                 | 2                 | 3                 | P51        | D    | K          |

|                   |                   |                   | SOT3_1     |      |            |

|                   |                   |                   | INT01_0    |      |            |

| 3                 | 3                 | 4                 | P52        | D    | K          |

|                   |                   |                   | SCK3_1     |      |            |

|                   |                   |                   | INT02_0    |      |            |

| 4                 | 4                 | -                 | P53        | D    | K          |

|                   |                   |                   | TIOA1_2    |      |            |

|                   |                   |                   | INT07_2    |      |            |

| 5                 | 5                 | -                 | P30        | D    | K          |

|                   |                   |                   | SCS60_1    |      |            |

|                   |                   |                   | TIOB0_1    |      |            |

|                   |                   |                   | INT03_2    |      |            |

|                   |                   |                   | MI2SWS6_1  |      |            |

| 6                 | 6                 | -                 | P31        | H    | K          |

|                   |                   |                   | SCK6_1     |      |            |

|                   |                   |                   | SI2CSCL6_1 |      |            |

|                   |                   |                   | INT04_2    |      |            |

|                   |                   |                   | MI2SCK6_1  |      |            |

| -                 | -                 | 5                 | P31        | H    | K          |

|                   |                   |                   | SCK6_1     |      |            |

|                   |                   |                   | SI2CSCL6_1 |      |            |

|                   |                   |                   | INT04_2    |      |            |

| 7                 | 7                 | -                 | P32        | H    | K          |

|                   |                   |                   | SOT6_1     |      |            |

|                   |                   |                   | SI2CSDA6_1 |      |            |

|                   |                   |                   | TIOB2_1    |      |            |

|                   |                   |                   | INT05_2    |      |            |

|                   |                   |                   | MI2SDO6_1  |      |            |

| -                 | -                 | 6                 | P32        | H    | K          |

|                   |                   |                   | SOT6_1     |      |            |

|                   |                   |                   | SI2CSDA6_1 |      |            |

|                   |                   |                   | TIOB2_1    |      |            |

|                   |                   |                   | INT05_2    |      |            |

| 引脚号               |                   |                   | 引脚名称       | 电路类型 | 引脚状态<br>类型 |

|-------------------|-------------------|-------------------|------------|------|------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |            |      |            |

| 8                 | 8                 | -                 | P33        | H    | K          |

|                   |                   |                   | ADTG_6     |      |            |

|                   |                   |                   | SIN6_1     |      |            |

|                   |                   |                   | INT04_0    |      |            |

|                   |                   |                   | MI2SDI6_1  |      |            |

| -                 | -                 | 7                 | P33        | H    | K          |

|                   |                   |                   | ADTG_6     |      |            |

|                   |                   |                   | SIN6_1     |      |            |

|                   |                   |                   | INT04_0    |      |            |

| 9                 | -                 | -                 | P34        | D    | K          |

|                   |                   |                   | SCS61_1    |      |            |

|                   |                   |                   | TIOB4_1    |      |            |

|                   |                   |                   | MI2SMCK6_1 |      |            |

| -                 | 9                 | -                 | P34        | D    | K          |

|                   |                   |                   | SCS61_1    |      |            |

|                   |                   |                   | MI2SMCK6_1 |      |            |

|                   |                   |                   | P35        |      |            |

| 10                | -                 | -                 | SCS62_1    | D    | K          |

|                   |                   |                   | TIOB5_1    |      |            |

|                   |                   |                   | INT08_1    |      |            |

|                   |                   |                   | P3A        |      |            |

| 11                | -                 | -                 | TIOA0_1    | D    | K          |

|                   |                   |                   | INT03_0    |      |            |

|                   |                   |                   | RTCCO_2    |      |            |

|                   |                   |                   | SUBOUT_2   |      |            |

|                   |                   |                   | IC1_CIN_0  |      |            |

| -                 | 10                | -                 | P3A        | D    | K          |

|                   |                   |                   | TIOA0_1    |      |            |

|                   |                   |                   | INT03_0    |      |            |

|                   |                   |                   | RTCCO_2    |      |            |

|                   |                   |                   | SUBOUT_2   |      |            |

| 12                | -                 | -                 | P3B        | D    | K          |

|                   |                   |                   | TIOA1_1    |      |            |

|                   |                   |                   | IC1_DATA_0 |      |            |

| -                 | 11                | -                 | P3B        | D    | K          |

|                   |                   |                   | TIOA1_1    |      |            |

| 13                | -                 | -                 | P3C        | D    | K          |

|                   |                   |                   | TIOA2_1    |      |            |

|                   |                   |                   | IC1_RST_0  |      |            |

| -                 | 12                | -                 | P3C        | D    | K          |

|                   |                   |                   | TIOA2_1    |      |            |

| 14                | -                 | -                 | P3D        | D    | K          |

|                   |                   |                   | TIOA3_1    |      |            |

|                   |                   |                   | IC1_VPEN_0 |      |            |

| 引脚号               |                   |                   | 引脚名称      | 电路类型 | 引脚状态<br>类型 |

|-------------------|-------------------|-------------------|-----------|------|------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |           |      |            |

| 15                | -                 | -                 | P3E       | D    | K          |

|                   |                   |                   | TIOA4_1   |      |            |

|                   |                   |                   | IC1_VCC_0 |      |            |

| 16                | -                 | -                 | P3F       | D    | K          |

|                   |                   |                   | TIOA5_1   |      |            |

|                   |                   |                   | IC1_CLK_0 |      |            |

| 17                | 13                | 8                 | MD0       | I    | F          |

| 18                | 14                | 9                 | PE2       | A    | A          |

|                   |                   |                   | X0        |      |            |

| 19                | 15                | 10                | PE3       | A    | B          |

|                   |                   |                   | X1        |      |            |

| 20                | -                 | -                 | P40       | D    | K          |

|                   |                   |                   | TIOA0_0   |      |            |

|                   |                   |                   | INT12_1   |      |            |

| 21                | -                 | -                 | P41       | D    | K          |

|                   |                   |                   | TIOA1_0   |      |            |

|                   |                   |                   | INT13_1   |      |            |

| 22                | -                 | -                 | P42       | D    | K          |

|                   |                   |                   | TIOA2_0   |      |            |

| 23                | -                 | -                 | P43       | D    | K          |

|                   |                   |                   | ADTG_7    |      |            |

|                   |                   |                   | TIOA3_0   |      |            |

| 24                | -                 | -                 | P4C       | D    | K          |

|                   |                   |                   | SCK7_1    |      |            |

|                   |                   |                   | TIOB3_0   |      |            |

| -                 | 16                | -                 | P4C       | D    | K          |

|                   |                   |                   | SCK7_1    |      |            |

| 25                | 17                | -                 | P4D       | D    | K          |

|                   |                   |                   | SOT7_1    |      |            |

| 26                | 18                | -                 | P4E       | D    | K          |

|                   |                   |                   | SIN7_1    |      |            |

|                   |                   |                   | INT06_2   |      |            |

| 27                | 19                | 11                | VCC       | -    | -          |

| 28                | 20                | 12                | C         | -    | -          |

| 29                | 21                | 13                | VSS       | -    | -          |

| 30                | 22                | 14                | P46       | C    | C          |

|                   |                   |                   | X0A       |      |            |

| 31                | 23                | 15                | P47       | C    | D          |

|                   |                   |                   | X1A       |      |            |

| 32                | 24                | 16                | INITX     | B    | E          |

| 33                | 25                | 17                | P60       | H    | K          |

|                   |                   |                   | TIOA2_2   |      |            |

|                   |                   |                   | INT15_1   |      |            |

|                   |                   |                   | CEC1_0    |      |            |

| 引脚号               |                   |                   | 引脚名称       | 电路类型 | 引脚状态<br>类型 |

|-------------------|-------------------|-------------------|------------|------|------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |            |      |            |

| 34                | -                 | -                 | P1E        | D    | K          |

|                   |                   |                   | RTS4_1     |      |            |

|                   |                   |                   | MI2SMCK4_1 |      |            |

| 35                | -                 | -                 | P1D        | D    | K          |

|                   |                   |                   | CTS4_1     |      |            |

|                   |                   |                   | MI2SWS4_1  |      |            |

| 36                | -                 | -                 | P1C        | D    | K          |

|                   |                   |                   | SCK4_1     |      |            |

|                   |                   |                   | MI2SCK4_1  |      |            |

| 37                | -                 | -                 | P1B        | D    | K          |

|                   |                   |                   | SOT4_1     |      |            |

|                   |                   |                   | MI2SDO4_1  |      |            |

| -                 | 26                | -                 | P1B        | D    | K          |

|                   |                   |                   | SOT4_1     |      |            |

| 38                | -                 | -                 | P1A        | H    | K          |

|                   |                   |                   | SIN4_1     |      |            |

|                   |                   |                   | INT05_1    |      |            |

|                   |                   |                   | CECO_0     |      |            |

|                   |                   |                   | MI2SDI4_1  |      |            |

| -                 | 27                | -                 | P1A        | H    | K          |

|                   |                   |                   | SIN4_1     |      |            |

|                   |                   |                   | INT05_1    |      |            |

|                   |                   |                   | CECO_0     |      |            |

| 39                | -                 | -                 | P1F        | D    | K          |

|                   |                   |                   | ADTG_5     |      |            |

| 40                | 28                | 18                | P10        | F    | J          |

|                   |                   |                   | AN00       |      |            |

| 41                | 29                | 19                | P11        | G    | J          |

|                   |                   |                   | AN01       |      |            |

|                   |                   |                   | SIN1_1     |      |            |

|                   |                   |                   | INT02_1    |      |            |

|                   |                   |                   | WKUP1      |      |            |

| 42                | 30                | 20                | P12        | F    | J          |

|                   |                   |                   | AN02       |      |            |

|                   |                   |                   | SOT1_1     |      |            |

| 43                | 31                | 21                | P13        | F    | J          |

|                   |                   |                   | AN03       |      |            |

|                   |                   |                   | SCK1_1     |      |            |

|                   |                   |                   | RTCCO_1    |      |            |

|                   |                   |                   | SUBOUT_1   |      |            |

| 44                | 32                | -                 | P14        | F    | J          |

|                   |                   |                   | AN04       |      |            |

|                   |                   |                   | SIN0_1     |      |            |

|                   |                   |                   | SCS10_1    |      |            |

|                   |                   |                   | INT03_1    |      |            |

| 45                | 33                | -                 | P15        | F    | J          |

|                   |                   |                   | AN05       |      |            |

|                   |                   |                   | SOT0_1     |      |            |

|                   |                   |                   | SCS11_1    |      |            |

| 引脚号               |                   |                   | 引脚名称     | 电路类型 | 引脚状态<br>类型 |

|-------------------|-------------------|-------------------|----------|------|------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |          |      |            |

| 46                | 34                | 22                | P23      | F    | J          |

|                   |                   |                   | AN06     |      |            |

|                   |                   |                   | SCK0_0   |      |            |

|                   |                   |                   | TIOA7_1  |      |            |

| 47                | 35                | 23                | P22      | F    | J          |

|                   |                   |                   | AN07     |      |            |

|                   |                   |                   | TIOB7_1  |      |            |

| 48                | 36                | 24                | VCC      | -    | -          |

| 49                | 37                | -                 | AVRH *   | -    | -          |

| 50                | 38                | 25                | AVRL     | -    | -          |

| 51                | 39                | 26                | P21      | E    | K          |

|                   |                   |                   | INT06_1  |      |            |

|                   |                   |                   | WKUP2    |      |            |

| 52                | -                 | -                 | P00      | E    | K          |

|                   |                   |                   | WKUP4    |      |            |

| 53                | 40                | 27                | P01      | D    | K          |

|                   |                   |                   | SWCLK    |      |            |

|                   |                   |                   | SOT0_0   |      |            |

| 54                | -                 | -                 | P02      | E    | K          |

|                   |                   |                   | WKUP5    |      |            |

| 55                | 41                | 28                | P03      | D    | K          |

|                   |                   |                   | SWDIO    |      |            |

|                   |                   |                   | SIN0_0   |      |            |

|                   |                   |                   | TIOB7_0  |      |            |

| 56                | 42                | 29                | P05      | E    | K          |

|                   |                   |                   | MD1      |      |            |

|                   |                   |                   | TIOA5_2  |      |            |

|                   |                   |                   | INT00_1  |      |            |

|                   |                   |                   | WKUP3    |      |            |

| 57                | 43                | -                 | VCC      | -    | -          |

| 58                | 44                | 30                | P80      | J    | G          |

| 59                | 45                | 31                | P81      | J    | G          |

| 60                | 46                | 32                | VSS      | -    | -          |

| 61                | 47                | -                 | P61      | H    | K          |

|                   |                   |                   | TIOB2_2  |      |            |

| 62                | -                 | -                 | P0B      | E    | K          |

|                   |                   |                   | TIOB6_1  |      |            |

|                   |                   |                   | WKUP6    |      |            |

| 63                | -                 | -                 | P0C      | E    | K          |

|                   |                   |                   | TIOA6_1  |      |            |

|                   |                   |                   | WKUP7    |      |            |

| 64                | 48                | 1                 | P0F      | E    | I          |

|                   |                   |                   | NMIX     |      |            |

|                   |                   |                   | WKUP0    |      |            |

|                   |                   |                   | RTCCO_0  |      |            |

|                   |                   |                   | SUBOUT_0 |      |            |

|                   |                   |                   | CROUT_1  |      |            |

\*: \*: 32 管脚封装产品的 AVRH 引脚在芯片内部与 VCC 引脚相连封装在一起。

## 引脚功能一览表

引脚名称（例如 XXX\_1 和 XXX\_2）中下划线（"\_"）后面的数字代表重定位端口号。有多个引脚可为同一路通道提供同一功能。使用扩展端口功能寄存器（EPFR）选择引脚。

| 引脚功能    | 引脚名称    | 功能说明                                 | 引脚号               |                   |                   |

|---------|---------|--------------------------------------|-------------------|-------------------|-------------------|

|         |         |                                      | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| ADC     | ADTG_5  | A/D 转换器外部触发输入引脚                      | 39                | -                 | -                 |

|         | ADTG_6  |                                      | 8                 | 8                 | 7                 |

|         | ADTG_7  |                                      | 23                | -                 | -                 |

| ADC     | AN00    | A/D 转换器模拟输入引脚。<br>ANxx 表示 ADC ch.xx。 | 40                | 28                | 18                |

|         | AN01    |                                      | 41                | 29                | 19                |

|         | AN02    |                                      | 42                | 30                | 20                |

|         | AN03    |                                      | 43                | 31                | 21                |

|         | AN04    |                                      | 44                | 32                | -                 |

|         | AN05    |                                      | 45                | 33                | -                 |

|         | AN06    |                                      | 46                | 34                | 22                |

|         | AN07    |                                      | 47                | 35                | 23                |

| 基本定时器 0 | TIOA0_0 | 基本定时器 ch.0 TIOA 引脚                   | 20                | -                 | -                 |

|         | TIOA0_1 |                                      | 11                | 10                | -                 |

| 基本定时器 1 | TIOB0_1 | 基本定时器 ch.0 TIOB 引脚                   | 5                 | 5                 | -                 |

|         | TIOA1_0 |                                      | 21                | -                 | -                 |

| 基本定时器 1 | TIOA1_1 | 基本定时器 ch.1 TIOA 引脚                   | 12                | 11                | -                 |

|         | TIOA1_2 |                                      | 4                 | 4                 | -                 |

|         | TIOA2_0 |                                      | 22                | -                 | -                 |

| 基本定时器 2 | TIOA2_1 | 基本定时器 ch.2 TIOA 引脚                   | 13                | 12                | -                 |

|         | TIOA2_2 |                                      | 33                | 25                | 17                |

|         | TIOB2_1 | 基本定时器 ch.2 TIOB 引脚                   | 7                 | 7                 | 6                 |

| 基本定时器 3 | TIOB2_2 |                                      | 61                | 47                | -                 |

|         | TIOA3_0 | 基本定时器 ch.3 TIOA 引脚                   | 23                | -                 | -                 |

|         | TIOA3_1 |                                      | 14                | -                 | -                 |

| 基本定时器 4 | TIOB3_0 | 基本定时器 ch.3 TIOB 引脚                   | 24                | -                 | -                 |

|         | TIOA4_1 |                                      | 15                | -                 | -                 |

| 基本定时器 5 | TIOB4_1 | 基本定时器 ch.4 TIOB 引脚                   | 9                 | -                 | -                 |

|         | TIOA5_1 | 基本定时器 ch.5 TIOA 引脚                   | 16                | -                 | -                 |

| 基本定时器 5 | TIOA5_2 |                                      | 56                | 42                | 29                |

|         | TIOB5_1 |                                      | 10                | -                 | -                 |

| 基本定时器 6 | TIOA6_1 | 基本定时器 ch.6 TIOA 引脚                   | 63                | -                 | -                 |

|         | TIOB6_1 |                                      | 62                | -                 | -                 |

| 基本定时器 7 | TIOA7_1 | 基本定时器 ch.7 TIOA 引脚                   | 46                | 34                | 22                |

|         | TIOB7_0 |                                      | 55                | 41                | 28                |

|         | TIOB7_1 |                                      | 47                | 35                | 23                |

| 调试器     | SWCLK   | 串行线调试接口时钟输入引脚                        | 53                | 40                | 27                |

|         | SWDIO   | 串行线调试接口数据输入/输出引脚                     | 55                | 41                | 28                |

| 引脚功能 | 引脚名称    | 功能说明           | 引脚号               |                   |                   |

|------|---------|----------------|-------------------|-------------------|-------------------|

|      |         |                | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| 外部中断 | INT00_0 | 外部中断请求 00 输入引脚 | 1                 | 1                 | 2                 |

|      | INT00_1 |                | 56                | 42                | 29                |

|      | INT01_0 | 外部中断请求 01 输入引脚 | 2                 | 2                 | 3                 |

|      | INT02_0 | 外部中断请求 02 输入引脚 | 3                 | 3                 | 4                 |

|      | INT02_1 |                | 41                | 29                | 19                |

|      | INT03_0 | 外部中断请求 03 输入引脚 | 11                | 10                | -                 |

|      | INT03_1 |                | 44                | 32                | -                 |

|      | INT03_2 |                | 5                 | 5                 | -                 |

|      | INT04_0 | 外部中断请求 04 输入引脚 | 8                 | 8                 | 7                 |

|      | INT04_2 |                | 6                 | 6                 | 5                 |

|      | INT05_1 | 外部中断请求 05 输入引脚 | 38                | 27                | -                 |

|      | INT05_2 |                | 7                 | 7                 | 6                 |

|      | INT06_1 | 外部中断请求 06 输入引脚 | 51                | 39                | 26                |

|      | INT06_2 |                | 26                | 18                | -                 |

|      | INT07_2 | 外部中断请求 07 输入引脚 | 4                 | 4                 | -                 |

|      | INT08_1 | 外部中断请求 08 输入引脚 | 10                | -                 | -                 |

|      | INT12_1 | 外部中断请求 12 输入引脚 | 20                | -                 | -                 |

|      | INT13_1 | 外部中断请求 13 输入引脚 | 21                | -                 | -                 |

|      | INT15_1 | 外部中断请求 15 输入引脚 | 33                | 25                | 17                |

|      | NMIX    | 不可屏蔽中断输入引脚     | 64                | 48                | 1                 |

| GPIO | P00     | 通用 I/O 口 0     | 52                | -                 | -                 |

|      | P01     |                | 53                | 40                | 27                |

|      | P02     |                | 54                | -                 | -                 |

|      | P03     |                | 55                | 41                | 28                |

|      | P05     |                | 56                | 42                | 29                |

|      | P0B     |                | 62                | -                 | -                 |

|      | P0C     |                | 63                | -                 | -                 |

|      | P0F     |                | 64                | 48                | 1                 |

| GPIO | P10     | 通用 I/O 口 1     | 40                | 28                | 18                |

|      | P11     |                | 41                | 29                | 19                |

|      | P12     |                | 42                | 30                | 20                |

|      | P13     |                | 43                | 31                | 21                |

|      | P14     |                | 44                | 32                | -                 |

|      | P15     |                | 45                | 33                | -                 |

|      | P1A     |                | 38                | 27                | -                 |

|      | P1B     |                | 37                | 26                | -                 |

|      | P1C     |                | 36                | -                 | -                 |

|      | P1D     |                | 35                | -                 | -                 |

|      | P1E     |                | 34                | -                 | -                 |

|      | P1F     |                | 39                | -                 | -                 |

| GPIO | P21     | 通用 I/O 口 2     | 51                | 39                | 26                |

|      | P22     |                | 47                | 35                | 23                |

|      | P23     |                | 46                | 34                | 22                |

| 引脚功能    | 引脚名称               | 功能说明                                                                                               | 引脚号               |                   |                   |

|---------|--------------------|----------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|

|         |                    |                                                                                                    | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| GPIO    | P30                | 通用 I/O 口 3                                                                                         | 5                 | 5                 | -                 |

|         | P31                |                                                                                                    | 6                 | 6                 | 5                 |

|         | P32                |                                                                                                    | 7                 | 7                 | 6                 |

|         | P33                |                                                                                                    | 8                 | 8                 | 7                 |

|         | P34                |                                                                                                    | 9                 | 9                 | -                 |

|         | P35                |                                                                                                    | 10                | -                 | -                 |

|         | P3A                |                                                                                                    | 11                | 10                | -                 |

|         | P3B                |                                                                                                    | 12                | 11                | -                 |

|         | P3C                |                                                                                                    | 13                | 12                | -                 |

|         | P3D                |                                                                                                    | 14                | -                 | -                 |

|         | P3E                |                                                                                                    | 15                | -                 | -                 |

|         | P3F                |                                                                                                    | 16                | -                 | -                 |

| GPIO    | P40                | 通用 I/O 口 4                                                                                         | 20                | -                 | -                 |

|         | P41                |                                                                                                    | 21                | -                 | -                 |

|         | P42                |                                                                                                    | 22                | -                 | -                 |

|         | P43                |                                                                                                    | 23                | -                 | -                 |

|         | P46                |                                                                                                    | 30                | 22                | 14                |

|         | P47                |                                                                                                    | 31                | 23                | 15                |

|         | P4C                |                                                                                                    | 24                | 16                | -                 |

|         | P4D                |                                                                                                    | 25                | 17                | -                 |

|         | P4E                |                                                                                                    | 26                | 18                | -                 |

| GPIO    | P50                | 通用 I/O 口 5                                                                                         | 1                 | 1                 | 2                 |

|         | P51                |                                                                                                    | 2                 | 2                 | 3                 |

|         | P52                |                                                                                                    | 3                 | 3                 | 4                 |

|         | P53                |                                                                                                    | 4                 | 4                 | -                 |

| GPIO    | P60                | 通用 I/O 口 6                                                                                         | 33                | 25                | 17                |

|         | P61                |                                                                                                    | 61                | 47                | -                 |

| GPIO    | P80                | 通用 I/O 口 8                                                                                         | 58                | 44                | 30                |

|         | P81                |                                                                                                    | 59                | 45                | 31                |

| GPIO    | PE2                | 通用 I/O 口 E                                                                                         | 18                | 14                | 9                 |

|         | PE3                |                                                                                                    | 19                | 15                | 10                |

| 多功能串口 0 | SIN0_0             | 多功能串口 ch.0 输入引脚                                                                                    | 55                | 41                | 28                |

|         | SIN0_1             |                                                                                                    | 44                | 32                | -                 |

|         | SOT0_0<br>(SDA0_0) | 多功能串口 ch.0 输出引脚。充当 UART/CSIO/LIN 引脚（运行模式 0 ~ 3）时，可用作 SOT0；充当 I <sup>2</sup> C 引脚（运行模式 4），可用作 SDA0。 | 53                | 40                | 27                |

|         | SOT0_1<br>(SDA0_1) |                                                                                                    | 45                | 33                | -                 |

|         | SCK0_0<br>(SCL0_0) |                                                                                                    | 46                | 34                | 22                |

| 引脚功能    | 引脚名称               | 功能说明                                                                                                          | 引脚号               |                   |                   |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|

|         |                    |                                                                                                               | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| 多功能串口 1 | SIN1_1             | 多功能串口 ch.1 输入引脚                                                                                               | 41                | 29                | 19                |

|         | SOT1_1<br>(SDA1_1) | 多功能串口 ch.1 的输出引脚。<br>充当 UART/CSIO/LIN 引脚 (运行模式 0 ~ 3) 时, 可用作 SOT1; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SDA1。 | 42                | 30                | 20                |

|         | SCK1_1<br>(SCL1_1) | 多功能串口 ch.1 的时钟 I/O 引脚。<br>充当 CSIO 引脚 (运行模式 2) 时, 可用作 SCK1; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SCL1。         | 43                | 31                | 21                |

|         | SCS10_1            | 多功能串口 ch.1 串行芯片选择 0 输入/输出引脚。                                                                                  | 44                | 32                | -                 |

|         | SCS11_1            | 多功能串口 ch.1 串行芯片选择 1 输出引脚。                                                                                     | 45                | 33                | -                 |

| 多功能串口 3 | SIN3_1             | 多功能串口 ch.3 输入引脚                                                                                               | 1                 | 1                 | 2                 |

|         | SOT3_1<br>(SDA3_1) | 多功能串口 ch.3 的输出引脚。<br>充当 UART/CSIO/LIN 引脚 (运行模式 0 ~ 3) 时, 可用作 SOT3; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SDA3。 | 2                 | 2                 | 3                 |

|         | SCK3_1<br>(SCL3_1) | 多功能串口 ch.3 的时钟 I/O 引脚。<br>充当 CSIO 引脚 (运行模式 2) 时, 可用作 SCK3; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SCL3。         | 3                 | 3                 | 4                 |

| 引脚功能    | 引脚名称               | 功能说明                                                                                                                                                                        | 引脚号               |                   |                   |

|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|

|         |                    |                                                                                                                                                                             | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| 多功能串口 4 | SIN4_1             | 多功能串口 ch.4 输入引脚                                                                                                                                                             | 38                | 27                | -                 |

|         | SOT4_1<br>(SDA4_1) | 多功能串口 ch.4 的输出引脚。<br>充当 UART/CSIO/LIN 引脚 (运行模式 0 ~ 3) 时, 可用作 SOT4; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SDA4。                                                               | 37                | 26                | -                 |

|         | SCK4_1<br>(SCL4_1) | 多功能串口 ch.4 的时钟 I/O 引脚。<br>充当 CSIO 引脚 (运行模式 2) 时, 可用作 SCK4; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SCL4。                                                                       | 36                | -                 | -                 |

|         | CTS4_1             | 多功能串口 ch4 CTS 输入引脚                                                                                                                                                          | 35                | -                 | -                 |

|         | RTS4_1             | 多功能串口 ch4 RTS 输出引脚                                                                                                                                                          | 34                | -                 | -                 |

| 多功能串口 6 | SIN6_1             | 多功能串口 ch.6 输入引脚                                                                                                                                                             | 8                 | 8                 | 7                 |

|         | SOT6_1<br>(SDA6_1) | 多功能串口 ch.6 的输出引脚。<br>充当 UART/CSIO/LIN 引脚 (运行模式 0 ~ 3) 时, 可用作 SOT6; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SDA6。<br>充当 I <sup>2</sup> S 引脚 (运行模式 2) 时, SOT6_1 引脚可用作 MI2SDO6_1。 | 7                 | 7                 | 6                 |

|         | SCK6_1<br>(SCL6_1) | 多功能串口 ch.6 的时钟 I/O 引脚。<br>充当 CSIO 引脚 (运行模式 2) 时, 可用作 SCK6; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SCL6。                                                                       | 6                 | 6                 | 5                 |

|         | SCS60_1            | 多功能串口 ch.6 串行芯片选择 0 输入/输出引脚。                                                                                                                                                | 5                 | 5                 | -                 |

|         | SCS61_1            | 多功能串口 ch.6 串行芯片选择 1 输出引脚。                                                                                                                                                   | 9                 | 9                 | -                 |

|         | SCS62_1            | 多功能串口 ch.6 串行芯片选择 2 输出引脚。                                                                                                                                                   | 10                | -                 | -                 |

| 多功能串口 7 | SIN7_1             | 多功能串口 ch.7 输入引脚                                                                                                                                                             | 26                | 18                | -                 |

|         | SOT7_1<br>(SDA7_1) | 多功能串口 ch.7 的输出引脚。<br>充当 UART/CSIO/LIN 引脚 (运行模式 0 ~ 3) 时, 可用作 SOT7; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SDA7。                                                               | 25                | 17                | -                 |

|         | SCK7_1<br>(SCL7_1) | 多功能串口 ch.7 的时钟 I/O 引脚。<br>充当 CSIO 引脚 (运行模式 2) 时, 可用作 SCK7; 充当 I <sup>2</sup> C 引脚 (运行模式 4), 可用作 SCL7。                                                                       | 24                | 16                | -                 |

| 引脚功能           | 引脚名称       | 功能说明                       | 引脚号               |                   |                   |

|----------------|------------|----------------------------|-------------------|-------------------|-------------------|

|                |            |                            | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| I2S(多功能串口)     | MI2SDI4_1  | I2S 串行数据输入引脚 (操作模式 2).     | 38                | -                 | -                 |

|                | MI2SDO4_1  | I2S 串行数据输出引脚(操作模式 2).      | 37                | -                 | -                 |

|                | MI2SCK4_1  | I2S 串行时钟输出引脚(操作模式 2).      | 36                | -                 | -                 |

|                | MI2SWS4_1  | I2S 字选择输出引脚 (操作模式 2).      | 35                | -                 | -                 |

|                | MI2SMCK4_1 | I2S 主机时钟输入/输出引脚 (操作模式 2).  | 34                | -                 | -                 |

|                | MI2SDI6_1  | I2S 串行数据输入引脚(操作模式 2).      | 8                 | 8                 | -                 |

|                | MI2SDO6_1  | I2S 串行数据输出引脚(操作模式 2).      | 7                 | 7                 | -                 |

|                | MI2SCK6_1  | I2S 串行时钟输出引脚(操作模式 2).      | 6                 | 6                 | -                 |

|                | MI2SWS6_1  | I2S 字选择输出引脚(操作模式 2).       | 5                 | 5                 | -                 |

|                | MI2SMCK6_1 | I2S 主机时钟输入/输出引脚(操作模式 2).   | 9                 | 9                 | -                 |

| 智能卡接口          | IC1_CIN_0  | 智能卡插入检测输出引脚                | 11                | -                 | -                 |

|                | IC1_CLK_0  | 智能卡串口时钟输出引脚                | 16                | -                 | -                 |

|                | IC1_DATA_0 | 智能卡串口数据输入/输出引脚             | 12                | -                 | -                 |

|                | IC1_RST_0  | 智能卡复位输出引脚                  | 13                | -                 | -                 |

|                | IC1_VCC_0  | 智能卡电源使能输出引脚                | 15                | -                 | -                 |

|                | IC1_VPEN_0 | 智能卡编程输出引脚                  | 14                | -                 | -                 |

| 实时时钟           | RTCCO_0    | 实时时钟的 0.5 秒脉冲输出引脚          | 64                | 48                | 1                 |

|                | RTCCO_1    |                            | 43                | 31                | 21                |

|                | RTCCO_2    |                            | 11                | 10                | -                 |

|                | SUBOUT_0   | 副时钟输出引脚                    | 64                | 48                | 1                 |

|                | SUBOUT_1   |                            | 43                | 31                | 21                |

|                | SUBOUT_2   |                            | 11                | 10                | -                 |

| HDMI-CEC//遥控接收 | CEC0_0     | HDMI-CEC/遥控接收 ch.0 输入/输出引脚 | 38                | 27                | -                 |

|                | CEC1_0     | HDMI-CEC/遥控接收 ch.1 输入/输出引脚 | 33                | 25                | 17                |

| 引脚功能   | 引脚名称       | 功能说明                                                     | 引脚号               |                   |                   |

|--------|------------|----------------------------------------------------------|-------------------|-------------------|-------------------|

|        |            |                                                          | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 |

| 低功耗模式  | WKUP0      | 深度待机模式唤醒信号输入引脚 0                                         | 64                | 48                | 1                 |

|        | WKUP1      | 深度待机模式唤醒信号输入引脚 1                                         | 41                | 29                | 19                |

|        | WKUP2      | 深度待机模式唤醒信号输入引脚 2                                         | 51                | 39                | 26                |

|        | WKUP3      | 深度待机模式唤醒信号输入引脚 3                                         | 56                | 42                | 29                |

|        | WKUP4      | 深度待机模式唤醒信号输入引脚 4                                         | 52                | -                 | -                 |

|        | WKUP5      | 深度待机模式唤醒信号输入引脚 5                                         | 54                | -                 | -                 |

|        | WKUP6      | 深度待机模式唤醒信号输入引脚 6                                         | 62                | -                 | -                 |

|        | WKUP7      | 深度待机模式唤醒信号输入引脚 7                                         | 63                | -                 | -                 |

| I2C 从机 | SI2CSCL6_1 | I2C 时钟引脚                                                 | 6                 | 6                 | 5                 |

|        | SI2CSDA6_1 | I2C 数据引脚                                                 | 7                 | 7                 | 6                 |

| 复位     | INITX      | 外部复位输入引脚。<br>INITX="L" 时, 复位有效。                          | 32                | 24                | 16                |

| 模式     | MD0        | 模式 0 引脚。<br>正常工作时, 须输入 MD0 = "L"。闪存串行编程时, 须输入 MD0 = "H"。 | 17                | 13                | 8                 |

|        | MD1        | 模式 1 引脚。<br>正常工作时, 不需要输入。<br>闪存串行编程时, 须输入 MD1 = "L"。     | 56                | 42                | 29                |

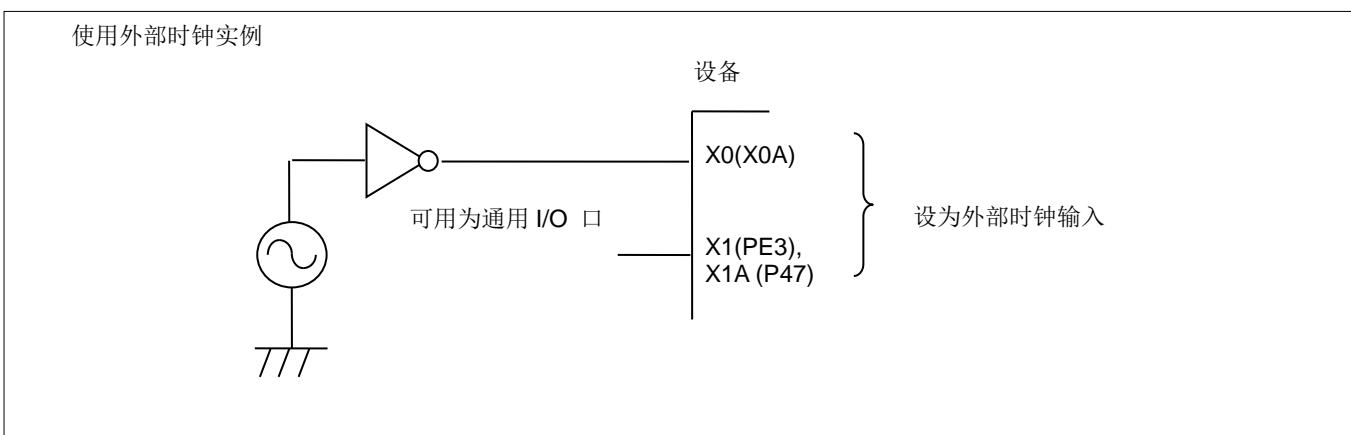

| 时钟     | X0         | 主时钟(振荡)输入引脚                                              | 18                | 14                | 9                 |

|        | X0A        | 副时钟(振荡)输入引脚                                              | 30                | 22                | 14                |

|        | X1         | 主时钟(振荡) I/O 引脚                                           | 19                | 15                | 10                |

|        | X1A        | 副时钟(振荡) I/O 引脚                                           | 31                | 23                | 15                |

|        | CROUT_1    | 高速内置 CR 振荡时钟输出口                                          | 64                | 48                | 1                 |

| 电源     | VCC        | 电源引脚                                                     | 27                | 19                | 11                |

|        | VCC        |                                                          | 48                | 36                | 24                |

|        | VCC        |                                                          | 57                | 43                | -                 |

| 地      | VSS        | 地引脚                                                      | 29                | 21                | 13                |

|        | VSS        |                                                          | 60                | 46                | 32                |

| 模拟基准电源 | AVRH *     | A/D 转换器的模拟基准高电压输入引脚                                      | 49                | 37                | -                 |

|        | AVRL       | A/D 转换器的模拟基准低电压输入引脚                                      | 50                | 38                | 25                |

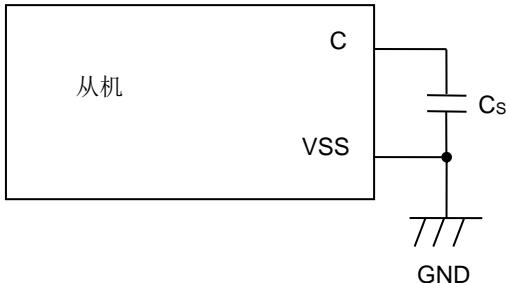

| C 引脚   | C          | 电源稳定电容引脚                                                 | 28                | 20                | 12                |

\*: 32 管脚封装产品的 AVRH 引脚在芯片内部与 VCC 引脚相连封装在一起。.

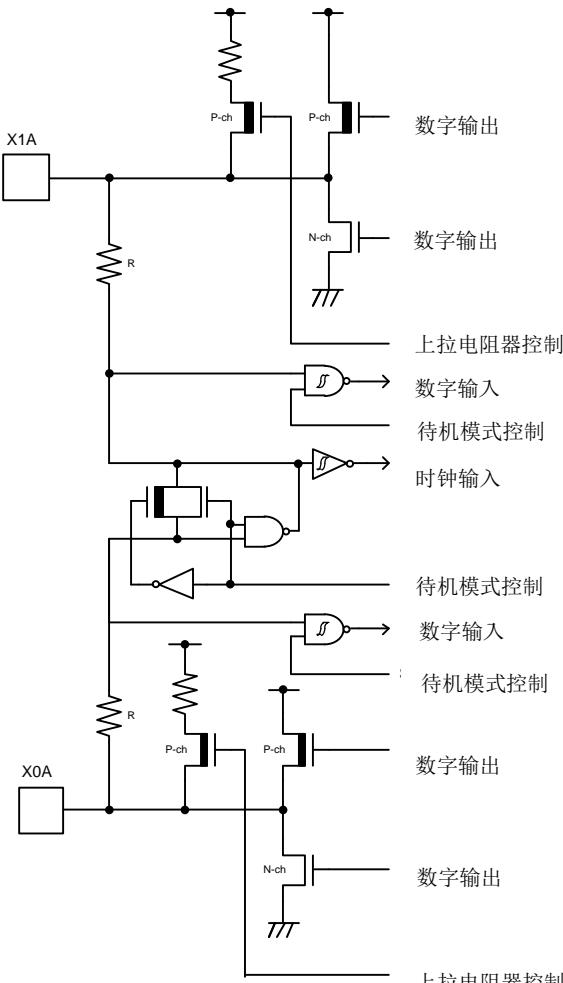

## 5. I/O 电路类型

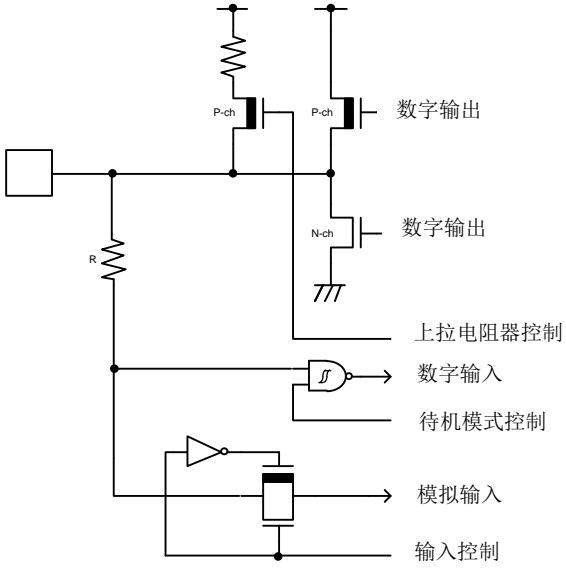

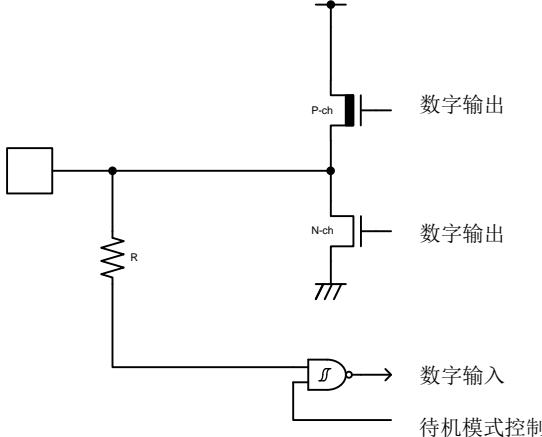

| Type | Circuit                                                                                                                               | Remarks                                                                                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | <p>数字输出<br/>上拉电阻器控制<br/>数字输入<br/>待机模式控制<br/>时钟输入<br/>待机模式控制<br/>数字输入<br/>待机模式控制<br/>数字输出<br/>数字输出<br/>上拉电阻器控制</p> <p>X1</p> <p>X0</p> | 可选择为主振荡时钟 / GPIO 功能<br>选择主振荡时钟功能时<br>· 振荡反馈电阻: 约 $1\text{ M}\Omega$<br>· 带待机模式控制<br>用作 GPIO 时<br>· CMOS 电平输出<br>· CMOS 电平迟滞输入<br>· 带上拉电阻控制<br>· 带待机模式控制<br>· 上拉电阻: 约 $33\text{ k}\Omega$<br>$I_{OH} = -4\text{mA}, I_{OL} = 4\text{mA}$ |

| B    | <p>Pull-up resistor</p> <p>数字输入</p>                                                                                                   | · CMOS 电平迟滞输入<br>· 上拉电阻: 约 $33\text{ k}\Omega$                                                                                                                                                                                          |

| Type | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Remarks |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| C    |  <p>数字输出<br/>数字输出<br/>上拉电阻器控制<br/>数字输入<br/>待机模式控制<br/>时钟输入<br/>待机模式控制<br/>数字输入<br/>待机模式控制<br/>数字输出<br/>数字输出<br/>上拉电阻器控制</p> <p>可选择为主振荡时钟/ GPIO 功能<br/>选择主振荡时钟功能时<br/>• 振荡反馈电阻: 约 <math>5\text{ M}\Omega</math><br/>• 带待机模式控制<br/><br/>用作 GPIO 时<br/>• CMOS 电平输出<br/>• CMOS 电平迟滞输入<br/>• 带上拉电阻控制<br/>• 带待机模式控制<br/>• 上拉电阻: 约 <math>33\text{ k}\Omega</math><br/><br/><math>I_{OH} = -4\text{ mA}</math>, <math>I_{OL} = 4\text{ mA}</math></p> |         |

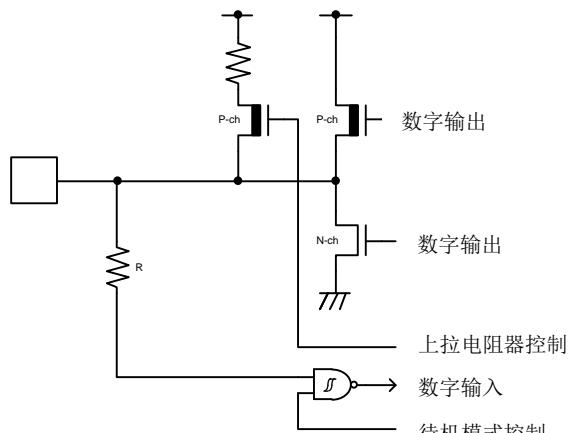

| Type | Circuit                                                                                                                                                    | Remarks                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

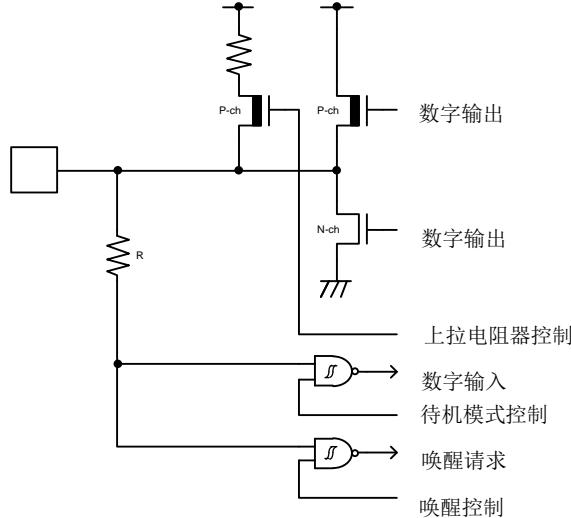

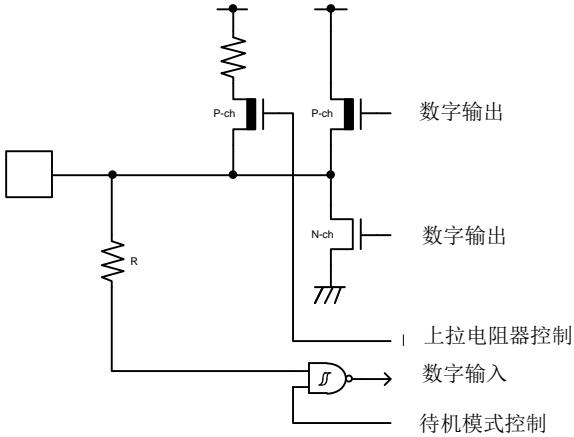

| D    |  <p>数字输出<br/>数字输出<br/>上拉电阻器控制<br/>数字输入<br/>待机模式控制</p>                     | <ul style="list-style-type: none"> <li>CMOS 电平输出</li> <li>CMOS 电平迟滞输入</li> <li>带上拉电阻控制</li> <li>带待机模式控制</li> <li>上拉电阻: 约 <math>33\text{ k}\Omega</math></li> <li>当用作 <math>\text{I}^2\text{C}</math> 引脚时, 数字输出 P-ch 晶体管始终处于关闭状态</li> </ul> <p><math>I_{OH} = -4\text{ mA}, I_{OL} = 4\text{ mA}</math></p> |

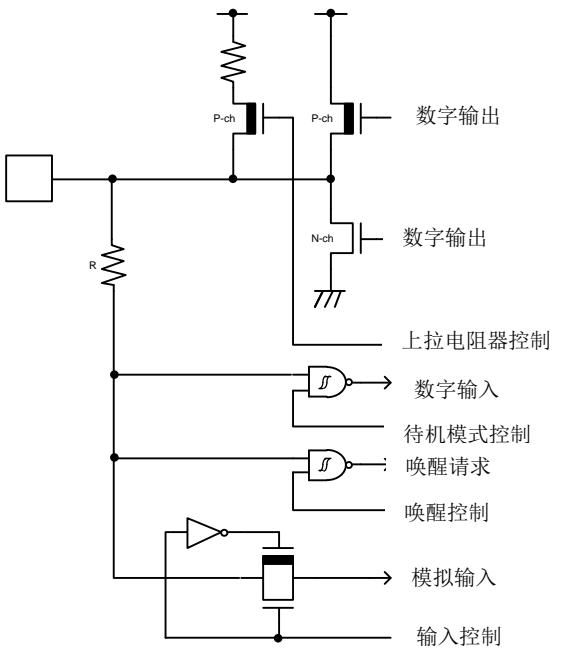

| E    |  <p>数字输出<br/>数字输出<br/>上拉电阻器控制<br/>数字输入<br/>待机模式控制<br/>唤醒请求<br/>唤醒控制</p> | <ul style="list-style-type: none"> <li>CMOS 电平输出</li> <li>CMOS 电平迟滞输入</li> <li>带上拉电阻控制</li> <li>带待机模式控制</li> <li>上拉电阻: 约 <math>33\text{ k}\Omega</math></li> <li>当用作 <math>\text{I}^2\text{C}</math> 引脚时, 数字输出 P-ch 晶体管始终处于关闭状态</li> </ul> <p><math>I_{OH} = -4\text{ mA}, I_{OL} = 4\text{ mA}</math></p> |

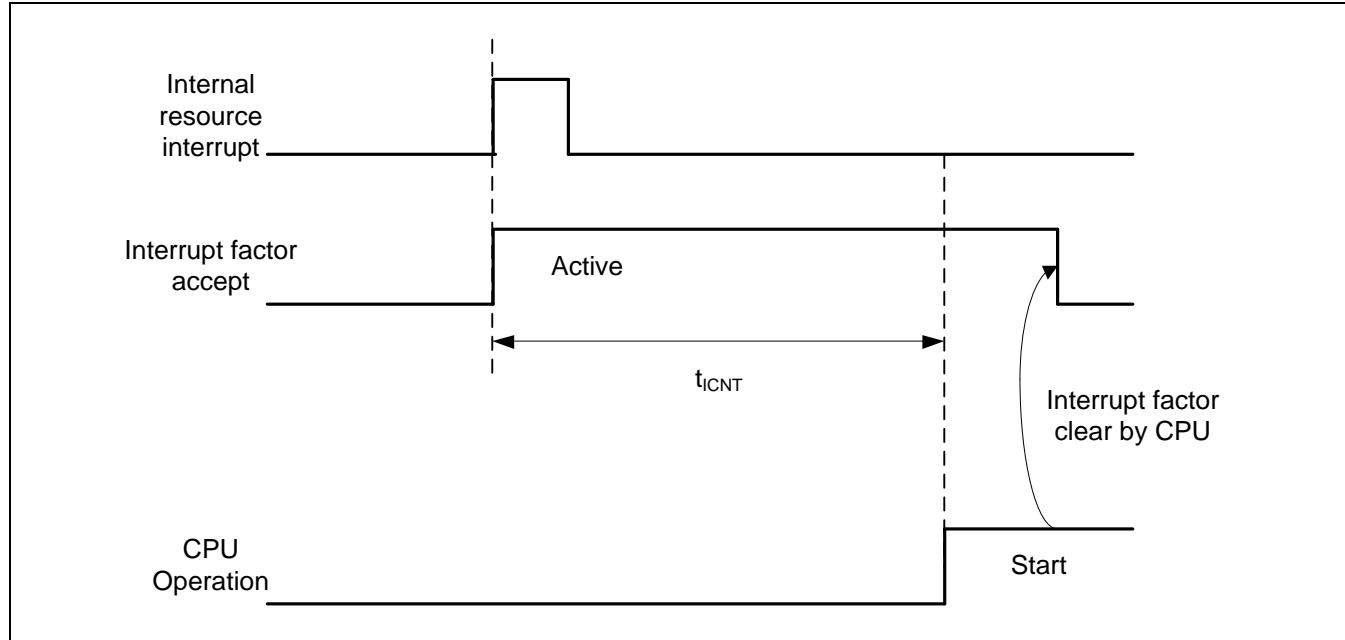

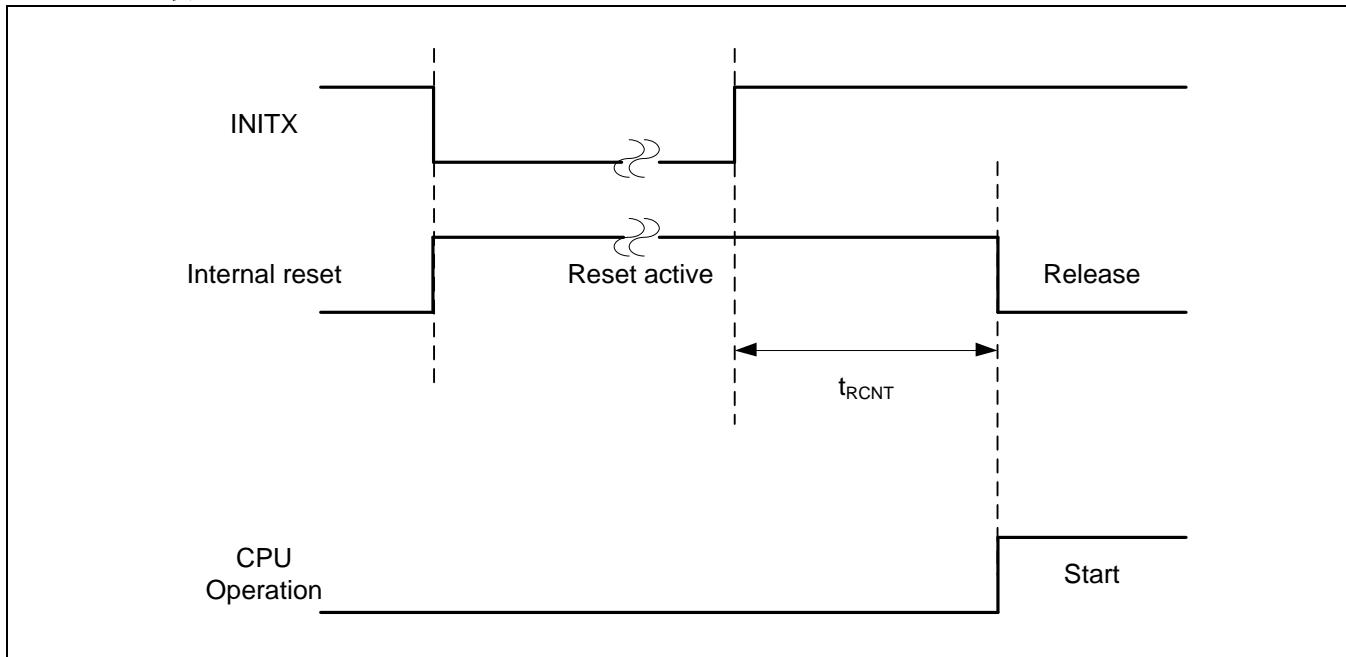

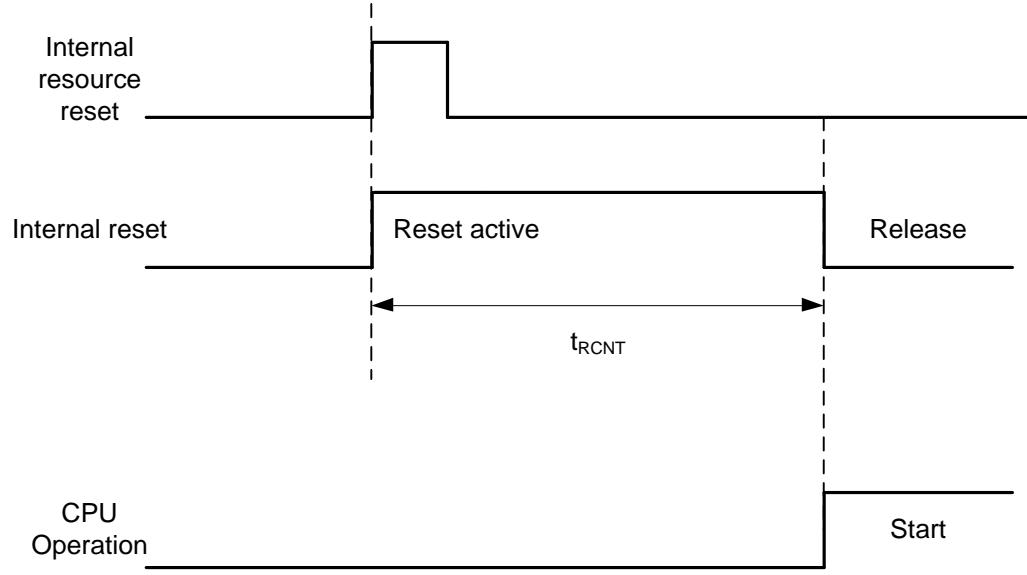

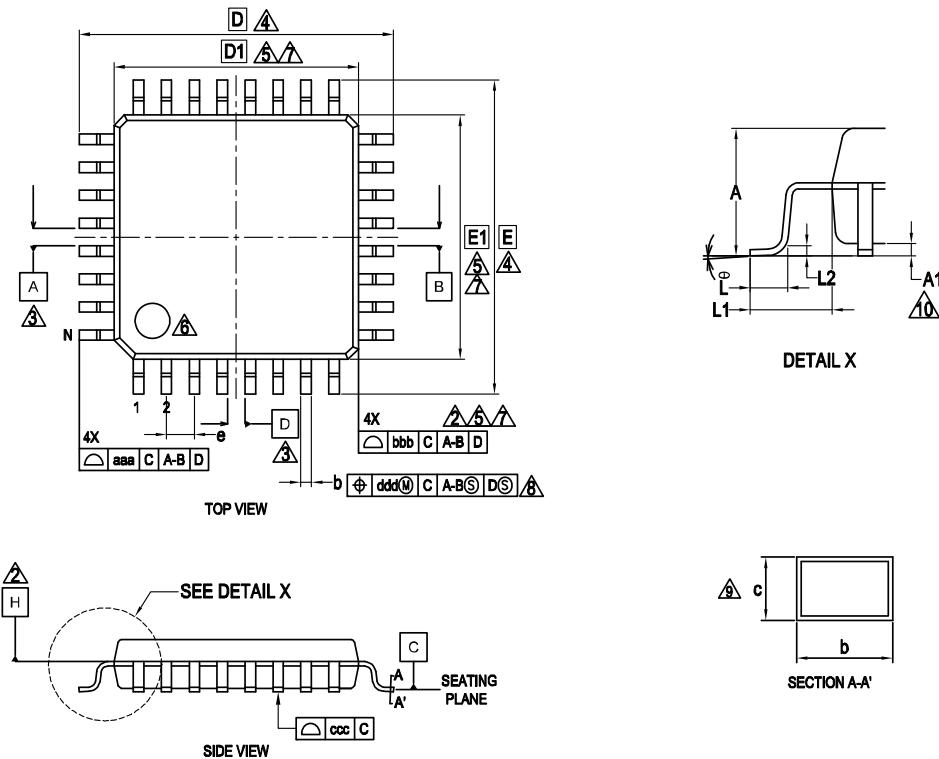

| Type | Circuit                                                                                                                                                            | Remarks                                                                                                                                                                                                                                                                                                                              |