## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

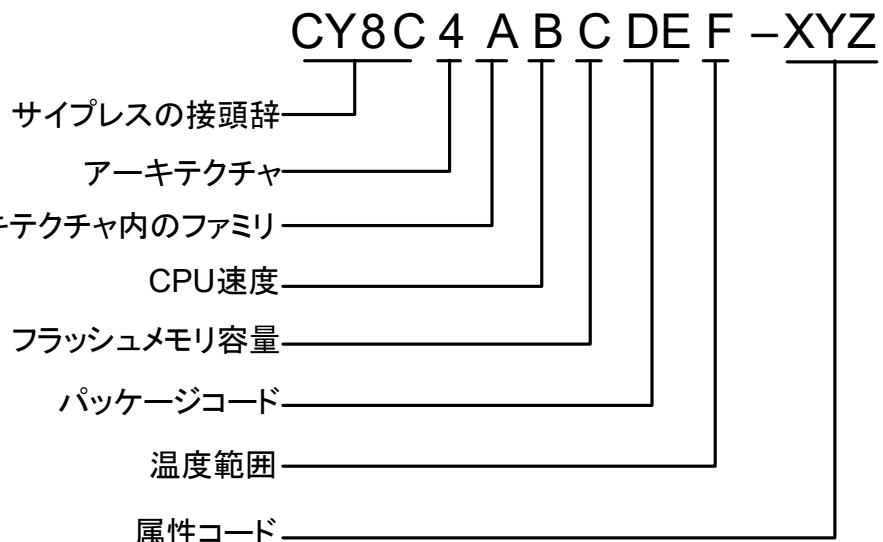

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

# プログラマブル システムオンチップ (PSoC)

## 概要説明

サイプレスの PSoC® アナログ コプロセッサは、複数のセンサーを備える組込みシステムの設計を簡素化するプログラマブル アナログ コプロセッサで、拡張性があり再設定可能なプラットフォーム アーキテクチャです。PSoC アナログ コプロセッサ デバイスは PSoC の柔軟なアナログ フロント エンド、プログラマブル アナログ フィルター、高分解能アナログ - デジタル変換器を効率が高く、強力な 32 ビット Arm® Cortex®-M0+ ベースの信号処理エンジンと組み合わせます。したがって、ホスト プロセッサがシリアル通信インターフェースを介して、集約、前処理、およびフォーマットされた複雑なセンサー データを簡単に取り出すことを可能にします。

## 特長

### プログラマブル アナログ ブロック

- 2 次のアナログ フィルター、12 ビット インクリメンタル デルタシグマ ADC、または 13 ビットの電圧 DAC について PSoC Creator を介してプログラム可能なスイッチ コンデンサ汎用アナログ ブロック (UAB)

- 12 ビット SAR ADC および 10 ビット シングルスロープ ADC を含む 2 個の専用アナログ - デジタル変換器 (ADC)

- カスタムのアナログ フロント エンド (AFE) を作成するための、4 個のオペアンプ、2 個の低消費電力コンバーティ、および 1 個の柔軟な 38 チャネルのアナログ マルチブレクサ

- 汎用または任意のピンでの静電容量センシング用途向けの 2 個の 7 ビット 電流 DAC (IDAC)

### CapSense® 容量センシング

- サイプレスの第 4 世代の CapSense シグマデルタ (CSD) はクラス最高の信号対ノイズ比 (SNR) および耐水性を提供

- サイプレスが提供するソフトウェア コンポーネントが静電容量センシングの設計を簡易化

- ハードウェア自動チューニング (SmartSense™)

### セグメント LCD ドライブ

- あらゆるピンでの LCD ドライブ (コモンまたはセグメント)

- ディープスリープ モードでの動作に対応、ピンごとに 4 ビット メモリ

### プログラマブルなデジタル ペリフェラル

- I2C、SPI または UART に実行時に設定可能な 3 個の独立したシリアル通信ブロック (SCB)

- 中央揃え、エッジ、および疑似乱数モードに対応する 8 個の 16 ビット タイマー / カウンター / パルス幅変調器 (TCPWM) ブロック

### 32 ビットの信号処理エンジン

- 最大 48MHz の Arm Cortex-M0+ CPU

- 読み出し加速装置を備えた最大 32KB のフラッシュ

- 最大 4KB の SRAM

- 8 チャネルのディスクリプタ ベースの DMA コントローラー

### 低消費電力動作

- 1.71V ~ 5.5V の動作

- ディープスリープ モードで動作可能なアナログと 2.5µA のデジタルシステム電流

- 時計用水晶発振器 (WCO)

### プログラマブルな GPIO ピン

- 駆動モード、駆動能力、およびスルーレートがプログラマブルで、アナログ、デジタル、CapSense、または LCD 機能に使用可能な最大 38 本の GPIO ピン

- 入力および出力信号上で PIN レベルのブール演算を実装するための 8 本のスマート I/O を含む

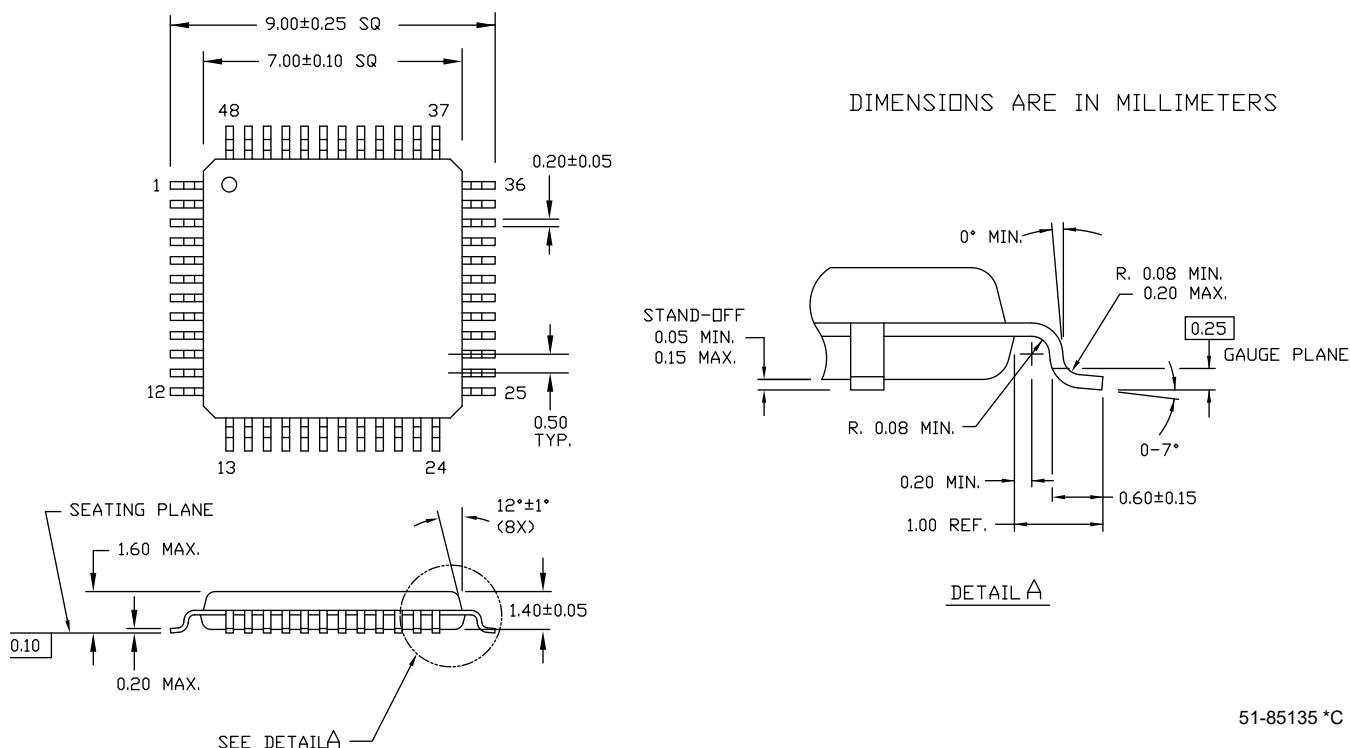

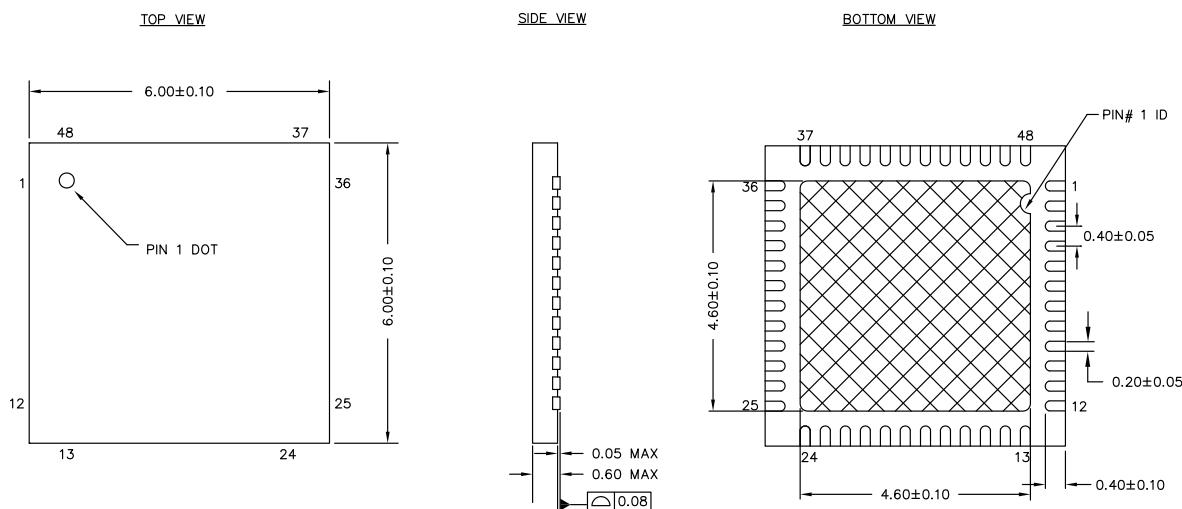

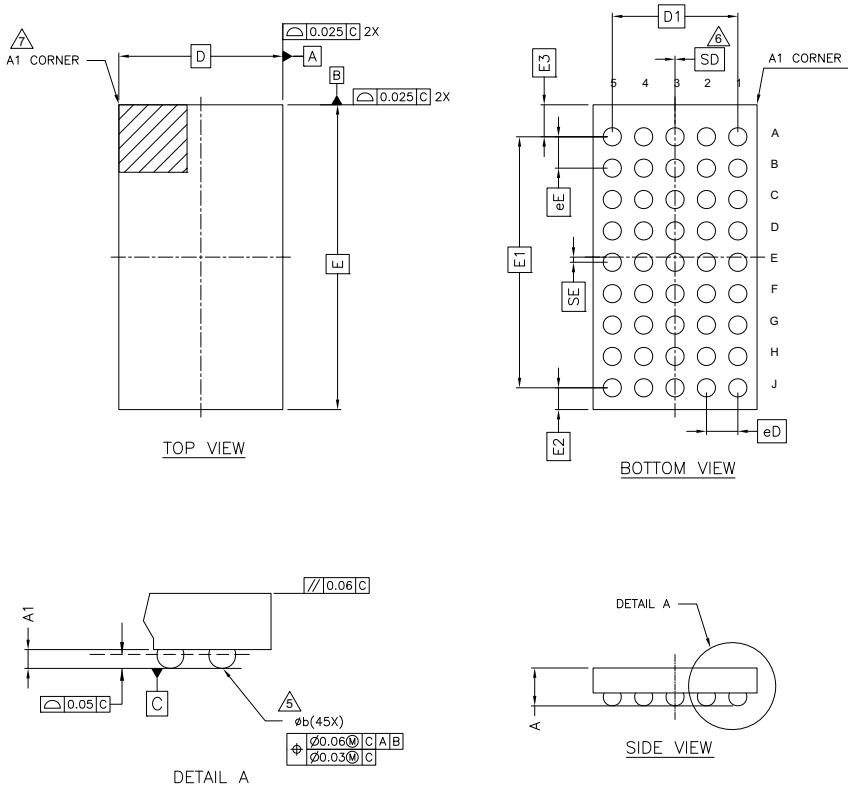

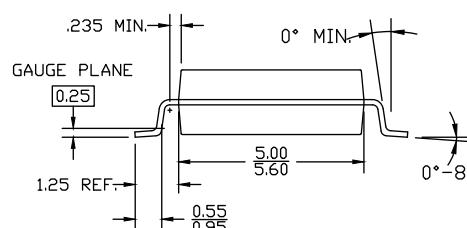

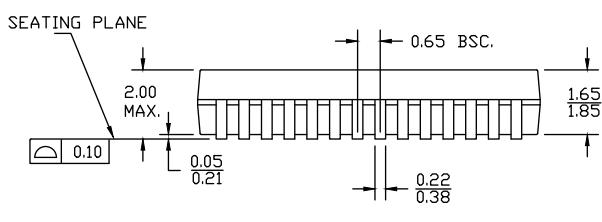

- 48 ピン QFN、48 ピン TQFP、28 ピン SSOP、および 45 ポール WLCSP パッケージ

### PSoC Creator 設計環境

- 統合設計環境 (IDE) が回路図キャプチャ設計の入力とビルド (アナログとデジタル信号の自動配線も備えている) および Arm-SWD デバッガを備えたファームウェアの同時設計を提供

- 完全に設計した組込み初期化、校正、補正アルゴリズムを持っている GUI ベースのコンフィギュレーション可能な PSoC コンポーネント

- すべての固定機能およびプログラミング可能なペリフェラル向けのアプリケーション プログラミング インターフェース (API)

### 業界標準のツールとの互換性

- 回路図キャプチャ後、ファームウェア開発を Arm ベースの業界標準の開発ツールで行うことが可能

## 詳細情報

サイプレスは、[www.cypress.com](http://www.cypress.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC デバイスを選択し、デバイスをデザインに迅速で効果的に統合する手助けをします。リソースの包括的なリストについては、知識ベース記事「[KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP](#)」を参照してください。以下は PSoC 4 のリソースの簡略化した一覧です。

- 概要 : PSoC ポートフォリオ、PSoC ロードマップ

- 製品セレクタ : [PSoC 1](#)、[PSoC 3](#)、[PSoC 4](#)、[PSoC 5LP](#)、また PSoC Creator 内にデバイス選択ツールがあります。

- アプリケーションノート : サイプレスは、基本レベルから上級レベルまでの様々なトピックに触れる大量の PSoC アプリケーションノートを提供しています。以下は、PSoC 4 入門用の推奨アプリケーションノートです。

- [AN79953](#): PSoC 4 入門

- [AN88619](#): PSoC 4 Hardware Design Considerations

- [AN86439](#): PSoC 4 および PSoC アナログ コプロセッサ – GPIO ピンの使用

- [AN57821](#): PSoC 3, PSoC 4 および PSoC 5LP のアナログ / デジタル混在回路基板レイアウトの注意事項

- [AN81623](#): PSoC 3, PSoC 4, PSoC 5LP デジタル設計のベストプラクティスについて

- [AN73854](#): Introduction To Bootloaders

- [AN89610](#): Arm Cortex Code Optimization

- [AN85951](#): PSoC® 4 および PSoC アナログ コプロセッサ CapSense® デザインガイド

- テクニカル リファレンスマニュアル (TRM) は 2 種類あります。

- [アーキテクチャ TRM](#): 各 PSoC 4 機能ブロックを詳細に説明します。

- [レジスタ TRM](#): 各 PSoC 4 レジスタを詳細に説明します。

- 開発キット

- [CY8CKIT-048](#) 5 つのオンボードセンサー、オンボードデバッガー、および Arduino シールド互換フォームファクターを備えた、PSoC アナログ コプロセッサー用のフル機能の開発ボード。

- MiniProg3 デバイスは、フラッシュのプログラミングとデバッグ用のインターフェースを提供します。

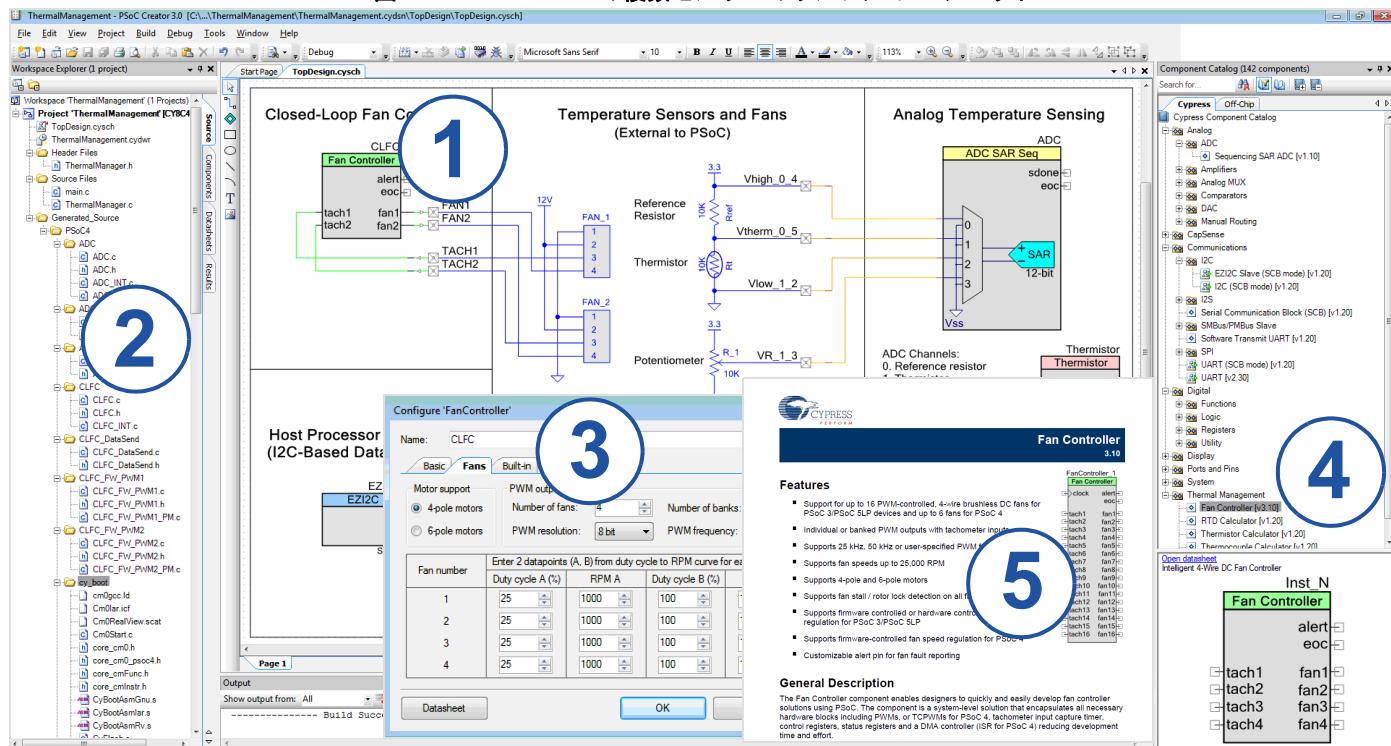

## PSoC Creator

PSoC Creator は無償の Windows ベースの統合設計環境 (IDE) です。このキットにより、PSoC 3、PSoC 4 および PSoC 5LP ベースのシステムのハードウェアとファームウェアの同時設計が可能です。100 以上の事前検証済みで量産使用が可能な PSoC Component をサポートしているクラシックで使い慣れた回路図キャプチャを使ってデザインを作成します。コンポーネントデータシートを参照してください。PSoC Creator により、以下のことことが可能です：

1. メイン デザイン ワークスペースで、コンポーネント アイコンをドラッグ アンド ドロップしてハードウェア システム デザインをビルト

2. PSoC Creator IDE の C コンパイラを使用してアプリケーションのファームウェアと PSoC ハードウェアを相互設計

3. コンフィギュレーション ツールを使ってコンポーネントを設定

4. 100 以上のコンポーネントのライブラリを利用

5. コンポーネント データシートを参照

**図 1. PSoC Creator の複数センサーのサンプル プロジェクト**

## 目次

|                            |           |

|----------------------------|-----------|

| <b>機能の詳細</b>               | <b>6</b>  |

| CPU およびメモリ サブシステム          | 6         |

| システム リソース                  | 6         |

| アナログ ブロック                  | 8         |

| 固定機能デジタル                   | 9         |

| GPIO                       | 9         |

| 特殊機能ペリフェラル                 | 9         |

| WLCSP ブートローダー              | 10        |

| <b>ピン配置</b>                | <b>11</b> |

| ピンの代替機能                    | 13        |

| <b>電源</b>                  | <b>15</b> |

| モード 1: 1.8V ~ 5.5V の外部電源   | 15        |

| <b>開発サポート</b>              | <b>16</b> |

| 資料                         | 16        |

| オンライン                      | 16        |

| ツール                        | 16        |

| <b>電気的仕様</b>               | <b>17</b> |

| 絶対最大定格                     | 17        |

| デバイス レベルの仕様                | 17        |

| <b>アナログ ペリフェラル</b>         | <b>21</b> |

| デジタル ペリフェラル                | 32        |

| メモリ                        | 34        |

| システム リソース                  | 34        |

| <b>注文情報</b>                | <b>37</b> |

| <b>パッケージ</b>               | <b>39</b> |

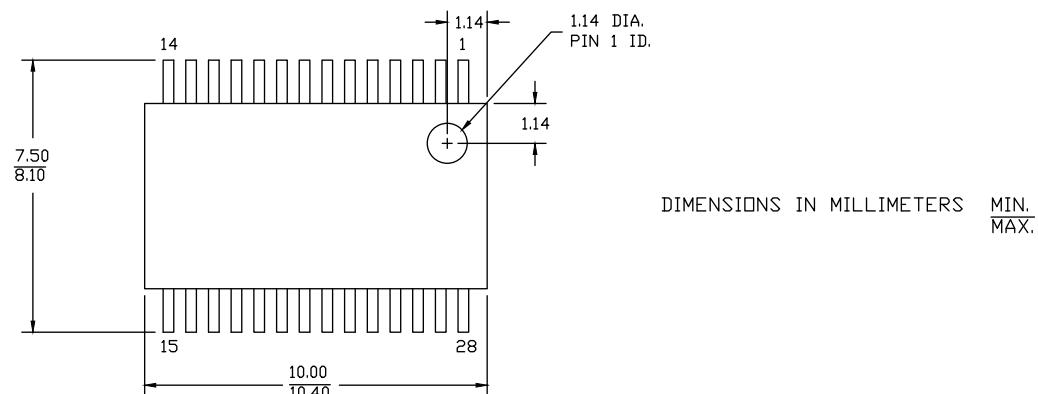

| 外形図                        | 40        |

| <b>略語</b>                  | <b>43</b> |

| <b>本書の表記法</b>              | <b>46</b> |

| 測定単位                       | 46        |

| <b>改訂履歴</b>                | <b>47</b> |

| <b>セールス、ソリューションおよび法律情報</b> | <b>48</b> |

| ワールドワイド販売と設計サポート           | 48        |

| 製品                         | 48        |

| PSoC® ソリューション              | 48        |

| サイプレス開発者コミュニティ             | 48        |

| テクニカル サポート                 | 48        |

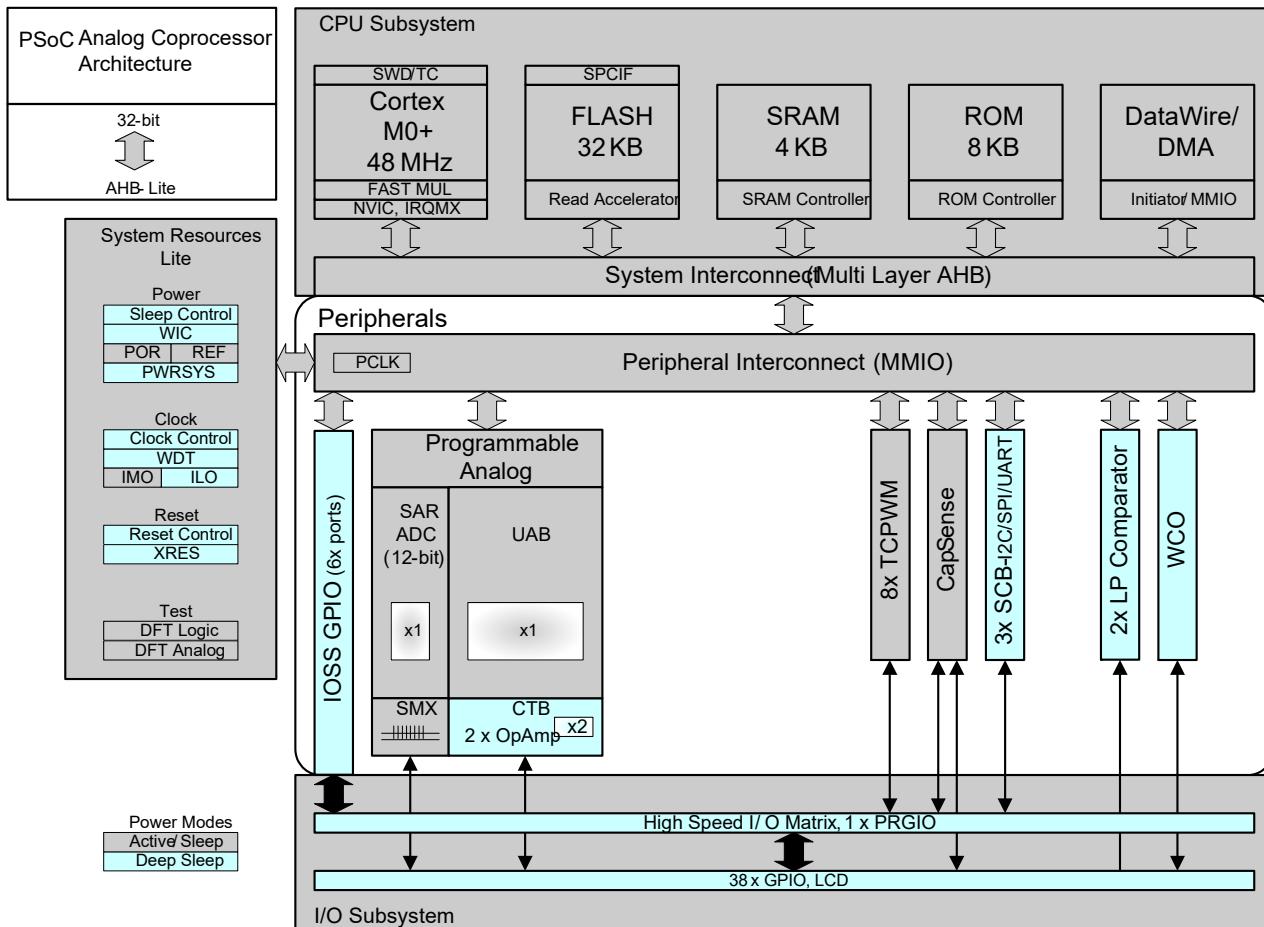

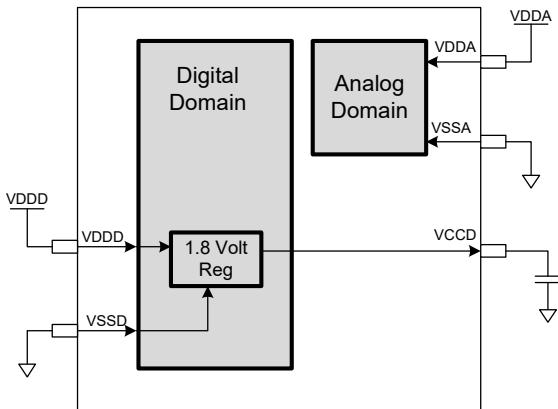

図 2. ブロック図

PSoC アナログ コプロセッサデバイスは、ハードウェアとファームウェアの両方についてプログラミング、テスト、デバッグ、およびトレースの幅広いサポートを備えています。

Arm シリアル ワイヤー デバッグ (SWD) インターフェースは、デバイスのプログラミングとデバッグ機能をすべてサポートします。

完全なデバッグ オン チップ (DoC) の機能により、標準の量産デバイスを使用した最終システムで完全なデバイスのデバッグ処理が可能になります。専用のインターフェースやデバッグ ポッド、シミュレータ、エミュレータは不要です。デバッグに完全に対応するために必要なものは、通常のプログラミングに使う接続だけです。

PSoC Creator IDE は、PSoC アナログ コプロセッサデバイス用の完全に統合されたプログラミングおよびデバッグのサポートを提供します。SWD インターフェースは、業界標準のサードパーティ製ツールと完全互換です。PSoC アナログ コプロセッサファミリは、マルチチップ アプリケーション ソリューションまたはマイクロコントローラーでは不可能なセキュリティ レベルを提供します。このファミリは次の利点を持っています。

- デバッグ機能を無効化が可能

- 堅牢なフラッシュ保護

- お客様独自の機能がプログラマブル オンチップ ブロックで実装可能

デバッグ回路はデフォルトで有効にされており、ファームウェアでのみ無効にできます。有効にされていない場合、再度有効にする唯一の方法は、デバイス全体を消去しフラッシュ保護もクリアしてデバッグ処理を有効にする新しいファームウェアでデバイスをプログラムし直すことです。従って、ファームウェアにより制御されるデバッグ処理は、ファームウェアを消去しなければオーバーライドできないため、セキュリティを向上させます。

さらに、悪意を持ってデバイスを再プログラムすることに起因するフィッシング攻撃、またはフラッシュ プログラミング シーケンスを開始して割り込むことでセキュリティ システムを突破しようという意図が懸念されるアプリケーションに対して、すべてのデバイス インターフェースを恒久的に無効にすることが可能です。デバイスの最高レベルのセキュリティが有効になっている場合、すべてのプログラミング、デバッグおよびテスト インターフェースは無効にされます。そのため、デバイスセキュリティ機能が有効にされたPSoC アナログ コプロセッサは、不具合解析のために返すことはできません。これはカスタマが PSoC アナログ コプロセッサでできるトレードオフです。

## 機能の詳細

### CPU およびメモリ サブシステム

#### CPU

PSoC アナログ コプロセッサの Cortex-M0+ CPU は、広範なクロック ゲーティングに対応し低消費電力動作用に最適化された 32 ビット MCU サブシステムの一部です。ほとんどの命令の長さは 16 ビットであり、CPU が Thumb-2 命令セットのサブセットを実行します。これは、8 つの割込み入力を備えたネスト型ベクタ割込みコントローラー (NVIC) ブロックとウェイクアップ割込みコントローラー (WIC) を含みます。WIC はディープスリープ モードからプロセッサを復帰させることができます。これにより、チップがディープスリープ モードにある時にメイン プロセッサへの電源を切れます。

また、CPU は JTAG の 2 線式のデバッグ インターフェースであるシリアル ワイヤ デバッグ (SWD) インターフェースも含んでいます。PSoC アナログ コプロセッサに使用するデバッグ コンフィギュレーションには、4 個のブレークポイント（アドレス）コンパレータと 2 個のウォッチポイント（データ）コンパレータがあります。

#### DMA/ データワイヤー

DMA エンジンはユーザー プログラム可能なディスクリプタ チェーンを介して、メモリ マップ内のどこにでも、独立したデータ転送を行えます。データワイヤー機能はメモリ内にある位置から別の位置への 1 つの要素転送を行うために使用されます。選択可能なトリガ ソースの範囲を備えた 8 つの DMA チャネルがあります。

#### フラッシュ

PSoC アナログ コプロセッサ デバイスは、フラッシュ ブロックからの平均アクセス時間を改善するために CPU に緊密に接続された、フラッシュ アクセラレータ付きのフラッシュ モジュールを持っています。低消費電力のフラッシュ ブロックは 48MHz で 2 ウェイト ステート (WS) アクセス時間を達成するように設計されます。フラッシュ アクセラレータはシングル サイクル SRAM のアクセス性能の平均 85% を達成します。

#### SRAM

48MHz で実行可能なゼロ ウェイトステート（待ち状態なし）のアクセスを備えた 4KB SRAM が提供されます。

#### SROM

ブートおよびコンフィギュレーション ルーチンを内蔵する 8KB SROM を提供されます。

#### システム リソース

##### 電源システム

電力システムは、[15 ページの電源](#) の節で詳しく説明されます。これは、電圧レベルがそれぞれのモードの要求に応じることを保証し、電圧レベルが適切な機能の要求に応じるまでモードへの移行を遅延させる（例えば、パワーオン リセット (POR) 時）か、またはリセットを生成します（例えば、電圧低下検出時）。PSoC アナログ コプロセッサは、1.8V $\pm$ 5%（外部安定化）または 1.8V ~ 5.5V（内部安定化）の外部電源電圧で動作し、3 つの異なる電力モードがあり、これらのモード間の遷移が電源システムにより管理されます。PSoC アナログ コプロセッサはアクティブ モードおよびスリープとディープ スリープ低消費電力 モードに対応します。

アクティブ モードでは、すべてのサブシステムが動作できます。スリープ モードでは、CPU サブシステム（CPU、フラッシュ、SRAM）はクロックがゲート オフになりますが、すべてのペリフェラルと割込みはウェイクアップ イベントの時に瞬時ウェイクアップ 機能によりアクティブになります。ディープスリープ モードでは、高速クロックおよび対応する回路がオフにされます。このモードからの復帰は 35 $\mu$ s かかります。オペアンプはこのディープスリープ モードでは依然として動作し続けます。

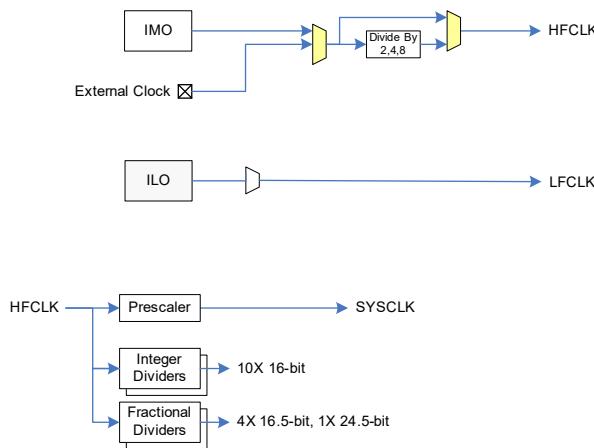

## クロックシステム

PSoC アナログ コプロセッサ クロック システムは、クロックを必要とするすべてのサブシステムにクロックを供給し、グリッチなしに異なるクロックソース間で切り替えることを担当します。また、クロック システムはメタステーブル状態が発生しないように保証します。

PSoC アナログ コプロセッサのクロック システムは、内蔵主発振器 (IMO)、内蔵低周波数発振回路 (ILO)、32kHz の時計用水晶発振器 (WCO) および外部クロック用の予備ピンから構成されます。クロック分周器は微調整の単位でペリフェラル用のクロックを生成するために提供されます。また、分数分周器は、UART 向けのより高いデータ転送速度でクロックの供給を可能にするためにも提供されます。

**図 3. PSoC アナログ コプロセッサの MCU クロッキング アーキテクチャ**

HFCLK 信号はアナログとデジタル ペリフェラル用に同期クロックを生成するために分周できます。PSoC アナログ コプロセッサは 15 個のクロック分周器を備えております。16 ビット分周器は細かい周波数値(大きな分周比用の 24 ビット分周器が 1 個ある)を柔軟に生成することが可能で、PSoC Creator で完全にサポートされます。

## IMO クロック ソース

IMO は PSoC アナログ コプロセッサの内部クロック供給の主なソースです。これはテスト段階中に、指定された精度を得るためにトリムされます。IMO のデフォルト周波数は 24MHz で、4MHz のステップで 24MHz から 48MHz までの範囲で調整できます。サイプレスが提供する校正設定では、IMO の許容誤差は ±2% です。

## ILO クロック ソース

ILO は、超低消費電力の 40kHz 発振器であり、ディープスリープ モードでウォッチドッグ タイマー (WDT) とペリフェラルの動作用にクロックを生成するために主に使用されます。ILO 制御のカウンターは、精度を改善するために IMO で校正できます。サイプレスは、校正を実行するソフトウェア コンポーネントを提供します。

## 時計用水晶発振器 (WCO)

PSoC アナログ コプロセッサ クロック サブシステムは、ウォッチドッグタイミング アプリケーションに採用できる低周波数(32kHz ウォッチ水晶) 発振回路を内蔵します。

## ウォッチドッグ タイマー

ウォッチドッグ タイマーは、ILO をクロック ソースとして動作するクロック ブロックに実装されます。これにより、ウォッチドッグがディープスリープ モードでも動作でき、設定されたタイムアウトが発生する前にウォッチドッグが処理されなかった場合にリセットが生成されます。ウォッチドッグ リセットは、ファームウェアが読み出し可能なりセット原因 (Reset Cause) レジスタに記録されます。

## リセット

PSoC アナログ コプロセッサは、ソフトウェア リセットを含む様々なソースからリセットできます。リセット イベントは非同期であり、チップを既存の状態に復帰することを保証します。リセットの原因是、ソフトウェアがリセットを原因を判断できるようにする、リセット中にスティッキーであるレジスタに記録されます。XRES ピンは、そのアクティブ レベルを LOW にアサートすることで外部リセット用に予約されます。XRES ピンには、常に有効になっている内部プルアップ抵抗があります。

## 電圧リファレンス

PSoC アナログ コプロセッサ リファレンス システムは、内部で必要なリファレンスをすべて生成します。1.2V 電圧リファレンスはコンパレータ用に提供されます。IDAC は ±5% 電圧リファレンスを参照します。

## アナログ ブロック

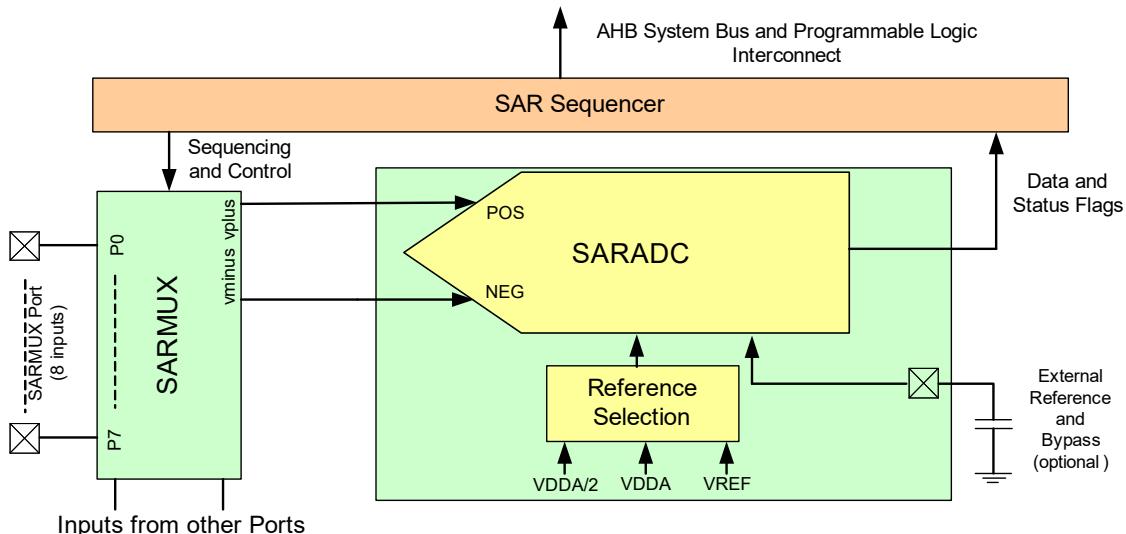

### 12 ビット SAR ADC

12 ビットの 1Msps SAR ADC は 18MHz の最大クロック レートで動作でき、12 ビット変換を行うためにその周波数で少なくとも 18 クロックを必要とします。

サンプル ホールド (S/H) のアバーチャがプログラム可能であるため、SAR 入力を駆動するアンプの整定時間を規定する利得帯域幅要件を必要に応じて緩和できます。内部リファレンス アンプ用として外部バイパス (固定したピン位置を介して) を提供できます。

SAR は 8 入力シーケンサを介して固定したピンに接続されます。シーケンサは、スイッチング オーバーヘッドの必要なく選択されたチャネルを自律的に巡回します (シーケンサ スキャン) (つまり、合計サンプリング帯域幅は、単一のチャネルか複数

のチャネルであるかにかかわらず 1Msps です)。シーケンサの切り替えは、ステート マシンまたはファームウェア駆動の切り替えにより行われます。シーケンサの 1 つの機能は、CPU 割込みサービスの要件を軽減するための各チャネルのバッファリングです。信号を様々なソース インピーダンスと周波数に適合させるために、チャネルごとに異なるサンプリング時間をプログラムできます。また、デジタル化された値がプログラムされた範囲を超えた場合、レンジレジスタの一対 (低と高レンジ値) による信号範囲の指定は、対応する範囲外の割込みで実施されます。これにより、シーケンサ スキャンが完了し、CPU が値を読み出してソフトウェア内で範囲外の値の有無を確認するのを待たず、範囲外の値を早く検出できます。

SAR は高速クロック (最大 18MHz) を必要とするため、ディープスリープ モードに対応していません。SAR の動作範囲は 1.71V ~ 5.5V です。

**図 4. SAR ADC**

### 4 個のオペアンプ (連続時間ブロック、CTB)

PSoC アナログ コプロセッサは、コンパレータ モードのある 4 個のオペアンプを持つことにより、外部コンポーネントの必要がなく、ほとんどの一般的なアナログ機能がオンチップで実行できます。PGA、電圧バッファ、フィルター、トランシスインピーダンス アンプ、とその他の機能は実現できる (いくつかの場合、外部受動コンポーネントで実現) ため、電力、コストおよび容量を削減できます。内蔵オペアンプは、外部バッファリングを必要とせずに ADC のサンプル ホールド回路を駆動するように十分な帯域幅に対応するように設計されています。

### 汎用アナログ ブロック (UAB) 離散時間ブロック

UAB ブロックはスイッチ コンデンサ フィードバックおよび 2 つのオペアンプの構造に接続されている入力ネットワークを含みます。構造の両半分は独立して使用できます。したがって、バイクアップ フィルタの構造はシングルエンド モードで両半分を独立して使用することで行えます。一般的なアナログ機能はスイッチ コンデンサ回路およびオペアンプで実装できます。例えば、UAB で実装可能な機能は DAC、多極フィルタ (カスケード接続可能なブロック)、デルタ シグマ変調器、ミキサー、積分器、PGA、およびサイプレス提供のソフトウェアコンポー

メントをサイプレス PSoC Creator で活用したその他の便利な機能です。

### 低消費電力コンパレータ (LPC)

PSoC アナログ コプロセッサは、ディープスリープ モードで動作できる低消費電力コンパレータの一対を内蔵しています。これにより、低電力モード中に外部電圧レベルを監視する能力を維持しながらアナログシステム ブロックを無効にできます。コンパレータ出力は、システム ウェイクアップ 回路がコンパレータの切り替えイベントによりアクティブになる非同期電力モードで動作している場合を除き、普通は準安定状態を避けるために同期化されています。LPC の出力はピンに接続できます。

### 電流 DAC

PSoC アナログ コプロセッサは、チップ上のすべてのピンを駆動できる 2 個の IDAC を備えています。これらの IDAC はプログラミング可能な電流範囲を持っています。

### アナログ多重化バス

PSoC アナログ コプロセッサは、中央から独立してチップの周辺を回る 2 個のバスを備えています。これらのバス (amux バス

ファームウェアでプログラム可能なアナログ スイッチに接続されています。

#### 温度センサー

製造中に校正され、標準  $\pm 1\%$  (最大  $\pm 5\%$ ) の偏差を達成する精度のオンチップ温度センサーを内蔵しています。SAR ADC は温度の測定に使用されます。

#### 固定機能デジタル

##### タイマー／カウンター／PWM (TCPWM) ブロック

TCPWM ブロックは、ユーザーがプログラム可能な周期長の 16 ビット カウンターからなります。キャプチャレジスタは、I/O イベントなどのイベントの時にカウント値を記録します。周期レジスタは、カウンターのカウントが周期レジスタのカウントに等しくなる時にカウントを停止し、または自動的にリロードします。比較レジスタは、PWM デューティ比出力として使用される比較信号を生成します。ブロックは、真出力と相補出力（それら間のオフセットがプログラミング可能）も提供しており、これらをデッドバンドがプログラミング可能な相補 PWM 出力として使用できます。また、出力を事前に決定された状態に移行させるキル (Kill) 入力もあります。例えば、モーター駆動システムでは、過電流状態が示され、FET を駆動している PWM をソフトウェア介入なしに直ちに止める必要がある時、キル入力が使用されます。PSoC アナログ コプロセッサは 8 個の TCPWM ブロックがあります。

##### シリアル通信ブロック (SCB)

PSoC アナログ コプロセッサは 3 個のシリアル通信ブロックが備え、必要に応じて SPI、I<sup>2</sup>C または UART 機能にプログラムできます。

**I<sup>2</sup>C モード**：ハードウェア I<sup>2</sup>C ブロックは、完全なマルチマスターとスレーブインターフェース（マルチマスターのアビトリレーションが可能）を実装します。このブロックは、最大 400kbps (高速モード) で動作可能で、CPU 用の割込みオーバヘッドとレイテンシを削減するためのフレキシブルなバッファリング オプションがあります。また、PSoC アナログ コプロセッサのメモリでメールボックスアドレス範囲を作り、メモリアレイへの読み出しと書き込みの I<sup>2</sup>C 通信を効果的に削減する EZI2C にも対応します。また、ブロックは送受信用に深さ 8 の FIFO にも対応します。これは、CPU がデータを読み出さなければならぬ規定の時間を増加することで、時間どおりに CPU が読み出すデータを取得しないことに起因したクロックストレッチの必要性を大幅に低減できます。

I<sup>2</sup>C ペリフェラルは、NXP I<sup>2</sup>C バス仕様とユーザー マニュアル (UM10204) で定義されたとおりに、I<sup>2</sup>C 標準モードとファストモード デバイスと互換性があります。I<sup>2</sup>C バス I/O は、オープンドレイン モードにある GPIO を使用して実装されます。

PSoC アナログ コプロセッサは、以下の点では I<sup>2</sup>C 仕様に完全に準拠しません。

- GPIO セルは過電圧耐性がないため、ホットスワップや、I<sup>2</sup>C システムの残りの部分から独立して電源を投入できません。

**UART モード**：これは 1Mbps で動作するフル機能の UART です。基本 UART プロトコルから少し発展した車載向けシングルワイヤ インターフェース (LIN)、赤外線インターフェース (IrDA)、SmartCard (ISO7816) プロトコルに対応します。また、共通の受信と送信ラインを介して接続したペリフェラルのアドレス指定を可能にする 9 ビット マルチプロセッサ モードに対

応します。パリティ エラー、ブレーク検出、フレーム エラーなどの一般的な UART 機能がサポートされています。深さ 8 の FIFO は、非常に大きい CPU サービス レイテンシを許容できます。

**SPI モード**：SPI モードは Motorola SPI、TI SSP (SPI コードックの同期化用の開始パルスを追加)、National Microwire (半二重の SPI) に完全に対応します。SPI ブロックは FIFO を使用できます。

#### GPIO

PSoC アナログ コプロセッサは最大 38 本の GPIO を持っています。GPIO ブロックは以下のものを実装します。

- 8 つの駆動モード

- アナログ入力モード (入力と出力バッファが無効)

- 入力のみ

- 強フルアップ、強フルダウン

- 強フルアップ、弱フルダウン

- オープンドレイン、強フルダウン

- オープンドレイン、強フルアップ

- 強フルアップ、強フルダウン

- 弱フルアップ、弱フルダウン

- 入力閾値選択 (CMOS あるいは LVTTL)

- 駆動強度モード以外に、入力と出力バッファのイネーブル／ディゼーブルの個別制御

- EMIを改善するためにdV/dt関連のノイズ制御用の選択可能なスルーレート

ピンは、8 ビット幅のポートと呼ばれる論理エンティティに構成されます (ポート 2 とポート 3 はより少ないビット幅です)。電源投入とリセットの時、入力への電流を止めない、および／または電源投入時に過電流を発生させないために、ブロックは無効状態に移行されます。高速 I/O マトリックスとして知られている多重化ネットワークは、1 本の I/O ピンに接続可能な複数の信号間に多重化するのに使用されます。

データ出力とピンステート レジスタは、それぞれピン上で駆動される値とそれらのピンのステートを格納します。

各 I/O ピンは有効になった場合に割込みを生成でき、各 I/O ポートはそれに対応する割込み要求 (IRQ) と割込みサービス ルーチン (ISR) ベクタがあります (PSoC アナログ コプロセッサでは、ベクタ数は 4 です)。スマート I/O ブロックはスイッチと LUT の構造体であり、ブール関数を GPIO ポートのピンに送信されている信号で実行することを可能にします。スマート I/O ブロックは、論理演算をチップの入力ピン、および出力として出る信号で実行できます。

#### 特殊機能ペリフェラル

##### CapSense

CapSense は、(アナログスイッチに接続された) アナログ マルチプレクサ バスを介してどのピンにも接続できる CSD ブロックにより、PSoC アナログ コプロセッサでサポートされています。従って、CapSense 機能はソフトウェアによる制御で、システム内のいかなる使用可能なピンかピン グループにも提供できます。ユーザーの便宜のために、PSoC Creator コンポーネントは CapSense ブロックに提供されています。

シールド電圧は、耐水機能を提供するために他のマルチプレクサ バス上で駆動できます。耐水性は、シールド電極を検知電極と同位相で駆動して、シールド容量が検知された入力を減衰させることで、備えられています。近接検知も実装できます。

CapSense ブロックは、2 個の IDAC を備えています。これらは、CapSense を使用しない (両方の IDAC とも使用可能) 場合、または CapSense が耐水性を備えずに使用する (どちらか一方の IDAC が使用可能) 場合、一般用途に使用できます。

た、CapSense ブロックは、CapSense 機能と併用できる 10 ビットのスロープ ADC 機能も提供します。

CapSense ブロックは高性能で、低ノイズのプログラマブルなブロック（つまり、感度と柔軟性を向上させるためにリファレンス電圧と電流源の範囲をプログラム可能）です。さらに、外部リファレンス電圧も利用できます。VDAA およびグランドのセンシングを代替し、電源関連のノイズをゼロにする全波 CSD モードがあります。

**WLCSPパッケージブートローダー**

WLCSP パッケージには、フラッシュにインストールされた I<sup>2</sup>C ブートローダーが付属しています。ブートローダーは、PSoC Creator ブートローダープロジェクトファイルと互換性があります。

## ピン配置

下表に、PSoC アナログ コプロセッサの 48 QFN、48 TQFP、45 WLCSP、および 28 SSOP パッケージ用のピン一覧を示します。すべてのポートピンは GPIO に対応します。

| 48 ピン QFN |           | 48 ピン TQFP |           | 28 ピン SSOP |           | 45 ポール CSP |           |

|-----------|-----------|------------|-----------|------------|-----------|------------|-----------|

| ピン        | 名称        | ピン         | 名称        | ピン         | 名称        | ピン         | 名称        |

| 28        | P0.0      | 28         | P0.0      | 21         | P0.0      | D3         | P0.0      |

| 29        | P0.1      | 29         | P0.1      | 22         | P0.1      | E2         | P0.1      |

| 30        | P0.2      | 30         | P0.2      | 23         | P0.2      | D2         | P0.2      |

| 31        | P0.3      | 31         | P0.3      |            |           | D1         | P0.3      |

| 32        | P0.4      | 32         | P0.4      |            |           | E1         | P0.4      |

| 33        | P0.5      | 33         | P0.5      |            |           | C3         | P0.5      |

| 34        | P0.6      | 34         | P0.6      |            |           | C2         | P0.6      |

| 35        | P0.7      | 35         | P0.7      |            |           | B2         | P0.7      |

| 36        | XRES      | 36         | XRES      | 24         | XRES      | B3         | XRES      |

| 37        | P4.0      | 37         | P4.0      |            |           | A1         | P4.0      |

| 38        | P4.1      | 38         | P4.1      |            |           | B1         | P4.1      |

| 39        | P5.0      | 39         | P5.0      | 25         | P5.0      | B4         | P5.0      |

| 40        | P5.1      | 40         | P5.1      |            |           | C1         | P5.1      |

| 41        | P5.2      | 41         | P5.2      | 26         | P5.2      | A2         | P5.2      |

| 42        | P5.3      | 42         | P5.3      | 27         | P5.3      | A3         | P5.3      |

| 43        | VDDA      | 43         | VDDA      | 28         | VDDA      | J2         | VDDA      |

| 44        | VSSA      | 44         | VSSA      |            |           | J3         | VSSA      |

| 45        | VCCD      | 45         | VCCD      | 1          | VCCD      | A4         | VCCD      |

|           |           |            |           |            |           | B5         | VDDD      |

| 46        | VSSD      | 46         | VSSD      | 2          | VSSD      | A5         | VSSD      |

| 47        | VDDD      | 47         | VDDD      | 3          | VDDD      |            |           |

| 48        | P1.0      | 48         | P1.0      | 4          | P1.0      | C5         | P1.0      |

| 1         | P1.1      | 1          | P1.1      | 5          | P1.1      | C4         | P1.1      |

| 2         | P1.2      | 2          | P1.2      | 6          | P1.2      | D5         | P1.2      |

| 3         | P1.3      | 3          | P1.3      | 7          | P1.3      | D4         | P1.3      |

| 4         | P1.4      | 4          | P1.4      |            |           | E3         | P1.4      |

| 5         | P1.5      | 5          | P1.5      |            |           | E4         | P1.5      |

| 6         | P1.6      | 6          | P1.6      |            |           |            |           |

| 7         | P1.7      | 7          | P1.7      |            |           | F3         | P1.7      |

| 8         | VDDA      | 8          | VDDA      | 8          | VDDA      | E5         | VDDA      |

| 9         | VSSA      | 9          | VSSA      | 9          | VSSA      | F5         | VSSA      |

| 10        | P2.0      | 10         | P2.0      | 10         | P2.0      | G3         | P2.0      |

| 11        | P2.1      | 11         | P2.1      | 11         | P2.1      | F4         | P2.1      |

| 12        | P2.2      | 12         | P2.2      | 12         | P2.2      | G4         | P2.2      |

| 13        | P2.3      | 13         | P2.3      | 13         | P2.3      | G5         | P2.3      |

| 14        | P2.4      | 14         | P2.4      |            |           | H5         | P2.4      |

| 15        | P2.5      | 15         | P2.5      |            |           | J4         | P2.5      |

| 16        | P2.6      | 16         | P2.6      |            |           | H4         | P2.6      |

| 17        | P2.7/VREF | 17         | P2.7/VREF | 14         | P2.7/VREF | J5         | P2.7/VREF |

| 48 ピン QFN |      | 48 ピン TQFP |      | 28 ピン SSOP |      | 45 ポール CSP |      |

|-----------|------|------------|------|------------|------|------------|------|

| ピン        | 名称   | ピン         | 名称   | ピン         | 名称   | ピン         | 名称   |

| 18        | VSSA | 18         | VSSA |            |      | J3         | VSSA |

| 19        | VDDA | 19         | VDDA | 15         | VDDA | J2         | VDDA |

| 20        | P3.0 | 20         | P3.0 |            |      | H2         | P3.0 |

| 21        | P3.1 | 21         | P3.1 | 16         | P3.1 | F2         | P3.1 |

| 22        | P3.2 | 22         | P3.2 | 17         | P3.2 | J1         | P3.2 |

| 23        | P3.3 | 23         | P3.3 | 18         | P3.3 | H3         | P3.3 |

| 24        | P3.4 | 24         | P3.4 |            |      | F1         | P3.4 |

| 25        | P3.5 | 25         | P3.5 |            |      | G2         | P3.5 |

| 26        | P3.6 | 26         | P3.6 | 19         | P3.6 | G1         | P3.6 |

| 27        | P3.7 | 27         | P3.7 | 20         | P3.7 | H1         | P3.7 |

電源ピンの説明は以下のとおりです。

VDDD: デジタル セクション用の電源。

VDDA: アナログ セクション用の電源。

VSS: グランド ピン。

VCCD: 安定化デジタル電源 (1.8V ± 5%)

48 ピン パッケージは 38 本の I/O ピンがあります。45 CSP および 28 SSOP パッケージはそれぞれ 37 本および 20 本の I/O ピンがあります。

## ピンの代替機能

それぞれのポート ピンは多機能の 1 つに割り当てられます。例えば、アナログ I/O、デジタル ペリフェラル機能、CapSense または LCD ピンなどになり得ます。ピンの割り当てを下表に示します。

| ポート/ピン | アナログ                               | スマート IO          | アクティブ                 |                   |                          |                         | ディープスリープ             |                      |

|--------|------------------------------------|------------------|-----------------------|-------------------|--------------------------|-------------------------|----------------------|----------------------|

|        |                                    |                  | ACT #0                | ACT #1            | ACT #2                   | ACT #3                  | DS #0                | DS #1                |

| P0.0   | lpcomp.in_p[0]                     | SmartIO[0].io[0] | tcpwm.line[4]:1       |                   | pass.dsi_sar_data[0]:0   | tcpwm.tr_in[0]          | cpuss.swd_data:0     | scb[0].spi_select1:0 |

| P0.1   | lpcomp.in_n[0]                     | SmartIO[0].io[1] | tcpwm.line_compl[4]:1 |                   | pass.dsi_sar_data[1]:0   | tcpwm.tr_in[1]          | cpuss.swd_clk:0      | scb[0].spi_select2:0 |

| P0.2   |                                    | SmartIO[0].io[2] | tcpwm.line[5]:1       |                   | srss.ext_clk:0           | pass.tr_gen_trig_in[0]  | pass.dsi_ctb_cmp0[0] | scb[0].spi_select3:0 |

| P0.3   |                                    | SmartIO[0].io[3] | tcpwm.line_compl[5]:1 |                   | pass.dsi_sar_data[2]:1   | pass.tr_gen_trig_in[1]  | pass.dsi_ctb_cmp1[0] |                      |

| P0.4   |                                    | SmartIO[0].io[4] | tcpwm.line[6]:1       | scb[1].uart_rx:0  | pass.dsi_sar_data[3]:1   | pass.tr_uab_trig0_out:0 | scb[1].i2c_scl:0     | scb[1].spi_mosi:0    |

| P0.5   |                                    | SmartIO[0].io[5] | tcpwm.line_compl[6]:1 | scb[1].uart_tx:0  | pass.dsi_sar_data[4]:1   | pass.tr_uab_trig1_out:0 | scb[1].i2c_sda:0     | scb[1].spi_miso:0    |

| P0.6   |                                    | SmartIO[0].io[6] |                       | scb[1].uart_cts:0 | pass.dsi_sar_data[5]:1   | pass.dsi_uab_cmp0       | lpcomp.comp[0]:0     | scb[1].spi_clk:0     |

| P0.7   |                                    | SmartIO[0].io[7] |                       | scb[1].uart_rts:0 | pass.dsi_sar_data[6]:1   | pass.dsi_uab_cmp1       | lpcomp.comp[1]:0     | scb[1].spi_select0:0 |

| P4.0   | wco.wco_in                         |                  | tcpwm.line[0]:2       | scb[2].uart_rx:1  | pass.dsi_sar_data[7]:1   | tcpwm.tr_in[5]          | scb[2].i2c_scl:1     | scb[2].spi_mosi:1    |

| P4.1   | wco.wco_out                        |                  | tcpwm.line_compl[0]:2 | scb[2].uart_tx:1  | pass.dsi_sar_data[8]:1   | tcpwm.tr_in[6]          | scb[2].i2c_sda:1     | scb[2].spi_miso:1    |

| P5.0   | csd.csheidpads                     |                  | tcpwm.line[7]:1       | scb[0].uart_rx:1  | pass.dsi_sar_data_valid  |                         | scb[0].i2c_scl:1     | scb[0].spi_mosi:1    |

| P5.1   | csd.vref_ext                       |                  | tcpwm.line_compl[7]:1 | scb[0].uart_tx:1  | pass.dsi_sar_sample_done |                         | scb[0].i2c_sda:1     | scb[0].spi_miso:1    |

| P5.2   | csd.dsi_cmod                       |                  | tcpwm.line[6]:2       | scb[0].uart_cts:1 | pass.tr_sar_out          |                         | pass.dsi_ctb_cmp0[1] | scb[0].spi_clk:1     |

| P5.3   | csd.dsi_csh_tank                   |                  | tcpwm.line_compl[6]:2 | scb[0].uart_rts:1 | pass.dsi_sar_data[9]:0   |                         | pass.dsi_ctb_cmp1[1] | scb[0].spi_select0:1 |

| P1.0   | ctb_pads[8]<br>lpcomp.in_p[1]      |                  | tcpwm.line[0]:1       | scb[1].uart_rx:1  | pass.dsi_sar_data[10]:0  | pass.tr_decm_intr0      | scb[1].i2c_scl:1     | scb[1].spi_mosi:1    |

| P1.1   | ctb_pads[9]<br>lpcomp.in_n[1]      |                  | tcpwm.line_compl[0]:1 | scb[1].uart_tx:1  | pass.dsi_sar_data[11]:0  | pass.tr_decm_intr1      | scb[1].i2c_sda:1     | scb[1].spi_miso:1    |

| P1.2   | ctb_pads[10]<br>ctb_oa0_out_10x[1] |                  | tcpwm.line[1]:1       | scb[1].uart_cts:1 | pass.dsi_sar_data[2]:0   |                         |                      | scb[1].spi_clk:1     |

| P1.3   | ctb_pads[11]<br>ctb_oa1_out_10x[1] |                  | tcpwm.line_compl[1]:1 | scb[1].uart_rts:1 | pass.dsi_sar_data[3]:0   |                         |                      | scb[1].spi_select0:1 |

| P1.4   | ctb_pads[12]                       |                  | tcpwm.line[2]:1       |                   |                          |                         |                      | scb[1].spi_select1:0 |

| P1.5   | ctb_pads[13]                       |                  | tcpwm.line_compl[2]:1 |                   |                          |                         |                      | scb[1].spi_select2:0 |

| P1.6   | ctb_pads[14]                       |                  | tcpwm.line[3]:1       |                   |                          |                         |                      | scb[1].spi_select3:0 |

| P1.7   | ctb_pads[15]                       |                  | tcpwm.line_compl[3]:1 |                   |                          |                         |                      |                      |

| P2.0   | ctb_pads[0]                        |                  | tcpwm.line[4]:0       | scb[2].uart_rx:0  | pass.dsi_sar_data[4]:0   |                         | scb[2].i2c_scl:0     | scb[2].spi_mosi:0    |

| ポート／ピン | アナログ                                | スマート IO | アクティブ                 |                   |                         |                | ディープスリープ         |                      |

|--------|-------------------------------------|---------|-----------------------|-------------------|-------------------------|----------------|------------------|----------------------|

|        |                                     |         | ACT #0                | ACT #1            | ACT #2                  | ACT #3         | DS #0            | DS #1                |

| P2.1   | ctb_pads[1]                         |         | tcpwm.line_compl[4]:0 | scb[2].uart_tx:0  | pass.dsi_sar_data[5]:0  |                | scb[2].i2c_sda:0 | scb[2].spi_miso:0    |

| P2.2   | ctb_pads[2]<br>ctb_oa0_out_10x[0]   |         | tcpwm.line[5]:0       | scb[2].uart_cts:0 | pass.dsi_sar_data[6]:0  |                |                  | scb[2].spi_clk:0     |

| P2.3   | ctb_pads[3]<br>ctb_oa1_out_10x[0]   |         | tcpwm.line_compl[5]:0 | scb[2].uart_rts:0 | pass.dsi_sar_data[7]:0  |                |                  | scb[2].spi_select0:0 |

| P2.4   | ctb_pads[4]<br>pass.lnfe_base_hv    |         | tcpwm.line[0]:0       |                   |                         |                |                  | scb[2].spi_select1:0 |

| P2.5   | ctb_pads[5]<br>pass.lnfe_emitter_hv |         | tcpwm.line_compl[0]:0 |                   |                         |                |                  | scb[2].spi_select2:0 |

| P2.6   | ctb_pads[6]                         |         | tcpwm.line[1]:0       |                   |                         |                |                  | scb[2].spi_select3:0 |

| P2.7   | ctb_pads[7]                         |         | tcpwm.line_compl[1]:0 |                   |                         |                |                  |                      |

|        | sar_ext_vref0<br>sar_ext_vref1      |         |                       |                   |                         |                |                  |                      |

| P3.0   | sarmux_pads[0]                      |         | tcpwm.line[2]:0       | scb[0].uart_rx:0  |                         |                | scb[0].i2c_scl:0 | scb[0].spi_mosi:0    |

| P3.1   | sarmux_pads[1]                      |         | tcpwm.line_compl[2]:0 | scb[0].uart_tx:0  | pass.dsi_sar_data[8]:0  |                | scb[0].i2c_sda:0 | scb[0].spi_miso:0    |

| P3.2   | sarmux_pads[2]                      |         | tcpwm.line[3]:0       | scb[0].uart_cts:0 |                         |                | cpuss.swd_data:1 | scb[0].spi_clk:0     |

| P3.3   | sarmux_pads[3]                      |         | tcpwm.line_compl[3]:0 | scb[0].uart_rts:0 |                         |                | cpuss.swd_clk:1  | scb[0].spi_select0:0 |

| P3.4   | sarmux_pads[4]                      |         | tcpwm.line[6]:0       |                   | pass.dsi_sar_data[10]:1 | tcpwm.tr_in[2] |                  | scb[0].spi_select1:1 |

| P3.5   | sarmux_pads[5]                      |         | tcpwm.line_compl[6]:0 |                   | pass.dsi_sar_data[11]:1 | tcpwm.tr_in[3] | csd.comp         | scb[0].spi_select2:1 |

| P3.6   | sarmux_pads[6]                      |         | tcpwm.line[7]:0       | scb[2].uart_rx:2  |                         | tcpwm.tr_in[4] | scb[2].i2c_scl:2 | scb[2].spi_mosi:2    |

| P3.7   | sarmux_pads[7]                      |         | tcpwm.line_compl[7]:0 | scb[2].uart_tx:2  |                         |                | scb[2].i2c_sda:2 | scb[2].spi_miso:2    |

## 電源

以下の電源システム図は、PSoC アナログ コプロセッサ用に実装された電源ピン セットを示します。システムは、アクティブモードで動作するデジタル回路用の 1 つのレギュレータがあります。アナログ レギュレータはありません。アナログ回路は V<sub>DAA</sub> 電源により動作します。

V<sub>DDD</sub> と V<sub>DAA</sub> は PCB 上で互いに短絡する必要があることに注意してください。

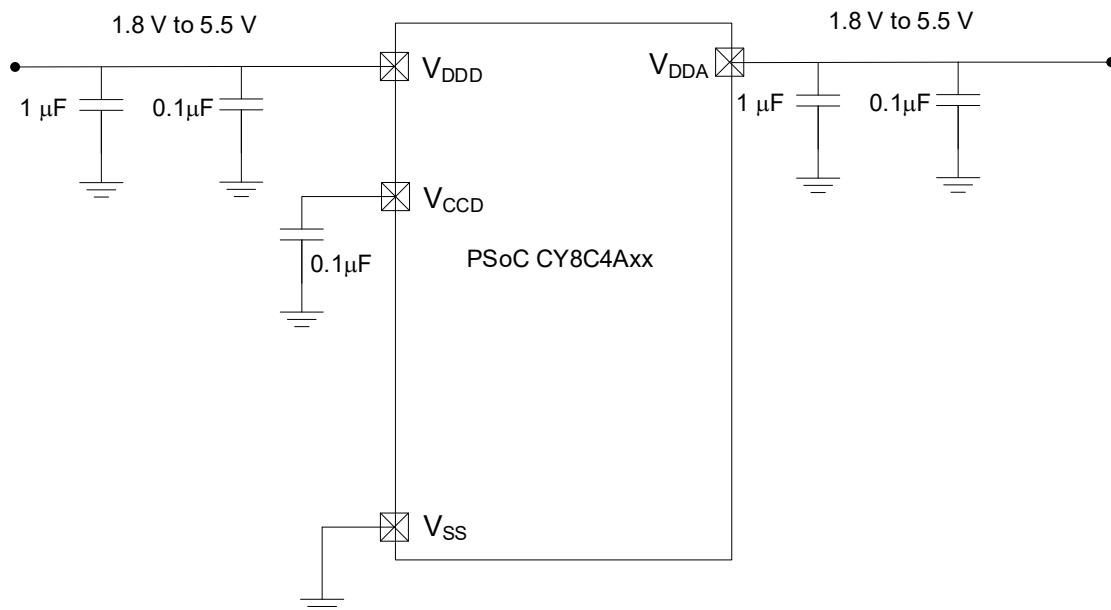

図 5. 電源接続

次の 2 つの異なる動作モードがあります。モード 1 では、供給電圧範囲は 1.8V ~ 5.5V (非安定化外部電源；内部レギュレータが動作可能) です。モード 2 では、供給電圧範囲は 1.8V ±5% (安定化外部電源；1.71 ~ 1.89、内部レギュレータがバイパスされる) です。

図 6. 内部レギュレータが有効でありながら 1.8V ~ 5.5V の外部電源

電源供給バイパス接続例

## 開発サポート

PSoC アナログ コプロセッサ ファミリには、ユーザーの開発プロセスを支援する豊富なドキュメント、開発ツールおよびオンライン リソースが用意されています。詳細については、[www.cypress.com/psoc4](http://www.cypress.com/psoc4) をご覧ください。

### 資料

ドキュメント一式が PSoC アナログ コプロセッサ ファミリをサポートし、ユーザーは、疑問点に対する答えを素早く見つけられます。重要な資料の幾つかは、本節にリストアップされています。

**ソフトウェア ユーザー ガイド** : PSoC Creator の操作方法の手引書。ソフトウェア ユーザー ガイドには、PSoC Creator によるビルド プロセスの詳細、PSoC Creator を用いたソース制御の使い方、その他が記載されています。

**コンポーネント データシート** : PSoC の柔軟性によって、デバイスが量産に入ってから長い期間の後でも新しいペリフェラル (コンポーネント) を作成できます。コンポーネント データシートには、ある特定のコンポーネントの選択および使用に必要な情報が、機能説明、API ドキュメント、サンプル コード、AC/DC 仕様を含んですべて記載されています。

**アプリケーション ノート** : PSoC アプリケーション ノートには、PSoC の特定のアプリケーションについて詳細な説明が記載されています。例として、ブラシレス DC モーターの制御やオンチップ フィルタリングがあります。アプリケーション ノートには、多くの場合、アプリケーション ノートのドキュメントに加えてサンプル プロジェクトが含まれています。

**テクニカル リファレンス マニュアル** : テクニカル リファレンス マニュアル (TRM) には、すべての PSoC レジスタの詳細な説明など、PSoC デバイスを使用する際に必要な技術的詳細がすべて記載されています。TRM は、[www.cypress.com/psoc4](http://www.cypress.com/psoc4) の「ドキュメント」セクションにあります。

### オンライン

印刷された資料のほかに、サイプレス PSoC フォーラムによって 24 時間 365 日、世界中の他の PSoC ユーザーや PSoC の専門家と連絡をとれます。

### ツール

業界標準のコア、プログラミングおよびデバッギング インターフェースを備えた PSoC アナログ コプロセッサ ファミリは、開発ツール エコシステムの一部です。革新的で使いやすい PSoC Creator IDE、サポートされるサード パーティのコンパイラ、プログラマ、デバッガ、および開発キットの最新情報については、サイプレスのウェブサイト [www.cypress.com/psoccreator](http://www.cypress.com/psoccreator) をご覧ください。

## 電気的仕様

### 絶対最大定格

表 1. 絶対最大定格<sup>[1]</sup>

| 仕様 ID# | パラメーター                      | 説明                                                                                               | Min  | Typ | Max                  | 単位 | 詳細／条件                                     |

|--------|-----------------------------|--------------------------------------------------------------------------------------------------|------|-----|----------------------|----|-------------------------------------------|

| SID1   | V <sub>DD_ABS</sub>         | V <sub>SS</sub> を基準としたデジタル電源またはアナログ電源                                                            | -0.5 | -   | 6                    | V  | V <sub>DDD</sub> 、V <sub>DDA</sub> 、絶対最大値 |

| SID2   | V <sub>CCD_ABS</sub>        | V <sub>SS</sub> を基準とした直接デジタル コア電圧入力                                                              | -0.5 | -   | 1.95                 |    | -                                         |

| SID3   | V <sub>GPIO_ABS</sub>       | GPIO 電圧                                                                                          | -0.5 | -   | V <sub>DD</sub> +0.5 |    | -                                         |

| SID4   | I <sub>GPIO_ABS</sub>       | GPIO 当たりの最大電流                                                                                    | -25  | -   | 25                   | mA | -                                         |

| SID5   | I <sub>GPIO_injection</sub> | GPIO 注入電流、V <sub>IH</sub> > V <sub>DDD</sub> の場合は Max、V <sub>IL</sub> < V <sub>SS</sub> の場合は Min | -0.5 | -   | 0.5                  |    | ピンごとの注入された電流                              |

| BID44  | ESD_HBM                     | 静電気放電 (人体モデル)                                                                                    | 2200 | -   | -                    | V  | -                                         |

| BID45  | ESD_CDM                     | 静電気放電 (デバイス帯電モデル)                                                                                | 500  | -   | -                    |    | -                                         |

| BID46  | LU                          | ラッチアップ時のピン電流                                                                                     | -140 | -   | 140                  | mA | -                                         |

### デバイス レベルの仕様

すべての仕様は、特に注記した場合を除いて、 $-40^{\circ}\text{C} \leq T_A \leq 85^{\circ}\text{C}$  および  $T_J \leq 105^{\circ}\text{C}$  の条件で有効です。仕様は注記した場合を除いて 1.71V ~ 5.5V において有効です。

表 2. DC 仕様

標準値は  $25^{\circ}\text{C}$  で、V<sub>DD</sub> = 3.3V 時に測定されます。

| 仕様 ID# | パラメーター            | 説明                                             | Min  | Typ | Max             | 単位 | 詳細／条件                 |

|--------|-------------------|------------------------------------------------|------|-----|-----------------|----|-----------------------|

| SID53  | V <sub>DD</sub>   | 電源供給入力電圧                                       | 1.8  | -   | 5.5             | V  | レギュレータが有効             |

| SID255 | V <sub>DD</sub>   | 電源供給入力電圧 (V <sub>CCD</sub> = V <sub>DD</sub> ) | 1.71 | -   | 1.89            |    | 内部的に安定化されない電源         |

| SID54  | V <sub>DDIO</sub> | V <sub>DDIO</sub> ドメインの電源                      | 1.71 | -   | V <sub>DD</sub> |    | -                     |

| SID55  | C <sub>EFC</sub>  | 外部レギュレータ電圧バイパス                                 | -    | 0.1 | -               | μF | X5R セラミックまたはこれより良質のもの |

| SID56  | C <sub>EXC</sub>  | 電源供給バイパス コンデンサ                                 | -    | 1   | -               |    | X5R セラミックまたはこれより良質のもの |

### アクティブ モード、V<sub>DD</sub> = 1.8V ~ 5.5V。標準値は $25^{\circ}\text{C}$ 、V<sub>DD</sub> = 3.3V で測定

|       |                   |                         |   |      |   |    |   |

|-------|-------------------|-------------------------|---|------|---|----|---|

| SID10 | I <sub>DD5</sub>  | フラッシュから実行；CPU 速度が 6MHz  | - | 2    | - | mA | - |

| SID16 | I <sub>DD8</sub>  | フラッシュから実行；CPU 速度が 24MHz | - | 5.6  | - |    | - |

| SID19 | I <sub>DD11</sub> | フラッシュから実行；CPU 速度が 48MHz | - | 10.4 | - |    | - |

### スリープ モード、V<sub>DDD</sub> = 1.8V ~ 5.5V (レギュレータが有効)

|       |       |                                           |   |     |   |    |       |

|-------|-------|-------------------------------------------|---|-----|---|----|-------|

| SID22 | IDD17 | I <sup>2</sup> C ウェイクアップ WDT、およびコンパレータが有効 | - | 1.1 | - | mA | 6MHz  |

| SID25 | IDD20 | I <sup>2</sup> C ウェイクアップ、WDT、およびコンパレータが有効 | - | 3.1 | - |    | 12MHz |

#### 注：

- 表 1 に記載されている絶対最大条件を超えて使用すると、デバイスに恒久的なダメージを与える可能性があります。長時間にわたって絶対最大条件下に置くと、デバイスの信頼性に影響を与える可能性があります。最大保管温度は JEDEC 標準「JESD22-A103、High Temperature Storage Life」に準拠した  $150^{\circ}\text{C}$  です。絶対最大条件以内で使用している場合でも、標準的な動作条件を超えると、デバイスが仕様どおりに動作しない可能性があります。

**表 2. DC 仕様 (続き)**

標準値は 25°C で、 $V_{DD} = 3.3V$  時に測定されます。

| 仕様 ID#                                                                           | パラメーター       | 説明                              | Min | Typ | Max | 単位      | 詳細／条件 |

|----------------------------------------------------------------------------------|--------------|---------------------------------|-----|-----|-----|---------|-------|

| <b>スリープ モード、<math>V_{DD} = 1.71V \sim 1.89V</math> (レギュレータ バイパス)</b>             |              |                                 |     |     |     |         |       |

| SID28                                                                            | $I_{DD23}$   | $I^2C$ ウェイクアップ、WDT、およびコンパレータが有効 | —   | 1.1 | —   | mA      | 6MHz  |

| SID28A                                                                           | $I_{DD23A}$  | $I^2C$ ウェイクアップ、WDT、およびコンパレータが有効 | —   | 3.1 | —   | mA      | 12MHz |

| <b>ディープスリープ モード、<math>V_{DD} = 1.8V \sim 3.6V</math> (レギュレータが有効)</b>             |              |                                 |     |     |     |         |       |

| SID31                                                                            | $I_{DD26}$   | $I^2C$ ウェイクアップと WDT が有効         | —   | 2.5 | —   | $\mu A$ | —     |

| <b>ディープスリープ モード、<math>V_{DD} = 3.6V \sim 5.5V</math> (レギュレータが有効)</b>             |              |                                 |     |     |     |         |       |

| SID34                                                                            | $I_{DD29}$   | $I^2C$ ウェイクアップと WDT が有効         | —   | 2.5 | —   | $\mu A$ | —     |

| <b>ディープスリープ モード、<math>V_{DD} = V_{CCD} = 1.71V \sim 1.89V</math> (レギュレータが有効)</b> |              |                                 |     |     |     |         |       |

| SID37                                                                            | $I_{DD32}$   | $I^2C$ ウェイクアップと WDT が有効         | —   | 2.5 | —   | $\mu A$ | —     |

| <b>XRES 電流</b>                                                                   |              |                                 |     |     |     |         |       |

| SID307                                                                           | $I_{DD\_XR}$ | XRES がアサートされている時の供給電流           | —   | 115 | 300 | $\mu A$ | —     |

**表 3. AC 仕様**

| 仕様 ID#               | パラメーター          | 説明                  | Min | Typ | Max | 単位      | 詳細／条件                       |

|----------------------|-----------------|---------------------|-----|-----|-----|---------|-----------------------------|

| SID48                | $f_{CPU}$       | CPU 周波数             | DC  | —   | 48  | MHz     | $1.71 \leq V_{DD} \leq 5.5$ |

| SID49 <sup>[2]</sup> | $T_{SLEEP}$     | スリープ モードからの復帰時間     | —   | 0   | —   | $\mu s$ | —                           |

| SID50 <sup>[2]</sup> | $T_{DEEPSLEEP}$ | ディープスリープ モードからの復帰時間 | —   | 35  | —   |         | —                           |

**注：**

2. 特性評価で保証されています。

**GPIO**

**表 4. GPIO の DC 仕様**

| 仕様 ID#                | パラメーター          | 説明                                     | Min                   | Typ | Max                  | 単位 | 詳細／条件                                 |

|-----------------------|-----------------|----------------------------------------|-----------------------|-----|----------------------|----|---------------------------------------|

| SID57                 | $V_{IH}^{[3]}$  | 入力電圧の HIGH 閾値                          | $0.7 \times V_{DDD}$  | —   | —                    | V  | CMOS 入力                               |

| SID58                 | $V_{IL}$        | 入力電圧の LOW 閾値                           | —                     | —   | $0.3 \times V_{DDD}$ |    | CMOS 入力                               |

| SID241                | $V_{IH}^{[3]}$  | LV TTL 入力、 $V_{DDD} < 2.7V$            | $0.7 \times V_{DDD}$  | —   | —                    |    | —                                     |

| SID242                | $V_{IL}$        | LV TTL 入力、 $V_{DDD} < 2.7V$            | —                     | —   | $0.3 \times V_{DDD}$ |    | —                                     |

| SID243                | $V_{IH}^{[3]}$  | LV TTL 入力、 $V_{DDD} \geq 2.7V$         | 2.0                   | —   | —                    |    | —                                     |

| SID244                | $V_{IL}$        | LV TTL 入力、 $V_{DDD} \geq 2.7V$         | —                     | —   | 0.8                  |    | —                                     |

| SID59                 | $V_{OH}$        | 出力 HIGH 電圧                             | $V_{DDD}-0.6$         | —   | —                    |    | $I_{OH} = 4mA, V_{DDD} \geq 3.3V$     |

| SID60                 | $V_{OH}$        | 出力 HIGH 電圧                             | $V_{DDD}-0.5$         | —   | —                    |    | $V_{DD} = 1.8V$ の時、<br>$I_{OH} = 1mA$ |

| SID61                 | $V_{OL}$        | 出力 LOW 電圧                              | —                     | —   | 0.6                  |    | $V_{DD} = 3.3V$ の時、<br>$I_{OL} = 8mA$ |

| SID62                 | $V_{OL}$        | 出力 LOW 電圧                              | —                     | —   | 0.6                  |    | $V_{DD} = 1.8V$ の時、<br>$I_{OL} = 4mA$ |

| SID62A                | $V_{OL}$        | 出力 LOW 電圧                              | —                     | —   | 0.4                  |    | $I_{OL} = 3mA, V_{DDD} \geq 3V$       |

| SID63                 | $R_{PULLUP}$    | プルアップ抵抗                                | 3.5                   | 5.6 | 8.5                  | kΩ | —                                     |

| SID64                 | $R_{PULLDOWN}$  | プルダウン抵抗                                | 3.5                   | 5.6 | 8.5                  |    | —                                     |

| SID65                 | $I_{IL}$        | 入力リーク電流（絶対値）                           | —                     | 2   | —                    | nA | —                                     |

| SID66                 | $C_{IN}$        | 入力静電容量                                 | —                     | 3   | 7                    | pF | —                                     |

| SID67 <sup>[4]</sup>  | $V_{HYSTTL}$    | 入力ヒステリシス LV TTL                        | 15                    | 40  | —                    | mV | $V_{DDD} \geq 2.7V$                   |

| SID68 <sup>[4]</sup>  | $V_{HYSMOS}$    | 入力ヒステリシス CMOS                          | $0.05 \times V_{DDD}$ | —   | —                    |    | $V_{DD} < 4.5V$                       |

| SID68A <sup>[4]</sup> | $V_{HYSMOS5V5}$ | 入力ヒステリシス CMOS                          | 200                   | —   | —                    |    | $V_{DD} > 4.5V$                       |

| SID69 <sup>[4]</sup>  | $I_{DIODE}$     | 保護ダイオードをとおって<br>$V_{DD}/V_{SS}$ に流れる電流 | —                     | —   | 100                  | μA | —                                     |

| SID69A <sup>[4]</sup> | $I_{TOT\_GPIO}$ | チップのソースまたはシンク電流<br>の合計最大値              | —                     | —   | 85                   | mA | —                                     |

**表 5. GPIO の AC 仕様**

(特性評価で保証)

| 仕様 ID# | パラメーター      | 説明                  | Min | Typ | Max | 単位 | 詳細／条件                              |

|--------|-------------|---------------------|-----|-----|-----|----|------------------------------------|

| SID70  | $T_{RISEF}$ | 高速ストロング モードでの立ち上り時間 | 2   | —   | 12  | ns | $3.3V V_{DDD}$ 、<br>$Cload = 25pF$ |

| SID71  | $T_{FALLF}$ | 高速ストロング モードでの立ち下り時間 | 2   | —   | 12  |    | $3.3V V_{DDD}$ 、<br>$Cload = 25pF$ |

| SID72  | $T_{RISES}$ | 低速ストロング モードでの立ち上り時間 | 10  | —   | 60  | ns | $3.3V V_{DDD}$ 、<br>$Cload = 25pF$ |

| SID73  | $T_{FALLS}$ | 低速ストロング モードでの立ち下り時間 | 10  | —   | 60  |    | $3.3V V_{DDD}$ 、<br>$Cload = 25pF$ |

注：

3.  $V_{IH}$  は  $V_{DDD} + 0.2V$  を超えてはいけません。

4. 特性評価で保証されています。

**表 5. GPIO の AC 仕様**

( 特性評価で保証 )( 続き )

| 仕様 ID# | パラメーター                | 説明                                                                     | Min | Typ | Max | 単位  | 詳細／条件                           |

|--------|-----------------------|------------------------------------------------------------------------|-----|-----|-----|-----|---------------------------------|

| SID74  | F <sub>GPIOOUT1</sub> | GPIO F <sub>OUT</sub> ; 3.3V ≤ V <sub>DDD</sub> ≤ 5.5V<br>高速ストロング モード  | —   | —   | 33  | MHz | 90/10%、負荷 25pF、<br>デューティ比 60/40 |

| SID75  | F <sub>GPIOOUT2</sub> | GPIO F <sub>OUT</sub> ; 1.71V ≤ V <sub>DDD</sub> ≤ 3.3V<br>高速ストロング モード | —   | —   | 16  |     | 90/10%、負荷 25pF、<br>デューティ比 60/40 |

| SID76  | F <sub>GPIOOUT3</sub> | GPIO F <sub>OUT</sub> ; 3.3V ≤ V <sub>DDD</sub> ≤ 5.5V<br>低速ストロング モード  | —   | —   | 7   |     | 90/10%、負荷 25pF、<br>デューティ比 60/40 |

| SID245 | F <sub>GPIOOUT4</sub> | GPIO F <sub>OUT</sub> ; 1.71V ≤ V <sub>DDD</sub> ≤ 3.3V<br>低速ストロング モード | —   | —   | 3.5 |     | 90/10%、負荷 25pF、<br>デューティ比 60/40 |

| SID246 | F <sub>GPIOIN</sub>   | GPIO 入力の動作周波数;<br>1.71V ≤ V <sub>DDD</sub> ≤ 5.5V                      | —   | —   | 48  |     | 90/10% V <sub>IO</sub>          |

XRES

**表 6. XRES の DC 仕様**

| 仕様 ID#               | パラメーター               | 説明            | Min                    | Typ                    | Max                    | 単位 | 詳細／条件                                      |

|----------------------|----------------------|---------------|------------------------|------------------------|------------------------|----|--------------------------------------------|

| SID77                | V <sub>IH</sub>      | 入力電圧の HIGH 閾値 | 0.7 × V <sub>DDD</sub> | —                      | —                      | V  | CMOS 入力                                    |

| SID78                | V <sub>IL</sub>      | 入力電圧の LOW 閾値  | —                      | —                      | 0.3 × V <sub>DDD</sub> |    |                                            |

| SID79                | R <sub>PULLUP</sub>  | プルアップ抵抗       | —                      | 60                     | —                      | kΩ | —                                          |

| SID80                | C <sub>IN</sub>      | 入力静電容量        | —                      | 3                      | 7                      | pF | —                                          |

| SID81 <sup>[5]</sup> | V <sub>HYSXRES</sub> | 入力ヒステリシス電圧    | —                      | 0.05 × V <sub>DD</sub> | —                      | mV | V <sub>DD</sub> > 4.5V 時の標準ヒステリシス電圧が 200mV |

**表 7. XRES の AC 仕様**

| 仕様 ID#                | パラメーター                  | 説明                  | Min | Typ | Max | 単位 | 詳細／条件 |

|-----------------------|-------------------------|---------------------|-----|-----|-----|----|-------|

| SID83 <sup>[5]</sup>  | T <sub>RESETWIDTH</sub> | リセット パルス幅           | 1   | —   | —   | μs | —     |

| BID194 <sup>[5]</sup> | T <sub>RESETWAKE</sub>  | リセット解除時からのウェイクアップ時間 | —   | —   | 2.7 | ms | —     |

注：

5. 特性評価で保証されています。

**アナログ ペリフェラル**

**表 8. CTB のオペアンプ仕様**

| 仕様 ID#   | パラメーター                   | 説明                                      | Min   | Typ  | Max                   | 単位  | 詳細／条件                                  |

|----------|--------------------------|-----------------------------------------|-------|------|-----------------------|-----|----------------------------------------|

|          | I <sub>DD</sub>          | オペアンプ ブロック電流、負荷なし                       |       |      |                       |     |                                        |

| SID269   | I <sub>DD_HI</sub>       | 電力 = 高                                  | —     | 1100 | 1850                  | μA  | —                                      |

| SID270   | I <sub>DD_MED</sub>      | 電力 = 中                                  | —     | 550  | 950                   |     | —                                      |

| SID271   | I <sub>DD_LOW</sub>      | 電力 = 低                                  | —     | 150  | 350                   |     | —                                      |

|          | G <sub>BW</sub>          | 負荷 = 20pF、0.1mA V <sub>DDA</sub> = 2.7V |       |      |                       |     |                                        |

| SID272   | G <sub>BW_HI</sub>       | 電力 = 高                                  | 6     | —    | —                     | MHz | 入力および出力は 0.2V ~ V <sub>DDA</sub> -0.2V |

| SID273   | G <sub>BW_MED</sub>      | 電力 = 中                                  | 3     | —    | —                     |     | 入力および出力は 0.2V ~ V <sub>DDA</sub> -0.2V |

| SID274   | G <sub>BW_LO</sub>       | 電力 = 低                                  | —     | 1    | —                     |     | 入力および出力は 0.2V ~ V <sub>DDA</sub> -0.2V |

|          | I <sub>OUT_MAX</sub>     | V <sub>DDA</sub> = 2.7V、電源レールから 500mV   |       |      |                       |     |                                        |

| SID275   | I <sub>OUT_MAX_HI</sub>  | 電力 = 高                                  | 10    | —    | —                     | mA  | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

| SID276   | I <sub>OUT_MAX_MID</sub> | 電力 = 中                                  | 10    | —    | —                     |     | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

| SID277   | I <sub>OUT_MAX_LO</sub>  | 電力 = 低                                  | —     | 5    | —                     |     | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

|          | I <sub>OUT</sub>         | V <sub>DDA</sub> = 1.71V、電源レールから 500mV  |       |      |                       |     |                                        |

| SID278   | I <sub>OUT_MAX_HI</sub>  | 電力 = 高                                  | 4     | —    | —                     | mA  | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

| SID279   | I <sub>OUT_MAX_MID</sub> | 電力 = 中                                  | 4     | —    | —                     |     | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

| SID280   | I <sub>OUT_MAX_LO</sub>  | 電力 = 低                                  | —     | 2    | —                     |     | 出力は 0.5V ~ V <sub>DDA</sub> -0.5V      |

|          | I <sub>DD_Int</sub>      | オペアンプ ブロック電流、内部負荷                       |       |      |                       |     |                                        |

| SID269_I | I <sub>DD_HI_Int</sub>   | 電力 = 高                                  | —     | 1500 | 2300                  | μA  | —                                      |

| SID270_I | I <sub>DD_MED_Int</sub>  | 電力 = 中                                  | —     | 700  | 1200                  |     | —                                      |

|          | G <sub>BW</sub>          | V <sub>DDA</sub> = 2.7V                 |       |      |                       |     |                                        |

| SID272_I | G <sub>BW_HI_Int</sub>   | 電力 = 高                                  | 8     | —    | —                     | MHz | 出力は 0.25V ~ V <sub>DDA</sub> -0.25V    |

|          |                          | 内部と外部モードの両方の一般的なオペアンプの仕様                |       |      |                       |     |                                        |

| SID281   | V <sub>IN</sub>          | チャージ ポンプがオン、<br>V <sub>DDA</sub> = 2.7V | -0.05 | —    | V <sub>DDA</sub> -0.2 | V   | —                                      |

| SID282   | V <sub>CM</sub>          | チャージ ポンプがオン、<br>V <sub>DDA</sub> = 2.7V | -0.05 | —    | V <sub>DDA</sub> -0.2 |     | —                                      |

| SID283   | V <sub>OUT_1</sub>       | 電力 = 高、I <sub>load</sub> =10mA          | 0.5   | —    | V <sub>DDA</sub> -0.5 |     | V <sub>DD</sub> = 2.7V                 |

**表 8. CTB のオペアンプ仕様 ( 続き )**

| 仕様 ID#  | パラメーター                | 説明                                                           | Min  | Typ  | Max                   | 単位      | 詳細／条件                                                                                                     |

|---------|-----------------------|--------------------------------------------------------------|------|------|-----------------------|---------|-----------------------------------------------------------------------------------------------------------|

| SID284  | V <sub>OUT_2</sub>    | 電力 = 高、I <sub>load</sub> =1mA                                | 0.2  | -    | V <sub>DDA</sub> -0.2 | V       | V <sub>DDA</sub> = 2.7V                                                                                   |

| SID285  | V <sub>OUT_3</sub>    | 電力 = 中、I <sub>load</sub> =1mA                                | 0.2  | -    | V <sub>DDA</sub> -0.2 |         | V <sub>DDA</sub> = 2.7V                                                                                   |

| SID286  | V <sub>OUT_4</sub>    | 電力 = 低、I <sub>load</sub> =0.1mA                              | 0.2  | -    | V <sub>DDA</sub> -0.2 |         | V <sub>DDA</sub> = 2.7V                                                                                   |

| SID288  | V <sub>OS_TR</sub>    | オフセット電圧 ( 調整後 )                                              | -1.0 | ±0.5 | 1.0                   | mV      | 大消費電力モード、入力は 0V ~ V <sub>DDA</sub> -0.2V                                                                  |

| SID288A | V <sub>OS_TR</sub>    | オフセット電圧 ( 調整後 )                                              | -    | ±1   | -                     |         | 中消費電力モード、入力は 0V ~ V <sub>DDA</sub> -0.2V                                                                  |

| SID288B | V <sub>OS_TR</sub>    | オフセット電圧 ( 調整後 )                                              | -    | ±2   | -                     |         | 小消費電力モード、入力は 0V ~ V <sub>DDA</sub> -0.2V                                                                  |

| SID290  | V <sub>OS_DR_TR</sub> | オフセット電圧ドリフト<br>( 調整後 )                                       | -10  | ±3   | 10                    | μV/C    | 大消費電力モード                                                                                                  |

| SID290A | V <sub>OS_DR_TR</sub> | オフセット電圧ドリフト<br>( 調整後 )                                       | -    | ±10  | -                     | μV/C    | 中消費電力モード                                                                                                  |

| SID290B | V <sub>OS_DR_TR</sub> | オフセット電圧ドリフト<br>( 調整後 )                                       | -    | ±10  | -                     |         | 小消費電力モード                                                                                                  |

| SID291  | CMRR                  | DC                                                           | 70   | 80   | -                     | dB      | 入力は 0V ~ V <sub>DDA</sub> -0.2V、<br>出力は 0.2V ~ V <sub>DDA</sub> -0.2V                                     |

| SID291A | CMRR2                 | DC                                                           | 60   | 70   | -                     |         | 入力は 0V ~ V <sub>DDA</sub> -0.2V、<br>出力は 0.2V ~ V <sub>DDA</sub> -0.2V、<br>1.71V ≤ V <sub>DDA</sub> < 2.7V |

| SID292  | PSRR                  | 周波数 = 1kHz、<br>リップル = 10mV                                   | 70   | 85   | -                     |         | V <sub>DDD</sub> = 3.6V、大消費電力<br>モード、入力は 0.2V ~<br>V <sub>DDA</sub> -0.2V                                 |

|         | Noise                 |                                                              |      |      |                       |         |                                                                                                           |

| SID294  | VN2                   | 基準入力、1kHz、電力 = 高                                             | -    | 72   | -                     | nV/rtHz | 入力および出力は 0.2V ~<br>V <sub>DDA</sub> -0.2V                                                                 |

| SID295  | VN3                   | 基準入力、10kHz、電力 = 高                                            | -    | 28   | -                     |         | 入力および出力は 0.2V ~<br>V <sub>DDA</sub> -0.2V                                                                 |

| SID296  | VN4                   | 基準入力、100kHz、電力 = 高                                           | -    | 15   | -                     |         | 入力および出力は 0.2V ~<br>V <sub>DDA</sub> -0.2V                                                                 |

| SID297  | C <sub>LOAD</sub>     | 最大負荷まで安定。50pF で<br>性能仕様を満たす                                  | -    | -    | 125                   | pF      | -                                                                                                         |

| SID298  | SLEW_RATE             | C <sub>LOAD</sub> = 50pF、消費電力 =<br>大、V <sub>DDA</sub> = 2.7V | 6    | -    | -                     | V/μs    | -                                                                                                         |

| SID299  | T_OP_WAKE             | 無効から有効まで、外付け<br>RC 無し                                        | -    | -    | 25                    | μs      | -                                                                                                         |

| SID299A | OL_GAIN               | オープン ループ ゲイン                                                 | -    | 90   | -                     | dB      | -                                                                                                         |

**表 8. CTB のオペアンプ仕様 ( 続き )**

| 仕様 ID#    | パラメーター                | 説明                                                   | Min | Typ  | Max | 単位      | 詳細／条件                                             |

|-----------|-----------------------|------------------------------------------------------|-----|------|-----|---------|---------------------------------------------------|

|           | COMP_MODE             | コンパレータ モード ; 50mV 駆動、 $T_{rise} = T_{fall}$ ( おおよそ ) |     |      |     |         |                                                   |

| SID300    | $T_{PD1}$             | 応答時間 ; 電力 = 高                                        | -   | 150  | 175 | ns      | 入力は $0.2V \sim V_{DDA}-0.2V$                      |

| SID301    | $T_{PD2}$             | 応答時間 ; 電力 = 中                                        | -   | 500  | -   |         | 入力は $0.2V \sim V_{DDA}-0.2V$                      |

| SID302    | $T_{PD3}$             | 応答時間 ; 電力 = 低                                        | -   | 2500 | -   |         | 入力は $0.2V \sim V_{DDA}-0.2V$                      |

| SID303    | $V_{HYST\_OP}$        | ヒステリシス                                               | -   | 10   | -   | mV      | -                                                 |

| SID304    | WUP_CTB               | イネーブルから使用可能までのウェイクアップ時間                              | -   | -    | 25  | $\mu s$ | -                                                 |

|           | オペアンプ<br>ディープスリープ モード | モード 2 は最小の電流範囲。モード 1 はより高い GBW を持つ                   |     |      |     |         |                                                   |

| SID_DS_1  | $I_{DD\_HI\_M1}$      | モード 1、高電流                                            | -   | 1400 | -   | $\mu A$ | -                                                 |

| SID_DS_2  | $I_{DD\_MED\_M1}$     | モード 1、中電流                                            | -   | 700  | -   |         | -                                                 |

| SID_DS_3  | $I_{DD\_LOW\_M1}$     | モード 1、低電流                                            | -   | 200  | -   |         | -                                                 |

| SID_DS_4  | $I_{DD\_HI\_M2}$      | モード 2、高電流                                            | -   | 120  | -   | $\mu A$ | -                                                 |

| SID_DS_5  | $I_{DD\_MED\_M2}$     | モード 2、中電流                                            | -   | 60   | -   |         | -                                                 |

| SID_DS_6  | $I_{DD\_LOW\_M2}$     | モード 2、低電流                                            | -   | 15   | -   |         | -                                                 |

| SID_DS_7  | $G_{BW\_HI\_M1}$      | モード 1、高電流                                            | -   | 4    | -   | MHz     | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_8  | $G_{BW\_MED\_M1}$     | モード 1、中電流                                            | -   | 2    | -   |         | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_9  | $G_{BW\_LOW\_M1}$     | モード 1、低電流                                            | -   | 0.5  | -   |         | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_10 | $G_{BW\_HI\_M2}$      | モード 2、高電流                                            | -   | 0.5  | -   | mV      | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_11 | $G_{BW\_MED\_M2}$     | モード 2、中電流                                            | -   | 0.2  | -   |         | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_12 | $G_{BW\_LOW\_M2}$     | モード 2、低電流                                            | -   | 0.1  | -   |         | 20pF 負荷、DC 負荷なし、<br>$0.2V \sim V_{DDA}-0.2V$      |

| SID_DS_13 | $V_{OS\_HI\_M1}$      | モード 1、高電流                                            | -   | 5    | -   | mV      | トリム $25^{\circ}C$ あり、<br>$0.2V \sim V_{DDA}-1.5V$ |

| SID_DS_14 | $V_{OS\_MED\_M1}$     | モード 1、中電流                                            | -   | 5    | -   |         | トリム $25^{\circ}C$ あり、<br>$0.2V \sim V_{DDA}-1.5V$ |

**表 8. CTB のオペアンプ仕様 ( 続き )**

| 仕様 ID#    | パラメーター             | 説明        | Min | Typ | Max | 単位 | 詳細／条件                                  |

|-----------|--------------------|-----------|-----|-----|-----|----|----------------------------------------|

| SID_DS_15 | $V_{OS\_LOW\_M1}$  | モード 1、低電流 | -   | 5   | -   | mV | トリム 25°C あり、<br>0.2V ~ $V_{DDA}$ -1.5V |

| SID_DS_16 | $V_{OS\_HI\_M2}$   | モード 2、高電流 | -   | 5   | -   |    | トリム 25°C あり、<br>0.2V ~ $V_{DDA}$ -1.5V |

| SID_DS_17 | $V_{OS\_MED\_M2}$  | モード 2、中電流 | -   | 5   | -   |    | トリム 25°C あり、<br>0.2V ~ $V_{DDA}$ -1.5V |

| SID_DS_18 | $V_{OS\_LOW\_M2}$  | モード 2、低電流 | -   | 5   | -   |    | トリム 25°C あり、<br>0.2V ~ $V_{DDA}$ -1.5V |

| SID_DS_19 | $I_{OUT\_HI\_M1}$  | モード 1、高電流 | -   | 10  | -   | mA | 出力は 0.5V ~ $V_{DDA}$ -0.5V             |

| SID_DS_20 | $I_{OUT\_MED\_M1}$ | モード 1、中電流 | -   | 10  | -   |    | 出力は 0.5V ~ $V_{DDA}$ -0.5V             |

| SID_DS_21 | $I_{OUT\_LOW\_M1}$ | モード 1、低電流 | -   | 4   | -   |    | 出力は 0.5V ~ $V_{DDA}$ -0.5V             |

| SID_DS_22 | $I_{OUT\_HI\_M2}$  | モード 2、高電流 | -   | 1   | -   |    | -                                      |

| SID_DS_23 | $I_{OU\_MED\_M2}$  | モード 2、中電流 | -   | 1   | -   |    | -                                      |

| SID_DS_24 | $I_{OU\_LOW\_M2}$  | モード 2、低電流 | -   | 0.5 | -   |    | -                                      |

**表 9. PGA 仕様**

| 仕様 ID#    | パラメーター    | 説明                     | Min | Typ | Max | 単位 | 詳細／条件 |

|-----------|-----------|------------------------|-----|-----|-----|----|-------|

| PGA のゲイン値 | -         | ゲイン値は 2、4、16、および 32    | 2   | -   | 32  | -  | -     |

| SID_PGA_1 | PGA_ERR_1 | 低レンジ用のゲイン誤差 ; ゲイン = 2  | -   | 1   | -   | %  | -     |

|           |           | 中レンジ用のゲイン誤差 ; ゲイン = 2  | -   | -   | 1.5 | %  | -     |

|           |           | 高レンジ用のゲイン誤差 ; ゲイン = 2  | -   | -   | 1.5 | %  | -     |

| SID_PGA_2 | PGA_ERR_2 | 低レンジ用のゲイン誤差 ; ゲイン = 4  | -   | 1   | -   | %  | -     |

|           |           | 中レンジ用のゲイン誤差 ; ゲイン = 4  | -   | -   | 1.5 | %  | -     |

|           |           | 高レンジ用のゲイン誤差 ; ゲイン = 4  | -   | -   | 1.5 | %  | -     |

| SID_PGA_3 | PGA_ERR_3 | 低レンジ用のゲイン誤差 ; ゲイン = 16 | -   | 3   | -   | %  | -     |

|           |           | 中レンジ用のゲイン誤差 ; ゲイン = 16 | -   | 3   | -   | %  | -     |

|           |           | 高レンジ用のゲイン誤差 ; ゲイン = 16 | -   | 3   | -   | %  | -     |

| SID_PGA_4 | PGA_ERR_4 | 低レンジ用のゲイン誤差 ; ゲイン = 32 | -   | 5   | -   | %  | -     |

|           |           | 中レンジ用のゲイン誤差 ; ゲイン = 32 | -   | 5   | -   | %  | -     |

|           |           | 高レンジ用のゲイン誤差 ; ゲイン = 32 | -   | 5   | -   | %  | -     |

**注：**

6. 特性評価で保証されています。

**表 10. 汎用アナログ ブロック (UAB) の仕様**

全USBブロックはPSoC Creatorコンポーネント経由により設定。

注：UAB 機能は互いに排他的です。UAB は、1 つまたは 2 つの電圧 DAC、1 つの 2 次アナログフィルター、または 1 つの 12 ビット増分デルタシグマ ADC として構成できます。

| 仕様 ID#            | パラメーター     | 説明                                       | Min  | Typ    | Max           | 単位          | 詳細／条件                                          |

|-------------------|------------|------------------------------------------|------|--------|---------------|-------------|------------------------------------------------|

| -                 | -          | ADC、DAC、およびフィルター用の主要な機能ブロックの仕様           | -    | -      | -             | -           | 仕様は $V_{DDA} \geq 2.7V$ の時に適用                  |

| 12 ビット デルタシグマ ADC | -          | 2 次デルタシグマ変調器で実現される（シングルエンド）              | -    | -      | -             | -           | オートゼロ モードで基準ドリフトを除く                            |

| SID_PADC_1        | GE_DS2     | ゲイン誤差                                    | -    | 0.1    | -             | %           | ADC エラー                                        |

| SID_PADC_2        | GED_DS2    | ゲイン誤差ドリフト                                | -    | 50     | -             | ppm / °C    | -                                              |

| SID_PADC_3        | VOS_DS2    | オフセット電圧                                  | -    | 1      | -             | mV          | -                                              |

| SID_PADC_4        | VSO_DS2    | オフセット ドリフト                               | -    | 50     | -             | ppm / °C    | -                                              |

| SID_PADC_5        | INL_DS2    | 積分非直線性 (INL)                             | -    | +3, -4 | -             | LSB         | -                                              |

| SID_PADC_6        | DNL_DS2    | 微分非直線性 (DNL)                             | -    | +2, -1 | -             | LSB         | -                                              |

| SID_PADC_7        | SINAD_DS2  | 信号対ノイズおよび歪み。<br>ENOB = (SINAD-1.76)/6.02 | -    | 61     | -             | dB          | -                                              |

| SID_PADC_8        | PSRR_DS2   | 電源電圧変動除去比                                | -    | 74     | -             | dB          | -                                              |

| SID_PADC_10       | FS_DS2     | サンプル レート (ksps)                          | -    | 1      | -             | ksps        | -                                              |

| SID_PADC_11       | FC_DS2     | サンプル周波数の一部としての<br>3dB の帯域幅               | 0.26 | 0.26   | 0.26          |             | -                                              |

| SID_PADC_12       | VIN_DS2    | 入力電圧範囲                                   | -    | 75     | -             | % $V_{REF}$ | サイプレス コンポーネントの使用に基づく                           |

| SID_PADC_13       | IDD_DS2    | ブロック電流                                   | -    | 900    | -             | μA          | 中消費電力モード                                       |

| SID_PADC_14       | WUP_DS2    | イネーブルから使用可能までの<br>ウェイクアップ時間              | -    | -      | 30            | μS          | クロック $\geq 1MHz$ の時                            |

| 13 ビット DAC        |            | 差動出力 VDAC 仕様は -20 ~ +85 °C で有効です。        |      |        |               |             |                                                |

| SID_DAC_1         | INL_MDAC1  | 積分非直線性 (INL)                             | -6   | -      | +5            | LSB         | -                                              |

| SID_DAC_2         | DNL_MDAC1  | 微分非直線性 (DNL)                             | -1   | -      | 4             |             | -                                              |

| SID_DAC_3         | VOUT_MDAC1 | 出力電圧範囲                                   | 0.2  | -      | $V_{DDA}-0.2$ | V           | 有効な出力範囲はレールから 200 LSB。レールの 200mV 以内のフルセトリング帯域幅 |

| SID_DAC_4         | VOS_MDAC1  | ゼロ スケール エラー ( 入力が「0」の変換器の出力 )            | -    | 20     | -             | mV          | ゼロ スケールはアナログ グランドにある                           |

| SID_DAC_5         | GE_MDAC1   | フルスケール エラーからオフセット エラーを差し引いた後の値           | -    | 0.3    | 2             | %           | $V_{DDA} \geq 2.7V$ ,<br>$V_{REF} = V_{DDA}/2$ |

| SID_DAC_6         | IDD_MMDAC1 | ブロック電流                                   | -    | 1.8    | -             | mA          | -                                              |

| SID_DAC_7         | PSRR_MDAC1 | 電源電圧変動除去比                                | -    | 50     | -             | dB          | $2.7V \leq V_{DDA} < 5.5V$                     |

**表 10. 汎用アナログ ブロック (UAB) の仕様 (続き)**

全USBブロックはPSoC Creatorコンポーネント経由により設定。

注：UAB 機能は互いに排他的です。UAB は、1つまたは2つの電圧 DAC、1つの2次アナログフィルター、または1つの12ビット増分デルタシグマ ADC として構成できます。

| 仕様 ID#                                                | パラメーター    | 説明                      | Min  | Typ | Max | 単位  | 詳細／条件                                                     |

|-------------------------------------------------------|-----------|-------------------------|------|-----|-----|-----|-----------------------------------------------------------|

| SID_DAC_8                                             | WUP_VDAC1 | イネーブルから使用可能までのウェイクアップ時間 | –    | –   | 39  | μs  | クロック $\geq 1\text{MHz}$ の時,<br>$V_{DDA} \geq 2.7\text{V}$ |

| SID_DAC_8A                                            | WUP_VDAC2 | イネーブルから使用可能までのウェイクアップ時間 | –    | –   | 72  | μs  | $V_{DDA} \leq 2.7\text{V}$                                |

| SID_DAC_9                                             | TS_VDAC1  | DAC のセトリング時間            | –    | –   | 2   | μs  | 500ksps 動作,<br>$2.7\text{V} < V_{DDA} \leq 5.5\text{V}$   |

| SID_DAC_9A                                            | TS_VDAC2  | DAC のセトリング時間            | –    | –   | 10  | μs  | 100ksps 動作,<br>$V_{DDA} \leq 2.7\text{V}$                 |

| <b>2極バイクアップ スイッチ コンデンサ フィルタ。ロー／バンド／ハイ／ノッチ パス フィルタ</b> |           |                         |      |     |     |     | サイプレス コンポーネントを介して設定される                                    |

| SID_SC_1                                              | SNR_SCF1  | 信号対ノイズ比                 | –    | 54  | –   | dB  | $V_{IN} 2.2\text{Vp-p}$ 、ロー パス、<br>OSR=100                |

| SID_SC_2                                              | THD_SCF1  | 全高調波歪み                  | –    | 60  | –   | dB  | $V_{IN} 2.2\text{Vp-p}$ 、ロー パス、<br>OSR=100                |

| SID_SC_3                                              | F0_SCF1   | 中心周波数範囲                 | 0.1  |     | 20  | kHz | OSR=100                                                   |

| SID_SC_4                                              | VOS_SFC1  | オフセット誤差                 | –    | 15  | –   | mV  | $V_{IN} 5\text{Vp-p}$ 、ロー パス、<br>OSR=100                  |

| SID_SC_7                                              | QRNG_SFC1 | Q 範囲                    | 0.25 | –   | 25  | –   | –                                                         |

| SID_SC_9                                              | FC_SCF1   | 最大サンプリング周波数             | 0.05 | –   | 2   | MHz | –                                                         |

| SID_SC_10                                             | FR_SCF1   | サンプリング周波数とコーナー周波数の比     | 8    | –   | 128 | –   | –                                                         |

| SID_SC_11                                             | IDD_SCF1  | ブロック電流                  | –    | 4   | –   | mA  | –                                                         |

| SID_SC_12                                             | WUP_SCF1  | イネーブルから使用可能までのウェイクアップ時間 | –    | –   | 39  | μs  | クロック $\geq 1\text{MHz}$ の時                                |

**表 11. コンパレータの DC 仕様**

| 仕様 ID#  | パラメーター        | 説明                   | Min | Typ | Max            | 単位            | 詳細／条件                                                                                                                  |

|---------|---------------|----------------------|-----|-----|----------------|---------------|------------------------------------------------------------------------------------------------------------------------|

| SID84   | $V_{OFFSET1}$ | 入力オフセット電圧、工場出荷時トリム   | -   | -   | $\pm 10$       | mV            | -                                                                                                                      |

| SID85   | $V_{OFFSET2}$ | 入力オフセット電圧、カスタム トリム   | -   | -   | $\pm 4$        |               | -                                                                                                                      |

| SID86   | $V_{HYST}$    | 有効時のヒステリシス           | -   | 10  | 35             |               | -                                                                                                                      |

| SID87   | $V_{ICM1}$    | 通常モードでの入力同相電圧        | 0   | -   | $V_{DDD}-0.1$  | V             | モード 1 およびモード 2                                                                                                         |

| SID247  | $V_{ICM2}$    | 低消費電力モードでの入力同相電圧     | 0   | -   | $V_{DDD}$      |               | -                                                                                                                      |

| SID247A | $V_{ICM3}$    | 超低消費電力モードでの入力同相電圧    | 0   | -   | $V_{DDD}-1.15$ |               | 温度 $< 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 2.2\text{V}$ 、<br>温度 $> 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 1.8\text{V}$ |

| SID88   | $C_{MRR}$     | 同相信号除去比              | 50  | -   | -              | dB            | $V_{DDD} \geq 2.7\text{V}$                                                                                             |

| SID88A  | $C_{MRR}$     | 同相信号除去比              | 42  | -   | -              |               | $V_{DDD} \leq 2.7\text{V}$                                                                                             |

| SID89   | $I_{CMP1}$    | ブロック電流、通常モード         | -   | -   | 400            | $\mu\text{A}$ | -                                                                                                                      |

| SID248  | $I_{CMP2}$    | ブロック電流、低消費電力モード      | -   | -   | 100            |               | -                                                                                                                      |

| SID259  | $I_{CMP3}$    | ブロック電流、超低消費電力モード     | -   | -   | 28             |               | 温度 $< 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 2.2\text{V}$ 、<br>温度 $> 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 1.8\text{V}$ |

| SID90   | $Z_{CMP}$     | コンパレータの DC 入力インピーダンス | 35  | -   | -              | MΩ            | -                                                                                                                      |

**表 12. コンパレータの AC 仕様**

| 仕様 ID# | パラメーター | 説明                                | Min | Typ | Max | 単位            | 詳細／条件                                                                                                                  |

|--------|--------|-----------------------------------|-----|-----|-----|---------------|------------------------------------------------------------------------------------------------------------------------|

| SID91  | TRESP1 | 応答時間、通常モード、<br>50mV オーバードライブ      | -   | 38  | 110 | ns            | すべての $V_{DD}$                                                                                                          |

| SID258 | TRESP2 | 応答時間、低消費電力モード、<br>50mV オーバードライブ   | -   | 70  | 200 |               | -                                                                                                                      |

| SID92  | TRESP3 | 応答時間、超低消費電力モード、<br>200mV オーバードライブ | -   | 2.3 | 15  | $\mu\text{s}$ | 温度 $< 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 2.2\text{V}$ 、<br>温度 $> 0^{\circ}\text{C}$ の場合、 $V_{DDD} \geq 1.8\text{V}$ |

**表 13. 温度センサー仕様**

| 仕様 ID# | パラメーター   | 説明       | Min | Typ     | Max | 単位 | 詳細／条件         |

|--------|----------|----------|-----|---------|-----|----|---------------|

| SID93  | TSENSACC | 温度センサー精度 | -5  | $\pm 1$ | 5   | °C | -40°C ~ +85°C |

**表 14. SAR 仕様**