# Bluetooth® LE 接続を備えた PSoC™ 63 MCU

## 概要

PSoC™ 6 MCU は、IoT アプリケーション向けのに作られた、高性能、超低消費電力、およびセキュアな MCU プラットフォームです。PSoC™ 6 MCU プラットフォームに基づいて設計される Bluetooth® LE を備えた PSoC™ 63 製品ラインは、高性能マイクロコントローラーおよび低消費電力フラッシュ技術とデジタルプログラマブル ロジック、高性能アナログ - デジタル変換、および標準通信とタイミングペリフェラルの組合せです。

PSoC™ 63 製品ラインは、Bluetooth® LE 5.0 準拠のワイヤレス接続を提供します。

## 特長

- 32 ビット デュアル CPU サブシステム

- シングルサイクルの乗算、浮動小数点、およびメモリ保護ユニット (MPU) に対応した 150 MHz Arm® Cortex®-M4F CPU (CM4)

- シングルサイクルの乗算と MPU に対応した 100 MHz Cortex® M0+ CPU (CM0+)

- ユーザー選択可能なコアロジック動作 (1.1 V または 0.9 V)

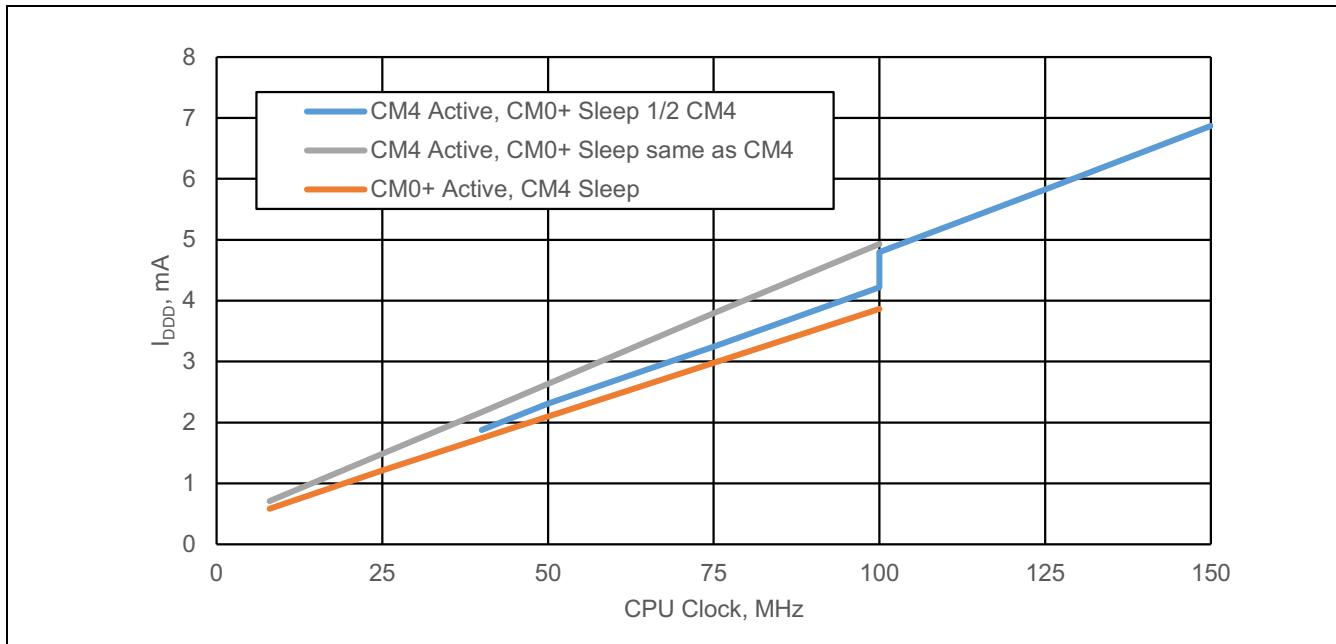

- 1.1 V コア動作のアクティブ CPU 電流勾配

- Cortex®-M4: 40 µA/MHz

- Cortex®-M0+: 20 µA/MHz

- 0.9V コア動作のアクティブ CPU 電流勾配

- Cortex®-M4: 22 µA/MHz

- Cortex®-M0+: 15 µA/MHz

- それぞれ 16 チャネルずつの 2 つの DMA コントローラー

- メモリ サブシステム

- 1 MB のアプリケーションフラッシュ、32 KB の補助フラッシュ (AUXflash)、および 32 KB の監視フラッシュ (SFlash)。読み出し時書き込み (RWW) のサポート。各 CPU に 1 つずつ、2 つの 8 KB フラッシュ キャッシュ。

- 電源およびデータ保持制御付き 288 KB SRAM

- ワンタイム プログラマブル (OTP) 1 Kb eFuse アレイ

- Bluetooth® Low Energy サブシステム

- 50Ω アンテナ駆動に対応する 2.4 GHz RF トランシーバー

- デジタル PHY

- マスターとスレーブ モードに対応した Link Layer エンジン

- 最大 4 dBm のプログラマブル TX パワー

- RX 感度 : -95 dBm

- RSSI: 4-dB 分解能

- 5.7 mA TX (0 dBm) と 6.7 mA RX (2 Mbps) 電流、3.3 V 電源および内部 SIMO 降圧コンバータを備える

- 4 つの接続を同時にサポートする Link Layer エンジン

- 2 Mbps データ速度をサポート

- 低消費電力 (1.7 V ~ 3.6 V) 動作

- 細かい電源管理用の 6 つの電源モード

- 64K SRAM 保持のディープスリープモード電流は 7 µA

- オンチップ Single In Multiple Out (SIMO) DC-DC 降圧コンバータ、1 µA 未満の静止電流

- 64 バイト メモリとリアルタイムクロックを備えるバックアップドメイン

- 柔軟な区ロッキング オプション

- ±2% 精度の 8 MHz 内部水晶発振器 (IMO)

- 超低電力 32 kHz 内部低速水晶発振器 (ILO)

## 特長

- オンチップ水晶発振器 (16 ~ 35 MHz および 32 kHz)

- クロック周波数遅倍用の位相ロック ループ (PLL)

- IMO 周波数遅倍用の周波数ロック ループ (FLL)

- 整数および小数のペリフェラルクロック分周器

- Quad SPI (QSPI)/シリアルメモリインターフェース (SMIF)

- 外部クアッド SPI フラッシュから直接実行 (XIP)

- オンザフライの暗号化と復号化

- 低い消費電力で XIP 性能を向上させる 4 KB のキヤッショ

- 最大 640 Mbps のスループットのシングル, デュアル, クアッド, デュアル-クアッド, およびオクタルイ ンターフェースに対応。

- セグメント LCD ドライブ

- 最大 83 セグメントと最大 8 コモンに対応

- シリアル通信

- 9 個の実行時再設定可能なシリアル通信ブロック (SCB)

- 8 SCB: SPI, I<sup>2</sup>C, または UART として設定可能

- 1 ディープスリープ SCB: SPI または I<sup>2</sup>C として設定可能

- USB フルスピード デバイスインターフェース

- オーディオサブシステム

- パルス密度変調 (PDM) チャネル 2 本と時分割多重 (TDM) モード付き I<sup>2</sup>S チャネル 1 本

- タイミングおよびパルス幅変調

- 32 個のタイマー / カウンター / パルス幅変調器 (TCPWM)

- 中央揃え, エッジ, および疑似乱数モード

- Kill 信号のコンパレータベースのトリガー

- プログラマブルアナログ

- 差動とシングルエンド モードおよび信号加算平均に対応したチャネルシーケンサを備えた 12 ビット の 1 Msps SAR ADC

- ディープスリープ モードおよびハイバネート モードで動作する 2 個の低消費電力コンパレータ

- ADC に接続される内蔵の温度センサー

- セトリング時間が 2 μs 未満の 1 個の 12 ビット電圧モードデジタル - アナログコンバータ (DAC)

- 低消費電力動作モードの 2 個のオペアンプ

- 最大 84 個のプログラマブル GPIO

- GPIO ピン上でブール演算を可能にする 2 つの Smart I/O ポート (16 I/O)。システムディープスリープ モード中に実行可能

- プログラム可能な駆動モード, 駆動強度, およびスルーレート

- 6 本の過電圧耐性 (OVT) ピン

- 静電容量センシング

- クラス最高の信号対ノイズ比 (SNR), 耐水性, および近接センシングを提供する CAPSENSE™

- 自己容量と相互容量の両方を動的に使用可能

- 自動のハードウェアチューニング (SmartSense)

- プラットフォームアーキテクチャに組み込まれたセキュリティ

- 無停電「Secure Boot」経由の ROM ベースの信頼のルート

- 実行イメージの段階的認証

- 保護された実行専用モードでのコードの安全な実行ルーチン

- すべてのデバッグおよびテスト入力パスを無効化可能

- 最大 8 つの保護コンテキスト

- 暗号化アクセラレータ

## 特長

- 対称および非対称暗号メソッドおよびハッシュ関数のハードウェアアクセラレーション

- 真の乱数生成器 (TRNG) 機能

- プログラマブルデジタル

- 12個のプログラマブルロジックブロック、それぞれに 8つのマクロセルと 1つの 8ビットデータパス (ユニバーサルデジタルブロック (UDB) と呼ばれる)

- ドラッグアンドドロップブールプリミティブ(ゲート, レジスタ)、または Verilog プログラマブルブロックとして使用可能

- UDB を使用した通信ペリフェラル(例えば、LIN, UART, SPI, I<sup>2</sup>C, S/PDIF およびその他のプロトコル), 波形ジェネレータ, 疑似ランダムシーケンス (PRS) 生成、およびその他多くの機能を備えたインフィニオン提供のペリフェラルコンポーネントライブラリ

- プロファイラー

- 8つのカウンターが、イベントまたはオンチップリソースの期間の監視を提供

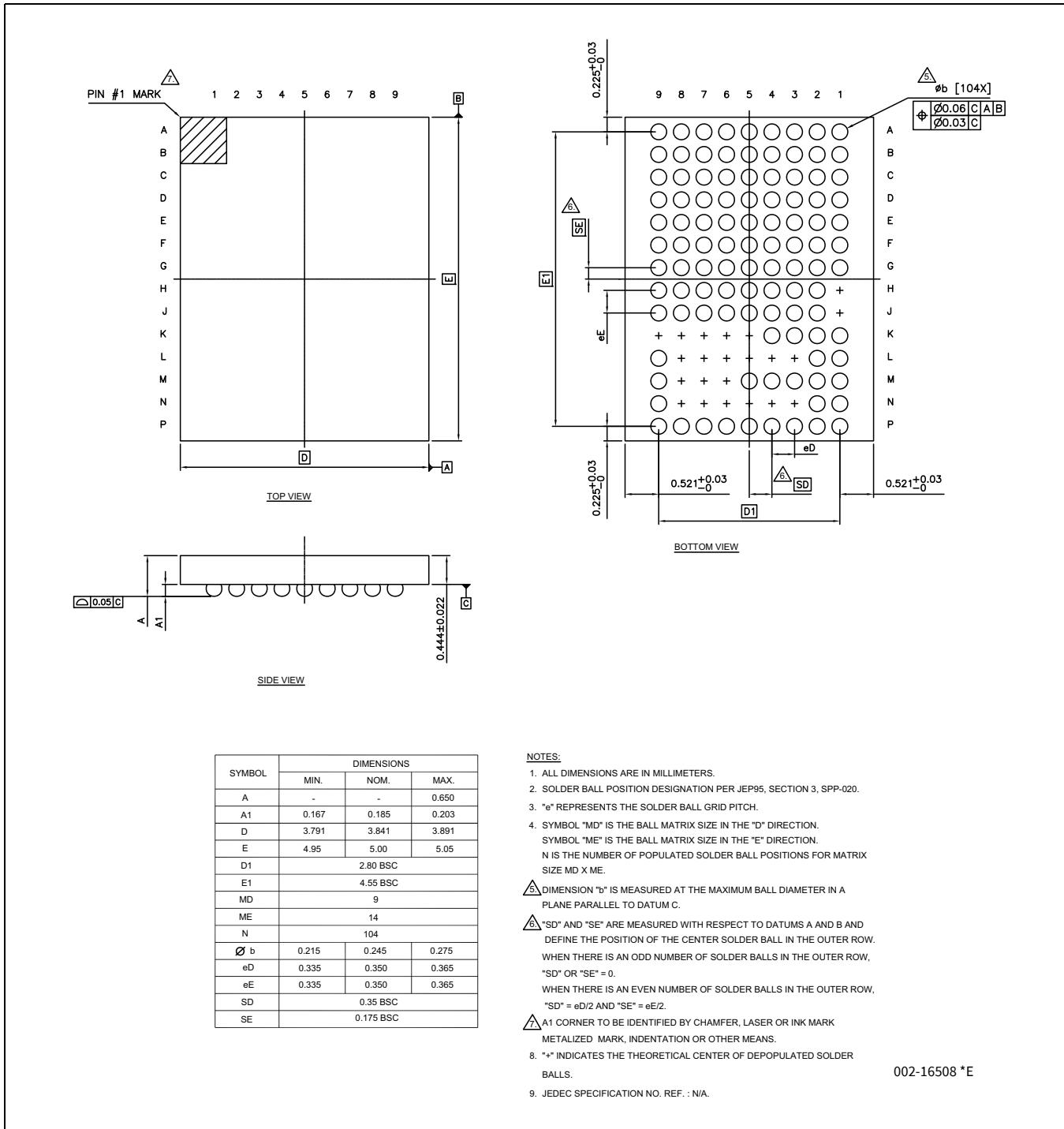

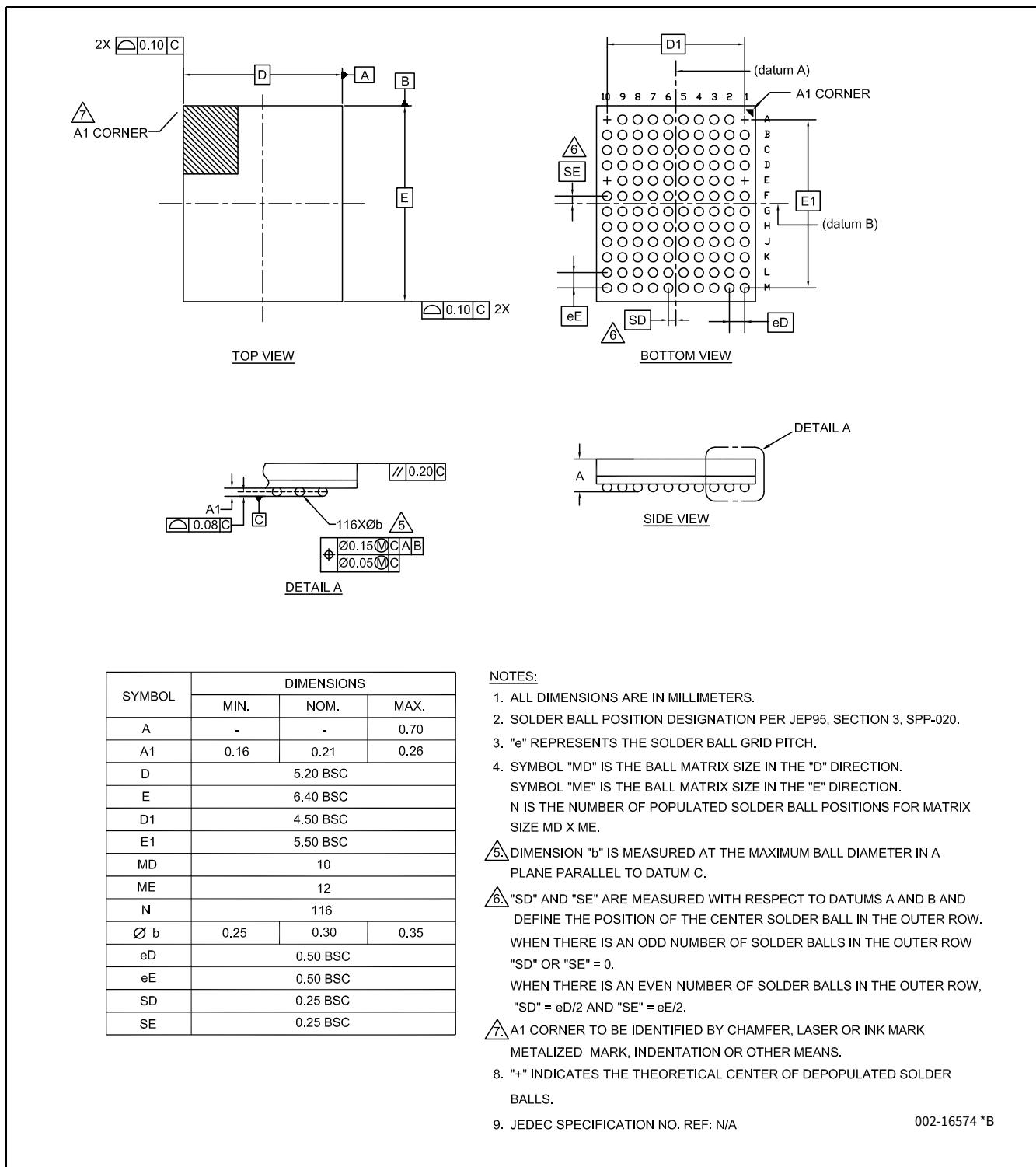

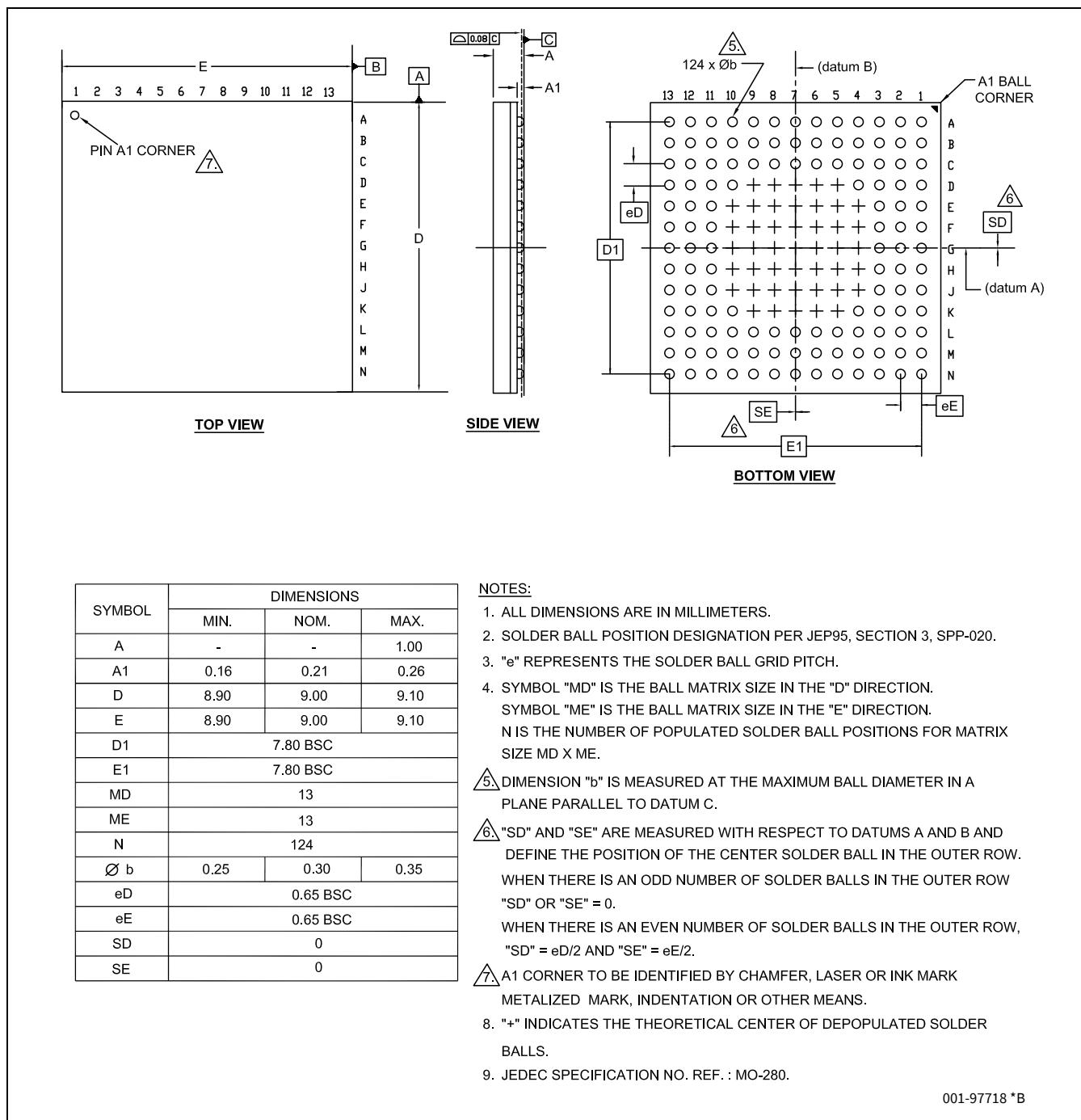

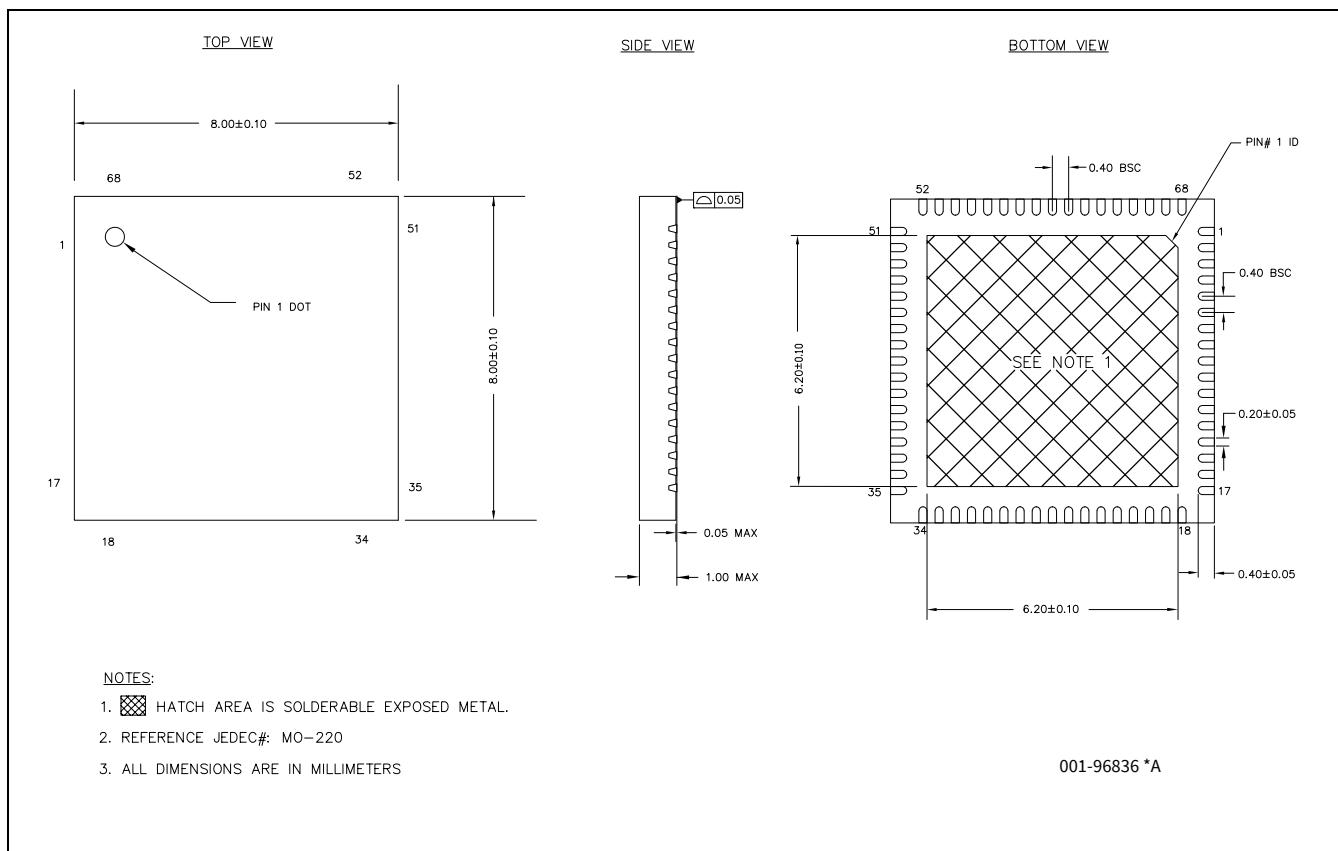

- パッケージ

- USB を備えた 124-BGA および 104-M-CSP

- USB の無い 116-BGA, 104-M-CSP, および 68-QFN

- デバイスの識別およびリビジョン

- 製品ライン ID (12ビット): 0x100

- メジャー /マイナーダイリビジョン ID: 2/4

- フームウェアリビジョン: Rom ブート: 4.1, Flash ブート: 1.20.1.45 ([ブートコードセクション](#)を参照してください。)

- この製品ラインには、SWJ インターフェースを介して利用できる JTAG ID があります。これは 32 ビット ID で、以下のとおりです。

- 最上位桁は、メジャー ダイリビジョンに基づいたデバイス リビジョンです。

- 次の 4 衡は、製品番号に対応します。(例: 16 進数の「E4B0」)

- 最下位 3 衡はメーカー ID です。この場合、16 進数の「069」です。

- シリコン ID システムコールは、ファームウェアでシリコン ID および ROM ブートデータを取得するために使用できます。詳細については、[technical reference manual \(TRM\)](#) を参照してください。

- Flash ブートバージョンは、指定されたアドレス 0x1600 2004 から直接読み出せます。詳細については、[technical reference manual \(TRM\)](#) を参照してください。

## 目次

## 目次

|                                              |    |

|----------------------------------------------|----|

| <b>概要</b>                                    | 1  |

| <b>特長</b>                                    | 1  |

| <b>目次</b>                                    | 4  |

| <b>1 Development ecosystem</b>               | 6  |

| 1.1 PSoC™ 6 MCU resources                    | 6  |

| 1.2 ModusToolbox™ Software                   | 7  |

| 1.3 PSoC™ Creator                            | 8  |

| <b>2 ブロックおよび機能</b>                           | 9  |

| <b>3 機能の説明</b>                               | 11 |

| 3.1 CPU およびメモリ サブシステム                        | 12 |

| 3.1.1 CPU                                    | 12 |

| 3.1.2 割込み                                    | 13 |

| 3.1.3 プロセッサ間通信 (IPC)                         | 13 |

| 3.1.4 DMA コントローラー                            | 13 |

| 3.1.5 暗号化アクセラレータ (暗号化)                       | 13 |

| 3.1.6 保護ユニット                                 | 14 |

| 3.1.7 メモリ                                    | 14 |

| 3.1.8 ブートコード                                 | 15 |

| 3.1.9 メモリ マップ                                | 16 |

| 3.2 システム リソース                                | 17 |

| 3.2.1 電源システム                                 | 17 |

| 3.2.2 電力モード                                  | 17 |

| 3.2.3 クロックシステム                               | 17 |

| 3.2.4 内部主発振器 (IMO)                           | 18 |

| 3.2.5 内部低速発振器 (ILO)                          | 18 |

| 3.2.6 高精度 ILO (PILO)                         | 18 |

| 3.2.7 外部水晶発振器                                | 19 |

| 3.2.8 ウオッチドッグ タイマー (WDT, MCWDT)              | 19 |

| 3.2.9 クロック分周器                                | 19 |

| 3.2.10 トリガールーティング                            | 20 |

| 3.2.11 リセット                                  | 20 |

| 3.3 Bluetooth® LE 無線およびサブシステム                | 20 |

| 3.4 プログラマブル アナログ サブシステム                      | 22 |

| 3.4.1 12ビット SAR ADC                          | 22 |

| 3.4.2 温度センサー                                 | 22 |

| 3.4.3 12ビットのデジタル アナログ変換器                     | 22 |

| 3.4.4 2個のオペアンプのある連続時間ブロックミニ (CTBm)           | 22 |

| 3.4.5 低消費電力コンパレータ                            | 23 |

| 3.5 プログラマブル デジタル                             | 25 |

| 3.5.1 Smart I/O                              | 25 |

| 3.5.2 ユニバーサル デジタル ブロック (UDB)                 | 25 |

| 3.6 固定機能デジタル                                 | 26 |

| 3.6.1 タイマー/カウンター/パルス幅変調器 (TCPWM) ブロック        | 26 |

| 3.6.2 シリアル通信ブロック (SCB)                       | 26 |

| 3.6.3 USB 12 Mbps device interface           | 27 |

| 3.6.4 QSPI インターフェース シリアル メモリ インターフェース (SMIF) | 27 |

| 3.6.5 LCD                                    | 27 |

| 3.7 GPIO                                     | 28 |

| 3.8 特殊機能ペリフェラル                               | 29 |

| 3.8.1 オーディオ サブシステム                           | 29 |

| 3.8.2 CAPSENSE™ サブシステム                       | 29 |

## 目次

|                         |     |

|-------------------------|-----|

| <b>4 ピン配置</b>           | 33  |

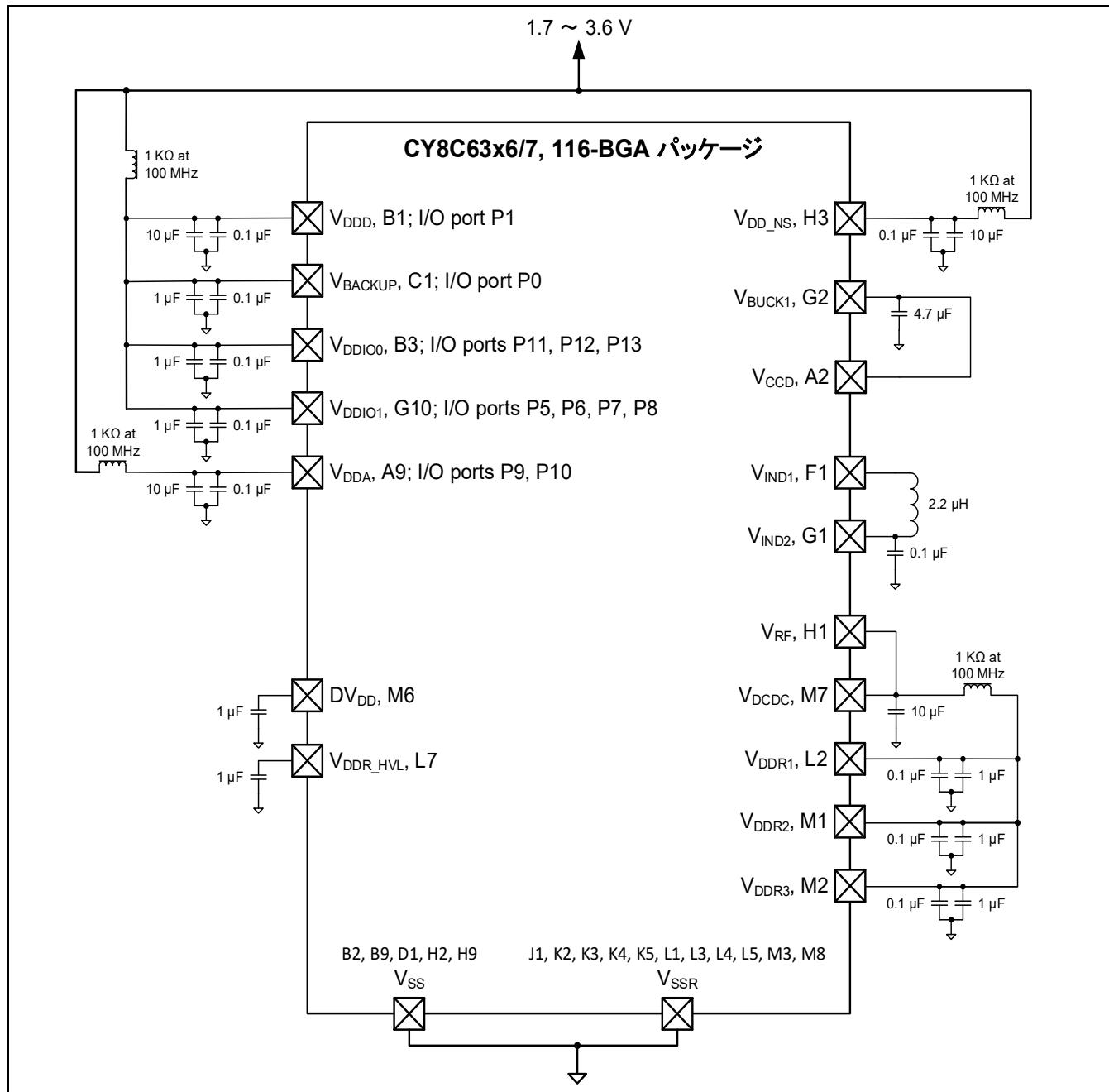

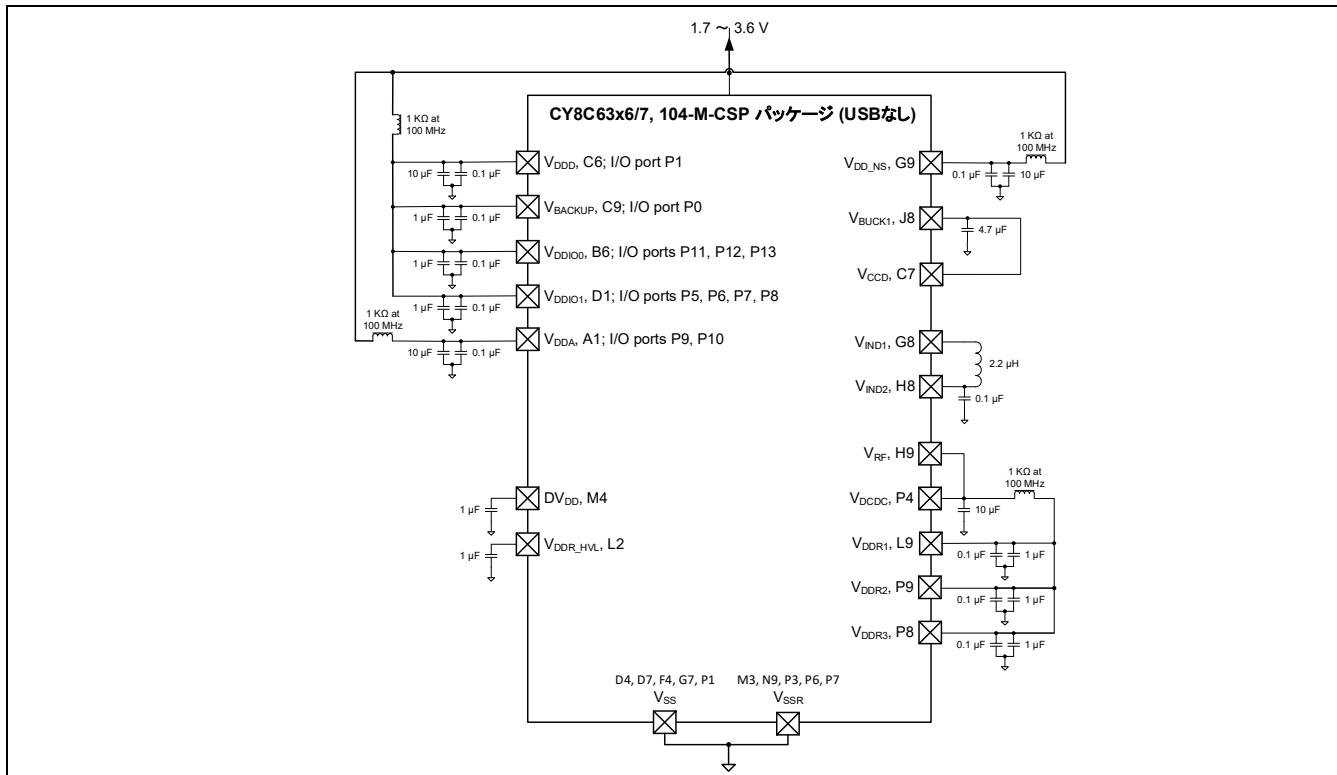

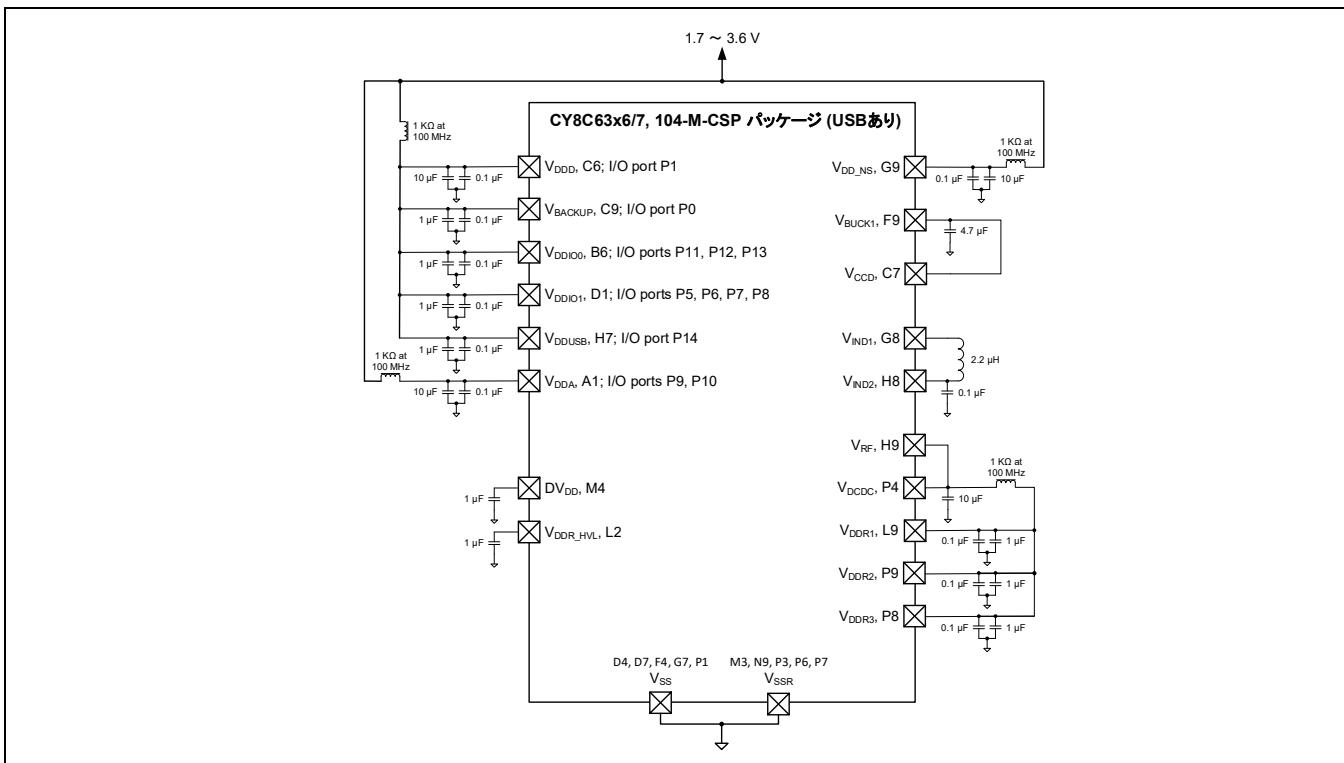

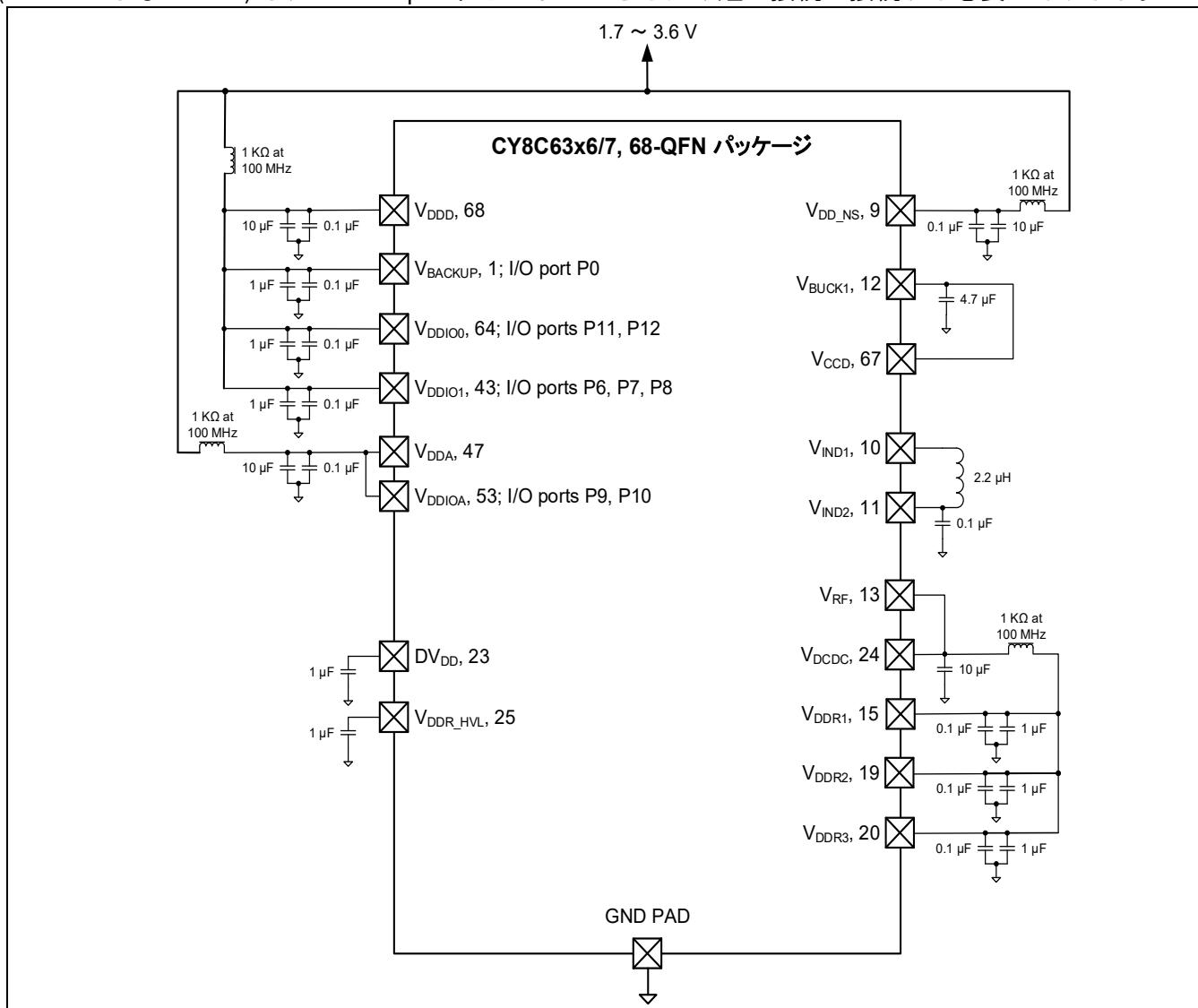

| <b>5 電源に関する考慮事項</b>     | 47  |

| <b>6 電気的仕様</b>          | 53  |

| 6.1 絶対最大定格              | 53  |

| 6.2 デバイスレベルの仕様          | 53  |

| 6.2.1 電源                | 54  |

| 6.2.2 CPU 電流および遷移時間     | 55  |

| 6.2.3 XRES              | 61  |

| 6.2.4 GPIO              | 61  |

| 6.3 アナログペリフェラル          | 63  |

| 6.3.1 オペアンプ             | 63  |

| 6.3.2 低消費電力(LP) コンパレータ  | 67  |

| 6.3.3 SAR ADC           | 68  |

| 6.3.4 DAC               | 70  |

| 6.3.5 CSD               | 70  |

| 6.4 デジタルペリフェラル          | 75  |

| 6.4.1 LCD の仕様           | 77  |

| 6.5 メモリ                 | 78  |

| 6.5.1 フラッシュ             | 78  |

| 6.6 システムリソース            | 79  |

| 6.6.1 パワーオンリセット         | 79  |

| 6.6.2 電源モニター            | 79  |

| 6.6.3 SWD および配線インターフェース | 80  |

| 6.6.4 内部主発振器            | 80  |

| 6.6.5 内部低速発振器           | 80  |

| 6.6.6 水晶発振器             | 81  |

| 6.6.7 外部クロック            | 81  |

| 6.6.8 PLL               | 81  |

| 6.6.9 クロックソースの切替え時間の仕様  | 81  |

| 6.6.10 FLL              | 82  |

| 6.6.11 UDB              | 82  |

| 6.6.12 USB              | 84  |

| 6.6.13 QSPI             | 84  |

| 6.6.14 オーディオサブシステム      | 85  |

| 6.6.15 Smart I/O        | 87  |

| 6.6.16 高精度ILO(PILO)     | 87  |

| 6.6.17 JTAG バウンダリースキャン  | 87  |

| 6.7 Bluetooth® LE       | 88  |

| <b>7 注文情報</b>           | 93  |

| 7.1 PSoC™ 6 MPN コード説明   | 94  |

| <b>8 パッケージ</b>          | 95  |

| <b>9 略語</b>             | 100 |

| <b>10 本書の表記法</b>        | 104 |

| 10.1 測定単位               | 104 |

| 改訂履歴                    | 105 |

| 免責事項                    | 106 |

## 1 Development ecosystem

### 1.1 PSoC™ 6 MCU resources

インフィニオンは、[www.infineon.com](http://www.infineon.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC™ デバイスを選択し、迅速かつ効率的にデザインに統合する手助けをします。以下は PSoC™ 6 MCU のリソースの要約です。

- **概要 : PSoC™ ポートフォリオ , PSoC™ ロードマップ**

- **製品セレクタ : PSoC™ 6 MCU**

- **Application notes** : 基本レベルから上級レベルまでの幅広いトピックを提供します。

- [AN221774](#): Getting Started with PSoC™ 6 MCU

- [AN210781](#): Getting Started with PSoC™ 6 MCU with Bluetooth® Low Energy Connectivity

- [AN218241](#): PSoC™ 6 MCU Hardware Design Guide

- [AN213924](#): PSoC™ 6 MCU Device Firmware Update Guide

- [AN215656](#): PSoC™ 6 MCU Dual-CPU System Design

- [AN219528](#): PSoC™ 6 MCU Power Reduction Techniques

- [AN221111](#): PSoC™ 6 MCU Creating a Secured System

- [AN85951](#): PSoC™ 4, PSoC™ 6 MCU CAPSENSE™ Design Guide

- **サンプルコード** : 製品の機能と使用法を示します。[Infineon GitHub repositories](#) からも利用可能です。

- **テクニカルリファレンスマニュアル (TRM)** : アーキテクチャとレジスタの詳細な説明をします。

- **PSoC™ 6 MCU Programming Specification** : PSoC™ 6 MCU 不揮発性メモリのプログラムに必要な情報を提供します。

- **開発ツール**

- **ModusToolbox™** ソフトウェア : しっかりと一体化されたツールとソフトウェアライブラリによって、クロスプラットフォームコードの開発が可能です。

- **CY8CKIT-062-BLE** - PSoC™ 6-Bluetooth® LE Pioneer Kit: PSoC™ 63 Bluetooth® LE 製品群の設計とデバッグを可能にするハードウェアプラットフォーム。

- **CY8CPROTO-063-BLE** - PSoC™ 6-Bluetooth® LE Prototyping Kit: スナップアウェイフォームファクターを備えた低コストの PSoC™ 63-Bluetooth® LE キット。

- **PSoC™ 6 CAD libraries** は、一般的なツールに対応したフットプリントと回路図を提供します。**BSDL files** および **IBIS models** も使用できます。

- **トレーニングビデオ : PSoC™ 6 MCU 101 シリーズ** を含む、幅広いトピックを提供します。

- **Infineon Developer Community** : 世界中の PSoC™ 開発者と常時連絡 / 情報交換が可能です。**PSoC™ 6 MCU の専用コミュニティ** もあります。

## 1.2 ModusToolbox™ Software

**ModusToolbox™ Software** は、インフィニオンのマルチプラットフォームツールとソフトウェアライブラリの包括的なコレクションであり、統合された MCU とワイヤレスシステムを作成するための没入型開発エクスペリエンスを可能にします。以下のとおりです。

- ・ 包括的 - 必要なリソースがあります。

- ・ 柔軟性 - 独自のワークフローでリソースを使用できます

- ・ アトミック - 必要なリソースだけを取得できます

インフィニオンは、[repositories on GitHub](#) の大規模なコレクションを提供しています。これは以下を含みます。

- ・インフィニオンキットと連携したボードサポートパッケージ (BSP)

- ・ハードウェアアブストラクションレイヤー (HAL) やペリフェラルドライバーライブラリ (PDL) などの低レベルのリソース

- ・CAPSENSE™, Bluetooth® Low Energy, およびメッシュネットワークなどの業界をリードする機能を可能にするミドルウェア

- ・徹底的にテストされた **code example applications** 広範なセット

**注:** HAL は、インフィニオン MCU のハードウェアブロックを構成および使用するための高レベルで簡素化されたインターフェースを提供します。これは、複数の製品ファミリで使用できる汎用インターフェースです。例えば、PSoC™ 6 PDL を簡略化された API でラップしますが、PDL はすべての低レベルの周辺機能を公開します。一部の部分でよりきめ細かい制御が必要な場合でも、ほとんどのアプリケーションで HAL のよりシンプルで汎用的なインターフェースを活用できます。

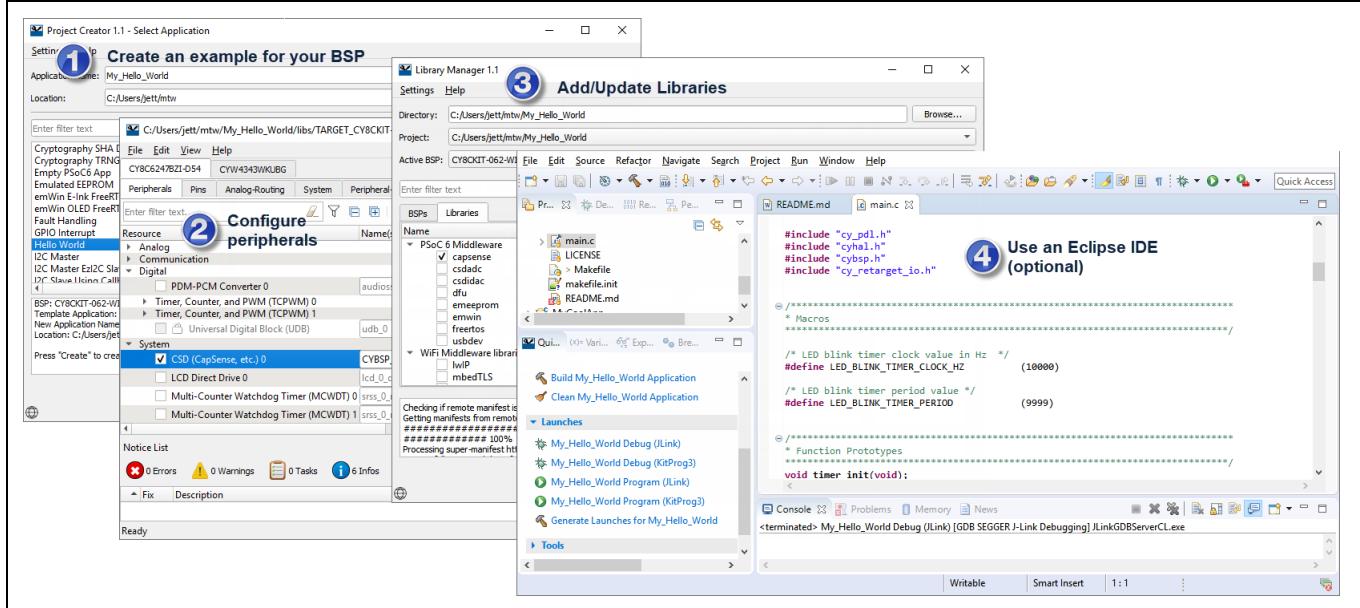

ModusToolbox™ ソフトウェアは IDE に依存せず、ワークフローや推奨される開発環境に簡単に適応できます。[Figure 1](#) に示すように、プロジェクトクリエーター、ペリフェラルおよびライブラリコンフィギュレーター、ライブラリマネージャー、および ModusToolbox™ 用のオプションの Eclipse IDE が含まれます。インフィニオンツールの使用については、ModusToolbox™ ソフトウェアに付属のドキュメントおよび [AN228571: Getting Started with PSoC™ 6 MCU on ModusToolbox™](#) を参照してください。

**Figure 1** ModusToolbox™ ソフトウェアツール

### 1.3 PSoC™ Creator

**注 : PSoC™ Creator は新規の設計には推奨されません。**

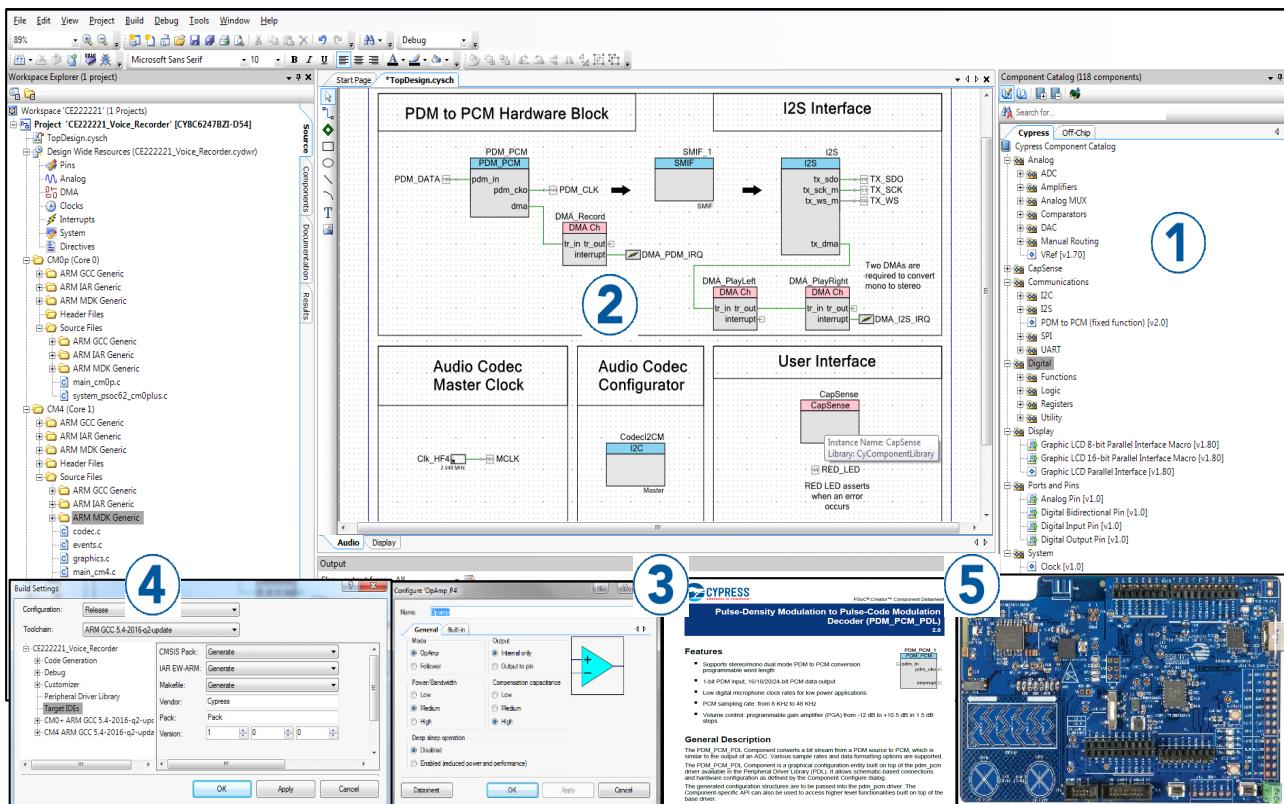

PSoC™ Creator は無料で利用できる Windows ベースの統合設計環境 (IDE) です。このツールにより、お客様は PSoC™ 6 MCU のハードウェアとファームウェアシステムを同時に設計できます。Figure 2 に PSoC™ Creator でできることを示します。

1. 200 以上のコンポーネントを含むライブラリを利用

2. コンポーネントをドラッグ アンド ドロップして、メインデザインワークスペースでハードウェアシステム デザインを構築

3. コンポーネント コンフィギュレーション ツールおよびコンポーネント データシートを使ってコンポーネントを設定

4. PSoC™ Creator IDE でアプリケーションファームウェアとハードウェアを相互設計するか、またはサードパーティ IDE でのプロジェクトを構築

5. PSoC™ 6 Pioneer Kits でソリューションのプロトタイプを設計。設計変更が必要な場合、PSoC™ Creator およびそのコンポーネントにより、ハードウェアを改訂せずその場で変更を行えます。

Figure 2 PSoC™ Creator の回路図入力およびコンポーネント

## ブロックおよび機能

## 2 ブロックおよび機能

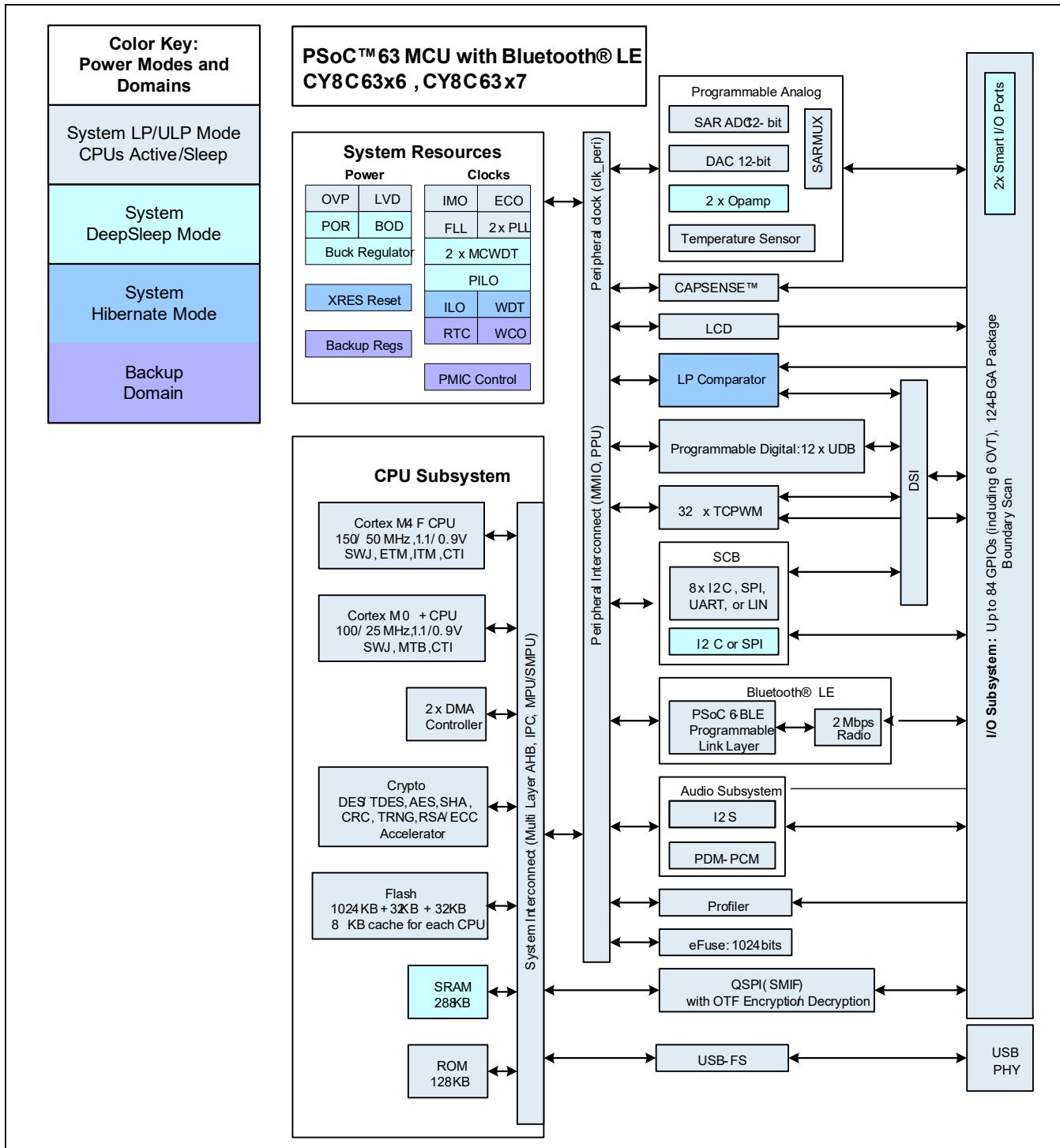

主なサブシステムとそれらの相互接続の簡略図を **Figure 3** に示します。色分けはブロックがまだ機能している最低限の消費電力モードを示します。例えば SRAM はディープスリープモードまで機能します。

**Figure 3** ブロック ダイヤグラム

## ブロックおよび機能

3つのデバッグアクセスポートがあり、それぞれが CM4 と CM0+、およびシステムポート用です。PSoC™ 6 MCU デバイスは、プログラミング、テスト、デバッグ、およびハードウェアとファームウェアの両方のトレースに対する広範なサポートを含みます。再プログラミングされたデバイスまたはフラッシュプログラミングシーケンスの開始と中断を懸念されるアプリケーションでは、すべてのデバイスインターフェースを永続的に無効にできます。すべてのプログラミング、デバッグ、およびテストインターフェースを無効にできます。

デバッグオンチップ機能により、標準の量産デバイスを使用した最終システムでデバイスの完全なデバッグ処理が可能です。専用のインターフェースやデバッギング ポッド、シミュレータ、エミュレータは不要です。デバッグをサポートするために必要なものは、通常のプログラミングに使う接続だけです。

ModusToolbox™ の Eclipse IDE および PSoC™ Creator<sup>[1]</sup> 統合開発環境 (IDE) は、これらのデバイスに完全に統合されたプログラミングおよびデバッグサポートを提供します。SWJ (SWD および JTAG) インターフェースは、業界標準のサードパーティ製プロープと完全に互換性があります。PSoC™ 6 は、デバッグ機能を無効にする機能、非常に堅牢なフラッシュ保護、およびオンチップのプログラマブルブロックにお客様独自の機能を実装できるようにすることで、複数レベルのデバイスセキュリティを提供します。

## 注

1. PSoC™ Creator は新規の設計には推奨されません。

## 機能の説明

### 3 機能の説明

**Figure 3** のブロックダイヤグラムに示されている各機能ブロックの特長、機能、および動作の概要を説明します。詳細については、以下の文書を参照してください。

- Board Support Package (BSP) Documentation

BSP は [GitHub](#) で入手できます。これらはインフィニオンキットと連携しており、ハードウェア構成ファイル、スタートアップコード、リンクーファイルなどの基本的なデバイス機能用のファイルを提供します。BSP には、キットをサポートするために必要な他のライブラリも含まれています。各 BSP には独自のドキュメントがありますが、通常、[here](#) の例のような API リファレンスが含まれています。この [検索リンク](#) では、インフィニオン GitHub サイトで現在利用可能なすべての BSP を検索できます。

- Hardware Abstraction Layer API Reference Manual

Hardware Abstraction Layer (HAL) は、インフィニオン MCU でハードウェアブロックを設定および使用するための高レベルのインターフェースを提供します。これは、複数の製品ファミリで使用できる汎用インターフェースです。一部の部分でよりきめ細かい制御が必要な場合でも、ほとんどのアプリケーションで HAL のよりシンプルで汎用的なインターフェースを活用できます。[HAL API Reference](#) には、完全な詳細が記載されています。HAL を使用するサンプルアプリケーションは、GitHub リポジトリから HAL を自動的にダウンロードします。

- Peripheral Driver Library (PDL) Application Programming Interface (API) Reference Manual

Peripheral Driver Library (PDL) は、デバイスヘッダーファイルと周辺機器ドライバーを 1 つのパッケージに統合し、すべての PSoC™ 6 MCU 製品ラインをサポートします。ドライバーは、ハードウェア関数を一連の使いやすい API に抽象化します。これらは、[PDL API Reference](#) に完全に文書化されています。PSoC™ 6 PDL を使用するサンプルアプリケーションは、GitHub リポジトリから PSoC™ 6 PDL を自動的にダウンロードします。

- Architecture Technical Reference Manual (TRM)

Architecture TRM は、デバイス内の各リソースを詳細に説明します。PDL が提供するソフトウェアで制御されたハードウェアの動作を理解する必要がある場合、2 つ目のリファレンスとして使用してください。各リソースのアーキテクチャと機能を説明し、すべてのモードでの各リソースの動作を説明します。関連するレジスタの使用に関する具体的なガイダンスを提供します。

- Register Technical Reference Manual

Register TRM は、デバイス内にあるすべてのレジスタの詳細なリストを提供します。すべてのレジスタフィールドの内訳、可能な設定、読み出し / 書き込みのアクセス可能性、およびデフォルトの状態が含まれます。一般的なアプリケーションで適切に使用されるすべてのレジスタには、PDL 内からそれらにアクセスする機能があります。ModusToolbox™ と PDL は一部のレジスタに対して、ハードウェアのデフォルトとは異なるソフトウェアのデフォルト条件を上書きする場合があることに注意してください。

## 機能の説明

### 3.1 CPU およびメモリサブシステム

**Figure 3** に示すように、PSoC™ 6 には複数のバスマスターがあります。それらは、CPU, DMA コントローラ, QSPI, USB, および暗号ブロックです。一般に、多層 Arm® AMBA 高性能バス (AHB) アービトレーションを介して、すべてのバスマスターがすべてのメモリと周辺機器にアクセスして共有できます。CPU 間のアクセスは、プロセッサ間通信 (IPC) ブロックを使用して同期できます。

#### 3.1.1 CPU

2つの Arm® Cortex® CPU があります。

Cortex®-M4 (CM4) には、シングルサイクル乗算, 浮動小数点ユニット (FPU), およびメモリ保護ユニット (MPU) があります。最大 150 MHz で実行できます。これは、短い割込み応答時間, 高いコード密度, および高いスループットのために設計されたメイン CPU です。

CM4 は、Thumb-2 テクノロジ ([Armv7-M Architecture Reference Manual](#) で定義) に基づいた Thumb 命令セットのバージョンを実装します。

Cortex®-M0+ (CM0+) には、シングルサイクル乗算と MPU があります。最大 100 MHz で実行できます。ただし、100 MHz を超える CM4 速度の場合、CM0+ およびバス周辺機器は CM4 の半分の速度に制限されます。したがって、150 MHz で動作する CM4 の場合、CM0+ および周辺機器はシステム低消費電力 (LP) モードでは 75 MHz に制限されます。システム超低消費電力 (ULP) モードでは CPU 速度はそれぞれ 50 MHz および 25 MHz に制限されます。

CM0+ はセカンダリ CPU です。システムコールとデバイスレベルの安全性および保護機能を実装するために使用されます。CM0+ は、安全で中断のないブート機能を提供します。これにより、起動後、システムの整合性がチェックされ、メモリおよび周辺機器のアクセス権限が適用されます。

CM0+ は Armv6-M Thumb 命令セットを実装します ([Armv6-M Architecture Reference Manual](#) で定義されます)。

CPU には、 $V_{DDD} = 3.3 \text{ V}$  で、内部降圧レギュレータを使用した以下の電力消費があります。

**Table 1 内部降圧レギュレータを使用した  $V_{DDD} = 3.3 \text{ V}$  でのアクティブ電流勾配**

| CPU | システム電源モード   |           |           |

|-----|-------------|-----------|-----------|

|     | ULP         |           | LP        |

|     | Cortex®-M0+ | 15 μA/MHz |           |

|     | Cortex®-M4  | 22 μA/MHz | 40 μA/MHz |

この CPU は、Arm® で定義されているスリープモードとディープスリープモードに選択的に配置できます。両方の CPU には、高速で確定的な割込み応答のためのネストされたベクトル割込みコントローラー (NVIC) と、ディープスリープ電源モードからの CPU ウェイクアップのためのウェイクアップ割込みコントローラー (WIC) があります。

この CPU は広範なデバッグをサポートします。PSoC™ 6 には、デバイスのプログラミングとデバッグのインターフェースとして機能するデバッグアクセスポート (DAP) があります。外部プログラマーまたはデバッガー（「ホスト」）は、デバイスのシリアルワイヤデバッグ (SWD) またはジョイントテストアクションループ (JTAG) インターフェースピンを介して DAP と通信します。DAP (および制限の対象) を介して、ホストはデバイスのメモリと周辺機器、および両方の CPU のレジスタにアクセスできます。

各 CPU は、次のデバッグおよびトレース機能を提供します。

- CM4 は、6 つのハードウェアブレークポイントと 4 つのウォッチポイント、4 ビット埋め込みトレースマクロセル (ETM)、シリアルワイヤビューアー (SWV)、およびシングルワイヤ出力 (SWO) ピンを介した printf() スタイルのデバッグをサポートします。

- CM0+ は、4 つのハードウェアブレークポイントと 2 つのウォッチポイント、および 4 KB の専用 RAM を備えたマイクロトレースバッファ (MTB) をサポートします。

PSoC™ 6 には、両方の CPU のデバッグとトレースを同期するための組込みクロストリガーもあります。

## 機能の説明

### 3.1.2 割込み

この製品ラインには 147 のシステムおよび周辺割込みソースがあり、両方の CPU で割込みとシステム例外をサポートします。CM4 には 147 の割込み要求ライン (IRQ) があり、割込みソース「n」は IRQn に直接接続されます。CM0+ には 32 個の割込み IRQ [31:0] があり、1 つのシステム割込みソースを IRQ [31:0] のいずれかに設定可能なマッピングがあります。

各割込みは、設定可能な優先度レベルをサポートします (CM4 では 8 レベル、CM0+ では 4 レベル)。1 つのシステム割込みは、CPU のマスク不能割込み (NMI) のそれぞれにマッピングできます。最大 41 個の割込みソースが、WIC を使用してデバイスをディープスリープパワーモードからウェイクアップできます。詳細については、[technical reference manual](#) を参照してください。

### 3.1.3 プロセッサ間通信 (IPC)

Arm® SEV および WFE 命令に加えて、ハードウェアプロセッサ間通信 (IPC) ブロックが含まれます。これには、16 個の IPC チャネルと 16 個の IPC 割込み構造が含まれます。IPC チャネルは、プロセッサ間のデータ通信を実装するために使用できます。各 IPC チャネルは、共有リソースの管理に使用できるロックスキームも実装しています。IPC 割込みにより、一方のプロセッサが他方のプロセッサに割り込み、イベントを通知します。これは、対応する IPC チャネルの通知や解放などのイベントをトリガーするために使用されます。[Table 2](#) に示すように、一部の IPC チャネルおよびその他のリソースは予約されています。

**Table 2 IPC チャネルおよびその他のリソースの分配**

| 利用可能なリソース                    | 消費されたリソース            |

|------------------------------|----------------------|

| IPC チャネル , 16 個利用可能          | 8 個予約済み              |

| IPC 割込み , 16 個利用可能           | 8 個予約済み              |

| 他の割込み                        | 1 個予約済み              |

| CM0+ NMI                     | 予約済み                 |

| 他のリソース : クロック分周器 , DMA チャネル等 | 1 個の CM0+ 割込みマルチプレクサ |

### 3.1.4 DMA コントローラー

それぞれ 16 チャネルの 2 つの DMA コントローラーがあり、メモリと周辺機器への CPU に依存しないアクセスをサポートします。DMA チャネルのディスクリプタは、SRAM またはフラッシュ内にあります。したがって、ディスクリプタの数はメモリのサイズによってのみ制限されます。各ディスクリプタは、設定可能なアドレス増分を使用して、ソースおよび宛先に 2 つのネストされたループでデータを転送できます。ディスクリプタごとのデータ転送のサイズは、DMA チャネルのタイプによって異なります。詳細については、[technical reference manual](#) を参照してください。

### 3.1.5 暗号化アクセラレータ (暗号化)

このサブシステムは、ハードウェアの実装と、暗号化機能と乱数生成器の高速化で構成されます。

暗号化サブシステムは次をサポートします。

- 暗号化 / 複合化機能

- データ暗号化基準 (DES)

- トリプル DES (3DES)

- Advanced Encryption Standard (AES) (128 ビット , 192 ビット , 256 ビット )

- 楕円曲線暗号 (ECC)

- RSA 暗号化機能

- ハッシュ機能

- セキュアハッシュアルゴリズム (SHA)

- SHA-1

- SHA-224/-256/-384/-512

- メッセージ認証機能 (MAC)

- ハッシュメッセージ認証コード (HMAC)

- 暗号ベースのメッセージ認証コード (CMAC)

## 機能の説明

- 32 ビットの巡回冗長コード (CRC) 生成器

- 亂数生成器

- 疑似乱数生成器 (PRNG)

- 真の乱数生成器 (TRNG)

### 3.1.6 保護ユニット

この製品ラインには、メモリおよび周辺レジスタへの誤ったまたは不正なアクセスを制御するための複数のタイプの保護ユニットがあります。CM4 および CM0+ には、バスマスターレベルでの保護のための ArmR MPU があります。他のバスマスターは追加の MPU を使用します。共有メモリ保護ユニット (SMPU) は、複数のバスマスター間で共有されるメモリリソースのメモリ保護の実装に役立ちます。周辺保護ユニット (PPU) は SMPU に似ていますが、周辺レジスタ空間を保護するために設計されています。

保護ユニットは、アドレス範囲、読み出し / 書き込み、コード / データ、特権レベル、保護 / 非保護、保護コンテキストなどのメモリおよび周辺機器アクセス属性をサポートします。

一部の保護ユニットリソースは、システム使用のために予約されています。詳細については、[technical reference manual \(TRM\)](#) を参照してください。

### 3.1.7 メモリ

PSoC™ 6 には、フラッシュ、SRAM、ROM、および eFuse メモリブロックが含まれます。

#### • フラッシュ

最大 1 MB のアプリケーションフラッシュがあり、256 KB のセクタで構成されます。2 つの 32 KB フラッシュセクタもあります。

- 通常、EEPROM エミュレーションに使用される補助フラッシュ (AUXflash)

- 監視フラッシュ (SFlash)。SFlash に保存されるデータには、デバイストリム値、**フラッシュ ブート** コード、および暗号化キーが含まれます。デバイスが「セキュア」ライフサイクルステージに移行すると、SFlash は変更できなくなります。

フラッシュには、電力を削減するために 128 ビット幅のアクセスがあります。書き込み操作は行レベルで実行できます。行(ページとも呼ばれる)は 512 バイトです。読み出し操作はシステム低消費電力モードと超低消費電力モードの両方でサポートされますが、書き込み操作はシステム超低消費電力モードでは実行できない場合があります。

フラッシュコントローラには、各 CPU に 1 つずつ、2 つのキャッシュがあります。各キャッシュは 8 KB で、4 ウェイのセットの関連性があります。

#### • SRAM

最大 288 KB の SRAM があります。電力制御と保持の粒度は 32 KB ブロックで実装されているため、ユーザーはディープスリープで保持されるメモリの量を制御できます。メモリはハイバネートモードでは保持されません。

#### • ROM

監視 ROM (SROM) とも呼ばれる 128 KB ROM は、いくつかのシステム機能にコード (**ROM ブート**) を提供します。ROM には、デバイスの初期化、フラッシュ書き込み、セキュリティ、eFuse プログラミング、およびその他のシステムレベルのルーチンが含まれます。ROM コードは、保護コンテキスト 0 の CM0+ CPU によってのみ実行されます。システム機能は、CPU または DAP によって開始できます。これにより、CM0+ で NMI が発生し、CM0+ がシステム機能を実行します。

#### • eFuse

ワンタイムプログラマブル (OTP) eFuse アレイは 1024 ビットで構成され、そのうち 512 ビットはシステム(ダイ ID、デバイス ID、初期トリム設定、デバイスライフサイクル、およびセキュリティ設定など)用に予約されています。残りのビットは、キー情報、ハッシュ値、固有の ID、または同様のカスタムコンテンツを保存するために使用できます。

各ヒューズは個別にプログラムされます。プログラムされる(または「切れる」と、その状態は変更できません。ヒューズが切れると、デフォルト状態の 0 から 1 に移行します。eFuse をプログラムするには、14 mA で  $V_{DDIO0}$  が  $2.5 \text{ V} \pm 5\%$  でなければいけません。

## 機能の説明

eFuse のブローは不可逆的なプロセスであるため、プログラミングは、制御された工場条件下での量産でのみ推奨されます。詳細については、[PSoC™ 6 MCU Programming Specifications](#) を参照してください。

### 3.1.8 ブートコード

**ROM ブート** と **フラッシュ ブート** の 2 つのコードブロックがデバイスに事前にプログラムされています。これらが連携してデバイスの起動と設定、基本的なセキュリティ機能、ライフサイクルステージ管理およびその他のシステム機能を提供します。

#### • ROM ブート

デバイスをリセットすると、ROM 内のブートコードが最初に実行されます。このコードは次を実行します。

- フラッシュブートコードの整合性チェック

- デバイスのトリミング設定（キャリブレーション）

- デバイス保護ユニットの設定

- ライフサイクル状態のデバイスアクセス制限の設定

ROM は変更できず、保護されたシステムで信頼のルートとして機能します。

#### • フラッシュ ブート

フラッシュブートは、SFlash およびアプリケーションフラッシュに格納されたファームウェアモジュールです。検証されたアプリケーションのみがデバイスで実行されることを保証します。また、悪意のある第三者などによってファームウェアイメージが変更されていないことも確認します。

フラッシュ ブート：

- ROM ブートによって保証されます

- ROM ブート後、ユーザーアプリケーションの前に実行

- システム コールを有効にします

- デバッグ アクセス ポートを設定します

- ユーザー アプリケーションを起動します

ユーザーアプリケーションを検証できない場合、フラッシュブートにより、デバイスが安全な状態に移行することが保証されます。

## 機能の説明

**3.1.9 メモリマップ**

両方の CPU には、メモリと周辺機器への共有アクセスを備えた固定アドレスマップがあります。32 ビット (4 GB) のアドレス空間は、Table 3 に示す領域に分割されます。コードは、Code および External RAM から実行できることに注意してください。

**Table 3 CM4 および CM0+ のアドレスマップ**

| アドレス範囲                     | 名称                     | 利用                                                                                       |

|----------------------------|------------------------|------------------------------------------------------------------------------------------|

| 0x0000 0000 – 0x1FFF FFFF  | Code                   | プログラムコード領域。ここにデータも配置できます。アドレス 0 で始まる例外ベクトルテーブルが含まれます。                                    |

| 0x2000 0000 – 0x3FFF FFFF  | SRAM                   | データ領域。この領域は PSoC™ 6 ではサポートされません。                                                         |

| 0x4000 0000 – 0x5FFF FFFF  | Peripheral             | すべての周辺レジスタ。コードはこの領域から実行できません。この領域の CM4 ビットバンドは PSoC™ 6 ではサポートされません。                      |

| 0x6000 0000 – 0x9FFF FFFF  | External RAM           | SMIF または <a href="#">QSPI インターフェースシリアルメモリインターフェース (SMIF)</a> セクションを参照)。この領域からコードを実行できます。 |

| 0xA000 0000 – 0xDFFF FFFF  | External Device        | 使用なし                                                                                     |

| 0xE000 0000 – 0xE00F FFFF  | Private Peripheral Bus | CPU コア内の周辺レジスタへのアクセスを提供します。                                                              |

| 0xE010 0A000 – 0xFFFF FFFF | Device                 | デバイス固有のシステムレジスタ。                                                                         |

Table 4 に示すデバイスマメリマップは、両方の CPU に適用されます。つまり、CPU はすべての PSoC™ 6 MCU メモリおよび周辺機器レジスタへのアクセスを共有します。

**Table 4 CM4 および CM0+ の内部メモリアドレスマップ**

| アドレス範囲                    | メモリタイプ                            | 容量        |

|---------------------------|-----------------------------------|-----------|

| 0x0000 0000 – 0x0001 FFFF | ROM                               | 128 KB    |

| 0x0800 0000 – 0x0804 7FFF | SRAM                              | 最大 288 KB |

| 0x1000 0000 – 0x100F FFFF | アプリケーション フラッシュ                    | 最大 1 MB   |

| 0x1400 0000 – 0x1400 7FFF | 補助フラッシュ。<br>EEPROM エミュレーションに使用可能。 | 32 KB     |

| 0x1600 0000 – 0x1600 7FFF | 監視フラッシュ                           | 32 KB     |

SRAM は両方の CPU の Arm® Code 領域にあります (Table 3 を参照)。CPU の Arm® SRAM 領域に物理メモリはありません。

## 機能の説明

### 3.2 システムリソース

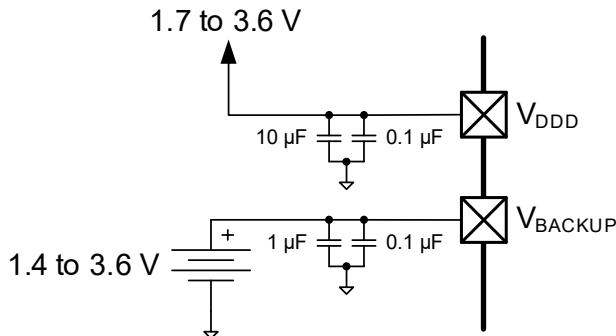

#### 3.2.1 電源システム

電源システムは各モードに応じた電圧レベルを保証します。これを実現するために、機能の正常な動作に必要な電圧レベルを達成するまでモードへの移行を遅延させる(例えば、パワーオンリセット(POR)の時)、または電源が指定されたレベルを下回った場合にリセットを発生させます(電圧低下検出(BOD))。このデザインは、電源電圧が規定されたレベル(例えば、1.7V)を下回ってからリセットが発生するまで安全なチップ動作を保証します。電圧シーケンスの要件はありません。

$V_{DDP}$  電源(1.7 ~ 3.6V)はオンチップ降圧レギュレータまたは低ドロップアウトレギュレータ(LDO)に電力を供給します。供給先はユーザーが選択可能です。さらに、降圧レギュレータおよびLDOの両方へ供給するコア動作電圧( $V_{CCD}$ )も、0.9Vまたは1.1Vから選択できます。この選択について、ユーザーは2つのシステム電源モードから選択できます。

- System Low Power (LP) は、1.1Vで $V_{CCD}$ を動作させ、デバイス構成の制限なしで高性能を提供します。

- System Ultra Low Power (ULP) は、例外的な低電力を得るために0.9Vで $V_{CCD}$ を動作させますが、最大クロック速度に制限を課します。

加えて、バックアップドメインは、バッテリやスーパーキャパシタなどのバックアップ電源( $V_{BACKUP}$ )によって供給される個別の電源ドメインを使用して、「常時オン」機能を追加します。32.768kHzの時計水晶発振器(WCO)でサポートされるアラーム機能を備えたリアルタイムクロック(RTC)、および電源管理IC(PMIC)制御が含まれます。詳細については[電源に関する考慮事項](#)を参照してください。

#### 3.2.2 電力モード

PSoC™ 6 MCU は、4つのシステムと3つのCPU電力モードで動作できます。これらのモードは、アプリケーションの平均消費電力を最小限に抑えることを目的とします。電力モードおよびその他の省電力設定オプションの詳細については、アプリケーションノート [AN219528: PSoC™ 6 MCU low-power modes and power reduction techniques](#) と [Architecture TRM の Power Mode 章](#) を参照してください。

PSoC™ 6 MCU でサポートされている電力モードは、電力消費の少ない順に次のとおりです。

- システム低電力(LP):すべての周辺機器とCPU電源モードは最大速度で利用可能

- システム超低電力(ULP):すべての周辺機器とCPU電源モードが利用可能ですが、速度は制限されている

- CPUアクティブ:CPUはシステムLPまたはULPモードでコードを実行

- CPUスリープ:CPUコードの実行は、システムLPまたはULPモードで停止

- CPUディープスリープ:システムLPまたはULPモードでCPUコードの実行が停止し、システムディープスリープが要求される

- システムディープスリープ:両方のCPUがCPUディープスリープモードに入った後は、低周波数の周辺機器のみが利用可能

- システムハイバネート:デバイスとI/Oの状態がフリーズし、デバイスがウェイクアップ時にリセット

CPUアクティブ、スリープ、およびディープスリープは、Arm® CPU 命令セットアーキテクチャ (ISA) でサポートされる標準の Arm® 定義電力モードです。システム LP, ULP, ディープスリープ、およびハイバネートモードは、PSoC™ 6 MCU でサポートされる追加の低電力モードです。ハイバネートモードは、PSoC™ 6 MCU の最低電力モードであり、ウェイクアップ時に、CPU およびすべての周辺機器がリセットされます。

#### 3.2.3 クロックシステム

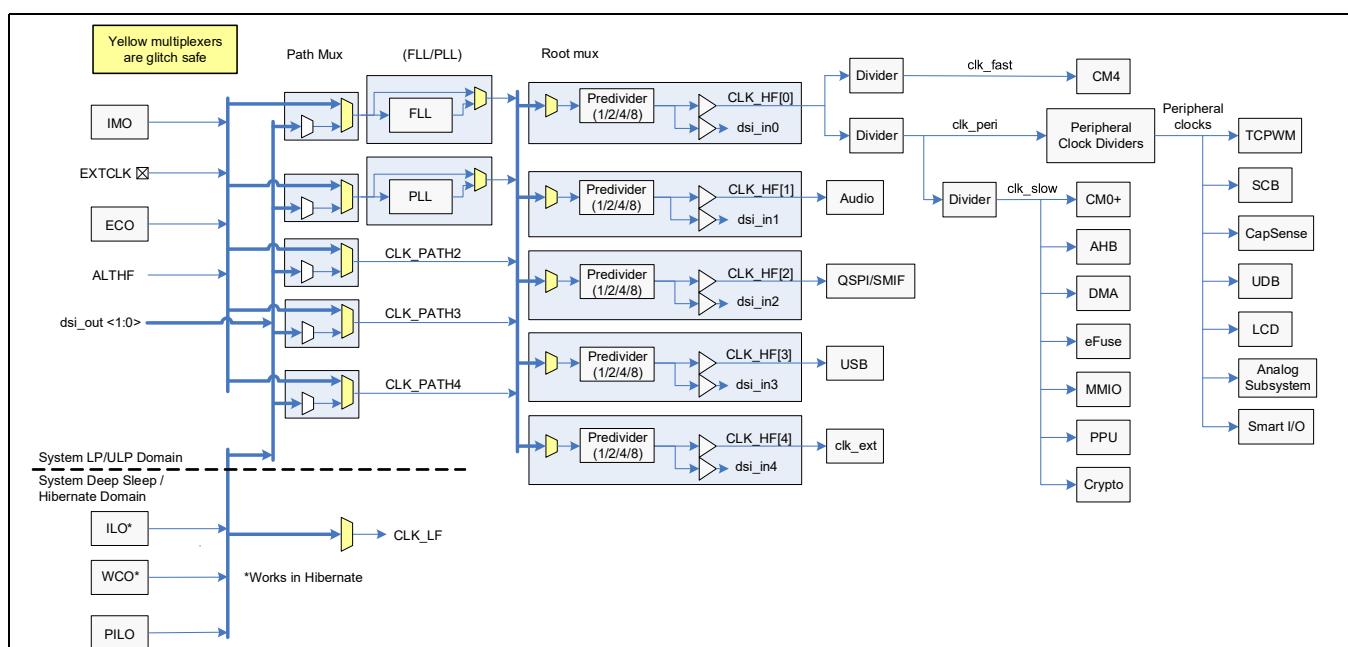

**Figure 4** に、クロックシステムが以下のもので構成されていることを示します。

- 内部主発振器(IMO)

- 内部低速発振器(ILO)

- 高精度 ILO (PILO)

## 機能の説明

- 時計用水晶発振器 (WCO)

- システムおよび Bluetooth® LE サブシステム用の外部 MHz 水晶発振器 (ECO)

- 外部クロック入力

- Phase-locked loop (PLL)

- Frequency-locked loop (FLL)

クロックはバッファリングされ、Smart I/O ポートのピンに引き出されます。

アプリケーションが起動時のデフォルトのクロックは、IMO と FLL によって駆動される CLK\_HF [0] です。CLK\_HF [0], clk\_fast, clk\_peri, および clk\_slow は、すべて 50 MHz (LP モード) または 25 MHz (ULP モード) のいずれかです。すべての周辺クロックを含む他のすべてのクロックはオフです。

### 3.2.4 内部主発振器 (IMO)

IMO は、内部クロックの主要供給源です。仕様の精度を達成するために出荷試験中に調整されます。IMO のデフォルト周波数は 8 MHz で、許容誤差は  $\pm 2\%$  です。

### 3.2.5 内部低速発振器 (ILO)

ILO は、公称 32 kHz の非常に低電力の発振器で、すべての電力モードで動作します。ILO は、精度を高めるために、より高い精度のクロックに対して較正できます。

### 3.2.6 高精度 ILO (PILO)

PILO は、ECO などの高精度クロックを使用して定期的にキャリブレーションされた場合、ILO よりも正確なクロックを供給できる 32.768 kHz クロックです。

Figure 4 クロック ダイヤグラム

## 機能の説明

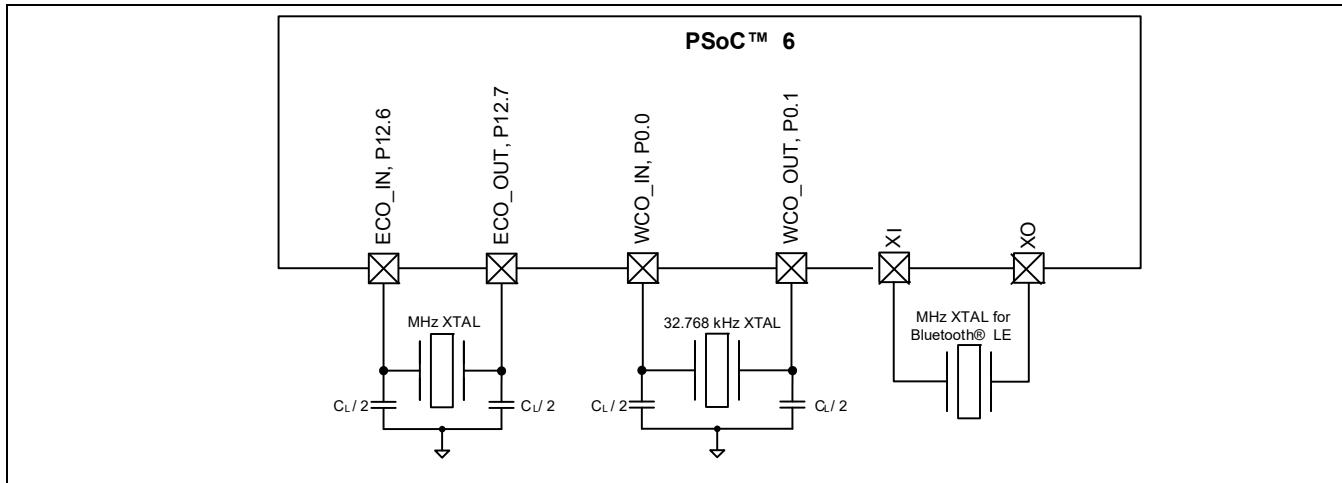

## 3.2.7 外部水晶発振器

**Figure 5** に、この製品ラインのすべての外部水晶発振器回路を示します。示されているコンポーネント値は典型的なものです。水晶の値については [ECO の仕様](#) を、負荷コンデンサの値については水晶のデータシートを確認してください。ECO と WCO には、平衡外部負荷コンデンサが必要です。Bluetooth® LE 発振器は外部負荷コンデンサを必要としません。詳細については、TRM および [AN218241, PSoC™ 6 MCU Hardware Design Considerations](#) を参照してください。

Figure 5 発振器回路

ECO を使用する場合、そのパフォーマンスは GPIO スイッチングノイズの影響を受けることに注意してください。**Table 5** に示すように、GPIO ポートを使用する必要があります。一般的なアナログサブシステムの使用に関する追加の制限については、**Table 6** も参照してください。

Table 5 ECO 使用ガイドライン

| ポート           | 最大周波数                  | $V_{DDD} \leq 2.7\text{ V}$ での駆動強度 | $V_{DDD} > 2.7\text{ V}$ での駆動強度 |

|---------------|------------------------|------------------------------------|---------------------------------|

| ポート 11        | SMIF の場合 60 MHz (QSPI) | DRIVE_SEL 2                        | DRIVE_SEL 3                     |

| ポート 12 および 13 | 低速スルーレート設定             | 制限なし                               | 制限なし                            |

## 3.2.8 ウオッヂドッグ タイマー (WDT, MCWDT)

PSoC™ 6 MCU には 1 つの WDT と 2 つのマルチカウンター WDT(MCWDT) があります。WDT には 16 ビットのフリーランニングカウンターがあります。各 MCWDT には、2 つの 16 ビットカウンターと 1 つの 32 ビットカウンターがあり、複数の動作モードがあります。すべての 16 ビットカウンターは、ウォッヂドッグデバイスリセットを生成できます。すべてのカウンターは、一致イベントで割込みを生成できます。

WDT は ILO によってクロックされます。システム LP/ULP, ディープスリープ, およびハイバネートモードで割込み / ウェイクアップの生成が行えます。MCWDT は LFCLK (ILO または WCO) によってクロックされます。システム LP/ULP およびディープスリープモードで定期的な割込み / ウェイクアップ生成を実行できます。

## 3.2.9 クロック分周器

ペリフェラルの使用とタイミングの目的で、以下の整数と分数のクロック分周器が用意されます。

- 8 つの 8 ビットクロック分周器

- 16 個の 16 ビット整数クロック分周器

- 4 つの 16.5 ビット分数クロック分周器

- 1 つの 24.5 ビット分数クロック分周器

## 機能の説明

### 3.2.10 トリガールーティング

PSoC™ 6 MCU には、トリガーマルチプレクサブロックが含まれます。これは、周辺機器ブロック間および GPIO と周辺機器ブロック間でトリガー信号をルーティングするために使用されるデジタルマルチプレクサとスイッチを集めたものです。

トリガールーティングには 2 つのタイプがあります。トリガーマルチプレクサは、送信元と宛先で再設定可能で、特定の送信元を宛先に接続する「1 対 1 トリガー」と呼ばれる有線スイッチもあります。ユーザーはルートを有効または無効にできます。

### 3.2.11 リセット

PSoC™ 6 MCU は、さまざまなソースからリセットできます。

- 電源がデバイスが正常に機能するために必要なレベルまで上昇する間、デバイスをリセット状態に保持するパワーオンリセット (POR)。POR は電源投入時に自動的にアクティブになります。

- ブラウンアウト検出 (BOD) リセットは、デジタル電圧供給 VDDD を監視し、VDDD が必要な最小ロジック動作電圧を下回った場合にリセットを生成します。

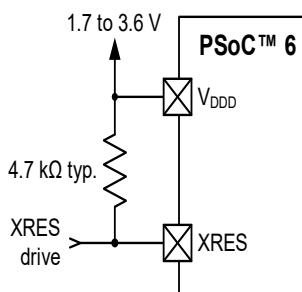

- 外部ソースを使用してデバイスをリセットする外部リセット専用ピン (XRES)。XRES ピンはアクティブ Low です。[Figure 6](#) に示すように、 $V_{DDD}$ へのプルアップ抵抗またはアクティブドライブ回路のいずれかに接続できます。プルアップ抵抗を使用する場合は、その値を選択して、ピンが Low に引き下げられたときの電流引き込みを最小限に抑えます。4.7 kΩ ~ 100 kΩ が標準です。

**Figure 6 XRES 接続ダイヤグラム**

- ウォッチドッグタイマー (WDT または MCWDT) は、ファームウェアが指定されたタイムアウト期間内にデバイスのサービスに失敗した場合にデバイスをリセットします。

- ファームウェアを使用してオンデマンドでデバイスをリセットするためのソフトウェア起動リセット。

- ロジック保護障害は、不正な操作条件が発生した場合に割込みをトリガーしたり、デバイスをリセットしたりできます。例えば、特権コードの実行中にデバッグブレークポイントに到達します。

- システムハイバネート低消費電力モードからデバイスを復帰させるためのハイバネート ウェイクアップリセット。

リセットイベントは非同期であり、デバイスを既知の状態に復帰させることができます。リセットソースの一部はレジスタに記録されます。これはリセットを通じて保持され、ソフトウェアがリセットの原因を特定できるようにします。

### 3.3 Bluetooth® LE 無線およびサブシステム

この製品ラインには、セキュリティエンジンを組み込んだ物理層 (PHY) およびリンク層 (LL) エンジンを含む Bluetooth® LE サブシステムを内蔵します。インフィニオンは、Bluetooth® LE の広範なドライバーライブラリとミドルウェアのサポートも提供します。[ModusToolbox™ Software](#) を参照してください。

物理層は、Bluetooth® LE 仕様 5.0 に準拠する 2.4 GHz ISM 帯域で 2 Mbps でガウス周波数シフトキーイング (GFSK) パケットを送受信するデジタル PHY と RF トランシーバーで構成されます。

ベースバンド コントローラーは、マスターおよびスレーブ モードの両方に対応する複合ハードウェアとファームウェア実装です。HCI やリンク制御などの重要なプロトコル要素はファームウェアに実装されま

## 機能の説明

す。暗号化、CRC、データホワイトニング、アクセスコード相関などのタイムクリティカルな機能ブロックはハードウェア(LLエンジン内)に実装されます。

RFトランシーバーは、マッチング/フィルタリングネットワークを介して  $50\Omega$  アンテナを駆動するシングルエンドRFポートピンを提供する集積バランを備えます。受信ではこのブロックでGFSK復調を行って、アンテナからのRF信号をデジタルビットストリームに変換します。送信ではこのブロックでGFSK変調を行った後、デジタルベースバンド信号を無線周波数に変換しアンテナから送信します。

ハードウェアとファームウェアに実装されている主な機能は以下のとおりです。

- 論理リンク制御と適応プロトコル(L2CAP)、属性プロトコル(ATT)、セキュリティマネージャ(SM)プロトコルに対応するマスターとスレーブシングルモードプロトコルスタック

- 一般属性プロファイル(GATT)、一般アクセスプロファイル(GAP)およびL2CAPへのAPIアクセス

- L2CAP接続向けチャネル(Bluetooth® 4.1の機能)

- GAP機能

- ブロードキャスター、オブザーバー、ペリフェラル、セントラルの役割

- セキュリティモード1:レベル1,2,3,および4、セキュリティモード2:レベル1および2

- ユーザー定義の通知データ

- 複数の接続に対応

- GATT機能

- GATT ClientおよびServer

- GATTサブプロシージャに対応

- 32ビットユニークスルーアイデンティティ(UUID)(Bluetooth® 4.1機能)

- セキュリティマネージャ(SM)

- ペアリング方式: Just works, Passkey Entry, and Out of Band

- LEセキュアコネクションペリングモデル

- 認証済みの中間者攻撃(MITM)保護とデータ署名

- リンク層(LL)

- マスターとスレーブの役割

- 128ビットAESエンジン

- 低デューティ比通知

- LE Ping

- LLプライバシー1.2(Bluetooth® 4.2機能)

- データ長の拡張(Bluetooth® 4.2機能)

- SIGが採用したすべてのBluetooth® LEプロファイルに対応

アドバタイズ(1.28秒, 31バイトパケット, 0 dBm TX出力電力)および接続(300ミリ秒, 0バイトパケット, 0 dBm TX出力電力)の消費電力は、それぞれ42 μWおよび70 μWです。

## 機能の説明

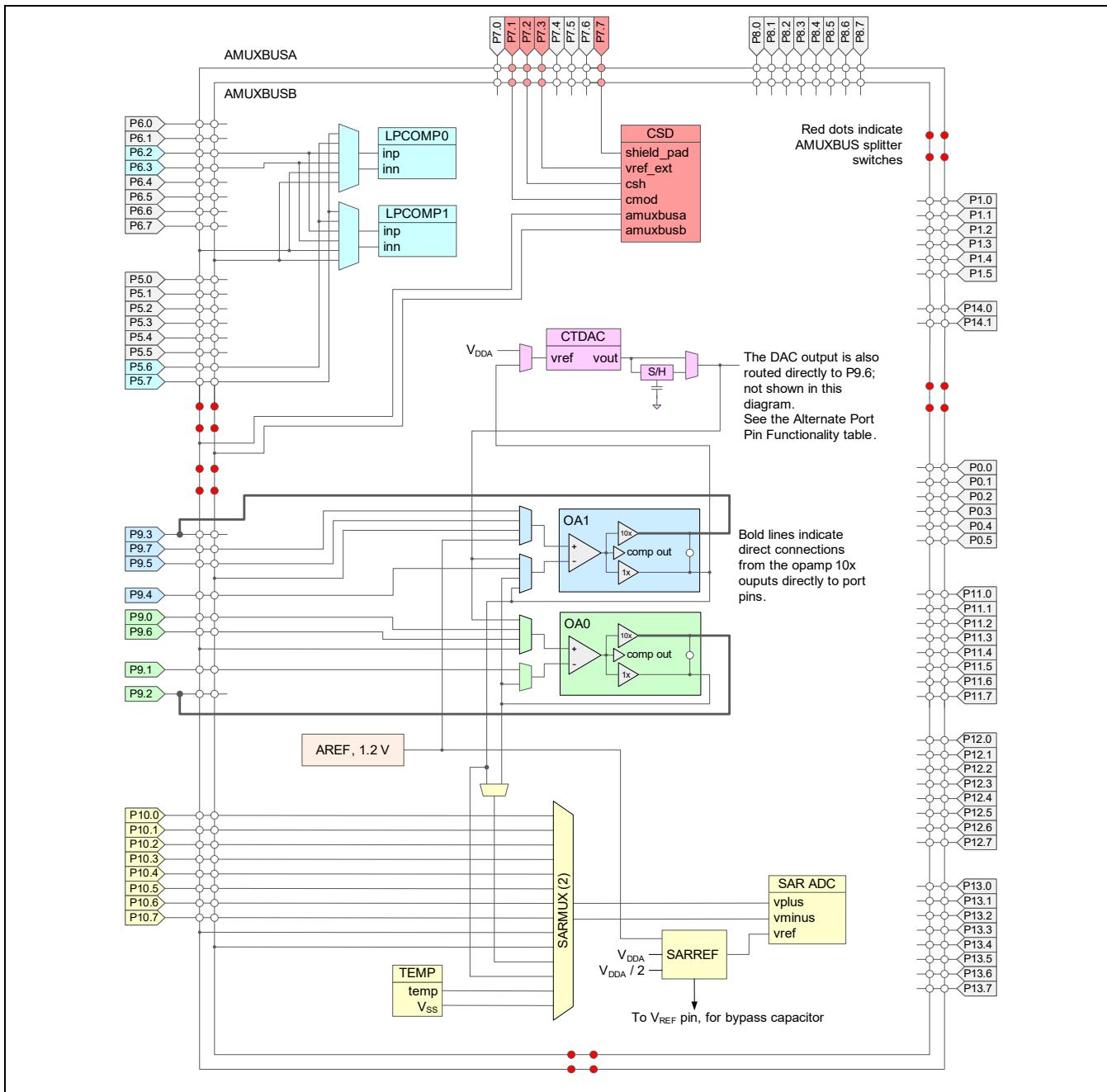

### 3.4 プログラマブルアナログサブシステム

#### 3.4.1 12ビットSAR ADC

12ビットの1Msps SAR ADCは、18MHzの最大クロックレートで動作でき、12ビット変換を行うにはその周波数で最低18クロックが必要です。ADCリファレンス電圧には、 $V_{DDA}$ ,  $V_{DDA/2}$ , およびアナログリファレンス(AREF)の3つの内部リファレンスのいずれかを使用できます。AREFは公称1.2Vで、±1%に調整されています。[Table 23](#)を参照してください。VREFピンを駆動することにより、外部リファレンスを使用することもできます。 $V_{DDA/2}$ またはAREFをリファレンスとして使用する場合、ノイズの多い状態でのパフォーマンスを向上させるために、外部バイパスコンデンサをVREFピンに接続できます。これらの参照オプションにより、使用される参照の精度でレシオメトリック読み出しありは絶対読み出しが可能です。ADCの入力範囲は、 $V_{SS}$ と $V_{DDA}/V_{DDIOA}$ の間の全電源電圧です。SARADCは、同じ設定でシングルエンド信号と差動信号を組み合わせて設定できます。

SAR ADCのサンプル/ホールド(S/H)アパートチャはプログラム可能で、必要に応じて、高インピーダンスの信号が十分に安定するのに十分な時間を確保できます。適切なリファレンス電圧が使用され、システムノイズレベルが許す限り、システム性能は真の12ビット精度で65dBです。ノイズの多い状態で性能を改善するために、内部リファレンスアンプ用の外部バイパスコンデンサを(固定「VREF」ピンを介して)追加できます。

SARは入力マルチプレクサを介して、決められたピンに接続されます。マルチプレクサは、スイッチングオーバーヘッドの必要はなく、選択されたチャネルを自律的に巡回します(シーケンサスキャン)(つまり、合計サンプリング帯域幅は、単一のチャネルか複数のチャネルであるかにかかわらず1Mspsです)。各チャネルの結果はバッファリングされるため、すべてのチャネルのフルスキャンが完了した場合のみ割込みがトリガーされます。また、入力が最小値または最大値、あるいはその両方を超えた場合に検出し、割込みを発生させるように、レンジレジスタのペアを設定できます。これにより、シーケンサのスキャンが完了するのを待たずに、範囲外の値を迅速に検出し、CPUが値を読み出し、ソフトウェアで範囲外の値をチェックできます。SARは、ファームウェア制御下で、アナログマルチプレクサバス(AMUXBUS)を介して他のほとんどGPIOピンにも接続できます。SARは、高速クロック(最大18MHz)を必要とするため、ディープスリープモードおよびハイバネート状態モードでは使用できません。SARの動作範囲は1.71~3.6Vです。

ADCの精度はGPIOスイッチングノイズの影響を受けます。精度を向上させるには、[Table 6](#)にリストされているGPIOポート制限を実装します。さらに、ポート9および10にスイッチング出力があつてはいけません。

#### 3.4.2 温度センサー

オンチップ温度センサーはSARシーケンサブロックの一部であり、SAR ADCによってスキャンされる場合があります。これは、電力を節約するために無効にできる電流源によってバイアスされるダイオードで構成されます。温度センサーは、測定チャネルの1つとしてSAR ADCに直接接続できます。ADCは温度センサーの出力をデジタル化し、インフィニオンが提供するソフトウェア機能を使用して、校正と直線化を含む読み出し値を温度に変換できます。

#### 3.4.3 12ビットのデジタルアナログ変換器

チップには、2μs以内で安定する12ビット電圧モードのDACが内蔵されます。DACはユーザー定義の波形を生成するためにDMAコントローラによって駆動されます。チップからのDAC出力は、抵抗ラダー出力(グランド近傍で高度にリニア)またはCTBmブロックのオペアンプを使用したバッファ付き出力のいずれかです。

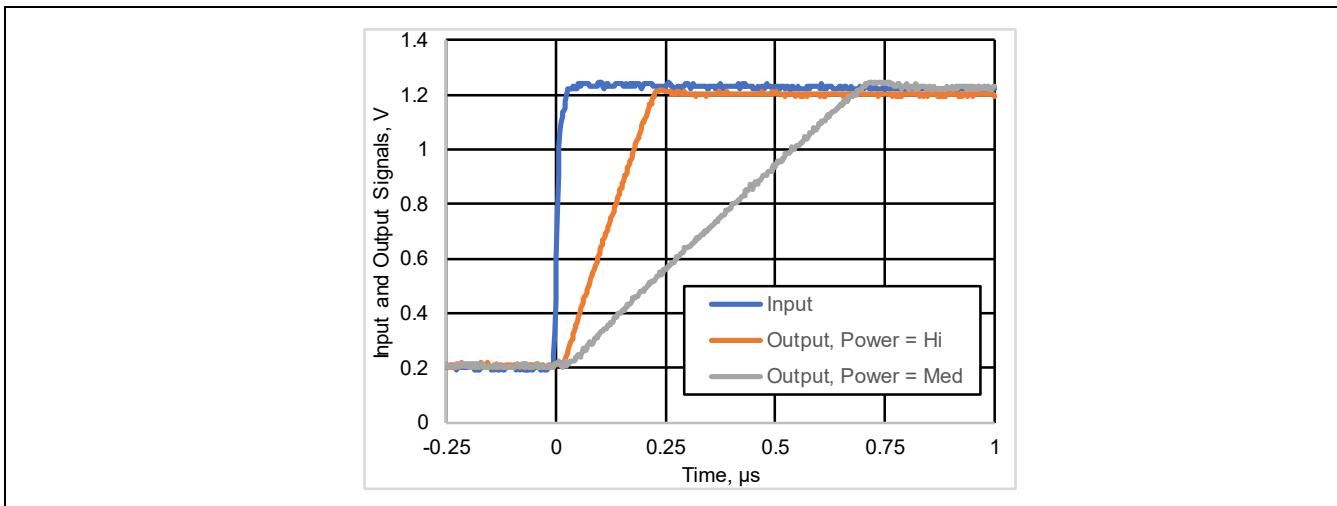

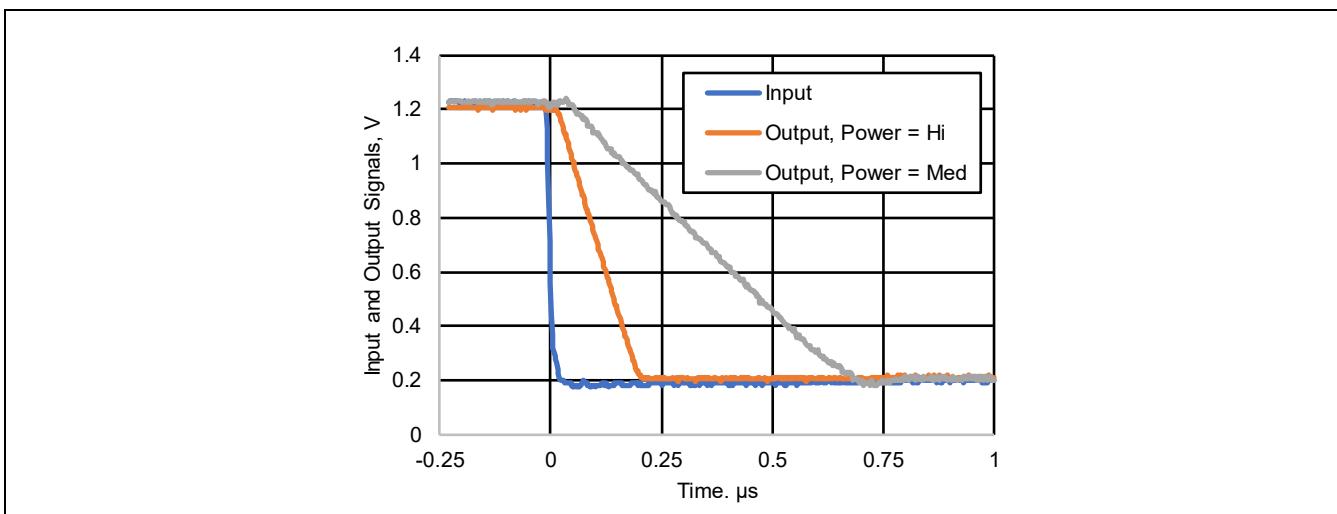

#### 3.4.4 2個のオペアンプのある連続時間ブロックミニ(CTBm)

[Figure 7](#)に示すように、このブロックは2つのオペアンプで構成され、それらは入力と出力はピンと他のアナログブロックに接続されます。3つの電力モード(高、中、および低)とコンパレータモードがあります。オペアンプは、SAR入力とDAC出力をバッファするため使用できます。これらのオペアンプの非反転入力は2つのピンのいずれかに接続でき、したがって、独立したセンサーを異なる時間に使用できます。ピンの選択はファームウェアを使って行われます。オペアンプは、システムのディープスリープモードでの動作にも対応し、パフォーマンスが低下し、消費電力が削減されます。

---

## 機能の説明

### 3.4.5 低消費電力コンパレータ

2つの低消費電力コンパレータが提供され、すべての電力モードで動作できます。これにより、システムディープスリープおよびハイバネートモード中に外部電圧レベルを監視する機能を維持しながら、他のアナログシステムリソースを無効にできます。システムウェイクアップ回路がコンパレータの切り替えイベントによりアクティブになる非同期電力モード(ハイバネート)で動作する場合を除き、準安定状態を避けるために、コンパレータ出力は通常同期化されます。

## 機能の説明

**Figure 7** に、アナログサブシステムの概要を示します。この図は、概略化した図です。接続の詳細については、[Architecture TRM](#) 参照してください。

**Figure 7** アナログサブシステム

## 機能の説明

## 3.5 プログラマブル デジタル

## 3.5.1 Smart I/O

Smart I/O デバイスの内部リソースから GPIO ピンに移動する信号、または外部ソースからデバイスに移動する信号のブール演算を可能にするプログラマブルロジックファブリックです。Smart I/O ブロックは、GPIO ピンと高速 I/O マトリックス (HSIOM) の間にあり、単一のポート専用です。

2 つの Smart I/O ブロックがあります。1 つはポート 8 に、もう 1 つはポート 9 にあります。Smart I/O が有効になっていない場合、ポート 8 およびポート 9 のすべての信号は Smart I/O ハードウェアをバイパスします。

Smart I/O は下記をサポートします。

- システムのディープスリープ動作

- CPU の介入なしのブール演算

- 非同期または同期 (クロック) 操作

各 Smart I/O ブロックには、データユニット (DU) と 8 つのルックアップテーブル (LUT) が含まれます。

DU は下記のとおりです。

- 選択可能なオペコードに基づいて独自の機能を実行します。

- 内部リソース、GPIO ポート、または DU レジスタの値から入力信号を発信できます。

- 各 LUT は下記のとおりです。

- 3 つの選択可能な入力ソースがあります。入力信号は、別の LUT、内部リソース、GPIO ピン、または DU からの外部信号から供給されます。

- プログラム可能なブール論理テーブルとして機能します。

- 同期または非同期にできます。

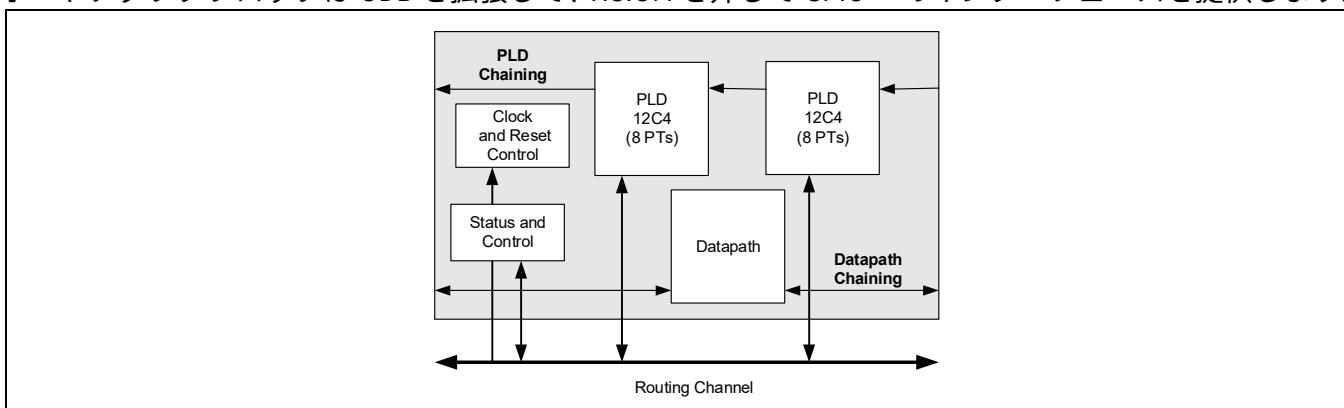

## 3.5.2 ユニバーサル デジタル ブロック (UDB)

この製品ラインは 12 個の UDB を内蔵します。UDB は、Figure 8 に示すように、一般的な組込み周辺機器とカスタム機能を作成するために最適化された、コミットされていないロジック (PLD) とナノ CPU (データパス) の集まりです。UDB データパスは 8 ビット幅であり、連鎖して 16, 24, および 32 ビット関数を形成できます。UDB には、デジタルシステムインターフェクト (DSI) が含まれます。これは、UDB、固定機能周辺機器、I/O ピン、およびその他のシステムブロック間で信号をルーティングして、フル機能のデバイス接続を実装します。DSI は、任意のデジタル機能と任意のピン間のルーティングを可能にします。ポートアダプタブロックは UDB を拡張して、HSIOM を介して GPIO へのインターフェースを提供します。

Figure 8 UDB ブロック ダイヤグラム

## 機能の説明

### 3.6 固定機能デジタル

#### 3.6.1 タイマー / カウンター / パルス幅変調器 (TCPWM) ブロック

- TCPWM は、次の動作モードをサポートします。

- 比較付きタイマーカウンター

- キャプチャ付きタイマーカウンター

- 直交デコード

- パルス幅変調 (PWM)

- 疑似乱数 PWM

- デッドタイム付き PWM

- アップ , ダウン , およびアップ / ダウンカウントモード

- クロック プリスケーリング (1, 2, 4, ... 64, 128 による分周 )

- 比較 / キャプチャおよび期間値のダブルバッファリング

- アンダーフロー , オーバーフロー , および出力信号のキャプチャ / 比較

- 割込みのサポート

- ターミナルカウント : モードに依存。通常、オーバーフローまたはアンダーフローで発生

- キャプチャ / 比較 : カウントがキャプチャレジスタにキャプチャされるか、カウンター値が比較レジスタの値と等しい

- PWM の相補出力

- 立ち上りエッジ , 立ち下りエッジ , 両方のエッジ , およびレベルトリガーオプションを使用して、各 TCPWM の選択可能な開始 , リロード , 停止 , カウント , およびイベント信号をキャプチャします。TCPWM には、強制的に出力を所定の状態にするための Kill 入力があります。

このデバイスには次のものがあります。

- 8 個の 32 ビット TCPWM

- 24 個の 16 ビット TCPWM

#### 3.6.2 シリアル通信ブロック (SCB)

この製品ラインには 9 つの SCB があります。

- 8 つは I<sup>2</sup>C, UART, または SPI のいずれかを実装できます。

- 1 つの SCB (SCB#8) は外部クロックを使用してシステムディープスリープモードで動作でき、この SCB は SPI スレーブまたは I<sup>2</sup>C スレーブのいずれかです。

**I<sup>2</sup>C モード :** SCB は完全なマルチマスターおよびスレーブインターフェースを実装できます（マルチマスターのアービトリレーションが可能です）。このブロックは、最大 1 Mbps (Fast Mode Plus) の速度で動作できます。また、メールボックスアドレス範囲を作成する EZI2C をサポートし、メモリ内のアレイの読み出しと書き込みに対する I<sup>2</sup>C 通信を効果的に削減します。SCB は、送受信用に 256 バイトの FIFO をサポートします。

I<sup>2</sup>C ペリフェラルは、NXP I<sup>2</sup>C バス仕様およびユーザーマニュアル (UM10204) で定義されている I<sup>2</sup>C 標準モード , Fast モード , および Fast モード プラス デバイスと互換性があります。I<sup>2</sup>C バス I/O は、オープンドレインモードにある GPIO を使って実装されます。

**UART モード :** 最大 8 Mbps で動作するフル機能の UART です。基本の UART プロトコルから少し発展した車載向けシングルワイヤインターフェース (LIN), 赤外線インターフェース (IrDA), SmartCard (ISO7816) プロトコルに対応します。また、共通の Rx と Tx ラインを介して接続したペリフェラルのアドレス指定を可能にする 9 ビットマルチプロセッサモードに対応します。パリティエラー , ブレーク検出 , フレームエラーなどの一般的な UART 機能がサポートされます。256 バイトの FIFO を使用すると、はるかに長い CPU サービスレイテンシを許容できます。

**SPI モード :** SPI モードは Motorola SPI, TI セキュア シンプルペアリング (SSP) (SPI コーデックの同期化用の開始パルスを本質的に追加 ), National Microwire ( 半二重の SPI ) に完全に対応します。SPI ブロックは、EZSPI モードをサポートします。このモードでは、データ交換はメモリ内の配列の読み出しと書き込みに限定されます。SPI インターフェースは 25 MHz クロックで動作します。

## 機能の説明

### 3.6.3 USB 12 Mbps device interface

PSoC™ 6 には、USB 12 Gbps デバイスインターフェースが組み込まれます。デバイスは、最大 8 つのエンドポイントを持っています。512 バイトの SRAM バッファが用意され、DMA がサポートされます。

注：USB ピンを使用しない場合は、 $V_{DDUSB}$  をグランドに接続し、P14.0/USBDP ピンと P14.1/USBDM ピンは未接続のままにしてください。

### 3.6.4 QSPI インターフェースシリアルメモリインターフェース (SMIF)

シリアルメモリインターフェースが提供され、最大 80 MHz で実行されます。シングル、デュアル、クワッド、デュアルクワッド、およびオクタルの SPI 設定をサポートし、最大 4 つの外部メモリデバイスをサポートします。次の 2 つの操作モードをサポートします。

- メモリマップ I/O (MMIO): SMIF レジスタおよび FIFO を介したデータアクセスを提供するコマンドモードインターフェース

- 所定の場所での実行 (XIP): AHB 読み出しおよび書き込みは、SPI 読み出しおよび書き込み転送に直接変換される。

XIP モードでは、外部メモリは PSoC™ 6 MCU 内部アドレス空間にマッピングされ、外部メモリから直接コードを実行できます。パフォーマンスを改善するために、4 KB のキャッシュが含まれます。XIP モードは、AES-128 のオンザフライ暗号化および復号化もサポートしているため、外部メモリのコードおよびデータの安全な保管とアクセスが可能です。

### 3.6.5 LCD

このブロックは、LCD コモンとセグメントを駆動します。ルーティングは、ほとんどの GPIO で使用できます。GPIO の 1 個から 8 個をコモンに使用する必要があり、残りはセグメントに使用できます。

LCD ブロックには、高速 (8MHz) と低速 (32kHz) の 2 つの動作モードがあります。どちらのモードもシステム LP モードと ULP モードで動作します。低速モードは、システムのディープスリープモードでコントラストを下げる動作します。このモードを使用する前に、コモンラインとセグメントラインの数、視野角の要件、プロトタイプのパフォーマンスを確認してください。

## 機能の説明

**3.7 GPIO**

この製品ラインには、最大 84 個の GPIO があり、以下を実装します。

- 8 つの駆動強度モード

- アナログ入力モード (入力と出力バッファが無効)

- 入力のみ

- 弱プルアップ、強プルダウン

- 強プルアップ、弱プルダウン

- オープンドレイン、強プルダウン

- オープンドレイン、強プルアップ

- 強プルアップ、強プルダウン

- 弱プルアップ、弱プルダウン

- 入力閾値選択 (CMOS または LVTTL)

前のステートをラッチするためのホールド モード (システムのハイバネート モードで I/O ステートを維持するため)

- EMI を改善するために、dV/dt に起因するノイズを制御するために選択可能なスルーレート

ピンは、最大 8 ビット幅のポートと呼ばれる論理エンティティに構成されます。データ出力とピンステートレジスタは、ピン上で駆動される値とピンの入力状態をそれぞれ格納します。

各ピンは有効になった場合に割込みを生成でき、各ポートにはそれに対応する割込み要求 (IRQ) があります。

ポート 1 ピンは、過電圧耐性 (OVT) 動作が可能であり、入力電圧は  $V_{DDD}$  よりも高い場合があります。OVT ピンは一般に I<sup>2</sup>C と共に使用され、機能に影響を与えることなく動作中の I<sup>2</sup>C バスへの物理的な接続を維持しながらチップの電源をオフにできます。

GPIO ピンは、より高い値の電流をソースまたはシンクするために連動させられます。OVT ピンを含む GPIO ピンは、絶対最大定格値より高くプルアップされない場合があります。[電気的仕様](#)を参照してください。

電源投入およびリセット中、ピンは強制的にアナログ入力駆動モードになり、入力および出力バッファが無効になり、入力をクローバーにしたり、過剰なターンオン電流が発生したりしないようにします。

高速 I/O マトリクス (HSIOM) と呼ばれる多重化ネットワークは、I/O ピンに接続される可能性のあるさまざまな周辺信号とアナログ信号の間で多重化するために使用されます。

アナログ性能は GPIO スイッチングノイズの影響を受けます。最高のアナログ性能を得るには、次の周波数とドライブモードの制約を適用する必要があります。DRIVE\_SEL 値 ([Table 6](#) を参照) は、ドライブの強度を表します (詳細については、[Architecture and Register TRMs](#) を参照してください)。

ECO の使用に関する追加の制限については、[Table 5](#) も参照してください。

**Table 6 DRIVE\_SEL の値**

| ポート          | 最大周波数                                    | $V_{DDD} \leq 2.7\text{ V}$ での駆動強度 | $V_{DDD} > 2.7\text{ V}$ での駆動強度 |

|--------------|------------------------------------------|------------------------------------|---------------------------------|

| ポート 0        | 8 MHz                                    | DRIVE_SEL 2                        | DRIVE_SEL 3                     |

| ポート 1        | 1 MHz; 低速スルーレート, 最大 2 出力                 |                                    |                                 |

| ポート 5 ~ 10   | 16 MHz; SPI の場合 25 MHz                   |                                    |                                 |

| ポート 11 ~ 13  | SMIF の場合 80 MHz (QSPI)                   | DRIVE_SEL 1                        | DRIVE_SEL 2                     |

| ポート 9 および 10 | 8 MHz; ADC 性能のための TQFP パッケージの低速スルーレート 設定 | 制限なし                               | 制限なし                            |

## 機能の説明

### 3.8 特殊機能ペリフェラル

#### 3.8.1 オーディオサブシステム

このサブシステムは、次のハードウェアブロックで構成されます。

- 1つのInter-IC Sound (I<sup>2</sup>S) インターフェース

- 2つのパルス密度変調 (PDM) からパルス符号変調 (PCM) デコーダーチャネル

- I<sup>2</sup>S インターフェースは 2 つの独立したハードウェア FIFO バッファ (TX および RX) を実装し、マスター モードまたはスレーブモードで動作できます。次の機能をサポートします。

- 複数のデータ形式 : I<sup>2</sup>S, 左寄せ, 時分割多重化 (TDM) モード A, および TDM モード B

- プログラム可能なチャネル / ワード長 : 8/16/18/20/24/32 ビット

- 内部 / 外部クロック動作。最大 192 ksps

- 割込みマスクイベント : トリガー, 非エンプティ, フル, オーバーフロー, アンダーフロー, ウオッチドッグ

- DMA をサポートする設定可能な FIFO トリガーレベル

I<sup>2</sup>S インターフェースは、一般的にオーディオコーデック, シンプルな DAC, およびデジタルマイクとの接続に使用されます。

PDM-PCM デコーダーは、ステレオまたはモノの 1 ビット PDM 入力ストリームを PCM データ出力にデコードする単一のハードウェア Rx FIFO を実装します。次の機能がサポートされます。

- プログラマブルデータ出力のワード長 : 16/18/20/24 ビット

- ボリュームコントロール用のプログラマブルゲインアンプ (PGA): 1.5 dB ステップで -12 dB から +10.5 dB まで

- 設定可能な PDM クロック生成。384 kHz ~ 3.072 MHz の範囲

- サンプリングのドループ補正と設定可能なデシメーションレート。最大 48 ksps。

- プログラム可能なハイパスフィルタゲイン

- 割込みマスクイベント . 非エンプティ, オーバーフロー, トリガー, アンダーフロー

- DMA をサポートする設定可能な FIFO トリガーレベル

PDM-PCM デコーダーは、一般にデジタル PDM マイクへの接続に使用されます。最大 2 つのマイクを同じ PDM データ回線に接続できます。

#### 3.8.2 CAPSENSE™ サブシステム

CAPSENSE™ は、CAPSENSE™ シグマデルタ (CSD) ハードウェアブロックを介して PSoC™ 6 MCU でサポートされます。高感度の自己容量および相互容量測定用に設計されており、特にユーザーインターフェースソリューション用に構築されています。

CAPSENSE™ に加えて、CSD ハードウェアブロックは 3 つの汎用機能をサポートします。これらは CAPSENSE™ が使用されていないときに利用可能です。あるいは、ファームウェア制御下のアプリケーションで 2 つ以上の機能を時間多重化することもできます。CSD ハードウェアブロックでサポートされる 4 つの機能は次のとおりです。

- CAPSENSE™

- 10 ビット ADC

- プログラマブル電流源 (IDAC)

- コンパレータ

#### CAPSENSE™

静電容量式タッチセンサーは、人体の静電容量に依存してセンサーの上または近くに指の存在を検出するユーザーインターフェース用に設計されます。CAPSENSE™ ソリューションは、IoT, 産業, 自動車, 家電などのアプリケーションに、エレガントで信頼性の高いシンプルな静電容量式タッチセンシング機能をもたらします。

CAPSENSE™ テクノロジーは、次の機能を提供します。

## 機能の説明

- クラス最高の信号対雑音比 (SNR) と過酷でノイズの多い条件下での堅牢なセンシング

- 自己容量 (CSD) および相互容量 (CSX) の検知方法

- ボタン, マトリックスボタン, スライダー, タッチパッド, 近接センサーなど、さまざまな Widget のサポート

- さまざまな材料にわたる高性能センシング

- クラス最高の耐液性

- 複雑な手動調整プロセスを回避するのに役立つ SmartSense 自動調整テクノロジー

- 外部ノイズに対する優れた耐性

- 低放射エミッション用のスペクトラム拡散クロック

- ジェスチャと内蔵のセルフテストライブラリ

- 超低消費電力

- リアルタイムのチューニング, テスト, およびデバッグ用の統合グラフィカル CAPSENSE チューナー

CAPSENSE™ の感度と精度は、GPIO スイッチングノイズの影響を受けます。感度と精度を向上させるには、[Table 6](#) にリストされている GPIO ポート制限を実装し、次の手順を実行してください。

- CAPSENSE™ ピンをポート 6 および 7 に制限してください。

- ポート 6 および 7 で他の GPIO 出力アクティビティがないようにする必要があります。

- ポート 5 と 8 には 2 つ以下の GPIO 出力が必要です。

- 低速スルーレート設定で、ポート 5 および 8 の GPIO 出力スイッチングを 1 MHz に制限してください。

### ADC

CAPSENSE™ サブシステム勾配 ADC は次の機能を提供します。

- 選択可能な 8 または 10 ビットの解像度

- 選択可能な入力範囲: 任意の GPIO 入力で GND から  $V_{REF}$  および GND から  $V_{DDA}$

- GPIO または外部コンポーネントを使用しない内部リファレンスに対する  $V_{DDA}$  の測定

### IDAC

CSD ブロックには、次の機能を提供する 2 つのプログラム可能な電流源があります。

- 7 ビット解像度

- シンクおよびソース電流モード

- 37.5 nA から 609  $\mu$ A までプログラム可能な電流源

- 1 つの 8 ビット IDAC を形成するために並行して使用できる 2 つの IDAC

### コンパレーター

CAPSENSE™ サブシステムコンパレータは、システム低消費電力および超低消費電力モードで動作します。反転入力は内部のプログラム可能な基準電圧に接続され、非反転入力は AMUXBUS を介して任意の GPIO に接続できます。

### CAPSENSE™ ハードウェアサブシステム

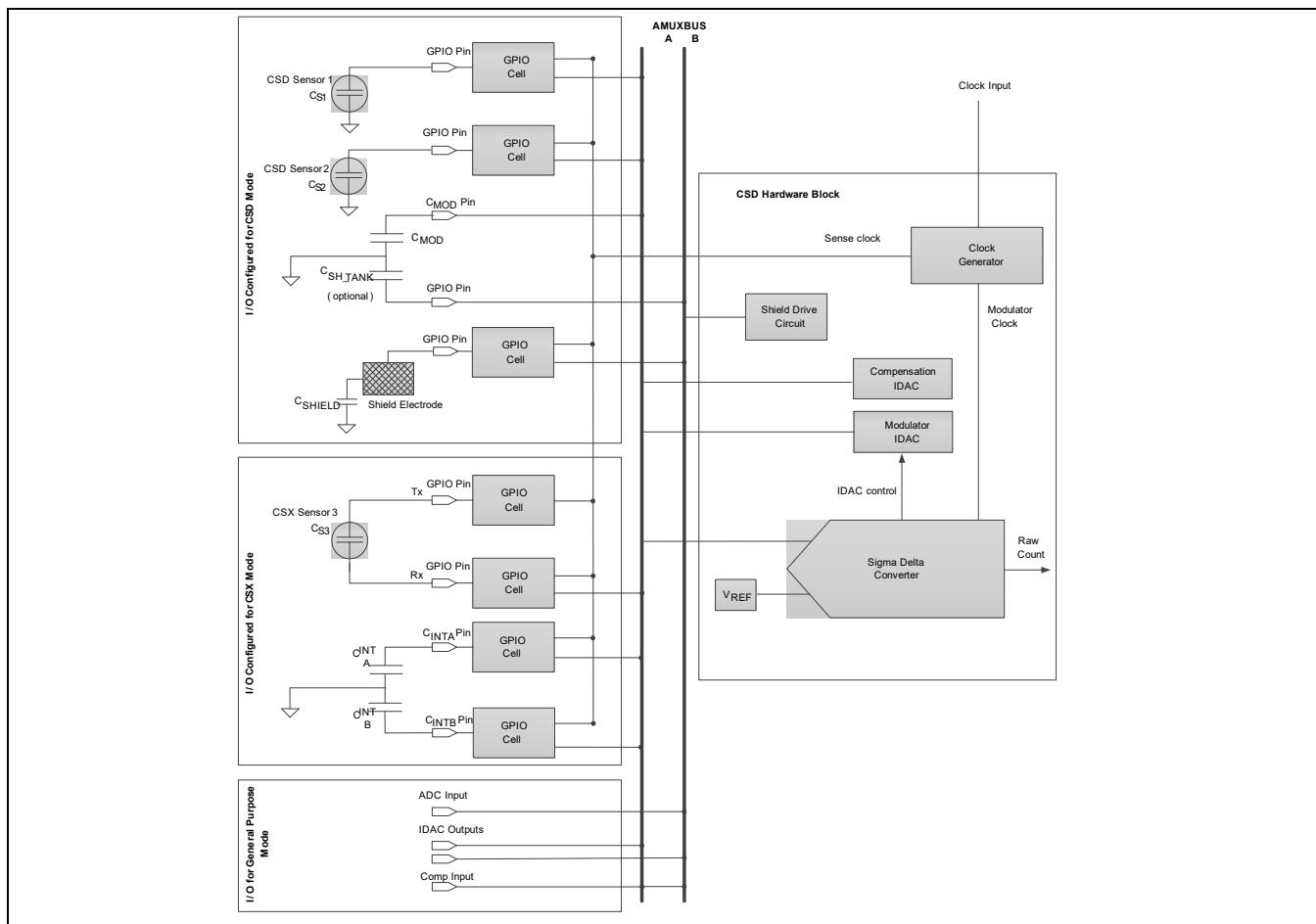

[Figure 9](#) は、デルタシグマコンバータ、内部クロック分周器、シールドドライバー、および 2 つのプログラム可能な電流源を含む CAPSENSE™ サブシステムの高レベルハードウェアの概要を示します。

入力は、アナログ多重化バス (AMUXBUS A/B) を介して管理されます。CSD ブロックが提供するすべての機能の入力と出力は、専用 GPIO を使用するコンパレータ出力と外部コンデンサを除き、ソフトウェア制御下の任意の GPIO または GPIO のグループに提供できます。

自己容量は、AMUXBUS A, 外部変調器コンデンサ、および各センサーの GPIO を使用する CSD ブロックによってサポートされます。自己容量センシング用のシールド電極 (オプション) があります。これは AMUXBUS B とオプションの外部シールドタンクコンデンサを使用してサポートされます (シールドドライバーの駆動能力を高めるため)。相互容量は、AMUXBUS A, 2 つの外部統合コンデンサ、および送信と受信電極用の GPIO を使用する CSD ブロックによってサポートされます。

## 機能の説明

ADCは外部コンポーネントを必要としません。AMUXBUS Aに接続できるGPIOは、ソフトウェア制御下でADCへの入力にできます。ADCは、GPIOを必要とせずにVDDAを入力として受け入れられます(バッテリ電圧測定などのアプリケーション用)。

汎用モードの2つのプログラム可能な電流源(IDAC)は、AMUXBUS AまたはBに接続できます。したがって、それらは任意のGPIOピンに接続できます。コンパレータは、デルタシグマコンバータにあります。コンパレータ反転入力はリファレンスに接続できます。AMUXBUS Bを使用して、両方のコンパレータ入力を任意のGPIOに直接接続します。[Figure 9](#)を参照してください。リファレンスは専用GPIOに直接接続しています。[Table 9](#)を参照してください。

CSD ブロックは、アクティブおよびスリープ CPU 電力モードで動作し、システムの LP モードと ULP モードをシームレスに移行できます。システムのディープスリープおよびハイバネートモードで電源を切れます。ハイバネートモードからウェイクアップすると、CSD ブロックの再初期化が必要です。ただし、ファームウェアの制御下でディープスリープモードを終了すると、再初期化せずに操作を再開できます。

**Figure 9 CAPSENSE™ ハードウェアサブシステム**

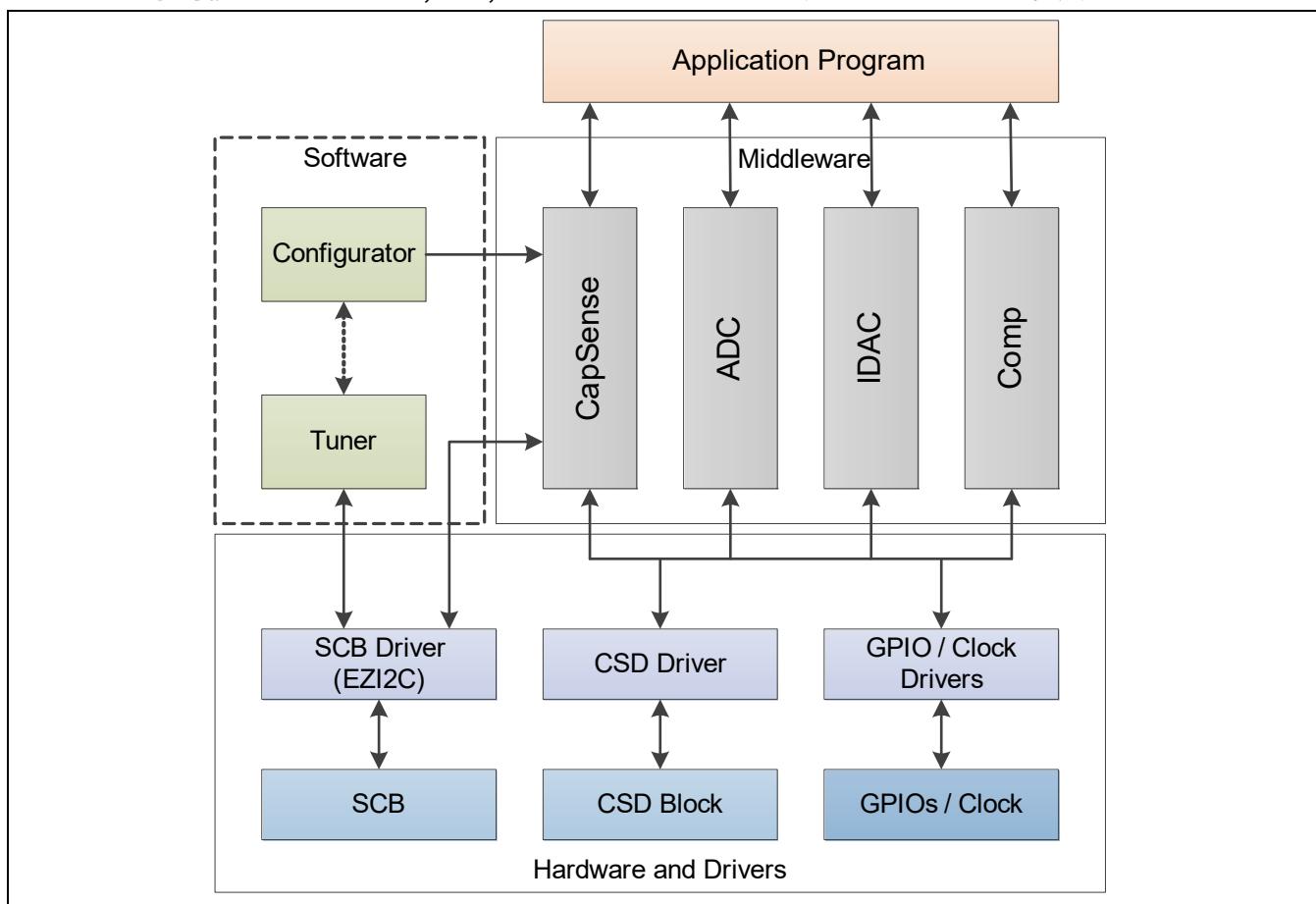

[Figure 10](#) は、高レベルのソフトウェアの概要を示します。インフィニオンは、[CAPSENSE™](#), [ADC](#), および [IDAC](#) のミドルウェアライブラリを GitHub で提供して迅速な統合を可能にします。CAPSENSE™ 機能を備えたキットのボードサポートパッケージには、BSP を使用するすべてのアプリケーションに CAPSENSE™ ライブラリが自動的に含まれます。

ユーザーアプリケーションはミドルウェアとのみ対話して、CSD ブロックの機能を実装します。ミドルウェアは、基盤となるドライバーと対話して、必要に応じてハードウェアにアクセスします。プロジェクトに複数の CSD 関連ミドルウェアが存在する場合、CSD ドライバーは CSD ハードウェアの時分割多重化を容易にします。この場合、アクセスの競合を防ぎます。

ModusToolbox™ ソフトウェアは、高速ライブラリ構成を可能にする CAPSENSE™ コンフィギュレーターを提供します。また、システムのパフォーマンス評価とリアルタイムチューニングのためのチューナーも提供します。チューナーは、リアルタイムのチューニング機能を有効にするために、アプリケーション

## 機能の説明

に EZI2C 通信インターフェースを必要とします。チューナーは、デバイス内およびコンフィギュレーター内で構成パラメーターを直接更新できます。

CAPSENSE™ および ADC ミドルウェアは、CSD 割込みを使用して、ノンブロッキングセンシングと A-D 変換を実装します。したがって、割込みサービスルーチンはミドルウェアの定義済み部分であり、アプリケーションによって初期化する必要があります。ミドルウェアとドライバーはどちらの CPU でも動作できます。サイプレスは、1 つの CPU でのみミドルウェアを使用することを推奨します。両方の CPU が CSD ドライバーにアクセスする必要がある場合、メモリアクセスはアプリケーションで管理する必要があります。

CSX センシング、CSD センシング、シールド電極の使用とその利点、および容量性システム設計ガイドラインの詳細については、[AN85951: PSoC™ 4 and PSoC™ 6 MCU CAPSENSE™ Design Guide](#) を参照してください。

GitHub で入手可能な [CAPSENSE™](#), [ADC](#), および [IDAC](#) の API リファレンスガイドを参照してください。

Figure 10 CAPSENSE™ ソフトウェア / ファームウェアサブシステム

---

## ピン配置

### 4 ピン配置

注 : CY8C63x6/CY8C63x7 データシートの [datasheet web page](#) には、ピン配置と HSIOM マッピングを備えたピン代替機能の統合リストを含むスプレッドシートが含まれます。

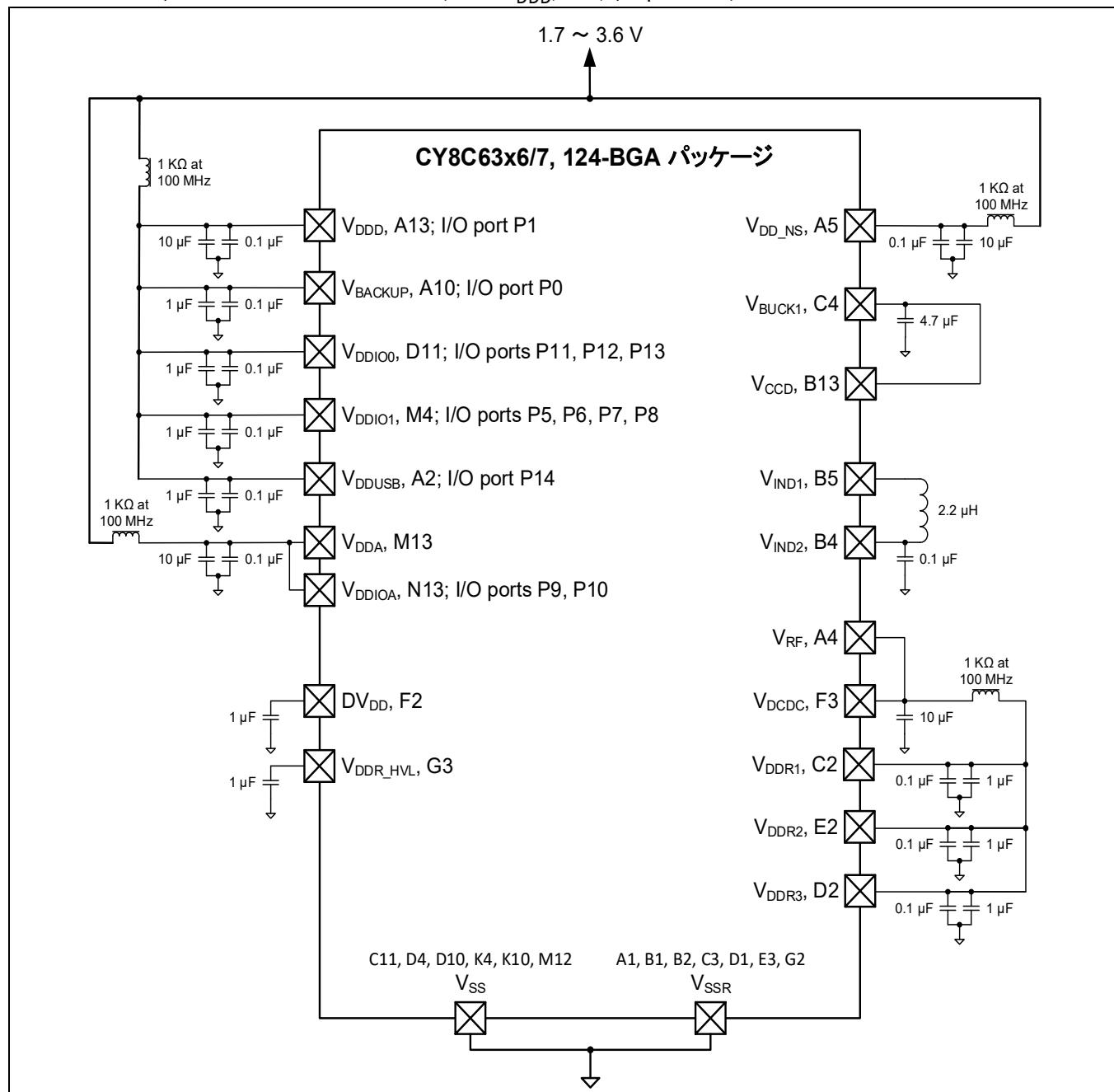

GPIO ポートは次のように  $V_{DDX}$  ピンから電力を供給されます。

- P0:  $V_{BACKUP}$

- P1:  $V_{DDIO}$  ポート 1 の GPIO ピンは過電圧耐性 (OVT) です。

- P5, P6, P7, P8:  $V_{DDIO1}$

- P9, P10:  $V_{DDIOA}$ ,  $V_{DDA}$  ( $V_{DDIOA}$  (存在する場合)、および  $V_{DDA}$  は PCB 上で一緒に接続する必要があります。)

- P11, P12, P13:  $V_{DDIO0}$

- P14:  $V_{DDUSB}$

## ピン配置

Table 7 パッケージおよびピン情報

| ピン                   | パッケージ                         |                                               |                      |                      |         |

|----------------------|-------------------------------|-----------------------------------------------|----------------------|----------------------|---------|

|                      | 124-BGA                       | 116-BGA                                       | 104-M-CSP<br>(USBなし) | 104-M-CSP<br>(USBあり) | 68-QFN  |

| V <sub>DDD</sub>     | A13                           | B1                                            | C6                   |                      | 68      |

| V <sub>CCD</sub>     | B13                           | A2                                            | C7                   |                      | 67      |

| V <sub>DDA</sub>     | M13                           | A9                                            | A1                   |                      | 47      |

| V <sub>DDIOA</sub>   | N13                           | -                                             | -                    |                      | 53      |

| V <sub>DDIO0</sub>   | D11                           | B3                                            | B6                   |                      | 64      |

| V <sub>DDIO1</sub>   | M4                            | G10                                           | D1                   |                      | 43      |

| V <sub>BACKUP</sub>  | A10                           | C1                                            | C9                   |                      | 1       |

| V <sub>DDUSB</sub>   | A2                            | -                                             | -                    | H7                   | -       |

| V <sub>SS</sub>      | C11, D4, D10, K4,<br>K10, M12 | B2, B9, D1, H2, H9                            | D4, D7, F4, G7, P1   |                      | GND PAD |

| V <sub>SSR</sub>     | A1, B1, B2, C3, D1, E3,<br>G2 | J1, K2, K3, K4, K5, L1,<br>L3, L4, L5, M3, M8 | M3, N9, P3, P6, P7   |                      | GND PAD |

| V <sub>DD_NS</sub>   | A5                            | H3                                            | G9                   |                      | 9       |

| V <sub>IND1</sub>    | B5                            | F1                                            | G8                   |                      | 10      |

| V <sub>IND2</sub>    | B4                            | G1                                            | H8                   |                      | 11      |

| V <sub>BUCK1</sub>   | C4                            | G2                                            | J8                   | F9                   | 12      |

| V <sub>RF</sub>      | A4                            | H1                                            | H9                   |                      | 13      |

| V <sub>DCDC</sub>    | F3                            | M7                                            | P4                   |                      | 24      |

| V <sub>DDR1</sub>    | C2                            | L2                                            | L9                   |                      | 15      |

| V <sub>DDR2</sub>    | E2                            | M1                                            | P9                   |                      | 19      |

| V <sub>DDR3</sub>    | D2                            | M2                                            | P8                   |                      | 20      |

| DV <sub>DD</sub>     | F2                            | M6                                            | M4                   |                      | 23      |

| V <sub>DDR_HVL</sub> | G3                            | L7                                            | L2                   |                      | 25      |

| XRES                 | A8                            | E2                                            | E5                   |                      | 8       |

| V <sub>REF</sub>     | N12                           | B10                                           | -                    |                      | 52      |

| ANT                  | C1                            | K1                                            | M9                   |                      | 17      |

| GANT                 | -                             | -                                             | -                    |                      | 16, 18  |

| XI                   | F1                            | M4                                            | M5                   |                      | 21      |

| XO                   | E1                            | M5                                            | P5                   |                      | 22      |

| P0.0                 | C9                            | C2                                            | D8                   |                      | 2       |

| P0.1                 | B9                            | D3                                            | E6                   |                      | 3       |

| P0.2                 | A9                            | E4                                            | D9                   |                      | 4       |

| P0.3                 | C8                            | E3                                            | E7                   |                      | 5       |

| P0.4                 | B8                            | F3                                            | E8                   |                      | 6       |

| P0.5                 | C7                            | D2                                            | E9                   |                      | 7       |

| P1.0                 | B7                            | G3                                            | F5                   |                      | -       |

| P1.1                 | A7                            | F2                                            | F6                   |                      | -       |

| P1.2                 | C6                            | J5                                            | -                    |                      | -       |

| P1.3                 | B6                            | J4                                            | F9                   | -                    | -       |

| P1.4                 | A6                            | J3                                            | F8                   |                      | -       |

| P1.5                 | C5                            | J2                                            | F7                   |                      | -       |

## ピン配置

**Table 7** パッケージおよびピン情報 (continued)

| ピン    | パッケージ   |         |                      |                      |        |

|-------|---------|---------|----------------------|----------------------|--------|

|       | 124-BGA | 116-BGA | 104-M-CSP<br>(USBなし) | 104-M-CSP<br>(USBあり) | 68-QFN |

| P5.0  | G1      | L6      |                      | J7                   | -      |

| P5.1  | H3      | K6      |                      | J5                   | -      |

| P5.2  | H2      | J6      |                      | J6                   | -      |

| P5.3  | H1      | K7      | H7                   | H6                   | -      |

| P5.4  | J3      | J7      | H6                   | H5                   | -      |

| P5.5  | J2      | L8      |                      | J4                   | -      |

| P5.6  | J1      | M9      |                      | K3                   | -      |

| P5.7  | K1      | -       |                      | K4                   | -      |

| P6.0  | K2      | K8      |                      | J3                   | 26     |

| P6.1  | K3      | J8      |                      | K2                   | 28     |

| P6.2  | L3      | L9      |                      | M2                   | 29     |

| P6.3  | L2      | K9      |                      | L1                   | 30     |

| P6.4  | L1      | J9      |                      | J2                   | 31     |

| P6.5  | M2      | M10     |                      | K1                   | 32     |

| P6.6  | M1      | L10     |                      | N2                   | 33     |

| P6.7  | N2      | K10     |                      | M1                   | 34     |

| P7.0  | N3      | J10     |                      | N1                   | 35     |

| P7.1  | M3      | H10     |                      | G6                   | 36     |

| P7.2  | N4      | H8      |                      | H4                   | 37     |

| P7.3  | N1      | H7      |                      | G5                   | 38     |

| P7.4  | L4      | H6      |                      | H3                   | 39     |

| P7.5  | N5      | G9      |                      | H2                   | 40     |

| P7.6  | M5      | G8      |                      | G3                   | 41     |

| P7.7  | L5      | G7      |                      | G2                   | 42     |

| P8.0  | N6      | F10     |                      | G4                   | 44     |

| P8.1  | M6      | F9      |                      | G1                   | 45     |

| P8.2  | L6      | F8      |                      | F3                   | 46     |

| P8.3  | N7      | F7      |                      | F2                   | -      |

| P8.4  | M7      | G6      |                      | F1                   | -      |

| P8.5  | L7      | E9      |                      | E3                   | -      |

| P8.6  | N8      | E8      |                      | E1                   | -      |

| P8.7  | M8      | E7      |                      | E2                   | -      |

| P9.0  | L9      | D10     |                      | D2                   | 48     |

| P9.1  | M9      | D9      |                      | C1                   | 49     |

| P9.2  | N9      | D8      |                      | D3                   | 50     |

| P9.3  | L8      | D7      |                      | B1                   | 51     |

| P9.4  | N10     | C10     |                      | -                    | -      |

| P9.5  | M10     | C9      |                      | -                    | -      |

| P9.6  | L10     | C8      |                      | -                    | -      |

| P9.7  | N11     | C7      |                      | -                    | -      |

| P10.0 | M11     | B8      |                      | C2                   | 54     |

| P10.1 | L13     | A8      |                      | B2                   | 55     |

## ピン配置

**Table 7** パッケージおよびピン情報 (*continued*)

| ピン            | パッケージ   |         |                      |                      |        |

|---------------|---------|---------|----------------------|----------------------|--------|

|               | 124-BGA | 116-BGA | 104-M-CSP<br>(USBなし) | 104-M-CSP<br>(USBあり) | 68-QFN |

| P10.2         | L12     | F6      | C3                   | -                    | -      |

| P10.3         | L11     | E6      | E4                   | -                    | -      |

| P10.4         | K13     | D6      | A2                   | -                    | -      |

| P10.5         | K12     | B7      | A3                   | -                    | -      |

| P10.6         | K11     | A7      | D5                   | -                    | -      |

| P10.7         | J13     | -       | B3                   | -                    | -      |

| P11.0         | J12     | F5      | C4                   | 56                   |        |

| P11.1         | J11     | E5      | C5                   | 57                   |        |

| P11.2         | H13     | D5      | D6                   | 58                   |        |

| P11.3         | H12     | C6      | B4                   | 59                   |        |

| P11.4         | H11     | B6      | A4                   | 60                   |        |

| P11.5         | G13     | A6      | B5                   | 61                   |        |

| P11.6         | G12     | B5      | A5                   | 62                   |        |

| P11.7         | G11     | A5      | A6                   | 63                   |        |

| P12.0         | F13     | A4      | B7                   | -                    |        |

| P12.1         | F12     | B4      | A7                   | -                    |        |

| P12.2         | F11     | C4      | B8                   | -                    |        |

| P12.3         | E13     | A3      | A8                   | -                    |        |

| P12.4         | E12     | C5      | C8                   | -                    |        |

| P12.5         | E11     | D4      | -                    | -                    |        |

| P12.6         | D13     | G5      | -                    | 65                   |        |

| P12.7         | D12     | H5      | -                    | 66                   |        |

| P13.0         | A12     | H4      | A9                   | -                    |        |

| P13.1         | C13     | G4      | B9                   | -                    |        |

| P13.2         | C12     | -       | -                    | -                    |        |

| P13.3         | B12     | -       | -                    | -                    |        |

| P13.4         | B11     | -       | -                    | -                    |        |

| P13.5         | A11     | -       | -                    | -                    |        |

| P13.6         | C10     | F4      | -                    | -                    |        |

| P13.7         | B10     | C3      | -                    | -                    |        |

| P14.0 / USBDP | B3      | -       | -                    | J8                   | -      |

| P14.1 / USBDM | A3      | -       | -                    | J9                   | -      |

| NC            | D3      | -       | H5, J9, P2           | P2                   | 14, 27 |

注: ボール H5 および J9 は、104-M-CSP パッケージのノーコネクト (NC) です。

## ピン配置

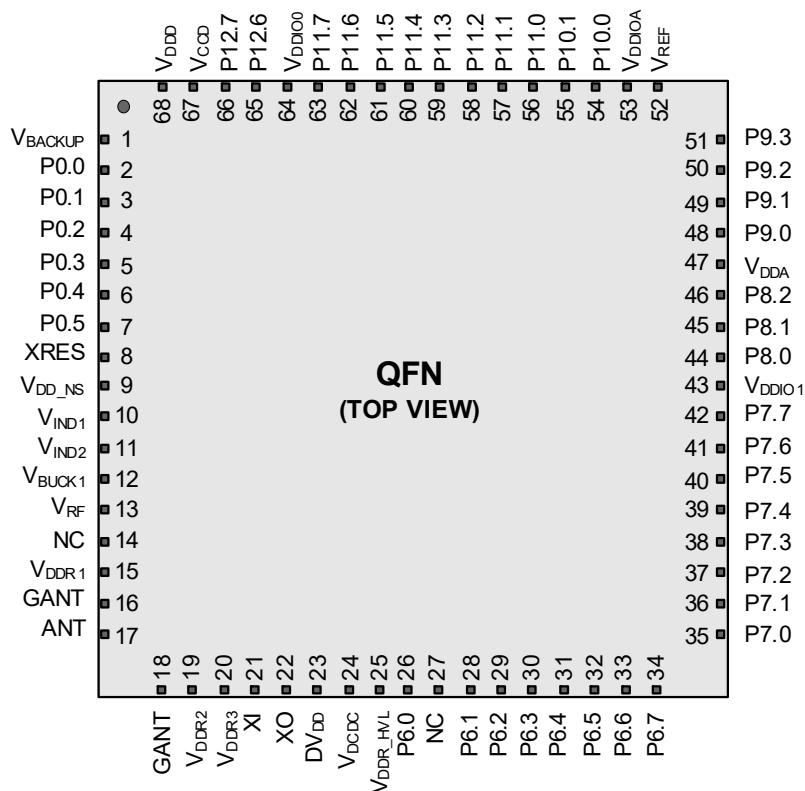

Figure 1168-QFN パッケージのデバイスピン配置<sup>[2]</sup>

**注:** USB ピンを使用しない場合は、V<sub>DDUSB</sub> をグランドに接続し、P14.0/USBDP ピンと P14.1/USBDM ピンは未接続のままにしてください。

## 注

2. 最高の機械的、熱的、および電気的性能を得るために、QFN パッケージのセンターパッドをデバイスの VDDx に対して PCB グランドに接続する必要があります。詳細については、[AN72845](#) QFN デバイスの設計ガイドラインを参照してください。

各ポートピンには複数の代替機能があります。Table 8 に示します。

**Table 8 複数の代替機能<sup>[3]</sup>**

| ポート/<br>ピン | ACT #0                   | ACT #1                    | DS #2 | ACT #4         | ACT #5 | ACT #6            | ACT #7           | ACT #8               | ACT #9 | ACT #10            | ACT #12                 | ACT #13 | ACT #14 | ACT #15 | DS #4           | DS #5 | DS #6 |

|------------|--------------------------|---------------------------|-------|----------------|--------|-------------------|------------------|----------------------|--------|--------------------|-------------------------|---------|---------|---------|-----------------|-------|-------|

| P0.0       | tcpwm[0].line[0]:0       | tcpwm[1].line[0]:0        |       | srss.ext_clk:0 |        |                   |                  | scb[0].spi_select1:0 |        |                    | peri.tr_io_iinput[0]:0  |         |         |         |                 |       |       |

| P0.1       | tcpwm[0].line_compl[0]:0 | tcpwm[1].line_compl[0]:0  |       |                |        |                   |                  | scb[0].spi_select2:0 |        |                    | peri.tr_io_iinput[1]:0  |         |         |         | cpuss.swj_trstn |       |       |

| P0.2       | tcpwm[0].line[1]:0       | tcpwm[1].line[1]:0        |       |                |        | scb[0].uart_rx:0  | scb[0].i2c_scl:0 | scb[0].spi_miso:0    |        |                    |                         |         |         |         |                 |       |       |

| P0.3       | tcpwm[0].line_compl[1]:0 | tcpwm[1].line_compl[1]:0  |       |                |        | scb[0].uart_tx:0  | scb[0].i2c_sda:0 | scb[0].spi_miso:0    |        |                    |                         |         |         |         |                 |       |       |

| P0.4       | tcpwm[0].line[2]:0       | tcpwm[1].line[2]:0        |       |                |        | scb[0].uart_rts:0 |                  | scb[0].spi_clk:0     |        |                    | peri.tr_io_ooutput[0]:2 |         |         |         |                 |       |       |

| P0.5       | tcpwm[0].line_compl[2]:0 | tcpwm[1].line_compl[2]:0  |       | srss.ext_clk:1 |        | scb[0].uart_cts:0 |                  | scb[0].spi_select0:0 |        |                    | peri.tr_io_ooutput[1]:2 |         |         |         |                 |       |       |

| P1.0       | tcpwm[0].line[3]:0       | tcpwm[1].line[3]:0        |       |                |        | scb[7].uart_rx:0  | scb[7].i2c_scl:0 | scb[7].spi_miso:0    |        |                    | peri.tr_io_iinput[2]:0  |         |         |         |                 |       |       |

| P1.1       | tcpwm[0].line_compl[3]:0 | tcpwm[1].line_compl[3]:0  |       |                |        | scb[7].uart_tx:0  | scb[7].i2c_sda:0 | scb[7].spi_miso:0    |        |                    | peri.tr_io_iinput[3]:0  |         |         |         |                 |       |       |

| P1.2       | tcpwm[0].line[4]:4       | tcpwm[1].line[12]:1       |       |                |        | scb[7].uart_rts:0 |                  | scb[7].spi_clk:0     |        |                    |                         |         |         |         |                 |       |       |

| P1.3       | tcpwm[0].line_compl[4]:4 | tcpwm[1].line_compl[12]:1 |       |                |        | scb[7].uart_cts:0 |                  | scb[7].spi_select0:0 |        |                    |                         |         |         |         |                 |       |       |

| P1.4       | tcpwm[0].line[5]:4       | tcpwm[1].line[13]:1       |       |                |        |                   |                  | scb[7].spi_select1:0 |        |                    |                         |         |         |         |                 |       |       |

| P1.5       | tcpwm[0].line_compl[5]:4 | tcpwm[1].line_compl[14]:1 |       |                |        |                   |                  | scb[7].spi_select2:0 |        |                    |                         |         |         |         |                 |       |       |

| P5.0       | tcpwm[0].line[4]:0       | tcpwm[1].line[4]:0        |       |                |        | scb[5].uart_rx:0  | scb[5].i2c_scl:0 | scb[5].spi_miso:0    |        | audioss.clk_i2s_if | peri.tr_io_iinput[10]:0 |         |         |         |                 |       |       |

| P5.1       | tcpwm[0].line_compl[4]:0 | tcpwm[1].line_compl[4]:0  |       |                |        | scb[5].uart_tx:0  | scb[5].i2c_sda:0 | scb[5].spi_miso:0    |        | audioss.tx_sck     | peri.tr_io_iinput[11]:0 |         |         |         |                 |       |       |

| P5.2       | tcpwm[0].line[5]:0       | tcpwm[1].line[5]:0        |       |                |        | scb[5].uart_rts:0 |                  | scb[5].spi_clk:0     |        | audioss.tx_ws      |                         |         |         |         |                 |       |       |

### 注

3. シグナルの表記法は、IPName [x].signal\_name [u]:y の形式です。

IPName = ブロックの名前(tcpwm など)、x = IP の一意のインスタンス、Signal\_name = 信号の名前、u = 特定の信号名に対して複数の信号がある場合の信号番号、y = 信号名のコピーを指定。例えば、tcpwm[0].line\_compl[3]:4 という名前は、これが tcpwm ブロックのインスタンス 0 であり、信号が line\_compl #3(行出力の補数)であり、これが次の 4 回目の出現(コピー)であることを示します。信号コピーは、ルーティングの柔軟性を可能にし、オンチップリソースの利用を最大化するために提供されています。

Table 8 複数の代替機能<sup>[3]</sup> (continued)

| ポート / ピン | ACT #0                   | ACT #1                    | DS #2            | ACT #4 | ACT #5 | ACT #6            | ACT #7           | ACT #8               | ACT #9 | ACT #10        | ACT #12                 | ACT #13                 | ACT #14 | ACT #15 | DS #4 | DS #5                | DS #6                |  |  |

|----------|--------------------------|---------------------------|------------------|--------|--------|-------------------|------------------|----------------------|--------|----------------|-------------------------|-------------------------|---------|---------|-------|----------------------|----------------------|--|--|

| P5.3     | tcpwm[0].line_compl[5]:0 | tcpwm[1].line_compl[5]:0  |                  |        |        | scb[5].uart_cts:0 |                  | scb[5].spi_select0:0 |        | audioss.tx_sdo |                         |                         |         |         |       |                      |                      |  |  |

| P5.4     | tcpwm[0].line[6]:0       | tcpwm[1].line[6]:0        |                  |        |        |                   |                  | scb[5].spi_select1:0 |        | audioss.rx_sck |                         |                         |         |         |       |                      |                      |  |  |

| P5.5     | tcpwm[0].line_compl[6]:0 | tcpwm[1].line_compl[6]:0  |                  |        |        |                   |                  | scb[5].spi_select2:0 |        | audioss.rx_ws  |                         |                         |         |         |       |                      |                      |  |  |

| P5.6     | tcpwm[0].line[7]:0       | tcpwm[1].line[7]:0        |                  |        |        |                   |                  | scb[5].spi_select3:0 |        | audioss.rx_sdi |                         |                         |         |         |       |                      |                      |  |  |

| P5.7     | tcpwm[0].line_compl[7]:0 | tcpwm[1].line_compl[7]:0  |                  |        |        |                   |                  | scb[3].spi_select3:0 |        |                |                         |                         |         |         |       |                      |                      |  |  |

| P6.0     | tcpwm[0].line[8]:0       | tcpwm[1].line[8]:0        | scb[8].i2c_scl:0 |        |        | scb[3].uart_rx:0  | scb[3].i2c_scl:0 | scb[3].spi_miso:0    |        |                | cpuss.fault_out[0]      |                         |         |         |       | scb[8].spi_mosi:0    |                      |  |  |

| P6.1     | tcpwm[0].line_compl[0]:1 | tcpwm[1].line_compl[8]:0  | scb[8].i2c_sda:0 |        |        | scb[3].uart_tx:0  | scb[3].i2c_sda:0 | scb[3].spi_miso:0    |        |                | cpuss.fault_out[1]      |                         |         |         |       | scb[8].spi_miso:0    |                      |  |  |

| P6.2     | tcpwm[0].line[9]:0       | tcpwm[1].line[9]:0        |                  |        |        | scb[3].uart_rts:0 |                  | scb[3].spi_clk:0     |        |                |                         |                         |         |         |       | scb[8].spi_clk:0     |                      |  |  |

| P6.3     | tcpwm[0].line_compl[1]:1 | tcpwm[1].line_compl[9]:0  |                  |        |        | scb[3].uart_cts:0 |                  | scb[3].spi_select0:0 |        |                |                         |                         |         |         |       | scb[8].spi_select0:0 |                      |  |  |

| P6.4     | tcpwm[0].line[10]:0      | tcpwm[1].line[10]:0       | scb[8].i2c_scl:1 |        |        | scb[6].uart_rx:2  | scb[6].i2c_scl:2 | scb[6].spi_mosi:2    |        |                | peri.tr_io_i_nput[12]:0 | peri.tr_io_o_utput[0]:1 |         |         |       | cpuss.swj_sw_o_tdo   | scb[8].spi_mosi:1    |  |  |

| P6.5     | tcpwm[0].line_compl[2]:1 | tcpwm[1].line_compl[10]:0 | scb[8].i2c_sda:1 |        |        | scb[6].uart_tx:2  | scb[6].i2c_sda:2 | scb[6].spi_miso:2    |        |                | peri.tr_io_i_nput[13]:0 | peri.tr_io_o_utput[1]:1 |         |         |       | cpuss.swj_sw_o_tdi   | scb[8].spi_miso:1    |  |  |

| P6.6     | tcpwm[0].line[11]:0      | tcpwm[1].line[11]:0       |                  |        |        | scb[6].uart_rts:2 |                  | scb[6].spi_clk:2     |        |                |                         |                         |         |         |       | cpuss.swj_sw_o_tms   | scb[8].spi_clk:1     |  |  |

| P6.7     | tcpwm[0].line_compl[3]:1 | tcpwm[1].line_compl[11]:0 |                  |        |        | scb[6].uart_cts:2 |                  | scb[6].spi_select0:2 |        |                |                         |                         |         |         |       | cpuss.swj_sw_o_tclk  | scb[8].spi_select0:1 |  |  |

| P7.0     | tcpwm[0].line[12]:0      | tcpwm[1].line[12]:0       |                  |        |        | scb[4].uart_rx:1  | scb[4].i2c_scl:1 | scb[4].spi_mosi:1    |        |                | peri.tr_io_i_nput[14]:0 | cpuss.trace_clock       |         |         |       |                      |                      |  |  |

| P7.1     | tcpwm[0].line_compl[4]:1 | tcpwm[1].line_compl[12]:0 |                  |        |        | scb[4].uart_tx:1  | scb[4].i2c_sda:1 | scb[4].spi_miso:1    |        |                | peri.tr_io_i_nput[15]:0 |                         |         |         |       |                      |                      |  |  |

| P7.2     | tcpwm[0].line[13]:0      | tcpwm[1].line[13]:0       |                  |        |        | scb[4].uart_rts:1 |                  | scb[4].spi_clk:1     |        |                |                         |                         |         |         |       |                      |                      |  |  |

## 注

3. シグナルの表記法は、IPName[x].signal\_name[u]:y の形式です。

IPName = ブロックの名前 (tcpwm など)、x = IP の一意のインスタンス、Signal\_name = 信号の名前、u = 特定の信号名に対して複数の信号がある場合の信号番号、y = 信号名のコピーを指定。例えば、tcpwm[0].line\_compl[3]:4 という名前は、これが tcpwm ブロックのインスタンス 0 であり、信号が line\_compl #3 (行出力の補数) であり、これが次の 4 回目の出現(コピー)であることを示します。

信号コピーは、ルーティングの柔軟性を可能にし、オンチップリソースの利用を最大化するために提供されています。

Table 8 複数の代替機能<sup>[3]</sup> (continued)

| ポート / ピン | ACT #0                   | ACT #1                    | DS #2 | ACT #4 | ACT #5 | ACT #6            | ACT #7           | ACT #8               | ACT #9            | ACT #10             | ACT #12                 | ACT #13                      | ACT #14               | ACT #15 | DS #4 | DS #5 | DS #6 |

|----------|--------------------------|---------------------------|-------|--------|--------|-------------------|------------------|----------------------|-------------------|---------------------|-------------------------|------------------------------|-----------------------|---------|-------|-------|-------|

| P7.3     | tcpwm[0].line_compl[5]:1 | tcpwm[1].line_compl[13]:0 |       |        |        | scb[4].uart_cts:1 |                  | scb[4].spi_select0:1 |                   |                     |                         |                              |                       |         |       |       |       |

| P7.4     | tcpwm[0].line[6]:1       | tcpwm[1].line[14]:0       |       |        |        |                   |                  | scb[4].spi_select1:1 |                   |                     |                         | bless.ext_lna_rx_ctl_out     | cpuss.trace_data[3]:2 |         |       |       |       |

| P7.5     | tcpwm[0].line_compl[6]:1 | tcpwm[1].line_compl[14]:0 |       |        |        |                   |                  | scb[4].spi_select2:1 |                   |                     |                         | bless.ext_pa_tx_ctl_out      | cpuss.trace_data[2]:2 |         |       |       |       |

| P7.6     | tcpwm[0].line[7]:1       | tcpwm[1].line[15]:0       |       |        |        |                   |                  | scb[4].spi_select3:1 |                   |                     |                         | bless.ext_pa_lna_chip_en_out | cpuss.trace_data[1]:2 |         |       |       |       |

| P7.7     | tcpwm[0].line_compl[7]:1 | tcpwm[1].line_compl[15]:0 |       |        |        |                   |                  | scb[3].spi_select1:0 | cpuss.clk_fm_pump |                     |                         |                              | cpuss.trace_data[0]:2 |         |       |       |       |

| P8.0     | tcpwm[0].line[0]:2       | tcpwm[1].line[16]:0       |       |        |        | scb[4].uart_rx:0  | scb[4].i2c_scl:0 | scb[4].spi_miso:0    |                   |                     | peri.tr_io_iinput[16]:0 |                              |                       |         |       |       |       |

| P8.1     | tcpwm[0].line_compl[0]:2 | tcpwm[1].line_compl[16]:0 |       |        |        | scb[4].uart_tx:0  | scb[4].i2c_sda:0 | scb[4].spi_miso:0    |                   |                     | peri.tr_io_iinput[17]:0 |                              |                       |         |       |       |       |

| P8.2     | tcpwm[0].line[1]:2       | tcpwm[1].line[17]:0       |       |        |        | scb[4].uart_rts:0 |                  | scb[4].spi_clk:0     |                   |                     |                         |                              |                       |         |       |       |       |

| P8.3     | tcpwm[0].line_compl[1]:2 | tcpwm[1].line_compl[17]:0 |       |        |        | scb[4].uart_cts:0 |                  | scb[4].spi_select0:0 |                   |                     |                         |                              |                       |         |       |       |       |

| P8.4     | tcpwm[0].line[2]:2       | tcpwm[1].line[18]:0       |       |        |        |                   |                  | scb[4].spi_select1:0 |                   |                     |                         |                              |                       |         |       |       |       |

| P8.5     | tcpwm[0].line_compl[2]:2 | tcpwm[1].line_compl[18]:0 |       |        |        |                   |                  | scb[4].spi_select2:0 |                   |                     |                         |                              |                       |         |       |       |       |

| P8.6     | tcpwm[0].line[3]:2       | tcpwm[1].line[19]:0       |       |        |        |                   |                  | scb[4].spi_select3:0 |                   |                     |                         |                              |                       |         |       |       |       |