### **Datasheet**

Trusted authentication for Qi charging

Easy-to-integrate solution for Qi authentication in automotive wireless charging

applications

# **Devices**

#### SLS37CSAE20TC

This document describes a solution for Qi authentication. The Qi standard is issued by the WPC (http://www.wirelesspowerconsortium.com). Please refer to WPC website for protocol details. Requirements for this **Provisioned Secure Storage Subsystems** are also defined in the **Manufacturer CA Agreement** between WPC and the provider of the HSM. This agreement may be confidential.

# **Key features**

## **SLS37CSAE20TC Qi authentication solution**

## **Easy integration**

- Full turnkey solution for authentication for wireless charging (Qi2 and higher)

- Full system integration support

- Customer specific certificate provided (provisioning)

- Host code and application notes for common host controller available

- Evaluation kit available

### Certificates and cryptographic algorithms

- X.509/WPC certificate format supported

- Authentication based on ECDSA NIST-P256

- Cryptography support: ECC256, RNG (GET\_RANDOM), SCP03

### Other key features

- SPI GP protocol

- Secure Channel over SPI using GlobalPlatform SCP03 (optional)

- In-field Update Mechanism (optional)

- 32 pin VQFN Package (5 mm x 5 mm)

- AEC-Q100 REV.G (Grade 2)

#### **Deliverables**

- Secure Storage Subsystem in line with Qi Specification

- Provisioned with device-unique key material and certificate(s) (in certified manufacturing site, Drivers and host software for integration with host controller)

### WPC Qi compliant certificate chain

• Infineon offers the service to act as a "WPC Manufacturer CA". Infineon will create Manufacturer CA certificates for Secure Storage Subsystems in Qi certified devices; Creation and loading of unit specific keys and certificates will take place in certified and audited production sites

### **Security certification**

Based on certified hardware according to Common Criteria Protection Profile (PP0084)

#### **Datasheet**

### **Target applications**

#### **Hardware**

- Tamper resistant security controller providing highest proven assets protection

- High performance crypto accelerator

- Shielding and sensors against physical and logical attacks, internal memory and bus encryption

- Memory

- Based on reliable, certifiable SOLID FLASH™ NVM technology and protected by encryption and additional error detection

- 17 years of data retention

- High-speed SPI interface up to 10 MHz

- Single voltage supply from 1.62 V to 3.6 V

# **Target applications**

SLS37CSAE20TC is a provisioned secure storage subsystem as defined by the Qi2 (and higher) standard. It offers core functionality for the authentication procedure to establish and verify the authenticity of a certified Power Transmitter to a Power Receiver. Being AEC-Q100 REV.G (Grade 2) qualified, SLS37CSAE20TC is optimized for use in automotive applications.

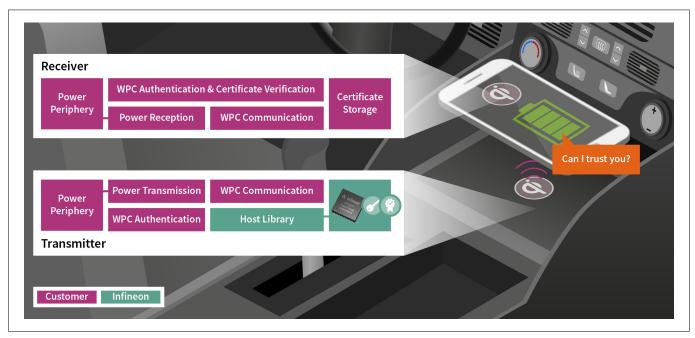

Figure 1 shows simplified the components of a power transmitter and power receiver according to the Qi authentication protocol.

Figure 1 Exemplary Wireless Charging System Architecture

### **Datasheet**

**About this document**

# **About this document**

### **Scope and purpose**

This datasheet provides an overview of the hardware, the software features and functionalities and information about the package characteristics of the OPTIGA™ Trust Charge Automotive.

Note:

OPTIGA™ Trust Charge Automotive secure storage subsystem is also referred to as HSM or

SLS37CSAE20TC.

### Intended audience

This datasheet is primarily intended for system developers. Target customers are automotive Original Equipment Manufacturers (OEMs), their Tier 1 suppliers as well as software partners.

# **Datasheet**

# **Table of contents**

# **Table of contents**

|         | Burlana                                                        |    |

|---------|----------------------------------------------------------------|----|

|         | Devices                                                        |    |

|         | Key features                                                   | 1  |

|         | Target applications                                            | 2  |

|         | About this document                                            | 3  |

|         | Table of contents                                              | 4  |

|         | List of tables                                                 | 6  |

|         | List of figures                                                | 7  |

| 1       | General description                                            | 8  |

| 1.1     | Overview                                                       | 8  |

| 1.2     | Main features and benefits                                     |    |

| 1.2.1   | Chip side hardware features                                    | 10 |

| 1.2.2   | Chip side software features                                    | 11 |

| 1.2.3   | Infineon OPTIGA™ Trust Charge Automotive host software package | 11 |

| 1.3     | Applications and use cases                                     |    |

| 1.4     | AEC-Q100 in-cabin qualification                                | 13 |

| 2       | Block diagram                                                  | 14 |

| 3       | Pin description                                                | 15 |

| 3.1     | Abbreviations in pin description                               | 15 |

| 3.2     | Pad-to-signal reference                                        | 16 |

| 3.3     | Typical schematic                                              | 18 |

| 3.4     | CAD files                                                      | 18 |

| 4       | HSM firmware                                                   | 19 |

| 5       | Electrical characteristics                                     | 20 |

| 5.1     | Absolute maximum ratings                                       | 20 |

| 5.2     | Operational characteristics                                    | 21 |

| 5.2.1   | DC electrical characteristics                                  | 21 |

| 5.2.2   | AC electrical characteristics                                  | 21 |

| 5.2.2.1 | Power-up considerations                                        | 22 |

| 5.3     | Particular interface characteristics                           | 23 |

| 5.3.1   | GPIO interface characteristics                                 | 23 |

| 5.3.2   | SPI interface characteristics                                  | 25 |

| 5.4     | Thermal resistance                                             | 29 |

| 5.5     | Storage and transport conditions                               | 29 |

| 5.6     | IBIS Model                                                     | 29 |

| 6       | Package description                                            | 30 |

| 6.1     | PG-VQFN-32-13                                                  | 30 |

# **Table of contents**

| 6.1.1 | Package outline                   | 30 |

|-------|-----------------------------------|----|

| 6.1.2 | Package footprint                 | 31 |

| 6.1.3 | Tape and reel packing             | 31 |

| 6.1.4 | Production sample marking pattern | 32 |

|       | References                        | 33 |

|       | Glossary                          | 34 |

|       | Revision history                  | 37 |

|       | RoHS compliance                   | 38 |

|       | Disclaimer                        | 39 |

# **Datasheet**

# infineon

# List of tables

# **List of tables**

| Table 1  | Abbreviations for pin type                                           | 15 |

|----------|----------------------------------------------------------------------|----|

| Table 2  | Abbreviations for buffer type                                        | 15 |

| Table 3  | I/O signals                                                          |    |

| Table 4  | Power supply                                                         | 17 |

| Table 5  | Not connected                                                        | 17 |

| Table 6  | Absolute maximum ratings                                             | 20 |

| Table 7  | DC characteristics                                                   | 21 |

| Table 8  | AC characteristics                                                   | 21 |

| Table 9  | GPIO operation supply and input voltages                             | 23 |

| Table 10 | GPIO DC electrical characteristics                                   | 23 |

| Table 11 | GPIO AC electrical characteristics                                   | 24 |

| Table 12 | Serial transfer mode                                                 |    |

| Table 13 | DC characteristics for 3.3 V supply voltage range                    | 25 |

| Table 14 | DC characteristics for 1.8 V supply voltage range                    | 26 |

| Table 15 | AC characteristics for 1.8 V and 3.3 V supply voltage range (Mode 0) | 26 |

| Table 16 | Thermal resistance                                                   |    |

| Table 17 | Storage and transport conditions                                     | 29 |

| Table 18 | Marking table for PG-VQFN-32-13 packages                             | 32 |

# **Datasheet**

**List of figures**

# **List of figures**

| Figure 1  | Exemplary Wireless Charging System Architecture |    |

|-----------|-------------------------------------------------|----|

| Figure 2  | OPTIGA™ Trust Charge Automotive Software Stack  |    |

| Figure 3  | Block diagram of the HSM                        | 14 |

| Figure 4  | PG-VQFN-32-13 package layout                    |    |

| Figure 5  | Typical schematic                               | 18 |

| Figure 6  | Recommended power-up behavior                   | 22 |

| Figure 7  | SPI Mode 0                                      |    |

| Figure 8  | Timing diagram Mode 0                           |    |

| Figure 9  | PG-VQFN-32-13 package outline                   | 30 |

| Figure 10 | PG-VQFN-32-13 package footprint                 |    |

| Figure 11 | PG-VQFN-32-13 tape and reel packing             | 31 |

| Figure 12 | PG-VQFN-32-13 sample marking pattern            | 32 |

|           |                                                 |    |

#### **Datasheet**

### 1 General description

#### **General description** 1

#### 1.1 **Overview**

The Infineon SLS37CSAE20TC OPTIGA™ Trust Charge Automotive is a provisioned secure storage subsystem in line with the WPC Qi2 (and higher) standard. OPTIGA™ Trust Charge Automotive offers core functions for the authentication of a Oi Power Transmitter to a Oi Power Receiver. Being based on a highly-secured, tamper resistant security controller with highest proven asset protection, this secure storage subsystem protects the private key that is associated with the public key in the Product Unit Certificate of Qi certified products and offers functions to prove the authenticity via ECDSA signing operations.

The hardware architecture is based on 32-bit ARM® SecureCore® SC300 CPU with an additional high performance asymmetric cryptographic engine and the latest generation of an hardware co-processor for symmetric cryptography.

The OPTIGA™ Trust Charge Automotive herein called Provisioned Secure Storage Subsystem, is interfacing to a host processor via SPI. With the OPTIGA™ Trust Charge Automotive being based on certified hardware according to Common Criteria (CC) EAL6+ high and AEC-Q100 (Grade 2) qualification, it is optimized for Automotive Security, meeting both the requirements of the harsh environment in the automotive industry as well as the highest security levels for the implementation of security and cryptography in cars. In addition, it fully meets the requirements for a Provisioned Secure Storage Subsystem in line with the WPC Oi2 (and higher) Specification.

The CC certificate can be found at https://www.tuv-nederland.nl/common-criteria/certificates.html by searching for the Hardware Identifier IFX\_CCI\_00005Ah and referring to the latest CC certificate.

The Qi standard is issued by the WPC (www.wirelesspowerconsortium.com). Please refer to WPC website for protocol details. Requirements for this **Provisioned Secure Storage Subsystems** are also defined in the Manufacturer CA Agreement between WPC and the provider of the Oi authenticator. This agreement may be confidential.

SLS37CSAE20TC comes pre-programmed with Infineon OPTIGA™ Trust Charge Automotive firmware and is ready-to-use.

Major blocks of the OPTIGA™ Trust Charge Automotive firmware in SLS37CSAE20TC are the embedded operating system and the Qi authentication protocol. In combination, they are providing high performance functionality including cryptographic operations (e.g. ECDSA signature generation), certificate and key storage/ management. Both, the Qi authentication and the underlying operating system, are based on the latest WPC standards and market requirements. This software is developed according to secure coding standards and security certifications.

For ease of use and faster time-to-market the SLS37CSAE20TC is complemented with a Host Software Package. This software package encompasses demo code to be included into the software running on the host- or application processor the SLS37CSAE20TC is connected to intending to facilitate an easy integration.

Within this setup SLS37CSAE20TC, provides the host-processor with secured storage of private keys and performs the respective cryptographic operations.

This includes but is not limited to:

- ECC private key management (generation, import, and deletion)

- ECDSA signature generation

- Storage of private keys and certificate data

- Infineon PKI provides customer-individual keys enabling a secured pairing between SLS37CSAE20TC and the respective host processor as well as secured in-field updates

Figure 1 shows a typical wireless charging system. The SLS37CSAE20TC in combination with the Host Software Package provide prepared communication messages according to the WPC Qi2 Authentication Protocol.

#### **Datasheet**

## 1 General description

#### 1.2 Main features and benefits

### **Easy integration**

- Full turnkey solution for Qi authentication for wireless charging

- Full system integration support

- Customer and chip unique certificates provided (provisioning)

- Host code and application notes for common host controllers available

- Evaluation kit available

### **Security features**

- Tamper resistant hardware platform enabling secured key storage and trusted execution of the respective cryptographic operations

- X.509 certificate format according to the WPC Qi2 supported

- Authentication based on ECDSA NIST-P256

- Cryptography support: ECC256, RNG (GET RANDOM), SCP03

- Optimized for use in automotive Qi certified systems, i.e. harsh automotive environments as well as highest security levels

- SPI GP protocol

- Secure Channel over SPI using GlobalPlatform SCP03

- In-field Update Mechanism

- VQFN32 package

- AEC-Q100 REV.G Grade 2

SLS37CSAE20TC is a Provisioned Secure Storage Subsystem in line with the WPC Oi2 standard. It is a plug-andplay security solution that allows manufacturers of Qi certified devices to implement the standard compliant (WPC Qi2 and higher) authentication procedure with very limited additional effort in software development and system integration and thus helps to reduce the total cost of ownership of the complete system.

#### **Datasheet**

### 1 General description

#### 1.2.1 **Chip side hardware features**

- 32-bit ARM® SecurCore® SC300 @100 MHz

- Secured storage inside the security controller leveraging SOLID FLASH™ which combines flexible flash memory technology with a sophisticated security mechanism and highest reliability

- Ultra Low Power design CMOS technology

- SPI Interface up to 10 MHz

- Symmetric co-processor (AES)

- Asymmetric co-processors: High Performance Cryptographic Engine (Crypto@2304T) for ECC calculations

- True and Pseudo Random Number Generator

- Hybrid Random Number Generation (TRNG and PRNG) according to latest BSI AIS20/31 and NIST SP800- A and B statistical tests

- Supply voltage range: 1.62 V to 3.63 V

- Extended temperature range: -40°C to +105°C

- All memories are protected by hardware Error Correction Code and Error Detection Code

- Security Sensors (Frequency, Light, Temperature, Glitch, Voltage)

- Unique chip tracking number stored into each chip

- **High Endurance**

- Data retention of 17 years

- Qualification according to AEC-Q100 (Grade 2)

- PPAP documentation

- ESD protection 2 kV (HBM)

- Package: VQFN32-13 SMD package (5 mm x 5 mm), CAD files available on request

#### **Datasheet**

### 1 General description

#### 1.2.2 Chip side software features

The OPTIGA™ Trust Charge Automotive application of SLS37CSAE20TC exposes its features to the host by providing an APDU Command Interface (API).

This API includes a set of features including reporting, management, storage and crypto functionalities required for the WPC Qi2 Authentication protocol including but not limited to the following:

- ECC key pair generation on the chip

- ECDSA sign

- NIST P-256/P-384

- Secured storage for up to 4 private keys

- Secured storage for up to 4 certificate chains each 2048 Bytes with configurable access conditions per user (write/read/change)

- RNG (GET RANDOM)

- Secure Channel Protocol 03 (SCP03) based on GlobalPlatform Card Specification v2.3 Amendment D Version 1.1.2

- Authentication scheme and user rights management including:

- Different users with configurable access rights

- Each user with key/password enabling dedicated encrypted and authenticated messaging channel (based on AES-256-CBC and AES-256-CMAC)

- Life cycle management: Supporting different life cycle states with different access conditions for each state and transition

- Secured and protected in-field update mechanism with rollback-prevention

- Minimal downtime during firmware update:

- Fast image signature verification

- Fast verified image installation (replaces current image)

- Data (private keys and certificate chains) stored in NVM is not impacted by the firmware update

#### **SPI Device Drivers and Protocols**

- SPI protocol implementing "GlobalPlatform APDU Transport over SPI/I2C Version 1.0" standard

- APDU compatible with ISO/IEC 7816-4: 2013

#### 1.2.3 Infineon OPTIGA™ Trust Charge Automotive host software package

For ease of integration OPTIGA™ Trust Charge Automotive offers a host software package abstracting its functionality and offering the corresponding functions to a host controller. The host software is developed with high re-usability in mind. Therefore the integration is split into two parts:

- The platform-independent core (OPTIGA™ Trust Charge Automotive Host Software.zip) contains the main logic for the OPTIGA™ Trust Charge Automotive host integration as well as examples on how to use the provided API

- It uses a custom platform abstraction layer (PAL) to be as generic as possible. When porting the integration to a new hardware platform the core can be reused as is.

- Platform-specific integrations (for example: OPTIGA™ Trust Charge Automotive Host Software AURIX™ TC3xx.zip) build on top of the core and add platform-specific implementations of the PAL

To be able to use the OPTIGA™ Trust Charge Automotive host integration you will at least need the core package as well as a platform integration matching your desired host platform and toolchain.

For more information on the core package please refer to its provided documentation. For an overview of the available platform integrations refer to your Infineon downloads or contact Infineon sales representative.

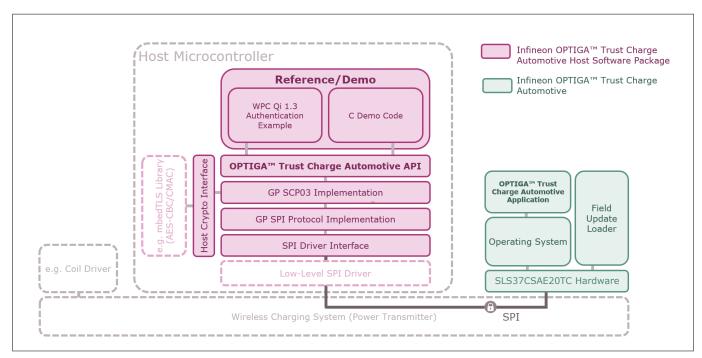

An overview of the components of the host software package is shown in Figure 2.

#### **Datasheet**

### 1 General description

Figure 2 **OPTIGA™** Trust Charge Automotive Software Stack

Figure 2 shows a generic wireless charging system, the middle section represents the code running on the host processor (OPTIGA™ Trust Charge Automotive host software package), the section on the right side reflects the software or firmware residing on the chip (SLS37CSAE20TC).

The OPTIGA™ Trust Charge Automotive Host Software Package consists of a demo module, which shows how to integrate and use the security controller or the target wireless charging system on a host platform. The Host Software Package is delivered as demo source code for the Evaluation Kit. Due to the modular approach, it is easy to use, to adapt or to integrate in other embedded systems.

#### **Features**

- Complete OPTIGA™ Trust Charge Automotive API Library with access to all APDU commands delivered as C source code including SPI protocol implementation and Global Platform Secure Channel Protocol 03 (SCP03)

- Example scripts for Initialization, WPC Oi Authentication messages preparation Application Note, In-Field Update, etc. delivered as C source code

- Wrapper functions for Host-side crypto (mbedTLS) and Host SPI driver for easy porting onto other platforms

#### 1.3 Applications and use cases

The Infineon security controller is a Provisioned Secure Storage Subsystem in line with WPC Qi2 (and higher) and as such is a turnkey authentication solution offering core functions for the authentication of a Qi certified Power Transmitter to a Power Receiver for the wireless charging use case.

### Power Transmitter authentication according to the WPC Qi Authentication

The secure storage subsystem offers core functions for the authentication procedure of a Qi certified power transmitter according to the latest WPC Qi2 Specification. Functions include, but are not limited to, secured storage of ECC private keys, Product Unit Certificate(s) and related certificate chain(s) and ECDSA signature generation as core function in order to prove the authenticity of a Qi certified device. Each chip has up to 4 private key and 4 file slots to store WPC Qi compliant certificate chains.

# **Datasheet**

# 1 General description

#### **AEC-Q100 in-cabin qualification** 1.4

Due to the security requirements for the OPTIGA™ Trust Charge Automotive, some features and tests, which might usually be available for a normal automotive component, are not possible and can not be provided:

- Re-Test and SCAN-Test are not possible

- No Design-FMEA exists for this product

The Infineon security division is not IATF 16949 certified. Note:

# infineon

2 Block diagram

# 2 Block diagram

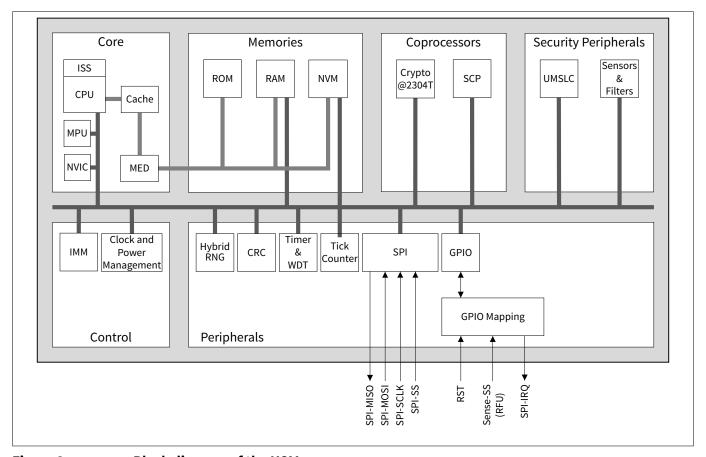

Figure 3 shows the hardware block diagram of the HSM.

Figure 3 Block diagram of the HSM

# **Datasheet**

# infineon

3 Pin description

# 3 Pin description

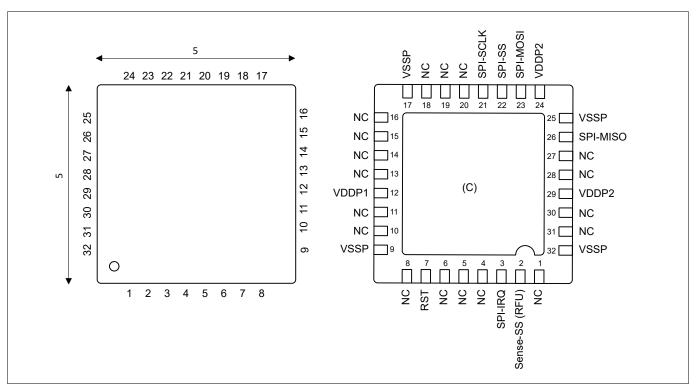

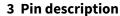

The pad usage of the HSM in a 32 pin VQFN package is illustrated by the next figure and table. A detailed description of the package can be found in Package description.

# 3.1 Abbreviations in pin description

The abbreviations listed here are used in the package description to classify each pin.

Table 1 Abbreviations for pin type

| Abbreviation                                                                | Description                                           |  |  |  |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| DNC Do Not Connect. Must be left floating. Please do not connect externally |                                                       |  |  |  |  |

| I                                                                           | Input. Digital levels                                 |  |  |  |  |

| 0                                                                           | Output. Digital levels                                |  |  |  |  |

| I/O                                                                         | Input/Output bi-directional. Digital levels           |  |  |  |  |

| PWR                                                                         | Power                                                 |  |  |  |  |

| GND                                                                         | Ground                                                |  |  |  |  |

| NCI                                                                         | Not Connected Internally. May be connected externally |  |  |  |  |

# Table 2 Abbreviations for buffer type

| Abbreviation | Description     |

|--------------|-----------------|

| GPIO_I       | GPIO input pad  |

| GPIO_O       | GPIO output pad |

| SPI_I        | SPI input pad   |

| SPI_O        | SPI output pad  |

3 Pin description

# **Datasheet**

#### Pad-to-signal reference 3.2

For the integration of OPTIGA™ Trust Charge Automotive onto a dedicated PCB board, the power supply, ground, the SPI interface pins and the additional pins have to be connected as shown in the following layout and tables:

Figure 4 PG-VQFN-32-13 package layout

Table 3 I/O signals

| Pad | Name     | Pin type | <b>Buffer type</b> | Signal function/remark                                                                                                                                                                                          |

|-----|----------|----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Sense-SS | I        | GPIO_I             | Shortcut to Pin 22 (SPI-SS sensing). Reserved for future use.                                                                                                                                                   |

| 3   | SPI-IRQ  | 0        | GPIO_O             | Interrupt Request, active high, host interrupt triggered on rising edge (SPI response ready) This pin is optional and does not have to be used. In this case, do not connect the pin and leave the pin floating |

| 7   | RST      | I        | GPIO_I             | Reset, active low, Evaluated by software after start-up, Internal pull-up This pin is optional and does not have to be used. In this case, do not connect the pin and leave the pin floating                    |

| 21  | SPI-SCLK | I        | SPI_I              | SPI Clock The SPI clock signal. Only SPI mode 0 (CPOL = 0, CPHA = 0) is supported by the device.                                                                                                                |

# **Datasheet**

# 3 Pin description

#### (continued) I/O signals Table 3

| Pad | Name     | Pin type | Buffer type | Signal function/remark                       |

|-----|----------|----------|-------------|----------------------------------------------|

| 22  | SPI-SS   | I        | SPI_I       | Slave Select, active low                     |

|     |          |          |             | The SPI chip slave select signal             |

|     |          |          |             | No internal pull-up                          |

| 23  | SPI-MOSI | I        | SPI_I       | SPI Master Out Slave In (SPI Data)           |

|     |          |          |             | SPI data which is received from the master   |

| 26  | SPI-MISO | 0        | SPI_O       | SPI Master In Slave Out (SPI Data)           |

|     |          |          |             | SPI data which is sent to the SPI bus master |

#### Table 4 **Power supply**

| Pad              | Name  | Pin type | Buffer type | Signal function/remark                      |

|------------------|-------|----------|-------------|---------------------------------------------|

| 9, 17, 25,<br>32 | VSSP  | GND      | -           | Power supply: Common ground reference (VSS) |

| 12               | VDDP1 | PWR      | -           | Power supply: Chip power                    |

| 24, 29           | VDDP2 | PWR      | -           | Power supply: Chip power                    |

#### Table 5 **Not connected**

| Pad         | Name | Pin type | Buffer type | Signal function/remark                                             |

|-------------|------|----------|-------------|--------------------------------------------------------------------|

| 6, 19, 20,  | NC   | DNC      | -           | Do Not Connect                                                     |

| 27, 28      |      |          |             | All pins must not be connected externally (must be left floating). |

| 1, 4, 5, 8, | NC   | NCI      | -           | Not Connected Internally                                           |

| 10, 11, 13, |      |          |             | All pins are not connected internally (can be                      |

| 14, 15, 16, |      |          |             | connected externally).                                             |

| 18, 30, 31  |      |          |             | ,                                                                  |

Note:

The exposed die pad referenced as (C) in Figure 4 must be connected to the common ground reference (GND) for heat distribution.

### **Datasheet**

# 3.3 Typical schematic

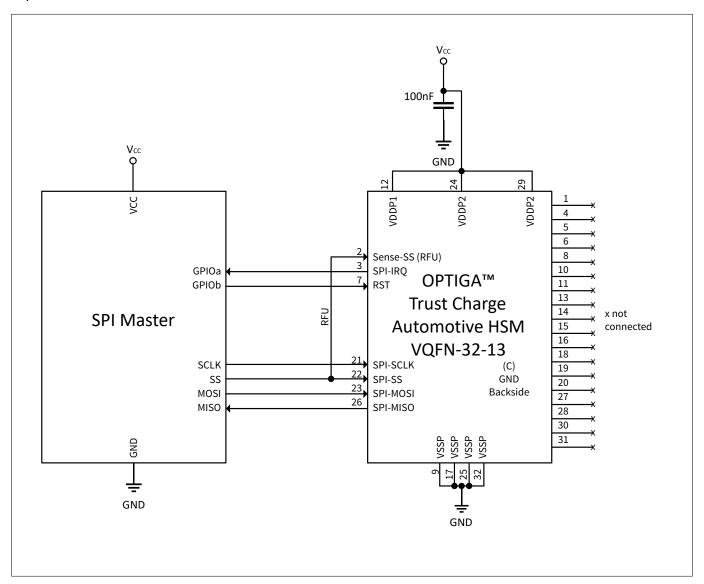

Figure 5 shows the typical schematic for the HSM. The power supply pins should be bypassed to GND with capacitors located close to the device.

Figure 5 Typical schematic

# 3.4 CAD files

CAD files for design-in of the HSM are available on request.

# $\mathbf{OPTIGA^{\mathsf{TM}}} \ \mathbf{Trust} \ \mathbf{Charge} \ \mathbf{Automotive}$

# **Datasheet**

# infineon

4 HSM firmware

# 4 HSM firmware

The HSM firmware is described in detail in the corresponding chapter of the OPTIGA™ Trust Charge Automotive databook.

#### **Datasheet**

### **5 Electrical characteristics**

#### **Electrical characteristics** 5

This section summarizes certain electrical characteristics of the controller. It provides operational characteristics as well as electrical DC and AC characteristics and particular interface characteristics.

$T_{\rm A}$  as given for the operating temperature range of the controller unless otherwise stated. Note:

All currents flowing into the controller are considered positive. Note:

V<sub>CC</sub> is connected to VDDP1 and VDDP2. Throughout this document VDDP1 and VDDP2 will simply be Note:

referred to as  $V_{CC}$ .

#### **Absolute maximum ratings** 5.1

#### Table 6 **Absolute maximum ratings**

| Parameter                                 | Symbol               |      | Values |      |    | Note or test condition                                   |  |

|-------------------------------------------|----------------------|------|--------|------|----|----------------------------------------------------------|--|

|                                           |                      | Min. | Тур.   | Max. |    |                                                          |  |

| Operating temperature, ambient            | T <sub>A</sub>       | -40  | _      | +105 | °C | T <sub>J</sub> must be kept                              |  |

| Junction temperature                      | TJ                   | _    | _      | +110 | °C | -                                                        |  |

| Supply voltage                            | V <sub>CC</sub>      | -0.3 | _      | 7.0  | V  | -                                                        |  |

| Input voltage, signal group <i>GPIO</i>   | V <sub>IN_GPIO</sub> | -0.3 | _      | 7.0  | V  |                                                          |  |

| Input voltage,<br>signal group <i>SPI</i> | V <sub>IN_SPI</sub>  | -0.5 | -      | 7.0  | V  | -                                                        |  |

| ESD robustness HBM                        | V <sub>ESD,HBM</sub> | -    | -      | 2000 | V  | According to EIA/JESD22-<br>A114-B                       |  |

| ESD robustness CDM                        | V <sub>ESD,CDM</sub> | -    | _      | 750  | V  | According to ESD Association<br>Standard STM5.3.1 - 1999 |  |

| Latchup immunity                          | I <sub>latch</sub>   | -    | _      | 150  | mA | According to EIA/JESD78<br>105°C, class II               |  |

Note:

Stresses exceeding the values listed under 'Absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions whose values exceed those indicated in the operational sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability, including NVM data retention and write/erase endurance.

### **Datasheet**

### **5 Electrical characteristics**

#### 5.2 **Operational characteristics**

This section specifies the AC and DC characteristics of the controller, along with details relating to the specific interfaces provided by the controller.

#### DC electrical characteristics 5.2.1

Table 7 **DC** characteristics

| Parameter            | Symbol                  | Values |      |      | Unit | Note or test condition                                                                                                                        |  |

|----------------------|-------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      |                         | Min.   | Тур. | Мах. |      |                                                                                                                                               |  |

| Supply voltage       | V <sub>CC</sub>         | 2.97   | 3.3  | 3.63 | V    | Overall functional range                                                                                                                      |  |

|                      |                         | 1.62   | 1.8  | 1.98 |      |                                                                                                                                               |  |

| Supply current       | / <sub>VCC_Active</sub> | -      | 16.0 | -    | mA   | During startup sporadic spikes up to 32 mA might occur                                                                                        |  |

| Supply current sleep | / <sub>VCCS_Sleep</sub> | -      | 120  | 200  | μΑ   | RST inactive (= $V_{CC}$ ),<br>SPI-IRQ inactive (= GND),<br>SPI-SS inactive (= $V_{CC}$ ),<br>SPI-MOSI, SPI-MISO and SPI-<br>SCLK do not care |  |

Current consumption does not include any currents flowing through resistive loads on output pins! Note:

#### **AC electrical characteristics** 5.2.2

Table 8 **AC characteristics**

| Parameter                   | Symbol            |      | Values |      | Unit | Note or test condition                                         |  |

|-----------------------------|-------------------|------|--------|------|------|----------------------------------------------------------------|--|

|                             |                   | Min. | Тур.   | Max. |      |                                                                |  |

| V <sub>CC</sub> rampup time | t <sub>VCCR</sub> | 1    | -      | -    | μs   | 0 to 100% of V <sub>CC</sub> target voltage ramp <sup>1)</sup> |  |

Please refer to Power-up considerations 1)

## **Datasheet**

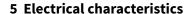

#### 5.2.2.1 **Power-up considerations**

The rampup times given in AC electrical characteristics apply under the assumption of a linear rise in voltage from 0% to 100% of the target voltage level. However, owing to possible current spike effects, it is recommended to follow the voltage characteristics shown in the figure below.

Figure 6 Recommended power-up behavior

### **Datasheet**

# 5 Electrical characteristics

# **5.3** Particular interface characteristics

This chapter provides electrical characteristics with respect to operation of particular interfaces of the controller.

Note:

Unless otherwise stated, all values in this section are measured at the pins of the used package, i.e., the resistance, capacitance and inductance, for example, of the package and the bond wires are already included in these values!

# **5.3.1 GPIO** interface characteristics

The electrical characteristics of the GPIOs including restrictions with respect to the maximum sink/source currents for all GPIOs of the controller are given below.

Table 9 GPIO operation supply and input voltages

| Parameter              | Symbol               | Values |      |                       | Unit | Note or test condition                                 |

|------------------------|----------------------|--------|------|-----------------------|------|--------------------------------------------------------|

|                        |                      | Min.   | Тур. | Max.                  |      |                                                        |

| GPIO pad input voltage | V <sub>IN_GPIO</sub> | -0.3   | _    | V <sub>CC</sub> + 0.3 | V    | $V_{\rm CC}^{1/2}$ is in the operational supply range. |

1) Table 7

Table 10 GPIO DC electrical characteristics

| Parameter                                  | Symbol           |                       | Values |                       | Unit | Note or test condition                                                  |

|--------------------------------------------|------------------|-----------------------|--------|-----------------------|------|-------------------------------------------------------------------------|

|                                            |                  | Min.                  | Тур.   | Max.                  |      |                                                                         |

| Input current, pull-up (weak) enabled      | I <sub>PUW</sub> | -3                    | _      | -20                   | μΑ   | $0 \text{ V} \le V_{\text{IN\_GPIO}} \le V_{\text{CC}} - 0.5 \text{ V}$ |

| Input current, pull-down<br>(weak) enabled | I <sub>PDW</sub> | 3                     | -      | 20                    | μΑ   | $0.5 \text{ V} \le V_{\text{IN\_GPIO}} \le V_{\text{CC}}$               |

| Pull-up (strong)<br>resistance             | R <sub>PUS</sub> | 2.5                   | -      | 5.5                   | kΩ   | $0 \text{ V} \le V_{\text{IN\_GPIO}} \le V_{\text{CC}} - 0.5 \text{ V}$ |

| Input leakage current                      | I <sub>LI</sub>  | -2                    | -      | 2                     | μΑ   | Pull-up/down off, output stage off;                                     |

|                                            |                  |                       |        |                       |      | $0 \text{ V} \leq V_{\text{IN\_GPIO}} \leq V_{\text{CC}}$               |

| Input low voltage                          | V <sub>IL</sub>  | -0.3                  | _      | 0.3 * V <sub>CC</sub> | V    |                                                                         |

| Input high voltage                         | $V_{IH}$         | 0.7 * V <sub>CC</sub> | _      | $V_{CC} + 0.3$        | V    |                                                                         |

| Output low voltage                         | V <sub>OL</sub>  | -                     | _      | 0.3                   | V    | I <sub>OL</sub> = 1 mA                                                  |

|                                            |                  | -                     | _      | 0.4                   | V    | $I_{OL} = 4 \text{ mA}, V_{CC} \ge 2.7 \text{ V}$                       |

| Output high voltage                        | V <sub>OH</sub>  | V <sub>CC</sub> - 0.3 | _      | -                     | V    | I <sub>OH</sub> = −1 mA                                                 |

|                                            |                  | V <sub>CC</sub> - 0.4 | _      | -                     | V    | $I_{OH} = -4 \text{ mA}, V_{CC} \ge 2.7 \text{ V}$                      |

| Input capacitance                          | C <sub>IN</sub>  | _                     | _      | 10                    | pF   |                                                                         |

# **Datasheet**

# **5 Electrical characteristics**

Table 11 GPIO AC electrical characteristics

| Parameter                          | Symbol                            |      | Values |      | Unit | Note or test condition                                                                                   |

|------------------------------------|-----------------------------------|------|--------|------|------|----------------------------------------------------------------------------------------------------------|

|                                    |                                   | Min. | Тур.   | Max. |      |                                                                                                          |

| Output signal rise time            | t <sub>r</sub>                    | -    | 3.5    | 15.0 | ns   | 10% V <sub>CC</sub> to 90% V <sub>CC</sub> ;                                                             |

|                                    |                                   |      |        |      |      | C <sub>LOAD</sub> = 15 pF, pull-up/down off, no DC load.                                                 |

| Output signal fall time            | t <sub>f</sub>                    | _    | 3.5    | 15.0 | ns   | 90% V <sub>CC</sub> to 10% V <sub>CC</sub> ;                                                             |

|                                    |                                   |      |        |      |      | C <sub>LOAD</sub> = 15 pF, pull-up/down off, no DC load; Slew Rate Control OFF (default operation mode). |

| Output signal fall time            | t <sub>f</sub>                    | 30.0 | 50.0   | _    | ns   | 70% V <sub>CC</sub> to 30% V <sub>CC</sub> ;                                                             |

|                                    |                                   |      |        |      |      | C <sub>LOAD</sub> = 50 pF, pull-up/down off, no DC load; slower slew rate.                               |

| Output signal fall time            | t <sub>f</sub>                    | 15.0 | 25.0   | _    | ns   | 70% V <sub>CC</sub> to 30% V <sub>CC</sub> ;                                                             |

|                                    |                                   |      |        |      |      | C <sub>LOAD</sub> = 50 pF, pull-up/down off, no DC load; faster slew rate.                               |

| GPIO input path low-pass filter    | $f_{CUTOFF}$                      | 20   | -      | 40   | MHz  | 50/50 duty cycle.                                                                                        |

| GPIO input path<br>low-pass filter | t <sub>CUTOFF</sub> <sup>1)</sup> | 12.5 | -      | 25   | ns   | High or low pulse width.                                                                                 |

<sup>1)</sup> Spikes shorter than min. are filtered, spikes longer than max. are not filtered.

### **Datasheet**

### 5 Electrical characteristics

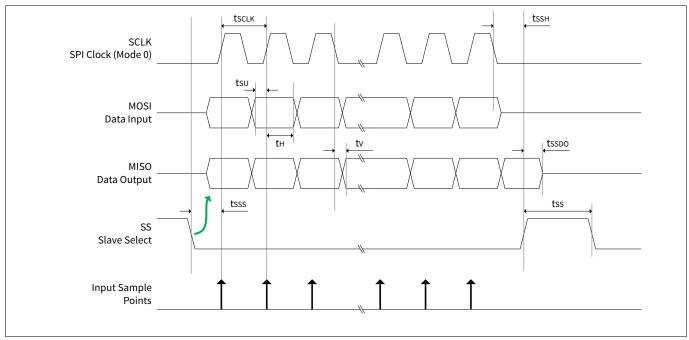

## **5.3.2** SPI interface characteristics

The HSM operates as SPI Slave. The clock signal is received from an external master and synchronizes the data transfer. Transmission and reception speeds are not depending on the internal system clock.

The HSM is configured for SPI mode 0 where polarity and phase is set to 0.

The assertion of the slave select signal starts the transfer. The rising clock edge is used to latch the incoming data bit while the falling clock edge shifts the next data bit onto the serial bus.

The following section describes the electrical characteristics of the SPI slave mode.

Table 12 Serial transfer mode

| Polarity | Phase | SPI<br>Mode | Description                                                                                                                                                                                                                                                                          |

|----------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0     | 0           | Signal transmission through MISO and MOSI pads is activated on assertion of slave select signal (green arrow in Figure 7). Data is latched by the receiver on the rising clock edge and is shifted by the transmitter on the falling clock edge. The idle state of the clock is low. |

Figure 7 SPI Mode 0

**Note**: A detailed timing diagram is shown in Figure 8 and the respective values are given in Table 15.

Table 13 DC characteristics for 3.3 V supply voltage range

| Parameter           | Symbol          |                       | Unit | Note or test condition |   |                           |

|---------------------|-----------------|-----------------------|------|------------------------|---|---------------------------|

|                     |                 | Min.                  | Тур. | Max.                   |   |                           |

| Pad supply voltage  | V <sub>CC</sub> | 2.70                  | _    | 3.63                   | V |                           |

| Input high voltage  | V <sub>IH</sub> | 0.7 * V <sub>CC</sub> | _    | V <sub>CC</sub> + 0.5  | V |                           |

| Input low voltage   | V <sub>IL</sub> | -0.5                  | _    | 0.3 * V <sub>CC</sub>  | V |                           |

| Output high voltage | V <sub>OH</sub> | 0.9 * V <sub>CC</sub> | _    | -                      | V | / <sub>OH</sub> = -100 μA |

| Output low voltage  | V <sub>OL</sub> | _                     | _    | 0.1 * V <sub>CC</sub>  | V | I <sub>OL</sub> = 1.5 mA  |

# **Datasheet**

# **5 Electrical characteristics**

Table 13 (continued) DC characteristics for 3.3 V supply voltage range

| Parameter                      | Symbol           | Values |      |      | Unit | Note or test condition                              |

|--------------------------------|------------------|--------|------|------|------|-----------------------------------------------------|

|                                |                  | Min.   | Тур. | Max. |      |                                                     |

| Pad leakage SPI input          | I <sub>SIL</sub> | -4     | _    | 4    | μΑ   | 0 V < V <sub>PAD</sub> < V <sub>CC</sub>            |

| pads                           |                  | -1.5   | _    | -    | mA   | $-0.5 \text{ V} < V_{PAD} < V_{CC} + 0.5 \text{ V}$ |

| Pad leakage SPI output<br>pads | I <sub>SOL</sub> | -4     | _    | 4    | μΑ   | 0 V < V <sub>PAD</sub> < V <sub>CC</sub>            |

|                                |                  | -3     | _    | -    | mA   | $-0.5 \text{ V} < V_{PAD} < V_{CC} + 0.5 \text{ V}$ |

Table 14 DC characteristics for 1.8 V supply voltage range

| Parameter             | Symbol           |                       | Values | i                     | Unit | Note or test condition                              |

|-----------------------|------------------|-----------------------|--------|-----------------------|------|-----------------------------------------------------|

|                       |                  | Min.                  | Тур.   | Max.                  |      |                                                     |

| Pad supply voltage    | V <sub>CC</sub>  | 1.62                  | -      | 1.98                  | V    |                                                     |

| Input high voltage    | V <sub>IH</sub>  | 0.7 * V <sub>CC</sub> | _      | V <sub>CC</sub> + 0.3 | V    |                                                     |

| Input low voltage     | V <sub>IL</sub>  | -0.3                  | _      | 0.3 * V <sub>CC</sub> | V    |                                                     |

| Output high voltage   | V <sub>OH</sub>  | 0.9 * V <sub>CC</sub> | _      | _                     | V    | I <sub>OH</sub> = -100 μA                           |

| Output low voltage    | V <sub>OL</sub>  | _                     | _      | 0.1 * V <sub>CC</sub> | V    | I <sub>OL</sub> = 1.5 mA                            |

| Pad leakage SPI input | I <sub>SIL</sub> | -4                    | _      | 4                     | μΑ   | 0 V < V <sub>PAD</sub> < V <sub>CC</sub>            |

| pads                  |                  | -1                    | _      | _                     | mA   | $-0.3 \text{ V} < V_{PAD} < V_{CC} + 0.3 \text{ V}$ |

| Pad leakage SPI       | I <sub>SOL</sub> | -4                    | _      | 4                     | μΑ   | 0 V < V <sub>PAD</sub> < V <sub>CC</sub>            |

| output pads           |                  | -1                    | -      | _                     | mA   | $-0.3 \text{ V} < V_{PAD} < V_{CC} + 0.3 \text{ V}$ |

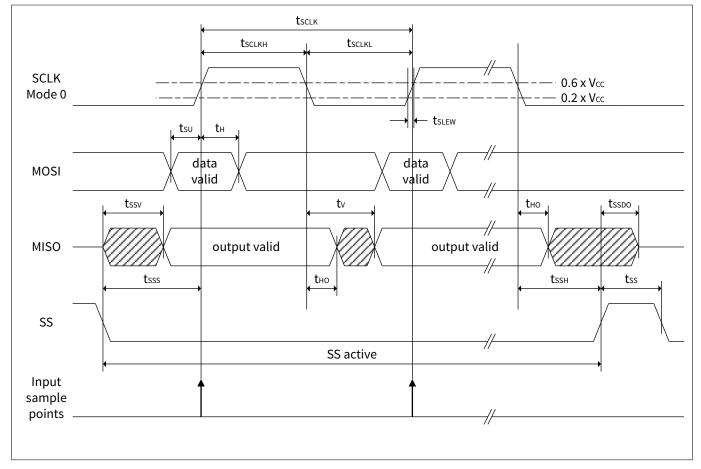

Table 15 AC characteristics for 1.8 V and 3.3 V supply voltage range (Mode 0)

| Parameter                 | Symbol                  |                          | Values                  | <b>;</b>                 | Unit | Note or test condition                                 |

|---------------------------|-------------------------|--------------------------|-------------------------|--------------------------|------|--------------------------------------------------------|

|                           |                         | Min.                     | Тур.                    | Max.                     |      |                                                        |

| SCLK frequency            | $f_{SCLK}$              | -                        | -                       | 10                       | MHz  | For 3.3 V supply voltage range                         |

|                           |                         | _                        | -                       | 10                       | MHz  | For 1.8 V supply voltage range                         |

| SCLK clock period         | t <sub>SCLK_range</sub> | 1/f <sub>SCLK</sub> - 5% | _                       | 1/f <sub>SCLK</sub> + 5% | μs   | Measured at input pad voltage of 0.5 * $V_{\rm CC}$    |

| SCLK nominal clock period | t <sub>SCLK</sub>       | _                        | 1/<br>f <sub>SCLK</sub> | _                        | μs   | Measured at input pad voltage of 0.5 * V <sub>CC</sub> |

| SCLK low time             | t <sub>SCLKL</sub>      | 0.45 * t <sub>SCLK</sub> | _                       | _                        | μs   | Measured at input pad voltage of 0.5 * V <sub>CC</sub> |

| SCLK high time            | t <sub>SCLKH</sub>      | 0.45 * t <sub>SCLK</sub> | -                       | _                        | μs   | Measured at input pad voltage of 0.5 * V <sub>CC</sub> |

| SCLK input slew-rate      | $t_{Slew}$              | 1                        | _                       | 4                        | V/ns | SCLK input voltage slew-rate measured between          |

|                           |                         |                          |                         |                          |      | 0.2 * V <sub>CC</sub> and 0.6 * V <sub>CC</sub>        |

# **Datasheet**

# **5 Electrical characteristics**

Table 15 (continued) AC characteristics for 1.8 V and 3.3 V supply voltage range (Mode 0)

| Parameter                               | Symbol            |      | Values |      | Unit | Note or test condition                                                                                                                                                   |

|-----------------------------------------|-------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |                   | Min. | Тур.   | Max. |      |                                                                                                                                                                          |

| SS inactive time                        | $t_{SS}$          | 30   | _      | -    | ns   | For 3.3 V supply voltage range                                                                                                                                           |

|                                         |                   | 60   | -      | -    | ns   | For 1.8 V supply voltage range                                                                                                                                           |

| SS setup time                           | $t_{\rm SSS}$     | 30   | -      | -    | ns   | For 3.3 V supply voltage range:<br>Setup time SS to SCLK rising<br>edge.                                                                                                 |

|                                         |                   | 60   | -      | -    | ns   | For 1.8 V supply voltage range:<br>Setup time SS to SCLK rising<br>edge.                                                                                                 |

| SS hold time                            | t <sub>SSH</sub>  | 5    | -      | -    | ns   | Hold time SCLK falling edge to SS inactive                                                                                                                               |

| MOSI setup time                         | t <sub>SU</sub>   | 2    | _      | _    | ns   | Data setup time to SCLK rising edge                                                                                                                                      |

| MOSI hold time                          | t <sub>H</sub>    | 3    | -      | -    | ns   | Data hold time from SCLK rising edge                                                                                                                                     |

| MISO valid delay time from SS active    | t <sub>SSV</sub>  | -    | -      | 28   | ns   | For 3.3 V supply voltage range:<br>Output valid delay time from<br>SS active                                                                                             |

|                                         |                   | -    | -      | 58   | ns   | For 1.8 V supply voltage range:<br>Output valid delay time from<br>SS active                                                                                             |

| MISO valid delay time<br>from SCLK edge | t <sub>V</sub>    | -    | -      | 21   | ns   | For 1.8 V supply voltage range Output valid delay time from SCLK falling edge SCLK input $t_{\rm slew} = 1  \rm V/ns$ MISO $C_{\rm load} = 30  \rm pF$                   |

|                                         |                   | -    | -      | 15   | ns   | For 3.3 V supply voltage range<br>Output valid delay time from<br>SCLK falling edge<br>SCLK input $t_{\rm slew} = 1  \text{V/ns}$<br>MISO $C_{\rm load} = 30  \text{pF}$ |

| MISO output disable time                | t <sub>SSDO</sub> | 0    | -      | 30   | ns   | For 3.3 V supply voltage range:<br>Output disable time from SS<br>inactive                                                                                               |

|                                         |                   | 0    | -      | 60   | ns   | For 1.8 V supply voltage range:<br>Output disable time from SS<br>inactive                                                                                               |

### **5 Electrical characteristics**

Table 15 (continued) AC characteristics for 1.8 V and 3.3 V supply voltage range (Mode 0)

| Parameter                       | Symbol          |      | Values |      | Unit | Note or test condition                                                                                                                                                |

|---------------------------------|-----------------|------|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                 | Min. | Тур.   | Max. |      |                                                                                                                                                                       |

| MISO hold time                  | t <sub>HO</sub> | 3.5  | -      | -    | ns   | For 1.8 V supply voltage range Output hold time to SCLK falling edge SCLK input $t_{\rm slew}$ = 4 V/ns MISO $C_{\rm load}$ = 10 pF                                   |

|                                 |                 | 1.5  | -      | -    | ns   | For 3.3 V supply voltage range<br>Output hold time to SCLK<br>falling edge<br>SCLK input $t_{\text{slew}} = 4 \text{ V/ns}$<br>MISO $C_{\text{load}} = 10 \text{ pF}$ |

| Input capacitance (package pin) | C <sub>IN</sub> | -    |        | 10   | pF   |                                                                                                                                                                       |

| Output load capacitance         | $C_{LOAD}$      | _    |        | 30   | pF   | A bigger load capacitance will decrease the performance.                                                                                                              |

**Note**: All values and timings in Table 15 are related to pin level.

Figure 8 Timing diagram Mode 0

#### **Datasheet**

#### 5 Electrical characteristics

# 5.4 Thermal resistance

Table 16 Thermal resistance

| Parameter           | Symbol Values |      |      |      |     | Note or test condition                |

|---------------------|---------------|------|------|------|-----|---------------------------------------|

|                     |               | Min. | Тур. | Max. |     |                                       |

| Junction to case    | $R_{th(JC)}$  | _    | 10.1 | _    | K/W | To exposed pad (bottom) <sup>1)</sup> |

|                     | $R_{th(JC)}$  | _    | 35.4 | _    | K/W | To top of package <sup>2)</sup>       |

| Junction to ambient | $R_{th(JA)}$  | -    | 37.2 | _    | K/W | 1) 3)                                 |

<sup>1)</sup> Not subject to production test, specified by design.

As shown in Table 6, a maximum junction temperature T<sub>J</sub> of 110°C must not be exceeded. Thermal simulations (done using the FEM software ANSYS°) show that this junction temperature T<sub>J</sub> limit is not reached at an ambient temperature of 105°C when the device is mounted on a PCB according to JEDEC 2s2p (JESD 51-7, JESD 51-5). If the device is mounted on a PCB compliant to JEDEC 1s0p (JESD 51-3), the simulation shows that due to self-

heating of the device, the maximum junction temperature is exceeded at an ambient temperature of 105°C.

# 5.5 Storage and transport conditions

Table 17 Storage and transport conditions

| Parameter                           | Symbol          | Values |      |                 | Unit  |

|-------------------------------------|-----------------|--------|------|-----------------|-------|

|                                     |                 | Min.   | Тур. | Max.            |       |

| Storage conditions                  |                 |        |      |                 | •     |

| Storage temperature                 | $T_{Storage}$   | +5     | _    | +40             | °C    |

| Storage humidity                    | RH              | 10     |      | 75              | %     |

| Storage time                        |                 |        |      | 3 <sup>1)</sup> | Years |

| Transport conditions                |                 | '      |      |                 |       |

| Transport temperature <sup>2)</sup> | $T_{Transport}$ | -25    | _    | +85             | °C    |

<sup>1)</sup> In reference to date code on BPL (Barcode Product Label).

Products shall be processed before the end of the maximum storage time defined above. Processing beyond expiring date may increase the risk of reduced processability, malfunction or non-function. Such recommendations are subject to storage time and storage conditions. Temperature, relative humidity, packing medium and environmental conditions.

### 5.6 IBIS Model

IBIS model is available on request.

<sup>2)</sup> https://www.infineon.com/cms/en/product/packages/PG-VQFN/PG-VQFN-32-13/

<sup>3)</sup> According to JEDEC JESD 51-5, JESD 51-7 at free convection and radiation on FR4 2s2p board. Board size 76.2 mm x 114.3 mm x 1.5 mm, 2 inner copper layers (35 μm), thermal via array under the exposed pad connected to the first inner copper layer. Also refer to <sup>2)</sup>.

BPL can be found on the Infineon packing.

<sup>2)</sup> short term ≤ 15 days

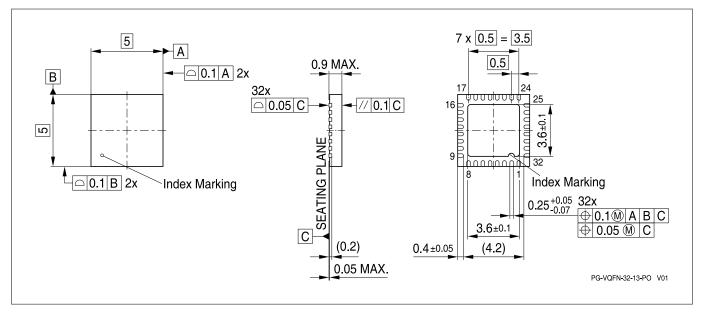

# 6 Package description

#### **Package description** 6

A detailed description of the package can be found under the following link: https://www.infineon.com/cms/en/product/packages/PG-VQFN/PG-VQFN-32-13/

#### **PG-VQFN-32-13** 6.1

Note:

The drawings below are for information only and not drawn to scale. More detailed information about package characteristics and assembly instructions is available on request.

#### Package outline 6.1.1

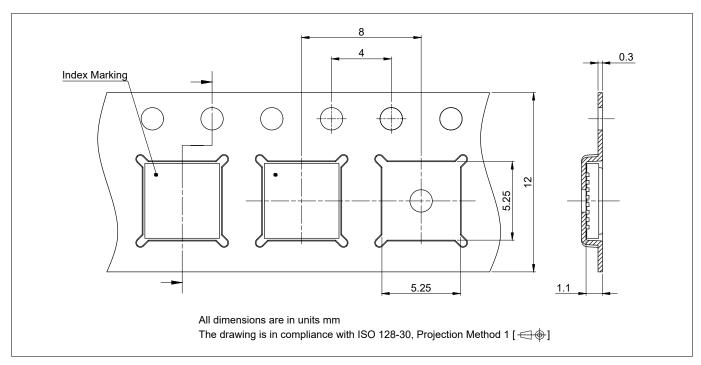

The package dimensions (in mm) of the controller in PG-VQFN-32-13 packages are given below.

Figure 9 PG-VQFN-32-13 package outline

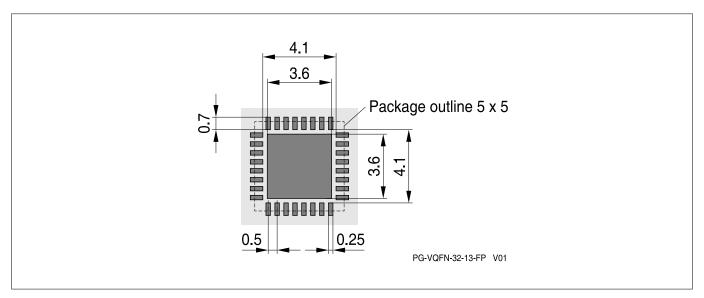

# 6 Package description

# 6.1.2 Package footprint

Figure 10 PG-VQFN-32-13 package footprint

# 6.1.3 Tape and reel packing

Figure 11 PG-VQFN-32-13 tape and reel packing

# infineon

6 Package description

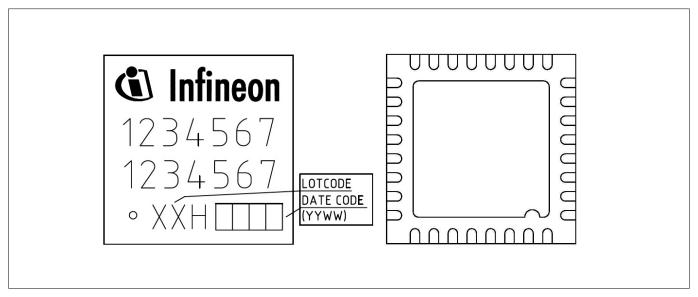

# 6.1.4 Production sample marking pattern

Figure 12 PG-VQFN-32-13 sample marking pattern

The black dot indicates pin 01 for the chip. The following table describes the sample marking pattern:

Table 18 Marking table for PG-VQFN-32-13 packages

| Indicator | Description                                                                    |

|-----------|--------------------------------------------------------------------------------|

| Infineon  | Manufacturer                                                                   |

| (line 1)  |                                                                                |

| SLS37TC   | Abbreviation for sales code SLS37CSAE20TC                                      |

| (line 2)  |                                                                                |

| OTCXXXA   | Short ROM code with xxx as placeholder for different short ROM codes           |

| (line 3)  |                                                                                |

| XXH□□□□   | Lot code and date code, defined and inserted during fabrication, issued by the |

| (line 4)  | packaging site                                                                 |

### **Datasheet**

References

# References

The following documents set out or describe specifications and/or standards referenced in the text of this document.

- [1] GlobalPlatform Technology: APDU Transport over SPI/I2C (Version 1.0), January 2020

- [2] GlobalPlatform Technology: Secure Channel Protocol '03' Amendment D (Version 1.2), April 2020

- [3] GlobalPlatform: Card Specification (Version 2.3.1), March 2018

- [4] ISO/IEC 7816-4: Identification cards Integrated circuit cards Part 4: Organization, security and commands for interchange (Second edition), 2005-01-15

- [5] NIST FIPS 186-4: Digital Signature Standard (DSS), July 2013

- [6] RFC 2119: Bradner, Scott. "Key words for use in RFCs to Indicate Requirement Levels." RFC2119 (1997) https://tools.ietf.org/rfc/rfc2119.txt

- [7] Wireless Power Consortium: *Qi Specification Authentication Protocol (latest version)*

# $\mathbf{OPTIGA^{\mathsf{TM}}} \ \mathbf{Trust} \ \mathbf{Charge} \ \mathbf{Automotive}$

# **Datasheet**

Glossary

# Glossary

| AC      | Access condition                                         |

|---------|----------------------------------------------------------|

| AC      | Alternating Current                                      |

| AEC     | Automotive Electronics Council                           |

| AES     | Advanced Encryption Standard                             |

| AES-CBC | Advanced Encryption Standard - Cipher Block Chaining     |

| AES-CCM | Advanced Encryption Standard - Counter with CBC MAC mode |

| APDU    | Application Protocol Data Unit                           |

| API     | Application Programming Interface                        |

| BPL     | Barcode Product Label                                    |

| BSI     | Bundesamt für Sicherheit in der Informationstechnik      |

| CA      | Certificate Authority                                    |

| CAD     | Computer-Aided Design                                    |

| СС      | Common Criteria                                          |

| CDM     | Charged-Device Model                                     |

| CMAC    | Cipher-based Message Authentication Code                 |

| CMOS    | Complementary Metal-Oxide-Semiconductor                  |

| СРНА    | Clock Phase                                              |

| CPOL    | Clock Polarity                                           |

| CPU     | Central Processing Unit                                  |

| CRC     | Cyclic Redundancy Check                                  |

| DC      | Direct Current                                           |

| DNC     | Do Not Connect                                           |

| EAL     | Evaluation Assurance Level                               |

| ECC     | Elliptic Curve Cryptography                              |

| ECDSA   | Elliptic Curve Digital Signature Algorithm               |

| ESD     | Electrostatic Discharge                                  |

| FMEA    | Failure Mode and Effects Analysis                        |

| GND     | Ground                                                   |

| GP      | GlobalPlatform                                           |

| GPIO    | General Purpose Input Output                             |

| НВМ     | Human Body Model                                         |

| HSM     | Hardware Security Module                                 |

| IATF    | International Automotive Task Force                      |

| I/O     | Input/Output                                             |

| I2C     | Inter-Integrated Circuit                                 |

| -       |                                                          |

# **Datasheet**

# Glossary

| IBIS  | Input/Output Buffer Information Specification  |

|-------|------------------------------------------------|

| IC    | Integrated Circuit                             |

| IEC   | International Electrotechnical Commission      |

| IMM   | Interface Management Module                    |

| IRQ   | Interrupt Request                              |

| ISO   | International Organization for Standardization |

| ISS   | Instruction Stream Signature                   |

| MAC   | Message Authentication Code                    |

| MED   | Memory Encryption Device                       |

| MISO  | Master In Slave Out                            |

| MOSI  | Master Out Slave In                            |

| MPU   | Memory Protection Unit                         |

| NCI   | Not Connected Internally                       |

| NIST  | National Institute of Standards and Technology |

| NVIC  | Nested Vector Interrupt Control                |

| NVM   | Non-Volatile Memory                            |

| OEM   | Original Equipment Manufacturer                |

| PCB   | Printed Circuit Board                          |

| PKI   | Public Key Infrastructure                      |

| PP    | Protection Profile                             |

| PPAP  | Production Part Approval Process               |

| PRNG  | Pseudo Random Number Generator                 |

| PWR   | Power                                          |

| RAM   | Random Access Memory                           |

| RFC   | Request For Comments                           |

| RFU   | Reserved for Future Use                        |

| RNG   | Random Number Generator                        |

| ROM   | Read-Only Memory                               |

| RST   | Reset                                          |

| SCLK  | Serial Peripheral Interface Clock              |

| SCP   | Symmetric Co-Processor                         |

| SCP03 | Secure Channel Protocol 03                     |

| SMD   | Surface-Mounted Device                         |

| SPI   | Serial Peripheral Interface                    |

| SS    | Slave Select                                   |

| TRNG  | True Random Number Generator                   |

# **Datasheet**

# Glossary

| Tx    | Transmit                        |

|-------|---------------------------------|

| Тур   | Typical                         |

| UMSLC | User Mode Security Life Control |

| VCC   | Supply Voltage                  |

| VQFN  | Very Thin Quad Flat No Leads    |

| WDT   | Watchdog Timer                  |

| WPC   | Wireless Power Consortium       |

# **Datasheet**

Revision history

# **Revision history**

| Reference                | Description                                        |  |

|--------------------------|----------------------------------------------------|--|

| Revision 1.2, 2024-09-03 |                                                    |  |

| All                      | Updated editorial changes                          |  |

| Revision 1.1, 2024-05-23 |                                                    |  |

| All                      | Updated Figure 12, Table 18, and editorial changes |  |

| Revision 1.0, 2023-01-20 |                                                    |  |

| All                      | Initial release                                    |  |

**Datasheet**

**RoHS** compliance

# **RoHS compliance**

On January 27, 2003 the European Parliament and the council adopted the directives:

- 2002/95/EC on the Restriction of the use of certain Hazardous Substances in electrical and electronic equipment ("RoHS")

- 2002/96/EC on Waste Electrical and Electrical and Electronic Equipment ("WEEE")

Some of these restricted (lead) or recycling-relevant (brominated flame retardants) substances are currently found in the terminations (e.g. lead finish, bumps, balls) and substrate materials or mold compounds.

The European Union has finalized the Directives. It is the member states' task to convert these Directives into national laws. Most national laws are available, some member states have extended timelines for implementation. The laws arising from these Directives have come into force in 2006 or 2007.

The electro and electronic industry has to eliminate lead and other hazardous materials from their products. In addition, discussions are on-going with regard to the separate recycling of certain materials, e.g. plastic containing brominated flame retardants.

Infineon is fully committed to giving its customers maximum support in their efforts to convert to lead-free and halogen-free<sup>1)</sup> products. For this reason, Infineon's "Green Products" are ROHS-compliant.

Since all hazardous substances have been removed, Infineon calls its lead-free and halogen-free semiconductor packages "green." Details on Infineon's definition and upper limits for the restricted materials can be found here.

The assembly process of our high-technology semiconductor chips is an integral part of our quality strategy. Accordingly, we will accurately evaluate and test alternative materials in order to replace lead and halogen so that we end up with the same or higher quality standards for our products.

The use of lead-free solders for board assembly results in higher process temperatures and increased requirements for the heat resistivity of semiconductor packages. This issue is addressed by Infineon by a new classification of the Moisture Sensitivity Level (MSL). In a first step the existing products have been classified according to the new requirements.

Lead-free

Balls, FC bumps, Lead finish

Halogen-free

Substrate, Mold compound

Any material used by Infineon is PBB and PBDE-free. Plastic containing brominated flame retardants, as mentioned in the WEEE directive, will be replaced if technically/economically beneficial.

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2024-09-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document?

Email:

CSSCustomerService@infineon.com

Document reference IFX-nvm1670304102379

#### Important notice

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.