## **Datasheet**

5G-ready eSIM turnkey solution for cellular-connected consumer devices to support GSMA remote SIM provisioning (RSP)

Document release reference: Z8F80745038-A

## **Features**

- Remote SIM provisioning (RSP) compatible with GSMA SGP.22 v2.5.0

- Multiple enabled profiles (MEP) compatible with GSMA SGP.22 v3

- Supports network technologies 3G, 4G (LTE), and 5G

- Supported network access applications: SIM, USIM, CSIM, and ISIM

- In-field OS update function

- Interoperable with worldwide commercial eSIM services following GSMA standards

- Up to 1.1 MB free memory for carrier profiles, applications, and data (additional applets integrable)

- Tiniest consumer eSIM solution with WLCSP (1.8 x 1.6 x 0.4 mm) and X2QFN20 (3.0 x 3.0 x 0.3 mm) packages

- Voltage classes: C (1.8 V), D (1.2 V)

- ETSI TS 102 221 and SPI interfaces

- Post-Quantum Cryptography ready

- Security evaluated according to the BSI-CC-PP-0100-2018 specified in GSMA SGP.25

- GSMA SAS-UP certified production process

- Temperature range: -25°C to +85°C

- Data retention: At least 10 years

# Infineon Consumer Consum

# **Description**

Infineon OPTIGA™ Connect Consumer OC1230 is an embedded universal integrated circuit card (eUICC) turnkey solution for embedded subscriber identity modules (eSIM) implementing GSMA's technical specification compatible with RSP GSMA SGP.22 v2.5.0 and MEP compatible with GSMA SGP.22 v3 for consumer mobile devices.

# **Potential applications**

For embedding into cellular-connected mobile devices such as:

- Handsets

- Wearables

- Tablets

- Laptops

## **Datasheet**

## **Support and services**

# **Support and services**

- Design-in support for hardware and software

- End-to-end test support with the Infineon Test SM-DP+ profile server

- Support for software patches

## **About this document**

## **Scope and purpose**

This document describes the features, functionality and operational characteristics of OPTIGA™ Connect Consumer OC1230.

## **Intended audience**

This document is primarily intended for OEM device integrators, system and application developers.

## **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC JESD47, JESD22, and J-STD-020.

## **Datasheet**

## **Table of contents**

# **Table of contents**

|             | Features                                            | 1  |

|-------------|-----------------------------------------------------|----|

|             | Description                                         | 1  |

|             | Potential applications                              | 1  |

|             | Support and services                                | 2  |

|             | About this document                                 | 2  |

|             | Product validation                                  | 2  |

|             | Table of contents                                   | 3  |

|             | List of tables                                      |    |

|             | List of figures                                     |    |

| 1           | Introduction                                        |    |

| -<br>2      | Operating system                                    |    |

| <b>2</b> .1 | GSMA eUICC framework                                |    |

| 2.1.1       | Multiple enabled profiles (MEP)                     |    |

| 2.1.2       | Logical secure element interfaces (LSI)             |    |

| 2.1.3       | Software reset (SWR)                                |    |

| 2.2         | Telecom framework                                   |    |

| 2.3         | GlobalPlatform framework                            |    |

| 2.4         | Java Card™ framework                                |    |

| 2.5         | Android ready SE                                    |    |

| 2.6         | Patching mechanism                                  | 11 |

| 2.7         | Power management                                    | 11 |

| 2.8         | Offline profile loading                             | 11 |

| 3           | Java Card™ applets                                  | 12 |

| 3.1         | GlobalPlatform secure element access control applet | 12 |

| 3.2         | Weaver applet                                       |    |

| 3.3         | Keymint applet                                      | 12 |

| 3.4         | OEM specific Java Card™ applets                     | 12 |

| 4           | Security features                                   | 13 |

| 5           | Support and services                                | 14 |

| 5.1         | Configuration and customization                     | 14 |

| 5.2         | Design-in support for software                      | 14 |

| 5.2.1       | Local profile assistant                             | 14 |

| 5.2.2       | Patch agent                                         | 14 |

| 5.2.3       | Android ready SE integration                        | 14 |

| 6           | Delivery forms                                      | 15 |

# **OPTIGA™ Connect Consumer OC1230**Datasheet

## **Table of contents**

| 6.1     | SMD packages                                    | 15 |

|---------|-------------------------------------------------|----|

| 6.1.1   | PG-X2QFN-20-1                                   | 16 |

| 6.1.2   | SG-XFWLB-16-1                                   | 21 |

| 7       | Electrical integration                          | 25 |

| 7.1     | Reference schematics for PG-X2QFN-20-1          | 25 |

| 7.2     | Reference schematics for SG-XFWLB-16-1          | 27 |

| 8       | Electrical characteristics                      | 29 |

| 8.1     | Key features                                    | 29 |

| 8.2     | Absolute maximum ratings                        | 29 |

| 8.3     | Operational characteristics                     | 30 |

| 8.3.1   | DC characteristics                              | 30 |

| 8.3.2   | AC characteristics                              | 30 |

| 8.3.2.1 | Power-on guidelines                             | 32 |

| 8.4     | Interfaces                                      | 33 |

| 8.4.1   | ISO 7816 interface and protocol characteristics | 33 |

| 8.4.1.1 | Electrical characteristics                      | 33 |

| 8.4.1.2 | ISO/IEC 7816-3 power-on sequence                | 36 |

| 8.4.2   | SPI interface and protocol characteristics      | 37 |

| 8.4.2.1 | Electrical characteristics                      | 38 |

| 8.4.3   | GPIO0.7 characteristics                         | 39 |

| 8.4.3.1 | GPIO0.7 as SPI interrupt (SPI IRQ)              | 39 |

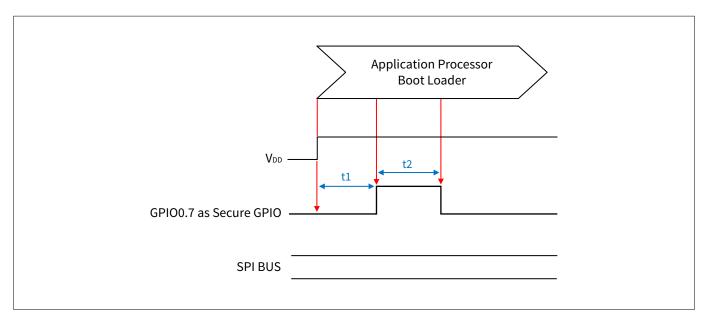

| 8.4.3.2 | GPIO0.7 as secure GPIO                          | 40 |

| 9       | Ordering information                            | 43 |

| 10      | Contact information                             | 44 |

|         | RoHS compliance                                 | 45 |

|         | References                                      | 46 |

|         | Glossary                                        | 47 |

|         | Revision history                                | 54 |

|         | Disclaimer                                      | 55 |

## **Datasheet**

# List of tables

## **List of tables**

| Table 1  | Marking table for PG-X2QFN-20-1 packages                                                   | 19   |

|----------|--------------------------------------------------------------------------------------------|------|

| Table 2  | Pinout for PG-X2QFN-20-1                                                                   | 20   |

| Table 3  | Marking table for SG-XFWLB-16-1 packages                                                   | 23   |

| Table 4  | Pinout for SG-XFWLB-16-1                                                                   | 24   |

| Table 5  | Key features                                                                               | 29   |

| Table 6  | Absolute maximum ratings                                                                   | 29   |

| Table 7  | DC electrical characteristics                                                              | 30   |

| Table 8  | AC electrical characteristics                                                              | 30   |

| Table 9  | ISO/IEC 7816-3 card maximum ratings                                                        | 33   |

| Table 10 | ISO/IEC 7816-3 card DC electrical characteristics                                          | . 33 |

| Table 11 | ISO/IEC 7816-3 card DC electrical characteristics - UART_RST                               | 34   |

| Table 12 | ISO/IEC 7816-3 card DC electrical characteristics - UART_CLK                               | 34   |

| Table 13 | ISO/IEC 7816-3 card DC electrical characteristics - UART_IO                                | . 34 |

| Table 14 | ISO/IEC 7816-3 card AC electrical characteristics - UART_RST                               | 35   |

| Table 15 | ISO/IEC 7816-3 card AC electrical characteristics - UART_CLK                               | 35   |

| Table 16 | ISO/IEC 7816-3 card AC electrical characteristics - UART_IO                                | 36   |

| Table 17 | ISO/IEC 7816-3 supported Fi/Di ratios                                                      | 36   |

| Table 18 | DC characteristics                                                                         | 38   |

| Table 19 | AC characteristics                                                                         | 38   |

| Table 20 | DC characteristics for 1.8 V supply voltage range                                          | . 40 |

| Table 21 | DC characteristics for 1.2 V supply voltage range                                          | . 40 |

| Table 22 | AC characteristics                                                                         | 40   |

| Table 23 | Boot signal characteristics                                                                | 41   |

| Table 24 | Secure GPIO operation supply and input voltages for (1.2 V and 1.8 V) supply voltage range | 41   |

| Table 25 | Secure GPIO DC electrical characteristics                                                  | 42   |

| Table 26 | Sales codes                                                                                | 43   |

## **Datasheet**

# List of figures

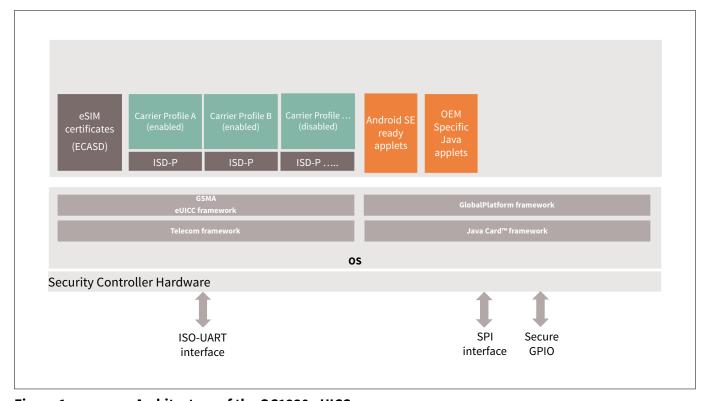

| Figure 1  | Architecture of the OC1230 eUICC                               |    |

|-----------|----------------------------------------------------------------|----|

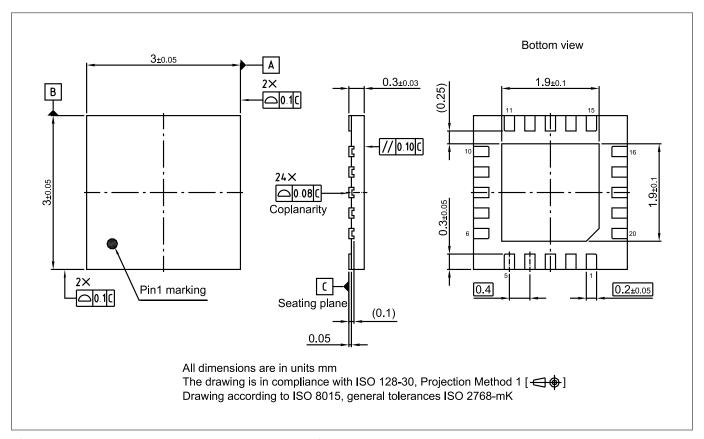

| Figure 2  | PG-X2QFN-20-1 package outline                                  |    |

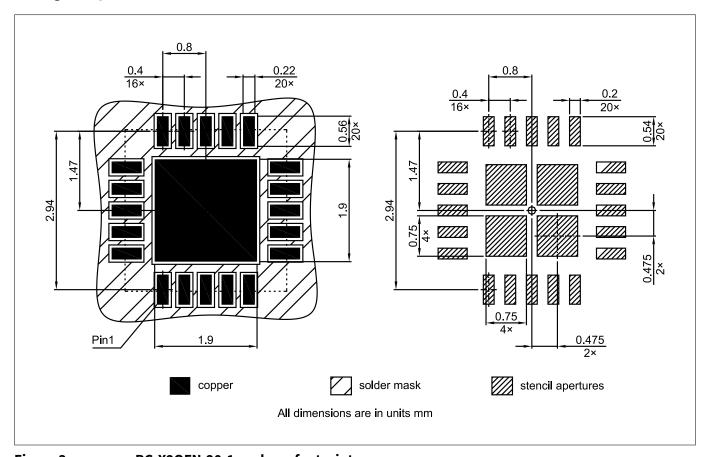

| Figure 3  | PG-X2QFN-20-1 package footprint                                | 17 |

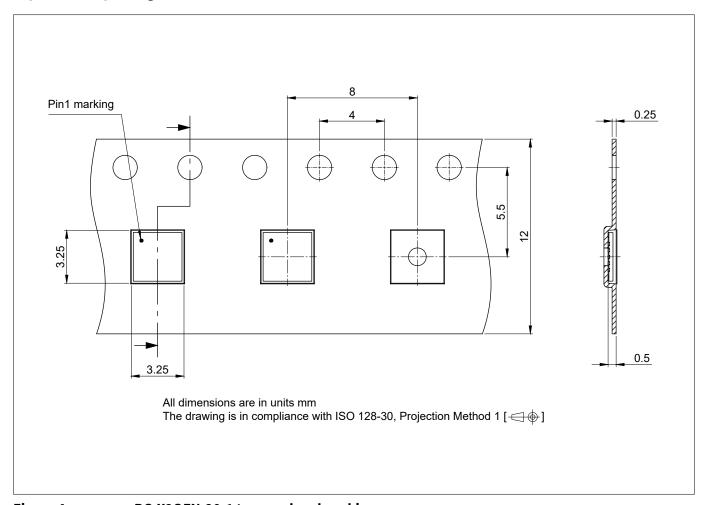

| Figure 4  | PG-X2QFN-20-1 tape and reel packing                            | 18 |

| Figure 5  | PG-X2QFN-20-1 sample marking pattern                           | 18 |

| Figure 6  | PG-X2QFN-20-1 PIN layout                                       | 19 |

| Figure 7  | SG-XFWLB-16-1 package outline                                  | 21 |

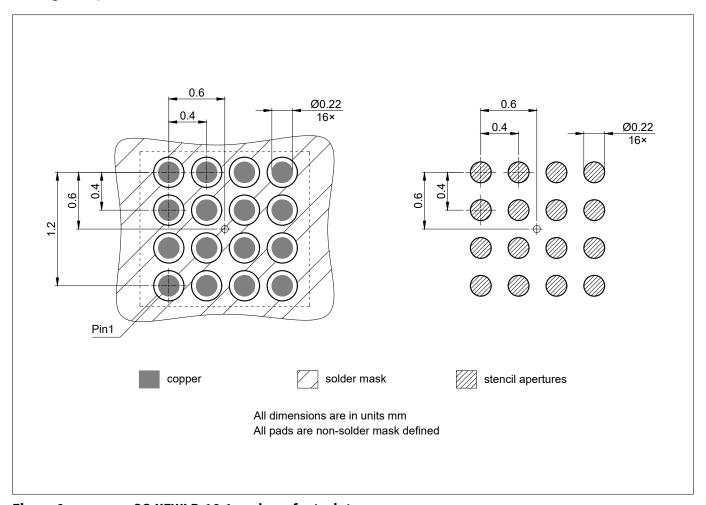

| Figure 8  | SG-XFWLB-16-1 package footprint                                | 22 |

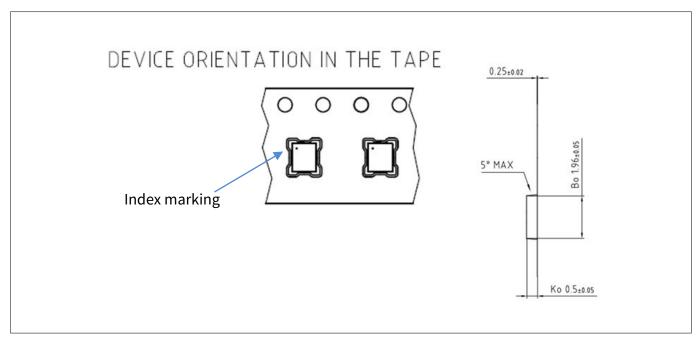

| Figure 9  | SG-XFWLB-16-1 tape and reel packing                            | 23 |

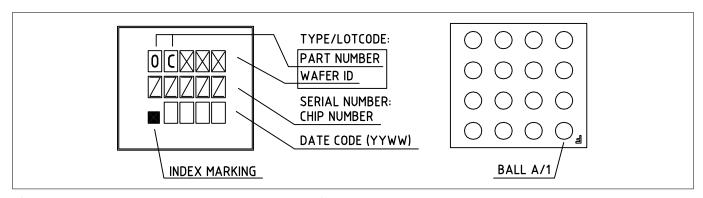

| Figure 10 | SG-XFWLB-16-1 sample marking pattern                           | 23 |

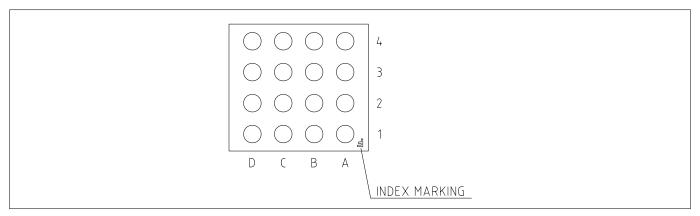

| Figure 11 | SG-XFWLB-16-1 PIN layout                                       | 24 |

| Figure 12 | Reference schematics for PG-X2QFN-20-1 ISO only                | 25 |

| Figure 13 | Reference schematics for PG-X2QFN-20-1 ISO + SPI + SPI IRQ     | 26 |

| Figure 14 | Reference schematics for PG-X2QFN-20-1 ISO + SPI + SECURE GPIO | 26 |

| Figure 15 | Reference schematics for SG-XFWLB-16-1 ISO only                | 27 |

| Figure 16 | Reference schematics for SG-XFWLB-16-1 ISO + SPI + SPI IRQ     | 28 |

| Figure 17 | Reference schematics for SG-XFWLB-16-1 ISO + SPI + SECURE GPIO | 28 |

| Figure 18 | Recommended power-on behavior                                  | 32 |

| Figure 19 | ISO/IEC 7816-3 power-on sequence                               |    |

| Figure 20 | Secure GPIO timing diagram                                     | 41 |

## **Datasheet**

## 1 Introduction

## 1 Introduction

The OPTIGA™ Connect Consumer OC1230 eUICC is Infineon's next generation of embedded subscriber identity modules (eSIM) implementing GSMA's technical specification SGP.22 [16] for mobile consumer devices.

The main purpose of the OC1230 eUICC is to provide secure network authentication to a selected and subscribed carrier network. The OC1230 allows changing and adding of carrier profiles in full compliance to GSMA eSIM specifications. With up to 1.1 MB of free user memory, the OC1230 has ample space for multiple carrier profiles as well as additional applications and user data.

The OC1230 is a certified and tested solution:

- GSMA SAS-UP certified production process [18]

- GSMA eUICC functional compliant [15] [16]

- GSMA eSA security certified

- Common Criteria certified according to protection profile PP-0100 [17]

- Java Card<sup>™</sup> functional compliant [25] [26]

Figure 1 Architecture of the OC1230 eUICC

The OC1230 eUICC is a system composed of a software layer residing on a security controller hardware. The central part of the software is the operating system (OS). This provides a platform that enables the hosting of carrier profiles, applications, and data.

The OS provides all services and features that make up the essence of an eUICC, respectively eSIM:

- GSMA eUICC framework to support remote SIM provisioning (RSP)

- A telecommunication framework with network access applications (NAAs), network authentication algorithms, file system services, and services for remote file management (RFM) and remote application management (RAM)

The OS serves as a foundation for user applications:

## **Datasheet**

# infineon

## 1 Introduction

- The OS implements a comprehensive GlobalPlatform (GP) framework to allow for secure and interoperable application deployment

- The OS implements the Java Card™ platform, including virtual machine, runtime environment, and APIs, to support the execution of user applications in the format of Java Card™ applets

The capability to host Java Card™ applets allows to tailor the OC1230 for different use cases. The OC1230 is capable of securely storing sensitive data such as end-user credentials, consumer device configurations, cryptographic keys, certificates, and others.

Further, the OS cares for efficient power management and provides a patching mechanism that allows for applying OS updates in the field.

The OC1230 eUICC supports the following interfaces:

- ISO/IEC 7816-3 interface (conforming with ETS 102 221 [1]), to connect a baseband controller

- SPI interface, to connect an application processor

- Secure GPIO mechanism, to support Android secure boot

## **Datasheet**

## 2 Operating system

# 2 Operating system

## 2.1 GSMA eUICC framework

The OC1230 supports the following key features to support GSMA remote SIM provisioning:

- Compliance with GSMA SGP.22 v2.5.0 [16]

- Support for local profile assistant in the consumer mobile device (LPAd)

- Multiple Enabled Profiles (MEP), option MEP-B, according to GSMA SGP.22 v3 [16]

- eSIM ports, according to GSMA SGP.22 v3 [16], aka logical secure element interfaces (LSI)

- TCA profile package interoperable [24] (backward compatible with [23])

- Multiple public key certificate issuers (PK CI)

- EC domains NIST-P256 and brainpoolP256r1

- Profile metadata tag BF76

## 2.1.1 Multiple enabled profiles (MEP)

The OC1230 supports multiple enabled profiles in compliance with GSMA SGP.22 v3.

If supported by the connected baseband controller, the OC1230 allows to enable up to 2 carrier profiles to establish up to 2 cellular connections at the same time. Multiple enabled profiles correspond to dual-SIM capability as known from classic SIM legacy.

# 2.1.2 Logical secure element interfaces (LSI)

Supporting multiple enabled profiles (MEP) requires the multiplexing of the APDU streams from an MEP-capable mobile device to concurrently enabled carrier profiles on a single physical interface. This ability is described by the ETSI (ETSI TS 102 221 [1]) as logical secure elements (LSE), which are addressed via logical secure element interfaces (LSI). The GSMA SGP.22 v3 [16] describes that as "eSIM port". An "LSI" or "eSIM port" allows the mobile device to address a dedicated carrier profile on the eSIM.

The OC1230 supports the following mechanisms to address eSIM ports (respectively LSIs) over the ISO 7816 interface:

- Via the APDU command MANAGE LSI (for protocol T=0 and T=1)

- Via the NAD byte (for protocol T=1)

For the selection of the ISD-R and the assignment of eSIM ports, the OC1230 supports option "MEP-B" of the GSMA SGP.22 v3 specification [16].

## 2.1.3 Software reset (SWR)

The OC1230 supports the management of logical secure elements (LSE) and logical secure element interfaces (LSI) over the ISO 7816 interface as defined in ETSI TS 102.221 [1]. This means, the OC1230 supports a dedicated APDU command MANAGE LSI, which allows:

- Selection of an LSI for subsequent APDUs (mandatory for protocol T=0, optional for protocol T=1)

- Resetting an LSE without affecting other LSEs

- Setup the LSI configuration to be used during the card session

The APDU command MANAGE LSI (reset LSE) allows the selection and the resetting of the LSE on the indicated LSI: All applets which have been previously selected on the logical channels corresponding to the LSI interface are deselected, the LSI transient objects are cleared and the default applet is selected on the logical channel 0. The resetting will not affect the other LSEs.

## **Datasheet**

## 2 Operating system

When used with the protocol T=1, the OC1230 supports a dedicated S-BLOCK for the host device to request a reset of a LSE: The S-BLOCK S(SWR request). The S(SWR request) is supported as defined in [GP22\_APDU] [12]. The S(SWR request) does not trigger a system reset of the OC1230, but a software reset of the indicated LSE, like the processing of the APDU command MANAGE LSI (reset LSE).

## 2.2 Telecom framework

The OC1230 OS offers a comprehensive telecom framework for supporting several network technologies, including 3G, 4G (LTE), and 5G. It also provides support for various network applications and authentication and key agreement algorithms.

Some of the key features supported by the telecom framework are:

- Compliance with network technologies, including 3G, 4G (LTE), and 5G

- Access to network applications, such as USIM, CSIM, and ISIM

- Authentication and key agreement algorithms, including:

- Comp 128-2/3

- MILENAGE (comp 128-4)

- TUAK

- CAVE

- 5G subscriber concealed identity (SUCI) protection scheme with on-chip SUCI generation, including a SUCI API

- ECIES scheme, Profile A

- ECIES scheme Profile B

- Null scheme

- Remote applet management (RAM) and remote file management (RFM)

- Over-the-air (OTA) services via CAT TP and HTTP

- Re-size files

- · BER-TLV files

- High update activity supported for all files

## 2.3 GlobalPlatform framework

The OC1230 OS is compliant to the following GlobalPlatform standards:

- GlobalPlatform: Technology Card Specification, v2.3.1

- GlobalPlatform CIC: Card Common Implementation Configuration, v2.1

- GlobalPlatform UICC: UICC Configuration, v2.0

- GlobalPlatform Amdment A: Confidential Card Content Management Card Specification, v1.2

- GlobalPlatform Amendment B: Remote Application Management over HTTP Card Specification, v1.2

- GlobalPlatform Amendment C: Contactless Services Card Specification, v1.3

- GlobalPlatform Amendment D: Secure Channel Protocol 03 Card Specification, v1.0

- GlobalPlatform Amendment F: Technology Secure Channel Protocol '11' Card Specification, v1.3

- GlobalPlatform Amendment H: Executable Load File Upgrade Card Specification, v1.1

- GlobalPlatform SEAC: Device Technology Secure Element Access Control, v1.1

- GlobalPlatform APDU: APDU Transport over SPI/I2C, v1.0

- GlobalPlatform API: Card API org.globalplatform, v1.7

- GlobalPlatform APIUPG: Card API ELF Upgrade API org.globalplatform.upgrade, v1.1

## **Datasheet**

## 2 Operating system

## 2.4 Java Card<sup>™</sup> framework

The OS implements a Java Card<sup>™</sup> framework, that is compliant with the following standards:

- JCRE: Java Card™ runtime environment specification, Java Card™ platform classic edition v3.1

- JCVM: Java Card™ virtual machine specification, Java Card™ platform classic edition v3.1

- JCAPI: Java Card<sup>™</sup> application programming interface, Java Card<sup>™</sup> platform classic edition v3.1

The OS supports extended-length application protocol data units (APDUs) as defined in ISO/IEC 7816-4 [22], for Java Card™ applets that implement the Java Card™ interface javacardx.apdu.ExtendedLength. Extended-length APDUs are supported through both UART and SPI communication interfaces. The extended length APDUs allow for larger APDUs than the standard length of 256 bytes, enabling more data to be transferred in a single APDU exchange. This can be particularly beneficial for certain types of applications, such as those involving large data sets or files.

The OS also supports a large selection of standard and optional Java Card™ API packages. The APIs enable various functionalities such as cryptography, secure messaging, and key management, among others, to be implemented in Java Card™ applets running on the device. The standard APIs are mandated by the Java Card™ specifications, while the optional APIs provide additional functionality that can be used to extend the capabilities of Java Card™ applets beyond the standard features.

The Java Card™ applets can either reside on the OC1230 as an integral part of a carrier profile, or as so-called "transversal" applets, which are separate and independent from any carrier profile.

## 2.5 Android ready SE

The OC1230 supports the security architecture defined by Google for Android devices in the context of the Android ready SE program.

## 2.6 Patching mechanism

The OC1230 implements a patching mechanism that allows for applying OS patches remotely, when the product is already in the field. The patching mechanism is designed to minimize any potential interferences with the consumer device, guaranteeing the best possible user experience.

## 2.7 Power management

The OC1230 supports power management in order to conserve energy and improve the overall efficiency of the consumer device.

When the OC1230 is powered-on, the OS checks if the ISO 7816 or the SPI interface have been activated.

- The ISO 7816 interface will get activated by active handling of the ISO-RST line in accordance to ISO/IEC 7816-3

- The SPI interface will get activated on assertion of the SPI slave select signal

If no interface has been activated, the OS will switch the OC1230 to idle state. The idle state is left by command reception via:

- ISO 7816 interface

- SPI interface

The OC1230 re-enters the idle state after the transmission of the last response.

# 2.8 Offline profile loading

The OC1230 implements a mechanism for device manufactures to load test profiles onto the eUICC during the manufacturing process.

## **Datasheet**

## 3 Java Card™ applets

## Java Card™ applets 3

Infineon offers a variety of Java Card<sup>™</sup> applets for the OC1230.

## GlobalPlatform secure element access control applet 3.1

The SEAC applet is used to manage and control the access of consumer device apps to the eSIM.

## 3.2 Weaver applet

Google Weaver is a secure inter-process communication (IPC) mechanism that is used to protect sensitive data in an Android-based mobile device OS. Weaver allows Android apps to communicate with each other securely, while preventing other Android apps or the Android OS from accessing the data.

## **Keymint applet** 3.3

Google Keymint is a module within Android's security architecture that is responsible for managing the secure storage of cryptographic keys. It is designed to provide a hardware-backed keystore solution, allowing for secure storage and retrieval of keys.

## 3.4 **OEM specific Java Card™ applets**

The OC1230 allows to host OEM-specific applets, either loaded by the OEM via GlobalPlatform compliant content management means or preloaded by Infineon.

## **Datasheet**

# infineon

## **4 Security features**

# 4 Security features

The OC1230 OS supports state-of-the-art security features:

- Security evaluated according to the BSI-CC-PP-0100-2018 specified in GSMA SGP.25 [17]

- GSMA SAS-UP certified production process

- All security-relevant methods are DPA/SPA/DFA-secured

- ANSI X9.17 software secure random number generator

- RSA coprocessor for RSA cryptography

- Post-quantum cryptography ready

- Secure GPIO mechanism

## **Datasheet**

5 Support and services

## **Support and services** 5

## **Configuration and customization** 5.1

The OC1230 can be configured in various ways and provides the option for individual customization, as follows:

- Preloading of test profiles

- Preloading and preinstallation of applets

Preloaded and preinstallation of content will be considered during the product configuration phase. The content will be added during Infineon's production process. This is a service that enables customers to have easy access to useful features right from the start, eliminating the need for later downloads and installations.

Further, Infineon's production process allows for chip individual diversification with respect to dedicated data elements.

## 5.2 **Design-in support for software**

Infineon offers a selection of reference software components, which allows for easy and seamless integration of the OC1230 into consumer devices. The reference software is available for host device architectures, based on the Android open source platform (AOSP) and Microsoft Windows.

## 5.2.1 Local profile assistant

Example implementations are provided to demonstrate the functionality of a local profile assistant (LPA). The LPA is responsible for profile management (for example, download, activation, and removal). Profile download can be demonstrated by using an activation code to retrieve a test profile from an SM-DP+ server.

Information of the available profiles and the eSIM details for example eID and supported specification versions and supported PKI IDs can be displayed in the user interface.

Depending on the host device architecture, either available system APIs are used or the required modules are delivered as part of the LPA SDK package.

## 5.2.2 **Patch agent**

The patch agent can be used to deploy in-field updates for the eSIM firmware. The example projects showcase the integration of the supplied libraries into an OEM application.

On the Android platform, this application would run as a system service and execute update scripts transparent to the user.

## 5.2.3 **Android ready SE integration**

Android ready SE provides native support for generic communication with the secure element (SE). This allows the Android system, as well as third-party apps to use specialized hardware for secured data storage (for example secret keys or access rules).

The example package contains implementations for the hardware abstraction layer (HAL) to communicate with the Keymint and Weaver applets installed on the SE. A generic HAL for low-level communication with the SE is also provided.

## **Datasheet**

## **6 Delivery forms**

# 6 Delivery forms

This chapter provides information about available delivery forms and how the product's interfaces are assigned to the package pins.

## 6.1 SMD packages

The following packages are available:

- PG-X2QFN-20-1

- SG-XFWLB-16-1

The figures in the sections below show the following aspects of the package:

- Package outline: It shows the package dimensions of the device in the individual packages

- Package footprint: It shows footprint recommendations

- Tape and reel packing: It shows device orientation in the tape with pin or index marking

- Sample marking pattern: It describes the productive sample marking pattern on the package

- **Package layout:** It shows a simple layout with the pin numbers described in the pin-to-signal reference section

## Notes:

- 1. The drawings are for information only and not drawn to scale. More detailed information about the package characteristics and assembly instructions are available on request.

- **2.** Unless specified otherwise, all figure dimensions are given in mm.

# infineon

## 6 Delivery forms

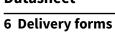

# 6.1.1 PG-X2QFN-20-1

## Package outline

Figure 2 PG-X2QFN-20-1 package outline

6 Delivery forms

# infineon

## **Package footprint**

Figure 3 PG-X2QFN-20-1 package footprint

## **6 Delivery forms**

## Tape and reel packing

Figure 4 PG-X2QFN-20-1 tape and reel packing

## **Production sample marking pattern**

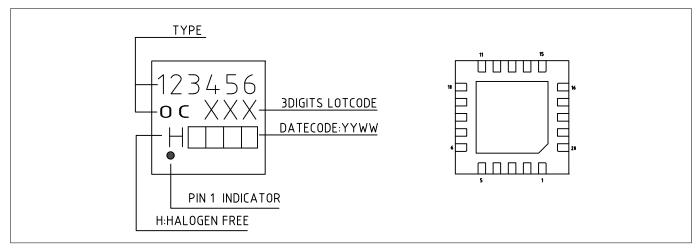

Figure 5 PG-X2QFN-20-1 sample marking pattern

The dot indicates pin 01 for the chip. The following table describes the sample marking pattern:

## **Datasheet**

Marking table for PG-X2QFN-20-1 packages Table 1

| Indicator         | Description                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 123456 (1st line) | Type code                                                                                                                                                                                                                        |

| OC (2nd line)     | Type code                                                                                                                                                                                                                        |

| XXX (2nd line)    | Lot code, defined and inserted during fabrication, issued by the packaging site                                                                                                                                                  |

| H                 | Engineering samples: "HE <yww>":  Halogen-free  Engineering Sample  <yy>: 2nd digit of production year  WW&gt;: Production week  Qualified production parts: "H<yyww>":  Halogen-free  YY&gt;: Production year</yyww></yy></yww> |

|                   | <ul><li><yy>: Production year</yy></li><li><ww>: Production week</ww></li></ul>                                                                                                                                                  |

## **PIN layout**

Figure 6 PG-X2QFN-20-1 PIN layout

It is recommended to connect the exposed die pad to the common ground reference (GND) for heat Note: distribution.

6 Delivery forms

# Pad-to-signal reference

## Pinout for PG-X2QFN-20-1 Table 2

| Pin no. | Name            | Pin type | Function                                                                                                                                  |  |  |  |  |

|---------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | NC              | NA       | No internal connection                                                                                                                    |  |  |  |  |

| 2       | RFU             | NA       | Do not connect                                                                                                                            |  |  |  |  |

| 3       | ISO_IO          | I/O      | ISO/IEC 7816-3 IO signal                                                                                                                  |  |  |  |  |

| 4       | NC              | NA       | No internal connection                                                                                                                    |  |  |  |  |

| 5       | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| 6       | V <sub>SS</sub> | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| 7       | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| 8       | V <sub>SS</sub> | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| 9       | GPIO0.7         | OUT      | If OC1230 is configured to support the SPI interrupt, then this pin acts as an SPI interrupt (SPI IRQ) signal. Do not connect if not used |  |  |  |  |

|         |                 | IN       | If OC1230 is configured to support the secure boot mechanism, then this pin acts as a secure GPIO signal. Do not connect if not used      |  |  |  |  |

| 10      | SPI_MISO        | OUT      | SPI slave data output signal; do not connect if not used                                                                                  |  |  |  |  |

| 11      | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| 12      | NC              | NA       | No internal connection                                                                                                                    |  |  |  |  |

| 13      | ISO_CLK         | IN       | ISO/IEC 7816-3 clock signal                                                                                                               |  |  |  |  |

| 14      | ISO_RST         | IN       | ISO/IEC 7816-3 reset signal                                                                                                               |  |  |  |  |

| 15      | SPI_CLK         | IN       | SPI clock signal; connect to V <sub>DD</sub> if not used                                                                                  |  |  |  |  |

| 16      | SPI_MOSI        | IN       | SPI slave data input signal; connect to V <sub>DD</sub> if not used                                                                       |  |  |  |  |

| 17      | SPI_SS          | IN       | SPI slave select signal; connect to V <sub>DD</sub> if not used                                                                           |  |  |  |  |

| 18      | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| 19      | V <sub>SS</sub> | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| 20      | NC              | NA       | No internal connection                                                                                                                    |  |  |  |  |

# infineon

6 Delivery forms

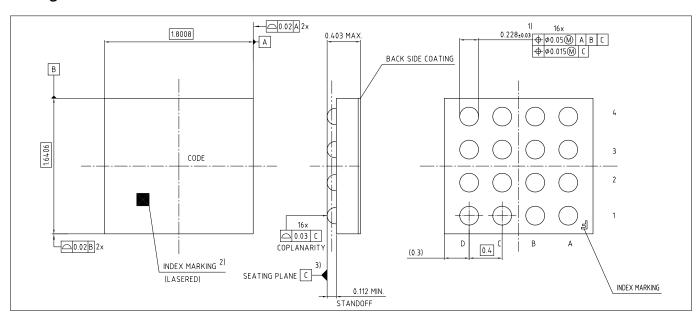

## 6.1.2 SG-XFWLB-16-1

## Package outline

Figure 7 SG-XFWLB-16-1 package outline

6 Delivery forms

## **Package footprint**

Figure 8 SG-XFWLB-16-1 package footprint

**6 Delivery forms**

## Tape and reel packing

Figure 9 SG-XFWLB-16-1 tape and reel packing

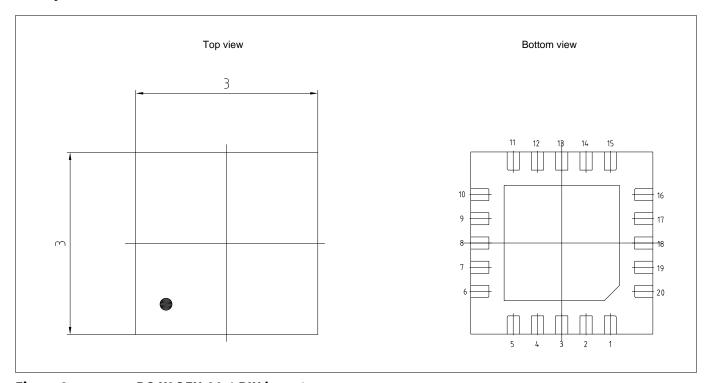

## **Production sample marking pattern**

Figure 10 SG-XFWLB-16-1 sample marking pattern

The square indicates ball A/1 for the chip.

Table 3 Marking table for SG-XFWLB-16-1 packages

| Indicator        | Description                                                                          |

|------------------|--------------------------------------------------------------------------------------|

| XXX (1st line)   | Lot code, defined and inserted during fabrication, issued by the packaging site      |

| OC (1st line)    | Type code                                                                            |

| 12345 (2nd line) | Serial number, defined and inserted during fabrication, issued by the packaging site |

|                  | Date code: "YYWW>":                                                                  |

|                  | <ul> <li><yy>: Production year</yy></li> </ul>                                       |

|                  | <ul> <li><ww>: Production week</ww></li> </ul>                                       |

## **Datasheet**

6 Delivery forms

## **PIN layout**

Figure 11 SG-XFWLB-16-1 PIN layout

It is recommended to connect the exposed die pad to the common ground reference (GND) for heat Note:

distribution.

## Pad-to-signal reference

Table 4 **Pinout for SG-XFWLB-16-1**

| Pin no. | Name            | Pin type | Function                                                                                                                                  |  |  |  |  |

|---------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A1      | V <sub>DD</sub> | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| A2      | V <sub>SS</sub> | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| A3      | A3 GPI00.7      |          | If OC1230 is configured to support the SPI interrupt, then this pin acts as an SPI interrupt (SPI IRQ) signal. Do not connect if not used |  |  |  |  |

|         |                 | IN       | If OC1230 is configured to support the secure boot mechanism, then this pin acts as a secure GPIO signal. Do not connect if not used      |  |  |  |  |

| A4      | ISO_CLK         | IN       | ISO/IEC 7816-3 clock signal                                                                                                               |  |  |  |  |

| B1      | ISO_IO          | I/O      | ISO/IEC 7816-3 IO signal                                                                                                                  |  |  |  |  |

| B2      | V <sub>DD</sub> | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| B3      | SPI_MISO        | OUT      | SPI slave data output signal; do not connect if not used                                                                                  |  |  |  |  |

| B4      | ISO_RST         | IN       | ISO/IEC 7816-3 reset signal                                                                                                               |  |  |  |  |

| C1      | RFU             | NA       | Do not connect                                                                                                                            |  |  |  |  |

| C2      | V <sub>SS</sub> | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| C3      | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| C4      | SPI_MOSI        | IN       | SPI slave data input signal; connect to V <sub>DD</sub> if not used                                                                       |  |  |  |  |

| D1      | $V_{SS}$        | GND      | Power supply: Common ground reference                                                                                                     |  |  |  |  |

| D2      | $V_{DD}$        | PWR      | Power supply: V <sub>DD</sub>                                                                                                             |  |  |  |  |

| D3      | SPI_SS          | IN       | SPI slave select signal; connect to V <sub>DD</sub> if not used                                                                           |  |  |  |  |

| D4      | SPI_CLK         | IN       | SPI slave clock signal; connect to V <sub>DD</sub> if not used                                                                            |  |  |  |  |

## 7 Electrical integration

## **Electrical integration** 7

This chapter provides information about the electrical integration of the product into a host device.

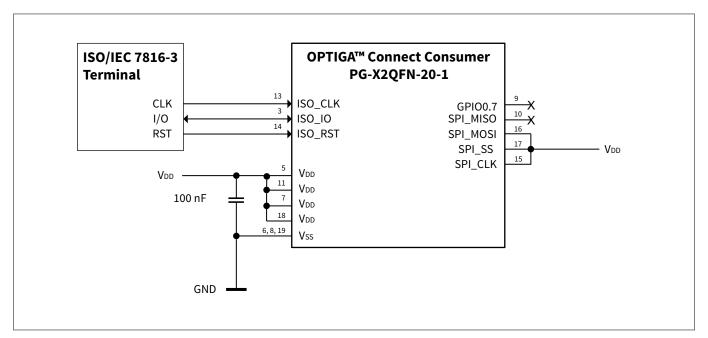

## 7.1 Reference schematics for PG-X2QFN-20-1

This chapter provides reference schematics for the OC1230 in the package type PG-X2QFN-20-1. It refers to a selection of typical use cases. For further recommendations on how to connect the OC1230, refer to Table 2.

## Electrical schematics for the use case "ISO/IEC 7816-3 only"

These schematics refer to the use case, in which the OC1230 is only connected to the baseband controller via the ISO/IEC 7816-3 interface. The SPI interface is not connected. The GPIO0.7 is not connected. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as SPI interrupt, as well as the configuration in which the GPIO0.7 acts as secure GPIO.

Note: SPI connection is optional, GPIO0.7 connection is optional.

Figure 12 Reference schematics for PG-X2QFN-20-1 ISO only

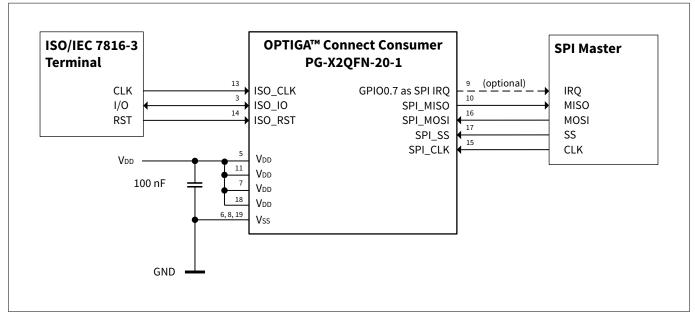

## Electrical schematics for the use case "ISO/IEC 7816-3, SPI with SPI IRQ"

These schematics refer to the use case, in which the OC1230 is connected to the baseband controller via the ISO/IEC 7816-3 interface, and to the application processor via SPI. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as an SPI interrupt. The GPIO0.7 as SPI interrupt is connected to the SPI master.

Note: SPI connection is optional, SPI IRQ connection is optional.

## **Datasheet**

## 7 Electrical integration

Figure 13 Reference schematics for PG-X2QFN-20-1 ISO + SPI + SPI IRQ

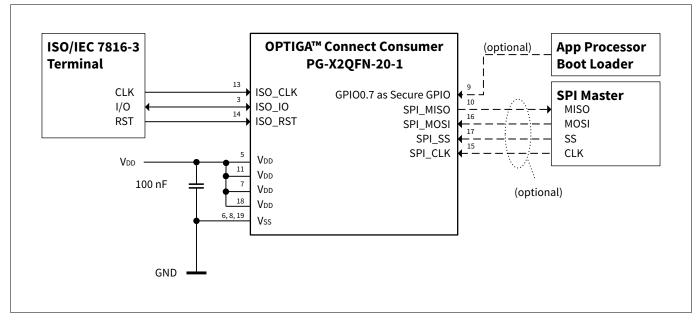

## Electrical schematics for the use case "ISO/IEC 7816-3, SPI, and secure GPIO"

These schematics refer to the use case, in which the OC1230 is connected to the baseband controller via the ISO/IEC 7816-3 interface, and to the application processor via SPI. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as a secure GPIO. The GPIO0.7 as a secure GPIO is connected to the application processor boot loader.

SPI connection is optional, secure GPIO connection is optional. Note:

Figure 14 Reference schematics for PG-X2QFN-20-1 ISO + SPI + SECURE GPIO

## **Datasheet**

## 7 Electrical integration

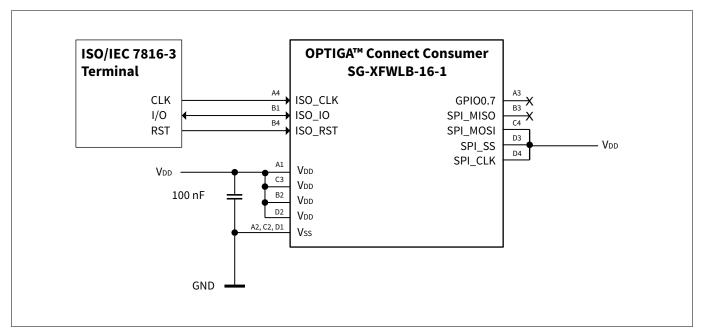

## 7.2 Reference schematics for SG-XFWLB-16-1

This chapter provides reference schematics for the OC1230 in the package type SG-XFWLB-16-1. It refers to a selection of typical use cases. For further recommendations on how to connect the OC1230, refer to Table 4.

## Electrical schematics for the use case "ISO/IEC 7816-3 only"

These schematics refer to the use case, in which the OC1230 is only connected to the baseband controller via the ISO/IEC 7816-3 interface. The SPI interface is not connected. The GPIO0.7 is not connected. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as SPI interrupt, as well as the configuration in which the GPIO0.7 acts as secure GPIO.

**Note**: SPI connection is optional, GPIO0.7 connection is optional.

Figure 15 Reference schematics for SG-XFWLB-16-1 ISO only

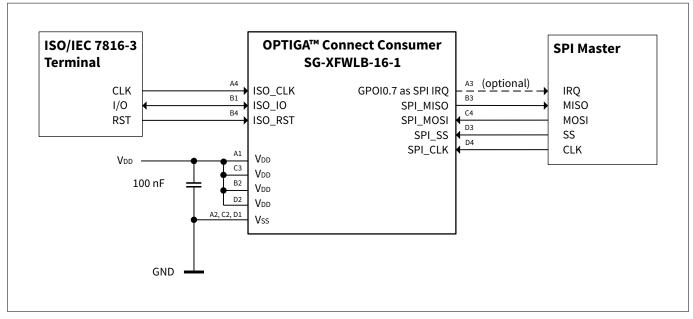

## Electrical schematics for the use case "ISO/IEC 7816-3, SPI with SPI IRQ"

These schematics refer to the use case, in which the OC1230 is connected to the baseband controller via the ISO/IEC 7816-3 interface, and to the application processor via SPI. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as an SPI interrupt. The GPIO0.7 as SPI interrupt is connected to the SPI master.

**Note**: SPI connection is optional, SPI IRO connection is optional.

## **Datasheet**

## 7 Electrical integration

Figure 16 Reference schematics for SG-XFWLB-16-1 ISO + SPI + SPI IRQ

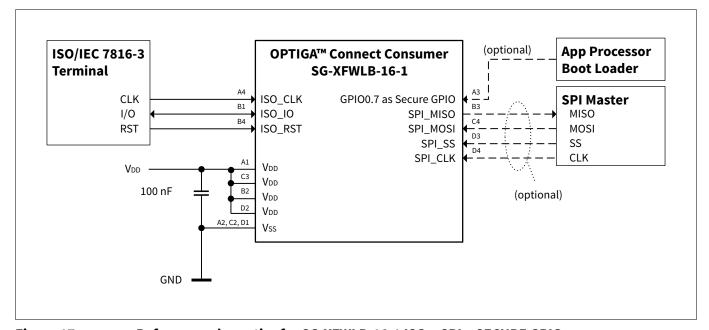

## Electrical schematics for the use case "ISO/IEC 7816-3, SPI, and secure GPIO"

These schematics refer to the use case, in which the OC1230 is connected to the baseband controller via the ISO/IEC 7816-3 interface, and to the application processor via SPI. These schematics refer to the OC1230 configuration, in which the GPIO0.7 acts as a secure GPIO. The GPIO0.7 as a secure GPIO is connected to the application processor boot loader.

**Note**: SPI connection is optional, secure GPIO connection is optional.

Figure 17 Reference schematics for SG-XFWLB-16-1 ISO + SPI + SECURE GPIO

## **Datasheet**

## 8 Electrical characteristics

## 8 Electrical characteristics

This section summarizes certain electrical characteristics of the controllers. It provides operational characteristics as well as electrical DC and AC characteristics and particular interface characteristics.

## Notes:

- **1.**  $T_A$  as given for the operating temperature range of the controller unless otherwise stated.

- **2.** All currents flowing into the controller are considered positive.

## 8.1 Key features

| Table 5        | Key features |                              |

|----------------|--------------|------------------------------|

| Voltage class  |              | Class C (1.8 V)              |

|                |              | Class D (1.2 V)              |

| Data retention |              | 10 years at room temperature |

## 8.2 Absolute maximum ratings

This section defines the absolute maximum ratings. Stresses exceeding the values listed in Table 6 may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions whose values exceed those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability, including NVM data retention and programming endurance.

All voltages are referenced to common ground (GND) reference, unless otherwise specified.

Table 6 Absolute maximum ratings

| Parameter                                | Symbol         |      | Value | es   | Unit | Note or test condition                                            |  |

|------------------------------------------|----------------|------|-------|------|------|-------------------------------------------------------------------|--|

|                                          |                | Min. | Тур.  | Max. |      |                                                                   |  |

| Human body model (HBM) <sup>1)</sup>     |                | -    | -     | -    | V    | 2000 V (GPIO signal group)<br>2000 V (SWP signal group)           |  |

| Charged device model (CDM) <sup>2)</sup> |                | -    | -     | -    | V    | 500 V (GPIO signal group)<br>500 V (SWP signal group)             |  |

| Storage temperature                      | T <sub>S</sub> | -40  | -     | +125 | °C   | Guaranteed by qualification results: 200h @ -40°C, 1000h @ +125°C |  |

| Operating temperature, ambient           | T <sub>A</sub> | -25  | -     | +85  | °C   | T <sub>J</sub> (max) must not be exceeded                         |  |

| Junction temperature                     | TJ             | -    | -     | +110 | °C   | -                                                                 |  |

| Supply voltage                           | $V_{DD}$       | -0.3 | -     | 2.5  | V    | -                                                                 |  |

<sup>1)</sup> Conditions and test setup according to ANSI/ESDA/JEDEC JS-001-2017: Joint JEDEC/ESDA Standard For Electrostatic Discharge Sensitivity Test - Human Body Model (HBM) - Component Level; 2017-05

<sup>2)</sup> Conditions and test setup according to ANSI/ESDA/JEDEC JS-002-2018: Joint Standard for Electrostatic Discharge Sensitivity Testing - Charged Device Model (CDM) - Device Level; 2019-01

## **Datasheet**

## **8 Electrical characteristics**

## 8.3 Operational characteristics

This section specifies the AC and DC characteristics of the controller, along with details relating to the specific interfaces provided by the controller.

## 8.3.1 DC characteristics

$T_{\rm A}$  as given for the security controller's operating ambient temperature range unless otherwise stated. All currents flowing into the security controller are considered positive.

Table 7 DC electrical characteristics

| Parameter                                 | Symbol                   | Values                     |       |                            | Unit | Note or test condition                                                                                                                                                                 |  |

|-------------------------------------------|--------------------------|----------------------------|-------|----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                           |                          | Min.                       | Тур.  | Max.                       |      |                                                                                                                                                                                        |  |

| Supply voltage                            | $V_{DD}$                 | 1.08                       | -     | 1.98                       | ٧    | Overall functional range of V <sub>DD</sub>                                                                                                                                            |  |

| Supply voltage variation during operation | V <sub>DD_op</sub>       | V <sub>DD_nom</sub> * 0.90 | -     | V <sub>DD_nom</sub> * 1.10 | V    | In operation and idle state phases, the supply voltage must stay within this range around the nominal supply voltage.  Maximum operating voltage must stay below V <sub>DD_max</sub> . |  |

| Supply current, operating state           | I <sub>1V2_operati</sub> | -                          | 12.75 | -                          | mA   | V <sub>DD</sub> = 1.2 V, ISO/IEC 7816                                                                                                                                                  |  |

| Supply current, operating state           | I <sub>1V8_operati</sub> | -                          | 12.90 | -                          | mA   | V <sub>DD</sub> = 1.8 V, ISO/IEC 7816                                                                                                                                                  |  |

| Supply current, idle state                | I <sub>1V2_idle</sub>    | -                          | 141   | -                          | μΑ   | V <sub>DD</sub> = 1.2 V, via ISO/IEC 7816 connected                                                                                                                                    |  |

| Supply current, idle state                | I <sub>1V8_idle</sub>    | -                          | 142   | -                          | μΑ   | V <sub>DD</sub> = 1.8 V, via ISO/IEC 7816 connected                                                                                                                                    |  |

## 8.3.2 AC characteristics

$T_{\rm A}$  as given for the security controller's operating ambient temperature range unless otherwise stated. All currents flowing into the security controller are considered positive.

Table 8 AC electrical characteristics

| Parameter                    | Symbol       | Values          |      | Unit | Note or test condition |                                       |

|------------------------------|--------------|-----------------|------|------|------------------------|---------------------------------------|

|                              |              | Min.            | Тур. | Max. |                        |                                       |

| V <sub>DD</sub> ramp-up time | $t_{ m VDD}$ | 2 <sup>1)</sup> | -    | -    | μs                     | 0% to 100% of the target voltage ramp |

(table continues...)

## **Datasheet**

## **8 Electrical characteristics**

(continued) AC electrical characteristics Table 8

| Parameter                                     | Symbol             |                      | Values | ;                | Unit       | Note or test condition                                                                                                                                                                                                                                                               |

|-----------------------------------------------|--------------------|----------------------|--------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |                    | Min.                 | Тур.   | Max.             |            |                                                                                                                                                                                                                                                                                      |

| System oscillator frequency                   | f <sub>OSC</sub>   | -                    | 100    | -                | MHz        | Average system frequency for a nominally adjusted oscillator at $T_j$ = +25°C and zero lifetime (without silicon aging).  The actual oscillator frequency may vary due to dynamic onchip power management functions (for example voltage drop monitor) and environmental conditions. |

| System oscillator frequency temperature drift | f <sub>OSC_T</sub> | -                    | -30    | -                | kHz/°<br>C | Average system oscillator frequency drift as a function of junction temperature                                                                                                                                                                                                      |

| System clock frequency                        | $f_{SYSCLK}$       | f <sub>OSC</sub> /32 | -      | f <sub>OSC</sub> | MHz        | -                                                                                                                                                                                                                                                                                    |

At a faster supply ramp-up time the chip internal ESD elements cause temporarily a cross current between  $V_{DD}$  and GND, which would be larger than the allowed  $I_{CC}$  for the relevant voltage class. 1)

# infine

## **8 Electrical characteristics**

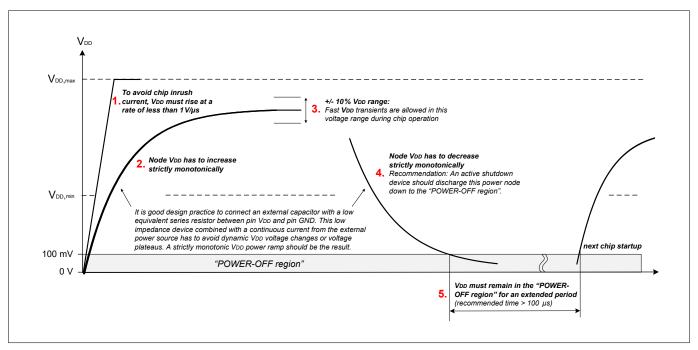

## 8.3.2.1 Power-on guidelines

The rampup times given in AC characteristics apply under the assumption of a linear rise in voltage from 0% to 100% of the target voltage level. However, owing to possible current spike effects, it is recommended to follow the voltage characteristics shown in the figure below.

Figure 18 Recommended power-on behavior

## **Datasheet**

## 8 Electrical characteristics

#### 8.4 **Interfaces**

This chapter provides electrical characteristics with respect to operation of particular interfaces of the controller.

Note:

Unless otherwise stated, all values in this section are measured at the pins of the used package. That is, resistance, capacitance, and inductance, for example, of the package and the bond wires are already included in these values!

The general characteristics of GPIO pins are stated at first covering the full operational range and various configuration options. The characteristics of a particular interfaces are stated with respect to the specific interface standards.

## 8.4.1 ISO 7816 interface and protocol characteristics

The ISO 7816 interface conforms with the ISO/IEC 7816-3, integrated circuit card (ICC) side, implementing the transport protocols T=0 and T=1.

This interface supports APDU multiplexing, allowing for efficient communication in context with multiple enabled carrier profiles. For more details, refer to Multiple enabled profiles (MEP) and Logical secure element

This interface supports logical channels according to ISO/IEC 7816-4. Logical channels allow multiple application protocols to share the same physical connection, enabling the consumer device to manage multiple applications simultaneously.

#### **Electrical characteristics** 8.4.1.1

## Notes:

- 1. All currents flowing out of the pad are considered to be positive

- 2. Symbol  $T_A$  describes the ambient temperature range

- ISO/IEC 7816-3 defines Class C as lowest supply voltage. Since this product supports lower voltages the 3. requirements and limits from Class C are used for the whole voltage range below Class C

## **Absolute maximum ratings**

#### Table 9 ISO/IEC 7816-3 card maximum ratings

| Parameter         | Symbol         | Values |      |                      | Unit | Note or test condition |

|-------------------|----------------|--------|------|----------------------|------|------------------------|

|                   |                | Min.   | Тур. | Max.                 |      |                        |

| Pad input voltage | V <sub>I</sub> | -0.3   | -    | V <sub>DD</sub> +0.3 | ٧    |                        |

## DC electrical characteristics

#### Table 10 ISO/IEC 7816-3 card DC electrical characteristics

| Parameter      | Symbol   | Values |      |      | Unit | Note or test condition                            |

|----------------|----------|--------|------|------|------|---------------------------------------------------|

|                |          | Min.   | Тур. | Max. |      |                                                   |

| Supply voltage | $V_{DD}$ | 1.08   | _    | 1.98 | ٧    | Note: V <sub>DD</sub> includes: V <sub>DD_C</sub> |

## **Datasheet**

## **8 Electrical characteristics**

Table 11 ISO/IEC 7816-3 card DC electrical characteristics - UART\_RST

| Parameter          | Symbol          |                       | Values |                        | Unit | Note or test condition                                          |

|--------------------|-----------------|-----------------------|--------|------------------------|------|-----------------------------------------------------------------|

|                    |                 | Min.                  | Тур.   | Max.                   |      |                                                                 |

| Input high voltage | V <sub>IH</sub> | 0.8 * V <sub>DD</sub> | -      | $V_{\mathrm{DD}}$      | V    | -150 μA < I <sub>IH</sub> < +20 μA<br>T <sub>A</sub> = 0°C 50°C |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{DD}$               | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                               |

| Input high voltage | V <sub>IH</sub> | 0.8 * V <sub>DD</sub> | -      | $V_{\mathrm{DD}}$      | V    | -20 μA ≤ I <sub>IH</sub><br>T <sub>A</sub> = -25°C +85°C        |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.12 * V <sub>DD</sub> | V    | -20 μA < I <sub>IL</sub> < 200 μA<br>T <sub>A</sub> = 0°C +50°C |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub>  | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                               |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub>  | V    | I <sub>IL</sub> ≤ 200 μA<br>T <sub>A</sub> = -25°C +85°C        |

Table 12 ISO/IEC 7816-3 card DC electrical characteristics - UART\_CLK

| Parameter          | Symbol          |                       | Values |                       | Unit | Note or test condition                                           |

|--------------------|-----------------|-----------------------|--------|-----------------------|------|------------------------------------------------------------------|

|                    |                 | Min.                  | Тур.   | Max.                  |      |                                                                  |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{\mathrm{DD}}$     | V    | -100 μA < I <sub>IH</sub> < +20 μA<br>T <sub>A</sub> = 0°C +50°C |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{DD}$              | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                                |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{\mathrm{DD}}$     | V    | -20 μA ≤ I <sub>IH</sub><br>T <sub>A</sub> = -25°C +85°C         |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub> | V    | -20 μA < I <sub>IL</sub> < 100 μA<br>T <sub>A</sub> = 0°C +50°C  |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub> | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                                |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub> | V    | I <sub>IL</sub> ≤ 20 μA<br>T <sub>A</sub> = -25°C +85°C          |

Table 13 ISO/IEC 7816-3 card DC electrical characteristics - UART\_IO

| Parameter          | Symbol          |                       | Values |                        | Unit | Note or test condition                                           |

|--------------------|-----------------|-----------------------|--------|------------------------|------|------------------------------------------------------------------|

|                    |                 | Min.                  | Тур.   | Max.                   |      |                                                                  |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{\mathrm{DD}}$      | V    | -20 μA < I <sub>IH</sub> < 300 μA<br>T <sub>A</sub> = 0°C +50°C  |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | -                      | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                                |

| Input high voltage | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -      | V <sub>DD</sub> + 0.3  | V    | -20 μA < I <sub>IH</sub> < 20 μA<br>T <sub>A</sub> = -25°C +85°C |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.15 * V <sub>DD</sub> | V    | -20 μA < / <sub>IL</sub> < 1000 μA<br>$T_A$ = 0°C +50°C          |

| Input low voltage  | V <sub>IL</sub> | 0                     | -      | 0.2 * V <sub>DD</sub>  | V    | <i>T</i> <sub>A</sub> = 0°C +50°C                                |

| Input low voltage  | V <sub>IL</sub> | -0.3                  | -      | 0.2 * V <sub>DD</sub>  | V    | I <sub>IL</sub> ≤ 1000 μA<br>T <sub>A</sub> = -25°C +85°C        |

(table continues...)

## **Datasheet**

## **8 Electrical characteristics**

Table 13 (continued) ISO/IEC 7816-3 card DC electrical characteristics - UART\_IO

| Parameter           | Symbol          |                       | Values |                        | Unit | Note or test condition                                                                                                             |

|---------------------|-----------------|-----------------------|--------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

|                     |                 | Min.                  | Тур.   | Max.                   |      |                                                                                                                                    |

| Output high voltage | V <sub>OH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{DD}$               | V    | $-20 \mu A < I_{OH}$<br>$20 k\Omega$ to $V_{DD}$<br>$T_A = 0$ °C +50°C                                                             |

| Output high voltage | V <sub>OH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{DD}$               | V    | 0 $\mu$ A < $I_{OH}$ < 20 $\mu$ A<br>20 $\mu$ C to $V_{DD}$<br>$T_A$ = 0°C +50°C                                                   |

| Output high voltage | V <sub>OH</sub> | 0.7 * V <sub>DD</sub> | -      | $V_{ m DD}$            | V    | Voltage class C<br>$I_{OH} = 20 \mu A$<br>$20 k\Omega \text{ to } V_{DD}$<br>$T_A = -25^{\circ}\text{C} \dots +85^{\circ}\text{C}$ |

| Output low voltage  | V <sub>OL</sub> | 0                     | -      | 0.15 * V <sub>DD</sub> | V    | -500 $\mu$ A = $I_{OL}$<br>$T_{A}$ = 0°C +50°C                                                                                     |

| Output low voltage  | V <sub>OL</sub> | 0                     | -      | 0.15 * V <sub>DD</sub> | V    | Voltage class C<br>-500 $\mu$ A < $I_{OL}$ < 0 $\mu$ A<br>$T_A$ = 0°C +50°C                                                        |

| Output low voltage  | V <sub>OL</sub> | 0                     | -      | 0.3                    | V    | -1000 μA = I <sub>OL</sub><br>T <sub>A</sub> = -25°C +85°C                                                                         |

## ISO/IEC 7816-3 card AC electrical characteristics

Table 14 ISO/IEC 7816-3 card AC electrical characteristics - UART\_RST

| Parameter              | Symbol                 |      | Valu | es   | Unit | Note or test condition              |

|------------------------|------------------------|------|------|------|------|-------------------------------------|

|                        |                        | Min. | Тур. | Max. |      |                                     |

| Rise/fall time         | $t_{\rm R}, t_{\rm F}$ | -    | -    | 1    | μs   | <i>T</i> <sub>A</sub> = 0°C +50°C   |

| Rise/fall time         | $t_{R}, t_{F}$         | -    | -    | 400  | μs   | <i>T</i> <sub>A</sub> = -25°C +85°C |

| Input load capacitance | $C_{LOAD}$             | -    | -    | 30   | pF   | -                                   |

Table 15 ISO/IEC 7816-3 card AC electrical characteristics - UART\_CLK

| Parameter              | Symbol                | Values |      |                                   | Unit | Note or test condition                                                                         |

|------------------------|-----------------------|--------|------|-----------------------------------|------|------------------------------------------------------------------------------------------------|

|                        |                       | Min.   | Тур. | Max.                              |      |                                                                                                |

| External frequency     | f <sub>UART_CLK</sub> | 1      | -    | 15                                | MHz  | @ duty cycle 40% 60%<br>$V_{\rm IL}$ < 0.1 * $V_{\rm DD}$<br>$V_{\rm IH}$ > 0.9 * $V_{\rm DD}$ |

| Rise/fall time         | $t_{R}, t_{F}$        | -      | -    | 0.9 * 1/<br>f <sub>UART_CLK</sub> | μs   | T <sub>A</sub> = 0°C +50°C<br>Measured between 10% and<br>90% of signal amplitude              |

| Rise/fall time         | $t_{R}, t_{F}$        | -      | -    | 50                                | ns   | T <sub>A</sub> = -25°C +85°C<br>measured between 10% and<br>90% of signal amplitude            |

| Input load capacitance | C <sub>LOAD</sub>     | -      | -    | 30                                | pF   | <i>T</i> <sub>A</sub> = -25°C +85°C                                                            |

# **Datasheet**

8 Electrical characteristics

Table 16 ISO/IEC 7816-3 card AC electrical characteristics - UART\_IO

| Parameter               | Symbol         | Symbol Values |      |      |    | Note or test condition              |

|-------------------------|----------------|---------------|------|------|----|-------------------------------------|

|                         |                | Min.          | Тур. | Max. |    |                                     |

| Rise/fall time          | $t_{R}, t_{F}$ | -             | -    | 1    | μs | <i>T</i> <sub>A</sub> = 0°C +50°C   |

| Rise/fall time          | $t_{R}, t_{F}$ | -             | -    | -    | μs | <i>T</i> <sub>A</sub> = -25°C +85°C |

| Input load capacitance  | $C_{LOAD}$     | -             | -    | 30   | pF | -                                   |

| Output load capacitance | $C_{LOAD}$     | -             | -    | 30   | pF | -                                   |

### ISO/IEC 7816-3 supported Fi/Di ratios Table 17

| Fi-Di             | F/D | Baud rate            |

|-------------------|-----|----------------------|

| 0x01 (%0000 0001) | 372 | 9600 Bd @3.579 MHz   |

| 0x02 (%0000 0010) | 186 | 19200 Bd @3.579 MHz  |

| 0x03 (%0000 0011) | 93  | 38400 Bd @3.579 MHz  |

| 0x08 (%0000 1000) | 31  | 115200 Bd @3.579 MHz |

| 0x11 (%0001 0001) | 372 | 9600 Bd @3.579 MHz   |

| 0x12 (%0001 0010) | 186 | 19200 Bd @3.579 MHz  |

| 0x13 (%0001 0011) | 93  | 38400 Bd @3.579 MHz  |

| 0x18 (%0001 1000) | 31  | 115200 Bd @3.579 MHz |

| 0x38 (%0011 1000) | 62  | 57600 Bd @3.579 MHz  |

| 0x93 (%1001 0011) | 128 | 31250 Bd @4.000 MHz  |

| 0x94 (%1001 0100) | 64  | 56000 Bd @3.579 MHz  |

| 0x95 (%1001 0101) | 32  | 156250 Bd @5.000 MHz |

| 0x96 (%1001 0110) | 16  | 312500 Bd @5.000 MHz |

| 0x97 (%1001 0111) | 8   | 625000 Bd @5.000 MHz |

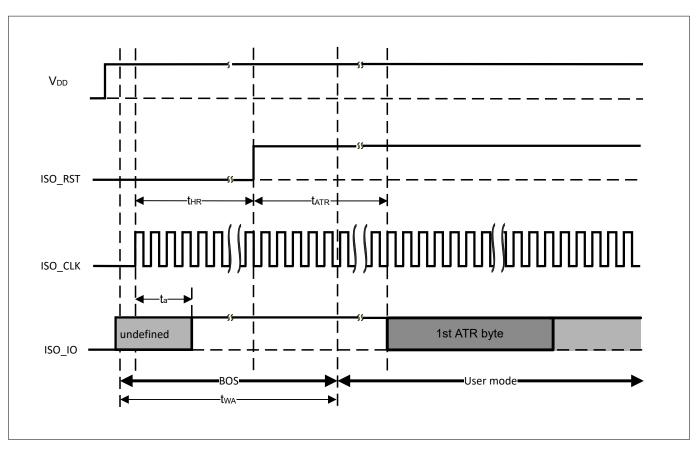

## 8.4.1.2 ISO/IEC 7816-3 power-on sequence

The power-on sequence is as follows:

- V<sub>DD</sub> is powered-on and ISO\_CLK is provided with a clock signal

- ISO\_IO must be set to 1-byte within 200 ISO clock cycles (t<sub>a</sub>)

- ISO\_RST should be held in the low state for a minimum of 80  $\mu$ s (t<sub>HR</sub>); that is equal to 400 clock cycles at 5 MHz before it is switched to the high state. At external clock frequencies higher than 5 MHz, more than 400 clock cycles are necessary to achieve the minimum hold time of 80 µs

- The execution of the boot software (BOS) starts as soon as internal power is stable. It configures the system and enters user mode. The BOS does not need to send the answer to reset (ATR) because user mode is entered long before the ISO/IEC 7816-3 timing limits are reached

- According to ISO/IEC 7816-3 [21], the first byte of the ATR signal has to be sent at the earliest 400 and at the latest 40,000 ISO\_CLK cycles after the rising edge of the ISO\_RST signal

# infineon

#### 8 Electrical characteristics

Figure 19 ISO/IEC 7816-3 power-on sequence

A warm reset as defined in ISO/IEC 7816-3 [21] triggers a system reset of the chip.

# 8.4.2 SPI interface and protocol characteristics

The SPI interface on the OC1230 is compliant with the GlobalPlatform APDU Transport protocol T=1', as defined in [GP22\_APDU] [12], implementing the "SPI slave" role, supporting the following details:

- SPI-configuration "mode 0"

- Null-byte value '00'

- Polling mode

Depending on the configuration of the OC1230, the SPI interface may also support the SPI interrupt mode. If supported, the interrupt mode can optionally be used to manage the flow of data and optimize the efficiency of the communication between the OC1230 and the consumer device. For more details refer to GPIO0.7 as SPI interrupt (SPI IRQ).

The electrical characteristics of the SPI interface lines SCL, MOSI, MISO, and SS are given below.

This interface supports logical channels according to ISO/IEC 7816-4. Logical channels allow multiple application protocols to share the same physical connection, enabling the consumer device to manage multiple applications simultaneously.

# **Datasheet**

# 8 Electrical characteristics

# 8.4.2.1 Electrical characteristics

# Notes:

- 1. All currents flowing into the pad are considered to be positive

- **2.**  $T_A$  as given for the controller's operating temperature range unless otherwise stated

Table 18 DC characteristics

| Parameter           | Symbol          | Values                |      |                       | Unit | Note or test condition                              |

|---------------------|-----------------|-----------------------|------|-----------------------|------|-----------------------------------------------------|

|                     |                 | Min.                  | Тур. | Max.                  |      |                                                     |

| Pad supply voltage  | $V_{DD}$        | 1.08                  | -    | 1.98                  | V    |                                                     |

| Input high voltage  | V <sub>IH</sub> | 0.7 * V <sub>DD</sub> | -    | V <sub>DD</sub> + 0.3 | V    |                                                     |

| Input low voltage   | V <sub>IL</sub> | -0.3                  | -    | 0.3 * V <sub>DD</sub> | V    |                                                     |

| Output high voltage | V <sub>OH</sub> | 0.9 * V <sub>DD</sub> | -    | -                     | V    | / <sub>OH</sub> = -100 μA                           |

| Output low voltage  | V <sub>OL</sub> | -                     | -    | 0.1 * V <sub>DD</sub> | V    | I <sub>OL</sub> = 1.5 mA                            |

| Pad leakage         | I <sub>L</sub>  | -2                    | -    | 2                     | μΑ   | 0 V < V <sub>PAD</sub> < V <sub>DD</sub>            |

| Pad leakage         | I <sub>L</sub>  | -1                    | -    | 0.02                  | mA   | $-0.3 \text{ V} < V_{PAD} < V_{DD} + 0.3 \text{ V}$ |

Table 19 AC characteristics

| Parameter                 | Symbol                 | Values                   |                         |                         | Unit | Note or test condition                                                                  |  |

|---------------------------|------------------------|--------------------------|-------------------------|-------------------------|------|-----------------------------------------------------------------------------------------|--|

|                           |                        | Min.                     | Тур.                    | Max.                    |      |                                                                                         |  |

| SCLK frequency,<br>mode 0 | $f_{SCLK}$             | -                        | -                       | 8                       | MHz  |                                                                                         |  |

| SCLK clock period         | t <sub>SCLK_rang</sub> | 1/f <sub>SCLK</sub> -5%  | -                       | 1/f <sub>SCLK</sub> +5% | μs   | Measured at input pad voltage of 0.5 * V <sub>DD</sub>                                  |  |

| SCLK nominal clock period | t <sub>SCLK</sub>      | -                        | 1/<br>f <sub>SCLK</sub> | -                       | μs   | -                                                                                       |  |

| SCLK low time             | t <sub>SCLKL</sub>     | 0.45 * t <sub>SCLK</sub> | -                       | -                       | μs   | Measured at input pad voltage of 0.5 * V <sub>DD</sub>                                  |  |

| SCLK high time            | t <sub>SCLKH</sub>     | 0.45 * t <sub>SCLK</sub> | -                       | -                       | μs   | Measured at input pad voltage of 0.5 * V <sub>DD</sub>                                  |  |