## 特長

### ■ ハーバードアーキテクチャ プロセッサ

- 最大 24 MHz のクロックで動作する M8C プロセッサ

- 8x8 乗算、32 ビット加算器

- 高速でありながら低消費電力

- 動作電圧 3.0V ~ 5.25V

- 工業用温度範囲に対応 : -40 °C ~ +85 °C

### ■ 高度な周辺回路 (PSoC® ブロック)

- 4 個の Rail to Rail アナログ PSoC ブロックの特長

- ・ 最大 14 ビットの ADC

- ・ 最大 8 ビットの DAC

- ・ プログラマブル ゲインアンプ

- ・ プログラマブル フィルタとプログラマブル コンパレータ

- 4 個のデジタル PSoC ブロックの特長

- ・ 8 ~ 32 ビットのタイマ、カウンタ、および PWM

- ・ CRC モジュールおよび PRS モジュール

- ・ UART

- ・ 複数の SPI マスタまたは SPI スレーブ

- ・ すべての GPIO ピンに接続可能

- ブロックの組み合わせで構成する複雑な周辺回路

- モータの制御に最適化された高速 8 ビット SAR ADC

- 高精度なプログラマブル クロック

- 24 MHz と 48 MHz の内部発振器 (精度 ± 5%)

- オプションの 32 kHz 水晶振動子と PLL による高精度な 24 MHz クロック

- 最大 24 MHz の外部発振器使用可能

- ウオッチドッグとスリープ用の内部発振器

### ■ 柔軟性のあるオンチップ メモリ

- 50,000 回の消去と書き込みが可能な 8K バイト フラッシュによるプログラム領域

- 256 バイト SRAM によるデータ領域

- システム内シリアル プログラミング (ISSP)

- フラッシュの部分的な更新に対応

- 柔軟性のある保護モード

- フラッシュによる EEPROM のエミュレーション

### ■ プログラマブルなピン構成

- すべての GPIO で 25 mA のシンクに対応

- すべての GPIO でプルアップ、プルダウン、High-Z、ストロング、オープン ドラインの各駆動モードに対応

- GPIO 上で最大 10 個のアナログ入力を実現

- GPIO 上で 2 個の 30 mA アナログ出力を実現

- すべての GPIO でコンフィグレーション可能な割り込み

### ■ その他のシステム リソース

- 400 kHz クロックの I<sup>2</sup>C によるスレーブ、マスタ、およびマルチマスター

- ウオッチドッグ タイマおよびスリープ タイマ

- ユーザ側でコンフィグレーション可能な低電圧検出

- 内蔵の監視回路

- 高精度なオンチップリファレンス電圧

- すべてを備えた開発ツール

- 無償の開発ソフトウェア (PSoC Designer™)

- 必要な機能を網羅したインサーキット エミュレータおよびインサーキット プログラマ

- フルスピードのエミュレーション

- 複雑なブレークポイント構造に対応

- 128K バイト トレース メモリ

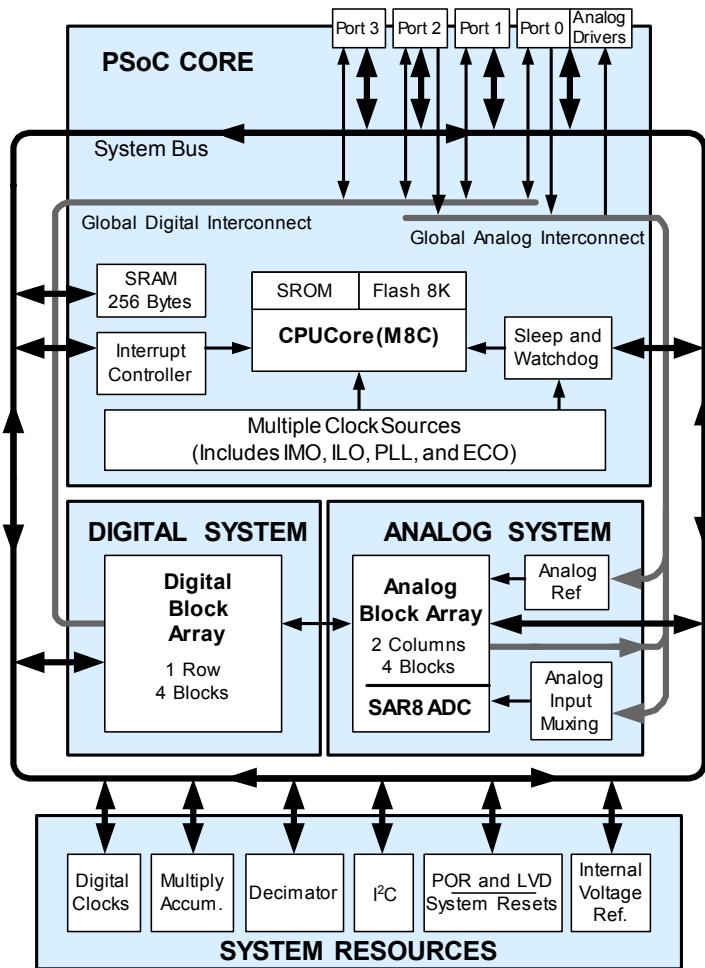

## ブロック図

## PSoC 機能の概要

PSoC ファミリは、オンチップのコントローラデバイスを搭載した多数の Programmable System-on-Chip で構成されます。これらのデバイスは、従来の MCU ベースのシステム部品を複数使用した構成を、低コストでプログラマブルなシングルチップデバイスで置き換えることを目的としています。PSoC デバイスは、コンフィグレーション可能なアナログロジックとデジタルロジックのブロックを備え、これらのブロック間の相互接続はプログラム可能です。このアーキテクチャによって、個々の用途の要件に合わせた周辺回路構成のカスタマイズが可能となります。さらに、高速 CPU、フラッシュプログラム領域、SRAM データ領域、およびコンフィグレーション可能な I/O が、使いやすいピン配列のパッケージに収められています。

ブロック図に示すように、PSoC アーキテクチャは、4 個の主要な領域である PSoC コア、デジタルシステム、アナログシステム、およびシステムリソースで構成されます。コンフィグレーション可能なグローバルバスにより、すべてのデバイスリソースを組み合わせて完全なカスタムシステムを構築できます。PSoC の CY8C24x33 ファミリは、グローバルデジタルとグローバルアナログにて相互接続可能な最大 3 個の I/O ポートを備えています。これらのポートから 4 個のデジタルブロックおよび 4 個のアナログブロックにアクセスできます。

### PSoC コア

PSoC コアは、充実した機能セットを持つ高性能なエンジンです。このコアは、CPU、メモリ、クロック、およびコンフィグレーション可能な GPIO（汎用 I/O）を備えています。

M8C CPU コアは最高 24 MHz で動作する高性能プロセッサで、4 MIPS の性能を持つ 8 ビットハーバードアーキテクチャマイクロプロセッサを提供します。この CPU では、11 のベクタを持つ割り込みコントローラを使用して、リアルタイム組み込みイベントのプログラミングを簡素化しています。プログラムの実行は、組み込まれたスリープタイマとウォッチドッグタイマ (WDT) を使用してタイミングが管理され、保護されます。

メモリは、プログラム領域用の 8 KB フラッシュ、データ領域用の 256 バイト SRAM、およびフラッシュを使用してエミュレートする最大 2 KB の EEPROM で構成されています。プログラム フラッシュには 64 バイトのブロックに対して 4 段階の保護レベルが用意されているので、これを使用してソフトウェアの IP 保護をカスタマイズできます。

PSoC デバイスは、柔軟性のある各種内部クロックジェネレータを備えています。広い範囲の温度と電圧にわたって ±5% の精度を発揮する 24 MHz IMO（内部メイン発振器）もこのジェネレータの 1 つです。この 24 MHz IMO は、周波数を 2 倍の 48 MHz にして、デジタルシステムで使用することもできます。スリープタイマと WDT 用に低消費電力の 32 kHz ILO（内部低速発振器）が用意されています。水晶精度を必要とする場合は、ECO（32.768 kHz の外部水晶振動子）をリアルタイムクロック (RTC) として使用できるほか、必要に応じ、PLL を使用して水晶精度の 24 MHz システムクロックを生成できます。これらのクロックを、プログラマブルなクロック分周器（システムリソースの一部）と組み合わせて使用すれば、ほぼあらゆるタイミング要件を PSoC デバイスに組み込むことができる柔軟性が得られます。

PSoC の GPIO は、デバイスの CPU、デジタルリソース、およびアナログリソースに接続しています。各ピンの駆動モードは 8 種類のオプションから選択できるため、外部とのインターフェースを非常に柔軟に設定できます。また、各ピンには、HIGH レベル、LOW レベル、および前回読み出し時からの変化に基づいてシステム割り込みを発生する機能もあります。

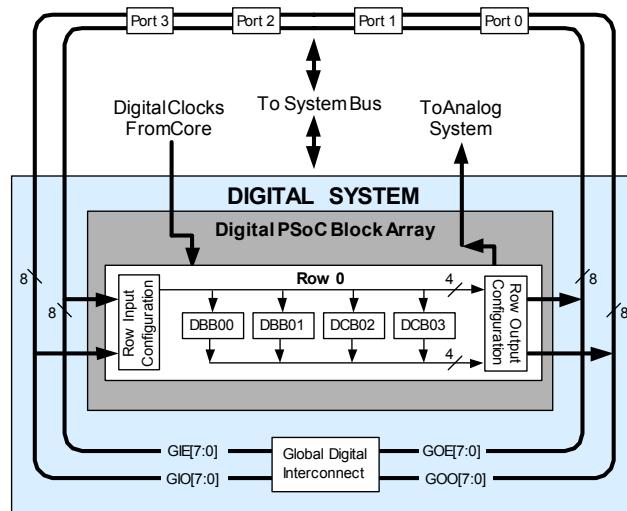

## デジタルシステム

デジタルシステムは 4 個のデジタル PSoC ブロックで構成されます。各ブロックは 8 ビットのリソースであり、単独で使用できるほか、他のブロックと組み合わせ、ユーザモジュールリファレンスという 8 ビット、16 ビット、24 ビット、および 32 ビットの周辺回路を構成することができます。

図 1. デジタルシステムのブロック図

デジタル周辺回路の構成には次のようなものが考えられます。

- PWM (8 ~ 32 ビット)

- デッドタイムを備えた PWM (8 ~ 32 ビット)

- カウンタ (8 ~ 32 ビット)

- タイマ (8 ~ 32 ビット)

- 選択可能なパリティを持つ UART 8 ビット (最大 1 個)

- SPI マスタおよび SPI スレーブ (最大 1 個)

- I2C スレーブと I2C マスタ (システムリソースとして 1 個可能)

- CRC チェッカ／ジェネレータ (8 ~ 32 ビット)

- IrDA (最大 1 個)

- 疑似ランダム系列発生器 (8 ~ 32 ビット)

すべての信号とピンの間を自由に配線できるグローバルバスを介して、任意の GPIO にデジタルブロックを接続します。また、バスを使用することで信号の多重化や論理演算も可能です。このような柔軟な構成により、固定された周辺コントローラに伴う制約を受けずに設計できます。

デジタルブロックは 4 個のローで構成され、ブロックの数は PSoC デバイスファミリごとに異なります。用途に応じて最適なシステムリソースを選択できます。5 ページの・にファミリリソースを示します。

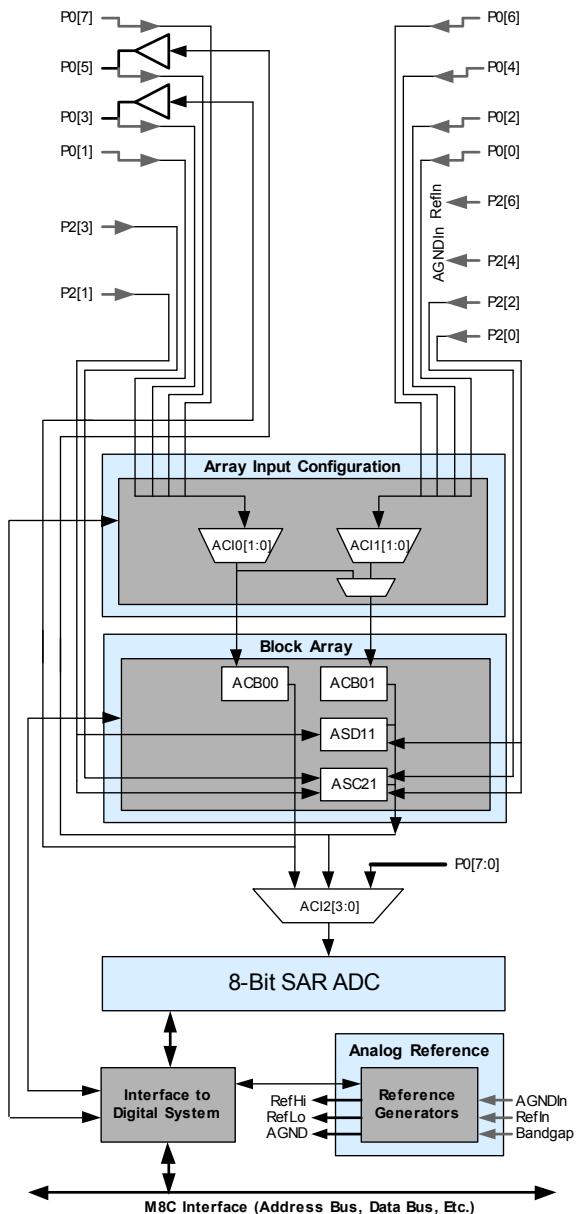

## アナログシステム

アナログシステムは、8ビットSAR ADCと4個のコンフィグレーション可能なブロックで構成されています。プログラマブルな8ビットSAR ADCは、最大300 Kspsで動作する最適化されたADCであり、単調性が保証されています。また、モータ制御の用途に対応する機能も備えています。

アナログブロックごとにオペアンプ回路を持っているので、複雑なアナログ信号系を構築できます。アナログ周辺回路には高い柔軟性があり、用途の具体的な要件に合わせてカスタマイズできます。一般的なPSoCアナログ機能として、以下の機能があります（ほとんどはユーザモジュールとして実現可能です）。

- フィルタ（2～4ポールのバンドパス、ローパス、およびノッチ）

- アンプ（最大2個、48xまでのゲインを選択可能）

- 計算用アンプ（最大1個、93xまでのゲインを選択可能）

- コンパレータ（最大2個、16種類のしきい値を選択可能）

- DAC（最大2個、6～9ビットの分解能）

- 乗算型DAC（最大2個、6～9ビットの分解能）

- 大電流出力ドライバ（30 mA駆動でコアリソースとして2個）

- 1.3Vリファレンス電圧（システムリソースとして可能）

- DTMF

- 变调器

- 相関器

- ピーク検出器

- 他に多数のトポロジが可能

アナログブロックは、1個のCT（連続時間）ブロックと2個のSC（スイッチドキャパシタ）ブロックの3個のブロックのコラムで編成されます。アナログコラム0には、標準のSCブロックではなく、SAR8 ADCブロックがあります。

図2. アナログシステムのブロック図

## その他のシステム リソース

システム リソースは、システムの構築に効果的な追加機能を提供します。一部のシステム リソースについてはすでに説明しました。この他の追加リソースとして、乗算器、デシメータ、低電圧検出、パワーオンリセットなどがあります。ここでは、各システム リソースの利点について簡単に説明します。

- デジタルクロック分周器は、各種用途向けにカスタマイズ可能な3種類のクロック周波数を提供します。このクロックは、デジタルとアナログの両方のシステムで使用できます。デジタル PSoC ブロックをクロック分周器として使用することで、別のクロックを生成できます。

- 積和演算器 (MAC) は、32ビット加算器による高速8ビット乗算器であり、一般的な数学演算とデジタル フィルタの実行に使用すると効果的です。

- デシメータは、デルタ シグマ ADC の作成などのデジタル信号処理用途向けにカスタムハードウェア フィルタを提供します。

- I2C モジュールは、100 kHz と 400 kHz による2線式の通信をサポートします。スレーブ、マスター、およびマルチマスターのいずれのモードにも対応できます。

- 低電圧検出 (LVD) 割り込みは、電圧レベルの低下を通知する信号をアプリケーションに送信します。同時に、高度なPOR (パワーオンリセット) 回路を使用することでシステム監視が不要になります。

- 1.3V の内部リファレンス電圧は、ADC や DAC などのアナログシステムにリファレンス電圧を提供します。

## PSoC デバイスの特性

PSoC デバイスの特性に応じて、デジタル システムとアナログ システムは 16 個、8 個、または 4 個のデジタル ブロックと 12 個、6 個、または 3 個のアナログ ブロックを持つことができます。次の表に特定の PSoC デバイス グループで使用可能なリソースを示します。

表 1. PSoC デバイスの特性

| PSoC 部品<br>番号 | デジタル<br>I/O<br>数 | デジタル<br>ロー<br>数 | デジタル<br>ブロ<br>ック<br>数 | デジタル<br>入力<br>数 | アナロ<br>グ<br>入力<br>数 | アナロ<br>グ<br>出力<br>数 | アナロ<br>グ<br>コラム<br>数 | アナロ<br>グ<br>ブロ<br>ック<br>数 | SAR8<br>ADC |

|---------------|------------------|-----------------|-----------------------|-----------------|---------------------|---------------------|----------------------|---------------------------|-------------|

| CY8C29x66     | 最大<br>64         | 4               | 16                    | 12              | 4                   | 4                   | 12                   | なし                        |             |

| CY8C27x43     | 最大<br>44         | 2               | 8                     | 12              | 4                   | 4                   | 12                   | なし                        |             |

| CY8C24x94     | 56               | 1               | 4                     | 48              | 2                   | 2                   | 6                    | なし                        |             |

| CY8C24633     | 最大<br>25         | 1               | 4                     | 12              | 2                   | 2                   | 4                    | あり                        |             |

| CY8C24x23A    | 最大<br>24         | 1               | 4                     | 12              | 2                   | 2                   | 6                    | なし                        |             |

| CY8C21x34     | 最大<br>28         | 1               | 4                     | 28              | 0                   | 2                   | 4 <sup>[1]</sup>     | なし                        |             |

| CY8C21x23     | 16               | 1               | 4                     | 8               | 0                   | 2                   | 4 <sup>[1]</sup>     | なし                        |             |

| CY8C20x34     | 最大<br>28         | 0               | 0                     | 28              | 0                   | 0                   | 3 <sup>[2]</sup>     | なし                        |             |

注:

1. アナログ機能に制約あり

2. 2 個のアナログ ブロックおよび 1 個の CapSense®

## Document History Page

**Document Title:** CY8C24633 PSoC(R) Programmable System-On-Chip (JA)

**Document Number:** 001-62916

| Revision | ECN     | Orig. of Change | Submission Date | Description of Change |

|----------|---------|-----------------|-----------------|-----------------------|

| **       | 2975948 | FSU             | 7/9/2010        | New Spec              |

---

© Cypress Semiconductor Corporation (サイプレス セミコンダクタ コーポレーション)、2010。本文書に記載される情報は、事前の予告なく変更されることがあります。サイプレス セミコンダクタ コーポレーションは、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対しても一切の責任を負いません。かつ、サイプレスセミコンダクタ コーポレーションは、特許またはその他の権利に基づくライセンスを譲渡することも、又は含意することもありません。サイプレス製品は、サイプレスとの書面による明示的な合意に基づくものではない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される、生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス 製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

PSoC Designer™、Programmable System-on-Chip™、および PSoC Creator™ はサイプレス セミコンダクタ コーポレーションの商標であり、PSoC® は、サイプレス セミコンダクタ コーポレーションの登録商標です。本文書で言及するその他全ての商標または登録商標は、各社の所有物です。

全てのソース コード (ソフトウェアおよび / またはファームウェア) はサイプレス セミコンダクタ コーポレーション (以下サイプレス) が所有し、全世界の特許権保護 (米国およびその他の国)、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占的かつ譲渡不能のライセンスであって、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび / またはカスタムファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することは全て禁止されます。

免責条項：サイプレスは、明示的または黙示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス 製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。