## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

1 ~ 33 ボタンと 0 ~ 6 スライダーの

SmartSense™ 自動チューニングを備えた 1.8V

プログラマブル CapSense® コントローラー

## 特長

- SmartSense自動チューニングを備えた低消費電力CapSense® ブロック

- 特許 CSA\_EMC、CSD センシング アルゴリズム

- SmartSense\_EMC 自動チューニング

- ・ 実行中に最適なセンサーの性能を設定し維持

- ・ 開発と量産段階のシステム チューニングの必要性を排除

- ・ 製造工程でのばらつきを補正。平均消費電力が低い：動作時に  $28\mu A$  センサー (125ms ごとに 1 回ウェイクアップしてスキャン)

- 高性能ハーバード アーキテクチャ プロセッサ

- 最高速度 24MHz の M8C CPU

- 動作電圧範囲 : 1.71V ~ 5.5V

- スタンバイ モード :  $1.1\mu A$  (Typ)

- ディープ スリープ :  $0.1\mu A$  (Typ)

- 動作温度範囲 : -40°C ~ +85°C

- 柔軟性のあるオンチップ メモリ

- 8KB フラッシュ、1KB SRAM

- 16KB フラッシュ、2KB SRAM

- 32KB フラッシュ、2KB SRAM

- EEPROM エミュレーションによる Read-While-Write 機能

- 5 万回の消去／書き込みが可能なフラッシュ

- インシステム プログラミングにより製造プロセスを簡略化

- 4 つのクロック ソース

- 内部主発振器 (IMO): 6 / 12 / 24MHz

- ウオッチドッグおよびスリープ タイマー用の 32kHz 内部低速発振器 (ILO)

- 32kHz 外部水晶発振器

- 外部クロック入力

- プログラマブルなピン構成

- ボタンまたはスライダーとして設定可能な最大36本の汎用 I/O (GPIO)

- デュアルモード GPIO (アナログ入力とデジタルI/Oに対応)

- 各 GPIO で 25mA の高いシンク電流に対応

- ・ すべての GPIO で合計 120mA までのシンク電流に対応

- ソース電流

- ・ ポート 0 と 1 では 5mA

- ・ ポート 2, 3, 4 では 1mA

- 設定可能な内部プルアップ、High-Z とオープン ドレイン モード

- ポート 1 上の選択可能な安定化デジタル I/O

- ポート 1 上の設定可能な入力閾値

- 汎用性の高いアナログ機能

- 内部アナログ バスは、連結近接センサーを形成するように複数のセンサー間の接続をサポート

- 高い電源電圧変動除去比 (PSRR) を実現する内部低ドロップアウト電圧レギュレータ

- フルスピード USB

- 12Mbps USB 2.0 に準拠

- その他のシステム リソース

- I2C スレーブ :

- ・ 50kHz、100kHz、または 400kHz を選択可能

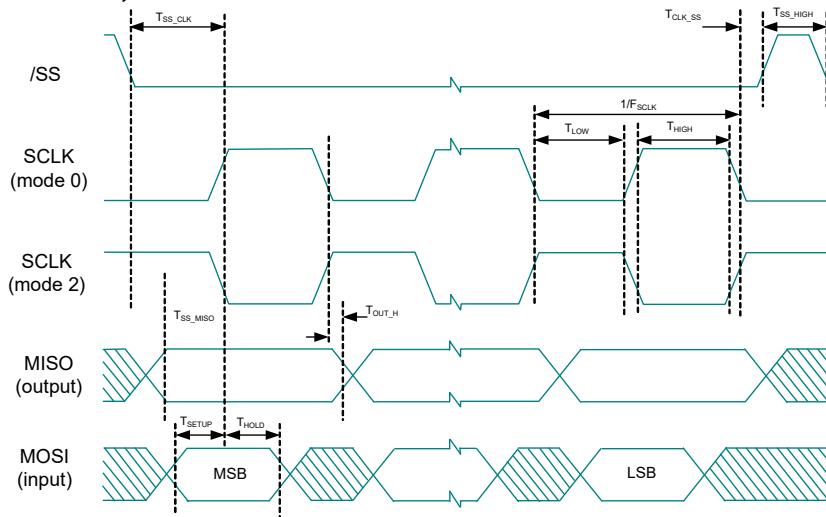

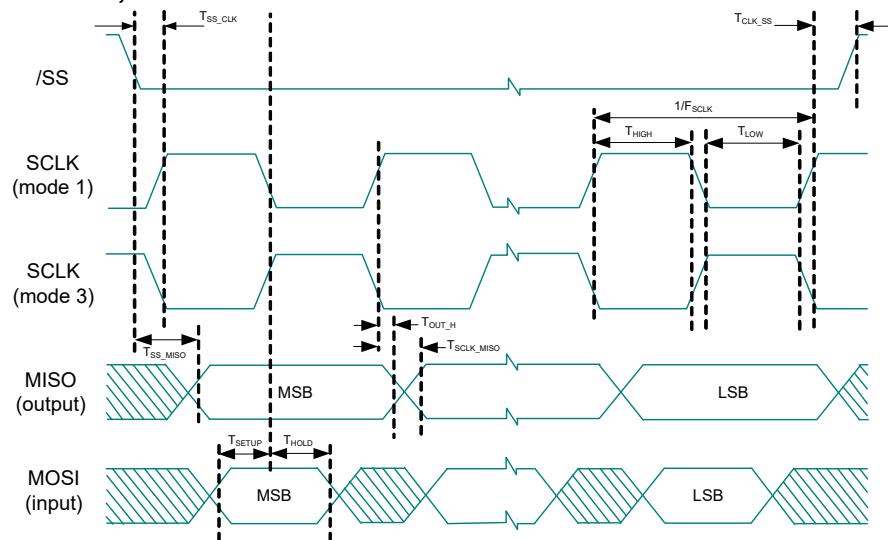

- 最大 12MHz の SPI マスターおよびスレーブとして構成可能

- 3 個の 16 ビット タイマー

- ウオッチドッグ タイマーとスリープ タイマー

- 内蔵の監視回路

- 内部基準電圧に対応した 10 ビット インクリメンタル アナログ - デジタル コンバーター (ADC)

- 2 個の汎用高速低消費電力アナログ コンバレータ

- 完全な開発ツール

- 無償の開発ツール (PSoC Designer™)

- センサーとパッケージのオプション

- 10 センサー - QFN 16, 24

- 16 センサー - QFN 24

- 22 / 25 センサー - QFN 32

- 24 センサー - WLCSP 30

- 31 センサー - SSOP 48

- 33 センサー - QFN 48

**エラッタ：**シリコン チップ エラッタに関する情報については、49 ページの「エラッタ」を参照してください。詳細には、トリガー条件、影響を受けるデバイス、および提案する回避策が含まれています。

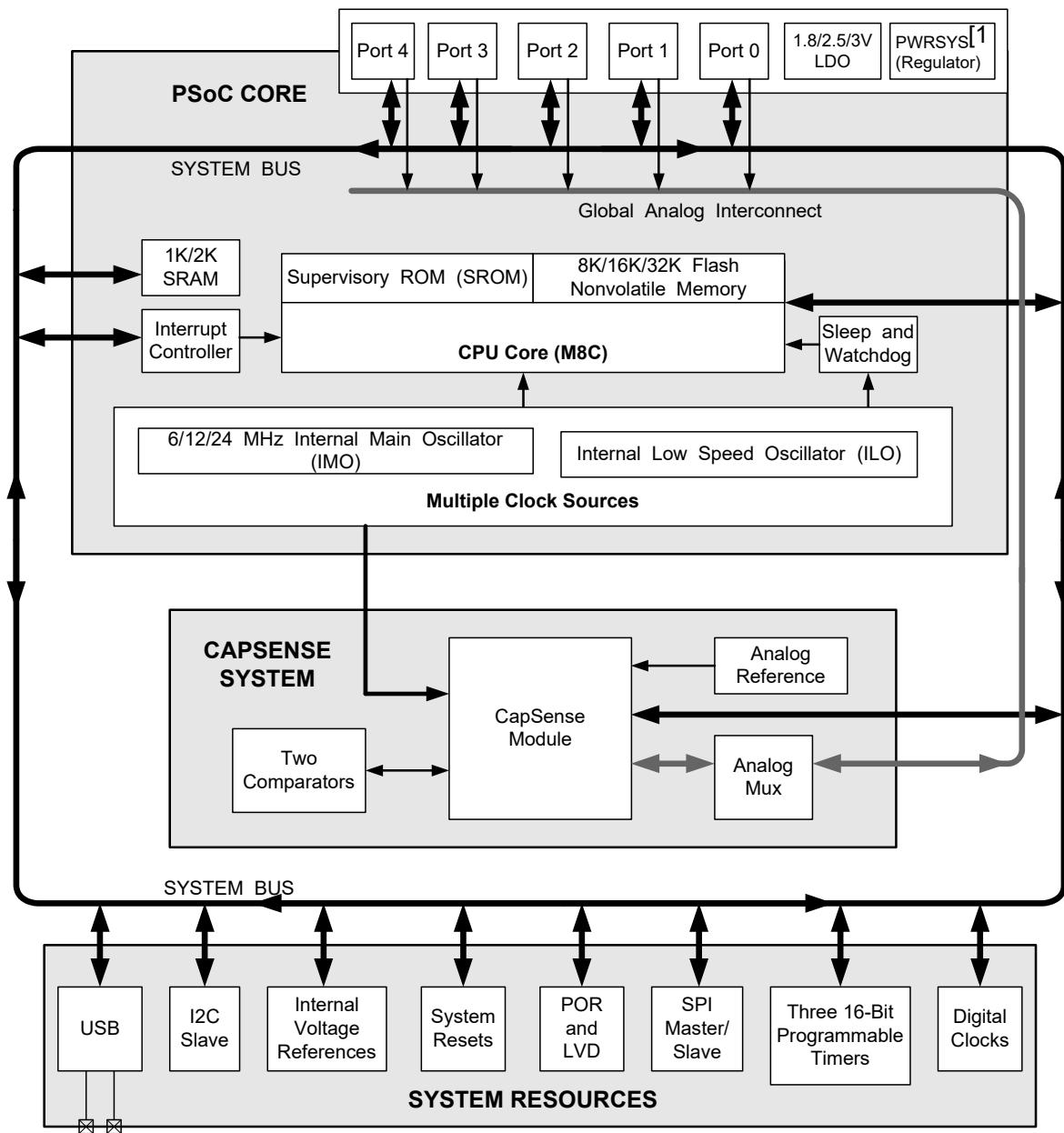

## 論理ブロック図

注：

- 内部回路用の内蔵電圧レギュレータ

## 詳細情報

サイプレスは、[www.cypress.com](http://www.cypress.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC デバイスを選択し、デバイスをデザインに迅速で効果的に統合する手助けをしています。リソースの総合リストについては、「[Resources Available for CapSense® Controllers - KBA92181](#)」知識ベース記事を参照してください。以下は CapSense のリソースの要約です。

- 概要 : CapSense ポートフォリオ、CapSense ロードマップ

- 製品セレクター: CapSense、CapSense Plus、CapSense Express、CapSense 付きの PSoC3、CapSense 付きの PSoC5、PSoC4。さらに、PSoC Designer は新規プロジェクト作成時のデバイス選択ツールも提供しています。

- アプリケーションノート: サイプレスは、基本レベルから上級レベルまでの様々なトピックに触れる CapSense アプリケーションノートを提供しています。以下は、CapSense 入門用の推奨アプリケーションノートです。

- [AN64846: CapSense 入門](#)

- [AN73034: CY8C20xx6A/H/AS CapSense® Design Guide](#)

- [AN2397: CapSense® データ表示ツール](#)

- テクニカルリファレンスマニュアル (TRM)

- [PSoC® CY8C20xx6A/AS/L Family Technical Reference Manual](#)

- 開発キット

- [CY3280-20x66 Universal CapSense Controller Kit](#) は、あらかじめ設定された制御回路、プラグイン ハードウェアを備

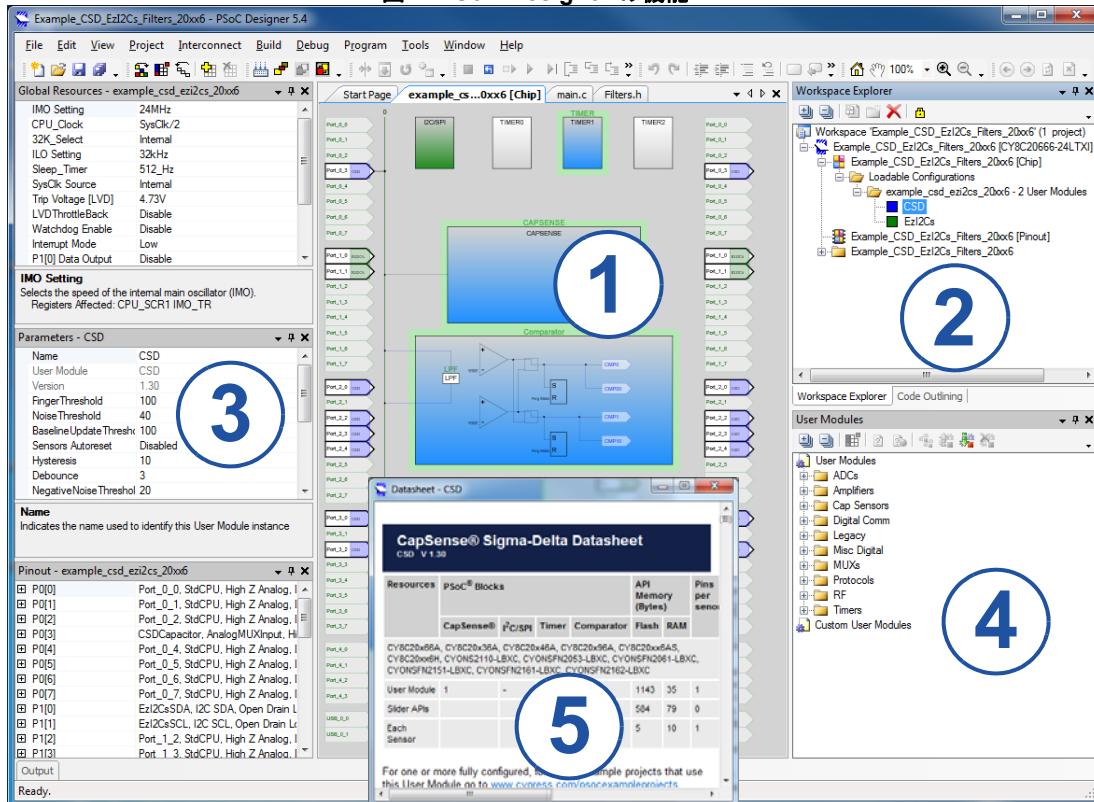

## PSoC Designer

PSoC Designer は無償の Windows ベースの統合開発環境 (IDE) です。このキットにより、CapSense ベースのシステムについて、ハードウェアとファームウェアの同時進行の設計が可能です (図 1 を参照してください)。PSoC Designer により、以下が可能となります。

1. ユーザー モジュールをドラッグ アンド ドロップして、メイン デザインワークスペースでハードウェアシステム デザインを構築します。

2. PSoC Designer IDE の C コンパイラを使用してアプリケーションのファームウェアと PSoC ハードウェアを相互設計します。

えており、プロトタイプやデバッグを簡単に行えます。調整およびデータ取得用にプログラミングおよび I2C-USB ブリッジ ハードウェアが含まれています。

- [CY3280-BMM Matrix Button Module Kit](#) は、4x4 マトリックス形式として構成される 8 個の CapSense センサーからなります (すなわち、16 個の物理的ボタンおよび 8 個の LED が形成される)。このモジュールは CY3280-20x66 ユニバーサル CapSense コントローラーを含むあらゆる CY3280 ユニバーサル CapSense コントローラー基板に接続します。

- [CY3280-BSM Simple Button Module Kit](#) は、10 個の CapSense ボタンと 10 個の LED からなります。このモジュールは CY3280-20x66 ユニバーサル CapSense コントローラーを含むあらゆる CY3280 ユニバーサル CapSense コントローラー基板に接続します。

[CY3217-MiniProg1](#) および [CY8CKIT-002 PSoC® MiniProg3](#) デバイスはフラッシュのプログラミング用のインターフェースを提供します。

3. ユーザー モジュールを設定します。

4. ユーザー モジュールのライブラリを利用します。

5. ユーザー モジュールのデータシートを確認します。

図 1. PSoC Designer の機能

## 目次

|                                        |    |                            |    |

|----------------------------------------|----|----------------------------|----|

| <b>PSoC® 機能概要</b>                      | 5  | プログラミングの DC 仕様             | 26 |

| PSoC コア                                | 5  | I2C の DC 仕様                | 27 |

| CapSense システム                          | 5  | リファレンスバッファの DC 仕様          | 27 |

| その他のシステム リソース                          | 6  | IDAC の DC 仕様               | 27 |

| <b>はじめに</b>                            | 7  | チップ レベルの AC 仕様             | 28 |

| CapSense 設計ガイド                         | 7  | GPIO の AC 仕様               | 29 |

| シリコン エラッタ                              | 7  | コンパレータの AC 仕様              | 30 |

| 開発キット                                  | 7  | 外部クロックの AC 仕様              | 30 |

| トレーニング                                 | 7  | プログラミングの AC 仕様             | 31 |

| CYPros コンサルタント                         | 7  | I2C の AC 仕様                | 32 |

| ソリューションズ ライブラリ                         | 7  | <b>パッケージ情報</b>             | 36 |

| テクニカル サポート                             | 7  | 熱インピーダンス                   | 40 |

| <b>開発ツール</b>                           | 8  | 水晶振動子ピンの静電容量               | 40 |

| PSoC Designer ソフトウェア サブシステム            | 8  | はんだリフローの仕様                 | 40 |

| <b>PSoC Designer を使用したデザイン</b>         | 9  | <b>開発ツールの選択</b>            | 41 |

| ユーザー モジュールの選択                          | 9  | ソフトウェア                     | 41 |

| ユーザー モジュールの設定                          | 9  | 開発キット                      | 41 |

| 構成および接続                                | 9  | 評価ツール                      | 41 |

| 生成、検証、およびデバッグ                          | 9  | デバイス プログラマ                 | 41 |

| <b>ピン配列</b>                            | 10 | アクセサリ (エミュレーションおよびプログラミング) | 42 |

| 16 ピン QFN (10 本のセンシング入力 )[3, 4]        | 10 | サードパーティ ツール                | 42 |

| 24 ピン QFN (17 本のセンシング入力 )[8]           | 11 | 基板上の PSoC エミュレータの構築        | 42 |

| 24 ピン QFN (15 本のセンシング入力 (USB 付き ))[13] | 12 | <b>注文情報</b>                | 43 |

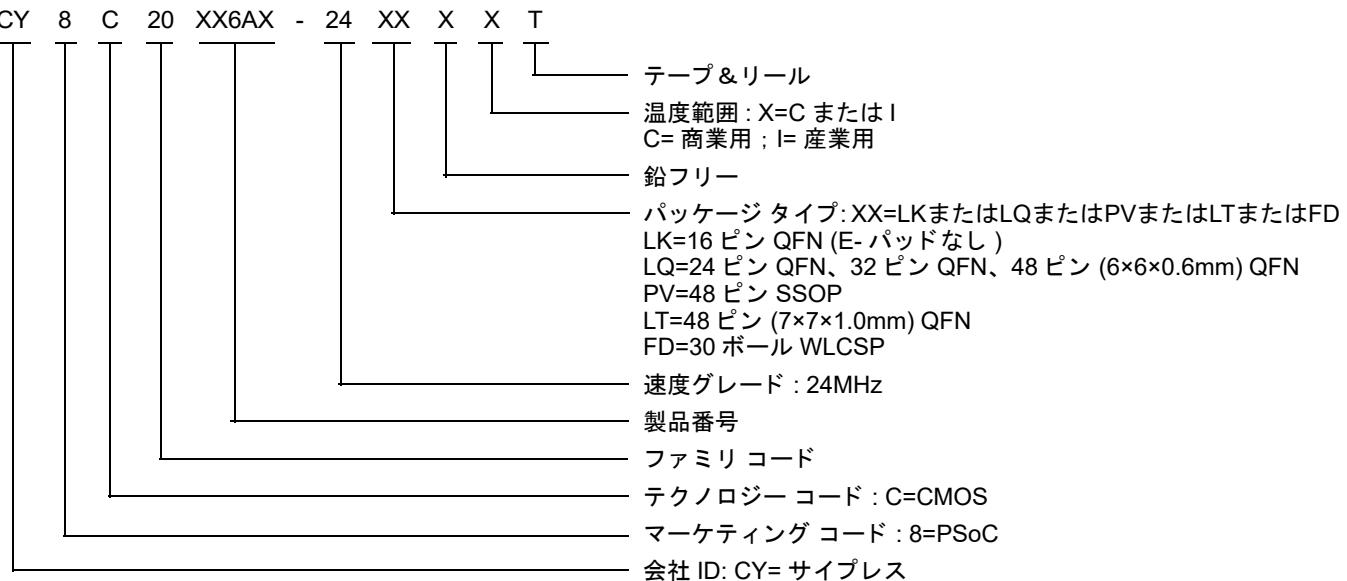

| 30 ポール WLCSP (24 本のセンシング入力 )[18]       | 13 | 注文コードの定義                   | 45 |

| 32 ピン QFN (25 本のセンシング入力 )[22]          | 14 | <b>略語</b>                  | 46 |

| 32 ピン QFN (22 本のセンシング入力 (USB 付き ))[27] | 15 | <b>参考資料</b>                | 46 |

| 48 ピン SSOP (31 本のセンシング入力 )[32]         | 16 | 本書の表記法                     | 47 |

| 48 ピン QFN (33 本のセンシング入力 )[36]          | 17 | 測定単位                       | 47 |

| 48 ピン QFN (33 本のセンシング入力 (USB 付き ))[41] | 18 | 数値の表記                      | 48 |

| 48 ピン QFN (OCD) (33 本のセンシング入力 )[46]    | 19 | <b>用語集</b>                 | 48 |

| <b>電気的仕様</b>                           | 20 | エラッタ                       | 49 |

| 絶対最大定格                                 | 20 | 認定の状態                      | 49 |

| 動作温度                                   | 20 | エラッタのまとめ                   | 49 |

| チップ レベルの DC 仕様                         | 21 | <b>改訂履歴</b>                | 52 |

| GPIO の DC 仕様                           | 22 | <b>セールス、ソリューションおよび法律情報</b> | 53 |

| アナログ マルチプレクサ バスの DC 仕様                 | 24 | ワールドワイドな販売と設計サポート          | 53 |

| 低消費電力コンパレータの DC 仕様                     | 24 | 製品                         | 53 |

| コンパレータ ユーザー モジュールの電気的仕様                | 25 | PSoC® ソリューション              | 53 |

| ADC の電気的仕様                             | 25 | サイプレス開発者コミュニティ             | 53 |

| POR および LVD の DC 仕様                    | 26 | テクニカル サポート                 | 53 |

## PSoC® 機能概要

PSoC ファミリは、複数の従来型マイクロコントローラー ユニット (MCU) ベースのコンポーネントを低コストのプログラム可能なシングルチップ コンポーネント 1 台で置き換えるように設計された、オンチップ コントローラー デバイスで構成されています。PSoC デバイスは、設定可能なアナログ ブロックとデジタル ブロック、およびプログラム可能な相互接続を備えています。このアーキテクチャによって、個々の用途の要件に合わせたペリフェラル構成のカスタマイズが可能となります。さらに、高速 CPU、フラッシュ プログラム メモリ、SRAM データ メモリ、および設定可能な I/O が、使いやすいピン配列でまとめられています。

2 ページの論理ブロック図に示すように、このデバイス ファミリのアーキテクチャは 3 個の主要な領域で構成されます。

### ■ コア

#### ■ CapSense アナログ システム

#### ■ システム リソース (フルスピード USB ポートを含む)

共通の汎用バスを使用し、I/O とアナログ システムを接続できます。

各 CY8C20XX6A/S PSoC デバイスは、容量センシングを利用したアプリケーション向けのセンシングとスキャンの制御回路を備えた専用の CapSense ブロックを内蔵します。PSoC のパッケージにより、最大 36 個の GPIO があります。GPIO は、MCU およびアナログ マルチプレクサへのアクセスを提供します。

## PSoC コア

PSoC コアは、充実した命令セットを持つ強力なエンジンです。このコアは、データ記憶用の SRAM、割り込みコントローラー、スリープ タイマーとウォッチドッグ タイマー、および IMO と ILO で構成されています。M8C と呼ばれる CPU コアは、最大 24MHz で動作する高性能プロセッサです。M8C は、4-MIPS の 8 ビット ハーバードアーキテクチャ マイクロプロセッサです。

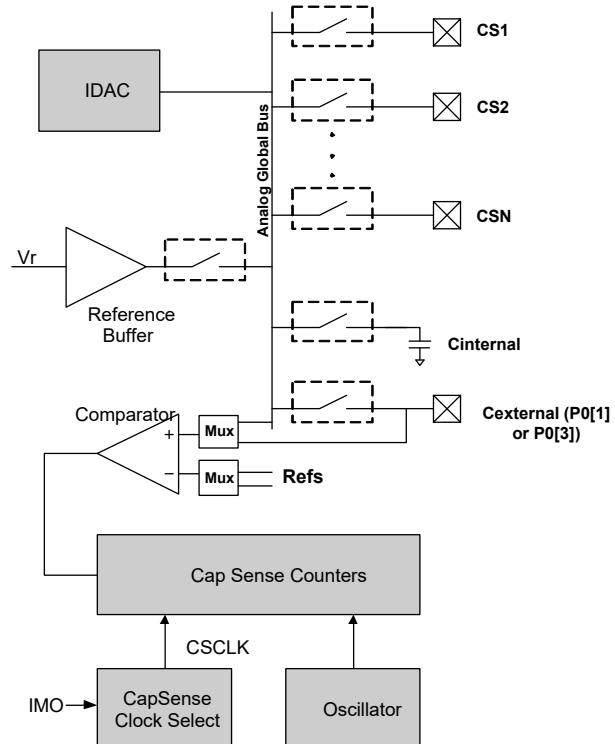

## CapSense システム

アナログ システムには、容量センシング ハードウェアが装備されています。サポートされているハードウェア アルゴリズムがいくつかあります。このハードウェアは、外部部品を必要とせずに容量センシングおよびスキャンを実現します。アナログ システムは、CapSense PSoC ブロックと 1V または 1.2V 内部アナログ基準電圧で構成され、これらはともに最大 33 本の入力の容量センシングに対応します<sup>[2]</sup>。容量センシングは、各 GPIO ピンで設定可能です。有効な CapSense ピンのスキャンは、複数のポートで迅速、容易に実行できます。

### SmartSense

SmartSense は、CapSense アプリケーションにおける手動による調整を排除する、サイクロスの画期的なソリューションです。このソリューションは使いやすく、安定したノイズ耐性を

提供します。必要なパラメーター全てを確立、監視、維持する、唯一の自動調整ソリューションです。SmartSense により、エンジニアは PCB やオーバーレイ素材の特性による製造ばらつきを再調整することなく、プロトタイピングから大量生産に移行できます。

### SmartSense\_EMC

SmartSense\_EMC ユーザー モジュールは、CapSense アプリケーションの手動チューニングを排除するための SmartSense 自動チューニング アルゴリズムの他に、高周波の伝導および放射ノイズに対する容量センシング アルゴリズム／回路の耐久性を改善する独自のアルゴリズムを組み込んでいます。各電子デバイスは、放射および伝導された外部ノイズの一定の制限を厳守する必要があります、これらの制限は規制機関 (FCC, CE, UL など) で規定されています。非常に優れた PCB レイアウト設計、電源設計およびシステム設計は、製品が伝導と放射ノイズ テストに合格するための必須条件です。理想的な PCB レイアウト、電源設計またはシステム設計は、製品のコストや形状の制限により実現できないことがあります。優れたノイズ耐性を持つ SmartSense\_EMC は、こうしたアプリケーションを放射と伝導ノイズ テストに合格させるために適しており、便利です。

図 2. CapSense システムのブロック図

注：

2. 36 本の GPIO= 容量センシング用の 33 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

### アナログ マルチプレクサ システム

アナログ マルチプレクサ バスは、どの GPIO ピンにも接続できます。ピンは、バスに個別に接続できるほか、任意の組み合わせでも接続できます。このバスをアナログ システムに接続すると、CapSense ブロック コンパレータによる分析も可能です。

スイッチ制御ロジックにより、選択したピンをハードウェア制御で連続的にプリチャージできます。これにより、タッチ センシングなどの用途で容量測定が可能になります。マルチプレクサには、他にも次のような用途があります。

- スライダーやタッチパッドなどの複雑な容量センシング インターフェース

- 任意の I/O ピンからアナログ入力が可能なチップ全体規模のマルチプレクサ

- 任意の I/O ピンの組み合わせによるクロスポイント接続

### その他のシステム リソース

システム リソースは、設定可能な USB、I<sup>2</sup>C スレーブおよび SPI マスター／スレーブの通信インターフェース、3 個の 16 ビット プログラマブルなタイマー、M8C がサポートする様々なシステム リセットなどの他の機能を提供します。

システム リソースは、完全なシステムに役立つ追加機能を提供します。その他の追加リソースとして、低電圧検出やパワーオン リセットなどがあります。各システム リソースの利点は、以下のとおりです。

- I<sup>2</sup>C スレーブと SPI マスタースレーブ モジュールは、2 線式で 50kHz、100kHz、および 400kHz での通信をサポートします。3 線式または 4 線式の SPI 通信速度は 46.9kHz ~ 3MHz です（低速のシステム クロックほどこの周波数が低くなります）。

- 低電圧検出 (LVD) 割り込みは、電圧レベルの低下を通知する信号をアプリケーションに送信します。その一方、高度な POR (パワーオン リセット) 回路を使用することでシステム 監視が不要になります。

- 内部基準電圧は、容量センシング用の絶対基準電圧を提供します。

- レジスタ制御バイパス モードを使用すると、LDO を無効にできます。

## はじめに

PSoC シリコン チップを効率的に理解するには、このデータシートを読み、PSoC Designer 統合開発環境 (IDE) を使用してみることをお勧めします。このデータシートは PSoC 集積回路の概要を紹介し、特定のピンとレジスタの仕様、および電気的仕様を示します。

詳細情報やプログラミングの詳細については、この CY8C20XX6A/SPSoc デバイスの [Technical Reference Manual](#) を参照してください。

注文、パッケージ、および電気的仕様の最新情報は [www.cypress.com/psoc](http://www.cypress.com/psoc) にある最新の PSoC デバイス データシートを参照してください。

### CapSense 設計ガイド

設計ガイドには、各種の CapSense 設計が掲載されています。これらは [www.cypress.com/go/CapSenseDesignGuides](http://www.cypress.com/go/CapSenseDesignGuides) から入手できます。

CapSense 設計に関する情報は「Getting Started with CapSense」設計ガイドを参照してください。また、CY8C20XX6A/AS CapSense コントローラーの特定の情報は「CY8C20XX6A/H/AS CapSense® Design Guide」を参照してください。

### シリコン エラッタ

シリコンに関する既知の問題を扱っているエラッタ資料には、エラッタのトリガ状況、影響の範囲、可能な回避手段、シリコン リビジョンの適用可能性について記載されています。CY8C20xx6A/AS/H ファミリーのデバイスに関するエラッタ情報は <http://www.cypress.com/?rID=56239> にある PSoC® CY8C20x36A/46A/66A/96A/46AS/66AS/36H/46H ファミリーのシリコン エラッタを参照してください。デバイスの完全な機能説

明については、エラッタ資料をデータシートと合わせて参照してください。

### 開発キット

PSoC Development Kits は、サイプレスのオンラインストアで入手できます。また、各地域や世界規模で Arrow、Avnet、Digi-Key、Farnell、Future Electronics、Newark などの販売代理店網からもお求めいただけます。

### トレーニング

Free PSoC technical training (オンデマンド、ウェビナー、ワークショップ) は、オンラインで [www.cypress.com](http://www.cypress.com) で受講できます。このトレーニングでは、各種のトピックやスキル レベルをカバーしており、お客様の設計を支援します。

### CYPros コンサルタント

認定された PSoC コンサルタントが、技術支援から完成した PSoC 設計までのあらゆるニーズに対応します。PSoC コンサルタントにお問い合わせになるには、またはコンサルタントになるには、[CYPros Consultants](#) ウェブサイトをご覧ください。

### ソリューションズ ライブラリ

ソリューションを重視した設計のライブラリをご覧ください。ライブラリには、設計を素早く完成するうえで役立つ、ファームウェアおよびハードウェア設計ファイルを含むさまざまなアプリケーション デザインが用意されています。

### テクニカル サポート

テクニカル サポート – 検索可能な知識ベースの記事と技術フォーラムもオンラインでご利用になれます。解決策が見つからない場合は、テクニカル サポート (1-800-541-4736) までご連絡ください。

## 開発ツール

画期的な統合設計環境(IDE)である PSoC Designer™ を使うとユーザーが必要とするアプリケーション要件を満たすよう PSoC をカスタマイズすることが可能になります。PSoC Designer ソフトウェアは、システム設計や市場投入までの時間を短縮するお手伝いをいたします。ユーザー モジュールと呼ばれるあらかじめ用意されたアナログ ペリフェラルやデジタル ペリフェラルのライブラリを、ドラッグ & ドロップによる設計環境内で利用して独自のアプリケーションを開発できます。そして、動的に生成されるアプリケーション プログラミング インターフェース(API)のコード ライブラリを活用しながら、デザインをカスタマイズします。最後に、インサーキット エミュレーションや標準ソフトウェア デバッグ機能などを備えた統合デバッグ環境で、デザインのデバッグおよびテストを行います。PSoC Designer には以下が含まれます。

- デバイス、ユーザー モジュール コンフィギュレーションおよびダイナミック リコンフィギュレーション用のアプリケーション エディターグラフィカル ユーザー インターフェース(GUI)

- 広範なユーザー モジュール カタログ

- 統合ソース コード エディター(C およびアセンブリ言語)

- サイズ制限や使用期限のない無償の C コンパイラ

- 内蔵デバッガ

- インサーキット エミュレータ

- 通信インターフェースの組み込みサポート機能は以下のとおりです。

- ハードウェアおよびソフトウェア I<sup>2</sup>C スレーブとマスター

- フルスピード USB 2.0

- 最大 4 個の全二重汎用非同期レシーバ／トランスマッタ (UART)、SPI マスターと SPI スレーブ、およびワイヤレス

PSoC Designer は、PSoC 1 デバイスの全ライブラリをサポートしており、Windows XP、Windows Vista、Windows 7 上で動作します。

## PSoC Designer ソフトウェア サブシステム

### 設計エントリ

まず、チップレベル ビューで対象の基本デバイスを選択します。次に、PSoC ブロックを使用するアナログとデジタルの各種オンボード コンポーネント(ユーザー モジュールと呼ばれる)を選択します。ユーザー モジュールの例として、アナログ - デジタル変換器(ADC)、デジタル - アナログ変換器(DAC)、アンプ、フィルタなどがあります。選択したアプリケーション向けにユーザー モジュールをコンフィギュレーションし、他のユーザー モジュールや適切なピンに接続します。その後、プロジェクトを生成します。それにより、アプリケーションのプログラミングに使用できるAPIとライブラリがプロジェクトに事前設定されます。

またこのツールを使用すると、複数のコンフィギュレーションと動的再設定を容易に開発できます。動的リコンフィギュレーションにより、実行中にコンフィギュレーションを変更できます。基本的に、この機能によって、1 つのアプリケーションで 100% 以上の PSoC リソースを使用できます。

### コード生成ツール

コード生成ツールは、PSoC Designer のインターフェース内で途切れることなく動作し、さまざまなデバッグツールでテスト済みです。C 言語、アセンブリ言語、または両方の組み合わせで設計を開発できます。

**アセンブリ**：アセンブリでは、アセンブリ コードを C コードとシームレスに組み合わせられます。リンク ライブラリでは、自動的に絶対アドレス指定を使用できるほか、相対モードでコンパイルしたうえで他のソフトウェア モジュールとリンクし、絶対アドレス指定も取得できます。

**C 言語コンパイラ**：PSoC ファミリのデバイスをサポートする C 言語コンパイラを利用できます。これらの製品を使用することで、PSoC ファミリ デバイス向けに完全な C プログラムを作成できます。これらの最適化 C コンパイラは、PSoC のアーキテクチャに合わせて設定した C 言語のすべての機能を提供します。コンパイラには、ポートとバスの動作、標準のキーパッドとディスプレイのサポート、および拡張演算機能を提供する組み込みライブラリが付属しています。

### デバッガ

PSoC Designer はハードウェアによるインサーキット エミュレーション機能を提供するデバッグ環境を備えており、PSoC デバイスの内部状態を観察しながら実システムでプログラムに対してテストを行えます。デバッガ コマンドを使用して、データ メモリの読み出しとプログラム、データ メモリの読み書き、I/O レジスタの読み書きが可能です。また、CPU レジスタの読み書き、ブレークポイントの設定と消去、プログラムの実行、停止、およびステップ制御が可能です。また、調査対象のレジスタとメモリ位置のトレース バッファをデバッガでも作成できます。

### オンライン ヘルプ システム

オンライン ヘルプ システムでは、オンラインで状況に応じたヘルプが表示されます。それぞれの機能のサブシステムには固有状況に応じたヘルプがあり、操作手順のヘルプやクイックリファレンスとして使用できます。また、このヘルプ システムは設計者を支援するためのチュートリアル、FAQ とオンライン サポート フォーラムへのリンクを提供しています。

### インサーキット エミュレータ

コストの低く、機能性の高いインサーキット エミュレータ(ICE)が開発作業をサポートするために用意されています。このハードウェアは単独のデバイスをプログラムできます。

エミュレータは、USB ポートを介して PC に接続する 1 つの基本ユニットで構成されています。この基本ユニットは汎用型で、すべての PSoC デバイスで動作します。各デバイス ファミリのエミュレーション ポッドは、それぞれ別々に用意されています。エミュレーション ポッドは、作業対象の基板上の PSoC デバイスと置き換わり、全速(24MHz)で動作します。

## PSoC Designer を使用したデザイン

PSoC デバイスの開発プロセスは、従来の固定機能マイクロプロセッサの開発プロセスとは異なります。コンフィギュレーション可能なアナログとデジタル ハードウェア ブロックは PSoC アーキテクチャに独特の柔軟性をもたらし、開発時の仕様変更の管理や在庫費用の削減に役立ちます。これらのコンフィギュレーション可能なリソースは PSoC ブロックと呼ばれ、ユーザーが選択可能なさまざまな機能を実装できます。PSoC 開発プロセスは次のとおりです。

6. ユーザー モジュールの選択

7. ユーザー モジュールの設定

8. 構成および接続

9. 生成、検証、およびデバッグ

### ユーザー モジュールの選択

PSoC Designer は、あらかじめ構築され、テスト済みのハードウェア周辺コンポーネント（ユーザー モジュールと呼ばれる）のライブラリを備えています。これらのユーザー モジュールにより、アナログとデジタル両方の周辺デバイスの選択と実装が簡単になります。

### ユーザー モジュールの設定

選択した各ユーザー モジュールにより、選択した機能を実装する基本的なレジスタ設定を確立できます。また、コンポーネントの的確なコンフィギュレーションを特定のアプリケーションに合わせるようにするパラメーターとプロパティも提供されます。例えば PWM ユーザー モジュールでは、1 個以上のデジタル PSoC ブロックをそれぞれが 8 ビット分解能を持つようコンフィギュレーションします。これらのパラメーターを使って、パルス幅とデューティ比を設定できます。選択したアプリケーションに対応するようパラメーターとプロパティをコンフィギュレーションします。値は直接入力またはドロップダウンメニューからの選択で入力してください。すべてのユーザー モジュールはデータシートに文書化され、PSoC Designer またはサイプレスのウェブサイトで直接確認できます。これらの [ユーザー モジュール データシート](#) には、ユーザー モジュールの内部動作に関する説明と性能仕様が記載されています。また、各データシートにはユーザー モジュールの各パラメーターの使用方法や、デザインを適切に実装するために必要なその他の情報もまとめられています。

### 構成および接続

ユーザー モジュールを他のモジュールおよび I/O ピンに相互接続することによって、チップレベルで信号チェーンを構築できます。すべてのオンチップ リソースを完全に制御できるように、選択、コンフィギュレーション、およびルーティングを行います。

### 生成、検証、およびデバッグ

ハードウェアのコンフィギュレーションのテスト、またはプロジェクトのコード開発の準備ができたら、「コンフィギュレーション ファイルの生成」手順を実行します。このステップで PSoC Designer によって生成されるソース コードは、仕様に合わせてデバイスを自動的にコンフィギュレーションし、システム用のソフトウェアを提供します。生成されたコードは、実行時に発生するハードウェア イベントの制御とそれに対する応答を実現する高レベル API、および必要に応じて修正して使用できる割り込みサービス ルーチンを提供します。

高い完成度のコード開発環境により、C、アセンブリ言語、またはその両方を使用したアプリケーションの開発とカスタマイズが可能です。

開発プロセスの最後のステップは、PSoC Designer のデバッガ内で進めます（接続のアイコンをクリックしてアクセスします）。PSoC Designer によって HEX イメージが ICE にダウンロードされ、フルスピードで実行されます。PSoC Designer のデバッグ機能は、それよりもはるかに高価なシステムの機能に匹敵します。デバッグ インターフェースは、シングルステップ実行、ブレークポイントまでの実行、変数値の追跡などの従来の機能のほか、大容量のトレース バッファを備えています。よって、アドレスとデータ バス値の監視、メモリ位置の監視、外部信号の監視などの複雑なブレークポイント イベントを定義できます。

## ピン配列

CY8C20XX6A/S PSoC デバイスは様々なパッケージで提供しています。各パッケージについて次の表に示します。すべてのポートピン（「P」というラベルが付いたもの）はデジタル I/O の機能を備えており、共通のアナログ バスに接続できます。ただし、V<sub>SS</sub>、V<sub>DD</sub>、および XRES はデジタル I/O の機能を備えていません。

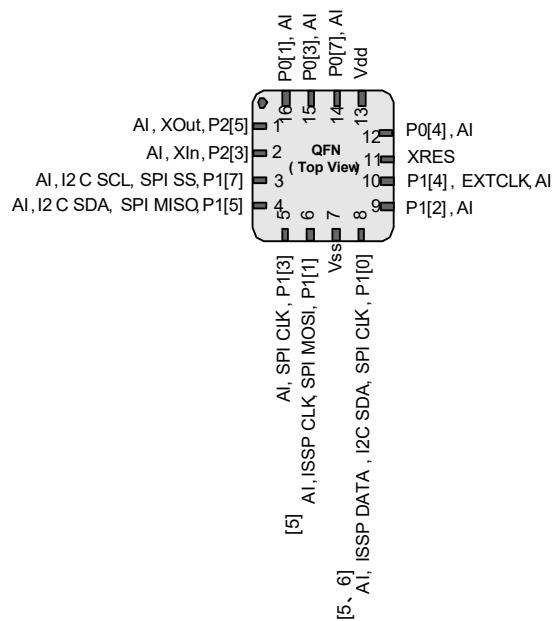

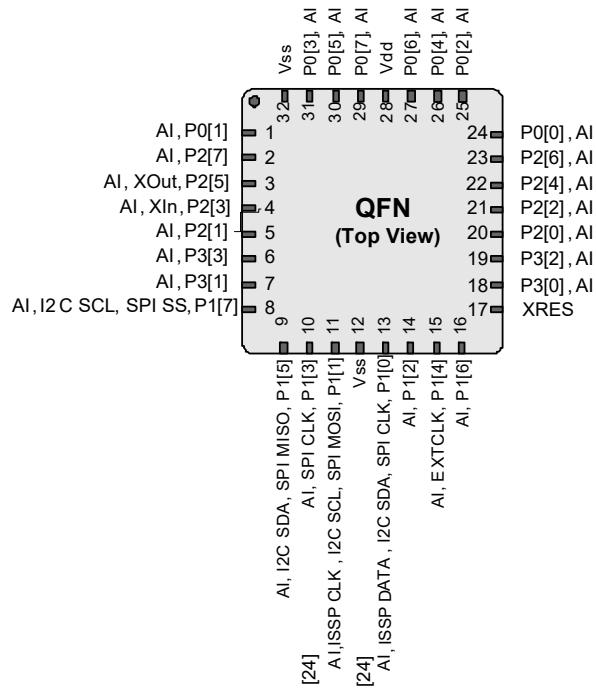

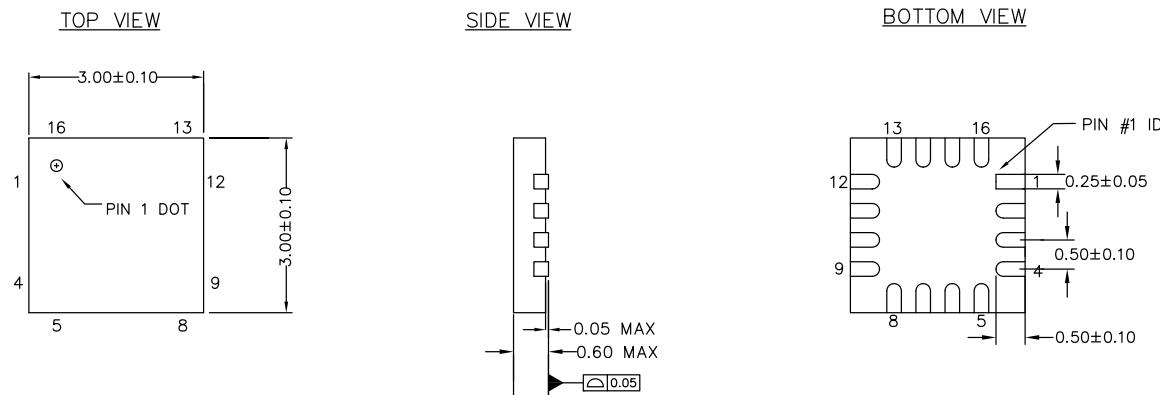

### 16 ピン QFN (10 本のセンシング入力)<sup>[3, 4]</sup>

表 1. ピンの定義 – CY8C20236A、CY8C20246A、CY8C20246AS PSoC デバイス

| ピン番号 | タイプ  |      | ピン名             | 説明                                                                    |

|------|------|------|-----------------|-----------------------------------------------------------------------|

|      | デジタル | アナログ |                 |                                                                       |

| 1    | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                                        |

| 2    | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                                         |

| 3    | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                           |

| 4    | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                         |

| 5    | IOHR | I    | P1[3]           | SPI CLK                                                               |

| 6    | IOHR | I    | P1[1]           | ISSP CLK <sup>[5]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                |

| 7    | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[7]</sup>                                                 |

| 8    | IOHR | I    | P1[0]           | ISSP DATA <sup>[5]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[6]</sup> |

| 9    | IOHR | I    | P1[2]           |                                                                       |

| 10   | IOHR | I    | P1[4]           | オプションの外部クロック (EXTCLK)                                                 |

| 11   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                          |

| 12   | IOH  | I    | P0[4]           |                                                                       |

| 13   | 電源   |      | V <sub>DD</sub> | 電源電圧                                                                  |

| 14   | IOH  | I    | P0[7]           |                                                                       |

| 15   | IOH  | I    | P0[3]           | 積分入力                                                                  |

| 16   | IOH  | I    | P0[1]           | 積分入力                                                                  |

凡例 : A= アナログ、I= 入力、O= 出力、OH=5mA HIGH 出力駆動、R= 安定化出力。

図 3. CY8C20236A、CY8C20246A、CY8C20246AS

#### 注 :

3. 13 本の GPIO= 容量センシング用の 10 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

4. センター パッドなし。

5. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサーした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

6. 代替 SPI クロック。

7. すべての VSS ピンは 1 つの共通 GND 面に引き寄せる必要があります。

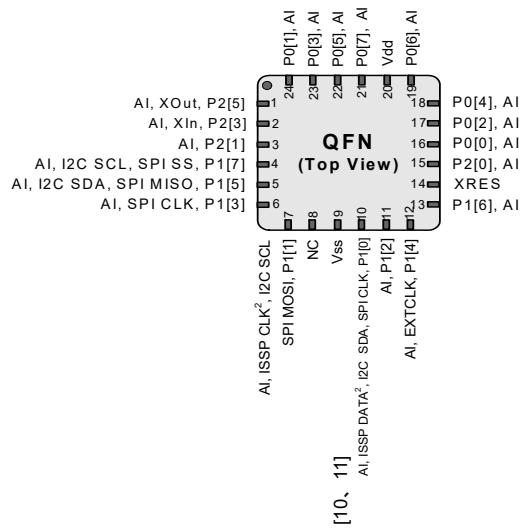

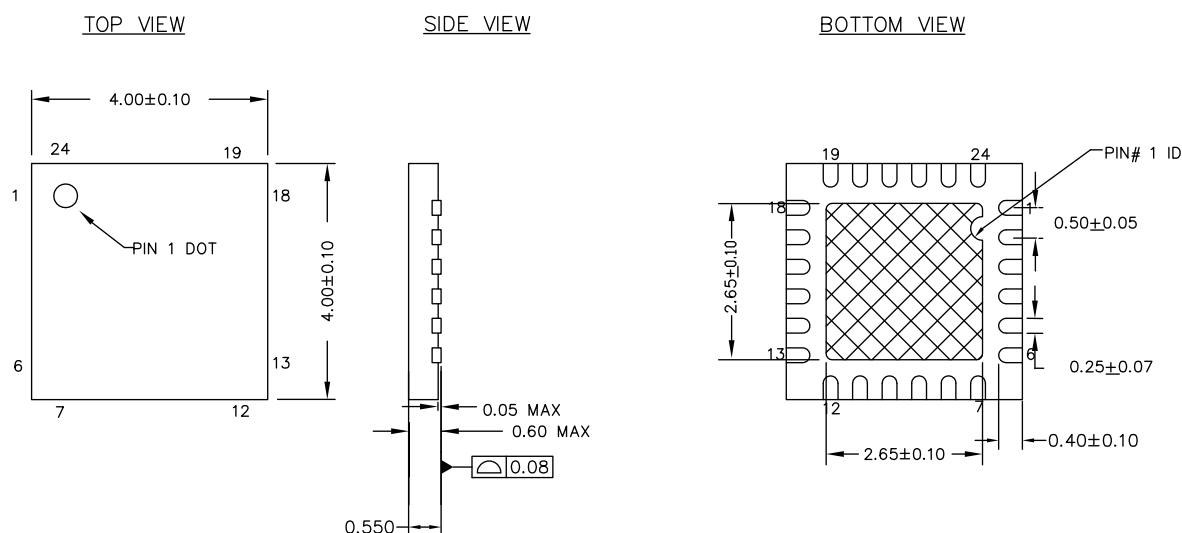

## 24 ピン QFN (17 本のセンシング入力)<sup>[8]</sup>

表 2. ピンの定義 – CY8C20336A、CY8C20346A、CY8C20346AS<sup>[9]</sup>

| ピン番号 | タイプ  |      | ピン名             | 説明                                                                      |

|------|------|------|-----------------|-------------------------------------------------------------------------|

|      | デジタル | アナログ |                 |                                                                         |

| 1    | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                                          |

| 2    | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                                           |

| 3    | I/O  | I    | P2[1]           |                                                                         |

| 4    | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| 5    | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| 6    | IOHR | I    | P1[3]           | SPI CLK                                                                 |

| 7    | IOHR | I    | P1[1]           | ISSP CLK <sup>[10]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| 8    | NC   |      |                 | 接続なし                                                                    |

| 9    | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[12]</sup>                                                  |

| 10   | IOHR | I    | P1[0]           | ISSP DATA <sup>[10]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[11]</sup> |

| 11   | IOHR | I    | P1[2]           |                                                                         |

| 12   | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                                 |

| 13   | IOHR | I    | P1[6]           |                                                                         |

| 14   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| 15   | I/O  | I    | P2[0]           |                                                                         |

| 16   | IOH  | I    | P0[0]           |                                                                         |

| 17   | IOH  | I    | P0[2]           |                                                                         |

| 18   | IOH  | I    | P0[4]           |                                                                         |

| 19   | IOH  | I    | P0[6]           |                                                                         |

| 20   | 電源   |      | V <sub>DD</sub> | 電源電圧                                                                    |

| 21   | IOH  | I    | P0[7]           |                                                                         |

| 22   | IOH  | I    | P0[5]           |                                                                         |

| 23   | IOH  | I    | P0[3]           | 積分入力                                                                    |

| 24   | IOH  | I    | P0[1]           | 積分入力                                                                    |

| CP   | 電源   |      | V <sub>SS</sub> | センター パッドをグランドに接続してください                                                  |

凡例 : A= アナログ、I= 入力、O= 出力、OH=5mA HIGH 出力駆動、R= 安定化出力。

図 4. CY8C20336A、CY8C20346A、CY8C20346AS

- 注 :

8. 20 本の GPIO= 容量センシング用の 17 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

9. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グランドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

10. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサークトした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

11. 代替 SPI クロック。

12. すべての V<sub>SS</sub> ピンは 1 つの共通 GND 面に引き寄せる必要があります。

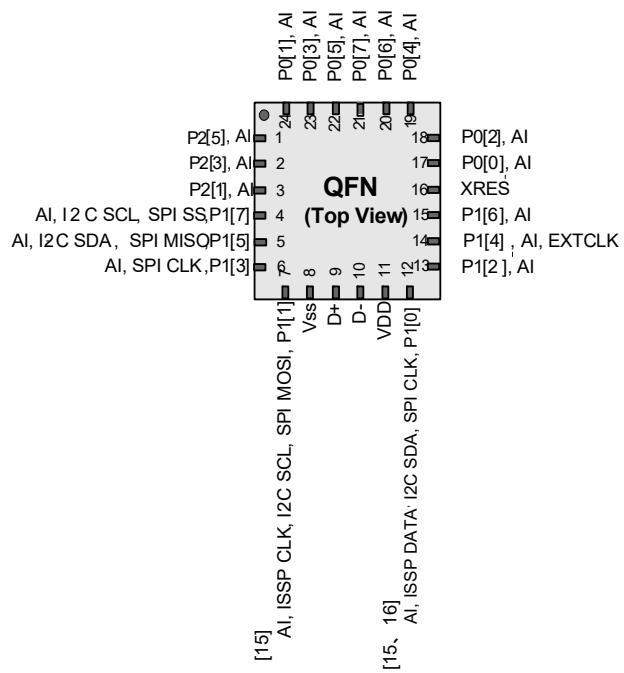

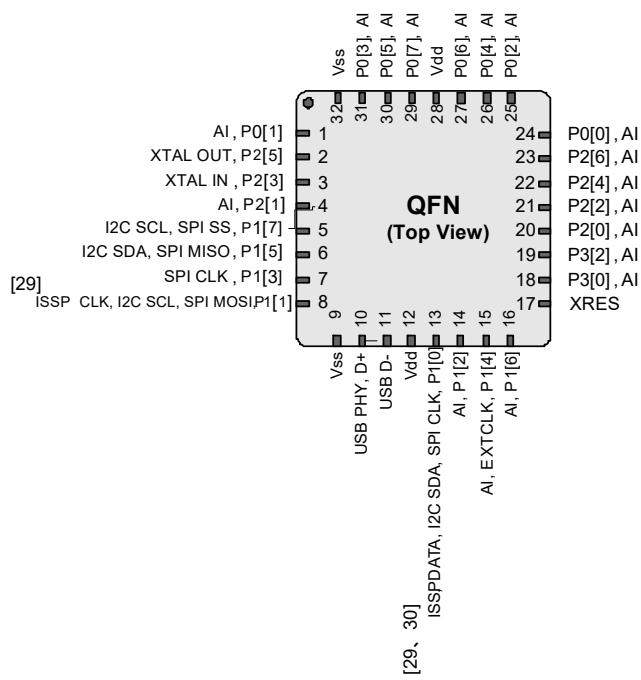

## 24 ピン QFN (15 本のセンシング入力 (USB 付き ))<sup>[13]</sup>

表 3. ピンの定義 – CY8C20396A<sup>[14]</sup>

| ピン番号 | タイプ    |      | ピン名             | 説明                                                                      |

|------|--------|------|-----------------|-------------------------------------------------------------------------|

|      | デジタル   | アナログ |                 |                                                                         |

| 1    | I/O    | I    | P2[5]           |                                                                         |

| 2    | I/O    | I    | P2[3]           |                                                                         |

| 3    | I/O    | I    | P2[1]           |                                                                         |

| 4    | IOHR   | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| 5    | IOHR   | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| 6    | IOHR   | I    | P1[3]           | SPI CLK                                                                 |

| 7    | IOHR   | I    | P1[1]           | ISSP CLK <sup>[15]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| 8    | 電源     |      | V <sub>SS</sub> | グランド <sup>[17]</sup>                                                    |

| 9    | I/O    | I    | D+              | USB D+                                                                  |

| 10   | I/O    | I    | D-              | USB D-                                                                  |

| 11   | 電源     |      | V <sub>DD</sub> | 電源                                                                      |

| 12   | IOHR   | I    | P1[0]           | ISSP DATA <sup>[15]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[16]</sup> |

| 13   | IOHR   | I    | P1[2]           |                                                                         |

| 14   | IOHR   | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                                 |

| 15   | IOHR   | I    | P1[6]           |                                                                         |

| 16   | リセット入力 |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| 17   | IOH    | I    | P0[0]           |                                                                         |

| 18   | IOH    | I    | P0[2]           |                                                                         |

| 19   | IOH    | I    | P0[4]           |                                                                         |

| 20   | IOH    | I    | P0[6]           |                                                                         |

| 21   | IOH    | I    | P0[7]           |                                                                         |

| 22   | IOH    | I    | P0[5]           |                                                                         |

| 23   | IOH    | I    | P0[3]           | 積分入力                                                                    |

| 24   | IOH    | I    | P0[1]           | 積分入力                                                                    |

| CP   | 電源     |      | V <sub>SS</sub> | センター パッドをグランドに接続してください                                                  |

凡例 : I= 入力、O= 出力、OH=5mA HIGH 出力駆動、R= 安定化出力。

図 5. CY8C20396A

- 注 :

13. 20 本の GPIO= 容量センシング用の 15 本のピン +I2C 用の 2 本のピン +USB 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

14. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グランドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

15. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサークトした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I2C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

16. 代替 SPI クロック。

17. すべての VSS ピンは 1 つの共通 GND 面に引き寄せる必要があります。

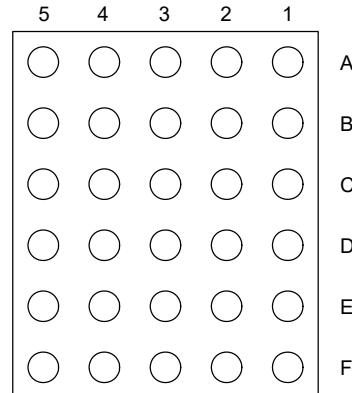

### 30 ポール WLCSP (24 本のセンシング入力)<sup>[18]</sup>

表 4. ピンの定義 – CY8C20766A、CY8C20746A 30 ポール WLCSP

| ピン番号 | タイプ  |      | ピン名             | 説明                                                                      |

|------|------|------|-----------------|-------------------------------------------------------------------------|

|      | デジタル | アナログ |                 |                                                                         |

| A1   | IOH  | I    | P0[2]           |                                                                         |

| A2   | IOH  | I    | P0[6]           |                                                                         |

| A3   | 電源   |      | V <sub>DD</sub> | 電源電圧                                                                    |

| A4   | IOH  | I    | P0[1]           | 積分入力                                                                    |

| A5   | I/O  | I    | P2[7]           |                                                                         |

| B1   | I/O  | I    | P2[6]           |                                                                         |

| B2   | IOH  | I    | P0[0]           |                                                                         |

| B3   | IOH  | I    | P0[4]           |                                                                         |

| B4   | IOH  | I    | P0[3]           | 積分入力                                                                    |

| B5   | I/O  | I    | P2[5]           | 水晶振動子出力 (Xout)                                                          |

| C1   | I/O  | I    | P2[2]           |                                                                         |

| C2   | I/O  | I    | P2[4]           |                                                                         |

| C3   | IOH  | I    | P0[7]           |                                                                         |

| C4   | IOH  | I    | P0[5]           |                                                                         |

| C5   | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                                           |

| D1   | I/O  | I    | P2[0]           |                                                                         |

| D2   | I/O  | I    | P3[0]           |                                                                         |

| D3   | I/O  | I    | P3[1]           |                                                                         |

| D4   | I/O  | I    | P3[3]           |                                                                         |

| D5   | I/O  | I    | P2[1]           |                                                                         |

| E1   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| E2   | IOHR | I    | P1[6]           |                                                                         |

| E3   | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                                 |

| E4   | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| E5   | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| F1   | IOHR | I    | P1[2]           |                                                                         |

| F2   | IOHR | I    | P1[0]           | ISSP DATA <sup>[19]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[20]</sup> |

| F3   | 電源   |      | V <sub>SS</sub> | 電源グランド <sup>[21]</sup>                                                  |

| F4   | IOHR | I    | P1[1]           | ISSP CLK <sup>[19]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| F5   | IOHR | I    | P1[3]           | SPI CLK                                                                 |

注:

18. 27 本の GPIO= 容量センシング用の 24 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

19. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサートした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

20. 代替 SPI クロック。

21. すべての VSS ピンは 1 つの共通 GND 面に引き寄せる必要があります。

図 6. CY8C20766A 30 ポール WLCSP

底面図

上面図

### 32 ピン QFN (25 本のセンシング入力)<sup>[22]</sup>

表 5. ピンの定義 – CY8C20436A、CY8C20446A、CY8C20446AS、CY8C20466A、CY8C20466AS<sup>[23]</sup>

| ピン番号 | タイプ  |      | ピン名             | 説明                                                                          |

|------|------|------|-----------------|-----------------------------------------------------------------------------|

|      | デジタル | アナログ |                 |                                                                             |

| 1    | IOH  | I    | P0[1]           | 積分入力                                                                        |

| 2    | I/O  | I    | P2[7]           |                                                                             |

| 3    | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                                              |

| 4    | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                                               |

| 5    | I/O  | I    | P2[1]           |                                                                             |

| 6    | I/O  | I    | P3[3]           |                                                                             |

| 7    | I/O  | I    | P3[1]           |                                                                             |

| 8    | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                                 |

| 9    | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                               |

| 10   | IOHR | I    | P1[3]           | SPI CLK                                                                     |

| 11   | IOHR | I    | P1[1]           | ISSP CLK <sup>[24]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                     |

| 12   | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[26]</sup>                                                      |

| 13   | IOHR | I    | P1[0]           | ISSP DATA <sup>[24]</sup> 、I <sup>2</sup> C SDA、<br>SPI CLK <sup>[25]</sup> |

| 14   | IOHR | I    | P1[2]           |                                                                             |

| 15   | IOHR | I    | P1[4]           | オプションの外部クロック入力<br>(EXTCLK)                                                  |

| 16   | IOHR | I    | P1[6]           |                                                                             |

| 17   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                                |

| 18   | I/O  | I    | P3[0]           |                                                                             |

| 19   | I/O  | I    | P3[2]           |                                                                             |

| 20   | I/O  | I    | P2[0]           |                                                                             |

| 21   | I/O  | I    | P2[2]           |                                                                             |

| 22   | I/O  | I    | P2[4]           |                                                                             |

| 23   | I/O  | I    | P2[6]           |                                                                             |

| 24   | IOH  | I    | P0[0]           |                                                                             |

| 25   | IOH  | I    | P0[2]           |                                                                             |

| 26   | IOH  | I    | P0[4]           |                                                                             |

| 27   | IOH  | I    | P0[6]           |                                                                             |

| 28   | 電源   |      | V <sub>DD</sub> | 電源電圧                                                                        |

| 29   | IOH  | I    | P0[7]           |                                                                             |

| 30   | IOH  | I    | P0[5]           |                                                                             |

| 31   | IOH  | I    | P0[3]           | 積分入力                                                                        |

| 32   | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[26]</sup>                                                      |

| CP   | 電源   |      | V <sub>SS</sub> | センター パッドをグランドに接続する必要があります。                                                  |

凡例: A= アナログ、I= 入力、O= 出力、OH=5mA HIGH 出力駆動、R= 安定化出力。

#### 注:

22. 28 本の GPIO= 容量センシング用の 25 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

23. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グランドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

24. 電源投入時、SDA(P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL(P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアセットした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

25. 代替 SPI クロック。

26. すべての V<sub>SS</sub> ピンは 1 つの共通 GND 面に引き寄せる必要があります。

図 7. CY8C20436A、CY8C20446A、CY8C20446AS、

CY8C20466A、CY8C20466AS

### 32 ピン QFN (22 本のセンシング入力 (USB 付き ))<sup>[27]</sup>

表 6. ピンの定義 – CY8C20496A<sup>[28]</sup>

| ピン番号 | タイプ  |      | ピン名             | 説明                                                                      |

|------|------|------|-----------------|-------------------------------------------------------------------------|

|      | デジタル | アナログ |                 |                                                                         |

| 1    | IOH  | I    | P0[1]           | 積分入力                                                                    |

| 2    | I/O  | I    | P2[5]           | XTAL 出力                                                                 |

| 3    | I/O  | I    | P2[3]           | XTAL 入力                                                                 |

| 4    | I/O  | I    | P2[1]           |                                                                         |

| 5    | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| 6    | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| 7    | IOHR | I    | P1[3]           | SPI CLK                                                                 |

| 8    | IOHR | I    | P1[1]           | ISSP CLK <sup>[29]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| 9    | 電源   |      | V <sub>SS</sub> | グランド ピン <sup>[31]</sup>                                                 |

| 10   | I    | I    | D+              | USB D+                                                                  |

| 11   |      |      | D-              | USB D-                                                                  |

| 12   | 電源   |      | V <sub>DD</sub> | 電源ピン                                                                    |

| 13   | IOHR | I    | P1[0]           | ISSP DATA <sup>[29]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[30]</sup> |

| 14   | IOHR | I    | P1[2]           |                                                                         |

| 15   | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                                 |

| 16   | IOHR | I    | P1[6]           |                                                                         |

| 17   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| 18   | I/O  | I    | P3[0]           |                                                                         |

| 19   | I/O  | I    | P3[2]           |                                                                         |

| 20   | I/O  | I    | P2[0]           |                                                                         |

| 21   | I/O  | I    | P2[2]           |                                                                         |

| 22   | I/O  | I    | P2[4]           |                                                                         |

| 23   | I/O  | I    | P2[6]           |                                                                         |

| 24   | IOH  | I    | P0[0]           |                                                                         |

| 25   | IOH  | I    | P0[2]           |                                                                         |

| 26   | IOH  | I    | P0[4]           |                                                                         |

| 27   | IOH  | I    | P0[6]           |                                                                         |

| 28   | 電源   |      | V <sub>DD</sub> | 電源ピン                                                                    |

| 29   | IOH  | I    | P0[7]           |                                                                         |

| 30   | IOH  | I    | P0[5]           |                                                                         |

| 31   | IOH  | I    | P0[3]           | 積分入力                                                                    |

| 32   | 電源   |      | V <sub>SS</sub> | グランド ピン <sup>[31]</sup>                                                 |

凡例: A= アナログ、I= 入力、O= 出力、OH=5mA HIGH 出力駆動、R= 安定化出力。

注:

- 27. 27 本の GPIO= 容量センシング用の 22 本のピン +I<sup>2</sup>C 用の 2 本のピン +USB 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

- 28. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グランドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

- 29. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアセットした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

- 30. 代替 SPI クロック。

- 31. すべての VSS ピンは 1 つの共通 GND 面に引き寄せる必要があります。

図 8. CY8C20496A

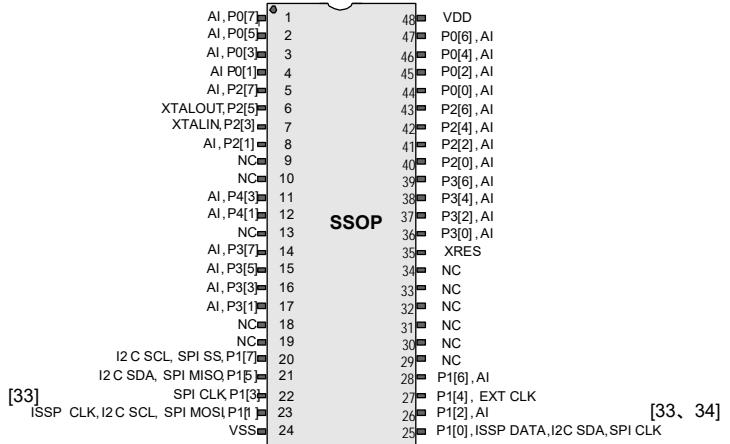

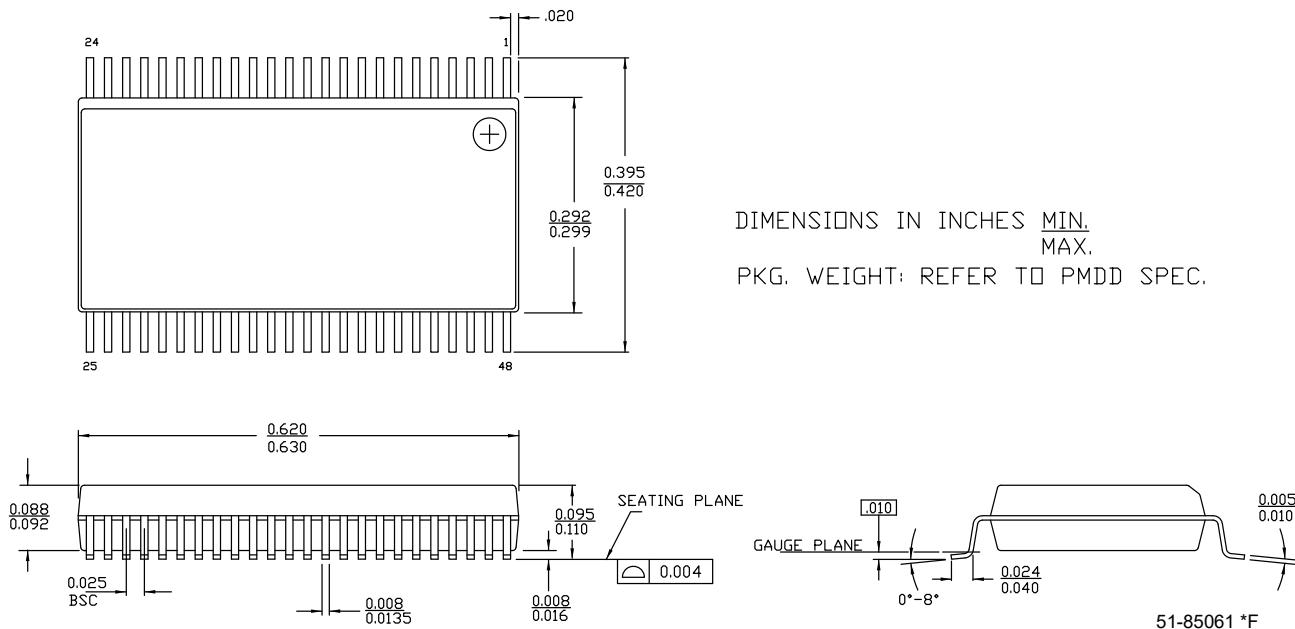

48 ピン SSOP (31 本のセンシング入力) <sup>[32]</sup>

表 7. ピンの定義 – CY8C20536A、CY8C20546A、および CY8C20566A<sup>[33]</sup>

| ピン番号 | デジタル | アナログ | ピン名             | 説明                                                                      |

|------|------|------|-----------------|-------------------------------------------------------------------------|

| 1    | IOH  | I    | P0[7]           |                                                                         |

| 2    | IOH  | I    | P0[5]           |                                                                         |

| 3    | IOH  | I    | P0[3]           | 積分入力                                                                    |

| 4    | IOH  | I    | P0[1]           | 積分入力                                                                    |

| 5    | I/O  | I    | P2[7]           |                                                                         |

| 6    | I/O  | I    | P2[5]           | XTAL 出力                                                                 |

| 7    | I/O  | I    | P2[3]           | XTAL 入力                                                                 |

| 8    | I/O  | I    | P2[1]           |                                                                         |

| 9    |      |      | NC              | 接続なし                                                                    |

| 10   |      |      | NC              | 接続なし                                                                    |

| 11   | I/O  | I    | P4[3]           |                                                                         |

| 12   | I/O  | I    | P4[1]           |                                                                         |

| 13   |      |      | NC              | 接続なし                                                                    |

| 14   | I/O  | I    | P3[7]           |                                                                         |

| 15   | I/O  | I    | P3[5]           |                                                                         |

| 16   | I/O  | I    | P3[3]           |                                                                         |

| 17   | I/O  | I    | P3[1]           |                                                                         |

| 18   |      |      | NC              | 接続なし                                                                    |

| 19   |      |      | NC              | 接続なし                                                                    |

| 20   | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| 21   | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| 22   | IOHR | I    | P1[3]           | SPI CLK                                                                 |

| 23   | IOHR | I    | P1[1]           | ISSP CLK <sup>[33]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| 24   |      |      | V <sub>SS</sub> | グランド ピン <sup>[35]</sup>                                                 |

| 25   | IOHR | I    | P1[0]           | ISSP DATA <sup>[33]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[34]</sup> |

| 26   | IOHR | I    | P1[2]           |                                                                         |

| 27   | IOHR | I    | P1[4]           | オプションの外部クロック入力(EXT CLK)                                                 |

| 28   | IOHR | I    | P1[6]           |                                                                         |

| 29   |      |      | NC              | 接続なし                                                                    |

| 30   |      |      | NC              | 接続なし                                                                    |

| 31   |      |      | NC              | 接続なし                                                                    |

| 32   |      |      | NC              | 接続なし                                                                    |

| 33   |      |      | NC              | 接続なし                                                                    |

| 34   |      |      | NC              | 接続なし                                                                    |

| 35   |      |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| 36   | I/O  | I    | P3[0]           |                                                                         |

| 37   | I/O  | I    | P3[2]           |                                                                         |

| 38   | I/O  | I    | P3[4]           |                                                                         |

| 39   | I/O  | I    | P3[6]           |                                                                         |

| 40   | I/O  | I    | P2[0]           |                                                                         |

**凡例:** A= アナログ、I= 入力、O= 出力、NC= 接続なし、H=5mA HIGH 出力駆動、R= 安定化出力オプション。

図 9. CY8C20536A、CY8C20546A、および CY8C20566A

注

32. 34 本のGPIO: 容量センシング用の 31 本のピン + I2C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

33. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサーした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I2C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

34. 代替 SPI クロック。

35. すべての VSS ピンは 1 つの共通 GND 面に引き寄せ必要があります。

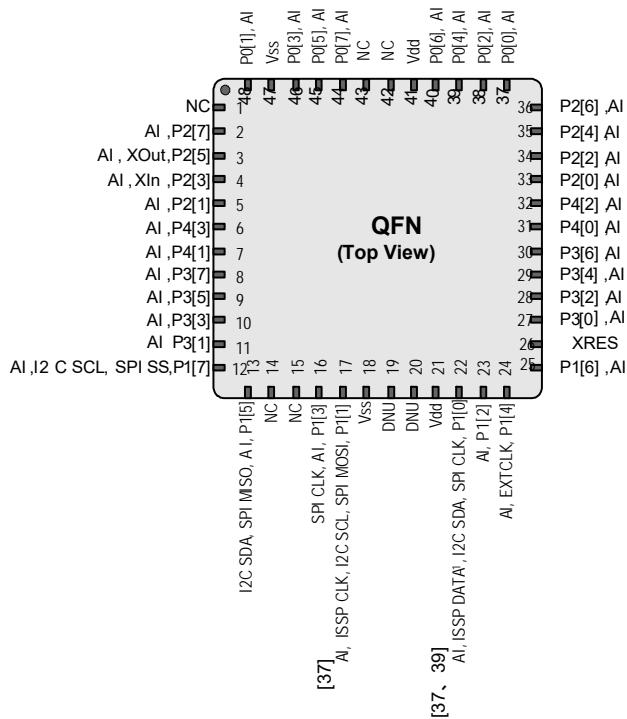

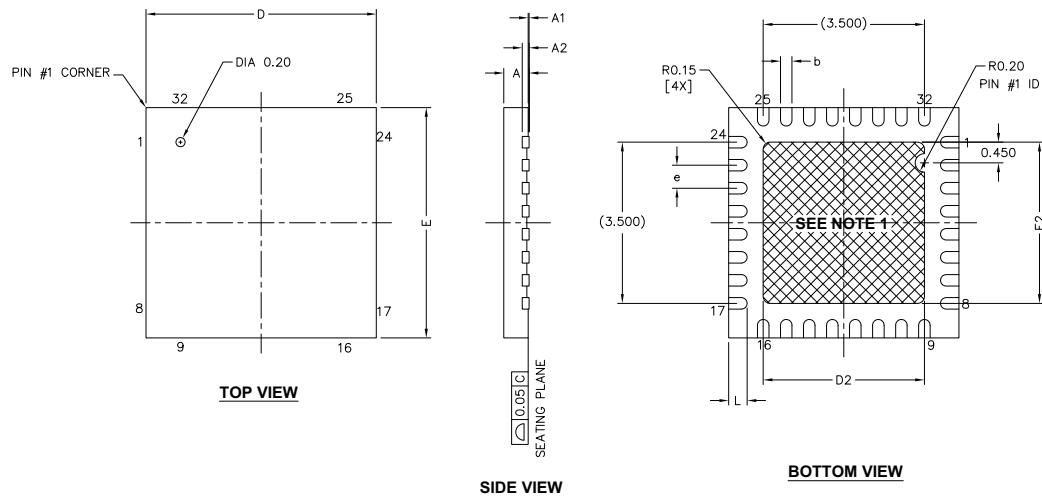

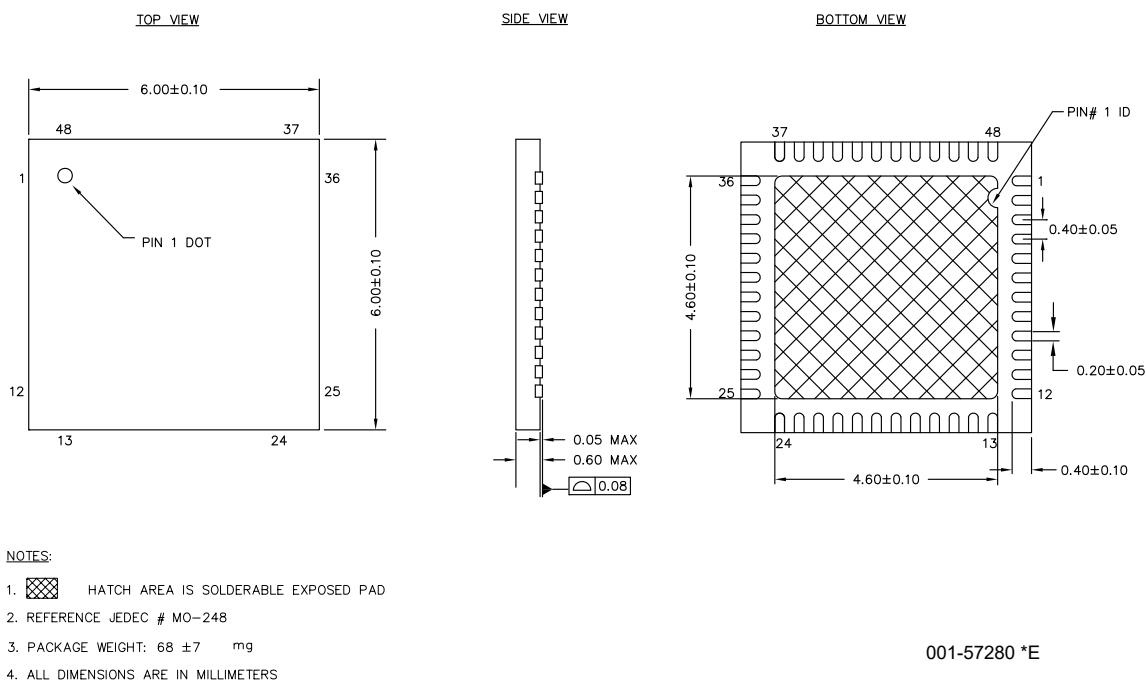

## 48 ピン QFN (33 本のセンシング入力)<sup>[36]</sup>

表 8. ピンの定義 – CY8C20636A<sup>[37, 38]</sup>

| ピン番号 | デジタル | アナログ | ピン名             | 説明                                             |

|------|------|------|-----------------|------------------------------------------------|

| 1    |      |      | NC              | 接続なし                                           |

| 2    | I/O  | I    | P2[7]           |                                                |

| 3    | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                 |

| 4    | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                  |

| 5    | I/O  | I    | P2[1]           |                                                |

| 6    | I/O  | I    | P4[3]           |                                                |

| 7    | I/O  | I    | P4[1]           |                                                |

| 8    | I/O  | I    | P3[7]           |                                                |

| 9    | I/O  | I    | P3[5]           |                                                |

| 10   | I/O  | I    | P3[3]           |                                                |

| 11   | I/O  | I    | P3[1]           |                                                |

| 12   | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                    |

| 13   | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MOSI                  |

| 14   |      |      | NC              | 接続なし                                           |

| 15   |      |      | NC              | 接続なし                                           |

| 16   | IOHR | I    | P1[3]           | SPI CLK                                        |

| 17   | IOHR | I    | P1[1]           | ISSP CLK[37]、I <sup>2</sup> C SCL、SPI MOSI     |

| 18   | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[40]</sup>                         |

| 19   |      |      | DNU             |                                                |

| 20   |      |      | DNU             |                                                |

| 21   | 電源   |      | V <sub>DD</sub> | 電源電圧                                           |

| 22   | IOHR | I    | P1[0]           | ISSP DATA[37]、I <sup>2</sup> C SDA、SPI CLK[39] |

| 23   | IOHR | I    | P1[2]           |                                                |

| 24   | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                        |

| 25   | IOHR | I    | P1[6]           |                                                |

| 26   | 入力   |      | XRES            | 内部プルダウン抵抗付きアクティブ HIGH 外部リセット                   |

| 27   | I/O  | I    | P3[0]           |                                                |

| 28   | I/O  | I    | P3[2]           |                                                |

| 29   | I/O  | I    | P3[4]           |                                                |

| 30   | I/O  | I    | P3[6]           |                                                |

| 31   | I/O  | I    | P4[0]           |                                                |

| 32   | I/O  | I    | P4[2]           |                                                |

| 33   | I/O  | I    | P2[0]           |                                                |

| 34   | I/O  | I    | P2[2]           |                                                |

| 35   | I/O  | I    | P2[4]           |                                                |

| 36   | I/O  | I    | P2[6]           |                                                |

| 37   | IOH  | I    | P0[0]           |                                                |

| 38   | IOH  | I    | P0[2]           |                                                |

| 39   | IOH  | I    | P0[4]           |                                                |

凡例： A= アナログ、 I= 入力、 O= 出力、 NC= 接続なし、 H=5mA HIGH 出力駆動、 R= 安定化出力。

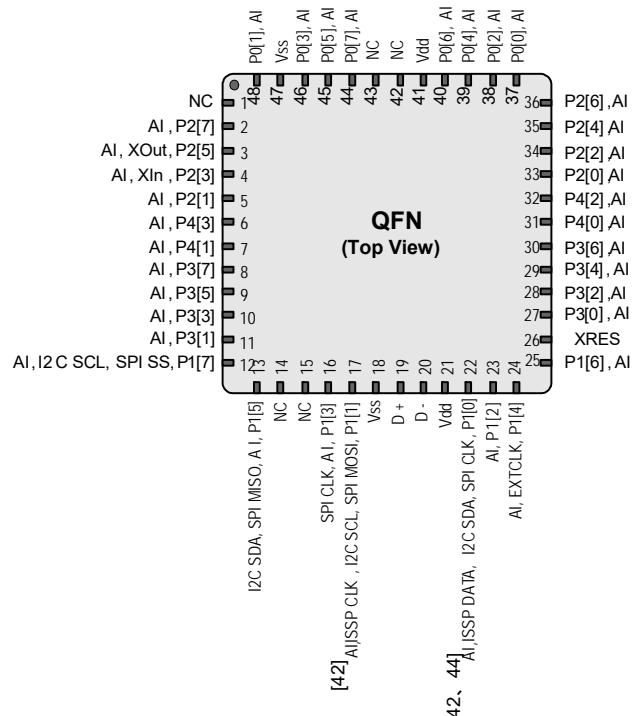

注：

- 36. 36 本の GPIO= 容量センシング用の 33 本のピン + I<sup>2</sup>C 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

- 37. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサートした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

- 38. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンターパッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グラウンドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

- 39. 代替 SPI クロック。

- 40. すべての V<sub>SS</sub> ピンは 1 つの共通 GND 面に引き寄せる必要があります。

図 10. CY8C20636A

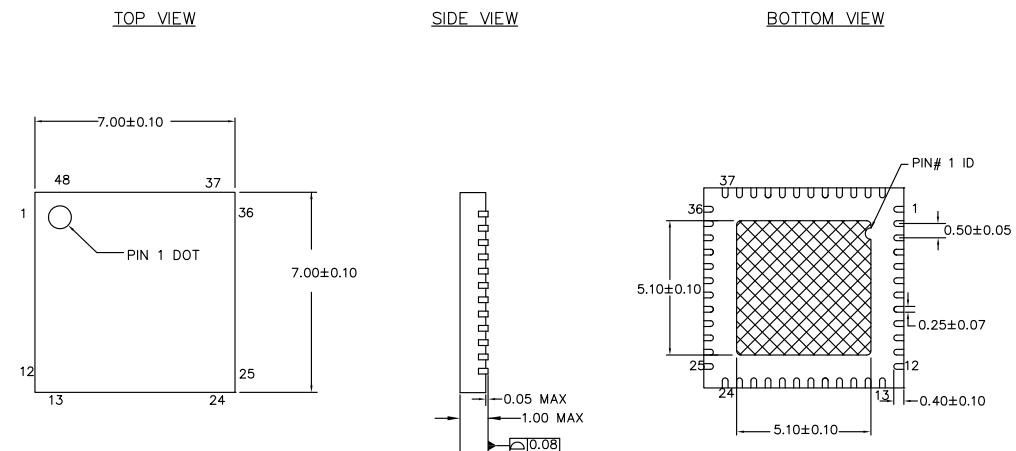

### 48 ピン QFN (33 本のセンシング入力 (USB 付き))<sup>[41]</sup>

表 9. ピンの定義 – CY8C20646A、CY8C20646AS、CY8C20666A、CY8C20666AS<sup>[42, 43]</sup>

| ピン番号 | デジタル | アナログ | ピン名             | 説明                                             |

|------|------|------|-----------------|------------------------------------------------|

| 1    |      |      | NC              | 接続なし                                           |

| 2    | I/O  | I    | P2[7]           |                                                |

| 3    | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                 |

| 4    | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                  |

| 5    | I/O  | I    | P2[1]           |                                                |

| 6    | I/O  | I    | P4[3]           |                                                |

| 7    | I/O  | I    | P4[1]           |                                                |

| 8    | I/O  | I    | P3[7]           |                                                |

| 9    | I/O  | I    | P3[5]           |                                                |

| 10   | I/O  | I    | P3[3]           |                                                |

| 11   | I/O  | I    | P3[1]           |                                                |

| 12   | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                    |

| 13   | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                  |

| 14   |      |      | NC              | 接続なし                                           |

| 15   |      |      | NC              | 接続なし                                           |

| 16   | IOHR | I    | P1[3]           | SPI CLK                                        |

| 17   | IOHR | I    | P1[1]           | ISSP CLK[42]、I <sup>2</sup> C SCL、SPI MOSI     |

| 18   | 電源   |      | V <sub>SS</sub> | グランド接続 [45]                                    |

| 19   | I/O  |      | D+              | USB D+                                         |

| 20   | I/O  |      | D-              | USB D-                                         |

| 21   | 電源   |      | V <sub>DD</sub> | 電源電圧                                           |

| 22   | IOHR | I    | P1[0]           | ISSP DATA[42]、I <sup>2</sup> C SDA、SPI CLK[44] |

| 23   | IOHR | I    | P1[2]           |                                                |

| 24   | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                        |

| 25   | IOHR | I    | P1[6]           |                                                |

| 26   | 入力   | XRES |                 | 内部ブルダウン抵抗付きアクティブ HIGH 外部リセット                   |

| 27   | I/O  | I    | P3[0]           |                                                |

| 28   | I/O  | I    | P3[2]           |                                                |

| 29   | I/O  | I    | P3[4]           |                                                |

| 30   | I/O  | I    | P3[6]           |                                                |

| 31   | I/O  | I    | P4[0]           |                                                |

| 32   | I/O  | I    | P4[2]           |                                                |

| 33   | I/O  | I    | P2[0]           |                                                |

| 34   | I/O  | I    | P2[2]           |                                                |

| 35   | I/O  | I    | P2[4]           |                                                |

| 36   | I/O  | I    | P2[6]           |                                                |

| 37   | IOH  | I    | P0[0]           |                                                |

| 38   | IOH  | I    | P0[2]           |                                                |

| 39   | IOH  | I    | P0[4]           |                                                |

図 11. CY8C20646A、CY8C20646AS、CY8C20666A、CY8C20666AS

| ピン番号 | デジタル | アナログ | ピン名             | 説明                         |

|------|------|------|-----------------|----------------------------|

| 40   | IOH  | I    | P0[6]           |                            |

| 41   |      | 電源   | V <sub>DD</sub> | 電源電圧                       |

| 42   |      |      | NC              | 接続なし                       |

| 43   |      |      | NC              | 接続なし                       |

| 44   | IOH  | I    | P0[7]           |                            |

| 45   | IOH  | I    | P0[5]           |                            |

| 46   | IOH  | I    | P0[3]           | 積分入力                       |

| 47   |      | 電源   | V <sub>SS</sub> | グランド接続 [45]                |

| 48   | IOH  | I    | P0[1]           |                            |

|      | CP   | 電源   | V <sub>SS</sub> | センター パッドをグランドに接続する必要があります。 |

凡例： A= アナログ、 I= 入力、 O= 出力、 NC= 接続なし、 H=5mA HIGH 出力駆動、 R= 安定化出力。

注：

41. 38 本の GPIO= 容量センシング用の 33 本のピン +I2C 用の 2 本のピン +USB 用の 2 本のピン + 変調コンデンサ用の 1 本のピン。

42. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサーントした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。どちらの場合も、これらのライン上のブルアップ抵抗がブルダウン抵抗 (5.6kΩ) と組み合わせ、潜在的な分圧回路を形成します。このため、電源投入イベントまたはリセットイベント中、P1[1] と P1[0] が I2C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

43. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続する必要があります。グランドに接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

44. 代替 SPI クロック。

45. すべての VSS ピンは 1 つの共通 GND 面に引き寄せる必要があります。

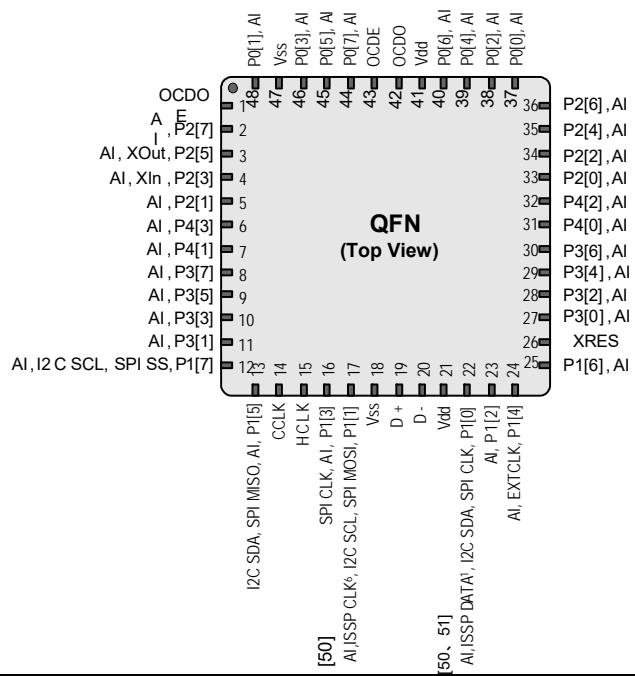

### 48 ピン QFN (OCD) (33 本のセンシング入力)<sup>[46]</sup>

48 ピン QFN 製品は CY8C20066A オンチップ デバッグ (OCD) 用です。この製品は、インサーキット デバッギングのみに使用されることに注意してください。

表 10. ピンの定義 – CY8C20066A<sup>[47, 48]</sup>

| ピン番号               | デジタル | アナログ | ピン名             | 説明                                                                      |

|--------------------|------|------|-----------------|-------------------------------------------------------------------------|

| 1 <sup>[49]</sup>  |      |      | OCDOE           | OCD モード方向ピン                                                             |

| 2                  | I/O  | I    | P2[7]           |                                                                         |

| 3                  | I/O  | I    | P2[5]           | 水晶振動子出力 (XOut)                                                          |

| 4                  | I/O  | I    | P2[3]           | 水晶振動子入力 (XIn)                                                           |

| 5                  | I/O  | I    | P2[1]           |                                                                         |

| 6                  | I/O  | I    | P4[3]           |                                                                         |

| 7                  | I/O  | I    | P4[1]           |                                                                         |

| 8                  | I/O  | I    | P3[7]           |                                                                         |

| 9                  | I/O  | I    | P3[5]           |                                                                         |

| 10                 | I/O  | I    | P3[3]           |                                                                         |

| 11                 | I/O  | I    | P3[1]           |                                                                         |

| 12                 | IOHR | I    | P1[7]           | I <sup>2</sup> C SCL、SPI SS                                             |

| 13                 | IOHR | I    | P1[5]           | I <sup>2</sup> C SDA、SPI MISO                                           |

| 14 <sup>[49]</sup> |      |      | CCLK            | OCD CPU クロック出力                                                          |

| 15 <sup>[49]</sup> |      |      | HCLK            | OCD 高速クロック出力                                                            |

| 16                 | IOHR | I    | P1[3]           | SPI CLK                                                                 |

| 17                 | IOHR | I    | P1[1]           | ISSP CLK <sup>[50]</sup> 、I <sup>2</sup> C SCL、SPI MOSI                 |

| 18                 | 電源   |      | V <sub>SS</sub> | グランド接続 <sup>[52]</sup>                                                  |

| 19                 | I/O  |      | D+              | USB D+                                                                  |

| 20                 | I/O  |      | D-              | USB D-                                                                  |

| 21                 | 電源   |      | V <sub>DD</sub> | 電源電圧                                                                    |

| 22                 | IOHR | I    | P1[0]           | ISSP DATA <sup>[50]</sup> 、I <sup>2</sup> C SDA、SPI CLK <sup>[51]</sup> |

| 23                 | IOHR | I    | P1[2]           |                                                                         |

| 24                 | IOHR | I    | P1[4]           | オプションの外部クロック入力 (EXTCLK)                                                 |

| 25                 | IOHR | I    | P1[6]           |                                                                         |

| 26                 | 入力   | XRES |                 | 内部ブルダウン抵抗付きアクティブ HIGH 外部リセット                                            |

| 27                 | I/O  | I    | P3[0]           |                                                                         |

| 28                 | I/O  | I    | P3[2]           |                                                                         |

| 29                 | I/O  | I    | P3[4]           |                                                                         |

| 30                 | I/O  | I    | P3[6]           |                                                                         |

| 31                 | I/O  | I    | P4[0]           |                                                                         |

| 32                 | I/O  | I    | P4[2]           |                                                                         |

| 33                 | I/O  | I    | P2[0]           |                                                                         |

| 34                 | I/O  | I    | P2[2]           |                                                                         |

| 35                 | I/O  | I    | P2[4]           |                                                                         |

| 36                 | I/O  | I    | P2[6]           |                                                                         |

凡例： A= アナログ、 I= 入力、 O= 出力、 NC= 接続なし、 H=5mA HIGH 出力駆動、 R= 安定化出力。

注：

- 46. 38 本の GPIO = 容量センシング用の 33 本のピン + I<sup>2</sup>C 用の 2 本のピン + USB 用の 2 本のピン + 变调コンデンサ用の 1 本のピン。

- 47. この製品は、プロトタイプ開発中のインサーキット デバッギング用として、限られた数量のみ提供されています。量産製品用としては提供できません。

- 48. 機械的、熱的、および電気的に最適な性能を得るために、QFN パッケージのセンター パッド (CP) を必ずグランド (V<sub>SS</sub>) に接続しないと、パッドは電気的に開放し、どの信号にも接続されていない状態になります。

- 49. デバイスのファームウェアをデバッグする場合、(OCD 製品のみに対応する) このピンは ICE-Cube インサーキット エミュレータの接続に必要です。ICE-Cube の使用に関する詳細は「CY3215-DK PSoC® IN-CIRCUIT EMULATOR KIT GUIDE」を参照してください。

- 50. 電源投入時、SDA (P1[0]) は 256 スリープ クロック サイクル間ストロング HIGH で駆動し、次の 256 スリープ クロック サイクル間レジスティブ LOW で駆動します。SCL (P1[1]) ラインは 512 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後両方のピンは高インピーダンス状態に移行します。リセット時、XRES がデアサートした後、SDA と SCL ラインは 8 スリープ クロック サイクル間レジスティブ LOW で駆動し、その後高インピーダンス状態に移行します。どちらの場合も、これらのライン上のブルドゥン抵抗がブルドゥン抵抗 (5.6kΩ) と組み合わせ、潜在的な分圧回路を形成します。このため、電源投入イベントまたはリセット イベント中、P1[1] と P1[0] が I<sup>2</sup>C バスに影響を与える場合があります。問題が発生する場合は別のピンを使用してください。

- 51. 替代 SPI クロック。

- 52. すべての V<sub>SS</sub> ピンは 1 つの共通 GND 面に引き寄せ必要があります。

図 12. CY8C20066A

## 電気的仕様

本節では、CY8C20XX6A/S PSoC デバイスの DC および AC 電気的仕様について説明します。最新の電気的仕様は <http://www.cypress.com/psoc> にアクセスして、最新のデータシートを確認してください。

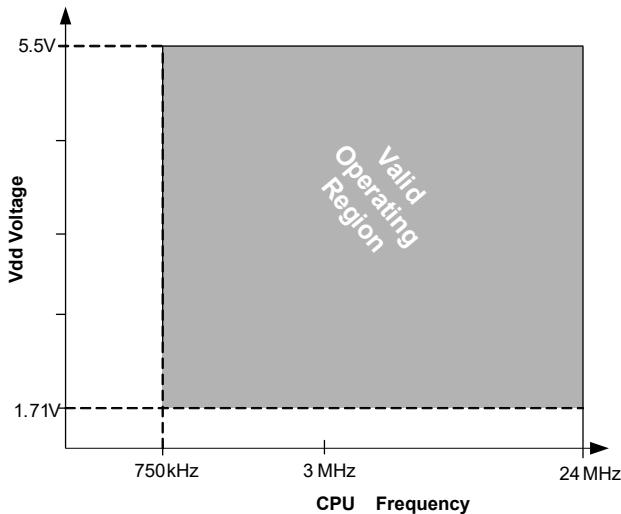

図 13. 電圧と CPU 周波数の関係

## 絶対最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。ユーザー ガイドラインは未テストです。

表 11. 絶対最大定格

| 記号                               | 説明                         | 条件                                                                                  | Min                  | Typ | Max                  | 単位 |

|----------------------------------|----------------------------|-------------------------------------------------------------------------------------|----------------------|-----|----------------------|----|

| T <sub>STG</sub>                 | 保管温度                       | 保管温度が高ければ高いほど、データ保存期間が短くなります。推奨保管温度は +25°C ±25°C です。85°C を超える温度で長期間保管すると、信頼性が低下します。 | -55                  | +25 | +125                 | °C |

| V <sub>DD</sub>                  | V <sub>SS</sub> を基準にした電源電圧 | –                                                                                   | -0.5                 | –   | +6.0                 | V  |

| V <sub>IO</sub>                  | DC 入力電圧                    | –                                                                                   | V <sub>SS</sub> -0.5 | –   | V <sub>DD</sub> +0.5 | V  |

| V <sub>IOZ</sub> <sup>[53]</sup> | トライステート ピンに印加する DC 電圧      | –                                                                                   | V <sub>SS</sub> -0.5 | –   | V <sub>DD</sub> +0.5 | V  |

| I <sub>MIO</sub>                 | ポート ピンへの最大電流               | –                                                                                   | -25                  | –   | +50                  | mA |

| ESD                              | 静電放電電圧                     | 人体モデルでの ESD                                                                         | 2000                 | –   | –                    | V  |

| LU                               | ラッチャップ電流                   | 規格 JESD78 に準拠                                                                       | –                    | –   | 200                  | mA |

## 動作温度

表 12. 動作温度

| 記号             | 説明      | 条件                                                                                                     | Min | Typ | Max  | 単位 |

|----------------|---------|--------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| T <sub>A</sub> | 周囲温度    | –                                                                                                      | -40 | –   | +85  | °C |

| T <sub>C</sub> | 民生用温度範囲 | –                                                                                                      | 0   | –   | 70   | °C |

| T <sub>J</sub> | 動作ダイ温度  | 周囲温度から接合部温度の上昇はパッケージによって異なります。 <a href="#">40 ページの熱インピーダンス</a> を参照してください。この要件を満たすように、消費電力を制限する必要があります。 | -40 | –   | +100 | °C |

注：

53. ポート 1 ピンは、High-Z モードで設定された I/O でホットスワップが可能で、ピンの入力電圧は V<sub>DD</sub> 以上です。

### チップ レベルの DC 仕様

表 13 に、電圧範囲および温度範囲の全域で保証されている最大値と最小値の仕様を示します。

表 13. チップ レベルの DC 仕様

| 記号                                              | 説明                                | 条件                                                                                        | Min  | Typ  | Max  | 単位      |

|-------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|---------|

| $V_{DD}$ <sup>[54, 55, 56, 57]</sup>            | 電源電圧                              | USB アクティビティなし。表を参照してください。 <a href="#">26 ページの「POR および LVD の DC 仕様」</a>                    | 1.71 | —    | 5.50 | V       |

| $V_{DD_{USB}}$ <sup>[54, 55, 56, 57]</sup>      | 動作電圧                              | USB アクティビティあり、USB レギュレータ有効                                                                | 4.35 | —    | 5.25 | V       |

|                                                 |                                   | USB アクティビティあり、USB レギュレータはバイパス                                                             | 3.15 | 3.3  | 3.60 | V       |

| $I_{DD24}$                                      | 電源電流、IMO=24MHz                    | 条件 : $V_{DD} \leq 3.0V$ 、 $T_A = 25^\circ C$ 、CPU=24 MHz。CapSense は 12MHz で動作、I/O ソース電流なし | —    | 2.88 | 4.00 | mA      |

| $I_{DD12}$                                      | 電源電流、IMO=12MHz                    | 条件 : $V_{DD} \leq 3.0V$ 、 $T_A = 25^\circ C$ 、CPU=12MHz。CapSense は 12MHz で動作、I/O ソース電流なし  | —    | 1.71 | 2.60 | mA      |

| $I_{DD6}$                                       | 電源電流、IMO=6MHz                     | 条件 : $V_{DD} \leq 3.0V$ 、 $T_A = 25^\circ C$ 、CPU=6MHz。CapSense は 6MHz で動作、I/O ソース電流なし    | —    | 1.16 | 1.80 | mA      |

| $I_{DDAVG10}$                                   | センサーごとの平均電源電流                     | 1 個のセンサーは 10mS レートでスキャン                                                                   | —    | 250  | —    | $\mu A$ |

| $I_{DDAVG100}$                                  | センサーごとの平均電源電流                     | 1 個のセンサーは 100mS レートでスキャン                                                                  | —    | 25   | —    | $\mu A$ |

| $I_{DDAVG500}$                                  | センサーごとの平均電源電流                     | 1 個のセンサーは 500mS レートでスキャン                                                                  | —    | 7    | —    | $\mu A$ |

| $I_{SB0}$ <sup>[58, 59, 60, 61, 62, 63]</sup>   | ディープ スリープ電流                       | $V_{DD} \leq 3.0V$ 、 $T_A = 25^\circ C$ 、I/O レギュレータはオフ                                    | —    | 0.10 | 1.05 | $\mu A$ |

| $I_{SB1}$ <sup>[58, 59, 60, 61, 62, 63]</sup>   | POR、LVD、およびスリープタイマーが有効な場合のスタンバイ電流 | $V_{DD} \leq 3.0V$ 、 $T_A = 25^\circ C$ 、I/O レギュレータはオフ                                    | —    | 1.07 | 1.50 | $\mu A$ |

| $I_{SBI2C}$ <sup>[58, 59, 60, 61, 62, 63]</sup> | $I^2C$ が有効な場合のスタンバイ電流             | 条件 : $V_{DD} = 3.3V$ 、 $T_A = 25^\circ C$ 、CPU=24MHz                                      | —    | 1.64 | —    | $\mu A$ |

注 :

- 54.  $V_{DD}$  が 1.71V ~ 1.9V の範囲にある時間が 50 $\mu s$  を超えている場合、1.71V ~ 1.9V の範囲から 2V 以上まで上昇する時に、POR をトリガしないようにするために、スルーレートを 1V/500 $\mu s$  未満にする必要があります。これ以外の電圧範囲や電圧の移行の際のスルーレートについては、SR<sub>POWER\_UP</sub> パラメーターが唯一の制限です。

- 55. スタンバイ スリープ モードで電源を遮断する場合、 $V_{DD}$  の電圧低下状態を適切に検出し、この状態から回復できるようにするには、次のいずれかの措置をとる必要があります。

- a. 電源を遮断する前にデバイスをスリープ状態から復帰させる。

- b. 再度電源を投入する前に、 $V_{DD}$  が 100mV を下回っているようになる。

- c. OSC\_CRO レジスタで No Buzz (ブザーなし) ビットを設定し、スリープ中に電圧監視回路への電源供給を維持する。

- d. ブザー レートを上げて、 $V_{DD}$  の立ち下がりエッジを取り込むようにする。レートは、SLP\_CFG レジスタで PSSDC ビットにより設定されます。リファレンスレジスタは [CY8C20X36 Technical Reference Manual](#) を参照してください。ディープ スリープ モードでは、追加の低電圧監視回路によって、1V/ms より遅いエッジ レートで  $V_{DD}$  電力低下状態を検出できます。

- 56. USB モードでは、バスパワーで動作するアプリケーション用の  $V_{DD}$  を 4.35 ~ 5.35V に制限する必要があります。セルフパワーで動作するアプリケーション用の  $V_{DD}$  は 3.15 ~ 3.45V でなければなりません。

- 57. 適切な CapSense ブロック機能のために、 $V_{DD}$  の低下が基準  $V_{DD}$  の 5% を超える場合、 $V_{DD}$  の低下率は 200mV/秒を超えてはいけません。基準  $V_{DD}$  は、1.8V ~ 5.5V です。

- 58. エラッタ : デバイスをスタンバイまたは I2C\_USB モードでスリープに移行し、かつバンドギャップ回路が 8ms (デフォルト) よりも長い間隔でリフレッシュされる場合、デバイスはスリープ終了の入力が受信される時、スリープを終了しない場合があります。詳細は [49 ページの「エラッタ」](#) を参照してください。

- 59. エラッタ : デバイスがスリープ モードへから移行している中に I2C マスターがトランザクションを開始すると、I2C ブロックはデータとバス破損エラーを示すことがあります。詳細は [49 ページの「エラッタ」](#) を参照してください。

- 60. エラッタ : レジスタ 0 のビット 1 (B0h (PT0\_CFG)) をセットすることでプログラム可能なタイマー 0 が「ワンショット」モードで使用されており、かつタイマー割り込みがデバイスをスリープからウェイクアップするために使用されている場合、割り込みサービス ルーチン (ISR) が 2 回実行される可能性があります。詳細は [50 ページの「エラッタ」](#) を参照してください。

- 61. エラッタ : スリープ モードのとき、GPIO 割り込みがタイマー 0 またはスリープ タイマー割り込みと同時に発生すると、GPIO 割り込みが見逃され、対応する GPIO ISR が実行されない場合があります。詳細は [50 ページの「エラッタ」](#) を参照してください。

- 62. エラッタ : ファームウェアがデバイスにスリープに入るよう命令する短い時間 (2.5 CPU サイクル以内) 前に割り込みが発行されたら、その割り込みは見逃されます。詳細は [ページの「エラッタ」](#) 51 を参照してください。

- 63. エラッタ : アナログ割り込みがトリガされると、デバイスはスリープから復帰します。詳細は [51 ページの「エラッタ」](#) を参照してください。

## GPIO の DC 仕様

下表に、次の電圧範囲と温度範囲それぞれで保証されている最大値と最小値の仕様を示します：3.0V ~ 5.5V と -40°C ≤ TA ≤ 85°C、2.4V ~ 3.0V と -40°C ≤ TA ≤ 85°C、または 1.71V ~ 2.4V と -40°C ≤ TA ≤ 85°C。標準バラメーターは、温度 25°C、電圧 5V および 3.3V の場合の値で、設計の参考としてのみ示します。

**表 14. 3.0V ~ 5.5V の GPIO の DC 仕様**

| 記号                    | 説明                                                     | 条件                                                                                                                                          | Min                   | Typ   | Max  | 単位 |

|-----------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|----|

| R <sub>PU</sub>       | プルアップ抵抗値                                               | -                                                                                                                                           | 4                     | 5.60  | 8    | kΩ |

| V <sub>OH1</sub>      | HIGH 出力電圧<br>ポート 2、3 または 4 のピン                         | I <sub>OH</sub> ≤10μA、すべての I/O でのソース電流<br>は最大 10mA                                                                                          | V <sub>DD</sub> -0.20 | -     | -    | V  |

| V <sub>OH2</sub>      | HIGH 出力電圧<br>ポート 2、3 または 4 のピン                         | I <sub>OH</sub> =1mA、すべての I/O でのソース電流は<br>最大 20mA                                                                                           | V <sub>DD</sub> -0.90 | -     | -    | V  |

| V <sub>OH3</sub>      | HIGH 出力電圧<br>ポート 0 または 1 のピン、ポート 1 では<br>LDO レギュレータは無効 | I <sub>OH</sub> <10μA、すべての I/O でのソース電流<br>は最大 10mA                                                                                          | V <sub>DD</sub> -0.20 | -     | -    | V  |

| V <sub>OH4</sub>      | HIGH 出力電圧<br>ポート 0 または 1 のピン、ポート 1 では<br>LDO レギュレータは無効 | I <sub>OH</sub> =5mA、すべての I/O でのソース電流は<br>最大 20mA                                                                                           | V <sub>DD</sub> -0.90 | -     | -    | V  |

| V <sub>OH5</sub>      | HIGH 出力電圧<br>ポート 1 のピン、3V 出力の LDO レギュレー<br>タは有効        | I <sub>OH</sub> <10μA、V <sub>DD</sub> >3.1V、最大 4 本の I/O ピ<br>ン、各ピンの供給電流は 5mA                                                                | 2.85                  | 3.00  | 3.30 | V  |

| V <sub>OH6</sub>      | HIGH 出力電圧<br>ポート 1 のピン、3V 出力の LDO レギュレー<br>タは有効        | I <sub>OH</sub> =5mA、V <sub>DD</sub> >3.1V、すべての I/O で供<br>給電流は最大 20mA                                                                       | 2.20                  | -     | -    | V  |

| V <sub>OH7</sub>      | HIGH 出力電圧<br>ポート 1 のピン、2.5V 出力の LDO は有効                | I <sub>OH</sub> <10μA、V <sub>DD</sub> >2.7V、すべての I/O での<br>供給電流は最大 20mA                                                                     | 2.35                  | 2.50  | 2.75 | V  |

| V <sub>OH8</sub>      | HIGH 出力電圧<br>ポート 1 のピン、2.5V 出力の LDO は有効                | I <sub>OH</sub> =2mA、V <sub>DD</sub> >2.7V、すべての I/O での<br>供給電流は最大 20mA                                                                      | 1.90                  | -     | -    | V  |

| V <sub>OH9</sub>      | HIGH 出力電圧<br>ポート 1 のピン、1.8V 出力の LDO は有効                | I <sub>OH</sub> <10μA、V <sub>DD</sub> >2.7V、すべての I/O での<br>供給電流は最大 20mA                                                                     | 1.60                  | 1.80  | 2.10 | V  |

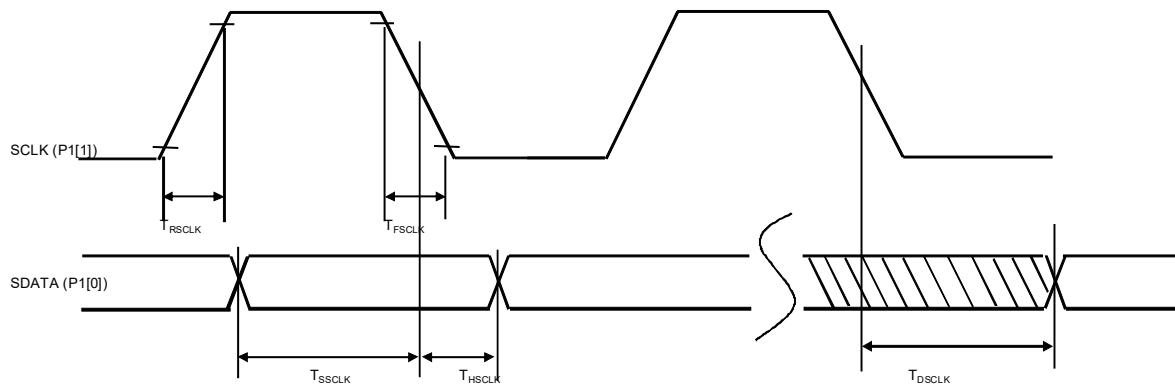

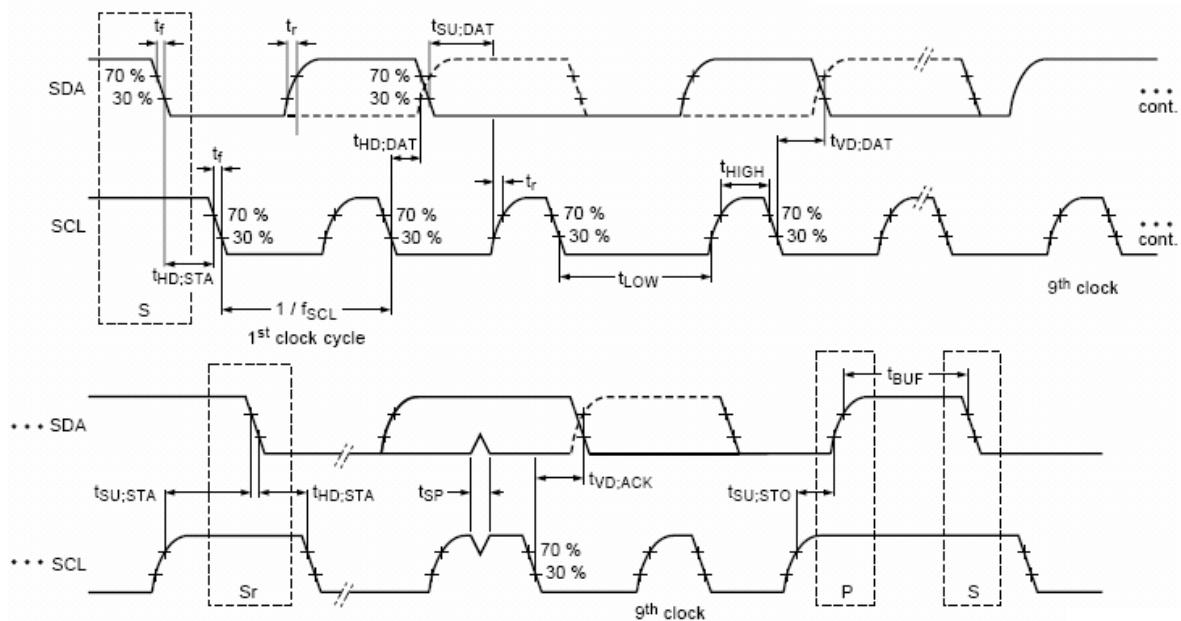

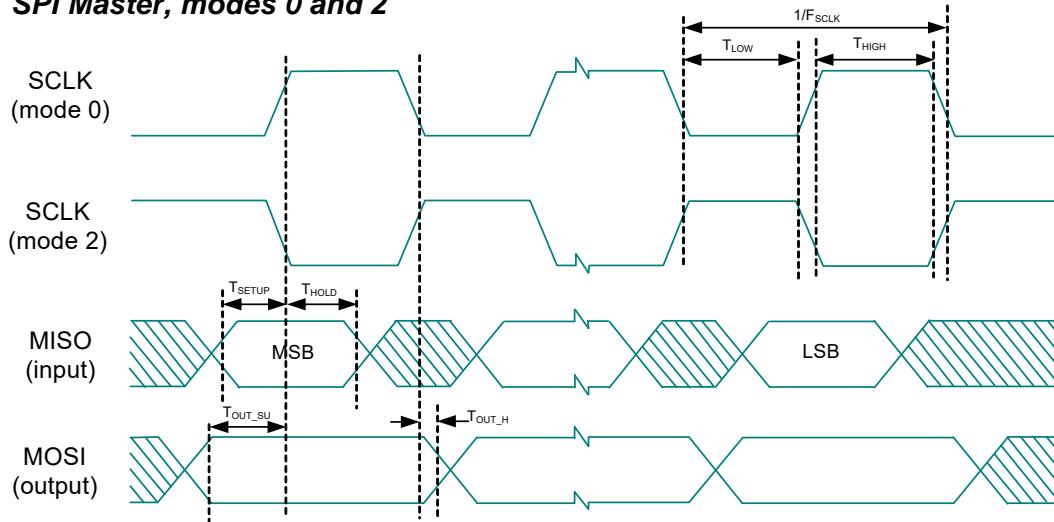

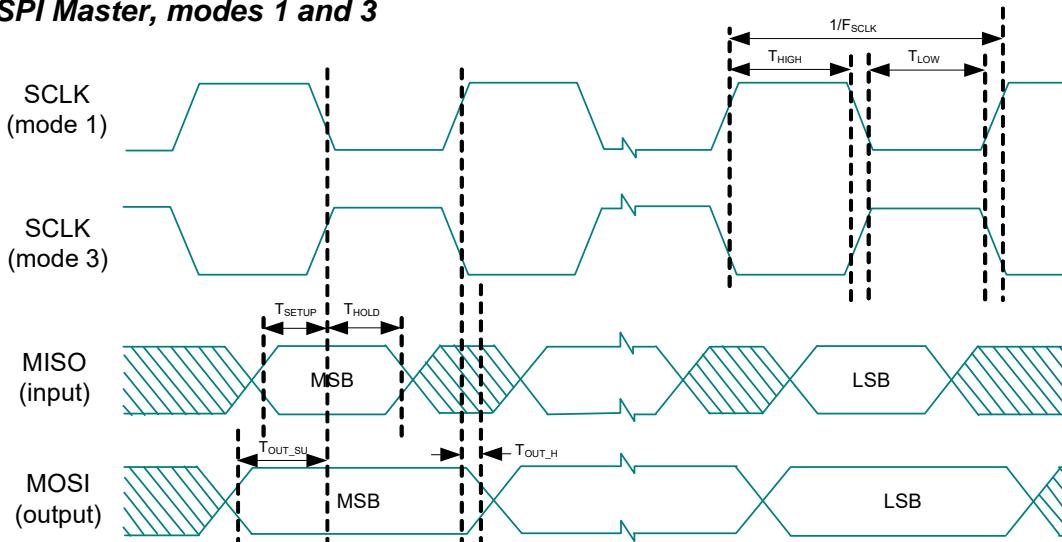

| V <sub>OH10</sub>     | HIGH 出力電圧<br>ポート 1 のピン、1.8V 出力の LDO は有効                | I <sub>OH</sub> =1mA、V <sub>DD</sub> >2.7V、すべての I/O での<br>供給電流は最大 20mA                                                                      | 1.20                  | -     | -    | V  |