## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

### **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# F<sup>2</sup>MC-8FX Programming Specifications

Document Number: 002-07004 Rev. \*B

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2006-2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR-POSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PROD-UCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any use of a Cypress product as a Critical Component in a High-Risk Device. You shall indemnify and hold Cypress, its directors, officers, employees, agents, affiliates, distributors, and assigns harmless from and against all claims, costs, damages, and expenses, arising out of any claim, including claims for product liability, personal injury or death, or property damage arising from any use of a Cypress product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any High-Risk Device except to the limited extent that (i) Cypress's published data sheet for the product explicitly states Cypress has qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to use the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1. | Outline    | And Configuration Example Of F2MC-8FX CPU                                                                                                        | 6    |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | 1.1        | Outline of F <sup>2</sup> MC-8FX CPU                                                                                                             | 7    |

|    | 1.2        | Configuration Example of Device Using F <sup>2</sup> MC-8FX CPU                                                                                  | 8    |

| 2. | Memory     | / Space                                                                                                                                          | 9    |

|    | 2.1        | CPU Memory Space                                                                                                                                 |      |

|    | 2.2        | Memory Space and Addressing                                                                                                                      |      |

|    |            | 2.2.1 Data Area                                                                                                                                  |      |

|    |            | 2.2.2 Program Area                                                                                                                               |      |

|    |            | 2.2.3 Arrangement of 16-bit Data in Memory Space                                                                                                 |      |

| 3. | Registe    | rs                                                                                                                                               | 18   |

|    | 3.1        | F <sup>2</sup> MC-8FX Registers                                                                                                                  |      |

|    | 3.2        | Program Counter (PC) and Stack Pointer (SP)                                                                                                      |      |

|    | 3.3        | Accumulator (A) and Temporary Accumulator (T)                                                                                                    |      |

|    |            | 3.3.1 How To Use The Temporary Accumulator (T)                                                                                                   |      |

|    |            | 3.3.2 Byte Data Transfer and Operation of Accumulator (A) and Temporary Acc                                                                      | umu- |

|    |            | lator (T)                                                                                                                                        |      |

|    | 3.4        | Program Status (PS)                                                                                                                              |      |

|    | 3.5        | Index Register (IX) and Extra Pointer (EP)                                                                                                       |      |

|    | 3.6        | Register Banks                                                                                                                                   |      |

|    | 3.7        | Direct Banks                                                                                                                                     | 31   |

| 4. | Interru    | ot Processing                                                                                                                                    | 32   |

|    | 4.1        | Outline of Interrupt Operation                                                                                                                   | 33   |

|    | 4.2        | Interrupt Enable/Disable and Interrupt Priority Functions                                                                                        |      |

|    | 4.3        | Creating an Interrupt Processing Program                                                                                                         |      |

|    | 4.4        | Multiple Interrupt                                                                                                                               |      |

|    | 4.5        | Reset Operation                                                                                                                                  | 38   |

| 5. | CPU Sc     | ftware Architecture                                                                                                                              | 39   |

|    | 5.1        | Types of Addressing Modes                                                                                                                        | 40   |

|    | 5.2        | Special Instructions                                                                                                                             | 44   |

| 6. | Detaile    | d Rules For Execution Instructions                                                                                                               | 48   |

|    | 6.1        | ADDC (ADD Byte Data of Accumulator and Temporary Accumulator with Carry t cumulator)                                                             |      |

|    | 6.2<br>6.3 | ADDC (ADD Byte Data of Accumulator and Memory with Carry to Accumulator). ADDCW (ADD Word Data of Accumulator and Temporary Accumulator with Car | 51   |

|    |            | to Accumulator)                                                                                                                                  | 53   |

| 6.4  | AND (AND Byte Data of Accumulator and Temporary Accumulator           |     |

|------|-----------------------------------------------------------------------|-----|

|      | to Accumulator)                                                       | 55  |

| 6.5  | AND (AND Byte Data of Accumulator and Memory to Accumulator)          | 57  |

| 6.6  | ANDW (AND Word Data of Accumulator and Temporary Accumulator          |     |

|      | to Accumulator)                                                       | 59  |

| 6.7  | BBC (Branch if Bit is Clear)                                          |     |

| 6.8  | BBS (Branch if Bit is Set)                                            |     |

| 6.9  | BC (Branch relative if C=1)/BLO (Branch if LOwer)                     |     |

| 6.10 | BGE (Branch Great or Equal: relative if larger than or equal to Zero) |     |

| 6.11 | BLT (Branch Less Than zero: relative if < Zero)                       |     |

| 6.12 | BN (Branch relative if N = 1)                                         |     |

| 6.13 | BNZ (Branch relative if Z = 0)/BNE (Branch if Not Equal)              | 73  |

| 6.14 | BNC (Branch relative if C = 0)/BHS (Branch if Higher or Same)         |     |

| 6.15 | BP (Branch relative if N = 0: PLUS)                                   |     |

| 6.16 | BZ (Branch relative if Z = 1)/BEQ (Branch if Equal)                   |     |

| 6.17 |                                                                       |     |

| 6.18 |                                                                       |     |

|      | CALLV (CALL Vectored subroutine) CLRB (Clear direct Memory Bit)       |     |

| 6.19 |                                                                       |     |

| 6.20 | CLRC (Clear Carry flag)                                               |     |

| 6.21 | CLRI (CLeaR Interrupt flag)                                           |     |

| 6.22 | CMP (CoMPare Byte Data of Accumulator and Temporary Accumulator)      |     |

| 6.23 | CMP (CoMPare Byte Data of Accumulator and Memory)                     |     |

| 6.24 | CMP (CoMPare Byte Data of Immediate Data and Memory)                  |     |

| 6.25 | CMPW (CoMPare Word Data of Accumulator and Temporary Accumulator)     |     |

| 6.26 | DAA (Decimal Adjust for Addition)                                     |     |

| 6.27 | DAS (Decimal Adjust for Subtraction)                                  |     |

| 6.28 | DEC (DECrement Byte Data of General-purpose Register)                 |     |

| 6.29 | DECW (DECrement Word Data of Accumulator)                             |     |

| 6.30 | DECW (DECrement Word Data of Extra Pointer)                           |     |

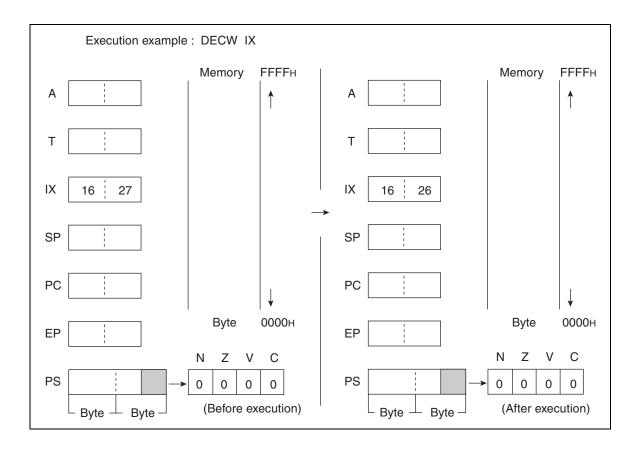

| 6.31 | DECW (DECrement Word Data of Index Pointer)                           | 110 |

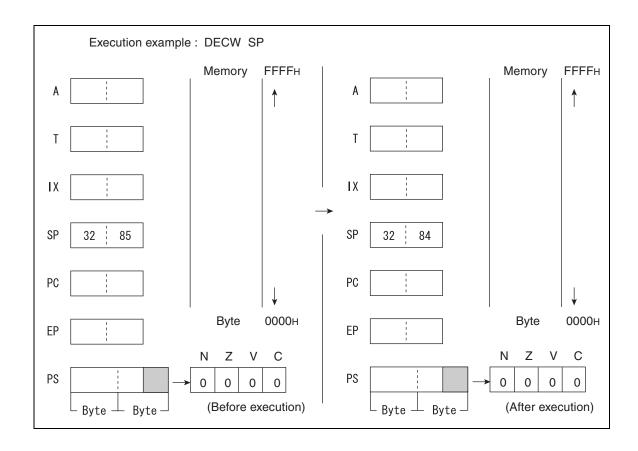

| 6.32 | DECW (DECrement Word Data of Stack Pointer)                           |     |

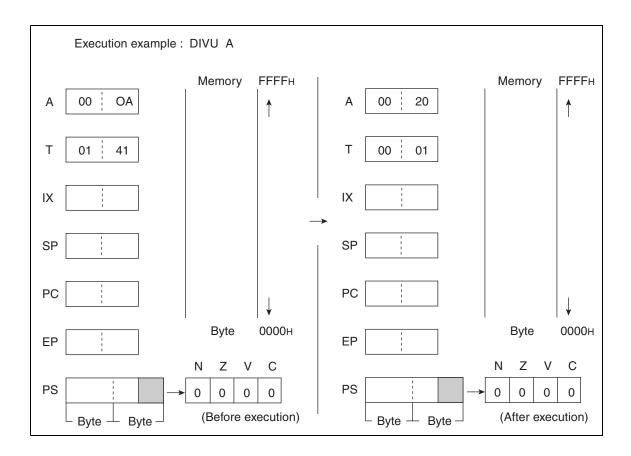

| 6.33 | DIVU (DIVide Unsigned)                                                | 114 |

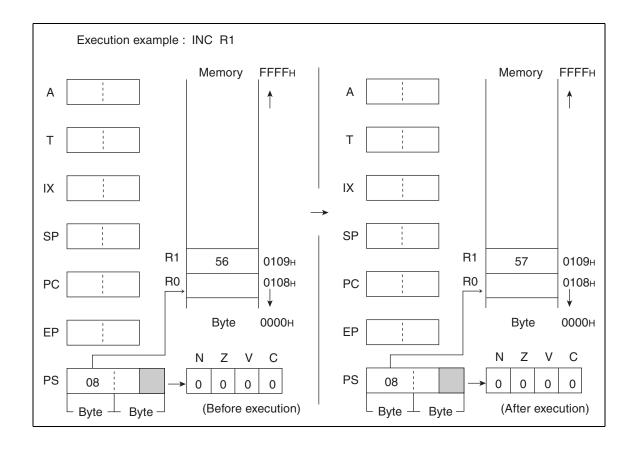

| 6.34 | INC (INCrement Byte Data of General-purpose Register)                 | 116 |

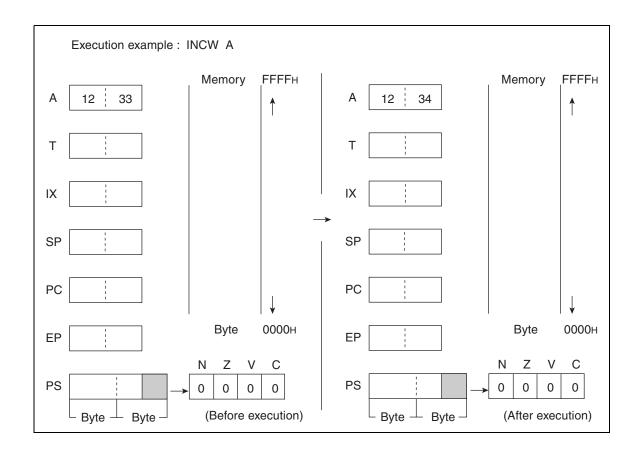

| 6.35 | INCW (INCrement Word Data of Accumulator)                             |     |

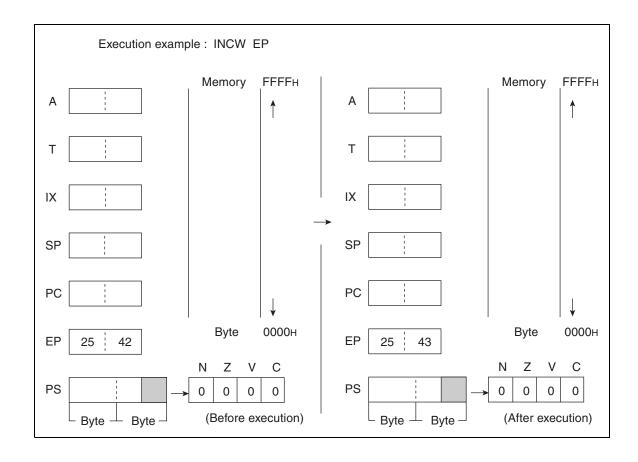

| 6.36 | INCW (INCrement Word Data of Extra Pointer)                           | 120 |

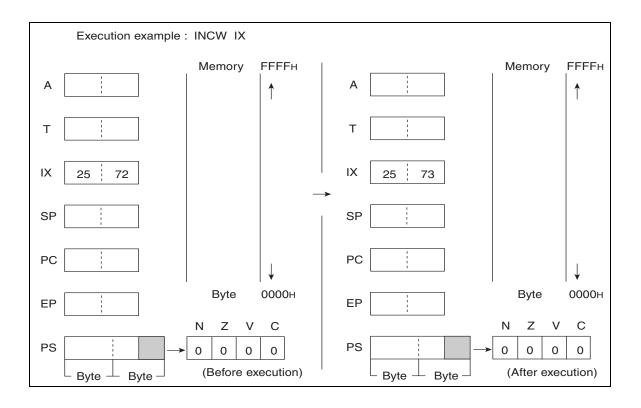

| 6.37 | INCW (INCrement Word Data of Index Register)                          | 122 |

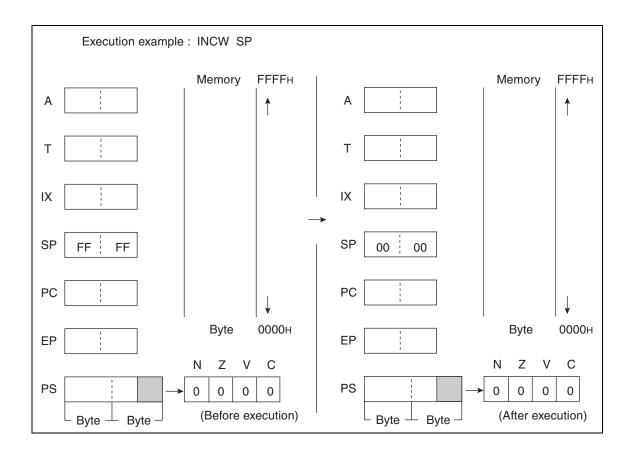

| 6.38 | INCW (INCrement Word Data of Stack Pointer)                           | 124 |

| 6.39 | JMP (JuMP to address pointed by Accumulator)                          | 126 |

| 6.40 | JMP (JuMP to effective Address)                                       |     |

| 6.41 | MOV (MOVE Byte Data from Temporary Accumulator to Address Pointed     |     |

|      | by Accumulator)                                                       | 130 |

| 6.42 | MOV (MOVE Byte Data from Memory to Accumulator)                       |     |

| 6.43 | MOV (MOVE Immediate Byte Data to Memory)                              |     |

| 6.44 | MOV (MOVE Byte Data from Accumulator to memory)                       |     |

| 6.45 | MOVW (MOVE Word Data from Temporary Accumulator to Address Pointed    |     |

|      | by Accumulator)                                                       | 138 |

| 6.46 | MOVW (MOVE Word Data from Memory to Accumulator)                      |     |

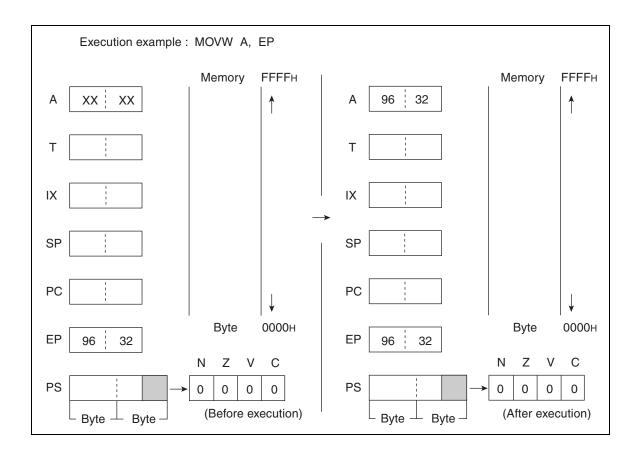

| 6.47 | MOVW (MOVE Word Data from Extra Pointer to Accumulator)               |     |

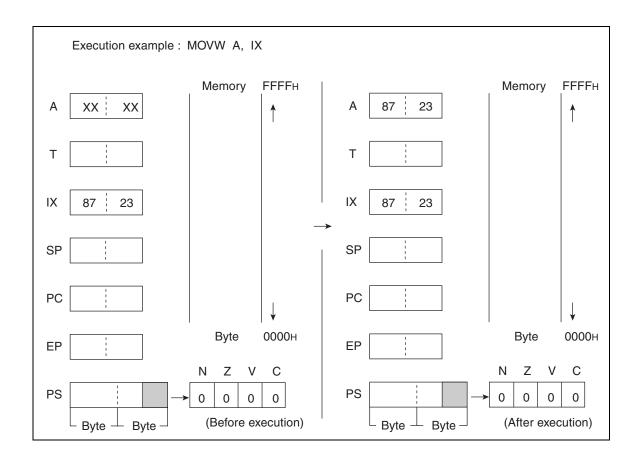

| 6.48 | MOVW (MOVE Word Data from Index Register to Accumulator)              |     |

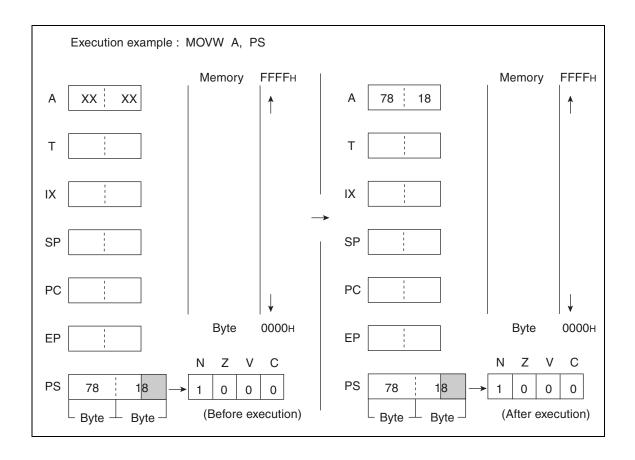

| 6.49 | MOVW (MOVE Word Data from Program Status Register to Accumulator)     |     |

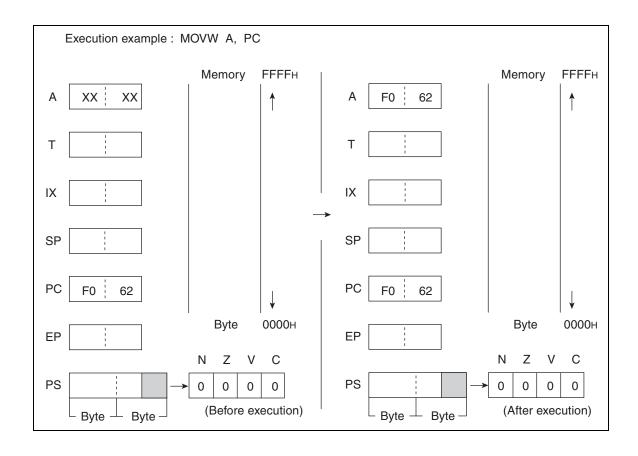

| 6.50 | MOVW (MOVE Word Data from Program Counter to Accumulator)             |     |

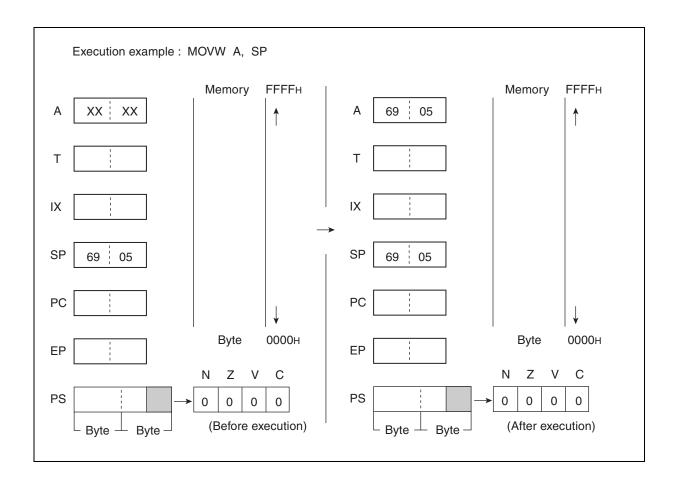

| 6.51 | MOVW (MOVE Word Data from Stack Pointer to Accumulator)               |     |

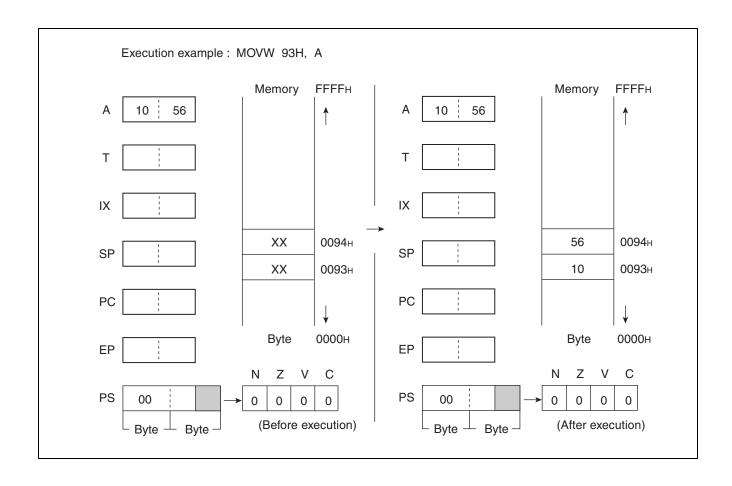

| 6.52 | MOVW (MOVE Word Data from Accumulator to Memory)                      |     |

| J.UZ | IND VIV (IND VE VVOID Data HOITI MODULITAIDID TO MICHOLY)             | ₁∪∠ |

| Re | vision Hi | story                                                                       | 262   |

|----|-----------|-----------------------------------------------------------------------------|-------|

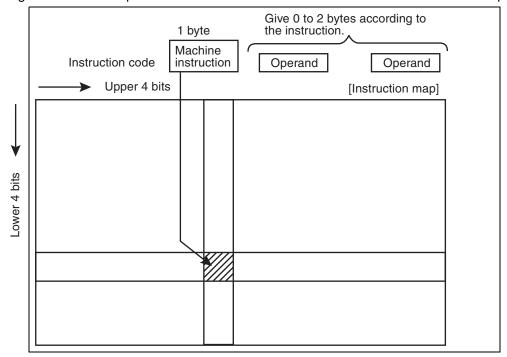

| C. | Instruct  | tion Map                                                                    | . 260 |

|    |           | eration List                                                                |       |

|    | •         | ion List                                                                    |       |

| Ма | ijor Chan | gesg                                                                        |       |

|    | 0.00      | to Accmulator)                                                              | 220   |

|    |           | XORW (eXclusive OR Word Data of Accumulator and Temporary Accumulator       | 0     |

|    | 6.85      | XOR (eXclusive OR Byte Data of Accumulator and Memory to Accumulator)       |       |

|    | 0.04      | to Accumulator)                                                             | 216   |

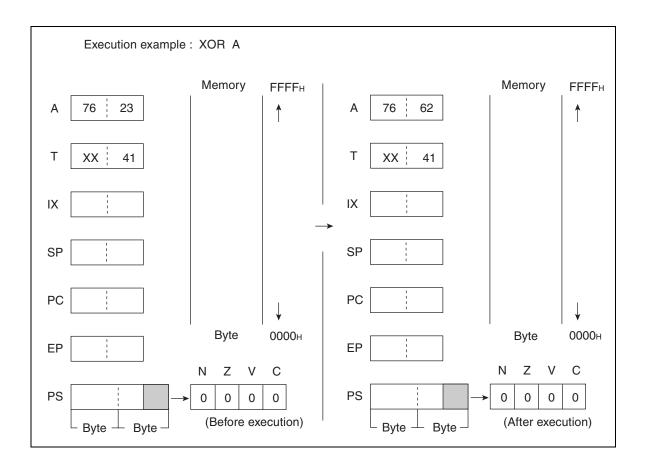

|    | 6.84      | XOR (eXclusive OR Byte Data of Accumulator and Temporary Accumulator        |       |

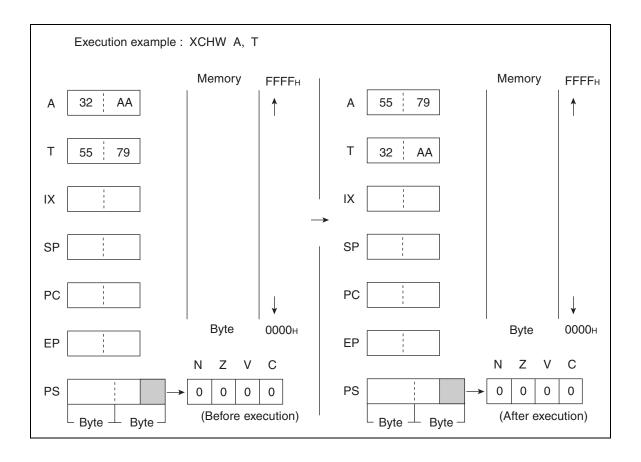

|    | 6.83      | XCHW (eXCHange Word Data Accumulator and Temporary Accumulator)             |       |

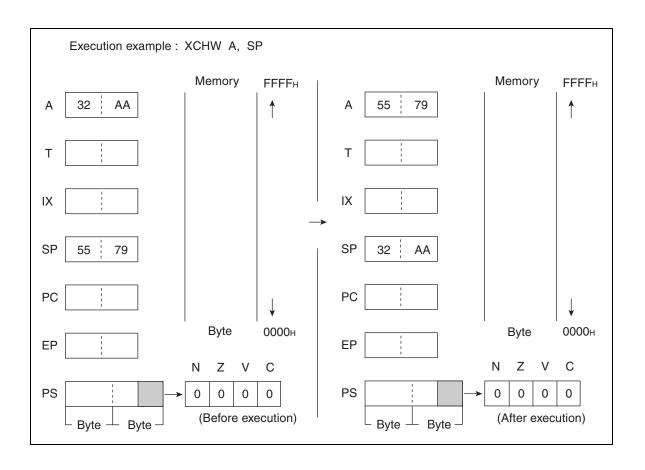

|    | 6.82      | XCHW (eXCHange Word Data Accumulator and Stack Pointer)                     |       |

|    | 6.81      | XCHW (eXCHange Word Data Accumulator and Program Counter)                   |       |

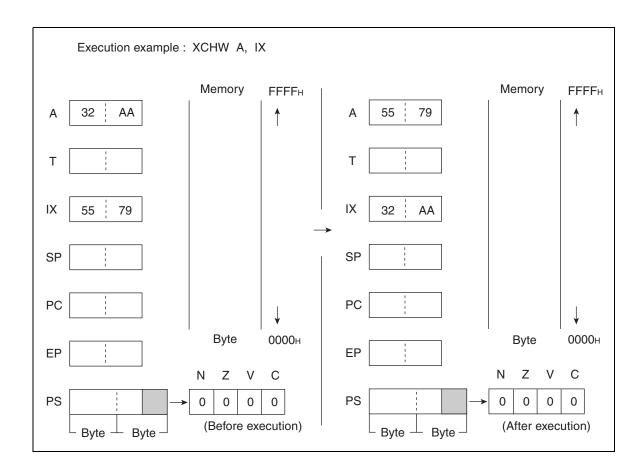

|    | 6.80      | XCHW (eXCHange Word Data Accumulator and Index Register)                    |       |

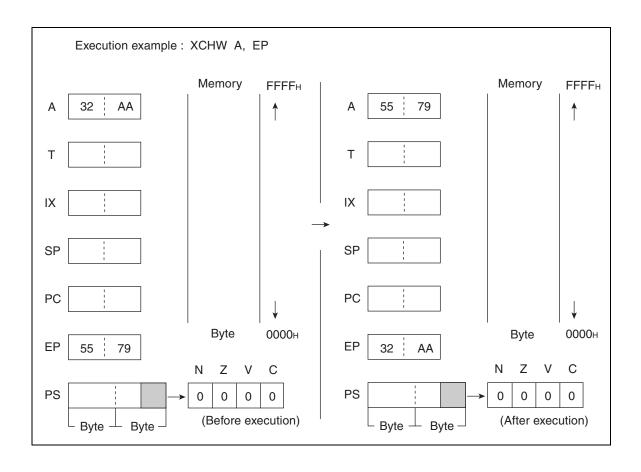

|    | 6.79      | XCHW (eXCHange Word Data Accumulator and Extrapointer)                      |       |

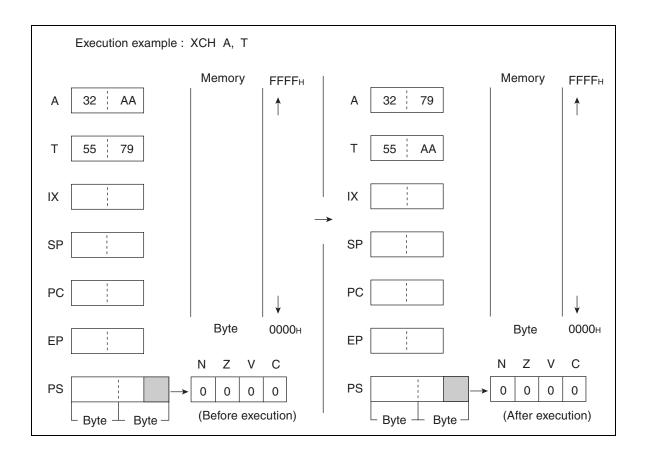

|    |           | XCH (eXCHange Byte Data Accumulator "L" and Temporary Accumulator "L")      |       |

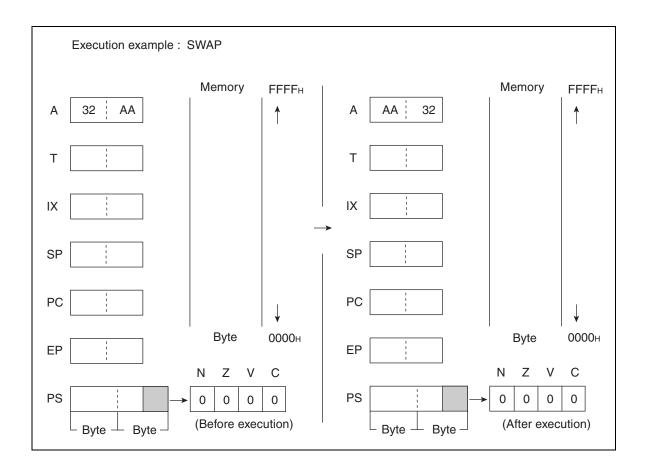

|    |           | SWAP (SWAP Byte Data Accumulator "H" and Accumulator "L")                   |       |

|    |           | SETI (SET Interrupt flag)                                                   |       |

|    |           | SETC (SET Carry flag)                                                       |       |

|    | 6.74      | SETB (Set Direct Memory Bit)                                                |       |

|    |           | with Carry to Accumulator)                                                  | 194   |

|    | 6.73      | SUBCW (SUBtract Word Data of Accumulator from Temporary Accumulator         |       |

|    |           | to Accumulator)                                                             | 192   |

|    | 6.72      | SUBC (SUBtract Byte Data of Memory from Accumulator with Carry              |       |

|    |           | Accumulator)                                                                |       |

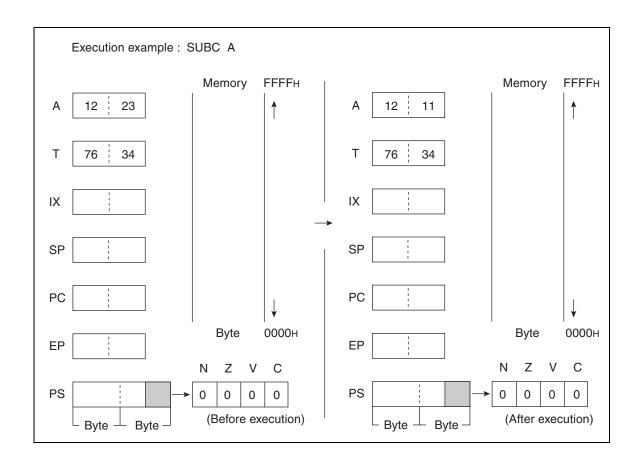

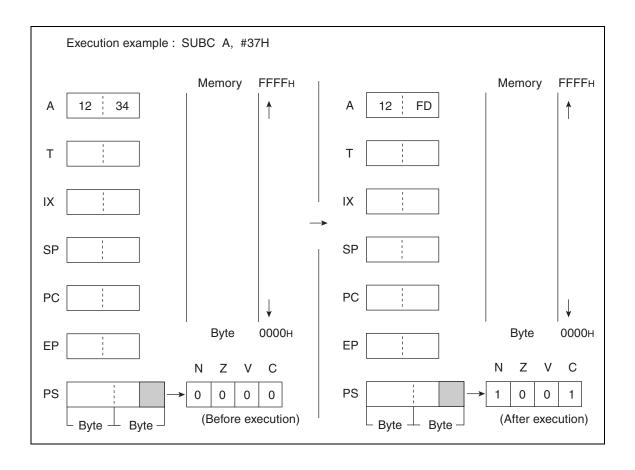

|    | 6.71      | SUBC (SUBtract Byte Data of Accumulator from Temporary Accumulator with Cal |       |

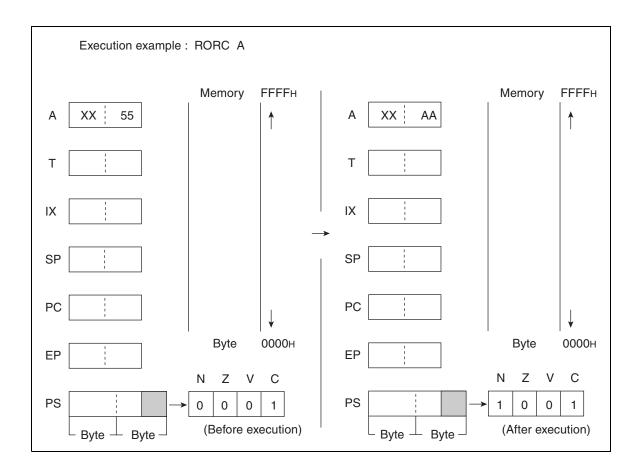

|    |           | RORC (Rotate Byte Data of Accumulator with Carry to Right)                  |       |

|    |           | ROLC (Rotate Byte Data of Accumulator with Carry to Left)                   |       |

|    | 6.68      | RETI (RETurn from Interrupt)                                                |       |

|    | 6.67      | RET (RETurn from subroutine)                                                |       |

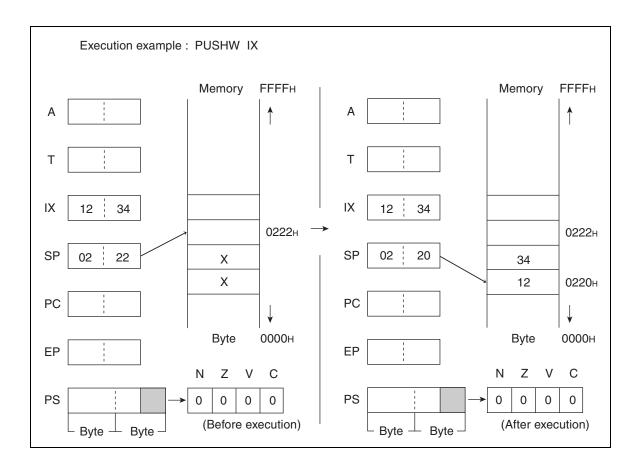

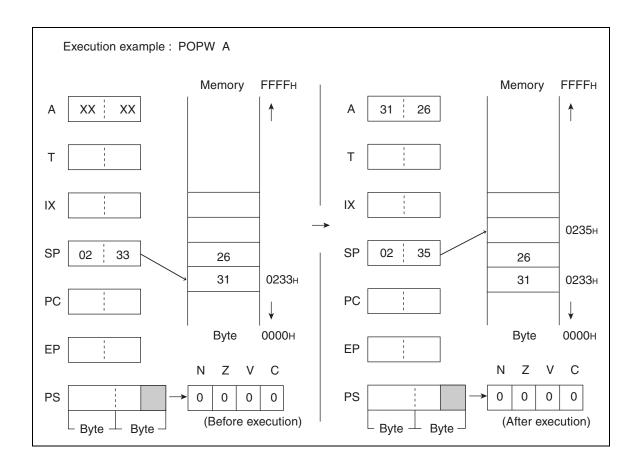

|    |           | POPW (POP Word Data of Intherent Register from Stack Memory)                |       |

|    | 6.65      | PUSHW (PUSH Word Data of Inherent Register to Stack Memory)                 |       |

|    |           | to Accumulator)                                                             | 176   |

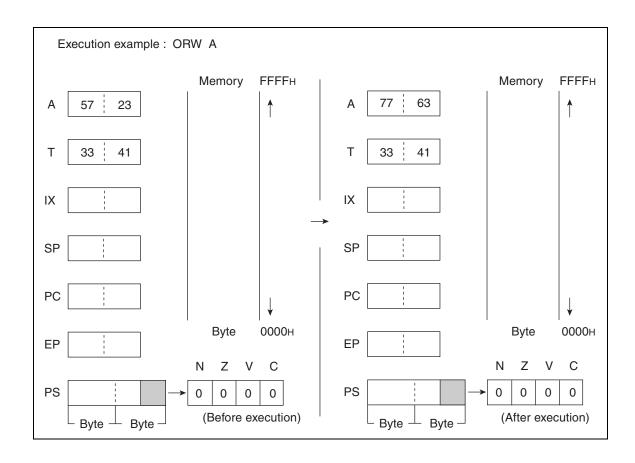

|    | 6.64      | ORW (OR Word Data of Accumulator and Temporary Accumulator                  |       |

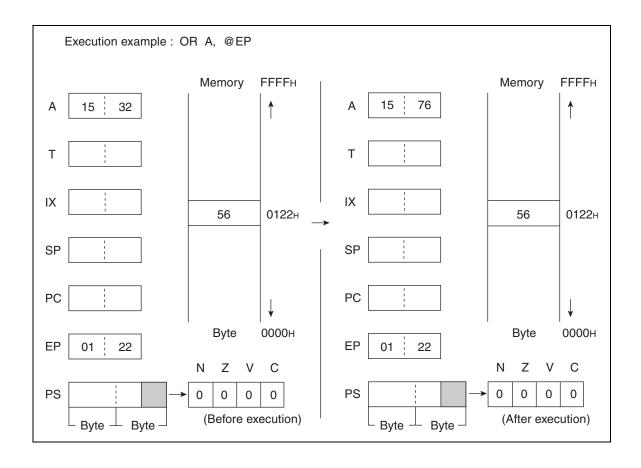

|    | 6.63      | OR (OR Byte Data of Accumulator and Memory to Accumulator)                  |       |

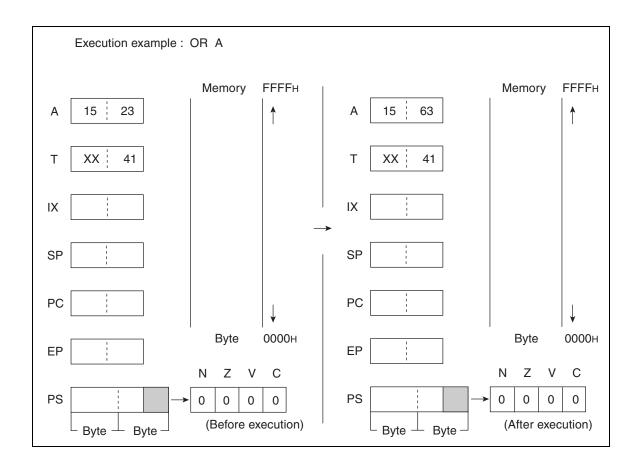

|    | 6.62      | OR (OR Byte Data of Accumulator and Temporary Accumulator to Accumulator)   |       |

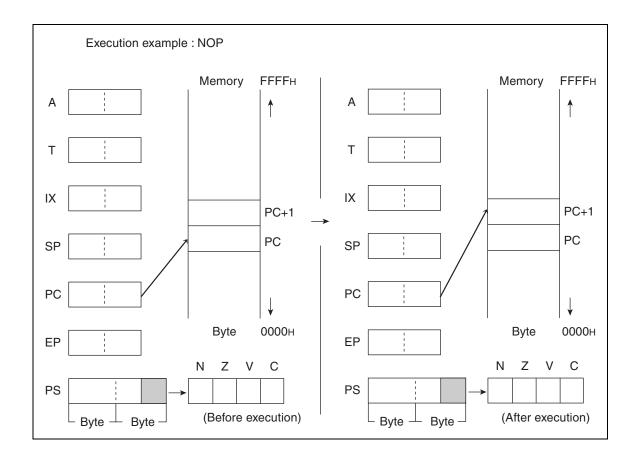

|    | 6.61      | NOP (NoOPeration)                                                           |       |

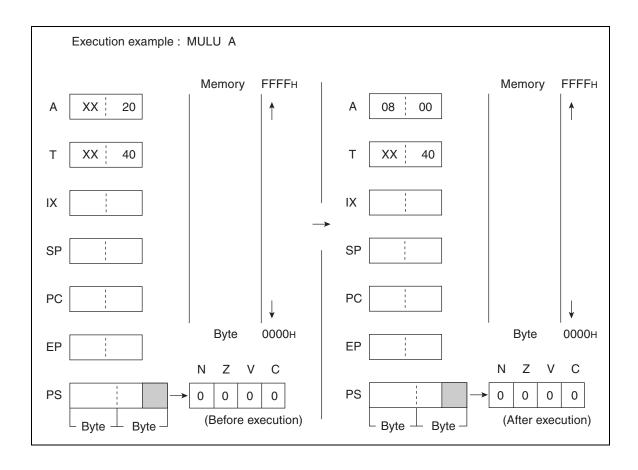

|    | 6.60      | MULU (MULtiply Unsigned)                                                    |       |

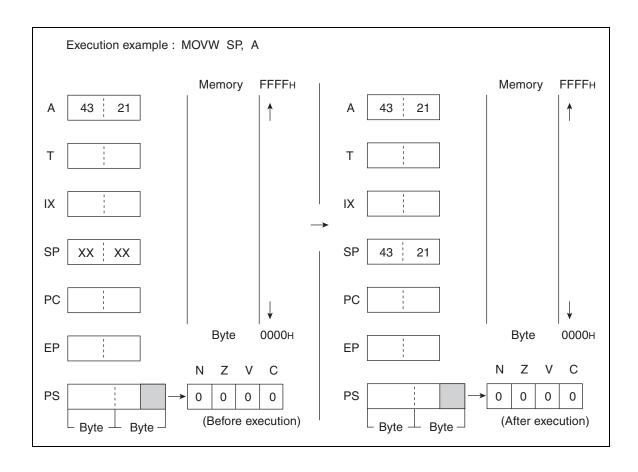

|    | 6.59      | MOVW (MOVE Word data from Accumulator to Stack Pointer)                     |       |

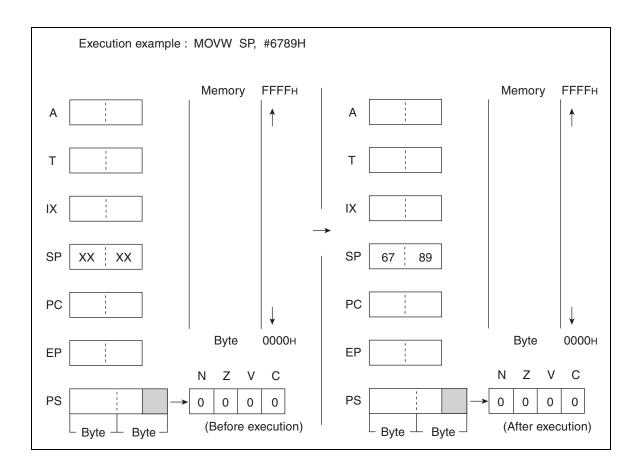

|    | 6.58      | MOVW (MOVE Immediate Word Data to Stack Pointer)                            |       |

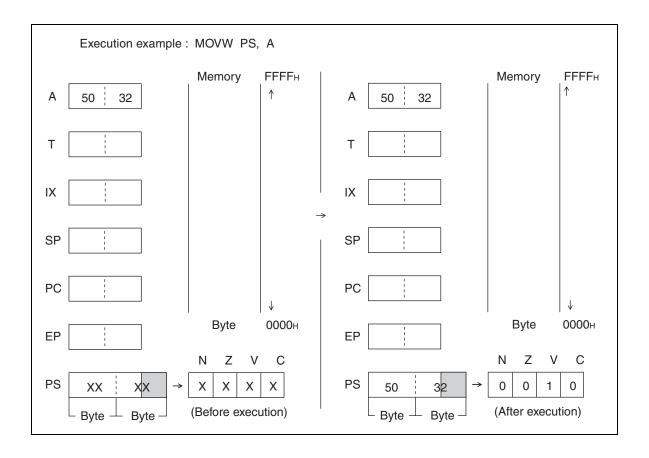

|    | 6.57      | MOVW (MOVE Word data from Accumulator to Program Status Register)           | 162   |

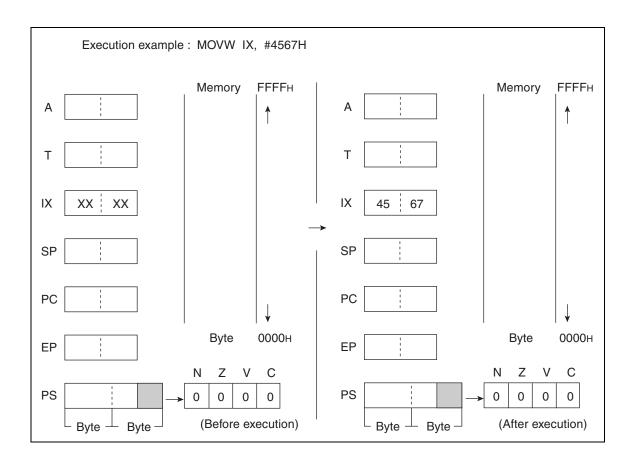

|    | 6.56      | MOVW (MOVE Immediate Word Data to Index Register)                           |       |

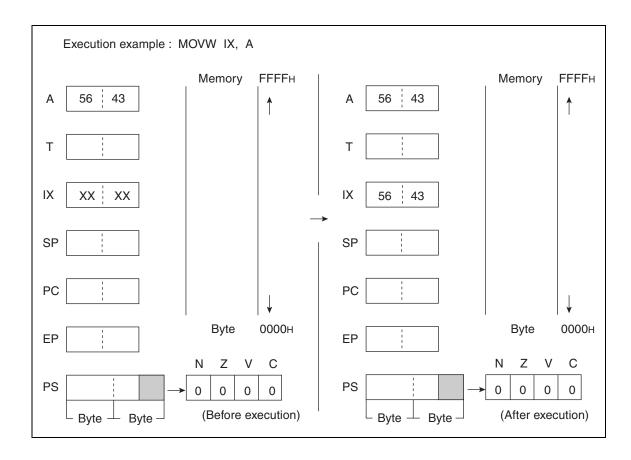

|    | 6.55      | MOVW (MOVE Word Data from Accumulator to Index Register)                    | 158   |

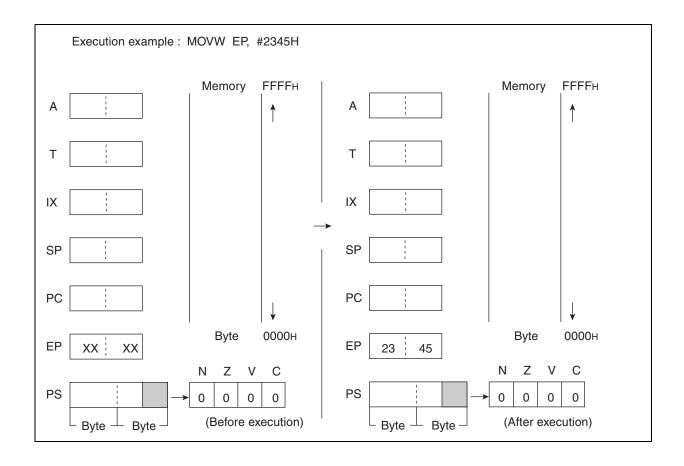

|    | 6.54      | MOVW (MOVE Immediate Word Data to Extra Pointer)                            | 156   |

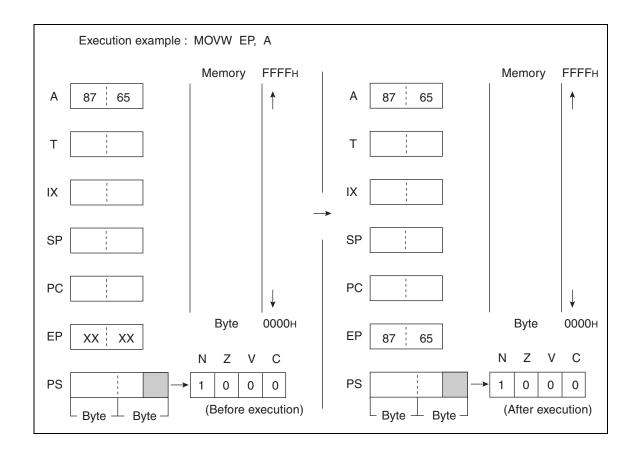

|    | 6.53      | MOVW (MOVE Word Data from Accumulator to Extra Pointer)                     | 154   |

# 1. Outline And Configuration Example Of F<sup>2</sup>MC-8FX CPU

This chapter outlines the F<sup>2</sup>MC-8FX CPU and explains its configuration by example.

- 1.1 Outline of F<sup>2</sup>MC-8FX CPU

- 1.2 Configuration Example of Device Using F<sup>2</sup>MC-8FX CPU

## 1.1 Outline of F<sup>2</sup>MC-8FX CPU

The F<sup>2</sup>MC-8FX CPU is a high-performance 8-bit CPU designed for the embedded control of various industrial and OA equipment.

## Outline of F<sup>2</sup>MC-8FX CPU

The  $F^2MC-8FX$  CPU is a high-performance 8-bit CPU designed for the control of various industrial and OA equipment. It is especially intended for applications requiring low voltages and low power consumption. This 8-bit CPU can perform 16-bit data operations and transfer and is suitable for applications requiring 16-bit control data. The  $F^2MC-8FX$  CPU is upper compatibility CPU of the  $F^2MC-8L$  CPU, and the instruction cycle number is shortened, the division instruction is strengthened, and a direct area is enhanced.

## F<sup>2</sup>MC-8FX CPU Features

The F<sup>2</sup>MC-8FX CPU features are as follows:

■ Minimum instruction execution time: 100 ns

Memory: 64 Kbytes

Instruction configuration suitable for controller

Data type: bit, byte, word Addressing modes: 9 types

High code efficiency

16-bit data operation: Operations between accumulator (A) and temporary accumulator (T)

Bit instruction: set, reset, check

Multiplication/division instruction:  $8 \times 8 = 16$  bits, 16/16 = 16 bits

Interrupt priorities : 4 levels

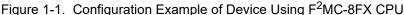

## 1.2 Configuration Example of Device Using F<sup>2</sup>MC-8FX CPU

The CPU, ROM, RAM and various resources for each F<sup>2</sup>MC-8FX device are designed in modules. The change in memory size and replacement of resources facilitate manufacturing of products for various applications.

## Configuration Example of Device Using F<sup>2</sup>MC-8FX CPU

Figure 1-1. shows a configuration example of a device using the F<sup>2</sup>MC-8FX CPU.

# 2. Memory Space

This chapter explains the  $F^2MC-8FX$  CPU memory space.

- 2.1 CPU Memory Space

- 2.2 Memory Space and Addressing

## 2.1 CPU Memory Space

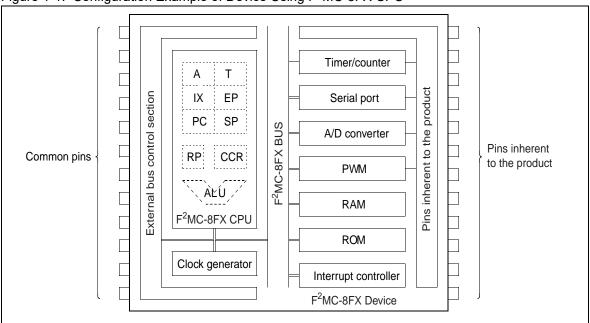

All of the data, program, and I/O areas managed by the  $F^2MC-8FX$  CPU are assigned to the 64 Kbyte memory space of the  $F^2MC-8FX$  CPU. The CPU can access each resource by indicating its address on the 16-bit address bus.

## **CPU Memory Space**

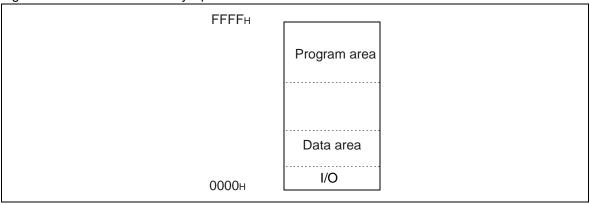

Figure 1-2. shows the address configuration of the F<sup>2</sup>MC-8FX memory space.

The I/O area is located close to the least significant address, and the data area is arranged right above it. The data area can be divided into the register bank, stack and direct areas for each application. In contrast to the I/O area, the program area is located close to the most significant address. The reset, interrupt reset vector and vector call instruction tables are arranged in the highest part.

Figure 1-2. F<sup>2</sup>MC-8FX Memory Space

### 2.2 Memory Space and Addressing

In addressing by the  $F^2MC-8FX$  CPU, the applicable addressing mode related to memory access may change according to the address.

Therefore, the use of the proper addressing mode increases the code efficiency of instructions.

## Memory Space and Addressing

The F<sup>2</sup>MC-8FX CPU has the following addressing modes related to memory access. ([ ] indicates one byte):

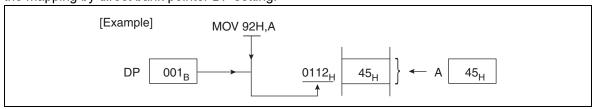

Direct addressing:Specify the lower 8 bits of the address using the operand. The accesses of operand address 00<sub>H</sub> to 7F<sub>H</sub> are always 0000<sub>H</sub> to 007F<sub>H</sub>. The accesses of operand address 80<sub>H</sub> to FF<sub>H</sub> are mapped to 0080<sub>H</sub> to 047F<sub>H</sub> by setting of direct bank pointer (DP).

```

[Structure] [\leftarrow OP code \rightarrow] [\leftarrow lower 8 bits \rightarrow] ([\leftarrow if operand available \rightarrow]

```

■ Extended addressing: Specify all 16 bits using the operand.

```

[Structure] [\leftarrow OP code \rightarrow] [\leftarrow upper 8 bits \rightarrow] [\leftarrow lower 8 bits \rightarrow]

```

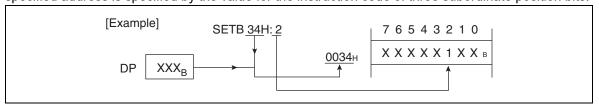

Bit direct addressing: Specify the lower 8 bits of the address using the operand. The accesses of operand address 00<sub>H</sub> to 7F<sub>H</sub> are always 0000<sub>H</sub> to 007F<sub>H</sub>. The accesses of operand address 80<sub>H</sub> to FF<sub>H</sub> are mapped to 0080<sub>H</sub> to 047F<sub>H</sub> by setting of direct bank pointer (DP). The bit positions are included in the OP code.

```

[Structure] [\leftarrow OP code: bit \rightarrow] [\leftarrow lower 8 bits \rightarrow]

```

■ Indexed addressing:Add the 8 bits of the operand to the index register (IX) together with the sign and use the result as the address.

```

[Structure] [\leftarrow OP \text{ code } \rightarrow] [\leftarrow 8 \text{ offset bits } \rightarrow] ([\leftarrow \text{ if operand available } \rightarrow])

```

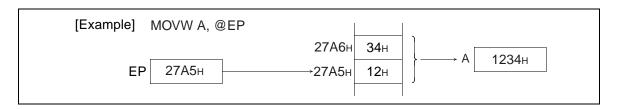

Pointer addressing: Use the contents of the extra pointer (EP) directly as the address.

```

[Structure] [\leftarrow OP code \rightarrow]

```

■ General-purpose register addressing:Specify the general-purpose registers. The register numbers are included in the OP code.

```

[Structure] [\leftarrow OP code: register \rightarrow]

```

■ Immediate addressing:Use one byte following the OP code as data.

```

[Structure] [\leftarrow OP \text{ code } \rightarrow] [\leftarrow Immediate data \rightarrow]

```

Vector addressing:Read the data from a table corresponding to the table number. The table numbers are included in the OP code.

```

[Structure] [\leftarrow OP code: table \rightarrow]

```

■ Relative addressing:Calculate the address relatively to the contents of the current PC. This addressing mode is used during the execution of the relative jump and bit check instructions.

[Structure] [

$$\leftarrow$$

OP code: table  $\rightarrow$ ] [ $\leftarrow$  8 bit relative value  $\rightarrow$ ]

Figure-1-2. shows the memory space accessible by each addressing mode.

#### 2 2 1 Data Area

The F<sup>2</sup>MC-8FX CPU data area can be divided into the following three for each purpose:

- General-purpose register bank area

- Stack area

- Direct area

## **General-Purpose Register Bank Area**

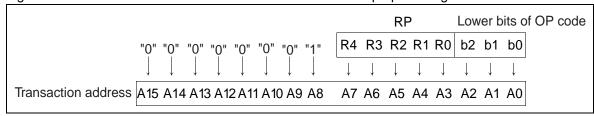

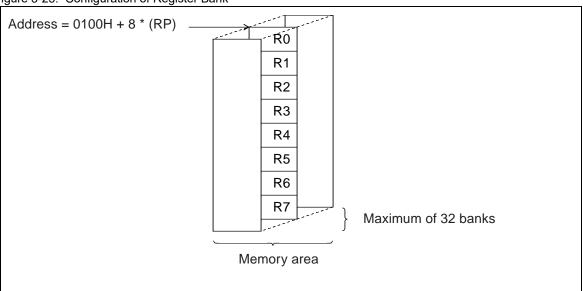

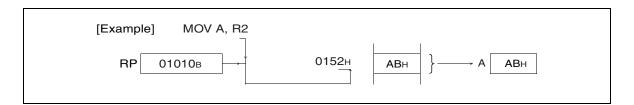

The general-purpose register bank area in the  $F^2MC-8FX$  CPU is assigned to  $0100_H$  to  $01FF_H$ . The general-purpose register numbers are converted to the actual addresses according to the conversion rule shown in Figure 1-4. by using the register bank pointer (RP) and the lower 3 bits of the OP code.

Figure 1-4. Conversion Rule for Actual Addresses of General-purpose Register Bank Area

#### Stack Area

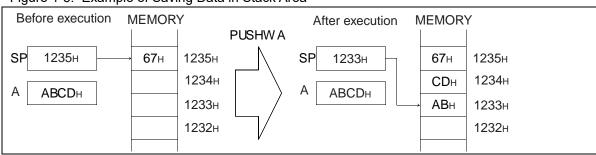

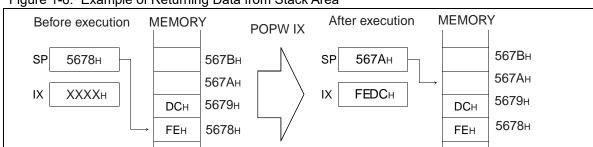

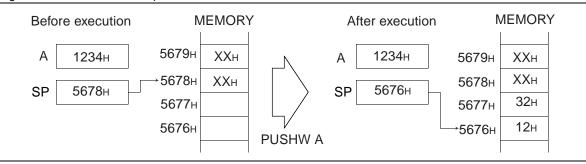

The stack area in the F<sup>2</sup>MC-8FX CPU is used as the saving area for return addresses and dedicated registers when the subroutine call instruction is executed and when an interrupt occurs. Before pushing data into the stack area, decrease the contents of the 16-bit stack pointer (SP) by 2 and then write the data to be saved to the address indicated by the SP. To pop data off the stack area, return data from the address indicated by the SP and then increase the contents of the SP by 2. This shows that the most recently pushed data in the stack is stored at the address indicated by the SP. Figure 1-5. and Figure 1-6. give examples of saving data in the stack area and returning data from it.

Figure 1-5. Example of Saving Data in Stack Area

Figure 1-6. Example of Returning Data from Stack Area

#### **Direct Area**

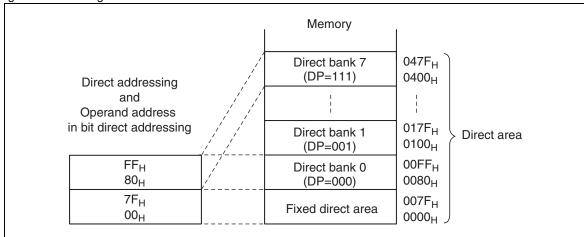

The direct area in the  $F^2MC-8FX$  CPU is located at the lower side of the memory space or the 1152 bytes from  $0000_H$  to  $047F_H$  and is mainly accessed by direct addressing and bit direct addressing. The area that can be used at a time by direct addressing and bit direct addressing is 256 bytes. 128 bytes of  $0000_H$  to  $007F_H$  can be used at any time as a direct area.  $0080_H$  to  $047F_H$  is a direct bank of 128 bytes  $\times$  8 and can use one direct bank as a direct area by setting the direct bank pointer (DP). Conversion from the operand address of direct addressing and bit direct addressing to the real address is done by the conversion rule shown in Table 2-1. by using DP.

Access to it is obtained by the 2-byte instruction.

The I/O control registers and part of RAM that are frequently accessed are arranged in this direct area.

Table 2-1. Conversion Rule for Actual Address of Direct Addressing and Bit Direct Addressing

| Operand address                    | Direct bank pointer (DP) | Actual address                         |

|------------------------------------|--------------------------|----------------------------------------|

| 00 <sub>H</sub> to 7F <sub>H</sub> |                          | 0000 <sub>H</sub> to 007F <sub>H</sub> |

|                                    | 000                      | 0080 <sub>H</sub> to 00FF <sub>H</sub> |

|                                    | 001                      | 0100 <sub>H</sub> to 017F <sub>H</sub> |

|                                    | 010                      | 0180 <sub>H</sub> to 01FF <sub>H</sub> |

| 80 <sub>H</sub> to FF <sub>H</sub> | 011                      | 0200 <sub>H</sub> to 027F <sub>H</sub> |

| оод ютт н                          | 100                      | 0280 <sub>H</sub> to 02FF <sub>H</sub> |

|                                    | 101                      | 0300 <sub>H</sub> to 037F <sub>H</sub> |

|                                    | 110                      | 0380 <sub>H</sub> to 03FF <sub>H</sub> |

|                                    | 111                      | 0400 <sub>H</sub> to 047F <sub>H</sub> |

#### 2.2.2 Program Area

The program area in the F<sup>2</sup>MC-8FX CPU includes the following two:

- Vector call instruction table

- Reset and interrupt vector table

### **Vector Call Instruction Table**

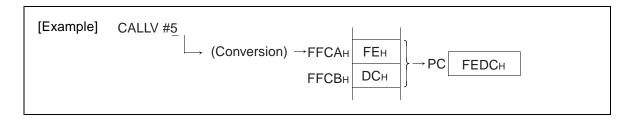

$FFCO_H$  to  $FFCF_H$  of the memory space is used as the vector call instruction table. The vector call instruction for the  $F^2MC-8FX$  CPU provides access to this area according to the vector numbers included in the OP code and makes a subroutine call using the data written there as the jump address. Table 2-2. indicates the correspondence of the vector numbers with the jump address table.

Table 2-2. CALLV Jump Address Table

| CALLV | Jump address table |                   |  |  |  |

|-------|--------------------|-------------------|--|--|--|

| #k    | Upper address      | Lower address     |  |  |  |

| #0    | FFC0 <sub>H</sub>  | FFC1 <sub>H</sub> |  |  |  |

| #1    | FFC2 <sub>H</sub>  | FFC3 <sub>H</sub> |  |  |  |

| #2    | FFC4 <sub>H</sub>  | FFC5 <sub>H</sub> |  |  |  |

| #3    | FFC6 <sub>H</sub>  | FFC7 <sub>H</sub> |  |  |  |

| #4    | FFC8 <sub>H</sub>  | FFC9 <sub>H</sub> |  |  |  |

| #5    | FFCA <sub>H</sub>  | FFCB <sub>H</sub> |  |  |  |

| #6    | FFCC <sub>H</sub>  | FFCD <sub>H</sub> |  |  |  |

| #7    | FFCE <sub>H</sub>  | FFCF <sub>H</sub> |  |  |  |

## **Reset and Interrupt Vector Table**

$FFCC_H$  to  $FFFF_H$  of the memory space is used as the table indicating the starting address of an interrupt or reset Table 2-3. indicates the correspondence between the interrupt numbers or resets and the reference table.

FFFCH: Reserved

Table 2-3. Reset and Interrupt Vector Table

| Interrupt No. | Table address     |                   | Interrupt No. | Table address     |                   |

|---------------|-------------------|-------------------|---------------|-------------------|-------------------|

| interrupt No. | Upper data        | Lower data        | interrupt No. | Upper data        | Lower data        |

| Reset         | FFFE <sub>H</sub> | FFFF <sub>H</sub> | #11           | FFE4 <sub>H</sub> | FFE5 <sub>H</sub> |

| Neset         | FFFC <sub>H</sub> | FFFD <sub>H</sub> | #12           | FFE2 <sub>H</sub> | FFE3 <sub>H</sub> |

| #0            | FFFA <sub>H</sub> | FFFB <sub>H</sub> | #13           | FFE0 <sub>H</sub> | FFE1 <sub>H</sub> |

| #1            | FFF8 <sub>H</sub> | FFF9 <sub>H</sub> | #14           | FFDE <sub>H</sub> | FFDF <sub>H</sub> |

Table 2-3. Reset and Interrupt Vector Table (continued)

| Interrupt No. | Table address     |                   | Interrupt No. | Table address     |                   |

|---------------|-------------------|-------------------|---------------|-------------------|-------------------|

| interrupt No. | Upper data        | Lower data        | interrupt No. | Upper data        | Lower data        |

| #2            | FFF6 <sub>H</sub> | FFF7 <sub>H</sub> | #15           | FFDC <sub>H</sub> | FFDD <sub>H</sub> |

| #3            | FFF4 <sub>H</sub> | FFF5 <sub>H</sub> | #16           | FFDA <sub>H</sub> | FFDB <sub>H</sub> |

| #4            | FFF2 <sub>H</sub> | FFF3 <sub>H</sub> | #17           | FFD8 <sub>H</sub> | FFD9 <sub>H</sub> |

| #5            | FFF0 <sub>H</sub> | FFF1 <sub>H</sub> | #18           | FFD6 <sub>H</sub> | FFD7 <sub>H</sub> |

| #6            | FFFE <sub>H</sub> | FFFF <sub>H</sub> | #19           | FFD4 <sub>H</sub> | FFD5 <sub>H</sub> |

| #7            | FFEC <sub>H</sub> | FFFD <sub>H</sub> | #20           | FFD2 <sub>H</sub> | FFD3 <sub>H</sub> |

| #8            | FFEA <sub>H</sub> | FFFB <sub>H</sub> | #21           | FFD0 <sub>H</sub> | FFD1 <sub>H</sub> |

| #9            | FFE8 <sub>H</sub> | FFF9 <sub>H</sub> | #22           | FFCE <sub>H</sub> | FFCF <sub>H</sub> |

| #10           | FFE6 <sub>H</sub> | FFE7 <sub>H</sub> | #23           | FFCC <sub>H</sub> | FFCD <sub>H</sub> |

FFFD<sub>H</sub>: Mode

Note: The actual number varies according to the product.

Use the interrupt number #22 and #23 exclusively for vector call instruction, CALLV #6 and CALLV #7

## 2.2.3 Arrangement of 16-bit Data in Memory Space

The F<sup>2</sup>MC-8FX CPU can perform 16-bit data transfer and arithmetic operation though it is an 8-bit CPU. Arrangement of 16-bit data in the memory space is shown below.

## **Arrangement of 16-bit Data in Memory Space**

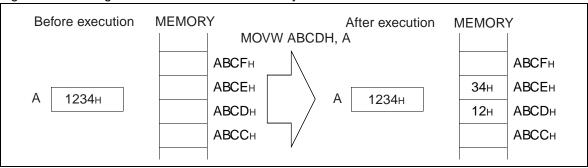

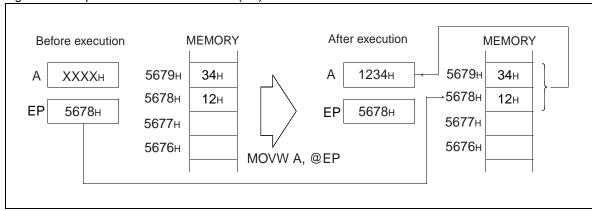

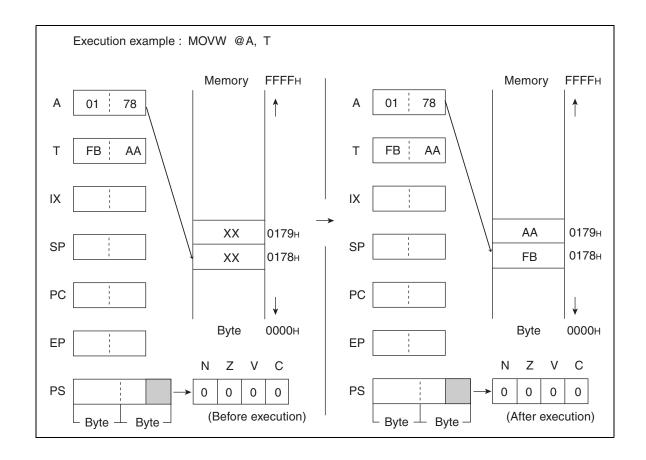

As shown in Figure 1-7., the F<sup>2</sup>MC-8FX CPU treats 16-bit data in the memory as upper data if it is written at the first location having a lower address and as lower data if it is written at the next location after that.

Figure 1-7. Arrangement of 16-bit Data in Memory

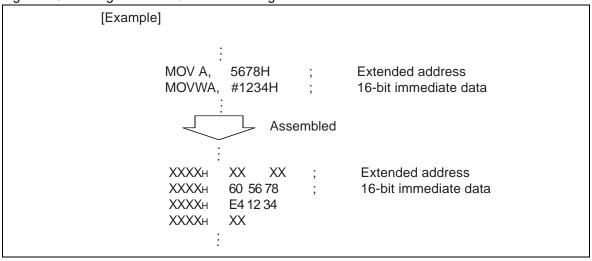

As when 16 bits are specified by the operand during the execution of an instruction, bytes are assumed to be upper and lower in the order of their proximity to the OP code. This applies when the operand indicates the memory address and 16-bit immediate data as shown in Figure 1-8..

Figure 1-8. Arrangement of 16-bit Data during Instruction Execution

The same may also apply to data saved in the stack by interrupts.

# 3. Registers

This chapter explains the F<sup>2</sup>MC-8FX dedicated registers and general-purpose registers.

- 3.1 F<sup>2</sup>MC-8FX Registers

- 3.2 Program Counter (PC) and Stack Pointer (SP)

- 3.3 Accumulator (A) and Temporary Accumulator (T)

- 3.4 Program Status (PS)

- 3.5 Index Register (IX) and Extra Pointer (EP)

- 3.6 Register Banks

- 3.7 Direct Banks

## 3.1 F<sup>2</sup>MC-8FX Registers

In the F<sup>2</sup>MC-8FX series, there are two types of registers: dedicated registers in the CPU, and general-purpose registers in memory.

## F<sup>2</sup>MC-8FX Dedicated Registers

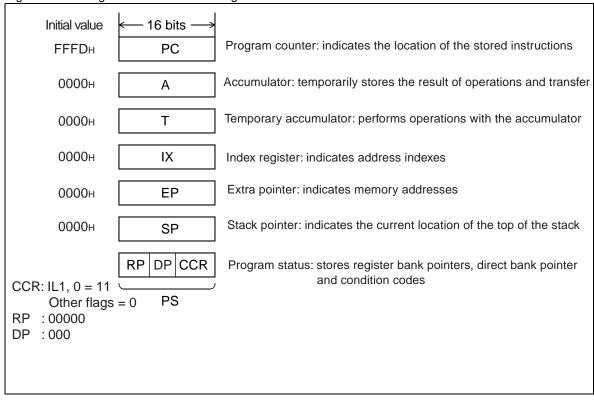

The dedicated register exists in the CPU as a dedicated hardware resource whose application is restricted to the CPU architecture.

The dedicated register is composed of seven types of 16-bit registers. Some of these registers can be operated with only the lower 8 bits.

Figure 3-9. shows the configuration of seven dedicated registers.

Figure 3-9. Configuration of Dedicated Registers

## F<sup>2</sup>MC-8FX General-Purpose Registers

The general-purpose register is as follows:

Register bank: 8-bit length: stores data

## 3.2 Program Counter (PC) and Stack Pointer (SP)

The program counter (PC) and stack pointer (SP) are application-specific registers existing in the CPU.

The program counter (PC) indicates the address of the location at which the instruction currently being executed is stored.

The stack pointer (SP) holds the addresses of the data location to be referenced by the interrupt and stack push/pop instructions. The value of the current stack pointer (SP) indicates the address at which the last data pushed onto the stack is stored.

## **Program Counter (PC)**

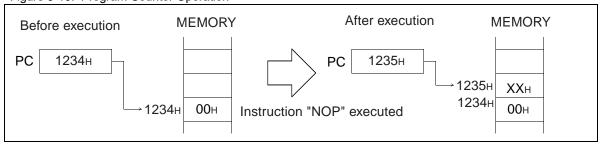

Figure 3-10. shows the operation of the program counter (PC).

Figure 3-10. Program Counter Operation

## **Stack Pointer (SP)**

Figure 3-11. shows the operation of the stack pointer (SP).

Figure 3-11. Stack Pointer Operation

## 3.3 Accumulator (A) and Temporary Accumulator (T)

The accumulator (A) and temporary accumulator (T) are application-specific registers existing in the CPU.

The accumulator (A) is used as the area where the results of operations are temporarily stored.

The temporary accumulator (T) is used as the area where the old data is temporarily saved for data transfer to the accumulator (A) or the operand for operations.

## **Accumulator (A)**

For 16-bit operation all 16 bits are used as shown in Figure 3-12.. For 8-bit operation only the lower 8 bits are used as shown in Figure 3-13..

Figure 3-12. Accumulator (A) Operation (16-bit Operation)

Figure 3-13. Accumulator (A) Operation (8-bit Operation)

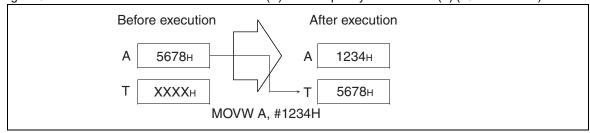

## Temporary Accumulator (T)

When 16-bit data is transferred to the accumulator (A), all the old 16-bit data in the accumulator is transferred to the temporary accumulator (T) as shown in Figure 3-14.. When 8-bit data is transferred to the accumulator, old 8-bit data stored in the lower 8 bits of the accumulator is transferred to the lower 8 bits of the temporary accumulator as shown in Figure 3-15.. Although all 16-bits are used as the operand for 16-bit operations as shown in Figure 3-16., only the lower 8 bits are used for 8-bit operations as shown in Figure 3-17..

Figure 3-14. Data Transfer between Accumulator (A) and Temporary Accumulator (T) (16-bit Transfer)

Figure 3-15. Data Transfer between Accumulator (A) and Temporary Accumulator (T) (8-bit Transfer)

Figure 3-16. Operations between Accumulator (A) and Temporary Accumulator (T) (16-bit Operations)

Figure 3-17. Operations between Accumulator (A) and Temporary Accumulator (T) (8-bit Operations)

#### 3.3.1 How To Use The Temporary Accumulator (T)

The F<sup>2</sup>MC-8FX CPU has a special-purpose register called a temporary accumulator. This section described the operation of this register.

### **How to Use the Temporary Accumulator (T)**

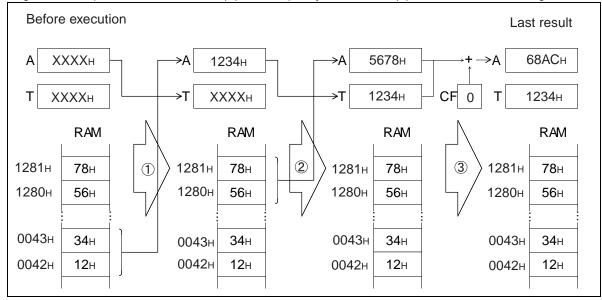

The  $F^2MC-8FX$  CPU has various binary operation instructions, some data transfer instructions and the temporary accumulator (T) for 16-bit data operation. Although there is no instruction for direct data transfer to the temporary accumulator, the value of the original accumulator is transferred to the temporary accumulator before executing the instruction for data transfer to the accumulator. Therefore, to perform operations between the accumulator and temporary accumulator, execute operations after carrying out the instruction for data transfer to the accumulator twice. Since data is not automatically transferred by all instructions to the temporary accumulator, see the columns of TL and TH in the instruction list for details of actual data transfer instructions. An example of addition with carry of 16-bit data stored at addresses 1280<sub>H</sub> and 0042<sub>H</sub> is shown below.

MOVW A, 0042H - ①

MOVW A, 1280H - ②

ADDCW A - ③

Figure 3-18. shows the operation for the accumulator and temporary accumulator when the above example is executed.

Figure 3-18. Operation of Accumulator (A) and Temporary Accumulator (T) in Word Data Processing

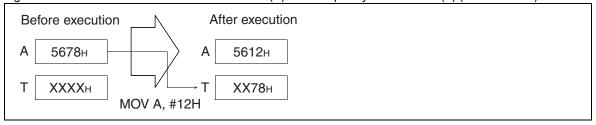

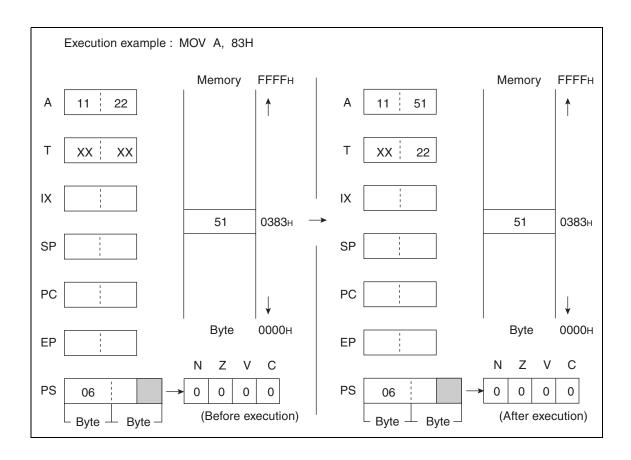

# 3.3.2 Byte Data Transfer and Operation of Accumulator (A) and Temporary Accumulator (T)

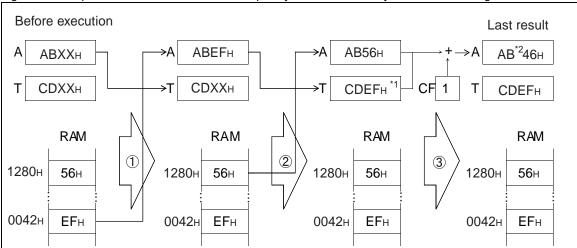

When data transfer to the accumulator (A) is performed byte-by-byte, the transfer data is stored in the AL. Automatic data transfer to the temporary accumulator (T) is also performed byte-by-byte and only the contents of the original AL are stored in the TL. Neither the upper 8 bits of the accumulator nor the temporary accumulator are affected by the transfer. Only the lower 8 bits are used for byte operation between the accumulator and temporary accumulator. None of the upper 8 bits of the accumulator or temporary accumulator are affected by the operation.

# Example of Operation of Accumulator (A) and Temporary Accumulator (T) in Byte Data Processing

An example of addition with carry of 8-bit data stored at addresses  $1280_{\rm H}$  and  $0042_{\rm H}$  is shown below.

MOV A, 0042H - ①

MOV A, 1280H - ②

ADDC A - ③

Figure 3-19. shows the operation of the accumulator and temporary accumulator when the above example is executed.

Figure 3-19. Operation of Accumulator and Temporary Accumulator in Byte Data Processing

<sup>\*1</sup> The TH does not change when there is automatic data transfer to the temporary accumulator.

<sup>\*2</sup> The AH is not changed by the result of the addition of the AL, TL, and CF.

## **Direct Data Transfer from Temporary Accumulator (T)**

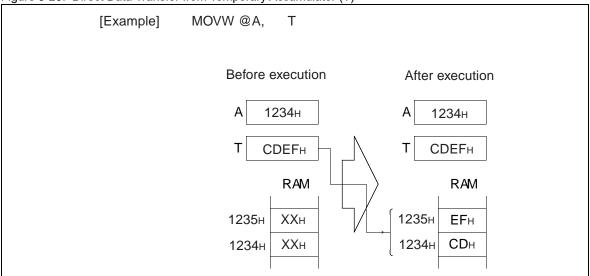

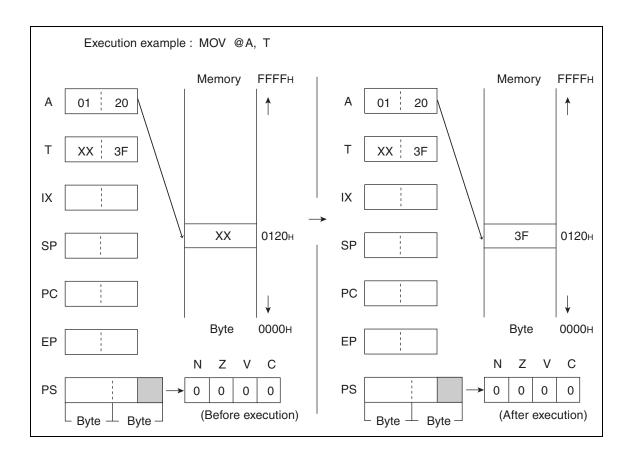

The temporary accumulator (T) is basically temporary storage for the accumulator (A). Therefore, data from the temporary accumulator cannot be transferred directly to memory. However, as an exception, using the accumulator as a pointer enabling saving of the contents of the temporary accumulator in memory. An example of this case is shown below.

Figure 3-20. Direct Data Transfer from Temporary Accumulator (T)

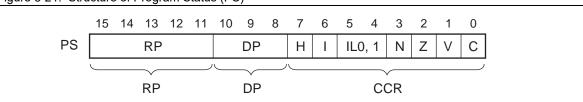

## 3.4 Program Status (PS)

The program status (PS) is a 16-bit application-specific register existing in the CPU. In upper byte of program status (PS), the upper 5-bit is the register bank pointer (RP) and lower 3-bit is the direct bank pointer (DP). The lower byte of program status (PS) is the condition code register (CCR). The upper byte of program status (PS), i.e. RP and DP, is mapped to address 0078<sub>H</sub>. So it is possible to make read and write accesses to them by an access to address 0078<sub>H</sub>.

## **Structure of Program Status (PS)**

Figure 3-21. shows the structure of the program status.

The register bank pointer (RP) indicates the address of the register bank currently in use. The relationship between the contents of the register bank pointer and actual addresses is as shown in Figure 3-22..

DP shows the memory area (direct bank) used for direct addressing and bit direct addressing. Conversion from the operand address of direct addressing and bit direct addressing to the real address follows the conversion rule shown in Table 3-4. by using DP.

The condition code register (CCR) has bits for indicating the result of operations and the content of transfer data and bits for controlling the operation of the CPU in the event of an interrupt.

Figure 3-21. Structure of Program Status (PS)

Figure 3-22. Conversion Rule for Actual Address of General-purpose Register Area

Table 3-4. Conversion Rule for Actual Address of Direct Addressing and Bit Direct Addressing

| Operand address                    | Direct bank pointer (DP) | Actual address                         |

|------------------------------------|--------------------------|----------------------------------------|

| 00 <sub>H</sub> to 7F <sub>H</sub> |                          | 0000 <sub>H</sub> to 007F <sub>H</sub> |

|                                    | 000                      | 0080 <sub>H</sub> to 00FF <sub>H</sub> |

|                                    | 001                      | 0100 <sub>H</sub> to 017F <sub>H</sub> |

|                                    | 010                      | 0180 <sub>H</sub> to 01FF <sub>H</sub> |

| 80 <sub>H</sub> to FF <sub>H</sub> | 011                      | 0200 <sub>H</sub> to 027F <sub>H</sub> |

| OOH TO TT H                        | 100                      | 0280 <sub>H</sub> to 02FF <sub>H</sub> |

|                                    | 101                      | 0300 <sub>H</sub> to 037F <sub>H</sub> |

|                                    | 110                      | 0380 <sub>H</sub> to 03FF <sub>H</sub> |

|                                    | 111                      | 0400 <sub>H</sub> to 047F <sub>H</sub> |

## **Program Status (PS) Flags**

The program status flags are explained below.

## H flag

This flag is 1 if a carry from bit 3 to bit 4 or a borrow from bit 4 to bit 3 is generated as the result of an operation, and it is 0 in other cases. Because it is used for decimal compensation instructions, it cannot be guaranteed if it is used for applications other than addition or subtraction.

## I flag

An interrupt is enabled when this flag is 1 and is disabled when it is 0. It is set to 0 at reset which results in the interrupt disabled state.

## IL1, IL0

These bits indicate the level of the currently-enabled interrupt. The interrupt is processed only when an interrupt request with a value less than that indicated by these bits is issued.

| IL1 | IL0 | Interrupt level | High and low |

|-----|-----|-----------------|--------------|

| 0   | 0   | 0               | Highest      |

| 0   | 1   | 1               | <b>†</b>     |

| 1   | 0   | 2               | $\downarrow$ |

| 1   | 1   | 3               | Lowest       |

## N flag

This flag is 1 when the most significant bit is 1 and is 0 when it is 0 as the result of an operation.

## Z flag

This flag is 1 when the most significant bit is 0 and is 0 in other cases as the result of an operation.

### V flag

This flag is 1 when a two's complement overflow occurs and is 0 when one does not as the result of an operation.

## C flag

This flag is 1 when a carry or a borrow, from bit 7 in byte mode and from bit 15 in word mode, is generated as the result of an operation but 0 in other cases. The shifted-out value is provided by the shift instruction.

## Access to Register Bank Pointer and Direct Bank Pointer

The upper byte of program status (PS), i.e. register bank pointer (RP) and direct bank pointer (DP), is mapped to address  $0078_{\rm H}$ . So it is possible to make read and write accesses to them by an access to address  $0078_{\rm H}$ , besides using instructions that have access to PS (MOVW A, PS or MOVW PS, A).

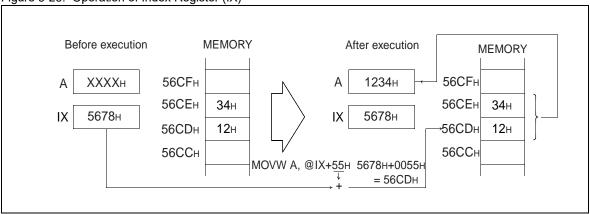

## 3.5 Index Register (IX) and Extra Pointer (EP)

The index register (IX) and extra pointer (EP) are 16-bit application-specific registers existing in the CPU.

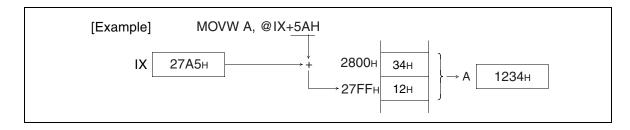

The index register (IX) adds an 8-bit offset value with its sign to generate the address stored by the operand.

The extra pointer (EP) indicates the address stored by the operand.

## Index Register (IX)

Figure 3-23. indicates the operation of the index register.

Figure 3-23. Operation of Index Register (IX)

## **Extra Pointer (EP)**

Figure 3-24. shows the operation of the extra pointer.

Figure 3-24. Operation of the Extra Pointer (EP)

## 3.6 Register Banks

The register bank register is an 8-bit general-purpose register existing in memory. There are eight registers per bank of which there can be 32 altogether. The current bank is indicated by the register bank pointer (RP).

## **Register Bank Register**

Figure 3-25. shows the configuration of the register bank.

Figure 3-25. Configuration of Register Bank

#### 3.7 Direct Banks

The direct bank is in  $0080_H$  to  $047F_H$  of direct area, and composed of 128 bytes  $\times$  8 banks. The access that uses direct addressing and bit direct addressing in operand address  $80_H$  to  $FF_H$  can be extended to 8 direct banks according to the value of the direct bank pointer (DP). The current bank is indicated by the direct bank pointer (DP).

#### **Direct Bank**

Figure 3-26. shows the configuration of a direct bank.

The access that uses direct addressing and bit direct addressing in operand address  $80_H$  to FF<sub>H</sub> can be extended to 8 direct banks according to the value of the direct bank pointer (DP). The access that uses direct addressing and bit direct addressing in operand address  $00_H$  to  $7F_H$  is not affected by the value of the direct bank pointer (DP). This access is directed to fixed direct area  $0000_H$  to  $007F_H$ .

Figure 3-26. Configuration of Direct Bank

# 4. Interrupt Processing

This chapter explains the functions and operation of F<sup>2</sup>MC-8FX interrupt processing.

- 4.1 Outline of Interrupt Operation

- 4.2 Interrupt Enable/Disable and Interrupt Priority Functions

- 4.3 Creating an Interrupt Processing Program

- 4.4 Multiple Interrupt

- 4.5 Reset Operation

## 4.1 Outline of Interrupt Operation

F<sup>2</sup>MC-8FX series interrupts have the following features:

- □ Four interrupt priority levels

- All maskable features

- Vector jump feature by which the program jumps to address mentioned in the interrupt vector.

## **Outline of Interrupt Operation**

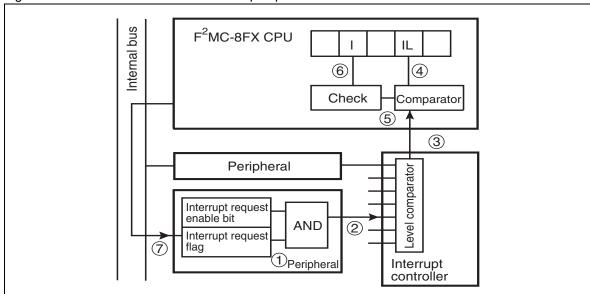

In the F<sup>2</sup>MC-8FX series, interrupts are transferred and processed according to the following procedure:

- 1. An interrupt source occurs in resources.

- 2. Refer to interrupt enable bits in resources. If an interrupt is enabled, interrupt requests are issued from resources to the interrupt controller.

- As soon as an interrupt request is received, the interrupt controller decides the priorities of the interrupt requested and then transfers the interrupt level corresponding to the interrupts applicable to the CPU.

- 4. The CPU compares the interrupt levels requested by the interrupt controller with the IL bit in the program status register.

- 5. In the comparison, the CPU checks the contents of the I flag in the same program status register only if the priority is higher than the current interrupt processing level.

- 6. In the check in 5., the CPU sets the contents of the IL bit to the requested level only if the I flag is enabled for interrupts, processes interrupts as soon as the instruction currently being executed is completed and then transfers control to the interrupt processing routine.

- 7. The CPU clears the interrupt source caused in 1. using software in the user's interrupt processing routine to terminate the processing of interrupts.

Figure 4-27. shows the flow diagram of F<sup>2</sup>MC-8FX interrupt operation.

Figure 4-27. Outline of F<sup>2</sup>MC-8FX Interrupt Operation

## 4.2 Interrupt Enable/Disable and Interrupt Priority Functions

In the F<sup>2</sup>MC-8FX series, interrupt requests are transferred to the CPU using the three types of enable/disable functions listed below.

- Request enable check by interrupt enable flags in resources

- Checking the level using the interrupt level determination function

- Interrupt start check by the I flag in the CPU

Interrupts generated in resources are transferred to the CPU with the priority levels determined by the interrupt priority function.

## Interrupt Enable/Disable Functions

- Request enable check by interrupt enable flags in resources

- This is a function to enable/disable a request at the interrupt source. If interrupt enable flags in resources are enabled, interrupt request signals are sent from resources to the interrupt controller. This function is used for controlling the presence or absence of an interrupt, resource-by-resource. It is very useful because when software is described for each resource operation, interrupts in another resource do not need to be checked for whether they are enabled or disabled.

- Checking the level using the interrupt level determination function

- ☐ This function determines the interrupt level. The interrupt levels corresponding to interrupts generated in resources are compared with the IL bit in the CPU. If the value is less than the IL bit, a decision is made to issue an interrupt request. This function is able to assign priorities if there are two or more interrupts.

- Interrupt start check by the I flag in the CPU

- ☐ The I flag enables or disables the entire interrupt. If an interrupt request is issued and the I flag in the CPU is set to interrupt enable, the CPU temporarily suspends the flow of instruction execution to process interrupts. This function is able to temporarily disable the entire interrupt.

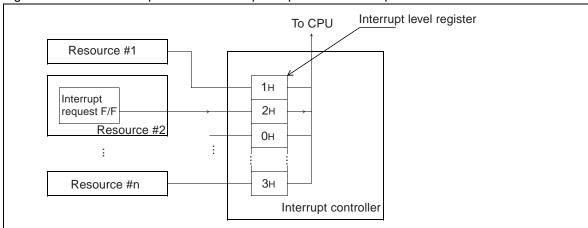

## Interrupt Requests in Resources

As shown in Figure 4-28., interrupts generated in resources are converted by the corresponding interrupt level registers in the interrupt controller into the values set by software and then transferred to the CPU.

The interrupt level is defined as high if its numerical value is lower, and low if it is higher.

Figure 4-28. Relationship between Interrupt Request and Interrupt Level in Resources

## 4.3 Creating an Interrupt Processing Program

In the  $F^2MC$ -8FX series, basically, interrupt requests from resources are issued by hardware and cleared by software.

## Creating an Interrupt Processing Program

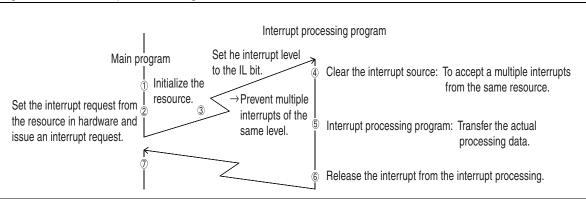

The interrupt processing control flow is as follows:

- 1. Initialize resources before operation.

- 2. Wait until an interrupt occurs.

- 3. In the event of an interrupt, if the interrupt can be accepted, perform interrupt processing to branch to the interrupt processing routine.

- 4. First, set software so as to clear the interrupt source at the beginning of the interrupt processing routine. This is done so that the resource causing an interrupt can regenerate the interrupt during the interrupt processing program.

- 5. Next, perform interrupt processing to transfer the necessary data.

- 6. Use the interrupt release instruction to release the interrupt from interrupt processing.

- 7. Then, continue to execute the main program until an interrupt recurs. The typical interrupt processing flow is shown in Figure 4-29..

The numbers in the figure correspond to the numbers above.

Figure 4-29. Interrupt Processing Flow

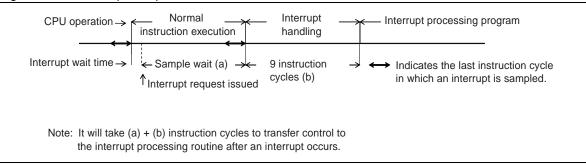

The time to transfer control to the interrupt processing routine after the occurrence of an interrupt 3 in Figure 4-29.) is 9 instruction cycles. An interrupt can only be processed in the last cycle of each instruction. The time shown in Figure 4-30. is required to transfer control to the interrupt processing routine after an interrupt occurs.

The longest cycle (17 + 9 = 26 instruction cycles) is required when an interrupt request is issued immediately after starting the execution of the DIVU instruction.

Figure 4-30. Interrupt Response Time

### 4.4 Multiple Interrupt

The F<sup>2</sup>MC-8FX CPU can have a maximum of four levels as maskable interrupts. These can be used to assign priorities to interrupts from resources.

### **Multiple Interrupt**

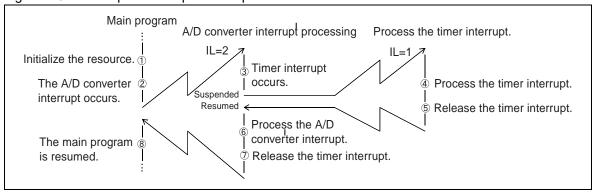

A specific example is given below.

When giving priority over the A/D converter to the timer interrupt

| START | MOV  | ADIL, | #2 | Set the interrupt level of the A/D converter to 2.                                                |

|-------|------|-------|----|---------------------------------------------------------------------------------------------------|

|       | MOV  | TMIL, | #1 | Set the interrupt level of the timer to 1. ADIL and TMIL are IL bits in the interrupt controller. |

|       | CALL | STAD  |    | Start the A/D converter.                                                                          |

|       | CALL | STTM  |    | Start the timer.                                                                                  |

|       |      |       |    |                                                                                                   |

|       | •    |       |    |                                                                                                   |

|       |      |       |    |                                                                                                   |

When the above program is started, interrupts are generated from the A/D converter and timer after an elapsed time. In this case, when the timer interrupt occurs while processing the A/D converter interrupt, it will be processed through the sequence shown in Figure 4-31..

Figure 4-31. Example of Multiple Interrupt

When starting processing of an A/D converter interrupt, the IL bit in the PS register of the CPU is automatically the same as the value of request (2 here). Therefore, when a level 1 or 0 interrupt request is issued during the processing of an A/D converter interrupt, the processing proceeds without disabling the A/D converter interrupt request. When temporarily disabling interrupts lower in priority than this interrupt during A/D converter interrupt processing, disable the I flag in the PS register of the CPU for the interrupts or set the IL bit to 0.

When control is returned to the interrupted routine by the release instruction after completion of each interrupt processing routine, the PS register is set to the value saved in the stack. Consequently, the IL bit takes on the value before interruption.

For actual coding, refer to the Hardware Manual for each device to check the addresses of the interrupt controller and each resource and the interrupts to be supported.

### 4.5 Reset Operation

In the  $F^2MC$ -8FX series, when a reset occurs, the flag of program status is 0 and the IL bit is set to 11. When cleared, the reset operation is executed from the starting address written to set vectors (FFFE<sub>H</sub>, FFFF<sub>H</sub>).

### **Reset Operation**

#### A reset affects:

- Accumulator, temporary accumulator: Initializes to 0000<sub>H</sub>

- ☐ Stack pointer: Initializes to 0000<sub>H</sub>

- Extra pointer, index register: Initializes to 0000<sub>H</sub>

- Program status: Sets flag to 0, sets IL bit to 11, sets RP bit to 00000 and Initializes DP bit to 000

- □ Program counter: Reset vector values

- □ RAM (including general-purpose registers): Keeps value before reset

- □ Resources: Basically stop

- Others: Refer to the manual for each product for the condition of each pin

- Refer to the manual for each product for details of the value and operation of each register for special reset conditions.

## 5. CPU Software Architecture

This chapter explains the instructions for the  $F^2MC-8FX\ CPU$ .

- 5.1 Types of Addressing Modes

- 5.2 Special Instructions

### 5.1 Types of Addressing Modes

The F<sup>2</sup>MC-8FX CPU has the following ten addressing modes:

- Direct addressing (dir)

- Extended addressing (ext)

- Bit direct addressing (dir:b)

- □ Indexed addressing (@IX+off)

- Pointer addressing (@EP)

- General-purpose register addressing (Ri)

- Immediate addressing (#imm)

- Vector addressing (#k)

- Relative addressing (rel)

- Inherent addressing

### **Direct Addressing (dir)**

This addressing mode, indicated as "dir" in the instruction list, is used to access the direct area from  $0000_H$  to  $047F_H$ . In this addressing, when the operand address is  $00_H$  to  $7F_H$ , it accesses  $0000_H$  to  $007F_H$ . Moreover, when the operand address is  $80_H$  to  $FF_H$ , the access is good to  $0080_H$  to  $047F_H$  at the mapping by direct bank pointer DP setting.

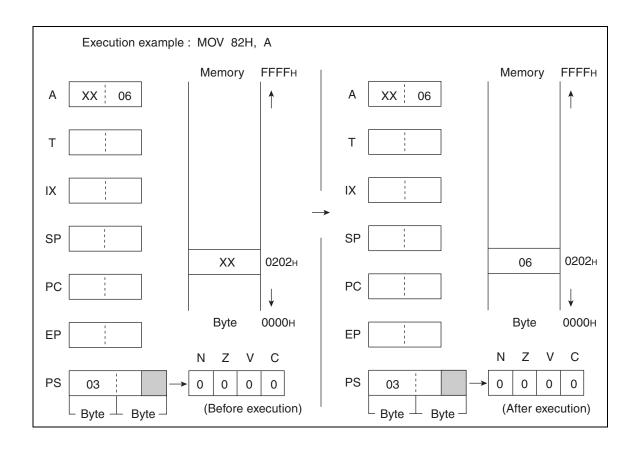

### **Extended Addressing (ext)**

This addressing mode, indicated as "ext" in the instruction list, is used to access the entire 64-Kbyte area. In this addressing mode, the upper byte is specified by the first operand and the lower byte by the second operand.

### Bit Direct Addressing (dir:b)

This addressing mode, indicated as "dir:b" in the instruction list, is used for bit-by-bit access of the direct area from  $0000_{\rm H}$  to  $047F_{\rm H}$ . In this addressing, when the operand address is  $00_{\rm H}$  to  $7F_{\rm H}$ , it accesses  $0000_{\rm H}$  to  $007F_{\rm H}$ . Moreover, when the operand address is  $80_{\rm H}$  to  $FF_{\rm H}$ , the access is good to  $0080_{\rm H}$  to  $047F_{\rm H}$  at the mapping by direct bank pointer DP setting. The position of the bit in the specified address is specified by the value for the instruction code of three subordinate position bits.

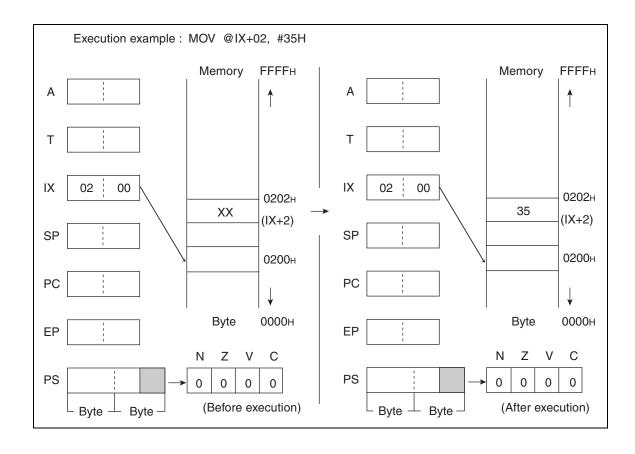

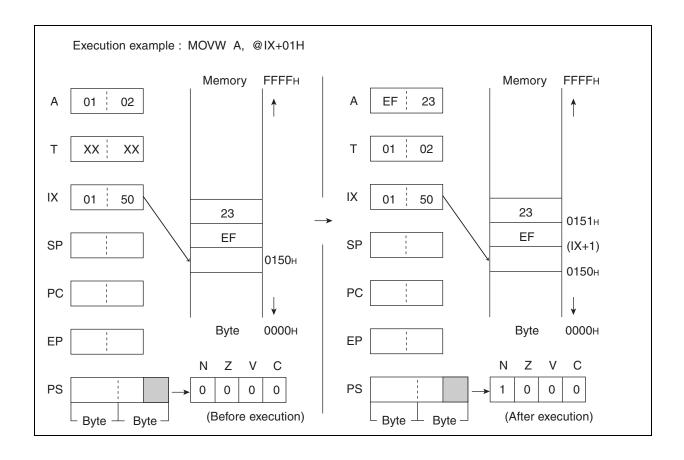

### Index Addressing (@IX+off)

This addressing mode, indicated as "@IX+off" in the instruction list, is used to access the entire 64-Kbyte area. In this addressing mode, the contents of the first operand are sign-extended and then added to the index register (IX). The result is used as the address.

### Pointer Addressing (@EP)

This addressing mode, indicated as "@EP" in the instruction list, is used to access the entire 64-Kbyte area. In this addressing mode, the contents of the extra pointer (EP) are used as the address.

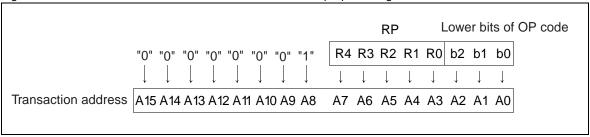

### General-Purpose Register Addressing (Ri)

This addressing mode, indicated as "Ri" in the instruction list, is used to access the register bank area. In this addressing mode, one upper byte of the address is set to 01 and one lower byte is created from the contents of the register bank pointer (RP) and the 3 lower bits of the instruction to access this address.

### Immediate Addressing (#imm)

This addressing mode, indicated as "#imm" in the instruction list, is used for acquiring the immediate data. In this addressing mode, the operand is used directly as the immediate data. The byte or word is specified by the instruction code.

```

[Example] MOV A, #56H A S6H

```

### **Vector Addressing (#k)**

This addressing mode, indicated as "#k" in the instruction list, is used for branching to the subroutine address registered in the table. In this addressing mode, the information about #k is contained in the instruction code and the table addresses listed in Table 5-5. are created.

Table 5-5. Jump Address Table

| #k | Address table (upper jump address: lower jump address) |

|----|--------------------------------------------------------|

| 0  | FFC0 <sub>H</sub> :FFC1 <sub>H</sub>                   |

| 1  | FFC2 <sub>H</sub> :FFC3 <sub>H</sub>                   |

| 2  | FFC4 <sub>H</sub> :FFC5 <sub>H</sub>                   |

| 3  | FFC6 <sub>H</sub> :FFC7 <sub>H</sub>                   |

| 4  | FFC8 <sub>H</sub> :FFC9 <sub>H</sub>                   |

| 5  | FFCA <sub>H</sub> :FFCB <sub>H</sub>                   |

| 6  | FFCC <sub>H</sub> :FFCD <sub>H</sub>                   |

| 7  | FFCE <sub>H</sub> :FFCF <sub>H</sub>                   |

### **Relative Addressing (rel)**

This addressing mode, indicated as "rel" in the instruction list, is used for branching to the 128-byte area across the program counter (PC). In this addressing mode, the contents of the operand are added with their sign, to the program counter. The result is stored in the program counter.

In this example, the program jumps to the address where the instruction code BNE is stored, resulting in an infinite loop.

### **Inherent Addressing**

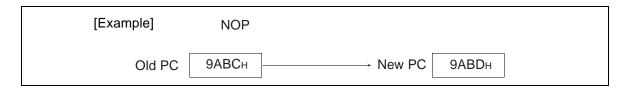

This addressing mode, which has no operand in the instruction list, is used for operations to be determined by the instruction code. In this addressing mode, the operation varies for every instruction.

### 5.2 Special Instructions

In the F<sup>2</sup>MC-8FX series, the following six special instructions are available:

- □ JMP @A

- MOVW A, PC

- □ MULU A

- DIVU A

- □ XCHW A, PC

- □ CALLV #k

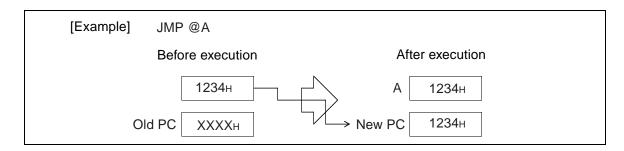

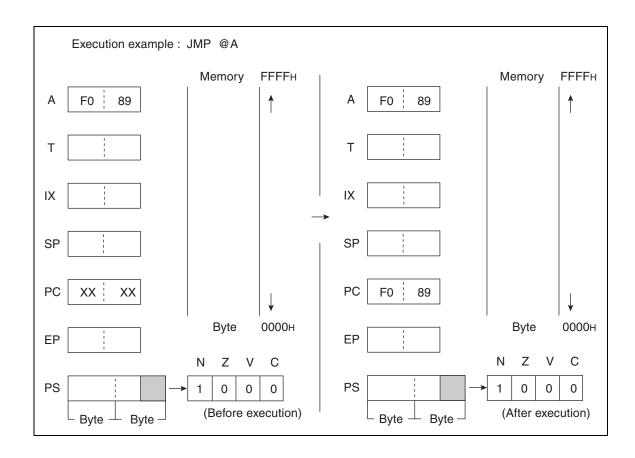

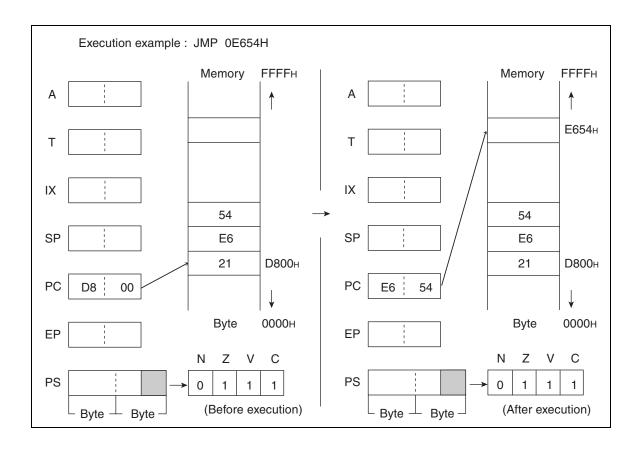

### JMP @A

This instruction is used for branching to an address where the contents of the accumulator (A) are used. The contents of one of the N jump addresses arranged in table form is selected and transferred to the accumulator. Executing this instruction enables the N-branch processing.

### **MOVW A, PC**

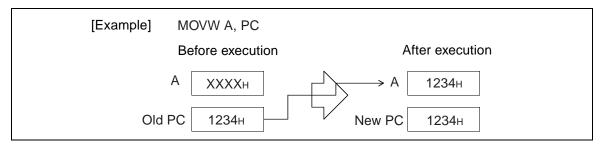

This instruction is used for performing the opposite operation to JMP @A. In other words, it stores, the contents of the program counter (PC) in the accumulator (A). When this instruction is executed in the main routine and a specific subroutine is to be called, make sure that the contents of the accumulator are the specified value in the subroutine, that is the branch is from the expected section, enabling a decision on crash.

When this instruction is executed, the contents of the accumulator are the same as those of the address where the code for the next instruction is stored and not the address where the code for this instruction is stored. The above example shows that the value 1234<sub>H</sub> stored in the accumulator agrees with that of the address where the instruction code next to MOVW A, PC is stored.

#### **MULU A**

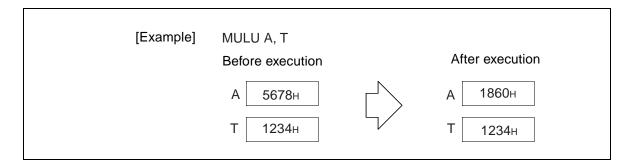

This instruction is used for multiplying 8 bits of the AL by 8 bits of the TL without a sign and stores the 16-bit result in the accumulator (A). The contents of the temporary accumulator (T) do not change. In the operation, the original contents of the AH and TH are not used. Since the flag does not change, attention must be paid to the result of multiplication when branching accordingly.

#### **DIVU A**

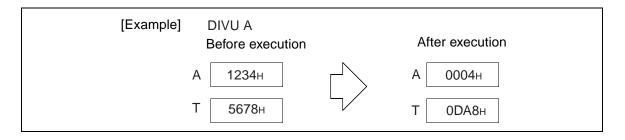

This instruction is used for dividing 16 bits of the temporary accumulator (T) by 16 bits of the A without a sign and stores the results as 16 bits in the A and the remainder as 16 bits in the T. When A is 0000<sub>H</sub>, Z flag is 1 as 0 division. At this time, the operation result is not guaranteed.

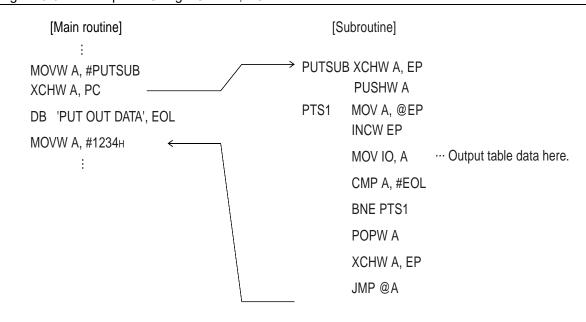

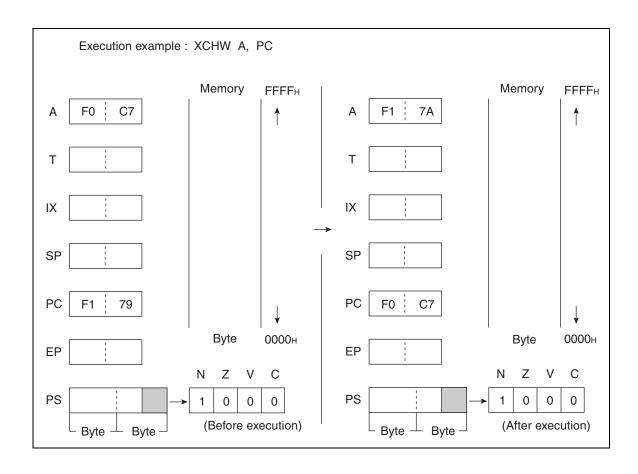

#### XCHW A, PC

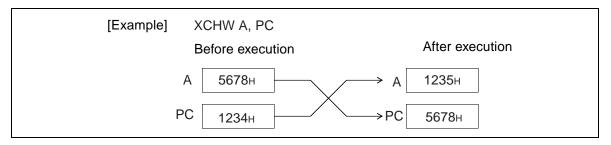

This instruction is used for exchanging the contents of the accumulator (A) for those of the program counter (PC). As a result, the program branches to the address indicated by the contents of the original accumulator and the contents of the current accumulator become the value of the address next to the one where the instruction code XCHW A, PC is stored. This instruction is provided especially for specifying tables using the main routine and for subroutines to use them.

When this instruction is executed, the contents of the accumulator are the same as those of the address where the code for the next instruction is stored and not the address where the code for this

instruction is stored. The above example shows that the value of the accumulator  $1235_{\rm H}$  agrees with that of the address where the instruction code next to XCHW A, PC is stored. Consequently,  $1235_{\rm H}$  not  $1234_{\rm H}$  is indicated.

Figure 5-32. Example of Using XCHW A, PC

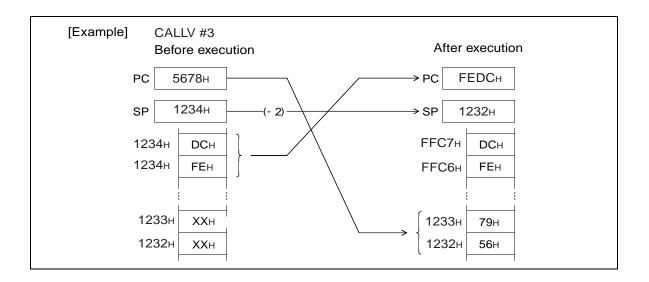

#### **CALLV #k**

This instruction is used for branching to a subroutine address registered in the table. In this addressing mode, the information about #k is included in the instruction code and the tale addresses listed in Table 5-6. are created. After saving the contents of the current program counter (PC) in the stack, the program branches to the address in the table. Because it is a 1-byte instruction, using it for frequently-used subroutines reduces the size of the entire program.

Table 5-6. Jump Address Table

| #k | Address table (upper jump address : lower jump address) |

|----|---------------------------------------------------------|

| 0  | FFC0 <sub>H</sub> :FFC1 <sub>H</sub>                    |

| 1  | FFC2 <sub>H</sub> :FFC3 <sub>H</sub>                    |

| 2  | FFC4 <sub>H</sub> :FFC5 <sub>H</sub>                    |

| 3  | FFC6 <sub>H</sub> :FFC7 <sub>H</sub>                    |

| 4  | FFC8 <sub>H</sub> :FFC9 <sub>H</sub>                    |

| 5  | FFCA <sub>H</sub> :FFCB <sub>H</sub>                    |

| 6  | FFCC <sub>H</sub> :FFCD <sub>H</sub>                    |

| 7  | FFCE <sub>H</sub> :FFCF <sub>H</sub>                    |

## 6. Detailed Rules For Execution Instructions

This chapter explains each execution instruction, used in the assembler, in reference format.

All execution insurrections are described in alphabetical order.

For information about the outline of each item and the meaning of symbols (abbreviations) explained for each execution instruction, see "5. CPU Software Architecture"

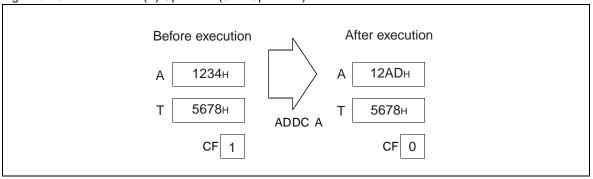

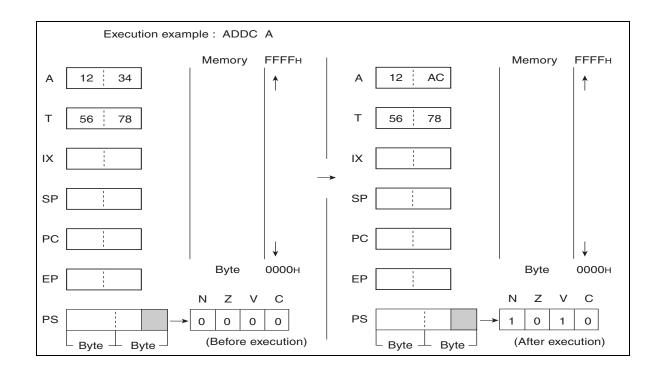

# 6.1 ADDC (ADD Byte Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

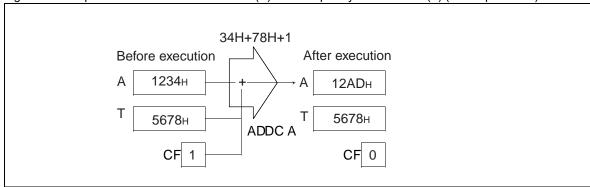

Add the byte data of TL to that of AL, add a carry to the LSB and then return the results to AL. The contents of AH are not changed.

# ADDC (ADD Byte Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

Operation

$(AL) \leftarrow (AL) + (TL) + (C)$  (Byte addition with carry)

Assembler format

ADDC A

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | + | + |

- +: Changed by executing instruction

- -: Not changed

- N: Set to 1 if the MSB of AL is 1 as the result of operation and set to 0 in other cases.

- Z: Set to 1 if the result of operation is 00<sub>H</sub> and set to 0 in other cases.

- V: Set to 1 if an overflow occurs as the result of operation and set to 0 in other cases.

- C: Set to 1 if a carry occurs as the result of operation and set to 0 in other cases.

Number of execution cycle: 1

Byte count: 1 OP code: 22

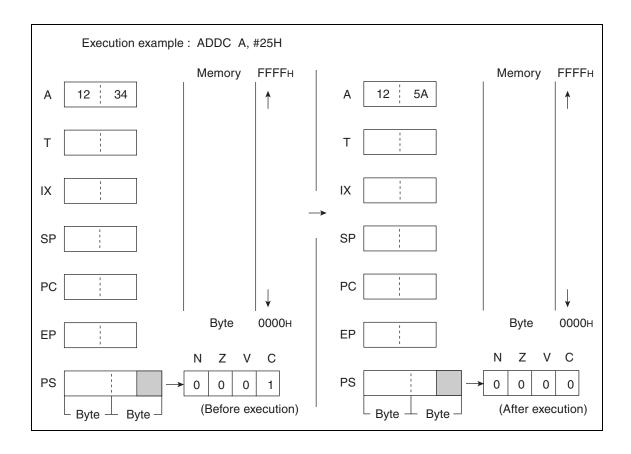

# 6.2 ADDC (ADD Byte Data of Accumulator and Memory with Carry to Accumulator)

Add the byte data of EA memory (memory expressed in each type of addressing) to that of AL, add a carry to the LSB and then return the results to AL. The contents of AH are not changed.

# ADDC (ADD Byte Data of Accumulator and Memory with Carry to Accumulator)

Operation

$(AL) \leftarrow (AL) + (EA) + (C)$  (Byte addition with carry)

Assembler format

ADDC A, EA

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | + | + |

- +: Changed by executing instruction

- -: Not changed

- N: Set to 1 if the MSB of AL is 1 as the result of operation and set to 0 in other cases.

- Z: Set to 1 if the result of operation is 00<sub>H</sub> and set to 0 in other cases.

- V: Set to 1 if an overflow occurs as the result of operation and set to 0 in other cases.

- C: Set to 1 if a carry occurs as the result of operation and set to 0 in other cases.

Table 6-7. Number of Execution Cycles / Byte Count / OP Code

| EA                         | #d8 | dir | @IX+off | @EP | Ri       |

|----------------------------|-----|-----|---------|-----|----------|

| Number of execution cycles | 2   | 3   | 3       | 2   | 2        |

| Byte count                 | 2   | 2   | 2       | 1   | 1        |

| OP code                    | 24  | 25  | 26      | 27  | 28 to 2F |

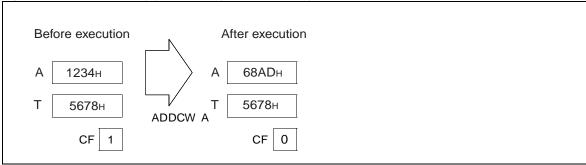

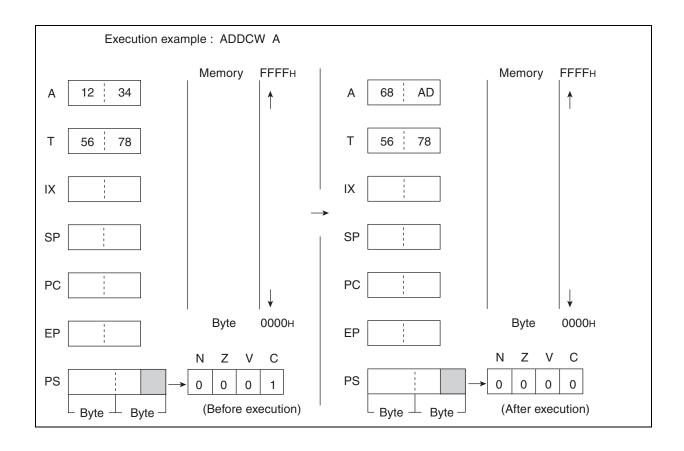

# 6.3 ADDCW (ADD Word Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

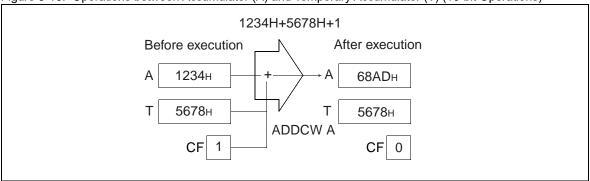

Add the word data of T to that of A, add a carry to the LSB and then return the results to A.

# ADDCW (ADD Word Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

Operation

$(A) \leftarrow (A) + (T) + (C)$  (Word addition with carry)

Assembler format

ADDCW A

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | + | + |

- +: Changed by executing instruction

- -: Not changed

- N: Set to 1 if the MSB of A is 1 as the result of operation and set to 0 in other cases.

- Z: Set to 1 if the result of operation is 0000<sub>H</sub> and set to 0 in other cases.

- V: Set to 1 if an overflow occurs as the result of operation and set to 0 in other cases.

- C: Set to 1 if a carry occurs as the result of operation and set to 0 in other cases.

Number of execution cycle: 1

Byte count: 1 OP code: 23

# 6.4 AND (AND Byte Data of Accumulator and Temporary Accumulator to Accumulator)

Carry out the logical AND on the byte data of AL and TL for every bit and return the result to AL. The byte data of AH is not changed.

# AND (AND Byte Data of Accumulator and Temporary Accumulator to Accumulator)

Operation

$(AL) \leftarrow (AL) \land (TL) (Byte AND)$

Assembler format

AND A

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | R | - |

+: Changed by executing instruction

-: Not changed

R: Set to 0 by executing instruction

N: Set to 1 if the MSB of AL is 1 as the result of operation and set to 0 in other cases.

Z: Set to 1 if the result of operation is  $00_{\mbox{\scriptsize H}}$  and set to 0 in other cases.

V: Always set to 0

C: Not changed

Number of execution cycle: 1

Byte count: 1 OP code: 62

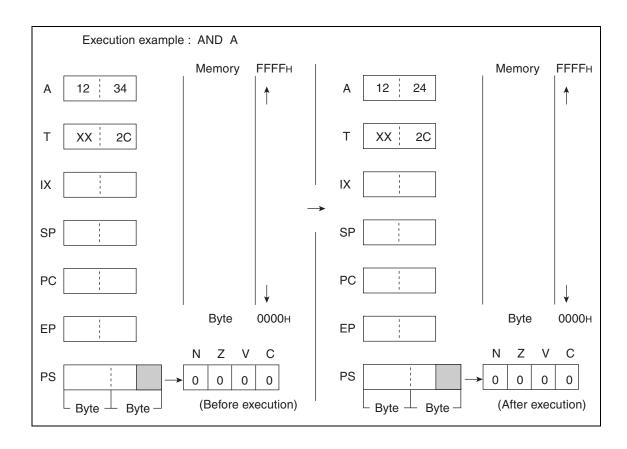

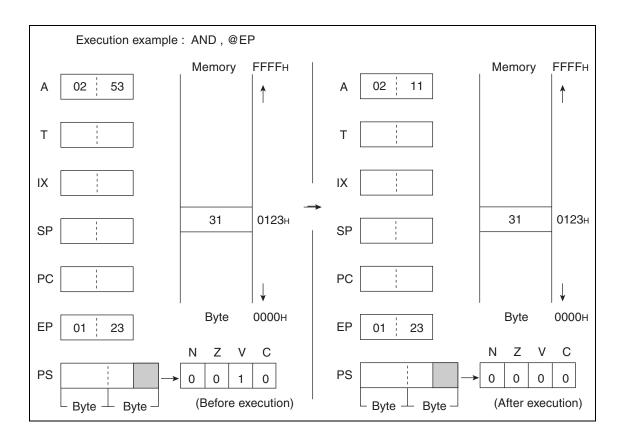

### 6.5 AND (AND Byte Data of Accumulator and Memory to Accumulator)

Carry out the logical AND on the byte data of AL and EA memory (memory expressed in each type of addressing) for every bit and return the result to AL. The byte data of AH is not changed.

### AND (AND Byte Data of Accumulator and Memory to Accumulator)

Operation

$(AL) \leftarrow (AL) \land (EA) (Byte AND)$

Assembler format

AND A, EA

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | R | - |

- +: Changed by executing instruction

- -: Not changed

- R: Set to 0 by executing instruction

- N: Set to 1 if the MSB of AL is 1 as the result of operation and set to 0 in other cases.

- Z: Set to 1 if the result of operation is 00<sub>H</sub> and set to 0 in other cases.

- V: Always set to 0

- C: Not changed

Table 6-8. Number of Execution Cycles / Byte Count / OP Code

| EA                         | #d8 | dir | @IX+off | @EP | Ri       |

|----------------------------|-----|-----|---------|-----|----------|

| Number of execution cycles | 2   | 3   | 3       | 2   | 2        |

| Byte count                 | 2   | 2   | 2       | 1   | 1        |

| OP code                    | 64  | 65  | 66      | 67  | 68 to 6F |

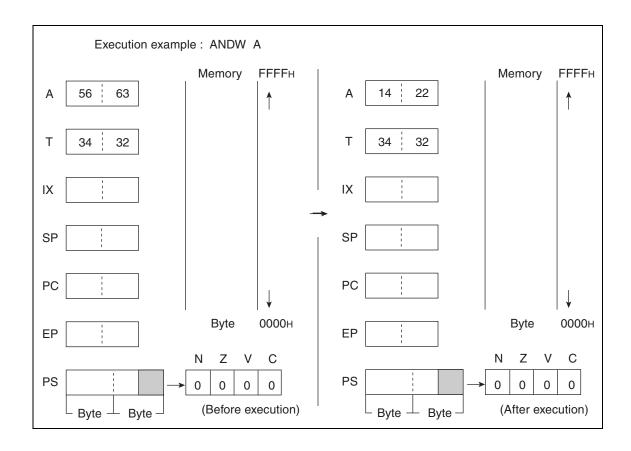

# 6.6 ANDW (AND Word Data of Accumulator and Temporary Accumulator to Accumulator)

Carry out the logical AND on the word data of A and T for every bit and return the results to A.

# ANDW (AND Word Data of Accumulator and Temporary Accumulator to Accumulator)

Operation

$(A) \leftarrow (A) \land (T) (Word AND)$

Assembler format

ANDW A

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| + | + | R | - |

- +: Changed by executing instruction

- -: Not changed

- R: Set to 0 by executing instruction

- N: Set to 1 if the MSB of A is 1 as the result of operation and set to 0 in other cases.

- Z: Set to 1 if the result of operation is 0000<sub>H</sub> and set to 0 in other cases.

- V: Always set to 0

- C: Not changed

Number of execution cycle: 1

Byte count: 1 OP code: 63

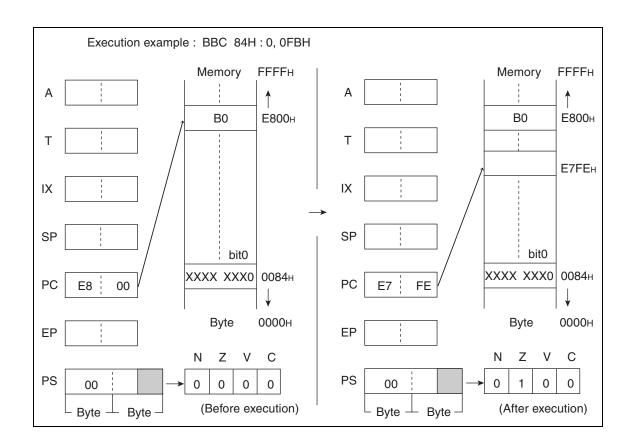

### 6.7 BBC (Branch if Bit is Clear)

Branch when the value of bit b in dir memory is 0. Branch address corresponds to the value of addition between the PC value (word value) of the next instruction and the value with rel code-extended (word value).

### **BBC** (Branch if Bit is Clear)

Operation

(bit)b = 0: (PC)  $\leftarrow$  (PC) + 3 + rel (Word addition)

(bit)b = 1: (PC)  $\leftarrow$  (PC) + 3 (Word addition)

Assembler format

BBC dir:b, rel

Condition code (CCR)

| N | Z | V | С |

|---|---|---|---|

| - | + | - | - |

+: Changed by executing instruction

-: Not changed

N: Not changed

Z: Set to 1 when the value of dir:b is 0 and set to 0 when it is 1.

V: Not changed

C: Not changed

Number of execution cycles: 5

Byte count: 3

OP code: B0 to B7

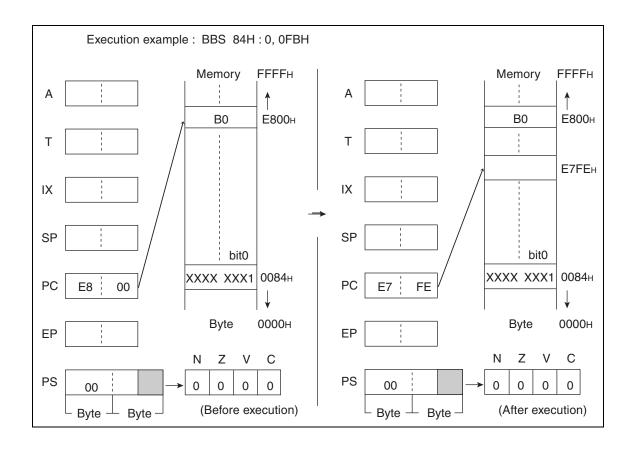

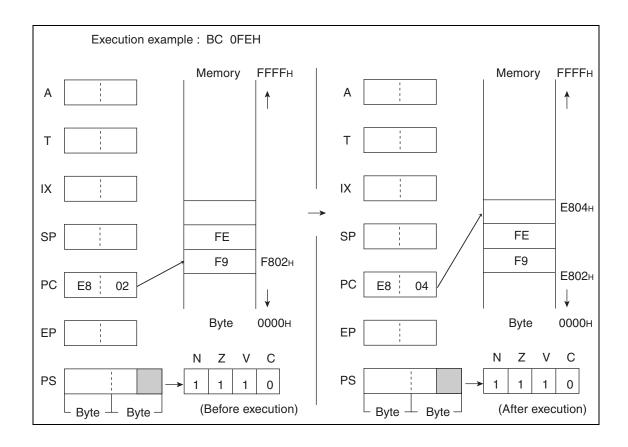

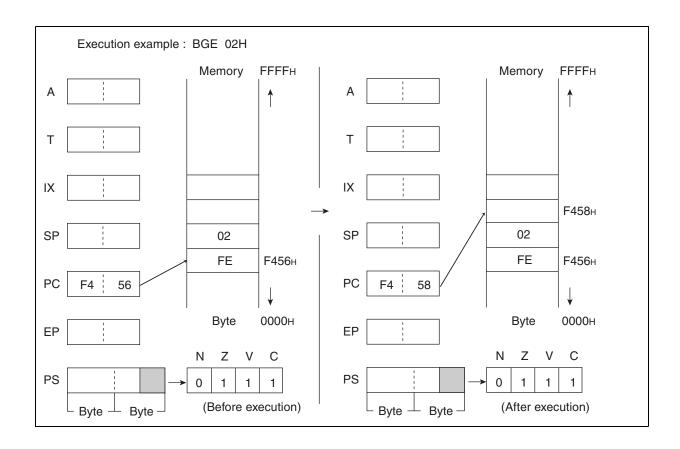

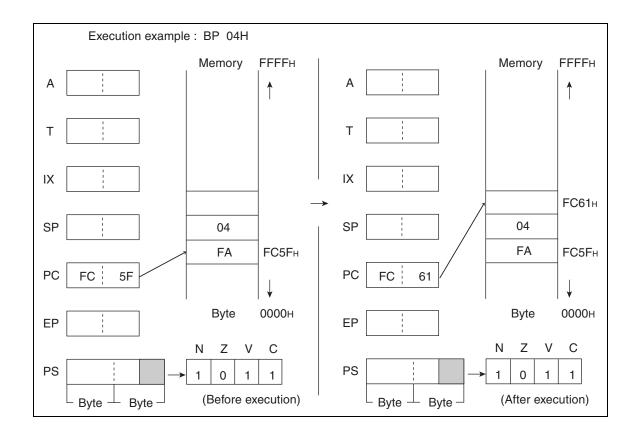

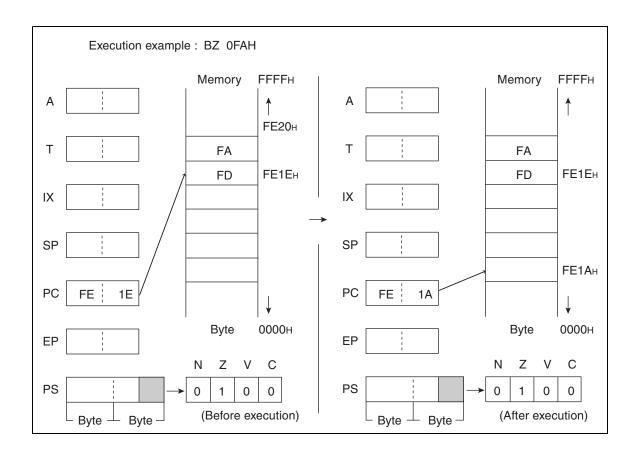

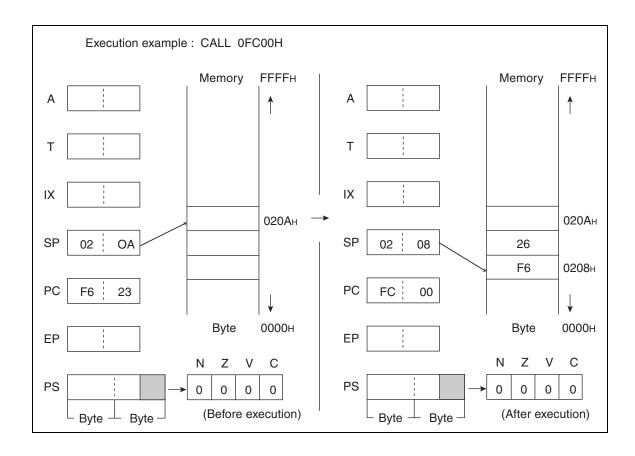

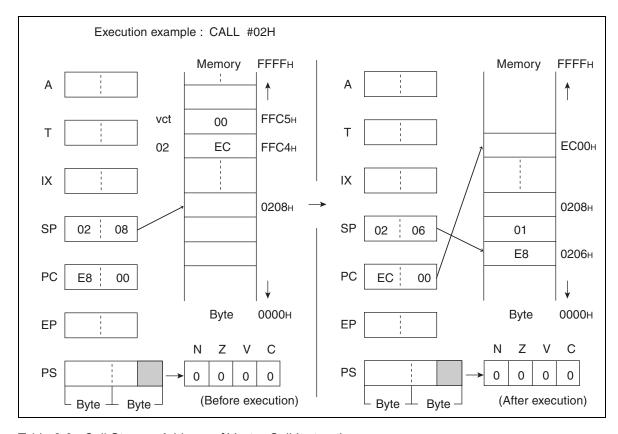

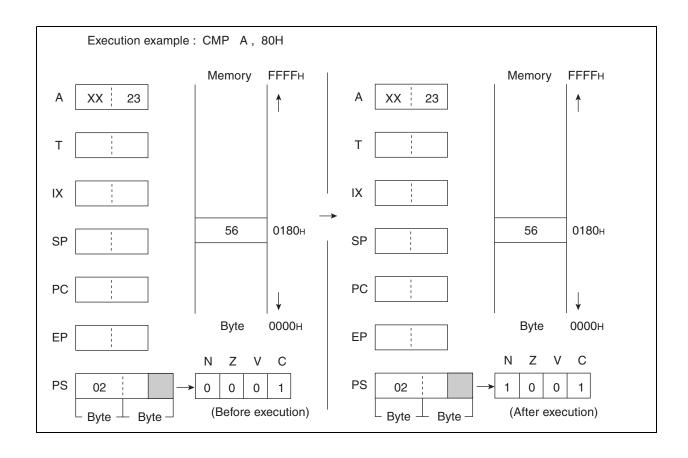

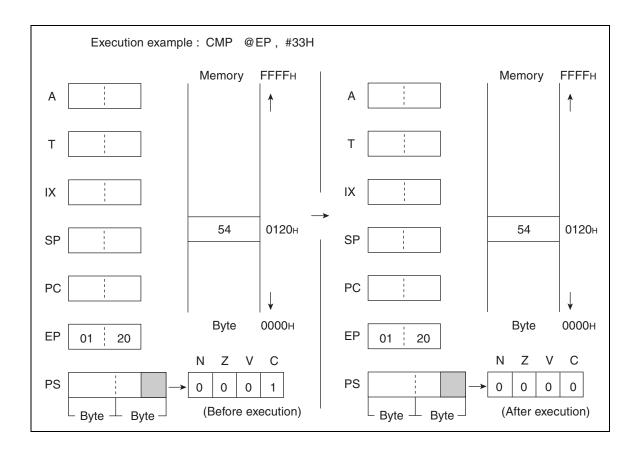

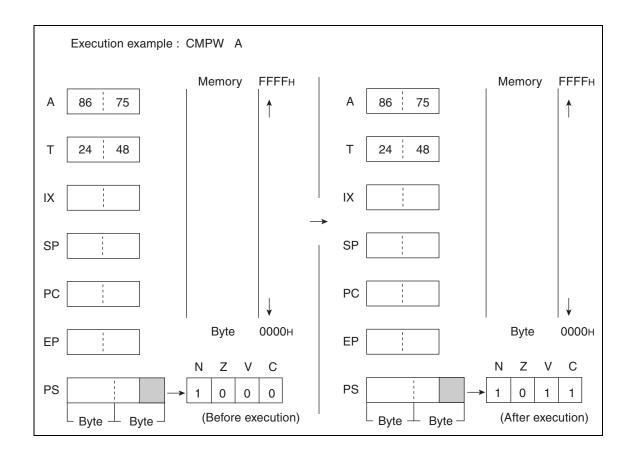

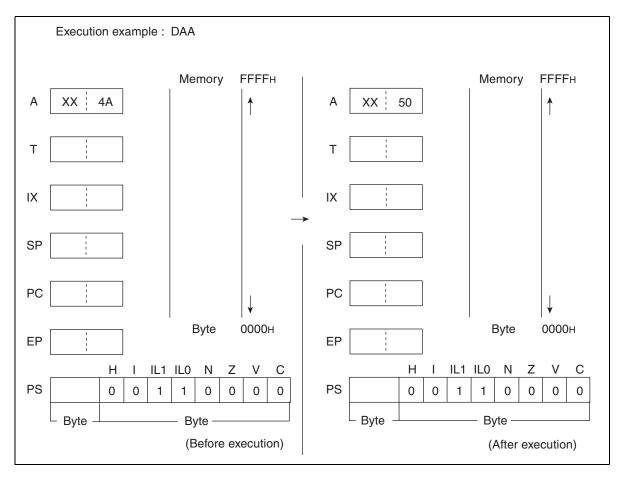

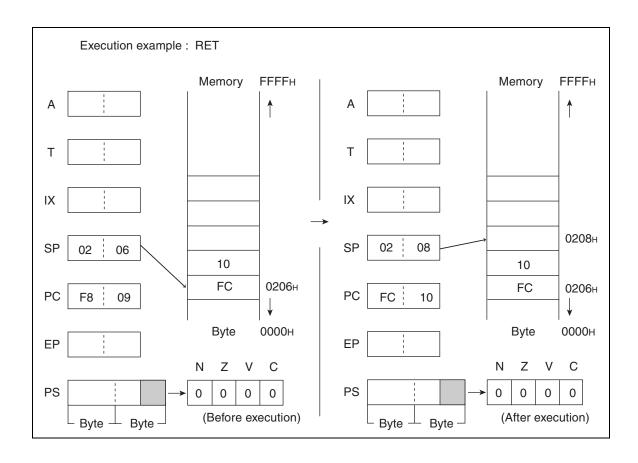

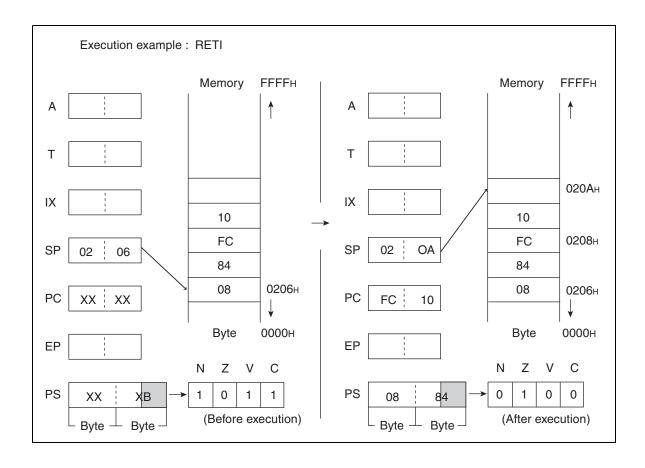

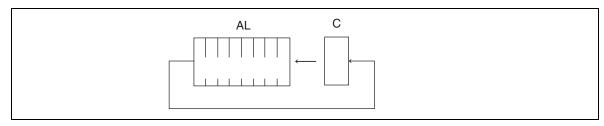

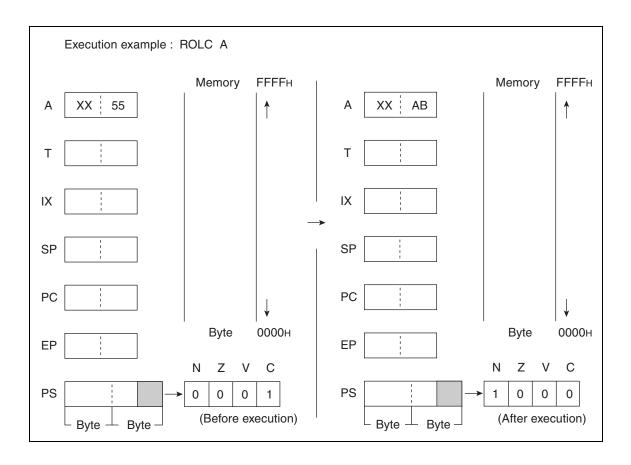

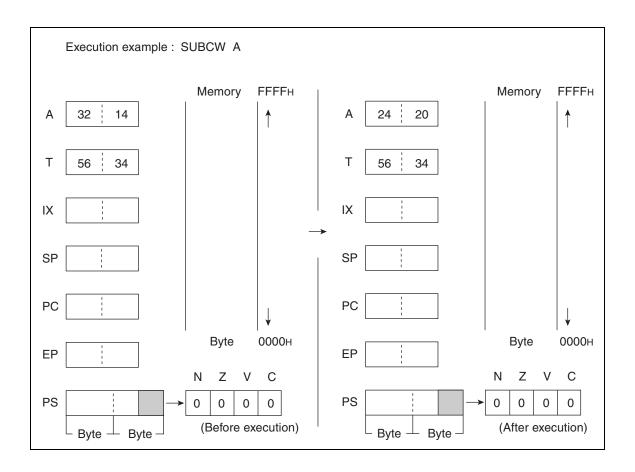

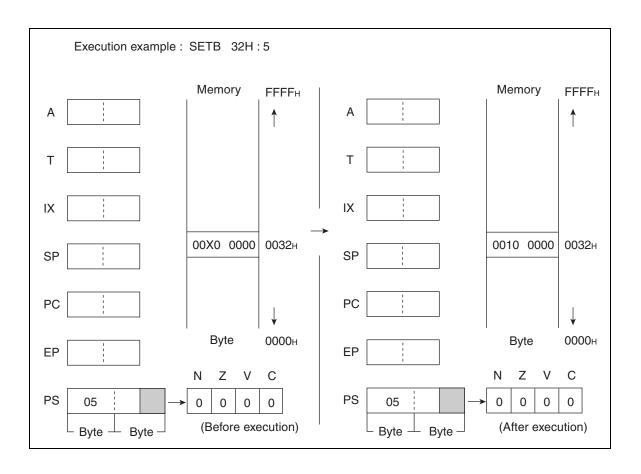

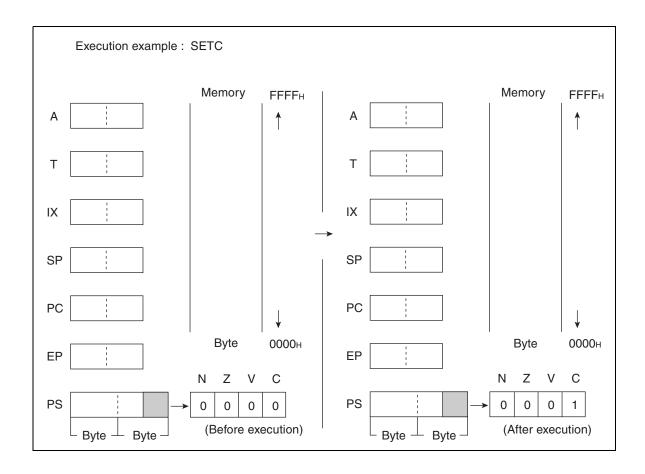

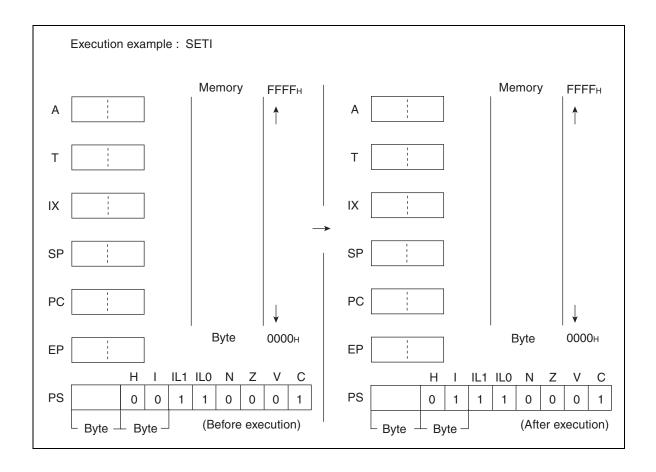

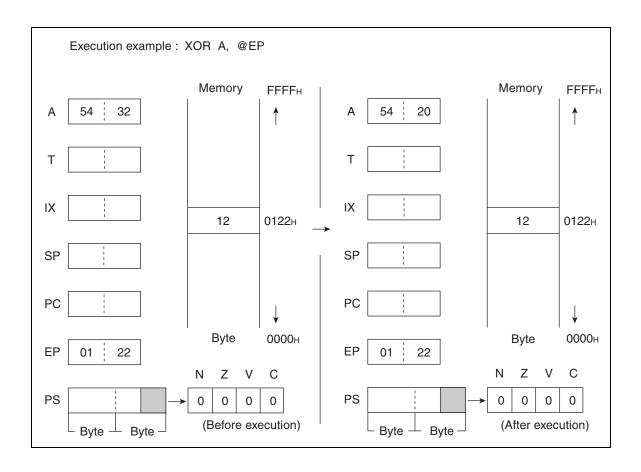

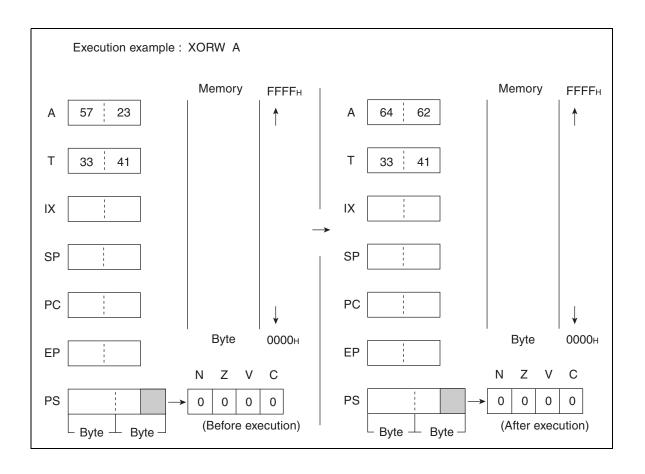

### 6.8 BBS (Branch if Bit is Set)