# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# THIS SPEC IS OBSOLETE

Spec No: 001-52209

Spec Title: AN52209 - CY8CLED0XX0X POWERPSOC(R) -

HARDWARE DESIGN GUIDELINES

Replaced by: NONE

# CY8CLED0xx0x PowerPSoC® – Hardware Design Guidelines

Doc. No. 001-52209 Rev. \*G

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2009-2021. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1. | Intro                                             | duction                                       |                                                                             | 5  |  |  |  |

|----|---------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|----|--|--|--|

|    | 1.1                                               | Overvie                                       | ew of Chapters                                                              | 5  |  |  |  |

|    |                                                   | 1.1.1                                         | Basic Thermal Guidelines for using PowerPSoC®                               | 5  |  |  |  |

|    |                                                   | 1.1.2                                         | PowerPSoC® PCB Design Guidelines for LED Driver Circuits                    | 5  |  |  |  |

|    |                                                   | 1.1.3                                         | Minimizing Power and Ground Transients in LED Driver Circuits               |    |  |  |  |

|    |                                                   | 1.1.4                                         | System Level ESD Considerations for a PowerPSoC® Based LED Driver           | 6  |  |  |  |

|    | 1.2                                               | Guideli                                       | nes on Prioritization (Trade-offs)                                          | 6  |  |  |  |

| 2. | Basic                                             | Basic Thermal Guidelines for using PowerPSoC® |                                                                             |    |  |  |  |

|    | 2.1                                               | Therma                                        | al Theory                                                                   | 7  |  |  |  |

|    |                                                   | 2.1.1                                         | Thermal Resistance                                                          | 7  |  |  |  |

|    |                                                   | 2.1.2                                         | Heat Transfer                                                               | 8  |  |  |  |

|    |                                                   | 2.1.3                                         | Power Dissipation                                                           | 9  |  |  |  |

|    |                                                   | 2.1.4                                         | Ambient Temperature                                                         | 9  |  |  |  |

|    | 2.2                                               | Powerl                                        | PSoC Thermal Model                                                          | 10 |  |  |  |

|    |                                                   | 2.2.1                                         | Accurately Estimating T <sub>junction</sub>                                 | 13 |  |  |  |

|    | 2.3                                               | Therma                                        | al Considerations                                                           | 14 |  |  |  |

|    | 2.4                                               | Therma                                        | al System <sup>[3, 4]</sup>                                                 | 14 |  |  |  |

|    | 2.5                                               | Optimiz                                       | zing Heat Flow Paths                                                        | 15 |  |  |  |

|    |                                                   | 2.5.1                                         | Heat Flow through Thermal Vias <sup>[2, 4]</sup>                            | 15 |  |  |  |

|    |                                                   | 2.5.2                                         | Heat Flow through PCB Area Surrounding the Device <sup>[2, 3]</sup>         | 16 |  |  |  |

|    |                                                   | 2.5.3                                         | Heat Flow into the Ambient or System Enclosure                              | 17 |  |  |  |

|    | 2.6                                               | Key PC                                        | CB Manufacturing Considerations from a Thermal Standpoint <sup>[2, 4]</sup> | 22 |  |  |  |

|    |                                                   | 2.6.1                                         | Solder Mask                                                                 | 22 |  |  |  |

|    |                                                   | 2.6.2                                         | Thermal Pad Connectivity                                                    | 22 |  |  |  |

|    |                                                   | 2.6.3                                         | Thermal Via Fill Material                                                   | 22 |  |  |  |

|    | 2.7 Illustrated Step-by-step Thermal Calculations |                                               | ted Step-by-step Thermal Calculations                                       | 23 |  |  |  |

|    | 2.8                                               | Summa                                         | ary                                                                         | 25 |  |  |  |

|    | 2.9                                               | Disclai                                       | mer                                                                         | 26 |  |  |  |

|    | 2.10                                              | Refere                                        | nces                                                                        | 26 |  |  |  |

| 3. | Powe                                              | erPSoC <sup>©</sup>                           | PCB Design Guidelines for LED Driver Circuits                               | 27 |  |  |  |

|    | 3.1                                               | Guideli                                       | nes and Checklist                                                           | 27 |  |  |  |

|    | 3.2                                               | Floatin                                       | g-Buck LED Driver                                                           | 28 |  |  |  |

|    | 3.3                                               | Compo                                         | nents Guidelines                                                            | 30 |  |  |  |

|    |                                                   | 3.3.1                                         | Place Key Components Close to Each Other                                    | 30 |  |  |  |

|    |                                                   | 3.3.2                                         | Test Points at Signal of Interest                                           | 31 |  |  |  |

|    |                                                   | 3.3.3                                         | Test Points Matched with Ground Test Points                                 | 32 |  |  |  |

|    | 3.4                                               | Boost 7                                       | Гороlogy                                                                    | 34 |  |  |  |

|    | 3.5                                               | Buck-B                                        | Soost Topology                                                              | 36 |  |  |  |

|    | 3.6                                               | PCB G                                         | uidelines                                                                   | 37 |  |  |  |

#### Contents

|     |                                                                   | 3.6.1 PCB Substrate                                                | 37 |  |

|-----|-------------------------------------------------------------------|--------------------------------------------------------------------|----|--|

|     |                                                                   | 3.6.2 Use Copper Sized for Power                                   | 38 |  |

|     |                                                                   | 3.6.3 Copper Pour                                                  | 39 |  |

|     |                                                                   | 3.6.4 Copper Thieving                                              | 39 |  |

|     |                                                                   | 3.6.5 Optimal Use of Vias                                          | 39 |  |

|     |                                                                   | 3.6.6 Placing Power Vias for Decoupling                            | 40 |  |

|     |                                                                   | 3.6.7 Via Size                                                     | 41 |  |

|     |                                                                   | 3.6.8 Via Quantity                                                 | 43 |  |

|     |                                                                   | 3.6.9 Thermal Power Connections                                    | 44 |  |

|     |                                                                   | 3.6.10 Minimize Trace Length                                       | 44 |  |

|     |                                                                   | 3.6.11 Prioritize Trace Routing                                    | 45 |  |

|     |                                                                   | 3.6.12 Route Sense Lines Differentially                            | 45 |  |

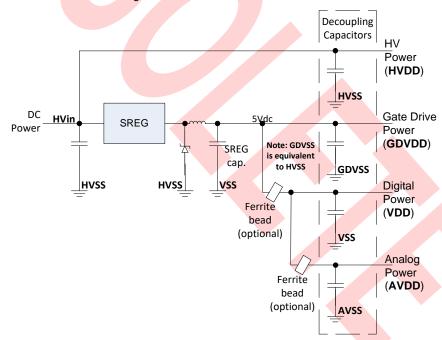

|     | 3.7                                                               | Power Guidelines                                                   | 46 |  |

|     |                                                                   | 3.7.1 Power Domains (Filtering)                                    | 46 |  |

|     |                                                                   | 3.7.2 Power and Voltage Loss                                       | 47 |  |

|     |                                                                   | 3.7.3 Multiple Vias for Power                                      | 48 |  |

|     |                                                                   | 3.7.4 Evaluate Current Loops                                       | 49 |  |

|     | 3.8                                                               | Common (Ground) Guidelines                                         | 50 |  |

|     |                                                                   | 3.8.1 Digital, Analog, Power, and Star Ground                      | 50 |  |

|     |                                                                   | 3.8.2 Ground Plane Cuts or Voids                                   |    |  |

|     | 3.9                                                               | Thermal Dissipation Guidelines                                     | 51 |  |

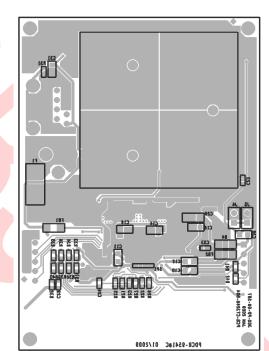

|     | 3.10                                                              | Example PCB layout                                                 |    |  |

|     | 3.11                                                              |                                                                    |    |  |

|     | 3.12                                                              | 12 References                                                      |    |  |

| 4.  | Mini                                                              | mizing Power and Ground Transients in LED Driver Circuits          | E  |  |

| 4.  |                                                                   |                                                                    |    |  |

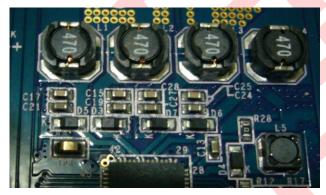

|     | 4.1                                                               | Power Domains                                                      |    |  |

|     | 4.2                                                               | Ground Domains                                                     |    |  |

|     | 4.3                                                               | Decoupling Capacitors                                              |    |  |

|     |                                                                   | 4.3.1 High Voltage (Channel) Input Decoupling Example – No Dimming |    |  |

|     |                                                                   | 4.3.2 High Voltage (Channel) Input Decoupling Example – Dimming    |    |  |

|     |                                                                   | 4.3.3 High Voltage (SREG) Input Decoupling Example                 |    |  |

|     |                                                                   | 4.3.4 Gate Driver Input Decoupling Example                         |    |  |

|     |                                                                   | 4.3.5 Digital Decoupling Example                                   |    |  |

|     |                                                                   | 4.3.6 Analog Decoupling Example                                    |    |  |

|     | 4.4                                                               | Ferrite Beads                                                      | 66 |  |

|     | 4.5                                                               | Summary                                                            | 67 |  |

| 5.  | System Level ESD Considerations for a PowerPSoC® Based LED Driver |                                                                    |    |  |

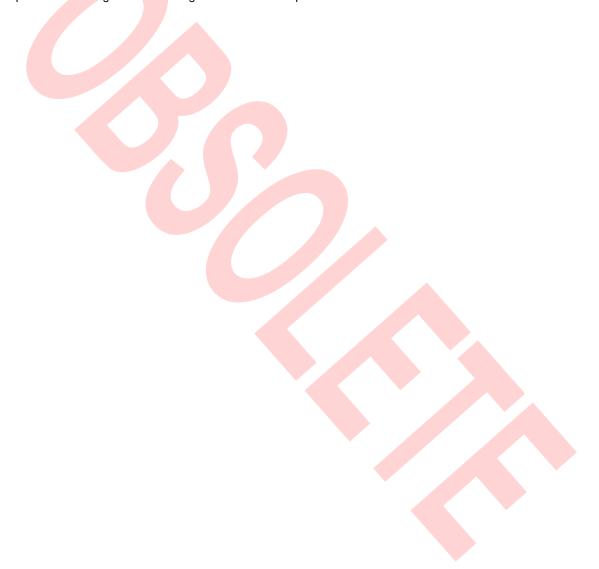

|     | 5.1                                                               | Circuit Level Improvements                                         | 68 |  |

|     | 5.2                                                               | System Level Improvements                                          | 70 |  |

|     | 5.3                                                               | Summary                                                            | 71 |  |

| Rev | vision                                                            | History                                                            | 72 |  |

|     | Doci                                                              | ument Revision History                                             | 72 |  |

# 1. Introduction

The Cypress PSoC® family of devices is well established in the field of programmable mixed-signal microcontroller-based devices. The traditional method of implementing power management systems (for example, high-brightness LED lighting systems) involves using a similar system-on-chip to interface with high-power discrete devices, such as constant current drivers and MOSFET switches.

In PowerPSoC®, the classic PSoC core is combined with high-performance power electronics. This results in an integrated intelligent power electronics solution in a single QFN package. The intent of PowerPSoC is to significantly reduce the BOM cost, part count, and board space for implementing power management systems while retaining performance. CY8CLED04D01 family of devices combines up to four independent channels of constant current drivers.

The level of integration and versatility offered by PowerPSoC can lead to considerable simplification of design, thus allowing the designers who are less familiar with power electronics domain to venture into these designs. In order to avoid oversimplification and/or overlooking of certain fundamental system-level considerations, Cypress offers this document to address the following four key issues in any power conversion system design: thermal, layout, transient handling, and ESD. By gaining familiarity with the issues and employing suggested techniques and guidelines in these chapters, the designers will certainly improve the integrity of their designs and likelihood of first pass success.

# 1.1 Overview of Chapters

### 1.1.1 Basic Thermal Guidelines for using PowerPSoC®

Power conversion systems' inefficiencies or losses result in generation of heat within the system. The control and dissipation of this heat is an important system design criterion, commonly known as thermal management. As the power density of systems increase, the system designers need to pay more attention in managing heat dissipation from key portions of the system to maintain devices within their optimum operating temperatures. This chapter provides a thermal model for PowerPSoC and lists key considerations for achieving a robust thermal design.

By reading this chapter, you will be able to create a first pass thermal model of the intended system and ensure that the device junction temperature stays within desired limits through design of appropriate thermal paths on the printed circuit board (PCB).

# 1.1.2 PowerPSoC® PCB Design Guidelines for LED Driver Circuits

Realization of PCB designs using PowerPSoC requires adherence to certain guidelines for optimal performance and first pass success. In this chapter, systematic guidelines with design examples are provided for PCB design of LED driver circuits using PowerPSoC.

The guidelines cover three major areas: component placement choices, circuit board choices, and power/grounding layout choices. Illustrated examples are given for layout considerations for floating buck, floating buck-boost, and grounded boost LED drivers. In addition, important information regarding via usage, trace selection, and other PCB routing details are provided. For a beginner, it may be overwhelming to assimilate and follow all the guidelines at once. In such cases, it is essential that the grounding and trace selection guidelines are followed more closely.

#### 1.1.3 Minimizing Power and Ground Transients in LED Driver Circuits

A high-brightness LED driver circuit has significant switching transients and current flow levels that can complicate the design. PowerPSoC simplifies many of these design aspects with its high integration of power components. This chapter provides guidelines for reducing transients in the power and ground domains, and the use of filtering components to optimize power supply design using PowerPSoC. Further, it describes how to select power supply decoupling capacitors and provides examples of minimum capacitance calculations based on system parameters. A section on the use of ferrite beads is also included.

This chapter contains detailed treatment of ground and power domains – definitions, recommendations, and examples. It alerts the designer that all **grounds** are not equal and careful identification of switching transients and their effects prior to layout prevents unwanted signal couplings. In addition, a set of examples are provided to illustrate the calculations of decoupling capacitors for various sections of the PowerPSoC application circuit. As illustrated, prevailing system requirements play a key role in the final determination of the decoupling capacitors.

### 1.1.4 System Level ESD Considerations for a PowerPSoC® Based LED Driver

This chapter highlights the ESD challenges in LED lighting systems with secondary side controllers and describes the design of PowerPSoC based products with robust system-level ESD performance. Protection is provided by including a few low-cost circuit components and by incorporating minor changes to the lighting fixture design.

While the focus of this compact chapter is on averting ESD events coming from the LED fixtures from impacting the PowerPSoC pins, the techniques described here are universally applicable. The key messages from this chapter are:

- Provide sufficient bypass paths for any external ESD or other transients so that they do not get to the vulnerable part of the system, i.e., PowerPSoC.

- Build sufficient protection at the CSP and CSN pins of the PowerPSoC in terms of bypass capacitors and TVS diodes as further precaution.

# 1.2 Guidelines on Prioritization (Trade-offs)

The chapters in this primer cover different aspects of board realization. It is natural and likely that during any specific circuit implementation, conflicts will arise between the guidelines from different chapters (or sometimes from within a chapter). As any engineering exercise involves making trade-offs, this should not be too surprising. Each application will have its own priorities and key requirements, so it is difficult to provide generalized guidelines. However, following points may help when you are trying to resolve the conflicts between guidelines (or prioritizing amongst them).

- Give primacy to thermal considerations without stable thermal operation, system design is meaningless.

- If system requirements involve exposure to external (human or material) electrostatic impulses, then build in the protection described in the ESD chapter.

- When designing decoupling capacitance, err on the side of choosing higher value in a smaller package.

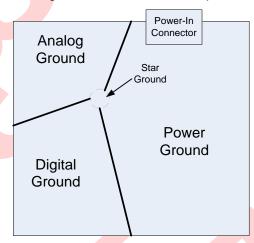

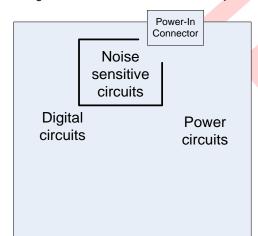

- For layout exercises, give primacy to using Star grounds and short traces for power nets.

# 2. Basic Thermal Guidelines for using PowerPSoC®

It is easier to model a thermal system by drawing analogy to an electrical system. In an electrical system, current flows through a path comprised of electrical resistance if there is a potential difference between two points. Similarly, in a thermal system, heat flows through a path comprised of thermal resistance if there is a temperature difference between two points.

From a semiconductor perspective, the goal of every thermal design is to keep the junction temperature well below the maximum datasheet specification. This can be achieved by optimizing the thermal path from the semiconductor junction to a thermal ground.

This document uses Cypress's PowerPSoC family of intelligent LED controllers to demonstrate the concepts with help of some examples. The PowerPSoC family, along with PSoC technology, features high-performance power electronics including 1 A, 2 MHz power FETs, hysteretic controllers, current sense amplifiers, and PrISM/PWM modulators. These features enable creation of intelligent power electronics solutions for LED power management with efficiencies greater than 90 percent.

This document covers the basic guidelines for a good thermal design. Although beyond the scope of this document, it is useful to note that intelligent thermal protection can be designed using the programmability available within PowerPSoC.

# 2.1 Thermal Theory

The design of a thermal system is usually governed by four factors – power dissipated by the devices, thermal resistance of the devices, thermal resistance of the heat sinking mechanism, and ambient temperature. Except for thermal resistance of the device, the designer has control over the other factors. Although different applications have a different balance of these factors, the goal is always the same – to minimize the junction temperature of critical devices. Critical devices are devices operating close to their rated power dissipation.

#### 2.1.1 Thermal Resistance

Similar to electrical systems where resistances impede current flow, a thermal system consists of thermal resistances that impede heat flow. Thermal resistance is usually specified in °C/W. The most common parameters found in power semiconductor manufacturer datasheets are -

- thermal resistance from device junction to ambient (θ<sub>JA</sub>) and

- thermal resistance from device junction to device case (θ<sub>JC</sub>).

Less common, but increasingly specified is the thermal resistance from device junction to solder  $(\theta_{JS})$  ('s' refers to the solder that connects the device thermal pad to the board), which is important for devices with a solderable thermal attachment and is becoming more prevalent in high-density designs.

Basic Thermal Guidelines for using PowerPSoC®

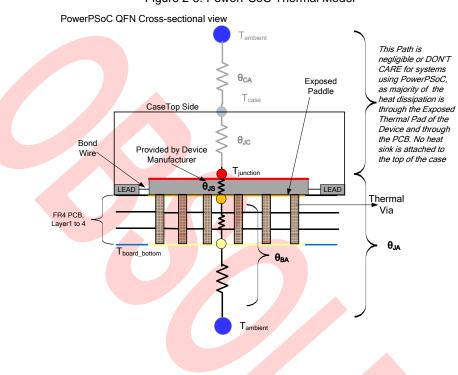

Thermal resistances are shown in Figure 2-1.  $\theta_{BA}$  and  $\theta_{CA}$ , which are thermal resistances from board-to-ambient and device case-to-ambient, are also shown. In PowerPSoC, almost 96 percent of the total heat is transferred through the bottom thermal pad. Therefore,  $\theta_{JA}$  is dictated by  $\theta_{JS}$  and  $\theta_{BA}$  and its  $\theta_{JC}$  and  $\theta_{CA}$  components are not considered.

This part is usually governed by heatsinking to device case

Total

Tota

Figure 2-1. Thermal Resistance Network

#### 2.1.2 Heat Transfer

Unlike electrical flow, which is always conductive, heat transfer can take place in any of the following three modes.

#### 2.1.2.1 Conduction

This mode of heat transfer occurs due to direct contact between two solid surfaces. Conductive heat transfer usually depends on geometry, type, thickness, and area of heat flow. Air has the lowest thermal conductivity. Hence, a copper or aluminum surface is usually required to accelerate heat removal from the device junction.

#### 2.1.2.2 Convection

This mode of heat transfer occurs due to the movement of fluids (liquid or gas) past a solid surface, which is at a temperature different from the fluid. Convective heat transfer usually depends on type, area, and amount of fluid flow. It is also possible to create forced convection (using fans) that increases the rate of fluid flow. However, due to cost and other complexities, natural convection is the preferred method in many high-density systems.

#### 2.1.2.3 Radiation

This mode of heat transfer occurs by electromagnetic waves through empty space. Radiated heat transfer usually depends on surface temperature, surface emissivity, and surrounding temperature.

#### 2.1.3 Power Dissipation

The source of heat in a power device is the **power dissipation** of the device. Power dissipation is the sum of all the losses in the device. As seen in Equation 1, junction temperature is a function of power dissipation.

$$T_{\text{junction}} = T_{\text{ambient}} + PD*(\theta_{JA})$$

Equation 1

Where:

T<sub>junction</sub> denotes junction temperature of the device in °C.

Tambient denotes ambient temperature of the system in °C.

PD denotes power dissipation of the device in W.

θ<sub>JA</sub> denotes thermal resistance from the device junction to ambient in °C/W.

Another method of computing the junction temperature is shown in Equation 2 and Equation 3.

$$T_{\text{junction}} = T_{\text{board}} + PD*(\theta_{JS})$$

Equation 2

$$T_{\text{board}} = T_{\text{ambient}} + PD*(\theta_{\text{BA}})$$

Equation 3

Where

Tboard denotes PCB temperature at a point on the top PCB layer below the PowerPSoC.

O<sub>JS</sub> denotes thermal resistance from device junction to thermal pad

$\theta_{BA}$  denotes thermal resistance from board to ambient.

#### 2.1.4 Ambient Temperature

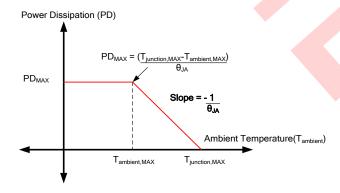

Ambient temperature or surrounding temperature affects the maximum junction temperature. The maximum ambient temperature value from the device datasheet can be used along with thermal resistance  $\theta_{JA}$  to de-rate the maximum power dissipation above maximum ambient, as shown in Figure 2-2.

Consider the following example to understand the relationship between ambient temperature and power dissipation.

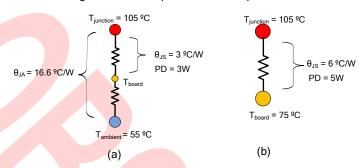

In Figure 2-3 (a),  $\theta_{JA}$  is 16.6 °C/W,  $T_{ambient}$  is 55 °C, and power dissipation is 3 W. However, the board temperature  $T_{board}$  is not specified. In Figure 2-3 (b),  $\theta_{JS}$  is 6 °C/W,  $T_{board}$  is 75 °C, and power dissipation is 5 W;  $T_{ambient}$  however, is not specified. In both cases, the junction temperature is maintained at 105 °C.

Figure 2-2. Maximum Power Dissipation De-rating

Thermal resistances may be specified on the datasheet in one or both ways, shown in Figure 2-3. However, it is often unclear whether a particular thermal resistance should be used for  $T_{junction}$  estimation. It is also unclear whether temperature should be measured at ambient, case, or board. The answer lies in determining path of least thermal resistance and deriving temperature drops along that path.

Figure 2-3. Example Datasheet Specifications

For PowerPSoC,  $\theta_{JS}$  should be considered for  $T_{junction}$  estimation. PowerPSoC is designed to dissipate almost 96 percent of the heat through the exposed thermal pad (integrated into the device package) to the PCB.

Comparing Figure 2-3 (a) and Figure 2-3 (b), it can be seen that the  $T_{board}$  is 96 °C (based on application of Equation 2,) for Figure 2-3 (a), while it is 75 °C for Figure 2-3 (b). This is despite lower values of  $\theta_{JS}$  and PD for the Figure 2-3 (a) scenario – indicating that the board layout and thermal management in Figure 2-3 (b) is good enough to keep the board temperature at 75 °C. For Figure 2-3 (a), it is not possible to dissipate 5 W through a system while retaining the junction at 105 °C. Either  $\theta_{JA}$  or  $T_{ambient}$  needs to be changed. In most cases it is easier to reduce  $\theta_{JA}$  by modifying the board design – for instance, using more copper or aluminum.

If it is not possible to change  $\theta_{JA}$  or  $T_{ambient}$ , then power dissipation must be de-rated using  $\theta_{JA}$  as illustrated in Figure 2-2.

#### 2.2 PowerPSoC Thermal Model

Typically, the majority of heat transfer in a PowerPSoC dc-dc Converter PCB is in the form of conduction. There is also a small amount in the form of convection and radiation. Using a regular PCB to model thermal resistances (as shown in Figure 2-1) is complex because a number of factors affect heat flow. Some of these factors are:

- Power dissipation

- Air velocity and direction

- PCB orientation, size, component density, and mounting

- Copper thickness, number of copper layers

- Die size

- Environment (ambient temperature)

This dependence on various factors leads to variation in specifications and test methodologies among manufacturers. The Joint Electron Device Engineering Council (JEDEC) has standardized the test procedure [1].

The thermal model for Cypress's PowerPSoC family was simulated using a JESD51-7 standard FR4 PCB with four metal layers, 2 oz copper weight on outer layers, and 1 oz on inner layers. Thermal via array below the device is laid out according to package manufacturers' recommendations<sup>[2]</sup>. The simulation results are shown in Table 2-1.

Table 2-1. Thermal Resistances for PowerPSoC

| Package | Body Size                | Air Flow | $\Theta_{JA}$ | Θ <sub>JC</sub> | θ <sub>Js</sub> |

|---------|--------------------------|----------|---------------|-----------------|-----------------|

| QFN-56  | 8 mm x 8 mm (1 mm thick) | 0 m/sec  | 16.6 °C/W     | Not Applicable  | 2 °C/W          |

#### In Table 2-1:

$\theta_{JA}$  denotes thermal resistance from device junction to ambient. It depends on the package, board, airflow, radiation, and system characteristics. Typically, effects of radiation are negligible.

Note The PowerPSoC family datasheet lists a value for natural convection only (no forced air).

$\theta_{JC}$  denotes thermal resistance from device junction to device case. Case is specified at a point on the outer surface of the package. It depends on package design and materials used. In the absence of a heat sink to case, a very small percentage of the heat dissipates through the top surface of the package. Hence,  $\theta_{JC}$  is not relevant for PowerPSoC based systems because the PCB is used as a heat sink to dissipate heat through the exposed thermal pad.

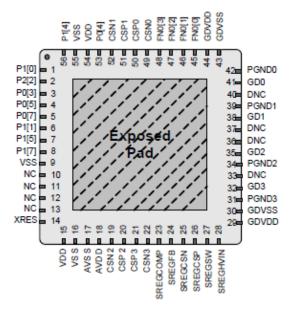

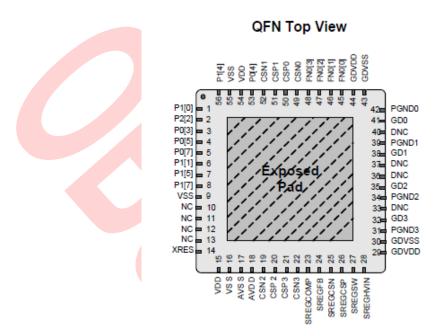

$\theta_{JS}$  denotes thermal resistance from device junction to solder, which connects the device thermal pad (as shown in Figure 2-4) to the board. This parameter includes thermal resistance from PowerPSoC's junction to a reference point on the bottom of the package through a solder point to the board under the package.  $\theta_{JS}$  parameter is important for devices in leadless packages that have a thermal attachment mechanism.

Figure 2-4. PowerPSoC Thermal Pad

#### **QFN Top View**

\* Connect Exposed Pad to PGNDx

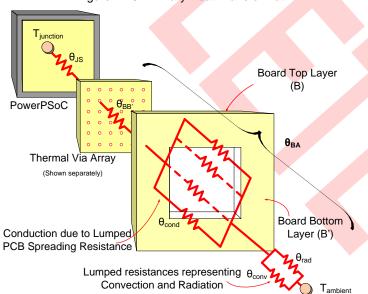

The PowerPSoC thermal model is shown in Figure 2-5.

Figure 2-5. PowerPSoC Thermal Model

#### 2.2.1 Accurately Estimating T<sub>junction</sub>

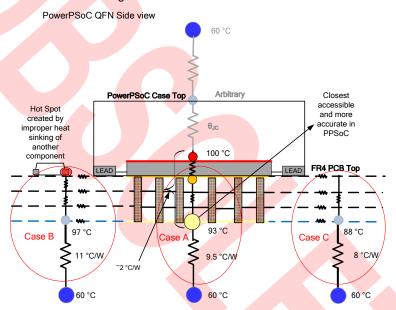

T<sub>junction</sub> can be accurately estimated if an appropriate measurement point on the board is chosen. If valid thermal resistances and board effects are not accounted for, the measurement will be erroneous. Consider the following example to understand how to make an accurate T<sub>junction</sub> measurement.

For this example,  $\theta_{JS}$  is equal to 2 °C/W (neglect thermal resistance through the thermal via array for this example); PD is 3.5 W. The intent is to retain  $T_{junction}$  at 100 °C at a  $T_{ambient}$  of 60 °C.  $\theta_{BA}$  varies when measured across different points, as shown in Figure 2-6. Using Equation 2 and Equation 3,  $T_{junction}$  and  $T_{board\_bottom}$  across the different points can be computed.  $T_{board\_bottom}$  is the board temperature at a point on the bottom layer of the board just below the PowerPSoC.

Figure 2-6. Accurate θ<sub>JS</sub> Estimation

As seen, every point can be at a different temperature depending on factors such as board design, airflow, component orientation, and hot spots created by another component in the proximity of the measurement point. In Case B, a hot spot created by another component increases the bottom layer board temperature. In Case C, the bottom layer board temperature measured away from the device is lower due to the effect of board spreading resistance. Power conversion systems have other power components (power rectifiers, inductors, and so on) that produce a fair amount of heat. If the measurement is not made at the appropriate point, interaction between multiple heat sources can lead to measurement errors. Therefore, when measuring junction temperature for PowerPSoC, the point at which the reading is most accurate is Case A (marked with a yellow circle). This point is on the bottom layer of the PCB that is connected to the PowerPSoC's exposed paddle through an array of thermal vias. Thermal vias offer very low thermal resistance.

**Note** The procedure to calculate thermal resistance of the thermal via array is outlined in the Illustrated Step-by-step Thermal Calculations section.

It can be inferred that  $\theta_{JS}$ , bottom layer board temperature, and resistance of the thermal via array are the key considerations when computing junction temperature for PowerPSoC.

#### 2.3 Thermal Considerations

Historically, thermal design is meant for finding out which of the components in the system generated the most heat and also coupling them to a heat sink. However, with power systems shrinking in size and becoming more cost sensitive, heat sinks have become a less attractive option. There is a need to use the PCB as a heat sink. Heat transfer through the PCB, similar to any other heat sink, is primarily in the form of conduction along the surface, and secondarily through convection and lastly through radiation to the ambient.

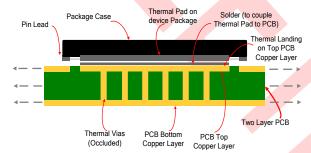

PowerPSoC is packaged in a QFN package with an integrated thermal pad on the bottom. The thermal pad provides a very low thermal-resistance path to conduct heat out of the device. Without this thermal pad, the thermal impedance of the package would be quite high and it would be unable to handle the power dissipation normally associated with its functioning. The heat is conducted to the structure that is attached to thermal pad. Typically, the pad connects to a copper landing on the PCB through a solder joint, effectively turning the PCB into a heat sink. In PowerPSoC, thermal pad is also electrically connected to power ground. (Refer to the PowerPSoC family datasheet for details on electrical specifications.)

It is important to ensure that the device is both thermally and electrically coupled to the PCB for optimum performance and system reliability. Not only does the heat need to conduct through the PCB, it must also effectively transfer into the surroundings as well as away from the device. Hence, it is critical to ensure robust thermal pad and PCB design. One challenge that immediately presents itself is that it is difficult (nearly impossible) to spread the heat on the top layer where the thermal pad is attached to the PCB. Thermal pad is completely surrounded by device pins, which have electrical connectivity requirements on the same layer. As a result, it is imperative to use the array of vias as depicted in the following section.

**Note** For designs using the PowerPSoC gate drivers to drive external MOSFETs, the heat generation primarily shifts to the external MOSFETs. Hence, guidelines recommended for MOSFET thermal landing layout should be considered while laying out the circuits.

# 2.4 Thermal System<sup>[3, 4]</sup>

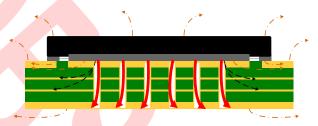

The QFN device and the surrounding PCB area under the package is essentially the "thermal system", which optimizes heat conduction as shown in Figure 2-7.

Figure 2-7. Thermal System Cross-sectional View

The system consists of the exposed thermal pad integrated on the bottom of the QFN package, a thermal landing on the PCB top layer, an array of vias designed to effectively transfer heat from the top to the bottom layer of the PCB, and a layer of solder paste (interface material) is used to couple the pad to the landing.

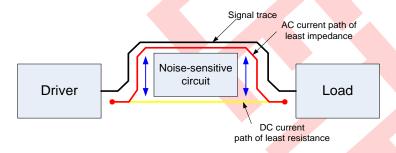

- Heat flow paths can be thought of as lumped heat flow paths as shown in Figure 2-8. Although this is not an accurate model for heat flow, it emphasizes the fact that most of the heat is conducted through the via array into the PCB.

- The goal of a good thermal design should be to optimize the various heat flow paths:

- Heat flow through the thermal vias

- Heat flow through PCB area surrounding the device

- Heat flow into the ambient or system enclosure

Figure 2-8. Heat Flow Paths

# 2.5 Optimizing Heat Flow Paths

#### 2.5.1 Heat Flow through Thermal Vias<sup>[2, 4]</sup>

Layout the thermal landing carefully, because it is part of the most critical path for heat conduction. Here are guidelines for a good thermal landing layout.

- Size of thermal landing on top layer of the PCB should be 6.05 mm x 6.05 mm. A similar copper pour should also be on the bottom layer, which should ideally extend into a large copper plane without any cuts or breaks.

- Copper thickness of 35 micron (1 oz. copper clad) is recommended when device dissipation is below 3 W, and 70 micron for higher dissipation levels.

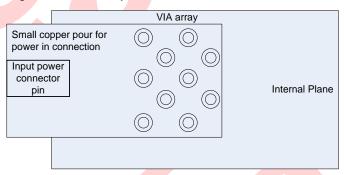

- A 6 x 6 via array (36 vias in total) should be used, as shown in Figure 2-9.

- The optimum number of vias recommended to achieve good thermal performance is 36.

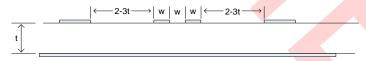

- Via diameter: 0.25 to 0.33 mm (to minimize solder wicking); spacing between adjoining via centers: 0.9 to 1.0 mm as shown in Figure 2-9.

Figure 2-9. PowerPSoC Landing Pattern

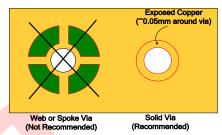

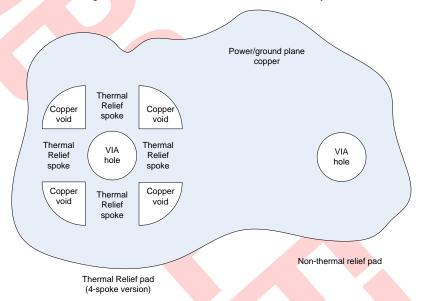

No thermal relief (web or spoke connections) on vias. There should be a continuous copper ring around the vias as shown in Figure 2-10.

Figure 2-10. Thermal Via

- Do not completely cover vias with solder mask as it can lead to excessive voiding.

- Vias should be internally plated with copper and filled with solder to avoid wicking. They may be filled with thermally conductive materials such as copper and silver epoxy to further improve thermal conductivity. Details on via filling are discussed later.

#### 2.5.2 Heat Flow through PCB Area Surrounding the Device<sup>[2, 3]</sup>

Heat conduction through the top copper plane is compromised by signal routing.

Thermal conductivity of the plane can be improved by filling unused PCB areas surrounding the device with copper. Note that copper pours should connect to appropriate electrical connections.

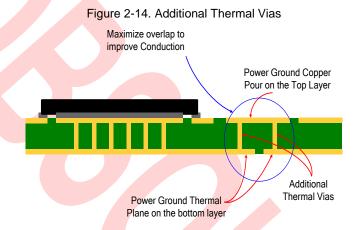

The thermal landing on top layer of the PCB should be connected to power ground copper pours to improve heat conductivity and satisfy electrical specifications for PowerPSoC. Further, thermal landing must be connected to power ground copper pours, if possible, on all inner and outer layers to maximize heat conduction through the PCB – this is illustrated in Figure 2-14.

#### 2.5.3 Heat Flow into the Ambient or System Enclosure

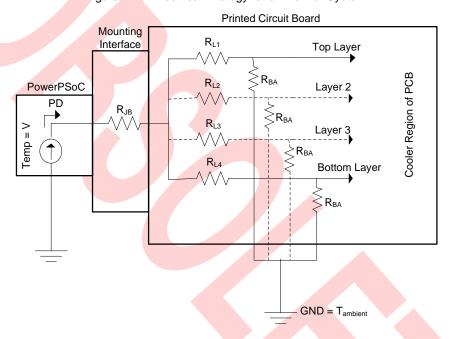

Effectively removing heat away from the device and into the ambient or system enclosure is dictated by PCB construction. The number of PCB layers, weight of copper on each layer, trace width, trace length, and trace and component placement plays an important role due to their influence on heat flow through the PCB. Figure 2-11 shows an electrical analogy for a thermal system. Power dissipated in the device can be modeled as a current source and temperature as an electrical voltage. The thermal resistances are modeled as resistors and the circuit can be solved for voltages that are analogous to temperatures. If the system is enclosed, thermally coupling the PCB to the enclosure maximizes heat transfer. Each of these PCB design criteria are discussed in detail.

Figure 2-11. Electrical Analogy for a Thermal System

#### 2.5.3.1 Number of PCB Layers

Increasing copper layers in a PCB improves conductivity. There can be as much as a 20 °C reduction in T<sub>junction</sub> when layers are increased from two to four<sup>[4]</sup>. However, it should be recognized that the capability of inner layers to disperse heat is limited and adequate number of thermal vias have to be added to bring the heat out to outer layers.

**Recommendation:** For systems with total PowerPSoC dissipation greater than 5 W, use four layers. If having four layers is not an option, other cooling techniques may have to be explored.

**Hint:** A PowerPSoC based system driving four channels with six 700 mA white LEDs each and a chip efficiency of 93 percent, dissipates approximately 5 W assuming a floating load buck topology with an operating switching frequency slightly under 2 MHz and conduction duty cycle of 75 percent.

#### 2.5.3.2 Copper Thickness

This denotes the copper thickness for PCB layers. Increasing the thickness lowers the thermal resistance. For cost sensitive designs, increasing copper thickness may be a good alternative for increasing the number of layers to optimize thermal performance.

Recommendation: Use 2 oz copper plating for outer layers in designs with total PD greater than 3 W.

#### 2.5.3.3 PCB Size<sup>[5]</sup>

Large boards have greater thermal mass. Recall that heat travels from the device to the PCB and then laterally conducts through the PCB surfaces. We can estimate a first pass lateral conductivity for a given PCB size by performing a few simplified calculations.

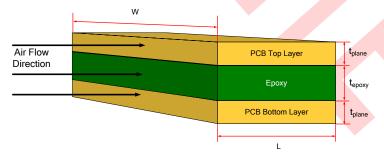

Consider a 2" x 2" (50.8 mm x 50.8 mm) board, 2 layers with 100% copper coverage, 2 oz copper per layer (layer thickness 0.071 mm =  $t_{top\_plane}$  =  $t_{bottom\_plane}$ ), both layers are at the same temperature, majority heat transfer is in the form of conductivity of copper is 0.386 W/mm°C (=  $k_{top\_plane}$  =  $k_{bottom\_plane}$ ), conductivity of epoxy material is 0.00025 W/mm°C (= $k_{epoxy}$ ), board thickness of 1.52 mm gives epoxy thickness of 1.38 mm (= $t_{epoxy}$ ),  $t_{board}$  is 85 °C, and the required  $t_{ambient}$  is 60 °C. The conduction is along the PCB surface as shown in Figure 2-12. Using one dimensional equations for conduction:

$$\theta_{PCB} = \left(\frac{L}{k_{eff}A}\right)$$

Equation 4

Where:

$\theta_{PCB}$  = the lumped 1D lateral resistance of the PCB surfaces.

keff = the effective thermal conductivity of the medium (PCB in this case).

A = the surface area of the medium normal to the direction of heat transfer. In our case, it is the product of length and PCB thickness.

L = the thickness of the medium.

Assuming heat flow through the PCB as one dimensional and disregarding heat flow from the side surfaces (shown in Figure 2-12), the effective thermal conductivity can be calculated as follows:

$$k_{eff} = \frac{(kt)_{epoxy} + (kt)_{top\_plane} + (kt)_{bottom\_plane}}{t_{pop}}$$

Equation 5

Where:

kepoxy, ktop plane, and kbottom plane denote thermal conductivity for epoxy and copper planes.

tepoxy, ttop\_plane, and tbottom\_plane denote thickness for epoxy and copper planes.

tPCB denotes overall thickness of the PCB.

Therefore, k<sub>eff</sub> = 0.036 W/mm°C

Figure 2-12. Heat Conduction through PCB Surface

Now we can calculate  $\theta_{PCB}$  as follows:

$$\theta_{PCB} = \left(\frac{L}{\mathbf{k}_{\text{eff}} * \mathbf{t}_{PCB} * W}\right)$$

Equation 6

Hence  $\theta_{PCB} = 18.30 \, ^{\circ}\text{C/W}$

Using Equation 3 with a board temperature of 85 °C and ambient of 60 °C, the 2" x 2" board can dissipate 1.37 W of power. Note that assumptions made in this example are highly simplified. This calculation is used to get a first pass estimation of conductive cooling that a particular board size can provide for a given temperature rise. The equations can be modified depending on the amount of copper (% copper) for each board layer.

For example, adding two inner layers of 1-oz copper reduces the  $\theta_{PCB}$  value to 12 °C/W and leads to 50 percent increase in power dissipation for the same area. If accurate modeling is required (considering the effects of traces and breaks in a continuous plane), it is recommended to simulate the system's thermal behavior using one of the many available CFD thermal analysis tools.

**Recommendation:** It is good practice to perform a first pass PCB thermal estimation in the initial design stages of the system.

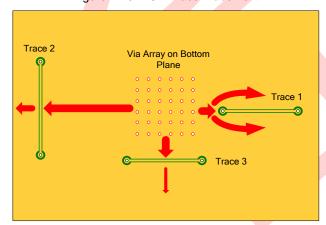

#### 2.5.3.4 Placement of PCB Traces 4

As shown in Figure 2-13, there are three ways to route traces on PCB layers. Placing traces close to the device must be minimized as they increase the thermal resistance and restrict heat flow away from the device. Avoid having traces on a layer that is used as a thermal plane for heat removal. If there is no option but to route on a thermal plane consider the following. Trace 3 runs parallel to the device and close to the device. So, Trace 3 significantly restricts heat flow (shown by red arrows) as it cuts the copper plane along the device periphery; Trace 2 on the other hand, being far away from the device, has a lower impact on heat flow. Trace 1 is the best option, because it cuts the plane in a perpendicular fashion with respect to the device; hence the impact on heat flow is minimal.

Note Although Trace 1 is the best routing option, placing multiple Trace 1s in parallel will have a significant negative impact on heat flow.

**Recommendation:** Avoid routing traces on the thermal layer. If unavoidable, use Trace 1 as an example for routing.

Figure 2-13. PCB Trace Placement

#### 2.5.3.5 Placement of Other Components

It is important to note that placing components close to the device not only restricts heat flow but can also create hot spots, if the component itself produces a fair amount of heat.

A topic not covered in detail in this chapter is the effects of other heat sources in various power system PCBs. It is assumed that the PCB contains only the dc-dc conversion circuitry with PowerPSoC as the primary power dissipating component. For systems that have, for instance, the ac-dc system or LED loads integrated onto the same PCB, PowerPSoC may no longer be the focus of the thermal design. Large LED loads, for instance, produce a lot of heat and therefore become the focus of thermal design. In cases where LEDs are the focus of thermal design, it is good practice to thermally couple the thermal pad of PowerPSoC to the heat sink used for the LEDs. However, ensure that there is electrical isolation.

**Note** Although it is recommended that other components should not be placed close to the device, there may be critical components that cannot be placed far away from the device due to electrical considerations. For example, in a dc-dc converter system the switching diode and inductor cannot be placed far away from the PowerPSoC device to optimize the high current loops. The system design must consider effects of all components on overall thermal performance.

**Recommendation:** Do not place components close to the device unless unavoidable. If unavoidable, carefully consider the effects of these components in your thermal analysis.

#### 2.5.3.6 Trace Length and Width

To effectively lower temperatures, longest and widest possible traces should be used. This facilitates maximum heat transfer away from the device. Again, it may not be possible to increase lengths for traces that connect critical components, due to electrical considerations. For example, the high current loops in a dc-dc converter cannot have long traces and should be routed using traces as short as possible. One way to improve thermal performance for this scenario is to make the traces wider.

**Recommendation:** Use long and wide traces whenever possible.

#### 2.5.3.7 Board Geometry and Aspect Ratio

Generally board geometries and aspect ratios are governed by system level and structural constraints. However, uniform geometries and aspect ratios enable effective electrical and thermal layouts facilitating optimum component placement.

For example, a 4" x 4" square PCB has better thermal performance when compared to a 1" x 16" PCB having the same surface area, assuming the heat source is at the center of the board.

**Recommendation:** Use uniform geometries and aspect ratios whenever possible.

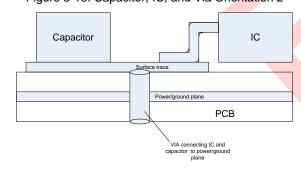

#### 2.5.3.8 Use of Additional Thermal Vias

Thermal vias, similar to the ones used for the thermal landing, can be used to connect internal and/or external thermal planes whenever electrically possible. This helps maximize the continuous copper plane area for heat conduction. Whenever possible, the overlap between planes should be maximized as shown in Figure 2-14.

**Note** Placing too many vias can hurt thermal performance because it depletes the continuous plane and may cause mechanical instability.

**Recommendation:** Use optimum number of vias to connect thermal planes and maximize overlap between thermal planes.

2.5.3.9 Use of Thermal Isolation Cuts [3] Sometimes the overall performance of the PCB of

Sometimes the overall performance of the PCB can be enhanced by carefully placing isolation cuts in the PCB to segregate components that can afford to run at higher temperatures. A component rated at a high temperature and dumping a lot of heat into the PCB can be isolated such that its heat does not affect other components that cannot tolerate high temperatures. Also, careful placement of components depending on the air flow direction can be made such that heat generating components are not placed upstream of other components.

**Recommendation:** These are advance techniques and should be carefully considered on a case-by-case basis. For thermally sensitive designs, a detailed thermal simulation should be performed.

#### 2.5.3.10 Effectively Coupling PCB to System Enclosure [3]

When the PCB is thermally saturated and the component temperatures are still too high, at the maximum obtainable system air velocity, other means of conducting heat from the PCB to even larger area system structures are required. The chassis or enclosure of the system, often the largest surface area structure in the system, is usually exposed to the ambient air. It often makes a good sink for heat that cannot be dissipated by the PCB alone. Mechanisms to conduct heat into the chassis or enclosure include chassis screws, gap fillers, connectors, and side rails.

**Recommendation:** Always try and thermally couple the PCB to the system chassis or enclosure to maximize heat conduction to the ambient.

# 2.6 Key PCB Manufacturing Considerations from a Thermal Standpoint<sup>[2, 4]</sup>

#### 2.6.1 Solder Mask

All copper areas should be covered by solder mask (to avoid electrical hazards), except:

- Thermal landing used to mount the device on the board

- Thermal copper pour on the bottom plane if an external heat sink needs to be attached

- Any copper required to couple the PCB to the system enclosure.

Opening solder masks may improve thermal performance, but safety considerations should take priority.

#### 2.6.2 Thermal Pad Connectivity

To ensure that heat is effectively removed from the package and to have a reliable electrical connection, the thermal pad must be soldered to the thermal landing. The amount of solder paste must be carefully controlled as less paste leads to voiding and more paste leads to the component floating in a pool of solder, causing bad pin to pad connectivity.

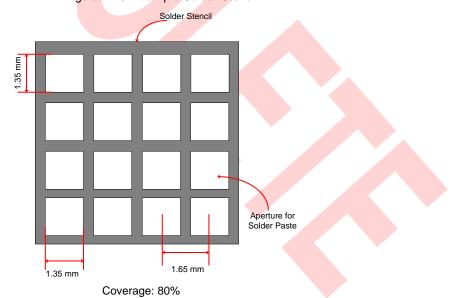

It is therefore recommended that a solder stencil with smaller multiple openings be used instead of one big opening. This results in 50 percent to 80 percent coverage. However, it is better to have about 75 percent coverage.

Figure 2-15 shows an example stencil with approximately 80 percent solder coverage. Area of the stencil matches the thermal pad area. It is good practice to X-RAY a few boards initially, to ensure the manufacturing process results in minimum voids at the interface junction between the PowerPSoC and the PCB.

Figure 2-15. Example Solder Stencil

#### 2.6.3 Thermal Via Fill Material

Thermal vias plated with copper must be filled with solder because it minimizes wicking and improves conductivity. If further reduction in thermal resistance is required, vias can be filled with copper or any of the thermally conductive materials available. Filling vias however, is expensive and is only recommended for highly sensitive designs where the added cost is bearable.

Equation 7

# 2.7 Illustrated Step-by-step Thermal Calculations

Consider a dc-dc LED driver system rated to deliver a maximum power of 20 W to the load. dc-dc switching power converters have conversion efficiencies above 90 percent; however, let us consider a conservative system efficiency of 85 percent. This results in a worst-case power dissipation of approximately 3.53 W. Depending on the choice of external components (low dissipation), switching frequency (high), and operating conditions (high duty ratio), there is a possibility that 90 percent of the total system power loss could happen in the PowerPSoC device alone. Hence, the worst-case power loss for PowerPSoC is 3.2 W.

As shown in Figure 2-1, the primary heat transfer path for the PowerPSoC is through the thermal vias and eventually through the PCB into the surroundings by means of conduction, convection, and radiation. This path primarily constitutes two thermal resistances:  $\theta_{JS}$  and  $\theta_{BA}$ .  $\theta_{JS}$  is specified as 2 °C/W for PowerPSoC.  $\theta_{BA}$  is a complex resistor because it depends on various PCB design characteristics as discussed earlier. The system designer has control over this resistance and to optimize heat transfer, this resistance must be optimized.

As shown in Figure 2-16,  $\theta_{BA}$  is further broken up into four lumped resistors (for simplicity):

$$\theta_{\rm BA} = \theta_{\rm BB} + \theta_{\rm cond} + (\theta_{\rm conv} // \theta_{\rm rad})$$

Where:

$\theta_{BB'}$  = Thermal resistance of the thermal via array along the thickness of the board (B-B').

$\theta_{cond}$  = Lumped resistance of the PCB along the surfaces. This governs lateral heat conduction through the PCB.

**Note** The value of this resistor is optimistic because it is based on simplified assumptions. PCB spreading resistance effects and effects of traces are not considered.

$\theta_{conv}$  = Lumped thermal resistance due to natural convection of heat from the PCB to the ambient.

$\theta_{rad}$  = Lumped thermal resistance due to radiation of heat from the PCB to the ambient.

The last two resistances act as parallel paths for heat dissipation, with convection path as the more dominant path.

Figure 2-16. Primary Heat Transfer Path

The steps to calculate each part of  $\theta_{BA}$  follows:

#### Step 1: Calculating θ<sub>BB</sub>

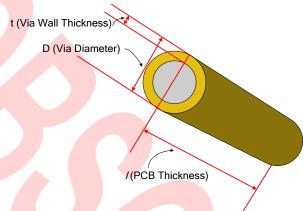

For PowerPSoC, it is recommended to have 36 thermal vias with diameter of ~0.25 mm. Via length is the same as the PCB thickness of 1.52 mm. Assume the via is plated to 1 oz copper (thickness: 0.036 mm) and internally filled with solder.

Figure 2-17. Thermal Via Dimensions

Using thermal conductivity for copper of 0.386 W/mm°C and 0.050 W/mm°C for solder. The thermal resistance of a single via is calculated as follows:

$$\theta_{VIA,solder} = \left(\frac{l}{k_{solder} * \Pi * \left(\frac{D-2*t}{2}\right)^2}\right)$$

$$\theta_{VIA,wall} = \left(\frac{l}{k_{cu} * \Pi * \left(\left(\frac{D}{2}\right)^2 - \left(\frac{D-2*t}{2}\right)^2\right)}\right)$$

Equation 9

$$\theta_{VIA} = \theta_{VIA,solder} \mid\mid \theta_{VIA,wall}$$

Equation 10

#### Where:

$\theta_{VIA,wall}$  = thermal resistance of the via wall.

$\theta_{VIA,solder}$  = thermal resistance of solder fill in the via.

$\theta_{VIA}$  = thermal resistance of a single copper plated, solder filled via.

$k_{cu}$  and  $k_{solder}$  = thermal conductivity for copper and solder.

Other variables, as described in Figure 2-17.

Using Equations 8, 9, and 10,  $\theta_{VIA}$  is 143.5 °C/W. Note that this figure is dominated by  $\theta_{VIA,wall}$  which is 162.7 °C/W and the solder fill plays a limited role in reducing the thermal resistance further. Thermal resistance can be further reduced by increasing plating thickness or filling the vias with copper or any other thermally conductive material.

Finally, the thermal resistance for the entire array can be thought of as a parallel network of 36 such single via resistances.

Hence  $\theta_{BB'} = 3.99$  °C/W.

#### Step 2: Calculating θ<sub>cond</sub>

As described earlier, lateral thermal resistance for a PCB can be estimated using the formula:

$$\theta_{PCB} = \left(\frac{l}{k_{eff}A}\right)$$

Equation 11

Where:

$\theta_{PCB}$  = The lumped 1D lateral resistance of the PCB surfaces.

k<sub>eff</sub> = The effective thermal conductivity of the medium (PCB in our case).

A denotes the surface area of the medium normal to the direction of heat transfer. In the example case, it is the product of length and PCB thickness.

$\ell$  = The thickness of the medium.

#### Step 3: Calculating θ<sub>conv</sub> and θ<sub>rad</sub>

As almost 96 percent of the heat in PowerPSoC is transferred through the thermal via array, eventually, majority of it is conducted through the PCB. Heat transfer by natural convection and radiation is minimal and can be neglected for simplicity. However, equations are provided for both natural convection and radiation. Detailed calculations are beyond the scope of this chapter. Refer to References [5] for details.

$$\theta_{conv} = \left(\frac{1}{h_{conv} * A_{surf}}\right)$$

Equation 12

$$\theta_{rad} = \left(\frac{1}{h_{rad} * A_{surf}}\right)$$

Equation 13

Where:

$h_{conv}$ ,  $h_{rad}$  = The convection and radiation heat transfer coefficients.

A<sub>surf</sub> = The heat transfer surface area.

Now that we are equipped with all the basic tools, let us get back to the example. Assume the device junction is at 90 °C and work our way outwards using Equation 2. The heat flow is through the series network of  $\theta_{\rm US}$  (2 °C/W) and  $\theta_{\rm BB}$  (3.99 °C/W) and with a power dissipation of 3.2 W, results in a board temperature (at a point on the bottom layer, just below the device) of ~71 °C. Furthermore, using the PCB as a heat sink further cooling is provided by means of conduction, convection, and radiation to ensure that the  $\theta_{\rm PCB}$  allows maintaining this PCB temperature (~71 °C) at the worst case ambient temperature.

# 2.8 Summary

With systems increasing in power densities, it is important for system designers to think about thermal analysis as early as the initial design phase rather than treat it as an afterthought.

The thermal model for the device and one-dimensional (1D) equations for heat transfer provide a good tool for first pass thermal performance estimation. Based on this first pass analysis, the system designer may decide to perform detailed thermal modeling and simulation for the system before making crucial design decisions.

In PowerPSoC based designs, the PCB can and must be effectively used as a heat sink. PCB layout should not only consider electrical performance, but also the thermal performance of the system.

At times the designer must consider thermal versus electrical layout recommendations, which may be conflicting. Depending on the overall impact, either the thermal or the electrical recommendation can take priority.

#### 2.9 Disclaimer

The techniques presented in this chapter are only meant for first pass thermal estimation. There is no single generalized method to calculate the combined impact of all the variables. Therefore, system designers are encouraged to use sophisticated CFD tools to model final component temperatures for their particular systems.

The chapter focuses primarily on the use of PCB as a heat sink. If using the PCB as a heat sink is not sufficient, other cooling techniques may have to be considered. These techniques are beyond the scope of this document.

In this document, "system" refers to a dc-dc converter. For systems having higher integration levels such as ac-dc circuitry or LED loads on the same PCB, techniques presented in this chapter may not apply. The focus of thermal analysis in this document revolves around PowerPSoC being the primary heat source.

Topics such as use of external heat sinks, forced convection, thermal interface materials, and specialized metal boards, are beyond the scope of this chapter.

#### 2.10 References

- 1. Relevant Standards: JESD51, JESD51-1, JESD51-2, JESD51-3, JESD51-5, and JESD51-7, available at www.jedec.org

- 2. Application Note: Surface Mount Assembly of Amkor's MicroLeadFrame Packages Amkor Technology, September 2008

- 3. Chapter 17: Printed Circuits Handbook (McGraw Hill Handbooks) 6<sup>th</sup> Edition, Darwin Edwards, Clyde F. Coombs, Jr., 2008

- 4. Application Note: Thermal Considerations for QFN packaged Integrated Circuits Circus Logic, July 2007

- Chapter 15: Heat Transfer A Practical Approach (McGraw Hill Science) 2<sup>nd</sup> Edition, Yunus A. Cengel, August 2002

# 3. PowerPSoC® PCB Design Guidelines for LED Driver Circuits

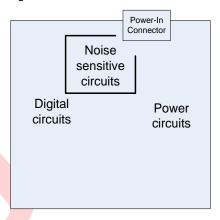

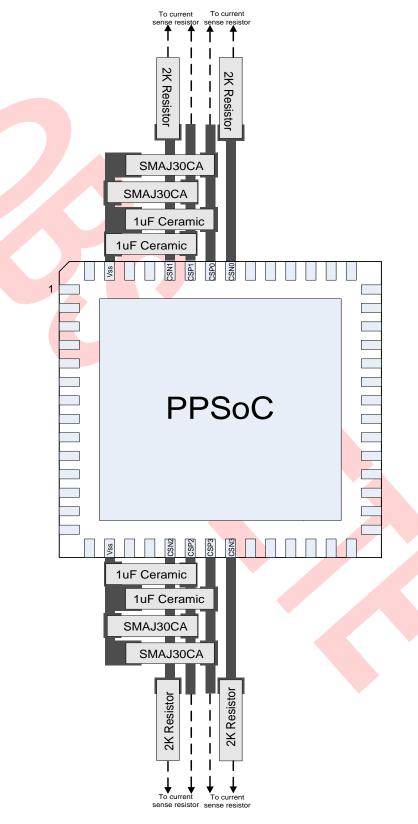

This chapter discusses component placement, signal routing, power routing, power paths, and thermal dissipation in the design of PCBs for LED drivers. The same guidelines apply for single or multiple LED drivers using a single PowerPSoC. Each section provides information on specific needs during the design process.

It is necessary for a PCB designer to understand that each circuit and design has its own critical parameters. A LED driver circuit is no exception, as there are significant levels of current flowing and switching throughout the circuit.

To understand an LED driver circuit, consider a switching voltage regulator. The difference between a switching voltage regulator and an LED driver is that a switching voltage regulator controls an output voltage, while an LED driver controls an output current.

For designers familiar with switching voltage regulator design, designing a power-LED driver using PowerPSoC should be an easy process, because many of the guidelines for a successful design are identical.

Even for designers less familiar with power electronics design, the PowerPSoC simplifies most of the design with its high integration of power components.

This chapter starts with a generic list of guidelines. These guidelines are explained in detail using an example of a single-channel floating-buck LED driver. Single-channel Boost LED driver, single channel Buck-Boost LED driver, and a four-channel LED driver design are all described subsequently in this document.

#### 3.1 Guidelines and Checklist

Following are the key guidelines that can also serve as a checklist for PCB layout using the PowerPSoC:

- 1. Component selection and placement

- Place key components close to each other

- a. Look for critical triangle

- Use Kelvin sense resistor

- Use appropriate power filters (ferrite beads)

- Use test points at signals of interest, place them appropriately and match with ground test points

- 2. PCB selection and trace routing

- Use copper sized for power

- Use copper pours and copper thieving

- Optimize via usage for power, control and signals

- Optimize trace length and routing

- Evaluate current loops

- a. Look for critical loops

- Kelvin sense lines routed differentially

- Kelvin sense lines isolated from cross coupling

- Grounding

- Digital, analog, power, and star ground

- Consider return (ground) current

- Follow power and ground guidelines

- 4. Thermal aspects

- Evaluate power losses in key components

- Evaluate thermal dissipation

- These guidelines are explained below using the example of a floating-buck LED driver.

### 3.2 Floating-Buck LED Driver

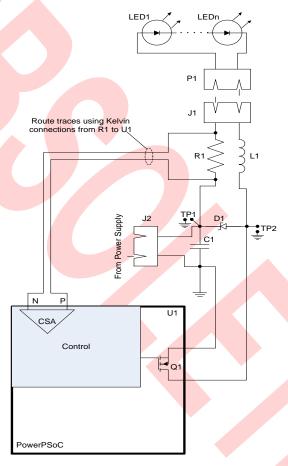

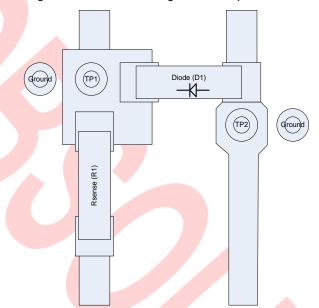

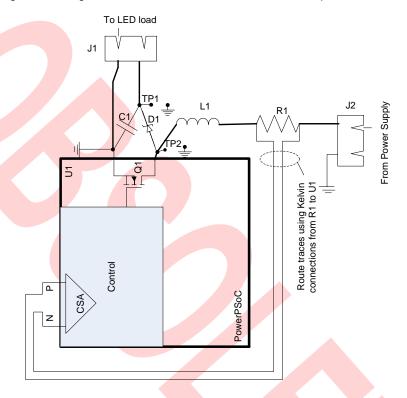

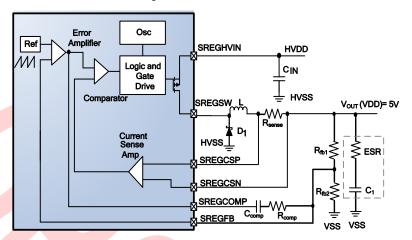

Figure 3-1. Single Channel Floating-Buck LED Driver

Figure 3-1 shows a generic diagram for a single channel floating-buck LED driver. The channel power components consist of

- Decoupling capacitor (C1),

- Sense resistor (R1),

- LED load (LED1 through LEDn),

- Freewheeling diode (D1),

- Inductor (L1), and

- Low side N-Channel MOSFET (Q1, which is within PowerPSoC)

Also shown are input power connector (J2), LED load connector (P1 and J1), test points (TP1 and TP2), and PowerPSoC LED controller (U1). For the purpose of this chapter, consider Q1 as separate from U1 when, in fact, Q1 is part of U1 (PowerPSoC).

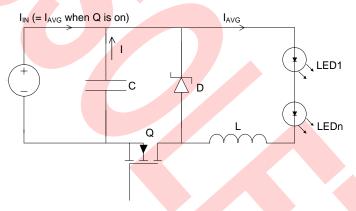

This LED driver has two operating modes, when Q1 is ON and when Q1 is OFF.

When Q1 is ON, the flux on L1 builds and the current loop is from C1, through R1, through LED load, through L1, through Q1, and finally back to C1. This loop is 'Current Loop: FET ON' (see Figure 3-2).

When Q1 is OFF, the flux on L1 decreases and the current loop is C1, through R1, through LED load, through L1, through D1, and back to C1. This loop is 'Current Loop: FET OFF' (see Figure 3-2).

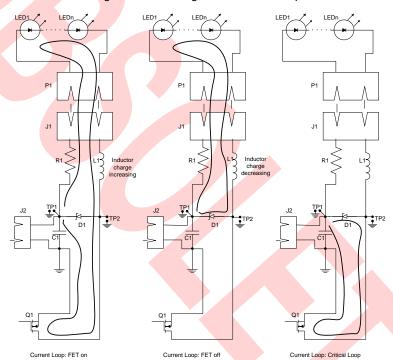

The third loop in shown Figure 3-2 is 'Current Loop: Critical Loop' is the area that must have close attention during component placement. Three components Q1, C1, and D1 form a "Critical Triangle" defining the critical loop. Keeping this triangle small is critical, as it is where the power switching is most evident. When Q1 is ON, all the current flows through Q1 and ground, back to C1 and no current flows through D1; alternatively, when Q1 is OFF, all the current flows through D1 and none through Q1.

The critical triangle area is where the transition between the two modes happens. Minimizing the critical loop area reduces the ground bounce. Ground bounce is undesirable as it can cause system accuracy and stability problems.

Figure 3-2. Floating-Buck Current Loops

# 3.3 Components Guidelines

This section discusses placement of key components, Kelvin sense resistor connections, test point placement, and test point placement for ground.

#### 3.3.1 Place Key Components Close to Each Other

In Figure 3-1, C1, D1, and Q1 define the critical triangle area. For these three components, place them close to each other, on the same side of the PCB, use no vias, and keep the copper interconnects short.

Figure 3-3 is similar to Figure 3-1, which is redrawn allowing the critical triangle relationship of C1, D1, and Q1 to be easily portrayed in a schematic representation.

Figure 3-3. Single Channel Floating-Buck Redrawn for Relative Component Association

#### 3.3.2 Test Points at Signal of Interest

In Figure 3-3, test points (TP1 and TP2) are close to the points in the circuit being measured. This is to highlight the need to place a test point connection as close to the measured point as possible.

Figure 3-4 shows a poor placement of test points in layout. In this diagram, placement of TP1 is not correct as it is at the end of a long trace. The use of a long trace connecting a test point to the point of interest causes problems with signal reflection and acts as an antenna on the PCB - radiating signals to surrounding systems. The importance of not creating antennas is very critical, especially with signal nets that have large dv/dt. Placement of TP2 is also not correct, as it is not near the anode of D1.

Figure 3-4. Test Point Usage - Poor Implementation

Figure 3-5 shows good placement of test points. In this diagram, the placement of TP1 and TP2 are correct according to the schematic that is showing TP1 close to the junction of R1 and D1, and TP2 is near the anode of D1.

Often, test points are accommodated as an afterthought on the layout and this can lead to poor implementation as shown in Figure 3-4. In such cases, having test points is worse than not having test points. It is preferable to have test point planning integral to the layout plan so that right trade-offs can be made.

Figure 3-5. Test Point Usage - Good Implementation

#### 3.3.3 Test Points Matched with Ground Test Points

In Figure 3-1, there is a ground connection shown near each test point. This is to highlight the need to place a ground test point connection as close to the test point as possible and not to use a long (3-6 inch) ground lead. Check your test equipment specification to determine the spacing recommended for test signal to ground.

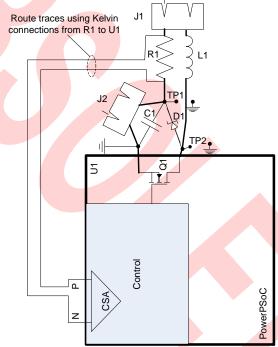

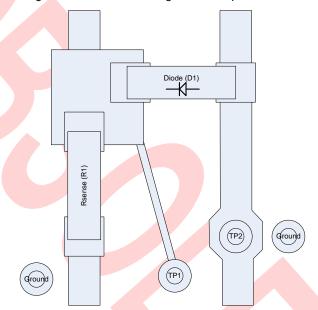

#### 3.3.3.1 Use Kelvin Sense Resistor

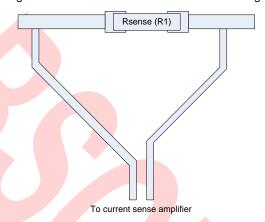

In Figure 3-1, a note for the connections from R1 to U1 indicates 'route traces using Kelvin connections', Figure 3-6 and Figure 3-7 show two implementations of Kelvin sense lines.

Figure 3-6 shows an incorrect design for Kelvin sense lines. The connections for the sense lines are not located at the pads of  $R_{\text{sense}}$ . As the Kelvin sense lines measure a small voltage across a small resistance (0.1 to 0.2  $\Omega$  typical); any small resistance in the trace between the Kelvin connection and the  $R_{\text{sense}}$  component also has a small voltage drop across it. That additional drop causes measurement errors.

Figure 3-6. Kelvin Sense Lines - Incorrect Design

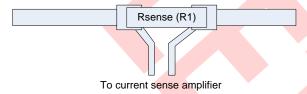

Figure 3-7 shows a correct design for Kelvin sense lines. The connections for the sense lines are located at the inner edge of the pads of  $R_{\text{sense}}$ . This is the best connection point for the Kelvin sense lines, as the voltage measured is the voltage developed across  $R_{\text{sense}}$ .

Figure 3-7. Kelvin Sense Lines - Correct Design

# 3.4 Boost Topology

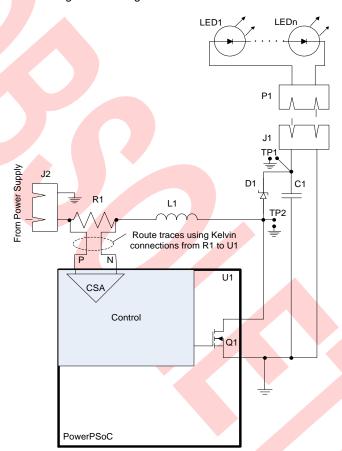

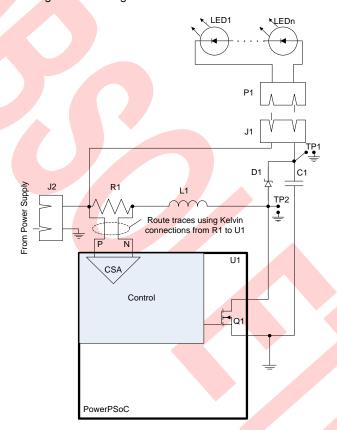

Figure 3-8 shows a generic diagram for a single channel boost LED driver. The channel power components (same as floating-buck LED driver) consist of decoupling capacitor (C1), sense resistor (R1), LED load (LED1 through LEDn), freewheeling diode (D1), inductor (L1), and low side N-Channel MOSFET (Q1). Also shown are input power connector (J2), LED load connector (P1 and J1), test points (TP1 and TP2), and PowerPSoC LED controller (U1).

Figure 3-8. Single Channel Boost LED Driver

In Figure 3-8, C1, D1, and Q1 define the critical triangle area. For these three components, place them close to each other, on the same side of the PCB, use no vias, and keep the copper interconnects short.

Figure 3-9 is similar to Figure 3-8, which is redrawn to portray the critical triangle relationship of C1, D1, and Q1 in a schematic representation.

The critical triangle components are arranged in the same manner as in a floating-buck LED driver.

Figure 3-9. Single Channel Boost Redrawn for Relative Component Association

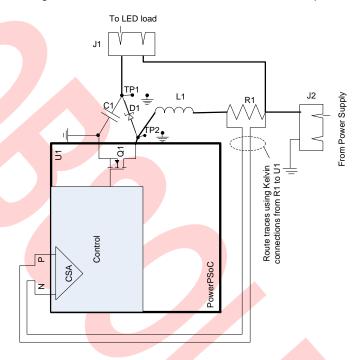

## 3.5 Buck-Boost Topology

In Figure 3-8, C1, D1, and Q1 define the critical triangle area. For these three components, place them close to each other, on the same side of the PCB, use no vias, and keep the copper interconnects short.

Figure 3-10 shows a generic diagram for a single channel buck-boost LED driver. The channel power components (same as floating-buck LED driver) consist of decoupling capacitor (C1), sense resistor (R1), LED load (LED1 through LEDn), freewheeling diode (D1), inductor (L1), and low side N-Channel MOSFET (Q1). Also shown are input power connector (J2), LED load connector (P1 and J1), test points (TP1 and TP2), and PowerPSoC LED controller (U1).

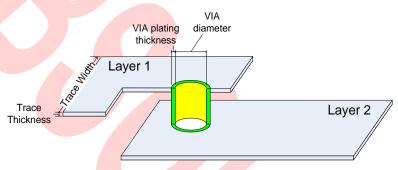

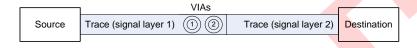

Figure 3-10. Single Channel Buck-Boost LED Driver