# Developing high-performance graphics with low-power optimization on PSOC™ Edge MCU

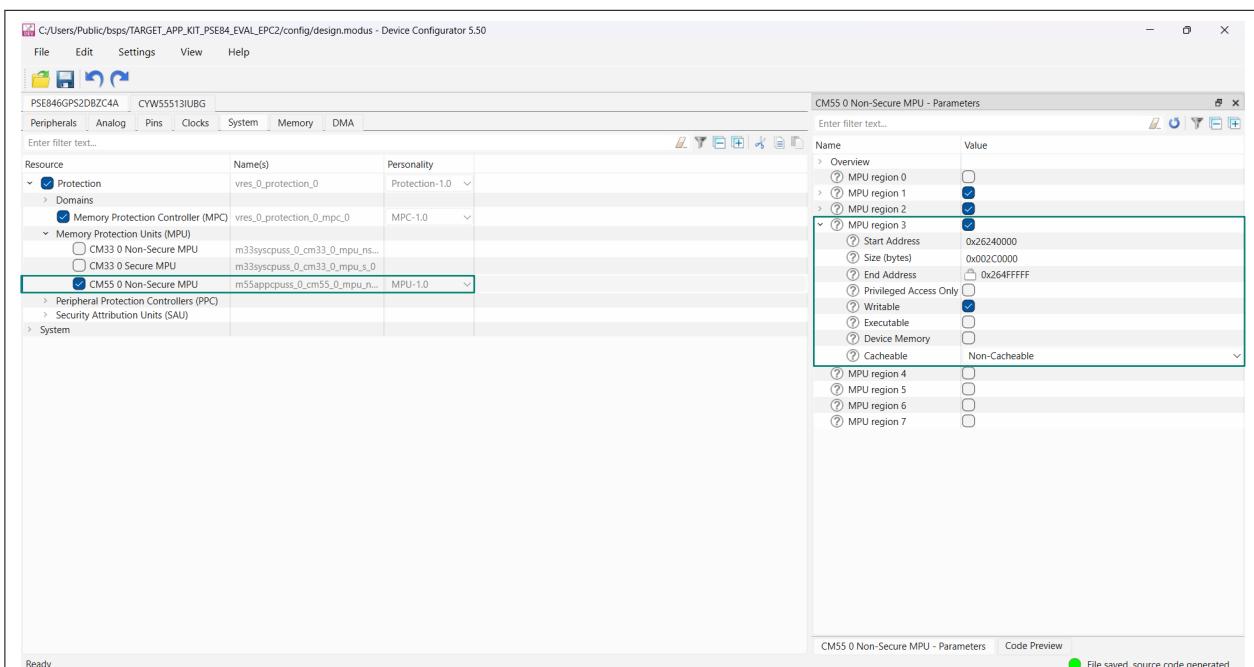

## About this document

### Scope and purpose

This application note guides developers in designing advanced, high-performance GPU graphics applications with a focus on low-power optimization for the PSOC™ Edge MCU. Developers will learn how to configure the graphics subsystem, balance power and performance, and apply proven optimization techniques. The document explains how to measure and reproduce performance metrics, and provides practical API references and code snippets tailored to the target audience. The practical guidance and implementation-focused insights covered in this application note enables developers to create graphics solutions that are both powerful and energy-efficient for modern embedded applications.

### Intended audience

This application note is tailored for hardware and software engineers, and system architects who are involved in the design and development of graphical applications using the PSOC™ Edge MCU.

### Table of contents

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| <b>About this document</b>                                                   | 1  |

| <b>Table of contents</b>                                                     | 2  |

| <b>1 PSOC™ Edge graphics subsystem overview</b>                              | 4  |

| <b>2 System architecture</b>                                                 | 5  |

| <b>3 Creating a graphical application with PSOC™ Edge MCU</b>                | 6  |

| 3.1 Identifying graphical application requirements                           | 6  |

| 3.2 Matching display resolution and color depth to hardware configuration    | 6  |

| 3.2.1 Framebuffer memory size requirements and location                      | 6  |

| 3.2.2 Verifying display compatibility based on memory bandwidth requirements | 7  |

| 3.2.3 Verifying display interface compatibility                              | 7  |

| <b>4 Graphics subsystem and display configuration</b>                        | 9  |

| 4.1 Clock configuration                                                      | 9  |

| 4.1.1 System and high frequency main clocks                                  | 9  |

| 4.1.2 DSI host clock                                                         | 11 |

| 4.2 Display type and interface                                               | 12 |

| 4.2.1 MIPI DSI video mode                                                    | 12 |

| 4.2.1.1 Setting up video timings per display resolution                      | 16 |

| 4.2.2 MIPI DSI command mode                                                  | 20 |

| <b>5 GPU configuration</b>                                                   | 23 |

| <b>6 Display controller configuration</b>                                    | 24 |

| 6.1 Three programmable DC layers                                             | 24 |

| 6.2 RLAD decoder                                                             | 27 |

| 6.2.1 Use case and application benefits                                      | 27 |

| 6.2.2 RLAD encoder tool                                                      | 28 |

| 6.2.3 RLAD decoder configuration                                             | 28 |

| <b>7 MIPI DSI host and D-PHY configuration</b>                               | 32 |

| 7.1 DSI host PHY parameters                                                  | 32 |

| <b>8 Interrupts</b>                                                          | 36 |

| <b>9 Functional analysis</b>                                                 | 39 |

| 9.1 High-performance graphics optimization                                   | 39 |

| 9.1.1 Use the 2.5D GPU effectively                                           | 39 |

| 9.1.2 Memory strategy for graphics                                           | 40 |

| 9.2 Low-power graphics optimization                                          | 43 |

| <b>10 Performance evaluation</b>                                             | 44 |

| 10.1 Power domains and current measurement jumpers                           | 44 |

| 10.2 Power consumption and frame rate                                        | 45 |

---

**Table of contents**

|        |                                           |    |

|--------|-------------------------------------------|----|

| 10.2.1 | Application state: High performance ..... | 49 |

| 10.2.2 | Application state: Low power .....        | 55 |

| 10.2.3 | Application state: Ultra-low power .....  | 61 |

|        | <b>Summary .....</b>                      | 63 |

|        | <b>References .....</b>                   | 64 |

|        | <b>Revision history .....</b>             | 65 |

|        | <b>Trademarks .....</b>                   | 66 |

|        | <b>Disclaimer .....</b>                   | 67 |

## 1 PSOC™ Edge graphics subsystem overview

### 1 PSOC™ Edge graphics subsystem overview

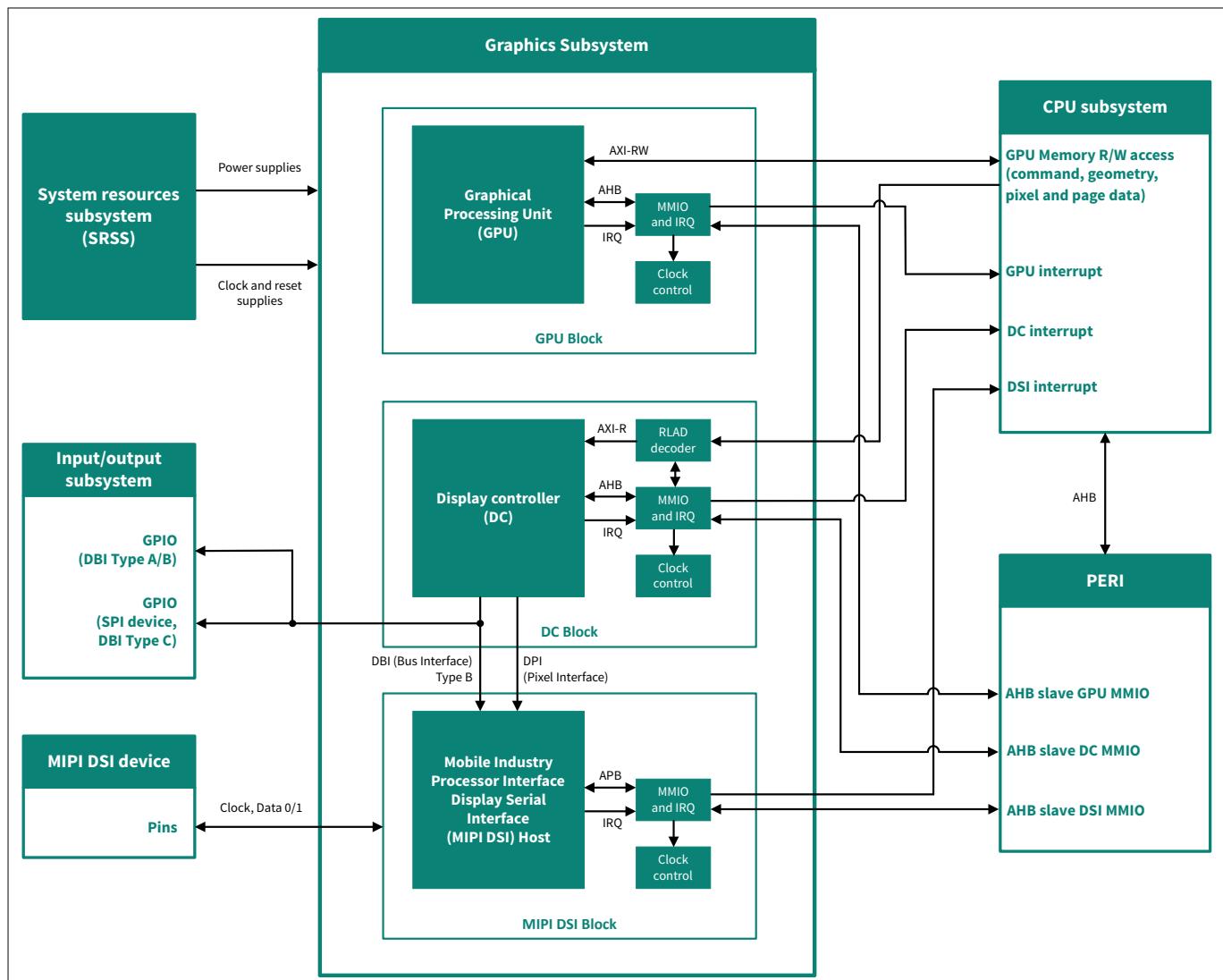

PSOC™ Edge MCU comprises a high-performance and low-power graphics subsystem to enable human machine interface (HMI)-based application development.

The graphics subsystem of the PSOC™ Edge E84 MCU consists of the following three blocks:

1. 2.5D graphics processing unit (GPU)

2. Display controller (DC)

3. Mobile Industry Processor Interface Display Serial Interface (MIPI DSI) host controller

The following [Figure 1](#) illustrates the architecture of the graphics subsystem, showcasing its various blocks and their arrangement.

Figure 1 Graphics subsystem architecture

## 2 System architecture

### 2 System architecture

The PSOC™ Edge MCU is a dual-CPU microcontroller featuring a Cortex®-M33 and a Cortex®-M55 core, with internal volatile memories including 1 MB of internal SRAM, ITCM, and DTCM on the CM55 side, and 5 MB of system SRAM shared between both cores.

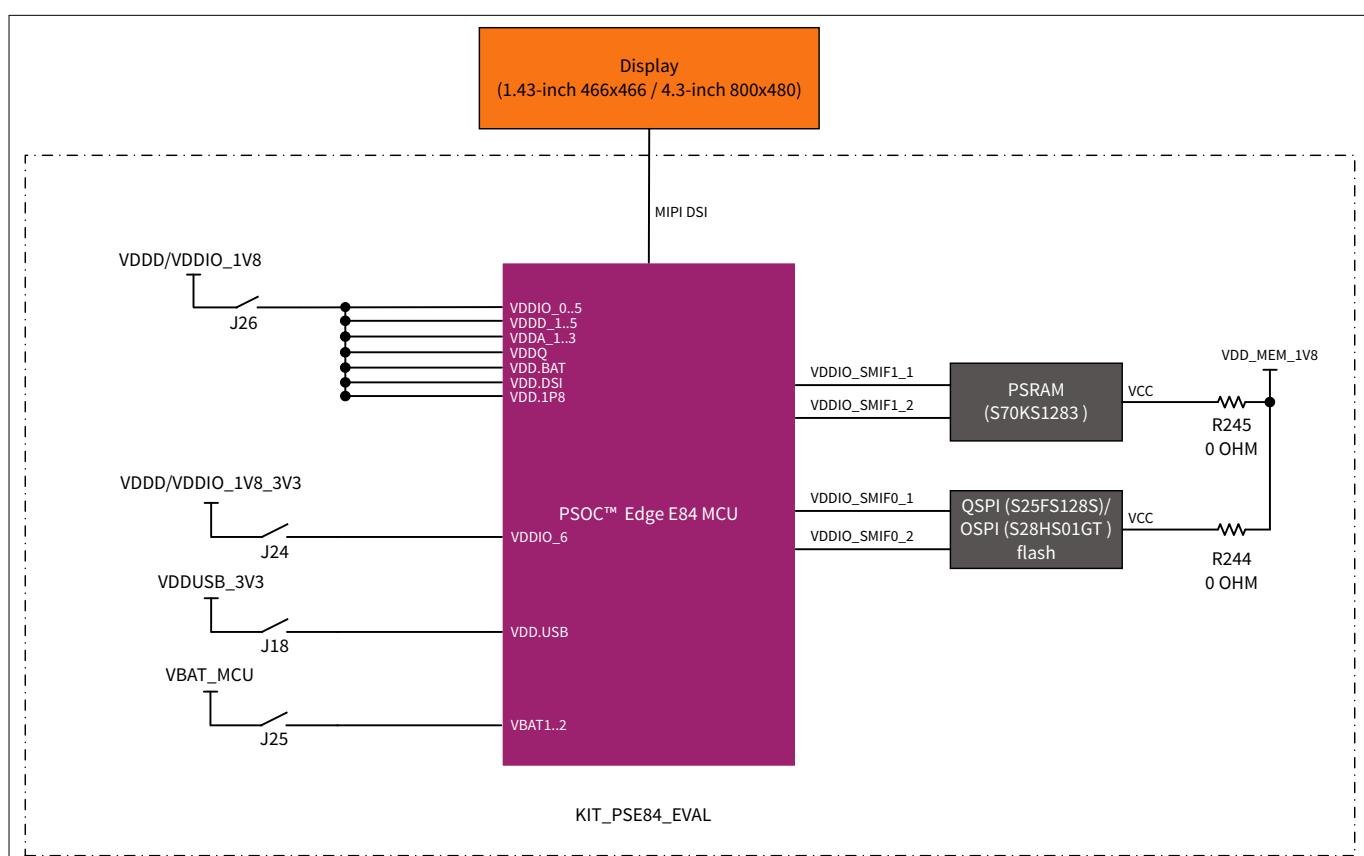

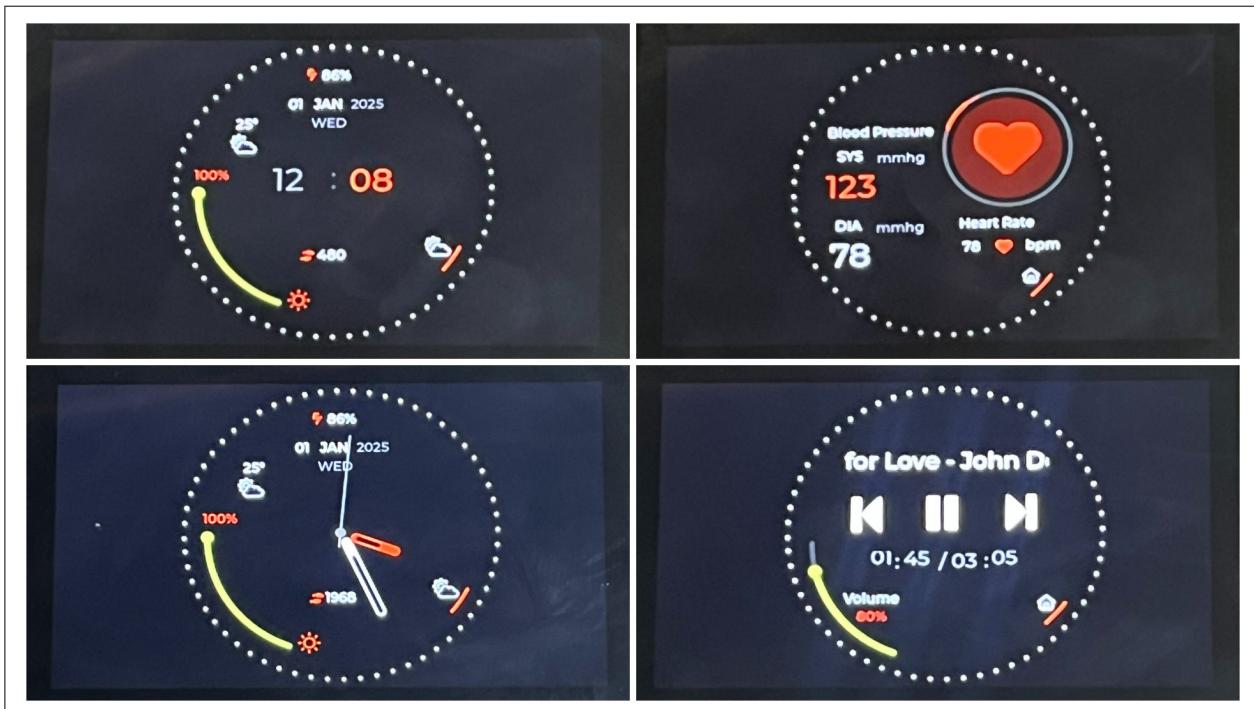

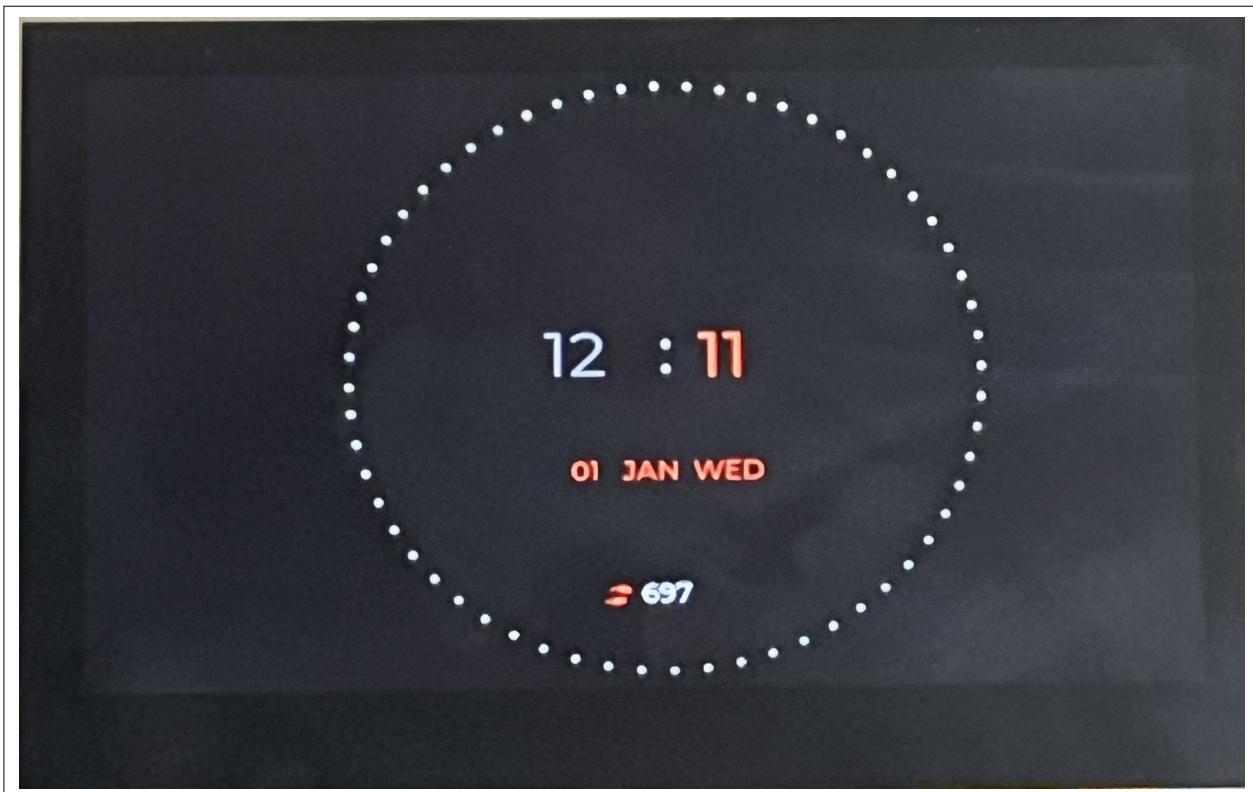

This application note uses the smartwatch code example running on the PSOC™ Edge E84 Evaluation Kit (KIT\_PSE84\_EVAL) to demonstrate end-to-end graphics rendering on MIPI DSI display panels and to evaluate the graphics subsystem's performance and power consumption. The document focuses on two representative targets: a 1.43-inch, 466×466 command-mode wearable panel driven by CO5300 display controller and a Waveshare 4.3-inch, 800×480 video-mode panel. Configuration steps, timing/clocking, and optimization techniques are presented in the context of these displays, providing repeatable measurements and practical guidance for both high-performance and low-power graphics use cases. For more information on these display panels, please refer to the smartwatch code example [readme](#).

The KIT\_PSE84\_EVAL offers PSRAM, quad and octal NOR flashes connected to PSOC™ Edge MCU via SMIF interface, as shown in block diagram (Figure 2). Additionally, the KIT\_PSE84\_EVAL board can be connected to different DSI display panels.

The 16 MB S70KS1283 PSRAM connected via SMIF 1 interface features an octal SPI interface that supports a maximum of 200 MHz DDR access. It can be utilized for frame buffers but is primarily used for data storage, particularly for large and infrequently accessed data.

Both 16 MB S25FS128S QSPI and 128 MB S28HS01GT OSPI NOR flashes, connected via SMIF 0 interface, are used for code execution and persistent data storage.

**Figure 2** KIT\_PSE84\_EVAL block diagram (on-board memory and display)

**Note:** At any given time, either QSPI or OSPI flash can be utilized as they share the same SMIF 0 interface with the PSOC™ Edge MCU.

### 3 Creating a graphical application with PSOC™ Edge MCU

## 3 Creating a graphical application with PSOC™ Edge MCU

This section outlines the steps required before and during the development of a graphical application using the PSOC™ Edge MCU. First, identify the application's requirements, then verify whether the chosen display is compatible with the hardware configuration.

### 3.1 Identifying graphical application requirements

Identifying the requirements of the graphical application is an essential first step. Before development, establish the key parameters such as display resolution, color depth, and the type of data to be displayed (static images, text, or animation). After defining these fundamental parameters, assess the graphical hardware architecture of the application and the necessary hardware resources by considering the following:

- Is external memory needed for the framebuffer like PSRAM?

- Is the external memory interface bus width sufficient?

- Is the DC interface set to RGB565 or ARGB8888 depending on the target application requirement and display module?

- Is external memory needed to store graphic primitives like QSPI or OSPI flash?

- Is the display type aligned with supported display interface standards such as MIPI DBI, MIPI DPI, and MIPI DSI?

- Is the required FPS within the bandwidth supported by the display panel?

### 3.2 Matching display resolution and color depth to hardware configuration

When kicking off an PSOC™ Edge based graphics project, the target display resolution and color depth are often predetermined. The critical checkpoint is verifying that these choices are practically feasible on the intended hardware platform. To make that determination:

1. Calculate the framebuffer footprint and decide where it will reside in memory

2. Ensure the display's refresh rate and resolution match the available framebuffer memory bandwidth

3. Validate the compatibility of the display panel interface with the MIPI DSI host and the display controller (DC)

The following sections break down each points and present recommended actions and examples to support application.

#### 3.2.1 Framebuffer memory size requirements and location

Determining the framebuffer memory size and location is crucial for display compatibility. The memory space needed for the framebuffer must be contiguous and is calculated by multiplying the display's resolution (width x height) by its color depth (bits per pixel), then divided by 8 to convert to bytes. For example:

Resolution: 800 x 480 pixels

Color depth: 16 bpp (which is 16 bits)

Memory space required:  $(800 \times 480 \times 16) / 8 = 768,000$  bytes

It is not necessary for the framebuffer color depth to match the display color depth; for example, an RGB888 display can use an RGB565 framebuffer.

**Note:** *The required framebuffer size is doubled for double-buffer configurations, commonly used in graphics applications where one buffer holds the current image while the other prepares the next.*

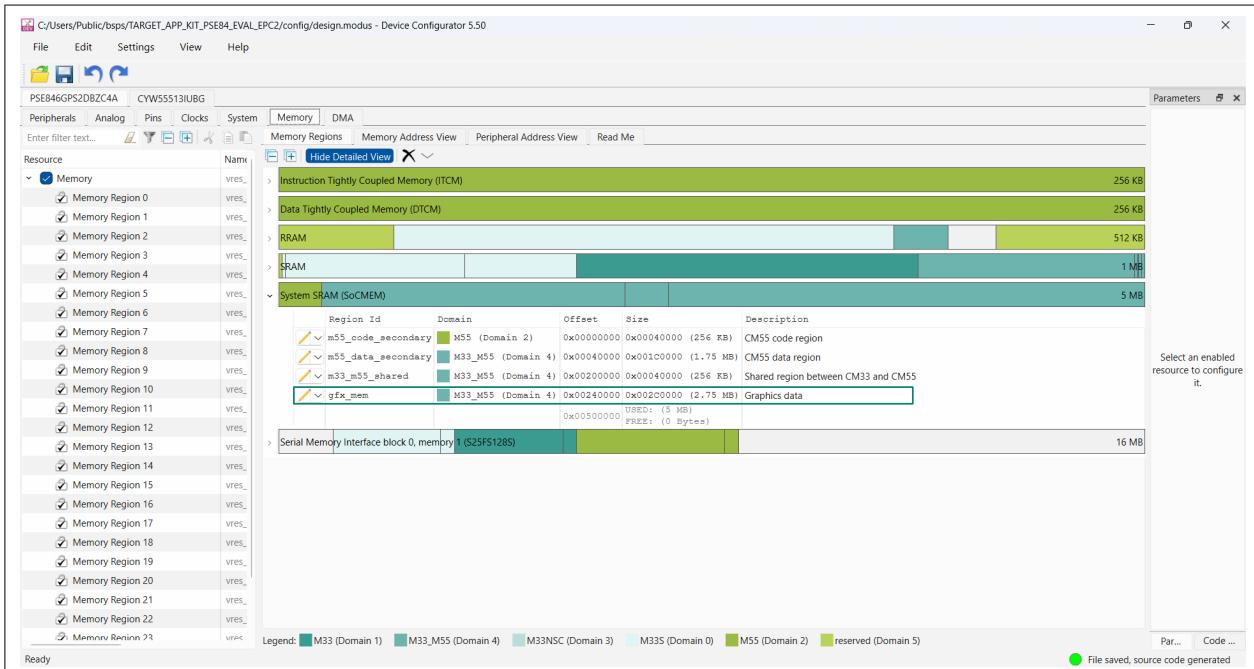

Depending on the required framebuffer size, the framebuffer can be located either in an internal SRAM (SRAM, System SRAM) or in an external memory such as PSRAM connected to the SMIF interface.

## 3 Creating a graphical application with PSOC™ Edge MCU

Using internal system SRAM instead of an external memory offers several advantages:

- Using an internal system SRAM as a framebuffer allows the maximum performances and avoids any bandwidth limitation issues for the GPU and DC

- Significantly higher throughput with zero wait-state access

- Reduces pin counts and lowers BOM cost when internal memory is adequate, eliminating the need for external memory

The only limitation of the internal system SRAM is its size, especially when it is shared among other application functions, such as for Machine Learning (ML) use cases. When the framebuffer size exceeds available memory, the external memory (via the SMIF interface) must be utilized. However, users should consider the potential bandwidth limitations with external memories. Refer to [AN239774](#) for more information on the selection and configuration of the various available memories on the PSOC™ Edge MCU.

### 3.2.2 Verifying display compatibility based on memory bandwidth requirements

This section outlines key bandwidth aspects and explains how to determine the bandwidth requirements based on the pixel clock, GPU, and DC. It also presents a straightforward method to assess whether a desired display size is compatible with a specific hardware configuration.

- **Memory bandwidth aspect**

To determine if the selected graphics memory bandwidth can support the GPU and DC required bandwidth, account for any concurrent memory accesses. Generally, a small framebuffer and GPU heap in internal system SRAM do not demand high bandwidth due to its low pixel clock, resulting in lower GPU and DC required bandwidth. A more complex scenario arises when the framebuffer and even GPU heap is in external memory

- **Memory bus concurrency**

- DC, GPU, and CPU masters

In a typical graphic application that uses an external memory for graphics memory, two or three main AHB masters concurrently use the same memory. The GPU or CPU updates the next image to be displayed while the DC fetches and renders the graphics frame. The memory bus load depends mainly on the GPU and DC required bandwidth.

- Other AXI/AHB masters

External memory is often shared by multiple masters, not just those for graphics. This concurrency can create a heavy bus load, impacting graphic performance

- **External PSRAM memory bus width**

When locating the framebuffer and GPU memory in external PSRAM, consider that the external memory's running frequency is approximately half of the system frequency. As a result, the memory bandwidth is often regarded as the bottleneck of the entire graphics system. Concurrent access by multiple masters to the same external memory results in increased latency and affects its throughput

### 3.2.3 Verifying display interface compatibility

After addressing display resolution, color depth, and memory, select the display panel by aligning PSOC™ Edge's interfaces (MIPI DBI A/B/C, MIPI DPI, MIPI DSI) with UI dynamics, bandwidth, memory, pin budget, and power targets. Generally, choose DBI for low-power partial updates using the panel's GRAM, DPI for continuous pixel streaming with deterministic timing, and DSI for higher bandwidth over fewer pins, using command-mode for sparse updates or video-mode for fluid animation.

Here are the key points to consider when finalizing the display based on the available display interfaces from PSOC™ Edge.

## 3 Creating a graphical application with PSOC™ Edge MCU

- MIPI DBI A/B (parallel 68xx/8080) and DBI-C (serial SPI/QSPI)

- Best for small/medium resolutions, static UIs, and partial updates; uses panel GRAM

- Low pin count (DBI-C) or moderate (A/B); lowest average power (link idles)

- Bandwidth-limited for full-screen 60 Hz; rely on Tearing Effect (TE) for tear-free partial refresh

- Verify pixel format, readback, alignment, and command set

- MIPI DPI (parallel RGB)

- Continuous video stream with strict HSYNC/VSYNC/DE/pixel-clock timing; predictable latency

- High pin count and EMI; needs full-frame buffers and DMA/display controller

- Validate porch/sync timing, pixel clock range, color coding, and drive levels

- MIPI DSI

- High bandwidth with few lanes; supports command-mode and video-mode

- Command-mode: partial updates, lower average power

- Video-mode: smooth 60+ Hz motion; requires sustained memory bandwidth and buffering

- Check lane count/rate headroom, D-PHY routing, DCS/initialization, TE, pixel formats, and power sequencing

## 4 Graphics subsystem and display configuration

### 4 Graphics subsystem and display configuration

At this stage of the graphical application development, with the application requirements already determined, configure the graphics subsystem of PSOC™ Edge to refine the application. See [AN239191 Getting started with graphics on PSOC™ Edge MCU](#) as a quick-start guide to develop graphics application on the PSOC™ Edge MCU.

#### 4.1 Clock configuration

The graphics subsystem has the following asynchronous clock domains:

- System clock and high frequency main clock

- MIPI DSI host clock

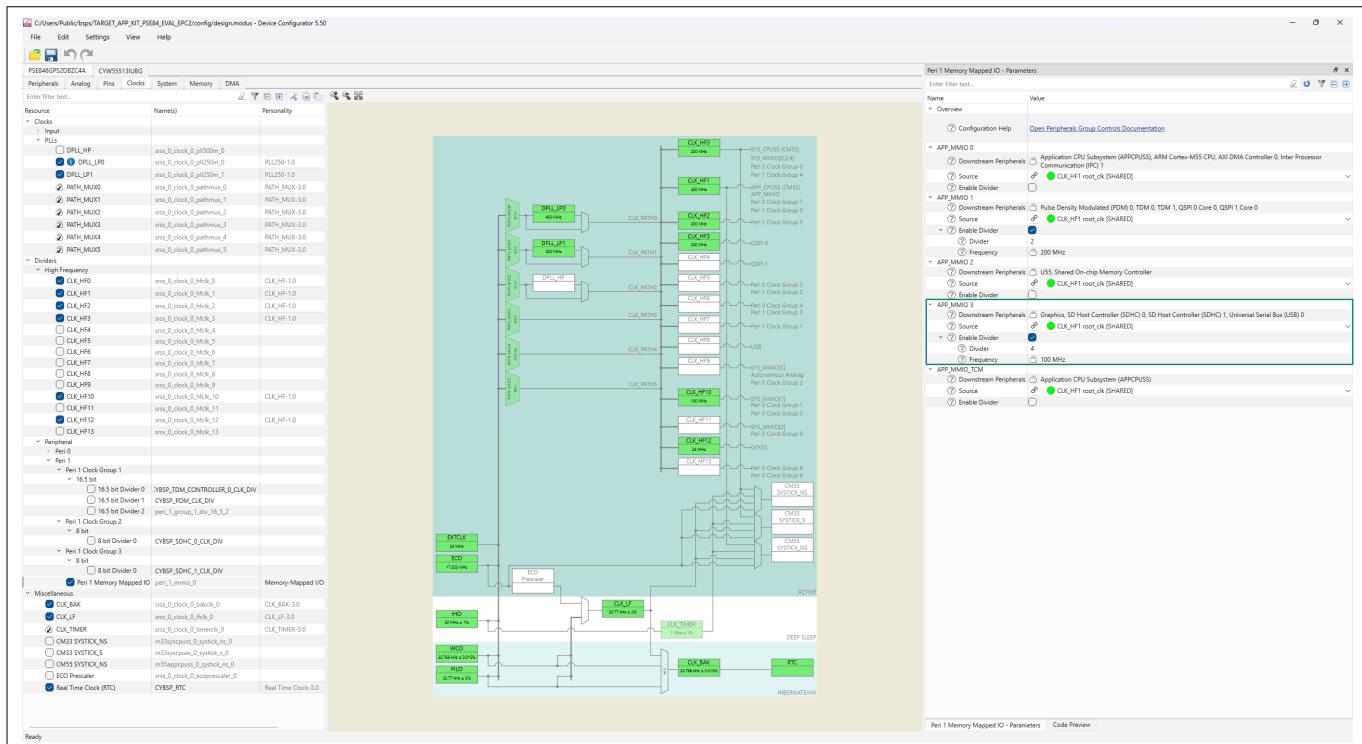

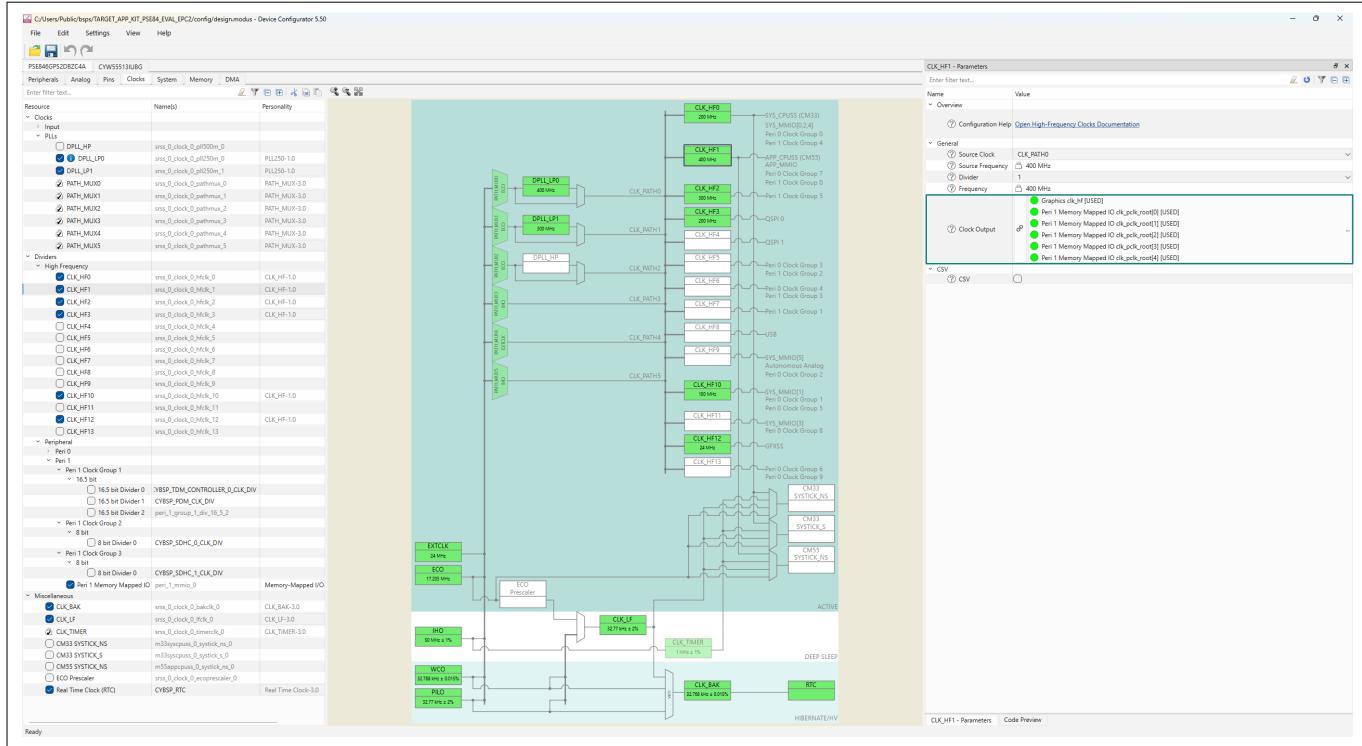

##### 4.1.1 System and high frequency main clocks

The system clock (clk\_sys) supplies inputs for the GPU system clock (clk\_sys\_gpu), DC (clk\_sys\_dc), and MIPI DSI (clk\_sys\_mipidsi), facilitating their configuration through MMIO and interrupt ports for each of the three aforementioned sub components. These clocks are configured with a 1:N ratio to the system's peripheral clock, up to a maximum of 100 MHz, as shown below in the [Figure 3](#).

**Figure 3** GFXSS system clock configuration

High frequency main clock (clk\_hf) sourced from CLK\_HF1, provides the high-frequency timing reference for the AXI ports used by the GPU and DC. It sets the pace for memory transactions (framebuffer reads/writes, textures, layers) and feeds dividers that generate the functional clocks for GPU core, DC scan-out logic, and standard display interfaces (e.g., DSI/DPI/DBI). In short, CLK\_HF determines throughput, latency, and timing determinism across the graphics pipeline, while its divided versions shape logic and I/O rates.

clk\_hf can be configured with a minimum frequency of 100 MHz and a maximum frequency of 400 MHz, as illustrated in [Figure 4](#). The minimum is not a strict limitation. Lower frequencies for clk\_hf are permitted (e.g., for ULP operation); however, they will affect the maximum frequencies achievable on display interfaces, in addition to having a general impact on rendering performance.

## Developing high-performance graphics with low-power optimization on PSOC™ Edge MCU

## 4 Graphics subsystem and display configuration

## Figure 4 GF XSS high frequency clock configuration

The following list of internal clocks for all three components of the graphics sub-system is auto-generated from the system and the high-frequency main clock.

**Table 1** **GFXSS internal clocks**

| Clock       | Value                                | Description                                                                                                                                                                                                                                                     |

|-------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_2d      | Minimum 50/64 MHz<br>Maximum 200 MHz | GPU core clock. Generated within the graphics sub-system core with a DIV2 from clk_hf.                                                                                                                                                                          |

|             |                                      | The frequency limits the peak pixel fill rate that the GPU can achieve (= 1 pixel/cycle). The min value ensures a comfortable margin in fill rate for a use case with 640x480 @60 Hz (24 MHz pixel clock). The maximum value is optimal for energy consumption. |

| clk2x_2d    | Minimum 100 MHz<br>Maximum 400 MHz   | GPU 2x core clock (by-pass of the internal DIV2). Used to realize dual port access to internal memories by the pixel engine.                                                                                                                                    |

| clk_hf_core | Minimum 50 MHz<br>Maximum 200 MHz    | Core and AXI clock for the DC. Division by 2 from clk_hf.                                                                                                                                                                                                       |

**(table continues...)**

#### 4 Graphics subsystem and display configuration

**Table 1** (continued) GFXSS internal clocks

| Clock       | Value                            | Description                                                                                                                                                                                                                                                          |

|-------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_hf_div  | Minimum 1 MHz<br>Maximum 200 MHz | Fractional division from clk_hf. 50% duty cycle. Systematic jitter on both edges is maximum $1/f_{clk\_hf}$ .<br><u>DPI Mode via GPIO or MIPI-DSI</u><br>Same as pixel clock frequency.<br><u>DBI Mode Type C via GPIO (SPI)</u><br>Twice the serial clock frequency |

| clk_sys_cfg | Minimum 17 MHz<br>Maximum 52 MHz | Configuration clock for the D-PHY. Generated by DIV2 from clk_sys_mipidsi.                                                                                                                                                                                           |

#### 4.1.2 DSI host clock

A correctly configured MIPI DSI host clock ensures that the display link can carry the required pixel stream (or command bursts) with sufficient margin while maintaining stability across the high speed/low power (HS/LP) transitions. [Table 2](#) presents the necessary clocks for the DSI host controller.

**Table 2** DSI host clock

| Clock type      | Value                     | Clock alias          | Description                                                                                                                                                                                                          |

|-----------------|---------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference clock | Typical 24 MHz            | clk_ref_mipidsi      | Reference clock for the D-PHY PLL (CLK_HF12).                                                                                                                                                                        |

| Lane byte clock | Max. 187.5 MHz            | lanebyteclk          | Internally generated from clk_ref_mipidsi with the D-PHY PLL, serves as a reference for the DSI host controller's packet interface, synchronizing the transmission of video and command data.                        |

| Pixel clock     | Min. 1 MHz<br>Max. 64 MHz | dipiclk              | Pixel clock for DPI via MIPI-DSI, auto generated by the DC based on video timings and clk_hf_div.<br>Max frequency corresponds to VESA 1024x768 @60 Hz (XGA), min to the slowest VESA mode of 160x120 @50 Hz (QVGA). |

| DBI clock       | Max. 37.5 MHz             | dbiclk               | Data clock for DBI Type B via MIPI-DSI. Generated by the DC. Max is 1/4 of max lanebyteclk per MIPI host controller specification.                                                                                   |

| LP mode clock   | Max. 20 MHz               | txclkesc<br>rxclkesc | Low-power (escape) clock for command/ULPS operations.                                                                                                                                                                |

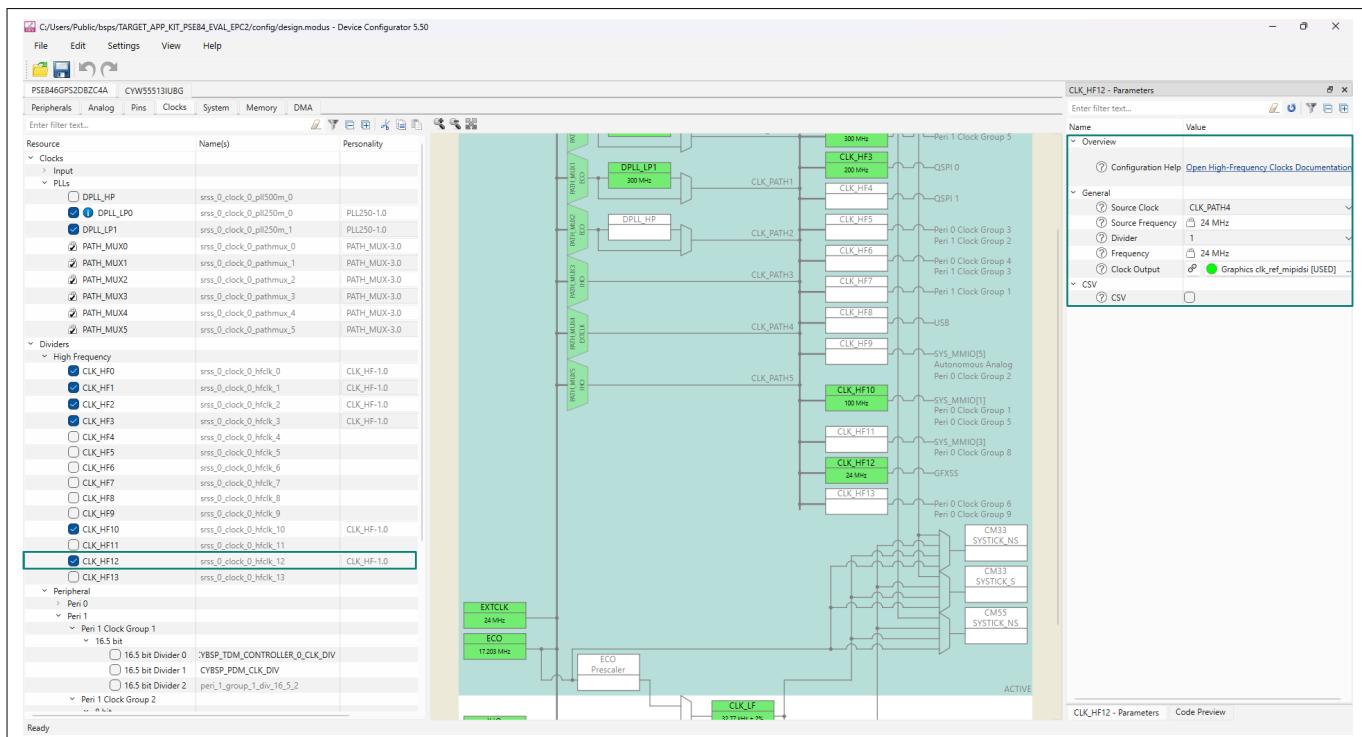

- D-PHY PLL reference clock (configured in device configurator)

- This needs to be configured as 24 MHz as shown in [Figure 5](#), sourced from either a dedicated external clock (EXTCLK) or clk\_hf. This low-jitter reference feeds the D-PHY PLL that synthesizes the high-speed lane bit rate. Its stability directly impacts link lock and signal integrity

- Lane byte clock (auto-derived)

- This internal clock drives packetization and TX FIFOs; too low and the FIFO may starve, too high and you may hit PHY limits

# Developing high-performance graphics with low-power optimization on PSOC™ Edge MCU

## 4 Graphics subsystem and display configuration

- The host computes the lane byte clock from the selected lane bit rate:  $\text{lanebyteclk} = \text{lannerate} / 8$ . It drives packetization and TX FIFOs and must sustain your video/command throughput with margin. With the chosen two 1-lane panels capped at 850 Mbps and 700 Mbps respectively,  $\text{lanebyteclk}$  is:

- 850 Mbps  $\rightarrow$  106.25 MHz

- 700 Mbps  $\rightarrow$  87.5 MHz

- Never exceed the panel's per-lane limit; if a shared configuration forces a common rate, cap at the lower (700 Mbps) so  $\text{lanebyteclk} = 87.5$  MHz

- TX escape (LP) clock (auto-derived,  $\leq 20$  MHz)

- Used for low-power commands, ULPS entry/exit, and error recovery. It is derived from  $\text{lanebyteclk}$  via an integer divider and must not exceed 20 MHz. It affects command/LP latency, not video bandwidth. Typical targets are 10–20 MHz as allowed by  $\text{lanebyteclk}$  / divider

Figure 5 D-PHY PLL reference clock configuration

## 4.2 Display type and interface

PSOC™ Edge supports MIPI DBI A/B/C, MIPI DPI, and MIPI DSI (Video and Command) display types; however, this application note and its code example focus exclusively on MIPI DSI single-lane displays in Video mode and Command mode used by the reference application. This section first shows how to configure a 4.3-inch single-lane DSI panel in Video Mode, followed by a 1.43-inch single-lane DSI panel in Command mode. In the Device Configurator, users begin by selecting the display type (Video or Command) and then choose the corresponding interface format and mode-specific parameters. Even when defaults are auto-filled, understanding these options helps making the right trade-offs for image quality, bandwidth, and power. Other interface types, such as DBI/DPI, are supported by the platform but are out of scope for this document.

### 4.2.1 MIPI DSI video mode

MIPI DSI video mode streams pixels continuously at fixed display timings, making it an ideal choice for smooth animations, video playback, and predictable end-to-end latency. It is used with displays that do not embed

## 4 Graphics subsystem and display configuration

graphic RAM capable of holding an entire frame and rely on the MIPI DSI host to provide a continuous pixel stream, as they lack an internal controller.

The MIPI DSI host video mode supports the following three transfer types:

**Table 3** **Video mode transfer type**

| Transfer type                   | Description                                                                                                                                                                                                                                                                                                                                                                                    | When to use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Burst mode                      | Active pixels are transmitted in brief high-speed bursts, and the remaining line/frame interval is left as blanking or low power idle, thereby reducing the high-speed duty cycle. This transmission mode requires that the DSI payload pixel FIFO has the capacity to store a full line of active pixel data inside of it                                                                     | <ul style="list-style-type: none"> <li>Panel can receive a full pixel line in a single packet burst to prevent overflow in the receiving buffer</li> <li>Lane rate has ample headroom vs payload (e.g., lower color depth or refresh)</li> <li>Desire to drop to low-power once per line</li> </ul>                                                                                                                                                                                                                                                                                                                                     |

| Non-burst mode with sync pulses | HSYNC and VSYNC are sent as explicit pulse packets, while blanking and active periods stream continuously. This aligns the DC interface input pixel bandwidth with the DSI link bandwidth. In this mode, the host controller and display do not need to store a full line of pixel data, only the content of one video packet, minimizing memory requirements                                  | <ul style="list-style-type: none"> <li>Default choice for broad compatibility and straightforward timing</li> <li>When lane rate is close to pixel payload</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Non-burst mode with sync events | Signals HSYNC/VSYNC with only “start” and “end” events; the blanking interval is the time between these events, not explicit sync-pulse packets. The link streams continuously in high speed during active video, with lower control overhead than non-burst with sync pulses. Clock-lane operation is continuous, making precise porch/sync programming essential, as timing defines blanking | <ul style="list-style-type: none"> <li>If the panel datasheet lists non-burst mode with sync events as supported/preferred and you want marginally leaner control traffic than non-burst mode with sync pulses</li> <li>When your per-lane rate is close to the pixel payload and you want to preserve a bit of headroom by trimming control overhead (without switching to Burst)</li> <li>In systems where you need deterministic continuous streaming but want to minimize unnecessary packetization during blanking</li> <li>When power behavior with continuous clock is acceptable and compatibility has been verified</li> </ul> |

Now in a MIPI DSI Video pipeline, “DPI-x” defines the on-wire color coding and packing used to encapsulate pixels into DSI video packets. This choice directly sets bits per pixel, required lane throughput, visual fidelity, and HS duty cycle. “Configuration 2” denotes packed mappings (no pad bits), which are the bandwidth-efficient variants for 18 bpp and 16 bpp. Always confirm that the target panel supports the selected coding and packing.

## 4 Graphics subsystem and display configuration

Following display interfaces are supported in MPI DSI video mode:

**Table 4** **Video mode display interface**

| Display interface                               | Description                                                                                                                                                                                                                          | When to use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPI-24 (RGB888, 24 bpp)                         | Delivers true color at 24 bpp (8 bits per R, G, B) with no precision loss, yielding excellent gradients and minimal banding but it imposes the highest payload and memory/display bandwidth demand.                                  | <ul style="list-style-type: none"> <li>When color quality and gradient smoothness are critical (photos, video, rich UI themes)</li> <li>When the single-lane link has ample headroom at the target resolution and refresh rate</li> <li>When the rendering pipeline already produces 24/32-bpp frames, avoiding conversion overhead</li> </ul> <p><b>Note:</b> <i>When using 24-bit color depth, the physical interface remains in the high-speed transmit state for a larger portion of each line or frame, increasing switching activity and potentially raising power consumption compared to lower-bpp modes.</i></p> |

| DPI-18 (configuration 2, RGB666 packed, 18 bpp) | Uses 6 bits per channel in a tightly packed format, preserving good visual quality with modest precision loss, while cutting payload by roughly 25% compared to RGB888 to improve lane-rate margin and reduce high-speed duty cycle. | <ul style="list-style-type: none"> <li>When we need extra throughput headroom on a single lane without a large quality compromise</li> <li>When the panel offers internal dithering or the graphics stack can dither to smooth gradients</li> <li>When power consumption must be trimmed relative to RGB888</li> </ul> <p><b>Note:</b> <i>Verify explicit support for “RGB666 packed/config 2 for the chosen display.” Check color order (RGB/BGR) and byte packing.</i></p>                                                                                                                                              |

**(table continues...)**

#### 4 Graphics subsystem and display configuration

**Table 4** (continued) Video mode display interface

| Display interface                               | Description                                                                                                                                                                                                                     | When to use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPI-16 (configuration 2, RGB565 packed, 16 bpp) | Encodes pixels with 5-6-5 bits for R-G-B in a tightly packed format, offering the most bandwidth-efficient standard option by reducing payload about 33% versus RGB888 and yielding the largest headroom for single-lane links. | <ul style="list-style-type: none"> <li>When lane-rate budget is tight at chosen fps, or when minimizing HS duty cycle, power, and low power consumption is a priority</li> <li>For UIs dominated by text, icons, and flat colors where limited precision is acceptable</li> <li>When memory footprint and bus bandwidth must be reduced (smaller frame buffers, lower read/write traffic)</li> </ul> <p><b>Note:</b> <i>Some banding may appear in smooth gradients; enable dithering if available. Confirm packed mapping and color order with the panel.</i></p> |

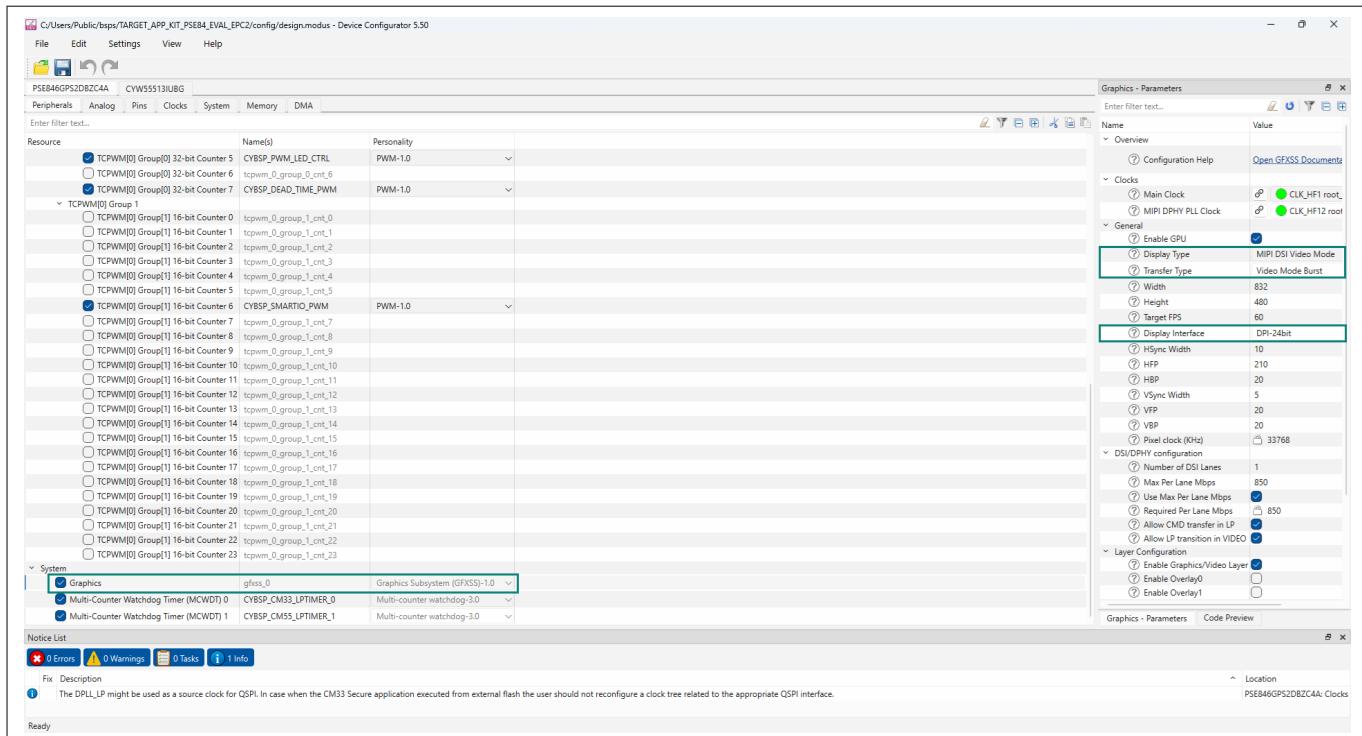

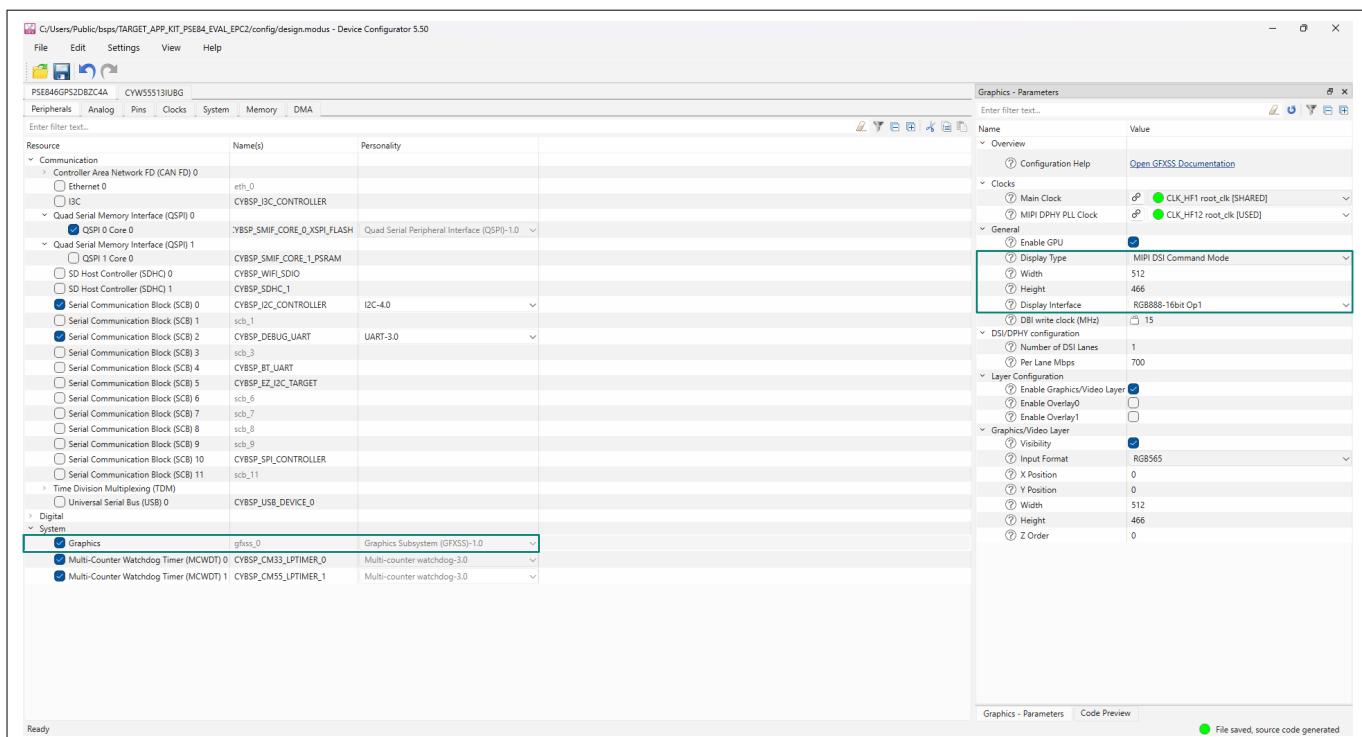

To apply these configurations, the user needs to enable the Graphics subsystem and select the following settings for the 4.3-inch single DSI lane 800x480 video mode display, as shown in the [Figure 6](#).

- Display Type: MIPI DSI Video Mode

- Transfer Type: Video Mode Burst

- Display Interface: DPI-24 bit

## 4 Graphics subsystem and display configuration

**Figure 6 MIPI DSI video mode display configuration**

In relation to the code example mentioned in this document, the single-lane panel supports up to 850 Mbps per lane and our calculated payload provides substantial margin. MIPI DSI is configured in Video Burst mode to compress active pixels into short high-speed bursts, thereby reducing the high-speed duty cycle. The application renders in RGB565 (16 bpp) for memory/bus efficiency, while the display interface is set to use DPI-24 (RGB888) on-wire color coding to match the panel's preferred input format. The available lane-rate headroom makes this on-the-fly expansion practical without risking under-runs. This combination preserves visual compatibility and quality on the link, benefits from lower average HS activity (potentially improving power), and maintains deterministic, tear-free scan-out.

### 4.2.1.1 Setting up video timings per display resolution

Once the video mode, transfer type, and display interface have been selected, it is essential to accurately configure the video timing parameters to ensure the display is driven at the exact cadence that the panel expects, delivering a stable image in MIPI DSI video mode. These timings are primarily associated with the display controller, which generates and sends them to the display module to ensure coordinated pixel and frame updates, preventing issues such as screen tearing.

For each resolution, it is necessary to define the active image area and the blanking regions surrounding it. Together with the target refresh rate, these parameters produce the horizontal and vertical totals that set the pixel clock, the rate at which the pixels must be delivered. These timing totals also determine the data payload that the DSI host must packetize and transmit over the lane(s), which in turn establishes the required DSI lane bit rate and the internal lane byte clock.

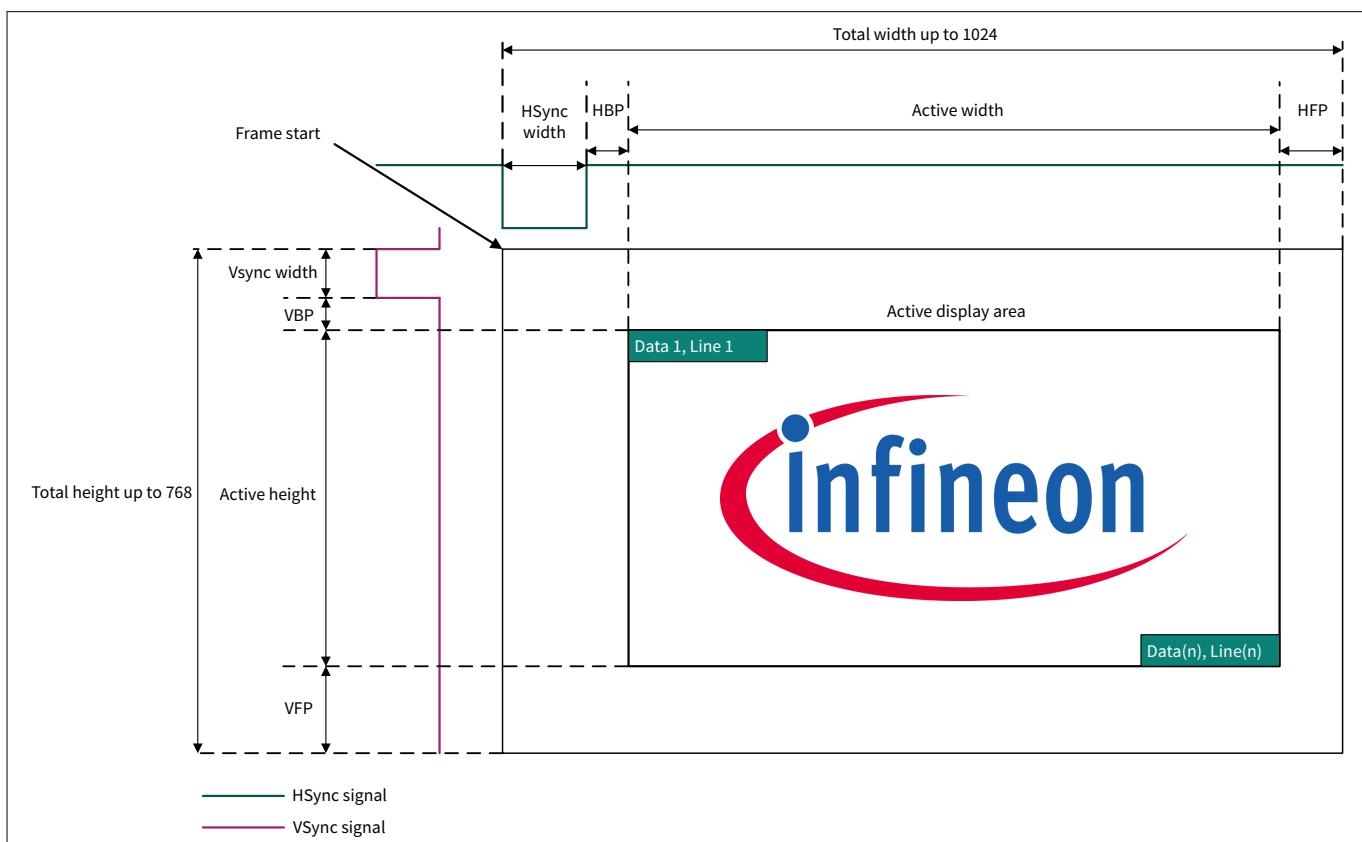

A display frame is composed of active video pixels (visible area) and several blanking intervals that are used for synchronization and signal processing. The two major timing domains are horizontal timing (per line) and vertical timing (per frame).

#### Horizontal timing parameters (per line)

- **Horizontal sync width (HSync width):** Duration of the horizontal sync pulse, signaling the start of a new line

## 4 Graphics subsystem and display configuration

- **Horizontal back porch (HBP):** Idle period after the horizontal sync pulse before starting to send active data pixels

- **Horizontal active (display active width):** The number of visible pixels in a single line (equal to horizontal resolution, for example 800 for 800x480 4.3-inch Waveshare display)

- **Horizontal front porch (HFP):** Idle period after the active pixels before the horizontal sync pulse. Used by the display to prepare for the next line

Formula for total horizontal period:

$$H_{TOTAL} \text{ [in pixels]} = HSync \text{ width} + HBP + \text{Display active width} + HFP$$

### Vertical timing parameters (per frame)

- **Vertical sync width (VSync width):** Number of lines during the active vertical sync pulse

- **Vertical back porch (VBP):** Number of idle lines after the VSync pulse before starting the next frame

- **Vertical active (display active height):** Number of lines of visible pixels per frame (equal to vertical resolution, for example 480 for 800x480 4.3-inch Waveshare display)

- **Vertical front porch (VFP):** Number of idle lines after completing active frame lines before the vertical sync pulse

Formula for total vertical period:

$$V_{TOTAL} \text{ [in lines]} = VSync \text{ width} + VBP + \text{Display active height} + VFP$$

Following figure illustrates fully programmable timings and resolutions.

Figure 7

Fully programmable timings and resolutions

## 4 Graphics subsystem and display configuration

### Calculating pixel clock, DSI clock, and bit clock

The pixel clock (PCLK) defines the rate at which pixels are transmitted to the panel.

$$\text{PCLK [in Hz]} = \text{H\_TOTAL} \times \text{V\_TOTAL} \times \text{Frame rate}$$

Where:

- Frame rate = Refresh rate or Target FPS (for example 60 Hz)

- H\_TOTAL and V\_TOTAL are total horizontal and vertical periods respectively

For a DSI-based interface:

- **DSI clock:** Determined by the pixel clock, the bits per pixel (BPP), and the number of data lanes in use

- **Bit clock formula:**

$$\text{Bit clock} = (\text{PCLK} \times \text{BPP}) / \text{Number of lanes}$$

Where:

- BPP depends on the color format (for example DPI-24 = 24 bits per pixel)

- Number of lanes depends on the DSI lanes configured for the display (for example 1 lane for 4.3-inch 800x480 Waveshare display)

- Final DSI clock may be set slightly higher to account for protocol overhead

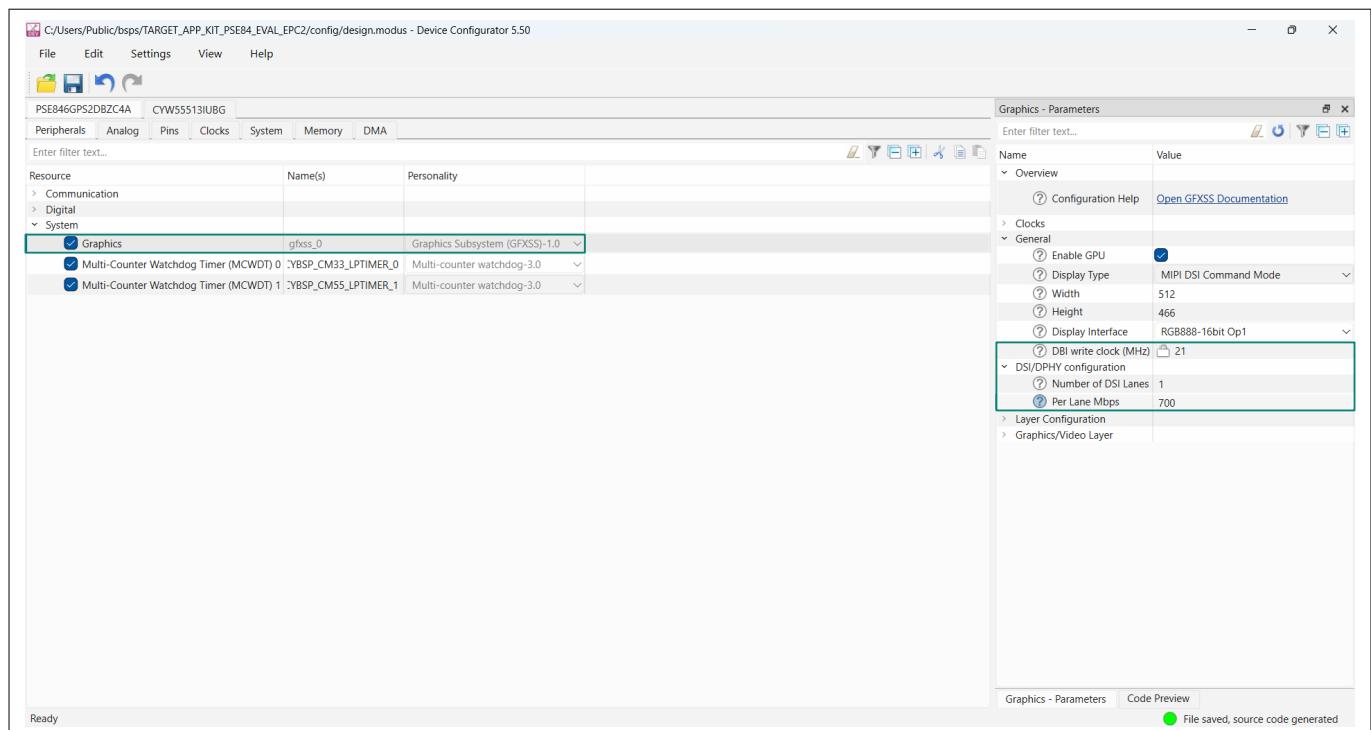

In the Device Configurator, set the parameters described above in the "General" section for the Waveshare 4.3-inch 800x480 MIPI DSI video mode display as follows, as depicted in [Figure 8](#).

- Width: 832 (if using RGB565 color format to achieve 128 byte stride alignment per DC requirement) else 800 matching the horizontal resolution

- Height: 480 matching the vertical resolution

- Target FPS: 60 as per the panel spec

- All HSync and VSync timings as per the panel datasheet which in turn auto calculate and set the pixel clock

# Developing high-performance graphics with low-power optimization on PSOC™ Edge MCU

## 4 Graphics subsystem and display configuration

**Figure 8 Video timings and display resolution configuration**

The video timings will reflect in the `cy_stc_mipidsi_display_params_t` configuration structure as shown in the snippet below after the configurations are saved in the Device Configurator.

### MIPI DSI display parameters

```

cy_stc_mipidsi_display_params_t GFXSS_mipidsi_display_params =

{

.pixel_clock      = 33768,

.hdisplay         = 832,

.hsync_width      = 10,

.hfp              = 210,

.hbp              = 20,

.vdisplay         = 480,

.vsync_width      = 5,

.vfp              = 20,

.vbp              = 20,

.polarity_flags   = 0,

};

```

### Polarity flags

Polarity flags define which logic level (high or low) is “active” for HSYNC, VSYNC, and DATAEN (DE) in a DPI-fed MIPI DSI Video mode path. Correct settings are essential for proper image alignment and stable scan-out. “Shutdown” and “Color mode” are auxiliary control signals; depending on the panel ecosystem, they may be implemented as GPIOs or not used at all (DSI panels often rely on DCS commands instead).

It is applicable only in Video mode (DPI input to the DSI Host). Not applicable in Command Mode (DBI input). For the 4.3-inch display, the polarity\_flags field is 0, indicating active high for HSYNC, VSYNC, and DE.

In case of interfacing a different display panel, manually set the polarity\_flags parameter of the `cy_stc_mipidsi_display_params_t` structure before initializing the graphics subsystem, according to the panel

## 4 Graphics subsystem and display configuration

datasheet. To quickly validate the configuration, generate test patterns (color bars/checkerboard) for the display. If the image shifts or rolls, swap the HSYNC/VSYNC polarity; if the active area is inverted, adjust the DE polarity.

### 4.2.2 MIPI DSI command mode

In MIPI DSI command mode, the display panel refresh is driven primarily by commands and data transferred via the DSI link, rather than a continuous pixel stream as in video mode. Pixel data is written into the panel's frame memory (GRAM) through short and long packets. The panel itself is responsible for scanning out the stored image to the display glass at the configured refresh rate. This allows asynchronous updates – only the regions that change need to be updated, reducing bus traffic and power consumption. Clock-lane operation is usually non-continuous to save power, and ULPM can be used during long idle periods.

The MIPI DSI host command mode supports following display interfaces:

#### 8-bit interface modes

##### 1. RGB332 (8 bpp)

- 3 bits Red, 3 bits Green, 2 bits Blue

- Pros: Very low data rate, extremely low memory footprint; ideal for icon/monochrome-dominant GUIs

- Cons: Very limited color depth, visible banding for gradients and photos

- Typical Use: Low-cost/simple GUIs, industrial HMI status displays

##### 2. RGB444 (8 bpp) (packed format)

- 4 bits per component, with specific packing rules for DBI

- Pros: Slightly better fidelity than RGB332 for gradients; still low bandwidth usage

- Cons: Not full 8 or 6 bits per component, still prone to visible artifacts in rich color content

- Typical Use: Low-power systems with moderate image quality needs

##### 3. RGB565 (8 bpp mode)

- Host transmits reduced pixel data with conversion handled internally by panel

- Pros: Good compromise on quality vs bandwidth even in constrained mode

- Cons: Requires panel-side mapping; limited flexibility in some controllers

##### 4. RGB666 and RGB888 (8 bpp mode)

- Encoded in compressed or reduced form for transmission; reconstructed by panel

- Pros: Achieves richer color depth with minimal transfer size

- Cons: Panel must internally expand and map correctly

#### 9-bit interface modes

##### 1. RGB666 (9 bpp)

- Allocates 6 bits per channel, sent with a 9-bit parallel structure in command packets

- Pros: Offers true 18-bit color resolution; good balance of fidelity and bandwidth

- Cons: Not as widely supported as 8 or 16-bit wide bus modes; marginally more complex hardware/firmware handling

- Typical Use: Medium-end GUIs where better gradients are needed without 24-bit transfers

#### 16-bit interface modes

##### 1. RGB332 (16-bit)

- Padding to meet 16-bit word alignment

- Pros: Very low bandwidth and processing cost; alignment can simplify DMA transfers

- Cons: Same fidelity limitations as 8-bit RGB332

## 4 Graphics subsystem and display configuration

### 2. **RGB444 (16-bit)**

- Padding/bus alignment improves per-pixel access overhead

- Pros: Slightly richer color representation than RGB332; efficient transfer in 16-bit systems

- Cons: Not photo-quality; visible quantization

### 3. **RGB565 (16-bit)**

- 5 bits Red, 6 bits Green, 5 bits Blue (packed into 2 bytes)

- Pros: Most common 16-bit mode; good compromise between fidelity and data rate; available in Option 1 and Option 2 packing

- Cons: Not true 24-bit color; minor gradients loss in certain images

- Typical Use: Embedded GUIs, wearable devices, control systems

### 4. **RGB666 (16-bit) (Option 1 and Option 2)**

- Encoded with specific padding/packing rules to match DCS protocol requirements

- Pros: Delivers near 18-bit fidelity with reasonable transfer width

- Cons: Requires careful configuration; not all panels support both packing options

### 5. **RGB888 (16-bit) (Option 1 and Option 2)**

- Two packing schemes used to fit 24-bit pixels into 16-bit aligned transfers

- Pros: Achieves full 24-bit color representation over a 16-bit interface; essential for photo-grade content

- Cons: Significantly higher data rate; bandwidth and memory impact; careful configuration required

- Typical Use: High-end GUIs, photo viewers, video rendering in command mode

When transmitting pixel formats such as RGB666 (18 bpp) or RGB888 (24 bpp) over a 16-bit wide DSI command mode interface (DBI-B), the pixel data does not align perfectly with the 16-bit word size. As a result, the MIPI DCS specification defines two common packing schemes for these formats: Option 1 and Option 2. The difference lies in whether pixels are word-aligned (loose packing) or packet-optimized (tight packing).

### 1. **Option 1 - loose packing (word-aligned)**

- **Description:**

Each pixel's data is sent starting at a new 16-bit word boundary. Any unused bits in the word are filled with padding (don't-care values)

- **RGB888:**

A 24-bit pixel is expanded to two 16-bit words. This introduces unused bits in the second word to keep pixel boundaries aligned

- **RGB666:**

An 18-bit pixel is padded to 2 bytes (16 bits), again introducing unused bits

- **Outcome:**

Simplifies both host and panel logic because each pixel is cleanly separated, but data rate is slightly higher due to padding

### 2. **Option 2 - tight packing (bit-optimized)**

- **Description:**

Pixels are packed back-to-back in memory without padding, and their bits can cross 16-bit word boundaries. Three consecutive bytes (RGB for one pixel in RGB888 or 18 bits for RGB666) are split between words as needed

- **RGB888:**

For example, the Blue component of one pixel and the Red component of the next may share the same 16-bit word

- **RGB666:**

# Developing high-performance graphics with low-power optimization on PSOC™ Edge MCU

## 4 Graphics subsystem and display configuration

Multiple pixels' bits are interleaved so that no padding is required, each word is fully utilized

### • **Outcome:**

Delivers maximum bandwidth efficiency, but increases packing/unpacking complexity in both the host and the panel

The MIPI DCS standard provides both options so that system designers can trade off between simplicity (Option 1) and link efficiency (Option 2). The correct choice depends on system bandwidth, panel support, and implementation complexity tolerance.

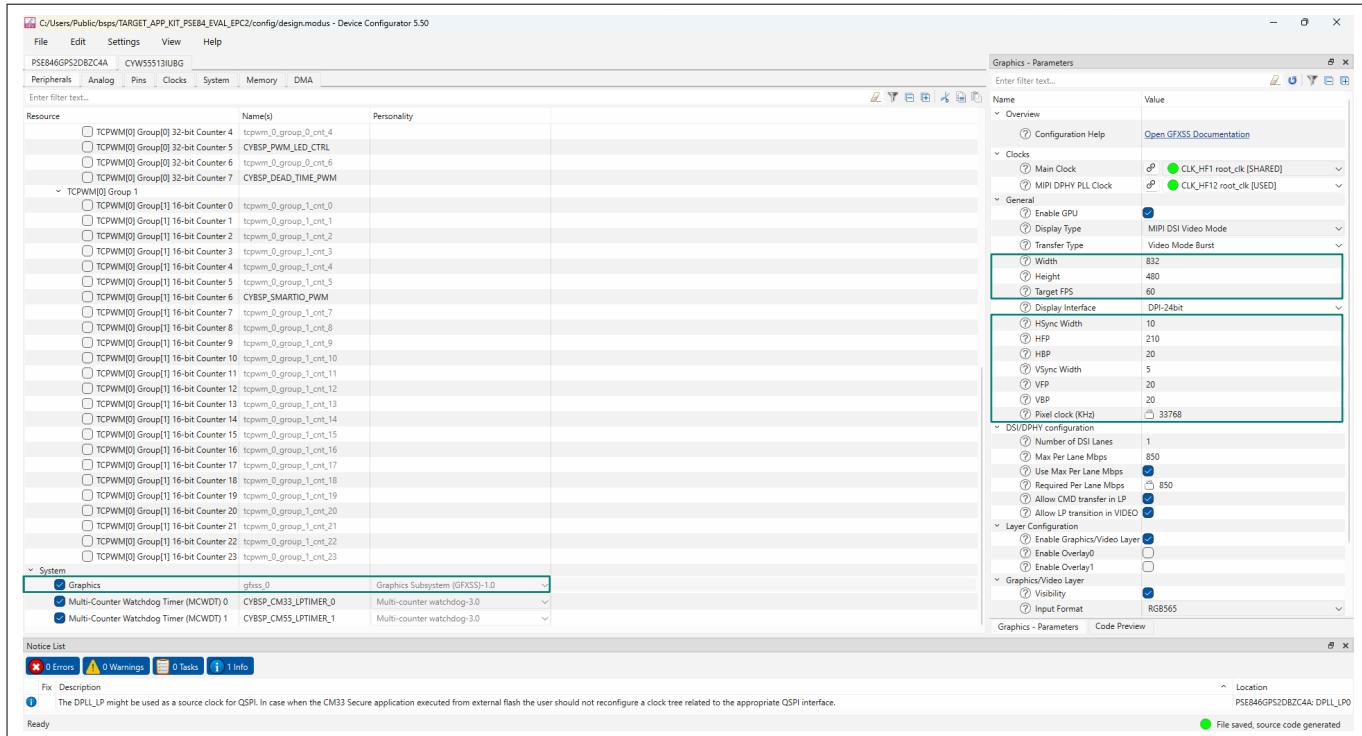

In our case, we utilize a 1.43-inch single lane 466x466 MIPI DSI command mode round display, where we configure the display's resolution and display interface to RGB888 16-bit Option 1, as shown in the [Figure 9](#) below. This choice is made on the following reasons:

### 1. **Simplicity of integration:**

Option 1 keeps each pixel aligned to a 16-bit word boundary, greatly simplifying the host controller's memory-to-DSI data mapping, and minimizing firmware complexity

### 2. **Panel compatibility:**

The selected 1.43" panel fully supports RGB888 Option 1 in command mode, ensuring straightforward compliance with the panel's datasheet without requiring custom tight-packing logic

### 3. **Adequate bandwidth headroom:**

Even though Option 1 is less efficient than Option 2, the actual pixel clock and DSI lane data rate for a small-format single-lane panel are well within the lane budget. Maintaining 20-30% margin avoids under-runs without the need for tight packing

### 4. **Reliability priority:**

For this application, robustness of the link and ease of debugging outweigh the marginal bandwidth gain from Option 2. With Option 1, data alignment issues are less likely to cause visible artifacts

**Figure 9** Command mode display configuration

**Note:** When using the RGB565 color format in Command Mode, set the horizontal width parameter to 512 instead of the actual active resolution of 466 pixels. This ensures a 128-byte stride alignment, which will be explained in detail in the [Display controller configuration](#) section.

## 5 GPU configuration

### 5 GPU configuration

GPU is a standalone functional block which does not have any direct interfacing to other modules (DC and MIPI DSI host) within graphics subsystem. Data exchange is software controlled via frame buffers in the system's video RAM which can be System SRAM or external PSRAM based on the application requirement. From a configuration standpoint, we simply enable the GPU in the device configurator for our application. It can also be disabled via the device configurator before the application build or dynamically enabled/disabled using following software APIs.

#### Enable GPU

```

cy_en_gfx_status_t Cy_GFXSS_Enable_GPU(GFXSS_Type *base, cy_stc_gfx_context_t *context)

Enable GPU for composition

Parameters

base    Pointer to the graphics sub system base address

context  context information used by the driver

Returns

SUCESS/TIMEOUT status

```

#### Disable GPU

```

cy_en_gfx_status_t Cy_GFXSS_Disable_GPU(GFXSS_Type *base, cy_stc_gfx_context_t *context)

Disable GPU and let display controller refresh display based on already composed buffer stored

in frame buffer address

Parameters

base    Pointer to the graphics sub system base address

context  context information used by the driver

Returns

SUCESS/TIMEOUT status

```

## 6 Display controller configuration

### 6 Display controller configuration

The Display Controller (DC) is the hardware block responsible for fetching image data from system memory, processing it according to display pipeline requirements, and outputting it to the target panel interface. Alternatively, it can drive standard I/O pins directly. It supports interfacing with panels having a total horizontal width of up to 1024 pixels and a total vertical height of up to 768 lines.

It supports operation in two distinct output modes:

- Video mode through the DPI interface to continuously drive HSync, VSync, and pixel clock signals for the video mode display panel, which is a 4.3-inch 800x480 display in our case

- Command mode via the DBI interface (including MIPI DSI in Command Mode) using DCS write transactions to update the panel's onboard frame buffer (GRAM), which is a 1.43-inch 466x466 display in our case

This unified architecture allows the same controller to be configured for either real-time continuous streaming (video mode) or asynchronous partial/full updates (command mode), depending on panel type and application needs.

The DC supports three independent display layers, composited into a final frame through per-pixel alpha blending.

#### 6.1 Three programmable DC layers

This section outlines the necessary steps to configure the DC layers, taking into account the display size and color depth. As previously mentioned, the DC features three independently configurable layers: one video/graphic layer and two overlay layers. The users can enable one, two, or all of the layers. By default, the graphics layer is enabled.

User must configure the following DC layer parameters separately for each enabled layer:

- Layer visibility

- Input format (RGB or YUV)

- Tiling type (tiled or linear)

- Window size and position

- Z-order of the layer

- Framebuffer start address (by default set to system SRAM (also known as SoCMEM) base address)

- YUV buffer start address (by default set to system SRAM base address)

Based on the Input format selection, the tiling type gets configured.

If the Input Format is RGB565/ARGB8888/ARGB1555/ARGB4444, then the Tiling type will be Linear. However, if the Input Format is Packed YUV422/YUV 420 semi-planar, then the Tiling type will be Tiled.

The user needs to configure the Windows X and Y positions according to the application requirements, ensuring that the Windows Width and Height are less than or equal to the resolution of the interfaced display to meet the application specifications.

By default, the framebuffer start address, or YUV buffer start address, will be configured to the system SRAM, also known as SoCMEM (used interchangeably throughout the document), base address. These parameters can be set manually by overriding the corresponding enabled graphic and overlay layer structures prior initializing the graphics subsystem as shown in the snippet below.

## 6 Display controller configuration

### Layer configuration during graphics subsystem initialization

```

/* Graphic layer configuration structure */

cy_stc_gfx_layer_config_t GFXSS_graphics_layer =

{

.layer_type = GFX_LAYER_GRAPHICS,

.buffer_address = (gctADDRESS *)CY_SOCMEM_RAM_BASE,

.uv_buffer_address = (gctADDRESS *)CY_SOCMEM_RAM_BASE,

.input_format_type = vivRGB565,

.tiling_type = vivLINEAR,

.pos_x = 0,

.pos_y = 0,

.width = 832,

.height = 480,

.zorder = 0,

.layer_enable = true,

.visibility = true,

};

/* Display controller configuration structure */

cy_stc_gfx_dc_config_t GFXSS_dc_config =

{

.gfx_layer_config = &GFXSS_graphics_layer,

.ovl0_layer_config = &GFXSS_overlay0_layer,

.ovl1_layer_config = &GFXSS_overlay1_layer,

.display_type = GFX_DISP_TYPE_DSI_DPI,

.display_format = vivD24,

.display_size = vivDISPLAY_CUSTOMIZED,

.display_width = 832,

.display_height = 480,

};

/* Frame buffers, where MY_DISP_HOR_RES = 832, MY_DISP_VER_RES = 480 and color format = RGB565

(16bpp ~ 2 bytes) for 4.3-inch display */

CY_SECTION(".cy_gpu_buf") LV_ATTRIBUTE_MEM_ALIGN uint8_t disp_buf1[MY_DISP_HOR_RES *

MY_DISP_VER_RES * 2];

CY_SECTION(".cy_gpu_buf") LV_ATTRIBUTE_MEM_ALIGN uint8_t disp_buf2[MY_DISP_HOR_RES *

MY_DISP_VER_RES * 2];

/* Frame buffers used by GFXSS to render UI */

void *frame_buffer1 = &disp_buf1;

void *frame_buffer2 = &disp_buf2;

/* Set frame buffer address to the GFXSS configuration structure */

GFXSS_config.dc_cfg->gfx_layer_config->buffer_address = frame_buffer1;

GFXSS_config.dc_cfg->gfx_layer_config->uv_buffer_address = frame_buffer1;

/* Initialize Graphics subsystem as per the configuration */

(void)Cy_GFXSS_Init(GFXSS, &GFXSS_config, &gfx_context);

```

## 6 Display controller configuration

Additionally, calling the following listed Set\_FrameBuffer\_YUV or Set\_FrameBuffer APIs for the respective graphic or overlay layer will set the framebuffer or YUV buffer start address parameters and render the frame to the display.

### APIs to set frame and YUV buffers

```

cy_en_gfx_status_t Cy_GFXSS_Set_FrameBuffer_YUV(GFXSS_Type *base, uint32_t* y_buffer, uint32_t* uv_buffer, cy_stc_gfx_context_t *context)

```

Sets Video/Graphics layer YUV buffer addresses

#### Parameters

base              Holds the base address of the Graphics block registers

y\_buffer          Pointer to the Y buffer address to be used by Display Controller **for** transferring frame

uv\_buffer        Pointer to the UV buffer address to be used by Display Controller **for** transferring frame

context           Pointer to the graphics config structure base address

#### Returns

CY\_GFX\_SUCCESS/CY\_GFX\_BAD\_PARAM

**Note:** YUV Framebuffer base address and stride **for** linear data should be **64**-byte aligned.

```

cy_en_gfx_status_t Cy_GFXSS_Set_FrameBuffer(GFXSS_Type *base, uint32_t* gfx_layer_buffer, cy_stc_gfx_context_t *context)

```

Sets Video/Graphics layer buffer address

#### Parameters

base              Holds the base address of the Graphics block registers

gfx\_layer\_buffer   Pointer to the frame buffer address to be used by Display Controller **for** transferring frame

context           Pointer to the graphics config structure base address

#### Returns

CY\_GFX\_SUCCESS/CY\_GFX\_BAD\_PARAM

**Note:** Framebuffer base address and stride **for** linear data should be **128**-byte aligned.

```

cy_en_gfx_status_t Cy_GFXSS_Set_Overlay0_YUV(GFXSS_Type *base, uint32_t* y_buffer, uint32_t* uv_buffer, cy_stc_gfx_context_t *context)

cy_en_gfx_status_t Cy_GFXSS_Set_Overlay0(GFXSS_Type *base, uint32_t* overlay0_buffer, cy_stc_gfx_context_t *context)

cy_en_gfx_status_t Cy_GFXSS_Set_Overlay1(GFXSS_Type *base, uint32_t* overlay1_buffer, cy_stc_gfx_context_t *context)

```

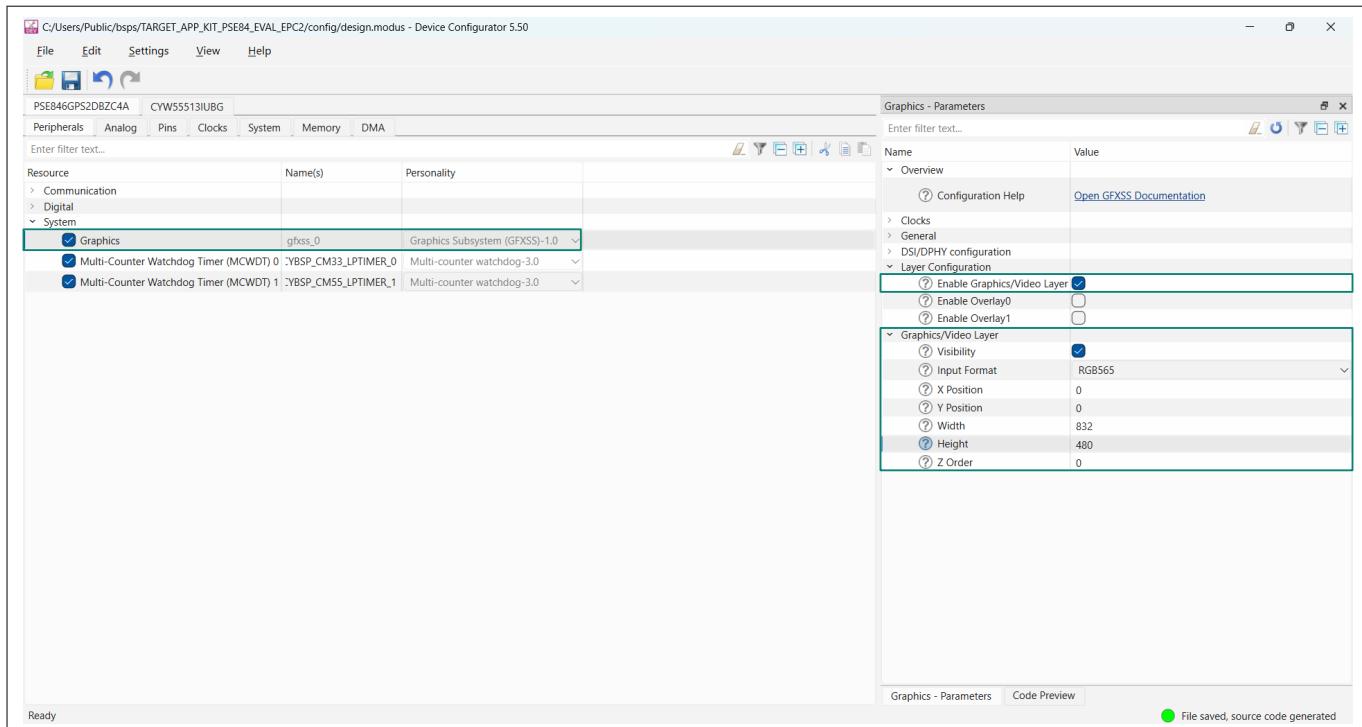

Following snapshot shows DC layer parameters configuration using Device Configurator for 4.3-inch 800x480 display.

## 6 Display controller configuration

**Figure 10 DC layer configuration**

Similarly, for 1.43-inch display, Width is set to 512 and Height as 466 while keeping Input Format as RGB565.

**Note:** Overlay1 layer does not support the tiled mode.

## 6.2 RLAD decoder

Run-Length Adaptive Dithering (RLAD) is a proprietary image compression format optimized for decoding hardware with low complexity and small design size. It supports both lossless and lossy compression and allows for the decompression of standard Run-Length encoded images according to TGA specifications.

The encoding is designed to be carried out by the RLAD encoder offline, while the RLAD decoder block is integrated into the display controller, which can be enabled for only one display layer to perform on-the-fly decoding.

The RLAD use case is demonstrated in the [PSOC™ Edge Graphics using RLAD](#) code example. See the [README](#) for more information about this code example.

### 6.2.1 Use case and application benefits

- Its main purpose is to store pre-rendered image assets such as static backgrounds, splash screens, and UI skins in compressed form, then decode and merge them with dynamic content on the fly

- In addition to image compression, RLAD can be used for RGB packing. For example, RGB888 or RGB666 images require DC to configure a 32 bpp frame buffer layout, despite the actual pixel data being only 24 and 18 bpp, respectively

- Example: Smartwatch face with moving hands, date, and other information being dynamic foreground

- Smartwatch background stored in compressed form and decoded on the fly

- For a 400x400 16 bpp pixel background image, compression will reduce image by 33%; reduces memory requirement by over 200 KB (400 KB for 32 bpp)

## 6 Display controller configuration

### 6.2.2 RLAD encoder tool

This tool allows to encode any PNG image asset into RL/RLA/RLAD/RLAD\_UNIFORM format offline. It generates a header file (.h) corresponding to the compressed image.

The tool takes three inputs:

1. Input file name (png only): file to be compressed. e.g., duck.png, selfie.png

2. Output file name(.h): name of a header file to be created. e.g., duck.h, selfie.h

3. Mode of compression: RL/RLA/RLAD/RLAD\_UNIFORM

The tool is distributed as part of the [mtb-example-psoc-edge-gfx-rlad](#) code example and can be used for any graphics application to leverage RLAD. Refer [RLAD encoder readme](#) for more information on its usage.

### 6.2.3 RLAD decoder configuration

By default, the RLAD decoder is disabled: the memory-to-display data stream is passed through unchanged (bypass mode) and all the RLAD registers remain in their reset state.

To use RLAD, the user must explicitly configure and enable the decoder in the application by following these steps.

1. Set up the RLAD decoder configuration structure (cy\_stc\_gfx\_rlad\_cfg\_t) shown below for one of the available DC layers

#### RLAD configuration structure

```

typedef struct

{

cy_en_gfx_layer_type_t    layer_id;           /*< Layer ID */

uint32_t                  image_width;        /*< Width of the image in number

of pixels minus one */

uint32_t                  image_height;       /*< Height of the image in number

of pixels minus one */

uint32_t                  compressed_image_size; /*< Size of the the encoded image

in number of 32-bit words minus one. Defined in image header file */

uint32_t                  *image_address;      /*< Image address */

cy_en_gfx_rlad_comp_mode_t compression_mode;  /*< RLAD compression mode */

cy_en_gfx_rlad_fmt_t      rlad_format;        /*< RLAD display format */

bool                      enable;              /*< RLAD state */

} cy_stc_gfx_rlad_cfg_t;

```

- layer\_id: Select the display layer (cy\_en\_gfx\_layer\_type\_t) that will receive decoded pixels. Only one layer should have RLAD decoding enabled at a time

#### Layer type

```

/* Layer type */

typedef enum {

GFX_LAYER_GRAPHICS, /*< Graphics layer */

GFX_LAYER_OVERLAY0, /*< Overlay 0 layer */

GFX_LAYER_OVERLAY1, /*< Overlay 1 layer */

} cy_en_gfx_layer_type_t;

```

- image\_width: Width of the resultant uncompressed image in number of pixels minus one. The DC layer must be setup for the same width

## 6 Display controller configuration

- `image_height`: Height of the resultant uncompressed image in number of lines minus one. The DC layer must be setup for the same height

- `compressed_image_size`: Size of the encoded image in number of 32-bit words minus one. The buffer must be readable to the subsequent 128 bytes boundary

- `image_address`: Base address of the encoded image buffer in multiple of 128 bytes. The DC layer must be configured to the same base address and with the smallest possible stride value (aligned to 128 bytes)

- `compression_mode`: Encoding/compression mode (`cy_en_gfx_rlad_comp_mode_t`) of the source image

### RLAD compression mode

```

/* RLAD compression mode */

typedef enum

{

CY_GFX_RLAD_MODE_RLAD,           /**< 'Run Length Adaptive Dithering'

compression. Lossy image compression type. */

CY_GFX_RLAD_MODE_RLAD_UNIFORM,  /**< 'Run Length Adaptive Dithering' compression

with uniform bits per pixel. Lossy image compression type. */

CY_GFX_RLAD_MODE_RLA,           /**< 'Run Length Adaptive' compression. Lossless

image compression type. */

CY_GFX_RLAD_MODE_RL           /**< 'Run Length Encoded' compression. Lossless

image compression type. */

} cy_en_gfx_rlad_comp_mode_t;

```

**Note:** The encoded image data is stored as a stream of **32-bit words** in memory. RLA and RLAD data fields are in little endian order within these words (the first field starts in the MSBits of a word). Standard RL encoding uses big endian. This is distinct from the byte endianness of the **32-bit words** in memory, which is a system property and does not affect the encoding/decoding process

- `rlad_format`: Color format of the uncompressed image. The RLAD block converts the configured format after decompression to ARGB8888, which is the format the DC layer has to be configured for (in linear order and with component swizzle ARGB). Alpha value is set to 255 for RGB and GRAY formats

## 6 Display controller configuration

### RLAD image format

```

/* RLAD image format */

typedef enum

{

CY_GFX_RLAD_FMT_ARGB4444,

CY_GFX_RLAD_FMT_ARGB1555,

CY_GFX_RLAD_FMT_RGB565,

CY_GFX_RLAD_FMT_ARGB8888,

CY_GFX_RLAD_FMT_RGB888,

CY_GFX_RLAD_FMT_RGB666,

CY_GFX_RLAD_FMT_RGB444,

CY_GFX_RLAD_FMT_GRAY8,

CY_GFX_RLAD_FMT_GRAY6,

CY_GFX_RLAD_FMT_GRAY4

} cy_en_gfx_rlad_fmt_t;

```

- enable: Enable/disable the RLAD decoder

2. Set the image configuration for RLAD during graphics subsystem initialization by calling the Cy\_GFXSS\_Init API. Alternatively, explicitly use the Cy\_GFXSS\_RLAD\_SetImage API, followed by Cy\_GFXSS\_RLAD\_Enable

3. After RLAD decoder is configured, render the RLAD encoded image frame to the target layer (as per layer\_id) using cy\_GFXSS\_Set\_FrameBuffer or Cy\_GFXSS\_Set\_Overlay0/1 APIs; the decoder streams decoded pixels on-the-fly into the configured layer without additional copying

4. Once the frame rendering is complete, RLAD decoder can be disabled using Cy\_GFXSS\_RLAD\_Disable API

The following snippet shows rendering a 800x480 32-bit image encoded in RLAD format using PSOC™ Edge MCU. For more information, see [mtb-example-psoc-edge-gfx-rlad](#) code example.

## 6 Display controller configuration

### RLAD

```

GFXSS_Type* base = (GFXSS_Type*) GFXSS;

cy_stc_gfx_context_t gfx_context;

/* RLAD configuration */

cy_stc_gfx_rlad_cfg_t rlad_cfg =

{

.layer_id          = GFX_LAYER_GRAPHICS,           /* Graphics Layer ID */

.image_width       = (IMG_PTR_WIDTH - 1U),          /* Image width */

.image_height      = (IMG_PTR_HEIGHT - 1U),          /* Image height */

.compressed_image_size = (SIZE_IN_WORDS - 1UL),      /* compressed image size */

.image_address     = (uint32_t*)gfx_buff,           /* Image address */

.compression_mode  = CY_GFX_RLAD_MODE_RLAD,         /* RLAD compression mode */

.rlad_format       = CY_GFX_RLAD_FMT_RGB888,        /* RLAD display format */

.enable            = 1,                                /* Enabled */

};

/* Prior rendering graphics subsystem and display are configured */

/* Copy the stored image asset to ram */

memcpy(gfx_buff, img_ptr, sizeof(img_ptr));

/* Set RLAD config and enable RLAD */

Cy_GFXSS_RLAD_SetImage(base, &rlad_cfg, &gfx_context);

Cy_GFXSS_RLAD_Enable(base, &gfx_context);

/* Set frame address as base address of compressed image */

Cy_GFXSS_Set_FrameBuffer(base, rlad_cfg.image_address, &gfx_context);

```

**Note:** The RLAD configuration must not be changed again before the frame-complete interrupt. Besides causing an inconsistent setup for a display frame, this can lead to data corruption in the active configuration.

## 7 MIPI DSI host and D-PHY configuration

### 7 MIPI DSI host and D-PHY configuration

The MIPI DSI Host sits between the MCU's display controller and the panel, converting rendered pixels and control commands into DSI packets that the D-PHY transmits over one or more serial lanes. The DSI host transmits the DSI packets in the form of parallel data to the D-PHY through the PHY protocol interface (PPI). The D-PHY serializes the packets and sends them across the serial link.

The DSI host has two types of system interfaces:

#### 1. DC interface

- In Video mode, DSI host receives a continuous pixel stream via DPI (DPI-24/18/16), packetizes per the selected transfer type (non-burst pulses/events or burst), and transmits in High-Speed with the required clock-lane behavior

- In Command mode, it ingests panel commands and windowed pixel bursts via DBI, using Low-Power packets for control and High-Speed long writes for image updates

#### 2. APB interface

- The DSI host also supports an APB Slave Generic Interface to send DCS or manufacturer-specific commands to a display in DBI and DPI mode. In particular, this includes get commands with read cycles, which are not supported by the DC in graphics subsystem

Clocking is provided by a D-PHY PLL locked to the 24 MHz reference, generating the HS lane bit rate and the lane byte clock that drive the Host's packetizer and FIFOs.

Both Video and Command mode are already described above. Next, the following will focus on configurations pertaining to MIPI DSI and D-PHY.

#### 7.1 DSI host PHY parameters

This section presents the D-PHY parameters controlled from the DSI host.

##### 1. Number of lanes

The DSI host provides a scalable architecture using one or two data lanes. Each DSI lane has a maximum of 1.5 Gbps data rate, for a total 3 Gbps rate in dual data lane mode. Even though the D-PHY supports 2 lanes but the panel dictates what we should actually use. Some panels require a single lane, others support two lanes with their own per-lane maximum bit rates. User must match the panel's lane capability and never exceed its per-lane limit, even if the host can drive faster.

Both the 800x480 4.3-inch video mode and the 466x466 1.43-inch command mode display support only a single lane. Accordingly, set the Number of DSI Lanes to 1 under the graphics tab in the device configurator.

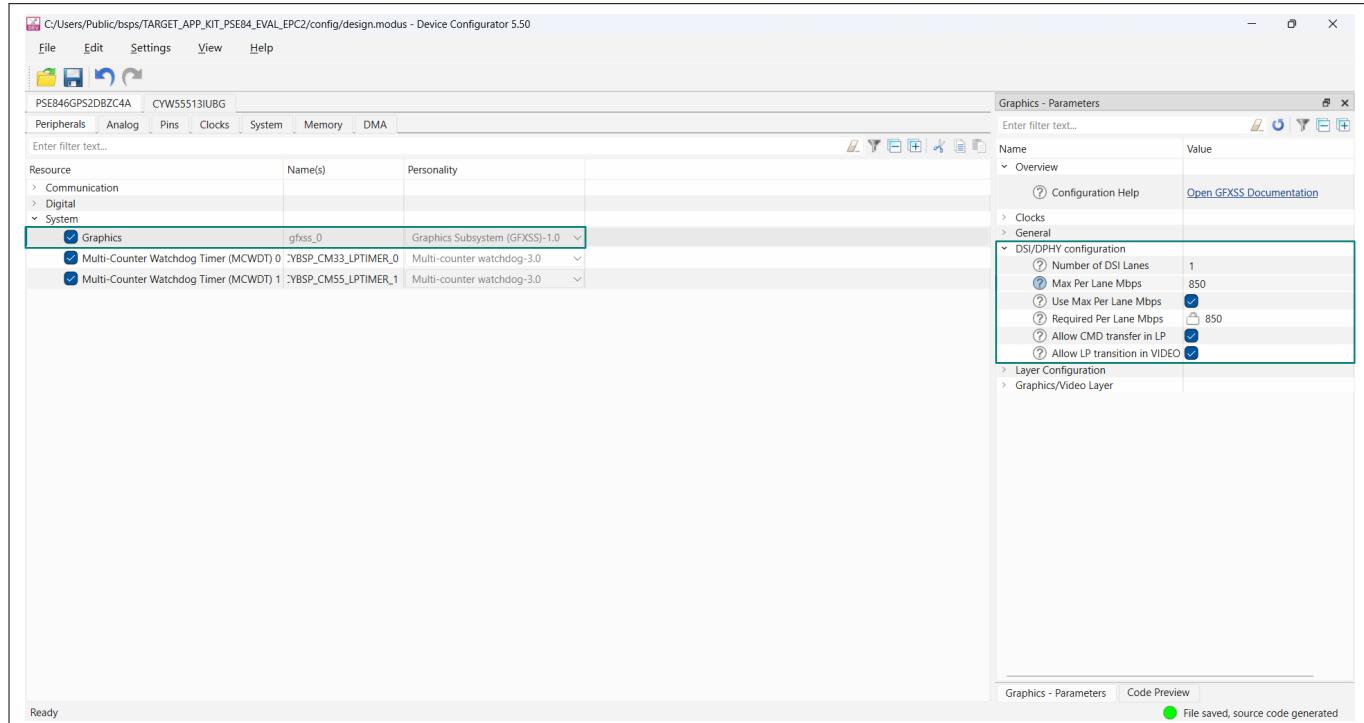

##### 2. Per lane rate

The per-lane high-speed bit rate defines how fast each D-PHY data lane transmits payload to the panel. It must always be within the panel's per-lane limit and the DSI host's capability. In this setup, the host supports up to 1.5 Gbps per lane, but the panels constrain the configuration: the 4.3-inch display is single-lane with a maximum of 850 Mbps per lane, and the 1.43-inch display is single-lane with a maximum of 700 Mbps per lane. Users should never exceed these panel caps, even if the host can drive faster.

###### • Per lane rate configuration for the video mode panel

- When Use Max Per Lane

Mbps option is checked

The DSI host sets the per lane rate (per\_lane\_mbps) to the maximum (e.g., 850 Mbps) specified in the Max Per Lane

Mbps field in the Device Configurator, regardless of the actual payload determined by video timings, target refresh, DPI format, and lane count. This

## 7 MIPI DSI host and D-PHY configuration

ensures a deterministic HS duty cycle and provides extra margin, but it may consume more power than necessary

- When Use Max Per Lane

Mbps option is unchecked

The DSI host calculates the lane rate based on the configured video timings and format, disregarding the configured maximum lane rate, and then operates only as fast as necessary to transmit the payload. This approach is power-efficient and minimizes the HS duty cycle, but it is important to maintain headroom and stay within the panel's per-lane limit

For 4.3-inch display in 16-bit (RGB565) color mode with DPI-24 interface:

per lane rate (per\_lane\_mbps) =  $H\_TOTAL \times V\_TOTAL \times \text{Total BPP} \times \text{Frame Rate} / (\text{Number of Lanes})$

Total Horizontal Period (H\_TOTAL) = HSync width + HBP + Display active width + HFP [in pixels] = 10 + 20 + 832 + 210 = 1072

Total Vertical Period (V\_TOTAL) = VSync width + VBP + Display active height + VFP [in lines] = 5 + 20 + 480 + 20 = 525

Total BPP = 3 bytes/pixel = 24 (DPI-24)

Frame Rate = 60 Hz

Number of Lanes = 1

per lane rate (per\_lane\_mbps) = 810 Mbps

### • Per lane rate configuration for the command mode panel

- The DSI host considers the entered value of Per Lane Mbps field and drives the display accordingly. In case of 1.43-inch command mode display, as per panel specification maximum of 700 Mbps per lane is configured

- The resulting per-lane high-speed bit rate determines our lane byte clock and, by extension, constrains the maximum DBI ingress clock we can use to feed the DSI TX FIFO. DBI clock determines how fast the display controller can feed commands and pixel data into the DSI host's transmit FIFO in command mode. If the DBI clock is too low, the FIFO starves and bursts take too long, risking missed update deadlines and visible stutter or tearing.

For example, in case of 1.43-inch command mode the DBI clock gets auto calculated as follows:

Lane rate = 700 Mbps (single lane)

Lane byte clock = Lane rate/8 = 87.5 MHz (Lane byte clock  $\geq 3 \times$  Rx escape clock)

DBI clock (max 37.5 MHz)  $\leq$  Lane byte clock/4 = 21.875 MHz within the limit

## 3. Video mode configuration flags

These flags control how the DSI host manages power and link behavior while streaming the video. They let the host send control commands in low-power (LP) mode and drop the link back to LP during vertical and horizontal blanking intervals, reducing the high-speed (HS) duty cycle without disturbing active video. Configuring them correctly can lower power, provided the panel supports these behaviors.

### • Enable command transmission in low-power mode

- Purpose: Send short DCS commands (Display On/Off, Sleep In/Out, Set Pixel Format, TE enable, brightness updates) using LP packets instead of HS, so the clock lane and data lanes need not remain in HS for control traffic