# **WLBGA Layout Design Guide**

**Associated Part Family: CYW43340**

This application note provides important information about the CYW43340 that pertains to WLBGA package layout design. Such information includes trace routing restrictions, parts placement, descriptions of the six layers of the CYW43340, and guidelines for layout, routing, and component selection.

## Contents

| 1 | About this Document1                | 7.1 XTAL Layout Guidelines         | 11 |

|---|-------------------------------------|------------------------------------|----|

|   | 1.1 Cypress Part Numbering Scheme 1 | 7.2 RF Routing Guidelines          | 12 |

|   | 1.2 Acronyms and Abbreviations 1    | 7.3 SDIO Layout Guidelines         | 13 |

| 2 | IoT Resources1                      | 7.4 HSIC Layout Guidelines         | 14 |

| 3 | Introduction2                       | 7.5 PMU—VBAT, CBUCK Guidelines     | 14 |

| 4 | Trace Routing Restrictions3         | 7.6 PMU—VOUT_3P3                   | 19 |

| 5 | Parts Placement4                    | 7.7 PMU—PMU_CLDO                   | 20 |

| 6 | Layers 5                            | 7.8 Power Rail—CLDO                | 21 |

|   | 6.1 Top Layer 5                     | 7.9 Power Rail— VOUT_LNLDO         | 22 |

|   | 6.2 Second Layer 6                  | 7.10 PMU—VOUT_2P5                  | 22 |

|   | 6.3 Third Layer 7                   | 7.11 PMU—BTLDO2P5                  | 23 |

|   | 6.4 Fourth Layer 8                  | 7.12 GND Cutout                    | 24 |

|   | 6.5 Fifth Layer 9                   | Document History Page              |    |

| 7 | Guidelines 11                       | Worldwide Sales and Design Support | 26 |

#### 1 About this Document

#### 1.1 Cypress Part Numbering Scheme

Cypress is converting the acquired IoT part numbers from Broadcom to the Cypress part numbering scheme. Due to this conversion, there is no change in form, fit, or function as a result of offering the device with Cypress part number marking. The table provides Cypress ordering part number that matches an existing IoT part number.

Table 1. Mapping Table for Part Number between Broadcom and Cypress

| Broadcom Part Number | Cypress Part Number |

|----------------------|---------------------|

| BCM43340             | CYW43340            |

#### 1.2 Acronyms and Abbreviations

In most cases, acronyms and abbreviations are defined on first use.

For a comprehensive list of acronyms and other terms used in Cypress documents, go to: http://www.cypress.com/glossary

#### 2 IoT Resources

Cypress provides a wealth of data at <a href="http://www.cypress.com/internet-things-iot\_to">http://www.cypress.com/internet-things-iot\_to</a> help you to select the right IoT device for your design, and quickly and effectively integrate the device into your design. Cypress provides customer access to a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates. Customers can acquire technical documentation and software from the Cypress Support Community website (<a href="http://community.cypress.com/">http://community.cypress.com/</a>).

## 3 Introduction

The CYW43340 has the following layers:

- Layer 1: Part placement, RF signal

- Layer 2: GND

- Layer 3: Digital, I/O signals and clock

- Layer 4: GND

- Layer 5: Most of the power lines

- Layer 6: GND

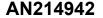

The mechanical size of the CYW43340 is 4.47 mm × 5.67 mm. The various blocks are shown in Figure 1.

Figure 1: CYW43340 Pin Map

# 4 Trace Routing Restrictions

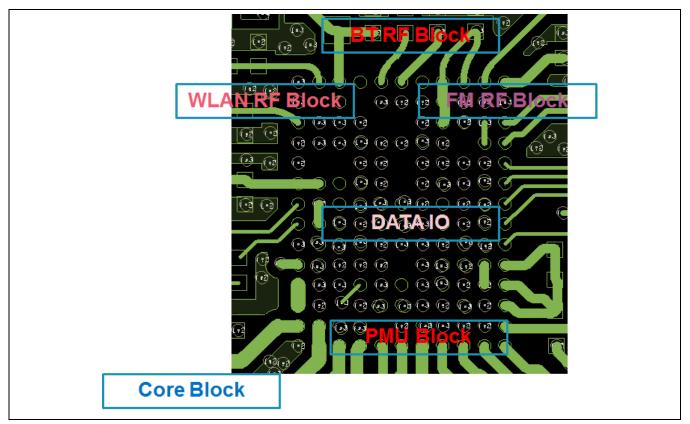

There are several keep-out areas on the CYW43340 WLBGA package, as shown in red in Figure 2. Do not route any traces below these areas on the top layer.

Figure 2. Keep-Out Areas

## 5 Parts Placement

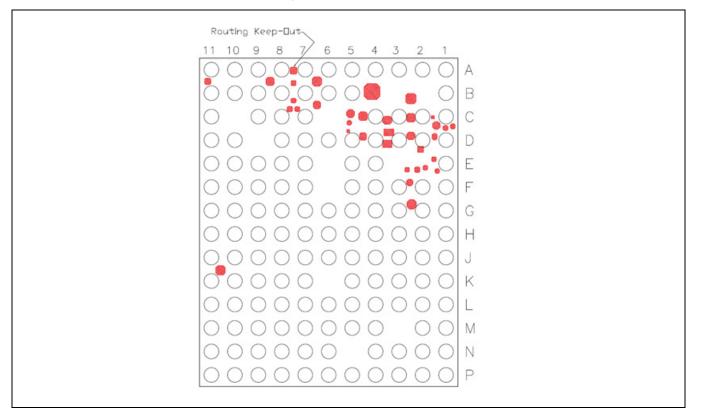

The locations of the various parts that are placed on the CYW43340 are shown in Figure 3.

Figure 3. Part Placement

# 6 Layers

# 6.1 Top Layer

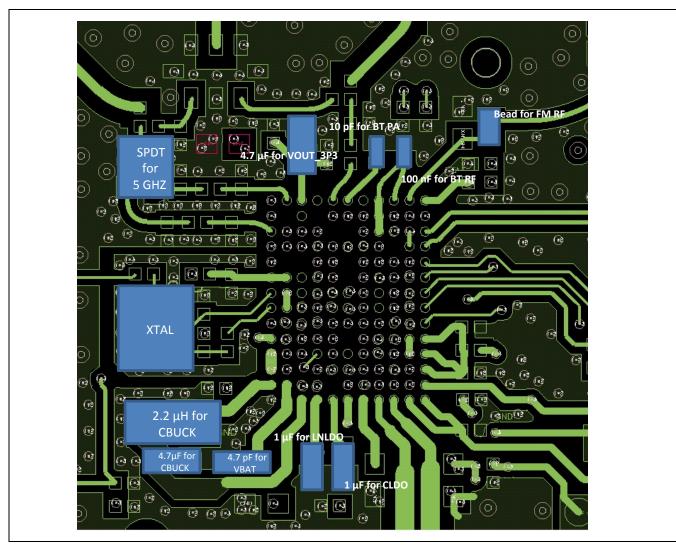

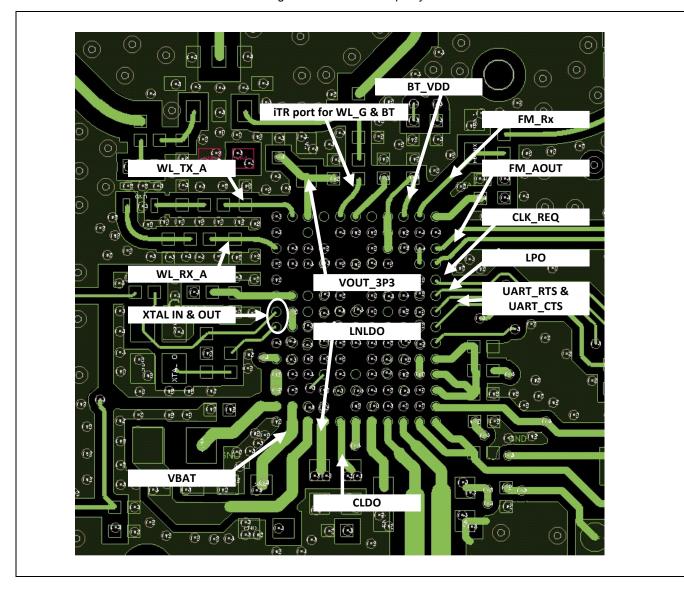

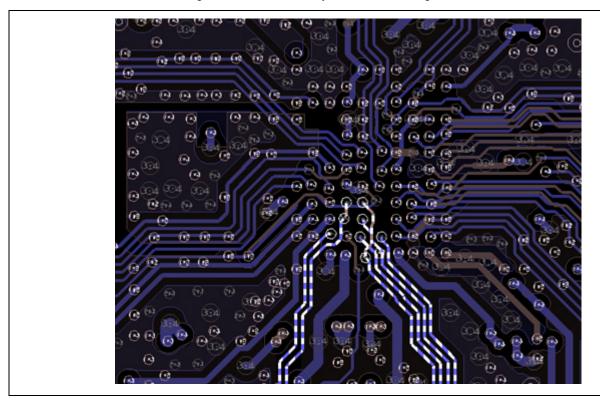

The top layer of the CYW43340 is shown in Figure 4.

Figure 4. CYW43340 Top Layer

## 6.2 Second Layer

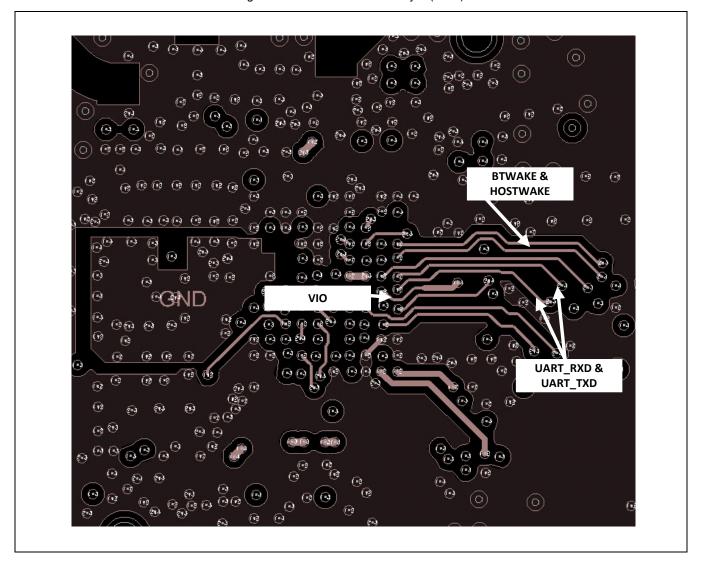

The second layer (GND) of the CYW43340 is shown in Figure 5.

Figure 5. CYW43340 Second Layer (GND)

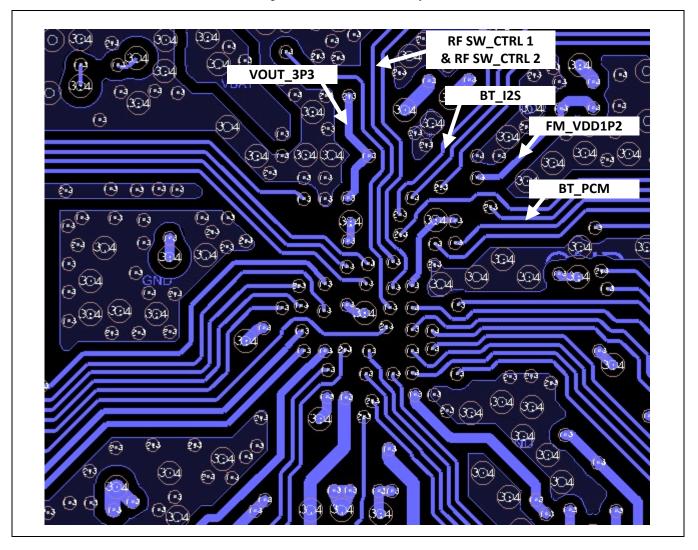

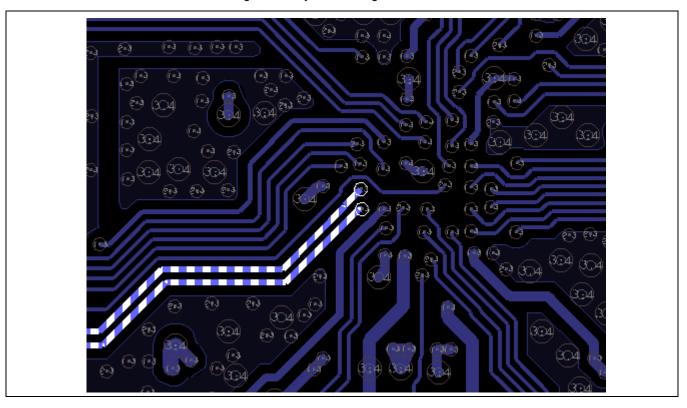

# 6.3 Third Layer

The third layer of the CYW43340 is shown in Figure 6.

Figure 6. CYW43340 Third Layer

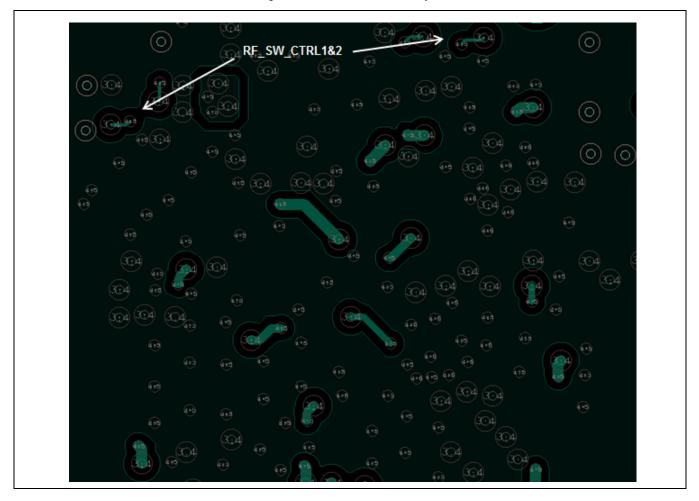

# 6.4 Fourth Layer

The fourth layer (GND) of the CYW43340 is shown in Figure 7.

Figure 7. CYW43340 Fourth Layer

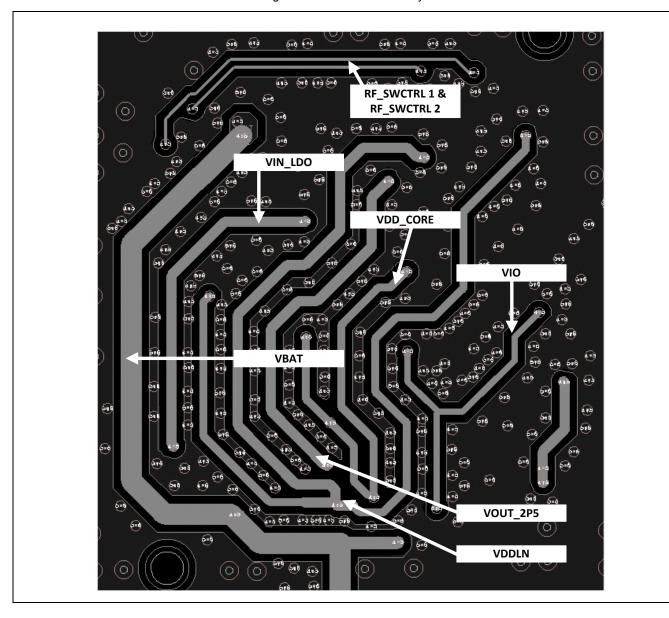

# 6.5 Fifth Layer

The fifth layer of the CYW43340 is shown in Figure 8.

Figure 8. CYW43340 Fifth Layer

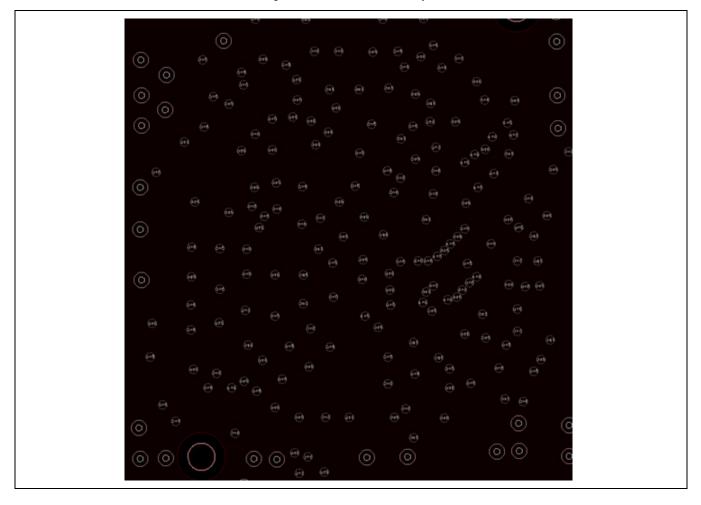

# 6.6 Sixth Layer

The sixth layer of the CYW43340 is shown in Figure 9.

Figure 9. CYW43340 Sixth Layer

## 7 Guidelines

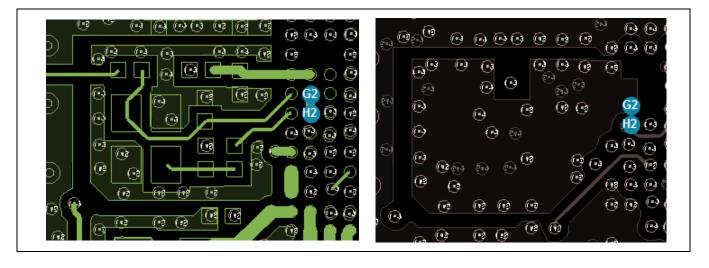

# 7.1 XTAL Layout Guidelines

- The GND and loading capacitors of the XTAL must have a low impedance and a direct path to pins G2 and H2 (see Figure 10).

- The XTAL GND plane should have a direct via to the reference GND plane.

- Isolate the XTAL GND from noisy lines to avoid coupling.

- Isolate the XTAL GND on the second and third layers.

Figure 10. G2 and H2 Pins on Top Layer (Left) and Second Layer (Right)

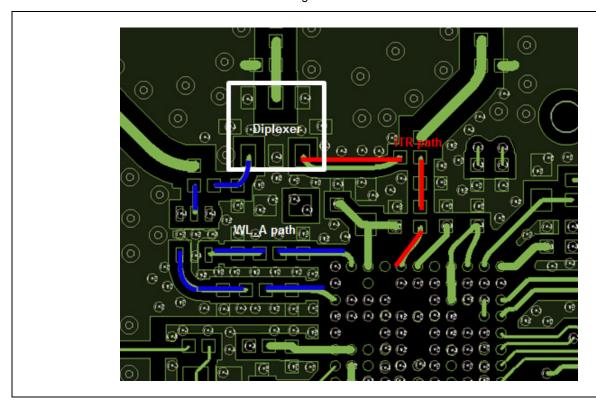

## 7.2 RF Routing Guidelines

- When routing RF lines, try to keep them on the same layer on the component side to avoid using a via on the RF lines.

- Add GND stitches around RF lines and ensure that they are 50-ohm impedance.

- Provide adequate isolation and spacing on each RF trace.

- Regarding the distance of the RF traces between the CYW43340 and the FEM, make sure that the TX line is the shorter of the two (see Figure 11).

Figure 11. RF Traces

## 7.3 SDIO Layout Guidelines

- The characteristic impedance of the SDIO2.0 traces should be 50 ohms.

- Do not leave any stubs on traces and limit the length of DATA trace to not exceed that of the CLK trace.

- Match the lengths of the SDIO lines to within ±100 mils. Note that the time delay is about 16.7 ps for every 100 mils of length.

- Keep the SDIO\_CLK line away from the SDIO CMD and DATA lines (use the 2:1 rule of thumb). Routing the SDIO\_CLK line parallel and close to command and data lines can cause glitches on the bus, thus affecting SDIO operation.

Figure 12. CYW43340 Layer 2 and 3 Showing SDIO Traces

# 7.4 HSIC Layout Guidelines

- Match the length of the traces to limit the time delay to less than 15 ps.

- The characteristic impedance of the traces should be 50 ohms.

- The trace length from the CYW43340 to the HOST chip should be less than 10 cm.

Figure 13. Layer 3 showing HSIC Traces

## 7.5 PMU—VBAT, CBUCK Guidelines

## 7.5.1 Component Selection

#### 7.5.1.1 CBUCK Output Capacitor

The nominal capacitance value is 4.7 µF.

Effective capacitance should not drop more than 27% below its nominal value under 1.5V.

Minimum capacitance =  $2 \mu F$  (only guarantees basic stability).

Recommended capacitors include:

- GRM188R60J475ME84D (0603 X5R 4.7 µF 20% 6.3V Murata)

- GRM188R60J475ME19D (0603 X5R 4.7 µF 20% 6.3V Murata)

- GRM188R61A475KE15 (0603 X5R 4.7 µF 20% 10V Murata)

- GRM155R60J475ME87D (0402 X5R 4.7 µF 20% 6.3V Murata)

- GRM155R60G106M (0402 X5R 10 µF 20% 4V Murata)

This capacitor has a typical self-resonance frequency = 3 MHz. Impedance/ESR = 2 m $\Omega$ . The ESR and ESL of the capacitor must be met to achieve good noise and transient performance.

#### 7.5.1.2 SR\_VDDBATP5V, SR\_VDDBATA5V Shared Capacitor

The nominal capacitance value is 4.7 µF.

The effective capacitance should *not* drop more than 80% below its nominal value at 4.8V bias nor more than 73% below its nominal value at 4.3V bias.

For good VBAT performance, noise suppression is 1.2 µF at the 4.3Vbat level.

Recommended capacitors are:

- GRM188R60J475ME84D (0603 X5R 4.7 µF 20% 6.3V Murata)

- GRM188R60J475ME19D (0603 X5R 4.7 µF 20% 6.3V Murata)

- GRM155R60J475M 87D (0402 X5R 4.7 µF 20% 6.3V Murata)

This capacitor has a typical self-resonance frequency = 3 MHz. Impedance/ESR = 2 m $\Omega$ . The ESR and ESL of the capacitor must be met to achieve good noise and transient performance.

#### 7.5.1.3 CBUCK Inductor

The nominal inductor value is 2.2 µH.

Table 2 lists the 0805/0806-inch inductors that have been qualified to work with the CYW43340 CBUCK.

Table 2. 0805/0806-inch Inductors Qualified to Work with the CYW43340 CBUCK

| Inductor Data Sheet<br>Specifications |                | Width | Length | Height | Тур L | L Tol | DCR Typ    | DCR Tol | I <sub>dc</sub> (mA) |

|---------------------------------------|----------------|-------|--------|--------|-------|-------|------------|---------|----------------------|

| Mfr                                   | Part No.       | mm    | mm     | mm_Max | μH    | %     | m <i>W</i> | %       | <i>D</i> T < 40°C    |

| Murata                                | LQM21PN2R2NGC  | 1.25  | 2      | 1      | 2.2   | 30    | 230        | 25      | 800                  |

| Murata                                | LQM2MPN2R2NG0L | 1.6   | 2      | 1      | 2.2   | 30    | 110        | 25      | 1200                 |

The inductors listed in Table 2 are multilayered inductors, which exhibit more dynamic characteristics compared to wire-wound inductors.

Inductors other than those listed in Table 2 must be assessed by the PMU team based on the following parameters:

- Inductor part-to-part tolerance preferably should be ±20% or, at most, ±30%.

- DCR

- DCR versus temperature

- ACR

- □ ACR versus frequency: Under no-load, mid-load, maximum-load conditions.

- ACR versus frequency: Under minimum, typical, maximum operating temperatures, at maximum-load conditions.

- □ ACR vs 4 MHz ripple current amplitude for no-load and maximum-load conditions.

- I<sub>sat1</sub>: Saturation current based on nominal Inductance 30%.

- I<sub>sat2</sub>: Saturation current based on +40°C self-heating temperature rise.

- Inductance under Isat2 versus operating temperature range (i.e., -40°C to +125°C)

- Shielding

All the above characteristics must be known before an inductor can be assessed for its suitability for CBUCK.

Other considerations:

- DCR

- DCR contributes to the conduction power losses of the CBUCK.

- ☐ Excessive DCR can lead to power loss by as much as 5%.

#### ■ ACR

- □ ACR contributes to switching power losses in the CBUCK.

- □ ACR should be < 1 ohm at a 4 MHz frequency under no-load conditions to ensure that lower switching losses occur at low loads. The ACR at a frequency of 4 MHz, within a temperature range of –40°C to +125°C, and under a 600 mA load should be less than 1 ohm.

#### ■ Saturation current I<sub>sat1</sub>

- ☐ Multilayered inductor data sheets usually do not display I<sub>sat1</sub> explicitly due to its lower current level. I<sub>sat1</sub> is defined as the load current that causes the inductance to drop by 30% from the nominal value.

- ☐ An excessive drop in inductance can lead to more inductor losses due to a larger inductor ripple current through ACR. A larger inductor ripple current can also lead to more switching current injection into ground.

- □ For PWM loop stability, effective inductance at a 600 mA load should be at least 0.6 µH across all parts (tolerance included).

- $\Box$  For best peak PWM efficiency at a 200 mA load point, the effective inductance at a 200 mA load should be at least 2  $\mu$ H for the nominal part.

#### ■ Saturation current I<sub>sat2</sub>

- □ I<sub>sat2</sub> is usually shown on multilayered data sheets and is usually higher than I<sub>sat1</sub>.

- $\Box$  I<sub>sat2</sub> is defined as the saturation current that causes the inductor to self-heat by +40 $^{\circ}$ C.

- □ I<sub>sat2</sub> should be at least 750 mA.

- Inductance under I<sub>sat2</sub> versus operating temperature range (i.e., -40°C to + 125°C)

- ☐ The inductance of the inductor should be characterized with I<sub>sat2</sub> across the full operating temperature range of the inductor.

- ☐ The recommended operating temperature range is –40°C to +125°C, inclusive of the inductor self-rise temperature (i.e., +40°C).

- □ The inductor operating temperature up to +125°C (which includes the inductor self-heating of +40°C) corresponds to the customer product temperature maximum value of 85°C.

- $\hfill\Box$  The inductance should not vary by more than  $\pm 4\%$  over the operating temperature range (–40°C to +125°C) under  $I_{sat2}.$

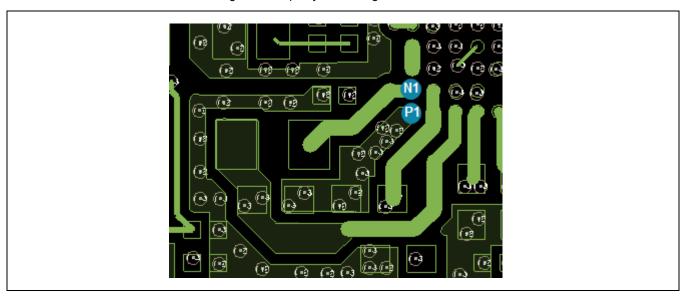

## 7.5.1.4 Top Layer

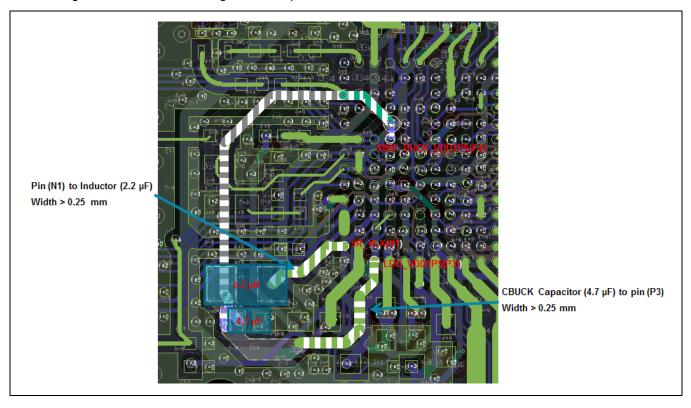

Figure 14. Top Layer Showing N1 and N2 Pins

- The bypass capacitor on VBAT and CBUCK should have many GND vias.

- Isolate the GND around CBUCK to avoid noise coupling.

- Use at least two vias on the bypass capacitor.

- To reduce EMI in the forward and return paths, the area enclosed by the following loops must be minimized:

- □ SR\_VLX1 (pin N1) to inductor and capacitor to SR\_PVSS (pin P1).

- □ SR\_VBAT to supply bypass capacitors to SR\_PVSS.

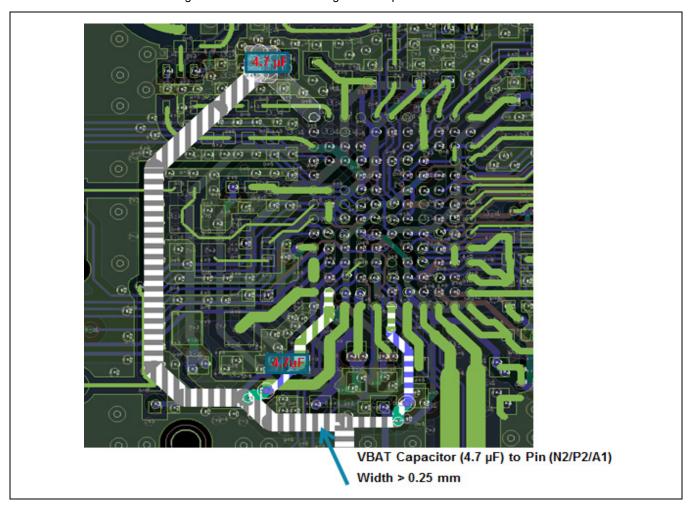

## 7.5.1.5 Power Rail: VBAT

Figure 15. Power Rail Showing VBAT Capacitor to Pin N2/P2/A1

#### 7.5.1.6 Power Rail: CBUCK

Figure 16. Power Rail Showing CBUCK Capacitor Connection to Pin P3 and Pin N1 Connection to Inductor

## 7.6 PMU—VOUT\_3P3

## 7.6.1 Component Selection

#### 7.6.1.1 LDO3P3 Output Capacitor

The nominal capacitance value is 4.7 µF.

The effective capacitance should not drop more than 66% from the nominal value under 3.3V bias.

The minimum C= 1  $\mu$ F.

Recommended capacitors include:

- GRM188R60J475ME84D (0603 X5R 4.7 µF 20% 6.3V Murata)

- GRM155R60J475ME87D (0402 X5R 4.7 µF 20% 6.3V Murata)

This capacitor has a typical self-resonance frequency = 3 MHz; impedance/ESR = 2 mohm. The ESR and ESL of the capacitor must be met to achieve good noise and transient performance.

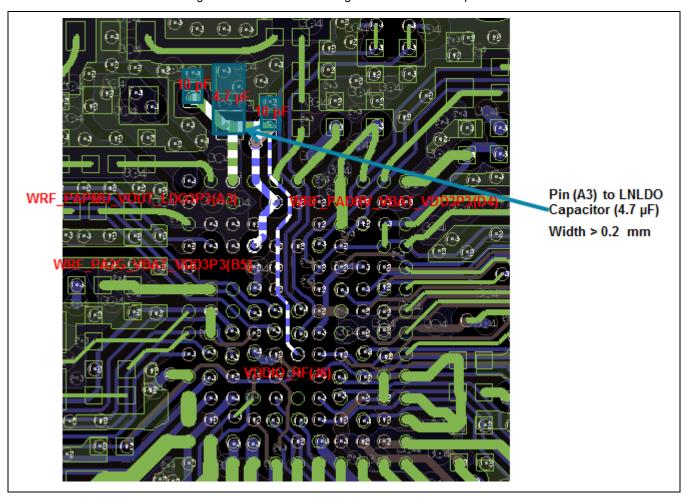

# 7.6.1.2 Power Rail—VOUT\_3P3

LDO 3P3 should have a star connection from each dedicated bypass capacitor to the pin.

Figure 17. Power Rail Showing Pin A3 to LNLDO Capacitor

# 7.7 PMU—PMU\_CLDO

## 7.7.1 Component Selection

#### 7.7.1.1 CLDO Output Capacitor

Nominal capacitance value is 1 µF.

- The effective capacitance should *not* drop more than 10% from the nominal value under 1.25V bias.

- The minimum  $C = 1 \mu F$ .

Recommended capacitors include:

- GRM188R60J105MA01 (0603 X5R 1 µF 20% 6.3V Murata)

- GRM155R60J105KE19D (0402 X5R 1 µF 20% 6.3V Murata)

This capacitor has a typical self-resonance frequency = 3 MHz; impedance/ESR = 2 mohm. The ESR and ESL of the capacitor must be met to achieve good noise and transient performance.

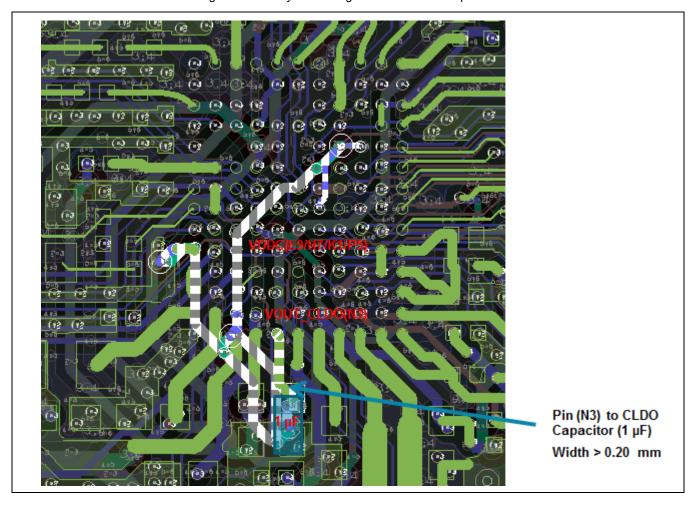

#### 7.8 Power Rail—CLDO

# 7.8.1 All Layer

The CLDO line should have a star connection routing from the source.

Figure 18. All Layer Showing Pin N3 to CLDO Capacitor

## 7.8.2 Component Selection

# 7.8.2.1 LNLDO Output Capacitor

The nominal capacitance value is 1 µF.

The effective capacitance should not drop more than 10% from the nominal value under 1.25V bias.

The minimum C = 1.22  $\mu$ F.

Recommended capacitors include:

- GRM188R60J105MA01 (0603 X5R 2.2 µF 20% 6.3V Murata)

- GRM155R60J105KE19D (0402 X5R 2.2 µF 10% 6.3V Murata)

This capacitor has a typical self-resonance frequency = 4.8 MHz; impedance/ESR = 3.5 mohm. The ESR and ESL capacitance must be met to achieve good noise and transient performance.

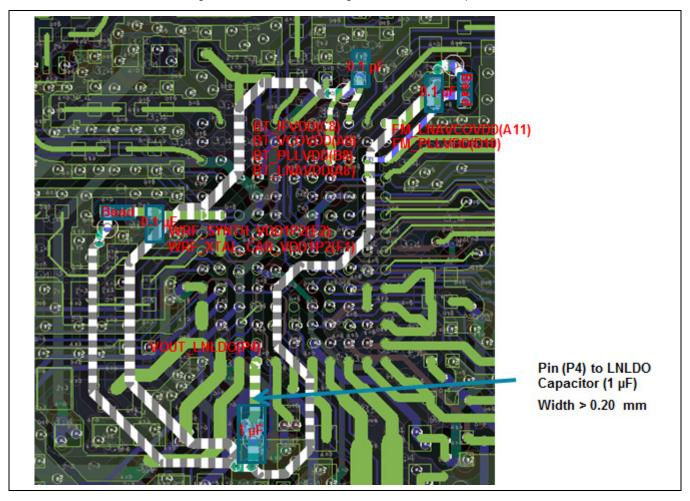

#### 7.9 Power Rail— VOUT\_LNLDO

The LNLDO line should have a star connection routing from the source.

Figure 19. Power Rail Showing Pin 94 to LNLDO Capacitor

#### 7.10 PMU—VOUT\_2P5

#### 7.10.1 **Component Selection**

#### LDO2P5 (VOUT\_2P5) Output Capacitor The nominal capacitance value is 2.2 $\mu F$ . 7.10.1.1

The capacitance should not drop more than 41% from the nominal value under 2.5V bias.

The minimum  $C = 0.85 \mu F$ .

Recommended capacitors include:

- GRM188R61A225KE34 (0603 X5R 2.2 µF 10% 10V Murata)

- GRM155R60J225ME15 (0402 X5R 2.2 µF 20% 6.3V Murata)

This capacitor has a typical self-resonance frequency = 4.8 MHz; impedance/ESR = 3.5 mohm. The ESR and ESL of the capacitor must be met to achieve good noise and transient performance.

## 7.11 PMU—BTLDO2P5

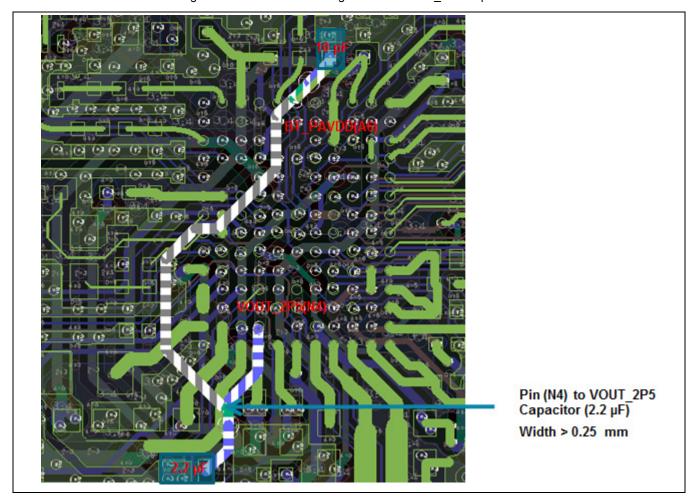

## 7.11.1 Power Rail—VOUT 2P5

The bypass capacitor (10 pF) should be placed close to pin A6 (BT\_PAVDD).

Figure 20. Power Rail Showing Pin N4 to VOUT\_2P5 Capacitor

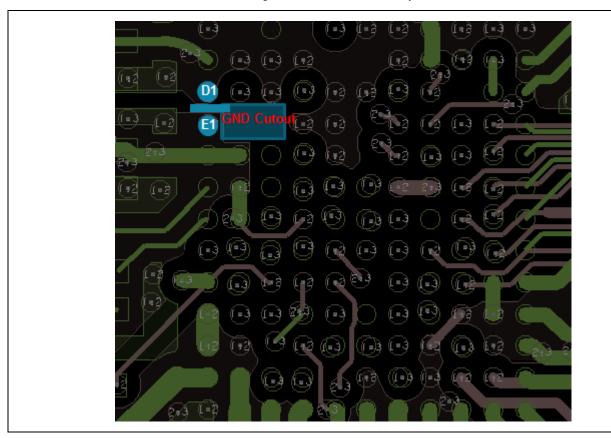

## 7.12 GND Cutout

A GND cutout is needed on layer 2, as shown in Figure 21.

On layer 2, pins D1 and E1 GND should be separated.

On layer 2, under Pin E2 and E3, GND should be cut out. If possible, the same GND cutting out on layer 3 is required.

Figure 21. GND Cutout on Layer 2

# **Document History Page**

| Document Title: AN214942 - WLBGA Layout Design Guide<br>Document Number: 002-14942 |         |                    |                    |                                                                   |  |

|------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------------------------------------|--|

| Rev.                                                                               | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                             |  |

| **                                                                                 | -       | _                  | 03/05/2014         | 43340-AN300-R<br>Initial release                                  |  |

| *A                                                                                 | 5478051 | UTSV               | 10/17/2016         | Updated in Cypress template. Added Cypress Part Numbering Scheme. |  |

| *B                                                                                 | 5824595 | AESATP12           | 07/19/2017         | Updated logo and copyright.                                       |  |

# **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

**USB Controllers**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

Wireless Connectivity cypress.com/wireless

# PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

cypress.com/usb

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2014-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1s) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.