## **Power Consumption Measurements**

**Associated Part Family: CYW43903**

This document describes procedures for measuring the current consumption of the Cypress CYW43903 WICED™ IEEE 802.11 b/g/n SoC with Embedded Applications Processor. It is intended for engineers who are designing products that include the CYW43903.

### Contents

| 1 | Abo   | ut this Document                   | 1 |

|---|-------|------------------------------------|---|

|   | 1.1   | Cypress Part Numbering Scheme      | 1 |

|   | 1.2   | Acronyms and Abbreviations         | 1 |

|   | 1.3   | References                         | 2 |

| 2 | IoT   | Resources                          | 2 |

| 3 | Intro | oduction                           | 3 |

|   | 3.1   | CYW43903 Overview                  | 3 |

|   | 3.2   | Hardware and Software Requirements | 4 |

|   | 3.3   | Clocks                             | 5 |

|   | 3.4   | Power Profiles                     | 5 |

| 4 | Mea   | surement Procedures                | 7 |

|   | 4.1   | Measurement Overview               | 7 |

|   | 4.2   | Configuration Prerequisites        | 7 |

|   | 4.3   |                                    |   |

|   | 4.4   | IEEE Power Save mode Under DTIM 1  |   |

|   |       | (2.4 GHz)                          | Ç |

| 4.5        | IEEE Power Save Mode Under DTIM 3 (2.4 GHz)                                         | 12 |

|------------|-------------------------------------------------------------------------------------|----|

| 4.6        | Use Case 1: Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep        | 13 |

| 4.7        | Use Case 2: Active Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep | 14 |

| 4.8        | Use Case 3: Low Bit Rate Data Reception                                             | 15 |

| 4.9        | Ping                                                                                | 16 |

| Appendix . | A: N6705B Configuration                                                             | 17 |

| Appendix   | B: Access Point Configuration                                                       | 21 |

| Appendix   | C: WICED SDK Requirements                                                           | 22 |

| Appendix   | D: PCB Hardware Setup                                                               | 25 |

| Appendix   | E: Reference Board Rework                                                           | 27 |

|            | F: Chip Revision Information                                                        |    |

|            | History PageSales and Design Support                                                |    |

|            |                                                                                     |    |

### 1 About this Document

## 1.1 Cypress Part Numbering Scheme

Cypress is converting the acquired IoT part numbers from Broadcom to the Cypress part numbering scheme. Due to this conversion, there is no change in form, fit, or function as a result of offering the device with Cypress part number marking. The table provides Cypress ordering part number that matches an existing IoT part number.

Table 1. Mapping Table for Part Number between Broadcom and Cypress

| Broadcom Part Number | Cypress Part Number |

|----------------------|---------------------|

| BCM43903             | CYW43903            |

| BCM43909             | CYW43909            |

### 1.2 Acronyms and Abbreviations

In most cases, acronyms and abbreviations are defined on first use. For a comprehensive list of acronyms and other terms used in Cypress documents, go to:

http://www.cypress.com/glossary

#### 1.3 References

The references in this section may be used in conjunction with this document.

**Note:** Cypress provides customer access to technical documentation and software through its Cypress Developer Community and Downloads and Support site (see IoT Resources).

For Cypress documents, replace the "xx" in the document number with the largest number available in the repository to ensure that you have the most current version of the document.

| Document (or Item) Name                                                       | Broadcom<br>Document Number | Cypress Document<br>Number | Source                         |

|-------------------------------------------------------------------------------|-----------------------------|----------------------------|--------------------------------|

| WICED <sup>™</sup> IEEE 802.11 b/g/n SoC with Embedded Applications Processor | 43903-DS1xx-R               |                            | Cypress Developer<br>Community |

| CYW43909 Programmer's Guide                                                   | 43909-PG1xx-R               |                            | Cypress Developer<br>Community |

| WICED <sup>™</sup> SDK                                                        | Version 3.5.x               | -                          | Cypress Developer<br>Community |

### 2 IoT Resources

Cypress provides a wealth of data at http://www.cypress.com/internet-things-iot to help you to select the right IoT device for your design, and quickly and effectively integrate the device into your design. Cypress provides customer access to a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates. Customers can acquire technical documentation and software from the Cypress Support Community website (http://community.cypress.com/).

#### 3 Introduction

#### 3.1 CYW43903 Overview

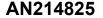

The CYW43903 embedded wireless SoC supports all rates specified in the IEEE 802.11 b/g/n specifications and includes an ARM Cortex-based applications processor, a single-stream IEEE 802.11n MAC/baseband/radio, single-band (2.4 GHz) transmit power amplifier (PA), and a receive Low Noise Amplifier (LNA).

Figure 1 shows the interconnections of all the major physical blocks in the CYW43903 and their associated external interfaces.

Figure 1. CYW43903 Functional Block Diagram

The datasheet for the CYW43903 (see References) contains detailed information on individual parts inside the chip. In this application note, the following blocks are referenced specifically:

- APPS: Application subsystem

- ACPU: Applications Processor (ARM Cortex-R4)

- WCPU: WLAN CPU (ARM Cortex-R4)

- WLAN PHY: Wireless LAN physical layer

- WLAN (WCPU + WLAN PHY)

- Backplane

#### 3.2 Hardware and Software Requirements

The following items are required to run the current measurement procedures described in this document:

- KeySight (formerly Agilent)N6705B DC Power Analyzer

- □ 14585A Control and Analysis Software for the N6705B

- Host PC: Standard Windows PC running Windows 7

- BCM943903WLBU\_1 (rev. P103) and BCM9WCD8EVAL1 (rev. P102) combo package (the reference board is pre-soldered to the evaluation board).

- A commercial 802.11n Access Point connected to a PC. The PC is used to configure the Access Point to send UDP packets to the DUT.

- WICED SDK that supports current measurement software (version 3.5.1 and above; consult your Cypress technical representative for details).

- 5V power supply

- USB cable

**Note:** The reference board must be reworked to facilitate current measurements. See Appendix E: "Reference Board Rework" for details.

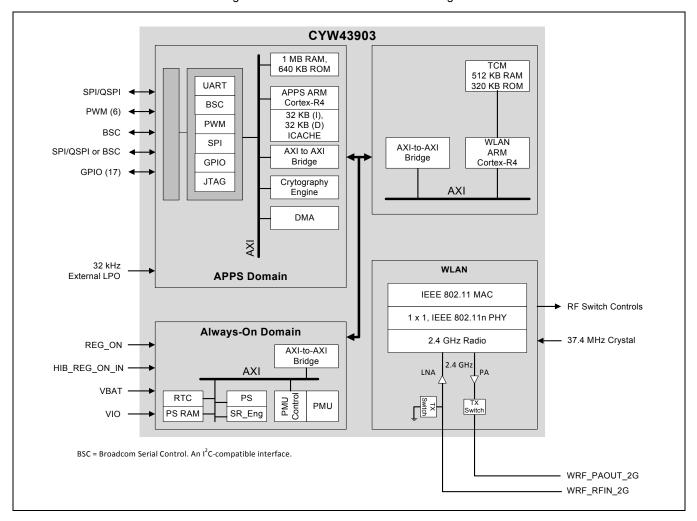

A block diagram of the hardware setup is shown in Figure 1. The reference board is plugged into the evaluation board and is powered by the N6705B through the VBAT input. The host PC (PC1) runs the WICED SDK and the power supply analysis software that controls N6705B through the LAN connection. The USB cable is used to transfer data between the evaluation board and the host PC. PC2 controls the 802.11n Access Point.

Figure 1: Current Measurement System Block Diagram

#### 3.3 Clocks

The CYW43903 has three base clocks.

- Idle Low Power (ILP): Generated by either a low-power oscillator (LPO) or by dividing the ALP clock frequency by a programmable value. Use of this clock maximizes power savings during idle states.

- Active Low Power (ALP): Supplied by an internal or external oscillator. This clock is requested by cores when accessing backplane registers in other cores or when performing minor computations. When an external crystal is used to provide reference clock, ALP clock frequency is determined by the frequency of the external oscillator. A 37.4 MHz reference clock is recommended.

- **High Throughput (HT)**: Supplied by an on-chip PLL. This clock is requested by cores when they transfer blocks of data to or from memory, perform computation-intensive operations, or need to meet the requirements of external devices. Cores that cannot tolerate operations at less than the HT clock frequency, such as the memory controller, may assert the HT clock request continuously.

The HT clock frequencies for ARM CPU and the backplane can be configured to one of five options as defined in Table 2. ARM CPU current consumption rises in tandem with the operating frequency.

| High Throughput Setting | ARM CPU Frequency (MHz) | Backplane Frequency (MHz) |

|-------------------------|-------------------------|---------------------------|

| 1                       | 320                     | 160                       |

| 2                       | 160                     | 160                       |

| 3                       | 120                     | 120                       |

| 4                       | 80                      | 80                        |

| 5                       | 60                      | 60                        |

Table 2. ACPU and Backplane HT Clock Frequencies

### 3.4 Power Profiles

The power profiles defined in this subsection reflect CYW43903 power modes in conjunction with real-world operating parameters.

#### 3.4.1 Sleep Mode, No Association to an Access Point

In this profile the CYW43903 APPS block is in a Power Down mode, the WLAN block is in Deep Sleep mode, the AON block is on, and no association has been established between the CYW43903 and an Access Point.

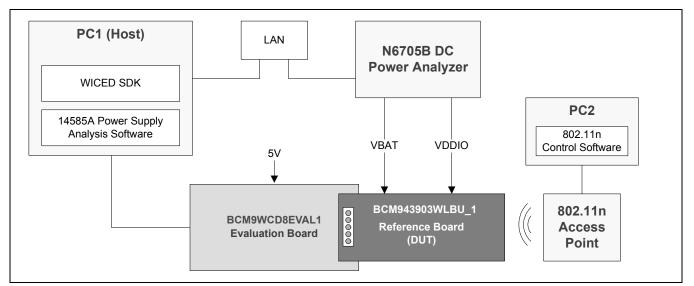

#### 3.4.2 IEEE Power Save Mode Under DTIM 1

In IEEE Power Save mode under Delivery Traffic Indication Map 1 (DTIM 1), the CYW43903 is associated with an Access Point before the CYW43903 APPS block goes into Power Down mode and the WLAN block goes into Deep Sleep mode. Before going into Deep Sleep mode, the WLAN block saves its state in memory (save-and-restore, or S/R) so that it can resume this state when it returns to Active mode (this feature is supported in the B1 and later versions of the CYW43903; see Appendix F: "Chip Revision Information" for details).

The S/R operation enables the WLAN block to wake up periodically to receive beacon packets from the Access Point. No data is transmitted, and the WLAN block returns to Deep Sleep mode after it receives a beacon packet.

In this operating scenario, the DTIM 1 duration is 102.4 ms (or 100 TU where 1 TU = 1.024 ms; see Figure 2). Three CYW43903 current measurements are taken:

- An average of the current consumed across the entire DTIM 1 interval.

- Current consumed between beacon packets, when the CYW43903 APPS block is in Power Down mode and the WLAN block is in Deep Sleep mode.

- Current consumed when the CYW43903 is receiving a beacon packet.

**Note:** The amount of time required to receive a beacon packet determines how long the WLAN block has to be active, which affects DTIM 1 current consumption. However, the Access Point can be programmed to shorten the beacon packet reception duration. See Appendix B: "Access Point Configuration" for details.

Figure 2. DTIM 1 Current Consumption

#### 3.4.3 IEEE Power Save Mode Under DTIM 3

This is identical to IEEE Power Save Mode Under DTIM 1, except the Access Point is programmed to transmit beacon packets once every 307.2 ms (300 TU) instead of every 102.4 ms (100 TU).

#### 3.4.4 Use Case 1: Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep

In this scenario, IEEE Power Save mode is enabled, and the WLAN block is in Deep Sleep mode. In this mode the APPS block is in a Wait For Instruction (WFI) state: it does not request any clock signals and there is no clock running on the backplane, but received packets will wake the APPS block and the ARM Cortex-R4. The WLAN block will enter Active mode and request a clock signal from the APPS backplane. The M2M DMA, running autonomously, requests a clock on the APPS backplane.

#### 3.4.5 Use Case 2: Active Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep

This scenario is identical to Use Case 1, except the APPS block is in Active Low Power mode and the ALP clock is running.

#### 3.4.6 Use Case 3: Low Bit Rate Data Reception

The WLAN block is in Active mode, the APPS block is in Active Low Power mode, and the Access Point is sending UDP packets at up to 2 Mbps.

#### 3.4.7 Ping

The WLAN block is in Active mode, the APPS is in Active Low Power mode, and the WLAN block is sending a ping packets to the associated Access Point at 1-second intervals.

### 4 Measurement Procedures

#### 4.1 Measurement Overview

This section contains measurement procedures for each power profile discussed in the previous section. The measurements are made on the BCM943903WLBU\_1 reference board, which is the Device Under Test (DUT) in this application note. Table 3 contains a summary of the measurement results. Further details on each test are provided in the following subsections.

Table 3. Summary of Current Measurements

| Profile                                                                   | Measurement                                             | I_VBAT<br>(VBAT = 3.6V) | I_VDDIO<br>(VDDIO = 3.3V) |

|---------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|---------------------------|

| Sleep mode, no association to an Access Point                             | _                                                       | 5.3 μΑ                  | 284 μA <sup>a</sup>       |

| IEEE Power Save mode under DTIM 1                                         | Current consumed across the DTIM 1 duration             | 1.96 mA                 | 107 μΑ                    |

|                                                                           | Current consumed between beacon packet reception events | 5.3 μΑ                  | 141 µA                    |

|                                                                           | Current consumed while receiving a beacon packet        | 54 mA                   | 52 μA                     |

| IEEE Power Save mode under DTIM 3                                         | Current consumed across the DTIM 3 duration             | 0.8 mA                  | 123 µA                    |

| Use Case 1: Waiting for Packets, IEEE Power Save Mode Enabled, WLAN Block | Current consumed across the DTIM 1 duration             | 3.1 mA                  | 1570 µA                   |

| in Deep Sleep                                                             | Current consumed between beacon packet reception events | 5.4 μA                  | 1720 µA                   |

| Use Case 2: Active Waiting for Packets, IEEE Power Save Enabled, WLAN in  | Current consumed across the DTIM 1 duration             | 14.4 mA                 | 932 μΑ                    |

| Deep Sleep                                                                | Current consumed between beacon packet reception events | 8 mA                    | 932 μΑ                    |

| Use Case 3: Low bit rate data reception                                   | _                                                       | 65.5 mA                 | 932 μΑ                    |

| Ping                                                                      | Current consumed during a ping transmission             | 327 mA                  | 932 μ                     |

a. The 284  $\mu$ A value is expected to be close to the expected VDDIO current consumption under DTIM when a beacon packet is not being received. This value is subject to change.

### 4.2 Configuration Prerequisites

The measurement procedures assume that the following have already been done:

- The BCM943909WCD1 PCB has been reworked as described in Appendix E: "Reference Board Rework"

- The hardware setup with the BCM9WCD8EVAL1 evaluation board has been done as described in Appendix D: "PCB Hardware Setup".

- The N6705B DC Power Analyzer has been configured as described in Appendix A: "N6705B Configuration".

- The WICED application for the BCM943903WLBU\_1 (the DUT) that corresponds to the test being run has been built and loaded. See Appendix C: "WICED SDK Requirements" for details.

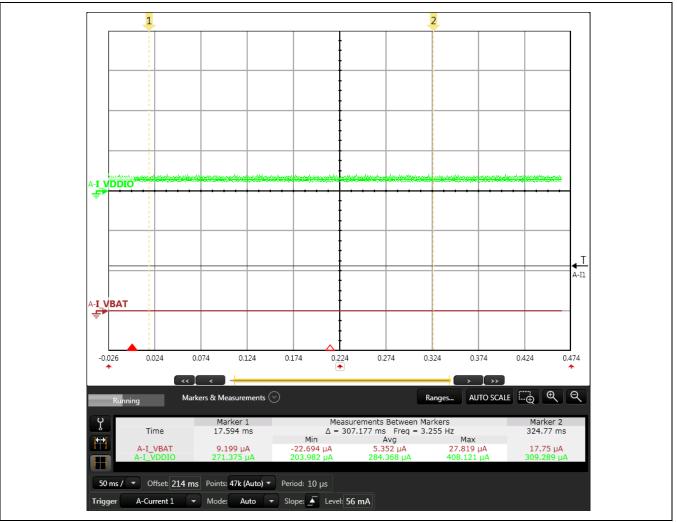

### 4.3 Sleep Mode, No Association to an Access Point

**Note:** This procedure requires the WICED DUT application to be built with Test Flag 1 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Set the Access point for DTIM 1.

- 2. Cycle power on the BCM943903WLBU\_1/BCM9WCD8EVAL1 combo board by removing and reconnecting the USB cable and cycling power on the N6750B power modules.

- 3. Measure the current from the VBAT and VDDIO power supplies. I\_VBAT should be 5.3  $\mu$ A and I\_VDDIO should be 284  $\mu$ A (see Figure 3).

Figure 3. Current—Sleep Mode, No association to an Access Point

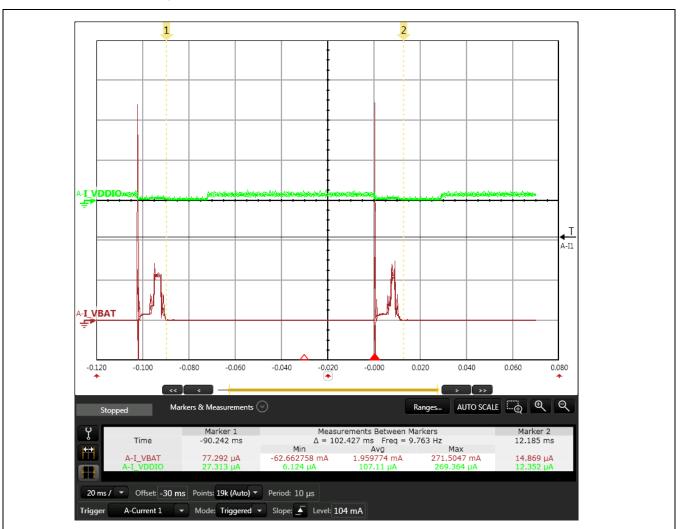

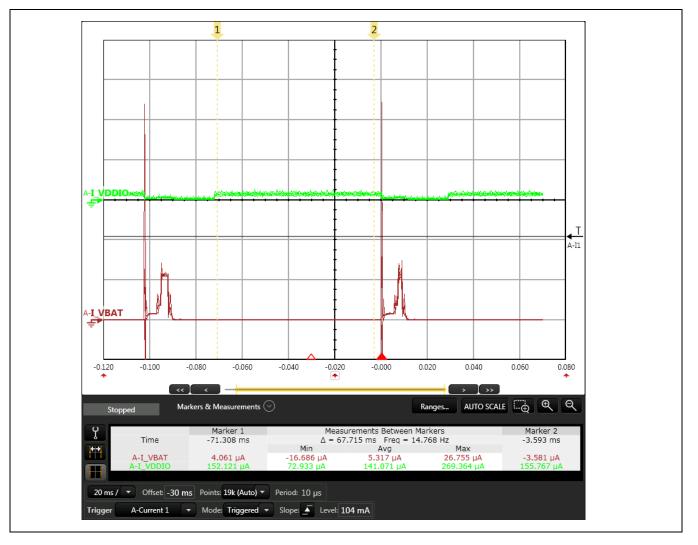

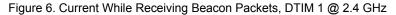

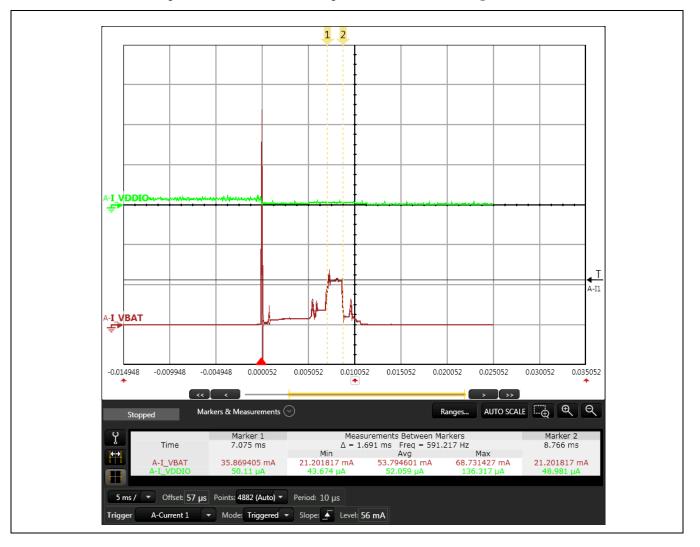

### 4.4 IEEE Power Save mode Under DTIM 1 (2.4 GHz)

**Note:** This procedure requires the WICED DUT application to be built with Test Flag 2 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Set the Access Point for DTIM 1.

- 2. Cycle power on the BCM943903WLBU\_1/BCM9WCD8EVAL1 combo board by removing and reconnecting the USB cable and cycling power on the N6750B power modules.

- Measure current consumed during the DTIM 1 duration, current consumed between beacon packets, and current consumed while a beacon packet is being received. The results are shown Table 4 and in Figure 4, Figure 5, and Figure 6.

Table 4. Current—DTIM 1, Between Beacons, and While Receiving Beacons (2.4 GHz)

| Measurement                                             | I_VBAT<br>(Average) | I_VDDIO<br>(Āverage) |

|---------------------------------------------------------|---------------------|----------------------|

| Current consumed across the DTIM 1 duration             | 1.96 mA             | 107 μΑ               |

| Current consumed between beacon packet reception events | 5.3 μΑ              | 141 μΑ               |

| Current consumed while receiving a beacon packet        | 54 mA               | 52 μΑ                |

Figure 4. Current Consumed Across the DTIM 1 Duration @ 2.4 GHz

Figure 5. Current Consumed Between Beacon Packets, DTIM 1 @ 2.4 GHz

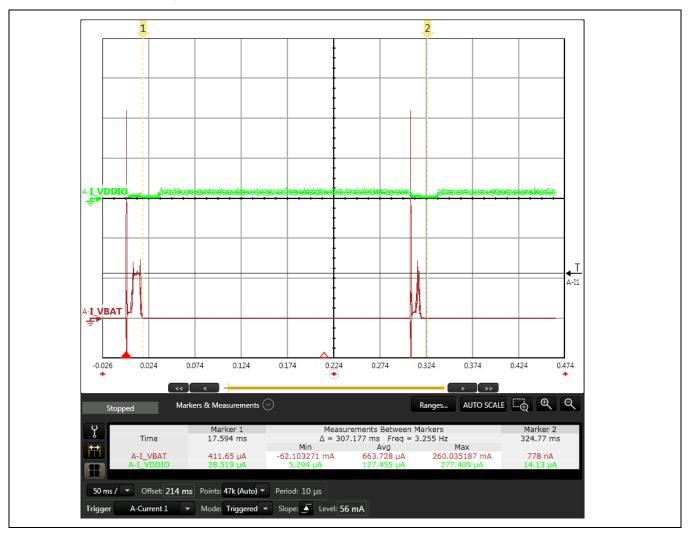

### 4.5 IEEE Power Save Mode Under DTIM 3 (2.4 GHz)

This procedure requires the WICED DUT application to be built with Test Flag 2 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Set the Access Point for DTIM 3.

- 2. Cycle power on the BCM943903WLBU\_1 (this can be done from the N6705B).

- 3. Measure the current from the VBAT and VDDIO power supplies. I\_VBAT should be 0.8 mA and I\_VDDIO should be 53 µA (see Figure 7).

Figure 7. Current Consumed Across the DTIM 3 Duration @ 2.4 GHz

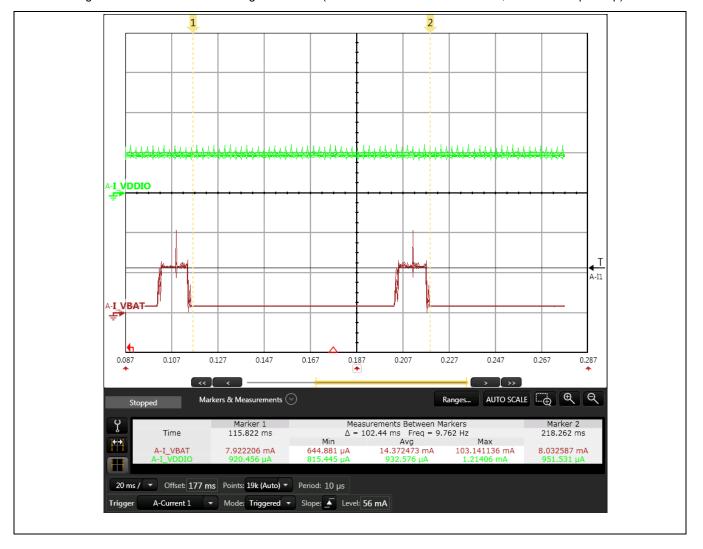

### 4.6 Use Case 1: Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep

Note: IEEE Power Save mode is enabled for this procedure.

**Note:** This procedure requires the WICED DUT application to be built with Test Flag 3 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Cycle power on the BCM943903WLBU\_1 (this can be done from the N6705B).

- 2. Measure current consumed during the DTIM 1 duration and current consumed between beacon packet reception events. The results are shown Table 5 and in Figure 8.

Table 5. Current—Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep

| Measurement                                             | I_VBAT<br>(Average) | I_VDDIO<br>(Āverage) |

|---------------------------------------------------------|---------------------|----------------------|

| Current consumed across the DTIM 1 duration             | 3.1 mA              | 1570 μΑ              |

| Current consumed between beacon packet reception events | 5.4 μA              | 1720 μΑ              |

Figure 8. Current—Waiting for Packets (IEEE Power Save Mode Enabled, WLAN = Deep Sleep)

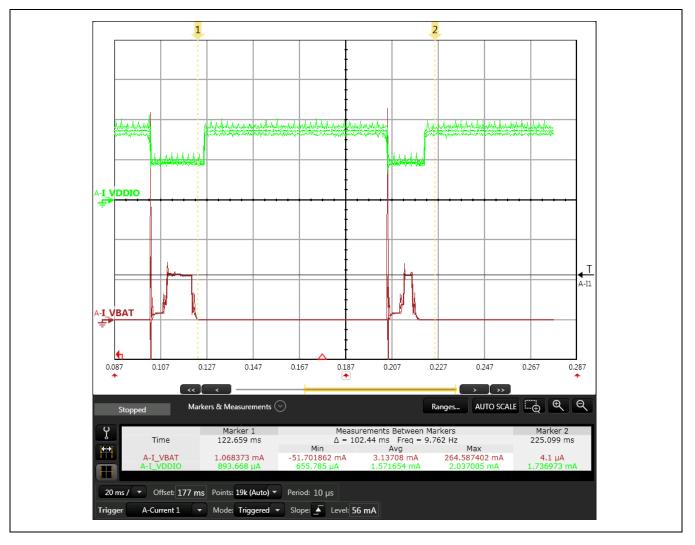

### 4.7 Use Case 2: Active Waiting for Packets, IEEE Power Save Enabled, WLAN in Deep Sleep

Note: IEEE Power Save mode is enabled for this procedure.

**Note:** This procedure requires the WICED DUT application to be built with Test Flag 4 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Cycle power on the BCM943909WCD1 (this can be done from the N6705B).

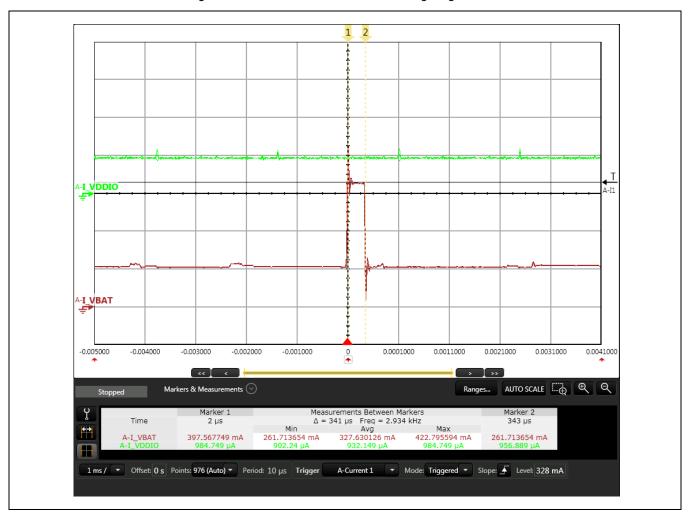

- 2. Measure current consumed during the DTIM 1 duration and current consumed between beacon packet reception events. The results are shown Table 6 and in Figure 9.

Table 6. Current—Active Waiting for Packets, IEEE Power Save Mode Enabled, WLAN in Deep Sleep

| Measurement                                             | I_VBAT<br>(Average) | I_VDDIO<br>(Āverage) |

|---------------------------------------------------------|---------------------|----------------------|

| Current consumed across the DTIM 1 duration             | 14.4 mA             | 932 μΑ               |

| Current consumed between beacon packet reception events | 8 mA                | 932 μΑ               |

Figure 9. Current—Active Waiting for Packets (IEEE Power Save Mode Enabled, WLAN = Deep Sleep)

#### 4.8 Use Case 3: Low Bit Rate Data Reception

The bit rate is controlled by the Access Point. Cypress engineers recommend a bit rate of 0.5 Mbps for this test. This can be done through the *Iperf* test utility by defining the -b BITRATE option in the command line. In the example below, 1 Mbps is selected:

```

iperf -c serveraddress -u -b 500k

```

See Appendix B: "Access Point Configuration" for more details on Access Point Configuration.

**Note:** This procedure requires the WICED DUT application to be built with Test Flag 5 enabled. See Appendix C: "WICED SDK Requirements" for details.

- 1. Cycle power on the BCM943909WCD1 (this can be done from the N6705B).

- 2. Open the appropriate COM port on the host PC.

```

- - X

COM19 - PuTTY

Starting WICED v3.5.1

Platform BCM943903WCD1 1 initialised

Started ThreadX v5.6

Initialising NetX Duo v5.7 sp2

Creating Packet pools

WWD SoC.43909 interface initialised

WLAN MAC Address : 02:0A:F7:62:8E:A9

WLAN Firmware

: w10: Oct 20 2015 12:30:35 version 7.15.168.50 (r594009) FWID

01-38dccb13

> Joining : GK-4360B

Successfully joined : GK-4360B

IPv4 network ready IP: 192.168.1.100

Setting IPv6 link-local address

IPv6 network ready IP: FE80:0000:0000:0000:000A:F7FF:FE62:8EA9

Spawning a listener.

Server listening on UDP port 5001

Receiving 1470 byte datagrams

UDP buffer size: 8.00 KByte (default)

```

- 3. The DUT should now be ready to receive data packets from the Access Point.

- 4. Enter the following command to send UDP packets from the Access Point to the DUT using the IP address (192.168.1.100):

```

iperf -c 192.168.1.100 -u -i1 -b500k

```

5. Measure the current from the VBAT and VDDIO power supplies. I\_VBAT should be 65.5 mA and I\_VDDIO should be 932  $\mu$ A.

### **4.9** Ping

This test measures current consumption when the DUT is sending a ping packet to the associated Access Point.

- 1. Build and download the snip.ping\_powersave-BCM943903WCD1\_1 download run application (see Appendix C: "WICED SDK Requirements").

- 2. Open the appropriate COM port on the host PC.

- 3. Cycle power on the DUT, then check the COM port terminal window on the host PC to confirm that the DUT is sending ping messages to the Access Point.

- 4. Measure current during the packet transmission as shown below. I\_VBAT should be 327 mA and I\_VDDIO should be 932  $\mu$ A (see Figure 10).

Figure 10. Current Consumed While Sending Ping Packets

## Appendix A: N6705B Configuration

### A.1. N6705B Overview

The N6705B DC power analyzer is used to measure current consumption. It has two embedded DC supply modules. In the context of this application note, Module 1 (N6782A) is connected to the VBAT input on the DUT (that is, the BCM943903WLBU\_1), and Module 2 (N6784A) is connected to the VDDIO input on the DUT.

**Agilent Technologies** N6705B DC Power Analyzer WLAN HW APPS EMB Source 3.5998 V 5.5664 uA Set 3.60000 V 8 TUV 9 WXYZ 3.30000 No Module No Module Power Supply 0 On On @I/O **™**LAN **Waveform Display**

Figure 11. N6705B DC Power Analyzer

## A.2. 14585A Control and Analysis Software

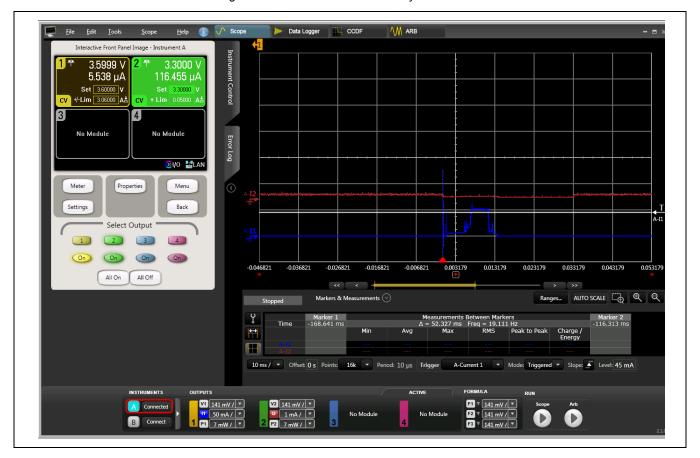

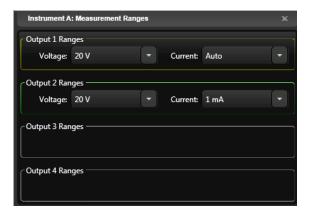

The N6705B is controlled through the 14585A control and analysis software running on the PC. The user interface is shown in Figure 12. 14585A software is used to set plotting parameters and to configure of the embedded power supply modules in the N6705B.

Measurement accuracy is function of current range settings. To configure the current range, open the **Scope** menu, select **Measurement Ranges**, and set the following current range parameters:

- 3A range = 0.03% + 250 µA

- 100 mA range = 0.025% + 10 µA

- 1 mA range = 0.025% + 100 nA

- 10 µA range = 0.025% + 8 nA

Figure 12. 14585A Control and Analysis Software

**Note:** Cypress engineers recommend that N6705B accuracy be verified by measuring a known voltage across a known resistance value (for example 3.3V across a 470 k $\Omega$  resistor).

## A.3. Configuring the Power Supply Modules

Cypress engineers recommend that the auto-ranging feature on the N6705B be enabled for the two power supplies used in the hardware setup. This feature is mandatory for the module connected to the VBAT supply on the BCM943903WLBU\_1 (Module 1 in the context of this application note) because it varies over a large range, from hundreds of milliamps down to a few microamps.

**Note:** Auto-ranging should also be enabled for Module 2 (VDDIO) if it is available. If auto-ranging is not available for Module 2, manually change the settings to the lowest possible range for a given measurement

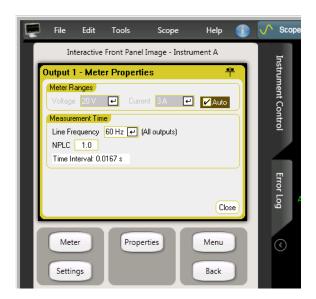

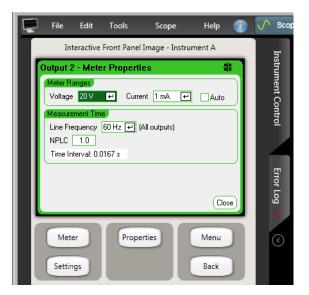

Follow the steps below to enable auto-ranging on Module 1.

1. In the Interactive Front Panel Image - Instrument A control panel, click 1 (Module 1), then click the Properties button. The Output 1 - Meter Properties control panel will open.

- 2. In the **Output 1 Meter Properties** control panel:

- a. Set the voltage as required for the test being run.

- b. Set the current as required for the test being run.

- c. Select the **Auto** option to enable auto-ranging.

- d. Click the Close button.

3. Repeat Step 1 on page 19 and Step 2 for Module 2. If auto-ranging is not available, select the lowest possible setting for the given test to get the best accuracy (for example, a limit of 1 mA should be set for DTIM tests).

- 4. The Module 1 and Module 2 settings must be duplicated in the 14584A "Soft Scope" in order for the current consumption calculations to be done correctly.

- a. Click the Scope button, then select Measurement Ranges. The Measurement Ranges window will open.

b. In the **Measurement Ranges** window, duplicate the settings chosen for Module 1 and Module 2. An example is shown below

## **Appendix B: Access Point Configuration**

### B.1. Access Point Overview

Any commercially available Access Point may be used for doing the current measurements. The following subsections define information that is relevant for the tests described in this application note.

#### B.1.1. DTIM Period

The Delivery Traffic Indication Map (DTIM) period is a parameter associated with an infrastructure network, and is advertised in an Access Point beacon frame. All beacon frames include a Traffic Indication Map (TIM) which indicates to the infrastructure stations (STAs) that buffered frames are available. Unicast frames buffered for individual stations are delivered in response to a query from the station. However, this polled approach is not suitable for multicast and broadcast frames because it takes too much capacity to transmit multicast and broadcast frames multiple times. Instead of the polled approach, broadcast and multicast frames are delivered after every DTIM interval.

Increasing the DTIM duration allows stations to conserve power, but at the cost of buffer space in the Access Point and delays in reception of multicast and broadcast frames by all stations, including stations in active mode.

The default DTIM beacon interval for most Access Points is either DTIM = 1 or DTIM = 3. In the case of DTIM = 3, the station need only wake from low power mode to receive every third beacon and any ensuing queued broadcast or multicast traffic.

### B.1.2. Beacon Packet Size

The access beacon size must be ≤101 bytes to get low current consumption numbers. This may be achieved by:

- Disabling WMM

- Disabling Wi-Fi Protected Setup (WPS)

- Reducing the country information. A beacon packet contains 6 bytes of information on the country in which the given Access Point is operating (this option may not be supported in some Access Points).

- Changing to 802.11b mode only (that is, rate 1) when operating at 2.4 GHz. For 5 GHz operation, the data rate can be 6 Mbps.

#### B.1.3. Band Setting

When testing 2.4 GHz or 5 GHz, ensure that the Access Point is set to the appropriate band.

## Appendix C: WICED SDK Requirements

## C.1. WLAN Firmware

WLAN firmware that supports the "save-and-restore" feature is required. Version 3.5.1 of the WICED SDK is the first release that supports this feature. The firmware is located in the following directory:

#### resources/firmware/43909B0.bin

This file must be named 43909B0.bin in order for the DUT application to function correctly.

### C.2. NVRAM

The WLAN NVRAM file is located in the following directory:

## platforms\BCM943903WCD1\_1\wifi\_nvram\_image.h

This file must be named wifi\_nvram\_image.h in order for the DUT application to function correctly.

## C.3. Updating Access Point information

Go to apps/test/powersave.c directory and enter the following line to update the Access Point Service Set Identifier (SSID):

```

* #define POWERSAVE_JOIN_COMMAND "join test123 open PASSWORD 192.168.1.100 192.168.1.255 192.168.1.1"

```

## C.4. Test Flags in powersave.c

The test flags in apps/test/powersave.c are defined in Table 7. Only one test flag is set to 1 at any time; all others are cleared. Different tests require different test flags to be enabled.

| Test Flag No. | Test Flag Name                                                      | Value  |

|---------------|---------------------------------------------------------------------|--------|

| 1             | #define POWERSAVE_STANDALONE_TEST_DEEPSLEEP_NO_ASSOC                | 0 or 1 |

| 2             | #define POWERSAVE_STANDALONE_TEST_DEEPSLEEP_ASSOC                   | 0 or 1 |

| 3             | #define POWERSAVE_STANDALONE_TEST_WAIT_FOR_WLAN                     | 0 or 1 |

| 4             | #define POWERSAVE_STANDALONE_TEST_ACTIVE_WAIT_FOR_WLAN              | 0 or 1 |

| 5             | #define POWERSAVE_STANDALONE_TEST_LOW_POWER_NETWORKING              | 0 or 1 |

| 6             | #define POWERSAVE_STANDALONE_TEST_WAKEUP_FROM_DEEP_SLEEP<br>PROFILE | 0 or 1 |

Table 7. List of Test Flags in apps/test/powersave.c

A separate instance of the DUT application must be created for each test flag being used. For example, when building an application to support a power profile in which the BCM943903WLBU\_1 is in a deep sleep state and is not associated with an Access point, the following test flag configuration would be used:

```

#define POWERSAVE_STANDALONE_TEST_DEEPSLEEP_NO_ASSOC 1

#define POWERSAVE_STANDALONE_TEST_DEEPSLEEP_ASSOC 0

#define POWERSAVE_STANDALONE_TEST_WAIT_FOR_WLAN 0

#define POWERSAVE_STANDALONE_TEST_ACTIVE_WAIT_FOR_WLAN 0

#define POWERSAVE_STANDALONE_TEST_LOW_POWER_NETWORKING 0

#define POWERSAVE_STANDALONE_TEST_WAKEUP_FROM_DEEP_SLEEP_PROFILE 0

```

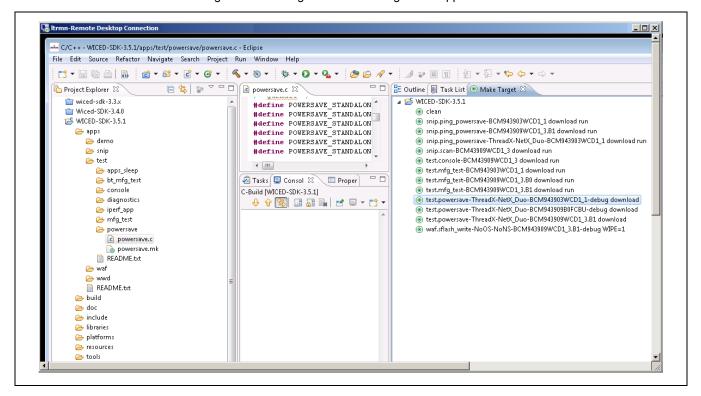

## C.5. Building and Downloading an Application

After updating the test flags in powersave.c, build the application as shown in Figure 13 using the following make target:

### test.powersave-ThreadX-NetX\_Duo-BCM43903WCD1\_1 download

JTAG must be enabled in order to download the application. To enable JTAG, configure the SW1 switch as follows:

- S1 = ON

- S2 = ON

- S3 = OFF

- S4 = OFF

Cycle power on the BCM943903WLBU\_1 after downloading the application.

Figure 13. Building and Downloading a Test Application

## C.6. Ping Mode Application

The WICED SDK includes the following application to measure current when the CYW43903 is sending a ping to the associated Access Point:

#### snip.ping\_powersave-BCM943909WCD1\_1 download run

In order for the ping application to work properly, some lines in a Wi-Fi configuration file must be edited:

#### Wiced-SDK/include/default\_wifi\_config\_dct.h

The specific lines that must be edited are:

```

#define CLIENT_AP_SSID "YOUR_AP_SSID"

#define CLIENT_AP_PASSPHRASE "YOUR_AP_PASSPHRASE"

#define CLIENT_AP_SECURITY WICED_SECURITY_WPA2_MIXED_PSK

```

#### The edits are shown below in bold:

```

#define CLIENT_AP_SSID "test123"

#define CLIENT_AP_PASSPHRASE ""

#define CLIENT_AP_SECURITY WICED_SECURITY_OPEN

```

Where the Access Point password (YOUR APP PASSPHRASE) is deleted and test123 represents the SSID of the Access Point being used.

# Appendix D: PCB Hardware Setup

## D.1. PCB Setup Overview

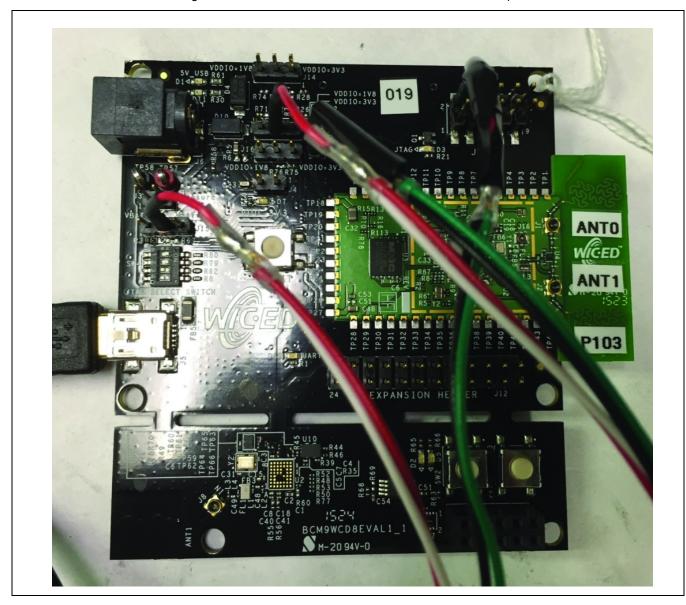

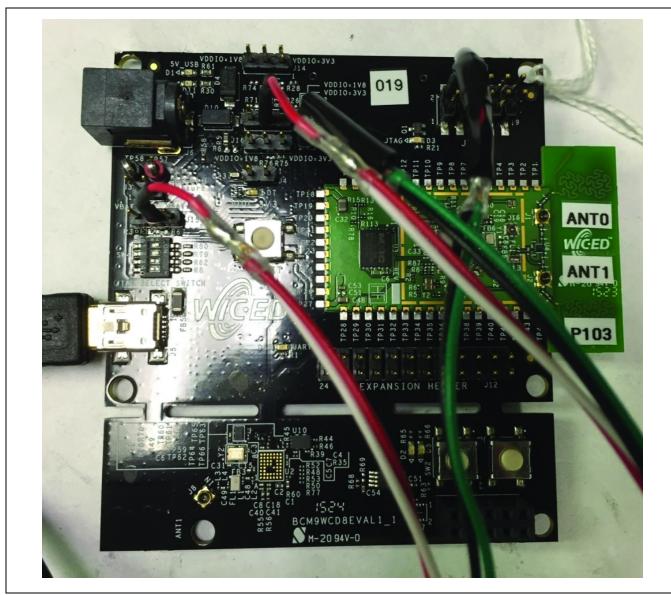

Figure 14 shows a picture of the PCB hardware setup, in which the BCM943903WLBU\_1 reference board (green) soldered onto the BCM9WCD8EVAL1 evaluation board (black).

Figure 14. Reference Board/Evaluation Board Hardware Setup

## D.2. Configuring the PCB Hardware Setup

**Note:** The procedures below assume that the rework described in Appendix E: "Reference Board Rework" has already been performed.

Follow the procedure below to set up the PCB hardware for current measurements:

- 1. On the BCM9WCD8EVAL1:

- a. Connect VBAT 3.6V to J15 pin 2 and connect a GND lead to J2 pin 2.

- b. Connect VDDIO 3.3V to J13 pin 2 and connect a GND lead to J1 pin 2.

- 2. On the host PC, open the Device Manager and confirm that the BCM943903WLBU 1 has been detected.

- 3. Load the WICED SDK DUT application into the BCM943903WLBU\_1.

- 4. Cycle power on the BCM943903WLBU\_1 by turning the embedded N6705B power supply modules off and then on.

## Appendix E: Reference Board Rework

## E.1. BCM943903WLBU\_1 Overview

The BCM943903WLBU\_1 (rev. P103) reference board is shown in Figure 15. The BCM943903WLBU\_1 and BCM9WCD8EVAL1 are shipped as a package with the two boards soldered together. Current consumption is measured on the reference board only. The purpose of the rework is to ensure that only the current going into the reference board (the green PCB) is measured.

Figure 15. BCM943903WLBU\_1 Reference Board

The rework required to configure the BCM943903WLBU\_1 to support CYW43903 current measurement is defined in Table 8.

## Table 8. BCM943903WLBU\_1 Rework Tasks

| Task No. | Description                                                                                                   | Comment |  |

|----------|---------------------------------------------------------------------------------------------------------------|---------|--|

| 1        | Remove R36                                                                                                    | _       |  |

| 2        | Remove R72                                                                                                    | _       |  |

| 3        | Connect VBAT 3.6V to J15 pin 2 and connect a GND lead to J2 pin 2                                             | _       |  |

| 4        | Connect VDDIO 3.3V to J13 pin 2 and connect a GND lead to J1 pin 2.                                           |         |  |

| 5        | Connect USB cable to the host PC. This will also supply 5V to the support circuits – on the evaluation board. |         |  |

| 6        | Set the SW1 configuration switch to enable JTAG:  ■ S1 and S2 = ON  ■ S3 and S4 = OFF.                        | _       |  |

|          | JTAG must be enabled in order to download an application to the CYW43903.                                     |         |  |

# Appendix F: Chip Revision Information

## F.1. Getting the CYW43903 Chip Revision

The silkscreen marking on the CYW43903 indicates the chip revision. P10, P20, and P21 correspond to revision A0, B0, and B1, respectively.

# **Document History Page**

| Document Title: AN214825 - Power Consumption Measurements Document Number: 002-14825 |         |          |            |                                                                   |  |

|--------------------------------------------------------------------------------------|---------|----------|------------|-------------------------------------------------------------------|--|

| Rev. ECN No. Orig. of Change Date Description of Change                              |         |          |            | Description of Change                                             |  |

| **                                                                                   | _       | _        | 12/22/2015 | 43903-AN100-R<br>Initial release                                  |  |

| *A                                                                                   | 5477983 | UTSV     | 11/08/2016 | Updated to Cypress template. Added Cypress Part Numbering Scheme. |  |

| *B                                                                                   | 5839074 | AESATMP8 | 07/31/2017 | Updated logo and Copyright.                                       |  |

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

## PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2015-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1s) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.