The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

### **How to Check the Ordering Part Number**

- 1. Go to <a href="https://www.cypress.com/pcn">www.cypress.com/pcn</a>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to <a href="https://www.cypress.com">www.cypress.com</a>.

1

# FR, MB91460, External Bus Interface

This Application Note describes how to achieve the maximum performance for external connected memories and how to connect the different types with the MB91460 series MCUs. The Application note is also covering the constraints which have to be taken into account for maximum bus frequencies and the selection of suitable memories for optimized performance.

#### Contents

| 1 | Int | troduction                     |    |

|---|-----|--------------------------------|----|

|   | 1.1 | Key Features                   | 1  |

| 2 | Th  | ne External Bus Interface      | 3  |

|   | 2.1 | Outline                        | 3  |

|   | 2.2 | Registers                      | 6  |

| 3 | Ini | tialization in Start.asm       |    |

|   | 3.1 | Start.asm                      | 21 |

| 4 | Ex  | ternal Bus Interface examples  | 30 |

|   | 4.1 |                                |    |

|   |     | memory                         | 30 |

|   | 4.2 |                                |    |

|   |     | memory                         |    |

| 5 | Tir | ming analysis                  | 31 |

|   | 5.1 | Flash Read AC characteristics  | 31 |

|   | 5.2 | RAM Read AC characteristics    | 32 |

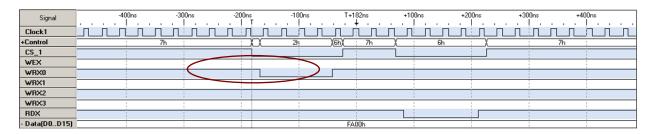

|   | 5.3 | RAM Write AC characteristics   | 33 |

|   | 5.4 | MCU External Bus Basic Timings | 34 |

| 35                 |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|

|                    |  |  |  |  |  |  |  |

| 36                 |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

| 37                 |  |  |  |  |  |  |  |

| 38                 |  |  |  |  |  |  |  |

| 41                 |  |  |  |  |  |  |  |

| kternal<br>41      |  |  |  |  |  |  |  |

| ed on<br>42        |  |  |  |  |  |  |  |

| ed on              |  |  |  |  |  |  |  |

| 42                 |  |  |  |  |  |  |  |

| 43                 |  |  |  |  |  |  |  |

| Document History44 |  |  |  |  |  |  |  |

|                    |  |  |  |  |  |  |  |

### 1 Introduction

High flexibility to adapt MCUs to different and fast external memories in a variety of voltage levels is a customer demand. To meet this requirement the MB91460 Series MCUs provide a external bus interface with the capabilities to connect Flash, SRAM and SDRAM with up to 8 different chip select lines.

This Application Note describes how to achieve the maximum performance for external connected memories and how to connect the different types with the MB91460 series MCUs. The Application note is also covering the constraints which have to be taken into account for maximum bus frequencies and the selection of suitable memories for optimized performance.

#### 1.1 Key Features

#### The External Bus Interface has the following features

- Addresses of up to 32 bits (4 GB space) can be output.

- Various kinds of external memory (8-bit/16-bit/32-bit modules) can be directly connected and multiple access timings can be mixed and controlled.

- Asynchronous SRAM and asynchronous ROM/FLASH memory (multiple write strobe method or byte enable method)

- Page mode ROM/FLASH memory (Page sizes 2, 4, and 8 can be used)

- Burst mode ROM/FLASH memory (such as MBM29BL160D/161D/162D)

- Address/data multiplex bus (8-bit/16-bit width only)

- SDRAM (FCRAM modules are also supported, including two and four bank types with CAS latency 1 to 8)

- Synchronous memory (such as ASIC built-in memory) (Synchronous SRAM cannot be directly connected)

- Eight independent banks (chip select areas) can be set, and chip select corresponding to each bank can be output.

- <sup>□</sup> The size of each area can be set in multiples of 64 KB (64 KB to 2 GB for each chip select area).

- An area can be set at any location in the logical address space (Boundaries may be limited depending on the size of the area.)

#### In each chip select area, the following functions can be set independently

- Enabling and disabling of the chip select area (Disabled areas cannot be accessed)

- Setting of the access timing type to support various kinds of memory

- Detailed access timing setting (individual setting of the access type such as the wait cycle)

- Setting of the data bus width (8-bit/16-bit)

- Setting of the order of bytes (big or little endian) (Only big endian can be set for the CS0 area)

- Setting of write disable (read-only area)

- Enabling and disabling of fetches from the built-in cache

- Enabling and disabling of the prefetch function

- Maximum burst length setting (1, 2, 4, 8)

#### A different detailed timing can be set for each access timing type

- For the same type of access timing, a different setting can be made in each chip select area.

- Auto-wait can be set to up to 15 cycles (asynchronous SRAM, ROM, Flash, and I/O area).

- □ The bus cycle can be extended by external RDY input (asynchronous SRAM, ROM, Flash, and I/O area).

- The first access wait and page wait can be set (burst, page mode, and ROM/FLASH area).

- Various kinds of idle/recovery cycles and setting delays can be inserted.

- Capable of setting timing values such as the CAS latency and RAS CAS delay (SDRAM area)

- Capable of controlling the distributed/centralized auto refresh, self refresh, and other refresh timings (SDRAM area)

#### ■ Fly-by transfer by DMA can be performed.

- Transfer between memory and I/O can be performed in a single access operation.

- □ The memory wait cycle can be synchronized with the I/O wait cycle in fly-by transfer.

- The hold time can be secured by only extending transfer source access.

- Idle/recovery cycles specific to fly-by transfer can be set.

- External bus arbitration using BRQ and BGRNT can be performed.

- Pins that are not used by the external interface can be used as general-purpose I/O ports through settings.

#### 2 The External Bus Interface

The basic functionality of the external bus interface

#### 2.1 Outline

The External Bus Interface allows the user to connect external peripherals or memory to the MCU. The Bus consists of data, address and control signals. Various settings are possible for several bus timings.

#### 2.1.1 Bus modes and access modes

#### Bus modes

The bus mode controls internal ROM operation and the external access function. The bus mode is specified by the mode setting pins (MD2, MD1, and MD0) and internal ROM enable bit.

The FR-family CPU has the following three bus modes.

#### Single chip mode

In this mode, internal I/O, internal RAM, and internal ROM are available but access to other areas is disabled. External pins are used either by the peripheral functions or as general-purpose ports. Pins cannot be used as bus pins. This mode cannot be used when using the fixed mode/reset vector as implemented on most of the MB91460 series devices.

#### Internal ROM, external bus mode

In this mode, internal I/O, internal RAM, and internal ROM are available, and access to areas for which external access is enabled results in access to the external area. Some external pins function as bus pins.

#### External ROM, external bus mode

In this mode, internal I/O and internal RAM are available but access to internal ROM is prohibited. Access to internal ROM areas and areas for which external access is enabled results in access to the external area. Some external pins function as bus pins.

#### Access mode

The access mode controls the width of the external data bus.

# 2.1.2 Address Maps Of Bus Modes

Figure 2-1 shows the different address maps for the three MCU bus modes for MB91F467DA.

Figure 2-1. Address maps of MB91F467DA bus modes

|                          | Single Chip                  |                        | Internal ROM,<br>External Bus |                        | External ROM,<br>External Bus |

|--------------------------|------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|

| 0000:0000 <sub>H</sub>   | I/0 (Direct addressing area) | 0000:0000 <sub>H</sub> | I/0 (Direct addressing area)  | 0000:0000 <sub>H</sub> | I/0 (Direct addressing area)  |

| 0000:0400 <sub>H</sub>   | I/O                          | 0000:0400 <sub>H</sub> | I/O                           | 0000:0400 <sub>н</sub> | I/O                           |

| 0000:1000 <sub>H</sub>   | DMA                          | 0000:1000 <sub>н</sub> | DMA                           | 0000:1000 <sub>H</sub> | DMA                           |

| 0000:2000 <sub>H</sub>   |                              | 0000:2000 <sub>н</sub> |                               | 0000:2000 <sub>H</sub> |                               |

| 0000:4000 <sub>H</sub>   | Flash-Cache (8KByte)         | 0000:4000 <sub>H</sub> | Flash-Cache (8KByte)          | 0000:4000 <sub>H</sub> | Flash-Cache (8KByte)          |

| 0000:6000 <sub>H</sub>   |                              | 0000:6000 <sub>н</sub> |                               | 0000:6000н             |                               |

| 0000:7000 <sub>H</sub>   | Flash Memory Control         | 0000:7000 <sub>H</sub> | Flash Memory Control          | 0000:7000 <sub>H</sub> | Flash Memory Control          |

| 0000:8000 <sub>H</sub>   |                              | 0000:8000 <sub>H</sub> |                               | 0000:8000 <sub>H</sub> |                               |

| 0000:B000 <sub>H</sub>   | Boot ROM (4KBytes)           | 0000:B000 <sub>H</sub> | Boot ROM (4KBytes)            | 0000:В000 <sub>Н</sub> | Boot ROM (4KBytes)            |

| 0000:C000 <sub>H</sub>   | CAN                          | 0000:С000 <sub>Н</sub> | CAN                           | 0000:C000 <sub>H</sub> | CAN                           |

| 0000:D000 <sub>H</sub>   |                              | 0000:D000 <sub>Н</sub> |                               | 0000:D000 <sub>H</sub> |                               |

| 0002:8000 <sub>H</sub>   | D-RAM (0 wait, 32Kbytes)     | 0002:8000 <sub>H</sub> | D-RAM (0 wait, 32Kbytes)      | 0002:8000 <sub>Н</sub> | D-RAM (0 wait, 32Kbytes)      |

| 0003:0000 <sub>H</sub>   | ID RAM (32KBytes)            | 0003:0000 <sub>Н</sub> | ID RAM (32KBytes)             | 0003:0000 <sub>H</sub> | ID RAM (32KBytes)             |

| 0003:8000 <sub>H</sub>   |                              | 0003:8000 <sub>н</sub> |                               | 0003:8000 <sub>H</sub> |                               |

| 0004:0000 <sub>H</sub>   |                              | 0004:0000 <sub>Н</sub> |                               | 0004:0000 <sub>н</sub> |                               |

|                          | Flash Memory<br>(1088KBytes) |                        | Flash Memory<br>(1088KBytes)  |                        | External Bus Area             |

| 0015:0000 <sub>H</sub>   |                              | 0015:0000 <sub>Н</sub> |                               | 0015:0000 <sub>н</sub> |                               |

| 0018:0000 <sub>H</sub>   |                              | 0018:0000 <sub>Н</sub> | External Bus Area             | 0018:0000 <sub>Н</sub> | External Bus Area             |

| 0050:0000 <sub>H</sub>   |                              | 0050:0000 <sub>H</sub> | External Bus Area             | 0050:0000 <sub>н</sub> | External Bus Area             |

| FFFF:FFFF <sub>H</sub> [ | Internal                     | FFFF:FFFF <sub>H</sub> | No Access                     | FFFF:FFFF <sub>H</sub> | External                      |

Figure 2-2. Address maps of MB91F467BA bus modes shows the different address maps for the three MCU bus modes for MB91F467BA.

Figure 2-2. Address maps of MB91F467BA bus modes

|                                                    | Single Chip                                               | _                                                  | Internal ROM,<br>External Bus                                  |                                                                                             | External ROM,<br>External Bus                                  |

|----------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 0000:0000 <sub>н</sub>                             | I/0 (Direct addressing area)                              | 0000:0000 <sub>H</sub>                             | I/0 (Direct addressing area)                                   | 0000:0000 <sub>H</sub>                                                                      | I/0 (Direct addressing area)                                   |

| 0000:0400 <sub>н</sub>                             | I/O                                                       | 0000:0400н                                         | I/O                                                            | 0000:0400 <sub>н</sub>                                                                      | I/O                                                            |

| 0000:1000 <sub>н</sub> -<br>0000-10FF <sub>н</sub> | DMA                                                       | 0000:1000 <sub>н</sub> -<br>0000-10FF <sub>н</sub> | DMA                                                            | 0000:1000 <sub>н</sub> -<br>0000-10FF <sub>н</sub>                                          | DMA                                                            |

| 0000:2000 <sub>H</sub> -<br>0000:5FFF              | Flash Memory I-Cache or<br>Instruction RAM                | 0000:2000 <sub>H</sub> -<br>0000:5FFF              | Flash Memory I-Cache or<br>Instruction RAM                     | 0000:2000 <sub>H</sub> -<br>0000:5FFF                                                       | Flash Memory I-Cache or<br>Instruction RAM                     |

| 0000:7000 <sub>H</sub> -<br>0000:70FF              | Flash Memory Control                                      | 0000:7000 <sub>H</sub> -<br>0000:70FF              | Flash Memory Control                                           | 0000:7000 <sub>H</sub> -<br>0000:70FF                                                       | Flash Memory Control                                           |

| 0000:8000 <sub>H</sub> -<br>0000: BFFF             | Boot ROM (4KBytes)                                        |                                                    | Boot ROM (4KBytes)                                             |                                                                                             | Boot ROM (4KBytes)                                             |

| 0000:C000 <sub>H</sub> -<br>0000:CFFF <sub>H</sub> | CAN                                                       | 0000:С000 <sub>н</sub> -<br>0000:СFFF <sub>н</sub> | CAN                                                            | 0000:С000 <sub>Н</sub> -<br>0000:СFFF <sub>Н</sub>                                          | CAN                                                            |

| 0002:0000 <sub>H</sub>                             | D-RAM (0 wait, 32Kbytes)  ID RAM (32KBytes)  Flash Memory | 0002:0000 <sub>H</sub>                             | D-RAM (0 wait, 32Kbytes)  ID RAM (32KBytes)  External Bus area | 0002:0000 <sub>H</sub> 0003:0000 <sub>H</sub> 0004:0000 <sub>H</sub> 0008:0000 <sub>H</sub> | D-RAM (0 wait, 32Kbytes)  ID RAM (32KBytes)  External Bus area |

| 0010:0000 <sub>H</sub>                             | (512KBytes)                                               | 0010:0000 <sub>H</sub>                             | Flash Memory<br>(512KBytes)                                    | 0010:0000н                                                                                  | External Bus area  External Bus area                           |

| 0014:0000 <sub>н</sub> -<br>0017:FFFF              | Flash Memory area<br>(32KBytes)                           | 0014:0000 <sub>H</sub> -<br>0017:FFFF              | External Bus area Flash Memory area (32KBytes)                 | 0014:0000 <sub>н</sub> -<br>0017:FFFF                                                       | Flash Memory area<br>(32KBytes)                                |

| 0018:0000 <sub>Н</sub>                             |                                                           | 0018:0000н                                         | External Bus area                                              | 0018:0000 <sub>H</sub>                                                                      | External Bus area                                              |

| 0050:0000 <sub>H</sub> -                           |                                                           | 0050:0000 <sub>H</sub>                             | External Bus area                                              | 0050:0000 <sub>H</sub>                                                                      | External Bus area                                              |

|                                                    | Internal                                                  |                                                    | No Access                                                      |                                                                                             | External                                                       |

# 2.2 Registers

#### 2.2.1 Area Select Registers (ASRn)

The Area Select Registers (ASR0-7) specifies the higher order bytes of start address of each chip select area of CSX0-CSX7.

Each chip select area starts with the address set in this register and covers the range set by the four bits ASZ3-0 of the Area Configuration Register (ACR0-7) registers.

| Register | Initial Value     |

|----------|-------------------|

| ASR0     | 0000 <sub>H</sub> |

| ASR1     | XXXX <sub>H</sub> |

| ASR2     | XXXX <sub>H</sub> |

| ASR3     | XXXX <sub>H</sub> |

| ASR4     | XXXX <sub>H</sub> |

| ASR5     | XXXX <sub>H</sub> |

| ASR6     | XXXX <sub>H</sub> |

| ASR7     | XXXX <sub>H</sub> |

The ASR0 register is initialized to  $0000_{\rm H}$  by INIT and RST. ASR1-7 are not initialized by INIT and RST, and are therefore undefined. After starting chip operation, be sure to set the corresponding ASR register before enabling each chip select area with the CSER register.

Lets for example if we set ASR1 to 0x2000 than start address for CS1 will start from H'20000000

# 2.2.2 Area Configuration Registers 0-7 (ACRn)

| Bit No. | Name     | Explanation                                            | Initial Value                                        | Value | Operation                                             |  |

|---------|----------|--------------------------------------------------------|------------------------------------------------------|-------|-------------------------------------------------------|--|

|         |          |                                                        |                                                      | 0000  | 64 KB (00010000H byte, ASR A[31:16] bits are valid)   |  |

|         |          |                                                        |                                                      | 0001  | 128 KB (00020000H byte, ASR A[31:17] bits are valid)  |  |

|         |          |                                                        |                                                      | 0010  | 256 KB (00040000H byte, ASR A[31:18] bits are valid)  |  |

|         |          |                                                        |                                                      | 0011  | 512 KB (00080000H byte, ASR A[31:19] bits are valid)  |  |

|         |          |                                                        |                                                      | 0100  | 1MB (00100000H byte, ASR A[31:20] bits are valid)     |  |

|         |          |                                                        |                                                      | 0101  | 2 MB(00200000H byte, ASR A[31:21] bits are valid)     |  |

|         |          |                                                        |                                                      | 0110  | 4 MB (00400000H byte, ASR A[31:22] bits are valid)    |  |

| 15-12   | ASZ3:ASZ | set area size                                          | 0000 <sub>B</sub> (ACR0)<br>1111 <sub>B</sub> (ACR1- | 0111  | 8 MB (00800000H byte, ASR A[31:23] bits are valid)    |  |

|         | U        |                                                        | 7)                                                   | 1000  | 16 MB (01000000H byte, ASR A[31:24] bits are valid)   |  |

|         |          |                                                        |                                                      | 1001  | 32 MB (02000000H byte, ASR A[31:25] bits are valid)   |  |

|         |          |                                                        |                                                      | 1010  | 64 MB (04000000H byte, ASR A[31:26] bits are valid)   |  |

|         |          |                                                        |                                                      | 1011  | 128 MB (08000000H byte, ASR A[31:27] bits are valid)  |  |

|         |          |                                                        |                                                      | 1100  | Valid) 512 MB (20000000H byte ASR A[31:20] bits are   |  |

|         |          |                                                        |                                                      | 1101  |                                                       |  |

|         |          |                                                        |                                                      | 1110  | 1024 MB (40000000H byte, ASR A[31:30] bits are valid) |  |

|         |          |                                                        |                                                      | 1111  | 2048 MB (80000000H byte, ASR A[31] bit isalid)        |  |

|         |          |                                                        |                                                      | 00    | 8 bits (byte access)                                  |  |

| 11-10   | DBW1:0   | set data bus width                                     | XX <sub>B</sub>                                      | 01    | 16 bits (half word access)                            |  |

|         |          |                                                        |                                                      | 10    | 32 bits (word access)                                 |  |

|         |          |                                                        |                                                      | 11    | Reserved Setting                                      |  |

|         |          |                                                        |                                                      | 00    | 1 (single access)                                     |  |

|         |          | set the maximum                                        |                                                      | 01    | 2 bursts (address boundary: 1 bit)                    |  |

| 9-8     | BST1:0   | set the maximum<br>burst length                        | XX <sub>B</sub>                                      | 10    | 4 bursts (address boundary: 2 bits)                   |  |

|         |          |                                                        |                                                      | 11    | 8 bursts (address boundary: 3 bits)                   |  |

| 7       | SREN     | enable or disable<br>sharing of chip<br>select area by | X <sub>B</sub>                                       | 0     | Disable sharing by BRQ/BGRNTX                         |  |

|     |                   | RQ/BGRNTX                                 |                   | 1                                          | Enable sharing by BRQ/BGRNTX            |  |

|-----|-------------------|-------------------------------------------|-------------------|--------------------------------------------|-----------------------------------------|--|

|     |                   |                                           |                   |                                            |                                         |  |

| 5   | enable or disable |                                           | Disable pre fetch |                                            |                                         |  |

|     | PFEN              | pre fetching of chip<br>select area       | X <sub>B</sub>    | 1                                          | Enable pre fetch                        |  |

|     | WREN              | enable or disable<br>writing to each chip | X <sub>B</sub>    | 0 Disable write                            |                                         |  |

|     |                   | select area                               | 2                 | 1                                          | Enable write                            |  |

| 4   | LEND*             | sets endian                               | X <sub>B</sub>    | 0 Big endian                               |                                         |  |

|     |                   |                                           |                   | 1                                          | Little endian                           |  |

|     |                   |                                           |                   | 00XX                                       | Normal access                           |  |

|     |                   |                                           |                   | 01XX                                       | Address data multiplex access           |  |

|     |                   |                                           |                   | 0XX0 Disable WAIT insertion by the RDY pin |                                         |  |

|     |                   |                                           |                   | 0XX1                                       |                                         |  |

|     |                   |                                           |                   | 0X0X                                       | Use the WRX0-WRX3 pins as write strobes |  |

|     |                   |                                           |                   | 0X1X                                       | Use the WEX pin as the write strobe     |  |

| 3:0 | TYP3:0**          | and the angeles time                      | VVVV              | 1000 Memory type A: SDRAM/FCRAM            |                                         |  |

| 3.0 | 1123:0            | set the access type                       | XXXX <sub>B</sub> | 1001                                       | Memory type B: FCRAM                    |  |

|     |                   |                                           |                   | 1010                                       | Setting disabled                        |  |

|     |                   |                                           |                   | 1011                                       | Setting disabled                        |  |

|     |                   |                                           |                   | 1100                                       | Setting disabled                        |  |

|     |                   |                                           |                   | 1101                                       | Setting disabled                        |  |

|     |                   |                                           |                   | 1100                                       | Setting disabled                        |  |

|     |                   |                                           |                   | 1111                                       | Mask area setting                       |  |

<sup>\*</sup>CS0 supports only the big endian method

\*\*Further information can be found in Appendix

### 2.2.3 Area Wait Register (AWRn)

The area wait registers (AWR0-7: Area Wait Register 0-7) specify various kinds of waits for each chip select area. The function of each bit changes according to the access type setting of the ACRn [TYP3:0] registers. More information about ACRn [TYP3:0] can be found in section 0

AWRn-register settings for ACRn [TYP3:0] is set to "SRAM" access type

| TYP3 | TYP2 | TYP1 | TYP0 | Access Type                                                             |

|------|------|------|------|-------------------------------------------------------------------------|

| 0    | 0    | x    | x    | Normal access (asynchronous SRAM, I/O, and single/page/burst-ROM/FLASH) |

| Bit No. | Name                                                                                                                                                                                                                                                                                                             | Explanation                                                                                                  | Initial Value                        | Value             | Operation                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|---------------------------------------------------------|

|         |                                                                                                                                                                                                                                                                                                                  |                                                                                                              | 0444                                 | 0000 <sub>B</sub> | Auto-wait cycle 0                                       |

| 15-12   | W15:12                                                                                                                                                                                                                                                                                                           | set number of auto-<br>wait cycles to be<br>inserted into the first                                          | 0111 <sub>B</sub> (AWR0)             | 0001 <sub>B</sub> | Auto-wait cycle 1                                       |

| 10 12   | W13.12                                                                                                                                                                                                                                                                                                           | access cycle of each cycle.                                                                                  | XXXX <sub>B</sub><br>(AWR1-7)        |                   |                                                         |

|         |                                                                                                                                                                                                                                                                                                                  |                                                                                                              |                                      | 1111 <sub>B</sub> | Auto-wait cycle 15                                      |

|         |                                                                                                                                                                                                                                                                                                                  |                                                                                                              |                                      | 0000 <sub>B</sub> | Auto-wait cycle 0                                       |

| 11-8    | W11:08                                                                                                                                                                                                                                                                                                           | set the number of<br>auto-wait cycles to be<br>inserted into the in                                          | 1111 <sub>B</sub><br>(AWR0)          | 0001 <sub>B</sub> | Auto-wait cycle 1                                       |

|         |                                                                                                                                                                                                                                                                                                                  | page access cycle<br>during burst access                                                                     | XXXX <sub>B</sub><br>(AWR1-7)        |                   |                                                         |

|         |                                                                                                                                                                                                                                                                                                                  |                                                                                                              | _                                    | 1111 <sub>B</sub> | Auto-wait cycle 15                                      |

|         | The read -> write idle cycle is set to prevent collision of read data and write data on the data bus when a write cycle follows a read cycle.  The read -> write idle cycle is set to prevent (AWR0)  XX <sub>B</sub> (AWR1-7)  11 <sub>B</sub> 01 <sub>B</sub> 1 Read -> write (AWR0)  XX <sub>B</sub> (AWR1-7) |                                                                                                              |                                      | 00 <sub>B</sub>   | 0 Read -> write idle cycles                             |

|         |                                                                                                                                                                                                                                                                                                                  | cycle is set to prevent collision of read data                                                               |                                      | 01 <sub>B</sub>   | 1 Read -> write idle cycles                             |

| 7:6     |                                                                                                                                                                                                                                                                                                                  | 2 Read -> write idle cycles                                                                                  |                                      |                   |                                                         |

|         |                                                                                                                                                                                                                                                                                                                  | read cycle.                                                                                                  |                                      | 11 <sub>B</sub>   | 3 Read -> write idle cycles                             |

|         |                                                                                                                                                                                                                                                                                                                  |                                                                                                              |                                      | 00 <sub>B</sub>   | 0 Write recovery cycles                                 |

| 5:4     | W05:04                                                                                                                                                                                                                                                                                                           | The write recovery cycle is set if a device that limits the access                                           | 11 <sub>B</sub><br>(AWR0)            | 01 <sub>B</sub>   | 1 Write recovery cycles                                 |

| 5.4     | W03.04                                                                                                                                                                                                                                                                                                           | period after write access is to be controlled                                                                | XX <sub>B</sub><br>(AWR1-7)          | 10 <sub>B</sub>   | 2 Write recovery cycles                                 |

|         |                                                                                                                                                                                                                                                                                                                  | Controlled                                                                                                   |                                      | 11 <sub>B</sub>   | 3 Write recovery cycles                                 |

| 3       | W03                                                                                                                                                                                                                                                                                                              | The WRX0-WRX3, WRXn output time setting selects whether to use write strobe output as an asynchronous strobe | 1 <sub>B</sub> (AWR0) X <sub>B</sub> | 0                 | MCLK synchronous write enable output (valid from ASX=L) |

|         |                                                                                                                                                                                                                                                                                                                  | or synchronous write enable.                                                                                 | (AWR1-7)                             | 1                 | Asynchronous write strobe output (normal operation)     |

| 2 | W02 | The address -> CSXn delay setting is made when a certain type of setup is required for the address when CSXn falls or CSXn edges are needed for successive accesses to the same chip select area. | O <sub>B</sub> (AWR0) X <sub>B</sub> (AWR1-7) | 0 | Assertion of CSX0-CSX7 starts at the same timing that ASX is asserted                                                                                    |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     |                                                                                                                                                                                                   |                                               | 1 | Assertion of CSX0-CSX7 starts when the external clock memory MCLK output rises                                                                           |

| 1 | W01 | The CSXn -> RDX/WRXn setup extension cycle is set to extend the period before the read/write strobe is asserted after CSXn is asserted.                                                           | 1 <sub>B</sub> (AWR0) X <sub>B</sub> (AWR1-7) | 0 | RDX/WRX0-WRX3/WRXn are output at the earliest when external clock MCLK output rises just after CSX is asserted                                           |

|   |     |                                                                                                                                                                                                   |                                               | 1 | RDX/WRX0-WRX3/WRXn are always output 1 cycle or more later                                                                                               |

| 0 | W00 | The RDX/WRXn -> CSXn hold extension cycle is set to extend the period before negating CSXn after the read/write strobe is negated.                                                                | 1 <sub>B</sub> (AWR0) X <sub>B</sub> (AWR1-7) | 0 | CSX0-CSX7 are negated after the hold delay after it starts on the rising edge of external memory clock MCLK output after RDX/WRX0-WRX3/WRXn are negated. |

|   |     |                                                                                                                                                                                                   |                                               | 1 | CSX0-CSX7 are negated one cycle later                                                                                                                    |

AWRn-register settings for ACRn [TYP3:0] is set to "SDRAM" access type

| TYP3 | TYP2 | TYP1 | TYP0 | Access Type                                                |

|------|------|------|------|------------------------------------------------------------|

| 1    | 0    | 0    | 0    | Memory type A: SDRAM/FCRAM (Auto - precharge is not used.) |

| Bit No. | Name         | Explanation                                                                                    | Initial Value                                            | Value            | Operation             |

|---------|--------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|-----------------------|

| 15      | W15          | Reserved                                                                                       |                                                          |                  |                       |

|         |              |                                                                                                | 111 <sub>B</sub>                                         | 000 <sub>B</sub> | 1 RAS-CAS delay cycle |

| 4440    | T-11 4 . 1 O | RAS - CAS delay                                                                                | (AWR0)                                                   | 001 <sub>B</sub> | 2 RAS-CAS delay cycle |

| 14-12   | W14:12       | Cycle                                                                                          | XXX <sub>B</sub>                                         |                  |                       |

|         |              |                                                                                                | (AWR1-7)                                                 | 111 <sub>B</sub> | 8 RAS-CAS delay cycle |

| 11      | W11          | Reserved                                                                                       |                                                          |                  |                       |

|         |              |                                                                                                | 111 <sub>B</sub>                                         | 000 <sub>B</sub> | 1 cycles              |

| 10:8    | W10:08       | Set CAS latency.                                                                               | (AWR0)                                                   | 001 <sub>B</sub> | 2 cycles              |

| 10.6    | W10.00       | Set CAS latericy.                                                                              | XXX <sub>B</sub> (AWR1-7)                                |                  |                       |

|         |              |                                                                                                | (AVVX1-7)                                                | 111 <sub>B</sub> | 8 cycles              |

|         | W07:06       | Set minimum number<br>of cycles from the last<br>read data input cycle<br>to the write command |                                                          | 00 <sub>B</sub>  | 1 cycles              |

| 7.0     |              |                                                                                                | 11 <sub>B</sub><br>(AWR0)<br>XX <sub>B</sub><br>(AWR1-7) | 01 <sub>B</sub>  | 2 cycles              |

| 7-6     |              |                                                                                                |                                                          | 10 <sub>B</sub>  | 3 cycles              |

|         |              |                                                                                                |                                                          | 11 <sub>B</sub>  | 4 cycles              |

|         | W05:04       | Set minimum number of cycles from the last write data output to the next read command          | 11 <sub>B</sub> (AWR0) XX <sub>B</sub> (AWR1-7)          | 00 <sub>B</sub>  | Prohibited            |

|         |              |                                                                                                |                                                          | 01 <sub>B</sub>  | 2 cycles              |

| 5:4     |              |                                                                                                |                                                          | 10 <sub>B</sub>  | 3 cycles              |

|         |              |                                                                                                |                                                          | 11 <sub>B</sub>  | 4 cycles              |

|         |              |                                                                                                | 01 <sub>B</sub>                                          | 00 <sub>B</sub>  | 1 cycles              |

| 3:2     | W03:02       | Set minimum number of cycles for RAS                                                           | (AWR0)                                                   | 01 <sub>B</sub>  | 2 cycles              |

| 3.2     | WUJ.UZ       | active time                                                                                    | XX <sub>B</sub>                                          | 10 <sub>B</sub>  | 3 cycles              |

|         |              |                                                                                                | (AWR1-7)                                                 | 11 <sub>B</sub>  | 4 cycles              |

|         |              |                                                                                                | 11 <sub>B</sub>                                          | 00 <sub>B</sub>  | 1 cycles              |

| 1:0     | W01:00       | Set RAS pre charge                                                                             | (AWR0)                                                   | 01 <sub>B</sub>  | 2 cycles              |

| 1.0     | WOI.00       | cycles                                                                                         | XX <sub>B</sub>                                          | 10 <sub>B</sub>  | 3 cycles              |

|         |              |                                                                                                | (AWR1-7)                                                 | 11 <sub>B</sub>  | 4 cycles              |

# 2.2.4 Memory Setting Register (MCRA)

The register serves as the area for making various settings for SDRAM/FCRAM connected to the chip select area for which the access type (TYP3 to TYP0 bits) in the ACR6 and ACR7 registers has been set as  $1000_B$

| Bit No. | Name                                                | Explanation                           | Initial<br>Value | Value            | Operation                                                |

|---------|-----------------------------------------------------|---------------------------------------|------------------|------------------|----------------------------------------------------------|

| 31      |                                                     | Reserved                              |                  |                  |                                                          |

|         |                                                     |                                       |                  | 000 <sub>B</sub> | 8-bit column address:A0 to A7(256 memory words)          |

|         |                                                     |                                       | ,                | 001 <sub>B</sub> | 9-bit column address:A0 to A8(512 memory words)          |

| 30-28   | PSZ2:0                                              | sets page size of SDRAM               | XXX <sub>B</sub> | 010 <sub>B</sub> | 10-bit column address:A0 to A9(1024 memory words)        |

|         |                                                     |                                       |                  | 011 <sub>B</sub> | 11-bit column address:A0 to A9,<br>A11(2048memory words) |

|         |                                                     |                                       |                  | 1XX <sub>B</sub> | Prohibited                                               |

| 27      | WBST                                                | Select t burst -<br>write or a single | X <sub>B</sub>   | 0                | Single write                                             |

|         |                                                     | write access                          |                  | 1                | Burst write                                              |

| 26      | Select number of BANK SDRAM banks to X <sub>R</sub> | X <sub>B</sub>                        | 0                | 2 banks          |                                                          |

|         |                                                     | be connected                          |                  | 1                | 4 banks                                                  |

|         |                                                     |                                       |                  | 00 <sub>B</sub>  | 1 banks                                                  |

| 25-24   | ABS1:0                                              | Select maximum number of banks to     | XX <sub>B</sub>  | 01 <sub>B</sub>  | 2 banks                                                  |

| 20-24   | ADSI:U                                              | be made active simultaneously         |                  | 10 <sub>B</sub>  | 3 banks                                                  |

|         |                                                     |                                       |                  | 11 <sub>B</sub>  | 4 banks                                                  |

# 2.2.5 Memory Setting Register (MCRB)

The register serves as the area for making various settings for FCRAM connected to the chip select area for which the access type (TYP3 to TYP0 bits) in the ACR6 and ACR7 registers has been set as  $1001_B$

| Bit No. | Name   | Explanation                                     | Initial<br>Value | Value            | Operation                                                |

|---------|--------|-------------------------------------------------|------------------|------------------|----------------------------------------------------------|

| 23      |        | Reserved                                        |                  |                  |                                                          |

|         |        |                                                 |                  | 000 <sub>B</sub> | 8-bit column address:A0 to A7(256 memory words)          |

|         |        |                                                 |                  | 001 <sub>B</sub> | 9-bit column address:A0 to A8(512 memory words)          |

| 22-20   | PSZ2:0 | sets page size of SDRAM                         | XXX <sub>B</sub> | 010 <sub>B</sub> | 10-bit column address:A0 to A9(1024 memory words)        |

|         |        |                                                 |                  | 011 <sub>B</sub> | 11-bit column address:A0 to A9,<br>A11(2048memory words) |

|         |        |                                                 |                  | 1XX <sub>B</sub> | Prohibited                                               |

| 19      | WBST*  | Select t burst - write or a single write access | X <sub>B</sub>   | 0                | Single write                                             |

|         |        |                                                 |                  | 1                | Burst write                                              |

| 18      | BANK   | Select number of SDRAM banks to                 | X <sub>B</sub>   | 0                | 2 banks                                                  |

|         |        | be connected                                    |                  | 1                | 4 banks                                                  |

|         |        |                                                 |                  | 00 <sub>B</sub>  | 1 banks                                                  |

| 17-16   | ABS1:0 | Select maximum number of banks to               | XX <sub>B</sub>  | 01 <sub>B</sub>  | 2 banks                                                  |

| 17-10   | ADDI.U | be made active simultaneously                   |                  | 10 <sub>B</sub>  | 3 banks                                                  |

|         |        |                                                 |                  | 11в              | 4 banks                                                  |

<sup>\*</sup>FCRAM supports neither burst read nor single write mode

# 2.2.6 I/O Wait Registers for DMAC (IOWRn)

The I/O wait registers for DMAC (IOWR0-3: I/O Wait Register for DMAC 0-3) set various kinds of waits during DMA fly-by access.

| Bit No.          | Name           | Explanation                                                                                                                | Initial<br>Value | Value | Operation                                                            |

|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------|------------------|-------|----------------------------------------------------------------------|

| 31,23,1          | RYEn           | set wait control,<br>using RDY, of<br>channels 0-3                                                                         | XB               | 0     | Disable RDY input for I/O access                                     |

| 5,7              |                | during DMAC fly-by access.                                                                                                 |                  | 1     | Enable RDY input for I/O access                                      |

| 30,22,1          | 30,22,1<br>4,6 | control the hold<br>cycle of the read<br>strobe signal on the<br>transfer source<br>access side during<br>DMA flyby access | ХВ               | 0     | Do not insert a hold extension cycle.                                |

| 4,6              |                |                                                                                                                            |                  | 1     | Insert a hold extension cycle to extend the read cycle by one cycle. |

|                  |                |                                                                                                                            |                  | 00    | 0 cycle                                                              |

| 29-28,<br>21-20, | WRn1:0         | select burst - write                                                                                                       | XXB              | 01    | 1 cycle                                                              |

| 13-12,<br>5-4    | WKIII.U        | or a single write access                                                                                                   | AAB              | 10    | 2 cycle                                                              |

| 0.               |                |                                                                                                                            |                  | 11    | 3 cycle                                                              |

|                  |                |                                                                                                                            |                  | 0000  | 0 cycle                                                              |

| 27-24,<br>19-16, | IVM/= Q.4      | set number of auto-<br>wait cycles for I/O                                                                                 | VVVVD            | 0001  | 1 cycle                                                              |

| 11-08,<br>03-00  | IWn3:1         | access during DMA fly-by access                                                                                            | XXXXB            |       |                                                                      |

|                  |                |                                                                                                                            |                  | 1111  | 15 cycle                                                             |

# 2.2.7 Chip Select Enable Register (CSER)

The chip select enable register (CSER: Chip Select Enable register) enables and disables each chip select area.

| Bit No. | Name  | Explanation                       | Initial<br>Value | Value | Operation |

|---------|-------|-----------------------------------|------------------|-------|-----------|

| 31      | CSE7  |                                   | 0                | 0     | Disable   |

| 31      | CSE / |                                   | U                | 1     | Enable    |

| 30      | CSE6  |                                   | 0                | 0     | Disable   |

| 30      | CSEO  |                                   | U                | 1     | Enable    |

| 29      | CSE5  |                                   | 0                | 0     | Disable   |

| 29      | CSES  |                                   | U                | 1     | Enable    |

| 28      | CSE4  |                                   | 0                | 0     | Disable   |

| 20      | CSE4  | chip select enable bits for CSX0- | U                | 1     | Enable    |

| 27      | CSE3  | CSX7                              | 0                | 0     | Disable   |

| 21      | CSES  |                                   | U                | 1     | Enable    |

| 26      | CSE2  |                                   | 0                | 0     | Disable   |

| 20      | CSEZ  |                                   | 0                | 1     | Enable    |

| 25      | CSE1  |                                   | 0                | 0     | Disable   |

| 25      | CSEI  |                                   | U                | 1     | Enable    |

| 24      | CSEO  |                                   | 1                | 0     | Disable   |

| 24      | CSE0  |                                   |                  | 1     | Enable    |

# 2.2.8 Cache Enable Register (CHER)

The cache enable register (CHER: CacHe Enable Register) controls the transfer of data read from each chip select area.

| Bit No. | Name | Explanation                                                                             | Initial Value   | Value | Operation                                                                       |                                                                                 |

|---------|------|-----------------------------------------------------------------------------------------|-----------------|-------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 22      | CHE7 |                                                                                         | 4               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 23      | CHE7 |                                                                                         | 1               | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 22      | CHE6 |                                                                                         | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 22      | CHEO |                                                                                         | 1               | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 21      | CHE5 |                                                                                         | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 21      | CHES |                                                                                         |                 | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 20      |      | enable or disable<br>each chip select<br>area for transfers<br>to the built-in<br>cache | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 20      | CHE4 |                                                                                         |                 | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 19      | CHE3 |                                                                                         | to the built-in |       | 0                                                                               | Not a cache area (data read from the applicable area is not saved in the cache) |

| 19      | CHES |                                                                                         | 1               | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 40      | CHEO |                                                                                         | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 18      | CHE2 |                                                                                         |                 | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 17      | CHE1 |                                                                                         | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

|         |      |                                                                                         |                 | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

| 16      | CHEO |                                                                                         | 1               | 0     | Not a cache area (data read from the applicable area is not saved in the cache) |                                                                                 |

| 16      | CHE0 |                                                                                         |                 | 1     | Cache area (data read from the applicable area is saved in the cache)           |                                                                                 |

### 2.2.9 Pin/Timing Control Register (TCR)

The pin/timing control register (TCR: Terminal and Limiting Control Register) controls the functions related to the general external bus interface controller, such as the setting of common pin functions and timing control.

| Bit No. | Name | Explanation                                         | Initial Value | Value | Operation                                               |

|---------|------|-----------------------------------------------------|---------------|-------|---------------------------------------------------------|

| 7       | BREN | enable BRQ pin<br>input and external<br>bus sharing | 0             | 0     | No bus sharing by BRQ/BGRNTX.<br>BRQ input is disabled. |

| /       |      |                                                     |               | 1     | Bus sharing by BRQ/BGRNTX.<br>BRQ input is enabled.     |

| 6       | PSUS | Control temporary stopping of pre-fetch             | 0             | 0     | Enable pre-fetch                                        |

|     |        |                                                                                                                                                                                                                        |                 | 1  | Suspend pre-fetch                                     |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|-------------------------------------------------------|

| 5   | PCLR   | completely clear<br>the pre-fetch                                                                                                                                                                                      | 0               | 0  | Normal state                                          |

|     |        | buffer                                                                                                                                                                                                                 |                 | 1  | Clear the pre-fetch buffer                            |

| 4-2 | CHE4   | Reserved                                                                                                                                                                                                               |                 |    |                                                       |

|     |        | These bits instruct all chip select areas and fly-by I/O channels to reduce only the number of autowait cycles in the auto-access cycle wait settings uniformly while the AWR register settings are retained unchanged | 00 <sub>B</sub> | 00 | Normal wait (AWR0-7 settings)                         |

| 1-0 | RDW1:0 |                                                                                                                                                                                                                        |                 | 01 | 1/2 (1-bit shift to the right) of the AWR0-7 settings |

|     |        |                                                                                                                                                                                                                        |                 | 10 | 1/4 (2-bit shift to the right) of the AWR0-7 settings |

|     |        |                                                                                                                                                                                                                        |                 | 11 | 1/8 (3-bit shift to the right) of the AWR0-7 settings |

### 2.2.10 Refresh Control Register (RCR)

The refresh control register (RCR) is used to make various refresh control settings for SDRAM.

The setting of this register is meaningless as long as SDRAM control is not set for any area, in that case the register value must not be updated from the initial state.

When read by a Read - modify - Write instruction, the SELF, RRLD, and PON bits always return to 0.

| Bit No. | Name          | Explanation                                      | Initial<br>Value    | Value | Operation                                                                                                                                                                |

|---------|---------------|--------------------------------------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | SELF          | Control the self -                               | 0                   | 0     | Auto - refresh or power - down                                                                                                                                           |

| 31      | SETE          | refresh mode                                     | U                   | 1     | Transition to self-refresh mode                                                                                                                                          |

|         |               | Start and reload the                             |                     | 0     | Disable (no operation)                                                                                                                                                   |

| 30      | RRLD          | fresh counter                                    | 0                   | 1     | Execute auto - refreshing once and reload the RFINT value.                                                                                                               |

| 29-24   | RFINT5:0      | Set interval for                                 | XXXXXX <sub>B</sub> |       | The auto - refresh interval can be obtained for distributed refresh mode {(REFINT5 - REFINT0 value) x 32 x (external bus clock cycle)}                                   |

|         | S-24 REINIS.0 | automatic refreshing                             | AAAAAAB             |       | The auto - refresh interval can be obtained for centralized refresh mode {(REFINT5 - REFINT0 value) x 32 x (RFC specified number of times) x (external bus clock cycle)} |

| 00      | 220           | control the operation mode for auto - refreshing |                     | 0     | Distributed refresh (Auto - refresh is activated at intervals.)                                                                                                          |

| 23      | BRST          |                                                  | X                   | 1     | Burst refresh (Auto - refresh is activated repeatedly at one time.)                                                                                                      |

|         | RFC2:0        | Set these bits to the                            | XXX <sub>B</sub>    | 000   | Refresh 256 times                                                                                                                                                        |

|         |               |                                                  |                     | 001   | Refresh 512 times                                                                                                                                                        |

|         |               |                                                  |                     | 010   | Refresh 1024 times                                                                                                                                                       |

| 22-20   |               | number of times a refresh must be                |                     | 011   | Refresh 2048 times                                                                                                                                                       |

| 22-20   | N1 02 • 0     | performed to refresh                             |                     | 100   | Refresh 4096 times                                                                                                                                                       |

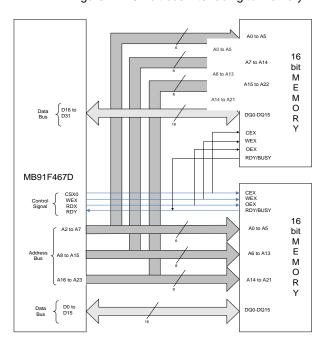

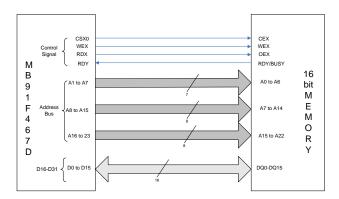

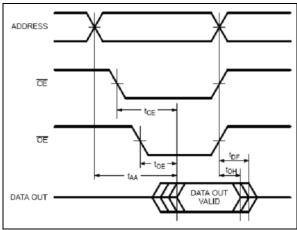

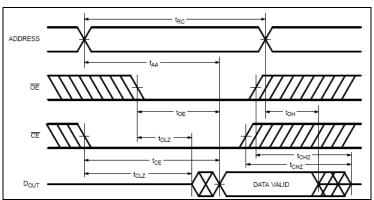

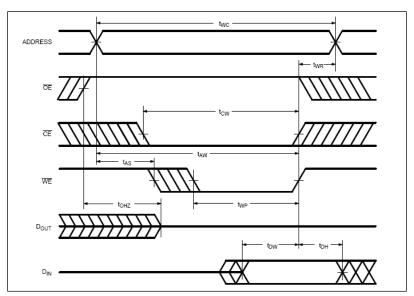

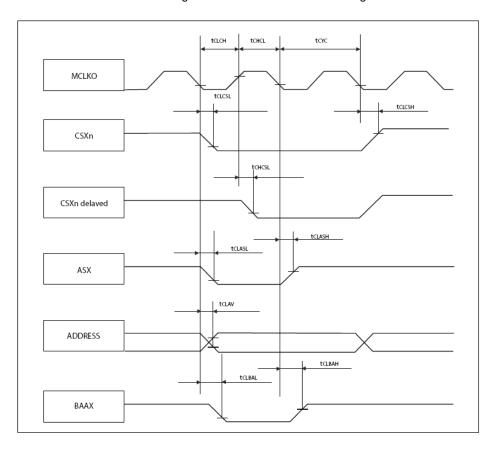

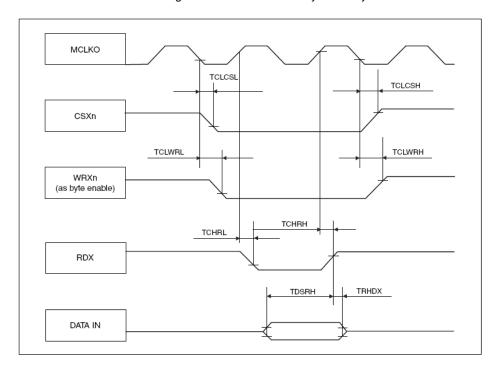

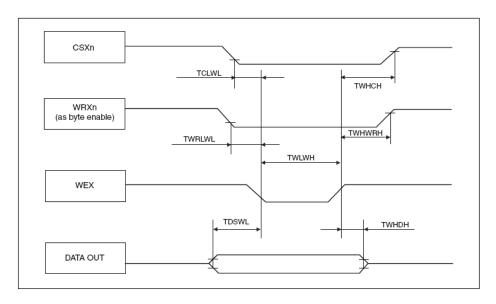

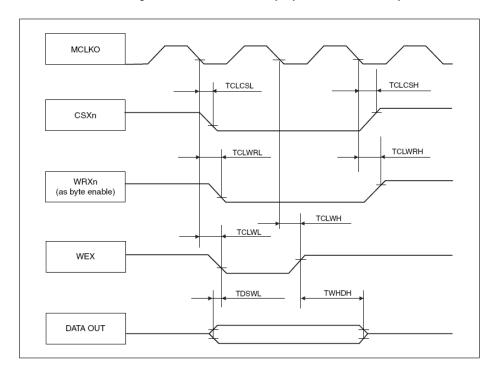

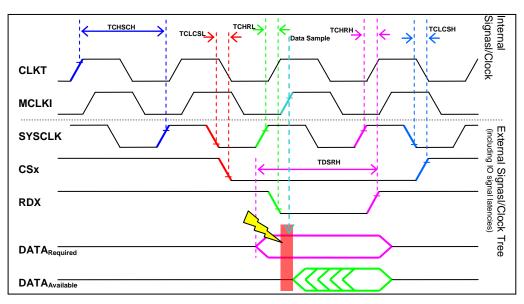

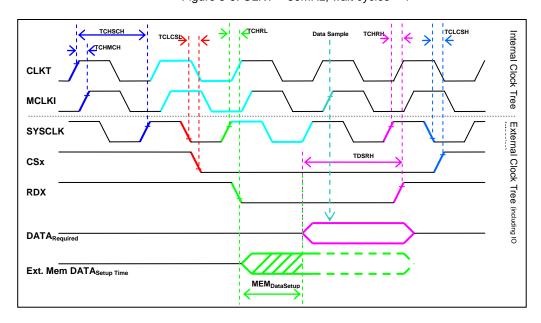

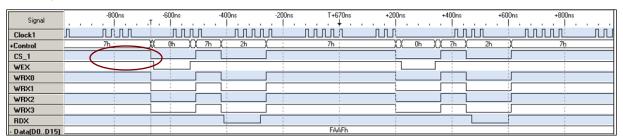

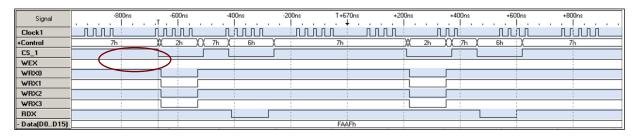

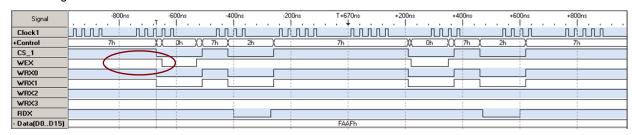

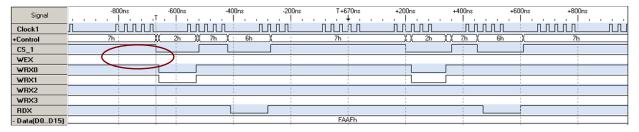

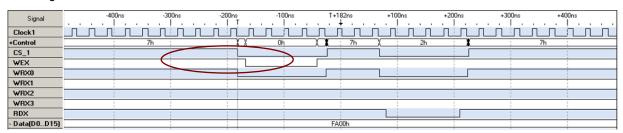

|         |               | all SDRAM                                        |                     | 101   | Refresh 8192 times                                                                                                                                                       |