## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# **EZ-PD™ PMG1 MCU Family**

# EZ-PD™ PMG1-S0 MCU Architecture Technical Reference Manual (TRM)

Document No. 002-31770 Rev. \*A July 30, 2021

Cypress Semiconductor An Infineon Technologies Company 198 Champion Court San Jose, CA 95134-1709

> www.cypress.com www.infineon.com

#### Copyrights

© Cypress Semiconductor Corporation, 2020-2021. This document is the property of Cypress Semiconductor Corporation, an Infineon Technologies company, and its affiliates ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED. WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING. BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any use of a Cypress product as a Critical Component in a High-Risk Device. You shall indemnify and hold Cypress, including its affiliates, and its directors, officers, employees, agents, distributors, and assigns harmless from and against all claims, costs, damages, and expenses, arising out of any claim, including claims for product liability, personal injury or death, or property damage arising from any use of a Cypress product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any High-Risk Device except to the limited extent that (i) Cypress's published data sheet for the product explicitly states Cypress has qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to use the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, Traveo, WICED, and ModusToolbox are trademarks or registered trademarks of Cypress or a subsidiary of Cypress in the United States or in other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# **Content Overview**

| Section A: | Overview                       | 9   |

|------------|--------------------------------|-----|

| 1.         | Introduction                   | 10  |

| 2.         | Getting Started                | 16  |

| 3.         | Document Construction          | 17  |

| Section B: | CPU System                     | 20  |

| 4.         | Cortex-M0 CPU                  | 21  |

| 5.         | Interrupts                     | 26  |

| Section C: | Memory System                  | 35  |

| 6.         | Memory Map                     | 36  |

| Section D: | System-Wide Resources          | 38  |

| 7.         | I/O System                     | 39  |

| 8.         | Clocking System                | 47  |

| 9.         | Power Supply and Modes         | 51  |

| 10.        | Chip Operational Modes         | 53  |

| 11.        | Watchdog Timer                 | 54  |

| 12.        | Reset System                   | 57  |

| 13.        | Device Security                | 59  |

| Section E: | Digital System                 | 60  |

| 14.        | Serial Communications (SCB)    | 61  |

| 15.        | Timer, Counter, and PWM        | 101 |

| Section F: | USB Power Delivery             | 123 |

| 16.        | USB Power Delivery             | 124 |

| Section G: | Program and Debug              | 126 |

| 17.        | Program and Debug Interface    | 127 |

| 18.        | Nonvolatile Memory Programming | 134 |

| Glossary   |                                | 150 |

|            |                                |     |

# Contents

| Section | A: Ov | erview  |                                              | 9  |

|---------|-------|---------|----------------------------------------------|----|

| 1.      | Intro | duction | 1                                            | 10 |

|         | 1.1   | Top Le  | evel Architecture                            | 12 |

|         | 1.2   |         | es                                           |    |

|         | 1.3   |         | nd Memory Subsystems                         |    |

|         |       | 1.3.1   | CPU                                          |    |

|         |       | 1.3.2   | Flash                                        | 13 |

|         |       | 1.3.3   | SROM                                         | 13 |

|         | 1.4   | USB P   | D Subsystem                                  |    |

|         |       | 1.4.1   | USB-PD Physical Layer                        |    |

|         |       | 1.4.2   | ADC                                          | 13 |

|         |       | 1.4.3   | Charger Detection                            | 14 |

|         |       | 1.4.4   | VBUS Undervoltage and Overvoltage Protection | 14 |

|         |       | 1.4.5   | VBUS Discharge FETs                          | 14 |

|         | 1.5   | Systen  | n-Wide Resources                             | 14 |

|         |       | 1.5.1   | Clocking System                              | 14 |

|         |       | 1.5.2   | Power System                                 | 14 |

|         |       | 1.5.3   | GPIO                                         | 14 |

|         | 1.6   | Fixed-I | Function Digital                             | 15 |

|         |       | 1.6.1   | Timer/Counter/PWM Block                      |    |

|         |       | 1.6.2   | Serial Communication Block (SCB)             | 15 |

| 2.      | Getti | ng Star | rted                                         | 16 |

|         | 2.1   | EZ-PD   | ™ PMG1 MCU Resources                         | 16 |

| 3.      | Docu  | ıment C | Construction                                 | 17 |

|         | 3.1   | Major S | Sections                                     | 17 |

|         | 3.2   | ,       | nentation Conventions                        |    |

|         |       | 3.2.1   | Register Conventions                         | 17 |

|         |       | 3.2.2   | Numeric Naming                               | 17 |

|         |       | 3.2.3   | Units of Measure                             |    |

|         |       | 3.2.4   | Acronyms                                     | 18 |

| Section | B: CF | U Syste | em                                           | 20 |

| 4.      | Corte | ex-M0 C | CPU                                          | 21 |

|         | 4.1   | Feature | es                                           | 21 |

|         | 4.2   | Block [ | Diagram                                      | 22 |

|         | 4.3   |         | Works                                        |    |

|         |       | 4.3.1   | Registers                                    |    |

|         |       | 4.3.2   | Operating Modes                              | 24 |

|         |       | 4.3.3   | Instruction Set                              | 24 |

|         |       | 4.3.4   | Systick Timer                                | 25 |

|         |            | 4.3.5 D           | Debug                                             | 25 |

|---------|------------|-------------------|---------------------------------------------------|----|

| 5.      | Interr     | upts              |                                                   | 26 |

|         | 5.1        | Features          |                                                   | 26 |

|         | 5.2        | How It Work       | (S                                                | 26 |

|         | 5.3        |                   | nd Exceptions - Operation                         |    |

|         |            |                   | nterrupt/Exception Handling in EZ-PD™ PMG1-S0 MCU |    |

|         |            |                   | evel and Pulse Interrupts                         |    |

|         |            |                   | xception Vector Table                             |    |

|         | 5.4        | •                 | Sources                                           |    |

|         |            |                   | Reset Exception                                   |    |

|         |            |                   | Ion-Maskable Interrupt (NMI) Exception            |    |

|         |            |                   | lardFault Exception                               |    |

|         |            |                   | Supervisor Call (SVCall) Exception                |    |

|         |            |                   | PendSV Exception                                  |    |

|         |            |                   | SysTick Exception                                 |    |

|         | 5.5        | •                 | urces                                             |    |

|         | 5.6        | •                 | Priority                                          |    |

|         | 5.7        | •                 | sabling Interrupts                                |    |

|         | 5.8        | •                 | States                                            |    |

|         | <b>5</b> 0 |                   | Pending Exceptions                                |    |

|         | 5.9        | •                 | e for Exceptions                                  |    |

|         | 5.10       | •                 | nd Low-Power Modes                                |    |

|         | 5.11       | •                 | Initialization and Configuration                  |    |

|         | 5.12       | •                 | D                                                 |    |

|         | 5.13       |                   | Documents                                         |    |

|         |            | mory Syste        | e <b>m</b>                                        | 35 |

| 6.      |            | ry Map            |                                                   | 36 |

|         | 6.1        |                   |                                                   |    |

|         | 6.2        | How It Work       | (S                                                | 36 |

| Section | D: Sy      | tem-Wide          | Resources                                         | 38 |

| 7.      | I/O Sy     | stem              |                                                   | 39 |

|         | 7.1        | Features          |                                                   | 39 |

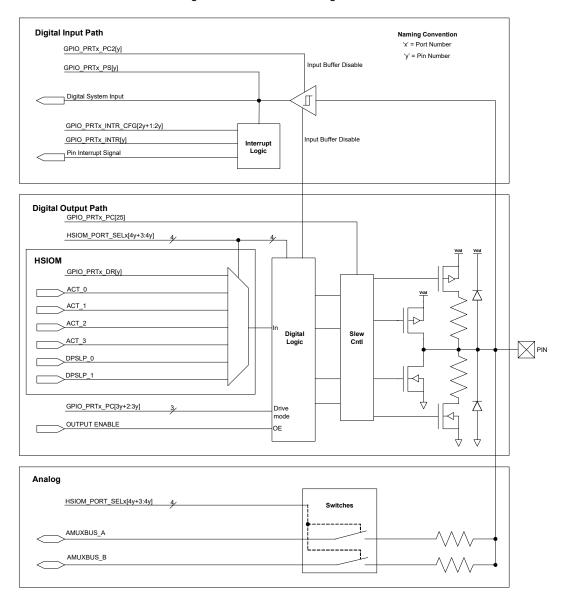

|         | 7.2        | Block Diagra      | am                                                | 40 |

|         | 7.3        | <b>GPIO</b> Drive | Modes                                             | 41 |

|         |            | 7.3.1 H           | ligh-Impedance Analog                             | 42 |

|         |            | 7.3.2 H           | ligh-Impedance Digital                            | 42 |

|         |            |                   | Resistive Pull-Up or Resistive Pull-Down          |    |

|         |            |                   | Open Drain Drives High and Open Drain Drives Low  |    |

|         |            |                   | Strong Drive                                      |    |

|         |            |                   | Resistive Pull-Up and Resistive Pull-Down         |    |

|         | 7.4        |                   | Control                                           |    |

|         | 7.5        |                   | TL Level Control                                  |    |

|         | 7.6        | GPIO-OVT          |                                                   | 43 |

|         | 7.7        | •                 | I/O Matrix                                        |    |

|         | 7.8        |                   | ontrolled GPIO                                    |    |

|         | 7.9        |                   | configuration                                     |    |

|         | 7.10       |                   | Power Up                                          |    |

|         | 7.11       |                   | Low-Power Modes                                   |    |

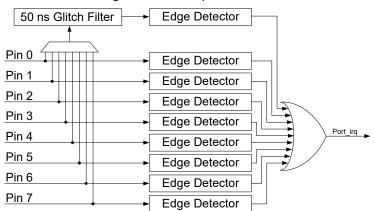

|         | 7.12       | GPIO Interr       | upt                                               | 45 |

|     |       | 7.12.1 Features                              |    |

|-----|-------|----------------------------------------------|----|

|     |       | 7.12.2 Interrupt Controller Block Diagram    |    |

|     | 7.13  | 7.12.3 Function and Configuration            |    |

| _   |       | · ·                                          |    |

| 8.  | Clock | king System                                  | 47 |

|     | 8.1   | Block Diagram                                |    |

|     | 8.2   | Clock Sources                                |    |

|     |       | 8.2.1 Internal Main Oscillator               |    |

|     |       | 8.2.2 Internal Low-speed Oscillator          |    |

|     |       | 8.2.3 External Clock                         |    |

|     | 8.3   | Clock Distribution                           |    |

|     |       | 8.3.1 HFCLK Input Selection                  |    |

|     |       | 8.3.2 HFCLK Predivider Configuration         |    |

|     |       | 8.3.3 SYSCLK Prescaler Configuration         |    |

|     | 8.4   | 8.3.4 Peripheral Clock Divider Configuration |    |

|     | 8.5   | Register List                                |    |

|     | 0.5   | Negislei List                                |    |

| 9.  | Powe  | r Supply and Modes                           | 51 |

|     | 9.1   | Block Diagram                                | 51 |

|     | 9.2   | Power System Requirement Overview            |    |

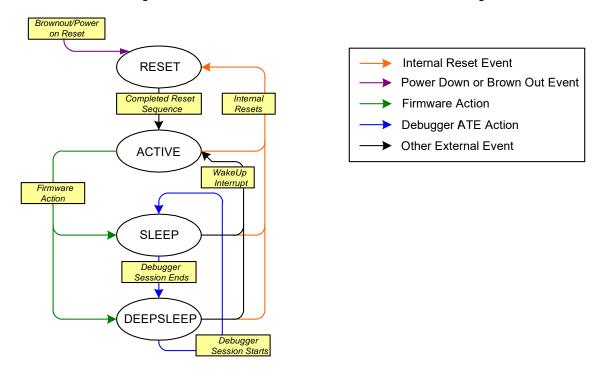

|     | 9.3   | Power Modes                                  | 52 |

|     | 9.4   | Mode Transitions                             | 52 |

| 10. | Chin  | Operational Modes                            | 53 |

|     | 10.1  |                                              |    |

|     | 10.1  |                                              |    |

|     | 10.2  |                                              |    |

|     | 10.4  | •                                            |    |

| 44  |       | ·                                            |    |

| 11. |       | hdog Timer                                   | 54 |

|     | 11.1  |                                              |    |

|     | 11.2  | Block Diagram                                |    |

|     | 11.3  | How It Works                                 |    |

|     |       | 11.3.1 Enabling and Disabling WDT            |    |

|     |       | 11.3.3 WDT Reset Mode                        |    |

|     | 11 4  | Register List                                |    |

| 40  |       | •                                            | 57 |

| 12. |       | t System                                     |    |

|     | 12.1  | Reset Sources                                |    |

|     |       | 12.1.1 Power-off Reset                       |    |

|     |       | 12.1.3 Watchdog Reset                        |    |

|     |       | 12.1.4 Software Initiated Reset              |    |

|     |       | 12.1.5 Protection Fault Reset                |    |

|     | 12.2  | Identifying Reset Sources                    |    |

|     |       | Register List                                |    |

| 12  |       | e Security                                   | 59 |

| 13. |       | •                                            |    |

|     |       | Features How It Works                        |    |

|     | 10.2  |                                              |    |

| Section I | E: Dig | ital Syst | tem                                                 | 60  |

|-----------|--------|-----------|-----------------------------------------------------|-----|

| 14.       | Serial | Commi     | unications (SCB)                                    | 61  |

|           | 14.1   | Features  | 5                                                   | 61  |

|           | 14.2   | Serial Pe | eripheral Interface (SPI)                           | 61  |

|           |        | 14.2.1    | Features                                            | 61  |

|           |        | 14.2.2    | General Description                                 | 62  |

|           |        | 14.2.3    | SPI Modes of Operation                              |     |

|           |        | 14.2.4    | Easy SPI (EZSPI) Protocol                           |     |

|           |        | 14.2.5    | SPI Registers                                       |     |

|           |        | 14.2.6    | SPI Interrupts                                      |     |

|           |        | 14.2.7    | Enabling and Initializing SPI                       |     |

|           |        | 14.2.8    | Internally and Externally Clocked SPI Operations    |     |

|           | 14 3   |           | morrany and Externally closing of Populations       |     |

|           |        | 14.3.1    | Features                                            |     |

|           |        | 14.3.2    | General Description                                 |     |

|           |        | 14.3.3    | UART Modes of Operation                             |     |

|           |        | 14.3.4    | UART Registers                                      |     |

|           |        | 14.3.5    | UART Interrupts                                     |     |

|           |        | 14.3.6    | Enabling and Initializing UART                      |     |

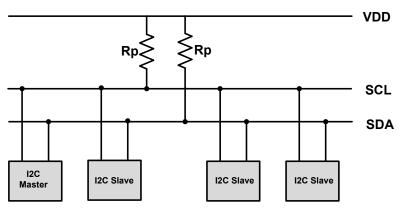

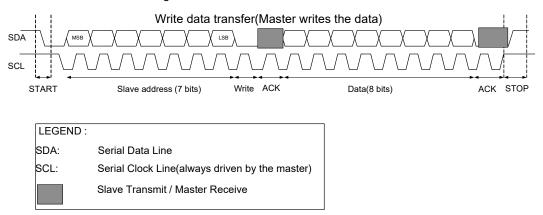

|           | 111    |           | egrated Circuit (I2C)                               |     |

|           | 14.4   | 14.4.1    | Features                                            |     |

|           |        | 14.4.1    | General Description                                 |     |

|           |        | 14.4.2    | Terms and Definitions                               |     |

|           |        | 14.4.4    |                                                     |     |

|           |        |           | I2C Modes of Operation                              |     |

|           |        | 14.4.5    | Easy I2C (EZI2C) Protocol                           |     |

|           |        | 14.4.6    | Memory Array Write                                  |     |

|           |        | 14.4.7    | Memory Array Read                                   |     |

|           |        | 14.4.8    | I2C Registers                                       |     |

|           |        | 14.4.9    | I2C Interrupts                                      |     |

|           |        | 14.4.10   | Enabling and Initializing the I2C                   |     |

|           |        | 14.4.11   | Internal and External Clock Operation in I2C        |     |

|           |        | 14.4.12   | Wake up from Sleep                                  |     |

|           |        | 14.4.13   | Master Mode Transfer Examples                       |     |

|           |        | 14.4.14   | Slave Mode Transfer Examples                        |     |

|           |        | 14.4.15   | EZ Slave Mode Transfer Example                      |     |

|           |        | 14.4.16   | Multi-Master Mode Transfer Example                  | 99  |

| 15.       | Timer  | , Count   | er, and PWM                                         | 101 |

|           | 15.1   | Features  | 3                                                   | 101 |

|           | 15.2   | Block Dia | agram                                               | 102 |

|           |        | 15.2.1    | Enabling and Disabling Counter in TCPWM Block       |     |

|           |        | 15.2.2    | Clocking                                            |     |

|           |        | 15.2.3    | Events Based on Trigger Inputs                      |     |

|           |        | 15.2.4    | Output Signals                                      |     |

|           |        | 15.2.5    | Power Modes                                         |     |

|           | 15.3   |           | of Operation                                        |     |

|           |        | 15.3.1    | Timer Mode                                          |     |

|           |        | 15.3.2    | Capture Mode                                        |     |

|           |        | 15.3.3    | Quadrature Decoder Mode                             |     |

|           |        | 15.3.4    | Pulse Width Modulation Mode                         |     |

|           |        | 15.3.5    | Pulse Width Modulation with Dead Time Mode          |     |

|           |        | 15.3.6    | Pulse Width Modulation Pseudo-Random Mode           |     |

|           |        | 10.0.0    | i also triati i vioquiation i scaqo-i (andom ivioqo |     |

|            | 15.4  | TCPWM Registers                                  | 122 |

|------------|-------|--------------------------------------------------|-----|

| Section F: | : US  | B Power Delivery                                 | 123 |

| 16. L      | JSB   | Power Delivery                                   | 124 |

|            |       | ADC                                              | 124 |

| Section G  | : Pro | ogram and Debug                                  | 126 |

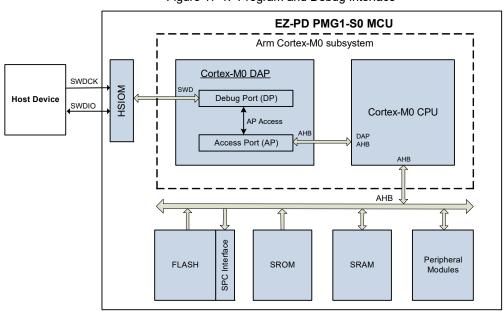

| 17. F      | Progi | ram and Debug Interface                          | 127 |

|            | 17.1  | Features                                         | 127 |

|            |       | Functional Description                           |     |

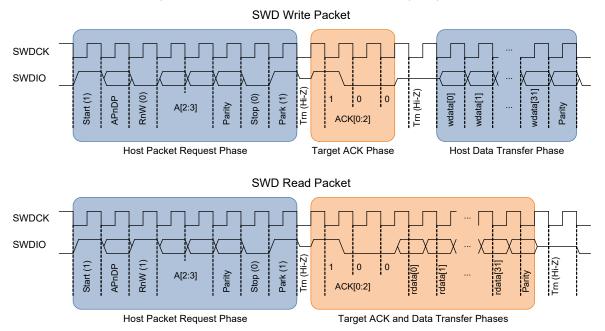

|            | 17.3  | ·                                                |     |

|            |       | 17.3.1 SWD Timing Details                        |     |

|            |       | 17.3.2 ACK Details                               | 129 |

|            |       | 17.3.3 Turnaround (Trn) Period Details           | 130 |

|            | 17.4  | Cortex-M0 Debug and Access Port (DAP)            | 130 |

|            |       | 17.4.1 Debug Port (DP) Registers                 | 130 |

|            |       | 17.4.2 Access Port (AP) Registers                | 130 |

|            | 17.5  |                                                  |     |

|            |       | 17.5.1 SWD Port Acquisition                      | 131 |

|            |       | 17.5.2 SWD Programming Mode Entry                | 132 |

|            |       | 17.5.3 SWD Programming Routines Executions       | 132 |

|            | 17.6  | EZ-PD™ PMG1-S0 MCU SWD Debug Interface           |     |

|            |       | 17.6.1 Debug Control and Configuration Registers |     |

|            |       | 17.6.2 Breakpoint Unit (BPU)                     |     |

|            |       | 17.6.3 Data Watchpoint (DWT)                     |     |

|            |       | 17.6.4 Debugging the EZ-PD™ PMG1-S0 MCU Device   |     |

|            | 17.7  | Registers                                        | 133 |

| 18. N      | Nonv  | olatile Memory Programming                       | 134 |

|            | 18.1  | Features                                         | 134 |

|            | 18.2  | Functional Description                           | 134 |

|            | 18.3  | System Call Implementation                       | 135 |

|            | 18.4  | Blocking and Non-Blocking System Calls           | 135 |

|            |       | 18.4.1 Performing a System Call                  | 135 |

|            | 18.5  | System Calls                                     | 136 |

|            |       | 18.5.1 Silicon ID                                | 136 |

|            |       | 18.5.2 Configure Clock                           | 137 |

|            |       | 18.5.3 Load Flash Bytes                          | 138 |

|            |       | 18.5.4 Write Row                                 | 139 |

|            |       | 18.5.5 Program Row                               | 139 |

|            |       | 18.5.6 Erase All                                 | 140 |

|            |       | 18.5.7 Checksum                                  | 141 |

|            |       | 18.5.8 Write Protection                          |     |

|            |       | 18.5.9 Non-Blocking Write Row                    |     |

|            |       | 18.5.10 Non-Blocking Program Row                 |     |

|            |       | 18.5.11 Resume Non-Blocking                      |     |

|            | 18.6  |                                                  |     |

|            | 18.7  | Non-Blocking System Call Pseudo Code             | 146 |

| Glossary   |       |                                                  | 150 |

# Section A: Overview

EZ-PD™ PMG1-S0 MCU Technical Reference Manual consists of 2 books. This EZ-PD™ PMG1-S0 MCU Architecture Technical Reference Manual is Book 1 of 2. For details on registers, refer to EZ-PD™ PMG1-S0 MCU Registers Technical Reference Manual (Book 2 of 2).

This section encompasses the following chapters:

- Introduction chapter on page 10

- Getting Started chapter on page 16

- Document Construction chapter on page 17

## **Document Revision History**

Table 1-1. Document Revision History

|   | Revision | Issue Date        | Description of Change                              |

|---|----------|-------------------|----------------------------------------------------|

|   | **       | December 15, 2020 | New EZ-PD™ PMG1-S0 MCU TRM.                        |

| ľ | *A       | July 30, 2021     | Updated 18.7 Non-Blocking System Call Pseudo Code. |

## 1. Introduction

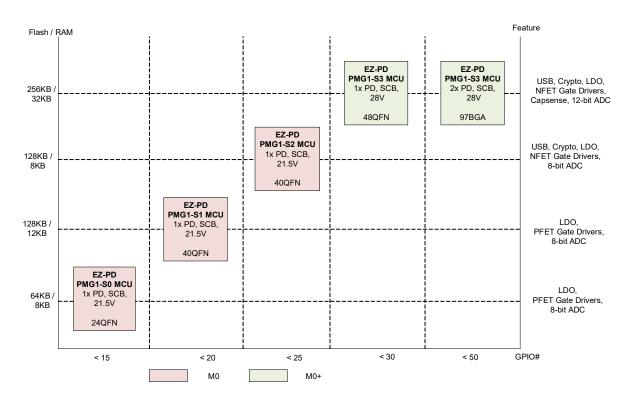

EZ-PD™ Power Delivery Microcontroller Gen1 (PMG1) is a family of high-voltage USB-C power delivery (PD) microcontrollers (MCU). These chips include an Arm® Cortex®-M0/M0+ CPU and USB-C PD controller along with analog and digital peripherals. EZ-PD™ PMG1 MCU is targeted at any embedded system that powers from a high-voltage USB-C PD port and leverages the microcontroller to provide additional control capability. Figure 1-1 shows the EZ-PD™ PMG1 MCU Family segmentation.

Figure 1-1. EZ-PD™ PMG1 MCU Family Segmentation

Table 1-1 shows the comparison of features of different MCUs of the EZ-PD™ PMG1 MCU Family. The rest of the document discusses EZ-PD™ PMG1-S0 MCU in detail.

Table 1-1. EZ-PD™ PMG1 MCU Family Feature Comparison

| Subsystem or Range      | Item                                                                    | EZ-PD™ PMG1-S0<br>MCU                                               | EZ-PD™ PMG1-S1<br>MCU                | EZ-PD™ PMG1-S2<br>MCU                                                                | EZ-PD™ PMG1-S3<br>MCU                                                              |

|-------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                         | Core                                                                    | Arm Cortex-M0                                                       | Arm Cortex-M0                        | Arm Cortex-M0                                                                        | Arm Cortex-M0+                                                                     |

| CPU & Memory            | Max Freq (MHz)                                                          | 48                                                                  | 48                                   | 48                                                                                   | 48                                                                                 |

| Sub-system              | Flash (KB)                                                              | 64                                                                  | 128                                  | 128                                                                                  | 256                                                                                |

|                         | SRAM (KB)                                                               | 8                                                                   | 12                                   | 8                                                                                    | 32                                                                                 |

|                         | Power Delivery Ports                                                    | 1                                                                   | 1                                    | 1                                                                                    | 2                                                                                  |

|                         | Role                                                                    | Sink                                                                | DRP                                  | DRP                                                                                  | DRP                                                                                |

| Power Delivery          | MOSFET Gate Drivers                                                     | 2x PFET                                                             | 2x PFET                              | 2x PFET/NFET                                                                         | 2XNFET                                                                             |

|                         | Fault Protections                                                       | VBUS OVP <sup>1</sup> and UVP <sup>2</sup>                          | VBUS OVP, UVP, and OCP <sup>3</sup>  | VBUS OVP and OCP                                                                     | VBUS OVP, OCP,<br>SCP <sup>4</sup> , and RCP <sup>5</sup>                          |

| USB                     | Integrated Full Speed USB<br>2.0 Device with Billboard<br>Class support | No                                                                  | No                                   | Yes                                                                                  | Yes                                                                                |

| Voltage Range           | Supply (V)                                                              | VDDD (2.7 - 5.5)<br>VBUS (4 - 21.5)                                 | VSYS (2.75 - 5.5)<br>VBUS (4 - 21.5) | VSYS (2.7 - 5.5)<br>VBUS (4 - 21.5)                                                  | VSYS (2.8 - 5.5)<br>VBUS (4 - 28)                                                  |

|                         | IO (V)                                                                  | 1.71 - 5.5                                                          | 1.71 - 5.5                           | 1.71 - 5.5                                                                           | 1.71 - 5.5                                                                         |

|                         | Serial communication blocks (configurable as I <sup>2</sup> C/UART/SPI) | 2                                                                   | 4                                    | 4                                                                                    | 8                                                                                  |

| Digital                 | TCPWM blocks (configurable as timer, counter or pulse width modulator)  | 4                                                                   | 2                                    | 4                                                                                    | 8                                                                                  |

|                         | Hardware Authentication<br>Block (Crypto)                               | No                                                                  | No                                   | Yes (AES <sup>6</sup> , SHA <sup>7</sup> ,<br>PRNG <sup>8</sup> , CRC <sup>9</sup> ) | Yes (AES, SHA,<br>TRNG <sup>10</sup> , Vector Unit)                                |

| Analog                  | ADC                                                                     | 2x 8-bit SAR                                                        | 1x 8-bit SAR                         | 2x 8-bit SAR                                                                         | 2x 8-bit SAR<br>1x 12-bit SAR                                                      |

|                         | On-chip Temperature Sensor                                              | Yes                                                                 | Yes                                  | Yes                                                                                  | Yes                                                                                |

| DMA                     | DMA                                                                     | No                                                                  | No                                   | No                                                                                   | Yes                                                                                |

| GPIO                    | Max # of I/O                                                            | 12 (10+2 OVT <sup>11</sup> )                                        | 17 (15+2 OVT)                        | 20 (18+2 OVT)                                                                        | 50                                                                                 |

| Charging Stan-<br>dards | Charging Standards                                                      | BC 1.2, Apple<br>Charging (AC)                                      | BC 1.2, AC                           | BC 1.2, AC                                                                           | BC 1.2, AC, AFC and<br>Quick Charge 3.0                                            |

| ESD Protection          | ESD Protection                                                          | Yes (Up to ± 8-kV contact discharge and up to ±15-kV air discharge) | Yes (Human Body<br>Model Only)       | Yes (Up to ± 8-kV contact discharge and up to ±15-kV air discharge)                  | Yes (Human Body<br>model and Charged<br>Device Model)                              |

| Packages                | Package Options                                                         | 24 QFN (4x4 mm,<br>0.5 mm pitch)                                    | 40 QFN (6×6 mm,<br>0.5 mm pitch)     | 40 QFN(6×6 mm,<br>0.5 mm pitch)                                                      | 48QFN (6x6 mm, 0.5<br>mm pitch)<br>97BGA (6x6 mm, 0.5<br>mm, and 0.65 mm<br>pitch) |

<sup>1.</sup> Overvoltage Protection

Undervoltage Protection

Overcurrent Protection

Short Circuit Protection

Short Circuit Protection

Reverse Current Protection

Advanced Encryption Standard

Secure Hash Algorithm

Pseudo Random Number Generation

Cyclic Redundancy Check

True Random Number Generation

Over Voltage Tolerant

EZ-PD™ PMG1-S0 MCU is the first member of the EZ-PD™ PMG1 MCU Family. It has a 32-bit Arm® Cortex®-M0 processor, 64-KB flash, a complete Type-C USB-PD transceiver, a pull-down termination resistor R<sub>D</sub> to support Sink on the Type-C port, and system-level ESD protection in a 24-pin QFN package.

EZ-PD™ PMG1-S0 MCU devices have these characteristics:

- High-performance, 32-bit 48 MHz Cortex-M0 CPU core

- Configurable timer/counter/PWM blocks

- Configurable serial communication blocks to support I<sup>2</sup>C, SPI, UART

- Integrated USB-PD BMC transceiver

- One charger detection block connected to a pair of DP/DM pins

- Termination resistor R<sub>D</sub>

- VBUS discharge FETs to reduce voltage during negative voltage transitions

This document describes each function block of the EZ-PD™ PMG1-S0 MCU device in detail. This information will help designers to create system-level designs.

## 1.1 Top Level Architecture

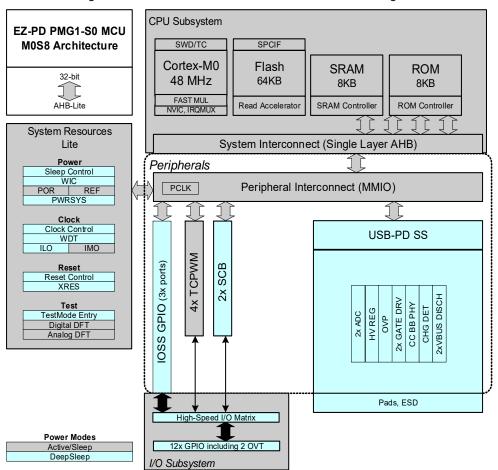

Figure 1-2 shows the major components of the EZ-PD™ PMG1-S0 MCU architecture.

Figure 1-2. EZ-PD™ PMG1-S0 MCU Functional Block Diagram

#### 1.2 Features

The main features of the EZ-PD™ PMG1-S0 MCU device are as follows:

- 32-bit Cortex-M0 CPU at 48 MHz

- 64 KB flash and 8 KB SRAM

- Integrated USB-PD BMC transceiver

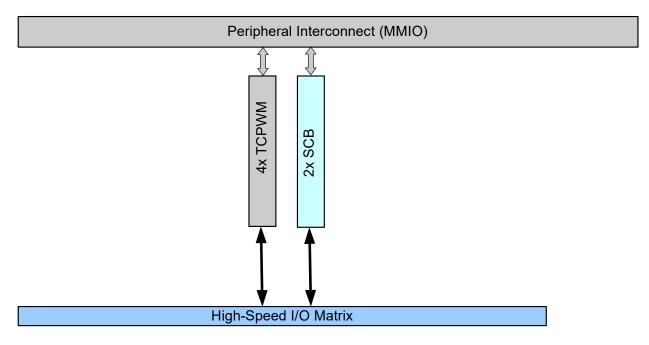

- Up to four dedicated Timers and Counters block to meet response times required by the USB-PD protocol

- Two independent run-time reconfigurable Serial Communication Blocks (SCB) with re-configurable I<sup>2</sup>C, SPI or UART functionality.

- Supports one USB Type-C port

- Integrated oscillator eliminating the need of external clock

- Programming and debugging through serial wire debug (SWD)

## 1.3 CPU and Memory Subsystems

#### 1.3.1 CPU

The Cortex-M0 CPU in EZ-PD™ PMG1-S0 MCU is part of the 32-bit MCU subsystem, which is optimized for low-power operation with extensive clock gating.

The CPU also includes a serial wire debug (SWD) interface, which is a two-wire form of JTAG. The debug configuration used for EZ-PD EZ-PD™ PMG1-S0 MCU has four break-point (address) comparators and two watchpoint (data) comparators.

#### 1.3.2 Flash

The EZ-PD EZ-PD™ PMG1-S0 MCU device has a flash module with one bank of 64 KB flash, a flash accelerator, tightly coupled to the CPU to improve average access times from the flash block.

#### 1.3.3 SROM

A supervisory ROM that contains boot and configuration routines is provided.

## 1.4 USB PD Subsystem

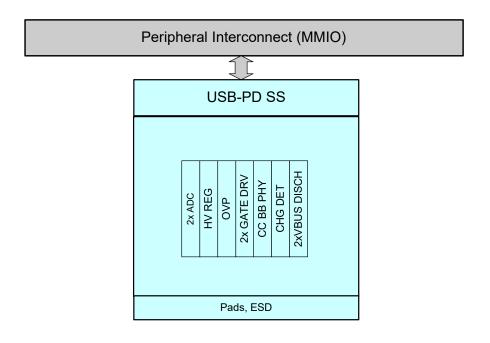

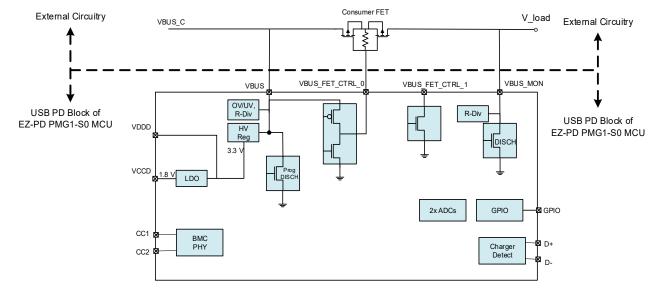

The USB-PD subsystem provides the interface to the Type-C USB port. This subsystem comprises of a high-voltage regulator, OVP, and supply switch blocks. This subsystem also includes all ESD required and supported on the Type-C port.

#### 1.4.1 USB-PD Physical Layer

The USB-PD Physical Layer consists of a transmitter and receiver that communicate BMC encoded data over the CC channel based on the PD 3.0 standard. All communication is half-duplex. The Physical Layer or PHY practices collision avoidance to minimize communication errors on the channel.

The USB-PD block includes the  $R_D$  termination resistor and switch as required by the USB-PD specification. The termination resistor is required to implement connection detection, plug orientation detection, and for establishing the sink power role. A dead-battery  $R_D$  termination enables identification as a sink while the EZ-PD<sup>TM</sup> PMG1-S0 MCU device is not powered.

#### 1.4.2 ADC

The ADC is a low-footprint 8-bit KS/second SAR ADC that is available for general purpose A-D conversion applications in the chip. This ADC can be accessed from all GPIOs and the DP/DM pins through an on-chip analog mux. EZ-PD™ PMG1-S0 MCU contains two instances of the ADC.

#### 1.4.3 Charger Detection

The charger detection block connected to the pair of DP/DM pins allow EZ-PD™ PMG1-S0 MCU to detect conventional battery chargers conforming to BC 1.2 and Apple Charging standard.

#### 1.4.4 VBUS Undervoltage and Overvoltage Protection

The EZ-PD™ PMG1-S0 MCU chip has an integrated hardware block for VBUS overvoltage protection (OVP)/undervoltage protection (UVP) with configurable thresholds and response times on the Type C port.

#### 1.4.4.1 PFET Gate Drivers on VBUS Path

EZ-PD™ PMG1-S0 MCU has integrated 2x PFET gate drivers to drive external PFETs on the VBUS consumer paths. The VBUS\_FET\_CTRL\_0 gate driver has an active pull-up, and thus can drive high, low or High-Z. The VBUS\_FET\_CTRL\_1 gate driver can drive only low or high-Z, thus requiring an external pull-up. These pins are VBUS voltage-tolerant.

#### 1.4.5 VBUS Discharge FETs

EZ-PD™ PMG1-S0 MCU also has integrated 2x VBUS discharge FETs used to reduce the VBUS voltage during negative voltage transitions. One of the VBUS discharge FETs is available on the VBUS power pin.

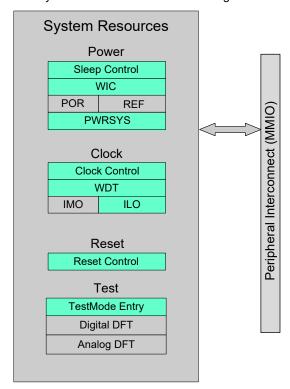

## 1.5 System-Wide Resources

#### 1.5.1 Clocking System

The clock system for the EZ-PD™ PMG1-S0 MCU controller consists of the internal main oscillator (IMO) and an internal low-speed oscillator (ILO) as internal clocks and has provision for an external clock.

The IMO is the primary source of internal clocking in EZ-PD™ PMG1-S0 MCU. It is trimmed during production to achieve the desired accuracy of ±2%. Trim values are stored in supervisory rows in the Flash memory. Additional trim settings from Flash can be used to compensate for changes. IMO Default frequency for EZ-PD™ PMG1-S0 MCU is 24 MHz ±2%.

The ILO is a 32-kHz low-power, less accurate oscillator and is used to generate clocks for peripheral operation in Deep-Sleep power mode.

#### 1.5.2 Power System

EZ-PD<sup>TM</sup> PMG1-S0 MCU can operate from two possible external supply sources: VBUS (3.0 V - 21.5 V) or VDDD (2.7 - 5.5 V). The VBUS supply is regulated inside the chip with an LDO. The switched supply, VDDD, is either used directly inside some analog blocks or further regulated down to VCCD, which powers majority of the core using the regulators. EZ-PD<sup>TM</sup> PMG1-S0 MCU has three different power modes: Active, Sleep, and Deep Sleep. Transitions between these power modes are managed by the power system. A separate power domain, VDDIO, is provided for the GPIOs. The VDDD and VCCD pins, both outputs of regulators, are brought out for connecting a 1- $\mu$ F capacitor for the regulator stability only. These pins are not supported as power supplies.

#### 1.5.3 GPIO

EZ-PD EZ-PD<sup>TM</sup> PMG1-S0 MCU has up to 12 GPIOs of which, some of them can be re-purposed to support functions of SCB ( $I^2$ C, UART, SPI). The  $I^2$ C pins from SCB 0 are overvoltage-tolerant.

The GPIO block implements the following:

- Seven drive strength modes:

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- □ Strong pull-up with strong pull-down

- □ Weak pull-up with weak pull-down

- Input threshold select (CMOS or LVTTL)

- Individual control of input and output buffer enabling/disabling in addition to the drive strength modes

- Hold mode for latching previous state (used for retaining I/O state in Deep Sleep mode)

- Selectable slew rates for dV/dt related noise control to improve EMI

During power-on and reset, the I/O pins are forced to the disable state so as not to crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a high-speed I/O matrix is used to multiplex between various signals that may connect to an I/O pin.

## 1.6 Fixed-Function Digital

#### 1.6.1 Timer/Counter/PWM Block

The TCPWM block of EZ-PD™ PMG1-S0 MCU supports four timers. These timers are available for internal timer use by firmware or for providing PWM based functions on the GPIOs.

#### 1.6.2 Serial Communication Block (SCB)

The EZ-PD™ PMG1-S0 MCU has two SCBs, which can each implement a serial communication interface as I<sup>2</sup>C, universal asynchronous receiver/transmitter (UART), or serial peripheral interface (SPI).

The features of SCB includes:

- Standard I<sup>2</sup>C multi-master and slave function

- Standard SPI master and slave function with Motorola, TI, and National (MicroWire) mode

- Standard UART transmitter and receiver function

## 2. Getting Started

#### 2.1 EZ-PD™ PMG1 MCU Resources

This chapter provides the complete list of EZ-PD™ PMG1 MCU resources that will help you get started with the device and design your applications with them. If you are new to EZ-PD™ PMG1 MCU, there is a wealth of data at www.cypress.com to help you to select the right EZ-PD™ PMG1 MCU device and quickly and effectively integrate it into your design.

The following is an abbreviated list of EZ-PD™ PMG1 MCU resources:

- Overview: EZ-PD™ PMG1 MCU webpage

- Datasheets describe and provide electrical specifications for each device family.

- Application Notes and Code Examples cover a broad range of topics, from basic to advanced level. Many of the application notes include code examples, which can be opened from ModusToolbox.

- Technical Reference Manuals (TRMs) provide detailed descriptions of the architecture and registers in each device family.

- Development Tools

- ModusToolbox is a free integrated design environment (IDE). It enables you to design hardware and firmware systems concurrently with EZ-PD™ PMG1 MCU devices. In addition, ModusToolbox includes a device selection tool to select devices for ModusToolbox projects.

- □ EZ-PD™ PMG1 MCU Prototyping Kits offer an easy-to-use, inexpensive platform to build EZ-PD™ PMG1 MCU-based systems.

- Additional Resources: Visit the EZ-PD™ PMG1 MCU webpage for additional resources such as IBIS, BSDL models, CAD Library Files, and Programming Specifications.

- Technical Support

- □ Forum: See if your question is already answered by fellow developers of the EZ-PD™ PMG1 MCU community.

- Cypress support: Visit our support page or contact a local sales representative.

## 3. Document Construction

The following sections in this document include these topics:

- Section B: CPU System on page 20

- Section C: Memory System on page 35

- Section D: System-Wide Resources on page 38

- Section E: Digital System on page 60

- Section F: USB Power Delivery on page 123

- Section G: Program and Debug on page 126

## 3.1 Major Sections

For ease of use, information is organized into sections and chapters that are divided according to device functionality.

- Section Presents the top-level architecture, how to get started, and conventions and overview information about any particular area that inform the reader about the construction and organization of the product.

- Chapter Presents the chapters specific to an individual aspect of the section topic. These are the detailed implementation and use information for some aspect of the integrated circuit.

- Glossary Defines the specialized terminology used in this technical reference manual (TRM). Glossary terms are presented in bold, italic font throughout.

- EZ-PD™ PMG1-S0 MCU Registers Technical Reference Manual Supplies all device register details summarized in the technical reference manual. These are additional documents.

#### 3.2 Documentation Conventions

This document uses only four distinguishing font types, besides those found in the headings.

- The first is the use of *italics* when referencing a document title or file name.

- The second is the use of **bold italics** when referencing a term described in the Glossary of this document.

- The third is the use of Times New Roman font, distinguishing equation examples.

- $\blacksquare$  The fourth is the use of Courier New font, distinguishing code examples.

#### 3.2.1 Register Conventions

Register conventions are detailed in the EZ-PD™ PMG1-S0 MCU Registers TRM.

#### 3.2.2 Numeric Naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah') and *hexadecimal* numbers may also be represented by a '0x' prefix, the *C* coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are *decimal*.

## 3.2.3 Units of Measure

This table lists the units of measure used in this document.

Table 3-1. Units of Measure

| Symbol | Unit of Measure                                 |

|--------|-------------------------------------------------|

| °C     | degrees Celsius                                 |

| dB     | decibels                                        |

| fF     | femtofarads                                     |

| Hz     | Hertz                                           |

| k      | kilo, 1000                                      |

| K      | kilo, 2^10                                      |

| КВ     | 1024 bytes, or approximately one thousand bytes |

| Kbit   | 1024 bits                                       |

| kHz    | kilohertz (32.000)                              |

| kΩ     | kilohms                                         |

| MHz    | megahertz                                       |

| ΜΩ     | megaohms                                        |

| μΑ     | microamperes                                    |

| μF     | microfarads                                     |

| μs     | microseconds                                    |

| μV     | microvolts                                      |

| μVrms  | microvolts root-mean-square                     |

| mA     | milliamperes                                    |

| ms     | milliseconds                                    |

| mV     | millivolts                                      |

| nA     | nanoamperes                                     |

| ns     | nanoseconds                                     |

| nV     | nanovolts                                       |

| Ω      | ohms                                            |

| pF     | picofarads                                      |

| рр     | peak-to-peak                                    |

| ppm    | parts per million                               |

| SPS    | samples per second                              |

| σ      | sigma: one standard deviation                   |

| V      | volts                                           |

## 3.2.4 Acronyms

This table lists the acronyms used in this document

Table 3-2. Acronyms

| Symbol | Unit of Measure                                                                                 |

|--------|-------------------------------------------------------------------------------------------------|

| ABUS   | analog output bus                                                                               |

| AC     | alternating current                                                                             |

| ADC    | analog-to-digital converter                                                                     |

| AHB    | AMBA (advanced microcontroller bus architecture) high-performance bus, an Arm data transfer bus |

Table 3-2. Acronyms (continued)

| Symbol           | Unit of Measure                                     |

|------------------|-----------------------------------------------------|

| API              | application programming interface                   |

| APOR             | analog power-on reset                               |

| вмс              | Bi-Phase Mark Coding                                |

| BR               | bit rate                                            |

| BRA              | bus request acknowledge                             |

| BRQ              | bus request                                         |

| CAN              | controller area network                             |

| СС               | Configuration Channel                               |

| CI               | carry in                                            |

| СМР              | compare                                             |

| СО               | carry out                                           |

| CPU              | central processing unit                             |

| CRC              | cyclic redundancy check                             |

| СТ               | continuous time                                     |

| DAC              | digital-to-analog converter                         |

| DC               | direct current                                      |

| DFP              | Downstream Facing Port                              |

| DI               | digital or data input                               |

| DMA              | direct memory access                                |

| DNL              | differential nonlinearity                           |

| DO               | digital or data output                              |

| DRP              | Dual Role Port                                      |

| DSI              | digital signal interface                            |

| DSM              | deep-sleep mode                                     |

| ECO              | external crystal oscillator                         |

| EEPROM           | electrically erasable programmable read only memory |

| EMCA             | Electronically Marked Cable Assembly                |

| EMIF             | external memory interface                           |

| FB               | feedback                                            |

| FIFO             | first in first out                                  |

| FSR              | full scale range                                    |

| GPIO             | general purpose I/O                                 |

| HCI              | host-controller interface                           |

| HFCLK            | high-frequency clock                                |

| I <sup>2</sup> C | inter-integrated circuit                            |

| IDE              | integrated development environment                  |

| ILO              | internal low-speed oscillator                       |

| IMO              | internal main oscillator                            |

| INL              | integral nonlinearity                               |

| I/O              | input/output                                        |

| IOR              | I/O read                                            |

| IOW              | I/O write                                           |

Table 3-2. Acronyms (continued)

| Symbol | Unit of Measure                   |  |

|--------|-----------------------------------|--|

| IRES   | initial power on reset            |  |

| IRA    | interrupt request acknowledge     |  |

| IRQ    | interrupt request                 |  |

| ISR    | interrupt service routine         |  |

| IVR    | interrupt vector read             |  |

| LRb    | last received bit                 |  |

| LRB    | last received byte                |  |

| LSb    | least significant bit             |  |

| LSB    | least significant byte            |  |

| LUT    | lookup table                      |  |

| MISO   | master-in-slave-out               |  |

| MMIO   | memory mapped input/output        |  |

| MOSI   | master-out-slave-in               |  |

| MSb    | most significant bit              |  |

| MSB    | most significant byte             |  |

| OVP    | over voltage protection           |  |

| PC     | program counter                   |  |

| PCH    | program counter high              |  |

| PCL    | program counter low               |  |

| PD     | power down                        |  |

| PFC    | power factor correction           |  |

| PGA    | programmable gain amplifier       |  |

| PM     | power management                  |  |

| PMA    | EZ-PD™ PMG1-S0 MCU memory arbiter |  |

| POR    | power-on reset                    |  |

| PPOR   | precision power-on reset          |  |

| PRS    | pseudo random sequence            |  |

| PSRR   | power supply rejection ratio      |  |

| PSSDC  | power system sleep duty cycle     |  |

| PWM    | pulse width modulator             |  |

| RAM    | random-access memory              |  |

| RETI   | return from interrupt             |  |

| RF     | radio frequency                   |  |

| ROM    | read only memory                  |  |

| RW     | read/write                        |  |

| SAR    | successive approximation register |  |

| SC     | switched capacitor                |  |

| SCB    | serial communication block        |  |

| SIE    | serial interface engine           |  |

| SIO    | special I/O                       |  |

| SE0    | single-ended zero                 |  |

| SNR    | signal-to-noise ratio             |  |

| SOF    | start of frame                    |  |

Table 3-2. Acronyms (continued)

| Symbol | Unit of Measure                             |  |  |

|--------|---------------------------------------------|--|--|

| SOI    | start of instruction                        |  |  |

| SOP    | Start of Packet                             |  |  |

| SP     | stack pointer                               |  |  |

| SPD    | sequential phase detector                   |  |  |

| SPI    | serial peripheral interconnect              |  |  |

| SPIM   | serial peripheral interconnect master       |  |  |

| SPIS   | serial peripheral interconnect slave        |  |  |

| SRAM   | static random-access memory                 |  |  |

| SROM   | supervisory read only memory                |  |  |

| SSADC  | single slope ADC                            |  |  |

| SSC    | supervisory system call                     |  |  |

| SYSCLK | system clock                                |  |  |

| SWD    | single wire debug                           |  |  |

| TC     | terminal count                              |  |  |

| TD     | transaction descriptors                     |  |  |

| UART   | universal asynchronous receiver/transmitter |  |  |

| UFP    | Upstream Facing Port                        |  |  |

| USB    | universal serial bus                        |  |  |

| USBIO  | USB I/O                                     |  |  |

| USB PD | USB Power Delivery                          |  |  |

| UVP    | under voltage protection                    |  |  |

| wco    | watch crystal oscillator                    |  |  |

| WDT    | watchdog timer                              |  |  |

| WDR    | watchdog reset                              |  |  |

| XRES   | external reset                              |  |  |

# Section B: CPU System

This section encompasses the following chapters:

- Cortex-M0 CPU chapter on page 21

- Interrupts chapter on page 26

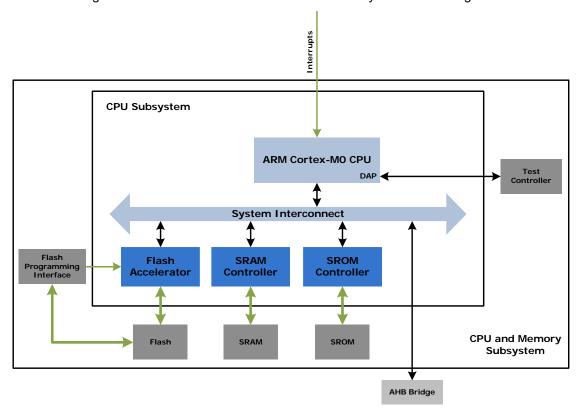

## **Top Level Architecture**

CPU System Block Diagram

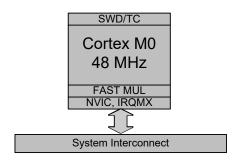

## 4. Cortex-M0 CPU

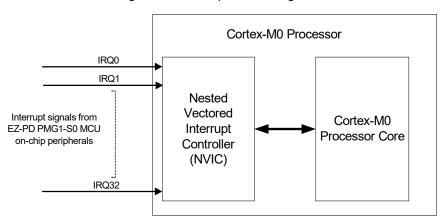

The EZ-PD™ PMG1-S0 MCU Arm Cortex-M0 core is a 32-bit CPU optimized for low-power operation. It has an efficient three-stage pipeline, a fixed 4-GB memory map, and supports the Armv6-M Thumb instruction set. The Cortex-M0 also features a low-latency interrupt service routine (ISR) entry and exit.

The Cortex-M0 processor includes a number of other components that are tightly linked to the CPU core. These include a nested vectored interrupt controller (NVIC), a SYSTICK timer, and debug.

This section gives an overview of the Cortex-M0 processor. For more details, see the Arm Cortex-M0 user guide or technical reference manual, both available at <a href="https://www.arm.com">www.arm.com</a>.

#### 4.1 Features

The EZ-PD™ PMG1-S0 MCU Arm Cortex-M0 has the following features:

- Easy to use, program and debug, ensuring easier migration from 8- and 16-bit processors

- Operates at up to 0.9 DMIPS/MHz; this helps to increase execution speed or reduce power

- Supports Thumb instruction set for improved code density, ensuring efficient use of memory

- NVIC unit to support interrupts and exceptions for rapid and deterministic interrupt response

- Extensive debug support including:

- Serial wire debug (SWD) port

- Breakpoints

- Watchpoints

## 4.2 Block Diagram

Figure 4-1. EZ-PD™ PMG1-S0 MCU CPU Subsystem Block Diagram

#### 4.3 How It Works

The Cortex-M0 is a 32-bit processor with a 32-bit data path, 32-bit registers, and a 32-bit memory interface. It supports most 16-bit instructions in the Thumb instruction set and some 32-bit instructions in the Thumb-2 instruction set.

#### 4.3.1 Registers

The Cortex-M0 has 16 32-bit registers, as Table 4-1 shows:

- R0 to R12 General-purpose registers. R0 to R7 can be accessed by all instructions; the other registers can be accessed by a subset of the instructions.

- R13 Stack pointer (SP). There are two stack pointers, with only one available at a time. In thread mode, the CONTROL register indicates the stack pointer to use, Main Stack Pointer (MSP) or Process Stack Pointer (PSP).

- R14 Link register. Stores the return program counter during function calls.

- R15 Program counter. This register can be written to control program flow.

Table 4-1. Cortex-M0 Registers

| Name    | Type <sup>1</sup> | Reset Value                                                                                        | Description                                                                                                                                                                                                                                   |  |  |

|---------|-------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R0-R12  | RW                | Unknown                                                                                            | R0-R12 are 32-bit general-purpose registers for data operations.                                                                                                                                                                              |  |  |

| MSP     | MSP               |                                                                                                    | The stack pointer (SP) is register R13. In thread mode, bit[1] of the CONTROL register indicates the stack pointer to use:                                                                                                                    |  |  |

|         | RW                | [0x00000000]                                                                                       | 0 = Main stack pointer (MSP). This is the reset value.                                                                                                                                                                                        |  |  |

| PSP     |                   |                                                                                                    | 1 = Process stack pointer (PSP).                                                                                                                                                                                                              |  |  |

|         |                   |                                                                                                    | On reset, the processor loads the MSP with the value from address 0x00000000.                                                                                                                                                                 |  |  |

| LR      | RW                | Unknown                                                                                            | The link register (LR) is register R14. It stores the return information for subroutines, function calls, and exceptions.                                                                                                                     |  |  |

| PC      | RW                | [0x00000004]                                                                                       | The program counter (PC) is register R15. It contains the current program address. On results of the processor loads the PC with the value from address 0x00000004. Bit[0] of the value is loaded into the EPSR T-bit at reset and must be 1. |  |  |

|         |                   |                                                                                                    | The program status register (PSR) combines:                                                                                                                                                                                                   |  |  |

| PSR     | RW                | / Unknown <sup>2</sup>                                                                             | Application Program Status Register (APSR).                                                                                                                                                                                                   |  |  |

| PSK     | KVV               |                                                                                                    | Execution Program Status Register (EPSR).                                                                                                                                                                                                     |  |  |

|         |                   |                                                                                                    | Interrupt Program Status Register (IPSR).                                                                                                                                                                                                     |  |  |

| APSR    | RW                | Unknown The APSR contains the current state of the condition flags from previous instruction execu |                                                                                                                                                                                                                                               |  |  |

| EPSR    | RO                | Unknown <sup>b</sup>                                                                               | Inknown <sup>b</sup> The EPSR contains the Thumb state bit.                                                                                                                                                                                   |  |  |

| IPSR    | RO                | 0                                                                                                  | The IPSR contains the exception number of the current ISR.                                                                                                                                                                                    |  |  |

| PRIMASK | RW                | 0                                                                                                  | The PRIMASK register prevents activation of all exceptions with configurable priority.                                                                                                                                                        |  |  |

| CONTROL | RW                | 0                                                                                                  | The CONTROL register controls the stack used when the processor is in Thread mode.                                                                                                                                                            |  |  |

Describes access type during program execution in thread mode and handler mode. Debug access can differ.

Bit[24] is the T-bit and is loaded from bit[0] of the reset vector.

Table 4-2 shows how the PSR bits are assigned.

Table 4-2. Cortex-M0 PSR Bit Assignments

| Bit   | PSR Register | Name | Usage                                                                                                                                                                                                       |  |

|-------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31    | APSR         | N    | Negative flag                                                                                                                                                                                               |  |

| 30    | APSR         | Z    | Zero flag                                                                                                                                                                                                   |  |

| 29    | APSR         | С    | Carry or borrow flag                                                                                                                                                                                        |  |

| 28    | APSE         | ٧    | Overflow flag                                                                                                                                                                                               |  |

| 27–25 | _            | -    | Reserved                                                                                                                                                                                                    |  |

| 24    | EPSR         | Т    | Thumb state bit. Must always be 1. Attempting to execute instructions when the T bit is 0 results in a HardFault exception.                                                                                 |  |

| 23–6  | _            | -    | Reserved                                                                                                                                                                                                    |  |

| 5–0   | IPSR         | N/A  | Exception number of current ISR:  0 = thread mode 1 = reserved 2 = Non maskable interrupt (NMI) 3 = HardFault 4 - 10 = reserved 11 = SVCall 12, 13 = reserved 14 = PendSV 15 = SysTick 16 = IRQ0 47 = IRQ31 |  |

Use the MSR or CPS instruction to set or clear bit 0 of the PRIMASK register. If the bit is 0, exceptions are enabled. If the bit is 1, all exceptions with configurable priority, that is, all exceptions except HardFault, NMI, and Reset, are disabled. See the Interrupts chapter on page 26 for a list of exceptions.

#### 4.3.2 Operating Modes

The Cortex-M0 processor supports two operating modes:

- Thread Mode used by all normal applications. In the thread mode, the MSP or PSP can be used. The CONTROL register bit 1 determines which stack pointer is used:

- □ 0 = MSP is the current stack pointer

- □ 1 = PSP is the current stack pointer

- Handler Mode used to execute exception handlers. The MSP is always used.

In thread mode, use the MSR instruction to set the stack pointer bit in the CONTROL register. When changing the stack pointer, use an ISB instruction immediately after the MSR instruction. This ensures that instructions after the ISB execute using the new stack pointer.

In handler mode, explicit writes to the CONTROL register are ignored, because the MSP is always used. The exception entry and return mechanisms automatically update the CONTROL register.

#### 4.3.3 Instruction Set

The Cortex-M0 implements a version of the Thumb instruction set. For details, see the Cortex-M0 Generic User Guide.

An instruction operand can be an Arm register, a constant, or another instruction-specific parameter. Instructions act on the operands and often store the result in a destination register. Many instructions are unable to use, or have restrictions on using, the PC or SP for the operands or destination register.

Table 4-3. Thumb Instruction Set

| Mnemonic | Brief Description                          |  |  |

|----------|--------------------------------------------|--|--|

| ADCS     | Add with Carry                             |  |  |

| ADD{S}   | Add                                        |  |  |

| ADR      | PC-relative Address to Register            |  |  |

| ANDS     | Bit wise AND                               |  |  |

| ASRS     | Arithmetic Shift Right                     |  |  |

| B{cc}    | Branch {conditionally}                     |  |  |

| BICS     | Bit Clear                                  |  |  |

| BKPT     | Breakpoint                                 |  |  |

| BL       | Branch with Link                           |  |  |

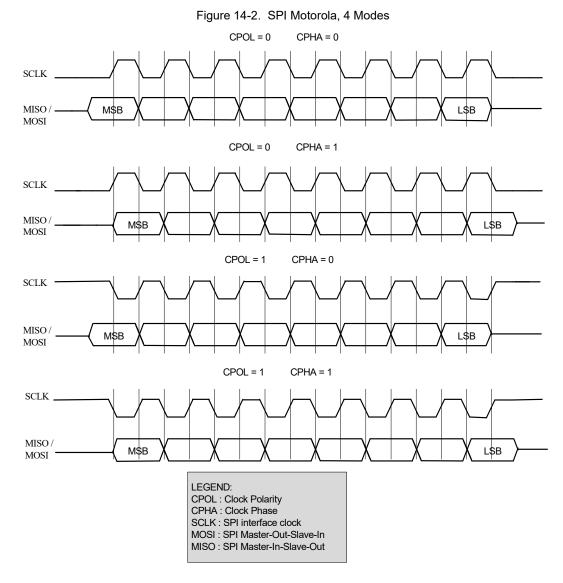

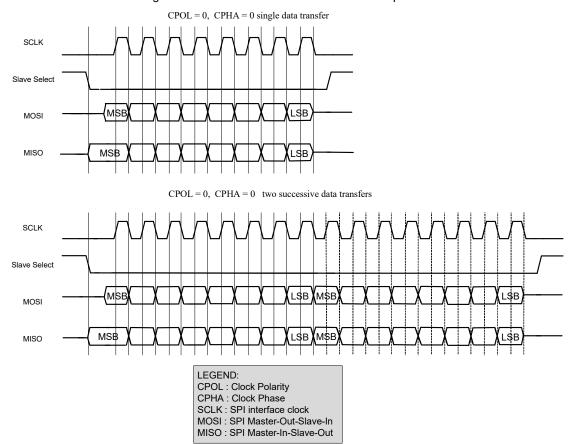

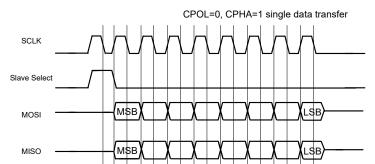

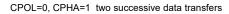

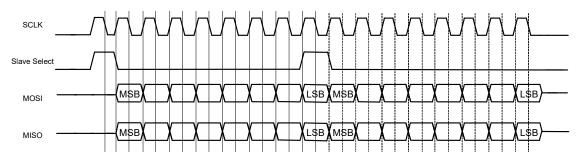

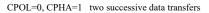

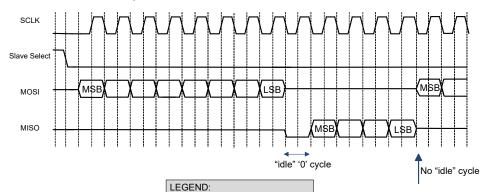

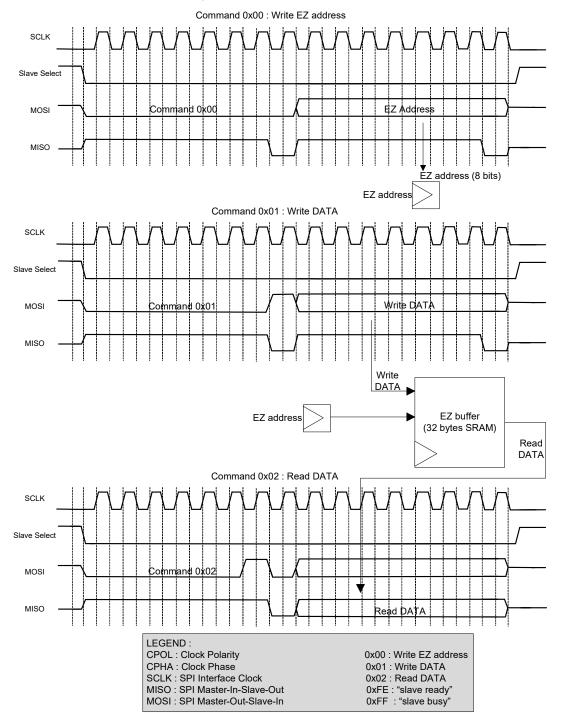

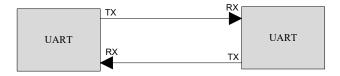

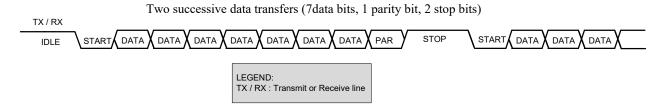

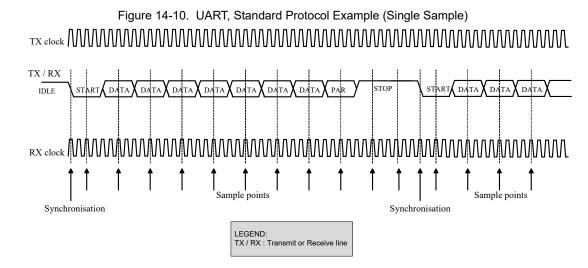

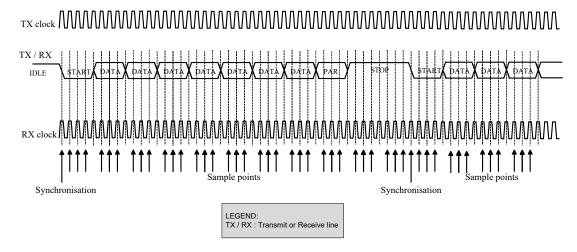

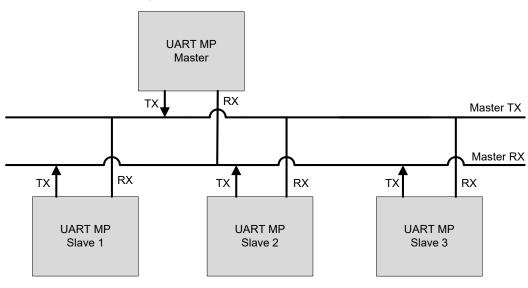

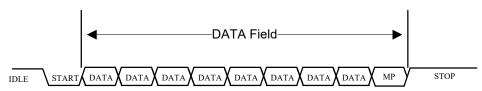

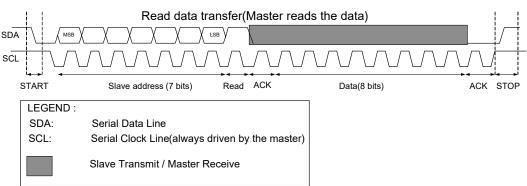

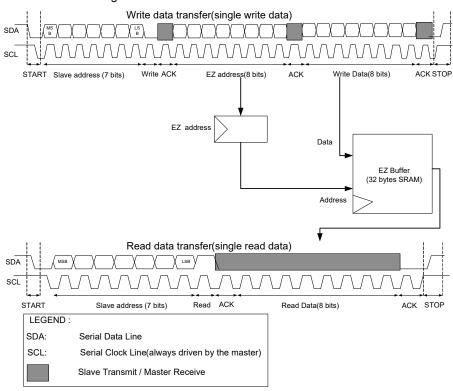

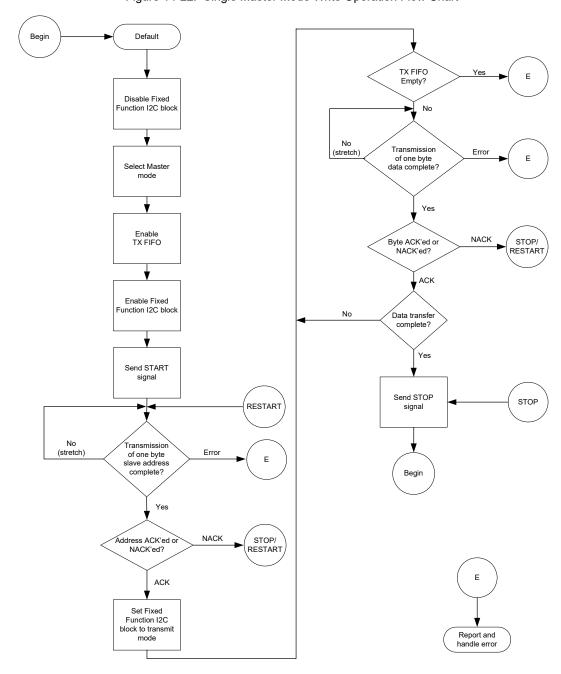

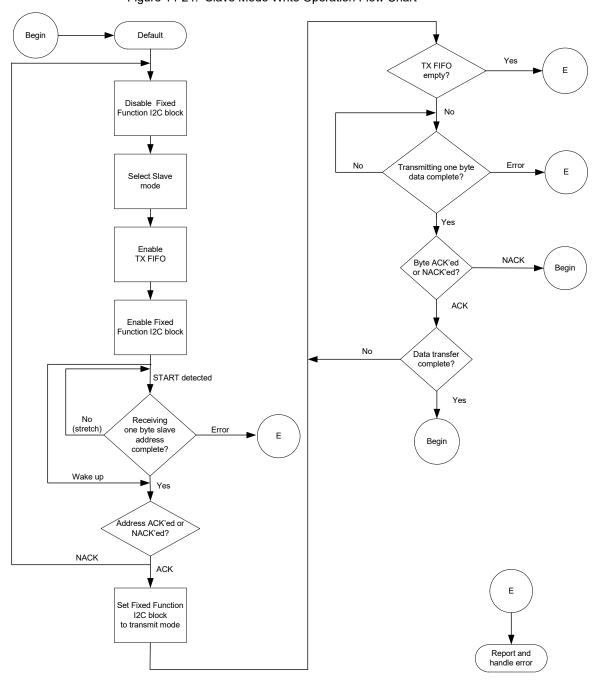

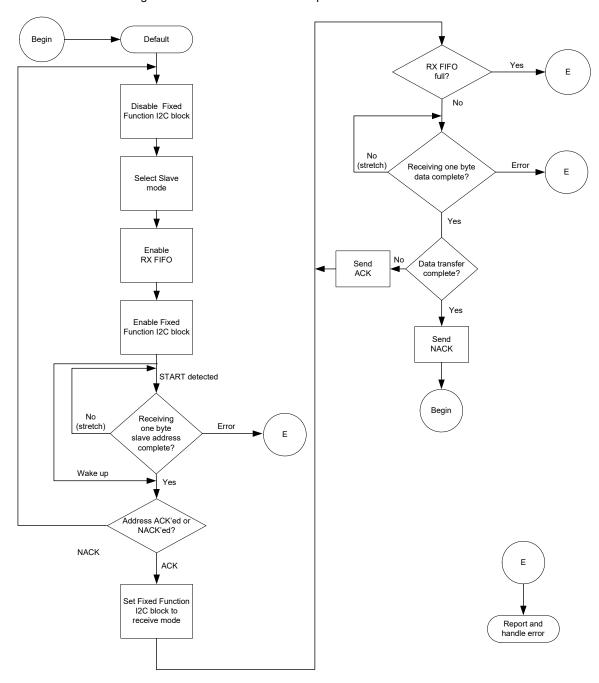

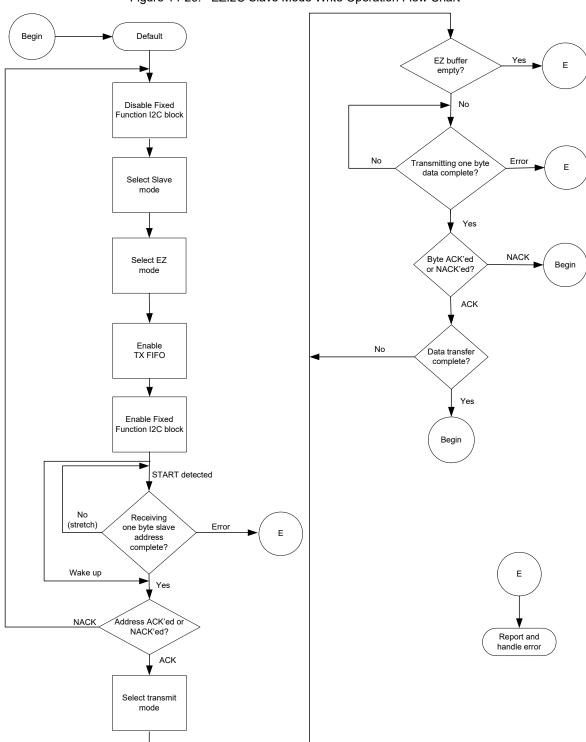

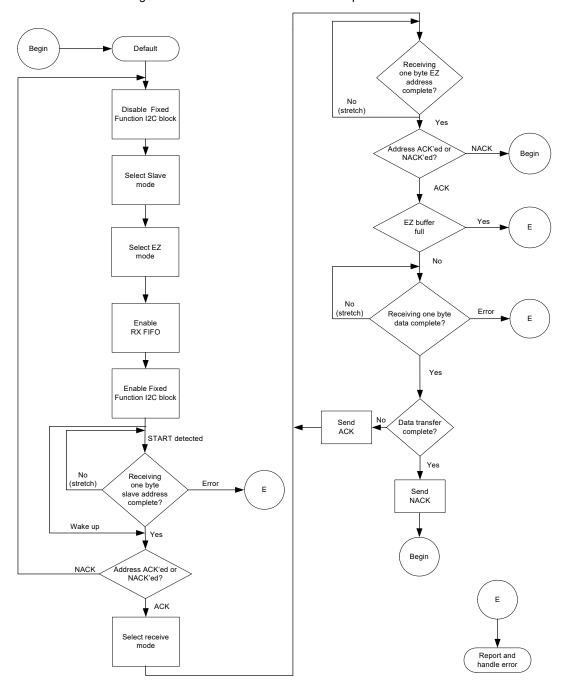

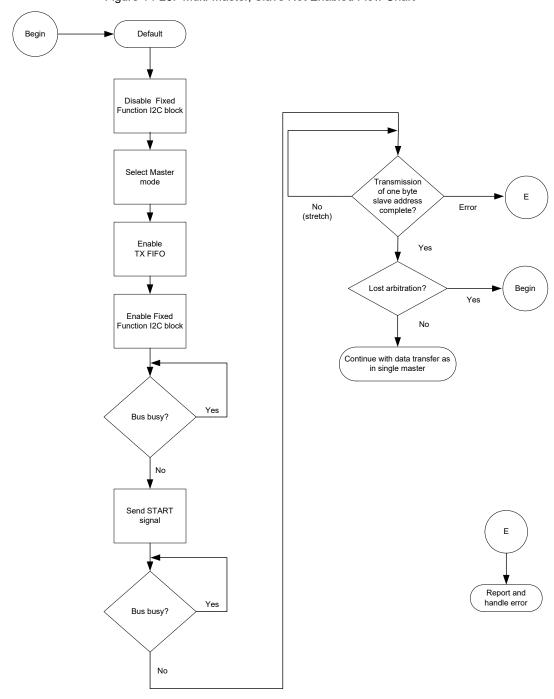

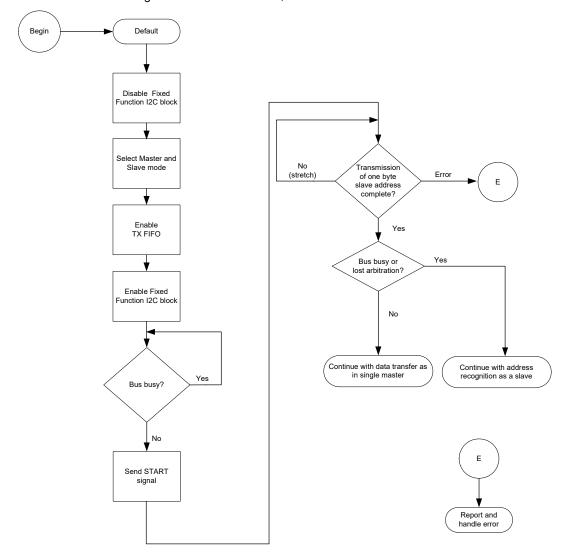

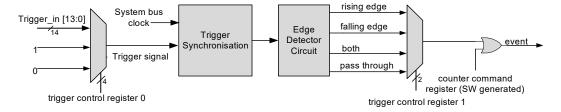

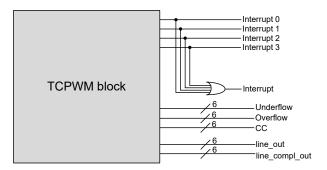

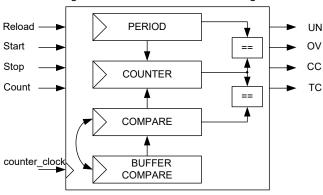

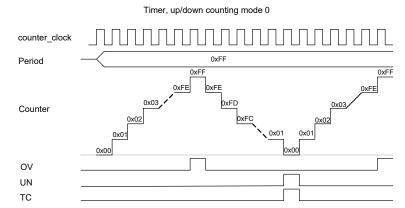

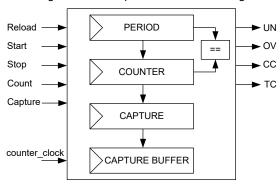

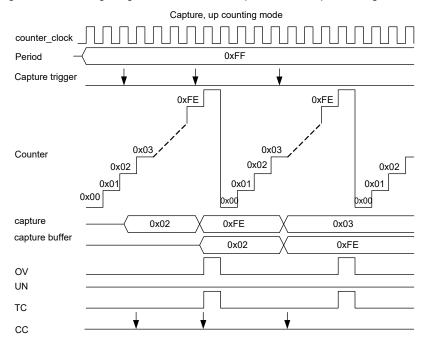

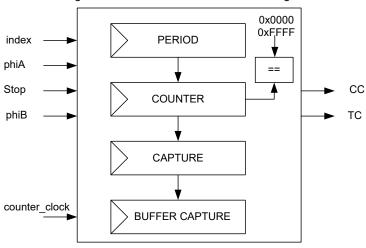

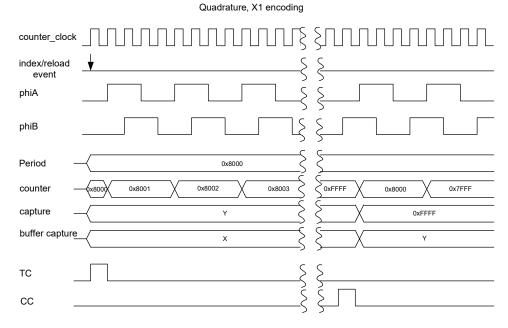

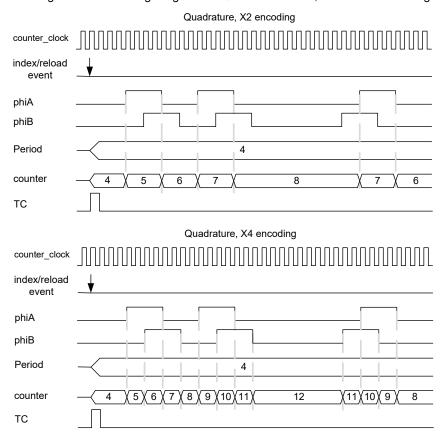

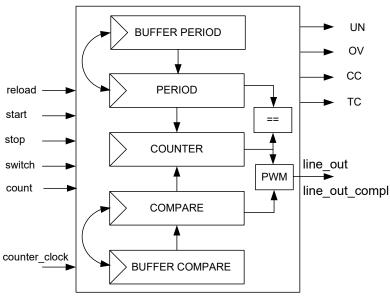

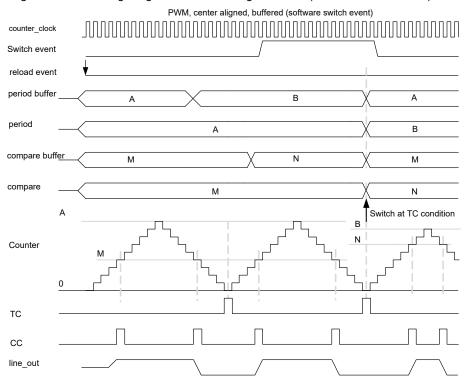

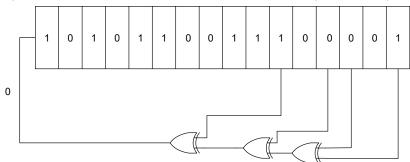

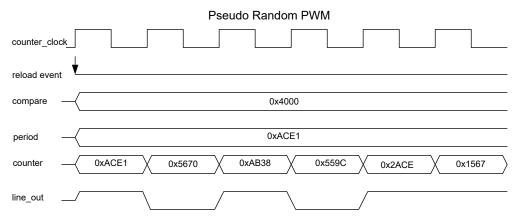

| BLX      | Branch indirect with Link                  |  |  |