# 英飞凌XDPS2221E PFC + HFB混合反激组合控制器

## 数据手册

### 特性

- 采用 DSO-14 (150mil) 封装的 QRM PFC 升压和 DC-DC HFB 混合反激式数字组合控制器

- 新颖的 ZVS 混合反激式 (HFB, 也称为非对称半桥) 拓扑结构, 可实现超高系统效率和高密度设计

- 支持 GaN 与 Si 开关的集成栅极驱动器

- 600 V 高压启动单元, 用于快速 VCC 充电

- 突发模式操作控制, 实现最低空载待机功耗

- 自适应 PFC 总线电压和 PFC 启用/禁用控制, 以最大限度地提高平均和轻载效率

- 可配置保护模式和系统性能的参数

- 无铅镀铅、无卤素 (符合 IEC61249-2-21) 、符合 RoHS 标准

- 可配置 PFC QRM 操作, 以提高平均效率

- PFC 脉冲跳跃可提高轻载效率

- 根据运行条件自动禁用/启用 PFC

- 自适应 PFC 总线电压水平遵循工作条件

- PFC 改善了动态负载响应, 从而减少了大容量电容

- HFB 峰值电流模式控制, 实现稳健、快速的线性与负载调整率

- 高侧和低侧开关的 HFB ZVS 操作 (在 DCM 中插入 ZVS 脉冲)

- HFB 可配置多模式操作, 可提高平均效率和轻载效率

### 潜在应用

- 高密度/宽输出电压范围电源

- 高功率密度开关电源

- 电池充电器

### 产品验证

符合 JEDEC47/20/22 相关的工业应用要求

### 描述

XDPS2221E PWM 控制器是一款高度集成的设备, 结合了多模 AC-DC PFC 控制器和多模 DC-DC 混合反激控制器, 支持宽输出电压范围设计。将 PFC 和混合反激式电路集成到单个封装中, 可以减少外部物料清单组件, 并通过两个阶段的协调操作来优化系统性能。

### 订购信息

| Product name | Marking   | Ordering code | Firmware version | Package   |

|--------------|-----------|---------------|------------------|-----------|

| XDPS2221E    | XDPS2221E | SP006063847   | 4.0.3            | PG-DSO-14 |

本数据手册的原文使用英文撰写。为方便起见, 英飞凌提供了译文; 由于翻译过程中可能使用了自动化工具, 英飞凌不保证译文的准确性。为确认准确性请务必访问 [infineon.com](http://infineon.com) 参考最新的英文版本 (控制文档)。

## 目录

|                                        |           |

|----------------------------------------|-----------|

| <b>目录 .....</b>                        | <b>2</b>  |

| <b>1 引脚配置和功能 .....</b>                 | <b>5</b>  |

| <b>2 代表性框图 .....</b>                   | <b>7</b>  |

| <b>3 简介 .....</b>                      | <b>8</b>  |

| <b>4 功能说明 .....</b>                    | <b>15</b> |

| 4.1 VCC 电源和高压启动单元管理 .....              | 15        |

| 4.1.1 VCC 电容充电和启动序列 .....              | 15        |

| 4.1.2 上电阶段采用Bang-bang模式运行 .....        | 16        |

| 4.1.3 保护模式运行期间的Bang-bang模式 .....       | 16        |

| 4.1.4 突发模式操作期间的VCC 电源 .....            | 17        |

| 4.2 PFC控制 .....                        | 17        |

| 4.2.1 组合PFC电流限制和过零检测 .....             | 19        |

| 4.2.2 多模式操作和频率规律 .....                 | 20        |

| 4.2.2.1 准谐振模式 .....                    | 20        |

| 4.2.2.2 低功耗模式 .....                    | 21        |

| 4.2.3 PFC 总线电压感测和调节 .....              | 21        |

| 4.2.4 PFC 总线电压目标设置 .....               | 21        |

| 4.2.5 PFC 软启动 .....                    | 21        |

| 4.2.6 PFC 栅极驱动器 .....                  | 21        |

| 4.3 混合反激式控制 .....                      | 21        |

| 4.3.1 PWM控制方案 .....                    | 22        |

| 4.3.1.1 连续谐振模式控制方案 .....               | 22        |

| 4.3.1.2 零电压谐振谷底开关模式控制方案 .....          | 23        |

| 4.3.1.3 谷底跳跃控制 .....                   | 24        |

| 4.3.1.4 CRM和ZV-RVS之间的模式转换 .....        | 24        |

| 4.3.2 输出控制 .....                       | 24        |

| 4.3.2.1 输出电流控制法则 .....                 | 25        |

| 4.3.2.2 保持ZVS操作以适应较宽的Vbus电压范围 .....    | 26        |

| 4.3.2.3 保持ZVS操作以实现宽输出电压范围 .....        | 26        |

| 4.3.2.4 CRM操作期间的ZVS操作和体二极管交叉传导预防 ..... | 26        |

| 4.3.2.5 传输延迟补偿 .....                   | 27        |

| 4.3.3 Vout 启动控制 .....                  | 27        |

| 4.3.4 频率抖动 .....                       | 27        |

| 4.3.5 半桥栅极驱动器 .....                    | 27        |

| 4.4 组合控制功能 .....                       | 28        |

| 4.4.1 突发模式控制 .....                     | 28        |

| 4.4.1.1 突发模式进出控制 .....                 | 29        |

| 4.4.1.2 突发模式操作 .....                   | 29        |

|            |                                        |    |

|------------|----------------------------------------|----|

| 4.4.1.3    | 自举预充电 .....                            | 29 |

| 4.4.2      | PFC启用/禁用控制.....                        | 30 |

| 4.4.3      | 母线电压目标水平.....                          | 30 |

| 4.5        | 保护措施.....                              | 31 |

| 4.5.1      | <b>保护模式</b> .....                      | 32 |

| 4.5.1.1    | 欠压闭锁后停用IC.....                         | 32 |

| 4.5.1.2    | 自动重启模式 .....                           | 32 |

| 4.5.1.3    | 锁存模式.....                              | 32 |

| 4.5.1.4    | 快速重启模式.....                            | 32 |

| 4.5.2      | <b>保护功能</b> .....                      | 33 |

| 4.5.2.1    | Vcc欠压锁定.....                           | 33 |

| 4.5.2.2    | HSVCC欠压闭锁.....                         | 33 |

| 4.5.2.3    | VCC过压保护.....                           | 33 |

| 4.5.2.4    | 欠压保护 .....                             | 33 |

| 4.5.2.5    | 过压保护 .....                             | 33 |

| 4.5.2.6    | 启动超时保护 .....                           | 33 |

| 4.5.2.7    | PFC总线过压保护 .....                        | 34 |

| 4.5.2.8    | 输入欠压保护 .....                           | 34 |

| 4.5.2.9    | 峰值电流限制 .....                           | 34 |

| 4.5.2.10   | PFC CCM 运行保护 .....                     | 34 |

| 4.5.2.11   | 混合反激式过流保护.....                         | 34 |

| 4.5.2.11.1 | 过流保护 .....                             | 35 |

| 4.5.2.11.2 | 一次侧过流保护 CSPROT.....                    | 35 |

| 4.5.2.12   | <b>过压和欠压保护</b> .....                   | 35 |

| 4.5.2.12.1 | Vout过压保护.....                          | 36 |

| 4.5.2.12.2 | Vout欠压保护.....                          | 36 |

| 4.5.2.12.3 | Vout短路保护.....                          | 36 |

| 4.5.2.13   | 短路保护 .....                             | 36 |

| 4.5.2.14   | FB引脚启动保护 .....                         | 37 |

| 4.5.2.15   | 混合反激式开环保护.....                         | 37 |

| 4.5.2.16   | 外部过温保护 .....                           | 37 |

| 4.5.2.17   | 内存奇偶校验 .....                           | 37 |

| 4.5.3      | MFIO 引脚上的错误读取.....                     | 37 |

| <b>5</b>   | <b>电气特性</b> .....                      | 38 |

| 5.1        | 绝对最大额定值.....                           | 38 |

| 5.2        | 封装特性.....                              | 40 |

| 5.3        | 工作条件.....                              | 40 |

| 5.4        | <b>特性</b> .....                        | 41 |

| 5.4.1      | 高电压 (HV 引脚) .....                      | 42 |

| 5.4.2      | 电源 (VCC 引脚) .....                      | 42 |

| 5.4.3      | 浮动 HS 域 (HSGND, HSVCC 和 HSGD 引脚) ..... | 43 |

| 5.4.4      | 总线电压检测 (PFCVS 引脚) .....                | 43 |

|        |                                |    |

|--------|--------------------------------|----|

| 5.4.5  | PFC 电流检测和过零检测 (PFCCS 引脚) ..... | 44 |

| 5.4.6  | 混合反激式过零检测 (ZCD 引脚) .....       | 44 |

| 5.4.7  | 多功能输入输出 (MFIO 引脚) .....        | 44 |

| 5.4.8  | 混合反激式电流感应 (CS 引脚) .....        | 45 |

| 5.4.9  | 混合反激输出反馈 (FB 引脚) .....         | 45 |

| 5.4.10 | 低侧栅极驱动器 (LSGD 引脚) .....        | 46 |

| 5.4.11 | PFC 栅极驱动器 (PFCGD 引脚) .....     | 46 |

| 5.4.12 | 中央控制功能 .....                   | 46 |

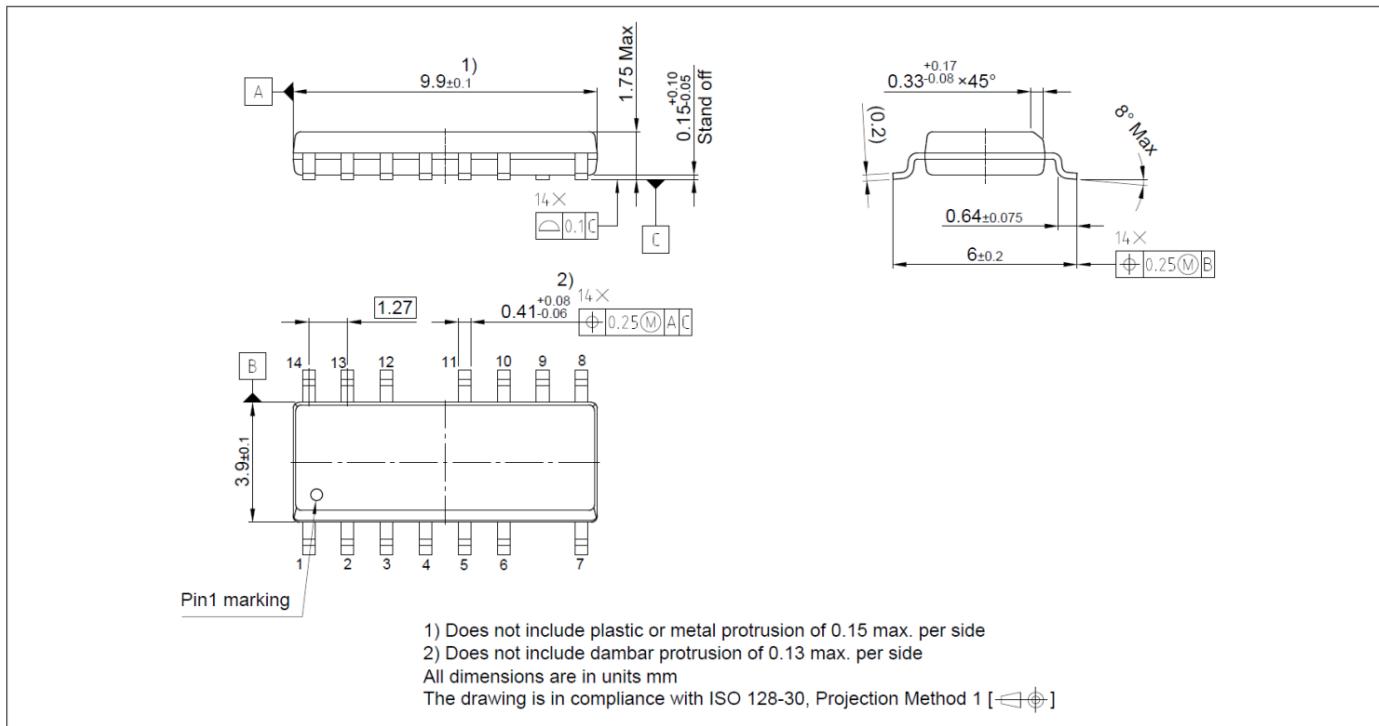

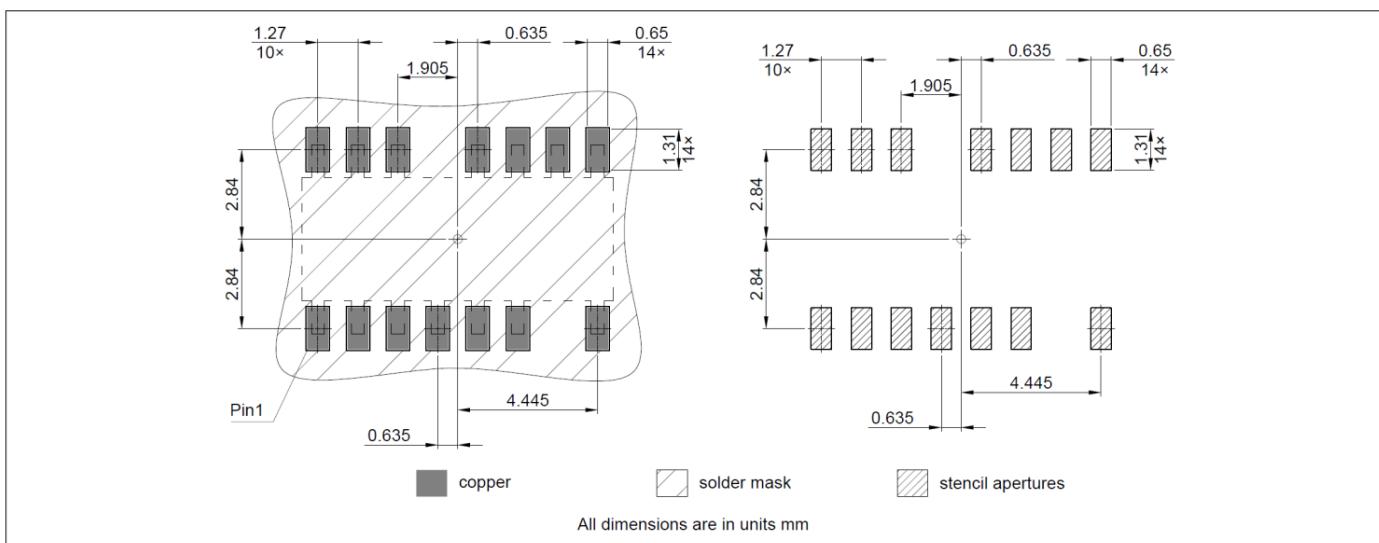

| 6      | 封装尺寸 .....                     | 48 |

| 7      | 修订记录 .....                     | 49 |

|        | 免责声明 .....                     | 50 |

## 1 Pin configuration and functionality

## 1 引脚配置和功能

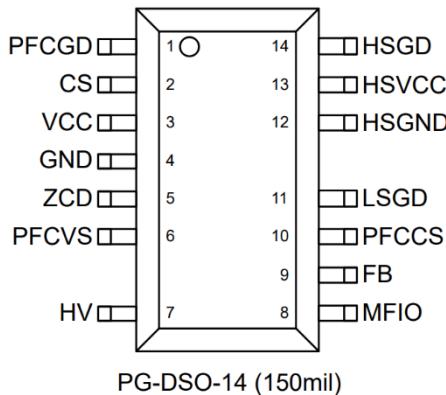

引脚配置如下图所示，功能见下表。

图 1 XDPS2221E引脚配置

表 1 引脚定义和功能

| Symbol | Pin | Type | Function                                                                                                                                                                                                                                                                                                        |

|--------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFCGD  | 1   | O    | <b>PFC gate driver</b><br>This pin drives the PFC transistor.                                                                                                                                                                                                                                                   |

| CS     | 2   | I    | <b>Hybrid-flyback current sense</b><br>Input pin for current sensing during the hybrid-flyback high-side gate driver turn-on phase.                                                                                                                                                                             |

| VCC    | 3   | I    | <b>Power supply</b><br>This pin supplies the IC. During start-up VCC is supplied internally from the AC via the HV pin, while during normal operation VCC is supplied from the auxiliary winding to the hybrid-flyback stage.                                                                                   |

| GND    | 4   | O    | <b>Ground</b><br>Ground level of the IC for supply voltage, gate drive and sense signals.                                                                                                                                                                                                                       |

| ZCD    | 5   | I    | <b>Hybrid-flyback zero-crossing detection</b><br>This pin provides zero-crossing detection after low-side gate driver is turned off, during pause phase in skip cycle and burst mode. Furthermore, the reflected output voltage at auxiliary winding can be measured during low-side gate driver turn-on phase. |

| PFCVS  | 6   | I    | <b>PFC bus voltage sense</b><br>This pin is connected to a high impedance resistor divider for bus voltage sensing.                                                                                                                                                                                             |

| HV     | 7   | I    | <b>High voltage input</b><br>The HV pin is connected to the input AC voltage. An internal HV start-up cell is used for initial VCC charging and AC monitoring                                                                                                                                                   |

(表格续下页.....)

## 1 Pin configuration and functionality

表 1 (续) 引脚定义和功能

| Symbol | Pin | Type | Function                                                                                                                                                                                                                                                                                                                        |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MFIO   | 8   | I    | <b>Multi-functional input output</b><br>This pin has different function depending on configuration. One example is to detect ambient temperature using an external NTC resistor connected between MFIO and GND. Furthermore, UART communication for parameter configuration and failure mode reporting is provided by this pin. |

| FB     | 9   | I    | <b>Feedback</b><br>Feedback signal indicating the required output current, typically connected to optocoupler for secondary side feedback.                                                                                                                                                                                      |

| PFCCS  | 10  | I    | <b>PFC current sense and PFC zero-crossing detection</b><br>This pin is configured for PFC current sensing in combination with zero-crossing detection of the PFC choke current.                                                                                                                                                |

| LSGD   | 11  | O    | <b>Hybrid-flyback low-side gate driver</b><br>This pin drives the low-side transistor of the hybrid-flyback half-bridge.                                                                                                                                                                                                        |

| HSGND  | 12  | I    | <b>High-side Ground</b><br>Ground reference node for hybrid-flyback floating high-side driver domain.                                                                                                                                                                                                                           |

| HSVCC  | 13  | I    | <b>High-side power supply</b><br>Power supply input for hybrid-flyback floating high-side driver domain.                                                                                                                                                                                                                        |

| HSGD   | 14  | O    | <b>High-side gate driver</b><br>This pin drives the high-side transistor of the hybrid-flyback half-bridge from the floating driver domain.                                                                                                                                                                                     |

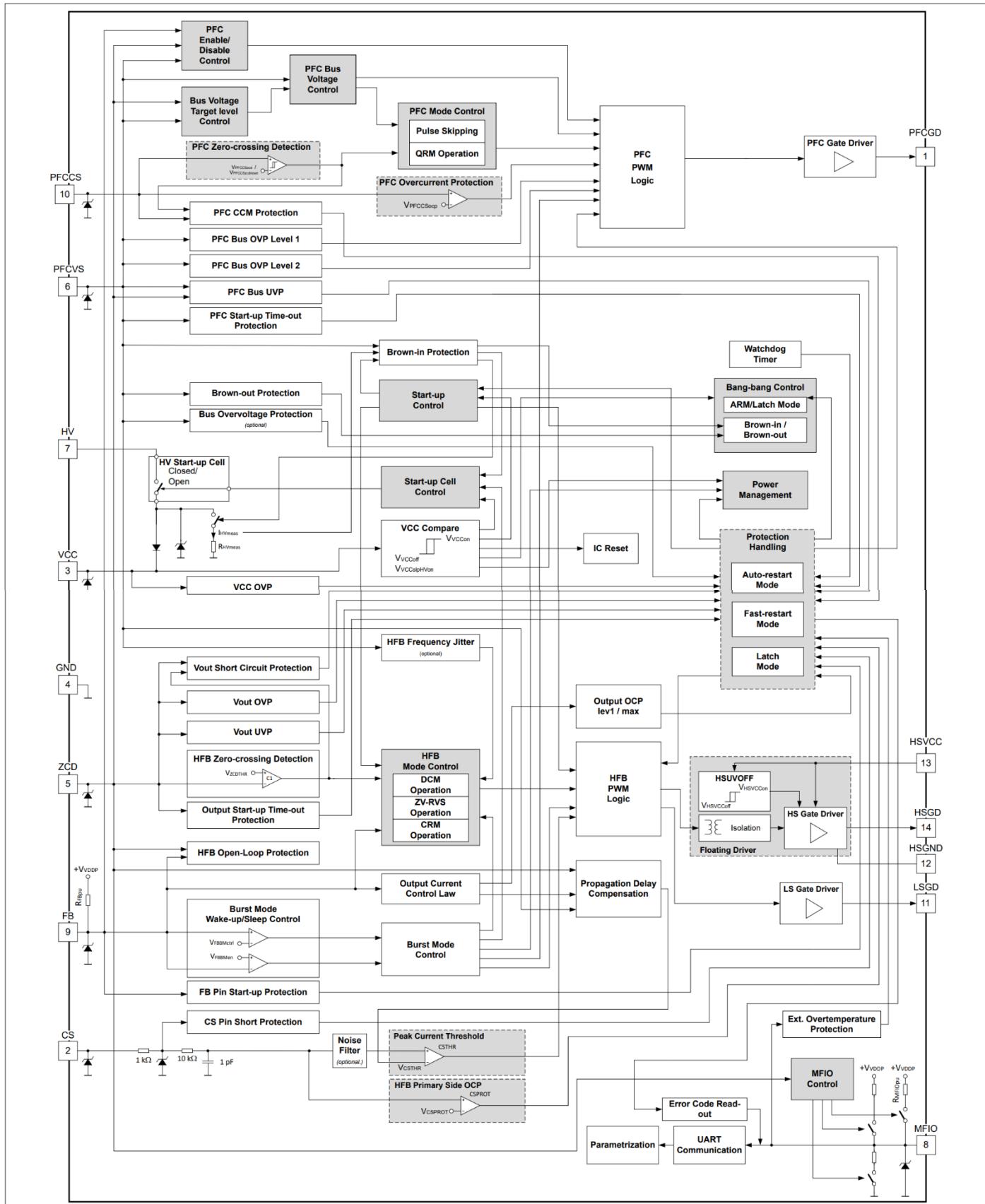

## 2 代表性框图

## 2 代表性框图

图 2

框图

### 3 简介

## 3 简介

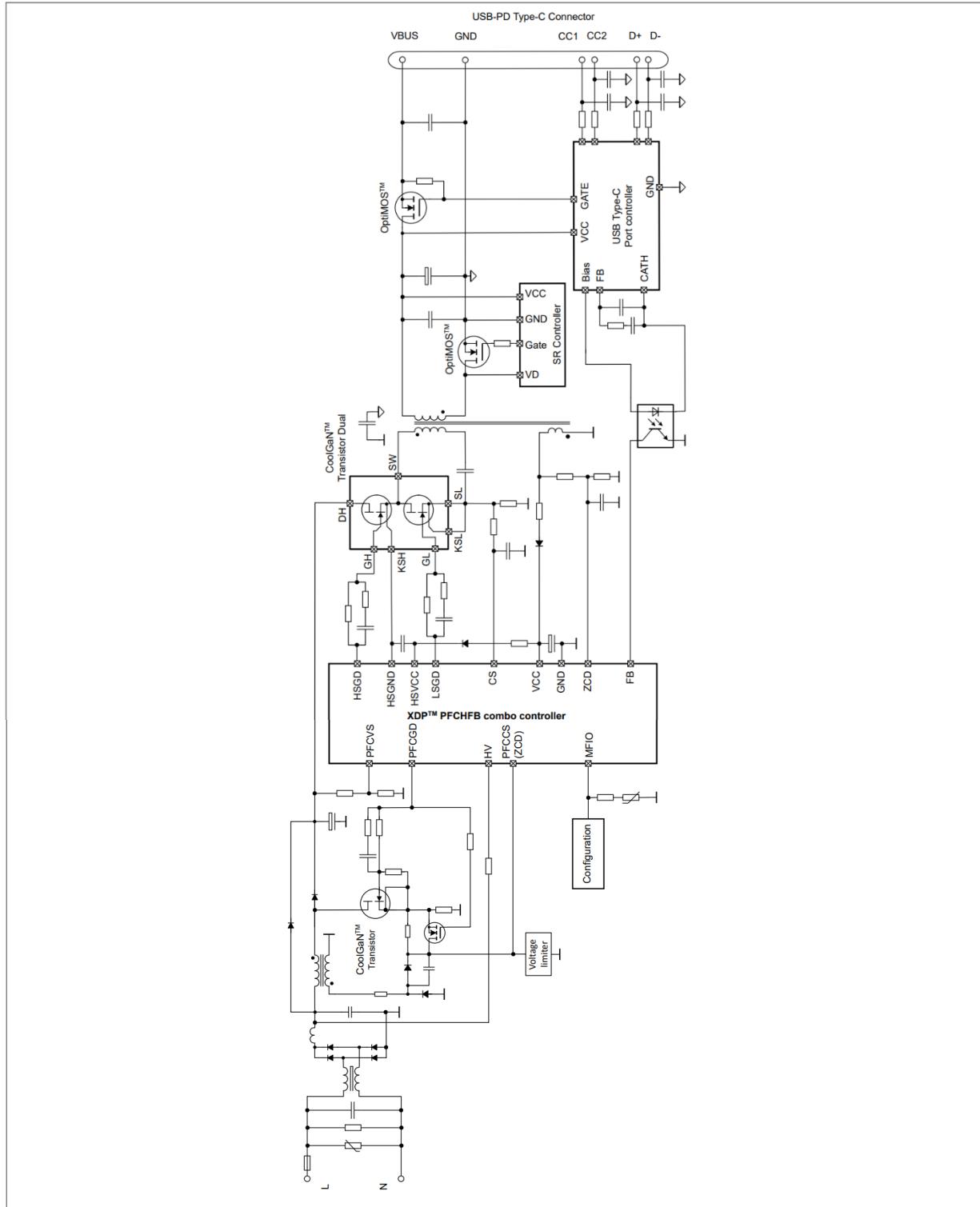

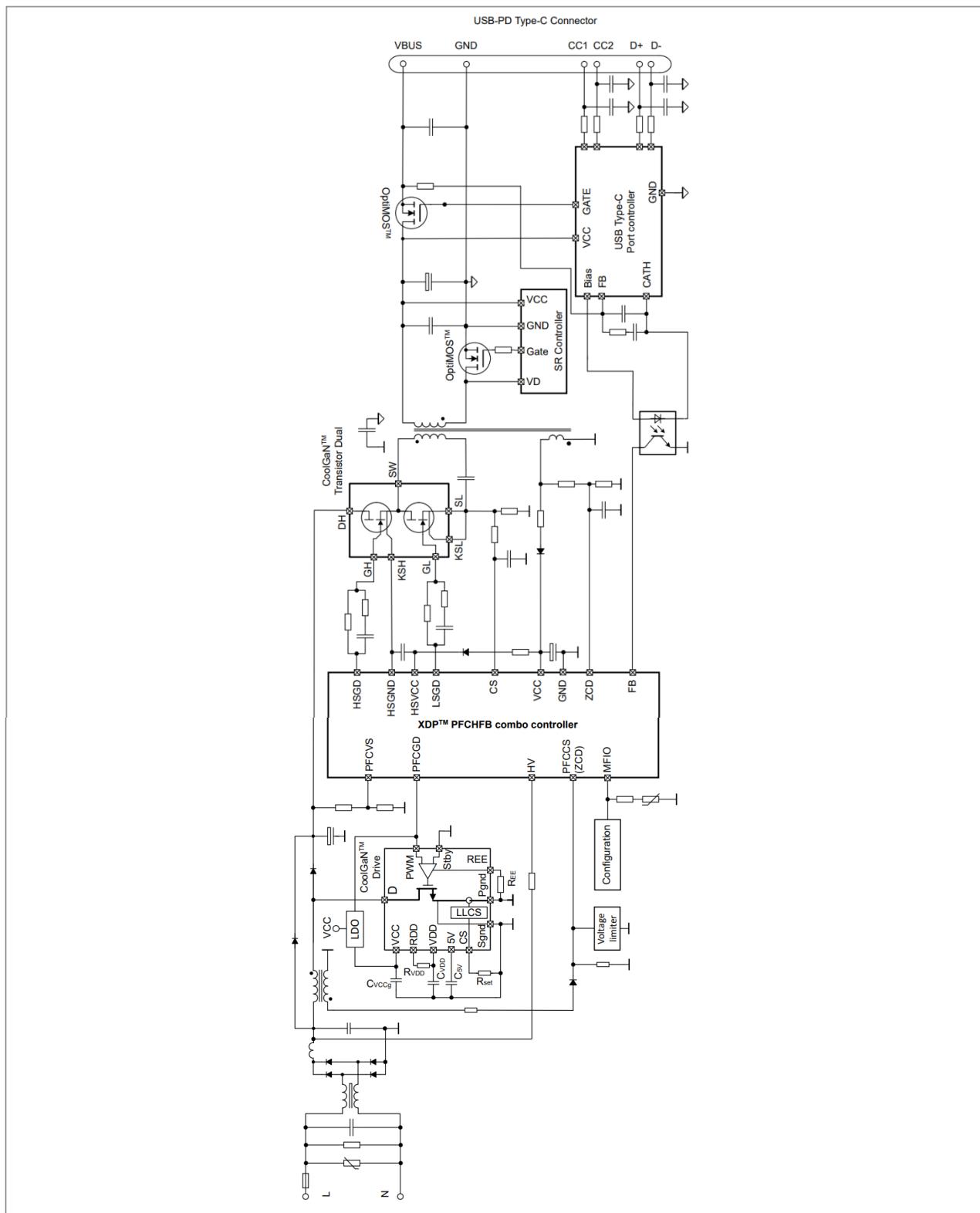

XDPS2221E PWM 控制器是一款高度集成的，结合了多模 AC-DC PFC 控制器和多模 DC-DC 混合反激 (HFB) 控制器。将 PFC 和混合反激式电路集成到单个控制器中，可以减少外部器件，并通过两者的联合操作优化性能阶段。它适用于具有宽输出电压的 USB-PD 充电器/适配器。

使用英飞凌 CoolMOS<sup>TM</sup>晶体管、CoolGaN<sup>TM</sup>晶体管、CoolGaN<sup>TM</sup>晶体管双路和 CoolGaN<sup>TM</sup> 驱动器以及 OptiMOS<sup>TM</sup> 晶体管可以进一步提高系统效率。

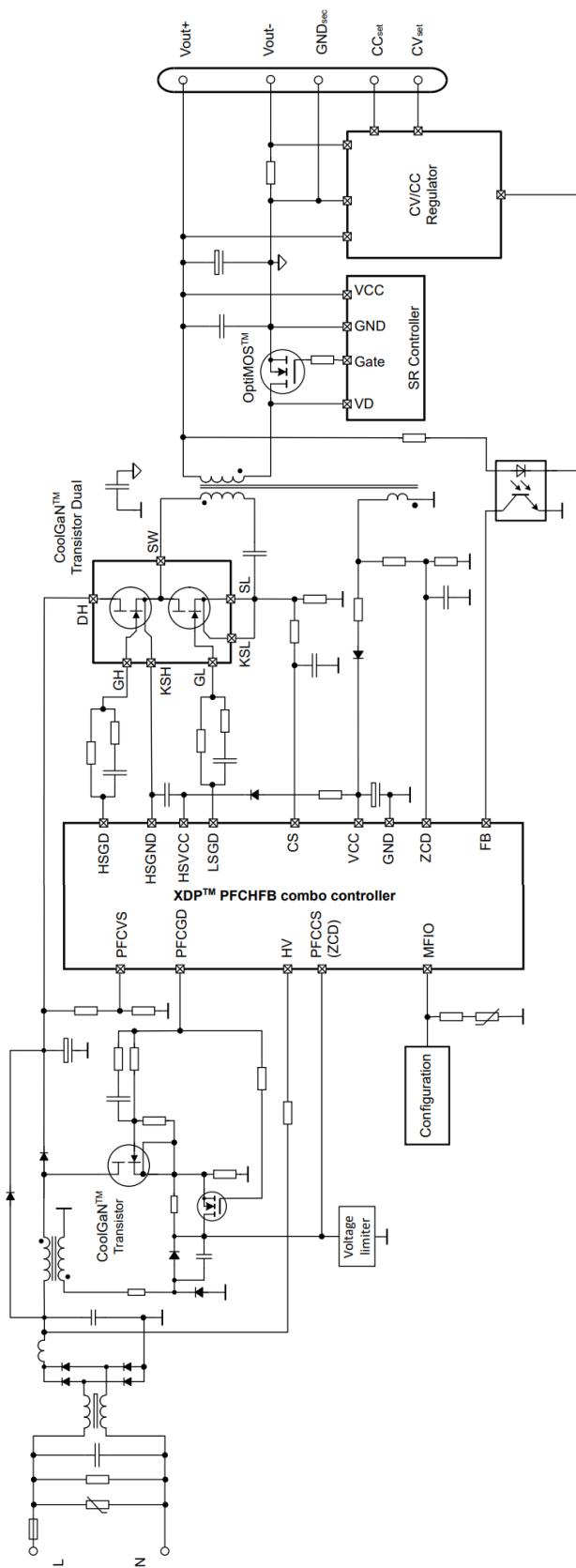

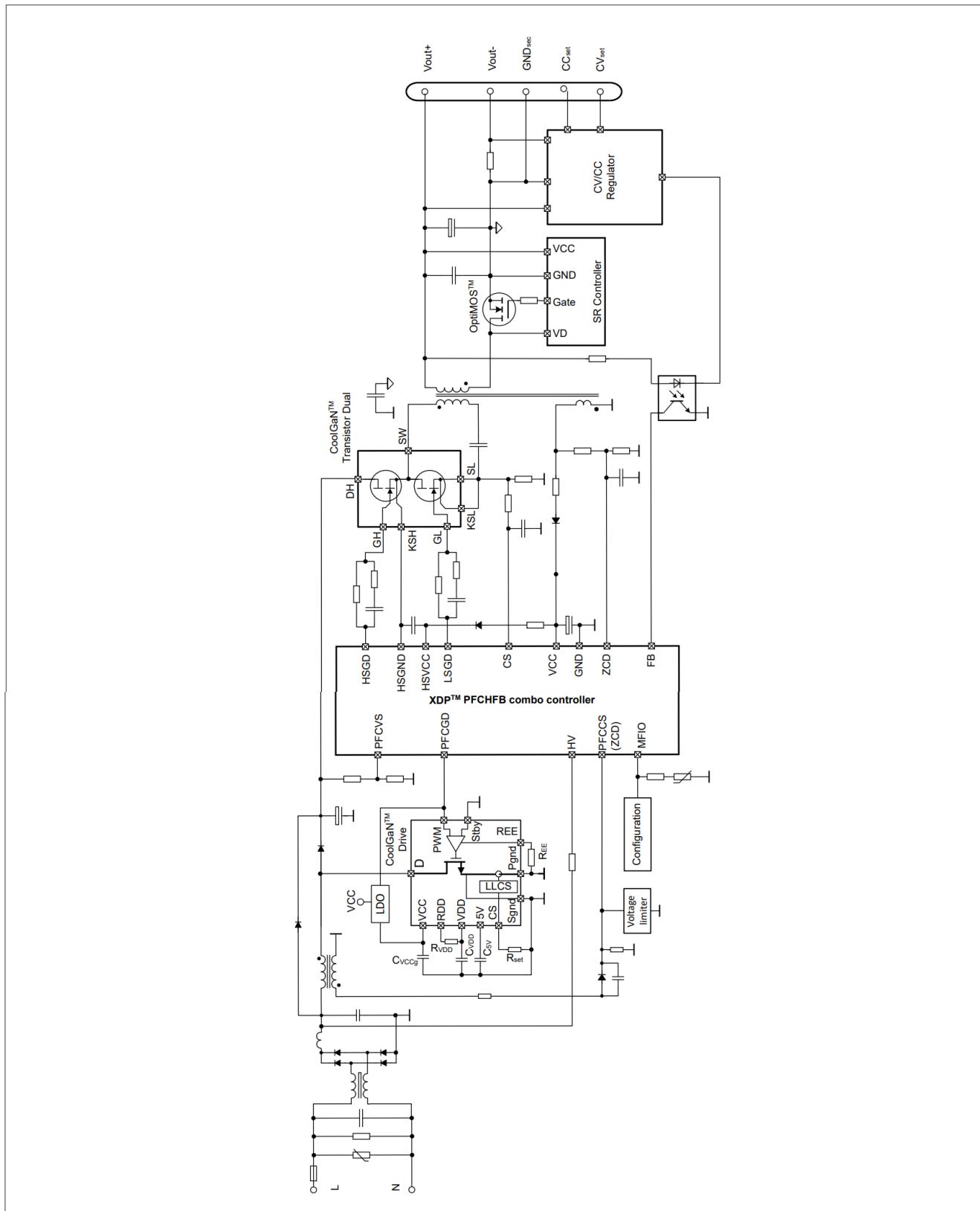

[图 3 至图 6](#) 展示使用 CoolGaN<sup>TM</sup>晶体管的潜在应用示意图， CoolGaN<sup>TM</sup> Transistor Dual、 CoolGaN<sup>TM</sup>Drive 和 OptiMOS<sup>TM</sup>晶体管可在 USB PD 和电池充电器应用中实现最高效率和功率密度。

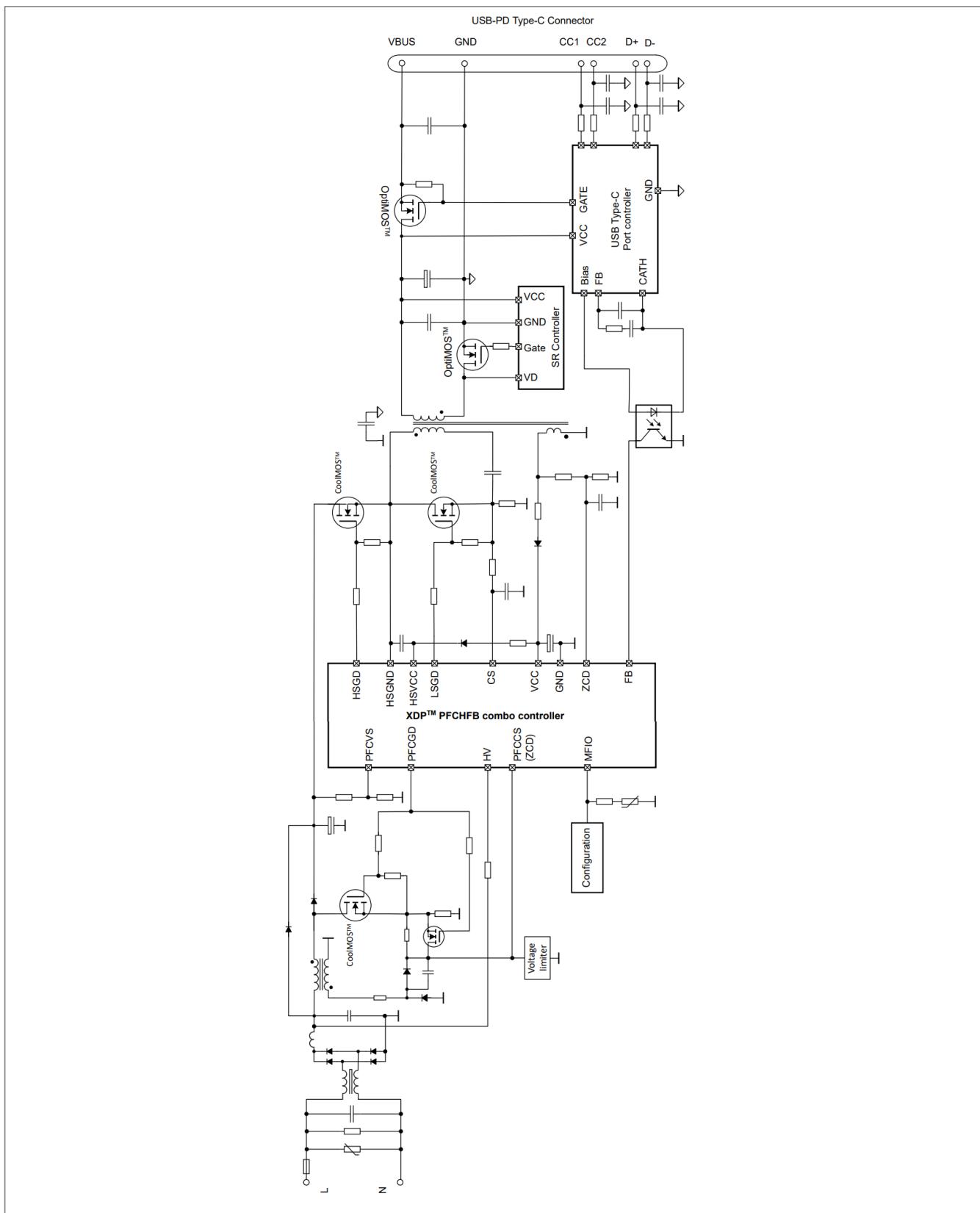

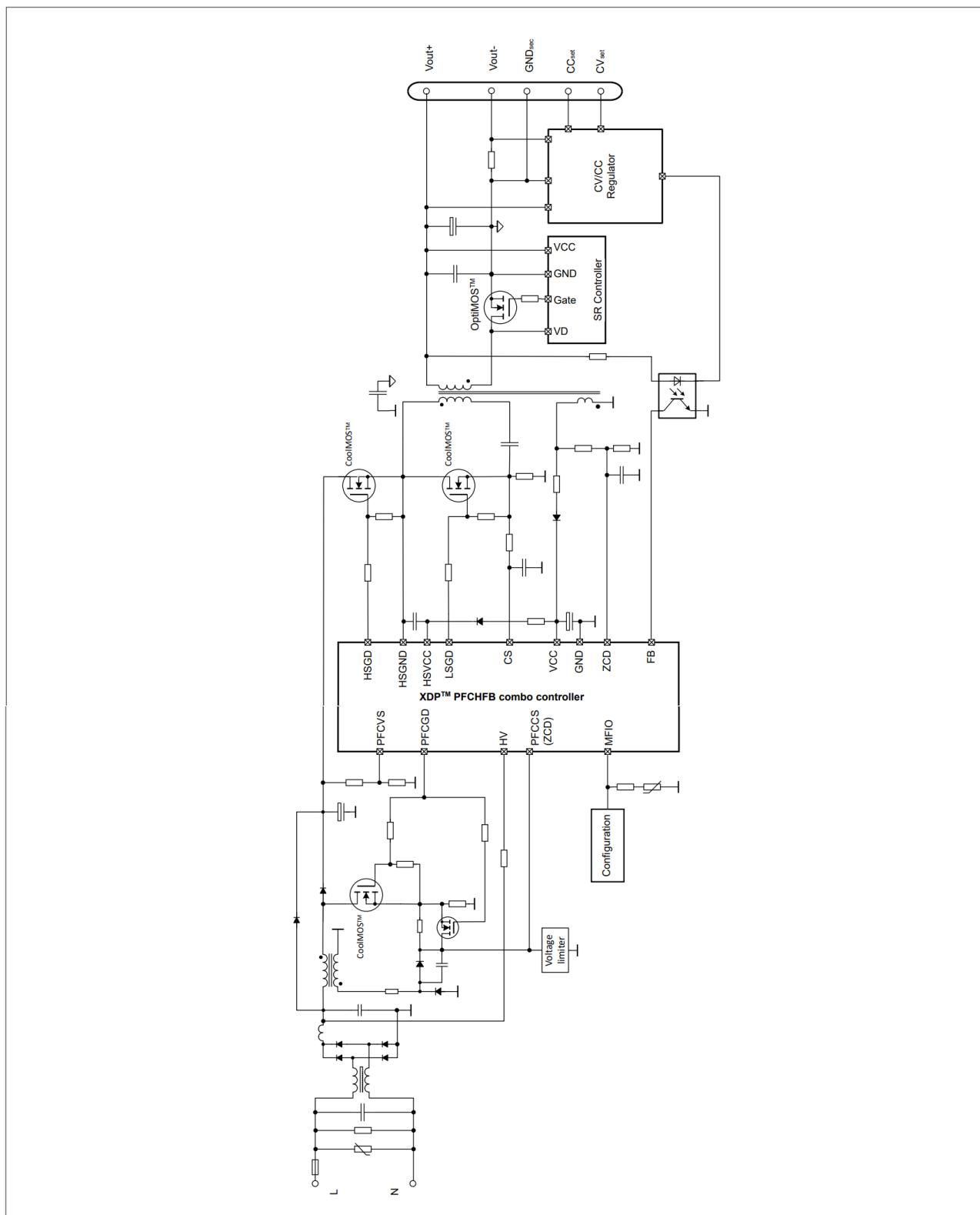

[图 7 和图8](#) 展示在USB PD 和电池充电器应用中使用 CoolMOS<sup>TM</sup> 和 OptiMOS<sup>TM</sup>晶体管的潜在应用示意图。

Figure 3

Typical USB PD application in combination with CoolGaN™ Transistor Single and CoolGaN™ Transistor Dual

Figure 4

Typical USB PD application in combination with CoolGaN™ Drive and CoolGaN™ transistor Dual

Datasheet

Figure 5 Typical battery charger application in combination with CoolGaN™ Transistor single and CoolGaN™ Transistor Dual

Figure 6

Typical battery charger application in combination with CoolGaN™ Drive and CoolGaN™ Transistor Dual

Figure 7

Typical USB PD application in combination with CoolMOS™ transistors

Figure 8

Typical battery charger application with CoolMOS™

## 4 Functional description

## 4 功能说明

### 4.1 VCC电源和高压启动单元管理

VCC 电源管理确保 IC 运行可靠且稳定。根据控制IC的工作模式不同，电源管理单元对VCC的供电方式也不同，详见下文。

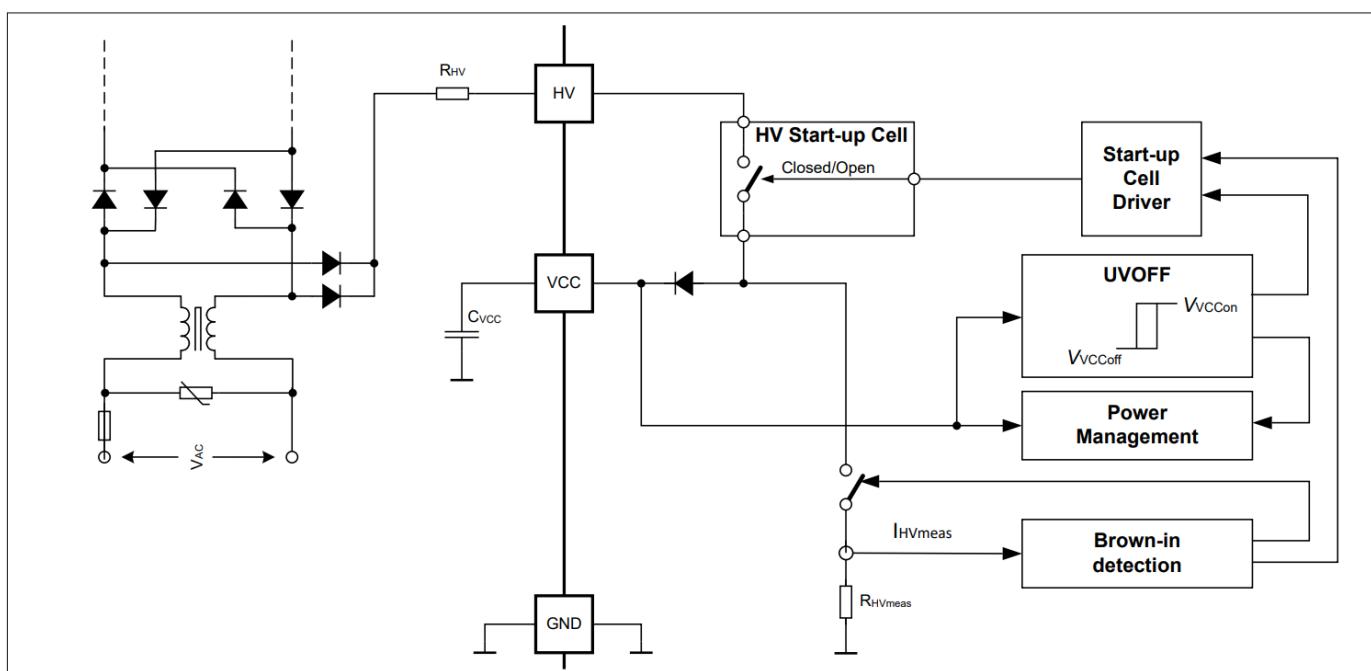

#### 4.1.1 VCC 电容充电和启动序列

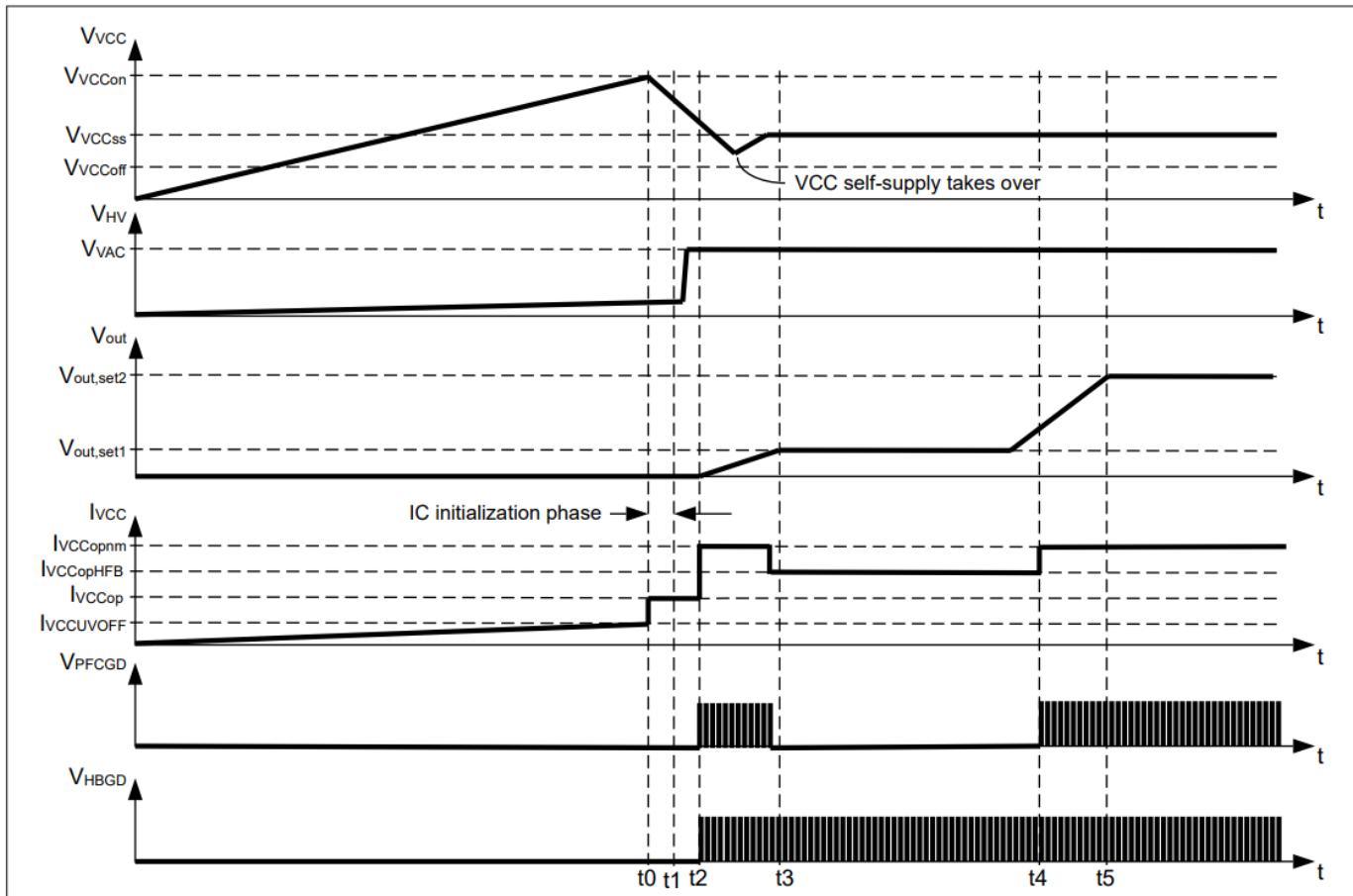

在 VCC 启动时，电容器  $C_{VCC}$  由内部 HV 启动单元通过 HV 引脚充电(见 [图9](#))。当  $V_{VCC}$  低于 IC 停用电压阈值  $V_{VCCoff}$  时，内部高压启动单元开启。当 VCC 引脚电压在时间  $t_0$  超过阈值  $V_{VCCon}$  时，高压启动单元关闭，IC 开始工作 (见 [图 10](#) )。

在时间  $t_1$  时，IC 检查启动条件。

需要满足以下正确启动条件才能在时间  $t_2$  开始混合反激式操作（混合反激式开关由信号  $V_{HBGD}$  指示）：

1. 上电 (BI) 条件： $V_{in} > V_{inbi}$  且  $V_{bus} > V_{inbi}$  (参见 [章节 4.5.2.4](#))

2. 无输入过压： $V_{bus} < V_{busovp3}$  (参见 [章节 4.5.2.7](#))

3. 反馈信号在调节范围内： $V_{FB} > V_{FBMctrl}$

4. 当 MFIO 引脚配置为过温保护 (OTP) 时，不会出现过温情况： $R_{MFIO} > R_{MFIOOTPrel0}$  (参见 [章节 4.5.2.16](#))

如果在  $t_{HVbit0}$  时间段内满足上述条件，混合反激式拓扑将开始开关，外部 Vcc 自供电将接管 IC 的供电。如果在  $t_{HVbit0}$  时间段内未满足上述任一条件，则 IC 进入 Bang-Bang 模式 (参见 [第 4.1.2 章](#) )。

一旦满足启动条件，PFC 和混合反激式拓扑都会开始工作。然而，PFC 的运行取决于输入和输出条件。[图 10](#) 显示这样一种情况：由于所需的低总线电压，PFC 在时间  $t_3$  停止运行，并在时间  $t_4$  恢复运行，此时输出电压升高 ( $V_{out, set2} > V_{out, set1}$ ) 并且 HFB 控制器请求更高的总线电压。

图9 用于启动和电压检测的高压控制

## 4 Functional description

图10 典型的启动序列

## 4.1.2 上电阶段采用 Bang-bang 模式运行

为了支持在满足电压接入条件后立即快速激活，VCC 电压保持在高水平。启动检查阶段的 Bang-Bang 模式操作可确保较高的 VCC 电平。

例如，在发生掉电 (BO) 事件后，IC 会进入睡眠模式，降低电流消耗 I<sub>VCCBB</sub>。一旦交流电可用，高压启动单元就会启动，并将 VCC 电压充电至阈值 V<sub>VCCon</sub>。一旦 V<sub>VCC</sub> 达到 V<sub>VCCon</sub>，IC 便会启动掉电检测。如果交流输入电压足够高，IC 便会检测到掉电状态。

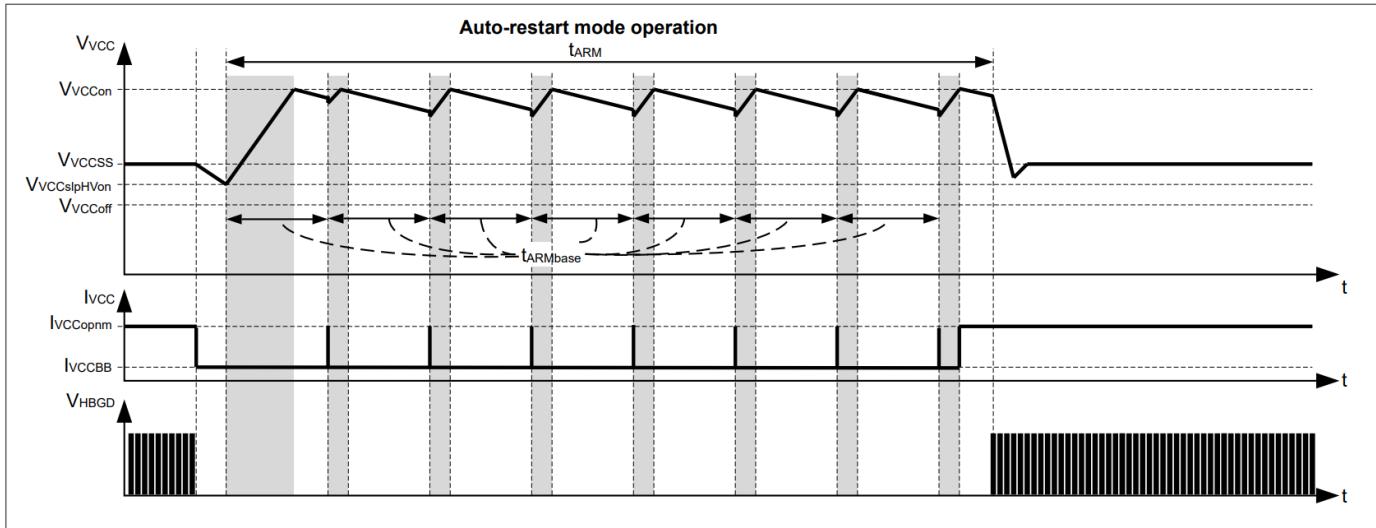

## 4.1.3 保护模式运行期间的 Bang-bang 模式

在自动重启操作中，高压启动单元会在一段时间 t<sub>ARMbase</sub> 后定期开启，并在达到 VCC 引脚电压阈值 V<sub>VCCon</sub> 时关闭。在此 Bang-Bang 模式操作期间，VCC 保持在高电平，以便在自动重启时间 t<sub>ARM</sub> 结束后支持正常的重启操作（参见图11）。

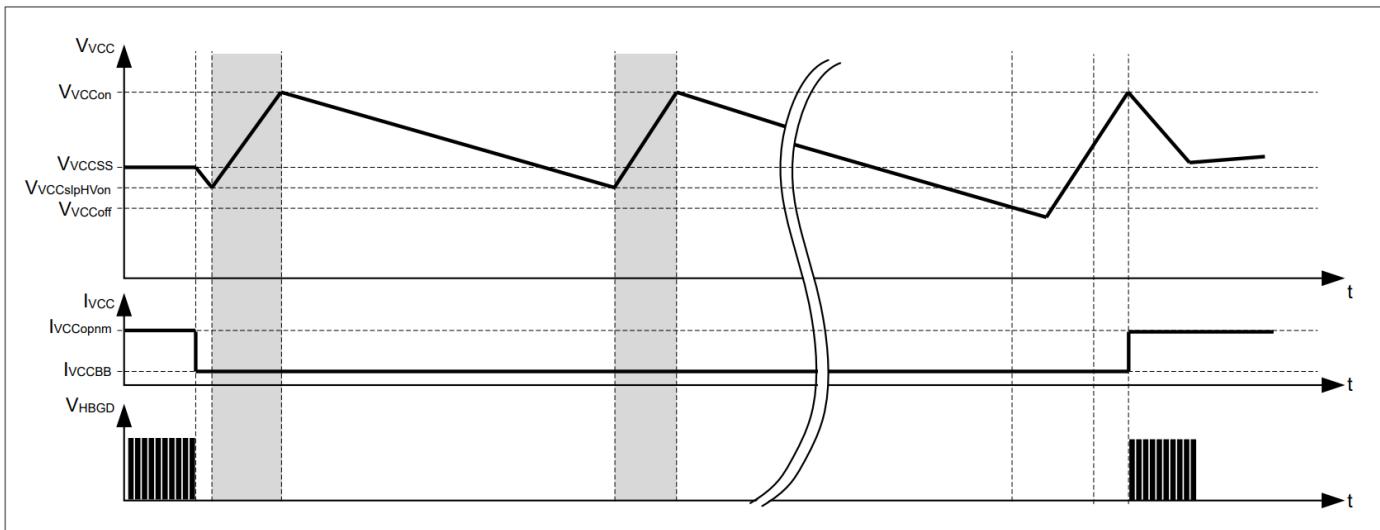

在锁存模式操作中，HV 启动单元在 VCC 引脚电压阈值 V<sub>VCCslpHVon</sub> 时开启，并在达到 VCC 引脚电压阈值 V<sub>VCCon</sub> 时关闭（见图 12）。只有当 VCC 电压降至阈值 V<sub>VCCoff</sub> 以下时才能实现复位，例如，断开交流线路。

## 4 Functional description

图 11 自动重启模式操作

图 12 锁存模式操作

## 4.1.4 突发模式操作期间的 VCC 电源

在突发模式 (BM) 操作期间，IC 反复进入省电模式，在此模式下 IC 电流消耗降低至  $I_{VCCBMPsm0}$

如果在 BM 工作期间 VCC 电压降至阈值  $V_{VCCslpHVon}$  以下，则 HV 启动单元将被激活，为 VCC 电容充电。需要特别注意 Vcc 的自供电，以避免 BM 期间启动单元激活导致待机功耗过高。

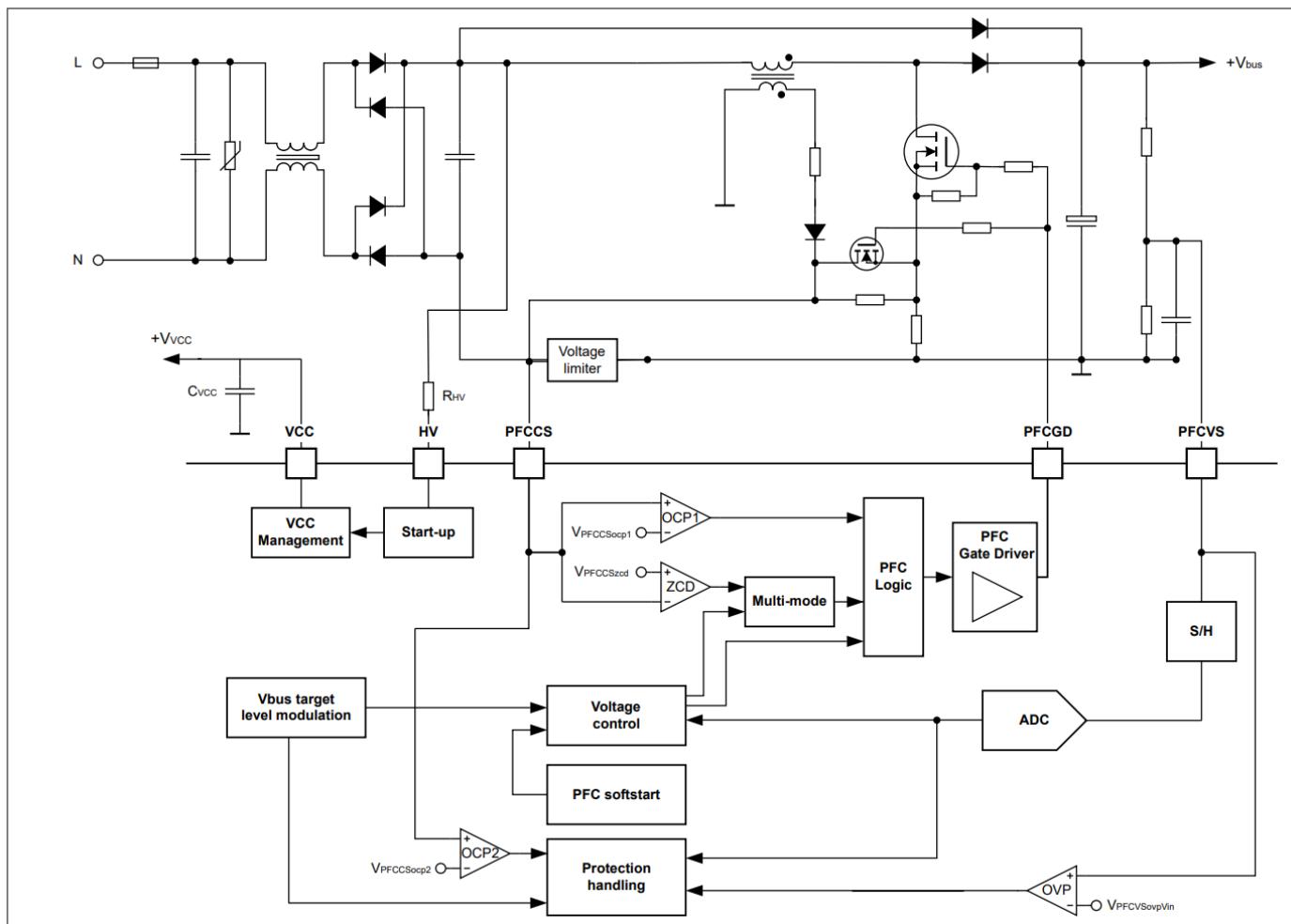

## 4.2 PFC 控制

PFC 控制器控制 PFC 栅极驱动器 PFCGD 的开启和关闭，以维持所需的总线电压  $V_{bus}$ ，同时交流输入电流  $I_{AC}$  跟随瞬时线路输入电压  $V_{AC}$ ，从而实现高功率因数和低谐波含量。该工作模式基于准谐振模式 (QRM)，即临界导通模式，具有谷底开关和谷底跳跃功能。电感电流退磁后，开关电压  $V_{PFC,ds}$  的振荡通过集成过零检测 (ZCD) 机制进行检测。ZCD 功能与引脚 PFCCS 处的 PFC 电流限制相结合。[图 13](#) 显示了包括 IC 的 AC 输入级和 PFC 控制部分的 PFC 电路布置。

## 4 Functional description

图 13 PFC 电路布置和相关的 PFC 控制

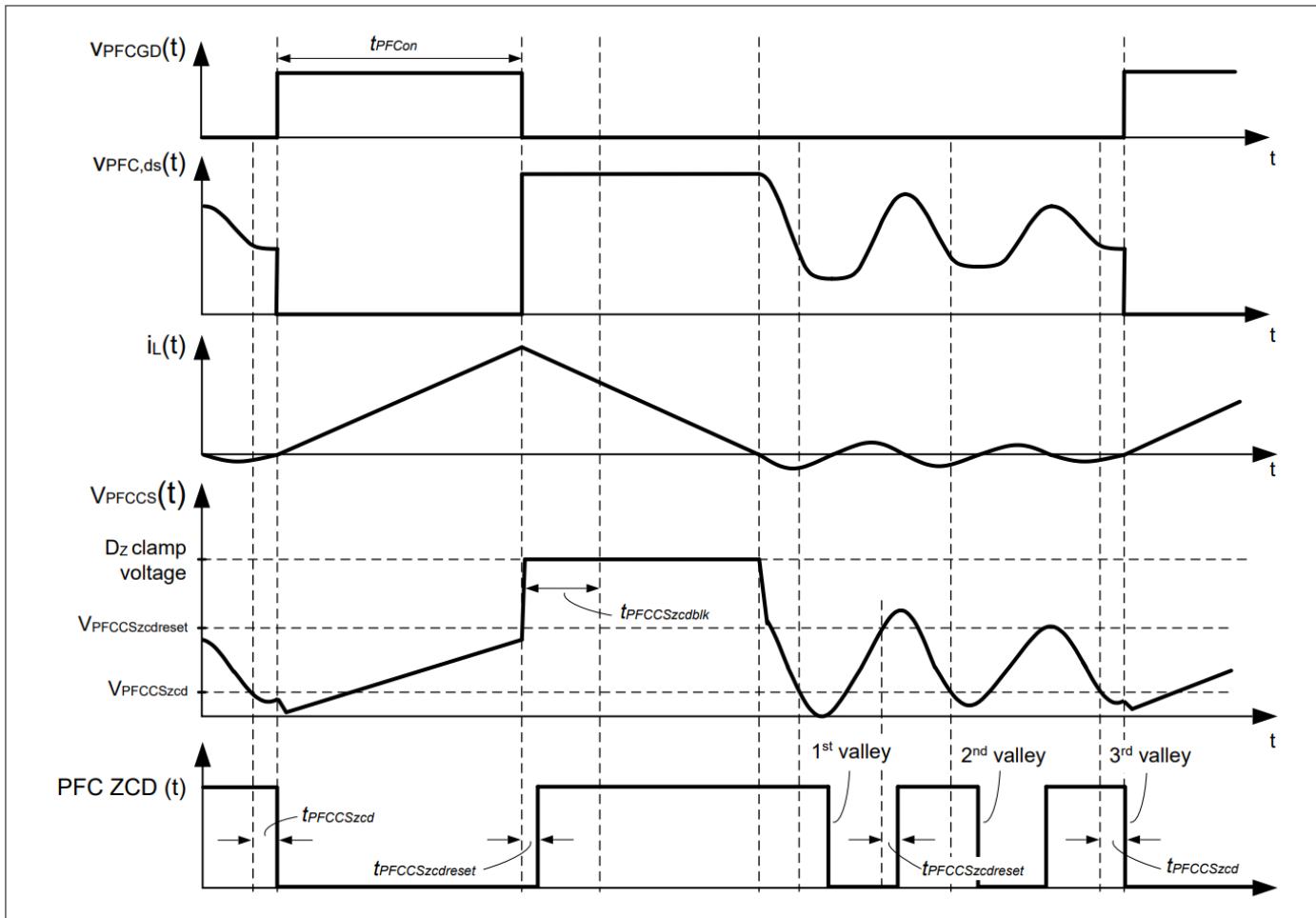

PFC控制器工作在准谐振模式，采用谷底开关。典型波形如图 14 所示。在所示情况下，PFC 在第三个谷底打开。

## 4 Functional description

图 14 PFC 开关周期，晶体管在第三个谷底导通 (QRM3)

## 4.2.1 组合 PFC 电流限制和过零检测

PFC 级在引脚 PFCCS 处使用电流检测 (CS) 和过零检测 (ZCD) 功能。在 PFC 栅极驱动器导通期间，该引脚用作 PFC 峰值电流限制的 CS；而在栅极驱动器关断期间，该引脚用作谷底开关的过零检测器。[图 13](#) 显示了 ZCD 和 CS 的相关电路。

谷值检测需要了解 PFC 开关漏极和源极端子两端电压振荡的信息。[图 13](#) 展示了一种方案，该方案将外部电路连接到耦合到 PFC 电感的辅助绕组。控制 IC 内部采用一个迟滞比较器进行过零检测，该比较器的上升沿阈值为  $V_{PFCCSzcdreset}$ ，下降沿阈值为  $V_{PFCCSzcd}$ 。仅当 PFC 栅极关断后电压  $V_{PFCCS}$  高于上限阈值  $V_{PFCCSzcdreset}$  的时间超过滤波器和延迟时间  $t_{PFCCSzcdreset}$ ，然后降至低于阈值  $V_{PFCCSzcd}$  的持续时间超过时间  $t_{PFCCSzcd}$  时，才会检测到 ZCD 事件。一旦达到目标阈值，栅极驱动器输出 PFCGD 将立即升高。为了抑制开关引起的振铃，在 PFGGD 下降沿之后， $V_{PFCCS}$  信号将在  $t_{PFCCSzcdblk}$  时间内消隐。[图 14](#) 说明了这种零交叉检测机制。

PFC 栅极驱动器导通期间，分流电阻  $R_{sPFC}$  处测得的电压用于限制 PFC 峰值电流。一旦 PFCCS 引脚电压超过阈值  $V_{PFCCSocp}$  且持续时间超过消隐时间  $t_{PFCCSocp}$ ，PFC 栅极 PFCGD 就会关闭。

如果采用具有过流保护功能的GaN器件作为PFC开关，PFC扼流圈电流将受到GaN器件的限制，并且PFC开关将自动关闭。但该电流限制并不直接反馈给 IC，因此 PFC 栅极信号仍然由 PFC 定时器控制，并且引脚 PFCCS 用作 PFC 谷值控制的 ZCD。

## 4 Functional description

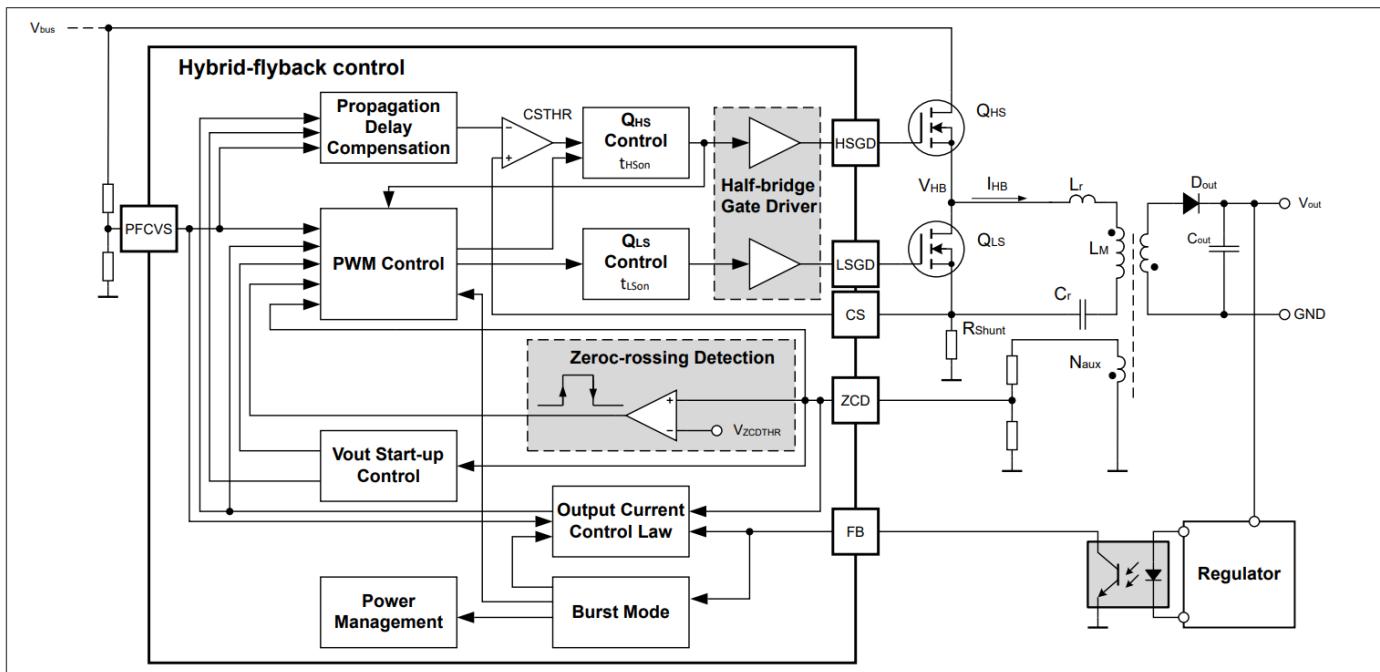

### 4.2.2 多模式操作和频率规律

PFC 控制器提供多种操作模式。从满载到空载，使用多种操作模式来优化效率和 EMI 行为。

PFC 转换器用于模拟交流输入的阻性负载  $R_e = V_{AC,RMS} / I_{AC,RMS}$ 。PFC 总线电压控制器的输出，即所需的 PFC 栅极导通时间  $t_{PFCon,des}$ ，与模拟阻性负载  $R_e$  成反比。因此， $t_{PFCon,des}$  随交流线路电压幅值的变化而变化，并与 RMS 输入电流  $I_{AC,RMS}$  成正比。

图 15 所示的频率规律表示在  $t_{PFCon,des}$  或  $I_{AC,RMS}$  范围内的完整工作模式。虽然开关频率在每个开关周期内都被限制在  $f_{swPFCmin}$  的最小值和  $f_{swPFCmax}$  的最大值之间，但 QRM 中的工作频率通常在  $f_{swQRmin}$  和  $f_{swQRmax}$  的范围内调节。一旦 PFC 开关频率超出  $f_{swQRmin}$  和  $f_{swQRmax}$  的范围，且持续时间超过给定的消隐时间  $t_{QRblkinc}$  和  $t_{QRblkdec}$ ，则目标谷值会发生变化，使开关频率回到该范围内（参见章节 4.2.2.1）。

图15 PFC频率规律

#### 4.2.2.1 准谐振模式

在准谐振模式 (QRM) 操作中，PFC 开关在退磁后开关漏源电压处出现的振荡谷中打开。QRM 操作减少了 PFC 晶体管的开关损耗并确保了 PFC 转换器的最高效率。

在 QR1 操作中，使用第一个谷底。一旦检测到第一个 ZCD 事件，晶体管就会打开。

随着负载减小或输入电压升高，PFC 开关频率会升高。一旦达到最大值  $f_{swQRmax}$ ，谷值数就会增加。另一方面，随着负载增大或输入电压降低，PFC 开关频率会降低。一旦达到最小值  $f_{swQRmin}$ ，谷值数就会减少。

然而，为了防止每个交流半周期内的谷值数量发生变化，需要使用谷值变化消隐时间  $t_{QRblkinc}$  和  $t_{QRblkdec}$ 。为了确保在 PFCCS 信号幅度变得太小之前进行正确的 ZCD 检测，仅支持第 1 个谷值 (QR1) 到定义的第  $n^{th}$  谷值  $N_{PFCvalleymax}$ 。

在 QR 谷值振荡期间，PFC 开关和 PFC 二极管均未导通，这会导致一些交流输入电流波形失真，并影响 PFC THD 性能。多模式 PFC 控制器采用逐周期导通时间优化来确保良好的输入电流整形并改善 PFC THD 性能。

## 4 Functional description

### 4.2.2.2 低功耗模式

在软启动和稳定运行中，只要总线电压控制器确定的导通时间  $t_{PFCon,des}$  小于某个值  $t_{PFConskip}$ ，就会跳过开关脉冲，并下拉 PFC 栅极驱动器。该值  $t_{PFConskip}$  经过调节以获得最佳性能。

在低输出负载下，组合控制器 IC 进入突发模式。PFC 突发模式操作与混合反激突发模式操作同步。

### 4.2.3 PFC 总线电压感测和调节

控制器通过引脚 PFCVS 感测 PFC 总线电压  $V_{bus}$ 。总线电压由非线性 PIT1 控制器调节，该控制器根据感测到的电压计算所需的导通时间  $t_{PFCon,des}$

从调节器计算出的 PFC 导通时间  $t_{PFCon,des}$  在应用于 PFCGD 之前被钳制在最小值  $t_{PFConmin}$  和最大值  $t_{PFConmax}$  之间。

PFC 目标总线电压和总线电压欠压保护水平  $V_{busUVP}$  由控制器动态设置。当总线电压  $V_{bus}$  下降并接近  $V_{busUVP}$  时，控制器会做出反应，将导通时间延长至最大导通时间  $t_{PFConmax}$ ，以便更快地提升总线电压。

该控制器对交流电和负载瞬变实施前馈补偿，以确保严格调节总线电压并降低大容量电容器的值。

### 4.2.4 PFC 总线电压目标设置

与传统的 PFC 升压转换器相比，总线电压目标电压  $V_{bustarget}$  并非固定不变，而是会随着工作条件的变化而变化。一方面，混合反激式级根据输出电压  $V_{out}$  请求特定的总线电压目标电压；另一方面，PFC 稳压器可以根据交流峰值电压设定目标总线电压电平。此功能将在 [章节4.4.3](#) 中更详细地介绍。

### 4.2.5 PFC 软启动

每次启用 PFC 时，PFC 都会启动软启动，以最大限度地降低 PFC 开关、二极管和电感的开关应力，并尽可能避免 CCM 工作。软启动期间，PFC 工作在 QR1 模式。一旦总线电压达到其目标值  $V_{bustarget}$  的 93.75%，软启动就会结束。初始导通时间可根据交流线路 RMS 值进行调整，具体取决于参数  $CFG_{PFContime}$  的设置。

### 4.2.6 PFC 栅极驱动器

控制器中集成了一个 PFC 栅极驱动器，其输出为引脚 PFCGD。为了驱动分立的 GaN-HEMT 器件，可能需要专用的外部 RC 网络。

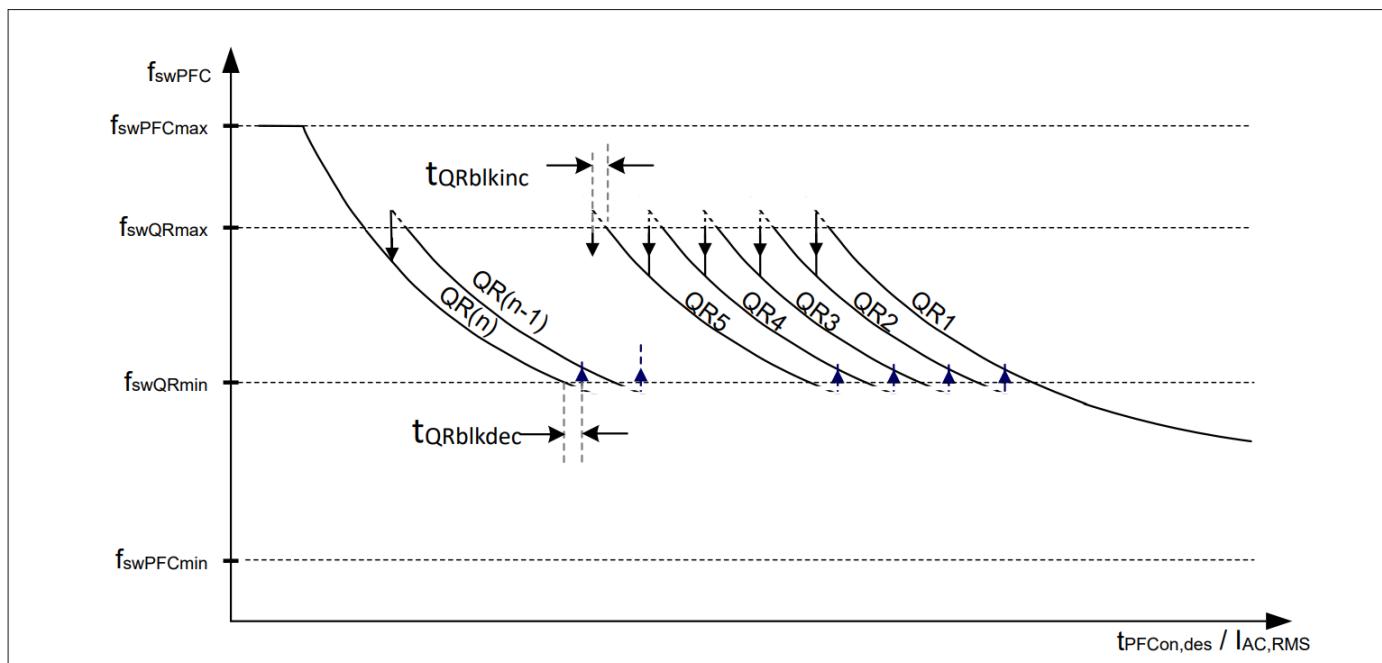

## 4.3 混合反激式控制

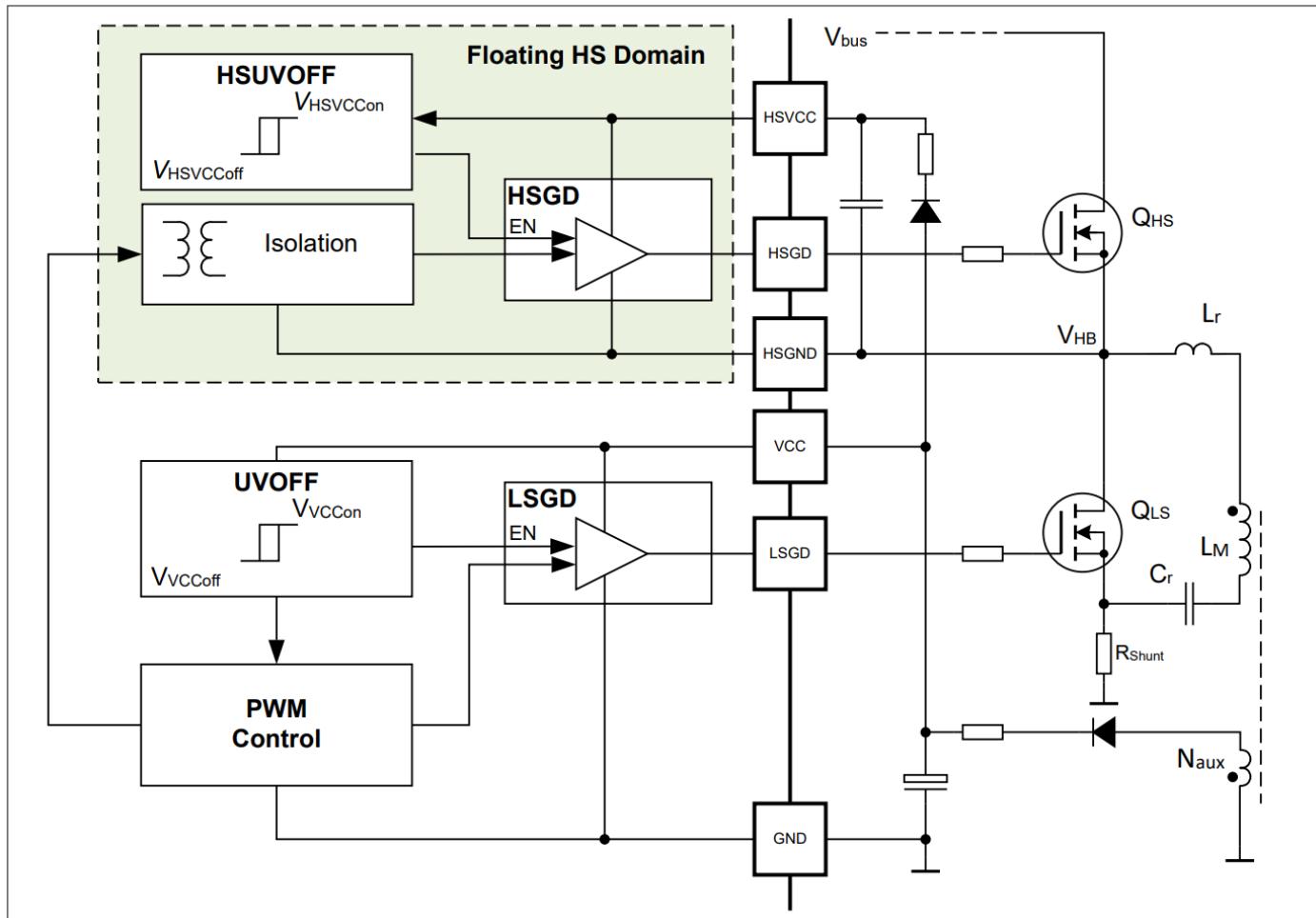

混合反激式转换器基于谐振不对称半桥拓扑结构，结合了正激式转换器和反激式转换器的优点。[图 16](#) 显示了混合反激式级及其相关控制块。

利用该控制器，混合反激功率级可以在正常运行下通过适当的系统设计实现初级侧的零电压开关 (ZVS) 操作和次级侧的零电流开关 (ZCS) 操作。为了实现 ZVS 操作和最佳效率，实施了两种控制方法：

- 连续谐振模式 (CRM) 操作

- 零电压谐振谷底开关 (ZV-RVS) 操作

## 4 Functional description

图 16 混合反激电路布置及相关控制块

输出电流控制使用 CTHR 比较器在高端开关导通时间  $t_{HSon}$  期间进行峰值电流控制。

### 4.3.1 PWM控制方案

在下一章中，我们将讨论不同控制模式的脉冲宽度调制（PWM）控制方法以及相关的模式转换。根据负载、输出电压和总线电压，调整控制方案以确保低侧（LS）和高侧（HS）开关的 ZVS 操作。

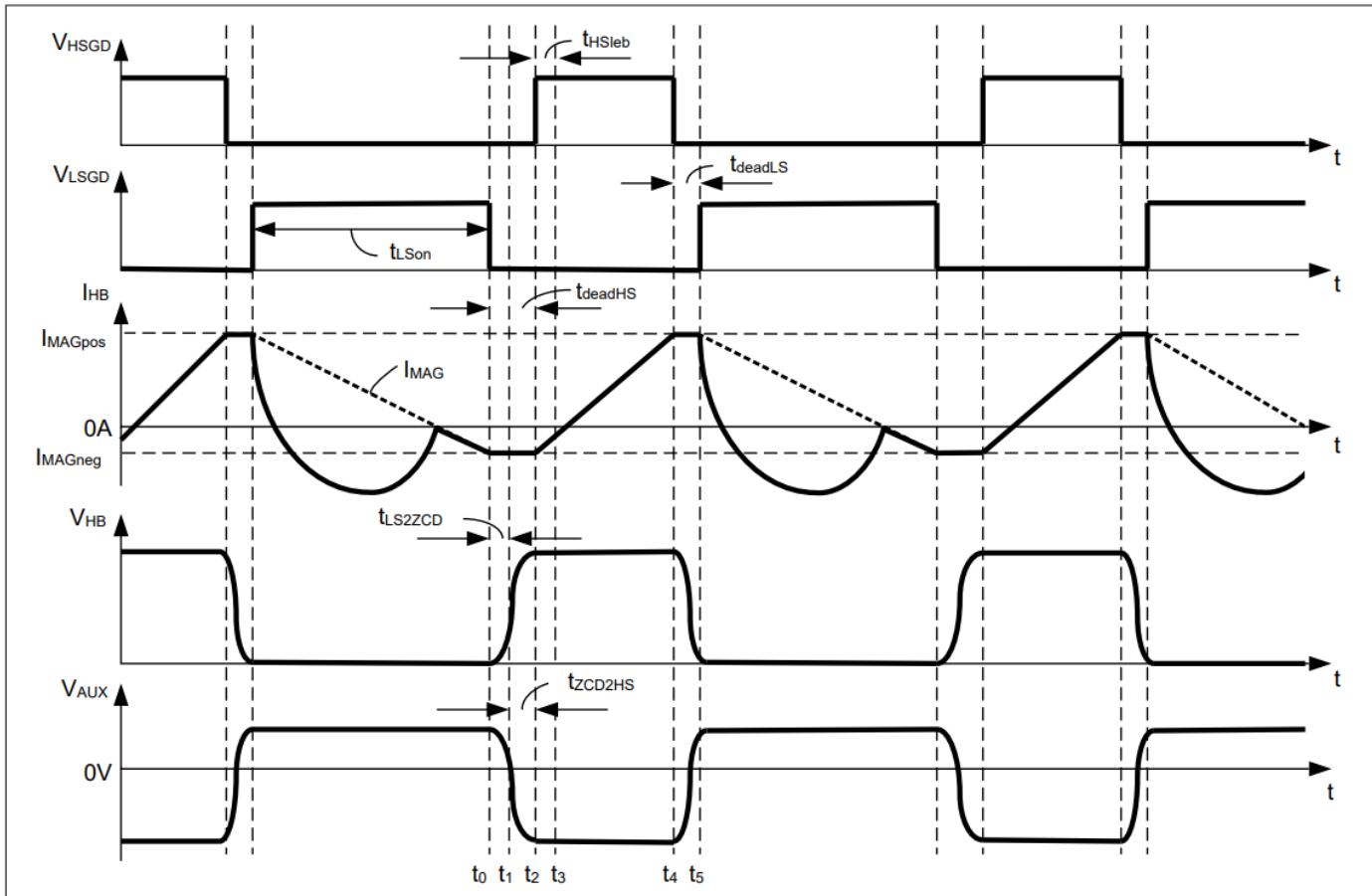

#### 4.3.1.1 连续谐振模式控制方案

在连续谐振模式（CRM）下，HS 开关和 LS 开关的切换以具有短死区时间的连续交替方式：在 HS 开关导通之前施加  $t_{deadHS}$ ，在 LS 开关导通之前施加  $t_{deadLS}$ 。

它通过调节负电流水平  $I_{MAGneg}$  来实现每个半桥开关周期的 ZVS 操作。

如图17所示显示了典型波形。由于峰值电流足够高，可以为 LS 开关提供适当的 ZVS 操作，因此 HS 和 LS 开关之间的死区时间  $t_{deadLS}$  是固定的。

在 CRM 操作中，死区时间  $t_{deadHS}$  由两个时间间隔组成：

$$t_{deadHS}(CRM) = t_{LS2ZCD} + t_{ZCD2HS}$$

#### 公式 1

LS 导通时间根据参数  $t_{TRANSnom}$ 、 $I_{MAGnegNom\%}$ 、 $t_{TRANSRV50\%}$  和在 ZCD 引脚处感测到的  $V_{out}$  逐周期进行调整，而  $t_{LS2ZCD}$  对于 LS 导通时间确定起着从属作用，但用于确保 ZCD 事件后 HS 导通。

时间段  $t_{ZCD2HS}(t_2 - t_1)$  会延迟  $t_2$  时刻的 HS 开关导通，以实现 HS 开关的 ZVS。

当死区时间  $t_{deadHS}$  (CRM) 结束或开关周期达到最小开关频率  $f_{swDCMmin}$  定义的值时，HS 开关被激活。

高速开关激活后，峰值电流控制决定高速开关的导通时间。磁化电流可在前沿尖峰消隐期  $t_{HSleb}$  后测量。此时  $t_{HSleb}$  决定了高速开关工作的最小导通时间。

## 4 Functional description

图 17 CRM 操作的半桥时序

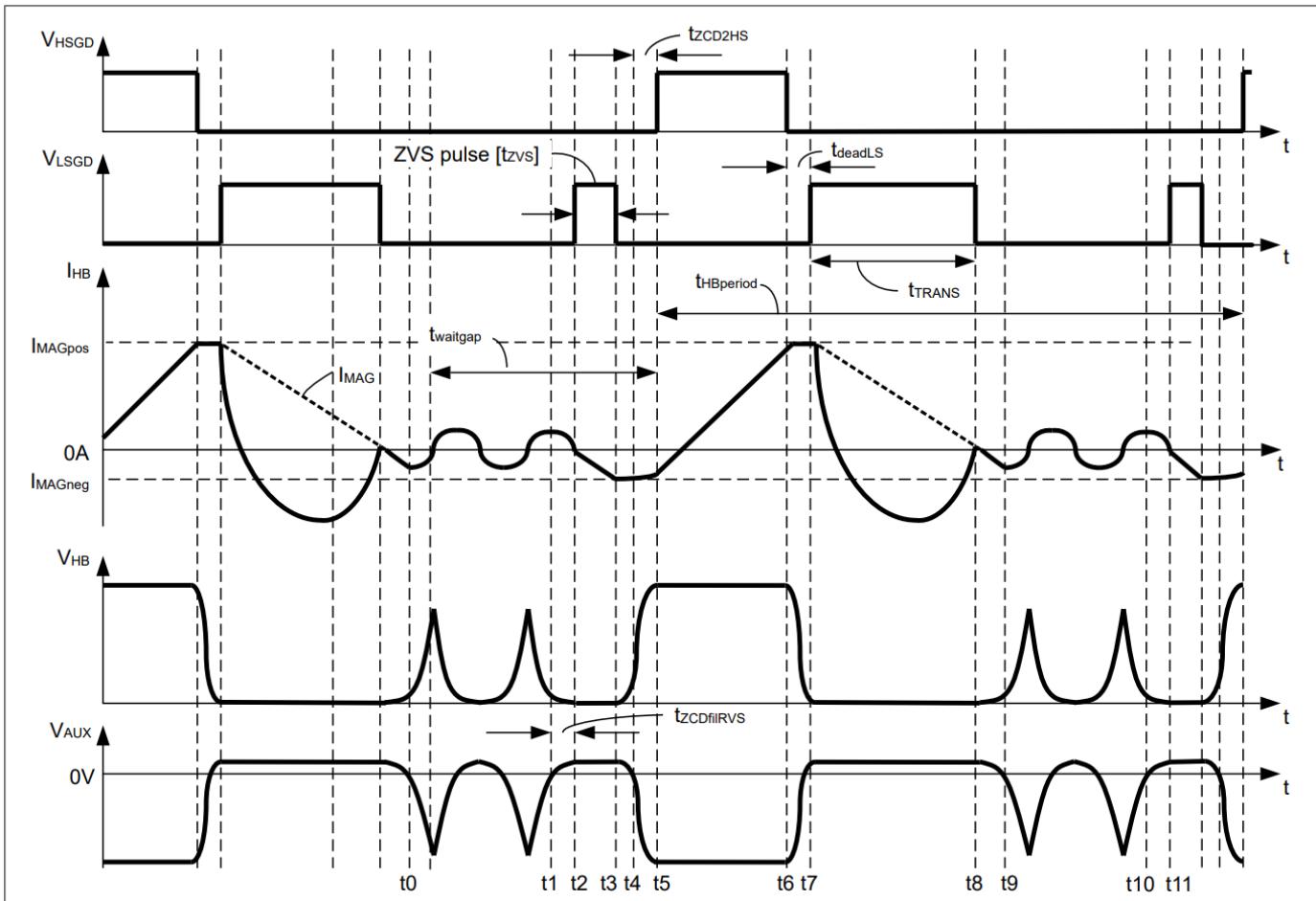

## 4.3.1.2 零电压谐振谷底开关模式控制方案

随着负载的降低，CRM 模式工作通常会导致较高的环流。此外，随着  $V_{out}$  的降低，退磁时间会变得比谐振时间的一半长得多。

周期由  $L_r$  和  $C_r$  决定，这可能导致进一步的谐振半桥振荡。在电流流过次级侧时关闭 LS 开关可能会导致次级整流器两端出现电压尖峰。

为了克服这些问题，我们采用了零电压谐振谷底开关 (ZV-RVS) 模式。该模式可将峰值磁化电流保持在所需范围内，同时保持高速开关和低速开关的软开关功能。通过降低开关频率并进行谷底同步，可以降低负载。[图 18](#) 显示了在第二个谷底运行时的典型波形。

在 ZV-RVS 模式下，每个 HFB 周期由两个 LS 脉冲、一个 HS 脉冲和一个等待时间  $t_{waitgap}$  组成。第一个 LS 脉冲 (ZVS 脉冲) 与谷底同步，因此 LS 开关在其漏源电压谷底和零磁化电流处导通。该脉冲引入一个小的负电流，确保后续 HS 开关导通时保持 ZVS 状态。

所需的 ZVS 脉冲宽度  $t_{ZVS}$  由目标负磁化水平  $I_{MAGneg}$ 、变压器磁化电感  $L_m$  和输出电压  $V_{out}$  决定。最小 ZVS 脉冲宽度发生在最低输入电压和最高输出电压时。此外，还存在一个下限  $t_{ZVSmin}$ 。

在 ZV-RVS 模式工作中，会插入等待时间  $t_{waitgap}$ 。在此等待时间内，会发生续流振荡，并由引脚 ZCD 和比较器感测。

输出电压控制是通过选择适当的谷值（因此适当的  $t_{waitgap}$ ）并在所需范围内调整 HS 导通时间（因此磁化峰值电流）来实现的。

## 4 Functional description

图 18 在 ZV-RVS 模式下运行的混合反激式

## 4.3.1.3 谷底跳跃控制

在 ZV-RVS 模式下工作时，会进行谷底检测以确定 ZVS 脉冲的开启时间。等待时间  $t_{waitgap}$  根据检测到的谷底目标数量进行控制。如果无法检测到目标谷底，则将改为控制开关频率。

## 4.3.1.4 CRM 和 ZV-RVS 之间的模式转换

模式转换控制基于目标峰值电流  $I_{MAGpos}$  和在 ZCD 引脚。首先，只有当通过 ZCD 感测到的输出电压达到特定值时，才有可能从 CRM 模式切换到 ZV-RVS 模式，反之亦然。只有当检测到的输出电压大于  $V_{outRVS2CRM}$  时，才有可能从 ZV-RVS 切换到 CRM（为了产生一定的滞后，只有当输出电压小于  $V_{outCRM2RVS}$  时，才会从 CRM 切换回 ZV-RVS）。其次，反馈信号  $V_{FB}$  决定内部电流设定点  $I_{SET}$ ，并与内部阈值进行比较以进行切换。

## 4.3.2 输出控制

HFB 控制器的目标是输出电流与反馈电压水平成比例。

在 CRM 模式下，假设系统理想，则以下公式适用于输出电流：

$$I_{out} = \frac{P_{out}}{V_{out}} = \frac{1}{2} \cdot N \cdot (I_{MAGpos} + I_{MAGneg})$$

## 公式 2

## 4 Functional description

与 CRM 工作模式相比，ZV-RVS 模式增加了等待时间间隔  $t_{waitgap}$ ，在此期间不发生能量传输。平均输出电流  $I_{out}$  随  $t_{waitgap}$  的增加而减小，公式如下：

$$I_{out} = \frac{P_{out}}{V_{out}} = \frac{t_{HBperiod} - t_{waitgap}}{t_{HBperiod}} \cdot \frac{1}{2} \cdot N \cdot (I_{MAGpos} + I_{MAGneg})$$

### 公式 3

输出电流主要通过调节正磁化电流水平  $I_{MAGpos}$  来调节。在 CRM 工作模式下，输出电流  $I_{out}$  由 FB 引脚反馈电压与相关内部电流设定点  $I_{SET}$  之间的线性关系控制，该关系将在 [章节 4.3.2.1](#) 中进行描述。调制负电流  $I_{MAGneg}$ ，实现 HS 的 ZVS。

输出电压通过辅助绕组的 ZCD 引脚测量并在控制器 IC 内部进行滤波，结果用于保护功能，进行补偿以确保 ZVS 在宽输出电压范围内运行。

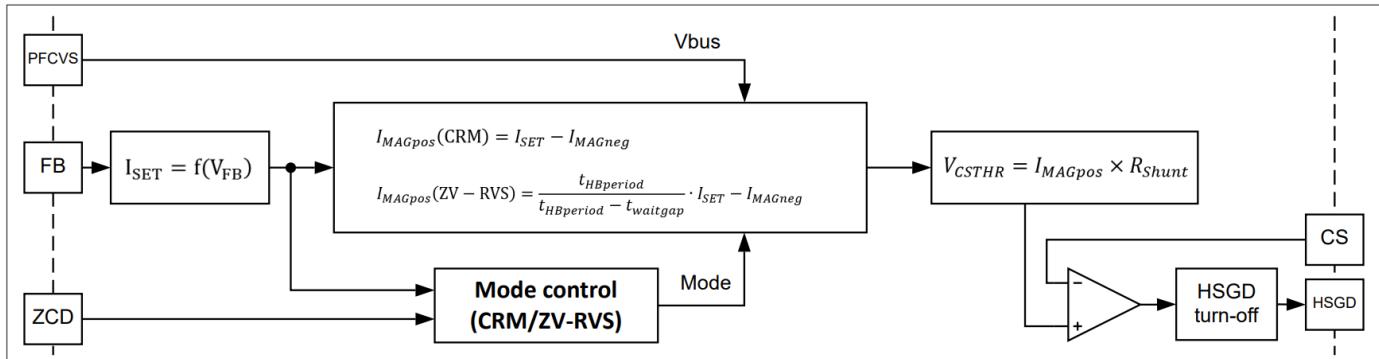

#### 4.3.2.1 输出电流控制法则

正磁化水平  $I_{MAGpos}$  通过将分流电阻  $R_{shunt}$  中的电压与内部值进行比较来控制：

$$V_{CSpeak} = I_{MAGpos} \cdot R_{Shunt}$$

### 公式 4

峰值电流调节容易因噪声而产生误差。与 CS 引脚相关的 PCB 设计应考虑这一敏感性。建议在 CS 引脚处使用外部 RC 滤波器。此外，可以设置一个滤波时间为  $t_{CSTHRfil}$  的数字滤波器来消隐 CSTHR 比较器事件。

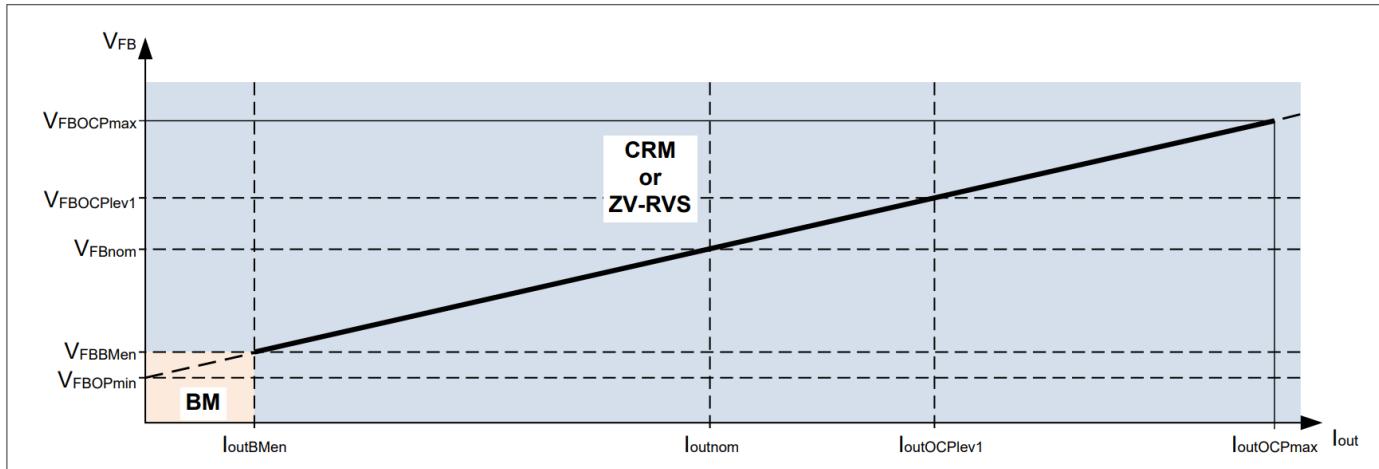

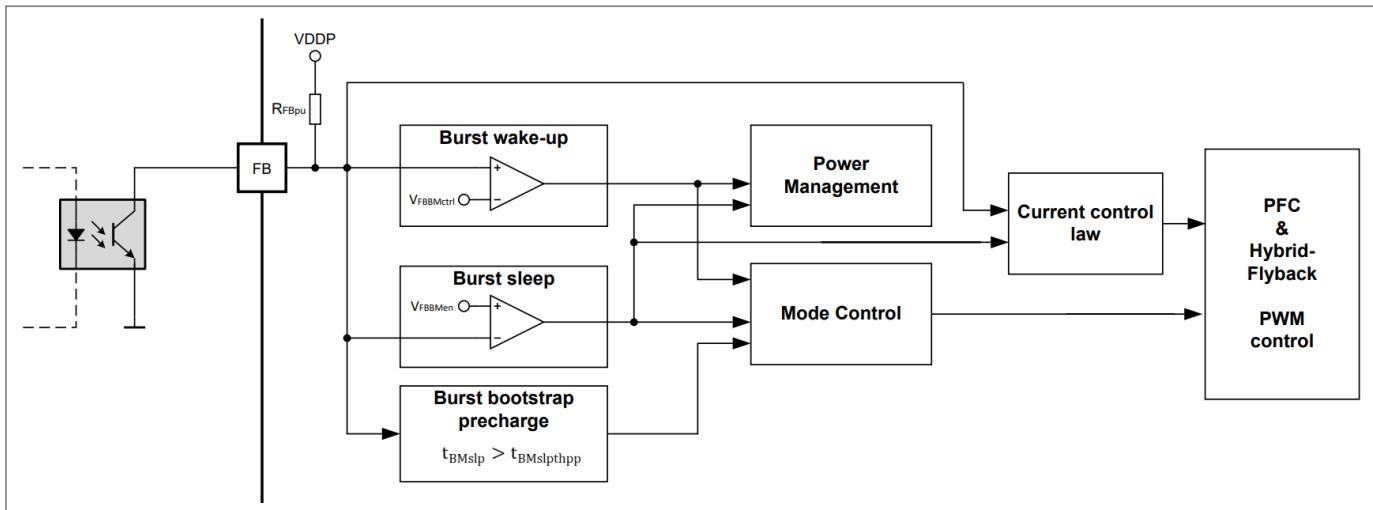

[图 19](#) 中显示了从 FB 引脚的反馈信号输入到 CS 引脚的峰值电流设置的控制路径。请求的输出电流等于相应反馈信号的内部  $I_{SET}$  值。然后，根据  $V_{bus}$  测量值和工作模式计算所需的峰值电流设置。

图 19 从反馈输入到峰值电流设置的控制路径

反馈引脚带有一个上拉电阻  $R_{FBpu}$ ，连接至内部参考电压 ( $V_{FB0c}$ )。反馈电压  $V_{FB}$  与输出电流  $I_{out}$  呈线性关系，介于突发模式进入电流水平和  $I_{outBMen}$  和最大输出电流  $I_{outOCPmax}$ 。[图 20](#) 显示输出电流和反馈电压之间的关系。

## 4 Functional description

图20 FB引脚反馈电压控制规律

输出电流  $I_{out}$  由等效内部电流设定点  $I_{SET}$  表示，该设定点随后映射到正磁化水平  $I_{MAGpos}$ 。峰值电流  $I_{MAGpos}$  由引脚 CS 处的可变阈值比较器控制。在 CRM 和 ZV-RVS 模式下， $I_{SET}$  和  $I_{MAGpos}$  之间的关系有所不同。

## 4.3.2.2 保持 ZVS 操作以适应较宽的 Vbus 电压范围

CRM 中的 ZVS 操作在 [章节 4.3.1.1](#)。在 ZV-RVS 中，ZVS 脉冲长度以负电流  $I_{MAGneg}$  为目标进行设置，如 [章节 4.3.1.2](#) 所述。此处， $I_{MAGnegnom}$  为最小负电流。对于其他母线电压等级，负磁化电流自动调整，实现零电压开关。

## 4.3.2.3 保持 ZVS 操作以实现宽输出电压范围

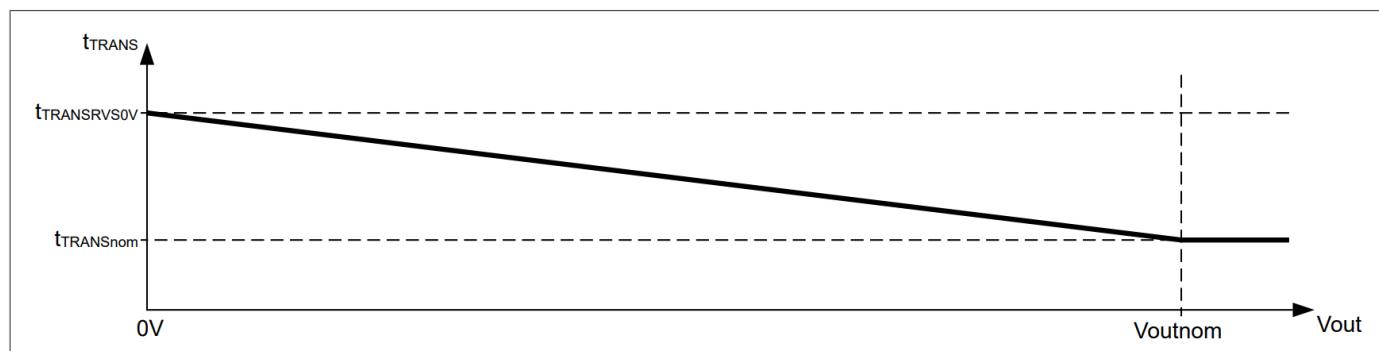

当输出电压  $V_{out}$  下降时，退磁过程会延长。在 CRM 中，通过调整 LS 开关的导通时间  $t_{LSon}$  以匹配变化的  $V_{out}$  来确保 ZVS 工作。在 ZV-RVS 中，ZVS 脉冲宽度  $t_{ZVS}$  是根据  $I_{MAGneg}$  和  $V_{out}$  计算得出的，而 LS 导通时间  $t_{TRANS}$  会随着  $V_{out}$  的增加而减小（见 [图 21](#)）。

图 21  $t_{Trans}$  调制与  $V_{out}$

## 4.3.2.4 CRM 操作期间的 ZVS 操作和体二极管交叉传导预防

如果 HS 导通时磁化电流仍为正，则 LS 导通时间过短可能导致硬开关，甚至体二极管交叉导通；另一方面，LS 导通时间过长会增加无功电流和传导损耗，甚至可能导致变压器饱和。为了排除硬开关和体二极管交叉导通，控制器仅在 ZCD 引脚电压指示半桥开关节点电压  $V_{HB}$  发生变化（ZCD 事件）后才激活 HS 开关。控制器会调整 LS 导通时间以确保 ZVS 状态。

## 4 Functional description

### 4.3.2.5 传输延迟补偿

在峰值电流控制期间，传播延迟会影响峰值电流，导致电流值过高。过冲取决于输入电压  $V_{bus}$  和谐振电容处的反射输出电压  $V_{Cr}$ 。对  $V_{bus}$  和  $V_{Cr}$  的这种依赖性会影响应用中的电流设定点阈值精度，需要进行补偿以避免反馈信号  $V_{FB}$  和内部电流设定点  $I_{SET}$  出现误差。

### 4.3.3 Vout启动控制

混合反激式启动发生在启动条件满足后，参见[章节 4.1.1](#)。第一步，施加多个 LS 脉冲对 HSVCC 引脚上的自举电容进行预充电。之后，ZV-RVS 开关周期随之而来，输出电压平稳上升。此时，第一个开关周期以较低的固定频率运行，直到 ZCD 引脚上的电压足够高以进行谷底检测。一旦反馈环路接管峰值电流控制，启动阶段就完成了。

在第一个 HS 脉冲期间，检查 CS 引脚电压是否分流电阻短路。对 ZVS 脉冲宽度应用最大时间，以防止由于在 ZCD 引脚测得的电压非常低而导致 ZVS 脉冲过长。在启动阶段，当引脚 ZCD 处采样的电压超过相关阈值时，就会发生从 ZV-RVS 到 CRM 的转换。

在混合反激式启动的第一个开关周期内，ZVS 脉冲后导通 HS 开关的死区时间固定为  $t_{deadHSRVS}$ ，而死区时间  $t_{deadLS}$  与 CRM 操作中的相同。

### 4.3.4 频率抖动

为了降低EMI噪声幅度，HFB级实现了开关频率抖动。在CRM和ZV-RVS工作模式下，如果参数  $I_{MAGnegjitter\%}$  为非零值且输出电流低于其OCP电平，则抖动功能会被激活。频率抖动的时间步长定义为参数  $t_{JitterStep0}$

### 4.3.5 半桥栅极驱动器

半桥栅极驱动器由一个用于低侧开关的低侧栅极驱动器（由 VCC 和 GND 引脚供电）和一个由 HSVCC 和 HSGND 引脚供电的浮动高侧栅极驱动器组成。浮动高侧栅极驱动器与 VCC 和 HSGND 引脚进行电气隔离，并通过无磁芯变压器进行控制。低侧栅极驱动器和高侧栅极驱动器的启用/禁用取决于相应的欠压闭锁阈值 ( $V_{VCCOn}, V_{VCCoff}$ ) 和 ( $V_{HSVCCOn}, V_{HSVCCoff}$ )（参见[章节 4.5.2.1](#) 和 [章节 4.5.2.2](#)）。两个驱动器均钳位在其最大栅极驱动器输出电压  $V_{LSDhigh}$  和  $V_{HSDhigh}$ 。如果禁用，栅极驱动器输出将保持主动下拉状态。当 HSVCC 超过阈值  $V_{HSVCCOn}$  时，高端栅极驱动器将在  $t_{HSGDondel}$  时间段后启用。

## 4 Functional description

图 22 带 MOSFET 开关的半桥栅极驱动器

为了驱动半桥中的分立 CoolGaN™ 器件，建议使用专用的外部 RC 网络，参见 [图 3](#)。

## 4.4 组合控制功能

在下一节中，我们将描述具有 PFC 和混合反激式控制器交互的组合控制器功能，以实现最佳系统控制。

### 4.4.1 突发模式控制

该 IC 包含一个突发模式控制块，可以在轻负载时进入高效运行模式。通过在睡眠模式下引入 IC 的长时间非开关阶段，可以减少突发模式操作期间的平均开关和偏置损耗。PFC 级和混合反激式电路均在低负载时进入突发模式。突发模式操作由混合反激控制器根据输出控制反馈电压  $V_{FB}$  反射的电流。通常，PFC 和混合反激式拓扑的突发模式操作是同步的，而 HFB 决定了突发帧。图 23 显示了突发模式控制的主要功能。

## 4 Functional description

图23 突发模式控制块

## 4.4.1.1 突发模式进出控制

一旦  $V_{FB}$  降至  $V_{FBMen}$  以下，下一个开关脉冲的产生就会停止，IC 会进入睡眠阶段，其电流消耗会降至  $I_{VCCBMpsm0}$

## 4.4.1.2 突发模式操作

通过将 FB 引脚电压与阈值  $V_{FBMen}$  和  $V_{FBMctrl}$  进行比较，可以控制突发帧的开启（突发）和关闭（休眠）。一旦 FB 电压下降并超过阈值  $V_{FBMen}$ ，IC 就会进入休眠阶段。在休眠阶段，一旦  $V_{FB}$  上升并超过阈值  $V_{FBMctrl}$ ，IC 就会被唤醒并进行突发，直到 FB 电压达到  $V_{FBMen}$ ，IC 再次进入休眠阶段。突发帧的占空比和频率完全由  $V_{FB}$  控制。

是否需要 PFC 操作，取决于操作条件（参见 [章节 4.4.2](#)），PFC 操作从突发导通时间开始时开始，并在总线电压达到其目标值或控制器再次进入突发关断状态时结束。否则，如果不需要 PFC 操作，则在突发操作期间不会进行 PFC 开关操作。

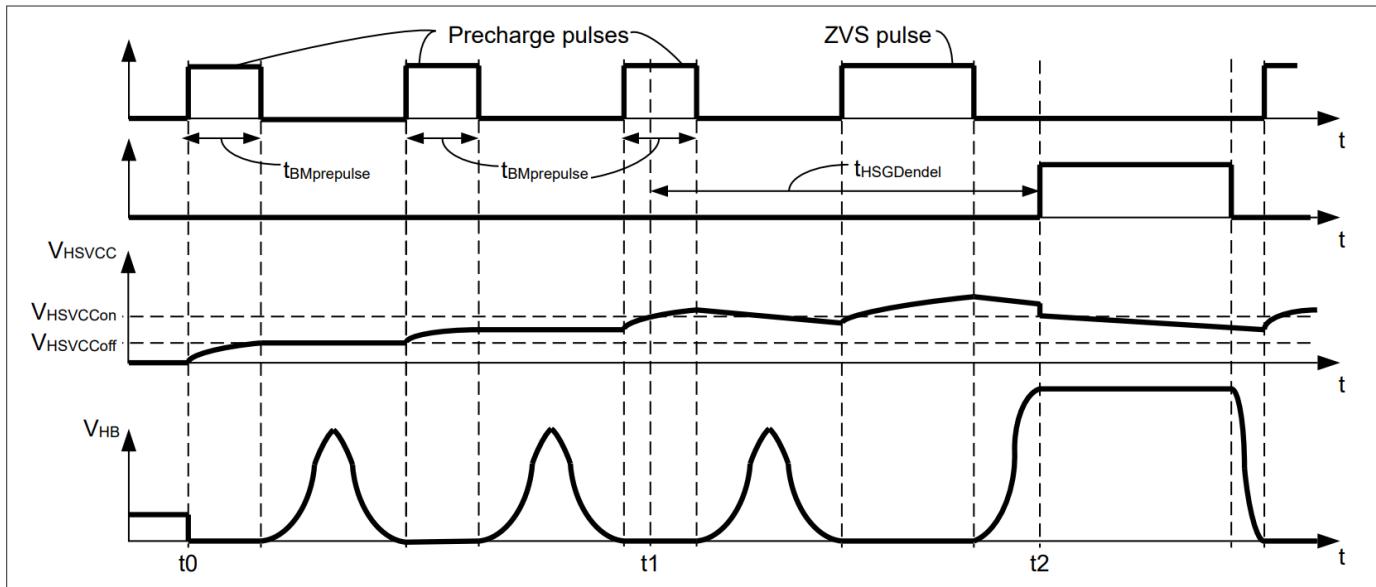

## 4.4.1.3 自举预充电

在极轻负载下进行突发模式操作会导致长时间的休眠阶段，期间无开关活动。在此休眠期间， $V_{HSVCC}$  电压可能会降至关断阈值  $V_{HSVCCoff}$  以下，随后浮动 HS 栅极驱动器将被停用。为了确保在长时间 IC 休眠阶段后，有合适的 HSVCC 电源来开启 HS 开关，但前提是捕获的突发模式休眠时间超过阈值  $t_{BMsplthrpp}$ ，在第一个 ZV-RVS 开关周期之前会引入一串  $N_{BMPrepulse}$  预充电脉冲。[图 24](#) 显示由  $N_{BMPrepulse}$  定义的预充电脉冲串模式。

**注意：** 如果由于 HSVCC 供电不当导致 HS 脉冲缺失，后续的 LS 脉冲可能会导致硬开关。因此，控制器会尝试检测这种情况，并可能停止开关操作。

## 4 Functional description

图24 预充电脉冲序列模式

## 4.4.2 PFC 启用/禁用控制

在系统启动时，PFC 处于活动状态。一旦 HFB 进入闭环运行，就会做出进一步的 PFC 操作决定，并由输出功率水平或输入电压和输出电压水平决定。

在一定的输出功率下，功率因数校正是强制性的，正如一些开关电源标准所规定的那样。如果 PFC 操作由输出功率决定，则需要使用阈值  $P_{PFCenable}$  和  $P_{PFCdisable}$ （它们构成滞后控制）以及用于禁用 PFC 级的消隐时间  $t_{PFCdisableblk}$

此外，尽管估计功率低于  $P_{PFCdisable}$ ，但 PFC 仍处于启用状态，以确保正确的混合反激操作。

组合 IC 根据输入电压和输出信息启用或禁用 PFC，并将总线电压调节到最佳点。

对于基于功率的 PFC 禁用，当估计功率低于  $P_{PFCdisable}$  时，消隐时间  $t_{PFCdisableblk}$  适用。

## 4.4.3 母线电压目标水平

组合控制器为总线电压设置提供了灵活的配置，既可以像使用传统 PFC 控制器一样设置为几乎固定的水平，也可以设置为由混合反激级或 PFC 本身设置的与工作条件相关的目标水平，并且与 PFC 启用/禁用控制密切相关（参见章节 4.4.2）。

为了使混合反激式级在宽输出电压范围内实现最佳运行，混合反激式级请求的 PFC 总线电压目标电平  $V_{bustarget,HFB}$  由控制器根据以下条件确定在引脚 ZCD 处测量的反射输出电压。

只有当目标总线电压高于交流线路峰值电压  $|V_{ACpk}|$  时，PFC 才能正常工作。因此，PFC 控制器还会确定一个总线电压目标值  $V_{bustarget,PFC}$ ，该值等于检测到的整流交流峰值电压加上一个偏移量  $V_{bustargetVacpkoffset}$ 。

每当 PFC 启用和切换时， $V_{bustarget,HFB}$  和  $V_{bustarget,PFC}$  中的较高值将用作 PFC 调节的目标值。

此外，总线电压目标值限制在最小值  $V_{bustargetmin}$  与最大值  $V_{bustargetmax}$  之间。

此外，母线电压目标值可以设置最大值  $V_{bustargetmax}$  通过参数  $V_{outThHiVbus}$ 。一旦测得的输出电压高于此值，则目标总线电压设置为最大值。

## 4 Functional description

## 4.5 保护措施

该 IC 支持多种保护功能，从而产生不同的保护反应。

对于大多数保护事件，IC 都会进入保护模式（参见第 4.5.1 章）。保护设置可配置，包括触发值和/或其响应模式。一旦触发保护，错误代码将通过切换 MFIO 引脚发出。

**表2 保护特性和反应**

| Protection feature                      | Symbol       | Error code                                               | Protection reaction                                          |

|-----------------------------------------|--------------|----------------------------------------------------------|--------------------------------------------------------------|

| VCC undervoltage lockout                | UVOFF        |                                                          | HW reset and restart                                         |

| HSVCC undervoltage lockout              | HSUVOFF      |                                                          | Disable HS gate driver                                       |

| VCC overvoltage protection              | VCCOVP       | 25                                                       | Configurable: Auto-restart or latch                          |

| Brown-in protection                     | BIP          | 18                                                       | Bang-bang mode, waiting for brown-in in start-up check phase |

| Brown-out protection                    | BOP          | 1 by $V_{bus}$ measurement; 2 by estimated AC peak value | Enter fast-restart mode                                      |

| PFC Start-up time-out protection        | PFCSTTOP     | 24                                                       | Configurable: Auto-restart or latch                          |

| Output start-up time-out protection     | VoutSTTOP    | 4                                                        | Configurable: Auto-restart or latch                          |

| Bus overvoltage protection              | BUSOVP       | 12                                                       | Configurable: Auto-restart or latch                          |

| PFC bus overvoltage protection level 1  | BUSOVPfcstop |                                                          | Stop PFC switching                                           |

| PFC bus overvoltage protection level 2  | PFCOVP2      |                                                          | Stop PFC switching (cycle-by-cycle)                          |

| PFC bus undervoltage protection         | PFCUVP       | 29 at start-up;<br>11 during operation                   | Fast-restart mode                                            |

| PFC overcurrent protection              | PFCOCP       |                                                          | Stop PFC switching (cycle-by-cycle)                          |

| PFC CCM protection                      | PFCCM        | 28                                                       | Configurable: Auto-restart or latch                          |

| Output overcurrent protection level 1   | OCPlev1      | 9                                                        | Configurable: Auto-restart or latch                          |

| Output maximum current protection       | OCPmax       | 8                                                        | Configurable: Auto-restart or latch                          |

| HFB primary side overcurrent protection | CSPROT       | 13                                                       | Configurable: Auto-restart or latch                          |

| Vout overvoltage protection             | VoutOVP      | 6                                                        | Configurable: Auto-restart or latch                          |

(表格续下页.....)

## 4 Functional description

**表 2 (续) 保护特性和反应**

| Protection feature                  | Symbol  | Error code                            | Protection reaction                                              |

|-------------------------------------|---------|---------------------------------------|------------------------------------------------------------------|

| Vout undervoltage protection        | VoutUVP | 7                                     | Configurable: Auto-restart or latch                              |

| Vout short circuit protection       | VoutSCP | 27                                    | Configurable: Auto-restart or latch                              |

| CS pin short protection             | CSSCP   | 3                                     | Configurable: Auto-restart or latch                              |

| FB pin start-up protection          | FBSTUP  | 14                                    | Stop operation and enter bang-bang mode for start-up check phase |

| HFB open-loop protection            | HFBOLP  | 26                                    | Latch                                                            |

| External overtemperature protection | extOTP  | 16 during operation<br>17 at start-up | Configurable: Auto-restart or latch                              |

| Watchdog timer                      | WDOG    | 19                                    | Auto-restart                                                     |

| Memory parity check                 | MEMPAR  | 23                                    | Auto-restart                                                     |

### 4.5.1 保护模式

一旦进入保护模式，IC 将停止 PFCGD、LSGD 和 HSGD 引脚上的栅极驱动器开关，并进入待机模式。在待机模式下，高压启动单元将以 Bang-Bang 模式工作（参见第 4.1.3 章），以保持 VCC 电压处于高电平，从而在 VCC 电容中存储足够的能量用于系统启动。IC 支持三种保护模式，详见下文。

本控制器集成了Cr放电功能。一旦检测到故障，它就会放电 Cr 电容器，并且其反应配置为自动重启或快速重启。这样，就可以避免下次启动时 LS 开关承受应力。

#### 4.5.1.1 欠压闭锁后停用IC

如果 VCC 低于  $V_{VCCoff}$ ，则会触发欠压锁定保护，IC 将完全停用，并且只能通过常规启动机制重新启动（参见章节 4.1.1）。

#### 4.5.1.2 自动重启模式

自动重启模式激活后，控制器停止在栅极驱动器引脚上进行开关操作。自动重启时间  $t_{ARM}$  过后，控制 IC 恢复工作。在自动重启时间  $t_{ARM}$  期间，控制器会在  $t_{ARMbase}$  之前唤醒，并将 VCC 重新充电至  $V_{VCCon}$ （参见第 4.1.3 节）。

#### 4.5.1.3 锁存模式

在锁存工作模式下，系统保持待机模式，无需任何重启尝试。只有当 VCC 降至 UVOFF 硬件复位阈值  $V_{VCCoff}$  以下时，才能复位锁存工作模式。在锁存工作模式下，高压启动单元在 VCC 引脚电压阈值  $V_{VCCslpHVon}$  时开启，并在达到 VCC 引脚电压阈值  $V_{VCCon}$  时关闭（参见第 4.1.3 章）。

#### 4.5.1.4 快速重启模式

在快速重启模式下，启动单元被阻断，所有栅极均被拉低。内核继续运行，并消耗 VCC 电容中存储的能量。当 VCC 降至  $V_{VCCoff}$  以下时，控制器将被迫进行新的冷重启。

## 4 Functional description

### 4.5.2 保护功能

#### 4.5.2.1 VCC 欠压锁定

VCC 欠压锁定 (UVOFF) 功能可确保 IC 根据 VCC 引脚的供电电压以特定方式激活和停用。UVOFF 包含一个滞后电路，其下限电压阈值  $V_{VCCoff}$  用于停用 IC，上限电压阈值  $V_{VCCon}$  用于激活 IC。一旦 VCC 电压降至下限阈值  $V_{VCCoff}$  以下，IC 将完全复位并停用。在复位状态下，高压启动单元将开启，直至 VCC 电压超过  $V_{VCCon}$ ，然后 IC 将开始新的启动（参见 [章节 4.1.1](#)）。

#### 4.5.2.2 HSVCC欠压闭锁

所实施的 HSVCC 欠压锁定 (UVOFF) 功能可确保浮动高端驱动器的激活和停用。HSUVOFF 包含一个滞后电路，其上限电压阈值  $V_{HSVCCon}$  用于激活高端栅极驱动器。当 HSVCC 电压降至下限阈值  $V_{HSVCCoff}$  以下时，高端驱动器会立即关闭并停用。在停用阶段，高端驱动器的电流消耗会降低。

#### 4.5.2.3 VCC过压保护

VCC 引脚具有过压检测功能。该检测功能由阈值  $V_{VCCOVP}$  和消隐时间  $t_{VCCOVP}$  组成。一旦  $V_{VCC}$  高于电压阈值且持续时间超过消隐时间，VCC 过压保护功能就会触发，控制 IC 会进入配置的保护模式。

#### 4.5.2.4 欠压保护

成功接入电源必须满足两个条件：

1. 输入电压高于阈值，且  $V_{in} > V_{inbo}$ ，通过引脚 HV 感测

2. PFC 总线电压高于阈值，且  $V_{bus} > V_{busbo}$ ，通过引脚 PFCVS 感测

当交流电压跌落条件在超时持续时间  $t_{HVbito}$  内不满足时，将触发交流电压跌落超时保护反应。

为了在检测到电源电压下降后启动系统，还需检查其他条件（[章节 4.1.1](#)）。

由于电压接入也基于感测到的总线电压，因此这种保护在启动期间还可充当 PFC 开环保护。

#### 4.5.2.5 过压保护

掉电检测基于估计的交流峰值电压和总线电压。

如果估算的交流峰值电压低于可配置阈值  $V_{inbo}$  的时间超过消隐时间  $t_{bo}$ ，则将触发保护模式，IC 进入掉电检测阶段。消隐时间  $t_{bo}$  仅在 IC 有效工作时间内计数。在突发休眠阶段，检测到掉电的总持续时间会相应增加。

如果测得的总线电压低于阈值  $V_{inbo}$  的时间超过消隐时间  $t_{bo}$ ，则触发 BOP。

之后，如 [第 4.1.2 章](#) 所述，如果交流输入电压高于电压跌落水平，则进入 Bang-Bang 模式并开始快速重启。

#### 4.5.2.6 启动超时保护

PFC 激活后，PFC 会执行软启动。如果软启动无法在  $t_{startPFC}$  时间内完成，则会进入保护模式（自动重启或锁存）。

混合反激式输出具有第二个启动超时功能。如果启动过程中发生过载，输出电压  $V_{out}$  可能无法达到调节目标电压，从而阻止系统进入调节状态。如果由  $V_{FB}$  确定的电流设定点在  $t_{startto}$  时间段内未降至由  $V_{out}$  确定的电流设定点以下，则检测到超时。

## 4 Functional description

### 4.5.2.7 PFC总线过压保护

第一个过压保护 (PFCOVP1) 阈值由可配置参数  $V_{busOVPFCstop}$  设定。超过此阈值后最迟在  $t_{SLWTASK}$  内，PFC 停止开关，而混合反激式级继续开关。当测量的总线电压低于阈值  $V_{busOVPFCresume}$ 。

第二个过压保护机制 (PFCOVP2) 使用基于 PFCVs 引脚瞬时值的硬件比较器实现。如果总线电压在极短时间内超过第一个 OVP 阈值且未触发 PFCOVP1，该机制将保护系统。相应的阈值  $V_{PFCVSOVP2}$  是一个固定电压。如果 PFCVS 检测到的电压超过阈值，则不会产生新的 PFC 栅极驱动脉冲。一旦 PFCVS 电压再次低于阈值  $V_{PFCVSOVP2}$ ，如果 PFCOVP1 事件阻止了 PFC 脉冲的产生，则会再次产生 PFC 脉冲。

PFCOVP1 和 PFCOVP2 事件都不会导致进入任何系统级保护模式。它们仅对 PFC 操作有影响，但对 HFB 阶段没有影响。

PFC 控制器提供三级母线过压保护，其电压阈值为  $V_{busOVP3}$ ，消隐时间为  $t_{VbusOVP3o}$ 。一旦测得的母线电压高于阈值  $V_{busOVP3}$ ，且持续时间超过  $t_{VbusOVP3}$ ，PFC 和 HFB 操作均会停止，控制器进入设定的保护模式。

### 4.5.2.8 输入欠压保护

母线电压的欠压检测是通过观察 HFB 开关时间间接完成的。一旦触发保护，系统就会进入快速重启模式。

### 4.5.2.9 峰值电流限制

一旦 PFCCS 引脚电压超过限流阈值  $V_{PFCCSOcp}$  且持续时间超过消隐时间  $t_{PFCCSOcp}$ ，PFC 栅极 PFCGD 即关闭。之后，ZCD 信号或 PFC 最大周期超时信号将启动下一个开关周期。此保护机制在每个开关周期均有效。

如果使用具有电流限制的 GaN 器件作为 PFC 开关（图 4）、PFC 电流检测在GaN器件内部完成，不再需要外部分流电阻。PFC开关过流会直接在GaN器件内部触发其关断。

### 4.5.2.10 PFC CCM运行保护

当 PFC 电感器中的磁化电流在电感器退磁时间内没有衰减到零时，PFC 开关漏源电压不会振荡，因此不会发生 ZCD 事件。PFC 最大开关周期超时触发 PFC 开关的开启并开始下一个开关周期。

在临界条件下，PFC 电流在每个周期内被推得更高，然后受到限制 PFC 电流限制器（参见第 4.5.2.9 节），它关闭 PFC 开关，而不是由 PFC 调节器控制的定时器。控制器监控 ZCD 信号缺失的时间段。当该时间段长于消隐时间  $t_{PFCCSccm}$  时，将触发 PFC CCM 保护，IC 进入保护模式。

### 4.5.2.11 混合反激式过流保护

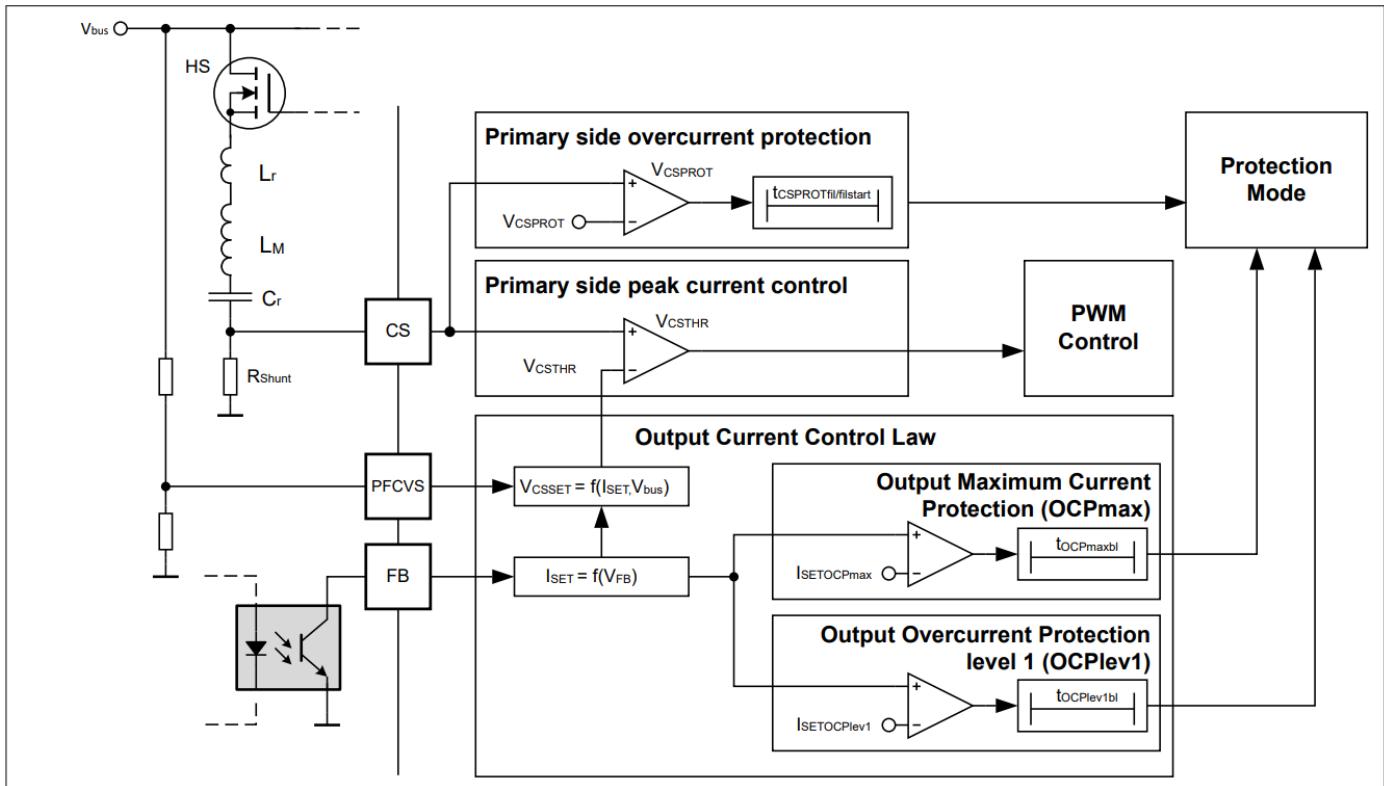

混合反激式过流保护包含多种检测功能，可防止应用在输出过流条件下运行或超过一次侧峰值电流（见图 25）。

## 4 Functional description

图 25 过流保护概览

## 4.5.2.11.1 过流保护

输出过流保护有两级：

- 输出过流保护等级 1，阈值为  $I_{OUTOCPlev1}$ ，消隐时间为  $t_{OCPlev1bl}$

- 输出最大电流保护，阈值为  $I_{OUTOCPMax}$ ，消隐时间为  $t_{OCPMaxbl}$

根据定义的输出过流保护水平  $I_{SETOCPlev1/max}$ ，内部阈值  $I_{SETOCPlev1/max}$  由输出电流控制律得出。一旦电流设定点  $I_{SET}$  超过阈值水平，定时器就会启动。当定时器达到阈值  $t_{OCPlev1bl/maxbl}$  时，将进入配置的保护模式（自动重启或锁存）。当  $I_{SET}$  降至阈值以下时，定时器将重置。

一旦通过  $V_{FB}$  控制请求对应于电流设定点  $I_{SET} > I_{SETOCPmax}$  的更高输出电流，HFB 电流保持受限。在此阶段，由于输出电流高于转换器提供的电流，输出电压会下降。

## 4.5.2.11.2 一次侧过流保护CSPROT

$V_{CSPROT}$  是一个固定阈值，且高于  $V_{CSTHRmax}$ 。在前沿消隐时间  $t_{HSleb}$  期间，CSPROT 功能不会被消隐。一旦 CS 引脚电压超过  $V_{CSPROT}$ ，就会进入配置的保护模式（自动重启或锁存）。

为避免错误的 CSPROT 事件，适用消隐时间  $t_{CSPROTFilstart}$  和  $t_{CSPROTFilo}$

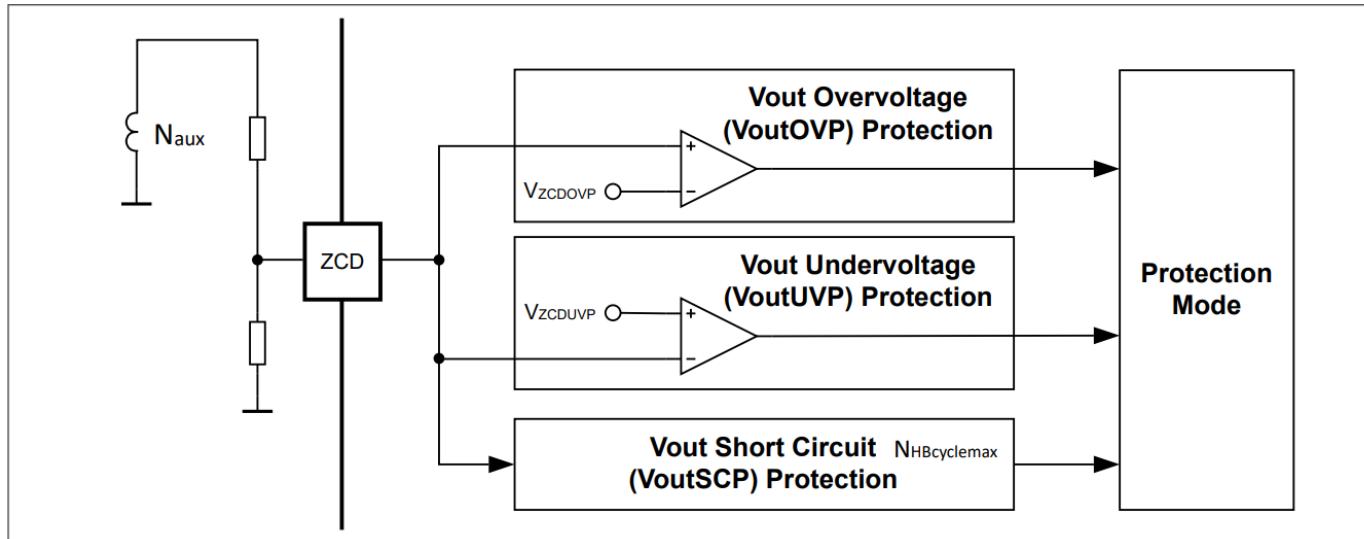

## 4.5.2.12 过压和欠压保护

该 IC 提供两种输出电压  $V_{out}$  保护机制，分别针对输出欠压和输出过压，以确保在规定的  $V_{out}$  工作范围内可靠运行。测量是在 LS 开关导通时的退磁阶段通过变压器辅助绕组的反射电压在引脚 ZCD 处进行的（参见图 26）。此外，还会监控启动阶段的过零检测，以检测输出端是否发生短路。

## 4 Functional description

图 26 输出电压保护

### 4.5.2.12.1 Vout 过压保护

该 IC 提供输出过压检测。这是通过在初级侧测量 ZCD 引脚上的电压来实现的，该电压来自变压器辅助绕组，并且在每个开关周期的 LS 导通时间内。当反反射输出电压超过阈值  $V_{ZCDOVP}$ （对应阈值  $V_{outOVP}$ ）持续超过消隐时间  $t_{outOVPbl}$ ，检测到输出过压。一旦检测到过压事件，就会触发保护模式。

### 4.5.2.12.2 Vout 欠压保护

输出欠压检测通过测量 ZCD 引脚的电压进行检测。启动完成后，当 ZCD 引脚的测量电压降至阈值  $V_{ZCDUVP}$ （对应于阈值  $V_{outUVP}$ ）以下时，触发 Vout 欠压保护。一旦触发保护，将进入相应的保护模式。在突发模式下从休眠状态唤醒后，由于各种原因，在 ZCD 引脚测量的电压可能会失真。为避免误触发输出欠压保护，输出欠压检测会消隐一段时间，该时间由 CFG 定义  $V_{outUVPBMo}$

### 4.5.2.12.3 Vout 短路保护

对于输出端的短路保护，实施了两种不同的机制。一个仅在启动期间处于活动状态，另一个在启动后处于活动状态。

在启动过程中，Vout 短路保护通过限制半桥开关周期数来实现。在未检测到过零的情况下，最多允许  $N_{HBcyclemax}$  个连续半桥开关周期。如果在未检测到过零的情况下超过  $N_{HBcyclemax}$  个周期，则启动阶段将停止，并进入配置的保护模式。

在启动后的正常工作中，另一项 Vout 短路保护机制处于激活状态。如果实际电压  $V_{ZCD}$  与其内部平均值  $V_{ZCDavg}$  之间的差值大于内部阈值  $\Delta V_{ZCDshort}$ （该阈值对应于参数  $\Delta V_{outSCP}$ ），则触发输出短路保护并进入保护模式。

### 4.5.2.13 短路保护

在第一个 HS 开关脉冲时，CS 引脚上的短路检测被激活，以保护采用缩短的  $R_{shunt}$  运行的应用程序。

## 4 Functional description

### 4.5.2.14 FB引脚启动保护

在启动条件检查阶段，将评估引脚FB的电压。仅当  $V_{FB} > V_{FBMctrl}$  也满足。否则，触发保护并进入参数  $EV_{StartFBlow}$  定义的模式。

### 4.5.2.15 混合反激式开环保护

开路控制环路保护采用与输出短路保护类似的方法（参见章节 4.5.2.12.3）。仅当 FB 反馈电压饱和时，才会评估通过 ZCD 引脚测量的反射输出电压：如果实际电压  $V_{ZCD}$  与其内部平均值  $V_{ZCDavg}$  之间的差值大于内部阈值  $\Delta V_{ZCDolp}$ ，该阈值与可配置输出电压有关阈值  $\Delta V_{outolp}$ ，触发开环保护并进入配置的保护模式。

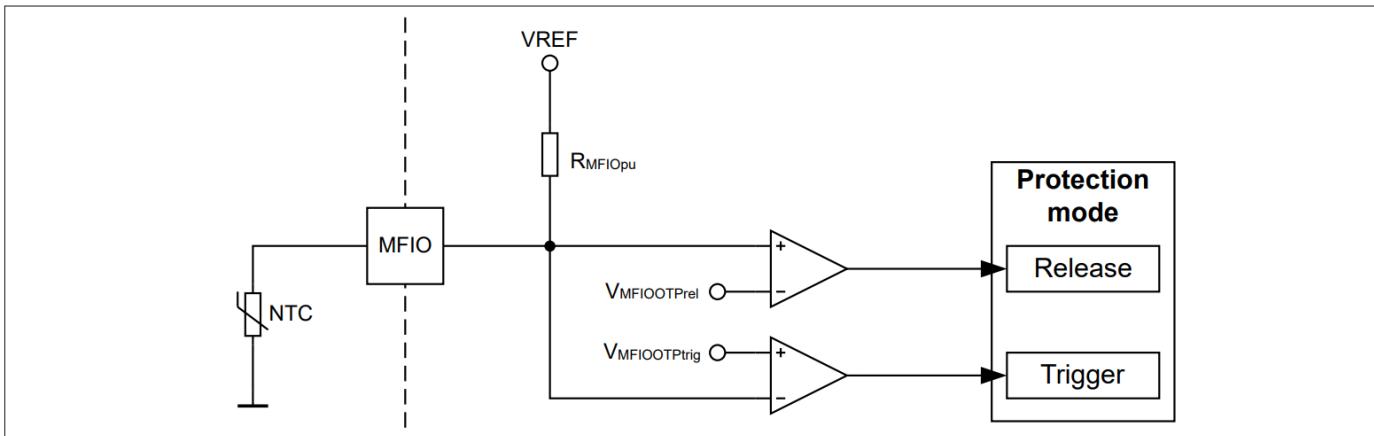

### 4.5.2.16 外部过温保护

外部过温保护 (ExtOTP) 基于测量引脚 MFIO 处的外部 NTC 热敏电阻，见图 27 一旦外部电阻降至阈值  $R_{MFIOOTPtrig}$  以下，控制器将进入过温保护模式。控制器首先尝试自动重启，但仅持续 OTP 事件的  $N_{OTPevmax}$  次，然后进入锁存模式。在自动重启的情况下，只有当外部电阻值超过阈值  $R_{MFIOOTPrel}$  时，才会发生重启周期。

图 27 使用 MFIO 引脚上的 NTC 热敏电阻实现外部过温保护

可选地，如果通过外部热敏电阻检测到过温事件（低于  $R_{MFIOOTPtrig}$ ），则降低一次侧峰值电流设定点，从而实现功率折返，以避免电源单元过热。一旦电源单元冷却下来，测量温度回到释放设定点  $R_{MFIOOTPrel}$ ，一次侧峰值电流将再次完全由反馈电压控制。

除了使用外部 NTC (OTP\_NTC) 实现的过温保护外，MFIO 引脚还集成了其他三种功能：ACT\_EN (IC 非突发工作时引脚高电平)、OTP\_NTC\_Pder (外部过温保护，一旦触发过温，功率会降低) 和 VoutTog (MFIO 引脚根据输出电压水平 (与  $V_{outMFIOOgL}$  和  $V_{outMFIOOgH}$  相比) 切换)。最终功能取决于  $MFIO_{funt}$  的配置。配置完成后，四个选项中只有一个有效。

### 4.5.2.17 内存奇偶校验

为了保证内存完整性，在操作期间会持续提供奇偶校验。一旦检测到奇偶校验错误，控制器就会重置并进入配置的保护模式（自动重启模式或锁存）。

### 4.5.3 MFIO 引脚上的错误读取

一旦触发保护，相应的错误代码（见表 2）在引脚 MFIO 处发送。

## 5 Electrical characteristics

## 5 电气特性

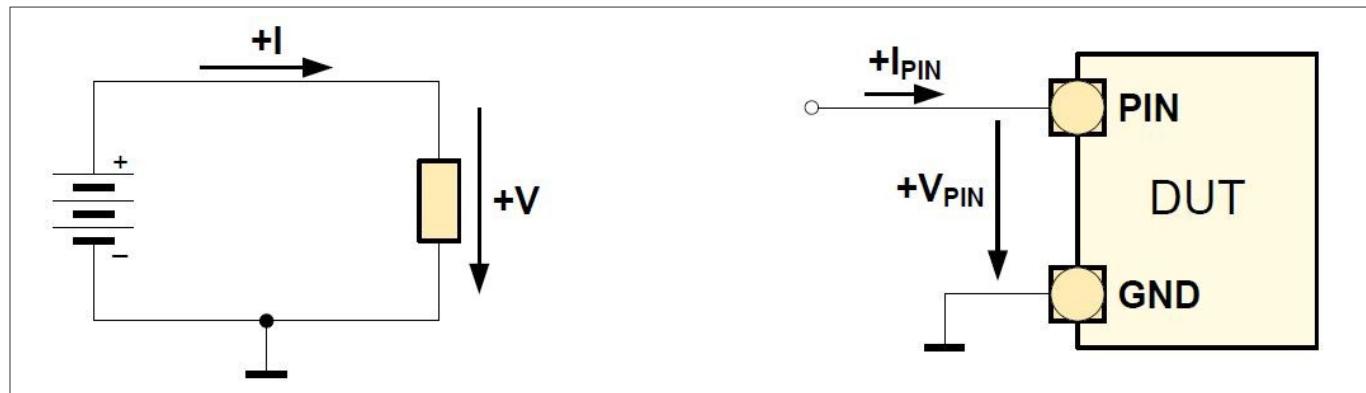

所有信号均相对于接地 GND 引脚进行测量。如果没有违背其他额定值，则电压电平都有效。

图 28 说明了本数据表中使用的电压和电流参数的定义。

图 28 电压与电流的定义

## 5.1 绝对最大额定值

超过此处所列的电气压力可能会对器件造成永久性损坏。长时间在绝对最大额定值条件下工作可能会影响器件的可靠性。最大额定值是绝对额定值；超过其中任何一个值都可能对集成电路造成不可逆转的损坏。

表 3 绝对最大额定值

| Parameter                                               | Symbol            | Values |      |      | Unit | Note or condition |

|---------------------------------------------------------|-------------------|--------|------|------|------|-------------------|

|                                                         |                   | Min.   | Typ. | Max. |      |                   |

| Voltage at pin HV                                       | $V_{HV}$          | -0.3   | -    | 600  | V    | <sup>1)</sup>     |

| Maximum current into pin HV                             | $I_{HV}$          | -      | -    | 10   | mA   | <sup>1)</sup>     |

| Voltage at pin VCC                                      | $V_{VCC}$         | -0.5   | -    | 26   | V    | <sup>1)</sup>     |

| Voltage at pin MFIO                                     | $V_{MFIO}$        | -0.5   | -    | 3.6  | V    | <sup>1)</sup>     |

| Voltage at pin PFCVS                                    | $V_{PFCVS}$       | -0.5   | -    | 3.6  | V    | <sup>1)</sup>     |

| Voltage at pin FB                                       | $V_{FB}$          | -0.5   | -    | 3.6  | V    | <sup>1)</sup>     |

| Voltage at pin ZCD                                      | $V_{ZCD}$         | -0.5   | -    | 3.6  | V    | <sup>1)</sup>     |

| Maximum negative transient voltage at pin ZCD           | $-V_{ZCDN\_TR}$   | -      | -    | 1.5  | V    | pulse < 500 ns    |

| Maximum permanent negative clamping current for pin ZCD | $-I_{ZCDCLN\_DC}$ | -      | -    | 2.5  | mA   | RMS               |

| Maximum transient negative clamping current for pin ZCD | $-I_{ZCDCLN\_TR}$ | -      | -    | 10   | mA   | pulse < 500 ns    |

| Voltage at pin CS                                       | $V_{CS}$          | -0.5   | -    | 3.6  | V    | <sup>1)</sup>     |

(表格续下页.....)

<sup>1)</sup> Permanently applied as DC value.

## 5 Electrical characteristics

表3 (续) 绝对最大额定值

| Parameter                                                 | Symbol                    | Values |      |                         | Unit | Note or condition                             |

|-----------------------------------------------------------|---------------------------|--------|------|-------------------------|------|-----------------------------------------------|

|                                                           |                           | Min.   | Typ. | Max.                    |      |                                               |

| Maximum negative transient voltage at pin CS              | -V <sub>CSN_TR</sub>      | -      | -    | 3                       | V    | pulse < 500 ns                                |

| Maximum permanent negative clamping current for pin CS    | -I <sub>CSCLN_DC</sub>    | -      | -    | 2.5                     | mA   | RMS                                           |

| Maximum transient negative clamping current for pin CS    | -I <sub>CSCLN_TR</sub>    | -      | -    | 10                      | mA   | pulse < 500 ns                                |

| Maximum permanent positive clamping current for pin CS    | I <sub>CSCLP_DC</sub>     | -      | -    | 2.5                     | mA   | RMS                                           |

| Maximum transient positive clamping current for pin CS    | I <sub>CSCLP_TR</sub>     | -      | -    | 10                      | mA   | pulse < 500 ns                                |

| Voltage at pin PFCCS                                      | V <sub>PFCS</sub>         | -0.5   | -    | 3.6                     | V    | <sup>1)</sup>                                 |

| Maximum negative transient voltage at pin PFCCS           | -V <sub>PFCCSN_TR</sub>   | -      | -    | 3                       | V    | pulse < 500 ns                                |

| Maximum permanent negative clamping current for pin PFCCS | -I <sub>PFCCSCLN_DC</sub> | -      | -    | 2.5                     | mA   | RMS                                           |

| Maximum transient negative clamping current for pin PFCCS | -I <sub>PFCCSCLN_TR</sub> | -      | -    | 10                      | mA   | pulse < 500 ns                                |

| Maximum permanent positive clamping current for pin PFCCS | I <sub>PFCCSCLP_DC</sub>  | -      | -    | 2.5                     | mA   | RMS                                           |

| Maximum transient positive clamping current for pin PFCCS | I <sub>CSCLP_TR</sub>     | -      | -    | 10                      | mA   | pulse < 500 ns                                |

| Voltage at pin LSGD                                       | V <sub>LSGD</sub>         | -0.5   | -    | V <sub>VCC</sub> +0.3   | V    | Limited by internal clamping                  |

| Voltage at pin PFCGD                                      | V <sub>PFCGD</sub>        | -0.5   | -    | V <sub>VCC</sub> +0.3   | V    |                                               |

| Voltage at pin HSVCC, HSGD and HSGND                      | V <sub>HSX</sub>          | -650   | -    | 650                     | V    | Isolation voltage, referred to GND            |

| Voltage at pin HSVCC                                      | V <sub>HSVCC</sub>        | -0.5   | -    | 24                      | V    | referred to HSGND                             |

| Voltage at pin HSGD                                       | V <sub>HSGD</sub>         | -0.5   | -    | V <sub>HSVCC</sub> +0.3 | V    | referred to HSGND                             |

| Slew-rate for floating high-side domain                   | dV <sub>HS</sub> /dt      | -50    | -    | 50                      | V/ns |                                               |

| Junction operation temperature                            | T <sub>J</sub>            | -40    | -    | 125                     | °C   |                                               |

| Storage temperature                                       | T <sub>S</sub>            | -55    | -    | 150                     | °C   |                                               |

| Maximum power dissipation                                 | P <sub>TOT</sub>          | -      | -    | 0.63                    | W    | T <sub>A</sub> =50 °C, T <sub>J</sub> =125 °C |

(表格续下页.....)

<sup>1)</sup> Permanently applied as DC value.

## 5 Electrical characteristics

表3 (续) 绝对最大额定值

| Parameter             | Symbol            | Values |      |      | Unit | Note or condition                                   |

|-----------------------|-------------------|--------|------|------|------|-----------------------------------------------------|

|                       |                   | Min.   | Typ. | Max. |      |                                                     |

| Soldering temperature | T <sub>Sold</sub> | -      | -    | 260  | °C   | <sup>2)</sup> Wave soldering                        |

| ESD HBM capability    | V <sub>HBM</sub>  | -      | -    | 2000 | V    | <sup>3)</sup> Human body model                      |

| ESD CDM capability    | V <sub>CDM</sub>  | -      | -    | 500  | V    | <sup>4)</sup> Charged device model                  |

| Latch-up capability   | I <sub>LU</sub>   | -      | -    | 150  | mA   | <sup>5)</sup> Pin voltages acc. to abs. max. rating |

## 5.2 封装特性

表4 封装特性

| Parameter                                                  | Symbol            | Values |      |      | Unit | Note or condition     |

|------------------------------------------------------------|-------------------|--------|------|------|------|-----------------------|

|                                                            |                   | Min.   | Typ. | Max. |      |                       |

| Thermal resistance from junction to ambient                | R <sub>thJA</sub> | -      | -    | 119  | K/W  | JEDEC 1s0p            |

| Thermal characterization parameter from junction to top    | $\Psi_{thJT}$     | -      | -    | 2    | K/W  | PG-DSO-14, JEDEC 1s0p |

| Creepage distance between HV and HSxxx to GND-related pins | D <sub>crp</sub>  | 2.1    | -    | -    | mm   |                       |

## 5.3 工作条件

下表显示了工作范围，其中下一章所示的电气特性有效。

表5 操作范围

| Parameter                      | Symbol            | Values |      |      | Unit | Note or condition                                  |

|--------------------------------|-------------------|--------|------|------|------|----------------------------------------------------|

|                                |                   | Min.   | Typ. | Max. |      |                                                    |

| Junction operation temperature | T <sub>J</sub>    | -25    | -    | 125  | °C   |                                                    |

| Voltage at pin HV              | V <sub>HV</sub>   | -0.3   | -    | 600  | V    |                                                    |

| External voltage at pin VCC    | V <sub>VCC</sub>  | 11     | -    | 24   | V    | Max. value needs to consider internal power losses |

| Voltage at pin MFIO            | V <sub>MFIO</sub> | -0.3   | -    | 3.3  | V    |                                                    |

(表格续下页.....)

<sup>2</sup> 根据 JESD22-A111

<sup>3</sup> 根据 ANSI/ESDA/JEDEC JS-001

<sup>4</sup> 根据 JESD22-C101

<sup>5</sup> 根据 JESD78,85°C (Class II) 温度

## 5 Electrical characteristics

表 5 (续) 工作范围

| Parameter                                            | Symbol             | Values |      |                   | Unit | Note or condition                                                 |

|------------------------------------------------------|--------------------|--------|------|-------------------|------|-------------------------------------------------------------------|

|                                                      |                    | Min.   | Typ. | Max.              |      |                                                                   |

| Voltage at pin FB                                    | $V_{FB}$           | -0.3   | -    | 3.3               | V    |                                                                   |

| Voltage at pin ZCD                                   | $V_{ZCD}$          | -0.3   | -    | 3.3               | V    |                                                                   |

| Voltage at pin CS                                    | $V_{CS}$           | -0.3   | -    | 3.3               | V    |                                                                   |

| Total maximum current out of pins FB and MFIO        | $-I_{FB}-I_{MFIO}$ | -      | -    | 0.63              | mA   | During sleep phase in burst mode                                  |

| Voltage at pin LSGD                                  | $V_{LSGD}$         | -0.3   | -    | $V_{VCC} + 0.3$   | V    | Internally clamped at $V_{LSGDhigh}$                              |

| Maximum low state output reverse current at pin LSGD | $-I_{LSGDLREV}$    | -      | -    | 100               | mA   | <sup>6)</sup> Applies if $V_{LSGD} < 0$ V and driver at low state |

| Voltage at pin HSGD                                  | $V_{HSGD}$         | -0.3   | -    | $V_{HSVCC} + 0.3$ | V    | Internally clamped at $V_{HSGDhigh}$                              |

| Maximum low state output reverse current at pin HSGD | $-I_{HSGDLREV}$    | -      | -    | 100               | mA   | Applies if $V_{HSGD} < 0$ V and driver at low state               |

| Voltage at pin HSVCC                                 | $V_{HSVCC}$        | 10     | -    | 24                | V    | Referred to HSGND                                                 |

| Voltage at pin HSGND                                 | $V_{HSGND}$        | -0.3   | -    | 600               | V    |                                                                   |

| UART Baudrate at pin MFIO                            | $t_{BD}$           | 10k    | -    | 115k              | Bd   |                                                                   |

| Voltage at pin PFCVS                                 | $V_{PFCVS}$        | -0.3   | -    | 3.3               | V    |                                                                   |

| Voltage at pin PFCCS                                 | $V_{PFCCS}$        | -0.3   | -    | 3.3               | V    |                                                                   |

| Voltage at pin PFCGD                                 | $V_{PFCGD}$        | -0.3   | -    | $V_{VCC} + 0.3$   | V    | Internally clamped at $V_{PFCGDhigh}$                             |

## 5.4 特性

电气特性涉及在指定电源电压和结温范围内给出的数值范围。典型值代表基于  $T_A = 25$  °C 的中值。所有电压均参考 GND，若无其他说明，则假设电源电压为  $VCC = 14.0$  V。

<sup>6)</sup> 设计保证。

## 5 Electrical characteristics

## 5.4.1 高电压 (HV引脚)

表 6 电气特性

| Parameter                         | Symbol            | Values |      |      | Unit          | Note or condition                                                                                                           |

|-----------------------------------|-------------------|--------|------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                   |                   | Min.   | Typ. | Max. |               |                                                                                                                             |

| HV VCC charge current capability  | $I_{HVchargeVCC}$ | 2.4    | 5.0  | 7.5  | mA            | <sup>7)</sup> $V_{VCC} = 1 \text{ V}$ , $V_{HV} = 30 \text{ V}$ ; Peak current limited in application by external resistors |

| Maximum leakage current at HV pin | $I_{HVLK}$        | -      | -    | 10   | $\mu\text{A}$ | $V_{HV} = 600 \text{ V}$ , HV start-up cell disabled                                                                        |

| Brown-in time-out                 | $t_{HVbito}$      | -      | 20   | -    | ms            | $I_{HVbi} > 0 \text{ mA}$                                                                                                   |

| Brown-in time-out                 | $t_{HVbito}$      | -      | 2    | -    | ms            | $I_{HVbi} = 0 \text{ mA}$                                                                                                   |

## 5.4.2 电源 (VCC引脚)

表 7 电源的电气特性 (VCC引脚)

| Parameter                                                      | Symbol           | Values |      |       | Unit          | Note or condition                                                |

|----------------------------------------------------------------|------------------|--------|------|-------|---------------|------------------------------------------------------------------|

|                                                                |                  | Min.   | Typ. | Max.  |               |                                                                  |

| Turn-on threshold                                              | $V_{VCCon}$      | 19.0   | -    | 22.0  | V             | Rising slope                                                     |

| Turn-off threshold                                             | $V_{VCCoff}$     | 7.98   | -    | 8.82  | V             | Falling slope, IC not in auto-restart or latch mode              |

| Turn-off threshold                                             | $V_{VCCoff}$     | 2.90   | -    | 5.70  | V             | Falling slope, IC in auto-restart or latch mode                  |

| Threshold to activate HV cell for VCC-supply during burst mode | $V_{VCCslpHVon}$ | 9.97   | 10.5 | 11.03 | V             | Falling slope                                                    |

| UVOFF current                                                  | $I_{VCCUVOFF}$   | -      | 20   | 40    | $\mu\text{A}$ | $V_{VCC} < V_{VCCoff(min)} - 0.3 \text{ V}$                      |

| Supply current                                                 | $I_{VCCopnm}$    | -      | 11   | 14.5  | mA            | Without gate driver gate charge losses and during brown-in phase |

| Quiescent current during burst mode power-saving phase         | $I_{VCCBMpsm0}$  | -      | 0.7  | 3.4   | mA            | Burst mode entered; pin MFIO and FB open                         |

(表格续下页.....)

<sup>7)</sup> 应用中的最大峰值充电电流受到连接到 HV 引脚的外部电阻的限制。

## 5 Electrical characteristics

表7 (续) 电源的电气特性 (VCC引脚)

| Parameter                               | Symbol       | Values |      |      | Unit | Note or condition                             |

|-----------------------------------------|--------------|--------|------|------|------|-----------------------------------------------|

|                                         |              | Min.   | Typ. | Max. |      |                                               |

| Quiescent current during bang-bang mode | $I_{VCCBB}$  | -      | 0.32 | 0.58 | mA   | Protection mode entered; pin MFIO and FB open |

| Overshoot protection threshold          | $V_{VCCOVP}$ | 22.0   | 23.0 | 24.0 | V    |                                               |

| Overshoot protection blanking time      | $t_{VCCOVP}$ | -      | 1.0  | -    | ms   |                                               |

## 5.4.3 浮动 HS 域 (HSGND、HSVCC 和 HSGD 引脚)

表8 HS域引脚电气特性

| Parameter                                                                   | Symbol           | Values |      |      | Unit          | Note or condition                                                 |

|-----------------------------------------------------------------------------|------------------|--------|------|------|---------------|-------------------------------------------------------------------|

|                                                                             |                  | Min.   | Typ. | Max. |               |                                                                   |

| HSVCC turn-on threshold                                                     | $V_{HSVCCon}$    | 8.7    | 9.2  | 9.7  | V             | Rising slope                                                      |

| HSVCC turn-off threshold                                                    | $V_{HSVCCoff}$   | 6.2    | 6.7  | 7.2  | V             | Falling slope                                                     |

| HSVCC idle current                                                          | $I_{HSVCCidle}$  | -      | 0.3  | 0.8  | mA            | Without gate driver gate charge losses, $V_{HSVCC} = 14\text{ V}$ |

| HSGD enabling delay time after HSVCC voltage is exceeding turn-on threshold | $t_{HSGDendel}$  | -      | 2.3  | 4.1  | $\mu\text{s}$ | $V_{HSVCC} = 11\text{ V}$                                         |

| HSGD voltage at high state                                                  | $V_{HSGDhigh}$   | 10     | 11   | 12   | V             | $I_{HSGD} = -20\text{ mA}$                                        |

| HSGD voltage at active shutdown                                             | $V_{HSGDaSD}$    | -      | 25   | 200  | mV            | $I_{HSGD} = 20\text{ mA}$ , $V_{HSVCC} = 5\text{ V}$              |

| HSGD peak source current                                                    | $-I_{HSGDpksrc}$ | 130    | -    | -    | mA            |                                                                   |

| HSGD peak sink current                                                      | $I_{HSGDpksnk}$  | 450    | -    | -    | mA            |                                                                   |

| HSGD driver output low impedance                                            | $R_{HSGDLS}$     | -      | -    | 5    | $\Omega$      | $I_{HSGD} = 100\text{ mA}$                                        |

## 5.4.4 总线电压检测 (PFCVS引脚)

表9 PFCVS引脚的电气特性

| Parameter                                           | Symbol          | Values |      |      | Unit          | Note or condition                       |

|-----------------------------------------------------|-----------------|--------|------|------|---------------|-----------------------------------------|

|                                                     |                 | Min.   | Typ. | Max. |               |                                         |

| Leakage current                                     | $I_{PFCVSlk}$   | -0.2   | -    | 0.2  | $\mu\text{A}$ | $0\text{ V} < V_{PFCVS} < 2.9\text{ V}$ |

| Dynamic voltage range                               | $V_{PFCVS}$     | 0.13   | -    | 2.75 | V             |                                         |

| Second level oversupply protection (OVP2) threshold | $V_{PFCVSovp2}$ | 2.7    | 2.8  | 2.9  | V             |                                         |

| PFC softstart time-out                              | $t_{startPFC}$  | -      | 500  | -    | ms            |                                         |

## 5 Electrical characteristics

## 5.4.5 PFC 电流检测和过零检测 (PFCCS 引脚)

表 10 PFCCS 引脚的电气特性

| Parameter                                  | Symbol              | Values |      |      | Unit | Note or condition |

|--------------------------------------------|---------------------|--------|------|------|------|-------------------|

|                                            |                     | Min.   | Typ. | Max. |      |                   |

| Overcurrent protection (OCP) threshold     | $V_{PFCCSocp}$      | 605    | 638  | 671  | mV   |                   |

| Overcurrent protection (OCP) blanking time | $t_{PFCCSocp}$      | 37.5   | 47.4 | 58.1 | ns   |                   |

| ZCD comparator logic "0" threshold         | $V_{PFCCSzcd}$      | 0.42   | 0.54 | 0.66 |      |                   |

| ZCD comparator logic "1" threshold         | $V_{PFCCSzcdreset}$ | 1.41   | 1.53 | 1.65 | V    |                   |

## 5.4.6 混合反激式过零检测 (ZCD 引脚)

表 11 ZCD 引脚的电气特性

| Parameter                                                          | Symbol          | Values |      |      | Unit    | Note or condition                       |

|--------------------------------------------------------------------|-----------------|--------|------|------|---------|-----------------------------------------|

|                                                                    |                 | Min.   | Typ. | Max. |         |                                         |

| Leakage current                                                    | $I_{ZCDlk}$     | -10    | -    | 10   | $\mu A$ | $V_{ZCD} = 0 \text{ V} / 3.0 \text{ V}$ |

| Maximum pin voltage threshold for $V_{out}$ overvoltage protection | $V_{ZCDOVPmax}$ | -      | 2.75 | -    | V       |                                         |

| Zero-crossing detection threshold                                  | $V_{ZCDTHR}$    | 15     | 40   | 70   | mV      | Falling slope                           |

| Input voltage negative clamping                                    | $-V_{ZCDCLN}$   | 140    | 180  | 220  | mV      |                                         |

## 5.4.7 多功能输入输出 (MFIO 引脚)

表 12 MFIO 引脚的电气特性

| Parameter                                     | Symbol         | Values |           |      | Unit       | Note or condition                            |

|-----------------------------------------------|----------------|--------|-----------|------|------------|----------------------------------------------|

|                                               |                | Min.   | Typ.      | Max. |            |                                              |

| Pull-up resistor                              | $R_{MFIOpu}$   | 8.8    | 11        | 13.2 | k $\Omega$ | <sup>8)</sup> MFIO <sub>funct</sub> = ExtOTP |

| Open circuit output voltage                   | $V_{MFIOoc}$   | -      | $V_{REF}$ | -    | V          | <sup>8)</sup> MFIO <sub>funct</sub> = ExtOTP |

| Input high current with active weak pull-down | $-I_{MFIOhpd}$ | 90     | -         | 300  | $\mu A$    | Measured at min. $V_{MFIOIH}$                |

| Leakage current                               | $I_{MFIOlk}$   | -5     | -         | 1    | $\mu A$    | $V_{MFIO} = 0 \text{ V} / 3.0 \text{ V}$     |

| Input capacitance                             | $C_{MFIOIN}$   | -      | -         | 10   | pF         |                                              |

| Input threshold for logic "0"                 | $V_{MFIOIL}$   | -      | -         | 1    | V          | <sup>8)</sup>                                |

| Input threshold for logic "1"                 | $V_{MFIOIH}$   | 2      | -         | -    | V          | <sup>8)</sup>                                |

| Output voltage for logic "0"                  | $V_{MFIOOL}$   | -      | -         | 0.8  | V          | <sup>8)</sup> $I_{MFIOOL} = 2 \text{ mA}$    |

(表格续下页.....)

<sup>8</sup> During active phase

## 5 Electrical characteristics

表 12 (续) MFIO 引脚的电气特性

| Parameter                              | Symbol         | Values |      |      | Unit | Note or condition                          |

|----------------------------------------|----------------|--------|------|------|------|--------------------------------------------|

|                                        |                | Min.   | Typ. | Max. |      |                                            |

| Output voltage for logic “1”           | $V_{MFIOOH}$   | 2.2    | -    | -    | V    | <sup>8)</sup> $I_{MFIOOH} = -2 \text{ mA}$ |

| Maximum output sink current            | $I_{MFIOOL}$   | -      | -    | 2    | mA   | <sup>8)</sup>                              |

| Maximum output source current          | $-I_{MFIOOH}$  | -      | -    | 2    | mA   | <sup>8)</sup>                              |

| Output rise time ( $0 \rightarrow 1$ ) | $t_{MFIOrise}$ | -      | -    | 25   | ns   | 20 pF load                                 |

| Output fall time ( $1 \rightarrow 0$ ) | $t_{MFIOfall}$ | -      | -    | 25   | ns   | 20 pF load                                 |

## 5.4.8 混合反激式电流感应 (CS 引脚)

表 13 CS 引脚的电气特性

| Parameter                       | Symbol         | Values |      |      | Unit          | Note or condition                                                |

|---------------------------------|----------------|--------|------|------|---------------|------------------------------------------------------------------|

|                                 |                | Min.   | Typ. | Max. |               |                                                                  |

| Leakage current                 | $I_{CSlk}$     | -10    | -    | 10   | $\mu\text{A}$ | $0 \text{ V} < V_{CS} < 2.8 \text{ V}$                           |

| Maximum operating current range | $V_{CSTHRmax}$ | 394    | 426  | 458  | mV            |                                                                  |

| CSTHR propagation delay         | $t_{CSTHRpd}$  | 121    | 213  | 305  | ns            | input signal slope,<br>$dV_{CS}/dt = 150 \text{ mV}/\mu\text{s}$ |

| CSPROT threshold                | $V_{CSPROT}$   | 550    | 600  | 650  | mV            |                                                                  |

## 5.4.9 混合反激输出反馈 (FB 引脚)

表 14 FB 引脚的电气特性

| Parameter                      | Symbol         | Values |      |       | Unit | Note or condition                   |

|--------------------------------|----------------|--------|------|-------|------|-------------------------------------|

|                                |                | Min.   | Typ. | Max.  |      |                                     |

| Open circuit output voltage    | $V_{FBoc}$     | 3.04   | 3.2  | 3.36  | V    |                                     |

| Threshold maximum usable range | $V_{FBOPmax}$  | -      | -    | 2.428 | V    |                                     |

| Burst mode wake-up threshold   | $V_{FBBMctrl}$ | 510    | 580  | 610   | mV   | During sleep phase<br>in burst mode |

<sup>8</sup> During active phase

## 5 Electrical characteristics

## 5.4.10 低侧栅极驱动器 (LSGD引脚)

表 15 LSGD 引脚的电气特性

| Parameter                   | Symbol           | Values |      |      | Unit     | Note or condition                                      |

|-----------------------------|------------------|--------|------|------|----------|--------------------------------------------------------|

|                             |                  | Min.   | Typ. | Max. |          |                                                        |

| Voltage at active shutdown  | $V_{LSGDaSD}$    | -      | -    | 1.6  | V        | $I_{LSGD} = 5 \text{ mA}$ ,<br>$V_{VCC} = 5 \text{ V}$ |

| Peak sink current           | $I_{LSGDpksnk}$  | 500    | -    | -    | mA       | $V_{LSGD} = 4.0 \text{ V}$                             |

| Peak source current         | $-I_{LSGDpksrc}$ | -      | 120  | -    | mA       |                                                        |

| Driver output low impedance | $R_{LSGDSL}$     | -      | -    | 7.0  | $\Omega$ | $I_{LSGD} = 100 \text{ mA}$                            |

## 5.4.11 PFC 栅极驱动器 (PFCGD 引脚)

表 16 PFCGD 引脚的电气特性

| Parameter                   | Symbol            | Values |      |      | Unit     | Note or condition                                       |

|-----------------------------|-------------------|--------|------|------|----------|---------------------------------------------------------|

|                             |                   | Min.   | Typ. | Max. |          |                                                         |

| Nominal output high voltage | $V_{PFCGDhigh}$   | 9.9    | 10.5 | 11.1 | V        | $I_{PFCGD} = -20 \text{ mA}$                            |

| Voltage at active shutdown  | $V_{PFCGDaSD}$    | -      | -    | 1.6  | V        | $I_{PFCGD} = 5 \text{ mA}$ ,<br>$V_{VCC} = 5 \text{ V}$ |

| Peak sink current           | $I_{PFCGDpksnk}$  | 800    | -    | -    | mA       | $V_{PFCGD} = 4.0 \text{ V}$                             |

| Peak source current         | $-I_{PFCGDpksrc}$ | -      | 360  | -    | mA       |                                                         |

| Driver output low impedance | $R_{PFCGDSL}$     | -      | -    | 4.4  | $\Omega$ | $I_{PFCGD} = 100 \text{ mA}$                            |

## 5.4.12 中央控制功能

表 17 中央控制功能的电气特性

| Parameter                                   | Symbol         | Values |               |       | Unit          | Note or condition |

|---------------------------------------------|----------------|--------|---------------|-------|---------------|-------------------|

|                                             |                | Min.   | Typ.          | Max.  |               |                   |

| VDDP power supply                           | $V_{VDDP}$     | 3.04   | 3.2           | 3.36  | V             |                   |

| VREF reference voltage                      | $V_{VREF}$     | 2.391  | 2.428         | 2.465 | V             |                   |

| Main clock oscillation period time base     | $t_{MCLK}$     | 15     | 15.8          | 16.6  | ns            |                   |

| Stand-by clock oscillation period time base | $t_{STBCLK}$   | 9      | 10            | 11.2  | $\mu\text{s}$ |                   |

| Slow task period time base                  | $t_{SLWTASK}$  | 111    | 120           | 129   | $\mu\text{s}$ |                   |

| Very slow task period time base             | $t_{VSLWTASK}$ | 4.68   | 5             | 5.32  | ms            |                   |

| Sampling time period                        | $t_{sample}$   | -      | $t_{SLWTASK}$ | -     | $\mu\text{s}$ |                   |

(表格续下页.....)

## 5 Electrical characteristics

表 17 (续) 中央控制功能的电气特性

| Parameter                                                                    | Symbol                  | Values |      |      | Unit | Note or condition                                                                       |

|------------------------------------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------|

|                                                                              |                         | Min.   | Typ. | Max. |      |                                                                                         |

| Restart step time base for auto-restart mode                                 | $t_{ARMbase}$           | 270    | 300  | 336  | ms   | Base for configurable auto-restart time $t_{ARM}$ when auto-restart mode entered        |

| Limited maximum change in on-time control for HS switch during CRM operation | $\Delta t_{HSonmaxCRM}$ | 75     | 80   | 85   | ns   | CRM operation, $t_{HSon}$ not limited by $V_{CSSET}$ , only applies for small $V_{bus}$ |

| Blanking time for brown-out protection                                       | $t_{bo}$                | -      | 70   | -    | ms   |                                                                                         |

## 6 封装尺寸

## 6 封装尺寸

您可以在我们的英飞凌网页“产品：<http://www.infineon.com/products>”上找到我们所有的封装、包装种类和其他信息。

图29 PG-DSO-14外形图

图 30 PG-DSO-14 封装

绿色产品（符合 RoHS 标准）

为了满足全球客户对环保产品的需求，并遵守政府法规，该器件以绿色产品的形式提供。绿色产品符合 RoHS 标准（即，引线采用无铅涂层，并且符合 IPC/JEDEC J-STD-020 标准，适用于无铅焊接）。更多封装信息请访问：<https://www.infineon.com/packages>

## 7 修订记录

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| Rev 1.0          | 2025-02-18      | Initial release        |

## 免责声明

请注意，本文件的原文使用英文撰写，为方便客户浏览英飞凌提供了中文译文。该中文译文仅供参考，并不可作为任何论点之依据。

由于翻译过程中可能使用了自动化程序，以及语言翻译和转换过程中的差异，最后的中文译文与最新的英文版本原文含义可能存在不尽相同之处。

因此，我们同时提供该中文译文版本的最新英文原文供您阅读，请参见 <http://www.infineon.com>

英文原文和中文译文版本之间若存有任何歧异，以最新的英文版本为准，并且仅认可英文版本为正式文件。

**您如果使用本文件，即表示您同意并理解上述说明。英飞凌不对因翻译过程中可能存在的任何不完整或不准确信息而产生的任何直接或间接损失或损害负责。英飞凌不承担中文译文版本的完整性和准确性责任。如果您不同意上述说明，请不要使用本文件。**

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

## 重要通知

**Infineon Technologies AG** 及其关联公司（以下简称“英飞凌”）销售或提供和交付的产品（可能也包括样品，且可能由硬件或软件或两者组成）

（以下简称“产品”），应遵守客户与英飞凌签订的框架供应合同或其他书面协议的条款和条件，如无上述合同或其他书面协议，则应遵守适用的英飞凌销售条件。只有在英飞凌明确书面同意的情况下，客户的一般条款和条件或对适用的英飞凌销售条件的偏离才对英飞凌具有约束力。

为避免疑义，英飞凌不承担不侵犯第三方权利的所有保证和默示保证，例如对特定用途/目的的适用性或适销性的保证。

英飞凌对与样品、应用或客户对任何产品的具体使用有关的任何信息或本文档中给出的任何示例或典型值概不负责。

本文件中包含的数据仅供具有技术资格和技能的客户代表使用。客户有责任评估产品对预期应用和客户特定用途的适用性，并在预期应用和客户特定用途中验证本文件中包含的所有相关技术数据。客户有责任正确设计、编程和测试预期应用的功能性和安全性，并遵守与其使用相关的法律要求。

除非英飞凌另行明确批准，否则产品不得用于任何因产品故障或使用产品的任何后果可合理预期会导致人身伤害的应用。但是，上述规定并不妨碍客户在英飞凌明确设计和销售的使用领域中使用任何产品，但是客户对应用负有全部责任。

英飞凌明确保留根据适用法律，如《德国版权法》(UrhG) 第 44b 条，将其内容用于商业资料和数据探勘 (TDM) 的权利。

如果产品包含安全功能：

由于任何计算设备都不可能绝对安全，尽管产品采取了安全措施，但英飞凌不保证产品不会被入侵、数据不会被盗或遗失，或不会发生其他漏洞（以下简称“安全漏洞”），英飞凌对任何安全漏洞不承担责任。

如果本文档包含或引用软件：

根据美国、德国和世界其他国家的知识产权法律和条约，该软件归英飞凌所有。英飞凌保留所有权利。因此，您只能按照软件附带的软件授权协议的规定使用本软件。

如果没有适用的软件授权协议，英飞凌特此授予您个人的、非排他性的、不可转让的软件知识产权授权（无权转授权）：(a) 对于以源代码形式提供的软件，仅在贵组织内部修改和复制该软件用于英飞凌硬件产品；及(b) 对于以二进制代码(binary code)形式对外向终端用户分发该软件，仅得用于英飞凌硬件产品。禁止对本软件进行任何其他使用、复制、修改、翻译或编译。有关产品、技术、交货条款和条件以及价格的详细信息，请联系离您最近的英飞凌办公室或访问 <https://www.infineon.com>。

版本 2025-12-24

**Infineon Technologies AG** 出版，

德国 Neubiberg 85579

版权 © 2025 Infineon Technologies AG

及其关联公司。

保留所有权利。

**Do you have a question about this

document?**

Email:

[erratum@infineon.com](mailto:erratum@infineon.com)