# **Preliminary Datasheet**

#### **Features**

- Wide input voltage range: 7 V to 80 V with surge immunity

- Integrated 100 V, ~3.2 m $\Omega$  OptiMOS<sup>TM</sup> FET with current sensor

- Digital controller and built-in GATE driver

- Maximum continuous current: up to 20 A

- Inrush current protection using digital SOA control with active FET SOA protection

- Parallel operation for higher current applications with active current sharing at start-up

- "Primary/standalone" or "secondary" device operation mode for stacking multiple eFuses

- Integrated die temperature sensor

- Analog current (IMON) reporting and monitoring with up to  $\pm 1\%$  accuracy

- Dedicated current and voltage ADCs: 12-bit resolution

- Accurate telemetry:  $V \le \pm 0.5\%$ ,  $I \le \pm 1\%$ ,  $P \le \pm 2\%$ ,  $E \le \pm 3\%$

- Telemetry averaging (V, I, P) with "peaks and valleys"

- · Fast, programmable short circuit protection

- Programmable fault response: auto-retry and latch-off

- Programmable fault protections: input undervoltage, input overvoltage, output undervoltage, overcurrent, severe overcurrent, turn-on time, pre-charged output voltage (VDS), FET health, thermal shutdown, etc.

- PMBus<sup>TM</sup> v1.3 interface with up to 1 MHz speed

- Permanent WRITE protection

- One-time programmable non-volatile memory

- At least seven unique programmable device addresses

- · Sequential turn-on capability

- IPC2221B and IPC9592B high-voltage compliant

- PG-LIQFN-23 lead, 6 mm x 5 mm package

- - 40°C to + 125°C operating junction temperature

#### **Potential applications**

- · Servers and datacenters

- Fan tray/control applications

- · Power distribution systems

- Industrial systems

- · Network routers and switches

#### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

#### Description

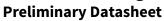

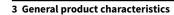

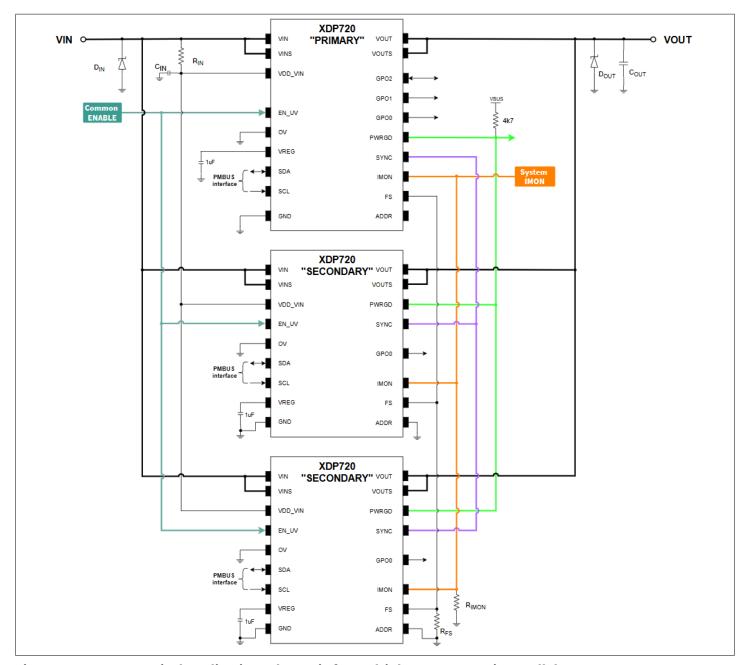

XDP720 is a 20 A smart eFuse with integrated  $\sim 3.2 \text{ m}\Omega \text{ R}_{DS(on)}$  OptiMOS<sup>TM</sup> FET, current sensor, digital controller and a built-in GATE driver. It is an IPC2221B and IPC9592B HV standard compliant device that ensures reliable inrush current control and continuous system health monitoring. The digital SOA control with active SOA protection ensures that the integrated MOSFET always operates under safe conditions. When multiple XDP720 ICs are connected in parallel, the active current sharing during start-up maintains safety conditions in high-power systems. A simplified schematic is shown below for reference.

XDP720 provides accurate system telemetry (V, I, P, T, E) and reports analog current at the IMON pin for post-processing. It incorporates various system protections and generates appropriate protection responses depending on the incident's severity. Auto-retry and latch-off are the allowed response types. The XDP720 has a one-time programmable non-volatile memory and a high-speed PMBus<sup>TM</sup> interface for communication.

The device is available in a 6 mm x 5 mm 23pin PG-LIQFN package and is specified over a - 40°C to + 125°C junction temperature range.

Description

2

# **Table of contents**

Table of contents

|            | Table of contents                | 3    |

|------------|----------------------------------|------|

| 1          | Pin configuration                | 6    |

| 2          | Functional description           | 9    |

| 2.1        | Operational states               | 9    |

| 2.2        | Configuration modes              | 13   |

| 2.3        | Power-up sequence                | 14   |

| 2.3.1      | FailSafe                         | 14   |

| 2.3.2      | SYNC procedure                   | 14   |

| 2.3.3      | Enable and disable               | 15   |

| 2.3.3.1    | Undervoltage function            | . 16 |

| 2.3.3.2    | Overvoltage function             | 17   |

| 2.4        | Inrush current control           | 17   |

| 2.5        | Current limit settings           | 20   |

| 2.5.1      | Start-up current setting         | 20   |

| 2.5.2      | Overcurrent setting              | . 20 |

| 2.5.2.1    | System overcurrent setting       | 20   |

| 2.5.2.2    | Local/backup overcurrent setting | . 21 |

| 2.5.3      | Severe overcurrent setting       | 21   |

| 2.6        | Power good (PWRGD)               | . 21 |

| 2.7        | Thermal protection               | 21   |

| 2.8        | Restart                          | . 21 |

| 2.9        | MOSFET power down                | . 22 |

| 2.10       | Quick output discharge           | 22   |

| 2.11       | General purpose pins             | 22   |

| 2.12       | Protections                      | . 23 |

| 2.12.1     | Faults                           | 23   |

| 2.12.1.1   | Memory fault                     | 24   |

| 2.12.1.2   | Damaged MOSFET faults            | . 25 |

| 2.12.1.3   | Voltage faults                   | 25   |

| 2.12.1.4   | Current faults                   | . 27 |

| 2.12.1.5   | Thermal faults                   | 29   |

| 2.12.1.6   | Power-up faults                  | 29   |

| 2.12.1.7   | Internal protection fault        | 31   |

| 2.12.2     | Fault response                   | 31   |

| 2.12.2.1   | Auto-retry                       | 31   |

| 2.12.2.2   | Latch-off                        | 31   |

| 2.12.2.2.1 | Latch-off release                | . 32 |

| 2.12.3     | Input surge immunity             | 32   |

| 2.12.4     | Warnings                         | 33   |

|            |                                  |      |

# **Preliminary Datasheet**

Table of contents

| 2.12.4.1 | Damaged MOSFET warning                | 34 |

|----------|---------------------------------------|----|

| 2.12.4.2 | Voltage warnings                      | 34 |

| 2.12.4.3 | Current warnings                      | 35 |

| 2.12.4.4 | Power warning                         | 35 |

| 2.12.4.5 | Thermal warnings                      | 35 |

| 2.12.4.6 | Communication warning                 | 35 |

| 2.12.5   | UV throttle                           | 35 |

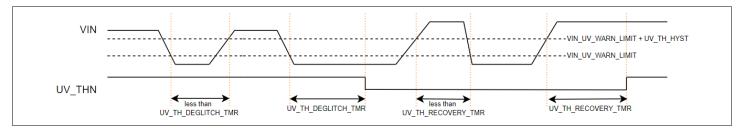

| 2.13     | Telemetry                             | 36 |

| 2.13.1   | Averaged and instantaneous telemetry  | 38 |

| 2.13.2   | Peaks and valleys                     | 39 |

| 2.13.3   | Telemetry via PMBus                   | 39 |

| 2.13.4   | Input power calculation               | 41 |

| 2.13.5   | Energy calculation                    | 41 |

| 2.14     | Communication interface (PMBus)       | 41 |

| 2.14.1   | Supported functions                   | 42 |

| 2.14.1.1 | Addressing                            | 42 |

| 2.14.1.2 | Protocol violations                   | 42 |

| 2.14.1.3 | Timeout                               | 42 |

| 2.14.2   | Protocol                              | 42 |

| 2.14.2.1 | Alert response address (ARA) protocol |    |

| 2.14.3   | PMBus commands                        | 47 |

| 2.14.4   | Permanent write protection            | 51 |

| 2.15     | Memory                                | 51 |

| 3        | General product characteristics       | 53 |

| 3.1      | Absolute maximum ratings              | 53 |

| 3.2      | Functional range                      | 54 |

| 3.3      | Thermal characteristics               | 55 |

| 3.4      | ESD robustness                        | 55 |

| 3.5      | Electrical characteristics            | 56 |

| 3.6      | Timing characteristics                | 64 |

| 4        | Application information               | 70 |

| 4.1      | Standalone operation                  | 70 |

| 4.2      | Parallel operation                    | 71 |

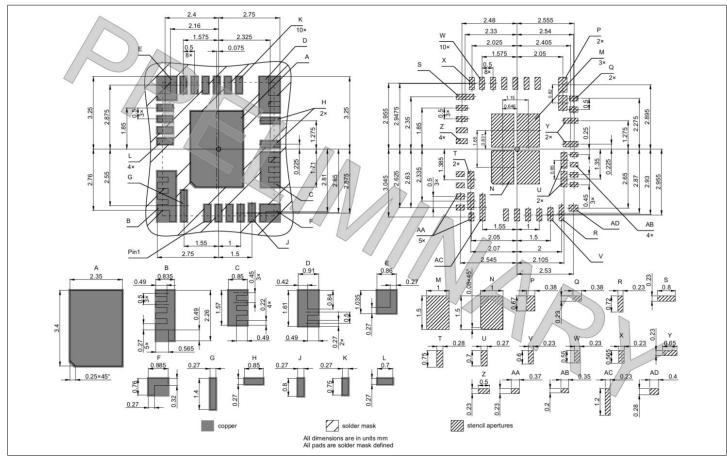

| 4.3      | Layout guidelines                     | 74 |

| 4.4      | PMBus direct format data conversion   | 75 |

| 4.4.1    | Voltage                               | 75 |

| 4.4.2    | Current                               | 76 |

| 4.4.3    | Temperature                           | 77 |

| 4.4.4    | Power                                 | 77 |

| 4.4.5    | Energy                                | 78 |

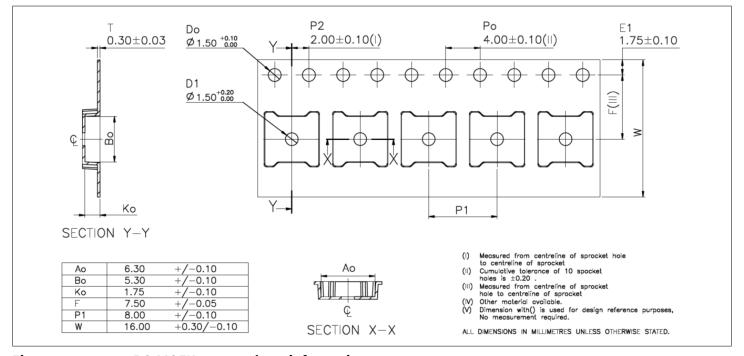

| 5        | Package information                   | 81 |

|          |                                       |    |

# **Preliminary Datasheet**

# Table of contents

|     | Disclaimer           | 25 |

|-----|----------------------|----|

| 6   | Revision history     | 84 |

| 5.2 | Package outline      | 81 |

| 5.1 | Ordering information | 81 |

|     |                      |    |

# **Preliminary Datasheet**

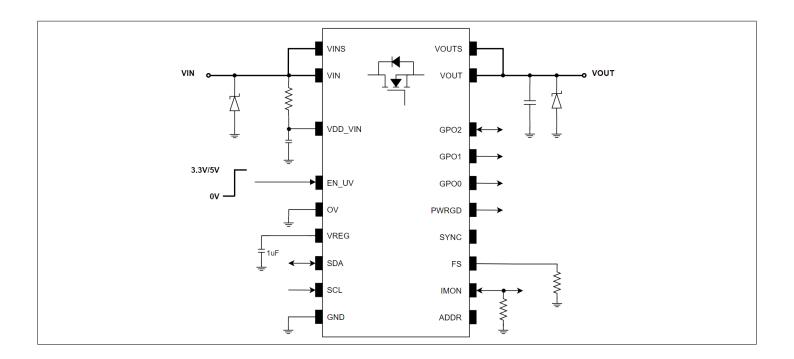

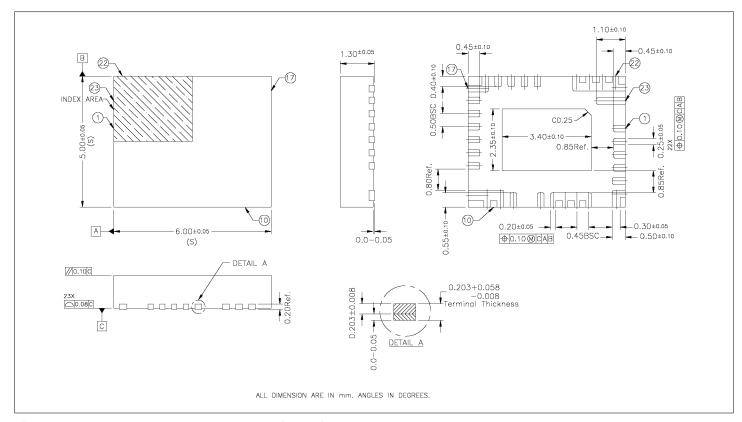

1 Pin configuration

# 1 Pin configuration

Figure 1 XDP720 device pinout (top view)

# Table 1 XDP720 pinout

| Pin<br># | Name | Typ<br>e | Description                                                                                                                                                                                                                                        | If unused, connect to                                    |

|----------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1        | VREG | 0        | VREG (internal 5 V regulator) output pin. A 1 μF capacitor from this pin to GND is mandatory.                                                                                                                                                      | Connect a 1 $\mu\text{F}$ capacitor from this pin to GND |

| 2        | IMON | Ю        | Analog current monitor pin.  This pin reports/sources a current proportional to the monitored MOSFET current (IMON) level. This pin is also monitored for current protection levels and telemetry. A resistor is recommended from this pin to GND. | Open                                                     |

| 3        | FS   | I        | Fail-safe pin for turn-on fail safety. A resistor greater than 8.9 $k\Omega$ is recommended from this pin to GND.                                                                                                                                  | Open                                                     |

| 4, 21    | NC   | -        | Not connected pin.                                                                                                                                                                                                                                 | -                                                        |

(table continues...)

# **Preliminary Datasheet**

1 Pin configuration

# Table 1 (continued) XDP720 pinout

| Pin<br>#  | Name                            | Typ<br>e | Description                                                                                                                                                                                                                                                                                                                                                    | If unused, connect to              |

|-----------|---------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 5         | GND                             | -        | Ground reference terminal (to be connected to system ground).                                                                                                                                                                                                                                                                                                  | GND                                |

| 6         | ADDR                            | I        | Device address configuration input pin.  It can be left open or tied to GND through a resistor for a total of seven unique PMBus <sup>TM</sup> device addresses. This pin is also used to configure the device mode. If this pin is directly tied to GND then the device operates as "SECONDARY" device, otherwise it operates as "PRIMARY/standalone" device. | Open                               |

| 7         | VOUT                            | 0        | Output voltage terminal.                                                                                                                                                                                                                                                                                                                                       | VOUT                               |

| 8         | VOUTS                           | I        | Output voltage sense pin.                                                                                                                                                                                                                                                                                                                                      | VOUT                               |

| 9         | VDD_VIN                         | I        | Power supply pin. A 100 $\Omega$ –100 nF RC filter is recommended at this pin.                                                                                                                                                                                                                                                                                 | VIN                                |

| 10,<br>22 | VIN                             | I        | Input voltage terminal.                                                                                                                                                                                                                                                                                                                                        | VIN                                |

| 11        | SDA                             | Ю        | PMBus™ data open drain pin.                                                                                                                                                                                                                                                                                                                                    | Pull-up to VREG or external source |

| 12        | SCL                             | I        | PMBus™ clock input pin. The interface is rated to 1 MHz.                                                                                                                                                                                                                                                                                                       | Pull-up to VREG or external source |

| 13        | GPO0/<br>FAULT/<br>SMBALER<br>T | 0        | General-purpose digital output 0. Pin configuration is programmable. FAULT open drain output. This pin asserts low when a fault has occurred. The faults that can trigger this pin are configurable. SMBALERT open drain output. It can be selected to report (active Low) faults and/or warnings. Default configuration: FAULT                                | Open                               |

| 14        | GPO1/<br>WARN                   | 0        | General-purpose digital output 1. Pin configuration is programmable. Warning open drain output. This pin is asserted low when a warning is triggered. The warnings that can trigger this pin are configurable. Default configuration: WARN                                                                                                                     | Open                               |

(table continues...)

# **Preliminary Datasheet**

1 Pin configuration

# Table 1 (continued) XDP720 pinout

| Pin<br># | Name                             | Typ<br>e | Description                                                                                                                                                                                                                                                                                                                                                                             | If unused, connect to |

|----------|----------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 15       | GPO2/<br>UV_THN/<br>RESTART<br>N | Ю        | General-purpose digital output 2. Pin configuration is programmable. UV throttle open drain output. This pin asserts low during input undervoltage throttling. RESTARTN input. Falling edge triggered automatic restart input (with internal pull-up resistor of 100 k $\Omega$ ). The MOSFET remains off for a configured time and then turns back on. Default configuration: RESTARTN | Open                  |

| 16       | EN_UV                            | I        | Enable/input undervoltage pin.  The MOSFET is turned on when $V_{\text{EN\_UV}} \ge V_{\text{EN\_UV\_UTH}}$ .  The UV fault is triggered if $V_{\text{EN\_UV}}$ level is lower than $V_{\text{UV\_LTH\_P}}$ (or $V_{\text{UV\_LTH\_S}}$ ).                                                                                                                                              | Pull-up to VREG       |

| 17       | DNC                              | -        | Do not connect pin.                                                                                                                                                                                                                                                                                                                                                                     | Open                  |

| 18       | OV                               | I        | Input overvoltage pin.  The OV fault is triggered if $V_{\text{OV}} > V_{\text{OV\_UTH}}$ .                                                                                                                                                                                                                                                                                             | -                     |

| 19       | PWRGD                            | 0        | Power good open drain output pin. It is asserted HIGH when VOUT has reached its final level i.e. steady state, the MOSFET is fully enhanced and no faults are detected.                                                                                                                                                                                                                 | Open                  |

| 20       | SYNC                             | 10       | SYNC open drain pin with internal pull-up. This pin is used to synchronize multiple XDP72x devices connected in parallel. It is similar to the FAULT pin with one exception, see details.                                                                                                                                                                                               | Open                  |

| 23       | VINS                             | I        | Input voltage sense pin.                                                                                                                                                                                                                                                                                                                                                                | VIN                   |

| EP       | VIN                              | I        | Input voltage terminal.                                                                                                                                                                                                                                                                                                                                                                 | VIN                   |

# **Preliminary Datasheet**

2 Functional description

# 2 Functional description

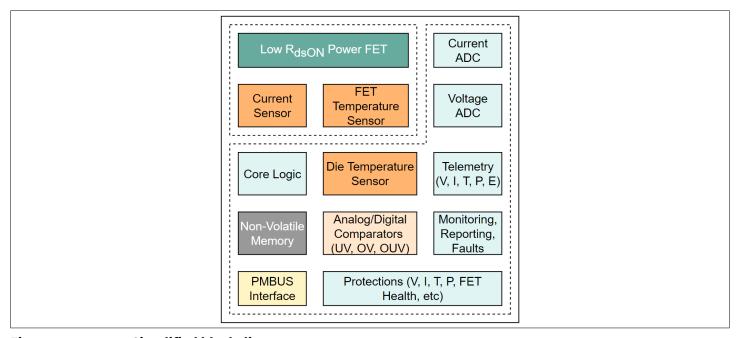

The XDP720 is a 20 A smart eFuse with integrated low R<sub>DS(on)</sub> OPTIMOS<sup>TM</sup> FET, current sensor, die temperature sensors, digital controller and a built-in GATE driver. It is PMBus<sup>TM</sup> v1.3 compliant, which allows the system microcontroller to control, configure and debug the device as well as monitor its telemetry data.

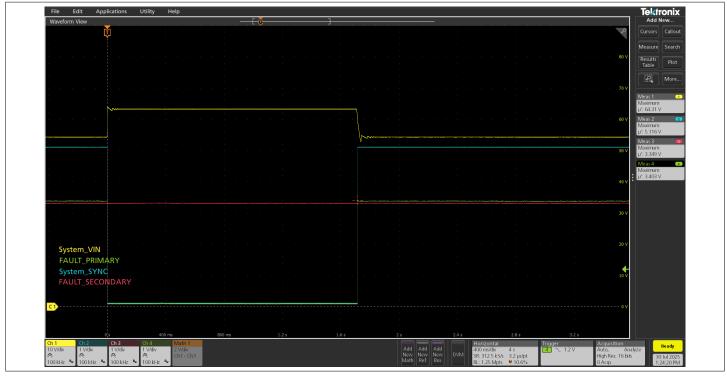

The device becomes fully operational when the voltage on the VDD\_VIN pin crosses 9 V. If there are no faults and the EN\_UV pin is pulled HIGH, then the enable deglitch timer is initiated which allows the input supply on VIN pins to stabilize. The device waits until this timer has expired and then starts the MOSFET turn-on procedure. Its proprietary digital SOA control ensures that the inrush current never exceeds the safe operating limits of the MOSFET. The device establishes stable output voltage at VOUT pins after the MOSFET is successfully turned on. The PWRGD pin is used to signal the load/microcontroller that VOUT is ready.

The input voltage, current, output voltage, internal MOSFET temperature and internal controller temperature are constantly monitored by the device for proper telemetry and protection. It also reports a current proportional to the current flowing through the device on the IMON pin. There are many protections incorporated in this device to protect itself and the system load. These include input undervoltage, input overvoltage, overcurrent, severe overcurrent, overtemperature, thermal shutdown and MOSFET health checks to name a few. All these protection-related settings are configured using PMBus<sup>TM</sup> commands. Also, it can intelligently protect the system load against input surge events. Depending on the retry settings, the device will either auto-retry or latch-off when a fault event has occurred. A dedicated user-triggerable RESTARTN pin/command is also available which will turn-off the MOSFET and then turns it back on after the RESTART timer has expired. This device has the ability to quickly discharge its output voltage based on the configuration. The one-time programmable (OTP) section of the memory allows the user to permanently store the device configuration. To enhance security, this device also comes with a "permanent WRITE protection" feature which makes it immune to all the future PMBus<sup>TM</sup> WRITE operations.

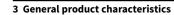

This device is designed to address the ever-increasing power demands of the market. Multiple XDP72x devices can be connected in parallel to increase the system power. The SYNC pin and FS pin always ensure that all the devices in the chain are synchronized, and the main/PRIMARY device is alive in the system. A fault in any device will cause all the devices to turn off their MOSFETs, thus disconnecting the system load from the input supply. The PRIMARY device will then react according to its fault response settings whereas the SECONDARY devices will simply follow the PRIMARY device.

Figure 2 Simplified block diagram

# 2.1 Operational states

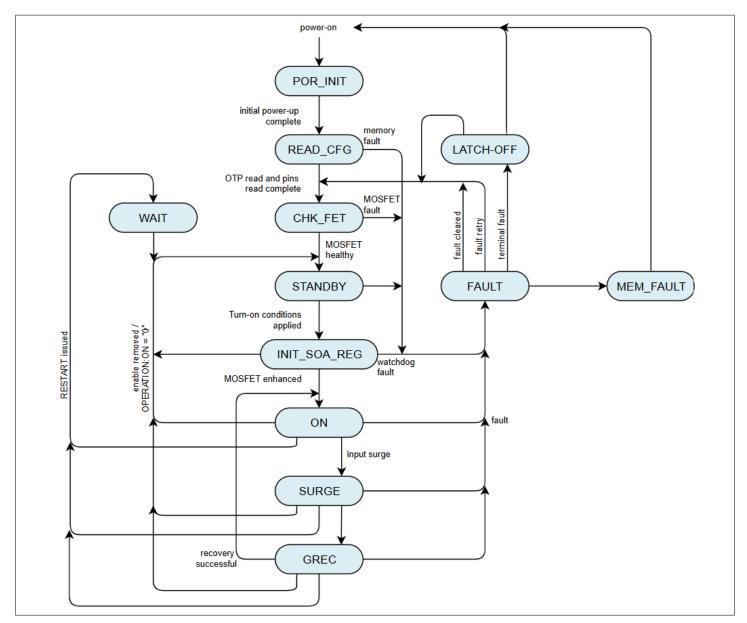

A simplified device state machine is shown in Figure 3. It shows all the important state transitions to understand the device operation.

# **Preliminary Datasheet**

2 Functional description

Figure 3 Simplified state machine

Table 2 Operational states description

|                       | State | Name     | Description                                                                                 | Next state | Next state |

|-----------------------|-------|----------|---------------------------------------------------------------------------------------------|------------|------------|

|                       |       |          |                                                                                             | (no fault) | (fault)    |

| Initialization        | 0     | POR_INIT | Internal circuitry is initialized as soon as VDD_VIN > 7 V.                                 | READ_CFG   | NA         |

|                       | 1     | READ_CFG | POR and initialization complete.<br>OTP memory and external pins<br>are read at this point. | CHK_FET    | FAULT      |

| Power-up<br>procedure | 2     | CHK_FET  | MOSFET is checked for gate to source or gate to drain shorts.                               | STANDBY    | FAULT      |

(table continues...)

Datasheet

# **Preliminary Datasheet**

2 Functional description

Table 2 (continued) Operational states description

|                                        | State | Name         | Description                                                                                                                                                   | Next state (no fault)           | Next state (fault) |

|----------------------------------------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|

|                                        | 3     | STANDBY      | VIN is within a valid range (within UV and OV limits), device temperature is in appropriate range and EN signal is deasserted or OPERATION:ON bit is cleared. | INIT_SOA_REG                    | FAULT              |

|                                        |       |              | Device transitions to next<br>state when MOSFET turn-on<br>conditions are applied and<br>the EN_DG timer has expired.                                         |                                 |                    |

|                                        | 4     | INIT_SOA_REG | MOSFET turn-on watchdog timer starts running. SOA regulation phase:                                                                                           | ON or<br>STANDBY                | FAULT              |

|                                        |       |              | Device regulates the current according to the programmed SOA, depending on VDS value (see details) in order to charge the output capacitor.                   |                                 |                    |

|                                        |       |              | • INIT_SOA_REG phase stops when MOSFET $V_{\rm DS}$ < 1.0 V, $V_{\rm GS}$ > 7.8 V and no faults are detected during this procedure.                           |                                 |                    |

|                                        |       |              | Due to the current regulation, the time spent in this state depends on the output capacitance value.      Due to the current regulation, the STANDRY.         |                                 |                    |

|                                        |       |              | Device transitions to STANDBY state if EN is deasserted or OPERATION:ON bit is cleared.                                                                       |                                 |                    |

| lormal<br>peration i.e.<br>teady state | 5     | ON           | Steady state is reached i.e. MOSFET is fully enhanced.  Turn-on watchdog timer is                                                                             | ON or<br>STANDBY or<br>SURGE or | FAULT              |

|                                        |       |              | <ul><li>reset at this point.</li><li>IMON pin starts reporting the proportional current.</li></ul>                                                            | WAIT                            |                    |

|                                        |       |              | Device transitions to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or SURGE state (if input surge is detected) or WAIT state (if        |                                 |                    |

(table continues...)

# **Preliminary Datasheet**

(continued) Operational states description Table 2

|     | State | Name      | Description                                                                                                                                                                                                                                                                                                            | Next state (no fault)       | Next state (fault) |

|-----|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|

| dle | 7     | FAULT     | Fault has occurred. Device will stay idle in FAULT state until:                                                                                                                                                                                                                                                        | CHK_FET or LATCH_OFF        | NA                 |

|     |       |           | <ul> <li>Fault conditions are cleared<br/>in the case of non-retry<br/>dependent faults.</li> </ul>                                                                                                                                                                                                                    | _                           |                    |

|     |       |           | <ul> <li>Cool down timer expires in<br/>the case of retry dependent<br/>faults.</li> </ul>                                                                                                                                                                                                                             |                             |                    |

|     |       |           | If retry counter has expired or latch-off fault has occurred, then the device will go to LATCH_OFF state directly after FAULT.                                                                                                                                                                                         |                             |                    |

|     |       |           | In case of memory fault, the device transitions into MEM_FAULT.                                                                                                                                                                                                                                                        |                             |                    |

|     | 8     | LATCH_OFF | If the maximum number of retries has been reached, the device will latch off until faults are cleared and latch-off is released.                                                                                                                                                                                       | POR_INIT or CHK_FET         | NA                 |

|     | 9     | MEM_FAULT | If an OTP read or write error is detected, the device will go to FAULT and consecutively MEM_FAULT state, which initiates the controller's latch-off. A power cycle is required to go out of MEM_FAULT.                                                                                                                | POR_INIT<br>(power cycling) | NA                 |

|     | 10    | WAIT      | <ul> <li>A RESTART command has been issued by the user.</li> <li>Device turns off its MOSFET and stays in this state until restart timer expires.</li> <li>After this time, the device goes to STANDBY and, if the necessary conditions are met, MOSFET is automatically turned back on, going to ON state.</li> </ul> | STANDBY                     | NA                 |

(table continues...)

# **Preliminary Datasheet**

2 Functional description

Table 2 (continued) Operational states description

|    |       |                                                                                                                                                                                                                 | (no fault)                                                                                                                                                                                                                                                                                                                                                  | (fault)                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | SURGE | Input surge (high dv/dt) suppression state. Device transitions to GREC state to attempt recovery or to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or WAIT state (if RESTART is issued). | GREC or<br>STANDBY or<br>WAIT                                                                                                                                                                                                                                                                                                                               | FAULT                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12 | GREC  | Recovery is attempted by pulling the $V_{GS}$ to the MOSFET's threshold voltage level.                                                                                                                          | ON or<br>STANDBY or                                                                                                                                                                                                                                                                                                                                         | FAULT                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |       | Device transitions to ON state if recovery is successful or to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or WAIT state (if                                                             | WALL                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 12    | 12 GREC                                                                                                                                                                                                         | transitions to GREC state to attempt recovery or to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or WAIT state (if RESTART is issued).  12 GREC Recovery is attempted by pulling the V <sub>GS</sub> to the MOSFET's threshold voltage level.  Device transitions to ON state if recovery is successful or to STANDBY state (if EN is | transitions to GREC state to attempt recovery or to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or WAIT state (if RESTART is issued).  12  GREC  Recovery is attempted by pulling the V <sub>GS</sub> to the MOSFET's threshold voltage level. Device transitions to ON state if recovery is successful or to STANDBY state (if EN is deasserted or OPERATION:ON bit is cleared) or WAIT state (if |

# 2.2 Configuration modes

In XDP720, the ADDR pin is used to configure two important parameters namely the device mode of operation and the PMBus device address. This pin is sensed in the READ\_CFG state during the device start-up sequence. As shown in Table 3 below, the device mode can only be set by using an appropriate resistor value from this pin to ground (GND). However, the PMBus device address can be either programmed through the PMBUS\_CFG command when ADDR pin is open or GND, or as a byproduct of the ADDR pin resistor setting.

Table 3 Configuration of ADDR pin

| ADDR pin voltage (V)             | ADDR pin resistance ( $k\Omega$ ) | Device mode | Base address field [6:4]  | Device address field [3:0]                       |

|----------------------------------|-----------------------------------|-------------|---------------------------|--------------------------------------------------|

| V <sub>ADDR</sub> > 2.8 (Open)   | Open                              | PRIMARY     |                           | set via PMBUS_CFG<br>command (default =<br>0000) |

| $2.2 < V_{\text{ADDR}} \le 2.8$  | 24.9                              |             |                           | 0001                                             |

| $1.7 < V_{ADDR} \le 2.2$         | 19.6                              |             |                           | 0010                                             |

| $1.3 < V_{ADDR} \le 1.7$         | 15                                |             | set via PMBUS_CFG command | 0011                                             |

| $0.9 < V_{ADDR} \le 1.3$         | 11                                |             | Default = 001             | 0100                                             |

| $0.6 < V_{ADDR} \le 0.9$         | 7.5                               |             |                           | 0101                                             |

| $0.3 < V_{ADDR} \le 0.6$         | 4.53                              |             |                           | 0110                                             |

| $V_{ADDR} \le 0.3 \text{ (GND)}$ | GND                               | SECONDARY   |                           | set via PMBUS_CFG<br>command (default =<br>0000) |

Connecting this pin directly to GND configures the device as a SECONDARY device otherwise it is configured as a PRIMARY device. This is extremely useful in parallelizing multiple XDP720 devices for high power designs. In order to turn-on its MOSFET, the SECONDARY device relies on the  $I_{\rm FS}$  current from the PRIMARY device for failsafe check using

# **Preliminary Datasheet**

2 Functional description

the FS pin. The SECONDARY device does not have an independent retry capability as it simply follows the PRIMARY device in the system. Refer Chapter 4 section for high power design.

Similar to the device mode configuration, the comparators used for the input undervoltage (UV) and overvoltage (OV) protections can also be configured. By default, UV and OV faults are triggered by sensing the voltage at the VINS pin using internal digital comparators. If the user desires a faster response then the analog comparators at UV and OV pins can be used by configuring the MODE (MODE:MODE\_P and MODE:MODE\_S) command.

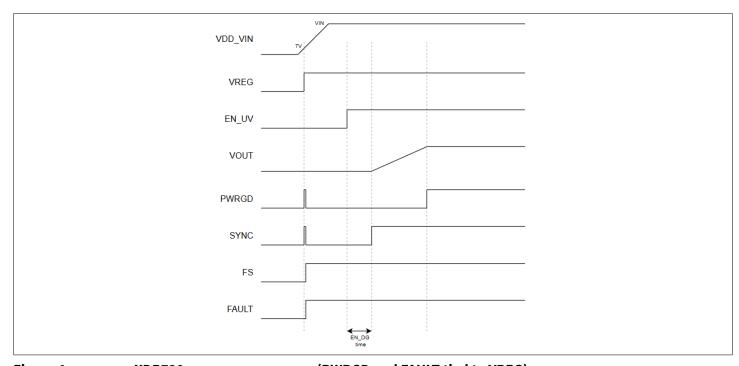

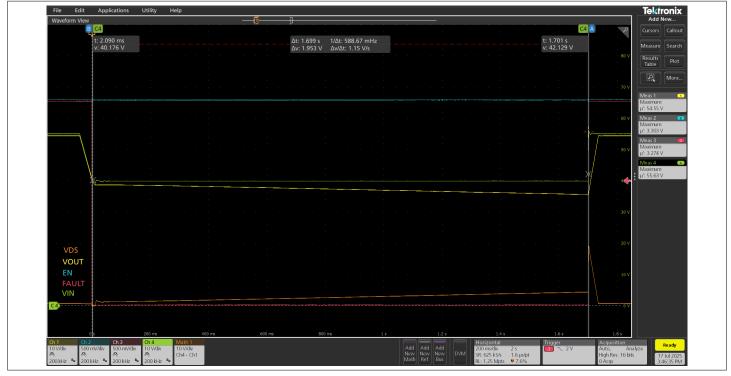

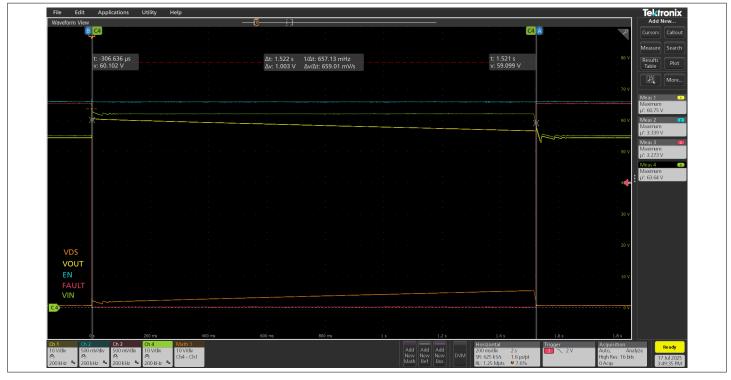

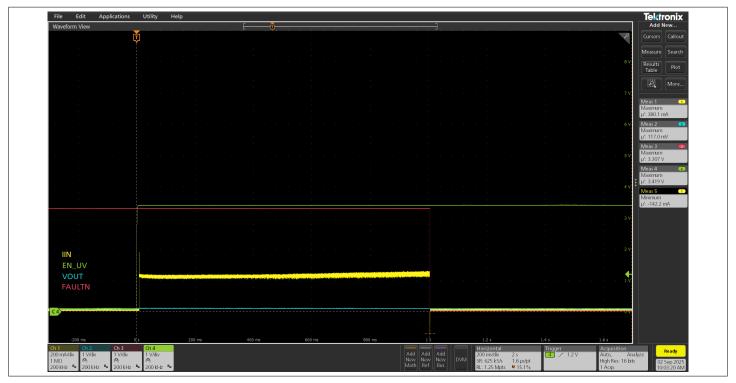

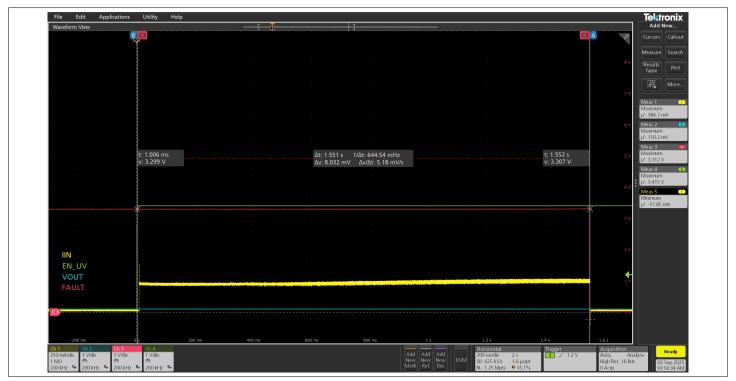

# 2.3 Power-up sequence

When using XDP720 in an application, the main input power supply bus is connected to the VIN pins whereas the VDD\_VIN pin is connected to the VIN through an RC filter. This RC filter helps to get a stabilized VDD\_VIN level, which is the input supply to the device's controller section. When the VDD\_VIN level rises above 7 V, the internal regulator VREG output is set to ~5 V level and all the analog/digital pins are released after a successful check. It is mandatory to connect a 1 uF capacitor from the VREG pin to GND. Figure 4 shows a simplified XDP720 power-up sequence.

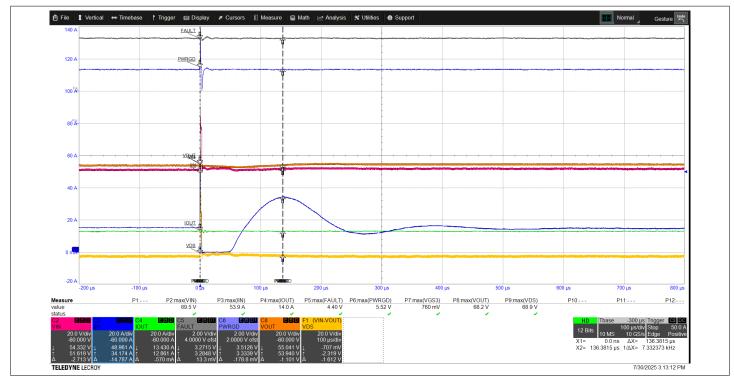

Figure 4 XDP720 power-up sequence (PWRGD and FAULT tied to VREG)

# 2.3.1 FailSafe

The device has a turn-on fail safety mechanism to ensure that the SECONDARY devices in the system will not turn-on their MOSFETs if the PRIMARY device is damaged. After a successful device power-up, the PRIMARY configured device will source  $I_{FS}$  current on the FS pin. A resistor from this pin to GND aids every device in the system to constantly sense its FS pin voltage i.e.  $V_{FS}$ . Each device will only allow its MOSFET to turn-on if the  $V_{FS} >= V_{FS\_TH}$ , otherwise it triggers a SYNC fault.

Note:

The device will enter LATCH-OFF state when a SYNC fault is triggered due to FS. It can only be released reliably, by performing a device power cycle.

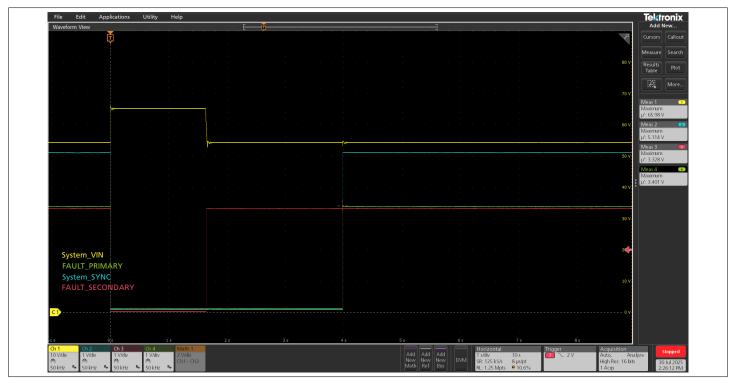

# 2.3.2 SYNC procedure

When multiple XDP72x devices are connected in parallel to increase system power, it becomes extremely crucial to properly synchronize them. This is achieved by connecting all the SYNC pins together. Every device has a SYNC pin with internal control and sense lines. At device power-up, the SYNC pin is internally held low by the device until all checks are successful. It is only released and pulled high once the enable deglitch timer has expired without any fault conditions. This way all the devices will turn-on their MOSFETs at the same time when SYNC goes high, provided all

# **Preliminary Datasheet**

2 Functional description

other turn-on conditions are present. When a fault is triggered, the device will pull its SYNC pin low based on the type of fault. This is seen by the other devices almost immediately, which forces them to turn-off their MOSFETs to protect the system. The SECONDARY configured device also performs a SYNC handshaking protocol to ensure that the PRIMARY device in the system is properly taking control over the SECONDARYs. If, for some reason, the PRIMARY device fails to respond within  $t_{\rm SYNC\_HSK}$  then the SECONDARY device will treat it as an unsuccessful SYNC handshaking and gets latched off.

Attention: SYNC pin is functionally similar to the FAULT pin.

Note:

- At power-up, the device starts to actively pull its SYNC pin LOW at the end of the READ\_CFG state.

- Disabling the SYNC fault and its reporting on the FAULT pin using ENABLE\_FAULTS and MASK\_FAULTS commands respectively, must be avoided.

#### 2.3.3 Enable and disable

The EN\_UV pin is used to enable or disable the device output by controlling the MOSFET. There is an analog comparator at the EN\_UV pin which senses its voltage. As shown in the table below, the MOSFET is allowed to turn-on if the voltage on this pin is higher than the threshold level i.e.  $V_{\text{EN_UV}}$  uth, along with mentioned conditions.

Table 4 MOSFET turn-on conditions

| FS                                   | SYNC | OPERATION:ON bit | EN | State of the MOSFET                     |

|--------------------------------------|------|------------------|----|-----------------------------------------|

| $V_{\text{FS}} >= V_{\text{FS\_TH}}$ | Н    | "1"              | Н  | Active (can be ON; or OFF due to fault) |

| $V_{\rm FS} < V_{\rm FS\_TH}$        | х    | х                | х  | OFF                                     |

| X                                    | L    | х                | х  | OFF                                     |

| Х                                    | х    | "0"              | х  | OFF                                     |

| X                                    | х    | х                | L  | OFF                                     |

An enable deglitch timer (EN\_DG) is started when the EN\_UV pin is pulled high. This timer protects the device from contact bouncing during hotswap events and is fully programmable via PMBus<sup>TM</sup>. It is highly recommended that a non-zero enable deglitch timer is always used. By default, the device has an 8 ms enable deglitch timer value. In addition to enabling/disabling the device, the EN\_UV pin can also be used to clear any faults using its HIGH-to-LOW transition as described in Chapter 2.12.2.2. Only the OTP memory (MEM) fault is not affected by this EN transition.

Attention: At power-up, the MOSFET can only be turned on when VINS is above the input undervoltage fault level plus hysteresis (or the EN\_UV pin voltage is above the  $V_{\rm EN_UV_UTH}$ ) and VINS is below the input overvoltage fault level minus hysteresis (or the OV pin voltage is below the  $V_{\rm OV_LTH}$ ).

# **Preliminary Datasheet**

2 Functional description

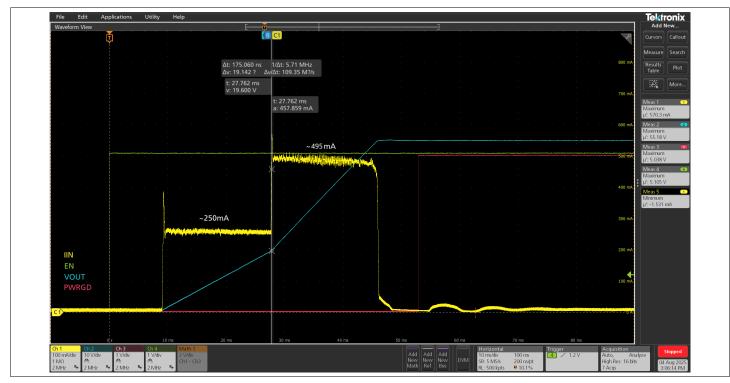

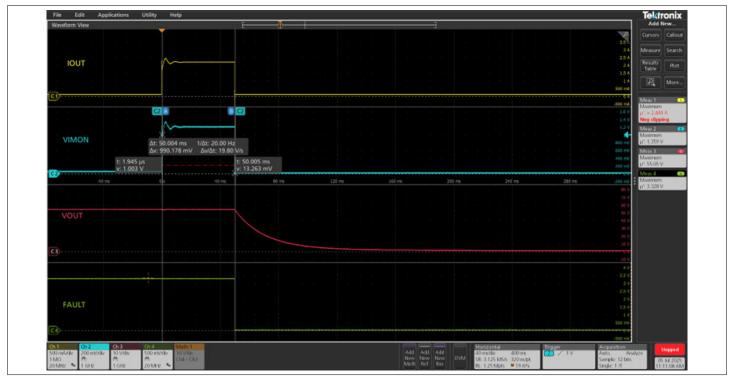

Figure 5 Default turn-on;  $C_{OUT} = 1 \text{ mF}$

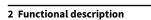

#### **Undervoltage function** 2.3.3.1

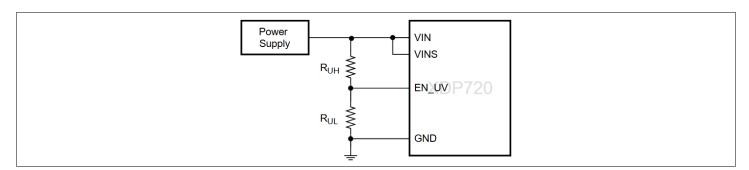

Generally, every system that uses an eFuse is designed for a specific operating voltage range. The XDP720 has two undervoltage protections for monitoring the minimum input and output voltages. By default, the input undervoltage is configured to sense the voltage at the VINS pin using a digital comparator. When VINS voltage falls to/below the digitally programmed limit, the input undervoltage protection (UV) is triggered. If needed, the device can be configured to use an analog comparator at the EN\_UV pin for faster response. When the EN\_UV pin voltage falls to/ below  $V_{\rm UV\ LTH\ P}$  (or  $V_{\rm UV\ LTH\ S}$ ), the input undervoltage protection (UV) is triggered. The equation below can be used to calculate the values of the resistor divider network at the EN\_UV pin as shown in Figure 6. At a given time, the input undervoltage can be configured to use either the digital comparator or the analog comparator. The output undervoltage protection is only achieved using the digital comparator at the VOUTS pin. Depending on the device configuration, the MODE command is used to select the appropriate comparator modes for UV and OV detections.

Figure 6 Input undervoltage protection

$$UV(V) = V_{UV\_LTH\_x}(V) \times \frac{R_{UH}(k\Omega) + R_{UL}(k\Omega)}{R_{UL}(k\Omega)}$$

(1)

where  $V_{UV\_LTH\_X}$  is the input undervoltage threshold ( $V_{UV\_LTH\_P}$  or  $V_{UV\_LTH\_S}$ ) in Volt and UV is the desired undervoltage limit in Volt.

16

# **Preliminary Datasheet**

2 Functional description

**Note**: Changing the UV comparator mode on the fly i.e. when the MOSFET is ON, must be avoided.

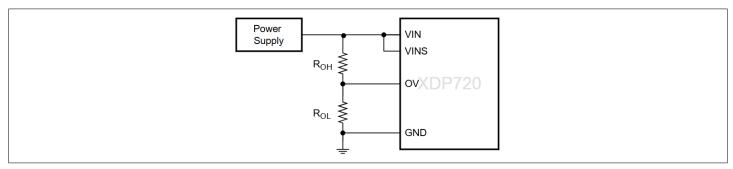

# 2.3.3.2 Overvoltage function

Similar to input undervoltage, the XDP720 has input overvoltage protection for monitoring the maximum input voltage. By default, the input overvoltage is configured to sense the voltage at the VINS pin using a digital comparator. When the VINS voltage rises to/above the digitally programmed limit, the input overvoltage protection (OV) is triggered. If needed, the device can be configured to use an analog comparator at the OV pin for faster response. When the OV pin voltage rises to/above  $V_{\text{OV\_UTH}}$ , the input overvoltage protection is triggered. The equation below can be used to calculate the values of the resistor divider network at the OV pin as shown in Figure 7. At a given time, the input overvoltage can be configured to use either the digital comparator or the analog comparator.

Figure 7 Input overvoltage protection

$$OV(V) = V_{OV\_UTH}(V) \times \frac{R_{OH}(k\Omega) + R_{OL}(k\Omega)}{R_{OL}(k\Omega)}$$

(2)

where  $V_{OV\ UTH}$  is the input overvoltage threshold in Volt and OV is the desired overvoltage limit in Volt.

**Note**: Changing the OV comparator mode on the fly i.e. when the MOSFET is ON, must be avoided.

In a PRIMARY configured device, there is an additional "backup" on-chip overvoltage (OVIN) limit to protect the device against bad design or OV configuration. It can be programmed to 70 V, 75 V, 80 V or 85 V using the V\_SNS\_CFG command. By default, the device is configured to have 80 V as the OVIN protection level.

# 2.4 Inrush current control

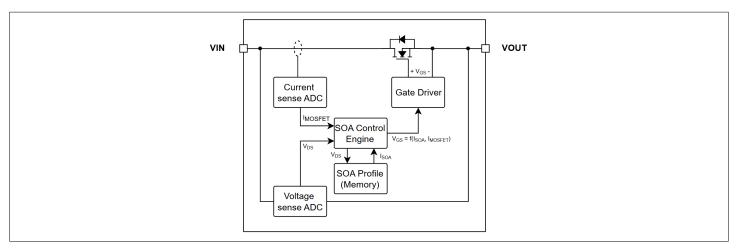

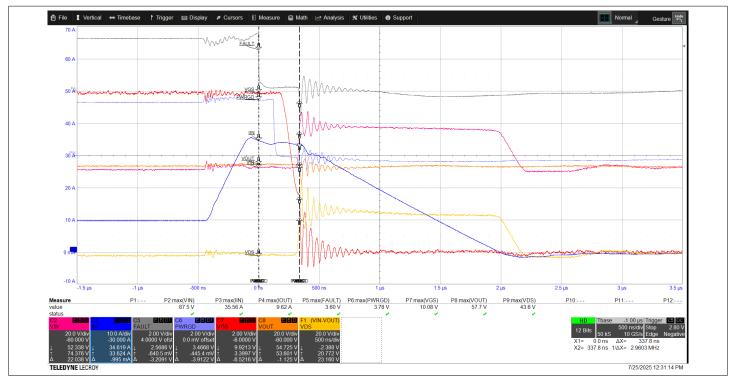

The main purpose of an eFuse is to minimize the inrush current during hotswap events, especially in high-availability systems such as servers, data centers, etc. Most eFuses in the market use soft-start, i.e. dvdt method of inrush current control. Although this approach is relatively simple to implement in eFuse, it is not completely safe for the MOSFET. During MOSFET turn-ON, the current can easily go beyond the safe operating area (SOA) limits due to the linear dvdt start-up method, which can damage the MOSFET. Therefore, we at Infineon use our proprietary "Digital SOA control" approach for the inrush current control as shown in Figure 8. This approach keeps the MOSFET in the SOA during the turn-ON procedure and is simple to configure from the user's perspective.

The SOA control loop consists of a closed loop system that senses the input voltage, output voltage and the current flowing through the MOSFET internally. The device calculates the MOSFET's  $V_{\rm DS}$  by subtracting VOUT from VIN i.e.  $V_{\rm DS}$  = VIN - VOUT, and regulates the MOSFET's current according to the SOA/control loop limits. This regulation is achieved by adjusting the MOSFET's  $V_{\rm GS}$ .

For legacy compatibility, there are a few pre-programmed constant SOA data lines (0.25 A, 0.5 A, 1 A, 1.5 A, 2 A) that can be selected using PMBus™ to mimic soft-start/dvdt method for inrush control.

2 Functional description

Figure 8 Digital SOA based inrush current control

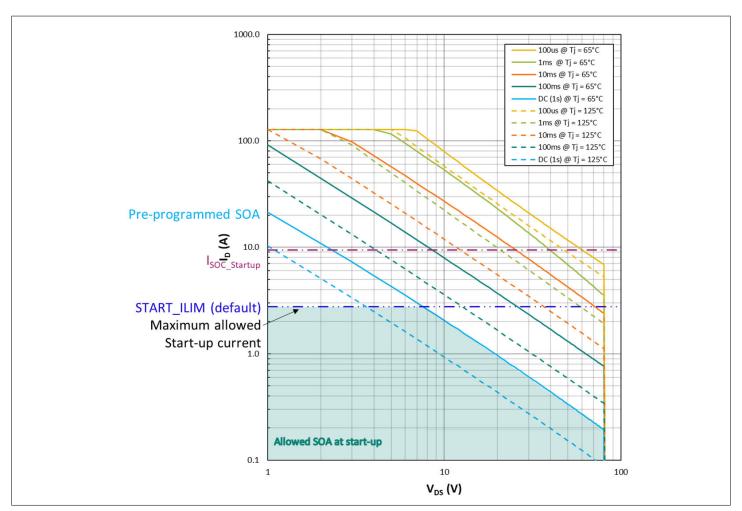

Figure 9 MOSFET's SOA chart

The control loop limits of a device are configured according to three different limits as shown in Figure 9.

• **Programmed MOSFET SOA limit**: The MOSFET's SOA data is pre-programmed into the device. This SOA is normalized to 65°C and 125°C junction temperature to account for systems that is working at higher ambient temperatures. Depending on the MOSFET temperature, the appropriate SOA line is used for inrush control. If the MOSFET temperature is below 105°C then 65°C SOA line is considered else 125°C SOA line is used.

# **Preliminary Datasheet**

2 Functional description

- **Severe overcurrent (SOC) limit**: The severe overcurrent limit ( $I_{SOC\_STARTUP}$ ) also known as short circuit current limit provides a fast response in case the inrush current reaches a critical level.

- **Start-up current (START\_ILIM) limit**: The maximum start-up current limit ( $I_{START_ILIM(MAX)}$ ) is fixed in every eFuse. Using PMBus<sup>TM</sup> command, the user can adjust this limit as a percentage of the  $I_{START_ILIM(MAX)}$ . This configurability allows the user to increase or decrease the MOSFET's turn-on time. The start-up current limit is only considered during inrush control i.e. MOSFET turn-on. It is disregarded as soon as steady state i.e. ON state is reached.

During MOSFET turn-on, the device provides a bias current to turn on the MOSFET in a controlled manner avoiding any SOA violations while ensuring that the system is turned on without any inrush event. The intersection of the previously mentioned three control loop limits define the maximum allowed start-up current.

The Figure 9 shows the MOSFET's SOA with the default control loop limits.

- Blue (solid and dash) lines indicate the pre-programmed SOA limits of the MOSFET.

- Magenta (long dash dot) line indicates the fixed SOC limit during start-up.

- Dark blue (long dash dot dot) line indicates the programmed default start-up current limit i.e. START\_ILIM.

- Highlighted area indicates the intersection of all the control loop limits i.e. allowed SOA at start-up.

The SOA is digitally stored as a look-up table with 80 values, corresponding to  $V_{\rm DS}$  = 1 V to 80 V. Each entry represents the MOSFET's current allowed for that  $V_{\rm DS}$  level and has a resolution of 0.5 A. The following example demonstrates the inrush current control in a typical 54 V input application.

- Before the MOSFET is turned on, there is 54 V at the input and 0 V at the output with respect to ground. As the output capacitor is discharged at the start-up,  $V_{DS} = 54 \text{ V}$ .

- The device starts charging the output capacitor by regulating the MOSFET. As shown in Figure 9, the control loop allows an  $I_{SOA}$  = 0.25 A at 54 V.

- As the capacitor charges, the V<sub>DS</sub> of the MOSFET starts to reduce which allows more current to flow through the MOSFET as per the control loop limits. For example, when V<sub>DS</sub> reaches 35 V, the allowed MOSFET current is increased to 0.5 A.

- Similarly, when V<sub>DS</sub> reaches 10 V the allowed MOSFET current will be increased to 2 A.

- Thus, the current increases until the capacitor is charged to the VIN level and the MOSFET is fully enhanced.

This current limitation delays the charging of the output capacitor, significantly reducing the inrush current at start-up while keeping the MOSFET within its SOA limits.

Figure 10 Inrush control with START\_ILIM set to 9% of  $I_{START\_ILIM(MAX)}$  i.e. ~495 mA;  $C_{OUT}$  = 270  $\mu$ F

# **Preliminary Datasheet**

2 Functional description

# 2.5 Current limit settings

The XDP720 has multiple current protection levels for maximum flexibility/configurability. This includes a start-up current limit (START\_ILIM), two overcurrent limits (SYS\_OC\_LIMIT and LOCAL\_OC\_LIMIT) and a severe overcurrent limit (SOC\_LIMIT\_x).

# 2.5.1 Start-up current setting

In this device, the start-up current limit is set using dedicated START\_ILIM bits in the I\_SNS\_CFG2 command. This level is active only during MOSFET turn-on i.e. INIT\_SOA\_REG state. By default, the start-up current limit is configured to be 50% of  $I_{START\_ILIM(MAX)}$ . The Table 5 below shows the allowed START\_ILIM settings.

Table 5 Start-up current limit settings

| START_ILIM [2:0] | Description                                   |  |  |  |  |  |

|------------------|-----------------------------------------------|--|--|--|--|--|

| 000              | 100% of / <sub>START_ILIM(MAX)</sub>          |  |  |  |  |  |

| 001              | 75% of / <sub>START_ILIM(MAX)</sub>           |  |  |  |  |  |

| 010              | 50% of I <sub>START_ILIM(MAX)</sub> (default) |  |  |  |  |  |

| 011              | 25% of / <sub>START_ILIM(MAX)</sub>           |  |  |  |  |  |

| 100              | 15% of / <sub>START_ILIM(MAX)</sub>           |  |  |  |  |  |

| 101              | 12.5% of I <sub>START_ILIM(MAX)</sub>         |  |  |  |  |  |

| 110              | 9% of I <sub>START_ILIM(MAX)</sub>            |  |  |  |  |  |

| 111              | 5% of / <sub>START_ILIM(MAX)</sub>            |  |  |  |  |  |

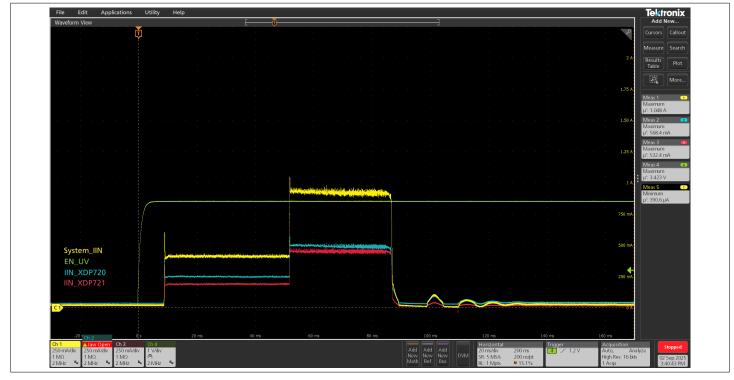

# 2.5.2 Overcurrent setting

After a successful start-up, the device enters the ON state and activates the overcurrent (OC) protection along with the continuous current reporting on its IMON pin. The IMON current gain is set digitally using the TELEMETRY\_AVG command. By default, the IMON gain is set to 18.2  $\mu$ A/A of the current flowing through the MOSFET. There are two overcurrent levels (i.e. system overcurrent and local overcurrent) that can trigger the overcurrent protection in the device.

# 2.5.2.1 System overcurrent setting

Only in a PRIMARY configured device, the system overcurrent protection is triggered if the IMON pin voltage ( $V_{\rm IMON}$ ) reaches the reference threshold ( $V_{\rm SYS\_OC}$ ) level set using I\_SNS\_CFG1:SYS\_OC\_LIMIT bits. The equation (3) is used to set this limit between 0 V to 1.35 V with ~6.5098 mV resolution step. By default, the SYS\_OC\_LIMIT = 154dec (i.e.  $V_{\rm SYS\_OC}$  = 1.0025 V) is programmed in the device.

$$SYS\_OC\_LIMIT(in \ decimal) = V_{SYS\_OC}(V) \times 153.61445$$

(3)

The IMON resistor required to generate the system overcurrent protection can be calculated using the following equation (4).

$$R_{IMON}(\Omega) = \frac{V_{SYS\_OC}(V)}{G_{IMON}(\mu A/A) \times 10^{-6} \times I_{SYS\_OC}(A)}$$

(4)

It is possible to add some deglitch/delay time to the system overcurrent detection. The SOA\_TMR:SOAD\_TMR command is used to configure the system overcurrent deglitch time between 0 ms and 2000 ms. The device comes pre-programmed with a 2 ms default system overcurrent deglitch time.

# **Preliminary Datasheet**

2 Functional description

**Note**: It is recommended to program the SYS\_OC\_LIMIT between 40dec (0x28) and 207dec (0xCF) for reliable OC

detection.

# 2.5.2.2 Local/backup overcurrent setting

There is a local/backup overcurrent limit to protect the device if the system overcurrent protection is not set properly. This local overcurrent limit is configurable from 0 A to ~69.85 A with 0.55 A resolution step using I\_SNS\_CFG1:LOCAL\_OC\_LIMIT bits. There is a programmable fast deglitch timer to delay the local overcurrent protection from 50 µs to 1 ms. Using the SOA\_TMR:LOCAL\_OC\_TMR bit, it can be selected between the fast deglitch timer (OCD\_TMR) or a slow deglitch timer (SOAD\_TMR) for the local overcurrent protection. By default, the device is configured to have 200 µs fast deglitch time for a local overcurrent limit of 44 A.

# 2.5.3 Severe overcurrent setting

During short circuit (i.e. surge or high di/dt current) events, the current flowing through the MOSFET may reach a dangerous level which can critically damage the system load. The device has a fast comparator to protect against such severe overcurrent (SOC) incidents. It can quickly respond by turning off the MOSFET with a strong pull-down current. The complete SOC response time from the moment it is detected till the MOSFET is turned off is  $t_{\rm SOC_DG}$ . The SOC protection level is digitally programmable using I\_SNS\_CFG2:SOC\_LIMIT\_x bits, from 0 A to 138.6 A with a 2.2 A resolution step. It is possible to have different SOC level settings based on the device configuration. There is also an analog deglitch timer that can be configured to delay the SOC detection. This timer is programmed (0 ns, 200 ns, 500 ns, 1000 ns) using SOA\_TMR command. By default, the device is pre-programmed to have 88 A (for PRIMARY) / ~96.8 A (for SECONDARY) SOC level and 0 ns deglitch time.

The SOC level during the start-up procedure is fixed to I<sub>SOC\_STARTUP</sub>.

# 2.6 Power good (PWRGD)

A power good (PWRGD) pin is available in this device which can be used as a flag or to control the system load. It is asserted i.e. pulled high when the device enters the ON state to indicate that the MOSFET is fully enhanced ( $V_{\rm GS}$  > 7.8 V and  $V_{\rm DS}$  < 1.0 V) and there are no fault conditions. When a fault is triggered or RESTART is issued, the MOSFET is turned off and this pin is de-asserted i.e. pulled low. It will also be de-asserted if the MOSFET turn on conditions, shown in Table 4 are not met. There are two separate digitally programmable deglitch timers associated with this pin. They help to delay the PWRGD pin assertion and de-assertion respectively. Using the PWRGD\_DG\_TMR command, these timers can be individually programmed from 0 ms to 15 ms. By default, the device is pre-programmed to have a 5 ms deglitch time for PWRGD pin assertion and 0 ms for de-assertion.

**Note**: The PWRGD pin remains asserted when the surge immunity feature is enabled and activated, regardless of the  $V_{GS}$  voltage level.

# 2.7 Thermal protection

Thermal protection is an important feature in any eFuse as it indicates and protects the device (and system load) against thermal instability. The device has two levels of thermal protection thanks to the dedicated temperature sensors in the MOSFET and controller. In this device, the "TEMPERATURE\_1" refers to the internal MOSFET temperature and "TEMPERATURE\_2" refers to the on-chip controller temperature. The MOSFET overtemperature protection level is digitally programmable using the OT\_FAULT\_LIMIT command. Additionally, the ONCHIP\_TSD\_FAULT\_LIMIT command is used for configuring the controller's thermal shutdown protection level. By default, the device is programmed to ~166.5°C and 145°C for MOSFET overtemperature and controller thermal shutdown level respectively.

#### 2.8 Restart

The user may want to "reset" the device anytime during steady state operation i.e. MOSFET is ON. This can be done by issuing a RESTART PMBus<sup>TM</sup> command. If this feature is triggered, the MOSFET will turn off, thus removing power from the output. Also, a user-configurable RESTART\_TMR is started immediately. The device will transition to the STANDBY

# **Preliminary Datasheet**

2 Functional description

state after RESTART\_TMR has expired. If all the necessary conditions shown in Table 4 are met, then the MOSFET automatically turns back on. The RESTART\_TMR is configured digitally using the RETRY command.

Depending on the GPO2 pin configuration, the RESTART can also be triggered using the GPO2 i.e. RESTARTN pin

Depending on the GPO2 pin configuration, the RESTART can also be triggered using the GPO2 i.e. RESTARTN pin (falling edge triggered). By default, the GPO2 pin is configured as RESTARTN pin and the RESTART TMR is set to 9.28 s.

**Note**: The OTP memory must not be programmed when the RESTART\_TMR is running.

# 2.9 MOSFET power down

The MOSFET turn-off can be triggered automatically due to a fault or manually by the user (EN or RESTART or OPERATION:ON bit). The MOSFET is generally turned off using  $I_{\text{GATE\_SPD}}$  pull-down current except for OVIN and SOC fault events. Since OVIN and SOC events are critical for the device and the system load, a strong/fast pull-down current  $I_{\text{GATE\_SPD}}$  is used for turning off the MOSFET immediately to avoid  $V_{\text{DS}}$  overshoots. The  $I_{\text{GATE\_SPD}}$  pull-down current is digitally configurable using the TURN\_OFF\_CTRL command. By default, the device is configured to turn off the MOSFET with 1250  $\mu$ A slow pull-down current and 1 A fast pull-down current.

# 2.10 Quick output discharge

The device has an output discharge feature to quickly discharge the output capacitor ( $C_{\rm OUT}$ ) at the VOUT pin using an internal current source  $I_{\rm QOD}$  to GND. This helps to quickly remove the residual charge left on the  $C_{\rm OUT}$ . The QOD feature is enabled/disabled using the MODE command. If enabled, it is activated when the user turns off the MOSFET using the EN, RESTART or OPERATION command. A fixed deglitch timer  $t_{\rm QOD}$  is started when the MOSFET is turned off. The current source  $I_{\rm QOD}$  is activated only after the deglitch timer has expired. The output discharge is automatically deactivated after  $t_{\rm QOD\_Discharge}$  time has elapsed. It can be immediately deactivated if any of the following conditions exist.

- MOSFET is turned ON i.e. the device transitions to INIT\_SOA\_REG state

- VOUT < 2 V</li>

- Fault condition occurred

This feature can elevate the device temperature due to the increased power dissipation from the internal current source. Therefore, the QOD is disabled if the thermal protections are triggered. By default, the device comes with QOD disabled.

# 2.11 General purpose pins

This device has three general purpose input/output pins to cover multiple functionalities. These include GPO0, GPO1 and GPO2 pins that can be configured using GPO\_CFG command. The different functionalities of these pins are shown in Table 6, Table 7 and Table 8 respectively.

Table 6 GPO0 pin configuration

| GPO_CFG:GPO0_CFG | Description                                                                                 |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| 00               | Pin is configured as active low FAULT (default)                                             |  |  |  |  |  |

| 01               | Pin reflects GPO0_ST status                                                                 |  |  |  |  |  |

| 10               | RESERVED                                                                                    |  |  |  |  |  |

| 11               | Pin is configured as active low SMBALERT, reporting depends on the GPO_CFG:SMBALERT setting |  |  |  |  |  |

#### Table 7 GPO1 pin configuration

| GPO_CFG:GPO1_CFG | Description                                    |

|------------------|------------------------------------------------|

| 00               | Pin is configured as active low WARN (default) |

(table continues...)

# **Preliminary Datasheet**

#### Table 7 (continued) GPO1 pin configuration

| GPO_CFG:GPO1_CFG | Description                 |

|------------------|-----------------------------|

| 01               | Pin reflects GPO1_ST status |

| 10               | RESERVED                    |

| 11               | RESERVED                    |

#### Table 8 GPO2 pin configuration

| GPO_CFG:GPO2_CFG | Description                                                         |  |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|--|

| 00               | Pin is configured as functional                                     |  |  |  |  |  |

| 01               | Pin is configured for UV throttle function                          |  |  |  |  |  |

| 10               | RESERVED                                                            |  |  |  |  |  |

| 11               | Pin is configured as RESTARTN input with pull-up resistor (default) |  |  |  |  |  |

Depending on the GPO0 and SMBALERT configuration, the SMBALERT pin can be configured to provide an overview of all the enabled warnings, faults or both. The SMBALERT pin can only be released/unlatched by following the Alert Response Address protocol in Chapter 2.14.2.1.

By default, the device is configured to have FAULT functionality, WARN functionality and RESTARTN functionality on GPO0, GPO1 and GPO2 pins respectively.

#### 2.12 Protections

#### 2.12.1 Faults

This device incorporates many protections that ensure safe operation of the device and system load in different scenarios. Depending on the device configuration shown in Table 3, this device can address up to 15 different faults. Using the ENABLE\_FAULTS command, the user can individually enable/disable each fault protection. There is a dedicated MASK\_FAULTS command to mask/unmask the reporting of each fault on the FAULT pin. A fault can be enabled with or without reporting on the FAULT pin but the reverse is not possible. The FAULT pin will be pulled low and the MOSFET is turned off when a fault is triggered. The FAULT pin remains low for a minimum of  $t_{\rm FAULT\_MIN}$  regardless of the duration of the actual fault condition. This ensures that the system microcontroller can properly detect the FAULT pin reporting. The status of the faults being triggered is checked using the STATUS\_FAULTS command. Masking a fault will only affect the FAULT pin but not its status bit. Therefore, it is highly recommended to unmask a particular fault at the same time when it is enabled. Depending on the fault type, the FAULT pin is released either after the fault condition is removed or when the fault status bit is cleared. The fault status bits will remain set until they are cleared:

- using CLEAR\_FAULTS command

- or, toggling EN pin HIGH-to-LOW

- or, by a power cycle

To service the faults properly, the CLEAR\_FAULTS command and EN pin toggling are ignored until fault processing has finished. There are priorities assigned to each fault. If a high-priority fault is triggered while processing a lower-priority fault, then the device will immediately start processing the higher-priority fault. The device will resume the lower-priority fault process only after the high-priority fault serving is finished. If multiple faults with the same priority are triggered at the same time, then the device will act on a first-come-first-serve basis. The GPO0 pin can be configured to operate as an active low SMBALERT pin. Depending on the SMBALERT configuration, the faults can be programmed to latch this pin.

# **Preliminary Datasheet**

2 Functional description

Note:

- FAULT pin is asserted low until the fault condition is removed. It also depends on the retry settings for retry-based faults.

- SMBALERT pin is latched low when a fault and/or warning has occurred. This pin can only be released/unlatched by following the Alert Response Address protocol (Chapter 2.14.2.1).

Table 9 provides an overview of when a fault's detection and processing is active.

Table 9 Faults overview table

| Fault                                  | State of the device |              |             |             |                      |                 |       |      |                 |      |                                 |                                |  |

|----------------------------------------|---------------------|--------------|-------------|-------------|----------------------|-----------------|-------|------|-----------------|------|---------------------------------|--------------------------------|--|

| name<br>and pri<br>ority* <sup>1</sup> | POR<br>_INIT        | READ<br>_CFG | CHK<br>_FET | STAND<br>BY | INIT<br>_SOA<br>_REG | ON              | SURGE | GREC | FAULT           | WAIT | MEM_<br>FAULT/<br>LATCH<br>_OFF | availa<br>bility* <sup>2</sup> |  |

| MEM (1)                                | -                   | Х            | Х           | Х           | Χ                    | Χ               | Х     | Χ    | Х               | Х    | Х                               | P/S                            |  |

| SGD (2)                                | -                   | -            | Х           | Х           | -                    | -               | -     | -    | Х               | -    | -                               | P/S                            |  |

| SGS (2)                                | -                   | -            | -           | -           | X*3                  | -               | -     | -    | -               | -    | -                               | P/S                            |  |

| UR (2)                                 | -                   | -            | -           | -           | -                    | -               | -     | -    | X* <sup>4</sup> | -    | -                               | Р                              |  |

| SOC (3)                                | -                   | -            | -           | -           | Х                    | X* <sup>5</sup> | -     | Х    | Х               | -    | -                               | P/S                            |  |

| VDS (4)                                | -                   | -            | -           | X*6         | -                    | -               | -     | -    | -               | -    | -                               | Р                              |  |

| OT (4)                                 | -                   | -            | -           | Х           | Χ                    | Х               | -     | Х    | -               | -    | -                               | P/S                            |  |

| TSD (4)                                | -                   | -            | -           | Х           | Х                    | Х               | -     | Х    | -               | -    | -                               | P/S                            |  |

| OVIN (5)                               | -                   | -            | -           | Х           | Х                    | Х               | -     | Х    | Х               | -    | -                               | Р                              |  |

| OV (6)                                 | -                   | -            | -           | Х           | Χ                    | Х               | -     | Х    | Х               | -    | -                               | P/S                            |  |

| UV (7)                                 | -                   | -            | -           | Х           | Х                    | Х               | -     | Х    | Х               | -    | -                               | P/S                            |  |

| OUV (8)                                | -                   | -            | -           | -           | -                    | Х               | -     | Х    | -               | -    | -                               | Р                              |  |

| WD (9)                                 | -                   | -            | -           | -           | Χ                    | -               | -     | Х    | -               | -    | -                               | P/S                            |  |

| OC (9)                                 | -                   | -            | -           | -           | -                    | Х               | -     | -    | -               | -    | -                               | P/S                            |  |

| SYNC<br>(10)                           | -                   | -            | -           | Х           | Х                    | Х               | -     | Х    | -               | -    | -                               | P/S                            |  |

#### Attention:

- \*1): Fault priority level decreases as we go down the table.

- \*2): Indicates the device configuration, P = PRIMARY and S = SECONDARY.

- \*3): Right at the point when the watchdog timer expires.

- \*4): It can only occur in the FAULT state when the retry counter expires after any of the retry fault events (SOC, OT, TSD, OUV, WD, OC, SYNC).

- \*5): If RETRY:SRG\_PROT\_EN bit is set to '0' (surge protection is disabled).

- \*6): Detection is active after POR or the RESTART event.

# 2.12.1.1 Memory fault

#### **OTP Memory (MEM) Fault**

During device power-up i.e. in READ\_CFG state, if an OTP (i.e. pre-configuration) read or write error is detected then a MEM fault is triggered in the device. As a result, the device turns off its MOSFET and gets latched off by entering the MEM\_FAULT state: This fault can be cleared only through a device power cycle i.e. the device will restart from the POR\_INIT state. This fault is reported only in the STATUS\_BYTE and STATUS\_WORD commands.

#### **Preliminary Datasheet**

2 Functional description

# 2.12.1.2 Damaged MOSFET faults

This device comes with three internal MOSFET checks to mainly determine if there are any shorted pins. To ensure that the MOSFET is not damaged, it is recommended to have the shorted MOSFET pin faults enabled and unmasked.

# **Shorted MOSFET Gate-Drain (SGD) fault**

This fault checks if the Gate and Drain pins of the MOSFET are shorted. It is triggered if:

- In the CHK\_FET state after t<sub>SGD\_FLT\_DG</sub> expires, the MOSFET's V<sub>GS</sub> goes above 1 V.

- Or, after the device enters the FAULT or STANDBY state and activates any gate pull-down, the MOSFET's  $V_{\rm GS}$  does not go below 1 V within  $t_{\rm FLT\_PD\_GATE}$ .

When this fault is triggered, the device will turn off its MOSFET and get latched off. The fault is released only through the latch-off release procedure.

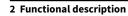

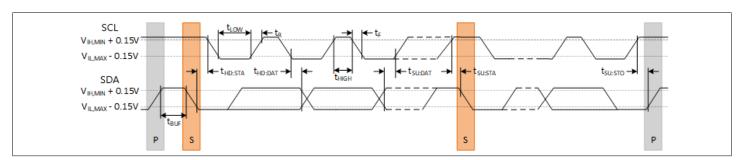

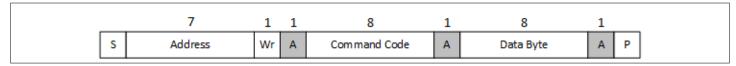

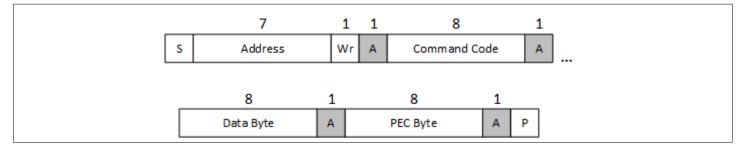

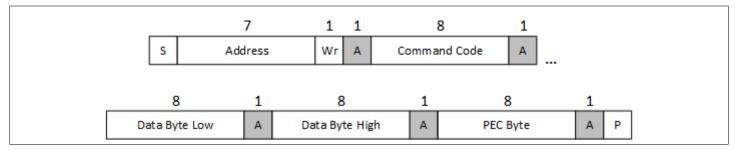

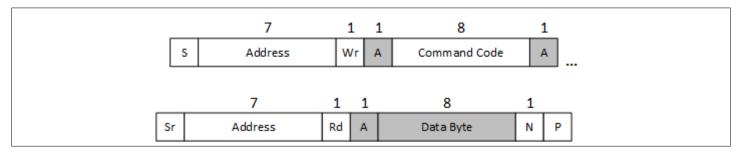

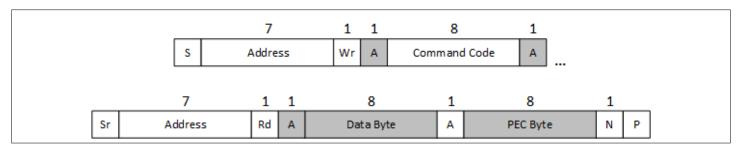

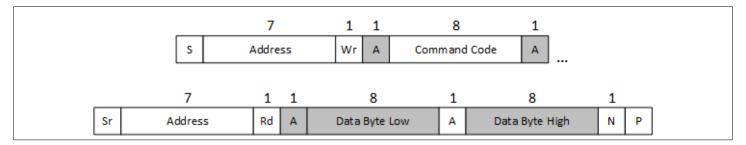

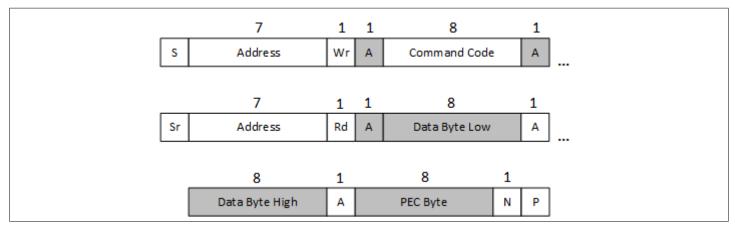

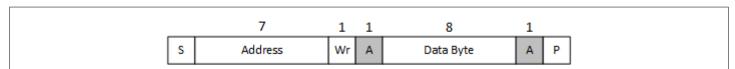

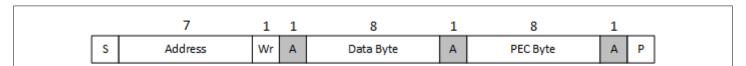

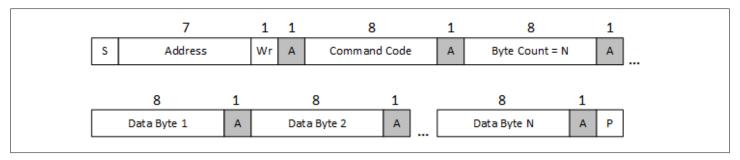

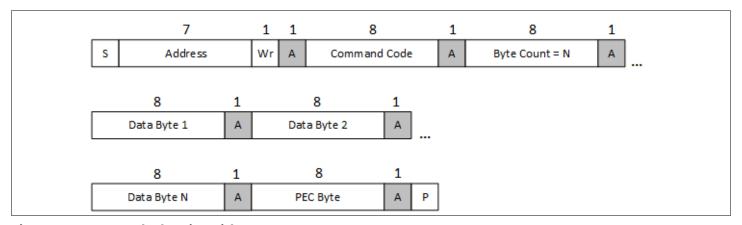

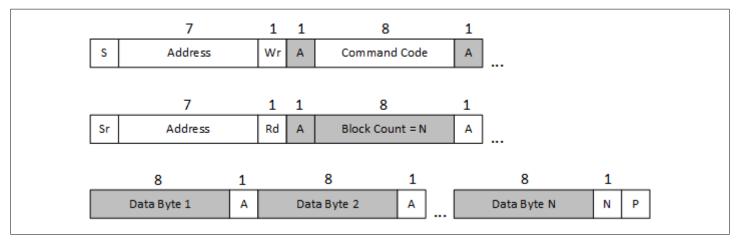

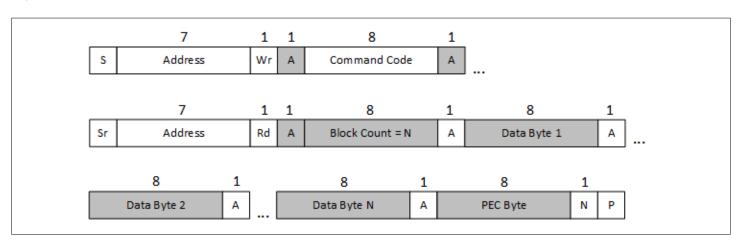

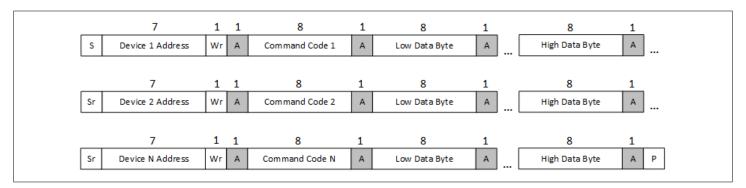

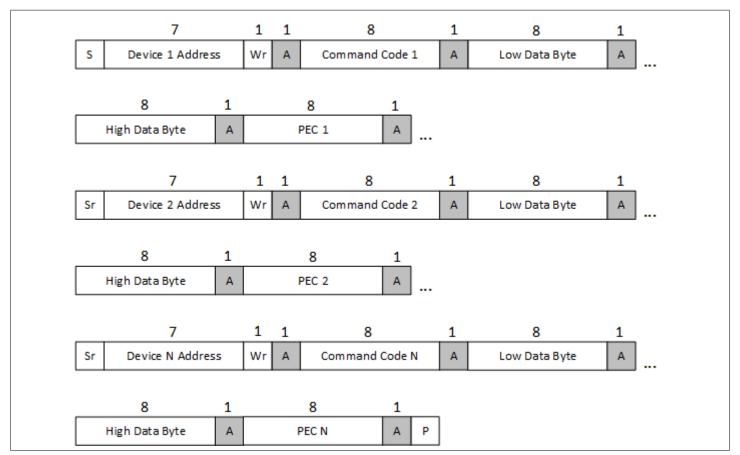

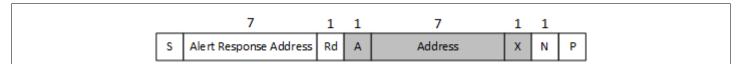

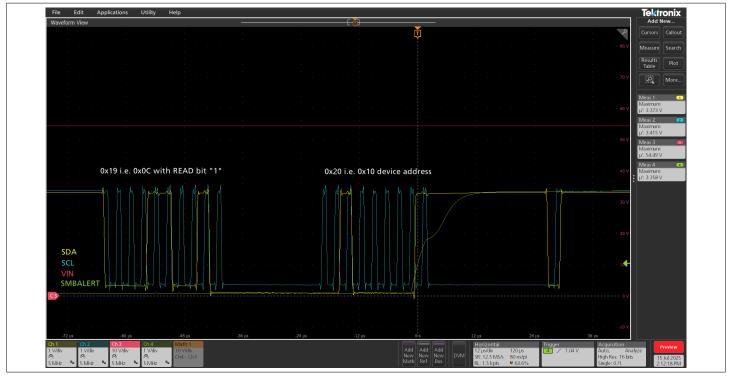

#### **Shorted MOSFET Gate-Source (SGS) fault**