## 特性

- 与英飞凌的OptiMOS™产品兼容

- 与英飞凌的Linear FET产品兼容

- 宽输入电压范围：-6.5 V 至 -80 V

- 瞬态耐受能力：高达 -100 V，持续 500 ms

- 专用电流和电压 ADC：12 位

- 可编程和预设 FET 主动 SOA 保护

- 用于外部 N 沟道 MOSFET 的集成栅极驱动器

- 可配置快速 FET 关闭：两步关闭或 1.5A 下拉电流

- PMBus 接口：1 MHz

- 精度输入输出电压监测和报告： $\leq 0.5\%$

- 精密 FET 的电流监控和报告：在整个 ADC 范围内  $\leq 1.3\%$

- 精确的输入功率监测和报告： $\leq 1.8\%$

- 能源监测和报告

- 可编程输入和输出 OV 和 UV 保护

- 支持外部温度传感器和过温保护 (OT)

- 顺序开启能力

- 29 引脚 (6 mm x 6 mm) VQFN 封装

- -40°C 至 125°C 结温

## 潜在应用

- -48 V 预隔离 DC/DC 电信基础设施

- -24 V/-48 V 工业系统

- 配电系统

- 智能电子保险丝

- 网络路由器和交换机

## 产品验证

符合 JEDEC47/20/22 相关的工业应用要求

## 描述

XDP700 是一款宽输入电压热插拔和系统监控控制器 IC，可驱动单个或多个并联 N 沟道 MOSFET。除了控制开启之外，XDP700 还提供持续的系统健康监控并通过 PMBus 接口与主 MCU 通信。通过 PMBus 进行高速通信允许系统设计人员完全或部分停用下行子系统。

它包含了多种系统保护措施以确保安全运行，并根据事件的严重程度生成各种保护响应。闭锁、重置、系统关闭和重试是响应类型的一些示例。其 SOA 保护有效保证系统 FET 始终在安全状态下工作。

## XDP700-001 - XDP700-002 比较表

以下是 XDP700-002 新增的改进和功能的摘要

- 支持 SMBAlert、连接器良好断开 (CGDN) 引脚功能

- 支持 SMBus 警报响应地址 (ARA)

- 添加了 PMBus 使能、LED 和重启功能。

- 可配置 Vin UV 故障滞回。

- 添加了更多英飞凌 FET SOA 配置文件。

- 关闭控制寄存器的大小已增加到 10 位，可以更好地控制 FET 关闭。

- 为看门狗定时器、UV\_EN 抗尖峰脉冲定时器、SOAD 定时器和启动电流限制 (IST) 添加了更多选项。

- 对升压模式进行改进，并添加全升压功能。

- 升压模式的可编程倍增因子。

本数据手册的原文使用英文撰写。为方便起见，英飞凌提供了译文；由于翻译过程中可能使用了自动化工具，英飞凌不保证译文的准确性。为确认准确性请务必访问 [infineon.com](http://infineon.com) 参考最新的英文版本（控制文档）。

描述

- 最小调节电流可低至 0.25A。

- 提高遥测精度

除了这些新增的功能之外，XDP700-002 中的所有勘误表都已修复，并且一些功能得到了改进。欲了解更多信息，请参阅 XDP7xx-001 - XDP7xx-002 兼容性和迁移应用说明。

|                    |    |

|--------------------|----|

| <b>目录</b>          | 3  |

| <b>1 框图</b>        | 5  |

| <b>2 引脚配置和封装</b>   | 6  |

| <b>3 产品基本特性</b>    | 12 |

| 3.1 绝对最大额定值        | 12 |

| 3.2 工作范围           | 13 |

| 3.3 热特性            | 15 |

| 3.4 电流消耗           | 16 |

| 3.5 ESD鲁棒性         | 16 |

| 3.6 电气特性           | 16 |

| 3.7 时序特性           | 25 |

| <b>4 产品特性</b>      | 32 |

| 4.1 功能说明           | 32 |

| 4.1.1 运行模式         | 32 |

| 4.1.2 运行状态         | 34 |

| 4.1.3 使能和停用        | 37 |

| 4.1.4 FET电流的控制     | 39 |

| 4.1.5 升压模式上电       | 44 |

| 4.1.6 电源良好         | 45 |

| 4.1.7 支持顺序打开       | 45 |

| 4.1.8 支持 OR-ing 功能 | 45 |

| 4.1.9 FET断电        | 45 |

| 4.1.10 重启          | 46 |

| 4.2 故障             | 46 |

| 4.2.1 内存故障         | 49 |

| 4.2.2 FET损坏故障      | 49 |

| 4.2.3 输入电压故障       | 50 |

| 4.2.4 输出电压故障       | 50 |

| 4.2.5 电流和温度故障      | 51 |

| 4.2.6 上电故障         | 53 |

| 4.2.7 内部保护故障       | 54 |

| 4.3 重试             | 54 |

| 4.4 闭锁             | 54 |

| 4.5 警告             | 55 |

| 4.5.1 FET损坏警告      | 57 |

| 4.5.2 输入电压和功率警告    | 57 |

| 4.5.3 输出电压警告       | 58 |

| 4.5.4 电流和温度警告      | 58 |

目录

|          |                                     |           |

|----------|-------------------------------------|-----------|

| 4.5.5    | 通讯警告 .....                          | 59        |

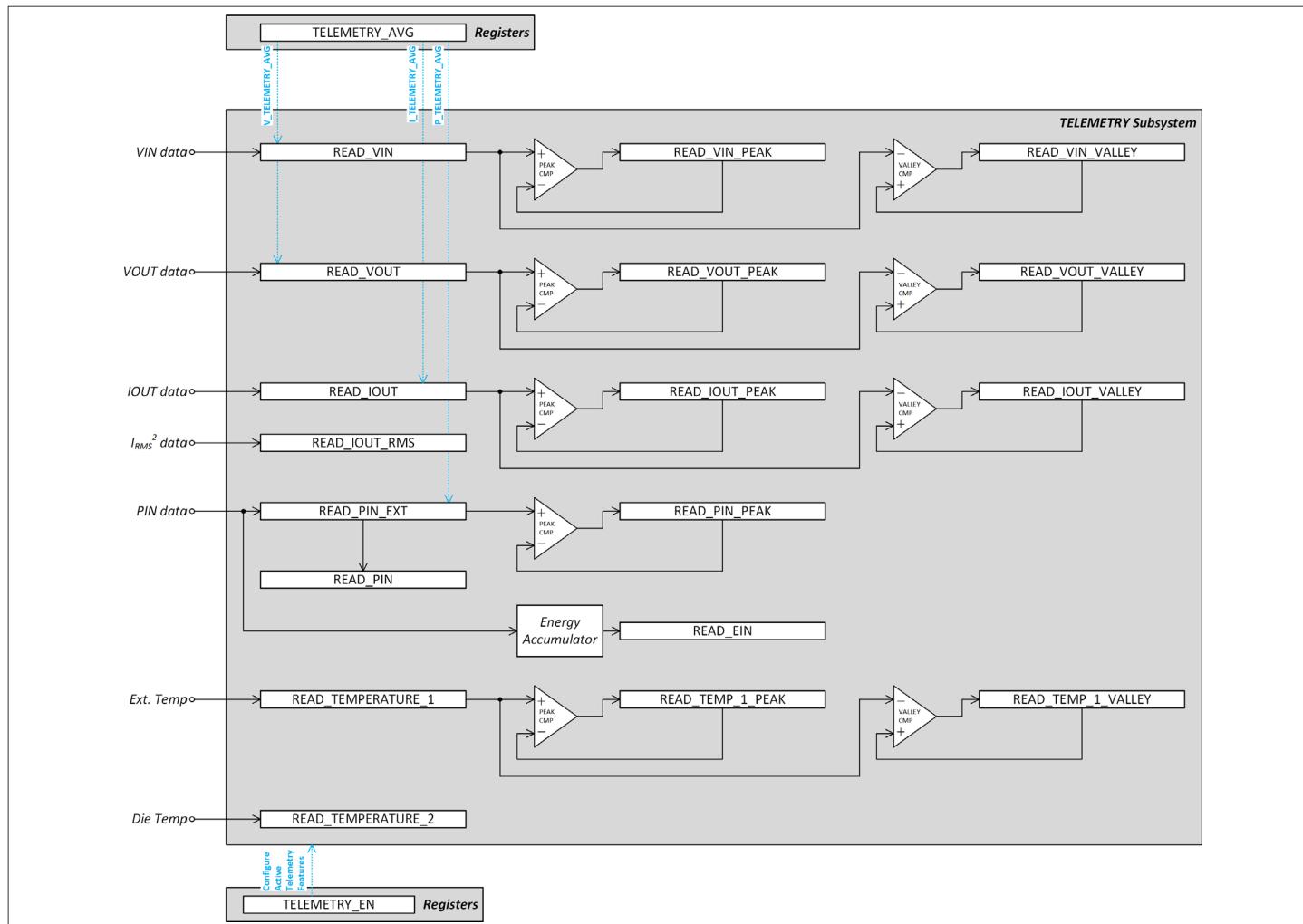

| 4.6      | 遥测 .....                            | 59        |

| 4.6.1    | 遥测摘要表 .....                         | 60        |

| 4.6.2    | 平均和瞬时遥测 .....                       | 61        |

| 4.6.3    | 峰值和谷值 .....                         | 61        |

| 4.6.4    | 通过 PMBus 进行遥测 .....                 | 62        |

| 4.6.5    | RMS 电流计算 .....                      | 64        |

| 4.6.6    | 输入功率计算 .....                        | 64        |

| 4.6.7    | 能量计算 .....                          | 64        |

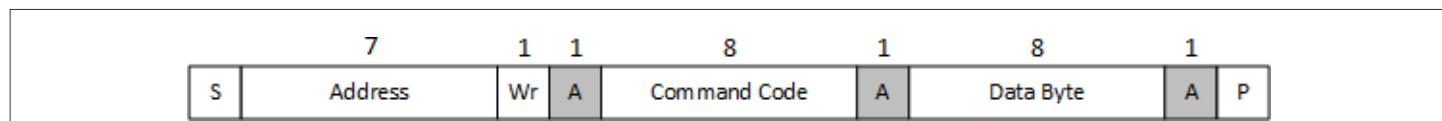

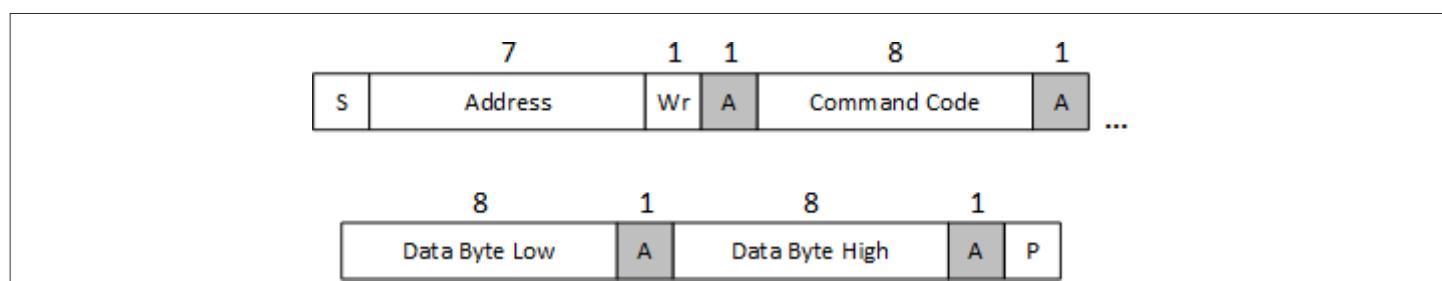

| 4.7      | 通信接口 .....                          | 65        |

| 4.7.1    | PMBus .....                         | 65        |

| 4.8      | 储存器 .....                           | 71        |

| <b>5</b> | <b>应用信息 .....</b>                   | <b>73</b> |

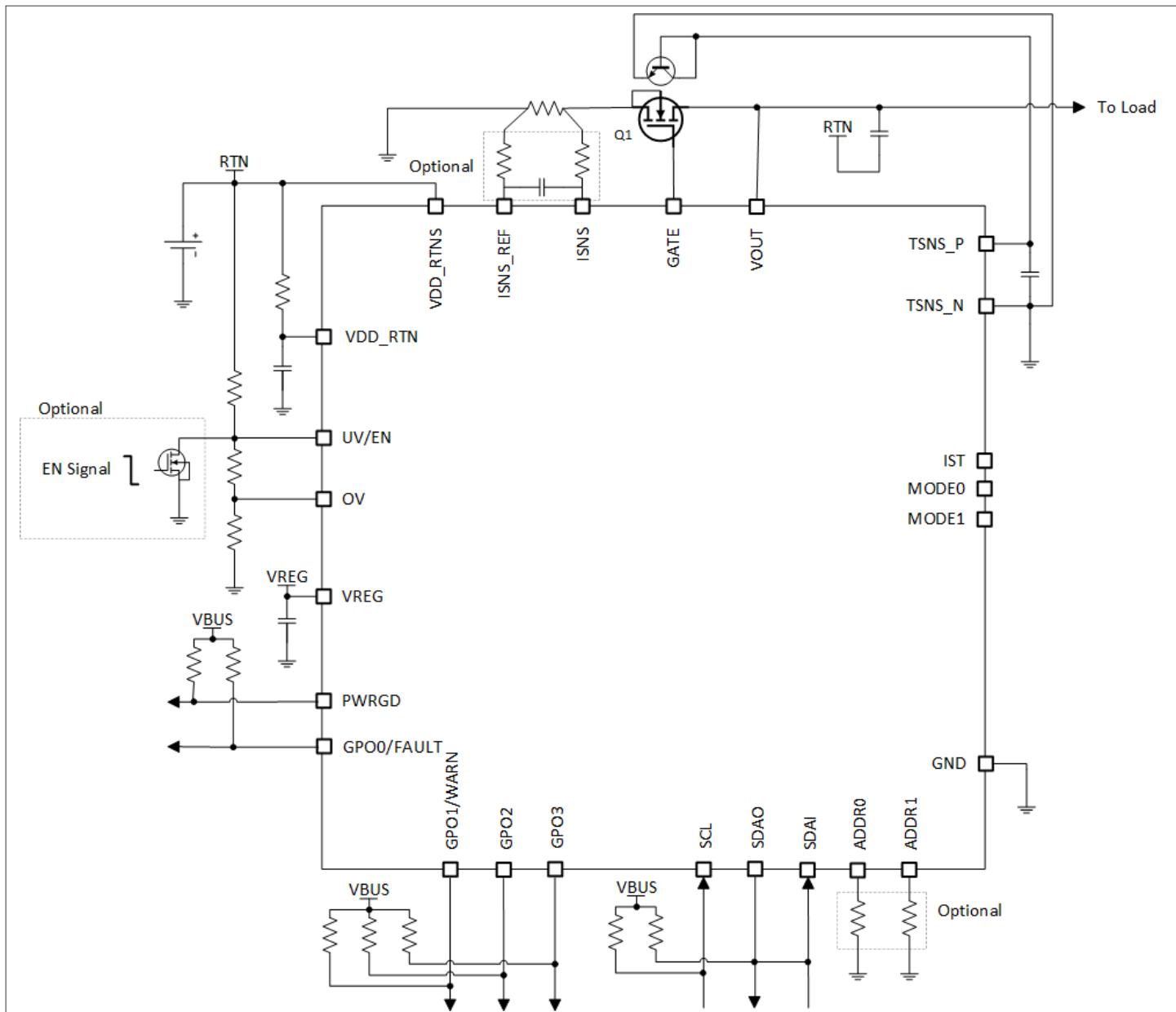

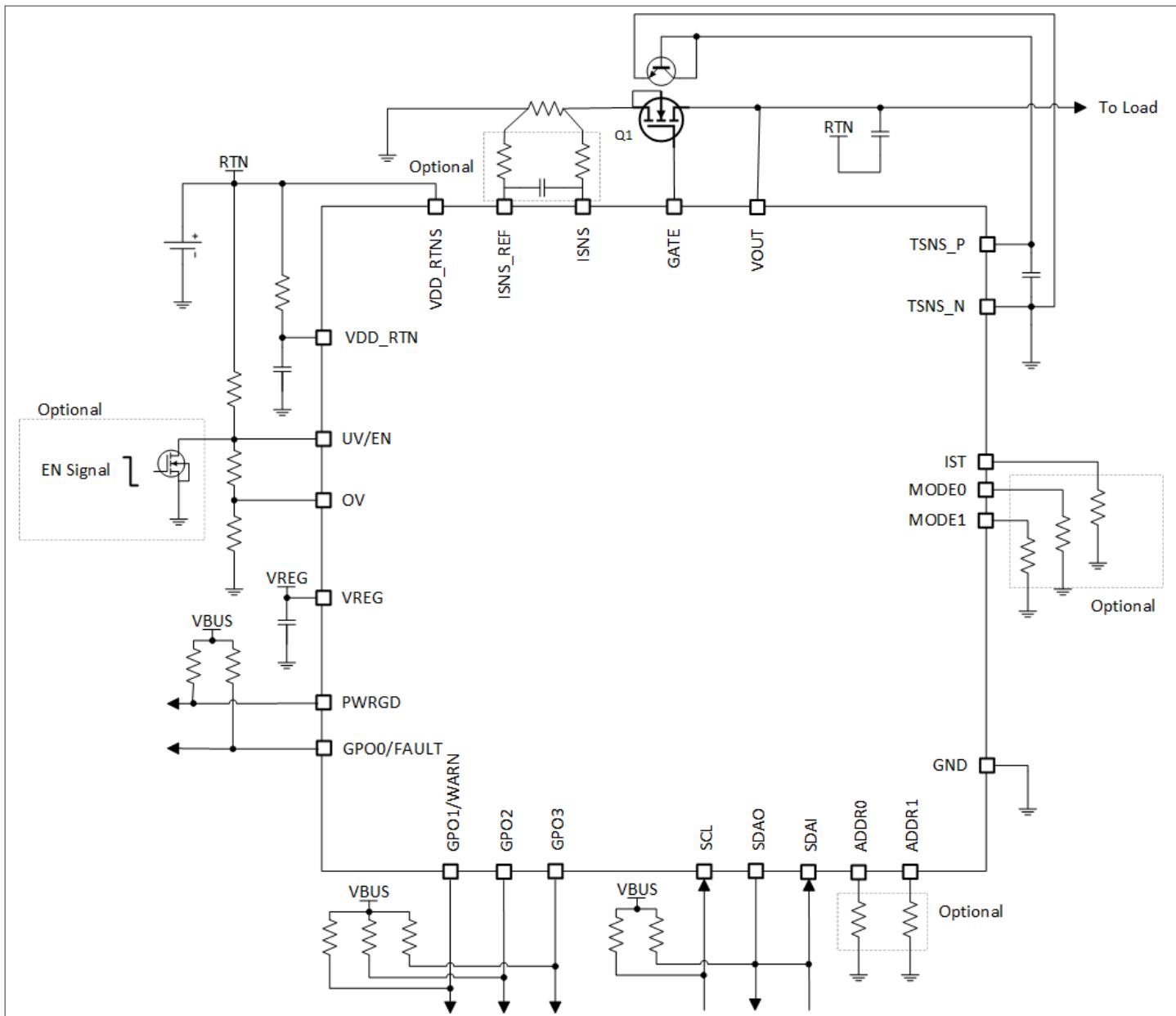

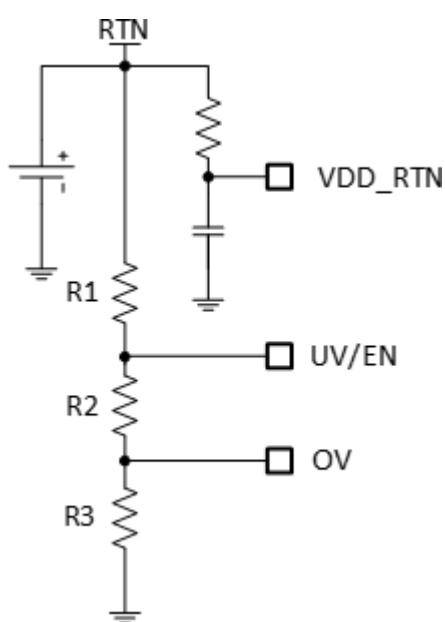

| 5.1      | 典型应用原理图 .....                       | 73        |

| 5.2      | 设置 loc .....                        | 75        |

| 5.3      | 在 ACM 中设置 OV 和 UV .....             | 76        |

| 5.4      | 在 AADM 中设置 MODE1/0 引脚的电压 .....      | 77        |

| 5.5      | 设置 ADDR1/0 引脚的电压 .....              | 77        |

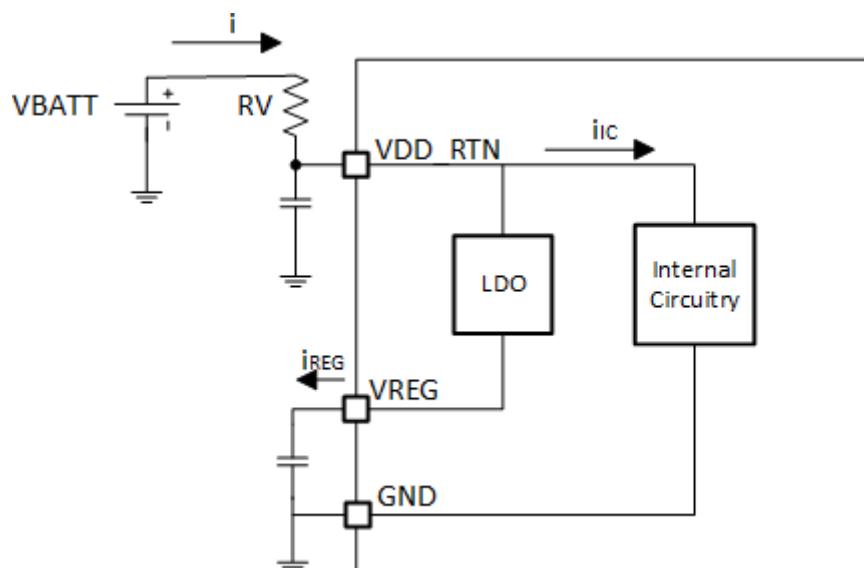

| 5.6      | 处理 VREG 引脚的外部电流 .....               | 77        |

| 5.7      | ISNS 输入过滤器 .....                    | 79        |

| 5.8      | FET 选择考虑因素 .....                    | 80        |

| 5.9      | 根据“真实世界”值计算 PMBus 直接格式限值，反之亦然 ..... | 80        |

| 5.9.1    | 电压 .....                            | 80        |

| 5.9.2    | 电流 .....                            | 81        |

| 5.9.3    | 功率 .....                            | 82        |

| 5.9.4    | 温度 .....                            | 84        |

| 5.9.5    | 能量 .....                            | 84        |

| 5.10     | 布局指南 .....                          | 86        |

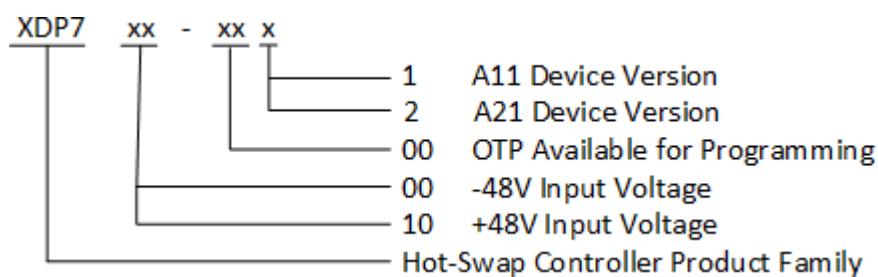

| <b>6</b> | <b>订购信息 .....</b>                   | <b>87</b> |

| <b>7</b> | <b>修订记录 .....</b>                   | <b>88</b> |

|          | <b>免责声明 .....</b>                   | <b>89</b> |

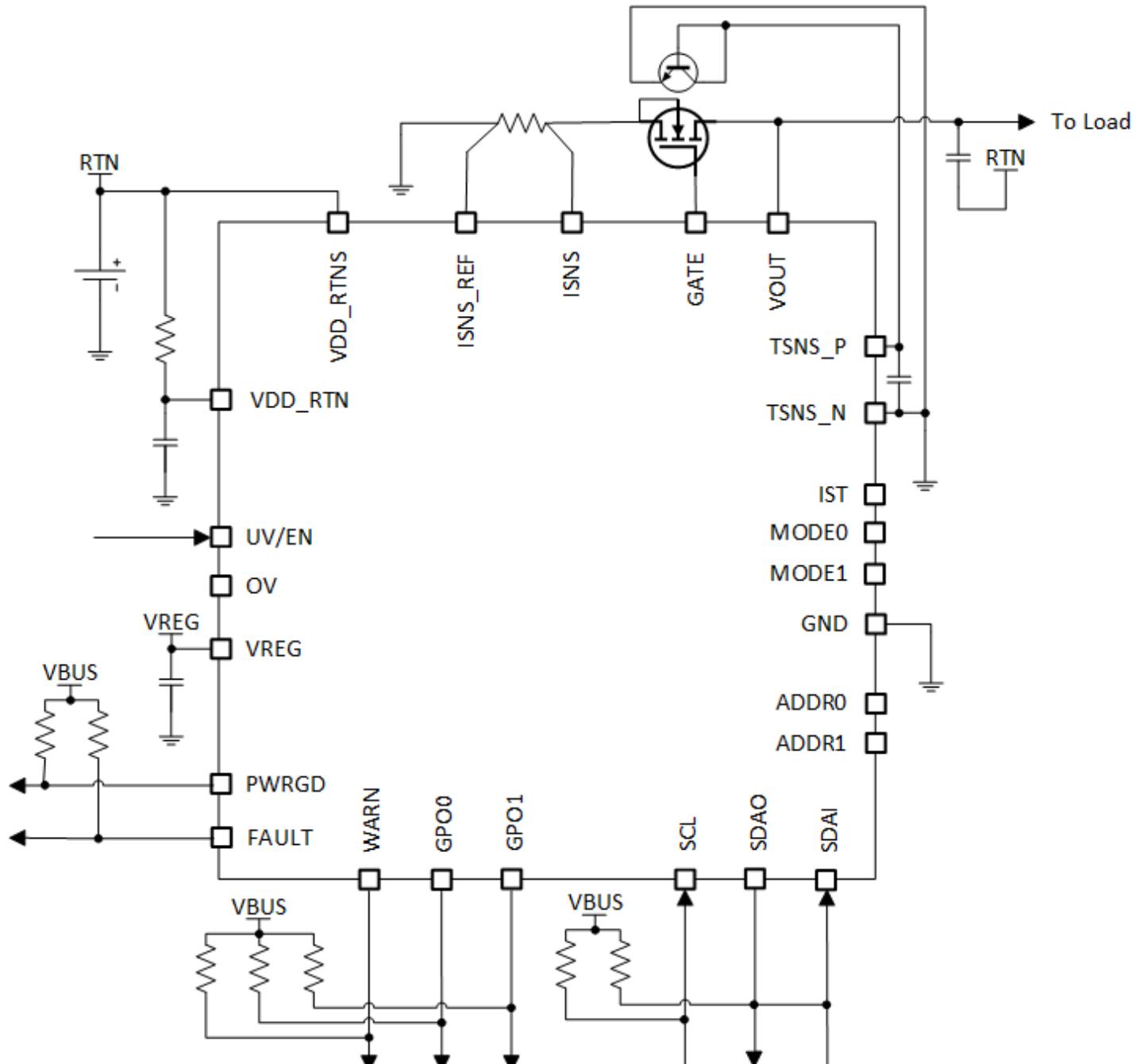

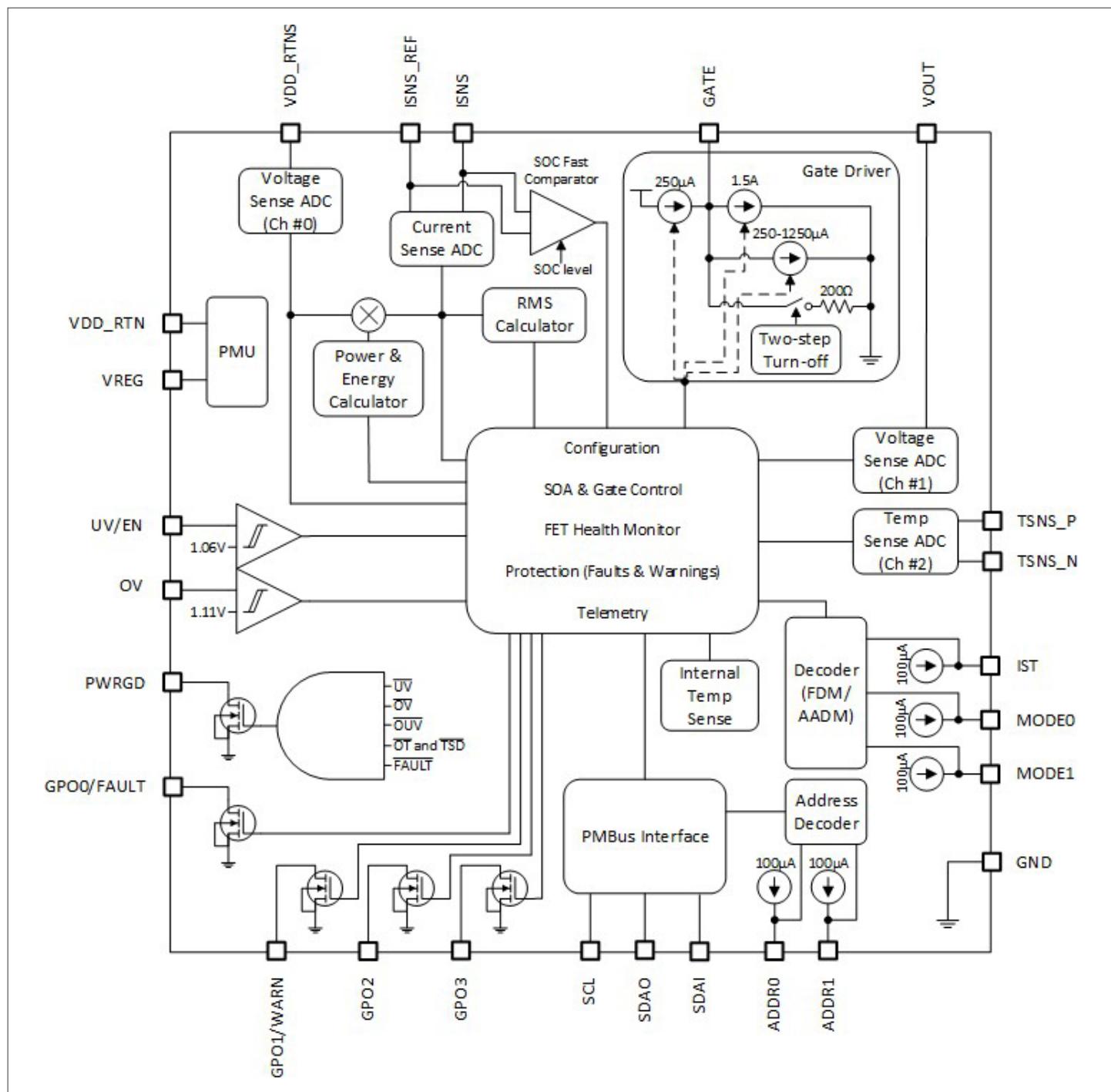

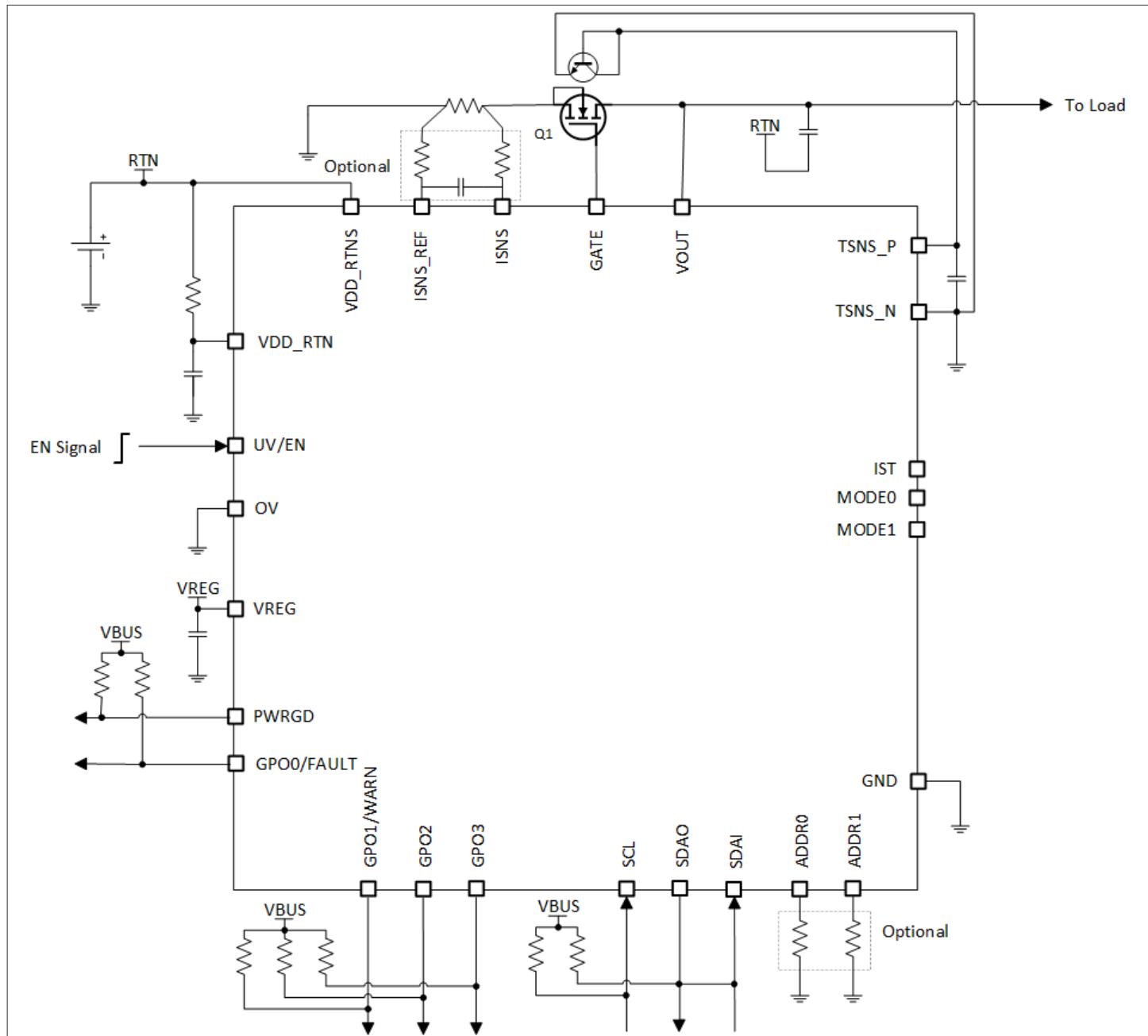

1 框图

## 1 框图

图 1 框图

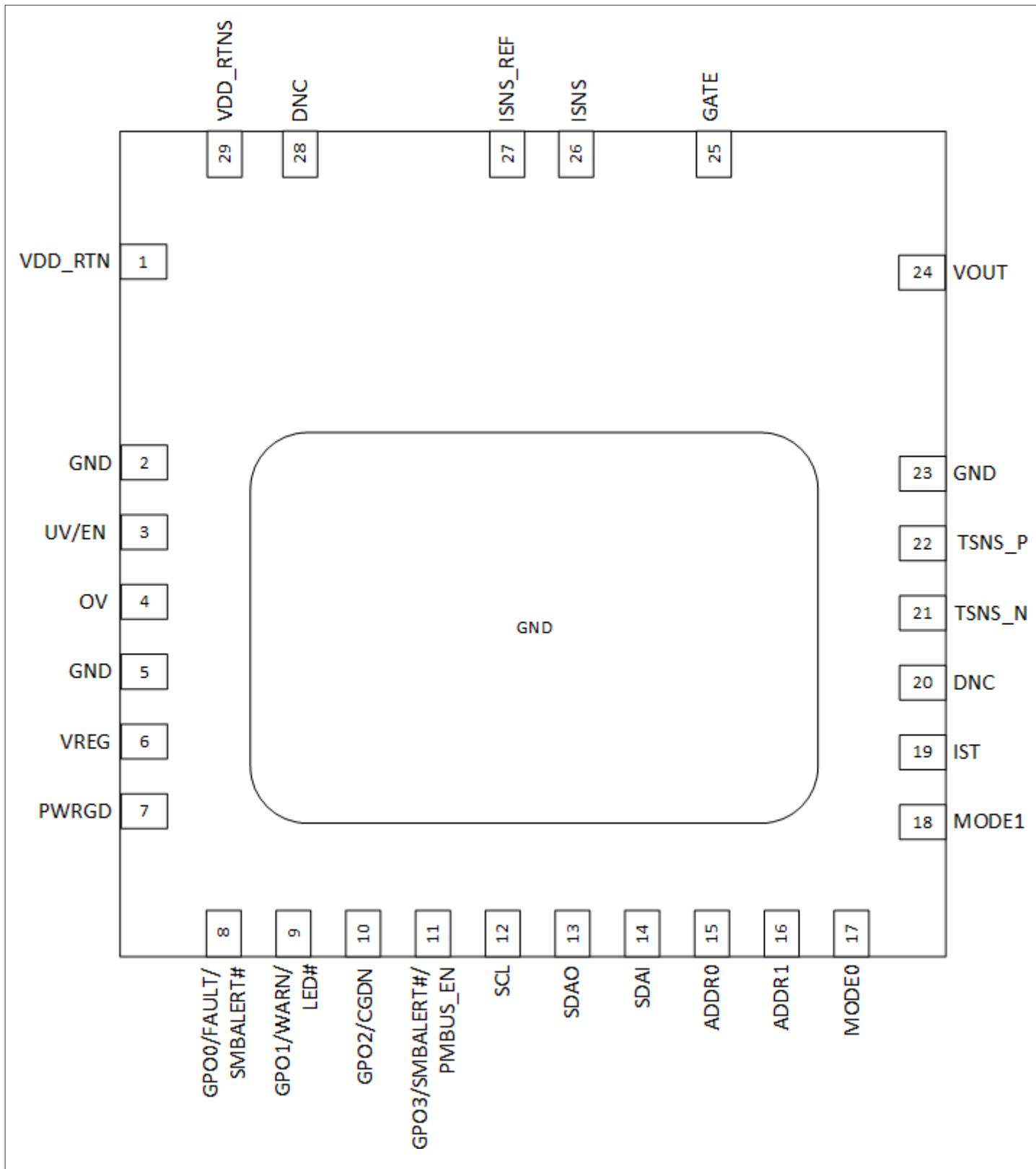

2 引脚配置和封装

## 2 引脚配置和封装

表 1 XDP700 引脚排列

| Pin # | Name                 | I/O | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Connection if unused                               |

|-------|----------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1     | VDD_RTN              |     | P    | <b>Return path</b> pin. Power supply. A 100nF capacitor from this pin to GND is strongly recommended.                                                                                                                                                                                                                                                                                                                                                                                                                 | VDD_RTN                                            |

| 2     | GND                  |     | G    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                                                                                                                                                                                                                                                                              | GND                                                |

| 3     | UV/EN                | I   | A    | <b>Undervoltage detection/enable</b> input. A voltage lower than $V_{UVEN\_LTH}$ on this pin turns off the FET.                                                                                                                                                                                                                                                                                                                                                                                                       | VREG                                               |

| 4     | OV                   | I   | A    | <b>Oversupply detection</b> input. A voltage higher than $V_{OV\_UTH}$ on this pin turns off the FET.                                                                                                                                                                                                                                                                                                                                                                                                                 | GND                                                |

| 5     | GND                  |     | G    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                                                                                                                                                                                                                                                                              | GND                                                |

| 6     | VREG                 |     | P    | <b>VREG</b> (internal 5 V regulator) output. Connect a 1 $\mu$ F capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                      | Connect a 1 $\mu$ F capacitor from this pin to GND |

| 7     | PWRGD                | O   | D    | <b>Power good open drain</b> output. Pin is asserted when VOUT has reached its final level and steady state, FET is fully enhanced and no faults are detected. Its polarity is configurable.                                                                                                                                                                                                                                                                                                                          | Open                                               |

| 8     | GPO0/FAULT/SMBALERT# | O   | D    | <p><b>General-purpose digital output 0.</b> Pin configuration is programmable.</p> <p><b>Fault open drain output</b> if configured, the pin asserts High/Low (programmable) when a fault occurs. The faults that can trigger the pin can be configured.</p> <p><b>SMBALERT# open drain output</b> if configured, the pin asserts low when a fault or warning occurs (depending on configuration). The faults and warnings that can trigger the pin can be configured.</p> <p><b>Default configuration:</b> FAULT.</p> | Open                                               |

(表格续下页.....)

2 引脚配置和封装

表 1 (续) XDP700 引脚排列

| Pin # | Name                            | I/O | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Connection if unused                       |

|-------|---------------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 9     | GPO1/<br>WARN/LED#              | O   | D    | <p><b>General-purpose digital output 1.</b> Pin configuration is programmable.</p> <p><b>Warning open drain output</b> if configured, the pin asserts High/Low (programmable) when a warning occurs. The warnings that can trigger the pin can be configured.</p> <p><b>LED# open drain output</b> if configured, the pin asserts low when a fault occurs. The faults that can trigger the pin can be configured.</p> <p><b>Default configuration:</b> WARN.</p> | Open                                       |

| 10    | GPO2/CGDN                       | I/O | D    | <p><b>General-purpose digital output 2.</b> Pin configuration is programmable.</p> <p><b>Connector Good (CGDN)</b> if configured, if this pin is pulled externally low, the controller is allowed to turn on the FET.</p> <p><b>Default configuration:</b> Disabled.</p>                                                                                                                                                                                         | Open                                       |

| 11    | GPO3/<br>SMBALERT#/<br>PMBUS_EN | I/O | D    | <p><b>General-purpose digital output 3.</b> Pin configuration is programmable.</p> <p><b>SMBALERT# open drain output</b> if configured, the pin asserts low when a fault or warning occurs (depending on configuration). The faults and warnings that can trigger the pin can be configured.</p> <p><b>PMBUS_EN:</b> if configured, enabled or disabled PMBus communication.</p> <p><b>Default configuration:</b> Disabled.</p>                                  | Open                                       |

| 12    | SCL                             | I   | D    | <b>PMBus clock</b> input. The interface is rated to 1 MHz.                                                                                                                                                                                                                                                                                                                                                                                                       | Pull-up to VREG or external voltage source |

| 13    | SDAO                            | O   | D    | <b>PMBus data output.</b> Open drain pin. The serial data is split into an input and an output for easy use with isolators.                                                                                                                                                                                                                                                                                                                                      | Pull-up to VREG or external voltage source |

| 14    | SDAI                            | I   | D    | <b>PMBus data input.</b> The serial data is split into an input and an output for easy use with isolators.                                                                                                                                                                                                                                                                                                                                                       | Pull-up to VREG or external voltage source |

(表格续下页.....)

表 1 (续) XDP700 引脚排列

| Pin # | Name   | I/O | Type | Description                                                                                                                                                                                                                                                      | Connection if unused |

|-------|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15    | ADDR0  | I   | A    | <b>Device address configuration 0 and 1</b><br>inputs. These pins can be tied to GND, left open or tied to GND through a resistor for a total of 16 unique PMBus device addresses.                                                                               | Open                 |

| 16    | ADDR1  | I   | A    | <b>Mode of operation 0 and 1</b> inputs.<br>These pins can be tied to GND, left open or tied to GND through a resistor to select between FDM and AADM.<br>Leave both pins open to select FDM.                                                                    | Open                 |

| 17    | MODE0  | I   | A    | <b>Start-up Current</b> setting input. A resistor to GND on this pin limits the maximum current allowed at start-up phase. This pin is used in AADM and it is to be kept open in FDM.                                                                            | Open                 |

| 18    | MODE1  | I   | A    | Shall be kept open (unconnected).                                                                                                                                                                                                                                | Open                 |

| 19    | IST    | I   | A    | <b>Temperature sense negative</b> terminal.<br>Tie this pin to the emitter of an external NPN BJT to sense the FET's temperature. Connect a 1nF capacitor from this pin to TSNS_P.<br>This pin must be connected locally to GND.                                 | GND                  |

| 20    | DNC    |     |      | <b>Temperature sense positive</b> terminal.<br>Tie this pin to the base and collector of an external NPN BJT to sense the FET's temperature. Connect a 1nF capacitor from this pin to TSNS_N.<br>If unused, this pin must be connected to GND.                   | GND                  |

| 21    | TSNS_N | I   | A    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                         | GND                  |

| 22    | TSNS_P | I   | A    | <b>Output voltage sense</b> input.                                                                                                                                                                                                                               | VOUT                 |

| 23    | GATE   | O   | A    | <b>Gate driver</b> output of single or multiple parallel external N channel FETs, which is/are regulated to a maximum allowed current by regulating the GATE pin voltage.<br>GATE is pulled down when the supply is not within UV and OV limits or fault occurs. | GATE                 |

(表格续下页.....)

2 引脚配置和封装

表 1 (续) XDP700 引脚排列

| Pin # | Name     | I/O | Type | Description                                                                                                                          | Connection if unused |

|-------|----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 26    | ISNS     | I   | A    | <b>Current Sense</b> input. Must be connected to the sense resistor pin that is connected to the source of the FET.                  | ISNS                 |

| 27    | ISNS_REF | I   | A    | <b>Current Sense</b> input. Must be connected to the sense resistor pin that's connected to system negative input (GND of the chip). | ISNS_REF             |

| 28    | DNC      |     |      | <b>Do not connect</b> pin (to provide isolation between high and low voltage signals).                                               | Open                 |

| 29    | VDD_RTNS | I   | A    | <b>Return Path Sense</b> input. Power supply sense input.                                                                            | VDD_RTN              |

| EP    | GND      |     | G    | <b>Ground</b> reference. The exposed pad must be connected to system negative input.                                                 | GND                  |

# XDP700-002 热插拔控制器 宽输入电压范围 (-6.5 V 至 -80 V) 系统监控和保护 IC

2引脚配置和封装

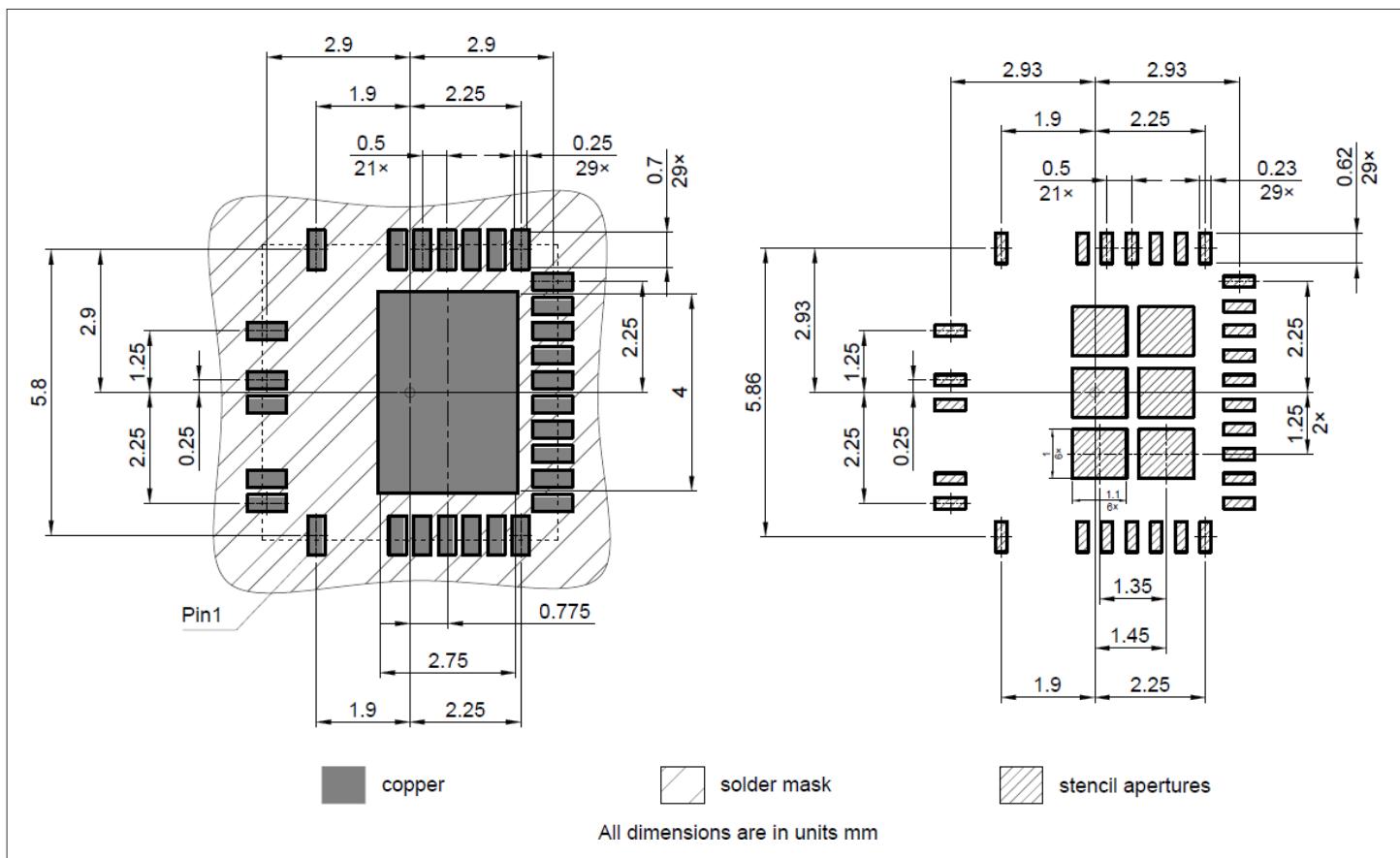

图 2

VQFN-29 6x6 引脚排列

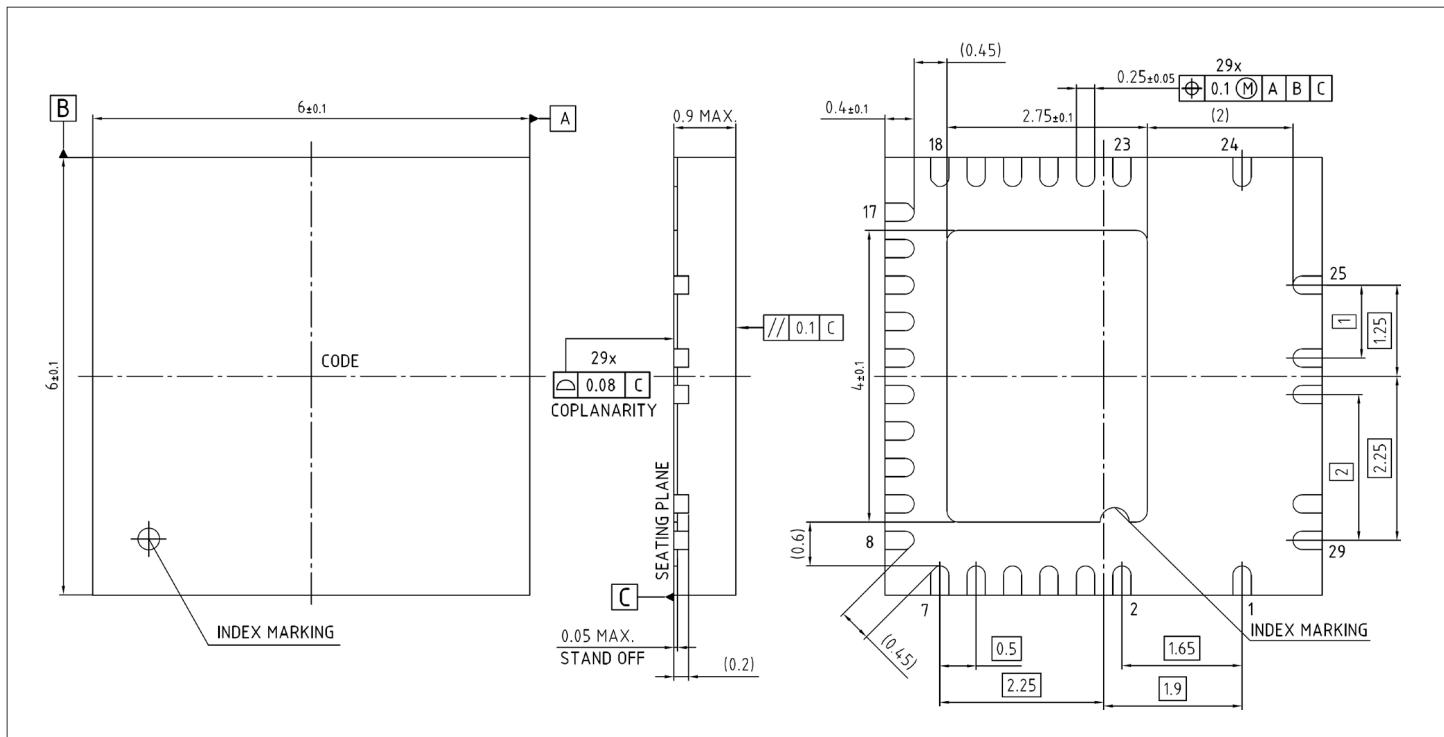

2 引脚配置和封装

图3 封装尺寸

图 4 建议占用空间

### 3 产品基本特性

## 3 产品基本特性

### 3.1 绝对最大额定值

**表 2 绝对最大额定值**

为了确保器件的正确操作和可靠性，不得超过以下操作条件。除非另有说明，所有电压参数均以 GND 为参考，正电流流入引脚。

| Parameter                                                                 | Symbol                                                                                                         | Values |      |      | Unit | Note or condition                                                                                                                                     |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           |                                                                                                                | Min.   | Typ. | Max. |      |                                                                                                                                                       |

| Supply voltage at VDD_RTN pin                                             | VDD_RTN <sub>DC</sub>                                                                                          | -0.3   | -    | 80   | V    |                                                                                                                                                       |

| Supply voltage transients at VDD_RTN pin                                  | VDD_RTN <sub>AC</sub>                                                                                          | -      | -    | 100  | V    | For 500 ms maximum.                                                                                                                                   |

| Voltage slew rate at VDD_RTN pin                                          | VDD_RTN <sub>SR</sub>                                                                                          | -      | -    | ±80  | V/μs | The RC filter (i.e. 10 Ω / 100 nF, or 100 Ω / 10 nF, etc.) on the pin is recommended, especially for high voltage (i.e. 48 V) applications.           |

| Voltage slew rate at VDD_RTNS pin                                         | VDD_RTNS <sub>SR</sub>                                                                                         | -      | -    | ±2   | V/ns | Max is defined by hot plug scenario. The resistor (i.e. 10 Ω) in series to the pin is recommended if an excessive dV/dt may occur in the application. |

| Voltage slew rate at VOUT pin                                             | VOUT <sub>SR</sub>                                                                                             | -      | -    | ±80  | V/μs | An output cap (10 μF min) limits a slew rate on the pin.                                                                                              |

| Output voltage at GATE pin                                                | V <sub>GATE</sub>                                                                                              | -0.3   | -    | 15   | V    |                                                                                                                                                       |

| GATE to SOURCE voltage                                                    | V <sub>GATE-SOURCE_DC</sub>                                                                                    | -0.3   | -    | 12   | V    |                                                                                                                                                       |

| GATE to SOURCE voltage transients                                         | V <sub>GATE-SOURCE_AC</sub>                                                                                    | -      | -    | 15   | V    | For 500ms max                                                                                                                                         |

| Output voltage at VREG pin                                                | V <sub>VREG</sub>                                                                                              | -0.3   | -    | 6    | V    |                                                                                                                                                       |

| Digital pins output voltage (PWRGD, FAULT, WARN, GPO <sub>x</sub> , SDAO) | V <sub>PWRGD</sub> , V <sub>FAULT</sub> , V <sub>WARN</sub> , V <sub>GPO<sub>x</sub></sub> , V <sub>SDAO</sub> | -0.3   | -    | 6    | V    |                                                                                                                                                       |

| Input voltage at VDD_RTNS pin                                             | VDD_RTNS <sub>DC</sub>                                                                                         | -0.3   | -    | 80   | V    |                                                                                                                                                       |

| Input voltage transients at VDD_RTNS pin                                  | VDD_RTNS <sub>AC</sub>                                                                                         | -      | -    | 100  | V    | For 500 ms maximum.                                                                                                                                   |

(表格续下页.....)

### 3 产品基本特性

**表 2 (续) 绝对最大额定值**

为了确保器件的正确操作和可靠性，不得超过以下操作条件。除非另有说明，所有电压参数均以 GND 为参考，正电流流入引脚。

| <b>Parameter</b>                                                                           | <b>Symbol</b>                                                                                                                                 | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b> |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------|-------------|--------------------------|

|                                                                                            |                                                                                                                                               | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                          |

| Input voltage at VOUT pin                                                                  | VOUT <sub>DC</sub>                                                                                                                            | -1            | -           | 80          | V           |                          |

| Input voltage transients at VOUT pin                                                       | VOUT <sub>AC</sub>                                                                                                                            | -             | -           | 100         | V           | For 500 ms maximum.      |

| Input voltage at ISNS_REF pin                                                              | V <sub>ISNS_REF</sub>                                                                                                                         | -0.3          | -           | 0.3         | V           |                          |

| Input voltage at ISNS pin                                                                  | V <sub>ISNS</sub>                                                                                                                             | -0.8          | -           | 0.8         | V           |                          |

| Current Sense input voltage (ISNS_REF - ISNS)                                              | V <sub>ΔISNS</sub>                                                                                                                            | -0.8          | -           | 0.8         | V           |                          |

| Analog pins input voltage (UV/EN, OV, ADDR <sub>x</sub> , MODE <sub>x</sub> , IST, TSNS_N) | V <sub>UV_EN</sub> , V <sub>OV</sub> , V <sub>ADDR<sub>x</sub></sub> , V <sub>MODE<sub>x</sub></sub> , V <sub>IST</sub> , V <sub>TSNS_N</sub> | -0.3          | -           | 6           | V           |                          |

| Input voltage at TSNS_P pin                                                                | V <sub>TSNS_P</sub>                                                                                                                           | -0.3          | -           | 2.5         | V           |                          |

| Digital pins input voltage (SCL, SDAI)                                                     | V <sub>SCL</sub> , V <sub>SDAI</sub>                                                                                                          | -0.3          | -           | 6           | V           |                          |

| Junction temperature range                                                                 | T <sub>J</sub>                                                                                                                                | -40           | -           | 150         | °C          |                          |

| Storage temperature range                                                                  | T <sub>s</sub>                                                                                                                                | -55           | -           | 150         | °C          |                          |

### 3.2 工作范围

**表3 功能和性能范围描述**

| <b>Absolute voltage range at VDD_RTN</b> | <b>Communication interface</b> | <b>FET gate</b>         | <b>VREG</b> |

|------------------------------------------|--------------------------------|-------------------------|-------------|

| 0 ≤ Vin < 6.5                            | Off                            | Off (passive pull-down) | Off         |

(表格续下页.....)

3 产品基本特性

表 3 (续) 功能和性能范围描述

| Absolute voltage range at VDD_RTIN | Communication interface | FET gate                                                                                               | VREG              |

|------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------|-------------------|

| 6.5 ≤ Vin < 9                      | On                      | Limited operation: - Off (active pull-down); - limited SOA regulation depending on gate driver supply; | 4.5V (minimum)    |

| 9 ≤ Vin < 14                       |                         | - On/enhancement is not guaranteed (but ≥ 4.5 V)                                                       | 5.0 V (typically) |

| 14 ≤ Vin ≤ 80                      |                         | Full operation: - Off (active pull-down); - full SOA regulation; - On/ enhancement (typically 10.5 V)  |                   |

表 4 工作范围

为确保器件正常工作和可靠性，不得超过以下工作条件。除非另有说明，所有电压参数均以GND为基准，正电流流入引脚，T<sub>A</sub>=25°C。

| Parameter                                                                          | Symbol                                                                                            | Values |            |      | Unit | Note or condition                                                                                                                        |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------|------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                    |                                                                                                   | Min.   | Typ.       | Max. |      |                                                                                                                                          |

| Supply voltage at VDD_RTIN pin                                                     | VDD_RTIN                                                                                          | 6.5    |            | 80   | V    |                                                                                                                                          |

| Supply voltage at VDD_RTIN pin to enable all features                              | VDD_RTIN <sub>EN</sub>                                                                            | 14     | -          | -    | V    | See Table 3.                                                                                                                             |

| VDD_RTNS sense pin input voltage                                                   | VDD_RTNS                                                                                          | 6.5    | 12, 24, 48 | 80   | V    |                                                                                                                                          |

| VOUT sense pin input voltage                                                       | VOUTS                                                                                             | 0      | -          | 80   | V    |                                                                                                                                          |

| Current sense input voltage (ISNS_REF - ISNS)                                      | V <sub>ΔISNS</sub>                                                                                | -0.4   | -          | 0.4  | V    |                                                                                                                                          |

| Minimum overcurrent setting                                                        | I <sub>OC_MIN</sub>                                                                               | 5      | -          | -    | A    | Minimum I <sub>OC</sub> (I <sub>OC</sub> = V <sub>SNS_CS</sub> / R <sub>SNS</sub> , see Setting I <sub>OC</sub> ) for optimum stability. |

| Analog pins input voltage (UV/EN, OV, ADDR <sub>x</sub> , MODE <sub>x</sub> , IST) | V <sub>UV_EN</sub> , V <sub>OV</sub> , V <sub>ADDRx</sub> , V <sub>MODEx</sub> , V <sub>IST</sub> | 0      | -          | 5.5  | V    |                                                                                                                                          |

(表格续下页.....)

### 3 产品基本特性

**表 4 (续) 功能范围**

为确保器件正常工作和可靠性，不得超过以下工作条件。除非另有说明，所有电压参数均以GND为基准，正电流流入引脚， $T_A=25^\circ\text{C}$ 。

| Parameter                                                    | Symbol                                                                                  | Values |      |      | Unit | Note or condition           |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------|------|------|------|-----------------------------|

|                                                              |                                                                                         | Min.   | Typ. | Max. |      |                             |

| Digital pins input voltage (SCL, SDAl)                       | $V_{\text{SCL}}, V_{\text{SDAI}}$                                                       | 0      | -    | 5.5  | V    |                             |

| Output voltage at VREG pin                                   | $V_{\text{VREG}}$                                                                       | 4.5    | 5    | 5.5  | V    | At 10 mA max external load. |

| Digital pins output voltage (PWRGD, FAULT, WARN, GPOx, SDAO) | $V_{\text{PWRGD}}, V_{\text{FAULT}}, V_{\text{WARN}}, V_{\text{GPOx}}, V_{\text{SDAO}}$ | 0      | -    | 5.5  | V    |                             |

| Junction temperature range                                   | $T_J$                                                                                   | -40    | -    | 125  | °C   |                             |

### 3.3 热特性

**表5 热特性**

| Parameter                                    | Symbol                     | Values |      |      | Unit | Note or condition                                              |

|----------------------------------------------|----------------------------|--------|------|------|------|----------------------------------------------------------------|

|                                              |                            | Min.   | Typ. | Max. |      |                                                                |

| Thermal resistance Junction-to-case (bottom) | $R_{\Theta\text{JC\_Bot}}$ | -      | 5    | -    | K/W  | PCB simulation setup as described in <a href="#">Table 6</a> . |

| Thermal resistance Junction-to-case (top)    | $R_{\Theta\text{JC\_Top}}$ | -      | 30   | -    | K/W  | PCB simulation setup as described in <a href="#">Table 6</a> . |

| Thermal resistance Junction-to-Ambient       | $R_{\Theta\text{JA}}$      | -      | 33   | -    | K/W  | PCB simulation setup as described in <a href="#">Table 6</a> . |

| Package power dissipation                    | $P_{\text{PAK}}$           | -      | -    | 0.8  | W    |                                                                |

**表6 热模拟的PCB特性**

|                                 |                                   | $\lambda_{\text{therm}} [\text{W/m}\cdot\text{K}]$ |

|---------------------------------|-----------------------------------|----------------------------------------------------|

| Metalization                    | JEDEC 2s2p (JESD 51-7, JESD 51-5) | 388                                                |

| Cooling Area [mm <sup>2</sup> ] | none                              | 388                                                |

### 3 产品基本特性

注释：热性能与印刷电路板 (PCB) 设计和工作环境直接相关。需要仔细考虑 PCB 的散热设计。

注释：此热数据根据 JEDEC JESD51 标准生成。更多信息，请访问 [www.jedec.org](http://www.jedec.org)

## 3.4 电流消耗

**表 7 电流消耗**

除非另有说明， $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = [V_{ISNS\_REF} - V_{ISNS}] = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  至  $+125^\circ\text{C}$ 。

| <b>Parameter</b>    | <b>Symbol</b> | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b>                                         |

|---------------------|---------------|---------------|-------------|-------------|-------------|------------------------------------------------------------------|

|                     |               | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                                                                  |

| Current consumption | $I_{VDD}$     | -             | 6           | 10          | mA          | VDD_RTN supply current:<br><br>FET is fully ON, telemetry in ON. |

## 3.5 ESD 鲁棒性

**表8 ESD鲁棒性**

| <b>Parameter</b>   | <b>Symbol</b>  | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b>                                      |

|--------------------|----------------|---------------|-------------|-------------|-------------|---------------------------------------------------------------|

|                    |                | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                                                               |

| ESD Robustness HBM | $V_{ESD\_HBM}$ | -             | -           | $\pm 2000$  | V           | Human Body Model sensitivity as per ANSI/ESDA/JEDEC JS-001    |

| ESD Robustness CDM | $V_{ESD\_CDM}$ | -             | -           | $\pm 500$   | V           | Charge Device Model sensitivity as per ANSI/ESDA/JEDEC JS-002 |

## 3.6 电气特性

**表9 电气特性**

除非另有说明， $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b> | <b>Symbol</b> | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b> |

|------------------|---------------|---------------|-------------|-------------|-------------|--------------------------|

|                  |               | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                          |

### UV/EN 和 OV

|                       |                                    |      |      |      |   |  |

|-----------------------|------------------------------------|------|------|------|---|--|

| Input upper threshold | $V_{UVEN\_UTH}$ ,<br>$V_{OV\_UTH}$ | 1.09 | 1.11 | 1.13 | V |  |

| Input lower threshold | $V_{UVEN\_LTH}$ ,<br>$V_{OV\_LTH}$ | 1.04 | 1.06 | 1.08 | V |  |

### TSNS\_P、 TSNS\_N

|                                |               |      |   |   |   |  |

|--------------------------------|---------------|------|---|---|---|--|

| TSNS_P operating voltage range | $V_{TSNS\_P}$ | 0.25 | - | 1 | V |  |

|--------------------------------|---------------|------|---|---|---|--|

(表格续下页.....)

3 产品基本特性

**表 9 (续) 电气特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b>         | <b>Symbol</b> | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b> |

|--------------------------|---------------|---------------|-------------|-------------|-------------|--------------------------|

|                          |               | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                          |

| TSNS_N operating voltage | $V_{TSNS\_N}$ | -             | 0           | -           | V           |                          |

**ISNS\_REF, ISNS**

|                                               |                |                      |       |       |    |                                                                                                                                                                      |

|-----------------------------------------------|----------------|----------------------|-------|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum detectable differential voltage level | $V_{SNS\_MIN}$ | 0.01 * $V_{SNS\_CS}$ | -     | -     | mV | Between ISNS_REF and ISNS pins.                                                                                                                                      |

| Current sense differential voltage range      | $V_{SNS\_CS}$  | -                    | 12.5  | -     | mV | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 00                                                                                                                            |

| Current sense differential voltage range      | $V_{SNS\_CS}$  | -                    | 25    | -     | mV | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 01                                                                                                                            |

| Current sense differential voltage range      | $V_{SNS\_CS}$  | -                    | 50    | -     | mV | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 10                                                                                                                            |

| Current sense differential voltage range      | $V_{SNS\_CS}$  | -                    | 100   | -     | mV | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 11                                                                                                                            |

| SOC Differential voltage level                | $V_{SNS\_soc}$ | 9.5                  | 12.5  | 15.5  | mV | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 000 and CS_RNG[1:0] = 00 or 01                                                           |

| SOC Differential voltage level                | $V_{SNS\_soc}$ | 15.75                | 18.75 | 21.75 | mV | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 001 and CS_RNG[1:0] = 00 or 01                                                           |

| SOC Differential voltage level                | $V_{SNS\_soc}$ | 22                   | 25    | 28    | mV | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 010 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 000 and CS_RNG[1:0] = 10 or 11 |

| SOC Differential voltage level                | $V_{SNS\_soc}$ | 34.5                 | 37.5  | 40.5  | mV | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 011 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 001 and CS_RNG[1:0] = 10 or 11 |

(表格续下页.....)

3 产品基本特性

表 9 (续) 电气特性

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| Parameter                      | Symbol         | Values |      |      | Unit | Note or condition                                                                                                                                                    |

|--------------------------------|----------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                | Min.   | Typ. | Max. |      |                                                                                                                                                                      |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 47     | 50   | 53   | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 100 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 010 and CS_RNG[1:0] = 10 or 11 |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 71     | 75   | 79   | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 101 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 011 and CS_RNG[1:0] = 10 or 11 |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 96     | 100  | 104  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 110 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 100 and CS_RNG[1:0] = 10 or 11 |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 145    | 150  | 155  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 111 and CS_RNG[1:0] = 00 or 01; or SOC_FAULT_LIMIT[2:0] = 101 and CS_RNG[1:0] = 10 or 11 |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 193    | 200  | 207  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 110 and CS_RNG[1:0] = 10 or 11                                                           |

| SOC Differential voltage level | $V_{SNS\_soc}$ | 290    | 300  | 310  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0] bits:<br>SOC_FAULT_LIMIT[2:0] = 111 and CS_RNG[1:0] = 10 or 11                                                           |

| Current sense ADC resolution   | $ADC_{RES}$    | -      | 12   | -    | bits |                                                                                                                                                                      |

| Max allowed negative current   | $I_{NEG\_MAX}$ | -      | 240  | -    | mA   | To trigger INEG warning.<br>$V_{SNS\_CS} = 12.5 \text{ mV}$ , $R_{sns} = 1 \text{ m}\Omega$ .                                                                        |

| Max allowed negative current   | $I_{NEG\_MAX}$ | -      | 520  | -    | mA   | To trigger INEG warning.<br>$V_{SNS\_CS} = 25 \text{ mV}$ , $R_{sns} = 1 \text{ m}\Omega$ .                                                                          |

| Max allowed negative current   | $I_{NEG\_MAX}$ | -      | 1100 | -    | mA   | To trigger INEG warning.<br>$V_{SNS\_CS} = 50 \text{ mV}$ , $R_{sns} = 1 \text{ m}\Omega$ .                                                                          |

(表格续下页.....)

3 产品基本特性

表 9 (续) 电气特性

除非另有说明,  $V_{DD\_RTN} - GND = 48 V$ ,  $V_{ISNS\_REF} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$

| Parameter                    | Symbol         | Values |      |      | Unit | Note or condition                                                            |

|------------------------------|----------------|--------|------|------|------|------------------------------------------------------------------------------|

|                              |                | Min.   | Typ. | Max. |      |                                                                              |

| Max allowed negative current | $I_{NEG\_MAX}$ | -      | 2200 | -    | mA   | To trigger INEG warning.<br>$V_{SNS\_CS} = 100 mV$ , $R_{SNS} = 1 m\Omega$ . |

栅极

|                                           |                           |       |      |       |          |                                                                                                                                             |

|-------------------------------------------|---------------------------|-------|------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Gate voltage                              | $V_{GATE}$                | 8.5   | 10.5 | 12.0  | V        | $14 V \leq V_{DD\_RTN} \leq 80 V$ , $I_{GATE} \leq 5 \mu A$ , FET is fully ON.                                                              |

| Gate voltage                              | $V_{GATE}$                | 4.5   | -    | -     | V        | $6.5 V \leq V_{DD\_RTN} < 14 V$ , $I_{GATE} \leq 5 \mu A$ .                                                                                 |

| Pull-up current                           | $I_{GATE\_PU}$            | 200   | 250  | 300   | $\mu A$  | At $V_{GATE} = 5 V$                                                                                                                         |

| Fast pull-down current                    | $I_{GATE\_FPD}$           | 0.825 | 1.5  | 2.175 | A        | Set by GATE_FAST_PD[0]: GATE_FAST_PD[0] = 0                                                                                                 |

| GATE pin two step turn-off fast pull-down | $R_{GATE\_2ST\_FAST\_PD}$ | 156   | 200  | 244   | $\Omega$ | Set by GATE_FAST_PD[0]: GATE_FAST_PD[0] = 1                                                                                                 |

| Slow pull-down current                    | $I_{GATE\_SPD}$           | 200   | 250  | 300   | $\mu A$  | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 00<br>Used for both regular/slow pull-down and second phase of the two-step turn-off. |

| Slow pull-down current                    | $I_{GATE\_SPD}$           | 400   | 500  | 600   | $\mu A$  | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 01<br>Used for both regular/slow pull-down and second phase of the two-step turn-off. |

| Slow pull-down current                    | $I_{GATE\_SPD}$           | 600   | 750  | 900   | $\mu A$  | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 10<br>Used for both regular/slow pull-down and second phase of the two-step turn-off. |

| Slow pull-down current                    | $I_{GATE\_SPD}$           | 1000  | 1250 | 1500  | $\mu A$  | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 11<br>Used for both regular/slow pull-down and second phase of the two-step turn-off. |

VDD\_RTNS

|                                                                                          |                 |   |    |   |         |                                                                  |

|------------------------------------------------------------------------------------------|-----------------|---|----|---|---------|------------------------------------------------------------------|

| Input current                                                                            | $I_{VDD\_RTNS}$ | - | 15 | - | $\mu A$ | At 48 V                                                          |

| On-chip input over voltage upper threshold for on-chip input overvoltage fault assertion | $OV_{IN\_UTH}$  | - | 70 | - | V       | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 00 |

(表格续下页.....)

3 产品基本特性

**表 9 (续) 电气特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b>                                                                         | <b>Symbol</b>   | <b>Values</b> |                            |             | <b>Unit</b>   | <b>Note or condition</b>                                             |

|------------------------------------------------------------------------------------------|-----------------|---------------|----------------------------|-------------|---------------|----------------------------------------------------------------------|

|                                                                                          |                 | <b>Min.</b>   | <b>Typ.</b>                | <b>Max.</b> |               |                                                                      |

| On-chip input over voltage upper threshold for on-chip input overvoltage fault assertion | $OV_{IN\_UTH}$  | -             | 75                         | -           | V             | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 01     |

| On-chip input over voltage upper threshold for on-chip input overvoltage fault assertion | $OV_{IN\_UTH}$  | -             | 80                         | -           | V             | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 10     |

| On-chip input over voltage upper threshold for on-chip input overvoltage fault assertion | $OV_{IN\_UTH}$  | -             | 85                         | -           | V             | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 11     |

| On-chip input over voltage lower threshold for on-chip input overvoltage fault release   | $OV_{IN\_LTH}$  | -             | $OV_{IN\_UTH} - 5\text{V}$ | -           | V             | For on-chip input overvoltage fault release.                         |

| <b>VOUT</b>                                                                              |                 |               |                            |             |               |                                                                      |

| Input current                                                                            | $I_{VOUT}$      | -             | 15                         | -           | $\mu\text{A}$ | At 48 V                                                              |

| Output over voltage upper threshold for output overvoltage fault assertion               | $OV_{OUT\_UTH}$ | -             | 70                         | -           | V             | Set by OVOUT_FAULT_LIMIT [1:0]<br>bits: OVOUT_FAULT_LIMIT [1:0] = 00 |

(表格续下页.....)

3 产品基本特性

**表 9 (续) 电气特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b>                                                           | <b>Symbol</b>   | <b>Values</b> |                             |             | <b>Unit</b> | <b>Note or condition</b>                                                         |

|----------------------------------------------------------------------------|-----------------|---------------|-----------------------------|-------------|-------------|----------------------------------------------------------------------------------|

|                                                                            |                 | <b>Min.</b>   | <b>Typ.</b>                 | <b>Max.</b> |             |                                                                                  |

| Output over voltage upper threshold for output overvoltage fault assertion | $OV_{OUT\_UTH}$ | -             | 75                          | -           | V           | Set by $OV_{OUT\_FAULT\_LIMIT}[1:0]$<br>bits: $OV_{OUT\_FAULT\_LIMIT}[1:0] = 01$ |

| Output over voltage upper threshold for output overvoltage fault assertion | $OV_{OUT\_UTH}$ | -             | 80                          | -           | V           | Set by $OV_{OUT\_FAULT\_LIMIT}[1:0]$<br>bits: $OV_{OUT\_FAULT\_LIMIT}[1:0] = 10$ |

| Output over voltage upper threshold for output overvoltage fault assertion | $OV_{OUT\_UTH}$ | -             | 85                          | -           | V           | Set by $OV_{OUT\_FAULT\_LIMIT}[1:0]$<br>bits: $OV_{OUT\_FAULT\_LIMIT}[1:0] = 11$ |

| Output over voltage lower threshold for output overvoltage fault release   | $OV_{OUT\_LTH}$ | -             | $OV_{OUT\_UTH} - 5\text{V}$ | -           | V           | For output overvoltage fault release.                                            |

**遥测**

|                                                     |            |    |            |           |   |                                                                                                                                                                       |

|-----------------------------------------------------|------------|----|------------|-----------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitored voltage range (input and output voltages) | $V_{TLM}$  | 22 | -          | 88        | V | Set by $VTLM\_RNG[1:0]$ bits:<br><ul style="list-style-type: none"> <li>• 2'b00: 88 V</li> <li>• 2'b01: 44 V</li> <li>• 2'b10: 22 V</li> <li>• 2'b11: n.a.</li> </ul> |

| Input voltage measurements accuracy                 | $A_{VIN}$  | -  | $\pm 0.2$  | $\pm 0.4$ | % | At $V_{DD\_RTNS}$ vs GND: $V_{DD\_RTNS} = 20 \text{ V}$ to $40 \text{ V}$ or $10 \text{ V}$ to $20 \text{ V}$ depending on corresponding programmed range $V_{TLM}$ . |

| Output voltage measurement s accuracy               | $A_{VOUT}$ | -  | $\pm 0.2$  | $\pm 0.4$ | % | At $V_{OUT}$ vs GND: $V_{OUT} = 20 \text{ V}$ to $40 \text{ V}$ or $10 \text{ V}$ to $20 \text{ V}$ depending on corresponding programmed range $V_{TLM}$ .           |

| Input voltage measurements accuracy                 | $A_{VIN}$  | -  | $\pm 0.25$ | $\pm 0.5$ | % | At $V_{DD\_RTNS}$ vs GND: $V_{DD\_RTNS} = 40 \text{ V}$ to $80 \text{ V}$ , $V_{TLM} = 88 \text{ V}$ .                                                                |

(表格续下页.....)

3 产品基本特性

表 9 (续) 电气特性

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| Parameter                           | Symbol     | Values |            |           | Unit | Note or condition                                                                                                                                                                                                                               |

|-------------------------------------|------------|--------|------------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     |            | Min.   | Typ.       | Max.      |      |                                                                                                                                                                                                                                                 |

| Output voltage measurement accuracy | $A_{VOUT}$ | -      | $\pm 0.25$ | $\pm 0.5$ | %    | At $V_{OUT}$ vs GND: $V_{OUT} = 40 \text{ V}$ to $80 \text{ V}$ , $V_{TLM} = 88 \text{ V}$ .                                                                                                                                                    |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.1$  | $\pm 0.2$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 100 \text{ mV}$ or $50 \text{ mV}$ .                                                                                                                       |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.2$  | $\pm 0.3$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 2$ , where $V_{SNS\_CS} = 100 \text{ mV}$ or $50 \text{ mV}$ .                                                                                                                   |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.35$ | $\pm 0.5$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 4$ , where $V_{SNS\_CS} = 100 \text{ mV}$ or $50 \text{ mV}$ .                                                                                                                   |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.16$ | $\pm 0.7$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 25 \text{ mV}$ .                                                                                                                                           |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.4$  | $\pm 1.2$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 2$ , where $V_{SNS\_CS} = 25 \text{ mV}$ .                                                                                                                                       |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.8$  | $\pm 2.3$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 4$ , where $V_{SNS\_CS} = 25 \text{ mV}$ .                                                                                                                                       |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.4$  | $\pm 1.3$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 12.5 \text{ mV}$ .                                                                                                                                         |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 0.8$  | $\pm 2.6$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 2$ , where $V_{SNS\_CS} = 12.5 \text{ mV}$ .                                                                                                                                     |

| Current measurement accuracy        | $A_{IIN}$  | -      | $\pm 1.5$  | $\pm 5.4$ | %    | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS\_CS} / 4$ , where $V_{SNS\_CS} = 12.5 \text{ mV}$ .                                                                                                                                     |

| Calculated input power accuracy     | $A_{PIN}$  | -      | $\pm 0.35$ | $\pm 0.7$ | %    | At $V_{DD\_RTNS}$ vs GND: $V_{DD\_RTNS} = 40 \text{ V}$ to $80 \text{ V}$ , $V_{TLM} = 88 \text{ V}$ .<br>And voltage between ISNS_REF & ISNS pins: $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 100 \text{ mV}$ or $50 \text{ mV}$ . |

| Calculated input power accuracy     | $A_{PIN}$  | -      | $\pm 0.41$ | $\pm 1.2$ | %    | At $V_{DD\_RTNS}$ vs GND: $V_{DD\_RTNS} = 40 \text{ V}$ to $80 \text{ V}$ , $V_{TLM} = 88 \text{ V}$ .<br>And voltage between ISNS_REF & ISNS pins: $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 25 \text{ mV}$                       |

(表格续下页.....)

3 产品基本特性

表 9 (续) 电气特性

除非另有说明,  $VDD\_RTN - GND = 48 V$ ,  $V_{ISNS\_REF} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$

| Parameter                                | Symbol        | Values |            |            | Unit | Note or condition                                                                                                                                                                             |

|------------------------------------------|---------------|--------|------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |               | Min.   | Typ.       | Max.       |      |                                                                                                                                                                                               |

| Calculated input power accuracy          | $A_{PIN}$     | -      | $\pm 0.65$ | $\pm 1.8$  | %    | At $VDD\_RTNS$ vs GND: $VDD\_RTNS = 40 V$ to $80 V$ , $V_{TLM} = 88 V$ .<br>And voltage between $ISNS\_REF$ & $ISNS$ pins: $V_{\Delta ISNS} = V_{SNS\_CS}$ , where $V_{SNS\_CS} = 12.5 mV$ .  |

| Calculated energy accuracy               | $A_{EIN}$     | -      | 1.4        | 2.1        | %    | At $VDD\_RTNS$ vs GND: $VDD\_RTNS = 40 V$ to $80 V$ , $V_{TLM} = 88 V$ . And voltage between $ISNS\_REF$ & $ISNS$ pins: $V_{\Delta ISNS} = VSNS\_CS$ , where $VSNS\_CS = 100 mV$ or $50 mV$ . |

| Calculated energy accuracy               | $A_{EIN}$     | -      | 1.4        | 2.7        | %    | At $VDD\_RTNS$ vs GND: $VDD\_RTNS = 40 V$ to $80 V$ , $V_{TLM} = 88 V$ . And voltage between $ISNS\_REF$ & $ISNS$ pins: $V_{\Delta ISNS} = VSNS\_CS$ , where $VSNS\_CS = 25 mV$               |

| Calculated energy accuracy               | $A_{EIN}$     | -      | 1.7        | 3.3        | %    | At $VDD\_RTNS$ vs GND: $VDD\_RTNS = 40 V$ to $80 V$ , $V_{TLM} = 88 V$ . And voltage between $ISNS\_REF$ & $ISNS$ pins: $V_{\Delta ISNS} = VSNS\_CS$ , where $VSNS\_CS = 12.5 mV$ .           |

| On-chip temperature monitored range      | $T_{ON-CHIP}$ | -40    | -          | 150        | °C   |                                                                                                                                                                                               |

| On-chip temperature measurement accuracy | $A_{T2}$      | -5     | -          | 5          | °C   |                                                                                                                                                                                               |

| Temperature measurements accuracy        | $A_{T1}$      | -      | $\pm 4.0$  | $\pm 12.5$ | °C   | Sourcing currents in $TSNS\_P$ pin.<br>Sense the voltage between $TSNS\_P$ & $TSNS\_N$ pins.<br>External transistor is: MMBT3904.                                                             |

| VREG           |           |     |     |     |   |                                                                                                                                                                             |

|----------------|-----------|-----|-----|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output voltage | $V_{REG}$ | 4.7 | 5.0 | 5.3 | V | $9 V \leq VDD\_RTN \leq 80 V$ .<br>$C_{VREG} = 1 \mu F$ .<br>Internal load + external load.<br>Package maximum power dissipation limit ( $P_{PAK}$ ) must not be violated.  |

| Output voltage | $V_{REG}$ | 4.5 | -   | -   | V | $6.5 V \leq VDD\_RTN \leq 9 V$ .<br>$C_{VREG} = 1 \mu F$ .<br>Internal load + external load.<br>Package maximum power dissipation limit ( $P_{PAK}$ ) must not be violated. |

(表格续下页.....)

3 产品基本特性

表 9 (续) 电气特性

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| Parameter                                  | Symbol    | Values |      |      | Unit | Note or condition |

|--------------------------------------------|-----------|--------|------|------|------|-------------------|

|                                            |           | Min.   | Typ. | Max. |      |                   |

| Current capability to supply external load | $I_{REG}$ | -      | -    | 10   | mA   |                   |

**PWRGD, GPOx, FAULT, WARN, SMBALERT#, CGDN, LED#**

|                         |                |     |   |     |               |                          |

|-------------------------|----------------|-----|---|-----|---------------|--------------------------|

| Output low voltage      | $V_{OL}$       | -   | - | 0.4 | V             | At 10 mA                 |

| Input Low Voltage       | $V_{IL}$       | -   | - | 0.8 | V             |                          |

| Input High Voltage      | $V_{IH}$       | 2.0 | - | -   | V             |                          |

| Leakage current         | $i_{LEAK}$     | -   | - | 5   | $\mu\text{A}$ | At 5.5 V, output is HiZ. |

| Current sink capability | $i_{GPO\_max}$ | -   | - | 10  | mA            |                          |

**SDAI, SDAO, SCL**

|                                 |            |     |            |     |               |          |

|---------------------------------|------------|-----|------------|-----|---------------|----------|

| Input high voltage              | $V_{IH}$   | 2.0 | -          | -   | V             |          |

| Input low voltage               | $V_{IL}$   | -   | -          | 0.8 | V             |          |

| Output low voltage              | $V_{OL}$   | -   | -          | 0.4 | V             | At 20 mA |

| Leakage current                 | $i_{LEAK}$ | -   | -          | 5.0 | $\mu\text{A}$ | At 5.5 V |

| Nominal bus voltage             | $V_{BUS}$  | 3.0 | 3.3 or 5.0 | 5.5 | V             |          |

| Capacitive load per bus segment | $C_L$      | -   | -          | 400 | pF            |          |

| Pin capacitance                 | $C_P$      | -   | 5          | 10  | pF            |          |

**ADDRx**

|                              |                 |   |     |   |               |                             |

|------------------------------|-----------------|---|-----|---|---------------|-----------------------------|

| Pin sense current            | $I_{ADDR}$      | - | 100 | - | $\mu\text{A}$ |                             |

| Programmability voltage step | $V_{ADDR-STEP}$ | - | 0.8 | - | V             | See Table 13 for more info. |

**MODEx**

|                          |            |   |     |   |               |  |

|--------------------------|------------|---|-----|---|---------------|--|

| MODEx pins sense current | $I_{MODE}$ | - | 100 | - | $\mu\text{A}$ |  |

|--------------------------|------------|---|-----|---|---------------|--|

(表格续下页.....)

### 3 产品基本特性

**表 9 (续) 电气特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b>             | <b>Symbol</b>          | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b>                    |

|------------------------------|------------------------|---------------|-------------|-------------|-------------|---------------------------------------------|

|                              |                        | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                                             |

| Programmability voltage step | $V_{\text{MODE-STEP}}$ | -             | 0.8         | -           | V           | See <a href="#">Table 12</a> for more info. |

#### IST

|                              |                       |   |                              |   |               |  |

|------------------------------|-----------------------|---|------------------------------|---|---------------|--|

| Pin sense current            | $I_{\text{IST}}$      | - | 100                          | - | $\mu\text{A}$ |  |

| Programmability voltage step | $V_{\text{IST-STEP}}$ | - | See <a href="#">Table 19</a> | - | V             |  |

#### 片上热关断

|                                                  |                       |     |                         |     |                  |                                                                                                                  |

|--------------------------------------------------|-----------------------|-----|-------------------------|-----|------------------|------------------------------------------------------------------------------------------------------------------|

| Protection trigger upper threshold               | $T_{\text{TS\_UTH}}$  | 130 | -                       | 145 | $^\circ\text{C}$ | Set by ONCHIP_TSD_FAULT_LIMIT[1:0] bits:<br>• 2'b00: 130°C<br>• 2'b01: 135°C<br>• 2'b10: 140°C<br>• 2'b11: 145°C |

| Protection trigger lower threshold               | $T_{\text{TS\_LTH}}$  | -   | $T_{\text{TS\_U}} - 10$ | -   | $^\circ\text{C}$ |                                                                                                                  |

| On-chip thermal shutdown warning upper limit     | $T_{\text{SDW\_UTH}}$ | -   | 125                     | -   | $^\circ\text{C}$ |                                                                                                                  |

| On-chip thermal shutdown warning lower threshold | $T_{\text{SDW\_LTH}}$ | -   | 115                     | -   | $^\circ\text{C}$ |                                                                                                                  |

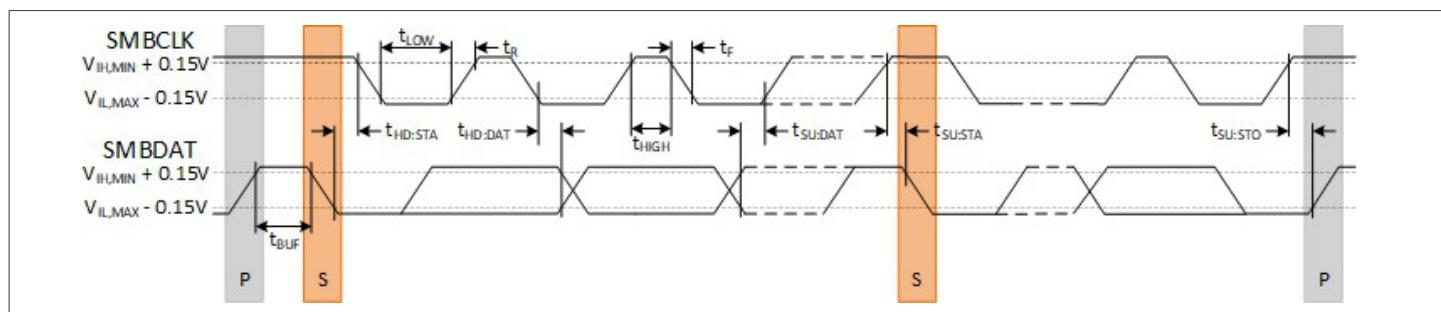

#### 3.7 时序特性

**表 10 时序特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

| <b>Parameter</b> | <b>Symbol</b> | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b> |

|------------------|---------------|---------------|-------------|-------------|-------------|--------------------------|

|                  |               | <b>Min.</b>   | <b>Typ.</b> | <b>Max.</b> |             |                          |

#### UV/EN

|                                 |                       |     |    |      |               |                                            |

|---------------------------------|-----------------------|-----|----|------|---------------|--------------------------------------------|

| UV/EN input fixed deglitch time | $t_{\text{UVEN\_DG}}$ | 6.5 | 10 | 13.5 | $\mu\text{s}$ | Input filter before processing the signal. |

|---------------------------------|-----------------------|-----|----|------|---------------|--------------------------------------------|

(表格续下页.....)

3 产品基本特性

**表10 (续) 时序特性**

除非另有说明,  $V_{DD\_RTN} - GND = 48 \text{ V}$ ,  $V_{ISNS\_REF} = 0 \text{ V}$ ,  $V_{\Delta ISNS} = (V_{ISNS\_REF} - V_{ISNS}) = 0 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

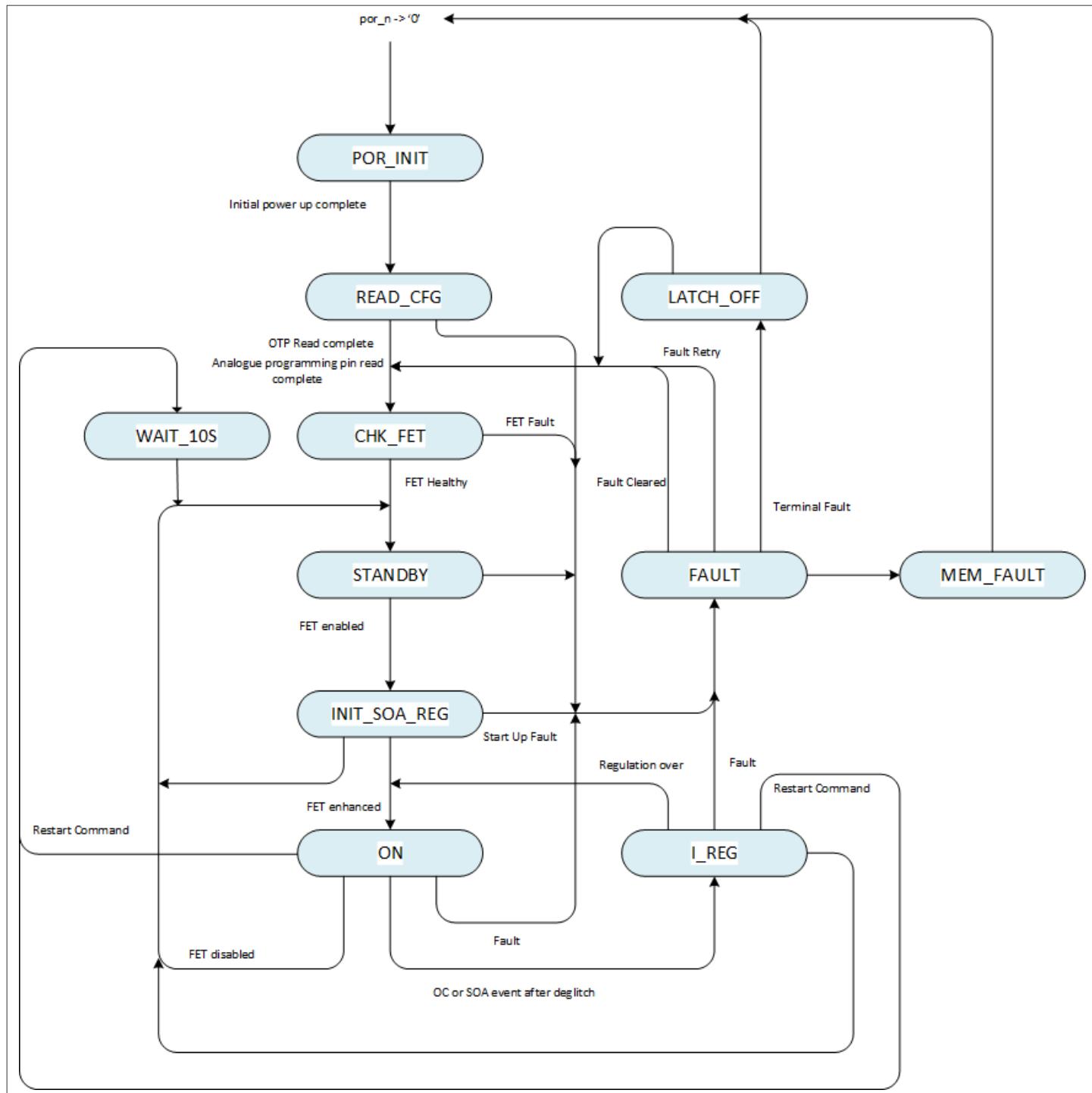

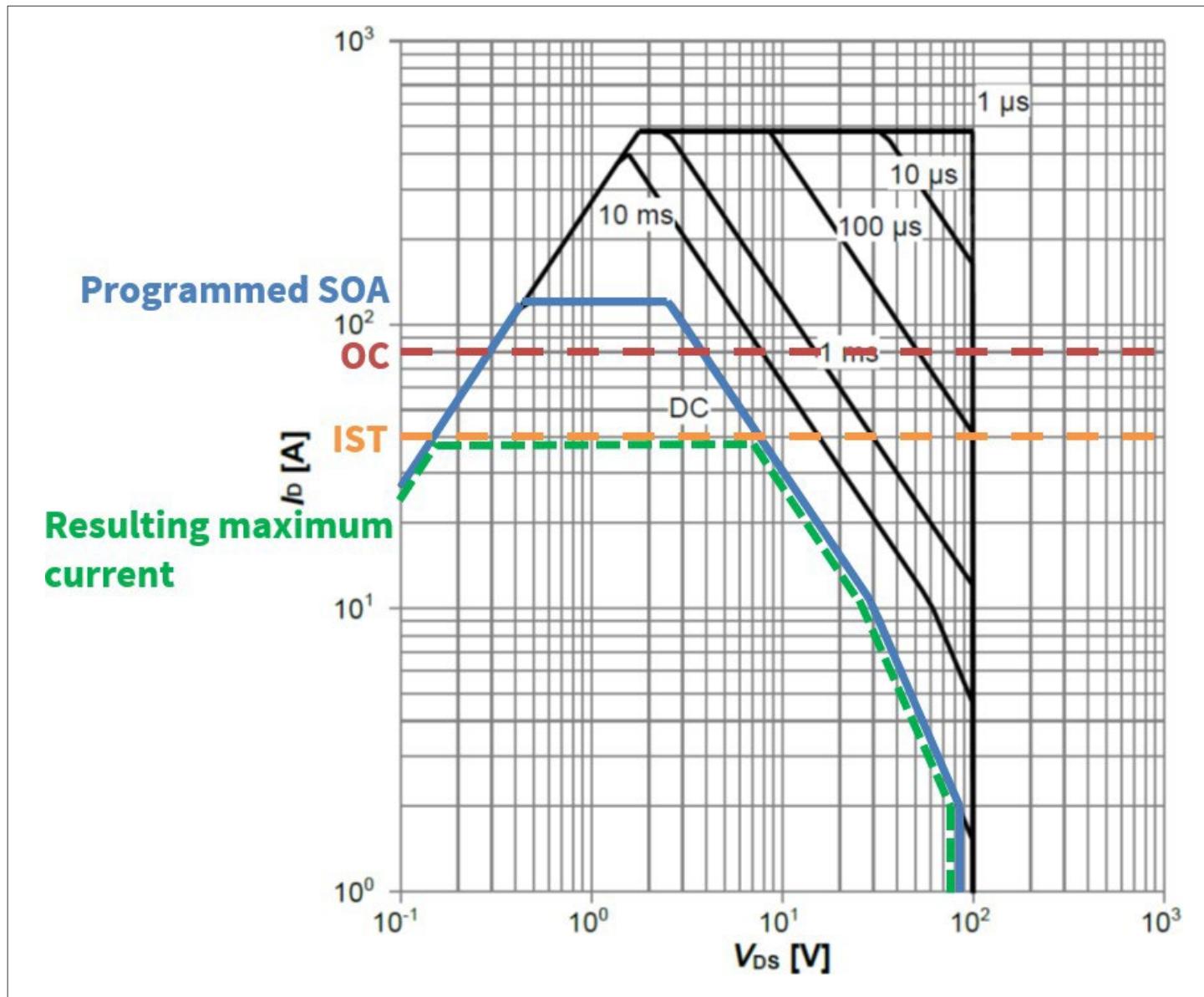

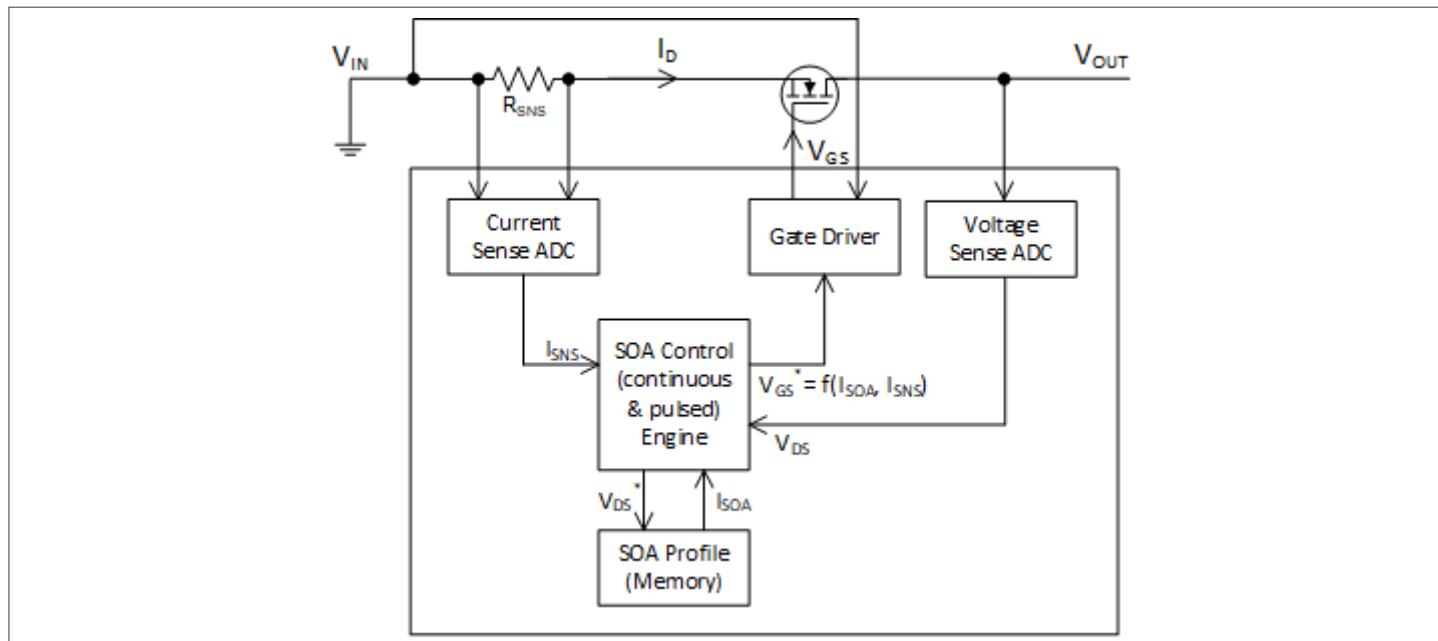

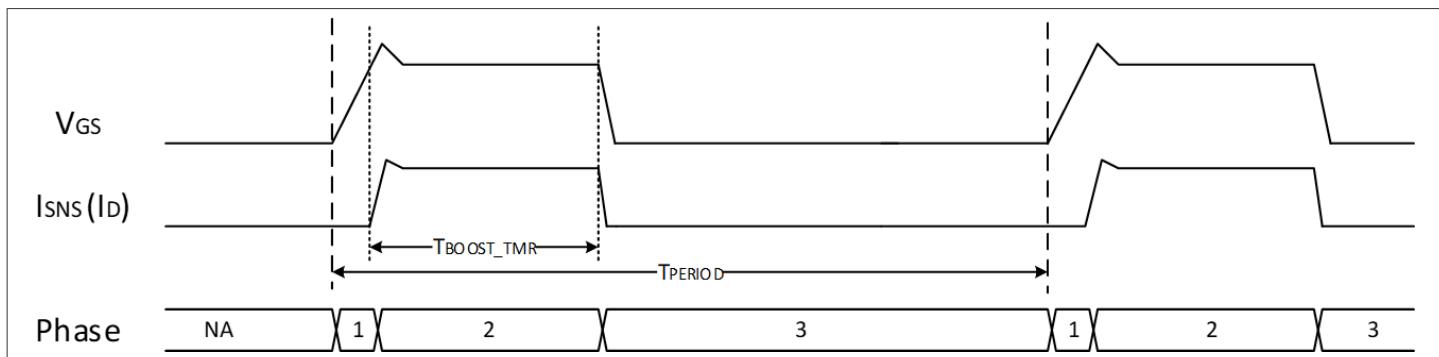

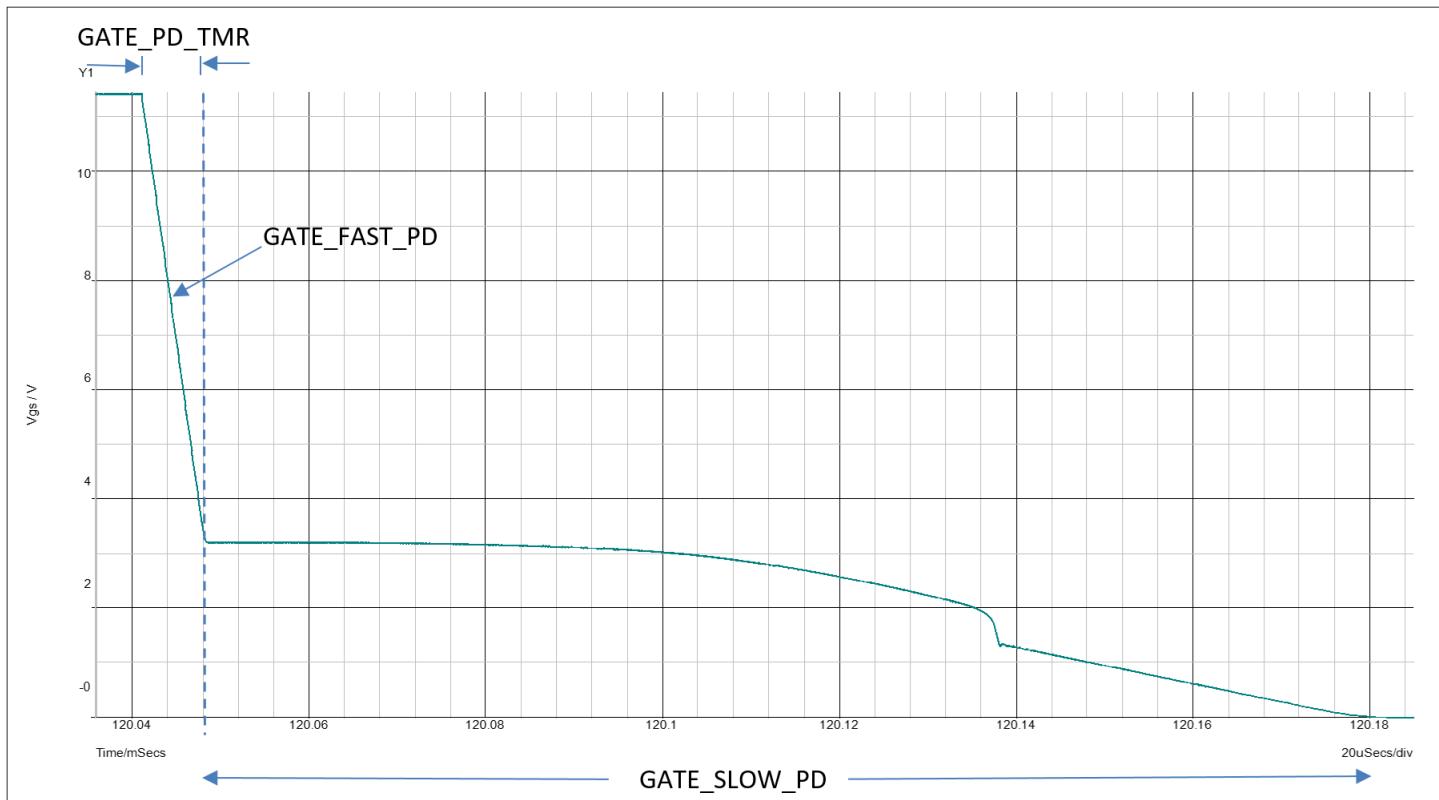

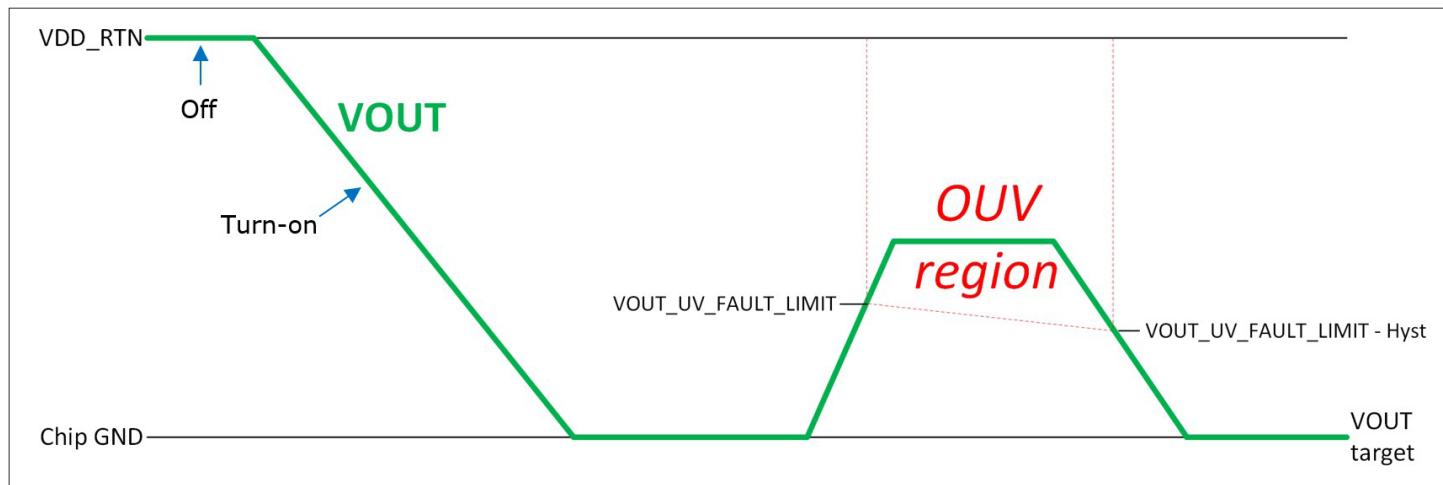

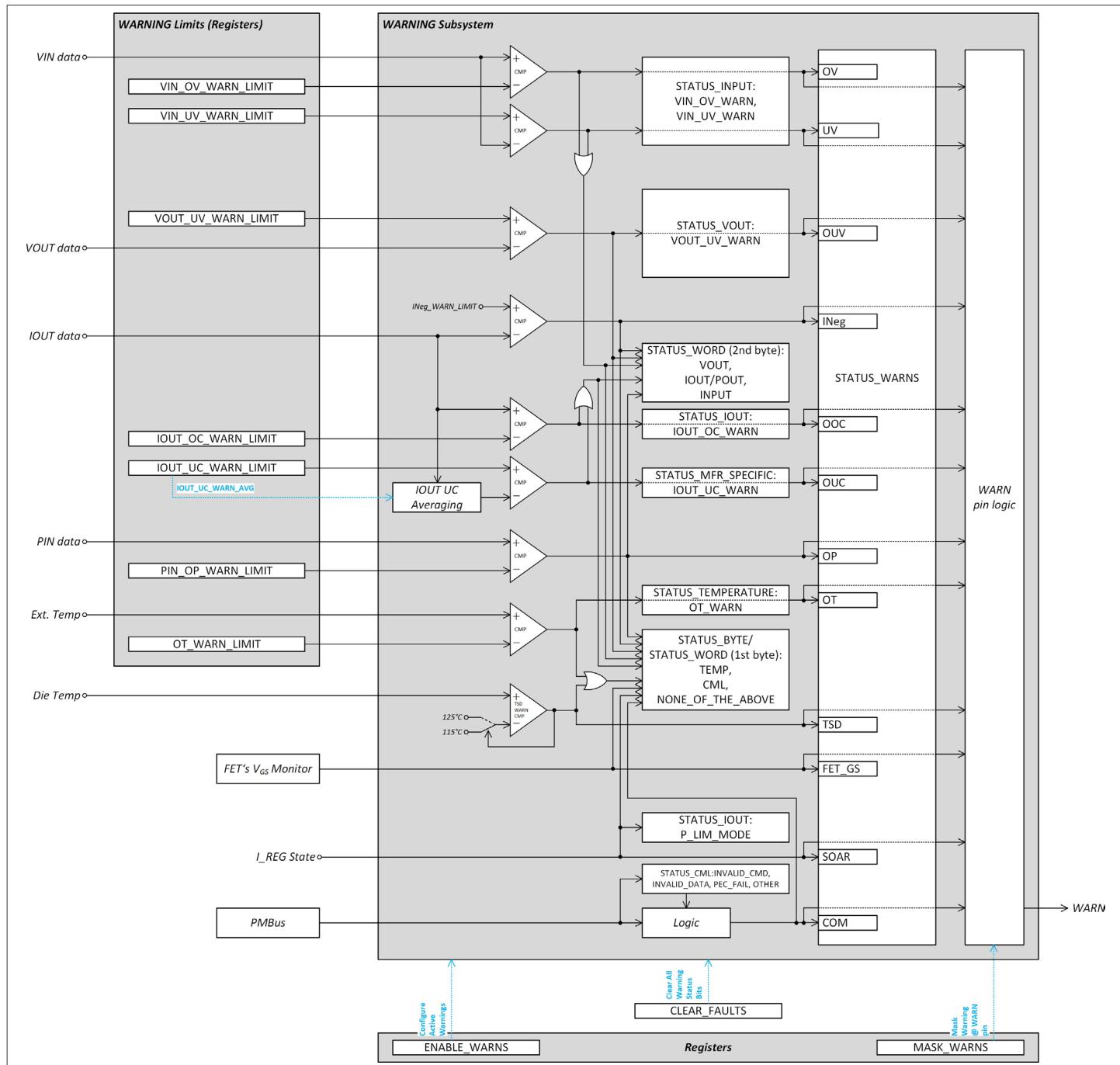

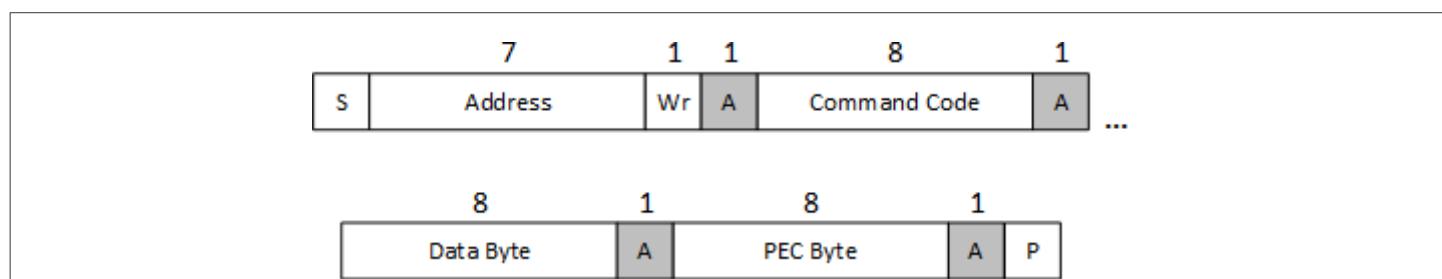

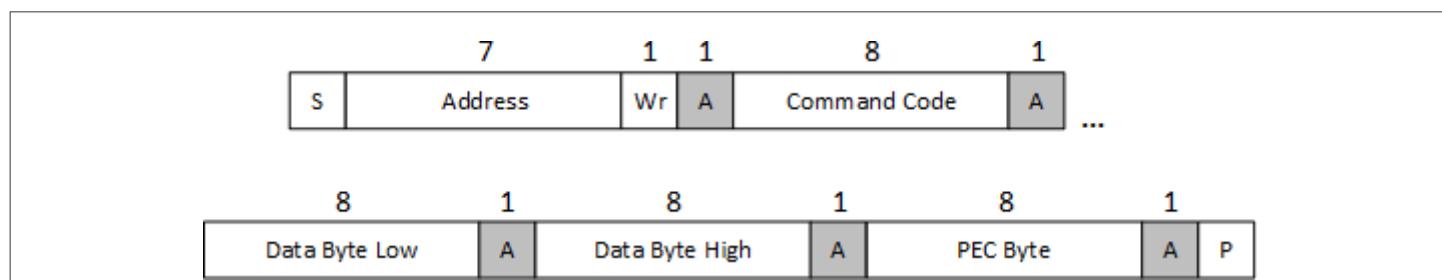

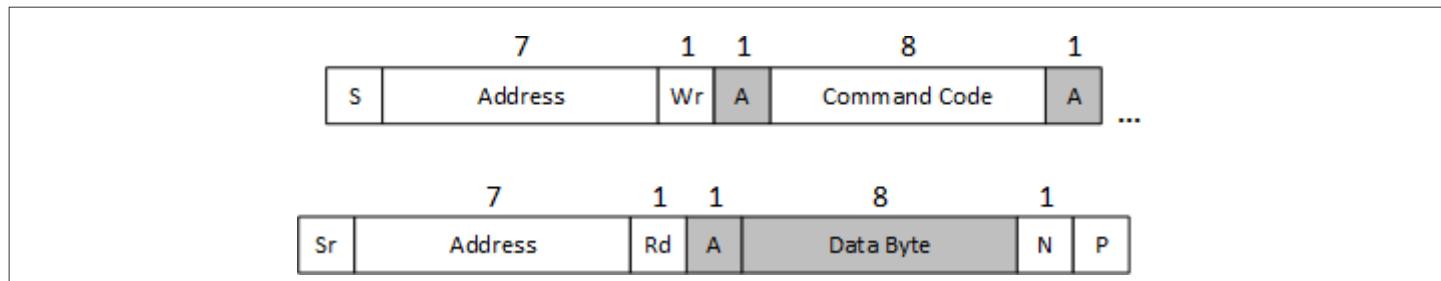

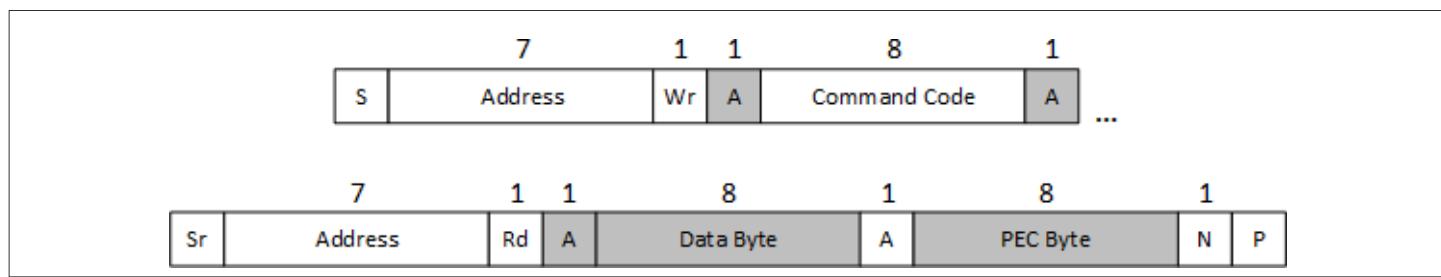

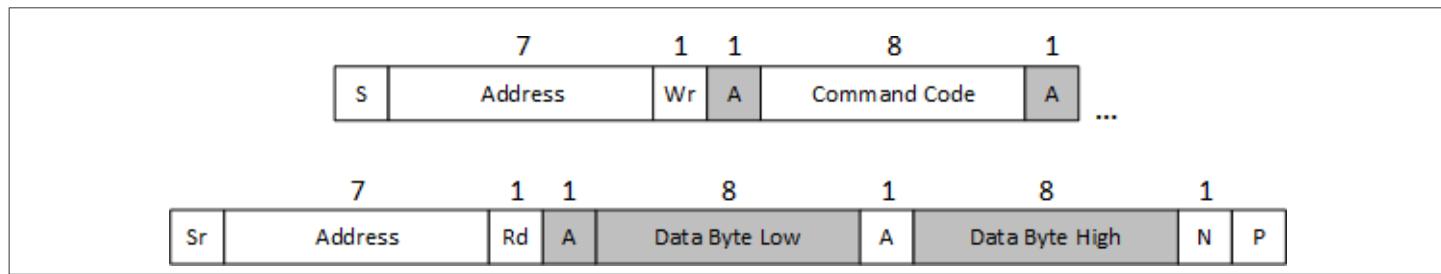

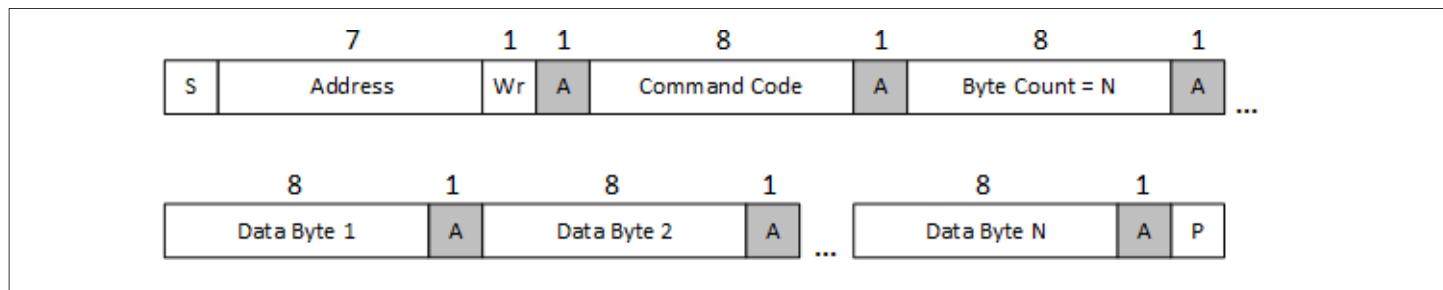

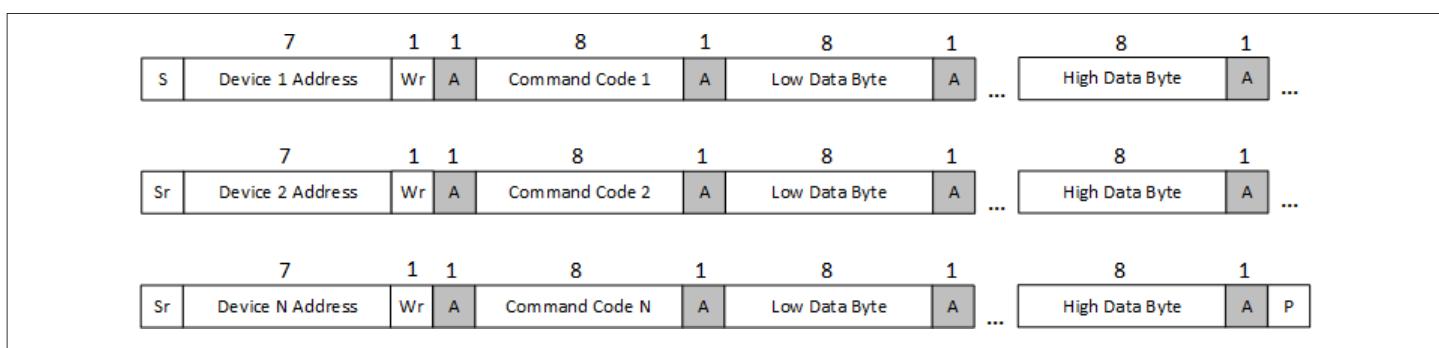

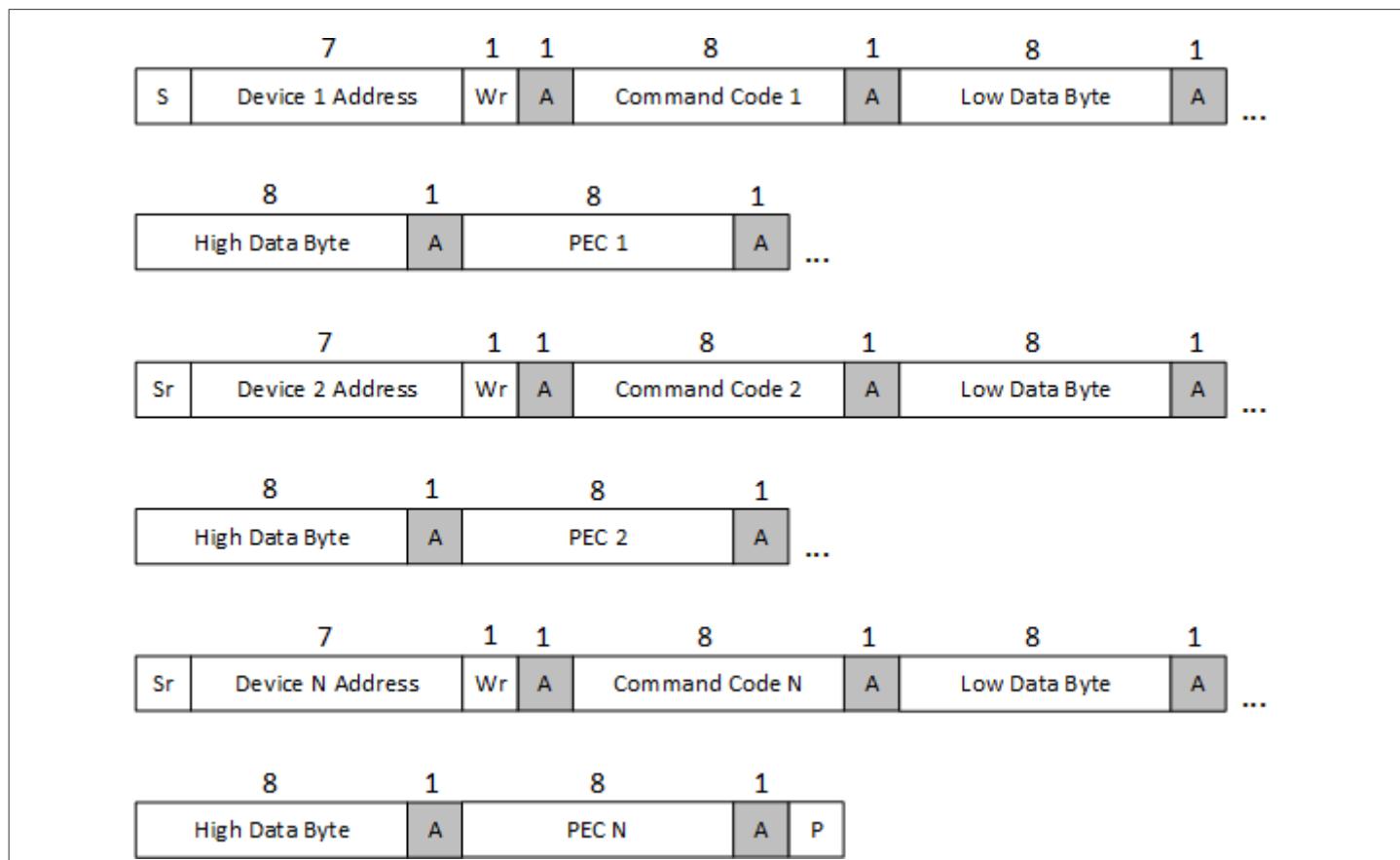

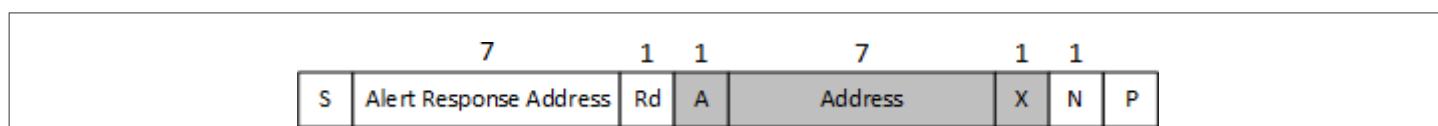

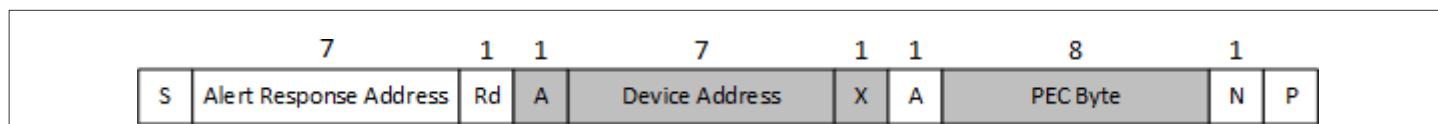

| <b>Parameter</b>                                        | <b>Symbol</b>  | <b>Values</b> |             |             | <b>Unit</b> | <b>Note or condition</b>                                                                                                                                                                                                                                                                                                                                                     |