## TLE4966V-1G

In Plane Sensing with Vertical Dual Hall Effect Latch for Automotive Applications

## **Data Sheet**

Revision 1.0, 2018-12-06

# Sense & Control

Edition 2018-12-06

Published by Infineon Technologies AG 81726 Munich, Germany © 2019 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Page or Item Subjects (major changes since previous revision) |  |

|---------------------------------------------------------------|--|

|                                                               |  |

| Revision 1.0, 2018-12-06                                      |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

|                                                               |  |

#### **Trademarks of Infineon Technologies AG**

AURIX $^{\text{TM}}$ , C166 $^{\text{TM}}$ , Canpak $^{\text{TM}}$ , CIPOS $^{\text{TM}}$ , CIPURSE $^{\text{TM}}$ , EconoPack $^{\text{TM}}$ , CoolMos $^{\text{TM}}$ , CoolSet $^{\text{TM}}$ , CORECONTROL $^{\text{TM}}$ , CROSSAVE $^{\text{TM}}$ , DAVE $^{\text{TM}}$ , EasyPIM $^{\text{TM}}$ , EconoBRIDGE $^{\text{TM}}$ , EconoDUAL $^{\text{TM}}$ , EconoPIM $^{\text{TM}}$ , EiceDRIVER $^{\text{TM}}$ , eupec $^{\text{TM}}$ , FCOS $^{\text{TM}}$ , HITFET $^{\text{TM}}$ , HybridPack $^{\text{TM}}$ , ISOFACE $^{\text{TM}}$ , IsoPack $^{\text{TM}}$ , MiPaQ $^{\text{TM}}$ , ModSTACK $^{\text{TM}}$ , my-d $^{\text{TM}}$ , NovalithIC $^{\text{TM}}$ , OptiMoS $^{\text{TM}}$ , ORIGA $^{\text{TM}}$ , PRIMARION $^{\text{TM}}$ , PrimePack $^{\text{TM}}$ , PrimeSTACK $^{\text{TM}}$ , PRO-SIL $^{\text{TM}}$ , PROFET $^{\text{TM}}$ , RASIC $^{\text{TM}}$ , ReverSave $^{\text{TM}}$ , Satric $^{\text{TM}}$ , Sieget $^{\text{TM}}$ , Sindrion $^{\text{TM}}$ , Sipmos $^{\text{TM}}$ , SmartLewis $^{\text{TM}}$ , Solid Flash $^{\text{TM}}$ , Tempfet $^{\text{TM}}$ , thinQ! $^{\text{TM}}$ , Trenchstop $^{\text{TM}}$ , TriCore $^{\text{TM}}$ .

#### **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

#### **Table of Contents**

### **Table of Contents**

|                                             | Table of Contents                                                                                                                                                                                           |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | List of Figures                                                                                                                                                                                             |

|                                             | List of Tables                                                                                                                                                                                              |

| <b>1</b><br>1.1<br>1.2                      | Product Description         7           Target Applications         7           Features         7                                                                                                          |

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Functional Description       8         General       8         Pin Configuration (top view)       10         Block Diagram       11         Start-up Behavior       12         Application Circuit       13 |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5        | Specification14Absolute Maximum Ratings14Operating Range15Electrical Characteristics16Magnetic Characteristics17Electro Magnetic Compatibility18                                                            |

| 4                                           | Timing Diagrams for the Speed and Direction Output                                                                                                                                                          |

| 5                                           | Package Information                                                                                                                                                                                         |

#### **List of Figures**

## **List of Figures**

| igure 1-1  | Image of TLE4966V in the PG-TSOP6-6-9 package                                                                           | 7  |

|------------|-------------------------------------------------------------------------------------------------------------------------|----|

| igure 1-2  | Target Application (top and side view): Sensing Direction parallel to target wheel                                      | 7  |

| igure 2-1  | Target Application: Side view and top view for In-Plane Sensing                                                         | 8  |

| igure 2-2  | Magnetic field signal with the corresponding speed & direction output including the definition of th direction signal 9 | е  |

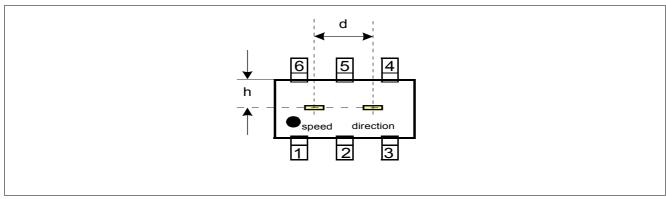

| igure 2-3  | PG-TSOP6-6-9 Pin Configuration and sensitive area (d = 1.25mm) (see table 2-2)                                          | 10 |

| Figure 2-4 | Functional Block Diagram of the TLE4966V-1G                                                                             |    |

| igure 2-5  | Start-up behavior of the at different magnetic start conditions                                                         |    |

| igure 2-6  | Basic Application Circuit                                                                                               |    |

| igure 2-7  | Enhanced Application Circuit for very high ESD robustness on system level                                               |    |

| igure 3-1  | EMC test circuit                                                                                                        |    |

| igure 4-1  | Timing Diagram TLE4966V                                                                                                 |    |

| igure 4-2  | TLE4966V - Output Voltage Signal over applied magnetic Field                                                            |    |

| igure 4-3  | TLE4966V - Definition of the direction signal                                                                           | 20 |

| igure 5-1  | Image of TLE4966V in the PG-TSOP6-6-9 package                                                                           | 21 |

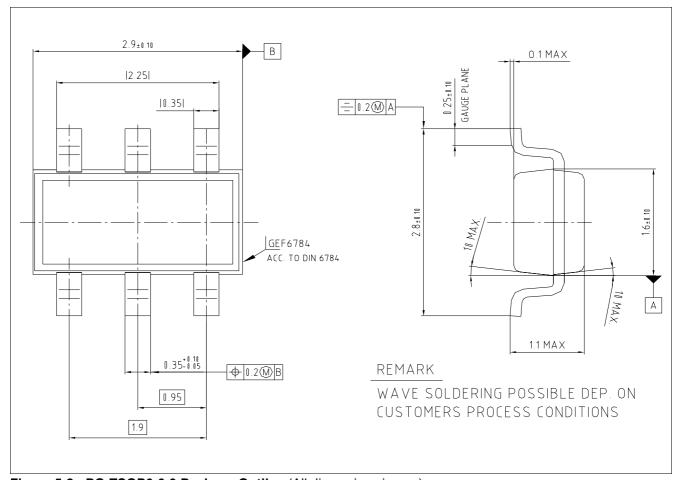

| igure 5-2  | PG-TSOP6-6-9 Package Outline (All dimensions in mm)                                                                     | 21 |

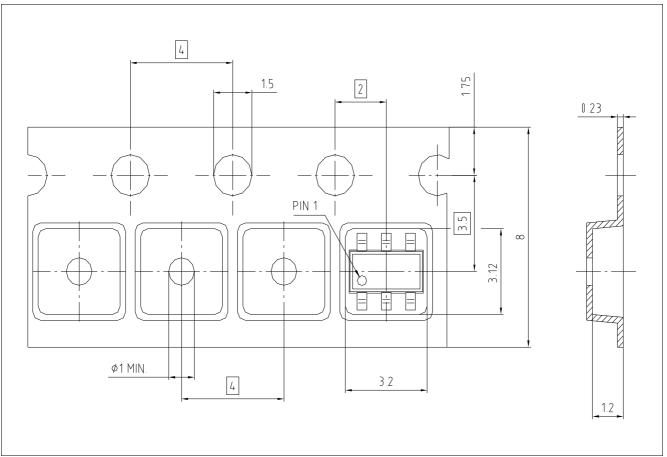

| igure 5-3  | PG-TSOP6-6-9 Packing (All dimensions in mm)                                                                             | 22 |

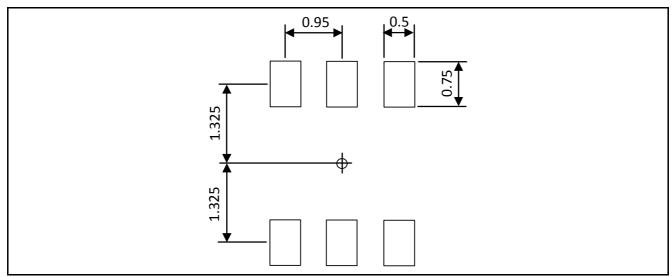

| igure 5-4  | Footprint of PG-TSOP6-6-9                                                                                               | 22 |

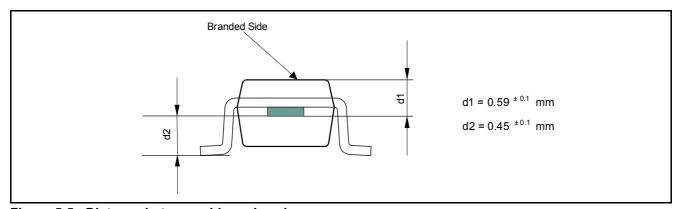

| igure 5-5  | Distance between chip and package                                                                                       | 23 |

| igure 5-6  | Marking of TLE4966V                                                                                                     |    |

5

#### **List of Tables**

### **List of Tables**

| Table 1-1 | Ordering Information               | . 7 |

|-----------|------------------------------------|-----|

| Table 2-1 | Output Pin Q1 Direction Signals    | . 9 |

| Table 2-2 | Pin Description PG-TSOP6-6-9       | 10  |

| Table 3-1 | Absolute Maximum Rating Parameters | 14  |

| Table 3-2 | ESD Protection (TA = 25°C)         | 14  |

| Table 3-3 | Operating Conditions Parameters    | 15  |

| Table 3-4 | General Electrical Characteristics | 16  |

| Table 3-5 | Magnetic Characteristics           | 17  |

| Table 3-6 | Magnetic Compatibility             | 18  |

| Table 3-7 | Electro Magnetic Compatibility     | 18  |

| Table 4-1 | Output Pin Q1 Direction Signals    | 20  |

**Product Description**

#### 1 Product Description

#### 1.1 Target Applications

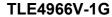

The TLE4966V-1G is specifically designed to detect the rotation direction and the rotation speed of a pole wheel. The sensing direction is **in-plane** to the sensor surface. Even at high distances to the hall elements the direction will be detected correctly.

Figure 1-1 Image of TLE4966V in the PG-TSOP6-6-9 package

Figure 1-2 Target Application (top and side view): Sensing Direction parallel to target wheel

#### 1.2 Features

- · In-Plane Sensing for parallel mounting of magnetic encoder and sensor

- Low current consumption

- · Direction Detection

- · Speed output for index counting applications

- 3.5V to 32V operating supply voltage

- Operating from unregulated power supply

- Reverse polarity protection (-18V)

- Over voltage capability up to 42V without external resistor

- Output over current and over temperature protection

- High robustness to mechanical stress by Active Error Compensation

- · Low drift of magnetic thresholds

- Low jitter (typ. 0.3us)

- SMD package PG-TSOP6-6-9

Table 1-1 Ordering Information

| Product Name | Product Type             | Ordering Code | Package      |

|--------------|--------------------------|---------------|--------------|

| TLE4966V-1G  | Dual Vertical Hall Latch | SP002983184   | PG-TSOP6-6-9 |

#### 2 Functional Description

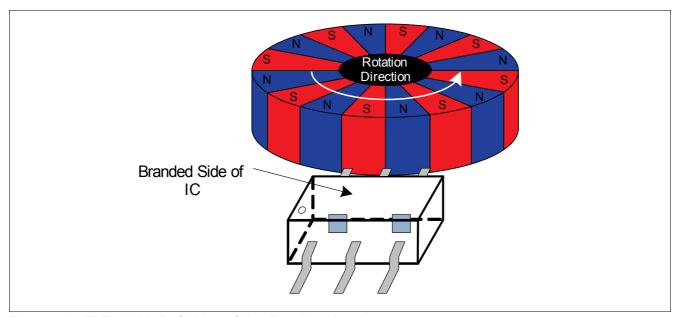

The TLE4966V-1G is specifically designed to detect the direction and rotational speed of a pole wheel as shown in **Figure 1-2**.

#### 2.1 General

The new Infineon Vertical Double Hall Switch TLE4966V-1G has integrated the functionality of detecting speed and direction of a rotating magnet, commonly known as pole wheel.

Note: Completely new is the in plane field direction which will be detected with the TLE4966V-1G shown in Figure 2-1 which enables completely new application layouts.

Figure 2-1 Target Application: Side view and top view for In-Plane Sensing

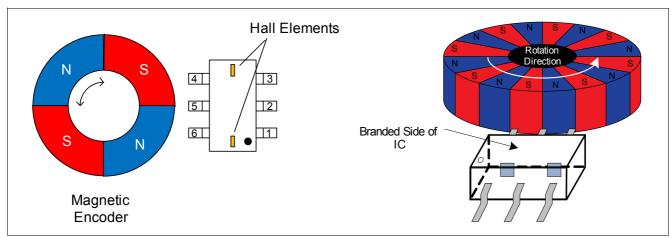

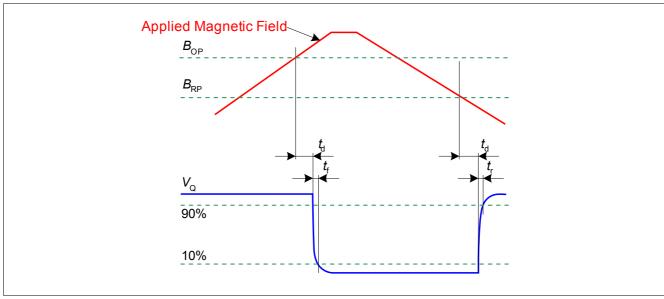

The sensor provides a speed output at Q2 with the status (high or low) corresponding to the magnetic field value. For positive magnetic fields (south pole) exceeding the threshold  $B_{OP}$  the output is low, whereas for negative magnetic fields (north pole) lower than  $B_{RP}$  the output switches to high. The output Q1 can be either high or low depending on the direction of rotation of the pole wheel. This direction information is calculated internally. (see Table 2-2)

Designed in a new technology, this device offers high voltage capabilities with very small current consumption. The product can be operated from unregulated power supplies which offers our customers unique freedom of design for their system.

This product is AEC Q100 certified and enables our customers to build systems for the highest automotive quality requirements. The product has a PG-TSOP6-6-9 package, which is RoHs compliant and fulfills the usual automotive environmental guidelines.

Application Examples are:

- · Window lifter (index counting)

- Power closing (index counting)

- All applications with the need of speed and direction detection.

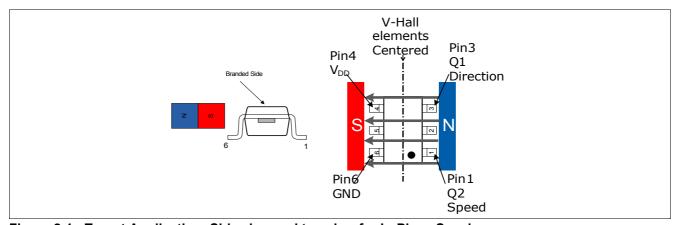

Figure 2-2 and Table 2-1 show the mapping of a pole wheel with the two corresponding output signals of the device.

Figure 2-2 Magnetic field signal with the corresponding speed & direction output including the definition of the direction signal

Table 2-1 Output Pin Q1 Direction Signals

| Rotation direction | State of direction output Q1 |  |  |  |  |

|--------------------|------------------------------|--|--|--|--|

| Counterclockwise   | Low                          |  |  |  |  |

| Clockwise          | High                         |  |  |  |  |

### 2.2 Pin Configuration (top view)

Figure 2-3 PG-TSOP6-6-9 Pin Configuration and sensitive area (d = 1.25mm) (see table 2-2)

Table 2-2 Pin Description PG-TSOP6-6-9

| Pin No. | Symbol   | Function                      |

|---------|----------|-------------------------------|

| 1       | Q2       | Speed                         |

| 2       | GND      | Recommended connection to GND |

| 3       | Q1       | Direction                     |

| 4       | $V_{DD}$ | Supply voltage                |

| 5       | GND      | Recommended connection to GND |

| 6       | GND      | Ground                        |

The sensitive elements are placed in an optimized distance (d) to guarantee the direction detection. To compensate package stress the sensitive elements are placed in the middle of the package (h).

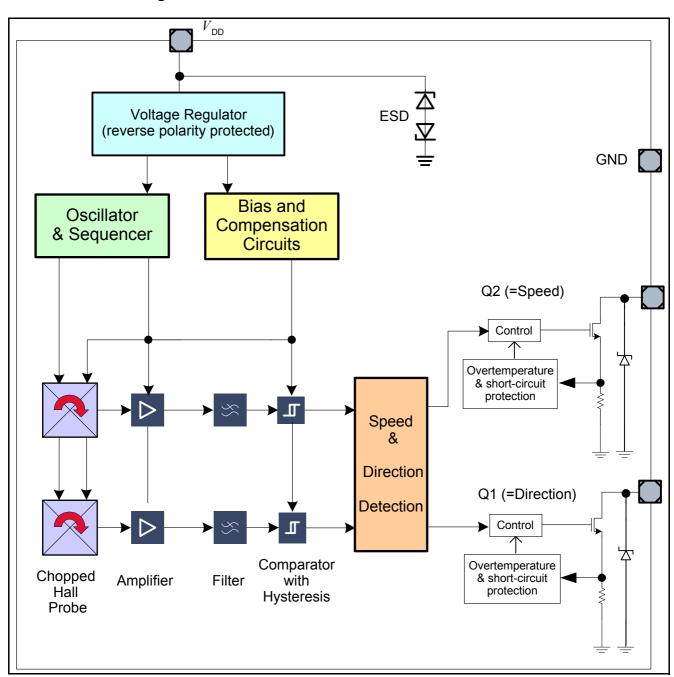

#### 2.3 Block Diagram

Figure 2-4 Functional Block Diagram of the TLE4966V-1G

The chopped Dual Hall IC switch comprises a Hall probe, bias generator, compensation circuits, oscillator and output transistor.

The bias generator provides currents for the Hall probe and the active circuits. Compensation circuits stabilize the temperature behavior and reduce influence of technology variations.

The active error compensations (chopping technique) rejects offsets in the signal path. Therefore the influence of mechanical stress to the Hall elements caused by molding and soldering processes and other thermal stress in the package is minimized. The chopped measurement principle together with the threshold generator and the comparator ensures highly accurate and temperature stable magnetic thresholds. The output transistor has an integrated over current and over temperature protection to prevent the device from destruction.

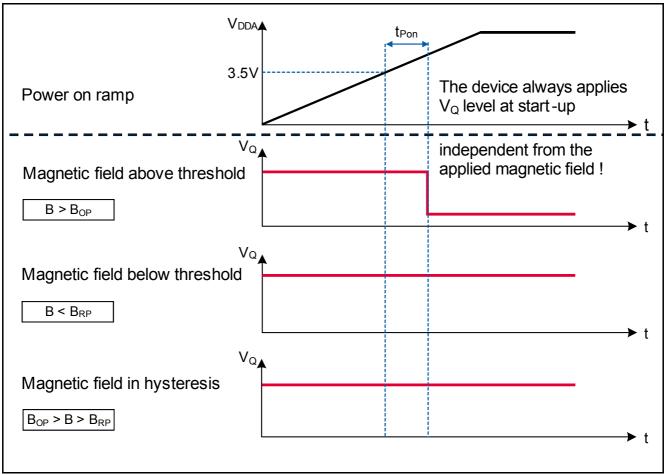

#### 2.4 Start-up Behavior

The magnetic threshold exhibit a hysteresis Bhys = Bop - Brp. In case of a power-on with a magnetic field B within hysteresis ( $B_{rp} < B < B_{op}$ ) the output of the sensor is set to the pull up voltage level " $V_q$ " per default. After the first crossing of  $B_{op}$  or  $B_{rp}$  of the magnetic field the internal decision logic is set to the corresponding magnetic input value.

$V_{\text{DDA}}$  is the internal supply voltage which is following the external supply voltage  $V_{\text{DD}}$ .

This means for B >  $B_{op}$  the output is switching for B >  $B_{rp}$  and  $B_{op}$  > B > Brp the output stays at  $V_{Q}$

Figure 2-5 Start-up behavior of the at different magnetic start conditions

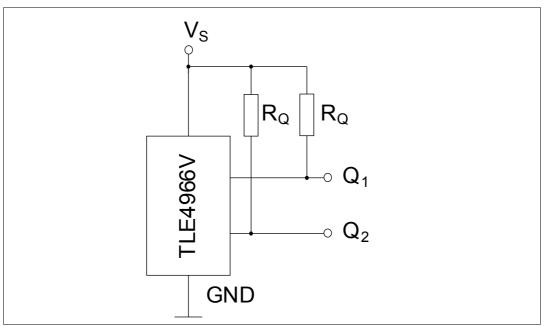

#### 2.5 Application Circuit

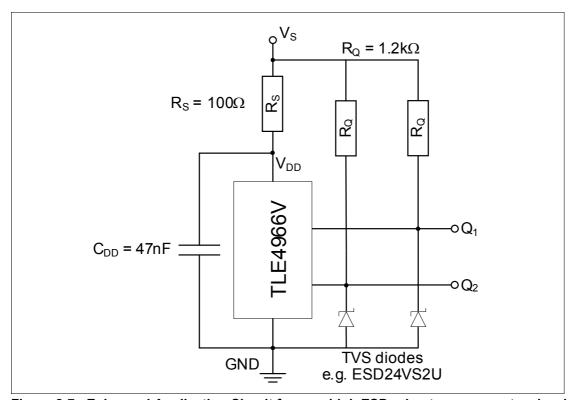

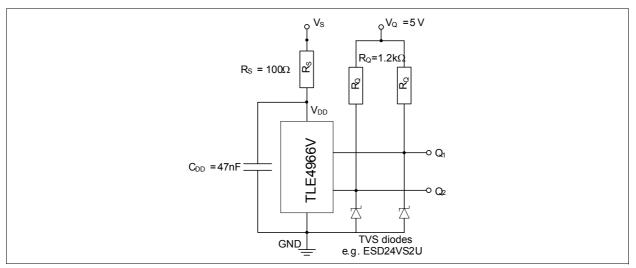

The **Figure 2-6** below shows the basic option of an application circuit. The Resistor Rq has to be in a dimension to match the applied Vs to keep Iq limited to the operating range of maximal 10mA.

For example: Vs = 12V, Iq = 10mA --> R = 12V / 0.01A =  $1.2k\Omega$ .

In **Figure 2-7** the additional ESD Diodes are optional to achieve an increased ESD robustness at the Q pins. Additional with the (optional) 47nF between Vdd and GND a high system level robustness is achieved.

Figure 2-6 Basic Application Circuit

Figure 2-7 Enhanced Application Circuit for very high ESD robustness on system level

### 3 Specification

#### 3.1 Absolute Maximum Ratings

Table 3-1 Absolute Maximum Rating Parameters

| Parameter                           | Symbol            | Lim  | Limit Values      |     | Note / Test Condition                                                           |  |

|-------------------------------------|-------------------|------|-------------------|-----|---------------------------------------------------------------------------------|--|

|                                     |                   | Min. | Max.              |     |                                                                                 |  |

| Supply voltage                      | V <sub>DD</sub>   | -18  | 32<br>42          | V   | 10h, no external resistor required                                              |  |

| Output voltage                      | V <sub>Q</sub>    | -0.5 | 32                | V   |                                                                                 |  |

| Reverse output current              | IQ                | -35  |                   | mA  |                                                                                 |  |

| Junction temperature                | T <sub>J</sub>    | -40  | 155<br>165<br>175 | °C  | for 2000h (not additive)<br>for 1000h (not additive)<br>for 168h (not additive) |  |

| Storage temperature                 | T <sub>S</sub>    | -40  | 150               | °C  |                                                                                 |  |

| Thermal resistance Junction ambient | R <sub>thJA</sub> |      | 200               | K/W | for PG-TSOP6-6-9                                                                |  |

| Thermal resistance<br>Junction lead | R <sub>thJL</sub> |      | 100               | K/W | for PG-TSOP6-6-9                                                                |  |

Attention: Stresses above the max. values listed here may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

Calculation of the dissipated power  $P_{DIS}$  and junction temperature  $T_J$  of the chip (TSPOP6 example):

e.g for:  $V_{DD}$  = 12 V,  $I_{S}$  = 10mA,  $V_{QSAT}$  = 0.5 V,  $I_{Q}$  = 10mA

Power dissipation:  $P_{DIS} = 12 \text{ V x } 10\text{mA} + 2 \text{ x } (0.5 \text{ V x } 10\text{mA}) = 120\text{mW} + 10\text{mW} = 130\text{mW}$

Temperature  $\Delta T = R_{thJA} \times P_{DIS} = 200 \text{K/W} \times 130 \text{mW} = 26 \text{K}$

For  $T_A = 100^{\circ}C$ :  $T_J = T_A + \Delta T = 100^{\circ}C + 26K = 126^{\circ}C$

Table 3-2 ESD Protection<sup>1)</sup> (TA =  $25^{\circ}$ C)

| Parameter                       | Symbol           | Limit Values |      | Unit | Note / Test Condition |

|---------------------------------|------------------|--------------|------|------|-----------------------|

|                                 |                  | Min.         | Max. |      |                       |

| ESD voltage (HBM) <sup>2)</sup> | V <sub>ESD</sub> | -2           | +2   | kV   | R = 1.5kΩ, C = 100pF  |

| System level test               |                  | -6           | +6   | kV   | Figure 2-7 3)         |

- 1) Characterization of ESD is carried out on a sample basis.

- 2) Human Body Model (HBM) tests according to EIA/JESD22-A114

- 3) Gun test ( $2k\Omega/330pF$  or  $330\Omega/150pF$ ) according to ISO 10605-2008

#### 3.2 Operating Range

Attention: The following operating conditions must not be exceeded in order to ensure correct operation of the TLE4966V-1G. All parameters specified in the following sections refer to these operating conditions unless otherwise mentioned.

**Table 3-3 Operating Conditions Parameters**

| Parameter                                     | Symbol           |      | Value | s                | Unit | Note / Test Condition |

|-----------------------------------------------|------------------|------|-------|------------------|------|-----------------------|

|                                               |                  | Min. | Тур.  | Max.             |      |                       |

| Supply voltage                                | $V_{DD}$         | 3.5  |       | 32 <sup>1)</sup> | V    |                       |

| Output voltage                                | $V_Q$            | -0.3 |       | 32               | V    |                       |

| Junction temperature                          | T <sub>i</sub>   | -40  |       | 150              | °C   |                       |

| Output current                                | IQ               | 0    |       | 10               | mA   |                       |

| Magnetic signal input frequency <sup>2)</sup> | f <sub>mag</sub> | 0    |       | 5                | kHz  |                       |

<sup>1)</sup> Latch-up test with factor 1.5 is not covered. Please see max ratings also.

<sup>2)</sup> For operation at the maximum switching frequency the magnetic input signal must be 1.4 times higher than for static fields. This is due to the -3dB corner frequency of the internal low-pass filter in the signal path.

#### 3.3 Electrical Characteristics

**Table 3-4 General Electrical Characteristics**

| Parameter                                                              | Symbol              | Values |      |      | Unit              | Note / Test Condition                                                                |  |

|------------------------------------------------------------------------|---------------------|--------|------|------|-------------------|--------------------------------------------------------------------------------------|--|

|                                                                        |                     | Min.   | Тур. | Max. |                   |                                                                                      |  |

| Supply current                                                         | Is                  | 3.9    | 5.8  | 7.5  | mA                |                                                                                      |  |

| Reverse current                                                        | I <sub>SR</sub>     | -      | 0.05 | 1    | mA                | for V <sub>DD</sub> = -18V                                                           |  |

| Output saturation voltage                                              | V <sub>QSAT</sub>   | -      | 0.2  | 0.5  | V                 | I <sub>Q</sub> = 10mA                                                                |  |

| Output leakage current                                                 | I <sub>QLEAK</sub>  | -      | -    | 5.0  | μΑ                | T=150°C, 12V                                                                         |  |

| Output current limitation                                              | I <sub>QLIMIT</sub> | 20     | 30   | 40   | mA                | internally limited & thermal shutdown                                                |  |

| Output fall time <sup>1)</sup>                                         | t <sub>f</sub>      | 0.1    | 0.2  | 1    | μs                | 1.2kΩ <sup>2)</sup> / 50pF, see <b>Figure 4-1</b>                                    |  |

| Output rise time <sup>1)</sup>                                         | t <sub>r</sub>      | 0.1    | 0.2  | 1    | μs                | 1.2kΩ <sup>2)</sup> / 50pF, see <b>Figure 4-1</b>                                    |  |

| Output jitter <sup>3)1)</sup>                                          | $t_{QJ}$            |        | 0.3  | 1    | μs                | For square wave signal with 1kHz                                                     |  |

| Effective noise value of the magnetic switching points <sup>4)1)</sup> | B <sub>Neff</sub>   |        | 45   |      | μT <sub>RMS</sub> |                                                                                      |  |

| Delay time <sup>5)1)</sup>                                             | t <sub>d</sub>      | 8      | 20   | 30   | μs                | B <sub>peak</sub> =10mT, Ramp=500mT/s;<br>see <b>Figure 4-1</b>                      |  |

| Signal Count Delay <sup>1)</sup>                                       | t <sub>dc</sub>     | 50     | 400  | 1000 | ns                | 1.2kΩ/50pF @ Vq=12V, Direction before Speed Signal, 50% to 50%                       |  |

| Power-on time <sup>6)1)</sup>                                          | t <sub>PON</sub>    | 48     | 84   | 120  | μs                | $V_{DD} = 3.5 \text{ V}, B \le B_{RP} - 0.5 \text{ mT or} $<br>B \ge B_{OP} + 0.5 mT |  |

| Chopper frequency <sup>1)</sup>                                        | f <sub>OSC</sub>    |        | 1300 |      | kHz               |                                                                                      |  |

<sup>1)</sup> Not subject to production test, verified by design/characterization

- 5) Systematic delay between magnetic threshold reached and output switching.

- 6) Time from applying  $V_{DD}$  = 3.0 V to the sensor until the output is valid.

<sup>2)</sup> Current limitation has to be taken into consideration for Vs > 12V in order not to exceed 10mA

<sup>3)</sup> Output jitter is the  $1\sigma$  value of the output switching distribution.

<sup>4)</sup> The magnetic noise is normal distributed and can be assumed as nearly independent to frequency without sampling noise or digital noise effects. The typical value represents a the rms-value and corresponds therefore to a 1  $\sigma$  probability of normal distribution. Consequently a 3  $\sigma$  value corresponds to 0.3% probability of appearance.

### 3.4 Magnetic Characteristics

**Table 3-5 Magnetic Characteristics**

| Parameter                                 | Symbol             | T (°C) | Values |       |      | Unit  | Note / Test Condition                            |

|-------------------------------------------|--------------------|--------|--------|-------|------|-------|--------------------------------------------------|

|                                           |                    |        | Min.   | Тур.  | Max. |       |                                                  |

| Operating point                           | B <sub>OP</sub>    | -40    | 1.1    | 2.8   | 4.5  | mT    |                                                  |

|                                           |                    | 25     | 0.9    | 2.5   | 4.1  |       |                                                  |

|                                           |                    | 150    | 0.4    | 1.9   | 3.3  |       |                                                  |

| Release point                             | B <sub>RP</sub>    | -40    | -4.5   | -2.8  | -1.1 | mT    |                                                  |

|                                           |                    | 25     | -4.1   | -2.5  | -0.9 |       |                                                  |

|                                           |                    | 150    | -3.3   | -1.9  | -0.4 |       |                                                  |

| Hysteresis                                | B <sub>Hys</sub>   | -40    | 3.6    | 5.3   | 7.4  | mT    |                                                  |

|                                           |                    | 25     | 3.4    | 5.0   | 6.8  |       |                                                  |

|                                           |                    | 150    | 2.5    | 3.7   | 5.2  |       |                                                  |

| Magnetic Matching                         | B <sub>Match</sub> |        | -1.0   |       | +1.0 | mT    | for (Bop1 - Bop2) and (Brp1 - Brp2);<br>-40125°C |

|                                           |                    |        | -1.5   |       | +1.5 |       | -40150°C                                         |

| Magnetic Offset                           | B <sub>Off</sub>   |        | -1.0   |       | +1.0 | mT    | (Bop + Brp) / 2; -40125°C                        |

|                                           |                    |        | -1.5   |       | +1.5 | mt    | (Bop + Brp) / 2; -40150°C                        |

| Temperature<br>Compensation <sup>1)</sup> | TC                 |        |        | -1700 |      | ppm/K | ferrite magnet                                   |

<sup>1)</sup> Not subject to production test, verified by design/characterization

The initial status of Q1 and Q2 after power on is Vq high (=OFF)!

#### 3.5 Electro Magnetic Compatibility

Characterization of Electro Magnetic Compatibility is carried out on a sample basis from one qualification lot. Not all specification parameters have been monitored during EMC exposure.

Figure 3-1 EMC test circuit

Ref: ISO 7637-2 (Version 2004), test circuit Figure 3-1(with external resistor, Rs =  $100\Omega$ )

Table 3-6 Magnetic Compatibility

| Parameter                  | Symbol           | Level / Type                                    | Status |

|----------------------------|------------------|-------------------------------------------------|--------|

| Testpulse 1                | V <sub>EMC</sub> | -90V                                            | С      |

| Testpulse 2a <sup>1)</sup> |                  | 60V/110V                                        | A/C    |

| Testpulse 2b               |                  | 10V                                             | С      |

| Testpulse 3a               |                  | -150V                                           | Α      |

| Testpulse 3b               |                  | 100V                                            | Α      |

| Testpulse 4 <sup>2)</sup>  |                  | -7V / -5.5V                                     | Α      |

| Testpulse 5b <sup>3)</sup> |                  | $U_S = 86.5 \text{ V} / U_S^* = 28.5 \text{ V}$ | Α      |

- 1) ISO 7637-2 (2004) describes internal resistance =  $2\Omega$  (former  $10\Omega$ ).

- 2) According to 7637-2 for test pulse 4 the test voltage shall be 12 V +/- 0.2 V.

- 3) A central load dump protection of 42 V is used.  $U_S^* = 42 \text{ V-}13.5 \text{V}$ .

Ref: ISO 7637-2 (Version 2004), test circuit Figure 3-1 (without external resistor,  $R_S = 0\Omega$ )

**Table 3-7 Electro Magnetic Compatibility**

| Parameter                  | Symbol    | Level / Type                                    | Status |   |

|----------------------------|-----------|-------------------------------------------------|--------|---|

| Testpulse 1                | $V_{EMC}$ | -50V                                            | С      | - |

| Testpulse 2a1)             |           | 45V                                             | Α      |   |

| Testpulse 2b               |           | 10V                                             | С      |   |

| Testpulse 3a               |           | -150V                                           | A      |   |

| Testpulse 3b               |           | 100V                                            | Α      |   |

| Testpulse 4 <sup>2)</sup>  |           | -7V / 5.5 V                                     | A      |   |

| Testpulse 5b <sup>3)</sup> |           | $U_S = 86.5 \text{ V} / U_S^* = 28.5 \text{ V}$ | Α      |   |

- 1) ISO 7637-2 (2004) describes internal resistance =  $2\Omega$  (former  $10\Omega$ ).

- 2) According to 7637-2 for test pulse 4 the test voltage shall be 12 V +/- 0.2 V.

- 3) A central load dump protection of 42 V is used.  $U_s^* = 42 \text{ V-}13.5 \text{V}$ .

**Timing Diagrams for the Speed and Direction Output**

## 4 Timing Diagrams for the Speed and Direction Output

Figure 4-1 Timing Diagram TLE4966V

Figure 4-2 TLE4966V - Output Voltage Signal over applied magnetic Field

#### **Timing Diagrams for the Speed and Direction Output**

Figure 4-3 TLE4966V - Definition of the direction signal

Table 4-1 Output Pin Q1 Direction Signals

| Rotation direction | State of direction output Q1 |  |

|--------------------|------------------------------|--|

| Counterclockwise   | Low                          |  |

| Clockwise          | High                         |  |

**Package Information**

## 5 Package Information

Figure 5-1 Image of TLE4966V in the PG-TSOP6-6-9 package

Figure 5-2 PG-TSOP6-6-9 Package Outline (All dimensions in mm)

#### **Package Information**

Figure 5-3 PG-TSOP6-6-9 Packing (All dimensions in mm)

Figure 5-4 Footprint of PG-TSOP6-6-9

#### **Package Information**

Figure 5-5 Distance between chip and package

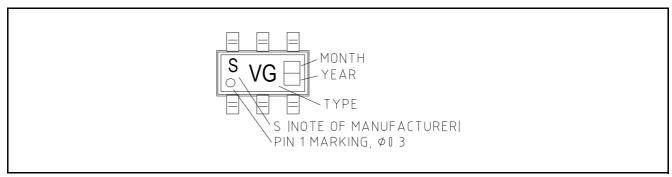

Figure 5-6 Marking of TLE4966V

www.infineon.com