## 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

### **Quality Requirement Category: Industrial**

#### **Features**

- Single 4.5 V to 17 V application or Wide Input Voltage Range from 3.0 V to 17 V with external Vcc

- Output Voltage Range: 0.25 V to 5.12 V based on Output Feedback resistor divider network

- Enhanced Fast COT Engine Stable with Ceramic output Capacitors without External Compensation

- Optional Forced Continuous Conduction Mode and Diode Emulation for Enhanced Light Load Efficiency

- Pin programmable Output Voltage, Switching Frequency/mode selection with 16 unique selectable settings

- Programmable Switching Frequency from 400 kHz to 2 MHz in steps of 200 kHz, excluding 1600 kHz

- Monotonic Start-Up with Selectable Soft-Start Time through PMBus commands & Pre-Bias Start-Up

- Thermally Compensated Internal Over Current Protection with Eight Selectable Settings

- Enable input with Voltage Monitoring Capability & Power Good Output

- PMBus system interface for reporting of Temperature, Voltage, Current, & Power telemetry

- Multiple Time Programming (MTP) with up to 14 writes for the USER section

- Digitally programmable load-line without any external components

- Operating temp: -40 °C < Tj < 125 °C</li>

- Small Size: 5 mm x 6 mm PQFN

- Lead-free, Halogen-free and RoHS2 Compliant with Exemption 7a

### **Applications**

- Server Applications

- Storage Applications

- Telecom & Datacom Applications

- Distributed Point of Load Power Architectures

## **Description**

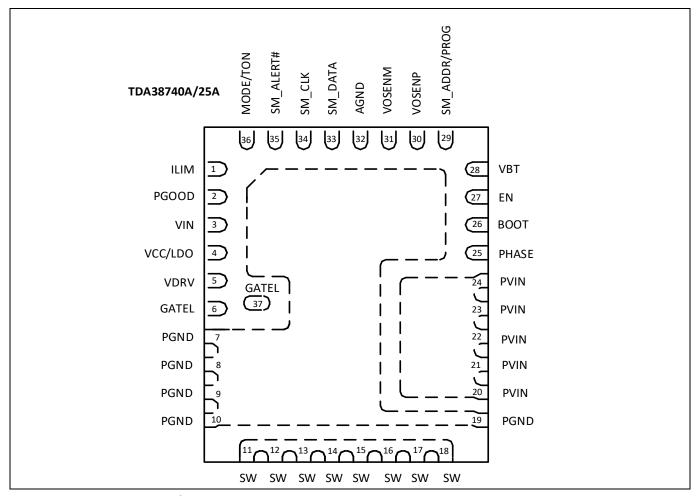

The TDA38740A/25A is an easy-to-use, fully integrated and highly efficient dc-dc regulator. The onboard PWM controller and OptiMOS™ FETs with integrated bootstrap diode make TDA38740A/25A a small footprint solution, providing high-efficiency power delivery. Furthermore, it uses a fast Constant On-Time (COT) control scheme, which simplifies the design efforts and achieves fast transient response.

TDA38740A/25A is a versatile regulator, operating with wide input and output voltage ranges, offering programmable switching frequency from 400 kHz to 2 MHz in steps of 200KHz excluding 1600KHz, and providing eight unique selectable current limits. It features a programmable dc loadline, which provides an additional tool to manage the transient response.

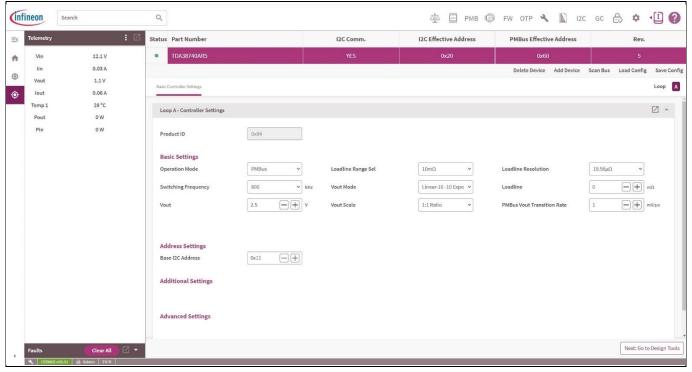

It also features important protection functions, such as pre-bias start-up, thermally compensated current limit, over voltage and under voltage protection, and thermal shutdown to give required system level security in the event of fault conditions. The device configuration can be easily defined using Infineon's XDP Designer GUI and is

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

stored in the on-chip memory. The controller requires the fewest possible external components and results in a simplified Bill of Materials (BOM).

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

# **Table of contents**

| 1            | Ordering Information                                                             | 5  |

|--------------|----------------------------------------------------------------------------------|----|

| 2            | Functional Block Diagram                                                         | 7  |

| 3            | Typical Application Diagram                                                      | 8  |

| 4            | Pin Descriptions                                                                 | 9  |

| 5            | Absolute Maximum Ratings                                                         | 11 |

| 6            | Thermal Characteristics                                                          |    |

| 7            | Electrical Specifications                                                        | 14 |

| 7.1          | Electrical Characteristics                                                       |    |

| 8            | Pin Strap Resistors Application Information                                      | 21 |

| 9            | Typical Efficiency and Power Loss Curves                                         | 26 |

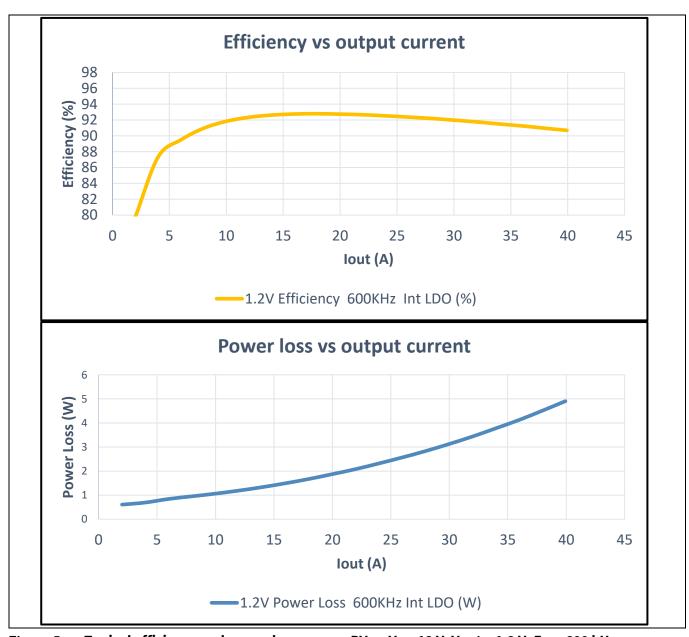

| 9.1          | PV <sub>in</sub> = V <sub>in</sub> = 12 V, Vout = 1.2V, F <sub>sw</sub> = 600kHz |    |

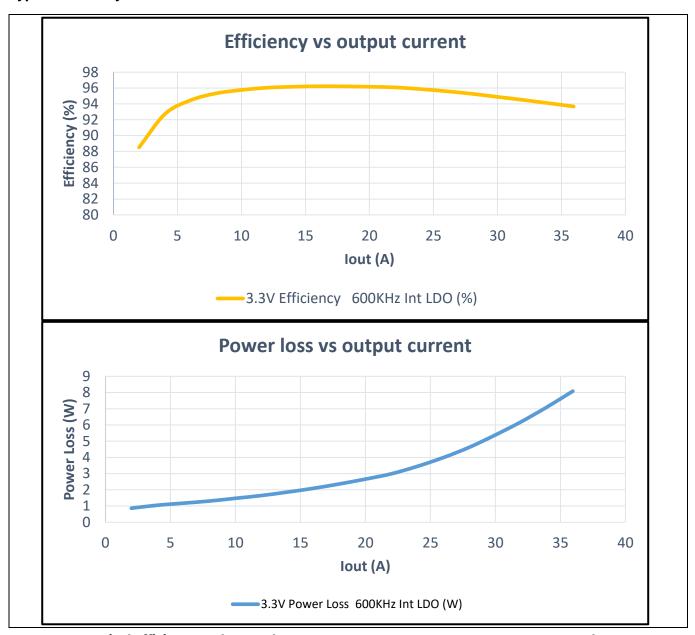

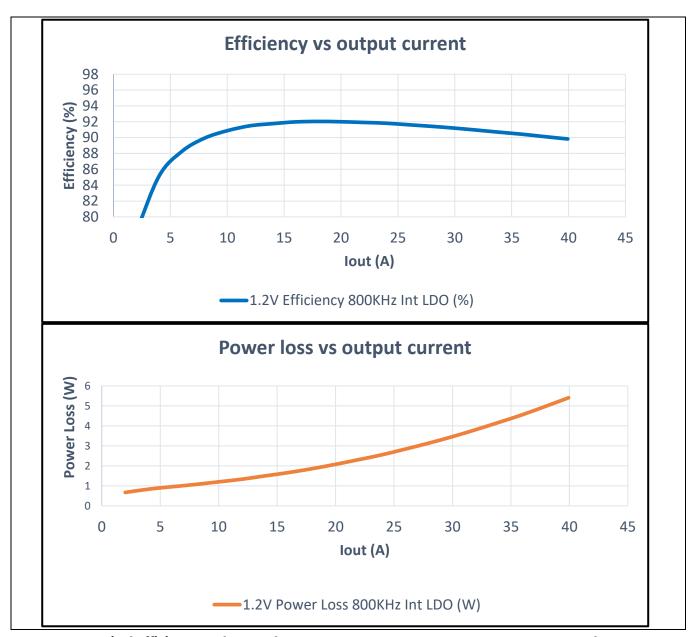

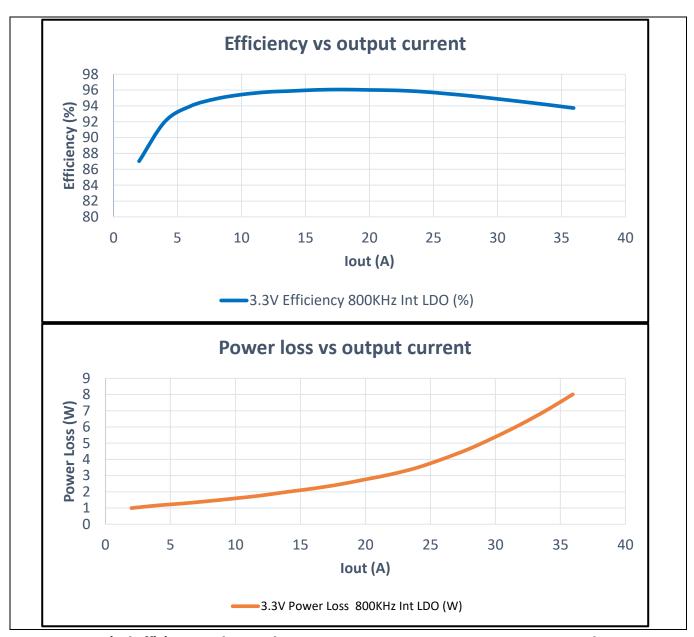

| 9.2          | $PV_{in} = V_{in} = 12 \text{ V}, F_{sw} = 800 \text{ kHz}$                      | 27 |

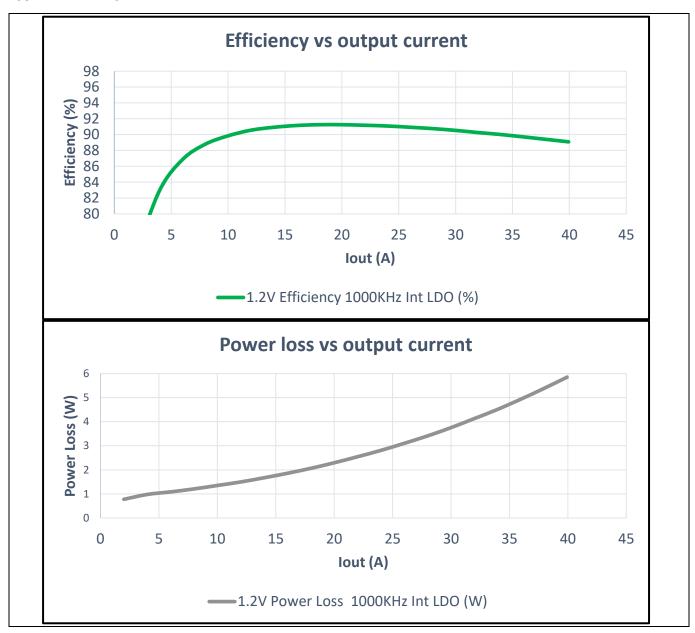

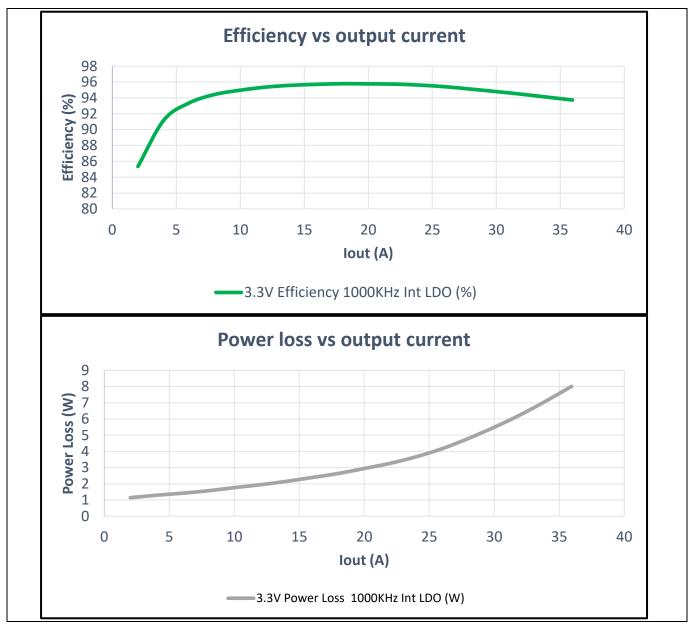

| 9.3          | $PV_{in} = V_{in} = 12 \text{ V}, F_{sw} = 1000 \text{ kHz}$                     | 29 |

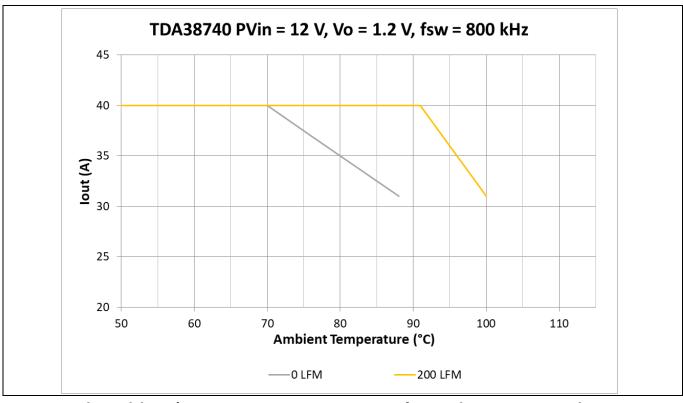

| 10           | Thermal De-rating curves                                                         | 32 |

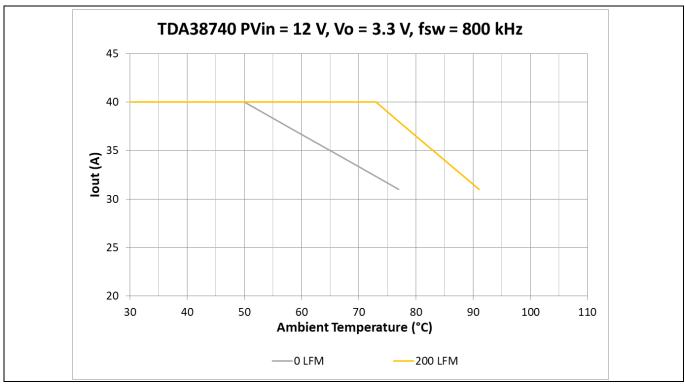

| 11           | RDS(on) of MOSFET Over Temperature                                               | 33 |

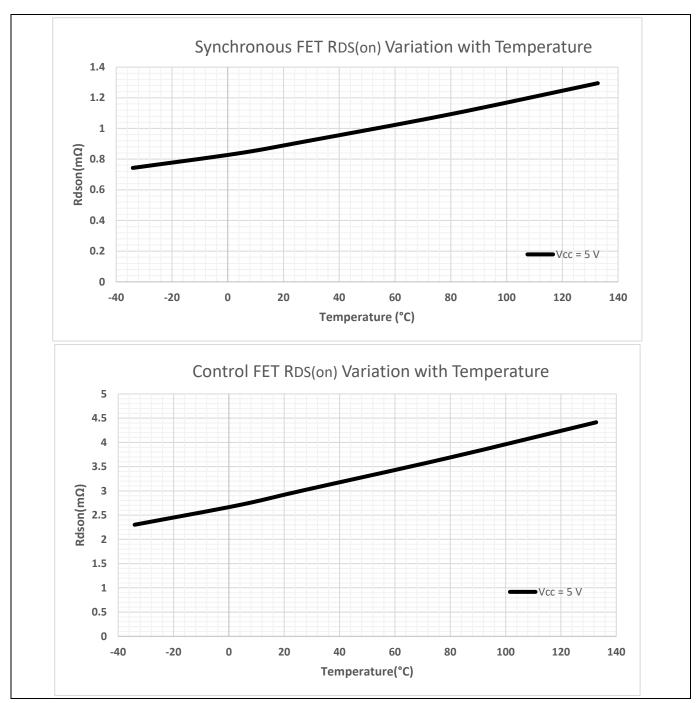

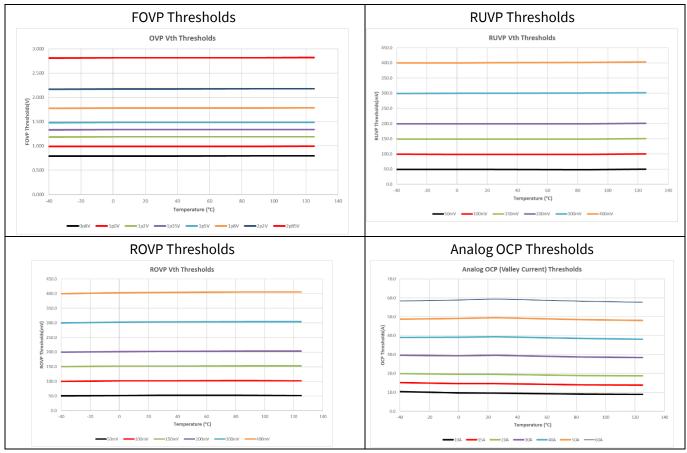

| 12           | Typical operating characteristics (-40 °C $\leq$ T <sub>j</sub> $\leq$ +125 °C)  | 34 |

| 13           | General Description                                                              | 36 |

| 13.1         | PMBUS Operating Mode                                                             |    |

| 13.2         | Multiple Time Programming Memory (MTP)                                           |    |

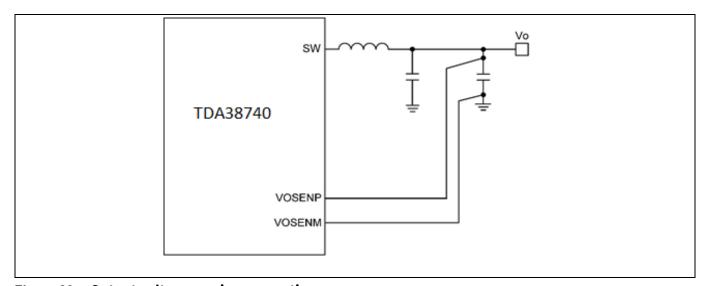

| 13.3         | Voltage Sense                                                                    |    |

| 13.4<br>13.5 | I2C & PMBus Interface                                                            |    |

| 13.5<br>13.6 | Infineon XDP Designer GUI<br>Programming                                         |    |

| 13.7         | Real-time Monitoring                                                             |    |

| 14           | Theory of Operation                                                              |    |

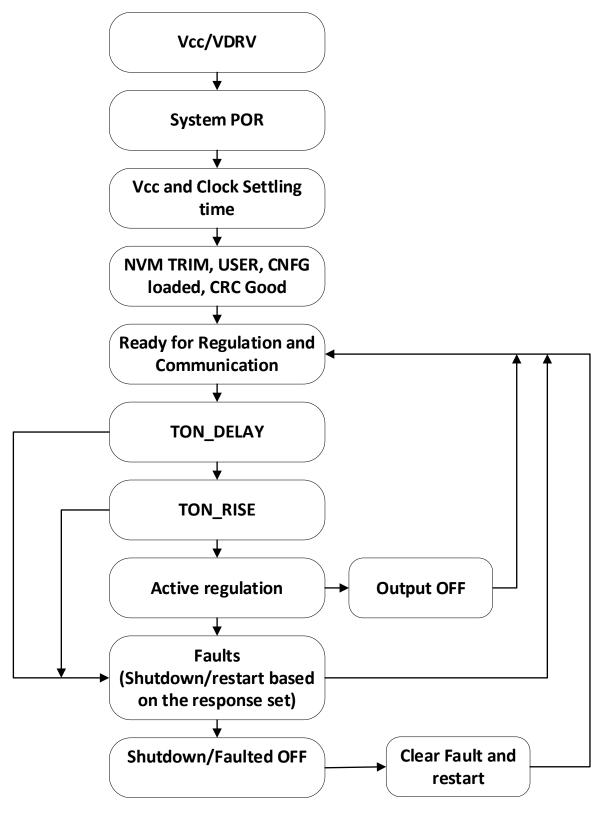

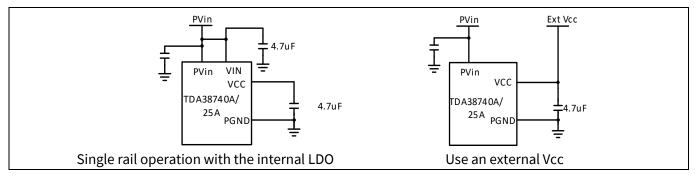

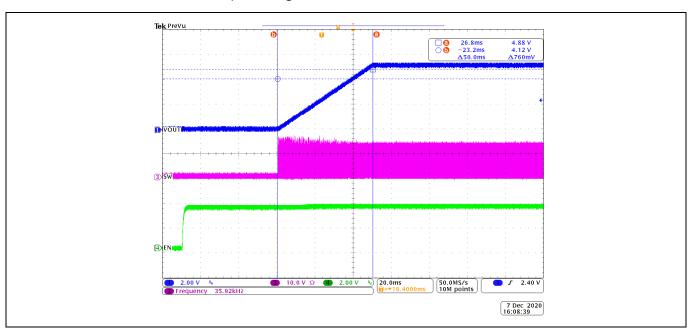

| 14.1         | Start up Configuration                                                           |    |

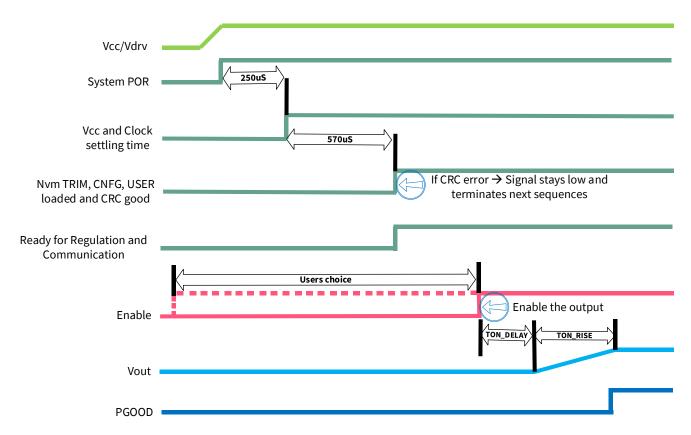

| 14.1.1       | Power On Reset and Configuration                                                 | 40 |

| 14.1.2       | TON_DELAY and TON_RISE (Soft-start)                                              | 40 |

| 14.1.3       | Active Regulation                                                                |    |

| 14.1.4       | Shutdown                                                                         |    |

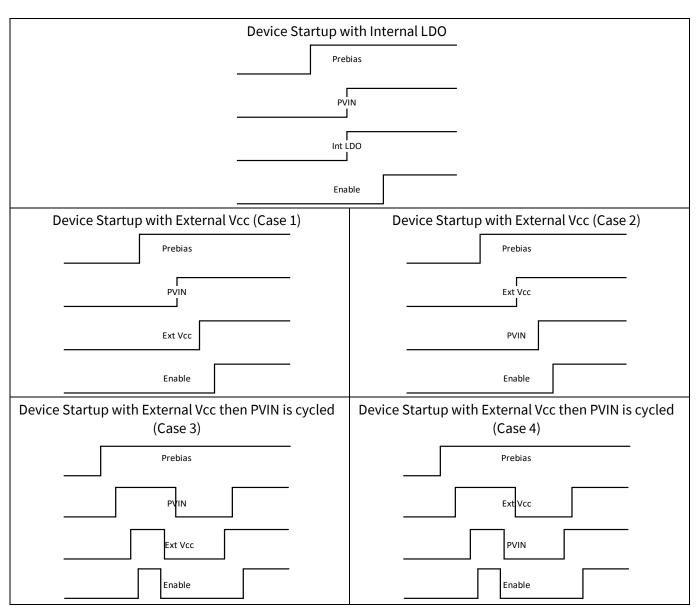

| 14.2         | Start up Sequence                                                                |    |

| 14.3<br>14.4 | Pre-bias start-upInternal Low-Droput (LDO) Regulator                             |    |

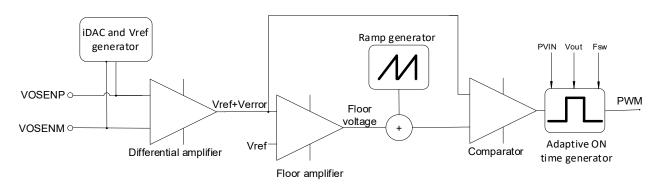

| 14.5         | Fast Constant ON-Time Control                                                    |    |

| 14.6         | EN (Enable) Pin                                                                  |    |

| 14.7         | Switching Frequency and FCCM/DEM Operation                                       |    |

| 14.8         | Soft Start                                                                       | 44 |

| 14.9         | Load-line                                                                        |    |

| 14.10        | Output Voltage Differential Sensing                                              |    |

| 14.11        | Output Current Sensing                                                           |    |

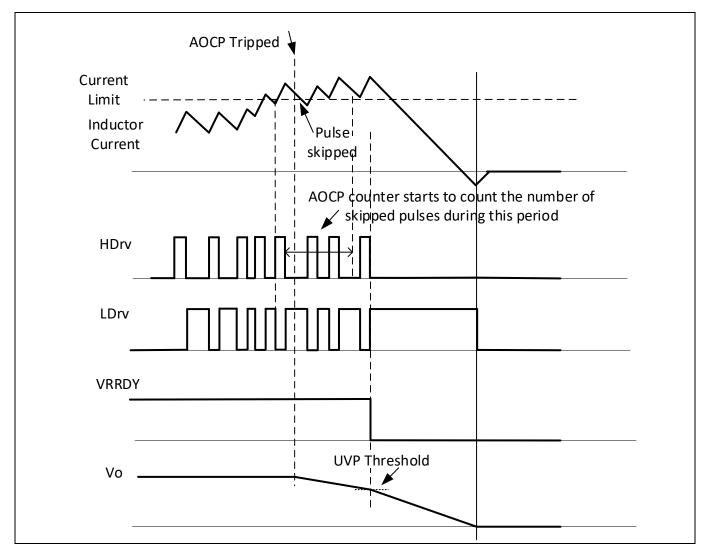

| <b>15</b>    | Faults and Protections                                                           |    |

| 15.1<br>15.2 | Over Current Protection (OCP)                                                    |    |

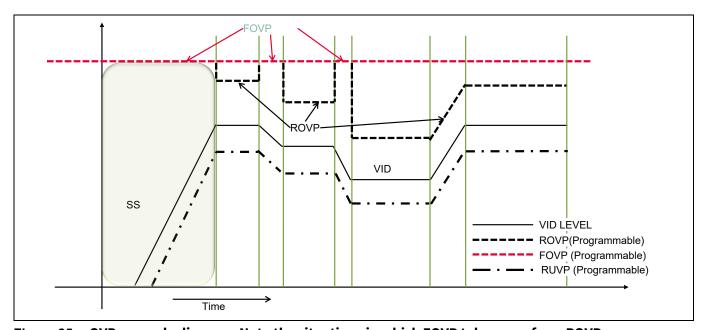

| 15.2<br>15.3 | Output Under Voltage Protection (UVP) Over Voltage Protection (OVP)              |    |

| 15.3<br>15.4 | Over Temperature Protection (OTP)                                                |    |

| 15.5         | Boot Under Voltage Lockout (UVLO)                                                |    |

| 15.6 | Minimum On - Time and Minimum Off - Time               | 50 |

|------|--------------------------------------------------------|----|

| 15.7 | High-Side Short (HSS) Detection                        | 50 |

| 16   | Faults Communication                                   | 51 |

| 16.1 | PMBUS Slave Addressing                                 | 51 |

| 16.2 | Real-Time Telemetry                                    | 51 |

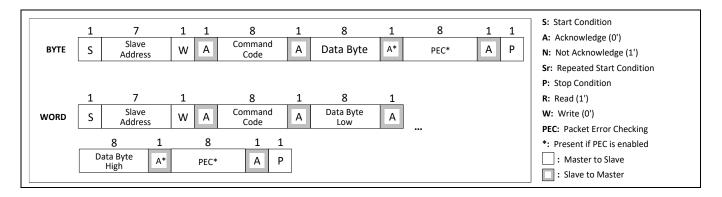

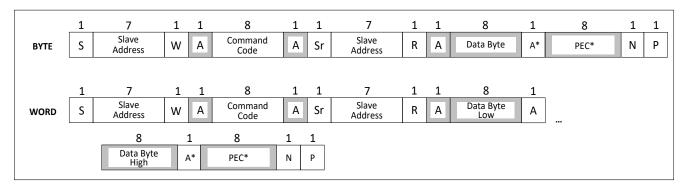

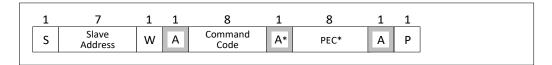

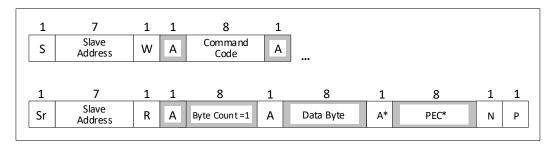

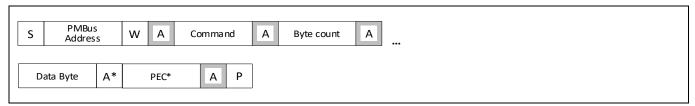

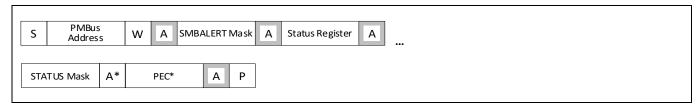

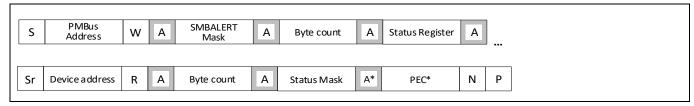

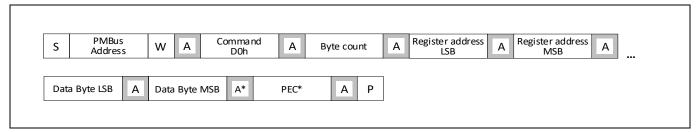

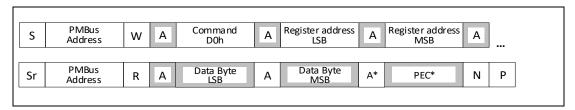

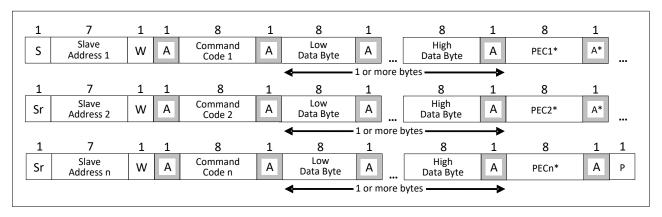

| 16.3 | SMBUS/PMBUS PROTOCOLS                                  | 51 |

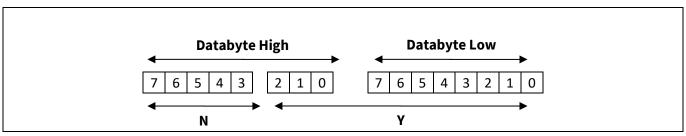

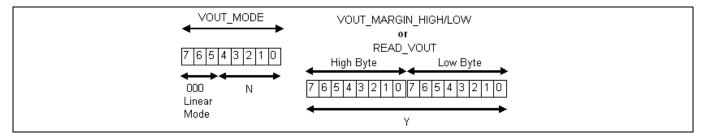

| 16.4 | 11-BIT Linear Data Format                              | 59 |

| 16.5 | 16-BIT Linear Data Format                              | 59 |

| 17   | Design example                                         | 60 |

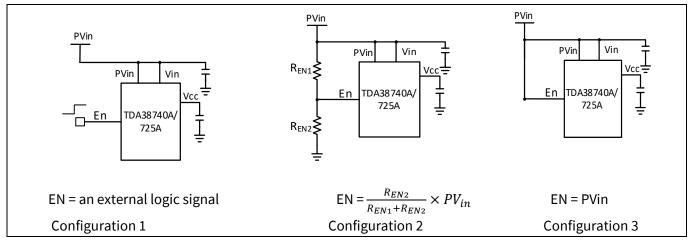

| 17.1 | Enabling the TDA38740A/25A                             | 60 |

| 17.2 | Programming the Switching Frequency and Operation Mode | 60 |

| 17.3 | Selecting Input Capacitors                             | 60 |

| 17.4 | Inductor Selection                                     | 61 |

| 17.5 | Output Capacitor Selection                             | 61 |

| 17.6 | Bootstrap Capacitor                                    | 62 |

| 17.7 | VIN and Vcc/LDO bypass Capacitor                       | 62 |

| 17.8 | Design Recommendations                                 | 62 |

| 18   | Layout Recommendations                                 | 63 |

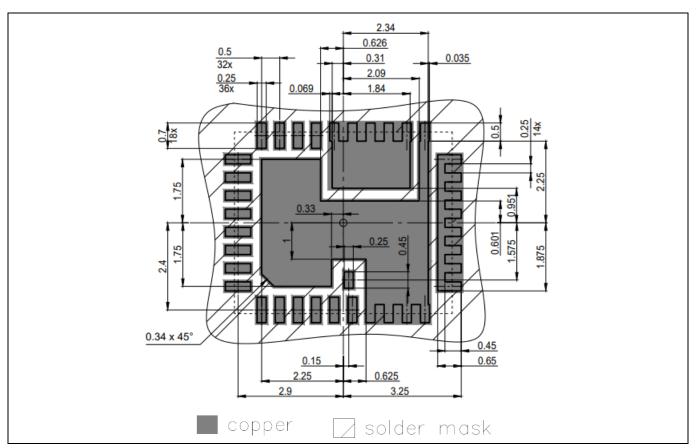

| 18.1 | PCB Metal and Component Placement                      | 64 |

| 18.2 | Solder Resist                                          | 64 |

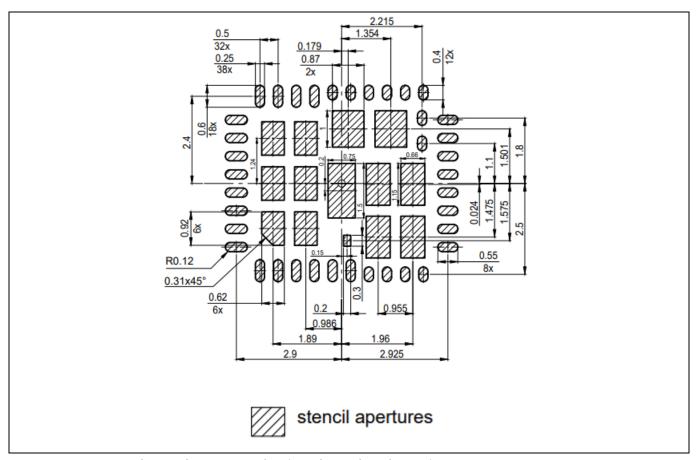

| 18.3 | Stencil Design                                         | 65 |

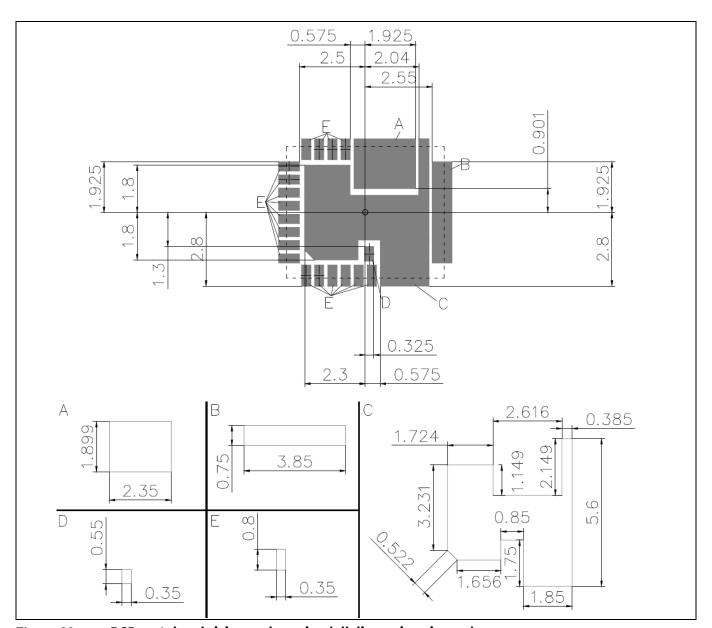

| 19   | Package                                                | 67 |

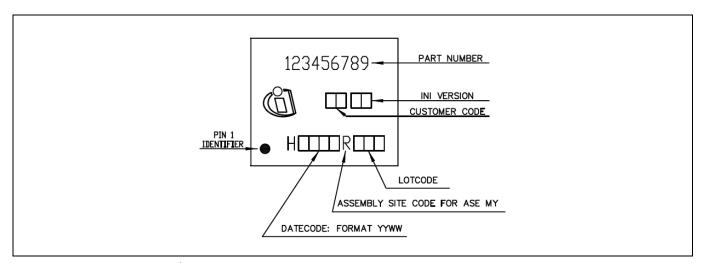

| 19.1 | Marking Information                                    | 67 |

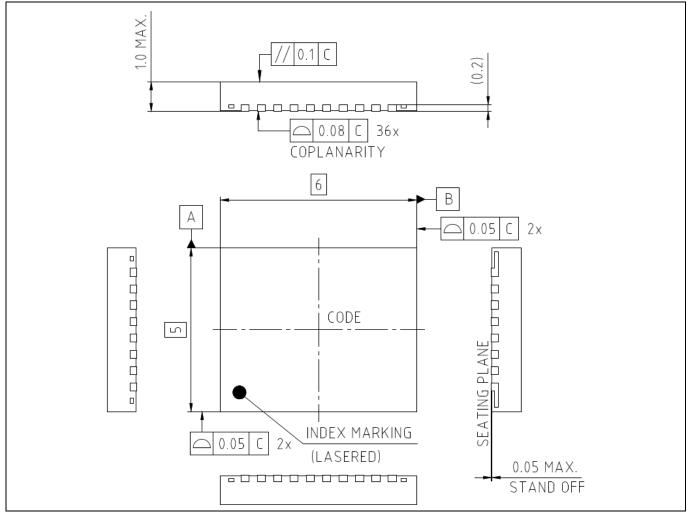

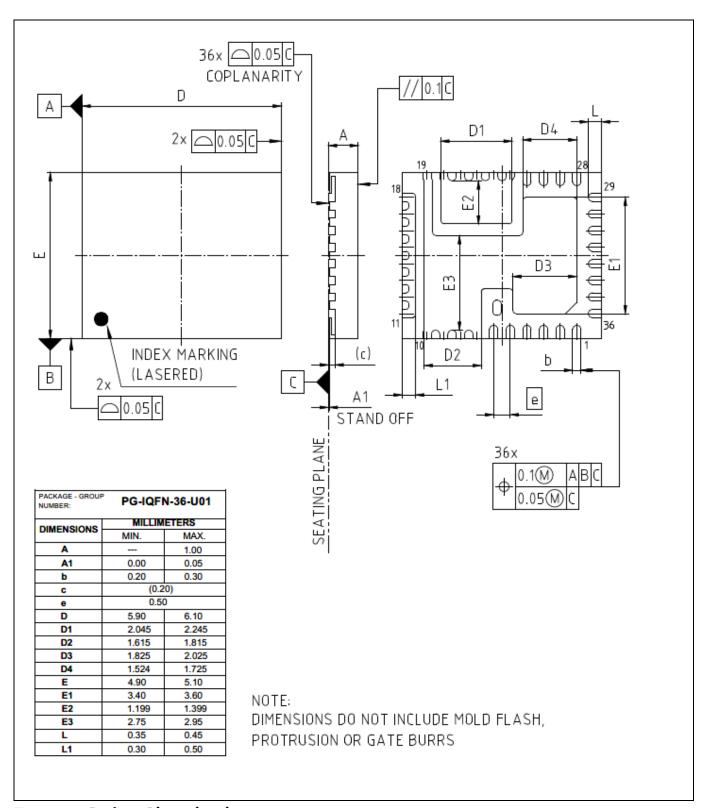

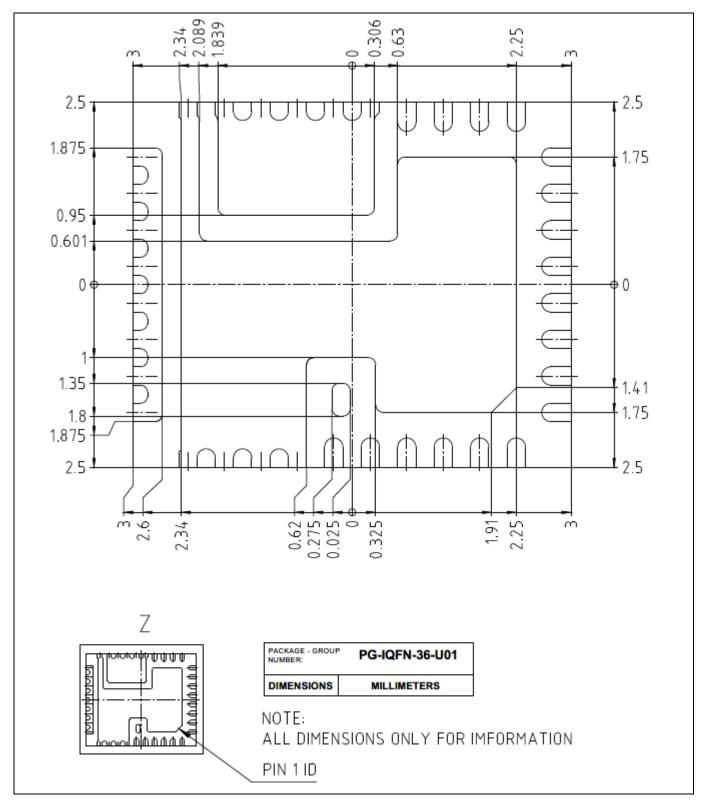

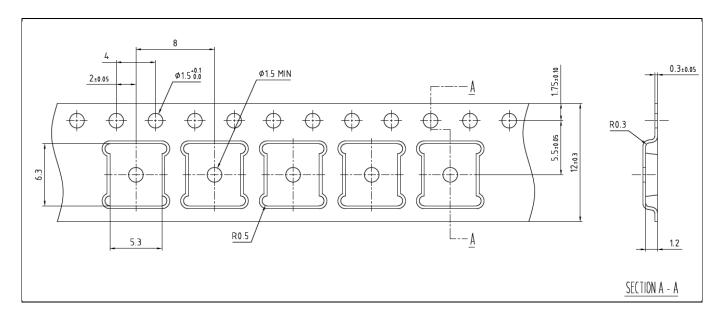

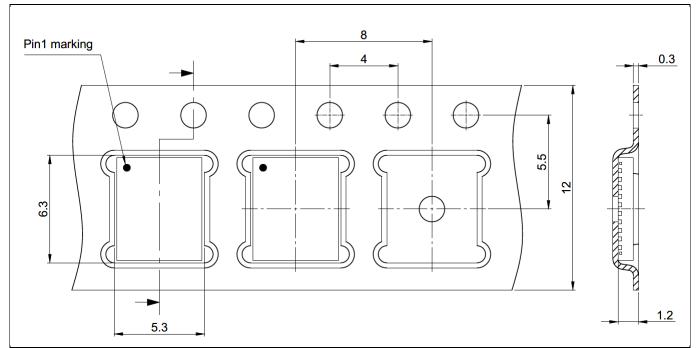

| 19.2 | Dimensions                                             | 67 |

| 19.3 | Tape and Reel Information                              | 70 |

| 20   | Environmental Qualifications                           | 71 |

| 21   | Revision History                                       | 72 |

### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

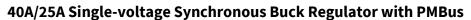

**Ordering Information**

# 1 Ordering Information

Table 1 Ordering Information

| Sales Part         | Package            | Standard Pack Form and Qty |      | Orderable Part Number | Part type                                                                                        |  |

|--------------------|--------------------|----------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------|--|

| Number             | Type               |                            |      |                       |                                                                                                  |  |

|                    | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38740A0000AUMA1    | 40A Generic Part–PMBus controlled configuration                                                  |  |

| TDA38740A-<br>aabb | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38740A0020AUMA1    | 40A Generic Part – Pin strap<br>controlled configuration with<br>VOUT_SCALE_LOOP set to 1:1      |  |

|                    | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38740A0030AUMA1    | 40A Generic Part – Pin strap<br>controlled configuration with<br>VOUT_SCALE_LOOP set to 1:2      |  |

|                    | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38740AaabbAUMA1    | 40A Custom part                                                                                  |  |

| TDA38725A-         | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38725A0000AUMA1    | 25A Generic Part-PMBus controlled configuration                                                  |  |

| aabb               | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38725A0020AUMA1    | 25A Generic Part – Pin strap<br>controlled configuration with<br>VOUT_SCALE_LOOP set to 1:1      |  |

|                    | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38725A0030AUMA1    | 25A Generic Part – Pin strap<br>controlled configuration with with<br>VOUT_SCALE_LOOP set to 1:2 |  |

|                    | QFN 5 mm x<br>6 mm | Tape<br>and Reel           | 5000 | TDA38725AaabbAUMA1    | 25A Custom part                                                                                  |  |

### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

## **Ordering Information**

Figure 1 Package Top View

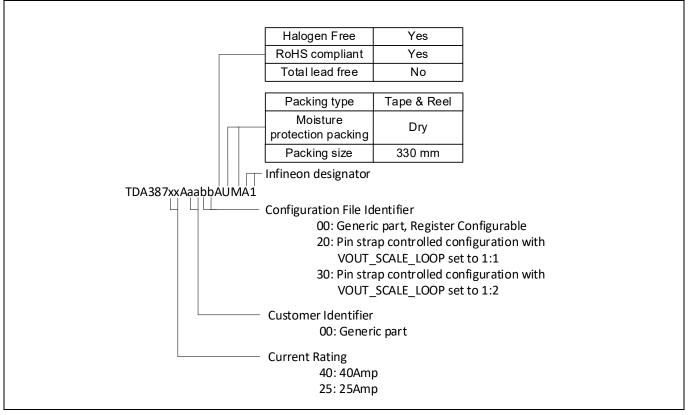

**Functional Block Diagram**

# 2 Functional Block Diagram

Figure 2 Block Diagram

**Typical Application Diagram**

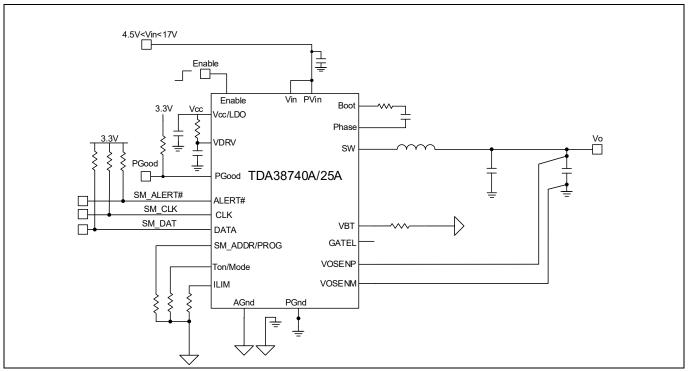

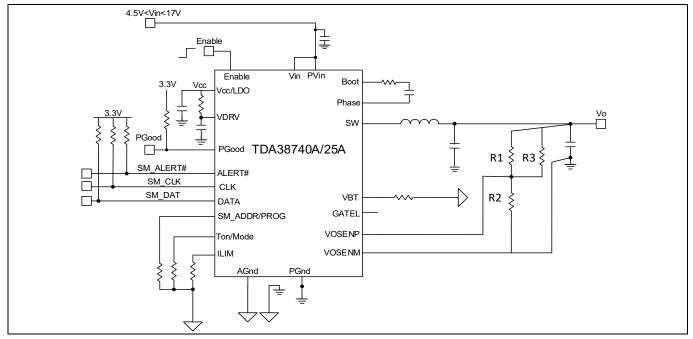

# 3 Typical Application Diagram

Figure 3 TDA38740A/25A application circuit for Vout< 2.5 V

Figure 4 TDA38740A/25A application circuit for Vout> 2.5 V

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Pin Descriptions**

# 4 Pin Descriptions

Note: A- Analog; D- Digital; [I]- INPUT; [O]- OUTPUT; [B]- BI-DIRECTIONAL; [P]- POWER

Table 2 Pin Descriptions

| Pin#                              | Pin Name     | Pin Type | Pin Description                                                                                                               |

|-----------------------------------|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------|

|                                   |              |          | Connect a resistor to ground to set Over Current Protection                                                                   |

| 1                                 | ILIM         | A[I]     | (OCP) limit. Eight user selectable OCP limits are available.                                                                  |

| 2                                 | PGood        | D[O]     | Power Good status output pin is open drain. Connect a pull up                                                                 |

|                                   |              | -[-]     | resistor from this pin to an external bias voltage.                                                                           |

|                                   |              |          | Input voltage for an Internal LDO. A 4.7 uF capacitor should be connected between this pin and PGND. If an external supply is |

| 3                                 | VIN          | A[I]     | connected to the Vcc/LDO pin, this pin should be shorted to the                                                               |

|                                   |              |          | Vcc/LDO pin and a 2.2 uF ceramic capacitor can be shared with                                                                 |

|                                   |              |          | Vin and Vcc/LDO.                                                                                                              |

|                                   |              |          | Input bias for an external Vcc voltage /Output of the internal                                                                |

|                                   |              |          | LDO. A 2.2 uF ceramic capacitor is recommended to use between Vcc/LDO, VDRV and the Power ground (PGND). An                   |

| 4                                 | Vcc/LDO      | A[P]     | optional decoupling capacitor can be placed between Vcc/LDO                                                                   |

|                                   |              |          | and AGND. Connect to external supply when internal LDO not                                                                    |

|                                   |              |          | being used.                                                                                                                   |

|                                   |              |          | VDRV should be shorted to the Vcc/LDO pin on the PCB. A 2.2 uF                                                                |

| 5                                 | VDRV         | A[P]     | ceramic capacitor is recommended to use between VDRV,                                                                         |

|                                   |              |          | Vcc/LDO and the Power ground (PGND). Connect to external                                                                      |

| -                                 |              |          | supply when internal LDO not being used. Gate of Low-side FET. The signal on this pin should be used for                      |

| 6, 37                             | GATEL        | A [O]    | test purposes only and should not have external components                                                                    |

| ,                                 | 9,1, ==      | [•]      | connected to it.                                                                                                              |

|                                   |              |          | Power Ground. Should be connected to the system's power                                                                       |

| 7, 8, 9, 10, 19                   | PGND         | -        | ground plane. PGND and AGND are internally connected via the                                                                  |

|                                   |              |          | lead frame.                                                                                                                   |

| 11, 12, 13, 14,<br>15, 16, 17, 18 | SW           | A [O]    | Switch Node. Connect these pins to an output inductor.                                                                        |

| 13, 10, 17, 10                    |              |          |                                                                                                                               |

| 20, 21, 22, 23,<br>24             | PVin         | A [P]    | Input supply for the power stage.                                                                                             |

|                                   |              |          | Course of High side FFT Courset a bootstrop course to                                                                         |

| 25                                | Phase        | A [O]    | Source of High-side FET. Connect a bootstrap capacitor between this pin and the Boot pin. A high temperature (X7R) 0.1        |

| 20                                | Tilase       | ۸ [٥]    | uF or greater value ceramic capacitor is recommended.                                                                         |

| 200                               | Doot         | Λ [1]    | Supply voltage for the high side driver. Connect this pin to the                                                              |

| 26                                | Boot         | A [I]    | Phase pin of the regulator through a bootstrap capacitor.                                                                     |

| 27                                | EN           | A [I]    | Enable pin to turn the IC on and off.                                                                                         |

| 28                                | VBT          | A[I]     | A resistor from this pin to ground defines the default boot                                                                   |

|                                   | VDT          | <u> </u> | voltage that the part will boot up in.                                                                                        |

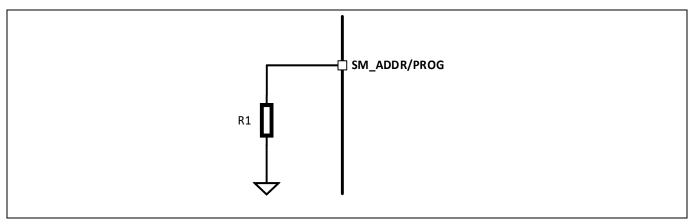

|                                   |              |          | PMBus Slave Address and PROG pin. A resistor to ground on this                                                                |

|                                   |              |          | pin points to one of the sixteen unique PMBus slave devices which needs to be addressed on the board. The same address        |

| 29                                | SM_ADDR/PROG | D[I]     | also defines the specific configuration from a multi image                                                                    |

|                                   |              |          | configuration file (supports 13 images max) that will be loaded                                                               |

|                                   |              |          | from the OTP during power-up.                                                                                                 |

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

# **Pin Descriptions**

| Pin# | Pin Name  | Pin Type | Pin Description                                                                                                                                               |

|------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30   | VOSENP    | A [I]    | Output voltage feedback pin. Connect this pin to the output of the regulator to regulate the output voltage.                                                  |

| 31   | VOSENM    | A [I]    | The pin provides the return path for the remote voltage sensing. It is used as a reference for the Analog Front End (AFE)                                     |

| 32   | AGND      | -        | Signal ground for the internal circuitry. AGND should be connected to PGND on the PCB.                                                                        |

| 33   | SM_DATA   | D [B]    | Serial data line I/O. PMBus bi-directional serial data line.                                                                                                  |

| 34   | SM_CLK    | D [I]    | Serial Clock Line Input. PMBus serial clock input. The interface is rated to max of 1 MHz                                                                     |

| 35   | SM_ALERT# | D [O]    | SMB Active low alert line                                                                                                                                     |

| 36   | MODE/TON  | D [I]    | Multi-function pin. This pin can be used to select one of eight switching frequencies, and FCCM or DEM mode by connecting a resistor from this pin to ground. |

#### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Absolute Maximum Ratings**

# 5 Absolute Maximum Ratings

Stresses higher than those mentioned in Table 3 below may result in permanent damage to the device. These are the absolute stress ratings only and the operation of the device is not recommended or implied at these or any other condition's in excess of those given in the recommended operating ratings in Table 5. Exposure of values over and above the recommended ratings for extended periods may adversely affect the operation and reliability of the device.

Table 3 Absolute Maximum Ratings

| Description                              | Symbol                                 | Values                         |     |                             |      | Note/Tost Conditions        |  |

|------------------------------------------|----------------------------------------|--------------------------------|-----|-----------------------------|------|-----------------------------|--|

| Description                              | Symbol                                 | Min                            | Тур | Max                         | Unit | Note/ Test Conditions       |  |

| Power Input voltage                      | $V_{PVIN}$                             | -0.3                           | -   | 25                          | V    | Note 1, PVIN Pin            |  |

| LDO Input voltage                        | V <sub>IN</sub>                        | -0.3                           | -   | 25                          | ٧    | Note 1, VIN Pin             |  |

| Enable voltage                           | $V_{EN}$                               | -0.3                           | -   | 25                          | V    | EN Pin                      |  |

| PVIN-PHASE voltage                       | V <sub>PVin</sub> -V <sub>PHASE</sub>  | -5 V for 5 ns, -<br>0.3 V dc   | -   | 34 V for 1 ns,<br>25 V dc   | V    | PVIN-PHASE pin              |  |

| PVin-Switch Node<br>voltage              | V <sub>PVin</sub> -V <sub>SW</sub>     | -5 V for 5 ns, -<br>0.3 V dc   | -   | 34 V for 1 ns,<br>25 V dc   | V    | VIN-PHASE pin               |  |

| PVIN-Switch Node<br>voltage              | V <sub>PVIN</sub> -V <sub>SW</sub>     | -5 V for 5 ns, -<br>0.3 V dc   | -   | 34 V for 1 ns,<br>25 V dc   | V    | PVIN- SW Pin                |  |

| Internal Driver voltage                  | $V_{DRV}$                              | -0.3                           | -   | 6                           | V    | Note 1, VCC/VDRV Pin        |  |

| Gate Low Pin voltage                     | $V_{GATEL}$                            | -0.3                           | -   | 6                           | ٧    | GateL Pin                   |  |

|                                          | V <sub>воот</sub>                      | -0.3 V for 5 ns, -<br>0.3 V dc | -   | 29 V dc                     | V    | BOOT Pin                    |  |

| BOOT voltage                             | V <sub>BOOT</sub> - V <sub>PHASE</sub> | -0.3                           | -   | 7 V for 5 ns,<br>6 V dc     | V    | BOOT – PHASE Pin            |  |

| Switch Node voltage                      | $V_{\sf SW}$                           | -7 V for 5 ns, -<br>0.3 V dc   | -   | 34 V for 1 ns,<br>25 V dc   | V    | Switch Node Pin             |  |

| Phase Node voltage                       | $V_{PHASE}$                            | -7 V for 5 ns, -<br>0.3 V dc   | -   | 34 V for 1 ns,<br>25 V dc   | V    | Phase Pin                   |  |

| Address/PROG voltage                     | V <sub>SM_ADDR/PROG</sub>              | -0.3                           | -   | 3.6                         | V    | Note 1,<br>SM_ADDR/PROG Pin |  |

| Output Positive Sense voltage            | V <sub>VOSENP</sub>                    | -1.5 V for 5 ns, -<br>0.3 V dc | -   | 3.6                         | V    | Note 1, VOSENP Pin          |  |

| Output Negative Sense voltage w.r.t AGND | V <sub>VOSENM</sub>                    | -0.3                           | -   | 0.3                         | V    | Note 1, VOSENM Pin          |  |

| Voltage Regulator Power<br>Good          | $V_{PGOOD}$                            | -0.3                           | -   | 3.6                         | V    | Note 1, PGOOD Pin           |  |

| ILIM Voltage                             | $V_{ILIM}$                             | -0.3                           | -   | 3.6                         | V    | Note 1, ILIM Pin            |  |

| MODE/TON voltage                         | V <sub>MODE/TON</sub>                  | -0.3                           | -   | 3.6                         | V    | Note 1, MODE/TON<br>Pin     |  |

| VBT voltage                              | $V_{VBT}$                              | -0.3                           | -   | 3.6                         | V    | Note 1, VBT voltage pin     |  |

| Power GND w.r.t Analog<br>GND voltage    | V <sub>PGND</sub> - V <sub>AGND</sub>  | -1.5 V for 5 ns, -<br>0.3 V dc | -   | 1.5 V for 5 ns,<br>0.3 V dc | V    | PGND – AGND Pin             |  |

| SM CLK voltage                           | V <sub>SM_CLK</sub>                    | -0.3                           | -   | 3.6                         | V    | SM_CLK Pin                  |  |

| Final Datasheet                          |                                        | 11 of 73                       |     |                             |      | V2.1                        |  |

## 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

#### **Absolute Maximum Ratings**

| Description         | Consola a I            | Values |     |     |      | Nata / Task Cara dikiana |  |

|---------------------|------------------------|--------|-----|-----|------|--------------------------|--|

| Description         | Symbol                 | Min    | Тур | Max | Unit | Note/ Test Conditions    |  |

| SM Data voltage     | $V_{SM\_DAT}$          | -0.3   | -   | 3.6 | V    | SM_DAT Pin               |  |

| SM Alert voltage    | V <sub>SM_ALERT#</sub> | -0.3   | -   | 3.6 | V    | SM_ALERT# Pin            |  |

| Juntion Temperature | $T_{Jmax}$             | -40    | -   | 150 | °C   | -                        |  |

| Storage Temperature | T <sub>STORAGE</sub>   | -55    | -   | 150 | °C   | -                        |  |

#### Note:

1. PGND and AGND pins are connected together.

Attention: Stresses beyond these listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.

## 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Thermal Characteristics**

### 6 Thermal Characteristics

#### **Table 4** Thermal Characteristics

| Description                            | Symbol                   | Values   | Test Conditions |

|----------------------------------------|--------------------------|----------|-----------------|

| Junction to Ambient Thermal Resistance | $\theta_{JA}$            | 19 °C/W  | Note 2          |

| Junction to PCB Thermal Resistance     | $\theta_{\text{JC-PCB}}$ | 1.1 °C/W | Note 3          |

| Junction to Case Top Termal Resistance | $\theta_{JC}$            | 24 °C/W  |                 |

#### Note:

- 2. Thermal resistance is measured with components mounted on a standard EVAL\_TDA38740\_1.2Vout demo board in free air

- 3. Thermal resistance is based on the board temperature near pin 22

### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Electrical Specifications**

# **7** Electrical Specifications

**Table 5** Recommended Operating Conditions for Reliable Operation

| Description                                   | Min  | Max  | Unit | Note                      |

|-----------------------------------------------|------|------|------|---------------------------|

| PVin Voltage Range with External Vcc          | 3    | 17   | ٧    | Note 4, Note 5            |

| PVin Voltage Range with Internal LDO          | 4.5  | 17   | V    | Note 5 , Note 6 & Note 10 |

| Vcc Supply Voltage Range                      | 4.5  | 5.5  | ٧    | Note 4 , Note 7           |

| Output Voltage Range                          | 0.25 | 5.12 | V    | Note 8                    |

| Continuous Output Current Range for TDA38740A |      | 40   | А    | Note 9                    |

| Continuous Output Current Range for TDA38725A |      | 25   | А    | Note 9                    |

| Switching Frequency (excluding 1600 kHz)      | 400  | 2000 | kHz  | Note 10                   |

| Operating Junction Temperature                | -40  | 125  | °C   |                           |

#### Note:

- 4. VCC/VDRV pin is connected to an external bias voltage when Pvin is less than 4.5 V

- 5. A common practice is to have 20% margin on the maximum SW node voltage in the design. For applications requiring PVin equal to or above 14 V, a small resistor in series with the Boot pin should be used to ensure the maximum SW node spike voltage does not exceed absolute maximum specs. Alternatively, a snubber can be used at SW node to reduce the SW node spike.

- 6.  $PV_{in}$  with internal LDO is used. For single-rail applications with the internal LDO and  $PV_{in} = 4.5 \text{ V}-5.4 \text{ V}$ , the internal LDO may enter dropout mode. AOCP limits can be reduced due to the lower VCC voltage.

- 7. The TDA38740A/25A is designed to function with VCC down to 4.5 V. However, electrical specifications such as AOCP limits may be degraded.

- 8. The maximum output voltage is limited by the minimum off-time. For output voltages above 2.56 V an external feedback resistor divider is needed.

- 9. Refer to Section 15.1 for maximum output current rating at different ambient temperature and OCP threshold tolerance

- 10. The maximum LDO output current must be limited within 50 mA for operations requiring the full operating temperature range of -40 °C  $\leq$   $T_J \leq$  125 °C. Thermal De-rating may be needed at an elevated ambient temperature to ensure the junction temperature remains within the recommended operating range.

## 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Electrical Specifications**

### 7.1 Electrical Characteristics

Unless otherwise specified, these specifications apply over,  $4.5 \text{ V} \le \text{Vin} = \text{PVin} \le 17 \text{ V}$ , in  $0 \text{ °C} < \text{T}_{\text{J}} < 125 \text{ °C}$ . Typical values are specified at Ta = 25 °C.

**Table 6 Electrical Characteristics**

|                                                   | - Characteristic          | <del></del>                                                                     |      |         |     |       |

|---------------------------------------------------|---------------------------|---------------------------------------------------------------------------------|------|---------|-----|-------|

| Parameter                                         | Symbol                    | Conditions                                                                      | Min  | Тур     | Max | Unit  |

| Power Stage                                       |                           |                                                                                 |      |         |     |       |

| Top Switch                                        | $R_{ds(on)\_Top}$         | VBoot – Vsw= 5.0 V, Io = 35 A, Tj =25 °C                                        | -    | 2.9     | -   | mΩ    |

| Bottom Switch                                     | $R_{ds(on)\_Bot}$         | Vcc = 5.0, lo= 35 A, Tj<br>=25 °C                                               | -    | 1.00    | -   | 11122 |

| Bootstrap Diode<br>Forward Voltage                |                           | I(Boot) = 25 mA                                                                 | -    | 780     | 950 | mV    |

|                                                   |                           | SW = 0 V, EN = 0 V                                                              | -    | -       | 175 |       |

| SW Leakage Current                                | I <sub>SW</sub>           | SW = 0 V, EN = high,<br>No Switching                                            | -    | -       | 175 | μΑ    |

| Dead Band Time                                    | T <sub>db</sub>           | SW Node rising edge,<br>40 A , Internal LDO,<br>T <sub>j</sub> =25 °C, Note 11  | -    | 10      | -   | ns    |

| Dead Danid Tillie                                 | I db                      | SW Node falling edge,<br>40 A , Internal LDO,<br>T <sub>j</sub> =25 °C, Note 11 | -    | 10      | -   | 113   |

| Supply Voltage                                    | PVin, Vin and E           | xternal VCC                                                                     |      |         |     |       |

| PVin range (using external VCC = 5V)              |                           |                                                                                 | -    | 3-17    | -   | V     |

| Vin Range (using                                  |                           | Fsw = 600 kHz                                                                   | -    | 4.5 -17 | -   | V     |

| internal LDO)                                     |                           | Fsw = 2000 kHz                                                                  | -    | 4.5 –17 | -   | V     |

| External VCC                                      |                           |                                                                                 | 4.5  | 5       | 5.5 | V     |

| Supply Current                                    | lin                       |                                                                                 |      |         |     |       |

| PVin Supply Current<br>(standby)(External<br>Vcc) | l <sub>in (Standby)</sub> | EN = Low, No Switching,<br>Note 14                                              | -    | 2       | -   |       |

| PVin Supply Current<br>(dynamic)(External<br>Vcc) | I <sub>in (Dyn)</sub>     | EN = High, Fs = 800kHz,<br>Vin=PVin=12 V,<br>Vout =1.1 V, Note 14               | -    | 15      | -   | mA    |

| PVin Supply Current<br>(standby)(Internal<br>Vcc) | l in (Standby)            | EN = Low, No Switching,<br>Note 14                                              | -    | 12      | -   | IIIA  |

| PVin Supply Current<br>(dynamic)(Internal<br>Vcc) | I <sub>in (Dyn)</sub>     | EN = High, Fs = 800kHz,<br>Vin=PVin=12 V,<br>Vout =1.1 V, Note 14               | -    | 48      | -   |       |

| Remote Voltage<br>Sense Inputs                    | VOSENP, VO                | SENM                                                                            |      |         |     |       |

| VOSEND Innut Current                              |                           | VOSENP = 3.6 V                                                                  | -    | -       | 230 | μΑ    |

| VOSENP Input Current                              |                           | VOSENP = -0.3 V                                                                 | -85  | -       | -   | μΑ    |

|                                                   |                           | VOSENM = 0.3 V                                                                  | -155 | -       | -   | μΑ    |

|                                                   |                           |                                                                                 |      |         |     |       |

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

| Parameter                           | Symbol            | Conditions                                                          | Min      | Тур   | Max   | Unit     |

|-------------------------------------|-------------------|---------------------------------------------------------------------|----------|-------|-------|----------|

| VOSENM Input<br>Current             |                   | VOSENM = -0.3 V                                                     | -200     | -     | -     | μΑ       |

| Differential Input<br>Voltage Range |                   |                                                                     | 1        | -     | 2.56  | V        |

| VOSENM Input CM<br>Voltage          |                   |                                                                     | 1        | ±300  | -     | mV       |

| MODE/TON                            |                   |                                                                     |          |       |       |          |

| Output Current                      |                   |                                                                     | -        | 104   | -     | μΑ       |

| VBT/ILIM/SM_ADD<br>R                |                   |                                                                     |          |       |       |          |

| Output Current                      |                   |                                                                     | 14.35    | 14.65 | 14.95 | μΑ       |

| Open-Drain<br>Outputs-20mA<br>Drive | SM_CLK, SM_DA     | AT, SM_ALERT#                                                       |          |       |       |          |

| Output Low Voltage                  |                   | I = 20 mA                                                           | -        | -     | 0.4   | V        |

| On Resistance                       |                   | I = 20 mA                                                           | -        | 7     | -     | Ω        |

| Tri-State Leakage                   |                   | 0 – 3.6 V                                                           | -5       | -     | 5     | μΑ       |

| On-Time Timer                       |                   |                                                                     | <u> </u> |       |       |          |

| Frequency Range (programmable)      |                   | Excluding 1600 kHz<br>and in steps of 200 kHz                       | 400      |       | 2000  | KHz      |

| Minimum On-Time                     |                   | Tj=25°C, PVin=12 V,<br>Vo=0 V, Note 11                              | -        | 25    | -     | ns       |

| Minimum Off-Time                    | Toff(Min)         | Tj=25°C, VFB=0 V,<br>Note 11                                        | -        | 150   | -     | ns       |

| System Set Point<br>Accuracy        |                   |                                                                     |          |       |       |          |

| 0.25 V ≤ Vout ≤ 0.445 V             |                   | -40 °C ≤ T」≤ 125°C                                                  | -        | ±10   | -     | mV       |

| 0.45 V ≤ Vout ≤ 0.995 V             |                   | Typ = $3\sigma$ , Note 11 & 12                                      | -        | ±8    | -     | mV       |

| 1.0 V ≤ Vout ≤ 2.52 V               |                   | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                             | -        | ±1    | -     | %        |

| VCC LDO Output                      | Vcc               | 1                                                                   |          |       |       | <u> </u> |

| Vcc Output Voltage                  | Vcc               | 5.5 V ≤ PVin ≤ 17 V,<br>when Icc =50 mA,<br>Cload = 2.2 uF, Tj=25°C | 4.7      | 5.0   | 5.3   | V        |

| VCC Dropout                         | Vcc_drop          | PVin = 4.5 V, Icc=50 mA,<br>Cload=2.2uF, Tj=25°C                    | -        | 650   | -     | mV       |

| Under Voltage<br>Lockout            |                   |                                                                     |          |       |       |          |

| Vcc_Good Start<br>Threshold         | VCC_UVLO_Start    | Vcc Rising Trip Level                                               | 3.8      | 4.0   | 4.2   | V        |

| Vcc_Good Stop<br>Threshold          | VCC_UVLO_Stop     | Vcc Falling Trip Level                                              | 3.6      | 3.8   | 4.0   | V        |

| Enable-Start-<br>Threshold          | Enable_UVLO_Start | Ramping up                                                          | 0.61     | 0.65  | 0.69  | V        |

| Enable-Stop-<br>Threshold           | Enable_UVLO_Stop  | Ramping down                                                        | 0.51     | 0.55  | 0.59  | V        |

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

|                                                          | 1                 | T                                     |     | T        | ı   | 1    |

|----------------------------------------------------------|-------------------|---------------------------------------|-----|----------|-----|------|

| Parameter                                                | Symbol            | Conditions                            | Min | Тур      | Max | Unit |

| Boot Rising Threshold                                    | BOOT_UVLO_Rising  | Boot-Phase Ramping up, Note 11        | 3.7 | 3.85     | 4.0 | .,   |

| Boot Falling<br>Threshold                                | BOOT_UVLO_Falling | Boot-Phase Ramping<br>down, Note 11   | 3.5 | 3.65     | 3.8 | V    |

| Over Current Limit                                       |                   |                                       |     | •        |     | - U  |

|                                                          |                   |                                       | -   | 10       | -   |      |

| TDA38740A Current<br>Limit Threshold                     |                   |                                       | -   | 15       | -   |      |

|                                                          |                   |                                       | -   | 20       | -   |      |

|                                                          | l <sub>oc</sub>   | Tj = 25 °C, Vcc =5.0 V,               | -   | 25       | -   | A    |

| (Valley Current)                                         | 100               | ,, 20 0, 100 010 1,                   | -   | 30       | -   |      |

|                                                          |                   |                                       | -   | 40       | -   |      |

|                                                          |                   |                                       | -   | 50<br>60 | -   |      |

|                                                          |                   |                                       |     | 10       | -   |      |

|                                                          |                   |                                       | _   | 15       | -   |      |

| TDA38725A Current<br>Limit Threshold<br>(Valley Current) |                   |                                       | -   | 20       | -   |      |

|                                                          |                   | Tj = 25 °C, Vcc =5.0 V                | -   | 25       | -   | _    |

|                                                          | l <sub>oc</sub>   |                                       | -   | 25       | -   | A    |

| (valley current)                                         |                   |                                       | -   | 25       | -   |      |

|                                                          |                   | _                                     | -   | 25       | -   |      |

|                                                          |                   |                                       | -   | 25       | -   |      |

| Current Limit<br>Threshold Accuracy                      |                   | See Note 11                           |     | ±20      |     | %    |

| Over Voltage<br>Protection                               |                   | 1                                     |     | Т        |     | 1    |

|                                                          |                   |                                       | -   | 0.8      | -   |      |

|                                                          |                   |                                       | -   | 1.0      | -   |      |

|                                                          |                   |                                       | -   | 1.2      | -   |      |

|                                                          |                   | In VOUT_SCALE_LOOP                    | -   | 1.35     | -   | 1    |

|                                                          |                   | 1:1 mode,<br>8 Discrete Options       | -   | 1.5      | -   | V    |

|                                                          |                   | o Discrete Options                    | -   | 1.8      | -   |      |

|                                                          |                   |                                       | -   | 2.2      | -   |      |

| Fixed OVP Threshold                                      |                   |                                       | -   | 2.85     | -   | 1    |

| (Programmable)                                           | OVP_Vth           |                                       | -   | 1.6      | -   |      |

|                                                          |                   |                                       | -   | 2.0      | -   | 1    |

|                                                          |                   | La VOUT COME LOGS                     | _   | 2.4      | -   | 1    |

|                                                          |                   | In VOUT_SCALE_LOOP 1:2 mode,          | -   | 2.7      | -   | 1    |

|                                                          |                   | 8 Discrete Options.                   | -   | 3.0      | -   | V    |

|                                                          |                   | Note 11 & 13                          | _   | 3.6      | -   | †    |

|                                                          |                   |                                       | _   | 4.4      | -   | 1    |

|                                                          |                   |                                       | _   | 5.7      | -   | -    |

| Output Fixed OVP Threshold Accuracy                      |                   | See note 11                           |     | ±5       |     | %    |

| zzo.acouracy                                             |                   | Relative to Vout in steps of 50 mV in | 50  | -        | 400 | mV   |

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

| Parameter                                   | Symbol          | Conditions                                                                                                            | Min | Тур      | Max | Unit |

|---------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|-----|----------|-----|------|

|                                             |                 | VOUT_SCALE_LOOP 1:1<br>mode, Note 14                                                                                  |     |          |     |      |

| Relative OVP<br>Threshold<br>(programmable) |                 | Relative to Vout in steps<br>of 50 mV in<br>VOUT_SCALE_LOOP 1:2<br>mode, Note 13 and 14                               | 100 | -        | 800 | mV   |

| Output Relative OVP                         |                 | VOUT_SCALE_LOOP 1:1<br>mode, Note 14                                                                                  | -   | ±50      | -   | mV   |

| Threshold Accuracy                          |                 | VOUT_SCALE_LOOP 1:2<br>mode, Note 13 & 14                                                                             | -   | ±100     | -   | mV   |

| Under Voltage<br>Protection                 |                 |                                                                                                                       |     |          |     |      |

| UVP Trip Threshold                          | UVP_Vth         | Relative to Vout in steps<br>of 50 mV in<br>VOUT_SCALE_LOOP 1:1<br>mode, Note 13                                      | 50  | -        | 400 | mV   |

|                                             |                 | Relative to Vout in steps<br>of 50 mV in<br>VOUT_SCALE_LOOP 1:2<br>mode, Note 13 and 14                               | 100 | -        | 800 | mV   |

| Output Relative UVP<br>Threshold Accuracy   |                 | VOUT_SCALE_LOOP 1:1<br>mode, Note 13                                                                                  | -   | ±50      | -   | mV   |

|                                             |                 | VOUT_SCALE_LOOP 1:2<br>mode, Note 13 & 14                                                                             | -   | ±100     | -   | mV   |

| IMON Reporting<br>Accuracy                  |                 |                                                                                                                       |     | ,        |     | 1    |

| IMON Accuracy                               | Imon            | 0 °C-125 °C,<br>4.5 V <vcc<5.5 v<br="">0 A ≤ lout ≤ 40 A<br/>0.25 V ≤ Vout ≤ 2.52 V<br/>Vin = 12 V, Note 11</vcc<5.5> | -   | ±6       | -   | %    |

| Power Good                                  | Pgood           |                                                                                                                       |     |          |     | •    |

| Pgood Sink Current                          | I <sub>PG</sub> | $V_{PG} = 0.5 \text{ V}, \text{Rpull-up} = 500 \Omega \text{ to } 3.3 \text{ V}$                                      | -   | 5        | 6   | mA   |

| Pgood Open Drain<br>Leakage Current         |                 | V <sub>PG</sub> = 3.6 V                                                                                               | -5  | -        | 5   | μА   |

| Pgood Low Voltage                           | $V_{PG_{L}}$    | Vin = Vcc = 5 V, I = 20 mA                                                                                            | -   | -        | 0.1 | V    |

| Pgood Low Voltage                           | $V_{PG\_H}$     | Vin = Vcc = 0 V, Rpull-up<br>= 4.7 kΩ to 3.3 V, Note<br>11                                                            | -   | -        | 0.7 | V    |

| Thermal Shutdown                            |                 |                                                                                                                       |     | <u>ı</u> |     | 1    |

| Thermal Shutdown                            |                 | Note 11                                                                                                               | -   | 140      | -   | _    |

| Hysteresis                                  |                 | Note 11                                                                                                               | -   | 20       | -   | °C   |

| PMBus Reporting                             |                 |                                                                                                                       | -   |          | -   |      |

| Bus Speed                                   |                 | Normal                                                                                                                | -   | 100      | -   | kHz  |

| Dus specu                                   |                 | Fast                                                                                                                  | -   | 400      | -   | kHz  |

# 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

| Parameter                                           | Symbol | Conditions                                                                                                         | Min  | Тур                                 | Max  | Unit |

|-----------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------|------|-------------------------------------|------|------|

|                                                     |        | High-Speed                                                                                                         | -    | 1000                                | -    | kHz  |

| Output Voltage<br>Resolution                        |        | See Note 14 & 15                                                                                                   | -    | 0.625,<br>0.977,<br>1.953,<br>3.906 | -    | mV   |

| Output Voltage Filter<br>Rate                       |        |                                                                                                                    | -    | 8                                   | -    | kHz  |

| Output Voltage Update<br>Rate                       |        |                                                                                                                    | -    | 379                                 | 1    | kHz  |

| Highest Penerted Vout                               |        | VOUT_SCALE_LOOP=1:                                                                                                 | -    | -                                   | 2.56 | V    |

| Highest Reported Vout                               |        | VOUT_SCALE_LOOP=1:<br>2                                                                                            | -    | -                                   | 5.12 | V    |

|                                                     |        | -40 °C - 125 °C (Tj),<br>4.5 V < Vcc < 5.5 V,<br>0.25 ≤ Vout ≤ 0.5;<br>VOUT_SCALE_LOOP in<br>1:1 mode              | -2   | -                                   | 2    | %    |

| Vout Reporting Accuracy                             |        | -40 °C - 125 °C (Tj),<br>4.5 V < Vcc < 5.5 V,<br>0.5 <vout 2.52;<br="" ≤="">VOUT_SCALE_LOOP in<br/>1:1 mode</vout> | -1   | -                                   | 1    | %    |

| Iout Resolution                                     |        |                                                                                                                    | -    | 0.0625                              | -    | А    |

| lout Filter Rate                                    |        |                                                                                                                    | -    | 8                                   | -    | kHz  |

| lout Update Rate                                    |        |                                                                                                                    | -    | 379                                 | -    | kHz  |

| lout Digital Monitoring<br>Range                    |        |                                                                                                                    | -    | -                                   | 64   | А    |

| lout Accuracy (PMBus)                               |        | 0 °C-125 °C,<br>4.5 V <vcc<5.5 v<br="">10 A ≤ lout ≤ 40 A<br/>0.25 V ≤ Vout ≤ 2.52 V</vcc<5.5>                     | -    | ±6                                  | -    | %    |

| Temperature Resolution                              |        |                                                                                                                    | -    | 1                                   | -    | °C   |

| Temperature Filter Rate                             |        |                                                                                                                    | -    | 4                                   | -    | kHz  |

| Temperature Update<br>Rate                          |        |                                                                                                                    | -    | 189                                 | -    | kHz  |

| Temperature Monitoring<br>Range                     |        |                                                                                                                    | -40  | -                                   | 125  | °C   |

| Temperature Reporting<br>Accuracy                   |        | Note 11                                                                                                            | -    | ±1                                  | -    | °C   |

| PMBus Interface<br>Specifications<br>SM_DAT, SM_CLK |        |                                                                                                                    |      |                                     |      |      |

| Input Low Voltage (V <sub>IL</sub> )                |        |                                                                                                                    | -    | _                                   | 0.8  | ٧    |

| Input High Voltage<br>(V <sub>IH</sub> )            |        |                                                                                                                    | 1.35 | -                                   | -    | V    |

#### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

#### **Electrical Specifications**

| Parameter                             | Symbol | Conditions  | Min | Тур | Max | Unit |

|---------------------------------------|--------|-------------|-----|-----|-----|------|

| Output Low Voltage (V <sub>OL</sub> ) |        |             | -   | -   | 0.4 | V    |

| Data and Clock pulldown resistance    |        |             | 5   | -   | 13  | Ω    |

| SMALERT# pulldown resistance          |        |             | 5   | -   | 20  | Ω    |

| Input Leakage                         |        |             | -1  | -   | 1   | μΑ   |

| Pin Capacitance                       |        | See Note 11 | -   | -   | 4   | pF   |

#### Note:.

- 11. Guaranteed by design and not tested in production

- 12. Cold temperature performance is guaranteed via correlation using statistical quality control. Not tested in production

- 13. FOVP, ROVP and RUVP threshold accuracies for VOUT\_SCALE\_LOOP 1:2 are based on the use of an output divider as specified in section 13.3

- 14. Guaranteed by Bench Characterization at Room Temperature and not tested in production

- 15. Actual output voltage resolution is limited by internal DAC

#### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Pin Strap Resistors Application Information**

# 8 Pin Strap Resistors Application Information

The TDA38740A/25A devices allow pin-strapping functionality to boot up the part with output voltage, current limit, switching frequency, FCCM/DEM mode and address offset parameters to a value determined by pin strap resistors. The pin functionality can be enabled by writing '0' to the registers ilim\_docp\_override\_pin(0x5E[0]), ilim\_aocp\_override\_pin(0x5E[1]), lcf\_zero\_override\_pin(0x5E[2]), vboot\_override\_pin(0x5E[3]), ton\_override\_pin(0x5E[4]), fccm\_override\_pin(0x5E[5]), fovp\_override\_pin(0x5E[6]), rovp\_override\_pin(0x5E[7]). The pinstrapping functionality is disabled on TDA38740A/25A-0000 parts and these parameters are set by PMBus commands. The TDA38740A/25A-0000 parts have VOUT\_COMMAND set to 0V and there will not be any output until the output is set to desired value. The pinstrapping functionality is enabled on TDA38740A-0020 and TDA38740A-0030 parts. Refer to Section 1 for custom part number information for Pin configurable and Register configurable parts.

The tables and descriptions below detail different parameters that can be set using pin strap resistor.

Table 7 MODE/TON Table

| Bin | MODE/TON (kΩ) | Freq (kHz) | MODE |

|-----|---------------|------------|------|

| 0   | SHORT         | 600        |      |

| 1   | 2.49          | 1000       |      |

| 2   | 3.24          | 1400       | FCCM |

| 3   | 4.02          | 2000       |      |

| 4   | 4.87          | 1200       |      |

| 5   | 5.76          | 1400       |      |

| 6   | 6.81          | 1800       |      |

| 7   | 7.87          | 2000       | DEM  |

| 8   | 9.09          | 400        | DEM  |

| 9   | 10.5          | 600        |      |

| 10  | 12.1          | 800        |      |

| 11  | 14            | 1000       |      |

| 12  | 15.8          | 400        |      |

| 13  | 17.8          | 1800       | FCCM |

| 14  | 20            | 1200       | FCCM |

| 15  | FLOAT         | 800        |      |

When operating in the pin strap resistor mode the switching frequency and the operating mode can be set by connecting a resistor from the MODE/TON pin to GND as per the table above. Switching frequency can be selected from 400 kHz to 2000 kHz in steps of 200 kHz except for 1600 kHz. Mode can be selected to operate the part in Forced Continous Conduction Mode (FCCM) mode or Diode Emulation Mode (DEM) mode.

#### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Pin Strap Resistors Application Information**

Table 8 TDA38740A/25A Boot Up Voltage and OVP Limits Table for VOUT\_SCALE\_LOOP 1:1.

|          |                     | <b>_</b> _            |               |

|----------|---------------------|-----------------------|---------------|

| VBT (kΩ) | BOOT-Up Voltage (V) | Relative OVP/UVP (mV) | Fixed OVP (V) |

| SHORT    | 0.4                 | 150                   | 0.8           |

| 5.62     | 0.5                 | 150                   | 1             |

| 9.53     | 0.6                 | 150                   | 1             |

| 14       | 0.7                 | 150                   | 1.2           |

| 21       | 0.8                 | 200                   | 1.2           |

| 30.1     | 0.90                | 200                   | 1.2           |

| 36.5     | 1                   | 200                   | 1.35          |

| 43.2     | 1.05                | 200                   | 1.35          |

| 51.1     | 1.1                 | 200                   | 1.35          |

| 61.9     | 1.2                 | 200                   | 1.5           |

| 75       | 1.25                | 250                   | 1.8           |

| 88.7     | 1.35                | 250                   | 1.8           |

| 105      | 1.5                 | 300                   | 2.2           |

| 127      | 1.65                | 300                   | 2.2           |

| 150      | 1.8                 | 300                   | 2.2           |

| FLOAT    | 2.5                 | 300                   | 2.85          |

|          |                     |                       |               |

Table 9 TDA38740A/25A Boot Up Voltage and OVP Limits Table for VOUT\_SCALE\_LOOP 1:2

|          | ,                   |                       | - · · · · · · · · · · · · · · · · · · · |

|----------|---------------------|-----------------------|-----------------------------------------|

| VBT (kΩ) | BOOT-Up Voltage (V) | Relative OVP/UVP (mV) | Fixed OVP (V)                           |

| SHORT    | 0.8                 | 200                   | 1.6                                     |

| 5.62     | 1.0                 | 200                   | 1.6                                     |

| 9.53     | 1.2                 | 200                   | 1.6                                     |

| 14       | 1.4                 | 300                   | 2.0                                     |

| 21       | 1.6                 | 300                   | 2.4                                     |

| 30.1     | 1.8                 | 300                   | 2.4                                     |

| 36.5     | 2.0                 | 300                   | 2.7                                     |

| 43.2     | 2.1                 | 300                   | 2.7                                     |

| 51.1     | 2.2                 | 300                   | 2.7                                     |

| 61.9     | 2.4                 | 300                   | 3.0                                     |

| 75       | 2.5                 | 300                   | 3.0                                     |

| 88.7     | 2.7                 | 300                   | 3.6                                     |

| 105      | 3.0                 | 300                   | 3.6                                     |

| 127      | 3.3                 | 300                   | 4.4                                     |

| 150      | 3.6                 | 300                   | 4.4                                     |

| FLOAT    | 5.0                 | 300                   | 5.7                                     |

When operating in the pin strap resistor mode, the output voltage can be selected by connecting a resistor from the VBT pin to GND per the table above. When oprating in pin strap mode for VBT, the PGOOD ON, PGOOD OFF and VOUT\_MAX track the VBT pin setting. PGOOD ON will be set to at 93.75% of VBT while PGOOD OFF will be set to 81.25% of VBT. VOUT\_MAX will be set to the Relative OVP setting of the VBT.

When setting the output voltage using VOUT\_COMMAND, the VOUT\_SCALE\_LOOP of 1:1 will provide a output voltage in the range of 0.25 V to 2.56 V. VOUT\_SCALE\_LOOP 1:2 will provide a output voltage range of 0.5V to 5.12 V. When operating in VOUT\_SCALE\_LOOP 1:1 mode the full output voltage should be fed back to the VOSENP pin as shown in Figure 3. When operating in VOUT\_SCALE\_LOOP 1:2 mode, half of the output voltage is fed back to the VOSENP Pin by using a resistor divider as shown in Figure 4. The VBT pin can be used to set the output voltages in the range of 0.4 V to 2.5 V in VOUT\_SCALE\_LOOP 1:1 and from 0.8 V to 5 V in VOUT\_SCALE\_LOOP 1:2.

## 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

**Pin Strap Resistors Application Information**

Table 10 TDA38740A OCP and Loop Compensation Filer Zero selection

| $R_{ILIM}(k\Omega)$ | Typical OCP(A) | Internal Loop-Compensation-Filter-<br>Zero Register (LCF), Note 16 | Default LCF zero capacitor value (pF) |

|---------------------|----------------|--------------------------------------------------------------------|---------------------------------------|

| SHORT               | 15             | LCF 0                                                              | 1                                     |

| 3.32                | 60             | LCF 4                                                              | 8                                     |

| 6.98                | 20             | LCF 2                                                              | 4                                     |

| 11                  | 10             | LCF 0                                                              | 1                                     |

| 15.4                | 15             | LCF 1                                                              | 2                                     |

| 21                  | 20             | LCF 1                                                              | 2                                     |

| 26.1                | 25             | LCF 2                                                              | 4                                     |

| 31.6                | 30             | LCF 2                                                              | 4                                     |

| 43.2                | 40             | LCF 3                                                              | 6                                     |

| 51.1                | 50             | LCF 4                                                              | 8                                     |

| 64.9                | 25             | LCF 1                                                              | 2                                     |

| 78.7                | 60             | LCF 3                                                              | 6                                     |

| 95.3                | 40             | LCF 2                                                              | 4                                     |

| 113                 | 50             | LCF 3                                                              | 6                                     |

| 133                 | 10             | LCF 1                                                              | 2                                     |

| FLOAT               | 30             | LCF 3                                                              | 6                                     |

Table 11 TDA38725A OCP and Internal Phase margin Zero selection

| $R_{\text{ILIM}}(k\Omega)$ | Typical OCP(A) | Internal Loop-Compensation-Filter-<br>Zero Register (LCF), Note 16 | Default LCF zero capacitor value (pF), Note 16 |

|----------------------------|----------------|--------------------------------------------------------------------|------------------------------------------------|

| SHORT                      | 15             | LCF 0                                                              | 1                                              |

| 3.32                       | 15             | LCF 4                                                              | 8                                              |

| 6.98                       | 20             | LCF 2                                                              | 4                                              |

| 11                         | 10             | LCF 0                                                              | 1                                              |

| 15.4                       | 15             | LCF 1                                                              | 2                                              |

| 21                         | 20             | LCF 1                                                              | 2                                              |

| 26.1                       | 25             | LCF 2                                                              | 4                                              |

| 31.6                       | 10             | LCF 2                                                              | 4                                              |

| 43.2                       | 15             | LCF 3                                                              | 6                                              |

| 51.1                       | 20             | LCF 4                                                              | 8                                              |

| 64.9                       | 25             | LCF 1                                                              | 2                                              |

| 78.7                       | 10             | LCF 3                                                              | 6                                              |

| 95.3                       | 15             | LCF 2                                                              | 4                                              |

| 113                        | 20             | LCF 3                                                              | 6                                              |

| 133                        | 10             | LCF 1                                                              | 2                                              |

| FLOAT                      | 25             | LCF 3                                                              | 6                                              |

#### 40A/25A Single-voltage Synchronous Buck Regulator with PMBus

#### **Pin Strap Resistors Application Information**

When operating in the pin strap resistor mode, the OCP limit can be selected by connecting a resistor from the ILIM pin to GND as per the table above. Loop Compensation Filter (LCF) Zero selection is also available on ILIM pin, however it does not affect the OCP operation and is part of the control loop tuning. This capacitance is built in within the IC and can be selected between 1pF and 8pF by appropriate selection of the ILIM resistor. This provides some flexibility to set the Loop Compensation Filter Zero using ILIM pin strap resistors. However, default selection of the capacitance value is limited and does not allow selection of all 8 possible capacitance values from 1pF to 8pF. If the desired performance could not be achieved with default LCF zero values available through the ILIM pin, the capacitance value can be selected from 1pF to 8pF in increments of 1pF through the register loop\_compensation\_filter\_zero\_0, 0x64[14:12] through PMBus. Please refer to the App note AN\_2311\_PL12\_2312\_233004 for more details on this register.

#### Note:

16. The default LCF value can be changed using Registers 0x64[14:12], 0x62[2:0], 0x62[6:4], 0x62[10:8], 0x62[14:12] for LCF 0, LCF 1, LCF 2, LCF 3, LCF 4 respectively

Table 12 SM\_ADDR/PROG Pin with the consecutive images starting from Config 0 at location 0

| Tuble 12 Jin_NB II() NOO! III With the consecutive images starting from coming out totalion o |                             |                                 |                            |                                       |  |

|-----------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|----------------------------|---------------------------------------|--|

| Resistor to GND                                                                               | SM_ADDR<br>function: Offset | PROG function: Config selection | PROG pin: Config selection | Programmability for single and multi- |  |

| (kΩ)                                                                                          | selection from the          | (For single -image              | (For Multi-image           | image config file                     |  |

|                                                                                               | base address                | Config)                         | Config)                    |                                       |  |