# RIC70847 - Rad hard 17.1 V buck controller with integrated gate drivers

### **Features**

- Wide input voltage range

- Accurate voltage reference over temperature and radiation

- Improved transient response with optional load line regulation

- Fixed frequency peak current mode control

- Wide programmable switching frequency enables optimization between solution size and performance

- Small minimum on time enables high step-down voltage ratio

- Integrated half bridge gate driver

- Integrated fault protections

- Integrated programmable soft start

- Radiation tolerance

- o High dose rate (50-300 rad(Si)/s) to 150 krad(Si) for 100 krad(Si) rating)

- Single event effect (SEE) hardness

- o No SEB or SEL up to LET of 81.9 MeV⋅cm²/mg

- o SET characterized up to LET of 81.9 MeV·cm²/mg

- Electrically screened and qualified to MIL-PRF-38535, Class V (DLA certification pending)

## **Product Summary**

- V<sub>IN</sub> (abs max) = 17.1 V

- $V_{OUT} = 0.6 \text{ V to } 5.25 \text{ V}$

- V<sub>REF</sub> + V<sub>OSEA</sub> = 600 mV ±1%

- f<sub>sw</sub> = 100 kHz to 2 MHz

- t<sub>minon</sub> (abs max) = 27 ns

# **Package**

24 pin flatpack

# **Potential applications**

- PoL converter for space grade FPGA, ASIC and DSP core rails

- Digital processing payload systems

- Distributed satellite power systems

# **Ordering information**

Table 1 Ordering information

| Orderable part number | Package type     | Device level         | Total ionizing dose level |

|-----------------------|------------------|----------------------|---------------------------|

| 5962R2320601VXA       | 24-lead flatpack | Level V <sup>1</sup> | 100 krad(Si)              |

| RIC70847F             | 24-lead flatpack | COTS <sup>2</sup>    |                           |

<sup>&</sup>lt;sup>1</sup> Per MIL-PRF-38535 (DLA certification pending)

<sup>&</sup>lt;sup>2</sup> Intended for engineering evaluation only, devices are only electrically tested at 25°C and for hermeticity

**Description**

# **Description**

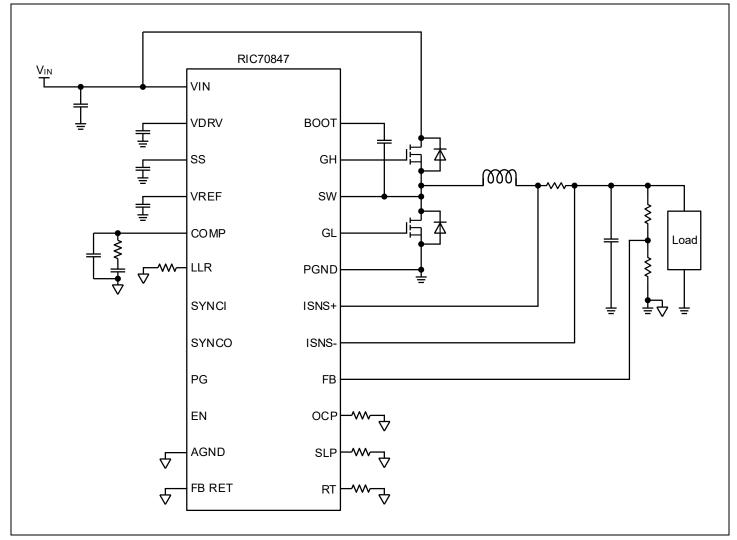

RIC70847 is a radiation hardened synchronous buck controller with integrated gate drivers. It is intended for harsh radiation environments such as space, with electrical parameters specified pre and post-irradiation up to 100 krad(Si) and single effect effects (SEE) characterized up to a linear energy transfer (LET) of 81.9 MeV·cm²/mg. RIC70847 is available in a hermetically sealed 24-lead flatpack and operates over the full military ambient temperature range of -55°C to 125°C.

The integrated half-bridge gate driver has a 5 V drive voltage and is intended to work with logic level FETs, such as IR HiRel R8 rad hard power FETs. RIC70847 supports a wide input voltage range including nominal inputs of 5 V and 12 V, and the output voltage can support from 0.6 V up to 5 V. This makes RIC70847 ideal for point of load (PoL) applications such as core rails of space rated FPGA and ASIC.

RIC70847 uses a fixed switching frequency peak current mode control algorithm. Externally adjustable slope compensation ensures stable operation over a wide range of conditions. The switching frequency is programmable from 100 kHz to 2 MHz with a single resistor, or it can be synchronized to an external clock or another RIC70847 for multiphase operation. It includes multiple integrated fault protections for increased reliability. It also has optional load-line regulation (also referred to as adaptive voltage positioning (AVP) or droop regulation), where the output voltage is dynamically adjusted based on the load current. This provides a system benefit of significantly reducing output capacitance.

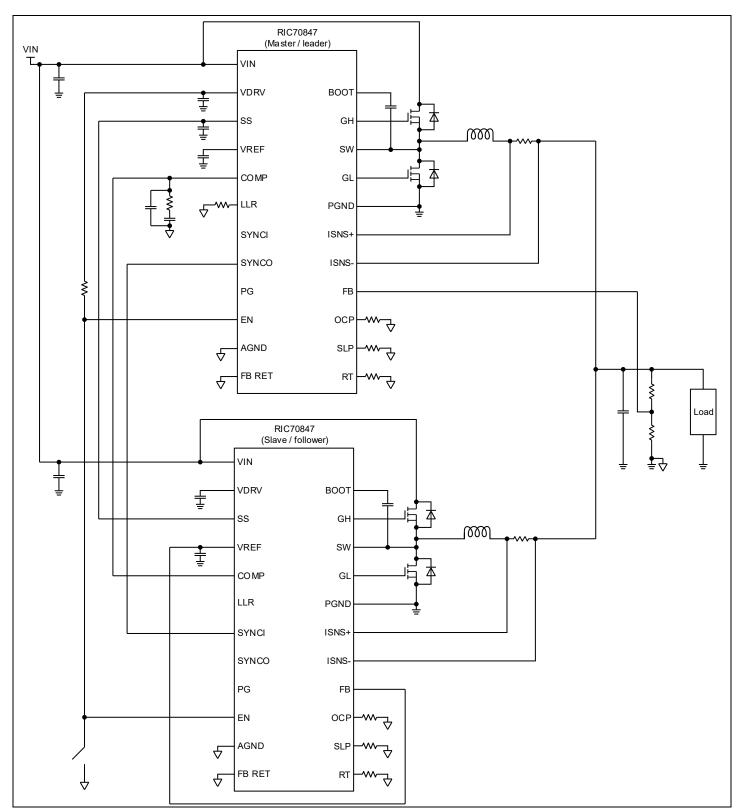

Figure 1 Typical PoL application block diagram

# Table of contents

# **Table of contents**

| Feati           | tures                                   | , 1 |

|-----------------|-----------------------------------------|-----|

| Prod            | duct Summary                            | 1   |

| Pack            | kage                                    | 1   |

| Pote            | ential applications                     | 1   |

| Orde            | ering information                       |     |

|                 | cription                                |     |

|                 | le of contents                          |     |

| 1               | Block diagram                           |     |

|                 | •                                       |     |

| <b>2</b><br>2.1 | Pin configuration                       |     |

| 2.1             | Pin configuration<br>Pin functionality  |     |

|                 | •                                       |     |

| <b>3</b><br>3.1 | Electrical parameters                   |     |

| 3.2             | Absolute maximum ratings<br>ESD ratings |     |

| 3.3             | Thermal characteristics                 |     |

| 3.4             | Recommended operating conditions        |     |

| 3.5             | Electrical characteristics              |     |

| 4               | Typical characteristics                 |     |

|                 | General description                     |     |

| <b>5</b><br>5.1 | Radiation performance                   |     |

| 5.1.1           | ·                                       |     |

| 5.1.2           |                                         |     |

| 5.2             | Input power and bias                    |     |

| 5.2.1           | ·                                       |     |

| 5.2.2           | , , , , , , , , , , , , , , , , , , ,   |     |

| 5.2.3           | -                                       |     |

| 5.3             | Return pins                             |     |

| 5.4             | Gate drive                              |     |

| 5.5             | Switching frequency                     |     |

| 5.5.1           |                                         |     |

| 5.5.2           |                                         |     |

| 5.5.3           |                                         |     |

| 5.6             | Control                                 |     |

| 5.6.1           | 1 Current sense amplifier               | 25  |

| 5.6.1.          | ·                                       |     |

| 5.6.1.          | 1.2 Current sense resistor              | 25  |

| 5.6.1.          | 1.3 Inductor DCR current sensing        | 26  |

| 5.6.2           | Slope compensation                      | 27  |

| 5.7             | Feedback                                | 28  |

| 5.7.1           | 1 Reference voltage                     | 28  |

| 5.7.2           | 2 Compensation                          | 28  |

| 5.8             | Soft start                              | 28  |

| 5.9             | Load-line regulation                    | 29  |

| 5.10            | ·                                       |     |

| 5.10.           | · ·                                     |     |

| 5.10.           | .1.1 OCP with current sense resistor    | 32  |

| Datasł          | sheet 3                                 |     |

# Rad hard 17.1 V buck controller with integrated gate drivers

# Table of contents

| 5.10.1.2 | OCP with DCR sensing                          | 32 |

|----------|-----------------------------------------------|----|

| 5.11     | Power good                                    | 33 |

| 5.12     | Enable                                        | 33 |

| 6 Ар     | oplication information and additional details | 34 |

| 6.1.1    | Two phase operation                           | 34 |

| 6.2      | Power sequencing                              | 35 |

| 6.3      | Recommended layout                            | 36 |

| 7 Pa     | ackage details                                |    |

| 7.1      | <b>G</b>                                      |    |

| Revision | n history                                     | 39 |

|          | ces                                           |    |

**Block diagram**

# 1 Block diagram

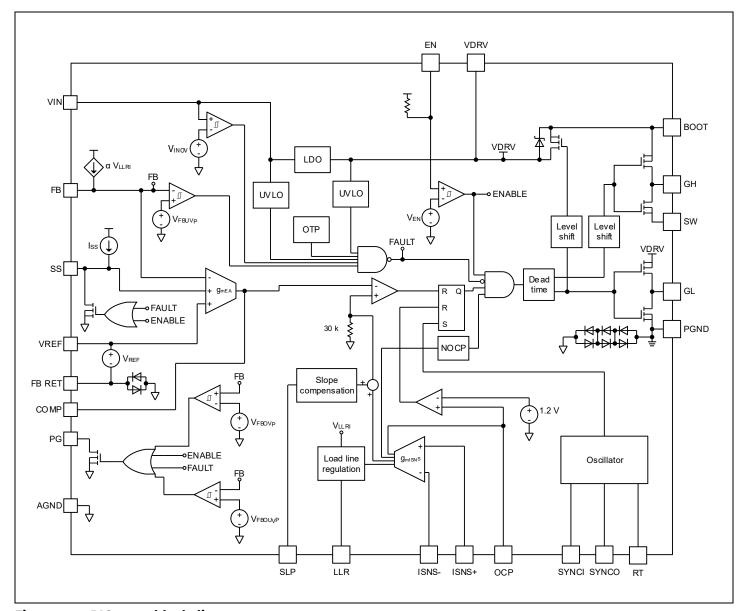

Figure 2 RIC70847 block diagram

**Pin configuration and functionality**

# 2 Pin configuration and functionality

# 2.1 Pin configuration

| 1  | SYNCI E          | N 24  |

|----|------------------|-------|

| 2  | RT P             | G 23  |

| 3  | SYNCO PGN        | ID 22 |

| 4  | ISNS+ VDR        | 21    |

| 5  | ISNS- PGN        | 20    |

| 6  | AGND G           | SL 19 |

| 7  | FB RET BOO       | DT 18 |

| 8  | VREF SV          | W 17  |

| 9  | FB G             | 16    |

| 10 | COMP VI          | IN 15 |

| 11 | SLP OC           | P 14  |

| 12 | SS LL            | R 13  |

|    | 24 lead flatpack |       |

Figure 3 RIC70847 pin assignments (top view)

# 2.2 Pin functionality

Table 2 Pin functionality

| Pin    | Symbol | Description                                                                                                                            |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SYNCI  | Input for external clock. Clock on this pin will determine switching frequency if higher than frequency set on RT.                     |

| 2      | RT     | Switching frequency selection. Connect a resistor from this pin to FB RET to set the switching frequency when in standalone operation. |

| 3      | SYNCO  | Output of external clock for synchronization.                                                                                          |

| 4      | ISNS+  | Positive input pin for inductor current sensing                                                                                        |

| 5      | ISNS-  | Negative input pin for inductor current sensing                                                                                        |

| 6, Lid | AGND   | Analog ground. Logic signals are referenced to this pin.                                                                               |

| 7      | FB RET | Feedback return ground. Feedback signals are referenced to this pin.                                                                   |

| 8      | VREF   | Output of internal 600 mV reference voltage. A ceramic capacitor is recommended between this pin and FB RET.                           |

| 9      | FB     | Feedback pin for output voltage sensing                                                                                                |

| 10     | COMP   | Output of internal transconductance error amplifier. Connect compensation network from this pin to AGND.                               |

# Rad hard 17.1 V buck controller with integrated gate drivers

Pin configuration and functionality

| Pin    | Symbol | Description                                                                                                                                                                                                                                       |

|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11     | SLP    | Slope compensation pin. Connect a resistor from this pin to FB RET to set slope compensation ramp.                                                                                                                                                |

| 12     | SS     | Soft start pin. A capacitor connected from this pin to FB RET sets the soft start ramp time.                                                                                                                                                      |

| 13     | LLR    | Load line regulation. To enable load line regulation, connect a resistor from this pin to AGND. For no load line regulation leave the pin unconnected.                                                                                            |

| 14     | ОСР    | Over current protection. Connect a resistor from this pin to FB RET to set overcurrent, short circuit and negative current protection threshold. This pin can additionally be used as an output for the sensed inductor current (ISNS+ to ISNS-). |

| 15     | VIN    | Input for internal LDO. A ceramic capacitor is recommended between this pin and PGND.                                                                                                                                                             |

| 16     | GH     | High side FET gate driver output                                                                                                                                                                                                                  |

| 17     | SW     | Switch node. Connect the high side FET source, low side FET drain and output inductor to this pin.                                                                                                                                                |

| 18     | воот   | Bootstrap supply for the high side FET gate driver. A ceramic capacitor is required between this pin and SW.                                                                                                                                      |

| 19     | GL     | Low side FET gate driver output                                                                                                                                                                                                                   |

| 20, 22 | PGND   | Power ground. Connect to the source of the low side FET and negative terminal of input and output capacitors.                                                                                                                                     |

| 21     | VDRV   | Output of 5V internal LDO. A ceramic capacitor of at least 1 $\mu\text{F}$ is required between VDRV and PGND                                                                                                                                      |

| 23     | PG     | Open drain power good signal. pulled low when fault triggers, EN is pulled low or output voltage is outside regulation window                                                                                                                     |

| 24     | EN     | Enable. Forcing low disables PWM on GH and GL and holds both driver outputs low.                                                                                                                                                                  |

# Rad hard 17.1 V buck controller with integrated gate drivers

**Electrical parameters**

# 3 Electrical parameters

# 3.1 Absolute maximum ratings

Absolute maximum ratings indicate limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to AGND unless otherwise stated in the table.

Table 3 Absolute maximum ratings

| Symbol          | Definition                                                           | Min  | Max      | Units |

|-----------------|----------------------------------------------------------------------|------|----------|-------|

| V <sub>IN</sub> | VIN                                                                  | -0.3 | 17.1     | V     |

| $V_{DRV}$       | VDRV to PGND                                                         | -0.3 | 6.5      | V     |

| воот            | BOOT to SW                                                           | -0.3 | 6.5      | V     |

|                 | SW to PGND (DC)                                                      | -1.3 | 17.1     | V     |

| SW              | SW to PGND (Pulse width < 20 ns)                                     | -2.5 |          | V     |

|                 | SW to PGND (Pulse width < 10 ns)                                     | -6.0 |          | V     |

|                 | GH to SW (DC)                                                        | -0.3 | VDRV+0.3 | V     |

| $G_{H}$         | GH to SW (Pulse width < 20 ns)                                       | -1.0 |          | V     |

|                 | GH to SW (Pulse width < 10 ns)                                       | -4.0 |          | V     |

|                 | GL to PGND (DC)                                                      | -0.3 | VDRV+0.3 | V     |

| $G_{L}$         | GL to PGND (Pulse width < 20 ns)                                     | -1.0 |          | V     |

|                 | GL to PGND (Pulse width < 10 ns)                                     | -4.0 |          | V     |

| $V_{EN}$        | EN                                                                   | -0.3 | 17.1     | V     |

| IN              | SYNCI, PG                                                            | -0.3 | 6.5      | V     |

| ISNS            | ISNS-, ISNS+ (DC)                                                    | -0.3 | 6.5      | V     |

| 121/12          | ISNS-, ISNS+ (Pulse width < 20 ns)                                   | -1.0 |          | V     |

| LGC             | SLP, RT, SYNCO, OCP, LLR, COMP, VREF, SS, FB                         | -0.3 | 3.6      | V     |

| LGC             | SLP, RT, SYNCO, OCP, LLR, COMP, VREF, SS, FB (LET ≤ 81.9 MeV·cm²/mg) | -0.3 | 3.1      | V     |

| CND             | FB RET to AGND (DC)                                                  | -0.3 | 0.3      | V     |

| $GND_A$         | FB RET to AGND (Pulse width < 20 ns)                                 | -0.5 | 0.5      | V     |

| CND             | PGND to AGND (DC)                                                    | -0.9 | 0.9      | V     |

| GND₽            | PGND to AGND (Pulse width < 20 ns)                                   | -3.0 | 3.0      | V     |

| TJ              | Operating junction temperature                                       | -55  | 150      | °C    |

| Ts              | Storage temperature                                                  | -65  | 150      | °C    |

| TL              | Lead temp (soldering, 10s, 0.063 in (1.6 mm) from case)              |      | 300      | °C    |

### Rad hard 17.1 V buck controller with integrated gate drivers

**Electrical parameters**

# 3.2 ESD ratings

### Table 4 ESD ratings

| Symbol              | Definition                                                                     | Value | Units |

|---------------------|--------------------------------------------------------------------------------|-------|-------|

| $V_{ESDHBM}$        | ESD Human Body Model (HBM), Class 3A per MIL-STD-883, Method 3015 <sup>1</sup> | 4     | kV    |

| V <sub>ESDCDM</sub> | ESD Charged device model (CDM) <sup>2</sup>                                    | 1     | kV    |

<sup>&</sup>lt;sup>1</sup> Per ANSI/ESDA/ JEDEC JS-001

### 3.3 Thermal characteristics

All ratings are specified under board mounted and still air conditions.

Table 5 Thermal characteristics

| Symbol          | Definition                              | Min | Тур | Max | Units |

|-----------------|-----------------------------------------|-----|-----|-----|-------|

| $R_{\Theta JC}$ | Thermal resistance, junction to case    |     | 1.7 |     | °C/W  |

| $R_{\Theta JA}$ | Thermal resistance, junction to ambient |     | 27  |     | °C/W  |

# 3.4 Recommended operating conditions

For proper operation the device should be used within the recommended operating conditions. All voltage parameters are absolute voltages referenced to AGND unless otherwise stated.

Table 6 Recommended operating conditions

| Symbol           | Definition                                           | Min  | Max   | Units |

|------------------|------------------------------------------------------|------|-------|-------|

| $V_{\text{IN}}$  | VIN bias voltage <sup>1</sup>                        | 4.75 | 13.2  | V     |

| $V_{DRV}$        | External voltage on VDRV pin (VIN=VDRV) <sup>1</sup> | 4.6  | 5.25  | V     |

| V <sub>OUT</sub> | Output voltage                                       | 0.6  | 5.25  | V     |

| $f_{SW}$         | Switching frequency (RT or SYNCI)                    | 100  | 2,000 | kHz   |

| T <sub>A</sub>   | Operating ambient temperature                        | -55  | 125   | °C    |

<sup>&</sup>lt;sup>1</sup> When voltage on VIN is less than 5.25 V, internal LDO in RIC70847 is in dropout which may cause VDRV voltage to drop too low under some operating conditions. When operating with low voltage input it is recommended to short VDRV to VIN pin.

<sup>&</sup>lt;sup>2</sup> Per ANSI/ESDA/JEDEC JS-002

## Rad hard 17.1 V buck controller with integrated gate drivers

**Electrical parameters**

## 3.5 Electrical characteristics

VIN = 4.75 V to 13.2 V and  $T_A = T_J = -55$  to 125°C unless otherwise stated. Logic pins (EN, SLP, RT, SYNCO, SYNCI, ISNS-, ISNS+, OCP, LLR, PG, COMP, VREF, SS, FB) are with respect to AGND = FB RET, power pins (VIN, VDRV, GL) are with respect to PGND and bootstrap pins (BOOT, GH) are with respect to SW. **All parameter ratings apply over a total ionizing dose (TID) of 100 krad(Si) with exposure at a high dose rate (HDR) of 50-300 rad(Si)/s**

**Table 7 Electrical characteristics**

| Symbol             | Definition                                                   | Min  | Тур  | Max  | Units | <b>Test Conditions</b>                        |

|--------------------|--------------------------------------------------------------|------|------|------|-------|-----------------------------------------------|

| Bias input pov     | wer                                                          |      |      |      |       |                                               |

| I <sub>INQNL</sub> | VIN operating current unloaded (500 kHz switching frequency) | 5    | 7    | 9    | mA    | EN=5 V,<br>RT=28.6kΩ, No<br>load on GL and GH |

| I <sub>INSD</sub>  | VIN standby current                                          | 2    | 4    | 7    | mA    | EN=0 V                                        |

| $V_{\text{INOV+}}$ | Input overvoltage shutdown rising                            | 15.5 | 16.6 | 17.1 | V     |                                               |

| $V_{INOV}$         | Input overvoltage shutdown falling                           | 15.2 | 16.2 | 17.1 | V     |                                               |

| V <sub>INOVH</sub> | Input OVP hysteresis                                         |      | 0.4  |      | V     |                                               |

| $V_{INUV}$         | VIN UVLO rising threshold                                    | 4.2  | 4.4  | 4.6  | V     |                                               |

| $V_{INUV}$         | VIN UVLO falling threshold                                   | 4.1  | 4.3  | 4.5  | V     |                                               |

| V <sub>INUVH</sub> | VIN UVLO hysteresis                                          |      | 100  |      | mV    |                                               |

| inear dropou       | it regulator (LDO)                                           |      |      |      |       |                                               |

| $V_{DRV}$          | VDRV voltage from LDO                                        | 4.7  | 5    | 5.3  | V     | VIN=9 V                                       |

| $V_{DRVD}$         | Dropout voltage (VIN-VDRV)                                   | 5    | 13   | 20   | mV    | VIN=4.5 V                                     |

|                    | Command limit from VDDV air                                  | 130  | 148  | 280  | mA    | EN=0 V, VIN=4.75                              |

| $I_{DRV}$          | Current limit from VDRV pin                                  | 170  | 203  | 310  | mA    | EN=0 V, VIN=13.2 V                            |

| $V_{DRVUV}$        | VDRV UVLO rising threshold                                   | 3.25 | 3.55 | 3.85 | V     |                                               |

| $V_{DRVUV}$        | VDRV UVLO falling threshold                                  | 3.0  |      | 3.65 | V     |                                               |

| $V_{DRVUVH}$       | VDRV UVLO hysteresis                                         |      | 130  |      | mV    |                                               |

| Driver             |                                                              |      |      |      |       |                                               |

| $V_{OHGH}$         | GH high output drive                                         | 4.95 |      |      | V     | I <sub>GH</sub> =20 mA,<br>BOOT=5 V           |

| $V_{OHGL}$         | GL high output drive                                         | 4.95 |      |      | V     | I <sub>GL</sub> =20 mA,<br>VDRV=5 V           |

| $V_{OLGH}$         | GH low output drive                                          |      |      | 0.05 | V     | I <sub>GH</sub> =20 mA,<br>BOOT=5 V           |

| $V_{OLGL}$         | GL low output drive                                          |      |      | 0.05 | V     | I <sub>GL</sub> =20 mA,<br>VDRV=5 V           |

| $R_{GHH}$          | GH turn on resistance                                        | 0.9  | 1.4  | 1.9  | Ω     | I <sub>GL</sub> =20 mA                        |

| $R_{GHL}$          | GH turn off resistance                                       | 0.6  | 1.0  | 1.5  | Ω     | I <sub>GL</sub> =20 mA                        |

| $R_{GLH}$          | GL turn on resistance                                        | 0.7  | 1.1  | 1.6  | Ω     | I <sub>GL</sub> =20 mA                        |

| $R_{GLL}$          | GL turn off resistance                                       | 0.7  | 1.0  | 1.6  | Ω     | I <sub>GL</sub> = 20 mA                       |

# Rad hard 17.1 V buck controller with integrated gate drivers

# **Electrical parameters**

| Symbol                         | Definition                                                             | Min  | Тур                 | Max  | Units | Test Conditions                      |

|--------------------------------|------------------------------------------------------------------------|------|---------------------|------|-------|--------------------------------------|

| $I_{GHH}$                      | GH turn on peak current <sup>1</sup>                                   |      | 2                   |      | Α     |                                      |

| $I_{GHL}$                      | GH turn off peak current <sup>1</sup>                                  |      | 2                   |      | Α     |                                      |

| I <sub>GLH</sub>               | GL turn on peak current <sup>1</sup>                                   |      | 2                   |      | Α     |                                      |

| I <sub>GLL</sub>               | GL turn off peak current <sup>1</sup>                                  |      | 2                   |      | Α     |                                      |

| $t_{minonGH}$                  | Minimum on time GH                                                     |      | 24                  | 27   | ns    |                                      |

| $t_{minonGL}$                  | Minimum on time GL                                                     |      | 24.5                | 30   | ns    |                                      |

| t <sub>dt</sub>                | Dead time <sup>1</sup>                                                 |      |                     | 15   | ns    |                                      |

| Oscillator                     |                                                                        | •    | 1                   | •    |       |                                      |

|                                |                                                                        | 450  | 500                 | 550  | kHz   | RT = 28.6 kΩ                         |

| $f_{RT}$                       | Internal oscillator frequency                                          | 900  | 1000                | 1100 | kHz   | RT = 13.7 kΩ                         |

| $V_{SYNCI}$                    | SYNCI input threshold (rising edge)                                    | 0.8  | 0.9                 | 1.0  | V     |                                      |

| t <sub>syncion</sub>           | SYNCI input minimum on and off pulse width <sup>1</sup>                |      |                     | 100  | ns    |                                      |

| I <sub>SYNCI</sub>             | SYNCI input current                                                    | -70  |                     | 60   | μΑ    | V <sub>SYNCI</sub> = 0 V or 5 V      |

| V <sub>SYNCOH</sub>            | SYNCO voltage, logic high                                              | 2.7  | 2.9                 | 3.1  | V     |                                      |

| V <sub>SYNCOL</sub>            | SYNCO voltage, logic low                                               |      |                     | 0.1  | V     |                                      |

| P <sub>SYNCO</sub>             | SYNCO phase delay (GH to SYNCO) <sup>1</sup>                           |      | 0.5/f <sub>RT</sub> |      | o     | 180° phase shift                     |

| Feedback and                   | error amplifier                                                        |      | 1                   |      |       |                                      |

| $V_{FB}$                       | Reference voltage (V <sub>REF</sub> ) + EA offset (V <sub>OSEA</sub> ) | 594  | 600                 | 606  | mV    |                                      |

| $V_{REF}$                      | Reference voltage                                                      | 594  | 600                 | 606  | mV    |                                      |

| I <sub>FB</sub>                | FB input leakage current                                               | -1   |                     | 1    | μΑ    | V <sub>FB</sub> = 600 mV, LLR = open |

| $V_{FBOVP}$                    | FB pin overvoltage protection                                          | 0.64 | 0.66                | 0.69 | ٧     |                                      |

| $V_{FBUVP}$                    | FB pin undervoltage protection                                         | 0.51 | 0.54                | 0.57 | V     |                                      |

| $t_{\scriptscriptstyleVFBUVP}$ | FB pin undervoltage propagation delay                                  | 0.3  | 0.5                 | 0.7  | μs    |                                      |

| $A_{EA}$                       | EA DC gain <sup>1</sup>                                                |      | 126                 |      | dB    |                                      |

| <b>g</b> <sub>mEA</sub>        | EA transconductance                                                    | 0.6  | 1                   | 1.6  | mS    |                                      |

| V <sub>OSEA</sub>              | EA offset voltage                                                      | -6   |                     | 6    | mV    |                                      |

| $G_{BWEA}$                     | EA gain bandwidth product <sup>1</sup>                                 |      | 155                 |      | MHz   |                                      |

| Soft start                     |                                                                        |      |                     |      |       |                                      |

| I <sub>SS</sub>                | Soft start current source                                              | 7.5  | 10                  | 12.5 | μΑ    |                                      |

| Current sense                  |                                                                        |      |                     |      |       |                                      |

| A <sub>ISNS</sub>              | Current sense amplifier DC gain                                        | 9.5  | 10                  | 10.5 | V/V   | ISNS+ to ISNS-<br>= ±5mV             |

# Rad hard 17.1 V buck controller with integrated gate drivers

# **Electrical parameters**

| Symbol             | Definition                                                  | Min   | Тур   | Max   | Units | <b>Test Conditions</b>                                          |  |

|--------------------|-------------------------------------------------------------|-------|-------|-------|-------|-----------------------------------------------------------------|--|

| $g_{mISNS}$        | Current sense amplifier transconductance                    | 280   | 333   | 380   | μS    | Measured on OCP pin                                             |  |

| $G_{BWISNS}$       | Current sense amplifier gain bandwidth product <sup>1</sup> |       | 30    |       | MHz   |                                                                 |  |

| I <sub>ISNS</sub>  | ISNS+ and ISNS- leakage current                             |       |       | 20    | μΑ    | ISNS+ = 0.6 V, 3.6 V,<br>ISNS- = 0.6 V, 3.6 V                   |  |

| V <sub>OCP</sub>   | Overcurrent threshold                                       | 1.195 | 1.215 | 1.235 | V     |                                                                 |  |

| M                  | No gotive every wreat threehold                             | -40   | -20   | -13   | mV    | Pre-irradiation                                                 |  |

| $V_{NOCP}$         | Negative overcurrent threshold                              | -40   | -20   | -10   | mV    | Post-irradiation                                                |  |

| t <sub>ocp</sub>   | Overcurrent threshold propagation delay                     | 0.2   | 0.4   | 0.5   | μs    | ISNS+ to ISNS- = 20mV                                           |  |

| Load line regu     | ılation                                                     |       |       |       |       |                                                                 |  |

| I <sub>LLRIN</sub> | Load line regulation current source from FB pin no load     | -0.01 | 0.01  |       | μΑ    | $R_{LLR} = 7.15 \text{ k}\Omega$ , ISNS+ to ISNS- = 0 mV        |  |

| $I_LLRL$           | Load line regulation current source from FB pin, with load  | -1.7  | -1.1  | -0.5  | μΑ    | $R_{LLR} = 7.15 \text{ k}\Omega$ ,<br>ISNS+ to ISNS-<br>= 20 mV |  |

| I <sub>LLRM</sub>  | Load line regulation current source maximum <sup>1</sup>    |       | 10    |       | μΑ    |                                                                 |  |

| $BW_LLR$           | LLR bandwidth¹                                              |       | 250   |       | kHz   |                                                                 |  |

| Enable             |                                                             |       |       |       |       |                                                                 |  |

| $V_{EN^+}$         | EN rising threshold                                         | 0.86  | 0.92  | 0.98  | V     |                                                                 |  |

| $V_{EN	ext{-}}$    | EN falling threshold                                        | 0.69  | 0.77  | 0.85  | V     |                                                                 |  |

| $V_{ENHYS}$        | EN pin hysteresis                                           |       | 200   |       | mV    |                                                                 |  |

| I <sub>EN</sub>    | EN pin leakage current                                      | -100  |       | 100   | nA    | EN = 0 V and 5 V                                                |  |

| Power good         |                                                             |       |       |       |       |                                                                 |  |

| $V_{PGOV}$         | V <sub>PG</sub> high limit for PG                           | 0.63  | 0.66  | 0.7   | V     |                                                                 |  |

| $V_{PGOVH}$        | V <sub>PG</sub> high limit hysteresis                       |       | 21    | mV    |       |                                                                 |  |

| $V_{PGUV}$         | V <sub>PG</sub> low limit for PG                            | 0.51  | 0.54  | 0.57  | V     |                                                                 |  |

| $V_{PGUVH}$        | V <sub>PG</sub> low limit hysteresis                        |       | 31    |       | mV    |                                                                 |  |

| $V_{PGL}$          | PG low output                                               | 0.1   | 0.25  | 0.4   | V     | I <sub>PGOUT</sub> = 2 mA                                       |  |

| $I_{PG}$           | PG active source current limit <sup>1</sup>                 |       |       | 4     | mA    |                                                                 |  |

| I <sub>PGLK</sub>  | PG high leakage current                                     |       |       | 100   | nA    |                                                                 |  |

| Overtemperat       | ture                                                        |       |       |       |       |                                                                 |  |

| $T_{SD}$           | Overtemperature shutdown <sup>1</sup>                       | 155   |       |       | °C    |                                                                 |  |

| $T_{HYS}$          | Overtemperature hysteresis <sup>1</sup>                     |       | 25    |       | °C    |                                                                 |  |

|                    |                                                             |       |       |       |       |                                                                 |  |

$<sup>^{1}</sup>$  Parameter not subject to production test. Parameter guaranteed by design and characterization.

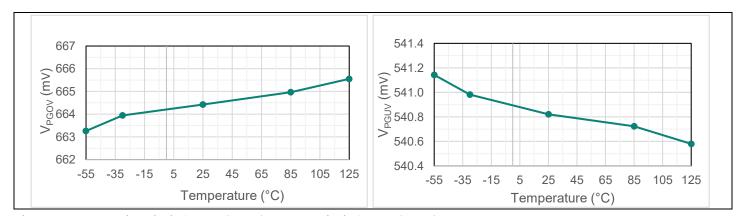

**Typical characteristics**

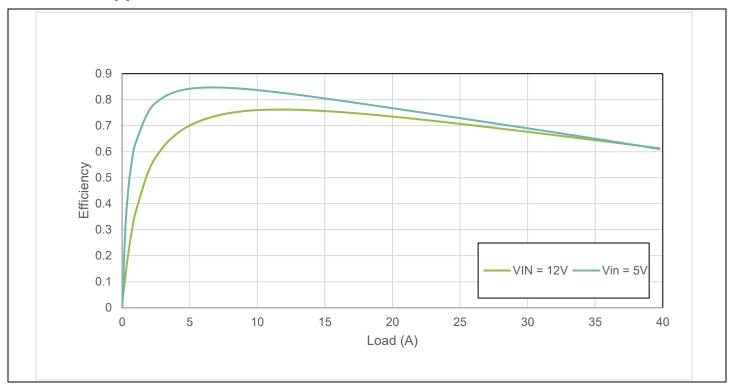

Figure 4 Efficiency over load at 500 kHz and  $V_{OUT}$ =1 V at  $V_{IN}$ =5 V and  $V_{IN}$ =12 V, L=270 nH, Cout=11,268  $\mu$ F

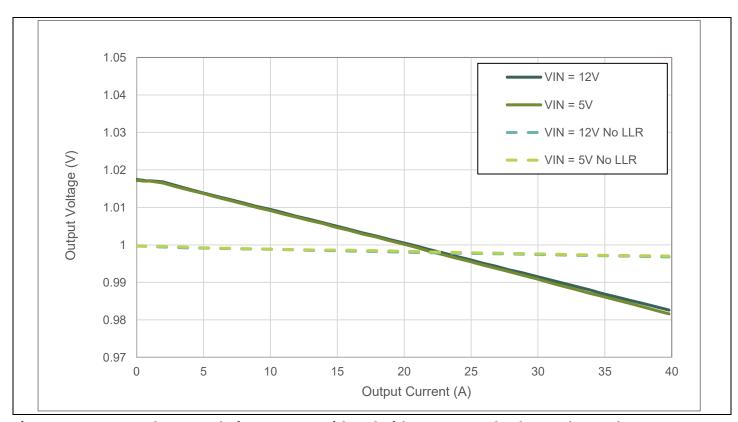

Figure 5 Output voltage regulation accuracy with and without LLR over load at 500 kHz and  $V_{\text{OUT}}$ =1.0 V at  $V_{\text{IN}}$ =5 V and  $V_{\text{IN}}$ =12 V, L=270 nH, Cout=11,268  $\mu\text{F}$

# Rad hard 17.1 V buck controller with integrated gate drivers

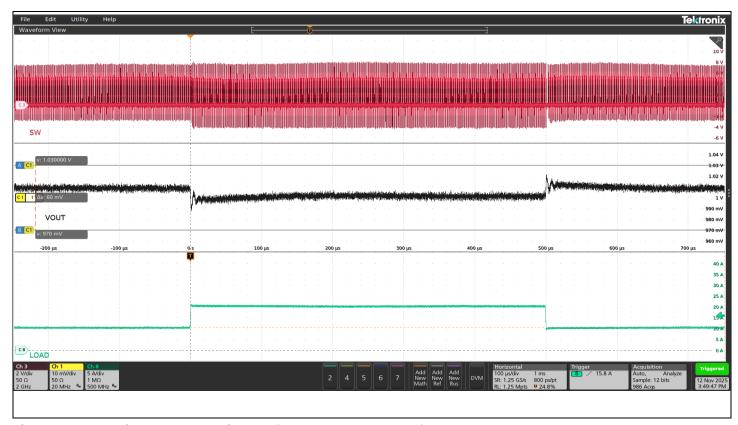

Figure 6 Transient response with LLR (10 A to 20 A at 10 A/μs)

Figure 7 Transient response with LLR (30 A to 40 A at 10 A/μs)

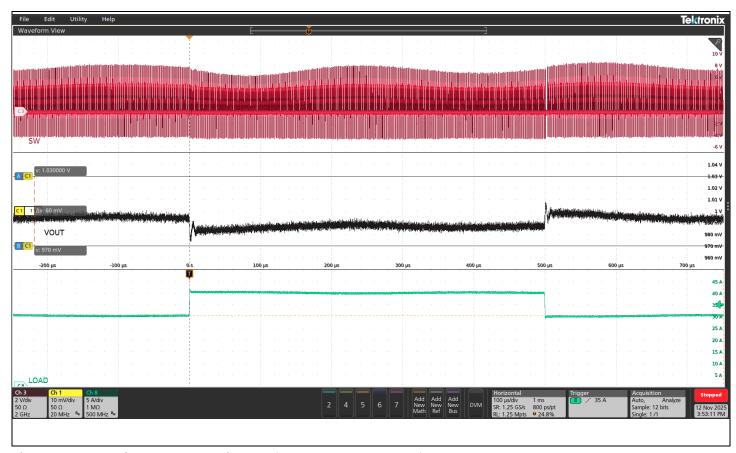

Figure 8 VIN standby current (I<sub>INSD</sub>) and VIN operating current at 500 kHz unloaded (I<sub>INQNL</sub>) over temperature

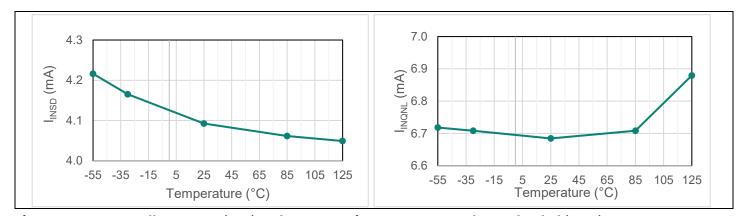

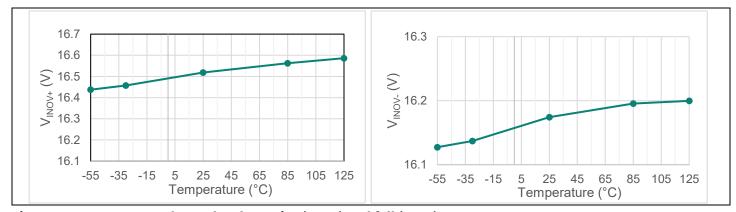

Figure 9 Input overvoltage shutdown rise (V<sub>INOV+</sub>) and fall (V<sub>INOV-</sub>) over temperature

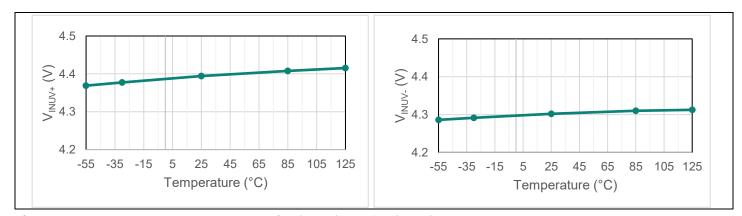

Figure 10 Input undervoltage lockout rise (VINUV+) and fall (VINUV-) over temperature

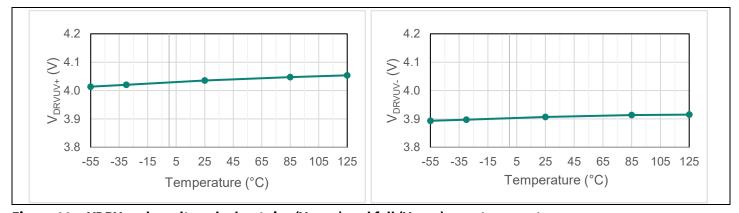

Figure 11 VDRV undervoltage lockout rise (VDRVUV+) and fall (VDRVUV-) over temperature

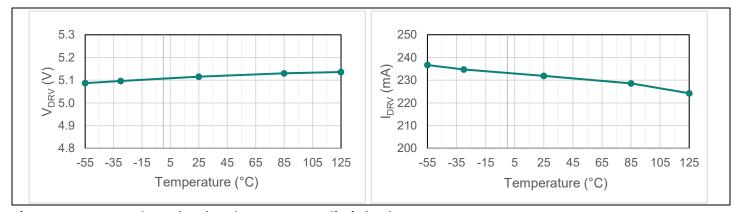

Figure 12 VDRV voltage (VDRV) and VDRV current limit (IDRV) over temperature

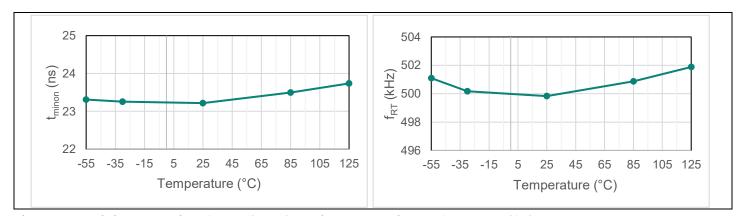

Figure 13 Minimum on time for GH ( $t_{minon}$ ) and internal oscillator frequency ( $f_{RT}$ ) over temperature

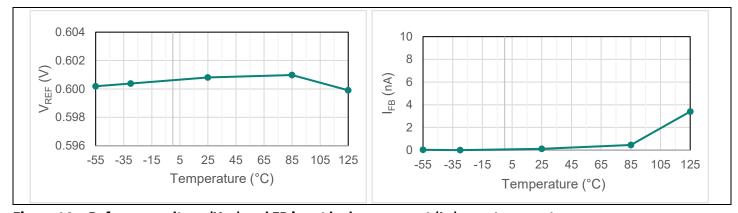

Figure 14 Reference voltage (VREF) and FB input leakage current (IFB) over temperature

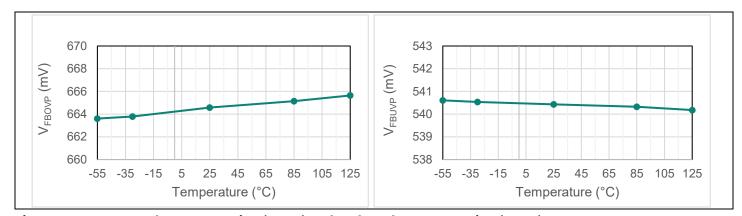

Figure 15 FB overvoltage protection (V<sub>FBOVP</sub>) and undervoltage protection (V<sub>FBUVP</sub>) over temperature

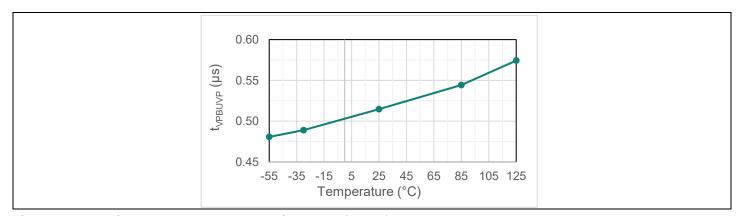

Figure 16 FB pin undervoltage propagation delay (tvfBUVP) over temperature

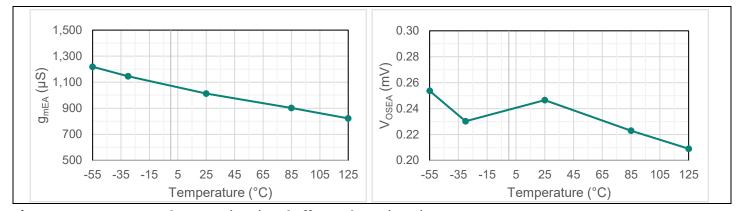

Figure 17 EA transconductance  $(g_{mEA})$  and offset voltage  $(V_{OSEA})$  over temperature

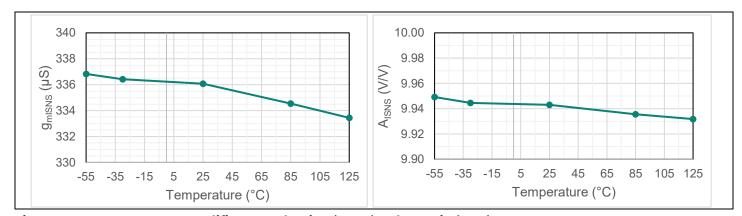

Figure 18 Current sense amplifier transduction (gmisns) and DC gain (Aisns) over temperature

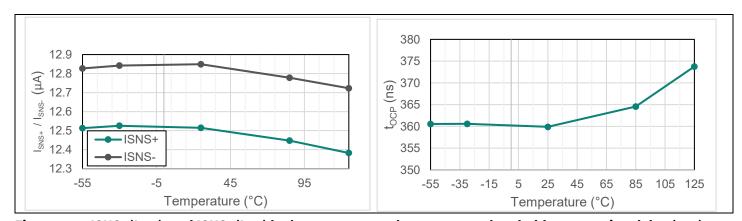

Figure 19 ISNS+( $I_{SNS+}$ ) and ISNS- ( $I_{SNS-}$ ) leakage current and overcurrent threshold propagation delay ( $t_{OCP}$ ) over temperature

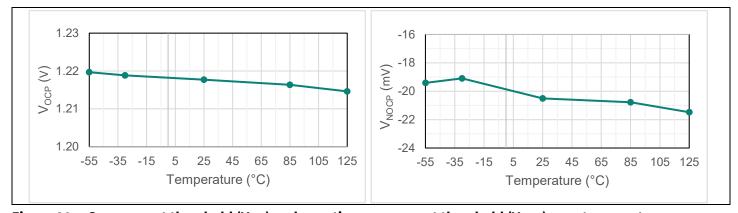

Figure 20 Overcurrent threshold ( $V_{OCP}$ ) and negative overcurrent threshold ( $V_{NOCP}$ ) over temperature

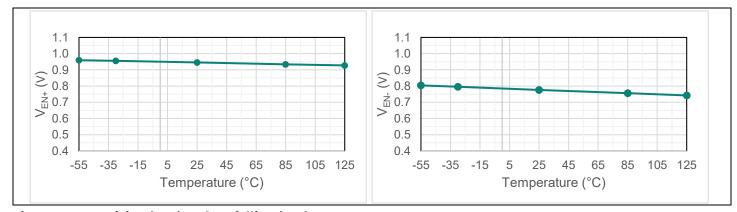

Figure 21 EN rising (V<sub>EN+</sub>) and EN falling (V<sub>EN-</sub>) over temperature

Figure 22 VFB high limit for PG (V<sub>PGOV</sub>) and low limit for PG (V<sub>PGUV</sub>) over temperature

# Rad hard 17.1 V buck controller with integrated gate drivers

Figure 23 Load line regulation current source from FB pin unloaded (ILLR<sub>NL</sub>) and loaded (ILLR<sub>L</sub>) over temperature

### Rad hard 17.1 V buck controller with integrated gate drivers

**General description**

# 5 General description

RIC70847 is a fixed switching frequency peak current mode buck controller intended for applications such as point of load (PoL) power conversion for space grade field programmable gate array (FPGA) core rails, microcontrollers and application-specific integrated circuits (ASICs). It is designed to work with radiation hardened logic level FETs, such as the <u>rad hard R8 FET family</u>. RIC70847 is certified for use in space applications per the Defense Logistics Agency (DLA) MIL-PRF-38535 Class V (DLA certification pending).

## **5.1** Radiation performance

RIC70847 is designed to work in space and other applications where there is significant ionizing radiation and energetic particles in the environment that can affect microcircuit performance. RIC70847 is characterized for operation up to a total ionizing dose (TID) of 100 krad(Si), with electrical parameters including limits post-irradiation. It is also characterized for single event effects (SEE) up to 81.9 MeV·cm²/mg.

The packaged versions of RIC70847 do not have any electrically floating metal, with all metal (including the lid) internally connected to a known, controlled potential. This allows for compliance with system level requirements prohibiting electrically floating metal without the need for additional wires.

## 5.1.1 Total ionizing dose (TID)

RIC70847 is tested over total ionizing dose (TID) to verify robustness to ionizing proton and electron radiation environments, such as space. The radiation hardness assurance (RHA) program at IR HiRel uses a Cobalt-60 (60 Co) source and heavy ion irradiation. Every wafer is tested per MIL-STD-883, Method 1019, test condition A "lonizing Radiation (Total Dose) Test Procedure." Both pre- and post-irradiation performance are tested to the limits specified in the electrical characteristics.

## 5.1.2 Single event effects (SEE)

RIC70847 is characterized in heavy ion environment for single event effects (SEE) up to a linear energy transfer (LET) of 81.9 MeV·cm²/mg. RIC70847 is found to be immune to destructive events single event burnout (SEB), single event gate rupture (SEGR) and single event latch-up (SEL) to a bias voltage of 16.7 V up to an LET of 81.9 MeV·cm²/mg. RIC70847 is also characterized for single event transient (SET) up to an LET of 81.9 MeV·cm²/mg.

## 5.2 Input power and bias

## 5.2.1 Power input

RIC70847 has an absolute maximum rating of 17.1 V on the VIN pin. This enables support of common input voltages such as 5 V or 12 V while meeting various tolerance and derating requirements typical of space applications. It is recommended that during initial startup the applied voltage on the VIN pin has a turn on slew rate of 0.1 V/ms or faster.

# 5.2.2 Drive voltage

RIC70847 features an internal linear low-dropout regulator (LDO) from VIN pin to VDRV pin. This internal LDO generates a 5 V (typical) supply. It is used for the internal logic and internal half bridge gate driver of RIC70847. It can additionally be used as a power rail for additional functions, such as a logic high voltage for the PG and EN pins. This LDO has a current limit I<sub>DRV</sub>, which if reached will cause the LDO to enter constant current mode and the output voltage to decrease. If the voltage on VDRV decreases below the undervoltage lockout threshold, RIC70847 will enter

#### **General description**

undervoltage lockout and stop PWM operation. A capacitance of at least 1  $\mu$ F from VDRV to PGND is required for proper operation.

When VIN=5 V and the VDRV pin is under heavy load (such as high switching frequency or large external load), the voltage drop of the internal LDO may cause the VDRV voltage to be lower than desired. To overcome this, an external voltage can be applied to VDRV. If an external voltage is applied to VDRV, it is recommended to apply the same voltage to VIN as well. If this is done it is recommended to keep VDRV pin voltage within the recommended limits specified in the electrical characteristics.

## 5.2.3 High side bootstrap circuit

RIC70847 features an integrated bootstrap circuit to provide bias for the integrated high side gate driver. The input for this bootstrap comes from VDRV. For proper operation, a ceramic capacitor of at least 100 nF is recommended from BOOT to SW pin.

## 5.3 Return pins

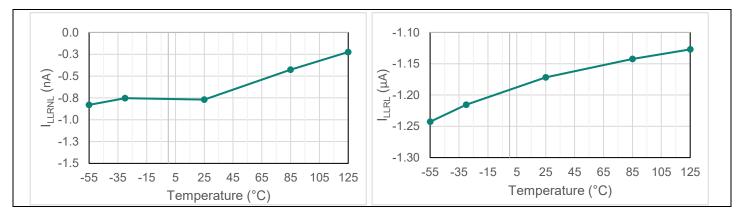

RIC70847 features 3 return pins, PGND, AGND and FB RET, along with a high side floating power return SW. PGND is intended for the power stage, where there are high amounts of ringing and electrical noise, and is used with VIN, VDRV and GL. SW is a power return for the high side gate driver and is used with BOOT and GH. AGND is intended for analog logic and is used with SYNCI, SYNCO, COMP, LLR, PG and EN pins. FB RET is a return for the feedback network that ties directly to the ground of the internal reference voltage. By providing a separate return for FB RET, RIC70847 has pseudo-differential output voltage sensing, which improves DC regulation accuracy over load. FB RET is intended for feedback circuitry that is referenced to the reference voltage, and is used with VREF, SLP, SS, RT and OCP pins.

All 3 return pins (PGND, AGND, FB RET) are internally connected in RIC70847 through diodes. These diodes clamp ringing, and potential noise coupling, across various returns. It is recommended to connect all 3 return pins (PGND, AGND, FB RET) externally together at the resistor divider network, which should be as close as possible to the load.

Figure 24 Example external connections for return pins PGND, AGND and FB RET

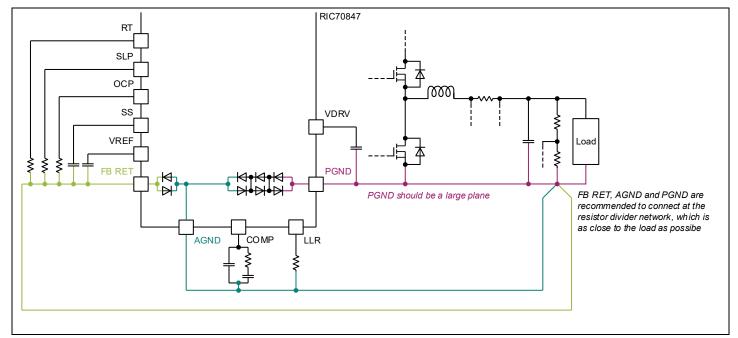

### 5.4 Gate drive

RIC70847 features and integrated half bridge driver with bootstrap and level shift. The drive voltage for both the high and low side is typically 5 V and is supplied from VDRV. The low side (GL) and high side (GH) have a gate drive strength of 2 A source and sink. Both drivers are intended to work with logic transistors such as the <u>rad hard R8</u> family.

In some instances, it may be desired to slow down the switching speed of the switches to reduce the voltage overshoot and ringing on the switch node or generated electromagnetic interference (EMI). This can be achieved by adding a resistor in series from GH ( $R_{GH}$ ) or GL ( $R_{GL}$ ) to the respective FET gate to slow down both the turn on and turn off switching time. Additionally, for the high side GH, a resistor ( $R_{GHON}$ ) can be added in series with the bootstrap capacitor to slow down turn on time but maintain fast turn off speed.

Figure 25 Optional external gate drive resistors

When the internal LDO is used to power the IC (bias power only applied to VIN), if large gate capacitance transistors are used (like IRHLNS87Y50) at high switching frequencies (1 MHz and above), the internal LDO current limit IDRV may be reached, reducing the effective maximum switching frequency. This occurs since the IDRV limit includes the internal gate driver. The current draw from the gate driver operation can be approximated with the following equation.

$$I_{gate\ driver} = (Q_{G\ HS} + Q_{G\ LS}) \times f_{sw}$$

Where,

- Igate driver is the current draw from the gate driver in amperes (A)

- Q<sub>G HS</sub> is the total gate charge of the high side transistor in Columb (C)

- Q<sub>GLS</sub> is the total gate charge of the low side transistor in Columb (C)

- f<sub>sw</sub> is the switching frequency in hertz (Hz)

It is recommended that I<sub>gate driver</sub> and any external load powered off of VDRV should always be less than I<sub>DRV</sub> when the internal LDO is used to generate VDRV (bias power only applied to VIN).

# 5.5 Switching frequency

RIC70847 operates in fixed switching frequency operation, where the switching frequency stays at a fixed value and the duty cycle is modulated to regulate the output voltage. The clock that sets the switching frequency can either come from an internal oscillator or from an external clock.

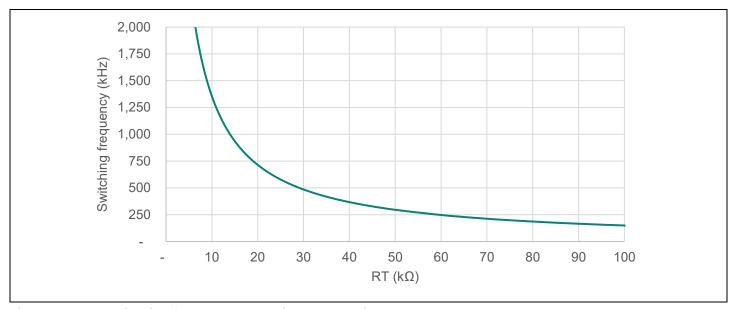

### 5.5.1 Internal oscillator

To operate from the internal oscillator, the switching frequency can be set from 100 kHz to 2 MHz with an external resistor  $R_{RT}$  from RT to FB RET. The switching frequency  $f_{sw}$  for  $R_{RT}$  can be calculated with the following equation.

$$f_{sw} = \frac{1}{66.12 \times 10^{-12} \times RT + 76 \times 10^{-9}}$$

Where,

- RT is resistor on RT pin to FB RET pin in ohms (Ω)

- f<sub>sw</sub> is the switching frequency in hertz (Hz)

Figure 26 Switching frequency vs. resistor on RT pin

#### 5.5.2 External clock

To operate RIC70847 from an external clock, the external clock needs to be applied from SYNCI to AGND. The clock is intended to be a square wave with amplitude anywhere between 1.8 V to 5 V logic with a logic high pulse width that is at least 100 ns long and logic low pulse width that is at least 100 ns long. The switching frequency is set by the period between rising edges of the external clock. When operating from an external clock applied to the SYNCI pin, the internal oscillator frequency on the RT pin must be set to at least 90% of the external clock frequency applied to SYNCI pin for proper operation. For example, if the external clock on SYNCI is 500 kHz, the internal oscillator frequency on the RT pin must be set at 450 kHz or greater.

RIC70847 selects operation from either the internal oscillator or external clock by whichever frequency is higher. If an external clock is applied to SYNCI at a frequency higher than RT, RIC70847 will follow the external clock. If there is no external clock applied to SYNCI ( $f_{SW}$ =0 Hz) or the external clock frequency is lower than the internal oscillator, RIC70847 will operate at the internal oscillator frequency. This allows for RIC70847 operation to be uninterrupted if it is following an external clock signal that either momentarily drops out or stops altogether.

# 5.5.3 Synchronization output

When operating from the internal oscillator (switching frequency set by RT pin), RIC70847 generates a 5 V PWM signal with a frequency equal to and phase 180° offset from the switching frequency on the SYNCO pin. This signal is

intended to connect to the SYNCI pin of another RIC70847 to allow them to operate in 2 phase interleaved operation. When an external clock is applied to SYNCI where the frequency is higher than the internal oscillator frequency set by a resistor on the RT pin and RIC70847 is in slave/follower mode, SYNCO output is disabled and is always held low.

### 5.6 Control

RIC70847 features peak current mode control for operation. As a result, it has both current sense and voltage sense along with compensation and control features.

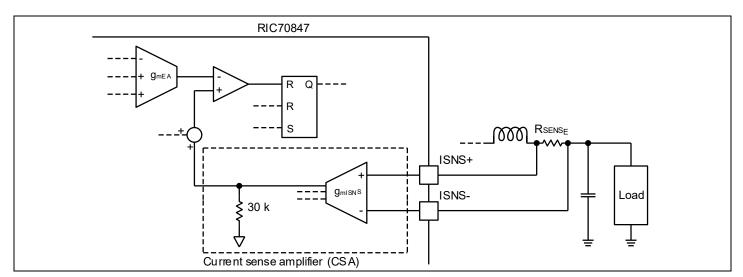

## 5.6.1 Current sense amplifier

For the current sensing, which is used for both regulation and fault protection, RIC70847 has a differential transconductance amplifier with input from ISNS+ pin to ISNS- pin. This sensed current is intended to come from either a current sense resistor in series with the output inductor or inductor DC resistance (DCR) current sensing. The transconductance amplifier has a typical gain  $g_{mISNS}$  of 333  $\mu$ S and an offset of 30  $\mu$ A. For the control loop, the output of this transconductance amplifier has a 30 k $\Omega$  resistor on the output, which provides an overall current sense amplifier gain  $G_{CSA}$  of 10. A simplified block schematic showing the key components for the control current sense are shown in Figure 27.

$$G_{CSA} = g_{mISNS} \times R = 333 \,\mu S \times 30 \,k\Omega = 10$$

Figure 27 Simplified schematic of RIC70847 current sense amplifier

## 5.6.1.1 Current sense monitoring

For some applications, such as telemetry and fault monitoring, it may be desired to monitor the output current. This can be achieved with the RIC70847 OCP pin. This pin is connected to the output of the current sense amplifier and creates a voltage that is proportional to the sensed current from ISNS+ to ISNS-. More information on this is in section 5.10.1.

#### 5.6.1.2 Current sense resistor

When a current sense resistor is used, it is recommended to have a kelvin connection from the ISNS+ and ISNS- pins to the current sense resistor. The resistance used will control the gain of the inner current control loop and is intended to be around  $0.5~m\Omega$ . It is required to keep the sense resistor connected on the output side of the inductor (between the inductor and output capacitors) to limit the voltage magnitude and electrical noise on the ISNS+ and ISNS- pins.

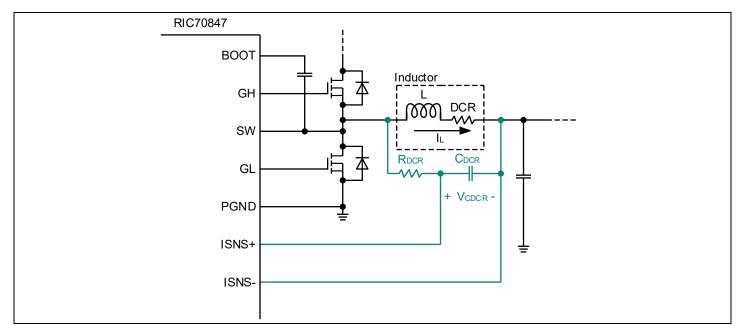

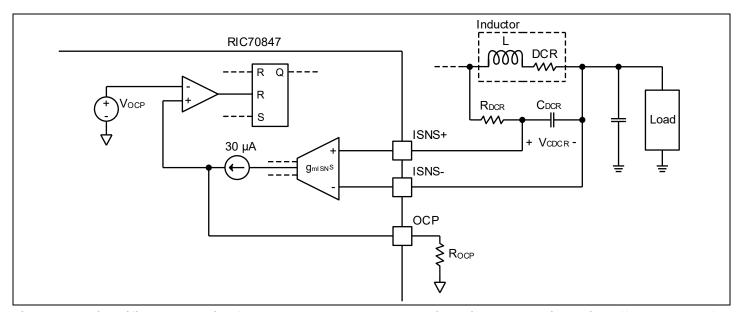

#### **Inductor DCR current sensing** 5.6.1.3

Inductor DCR current sensing is a technique where the DC resistance of the output inductor is used to sense the current. This allows for the current sense resistor to be eliminated, which improves the efficiency of the power supply. To implement DCR current sensing, an RC network must be added in parallel with the output inductor and ISNS+ and ISNS- pins connected across the capacitor, as shown in Figure 28, where DCR is the DC resistance of the inductor and R<sub>DCR</sub> and C<sub>DCR</sub> are added external components.

Figure 28 RIC70847 with inductor DCR current sensing

$R_{DCR}$  and  $C_{DCR}$  can be calculated from the following equation.

$$R_{DCR} \times C_{DCR} = \frac{L}{DCR}$$

Where,

- $R_{DCR}$  is the added resistor in ohms ( $\Omega$ ), recommended resistor value between  $1k\Omega 10k\Omega$

- C<sub>DCR</sub> is the added capacitor in farads (F)

- L is the inductance of the output inductor in henry (H)

- DCR is the DC winding resistance of the inductor in in ohms  $(\Omega)$

The voltage on C<sub>DCR</sub> (V<sub>CDCR</sub>) can be calculated with the following equation.

$$V_{CDCR} = I_L \times DCR$$

Where,

**Datasheet**

- V<sub>CDCR</sub> is the voltage across C<sub>DCR</sub> in volts (V)

- I<sub>L</sub> is the current in the output inductor in amperes (A)

- DCR is the DC winding resistance of the inductor in in ohms  $(\Omega)$

For general design guidelines, it is recommended to limit V<sub>CDCR</sub> so that voltage on ISNS+ and ISNS- do not exceed the absolute maximum limits of these pins.

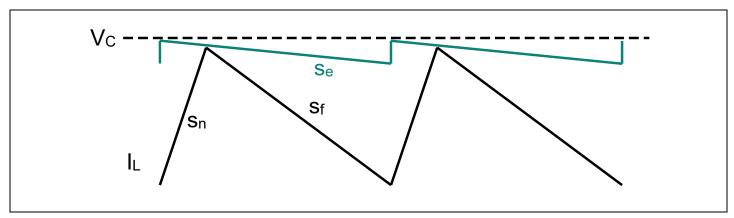

#### 5.6.2 Slope compensation

Due to the peak current mode control operation, there is the potential for subharmonic oscillation, especially if the duty cycle exceeds 50%. This subharmonic oscillation can cause the duty cycle to have large variation between switching cycles and appear unstable. To eliminate this, RIC70847 features programmable integrated slope compensation. Key waveforms for this integrated slope compensation are shown in Figure 29, where S<sub>n</sub> is the ontime ramp slope of the sensed inductor current,  $S_i$  is the off-time ramp slope of the sensed inductor current,  $s_e$  is the ramp slope of the slope compensation and  $V_c$  is the control voltage (output of the compensator).

Figure 29 Key waveforms for integrated slope compensation in RIC70847

To maintain stability for a fixed frequency controller where the clock initiates the on time like RIC70847, the following equation is used.

$$\alpha = \frac{S_f - S_e}{S_n + S_e}$$

Where,

- α is the ratio of change of inductor current from one switching cycle to the next, where values greater than 1 represent instability

- $S_F$  is the off-time ramp slope in amperes per microsecond (A/ $\mu$ s)

- $S_n$  is the on-time ramp slope amperes per microsecond (A/ $\mu$ s)

- $S_e$  is the slope of the external ramp (internal to the IC) in amperes per microsecond (A/ $\mu$ s)

If the duty cycle is above 50% (on time is longer than off time) and there is no external ramp ( $S_e=0$ ),  $S_F$  is larger than  $S_N$ , resulting in  $\alpha$  being greater than 1 and an unstable system. To mitigate this, external slope compensation  $S_e$  is added to reduce α below 0.5. Generation of S<sub>e</sub> is integrated in RIC70847, where the ramp slope is set with a resistor R<sub>SLP</sub> from SLP to FB RET and corresponding ramp slope calculated with the following equation

$$s_e = \frac{3,600}{R_{SENSE} * R_{SLP}}$$

Where,

Datasheet

- $s_e$  is the slope of the external ramp (internal to RIC70847) in amperes per microsecond (A/ $\mu$ s)

- $R_{SENSE}$  is the current sense resistor in series with the output inductor in ohms ( $\Omega$ )

- $R_{SLP}$  is the resistor on the SLP pin to FB RET pin in ohms ( $\Omega$ )

More information on slope compensation, including how these equations and theory were derived, is available in [1].

### 5.7 Feedback

For output voltage regulation, the sensed output voltage is compared to an internal 600 mV reference voltage through the FB pin. To set the regulated output voltage, a resistor divider is recommended from the output voltage to ground. It is recommended to externally connect all returns for RIC70847 (PGND, AGND, FB RET) at this feedback divider network.

## 5.7.1 Reference voltage

RIC70847 features a precises 600 mV reference voltage to maintain high accuracy of the output voltage. The two parameters of RIC70847 that account for offset, tolerance of reference voltage  $V_{REF}$  and error amplifier (EA) offset voltage  $V_{OSEA}$  are combined in a single parameter voltage feedback  $V_{FB}$ , which has its own guaranteed minimum and maximum limit in the electrical characteristics. For aspects of design that depend on these tolerances, like output voltage DC regulation accuracy, it is recommended to use the combined parameter  $V_{FB}$ .

To improve robustness against single event effects, a 1 nF ceramic capacitor is recommended between VREF pin and FB RET as close to the pins as possible. It is not recommended to apply any external load to this pin.

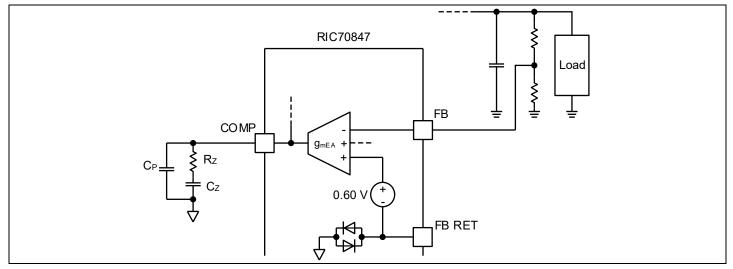

## 5.7.2 Compensation

RIC70847 has an integrated transconductance amplifier for the compensation of the outer voltage control loop. The transconductance amplifier has a typical gain  $g_{mEA}$  of 1 mS. It can be used with a type 2 compensator, as shown in Figure 30.

Figure 30 Simplified schematic of RIC70847 compensation with type 2 compensation

#### 5.8 Soft start

RIC70847 features soft start to allows for a monotonic ramp of the output voltage, regardless of any pre-bias voltage on the output, within a programmable time  $t_{ss}$ . The soft start functionality works by charging an external capacitor  $C_{ss}$  from the SS to FB RET pin with a 10  $\mu$ A (typical) current source  $I_{ss}$ . When the voltage on SS pin is less than the 600 mV reference, the voltage on the soft start pin is used as the reference voltage to regulate the output voltage. Once the voltage on the SS pin exceeds 600 mV, the internal 600 mV reference takes over and is used for regulation. The capacitance on SS pin to FB RET pin to achieve a desired startup time can be calculated with the following equation.

#### **General description**

$$C_{SS} = \frac{t_{SS} \times I_{SS}}{V_{ref}} = \frac{t_{SS} \times 10 \,\mu A}{0.6 \,V}$$

Where,

- C<sub>SS</sub> is the capacitor on SS pin to FB RET pin in farads (F)

- t<sub>ss</sub> is the desired startup time in seconds (s)

- $I_{SS}$  is the internal current source on the SS pin, which is typically 10  $\mu$ A

- V<sub>ref</sub> is the internal reference voltage, which is typically 0.6 V

Figure 31 Soft start ramp time t<sub>ss</sub> vs. SS pin capacitance C<sub>ss</sub>

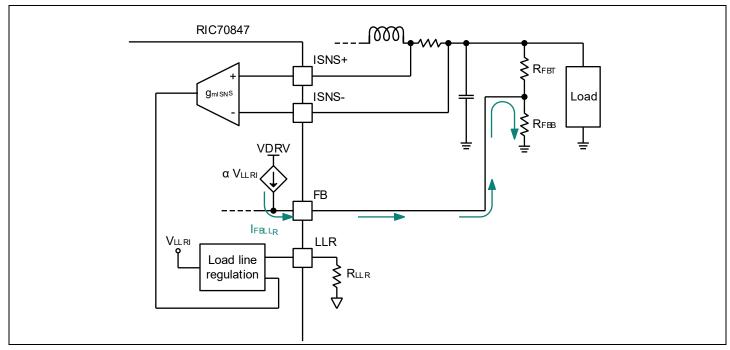

# 5.9 Load-line regulation

Load-line regulation (LLR), also called droop regulation or adaptive voltage positioning (AVP), is an output voltage regulation control technique where the output voltage is adjusted based on the load current. This adjustment in the output voltage reduces the voltage overshoot and undershoot during transient load steps, which can enable a reduction in required output capacitance. For more information on LLR refer to the application note <a href="How load-line will help the application">How load-line will help the application</a>.

LLR for RIC70847 works by injecting a current out of the FB pin, which goes through the bottom feedback resistor  $R_{\text{FBB}}$  to ground. Since RIC70847 regulation forces the voltage on FB pin to stay at the 600 mV reference voltage, this injected current causes the current through the top feedback resistor  $R_{\text{FBT}}$  to decrease, which correspondingly causes the output voltage to decrease. To achieve LLR, the magnitude of this injected current increases with higher load current as sensed across ISNS+ and ISNS- pins. The magnitude of the output voltage drop from LLR is dependent on the ratio between  $R_{\text{FBT}}$  and  $R_{\text{LLR}}$ , which is the resistor on the LLR to AGND pin which sets the magnitude of the current source. Note that when LLR is enabled the feedback resistor divider network may need to be adjusted slightly to account for an output voltage level offset, since "no load" for the design may not be 0 A load as sensed on ISNS+ and ISNS- pins (for example a preload resistor). This can most easily be achieved by reducing the resistance of  $R_{\text{FBB}}$ .

Figure 32 Simplified schematic of LLR operation in RIC70847

The injected current out of the FB pin can be calculated with the following equation.

$$I_{FBLLR} = \frac{6.665 \times R_{SENSE} \times I_L}{16 \times R_{LLR}}$$

#### Where,

- IFBLLR is the current out of the FB pin from the LLR circuit in amperes (A)

- $R_{SENSE}$  is the current sense resistor in series with the output inductor in ohms ( $\Omega$ )

- I<sub>L</sub> is the desired output overcurrent limit in amperes (A)

- R<sub>LLR</sub> is the resistor on the LLR pin to AGND pin in ohms (Ω)

With IFBLLR, the change in output voltage can be calculated with the following equation

$$V_{OUTOS} = I_{FBLLR} \times R_{FBT}$$

#### Where,

- V<sub>OUTOS</sub> is the shift in output voltage in volts (V)

- $R_{FBT}$  is the top resistor in the output resistor divider network in ohms ( $\Omega$ )

Alternately, the desired load-line resistance can be calculated with the following equation

$$LL = \frac{R_{SENSE} \times R_{FBT}}{1.2 \times R_{ILR}}$$

#### Where,

- LL is the desired load line resistance in ohms (Ω)

- $R_{SENSE}$  is the current sense resistor in series with the output inductor in ohms  $(\Omega)$

- $R_{FBT}$  is the top resistor in the output resistor divider network in ohms ( $\Omega$ )

### Rad hard 17.1 V buck controller with integrated gate drivers

### **General description**

•  $R_{LLR}$  is the resistor on the LLR pin to AGND pin in ohms ( $\Omega$ )

For best operation of LLR, it is recommended to select  $R_{\text{FBB}}$  resistance value that is less than around 25 k $\Omega$ . Additionally the internal LLR bandwidth is 250 kHz. It is recommended that the outer voltage loop control bandwidth is below 250 kHz, otherwise the LLR operation will cause additional ringing during load steps.

If LLR operation is not desired, LLR can be disabled by leaving the LLR pin open circuit. This will disable the injected current source on the FB pin. In this case the LLR pin is still electrically connected to internal circuitry, so it is not floating metal. If output voltage regulation is desired at 0.6 V and FB is connected directly to the output voltage, LLR feature can still be implemented with a R<sub>FBT</sub> resistor, while the bottom feedback resistor is not populated.

# 5.10 Fault protections

RIC70847 features multiple integrated fault protections, which are summarized in Table 8. Fault protections include VIN undervoltage lockout (UVLO), VIN overvoltage (OVP), VDRV undervoltage lockout (VDRV UVLO), output voltage overvoltage (VOUT OVP), overcurrent protection (OCP), negative overcurrent protection (NOCP), overtemperature protection (OTP) and loss of SYNCI signal.

Table 8 Fault response summary

| Fault type              | Description                                                                  | Response                                                                                                                                |  |  |

|-------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VIN UVLO                | Voltage on VIN pin decreases below UVLO threshold                            | Shutdown (GH and GL both go low) until VIN voltage increases above UVLO turn on, then attempt startup with soft start sequence          |  |  |

| VIN OVP                 | Voltage on VIN pin exceeds OVP threshold                                     | Shutdown (GH and GL both go low) until voltage on VIN reduces below OVP faling threshold, then attempt startup with soft start sequence |  |  |

| VDRV UVLO               | Voltage on VDRV pin decreases below UVLO threshold                           | Shutdown (GH and GL both go low) until VDRV voltage increases above UVLO turn on, then attempt startup with soft start sequence         |  |  |

| VOUT OVP                | Overvoltage threshold on FB pin exceeded                                     | Shutdown (GH and GL both go low) then attempt startup with soft start sequence                                                          |  |  |

| ОСР                     | Sensed current from ISNS+ to ISNS- pin exceeds positive limit set on OCP pin | Truncate PWM pulse for current switching cycle (GH goes low, GL goes high), continue normal operation for next switching cycle          |  |  |

| NOCP                    | Sensed current from ISNS+ to ISNS- pin exceeds negative limit set on OCP pin | Truncate GL for current switching cycle (GL goes low), continue normal operation for next switching cycle                               |  |  |

| ОТР                     | Junction temperature exceeds T <sub>SD</sub>                                 | Shutdown (GH and GL both go low) until die temperature reduces by T <sub>HYS</sub> , then attempt startup with soft start sequence      |  |  |

| Loss of<br>SYNCI signal | While in follow mode lose signal on SYNCI                                    | Run at frequency of internal oscillator set by resistor on RT pin                                                                       |  |  |

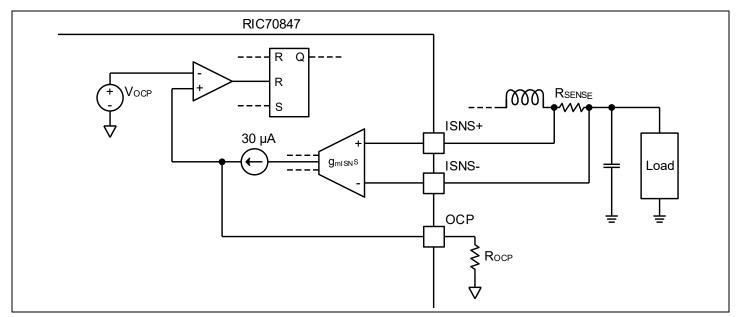

# **5.10.1** Overcurrent protection

The threshold for OCP is set with a resistor from OCP to FB RET. Similar to the current sense for the control loop, the current sense for OCP is sensed from the ISNS+ to ISNS- pins to a transconductance amplifier with a gain  $g_{mISNS}$  of 333  $\mu$ S. The output of this transconductance amplifier is connected to the OCP pin, where a resistor  $R_{OCP}$  on the OCP pin will convert the output to a voltage. This voltage is compared to  $V_{OCP}$ , and if the voltage exceeds  $V_{OCP}$  the switching

cycle is truncated for that switching cycle from OCP protection. The same output is compared to  $V_{NOCP}$ , and if the voltage exceeds  $V_{NOCP}$  the GL gate drive is truncated for that switching cycle from NOCP protection. The resistor  $R_{OCP}$  sets the overall gain of the overcurrent protection current sense amplifier and corresponding overcurrent limit.

### 5.10.1.1 OCP with current sense resistor

For current sense resistor sensing, the following equation can be used to determine the  $R_{OCP}$ , where  $I_{OCP}$  is the desired peak current limit and  $R_{SENSE}$  is the current sense resistor resistance.

$$R_{OCP} = \frac{V_{OCP}}{(333 \,\mu\text{S} \times R_{SENSE} \times I_{OCP}) + 30 \,\mu\text{A}}$$

Where,

- R<sub>OCP</sub> is the resistor on the OCP pin to FB RET pin in ohms (Ω)

- V<sub>OCP</sub> is the internal threshold voltage which exceeding results in OCP protection in volts (V)

- $R_{SENSE}$  is the current sense resistor in series with the output inductor in ohms ( $\Omega$ )

- I<sub>OCP</sub> is the peak inductor current that triggers OCP in amperes (A)

Figure 33 Simplified schematic of RIC70847 overcurrent protection with current sense resistor, with offset current of 30 μA shown externally for clarity

# 5.10.1.2 OCP with DCR sensing

For DCR current sensing, the following equation can be used to determine the  $R_{\text{OCP}}$ , where  $I_{\text{OCP}}$  is the desired peak current limit and  $V_{\text{CDCR}}$  is the sensed voltage across the DCR sensing capacitor. Calculations for the DCR current sensing resistor  $R_{\text{DCR}}$  and capacitor  $C_{\text{DCR}}$  are in section 5.6.1.3.

$$R_{OCP} = \frac{V_{OCP}}{(333 \,\mu\text{S} \times V_{CDCR}) + 30 \,\mu\text{A}}$$

$$V_{CDCR} = I_{OCP} \times DCR$$

#### **General description**

Where.

- R<sub>OCP</sub> is the resistor on the OCP pin to FB RET pin in ohms (Ω)

- V<sub>OCP</sub> is the internal threshold voltage which exceeding results in OCP protection in volts (V)

- V<sub>CDCR</sub> is the voltage across C<sub>DCR</sub> in volts (V)

- DCR is the DC winding resistance of the inductor in in ohms  $(\Omega)$

- I<sub>OCP</sub> is the peak inductor current that triggers OCP in amperes (A)

Figure 34 Simplified schematic of RIC70847 overcurrent protection with DCR sensing, with offset current of 30 μA shown externally for clarity

## 5.11 Power good

RIC70847 has a power good signal from the PG pin. This pin is an open drain configuration, where the pin is actively pulled to AGND when any of the following criteria are met.

- Fault VIN UVLO, VIN OVP, VDRV UVLO, VOUT OVP or OTP active

- Operation disabled by pulling EN pin low

- Sensed output voltage exceeds limits

When none of the event criteria are met, the PG pin is high impedance. It can be connected to an external voltage source, such as VDRV, with a pull up resistor, to create a logic high signal.

### 5.12 Enable

RIC70847 operation can be externally controlled with the EN pin. If this pin is held low, PWM operation is disabled with both GH and GH held low and voltage on SS pin discharged. If the voltage on the EN pin is above  $V_{EN}$ , RIC70847 initiates a soft start sequence and operates as expected. There is hysteresis on EN threshold to prevent chatter during state change. If there is no external voltage to apply on EN pin, or EN functionality is not desired, EN pin can be connected to VDRV through a pull up resistor.

## Rad hard 17.1 V buck controller with integrated gate drivers

**Application information and additional details**

# 6 Application information and additional details

# **6.1.1** Two phase operation

RIC70847 can synchronize with other RIC70847 for two phase operation, where one RIC70847 acts in a master/leader mode and another RIC70847 operates in slave/follower mode. The master/leader RIC70847 sets the switching frequency and performs the outer voltage loop regulation. The slave/follower RIC70847 follows the switching frequency and duty cycle set by the master/leader RIC70847, but it performs its own inner current control and fault protection.

RIC70847 can be configured to work in two phase mode with the following

- SYNCO pin of master/leader RIC70847 is connected to SYNCI pin of follower/slave RIC70847

- SS pin of master/leader RIC70847 is connected to SS pin of follower/slave RIC70847

- COMP pin of master/leader RIC70847 is connected to COMP pin of follower/slave RIC70847

- FB pin of follower/slave RIC70847 is connected to VREF pin of follower/slave RIC70847

An example schematic of two RIC70847 configured in 2 phase operation is shown in Figure 35.

**Application information and additional details**

Figure 35 Simplified schematic of two-phase stand-alone operation

# 6.2 Power sequencing

The PG and EN pins of RIC70847 are rated such that they can be connected in tandem for power sequencing, where the PG pin of one RIC70847 can drive the EN pin of another RIC70847.

## Rad hard 17.1 V buck controller with integrated gate drivers

**Application information and additional details**

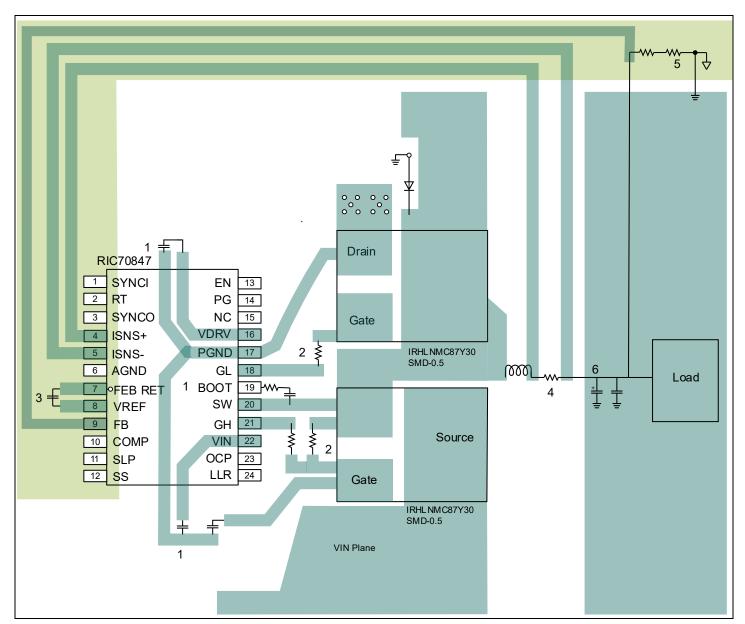

## 6.3 Recommended layout

To achieve high performance a good PCB layout is required. A poor layout can introduce parasitic inductance and capacitance, which couple with electrical noise that interferes with operation. Below are some recommendations to reduce these undesired effects.

- 1. For the bypass capacitor for power rails VIN to PGND, VDRV to PGND and BOOT to SW, use a ceramic capacitor and place as close to the pins as possible

- 2. For external FETs, place as close to their respective gate drive output and gate drive return as possible (high side FET with GH, SW and low side FET with GL, PGND)

- 3. For bypass capacitor for VREF, place as close as possible to VREF and FB RET pins

- 4. If current sense resistor is used, place the resistor on the output side of the inductor (between the inductor and output capacitors) to reduce noise on signal and peak voltage applied to ISNS+ and ISNS- pins

- 5. Externally connect returns PGND, AGND and FB RET at feedback network, which is as close to the load as possible to improve output voltage regulation accuracy over load

- 6. Use a mix of tantalum and ceramic capacitors for output capacitance, especially if there is a transient load step with high slew rate

**Application information and additional details**

Figure 36 Recommended PCB layout for RIC70847

**Package details**

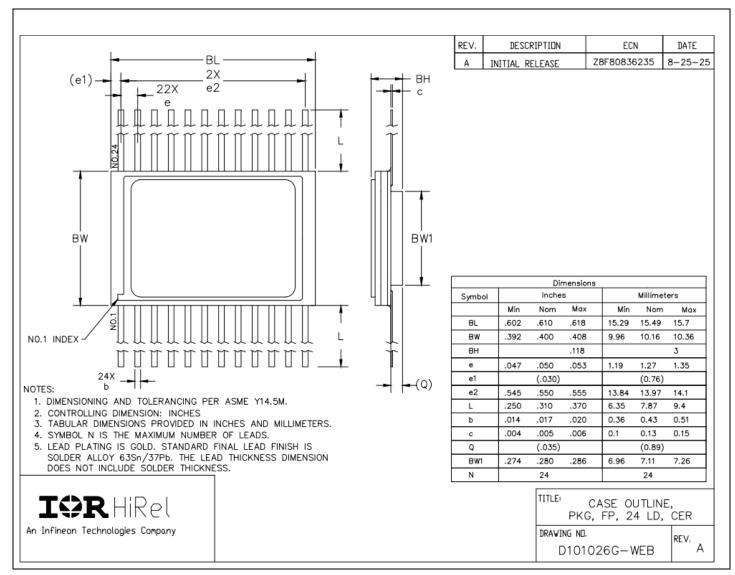

# 7 Package details

# 7.1 Flatpack

For our latest package drawing please refer to 24 Pin Hermetic Flatpack.

Figure 37 24-lead flatpack package outline

Package details

|   |     | <br>,            |   |     |    |

|---|-----|------------------|---|-----|----|

| - | ^,, | <br>$\mathbf{n}$ | h | **^ | ~~ |

|   | _~  |                  |   |     |    |

|   | -v  | <br>on           |   | ,,, |    |

|   |     |                  |   |     |    |

| Document revision | Date | Description of changes |

|-------------------|------|------------------------|

|                   |      |                        |

|                   |      |                        |

|                   |      |                        |

|                   |      |                        |

|                   |      |                        |

# References

[1] R.B. Ridley, "A New Small-Signal Model for Current-Mode Control", PhD Dissertation, Virginia Polytechnic Institute and State University, November

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2025-09-15 Published by

International Rectifier HiRel Products,

An Infineon Technologies company El Segundo, California 90245 USA

© 2025 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference

#### Important notice

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### Warnings

Due to technical requirements our products may contain dangerous substances. For information on the types in question, please contact your nearest International Rectifier HiRel Products, Inc., an Infineon Technologies company, office.