# 英飞凌 XDPP1100 数字电源控制器

## 带 PMBus 接口和 ARM CORTEX™ M0 的数字电源控制器

### 特性

- 数字控制器辅助高性能模拟前端和完全可编程的 ARM® Cortex™-M0 处理器

- 100 MHz 时钟, 32 位

- 64 kB OTP

- 32 kB RAM

- 80 kB ROM

- 基于固件的系统配置管理和命令执行

- 可编程支持一个或两个全数字控制电压轨

- 高性能、低延迟数字硬件控制环路

- 通过变压器绕组进行初级侧电流信号模拟和初级电压感应的次级侧调节

- 高速电压检测

- 100 MHz 11位ADC, 精度为1.25 mV/LSB

- 高达 2.1 V 的差分电压范围

- 自动校准偏移

- 在 1.2 V 至 2.1 V 的温度范围内, 设定点精度在 +/-1% 以内

- 200 MHz 边缘检测比较器

- 用于 OVP 和 UVP 的低延迟保护比较器

- 最多 3 个差分感测通道, 用于输出电压和变压器整流器电压感测

- 高速电流检测

- 25 MHz 9 位 ADC, 增益可选范围为 100  $\mu$ V/LSB 和 1.45 mV/LSB

- 支持集成功率级的电流检测

- 用于 OCP 和正/负峰值电流限制的低延迟保护比较器

- 最多 2 个差分感测通道, 用于次级电流、初级电流或第二环路电流感测

- 最多 12 个高分辨率数字脉冲宽度调制 (DPWM) 输出

- 78.125 ps 脉冲宽度分辨率

- 输出之间的可调相移

- PWMx可重映射

- 逐周期占空比匹配

- 上升沿和下降沿的对间死区时间可调

- 死区时间分辨率1.25 ns

- 高达 2 MHz 的开关频率

- 频率/周期分辨率20ns

- 可配置PWM边沿对齐

本数据手册的原文使用英文撰写。为方便起见，英飞凌提供了译文；由于翻译过程中可能使用了自动化工具，英飞凌不保证译文的准确性。为确认准确性请务必访问 [infineon.com](http://infineon.com) 参考最新的英文版本（控制文档）。

## 特性

- 后沿调制（前沿对齐）

- 前导调制（后沿对齐）

- 三角调制（中心对齐PWM）

- 可配置反馈控制

- 电压模式

- 峰值电流模式

- 恒流模式

- 恒定功率模式

- 可配置的调制方式

- 脉宽调制

- 相移调制

- 多达16个GPIO引脚

- 有或无预偏置的软启动/停止

- 无需初级电压感测的前馈补偿

- 高效率和轻载管理

- 突发模式

- 二极管仿真

- 待机功率低

- 铜线电流感应

- 温度补偿 3900 ppm/°C

- 通量平衡

- 相电流平衡

- 功能丰富的故障保护

- 可编程过压和欠压保护（OVP、UVP）阈值和响应

- 可编程过流和欠流保护（OCP、UCP）阈值和响应

- 可编程过温或欠温保护（OTP、UTP）阈值和滞后

- 可编程正/负峰值电流限制阈值

- 内部和外部温度传感器

- SR负电流保护

- 反馈开环保护

- 可编程消隐时间

- 与外部时钟同步

- 6通道、9位、1Msps通用ADC

- 通讯外设

- 具有可定制命令集的 1 MHz I<sup>2</sup>C/PMBUS

- 可选支持辅助串行端口：I<sup>2</sup>C M/S

- 全双工UART

- 固件增强了应用程序功能定制的能力

- PMBus 命令

- GPIO功能

- 保护和故障检测/监控

- 控制增强

## 典型应用

- 系统监控

- 内置看门狗

- 极低的工作电流和静态电流

- 40 引脚和 24 引脚 VQFN 封装

- 工作温度：-40 °C 至 125 °C

- 调试接口

- GUI 界面用于可配置接口、控制和保护功能，可实现快速、稳健的设计

## 典型应用

- 隔离/非隔离 DC-DC 瓦型模块

- 中间总线转换器

- 非隔离式降压-升压转换器

- 针对电信基础设施优化的电源

- 标准 48V 至 12V 隔离 DC-DC 转换器

- 工业应用智能电力系统

## 产品验证

符合 JEDEC47/20/22 相关测试的工业应用要求

**表 1 ESD 和 MSL 额定值**

|                            |                     |                                                         |

|----------------------------|---------------------|---------------------------------------------------------|

| ESD                        | Charge Device Model | Class C3 (1000V)<br>(per JEDEC standard JS-002)         |

|                            | Human Body Model    | Class 2 (2000V)<br>(per EIA/JEDEC standard EIA/ JS-001) |

| Moisture Sensitivity Level |                     | MSL2<br>(per IPC/JEDEC J-STD-020E)                      |

## 订购信息

**表 2 订购信息**

| Base Part Number | Package Type           | Standard Pack Form and Qty |      | Orderable Part Number |

|------------------|------------------------|----------------------------|------|-----------------------|

| XDPP1100-Q024    | VQFN (24), 4 mm x 4 mm | Tape & Reel                | 5000 | XDPP1100Q024XUMA1     |

| XDPP1100-Q040    | VQFN (40), 6 mm x 6 mm | Tape & Reel                | 4000 | XDPP1100Q040XUMA1     |

## 描述

### 描述

XDPP1100 器件是英飞凌科技推出的一款高度集成且可编程的数字电源控制器。该器件为采用隔离和非隔离拓扑的各种 DC-DC 电源应用提供先进的电源控制解决方案。得益于英飞凌先进的设计技术，XDPP1100 采用 4mm<sup>2</sup>QFN封装，提供业界最小的数字电源控制器解决方案。

XDPP1100 设备具有独特的架构，其中包括许多优化的电源处理数字模块，以增强隔离式 DC-DC 转换器的性能、减少外部元件并最大限度地减少固件开发工作。为了实现先进的电源转换和监控，XDPP1100 设备还为系统通信提供了精确的遥测和电源管理总线 (PMBus™) 接口。这些先进的功能使其成为电信基础设施、48V 服务器主板、数据中心和工业 4.0 应用中使用的现代高端电源系统的理想电源控制器。

XDPP1100 控制器是一种高度可编程且用途广泛的设备。其数字设计包含许多优化功能和创新调节算法，以加快产品上市时间，而 XDPP1100 的多功能特性使设计人员能够根据应用需求定制和区分他们的解决方案。英飞凌提供支持工具，例如补充图形用户界面 (GUI)，允许客户配置和监控关键参数。此外，开发人员可以完全控制他们的应用程序和固件开发过程。英飞凌允许系统设计人员在任何常用的基于 ARM™ 开发环境中开发和编译其定制的固件。

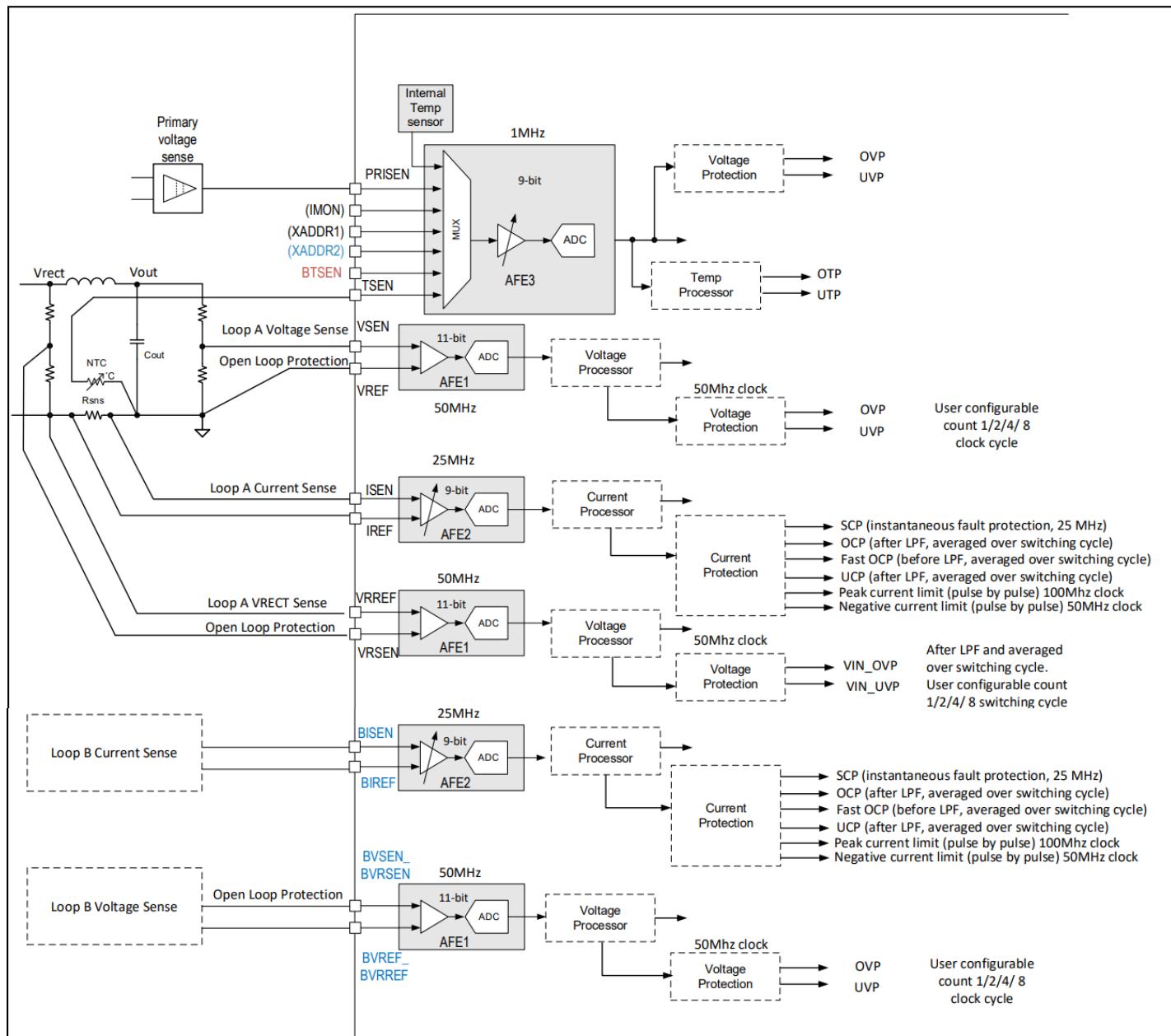

XDPP1100 设备是一个双独立环路控制器，其中环路外设包括最先进的模拟前端 (AFE) 实现。AFE 使用专用高速电压和电流感应模数转换器 (ADC) 和比较器来感应输入/输出电压和电流测量。有多达三个高速 100 MHz、11 位电压感应 ADC，可提供出色的前馈性能、负载瞬态响应和动态 SR 死区时间优化。还有最多两个 9 位高分辨率电流检测 ADC，时钟速度为 25MHz，支持差分检测。该设备还包含一个 9 位通用 ADC，具有最多六个可用通道，有助于实现有源电流均流、初级电压感应和温度感应。来自 AFE 的信息被馈送到 XDPP1100 的数字核心，该核心生成用于调节和控制的可编程 PWM 信号。有多达 12 个数字调制 PWM，脉冲宽度分辨率为 78.125 ps，以及一个基于 PID 的数字补偿器，提供一个原点极点、2 个高频极点和 2 个零点。XDPP1100 设备采用基于有限状态机的可配置控制环路架构，支持各种操作模式，包括电压、峰值电流、恒定电流和恒定功率模式。

为了促进系统级通信，该控制器支持 PMBus™ 1.3 子集并包含 UART 和 I2C 等其他接口。PMBus™ 命令集是运行时可编程的，允许动态配置命令。

XDPP1100 包括一个 32 位、100 MHz ARM® Cortex™ -M0 RISC 微控制器子系统，可用于增强控制、实时监控、外围设备配置和管理通信。它还允许基于固件的定制和实现排序、优化和接口等管理功能。英飞凌在设备 ROM 中预先编程了许多基本和高级电源控制功能。附加程序可以存储在非易失性存储器以及片上 RAM 和 OTP 中并执行。

XDPP1100 设备具有许多预编程的电源管理外设，包括：

- 轻负载突发模式

- 同步整流

- 输入电压前馈

- 使用专用电流检测 ADC 进行温度补偿铜迹线电流检测

## 描述

- 二极管仿真

- 通量平衡

- 预偏置软启动

- 故障管理

- 次级侧输入电压检测

- 一种名为快速瞬态响应 (FTR) 的革命性瞬态保护方案

该设备 ROM 包含英飞凌专利的调节算法，有助于提高转换器效率和空间受限电源模块的功率密度。先进的故障管理和保护功能可提高系统健康和寿命。XDPP1100 设备支持许多常用的 DC-DC 拓扑，例如硬开关全桥和半桥、相移全桥、有源钳位正激、全桥和半桥电流倍增整流器、交错有源钳位正激、交错半桥和交错全桥。双轨版本还支持预降压或后降压配置。

这种高性能模拟前端、基于状态机的数字控制环路和集成在单个芯片上的微控制器的独特组合，使 XDPP1100 成为一种高度集成、可编程且上市时间最快的电源模块开发技术。

XDPP1100 提供两种封装。

**表 3 XDPP1100 器件封装**

| Part number   | Package type | Size              | Application                            |

|---------------|--------------|-------------------|----------------------------------------|

| XDPP1100-Q024 | VQFN (24)    | 4.00 mm × 4.00 mm | Single-rail control with 6 PWM outputs |

| XDPP1100-Q040 | VQFN (40)    | 6.00 mm × 6.00 mm | Dual-rail control with 12 PWM outputs  |

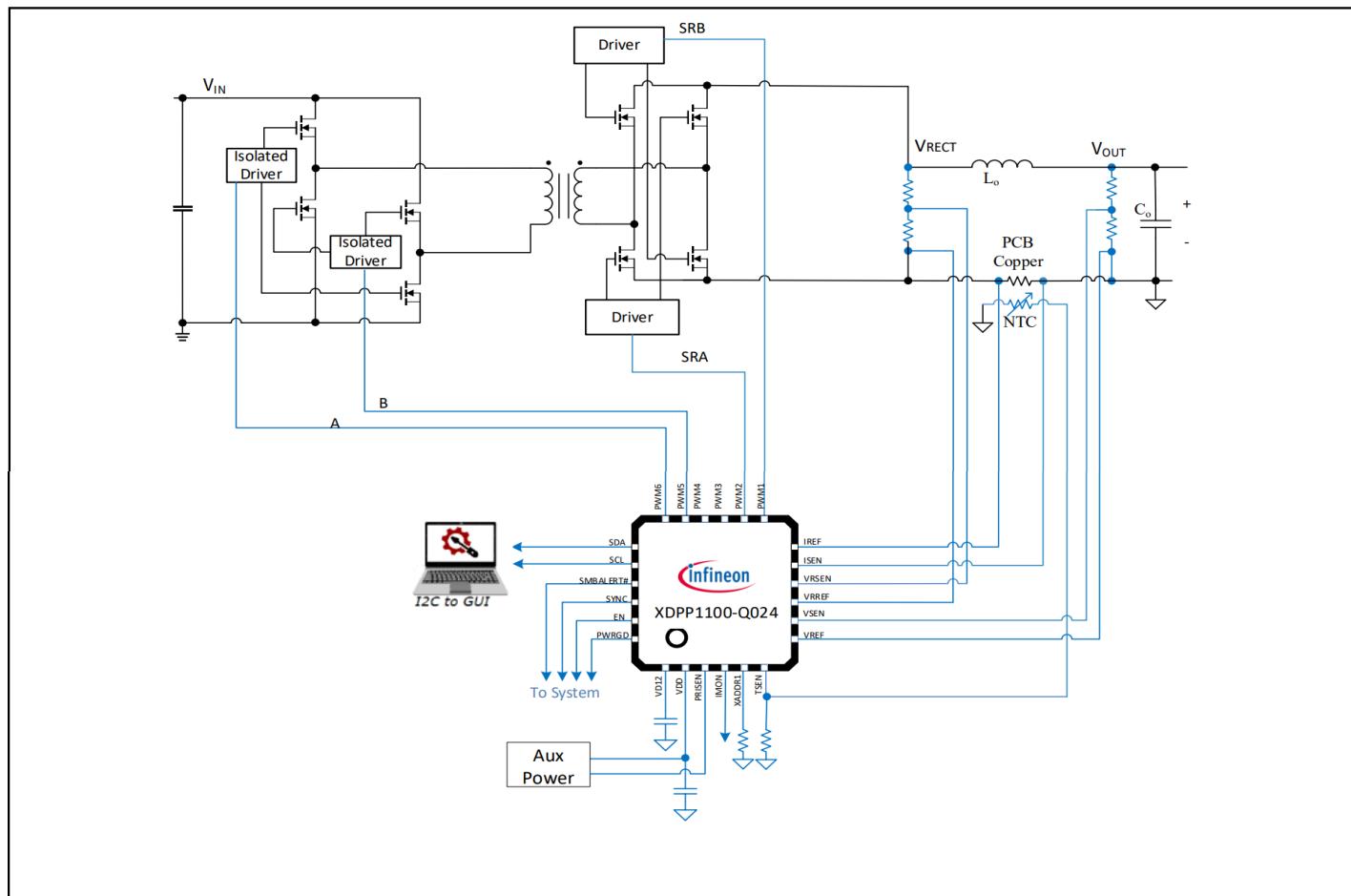

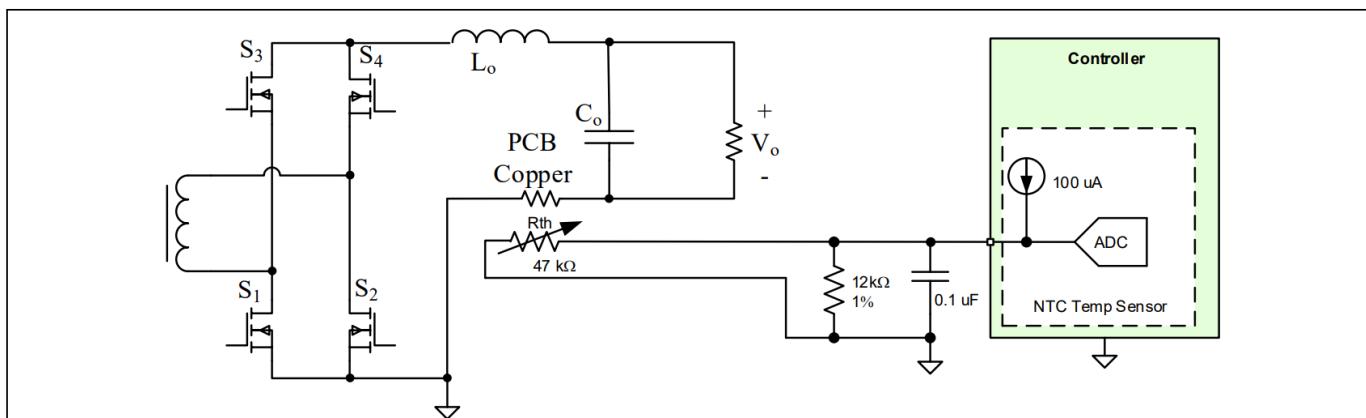

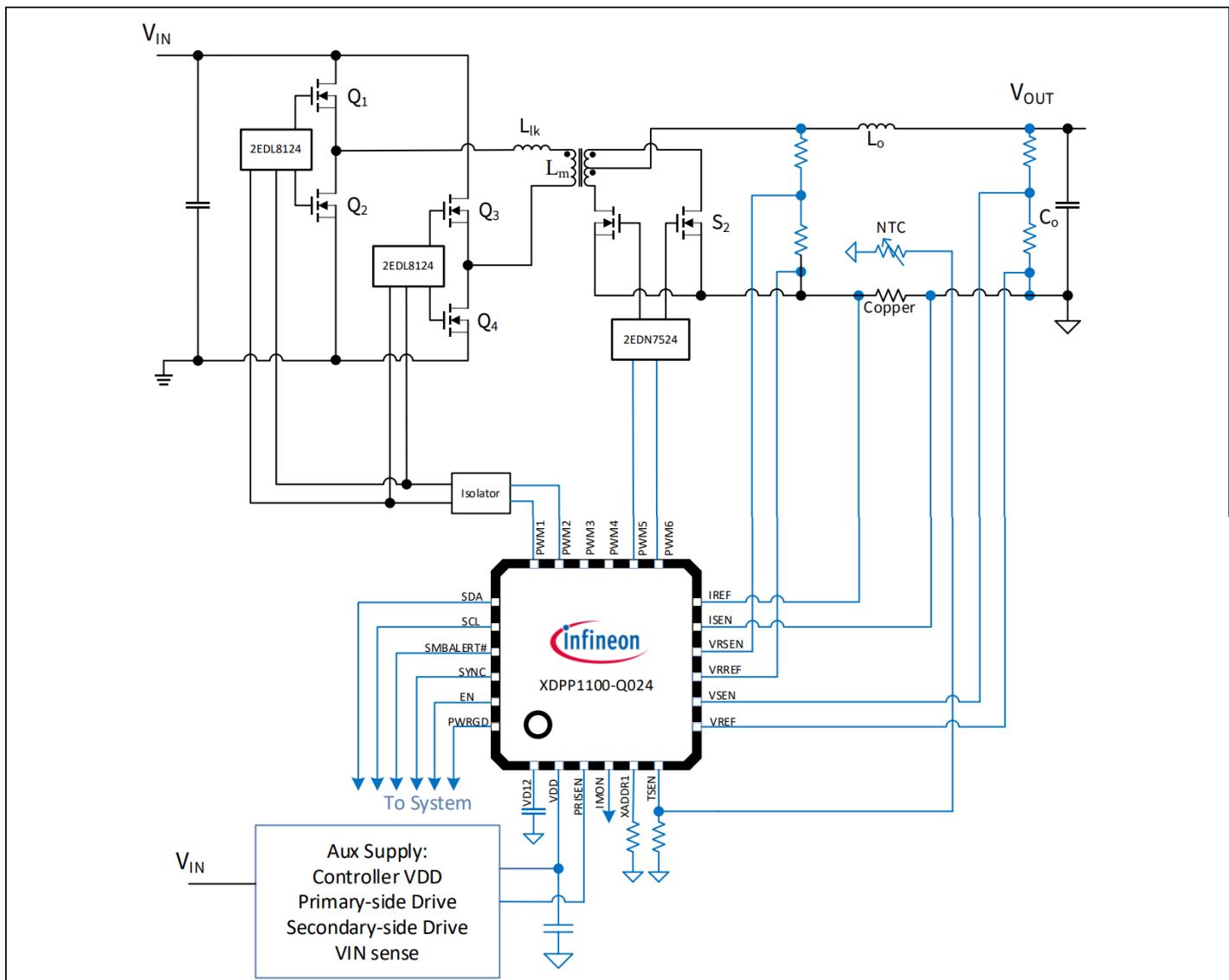

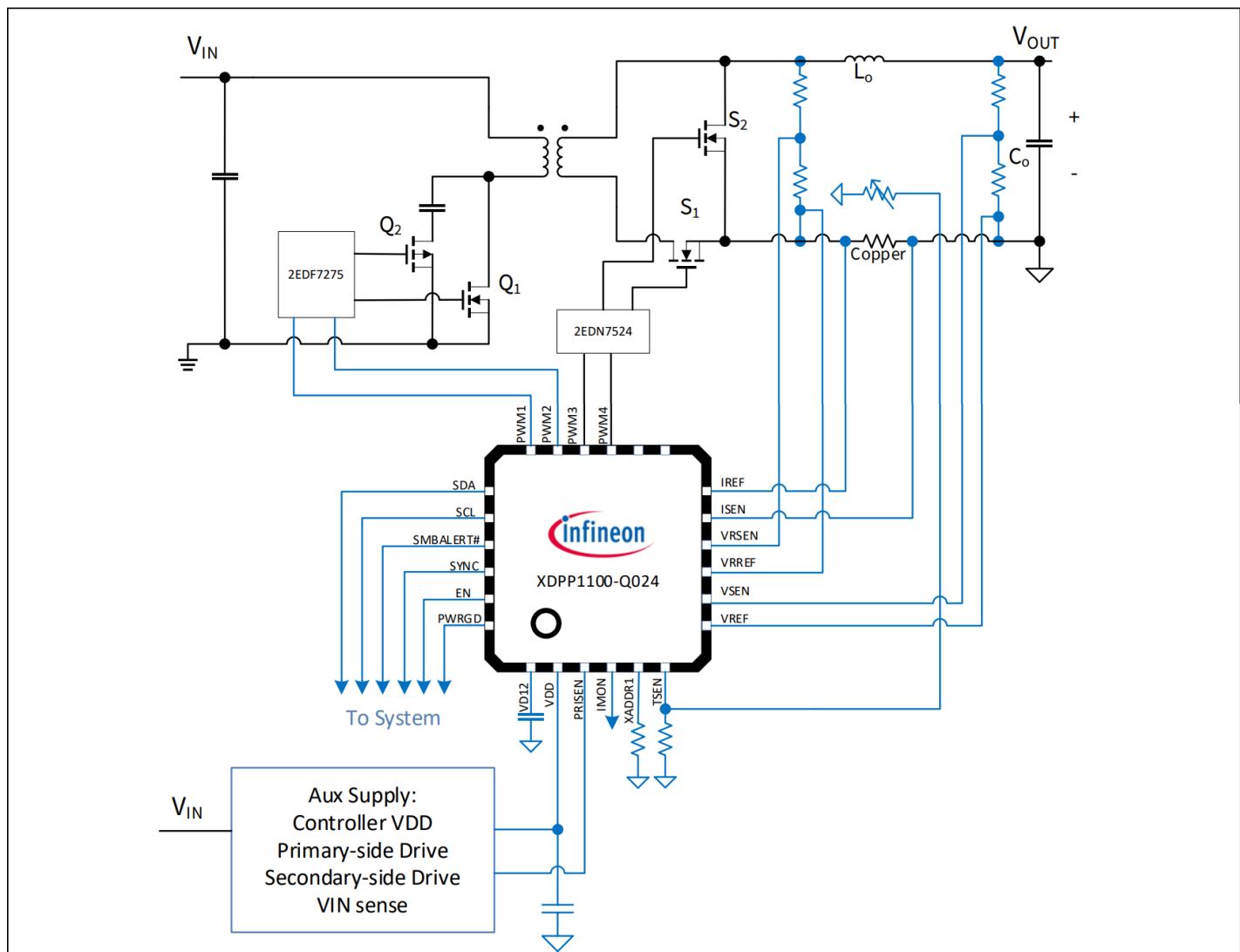

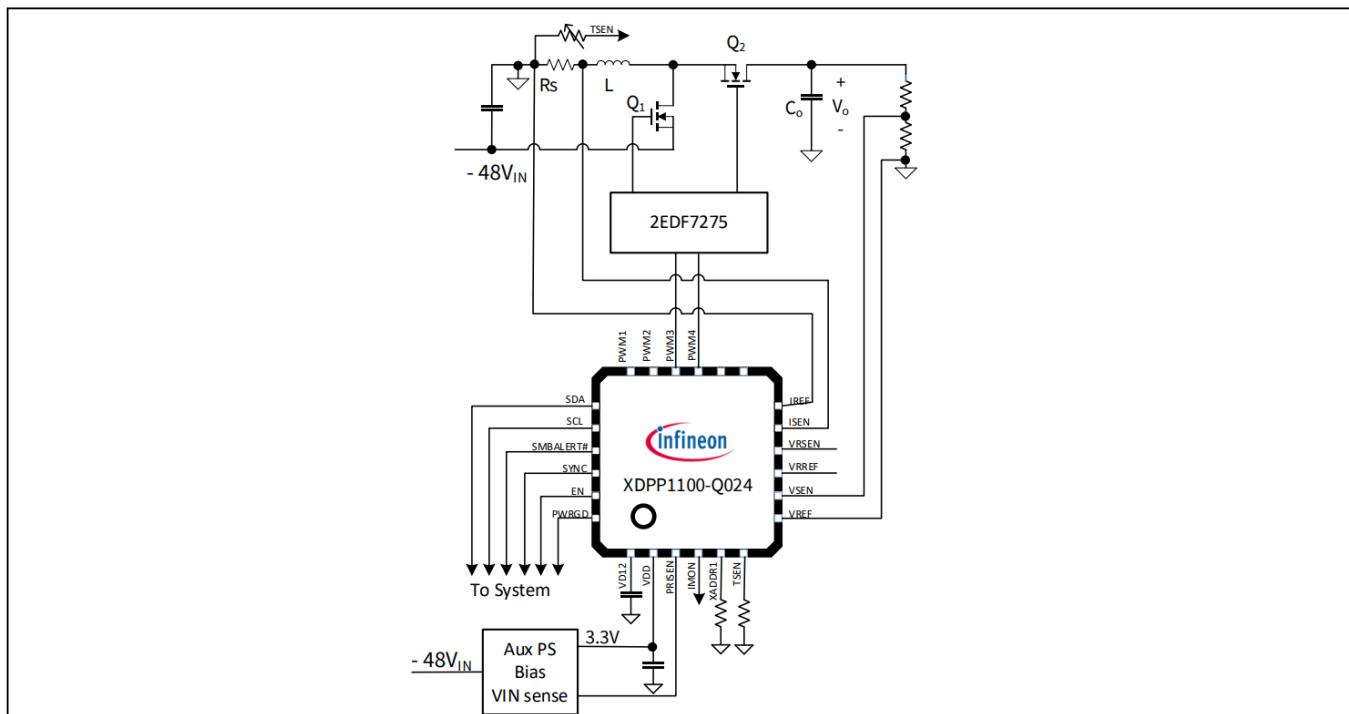

图 1 显示了 XDPP1100 器件在隔离全桥 DC-DC 降压转换器中的典型应用实现：

**图1 典型应用图**

## 目录

## 目录

|                                       |    |

|---------------------------------------|----|

| 特性 .....                              | 1  |

| 典型应用 .....                            | 3  |

| 产品验证 .....                            | 3  |

| 订购信息 .....                            | 3  |

| 描述 .....                              | 4  |

| 目录 .....                              | 6  |

| 1 功能框图 .....                          | 8  |

| 2 产品选择矩阵 .....                        | 9  |

| 3 终端配置和功能 .....                       | 10 |

| 3.1 XDPP1100-Q040 封装 .....            | 10 |

| 3.2 XDPP1100-Q024 封装 .....            | 12 |

| 4 规格 .....                            | 14 |

| 4.1 绝对最大额定值 .....                     | 14 |

| 4.2 热特性 .....                         | 14 |

| 4.3 推荐运行条件 .....                      | 15 |

| 4.4 电气特性 .....                        | 15 |

| 5 功能概述 .....                          | 19 |

| 5.1 简介 .....                          | 19 |

| 5.1.1 ARM® Cortex™ -M0 核心 .....       | 19 |

| 5.1.2 存储器 .....                       | 19 |

| 5.1.3 通信端口 .....                      | 20 |

| 5.1.3.1 I <sup>2</sup> C/ PMBUS ..... | 20 |

| 5.1.3.2 UART .....                    | 20 |

| 5.1.3.3 地址偏移 .....                    | 20 |

| 5.1.4 GPIO .....                      | 22 |

| 5.1.5 寄存器映射 .....                     | 22 |

| 5.2 模拟模块和子系统 .....                    | 23 |

| 5.2.1 电源 .....                        | 23 |

| 5.2.2 振荡器和PLL .....                   | 23 |

| 5.2.3 电压检测 AFE1 .....                 | 25 |

| 5.2.4 电流检测 AFE2 .....                 | 27 |

| 5.2.5 通用 AFE3 .....                   | 29 |

| 5.2.5.1 IMON 和主动电流均流 .....            | 30 |

| 5.2.5.2 温度感应 .....                    | 31 |

| 5.2.5.3 PRISEN .....                  | 32 |

| 5.3 控制回路子系统 .....                     | 32 |

| 5.3.1 状态图 .....                       | 32 |

| 5.3.2 软启动 .....                       | 33 |

| 5.3.3 电压模式控制(VMC) .....               | 34 |

| 5.3.4 峰值电流模式控制 .....                  | 35 |

| 5.3.5 PID 和控制回路 .....                 | 36 |

| 5.3.6 关机 .....                        | 37 |

| 5.3.7 电流检测估计器 .....                   | 37 |

| 5.3.8 载重线(下垂) .....                   | 38 |

| 5.3.9 最快的瞬态响应 .....                   | 38 |

| 5.3.10 输入电压前馈 .....                   | 39 |

## 目录

|             |                                    |           |

|-------------|------------------------------------|-----------|

| 5.3.11      | 电流平衡.....                          | 40        |

| 5.3.12      | 电流均流 .....                         | 40        |

| 5.3.13      | 通量平衡.....                          | 40        |

| 5.3.14      | 突发模式.....                          | 41        |

| 5.4         | 保护和故障.....                         | 42        |

| <b>6</b>    | <b>应用信息 .....</b>                  | <b>44</b> |

| 6.1         | PWM 全桥转换器 .....                    | 44        |

| 6.1.1       | VMC中带中心抽头输出的PWM全桥 .....            | 44        |

| 6.1.2       | 带PCMC的PWM全桥 .....                  | 45        |

| 6.2         | PWM半桥转换器.....                      | 46        |

| 6.3         | 有源钳位正激变换器.....                     | 47        |

| 6.4         | 交错有源钳位正向.....                      | 48        |

| 6.5         | 双环路转换器.....                        | 48        |

| 6.6         | 非隔离转换器.....                        | 49        |

| 6.7         | 布局指南.....                          | 50        |

| 6.7.1       | 元件放置.....                          | 50        |

| 6.7.2       | 布线 .....                           | 51        |

| 6.7.3       | 通过铜线感测输出电流.....                    | 51        |

| <b>7</b>    | <b>封装信息 .....</b>                  | <b>53</b> |

| 7.1         | XDPP1100-Q024 QFN 4x4 - 24引脚 ..... | 53        |

| 7.2         | XDPP1100-Q040 QFN 6x6 - 40引脚 ..... | 53        |

| 7.3         | 零件标记.....                          | 54        |

| <b>修订记录</b> | <b>.....</b>                       | <b>55</b> |

## 功能框图

## 1 功能框图

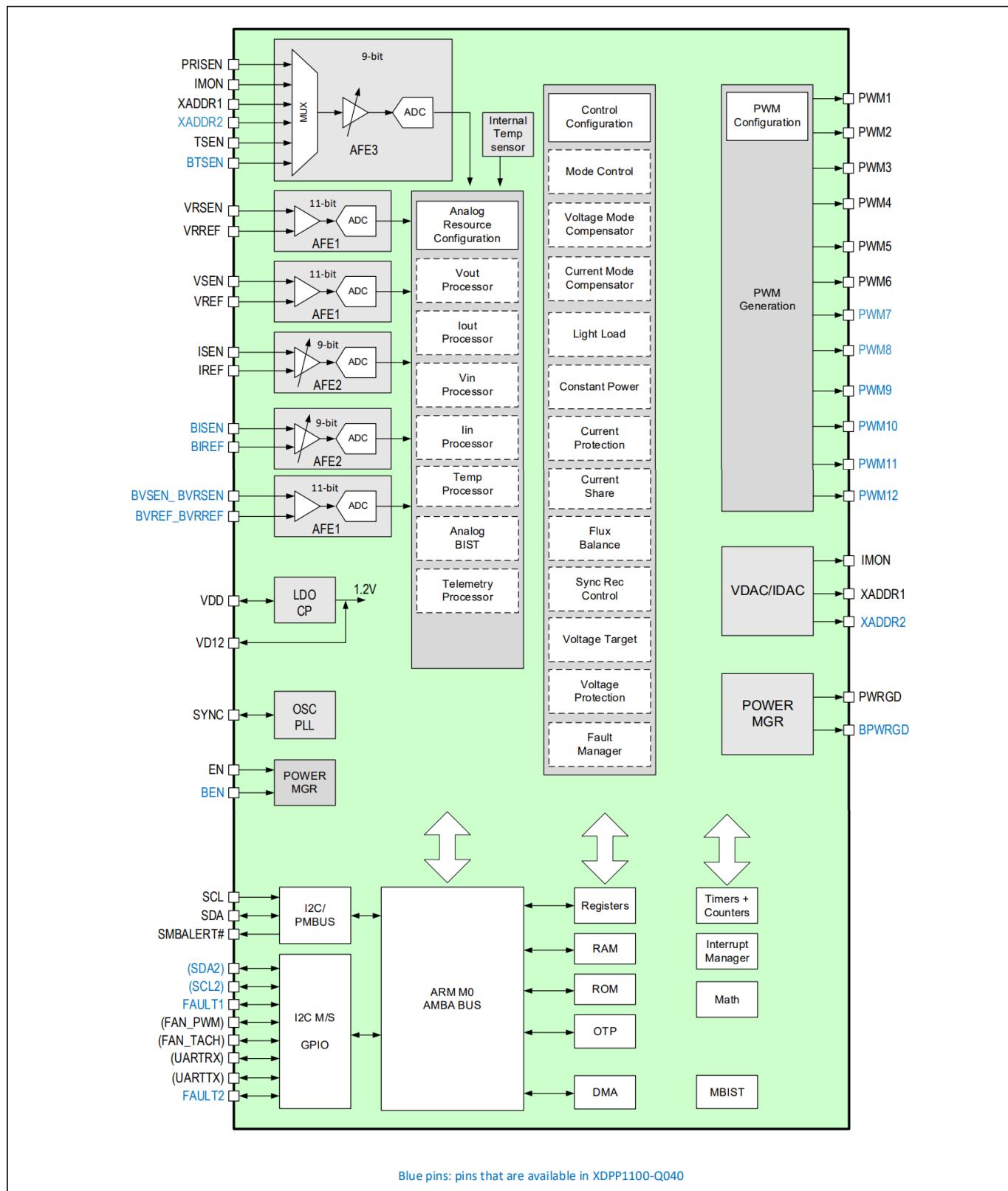

图 2 展示了 XDPP1100 设备架构的功能框图。

图2 框图

## 产品选择矩阵

## 2 产品选择矩阵

表4 产品选型表

| FEATURE                                            | XDPP1100-Q040                  | XDPP1100-Q024                  |

|----------------------------------------------------|--------------------------------|--------------------------------|

| ARM M0 core processor                              | 100 MHz                        | 100 MHz                        |

| High resolution DPWM outputs (78.125ps resolution) | 12                             | 6                              |

| Number of high-speed independent feedback rails    | 2                              | 1                              |

| Number of voltage sense ADC                        | 3                              | 2                              |

| Number of current sense ADC                        | 2                              | 1                              |

| 9-bit, 1Msps, general purpose ADC channels         | 6                              | 4                              |

| OTP                                                | 64 kB                          | 64 kB                          |

| RAM                                                | 32 kB                          | 32 kB                          |

| ROM                                                | 80 kB                          | 80 kB                          |

| DPWM switching frequency                           | Up to 2 MHz                    | Up to 2 MHz                    |

| Secondary serial bus (I <sup>2</sup> C M/S)        | Yes                            | No                             |

| UART                                               | Yes                            | Yes                            |

| PMBus                                              | Yes                            | Yes                            |

| Watchdog                                           | Yes                            | Yes                            |

| On chip oscillator                                 | Yes                            | Yes                            |

| Sync in and sync out functions                     | Yes                            | Yes                            |

| Temperature sense inputs                           | 2                              | 1                              |

| Enable inputs                                      | 2                              | 1                              |

| Power good outputs                                 | 2                              | 1                              |

| Total GPIO (General purpose I/O pins)              | 16                             | 11                             |

| Package offering                                   | VQFN-40 (6x6 mm <sup>2</sup> ) | VQFN-24 (4x4 mm <sup>2</sup> ) |

## 终端配置和功能

### 3 终端配置和功能

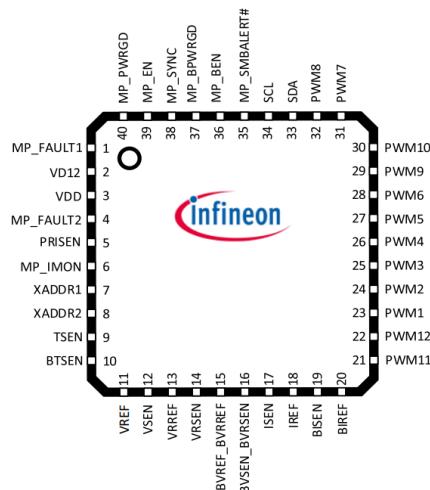

#### 3.1 XDPP1100-Q040 封装

图3 XDPP1100-Q040引脚分配

表5 XDPP1100-Q040引脚定义

| Pin No. | Name      | Primary Assignment                                             | Alternate assignment         | Configurable GPIO? |

|---------|-----------|----------------------------------------------------------------|------------------------------|--------------------|

| 1       | MP_FAULT1 | Fault 1                                                        | SYNC/ FAN2_PWM/ SDA2/ UARTRX | Yes                |

| 2       | VD12      | 1.2V supply bypass                                             |                              |                    |

| 3       | VDD       | 3.3V main supply input                                         |                              |                    |

| 4       | MP_FAULT2 | Fault 2                                                        | SYNC/FAN2_TACH/ SCL2/ UARTTX | Yes                |

| 5       | PRISEN    | Primary voltage sensing input                                  | GPA1                         |                    |

| 6       | MP_IMON   | Current monitor output                                         | GPA2/ SYNC/ FAN1_TACH        | Yes                |

| 7       | XADDR1    | Address 1                                                      | GPA3                         |                    |

| 8       | XADDR2    | Address 2                                                      | GPA4                         |                    |

| 9       | TSEN      | Temperature sensing input of the first rail                    | GPA5                         |                    |

| 10      | BTSEN     | Temperature sensing input of the second rail                   | GPA6                         |                    |

| 11      | VREF      | Differential voltage sensing of the first rail, negative input |                              |                    |

| 12      | VSEN      | Differential voltage sensing of the first rail, positive input |                              |                    |

| 13      | VRREF     | Transformer winding voltage sense, negative input              |                              |                    |

## 终端配置和功能

| Pin No. | Name         | Primary Assignment                                                               | Alternate assignment                                        | Configurable GPIO? |

|---------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|

| 14      | VRSEN        | Transformer winding voltage sense or primary input voltage sense, positive input |                                                             |                    |

| 15      | BVREF_BVRREF | Differential voltage sensing of the second rail, negative input                  | Transformer winding voltage sense return of the second rail |                    |

| 16      | BVSEN_BVRSEN | Differential voltage sensing of the second rail, positive input                  | Transformer winding voltage sense of the second rail        |                    |

| 17      | ISEN         | Differential current sensing of the first rail, positive input                   |                                                             |                    |

| 18      | IREF         | Differential current sensing of the first rail, negative input                   |                                                             |                    |

| 19      | BISEN        | Differential current sensing of the second rail, positive input                  |                                                             |                    |

| 20      | BIREF        | Differential current sensing of the second rail, negative input                  |                                                             |                    |

| 21      | PWM11        | PWM11 output                                                                     | SYNC/ FAN1_PWM                                              | Yes                |

| 22      | PWM12        | PWM12 output                                                                     | SYNC/ FAN1_TACH                                             | Yes                |

| 23      | PWM1         | PWM1 output                                                                      | SYNC                                                        | Yes                |

| 24      | PWM2         | PWM2 output                                                                      | SYNC                                                        | Yes                |

| 25      | PWM3         | PWM3 output                                                                      | SYNC                                                        | Yes                |

| 26      | PWM4         | PWM4 output                                                                      | SYNC                                                        | Yes                |

| 27      | PWM5         | PWM5 output                                                                      | SYNC/ UARTRX                                                | Yes                |

| 28      | PWM6         | PWM6 output                                                                      | SYNC/ UARTTX                                                | Yes                |

| 29      | PWM9         | PWM9 output                                                                      | SYNC                                                        | Yes                |

| 30      | PWM10        | PWM10 output                                                                     | SYNC                                                        | Yes                |

| 31      | PWM7         | PWM7 output                                                                      | SYNC/ FAN2_PWM                                              | Yes                |

| 32      | PWM8         | PWM8 output                                                                      | SYNC/ FAN2_TACH                                             | Yes                |

| 33      | SDA          | I <sup>2</sup> C serial data line                                                |                                                             |                    |

| 34      | SCL          | I <sup>2</sup> C serial clock line                                               |                                                             |                    |

| 35      | MP_SMBALERT# | PMBus alert                                                                      | SYNC                                                        | Yes                |

| 36      | MP_BEN       | Enable input of the second rail                                                  | SYNC/ SDA2/ UARTRX                                          | Yes                |

| 37      | MP_BPWRGD    | Power good output of the second rail                                             | SYNC / SCL2/ UARTTX                                         | Yes                |

| 38      | MP_SYNC      | Synchronize pin                                                                  | FAN1_PWM                                                    | Yes                |

| 39      | MP_EN        | Enable input of the first rail                                                   | SYNC                                                        | Yes                |

| 40      | MP_PWRGD     | Power good output of the first rail                                              | SYNC                                                        | Yes                |

|         | GND          | Ground pin                                                                       |                                                             |                    |

注： GND是芯片下面的金属焊盘

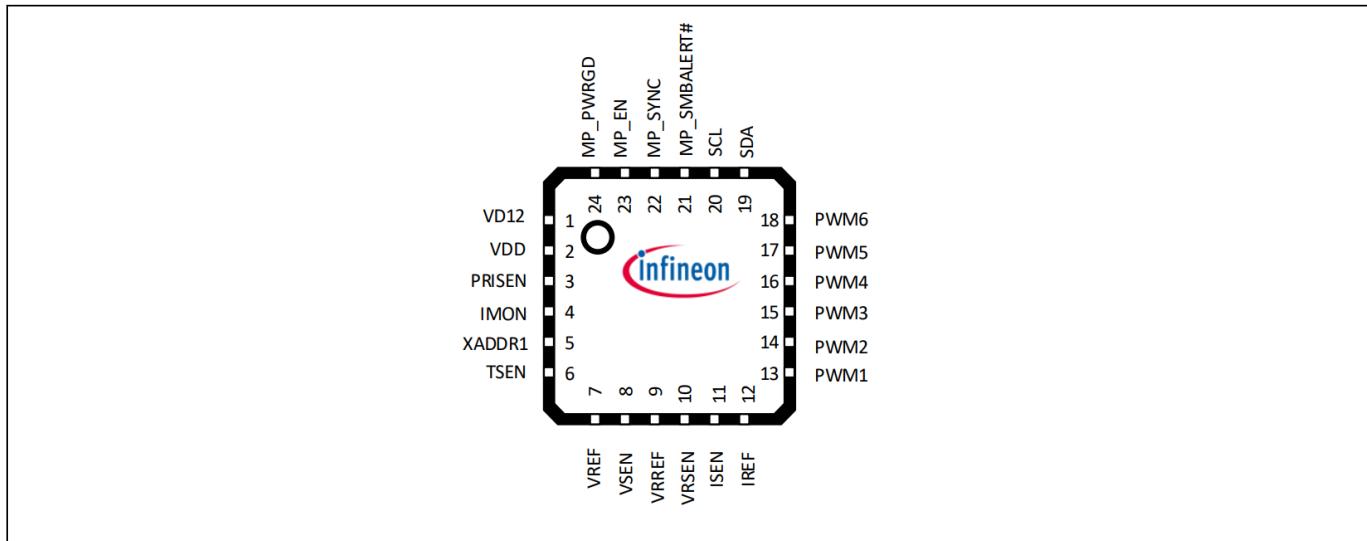

### 3.2 XDPP1100-Q024 封装

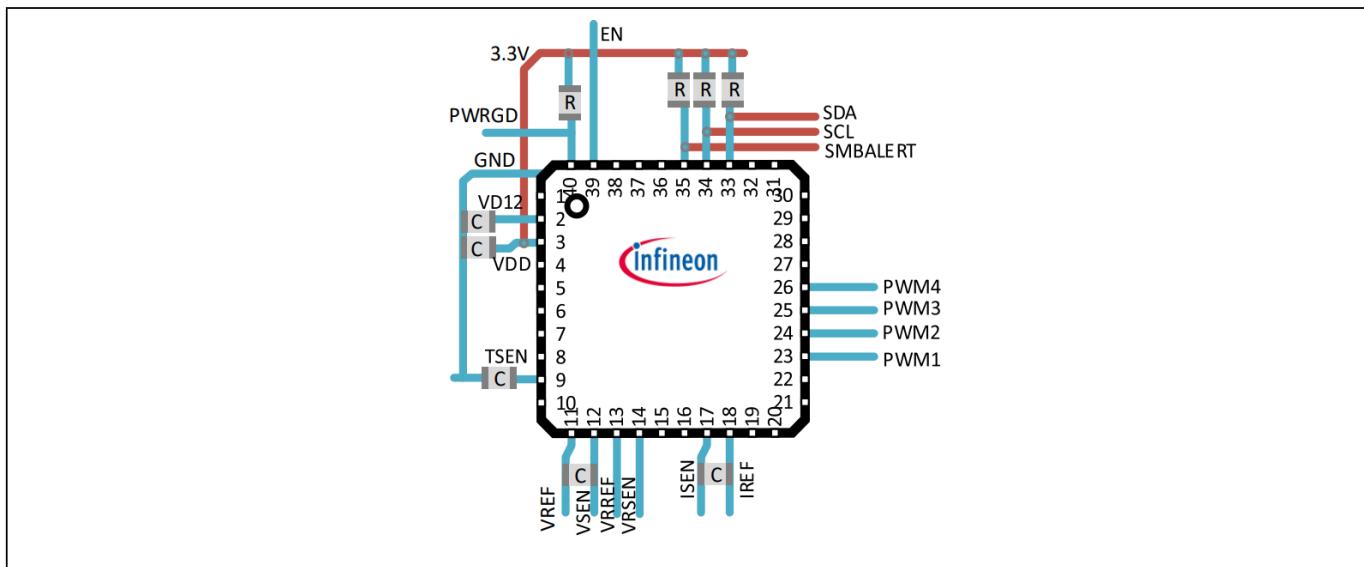

图4

表6 XDPP1100-Q024引脚分配

XDPP1100-Q024引脚定义

| Pin No. | Name    | Primary Assignment                                                               | Alternate assignment  | Configurable GPIO? |

|---------|---------|----------------------------------------------------------------------------------|-----------------------|--------------------|

| 1       | VD12    | 1.2V supply bypass                                                               |                       |                    |

| 2       | VDD     | 3.3V main supply input                                                           |                       |                    |

| 3       | PRISEN  | Primary voltage sensing input                                                    | GPA1                  |                    |

| 4       | MP_IMON | Output current monitor                                                           | GPA2/ SYNC/ FAN1_TACH | Yes                |

| 5       | XADDR1  | Address 1                                                                        | GPA3                  |                    |

| 6       | TSEN    | Temperature sensing input                                                        | GPA4                  |                    |

| 7       | VREF    | Differential voltage sensing, negative input                                     |                       |                    |

| 8       | VSEN    | Differential voltage sensing, positive input                                     |                       |                    |

| 9       | VRREF   | Transformer winding voltage sense, negative input                                |                       |                    |

| 10      | VRSEN   | Transformer winding voltage sense or primary input voltage sense, positive input |                       |                    |

| 11      | ISEN    | Differential current sensing, positive input                                     |                       |                    |

| 12      | IREF    | Differential current sensing, negative input                                     |                       |                    |

| 13      | PWM1    | PWM1 output                                                                      | SYNC                  | Yes                |

| 14      | PWM2    | PWM2 output                                                                      | SYNC                  | Yes                |

| 15      | PWM3    | PWM3 output                                                                      | SYNC                  | Yes                |

| 16      | PWM4    | PWM4 output                                                                      | SYNC                  | Yes                |

## 终端配置和功能

| Pin No. | Name         | Primary Assignment                 | Alternate assignment | Configurable GPIO? |

|---------|--------------|------------------------------------|----------------------|--------------------|

| 17      | PWM5         | PWM5 output                        | SYNC/ UARTRX         | Yes                |

| 18      | PWM6         | PWM6 output                        | SYNC/ UARTTX         | Yes                |

| 19      | SDA          | I <sup>2</sup> C serial data line  |                      |                    |

| 20      | SCL          | I <sup>2</sup> C serial clock line |                      |                    |

| 21      | MP_SMBALERT# | PMBus alert                        | SYNC                 | Yes                |

| 22      | MP_SYNC      | Synchronize pin                    | FAN1_PWM             | Yes                |

| 23      | MP_EN        | Enable input                       | SYNC                 | Yes                |

| 24      | MP_PWRGD     | Power good output                  | SYNC                 | Yes                |

|         | GND          | Ground pin                         |                      |                    |

## 注意

1. GND 是芯片下面的金属焊盘

2. NC：无连接引脚

3. SDA 和 SCL 是开漏 I/O 引脚

4. 所有数字 GPIO 引脚均为 3.3V 电平 CMOS，输出可编程为 CMOS 或开漏

## 规格

## 4 规格

## 4.1 绝对最大额定值

使控制器承受的压力高于 表7中所列的绝对最大额定值 可能会对器件造成永久性损坏。这些仅为绝对应力额定值，并不暗示或建议器件在这些条件下或任何其他超过本规范“建议工作条件”部分规定的条件下正常工作。长时间暴露于绝对最大额定值可能会对器件的运行和可靠性产生不利影响。

表7 绝对最大额定值

| Parameters                     | Symbol    | Min. | Max. | Units | Remarks                         |

|--------------------------------|-----------|------|------|-------|---------------------------------|

| VDD Supply Voltage             | $V_{DD}$  | -0.3 | 4    | V     | Instantaneous voltage, see Note |

|                                |           |      | 3.7  | V     | Continuous voltage              |

| VSEN, VRSEN, BVSEN_BVRSEN      |           | -0.3 | 3.7* | V     | *The lesser of 3.7V or VDD+0.2V |

| VREF, VRREF, BVREF_BVRREF      |           | -0.3 | 0.5  | V     |                                 |

| ISEN, BISEN, IREF, BIREF       |           | -0.3 | 3.7* | V     | *The lesser of 3.7V or VDD+0.2V |

|                                |           | -0.3 | 2.0  | V     | IPS mode                        |

| 1.2V Supply                    | $V_{D12}$ | -1   | 1    | mA    |                                 |

| All other pins                 |           | -0.3 | 3.7* | V     | *The lesser of 3.7V or VDD+0.2V |

| Operating Junction Temperature | $T_J$     | -40  | 150  | °C    |                                 |

| Storage Temperature            | $T_S$     | -65  | 150  | °C    |                                 |

注意： 绝对最大  $VDD$  电源电压为 4.0V，条件是结温范围保持在  $-40^{\circ}\text{C} < T_J < +125^{\circ}\text{C}$  之间，并且产品在使用寿命期间不会在绝对最大  $VDD$  电源电压下累计运行超过 24 小时。

## 4.2 热特性

表8 热阻抗

| Parameters                                          | Symbol           | Value | Units | Remarks    |

|-----------------------------------------------------|------------------|-------|-------|------------|

| Thermal Resistance, Junction to Ambient, at 0 lfm   | $R_{\theta JA}$  | 30.3  | °C/W  | QFN-40 6x6 |

|                                                     |                  | 53.5  |       | QFN-24 4x4 |

| Thermal Resistance, Junction to Ambient, at 200 lfm | $R_{\theta JA}$  | 26.2  | °C/W  | QFN-40 6x6 |

|                                                     |                  | 36.9  |       | QFN-24 4x4 |

| Thermal Resistance, Junction to Ambient, at 500 lfm | $R_{\theta JA}$  | 23.4  | °C/W  | QFN-40 6x6 |

|                                                     |                  | 30.3  |       | QFN-24 4x4 |

| Thermal Resistance, Junction to Case (bottom)       | $R_{\theta JCB}$ | 1.3   | °C/W  | QFN-40 6x6 |

|                                                     |                  | 3.6   |       | QFN-24 4x4 |

| Thermal Resistance, Junction to Case (top)          | $R_{\theta JCT}$ | 18.9  | °C/W  | QFN-40 6x6 |

|                                                     |                  | 33.1  |       | QFN-24 4x4 |

## 规格

### 4.3 推荐运行条件

为了正常运行，应在建议的条件下使用该设备。

**表 9 推荐运行条件**

| Parameters           | Symbol   | Min. | Nom. | Max. | Units | Remarks |

|----------------------|----------|------|------|------|-------|---------|

| Supply Voltage       | $V_{DD}$ | 2.97 | 3.3  | 3.63 | V     |         |

| Junction Temperature | $T_J$    | -40  | 25   | 125  | °C    |         |

### 4.4 电气特性

$V_{DD}=2.97\text{ V}$  至  $3.63\text{ V}$ ,  $1\text{ }\mu\text{F}$  电容从  $VD12$  到  $GND$ ,  $T_J=-40\text{ }^{\circ}\text{C}$  至  $125\text{ }^{\circ}\text{C}$ , 除非另有说明。

**表 10 电源部分电气特性**

| Parameters                  | Symbol             | Min. | Typ. | Max. | Units | Remarks                                                                      |

|-----------------------------|--------------------|------|------|------|-------|------------------------------------------------------------------------------|

| Supply current              | $I_{DD0}$          |      | 11   | 16.5 | mA    | Both loops in off mode                                                       |

| Supply current              | $I_{DD1}$          |      | 21   |      |       | Single-loop operation, 4<br>PWMS switching at 250<br>kHz<br>without any load |

| Supply current              | $I_{DD2}$          |      | 24   |      |       | Dual-loop operation, all 12<br>PWMS switching at 250 kHz<br>without any load |

| $V_{DD}$ power on threshold | $V_{DD\text{ on}}$ |      | 2.78 | 2.95 | V     |                                                                              |

**表 11 电压 ADC AFE1 部分**

| Parameters                       | Symbol   | Min. | Typ.  | Max. | Units | Remarks                                                                                                                                                    |

|----------------------------------|----------|------|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input differential voltage range |          | 0.25 |       | 2.1  | V     | Voltage below 0.5 V is not production tested                                                                                                               |

| Error voltage digital resolution |          |      | 1.25  |      | mV    |                                                                                                                                                            |

| Input impedance                  | $R_{EA}$ |      | > 1   |      | MΩ    |                                                                                                                                                            |

| Sample rate                      |          |      | 100   |      | MHz   |                                                                                                                                                            |

| VS ADC Accuracy (Note 5)         |          | -1   | ±0.75 | 1    | %     | Setpoint 1.2 V to 2.1 V,<br>$-40\text{ }^{\circ}\text{C} < T_A < 125\text{ }^{\circ}\text{C}$ , $2.97\text{ V} < V_{DD} < 3.63\text{ V}$ , Typ = $3\sigma$ |

|                                  |          | -1.4 | ±1.0  | 1.4  | %     | Setpoint 1.0 V,<br>$-40\text{ }^{\circ}\text{C} < T_A < 125\text{ }^{\circ}\text{C}$ , $2.97\text{ V} < V_{DD} < 3.63\text{ V}$ , Typ = $3\sigma$          |

|                                  |          | -1.8 | ±1.2  | 1.8  | %     | Setpoint 0.8 V,<br>$-40\text{ }^{\circ}\text{C} < T_A < 125\text{ }^{\circ}\text{C}$ , $2.97\text{ V} < V_{DD} < 3.63\text{ V}$ , Typ = $3\sigma$          |

|                                  |          |      | ±0.45 |      | %     | Setpoint 1.2 V to 2.1 V,<br>$T_A = 25\text{ }^{\circ}\text{C}$ , $V_{DD} = 3.3\text{ V}$ , Typ = $3\sigma$                                                 |

|                                  |          |      | ±0.65 |      | %     | Setpoint 1.0 V,<br>$T_A = 25\text{ }^{\circ}\text{C}$ , $V_{DD} = 3.3\text{ V}$ , Typ = $3\sigma$                                                          |

## 规格

| Parameters | Symbol | Min. | Typ.  | Max. | Units | Remarks                                                                                                                                   |

|------------|--------|------|-------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

|            |        |      | ±0.9  |      | %     | Setpoint 0.8 V,<br>$T_A = 25^\circ\text{C}$ , $V_{DD} = 3.3 \text{ V}$ , Typ =<br>$3\sigma$                                               |

|            |        |      | ±10.5 |      | mV    | Setpoint 0.25 V to 0.5 V,<br>$-40^\circ\text{C} < T_A < 125^\circ\text{C}$ , $2.97 \text{ V} < V_{DD} < 3.63 \text{ V}$ , Typ = $3\sigma$ |

表 12 电流 ADC AFE2 部分 (高增益)

| Parameters                       | Symbol       | Min. | Typ. | Max. | Units | Remarks                                      |

|----------------------------------|--------------|------|------|------|-------|----------------------------------------------|

| Input differential voltage range |              | -22  |      | 22   | mV    | Voltage below -3 mV is not production tested |

| Error voltage digital resolution |              |      | 100  |      | µV    |                                              |

| Input impedance                  | $R_{EA}$     |      | > 1  |      | MΩ    |                                              |

| IS ADC Offset                    | $V_{OFFSET}$ | -4   |      | 4    | LSB   |                                              |

| Sample rate                      |              |      | 25   |      | MHz   |                                              |

| IS ADC accuracy                  |              | -4   | ±2.7 | 4    | %     | 11 mV differential input,<br>Typ = $3\sigma$ |

|                                  |              | -3.5 | ±2.4 | 3.5  | %     | 22 mV differential input,<br>Typ = $3\sigma$ |

表 13 电流 ADC AFE2 部分 (低增益)

| Parameters                       | Symbol       | Min. | Typ. | Max. | Units | Remarks                                       |

|----------------------------------|--------------|------|------|------|-------|-----------------------------------------------|

| Input differential voltage range |              | -280 |      | 395  | mV    | Voltage below -50 mV is not production tested |

| Error voltage digital resolution |              |      | 1.45 |      | mV    |                                               |

| Input impedance                  | $R_{EA}$     |      | > 1  |      | MΩ    |                                               |

| IS ADC Offset                    | $V_{OFFSET}$ | -2.5 |      | 2.5  | LSB   |                                               |

| Sample rate                      |              |      | 25   |      | MHz   |                                               |

| IS ADC accuracy                  |              | -3   | ±1.5 | 3    | %     | 200 mV differential input,<br>Typ = $3\sigma$ |

|                                  |              | -2   | ±1.2 | 2    | %     | 395 mV differential input,<br>Typ = $3\sigma$ |

表 14 电流 ADC AFE2 部分 (IPS 模式)

| Parameters                       | Symbol       | Min. | Typ. | Max. | Units | Remarks                                       |

|----------------------------------|--------------|------|------|------|-------|-----------------------------------------------|

| Input common voltage range       |              | 1.11 |      | 1.3  | V     |                                               |

| Input differential voltage range |              | -200 |      | 425  | mV    | Voltage below -50 mV is not production tested |

| Error voltage digital resolution |              |      | 1.45 |      | mV    |                                               |

| Input impedance                  | $R_{EA}$     |      | > 1  |      | MΩ    |                                               |

| IS ADC Offset                    | $V_{OFFSET}$ | -2.5 |      | 2.5  | LSB   |                                               |

| Sample rate                      |              |      | 25   |      | MHz   |                                               |

| IS ADC accuracy                  |              | -3   | ±1.4 | 3    | %     | 200 mV differential input,<br>Typ = $3\sigma$ |

|                                  |              | -1.7 | ±1.1 | 1.7  | %     | 395 mV differential input,<br>Typ = $3\sigma$ |

## 规格

表 15 通用 ADC AFE3 部分

| Parameters                       | Symbol       | Min. | Typ.    | Max. | Units | Remarks |

|----------------------------------|--------------|------|---------|------|-------|---------|

| Input differential voltage range |              |      | 0 - 1.2 |      | V     |         |

| Error voltage digital resolution |              |      | 2.344   |      | mV    |         |

| Input impedance                  | $R_{EA}$     |      | > 1     |      | MΩ    |         |

| TS ADC offset error              | $V_{OFFSET}$ | -2   |         | 2    | LSB   |         |

| Sample rate                      |              |      | 1       |      | MHz   |         |

| TS ADC Gain error                |              | -1   |         | 1    | %     |         |

表 16 IMON DAC 部分

| Parameters                | Symbol | Min. | Typ.  | Max. | Units | Remarks          |

|---------------------------|--------|------|-------|------|-------|------------------|

| Output current range      |        |      | 0-640 |      | μA    |                  |

| Output current resolution |        |      | 10    |      | μA    |                  |

| TSIDAC accuracy           |        | -3   |       | 3    | %     | Tested at 100 μA |

表 17 XADDR1、XADDR2 引脚

| Parameters          | Symbol | Min. | Typ.  | Max. | Units | Remarks |

|---------------------|--------|------|-------|------|-------|---------|

| Current measurement |        |      | 0-640 |      | μA    |         |

表 18 GPIO 输入/输出 (FAULT1/2、IMON、PWM1-5、PWM7-10、PWM12、EN、BEN、SYNC)

| Parameters                | Symbol   | Min. | Typ. | Max. | Units | Remarks                  |

|---------------------------|----------|------|------|------|-------|--------------------------|

| Low-level output voltage  | $V_{OL}$ |      |      | 0.4  | V     | $I_{OL} = 5 \text{ mA}$  |

| High-level output voltage | $V_{OH}$ | 2.6  |      |      |       | $I_{OH} = -5 \text{ mA}$ |

| Low-level input voltage   | $V_{IL}$ |      |      | 1.0  |       |                          |

| High-level input voltage  | $V_{IH}$ | 2.1  |      |      |       |                          |

| Leakage current           | $I_{OZ}$ | -1   |      | 1    |       | μA                       |

表 19 GPIO 输入/输出 (PWRGD、BPWRGD、PWM6、PWM11)

| Parameters                | Symbol   | Min.    | Typ. | Max.    | Units | Remarks                  |

|---------------------------|----------|---------|------|---------|-------|--------------------------|

| Low-level output voltage  | $V_{OL}$ |         |      | 0.4     | V     | $I_{OL} = 5 \text{ mA}$  |

| High-level output voltage | $V_{OH}$ | 2.6     |      |         |       | $I_{OH} = -5 \text{ mA}$ |

| Low-level input voltage   | $V_{IL}$ |         |      | 0.3 VDD |       |                          |

| High-level input voltage  | $V_{IH}$ | 0.7 VDD |      |         |       |                          |

| Leakage current           | $I_{OZ}$ | -1      |      | 1       |       | μA                       |

表 20 SDA、SCL、SMBALERT 引脚

| Parameters               | Symbol    | Min. | Typ. | Max. | Units | Remarks                   |

|--------------------------|-----------|------|------|------|-------|---------------------------|

| Output low voltage       | $V_{OL}$  |      |      | 0.4  | V     | $I_{OL} = 20 \text{ mA}$  |

| Low-level input voltage  | $V_{IL}$  |      |      | 1.0  |       |                           |

| High-level input voltage | $V_{IH}$  | 2.1  |      |      |       | Configured as 3.3V buffer |

| Low-level input voltage  | $V_{IL}$  |      |      | 0.6  |       |                           |

| High-level input voltage | $V_{IH}$  | 1.35 |      |      |       | Configured as 1.8V buffer |

| Leakage current          | $I_{OZ}$  | -1   |      | 1    | μA    |                           |

| Pin capacitance          | $C_{PIN}$ |      | 1.5  |      | pF    |                           |

## 规格

表 21 系统性能

| Parameters                       | Symbol | Min. | Typ.     | Max. | Units | Remarks |

|----------------------------------|--------|------|----------|------|-------|---------|

| Processor master clock           |        |      | 100      |      | MHz   |         |

| Internal oscillator frequency    |        | 190  | 200      | 210  | MHz   |         |

| Switching Frequency              | Fsw    |      | 100-2000 |      | kHz   |         |

| Switching Period time resolution |        |      | 20       |      | ns    |         |

| Sync Frequency range             |        |      | +/-6.25  |      | %     |         |

表 22 温度传感器

| Parameters                              | Symbol | Min. | Typ.    | Max. | Units | Remarks                                                                 |

|-----------------------------------------|--------|------|---------|------|-------|-------------------------------------------------------------------------|

| Input Voltage Range                     |        |      | 0 – 1.2 |      | V     | ATSEN, BTSEN                                                            |

| Bias Current                            |        |      | 100     |      | µA    | Source current to measure external NTC or PTC resistor, can be disabled |

| Accuracy of internal temperature sensor |        |      | ±5      |      | °C    |                                                                         |

注意:

5. VS ADC 精度适用于VSEN 和BVSEN\_BVRSEN 电压检测

## 功能概述

# 5 功能概述

## 5.1 简介

隔离式 DC-DC 电源转换器定义为使用变压器在转换器的输入和输出端之间提供电气隔离的电源转换器。控制器可以放置在变压器的初级侧并直接连接到输入电压，也可以放置在变压器的次级侧。在初级侧控制的情况下，通常使用模拟控制器，因为其成本低、保护功能简单而有效、电压前馈能力强，并且经过数十年的行业使用验证，具有可靠性。

然而，近年来，数字电源转换方法在电信和计算等主要应用领域越来越受欢迎。这些应用程序需要系统级通信(即PMBus) 和精确遥测技术，因此基于数字控制器的转换器更具吸引力。数字电源控制器通常在变压器的次级侧实现，以减少隔离电路。与模拟 PWM 控制器不同，数字控制器提供数字 PWM，并且需要用于功率 MOSFET 和辅助电源的外部栅极驱动器。

XDPP1100 是一款灵活且功能丰富的数字次级侧控制器，针对隔离式 DC-DC 应用进行了优化，有助于以最少的元件数量进行设计，并通过基于微控制器的子系统最大限度地提高系统灵活性。XDPP1100 旨在实现灵活性，并为基于变压器的隔离式 DC-DC 转换器和非隔离式拓扑提供出色的数字控制。它适用于所有主要的固定频率拓扑：脉冲宽度调制 (PWM) 半桥 (HB)、PWM 全桥 (FB)、相移全桥 (PSFB)、有源钳位正激 (ACF)、开环固定频率谐振半桥或全桥 (FF LLC)、非隔离式降压、升压和降压-升压。XDPP1100 支持上述任何拓扑的交错操作。双环路版本 XDPP1100-Q040 还提供后降压或后升压调节。控制环路 PID 数字滤波器和补偿功能已集成，可通过 I<sup>2</sup>C 端口进行编程。行业标准 PMBus 接口还提供对众多监控和系统控制功能的访问。集成的 ARM COTEX™ M0 微控制器和内置非易失性存储器提供丰富的编程和功能定制能力，例如集成环路滤波器、PWM 信号时序、非线性瞬态抑制方案、软启动时序和排序。XDPP1100 需要 3.3 V 辅助电源才能运行。

### 5.1.1 Arm® Cortex® M0 核心

XDPP1100 芯片嵌入了最小的ARM处理器——ARM® Cortex® -M0 处理器。它是一款具有成本竞争力的高性能 32 位处理器，具有极低的门数、最小的功率要求和减少的代码占用空间。它是一个优化的中断控制器，允许在硬实时应用中使用。XDPP1100 ARM® Cortex® -M0 处理器时钟频率为 100 MHz。

### 5.1.2 存储器

XDPP1100 具有 80 kB 启动 ROM，其中包含用于 PMBUS 通信的初始固件启动例程。此启动 ROM 在上电复位检查后执行。XDPP1100 还支持自定义启动程序，允许从一次性可编程 (OTP) 非易失性存储器 (NVM) 执行备用启动例程。控制寄存器可通过串行通信 (I<sup>2</sup>C) 总线在现场重新编程，并存储到 OTP NVM 中。对于运行时数据存储和暂存器，提供 32 kB RAM。

## 功能概述

### 5.1.3 通信端口

该设备提供主 I<sup>2</sup>C、次 I<sup>2</sup>C 和 UART 通信端口。

#### 5.1.3.1 I<sup>2</sup>C/ PMBus

设备中的所有工作参数均可通过主 I<sup>2</sup>C 串行接口（SDA、SCL）进行配置。辅助 I<sup>2</sup>C 接口提供额外的通信端口，例如用于访问外部存储器。SDA 和 SCL 支持两种逻辑电平：3.3 V 和 1.8 V。该设备支持三种 I<sup>2</sup>C 速度：标准 (100 kHz)、快速 (400 kHz) 以及快速模式加 (1 MHz) 工作频率。I<sup>2</sup>C 的速度可通过图形用户界面 (GUI) 配置。

XDPP1100 器件符合 PMBus™ 电源系统管理协议规范修订版

1.3.1. I<sup>2</sup>C/PMBus 接口允许用户配置设备以及监控故障状态、电压、电流、功率和温度遥测。

#### 5.1.3.2 UART

该设备包含一个全双工通用异步接收器/发送器 (UART) 接口。波特率、字长、缓冲区深度、IrDA、调制解调器操作可通过寄存器配置。还可以设置环回功能以进行固件验证。

UARTTX 和 UARTRX 引脚组可使用已分配的 GPIO 引脚进行配置。参见表 26 了解 GPIO 引脚列表以及每个引脚的预定义功能。

#### 5.1.3.3 地址偏移

XDPP1100-Q040 使用两个引脚 XADDR1 和 XADDR2 进行 I<sup>2</sup>C/PMBus 地址解码。XDPP1100-Q024 有一个地址引脚 XADDR1，当需要两个 XADDR 引脚时，可以通过固件补丁修改 IMON 引脚的功能以进行地址解码。固件补丁示例可在英飞凌网站上找到。

I<sup>2</sup>C 和 PMBus 的基地址应通过 MFR PMBus 命令 0xC9 FW\_CONFIG\_PMBUS 配置。I<sup>2</sup>C 和 PMBus 的地址偏移可以通过 0xC9 的地址偏移字段配置，也可以通过将 XADDR1 或 XADDR2 引脚上的电阻接地，通过 XADDR1 和 XADDR2 引脚解码。要使用电阻地址偏移，必须通过 FW\_CONFIG\_PMBUS 启用相应的位。XDPP1100 在初始化状态下测量 XADDR 电阻偏移，不支持动态修改。FW\_CONFIG\_PMBUS 的配置必须存储在 OTP 存储器中，并且需要重新开启 VDD 才能使修改生效。

XDPP1100 设备支持 16 价或 8 价地址表，如表 23 和表 25 所示。为了正确设置设备地址，必须连接容差为 1% 的电阻。编程电阻的设计允许使用 E12 电阻，以节省系统成本。推荐的 E12 电阻串联组合如表 24 所示。

**表 23 16 段解码的 I<sup>2</sup>C/PMBus 地址偏移**

| Resistor-to-GND (1%) | Address offset |

|----------------------|----------------|

| XADDR1, or<br>XADDR2 | 780Ω           |

|                      | 1.10 kΩ        |

|                      | 1.50 kΩ        |

|                      | 2.02 kΩ        |

|                      | 2.70 kΩ        |

## 功能概述

|                    |      |

|--------------------|------|

| 3.52 kΩ            | 0x0A |

| 4.70 kΩ            | 0x09 |

| 6.07 kΩ            | 0x08 |

| 8.00 kΩ            | 0x07 |

| 10.20 kΩ           | 0x06 |

| 13.20 kΩ           | 0x05 |

| 17.20 kΩ           | 0x04 |

| 22.47 kΩ           | 0x03 |

| 29.20 kΩ           | 0x02 |

| 39.00 kΩ           | 0x01 |

| 56.00 kΩ (or open) | 0x00 |

表 24 XADDR 16 段解码的推荐 E12 电阻

| XADDR Resistance (Ω) | R1    | R2   |

|----------------------|-------|------|

| 780                  | 680   | 100  |

| 1100                 | 1000  | 100  |

| 1500                 | 1500  | 0    |

| 2020                 | 1800  | 220  |

| 2700                 | 2700  | 0    |

| 3520                 | 3300  | 220  |

| 4700                 | 4700  | 0    |

| 6070                 | 5600  | 470  |

| 8000                 | 6800  | 1200 |

| 10200                | 10000 | 200  |

| 13200                | 12000 | 1200 |

| 17200                | 15000 | 2200 |

| 22470                | 22000 | 470  |

| 29200                | 27000 | 2200 |

| 39000                | 39000 | 0    |

| 56000                | 56000 | 0    |

如果只需要 8 段解码，XDPP1100 也可以按照表 25 进行配置。所有电阻均为 1% E12 电阻。寄存器 xv\_decode\_sel 用于配置 xValent 的选择。

表 25 8 段解码的 I<sup>2</sup>C/PMBus 地址偏移

| Resistor-to-GND (1%) | Address offset     |

|----------------------|--------------------|

| XADDR1, or XADDR2    | 1.20 kΩ            |

|                      | 1.80 kΩ            |

|                      | 2.70 kΩ            |

|                      | 3.90 kΩ            |

|                      | 6.80 kΩ            |

|                      | 10.00 kΩ           |

|                      | 18.00 kΩ           |

|                      | 47.00 kΩ (or Open) |

## 功能概述

### 5.1.4 GPIO

XDPP1100 提供多达 16 个通用输入/输出 (GPIO)。每个 GPIO 引脚均可通过软件配置为输入（带或不带上拉或下拉）或输出（推挽或开漏）。所有 GPIO 引脚均与其他功能共享。如果需要遵循特定功能，可以锁定 I/O 配置。GPIO 配置由名为 xxxx\_func 的每个 GPIO 引脚的功能寄存器和 FW\_CONFIG\_PMBUS 命令进行编程。

表 26 显示多用途GPIO功能映射。

**表 26      GPIO 多用途引脚**

| Name         | Function 0              | Function 1  | Function 2  | Function 3 | Function 4  | Function 5  | Function 6 | Function 7 |

|--------------|-------------------------|-------------|-------------|------------|-------------|-------------|------------|------------|

| MP_FAULT1    | IO:GPIO0[2]<br>(FAULT1) | IO:GPIO0[2] | IO:GPIO1[2] | IO:SYNC    | O:FAN2_PWM  | IO:SDA2     | UARTRX     | na         |

| MP_FAULT2    | IO:GPIO1[2]<br>(FAULT2) | IO:GPIO0[2] | IO:GPIO1[2] | IO:SYNC    | I:FAN2_TACH | IO:SCL2     | UARTTX     | na         |

| MP_IMON      | A:IMON                  | IO:GPIO0[3] | IO:GPIO1[3] | IO:SYNC    | I:FAN1_TACH | na          | na         | na         |

| PWM11        | O:PWM11                 | IO:GPIO0[6] | IO:GPIO1[6] | IO:SYNC    | O:FAN1_PWM  | na          | na         | na         |

| PWM12        | O:PWM12                 | IO:GPIO0[7] | IO:GPIO1[7] | IO:SYNC    | I:FAN1_TACH | na          | na         | na         |

| PWM1         | O:PWM1                  | IO:GPIO0[5] | IO:GPIO1[5] | IO:SYNC    | na          | na          | na         | na         |

| PWM2         | O:PWM2                  | IO:GPIO0[7] | IO:GPIO1[7] | IO:SYNC    | na          | na          | na         | na         |

| PWM3         | O:PWM3                  | IO:GPIO0[1] | IO:GPIO1[1] | IO:SYNC    | na          | na          | na         | na         |

| PWM4         | O:PWM4                  | IO:GPIO0[2] | IO:GPIO1[2] | IO:SYNC    | na          | na          | na         | na         |

| PWM5         | O:PWM5                  | IO:GPIO0[3] | IO:GPIO1[3] | IO:SYNC    | UARTRX      | na          | na         | na         |

| PWM6         | O:PWM6                  | IO:GPIO0[4] | IO:GPIO1[4] | IO:SYNC    | UARTTX      | na          | na         | na         |

| PWM9         | O:PWM9                  | IO:GPIO0[4] | IO:GPIO1[4] | IO:SYNC    | na          | na          | na         | na         |

| PWM10        | O:PWM10                 | IO:GPIO0[5] | IO:GPIO1[5] | IO:SYNC    | na          | na          | na         | na         |

| PWM7         | O:PWM7                  | IO:GPIO0[5] | IO:GPIO1[5] | IO:SYNC    | O:FAN2_PWM  | na          | na         | na         |

| PWM8         | O:PWM8                  | IO:GPIO0[6] | IO:GPIO1[6] | IO:SYNC    | I:FAN2_TACH | na          | na         | na         |

| MP_SMBALERT# | IO:SMBALERT_N           | IO:GPIO0[6] | IO:GPIO1[6] | IO:SYNC    | IO:GPIO0[7] | IO:GPIO1[7] | na         | na         |

| MP_BEN       | IO:GPIO1[0]<br>(BEN)    | IO:GPIO0[0] | IO:GPIO1[0] | IO:SYNC    | UARTRX      | IO:SDA2     | na         | na         |

| MP_BPWRGD    | IO:GPIO1[1]<br>(BPWRGD) | IO:GPIO0[1] | IO:GPIO1[1] | IO:SYNC    | UARTTX      | IO:SCL2     | na         | na         |

| MP_SYNC      | na                      | IO:GPIO0[7] | IO:GPIO1[7] | IO:SYNC    | O:FAN1_PWM  | na          | na         | na         |

| MP_EN        | IO:GPIO0[0](EN)         | IO:GPIO0[0] | IO:GPIO1[0] | IO:SYNC    | na          | na          | na         | na         |

| MP_PWRGD     | IO:GPIO0[1]<br>(PWRGD)  | IO:GPIO0[1] | IO:GPIO1[1] | IO:SYNC    | na          | na          | na         | na         |

注意:

1. 阴影行表示所有封装中均可提供

2. 以“A:”为前缀的模拟功能

3. 数字输入以“I:”为前缀，输出以“O:”为前缀，输入输出以“IO:”为前缀

4. 按最低引脚编号确定输入优先级（例如，如果 MP\_FAULT1 和 PWM11 均编程为 SYNC，则由于引脚编号较低，输入取自 MP\_FAULT1）

### 5.1.5 寄存器映射

XDPP1100 器件通过加载到控制寄存器中的应用特定参数设置进行配置。控制寄存器映射可以通过 I<sup>2</sup>C 和 PMBus 访问。模块制造商可以使用 I<sup>2</sup>C 设置控制器功能和参数。PMBus 命令允许最终用户定制系统应用。

XDPP1100 GUI 支持对寄存器映射的访问。寄存器映射的详细信息可以在 GUI 安装包附带的寄存器描述文档中找到。

## 功能概述

对于典型的应用，控制寄存器在工厂预先编程并存储在片上非易失性存储器（NVM）中，然后在控制器上电初始化期间下载到控制寄存器中。控制寄存器可以通过串行通信（I2C）总线在现场重新编程并存储到NVM中。XDPP1100 控制器支持多个重新编程周期，可通过 XDPP1100 GUI 或系统编程器软件轻松完成。

除了支持多个重新编程周期之外，XDPP1100 控制器还支持在 NVM 中存储多个配置，其中初始化设置是根据连接到 XADDR 引脚的外部电阻器的值从这些存储的配置之一中选择的。此功能称为多配置。这允许单个配置文件支持多个应用程序，这在系统中使用多个控制器时很有用，但由于它们支持多种类型的输出轨，因此需要不同的配置。通过多配置，XDPP1100 控制器能够存储多达 16 种配置，并且可以根据需要重新编程这些配置。控制器根据存储在配置中的信息来识别要加载的正确配置，即标识应使用多配置的指示位和指向 NVM 中多配置空间位置的指针。

## 5.2 模拟模块和子系统

### 5.2.1 电源

控制器采用单个 +3.3 V (VDD) 电源供电，片上低压差 (LDO) 稳压器在 VD12 引脚产生内部 +1.2 V 电压。VDD 和 VD12 引脚均应有  $1 \mu\text{F}+0.1 \mu\text{F}$  陶瓷旁路电容器用于噪声过滤。将旁路电容尽可能靠近 VDD 和 VD12 引脚放置。请勿对 VD12 引脚施加电压或接地。VD12 引脚也不应用作 1.2 V 参考。

### 5.2.2 振荡器和 PLL

该设备内置一个 200 MHz 内部 PWM 振荡器。XDP 设备配备 6 位插值器，采用 11 位基于时间的周期和频率控制，可提供低至 78.125 ps 的高 PWM 分辨率。XDPP1100 支持的最大脉冲宽度为 10.24  $\mu\text{s}$  ( $2048 \times 5\text{ns}$ )；这将最小开关频率限制为约 100 kHz。最大开关频率为 2MHz，频率分辨率为 20ns。在 20 ns 分辨率下，目标频率无法在 100 kHz 至 2 MHz 范围内线性配置。例如，将开关频率设置为 350 kHz ( $T_s = 2857 \text{ ns}$ )，则开关周期将四舍五入为 352 kHz，为 2840 ns。XDPP1100 GUI 可以帮助用户在使用 FREQUENCY\_SWITCH 命令时找出实际的开关频率。

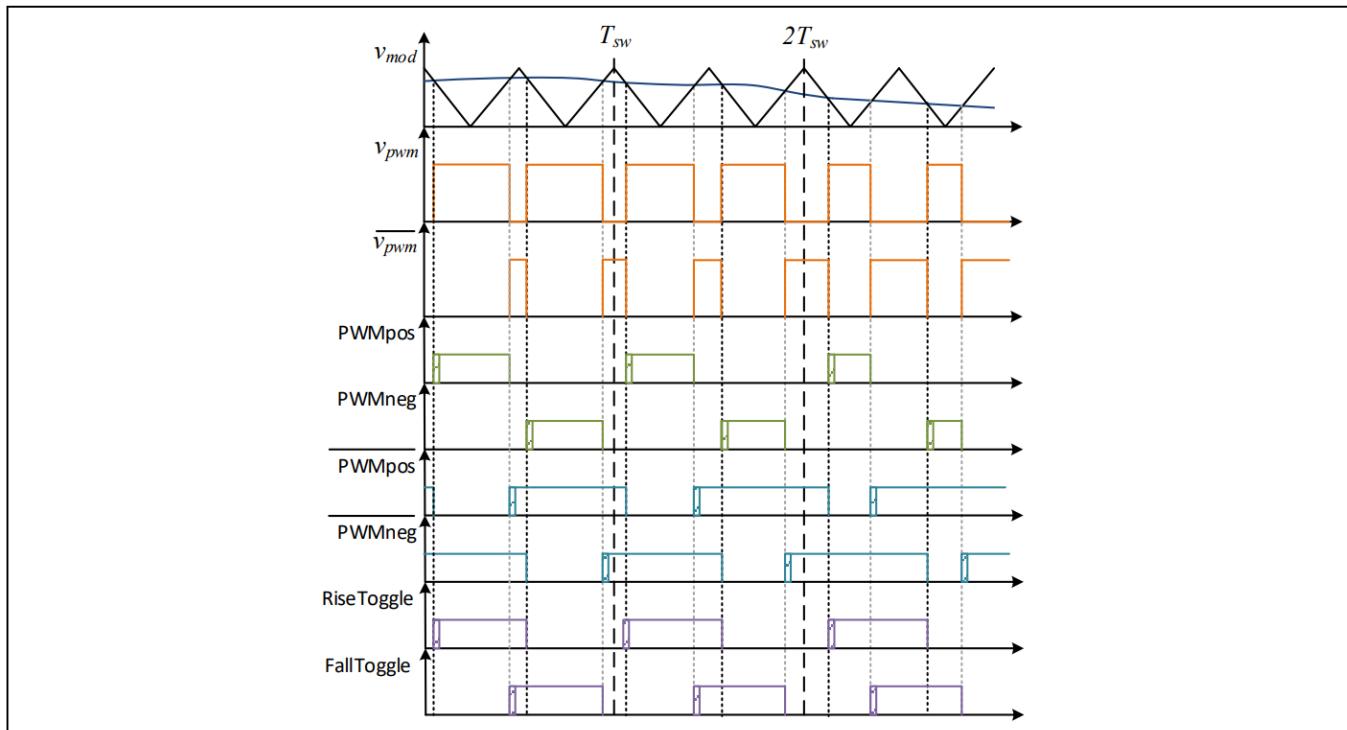

图 5 显示了典型的 PWM 生成波形。上轴显示双边沿调制器 (Vmod) 和补偿误差信号（即 PID 输出）的模拟行为波形。下轴显示生成的 PWM 波形，以及反相 PWM 信号。底部 8 个轴上的信号带有阴影线，表示死区时间应用于信号的位置。

## 功能概述

**图5**      **PWM生成**

死区时间是指从一个开关关闭到另一个开关打开之间的时间量，此时两个开关都处于关闭状态，以防止意外短路情况。实现死区时间的标准方法是使用前沿消隐。PWM发生器的每个信号都能够以1.25 ns 的增量将上升沿消隐 0-318.75 ns 的可编程量。如果需要额外的消隐时间，XDPP1100 还支持调整每个 PWM 的下降沿。死区时间的值在正常运行期间是可以改变的，以优化电源效率。

PWM 输出是 3.3 V 兼容信号，在重置、配置和初始化期间设置为高阻抗。固件完成配置和初始化后，映射到环路以驱动 MOSFET 的 PWM 输出将被拉低。在 PWM 引脚上不强制使用外部下拉电阻。

多用途 MP\_SYNC 引脚可配置为输入，以允许与外部时钟信号同步，或配置为输出，以提供其他转换器同步的时钟。为了获得最佳灵活性，所有 GPIO 引脚都可以配置为 SYNC 引脚。

当 SYNC 引脚配置为输入时，PLL 接收可分配给任一环路的周期信号（在支持双环路操作的封装中）。输入信号将被限制为编程开关频率的 +/-6.25% 以锁定同步时钟。一旦锁定，同步输入信号可以游离至编程频率的 +/- 12.5%。

当斜坡定时器超过编程阈值时，设置 SYNC 信号输出。这允许设置 SYNC 信号的相位。同步功能将提供一个表示同步成功的信号，如果无法同步则会提供一个故障信号。

## 功能概述

## 5.2.3 电压检测 AFE1

XDPP1100 提供 3 个专用高速电压模拟/数字转换器 (ADC) 作为模拟前端 (AFE1)。按照功能，电压检测 AFE1 可以作为电压检测处理器 (VSP) 或者整流电压检测处理器 (VRSP)。

VSP及其相关块的主要功能是：

- 电压 ADC 全速率接口至数字域

- 电压 ADC 增益和偏移调整（数字调整）

- 电压调节（外部电阻分压器）

- 输出电压计算

- 输出过压/欠压保护比较器和故障

- 快速瞬态 (FTR) 模式和 FTR 出口比较器

- 开放式感测保护和故障比较器

- 突发模式和突发模式退出比较器

VRSP及其相关块除了上述功能外，还具有以下功能：

- 带有数字去毛刺器的 200 MHz 边缘比较器

- 测量桥式拓扑偶数半周和奇数半周的  $V_{RECT}$  电压

- 测量非桥式拓扑结构偶数周期的  $V_{RECT}$  电压

- 对测量的偶数和奇数  $V_{RECT}$  电压取平均值

- 磁通平衡电路

- 输入电压处理

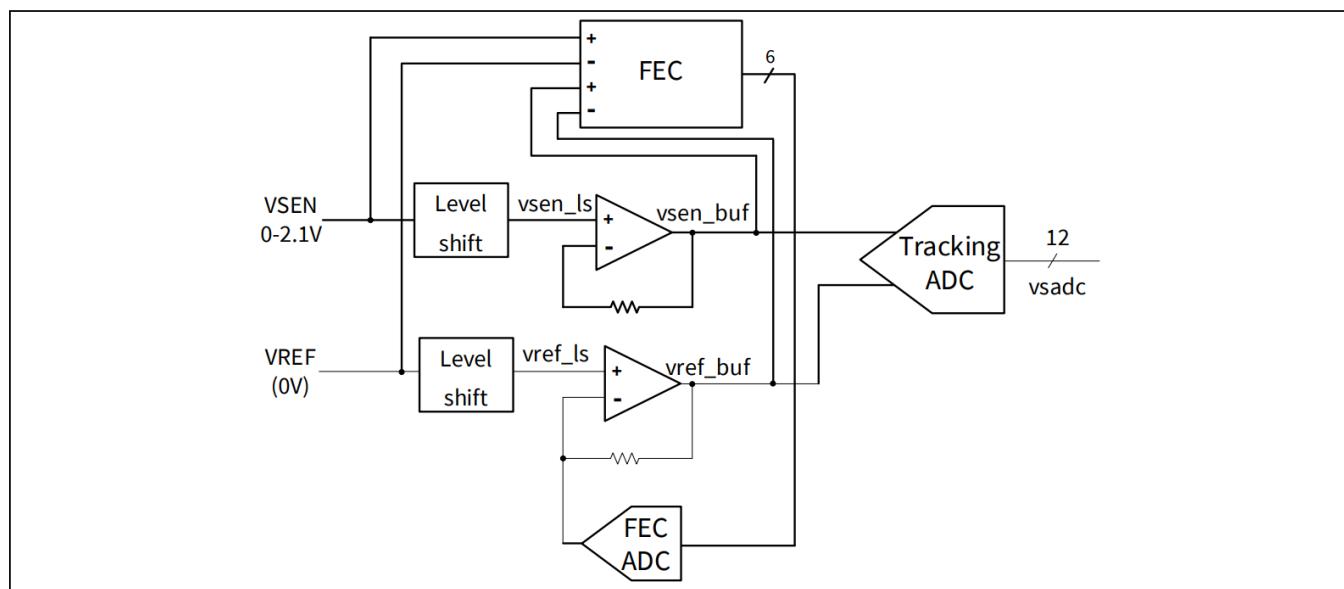

简化的VSADC框图如。

图6 电压检测ADC框图

## 功能概述

电平转换器允许较宽的输入电压范围，0.0 至 2.1V，并提供高输入阻抗。单位增益缓冲器为跟踪 ADC 输入级提供额外的驱动强度。前端失调补偿器 (FEC) 用于减少 AFE 中的温度、应力和寿命失调漂移的影响。

跟踪ADC的简化框图如图7所示。加法放大器放大缓冲差分感测电压与DAC输出电压之间的差值。

加法放大器的输出驱动比较器，比较器的输出决定跟踪积分器下一步的大小和方向。跟踪积分器输出代表模拟到数字转换的感测电压。它还用于驱动 DAC，其输出在加法放大器中相加。

**图7 跟踪ADC框图。**

跟踪 ADC 分辨率为 12 位，输入参考 LSB 权重为 1.25mV。请注意，AFE 输入范围限制为最大 2.1V，这意味着实际仅使用 ADC 输出的低 11 位。对于输出电压感应，将 3 位调制添加到参考电压以实现 156  $\mu$ V 分辨率。

电压检测输入的标称输入阻抗为  $1 \text{ M}\Omega$ 。ADC 的时钟频率为 100 MHz，电压检测前端放大器以 50 MHz 的频率处理电压。无需抗混叠滤波，但添加更高带宽的外部 RC 滤波器网络可能会有所帮助，以增强对可能耦合到电压检测线路上的高频噪声的衰减。该附加滤波器对反馈环路的相位裕度影响极小。如果使用此类附加滤波器，建议使用  $R_{\text{EXT}} = 10 \Omega$  和  $C_{\text{EXT}} = 220 \text{ pF}$  的值。

如果外部反馈回路连接失败，VSEN/BVSEN 能够检测到开路感测线。有关开路感测故障保护的更多详细信息，请参阅应用说明。

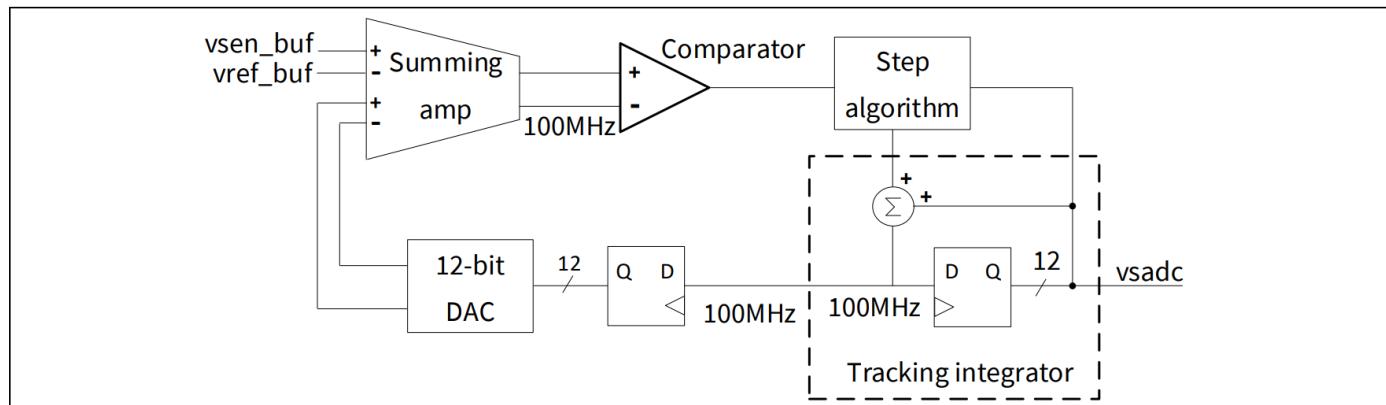

VRSP 负责控制 VRSEN ADC，用于测量整流电压波形 ( $V_{\text{RECT}}$ )。图 8 中的波形说明了如何对  $V_{\text{RECT}}$  波形进行采样。为了强调采样窗口时序的重要性，我们在理想的  $V_{\text{RECT}}$  波形中添加了噪声。AFE1 有一个工作在 200 MHz 时钟频率的边沿检测器。它可以感应  $V_{\text{RECT}}$  波形的上升沿和下降沿。 $T_{\text{detect}}$  波形是边沿检测器逻辑的输出。它检测整流电压波形的上升沿，并在其中添加一些可编程的消隐窗口。消隐时间应配置为长于电压尖峰和振铃持续时间。消隐时间也应设置为长 250ns，以便跟踪ADC 稳定下来。消隐窗口之后，可以对整流电压进行采样（如图中  $T_{\text{sample}}$  波形所示）。VRS 的比较器预设为最后一个周期的值，以最大限度地缩短 ADC 正确跟踪电压所需的时间。当相关 PWM 信号变为低电平时，采样窗口结束。

当 VRSP 用于输入电压感应时，它将检测到包括输入过压和欠压在内的故障和警告。这些由 PMBus 命令设置；并且响应由 CPU 处理。

## 功能概述

图8 VRSP采样窗口

整流电压波形的上升沿和下降沿的时序以及幅度用于变压器保护。例如，在全桥电压模式转换器中， $V_{RECT}$  的时序和幅度用于伏秒磁通平衡。为避免波形失真或时序延迟，在使用  $V_{RECT}$  检测模式时，建议不要在 VRSEN 的输入端添加任何滤波器。

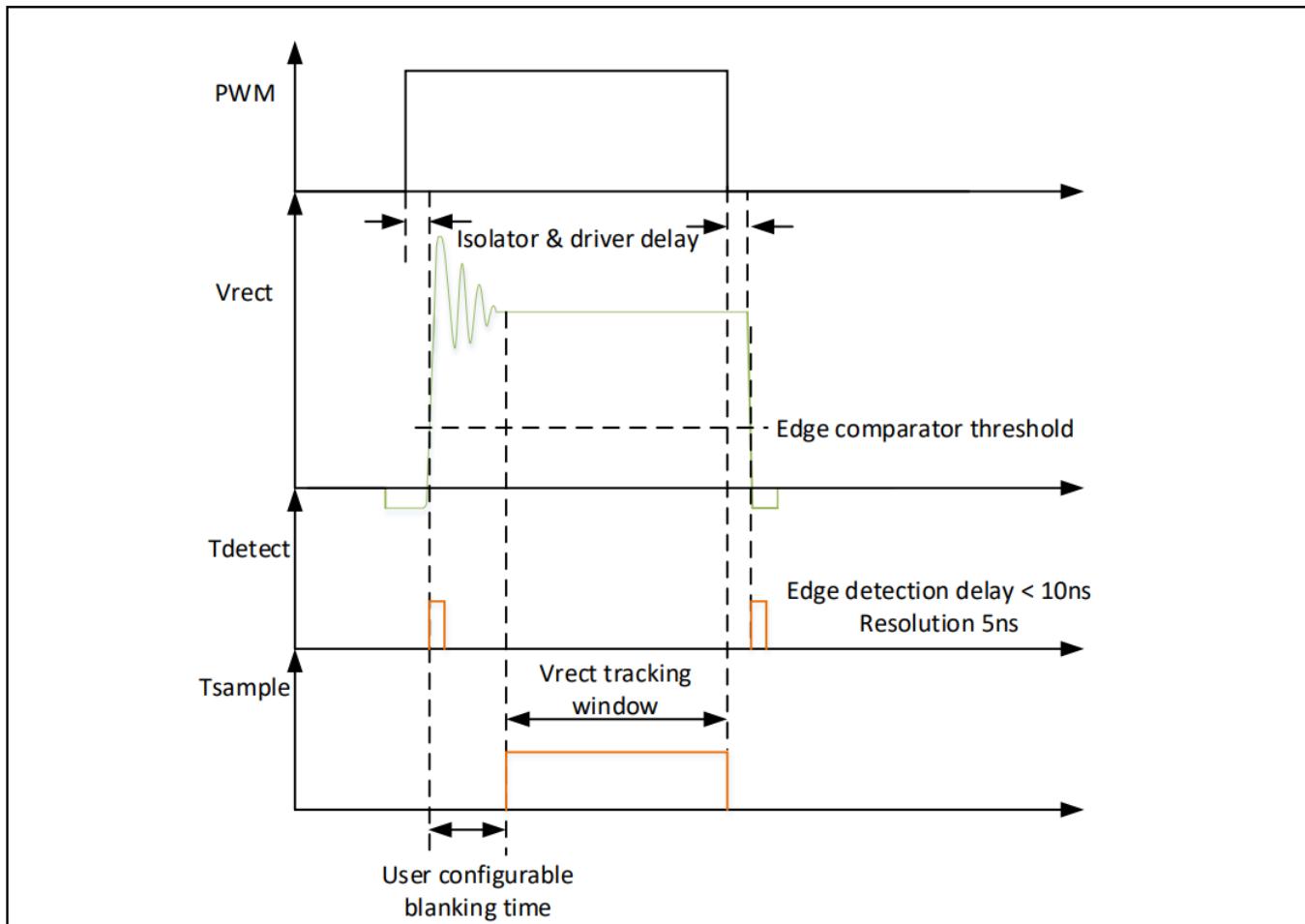

### 5.2.4 电流检测 AFE2

专用差分电流检测 ADC (AFE2) 设计用于通过低欧姆检测电阻或 PCB 铜走线检测输出电流。ISADC (ISEN、BISEN) 是 9.25 位跟踪 ADC，通过电流模拟插值至 13 位。它的工作频率为 25 MHz，可提供高速逐周期峰值电流限制。峰值电流限制比较器工作在 100MHz 时钟频率，为系统提供快速保护。

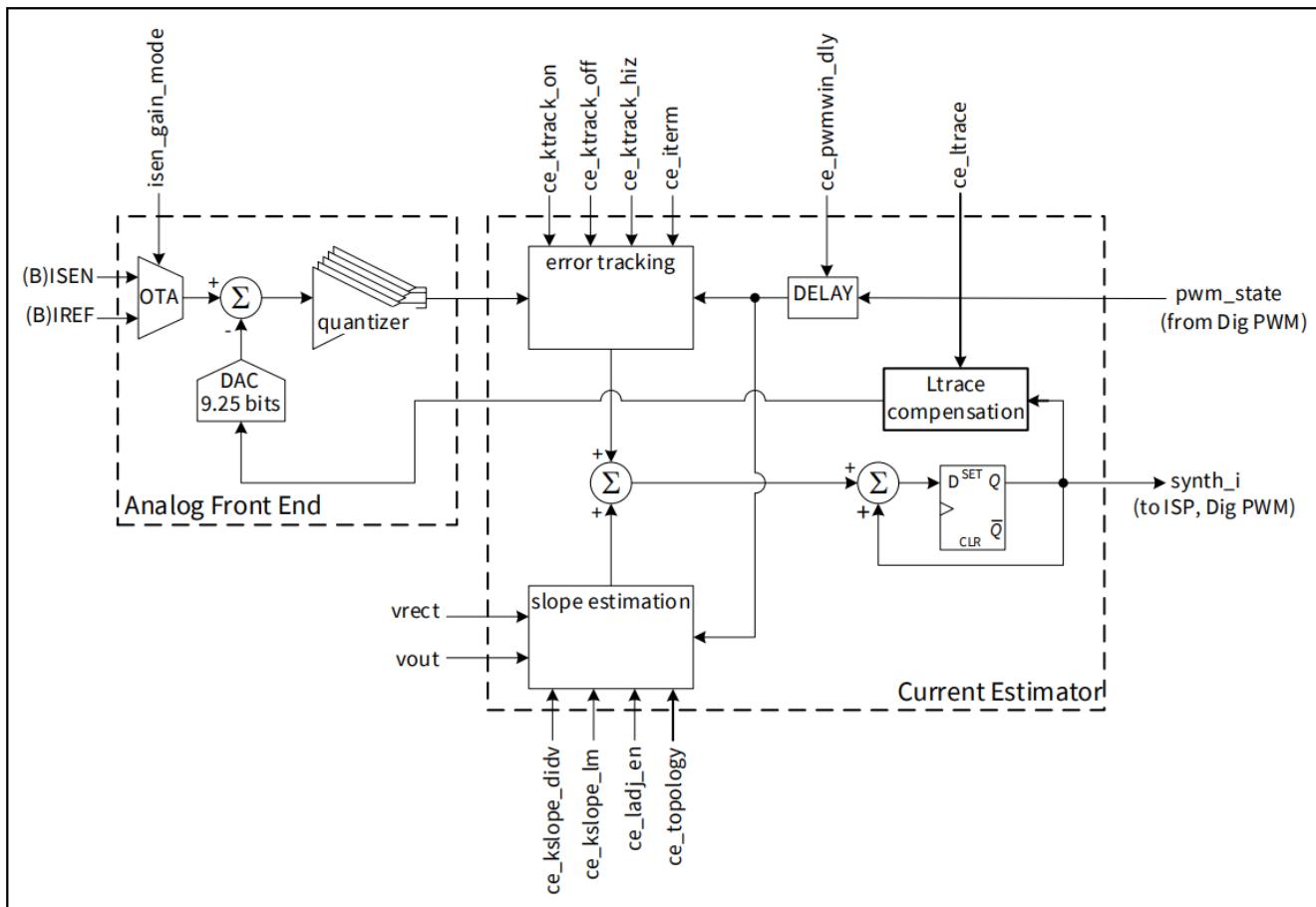

电流检测ADC的简化框图如图9所示。第一个子模块可编程增益放大器 (OTA) 将电流检测电压转换为与 DAC 电流相加的电流。OTA 的增益水平以及电流检测电压的参考电平均可编程。高增益模式为 100  $\mu$ V/LSB，低增益模式为 1.45 mV/LSB。除 IPS 模式外，参考电平均为地。

第二个子模块是 9.25 位 DAC，具有 640 个量化级。然而，部分位元用于失调校正，有效位元较少，具体取决于 OTA 增益设置。各增益设置下 ISADC 的有效输入电压范围如表12，表13和表14所示。

## 功能概述

图9 电流检测ADC的简化框图。

量化器由五个比较器组成，它们产生6级 ( $\pm 1$ 、 $\pm 3$ 、 $\pm 5$ ) 误差跟踪信号，供电流估计器用来校正电流估计。

电流估算器根据电流检测输入引脚配置，提供次级侧电感电流或初级侧电流的数字重建。该电流的形状是通过斜率估计函数获得的。电流估计器的详细信息可以在 XDPP1100 技术参考手册中找到。

如果使用 PCB 铜走线进行电流感应，则应考虑温度补偿来补偿铜走线的温度变化。控制器持续监测温度，并利用此信息根据铜的温度系数以数字方式补偿电阻随温度的变化。温度补偿电流读数也用于确定故障状态。

控制器提供了几种提高电流感应精度的机制。为了减少电路板噪声对电流检测的影响，在 PWM 转换时实施了前沿消隐和后沿消隐时间。消隐时间可配置为 0 至 280 ns。通过使用内部相电流估计器，实现了出色的抗噪能力。根据 PWM 脉冲的状态，控制器不断预测每个单独的相直流和纹波电流。预测的结果与实际测量的相电流相结合，由控制器进行处理。因此，可以滤除测量中的瞬时噪声，而不会丢失宝贵的纹波电流信息。此外，XDPP1100 会进行多次电流测量，并在每个开关周期内计算读数的平均值。到

## 功能概述

提高电流检测精度，XDPP1100还允许补偿电流检测电阻的寄生电感。

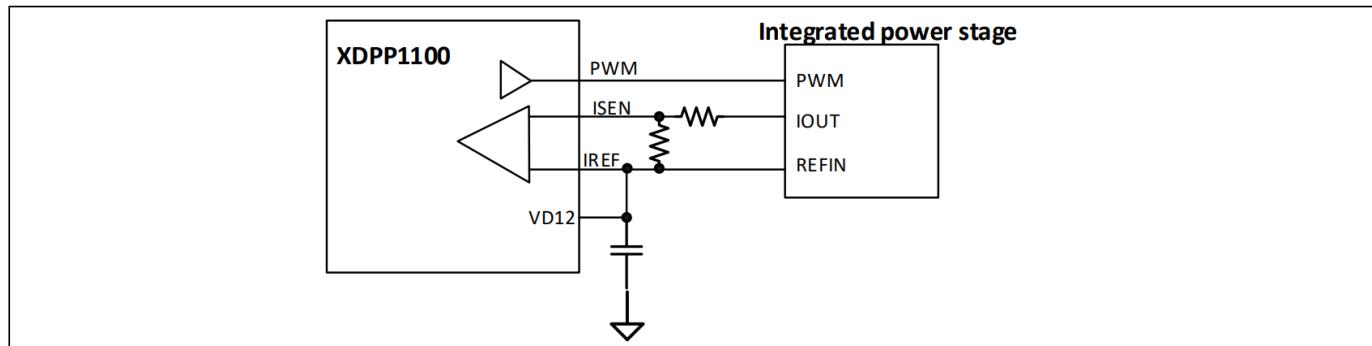

XDPP1100 控制器可配置为与集成功率级 (IPS) 一起运行，该功率级包括集成电流感应功能（例如，英飞凌的IR3555A）。当电流检测设置为 IPS 模式时，应将 1.2 V 共模电压施加到电流参考引脚，如图 10 所示。与传统 DCR 电流检测相比，集成电流检测的优点包括：

1. 卓越的部件间电流感应增益控制：与 PCB 铜走线相比，集成功率级的增益变化要低得多。

2. 卓越的温度电流感应精度：电流镜感应能够理想地跟踪温度范围内的信号。

请注意，只有 PWM6 和 PWM11 支持三态输出。如果集成功率级需要三态输出来关闭两个 MOSFET，以实现 Body-Breaking™ 或降相功能，请使用 PWM6 或 PWM11 引脚驱动功率级。对于其他 PWM 输出，需要更改固件以强制各个 PWM 输出进入 HiZ 模式，从而启用三态输出。

**图10** 集成电流检测

电流检测处理器 (ISP) 及其相关模块的主要功能是：

- 电流 ADC 全速率接口至数字域

- 电流 ADC 增益和偏移调整（数字调整）

- 电流缩放

- 输出电流计算

- 输出电流分流温度补偿

- 输出过流/欠流保护比较器和故障

- 输入电流估算

- 输入过流保护比较器和故障（PCMC 期间）

- 逐周期峰值电流限制

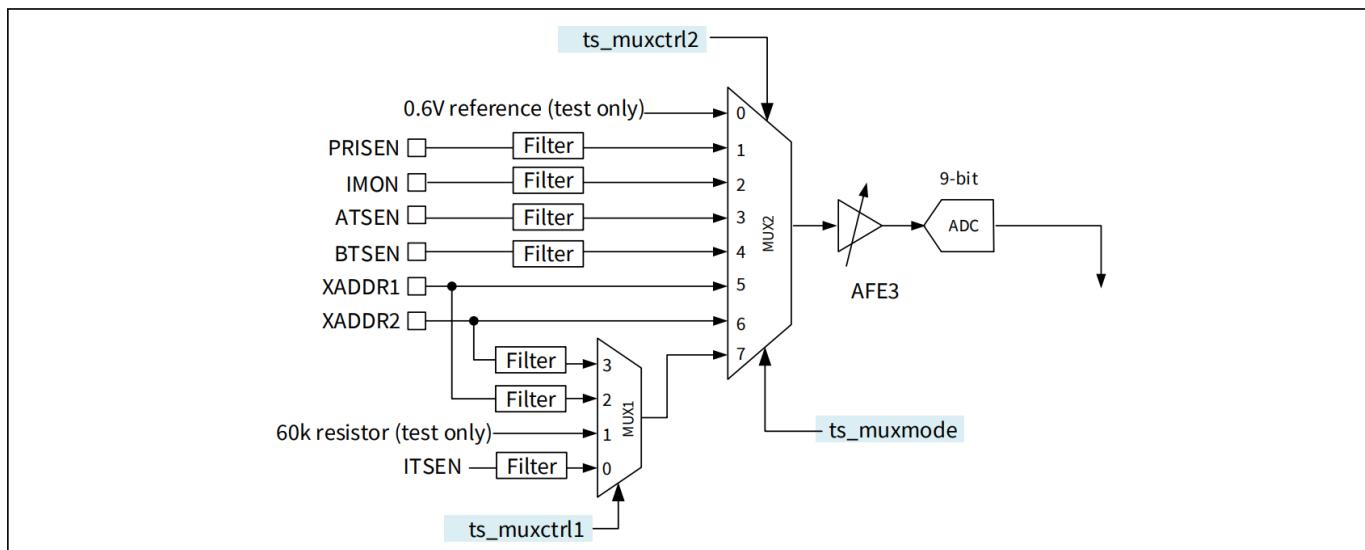

### 5.2.5 通用 AFE3

通用ADC AFE3，也称为遥测ADC (TS ADC)，是一款9位高速模数转换器。该通用ADC的电压分辨率为2.344 mV，采样频率为1 MHz。该通用ADC模块包含8个通道，其中6个可用通道如图11所示。它可以配置为数字化电压、电流、阻抗和温度。

## 功能概述

**图 11 遥测感测块**

通道的转换顺序可以由用户定义，也可以设置为每个多路复用控制寄存器的自动排序。

### 5.2.5.1 IMON 和主动电流均流

IMON 引脚有一个代表输出电流的模拟 DAC 输出。IMON 可用于输出电流监视器，以及用于多个并联模块之间的主动电流平衡。与 loop0 的输出电流成比例的内部电流源来自 IMON 引脚。IMON 电流 DAC (IDAC) 是 6 位 DAC，输出电流范围为 0 至  $640 \mu\text{A}$ 。有 4 位累积抖动驱动额外的 LSB 输入到 DAC，以获得额外的分辨率（总共 6+4 位）。电流源的增益是可配置的，允许用户根据应用程序缩放电流源。最大源电流为  $640 \mu\text{A}$ 。无负载时，该源电流为  $320 \mu\text{A}$ 。IMON 源电流低于  $320 \mu\text{A}$  表示该模块中存在负电流。

IMON 和地之间连接一个  $1.875 \text{ k}\Omega$  精密电阻 ( $R_{ishare}$ )，它将产生与每个模块输出电流成比例的电压。为了平滑 IDAC 抖动纹波，建议将一个  $1 \text{ nF}$  电容与  $R_{ishare}$  并联。满载时，IMON 电压为  $1.2 \text{ V}$  ( $640 \mu\text{A} \times 1.875 \text{ k}\Omega$ )；空载时，IMON 电压为  $0.6 \text{ V}$ 。

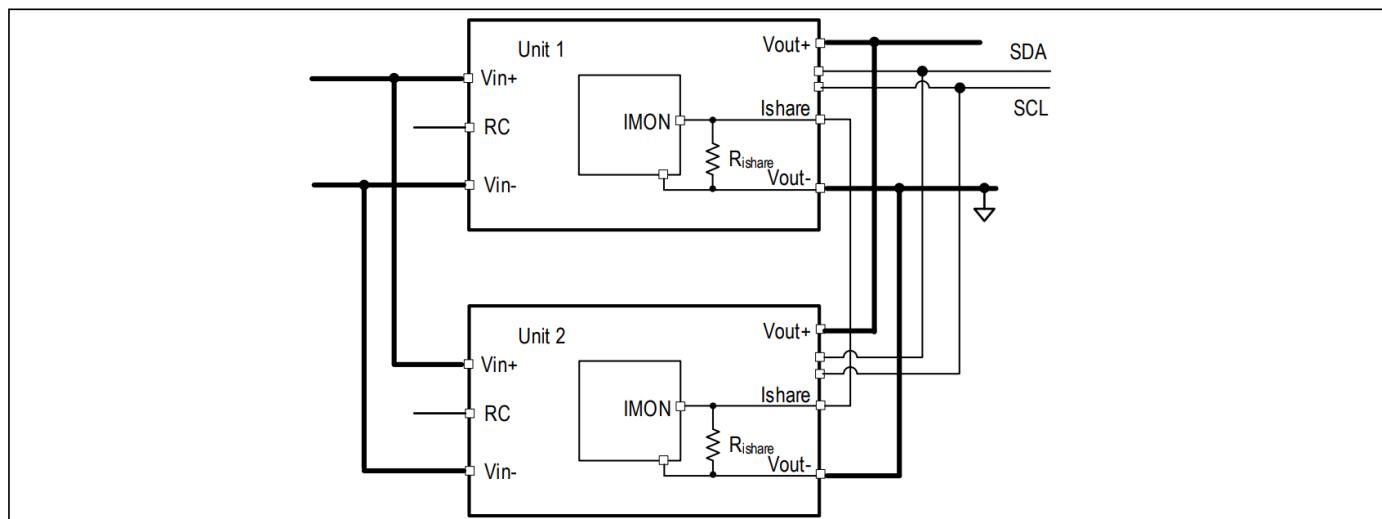

将并联转换器的 IMON 连接在一起可使 IC 检测平均电流的水平。每个电源转换器都会将自己的输出电流与平均电流进行比较，并做出相应的调整。为了防止小误差电流产生振荡，在电流均流块中设置了一个死区。当误差电流小于死区时，电流均流不激活。

XDPP1100 在有源电流均流期间提供正向和负向钳位以调整电压。这将输出电压限制在安全范围内。如果输出电压达到钳位水平，而电流误差仍然大于死区，则会报告均流故障。

## 功能概述

图12 并联模块均流

## 5.2.5.2 温度感应

XDPP1100 支持外部和内部温度感应，以进行保护和监控。外部温度感应是通过连接在 TSEN 或 BTSEN 和地之间的热敏电阻来实现的。IC 支持采用廉价NTC热敏电阻方式的外部温度传感器。外部传感器组件应靠近目标元件并与其紧密耦合，例如功率级组件或电流检测电阻。

xTSEN 引脚应通过并联电阻和滤波电容组成的网络连接到 NTC，如图 13 所示。NTC 引脚应以差分方式连接至 xTSEN 信号线，并返回控制器地。通过注入  $100 \mu\text{A}$  电流并测量 xTSEN 上的电压来检测温度。该温度用于有效补偿电流检测元件的温度系数，并通过生成警告和故障信号来提供过温保护。如果不使用温度传感器，则必须将 xTSEN 引脚连接至 GND。

XDPP1100 控制器包括一个预编程查找表，该表针对推荐的 NTC 选项 Murata NCP15WB473F03RC 或 Panasonic ERT-J0EP473J 进行了优化，标称值为  $47 \text{ k}\Omega$ ，并与一个固定的  $12 \text{ k}\Omega$  电阻并联。如果需要其他温度传感设备（例如 PTC 或 Vbe 温度传感设备），它还支持用户定义的温度查找表。

图13 NTC温度传感

## 功能概述

在 PCB 布局中还应格外小心，确保温度感应走线的布线与噪声源隔离。

内部温度传感器是控制器芯片内产生的 PTAT（与绝对温度成比例）电压，它反映控制器的结温。

### 5.2.5.3 PRISEN

PRISEN 用于检测原边电压，用于输入电压遥测和前馈补偿。在隔离应用中，应在原边检测  $V_{IN}$  电压，并通过隔离放大器将其馈送到 PRISEN 引脚。PRISEN 的斜率和偏移量可通过 `vin_pwl_slope` 和 `vin_trim` 寄存器配置。

输入电压遥测和保护可以配置为使用 PRISEN 或 VRSEN 作为输入电压信号源。差异如下所示。

通过 PRISEN 感测  $V_{IN}$ ：使用通用 ADC（1MHz 采样率），采样率与其他 5 个输入（温度感测、IMON 等）共享。即使转换器处于关闭模式，PRISEN 也始终启用。前馈响应比基于 VRSEN 的输入电压感测更慢。

通过 VRSEN 感测  $V_{IN}$ ：使用高速 ADC（采样率为 50 MHz），提供极快的前馈响应和过压/欠压保护。使用 VRSEN 进行  $V_{IN}$  遥测时，可以通过将 `vsp1_vrs_sel` 寄存器设置为“通用 ADC 模式”来感测直流输入电压，或通过将 `vsp1_vrs_sel` 寄存器设置为“ $V_{RECT}$  感测 (VRS) 模式”来感测变压器次级绕组。设置为“ $V_{RECT}$  感测模式”时，转换器未处于开关状态时， $V_{IN}$  遥测处于非活动状态。

PRISEN 和 VRSEN 电压检测可以组合使用，以获得最佳系统性能。XDPP1100 允许独立配置输入电压遥测和输入电压前馈。使用 PRISEN 进行输入电压遥测可以实现持续的输入电压监控和预启动保护；通过 VRSEN 使用  $V_{RECT}$  检测可以实现快速前馈响应和磁通平衡功能。

## 5.3 控制回路子系统

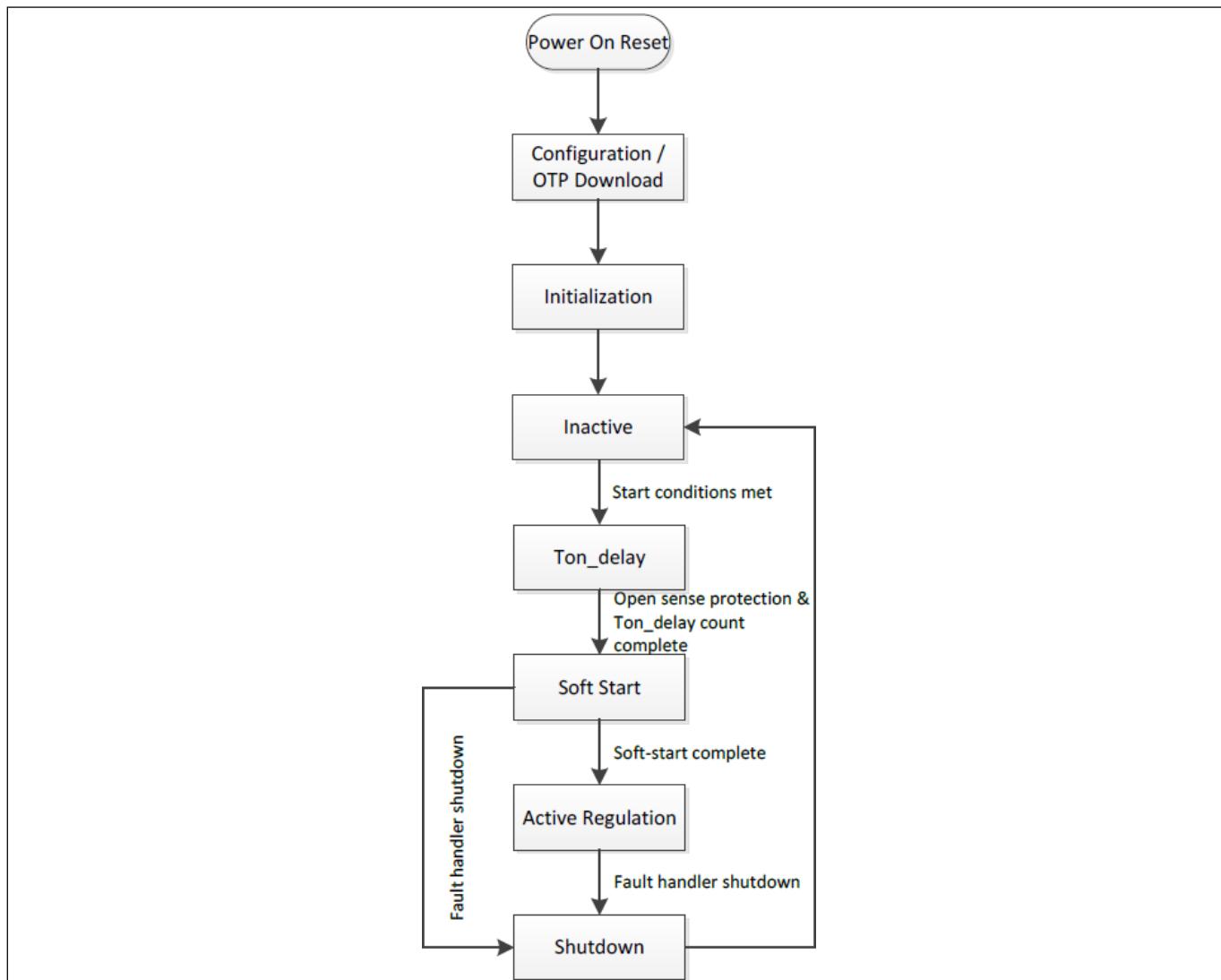

### 5.3.1 状态图

状态图如图 14 所示。

控制器操作由具有内部阈值的上电电路初始化。在控制器配置期间，OTP NVM 的内容将下载到控制寄存器。在此期间，GPIO 引脚保持高阻抗 (Hi-Z) 状态，允许电路板上拉或下拉电阻为静态输入信号（例如 I<sup>2</sup>C 地址 (XADDR1、XADDR2)）设置正确的默认电平。

在初始化状态下，控制器会测量内部和外部温度、输入和输出电压，并执行 IC 内部的各种校准程序。在退出初始化状态之前，控制器会执行用于设置 I<sup>2</sup>C 串行地址的外部电阻引脚设置测量。一旦确定了有效的 I<sup>2</sup>C 地址，即可通过控制器的 I<sup>2</sup>C 总线与控制器建立通信。

## 功能概述

**图 14 状态图**

初始化过程完成后，控制器将进入非活动状态。控制器将在启动系统之前验证以下条件是否满足：

- 有效 VDD：施加到 VDD 的电压必须超过 2.78 V，才能使内部电源有效信号有效。上电后，若 VDD 电压低于 2.38V，IC 再次复位。

- 未激活在编程的关断掩码中定义的关断故障。

- 如果 ON\_OFF\_CONFIG 设置为“响应 EN”，则使能 (EN/BEN) 有效。建议仅在 VDD、VIN 和功率级电源准备就绪后，才将 EN/BEN 激活。

- TSEN/BTSEN 输入和内部温度在工作范围内。

一旦满足上述启动条件，控制器将等待一段可编程的时间段 (TON\_DELAY)，然后再提高输出电压。

### 5.3.2 软启动

在进入主动调节状态之前，控制器对电压输出执行受控的、单调的软启动斜坡。在软启动期间，控制器将执行预偏置条件测量

## 功能概述

输出电压。控制器可以禁用同步整流器输出（二极管仿真模式），这样它就不会从预偏置输出吸收电流。可以使用 PMBus 命令配置启动中的二极管仿真模式。软启动是通过主动调节输出电压，同时以数字方式将参考电压从测量的预偏置电压上升到其最终目标值来实现的。可以在软启动过程中配置目标输出电压、斜率、开启上升时间以及开启试验次数。

控制环路将二极管整流（DE）到同步整流（SR）的转换视为负载释放。为了避免电压故障，控制回路会重置 PID 累积误差，并在启用 SR 时使用前馈占空比。因此，当 SR 开启时，环路立即具有校正的占空比，从而避免了反馈环路的响应缓慢。此功能适用于电压模式控制。

当转换器完成初始输出斜坡至目标输出电压时，它进入主动调节状态。电源良好信号 PWRGD 有效，表明输出电压在调节窗口内。

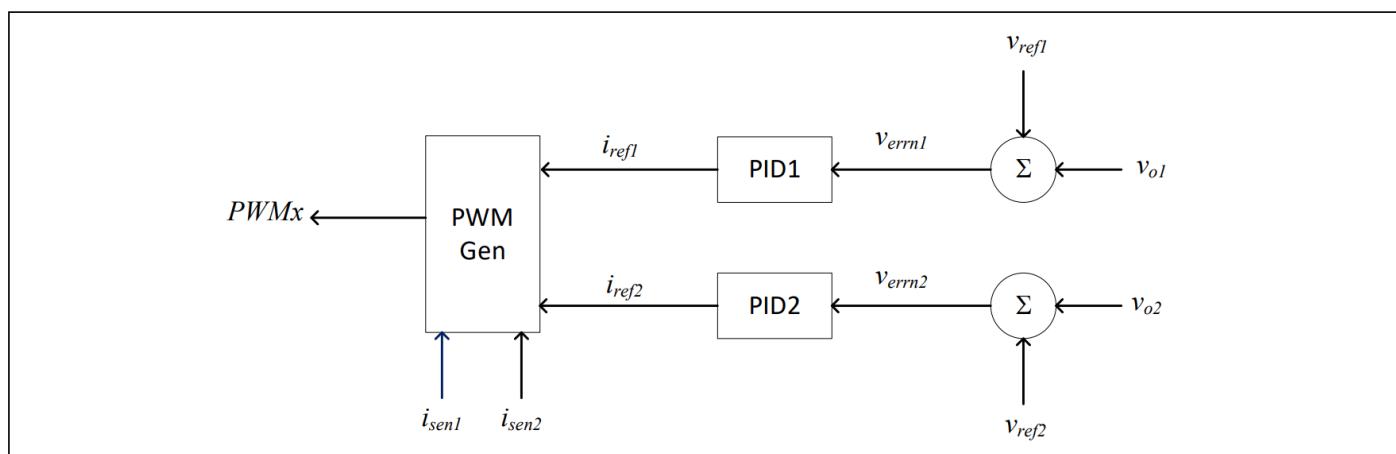

### 5.3.3 电压模式控制 (VMC)

电压模式控制 (VMC) 是 XDPP1100 支持的最基本的控制模式，如图 15 所示为双环路操作。每个环路的输出电压与其期望电压 ( $v_{ref}$ ) 进行比较，产生一个误差电压，该误差电压馈入 PID 补偿网络。PWM 生成模块使用 PID 的输出来创建给定拓扑所需的信号。

图15 电压模式控制环路

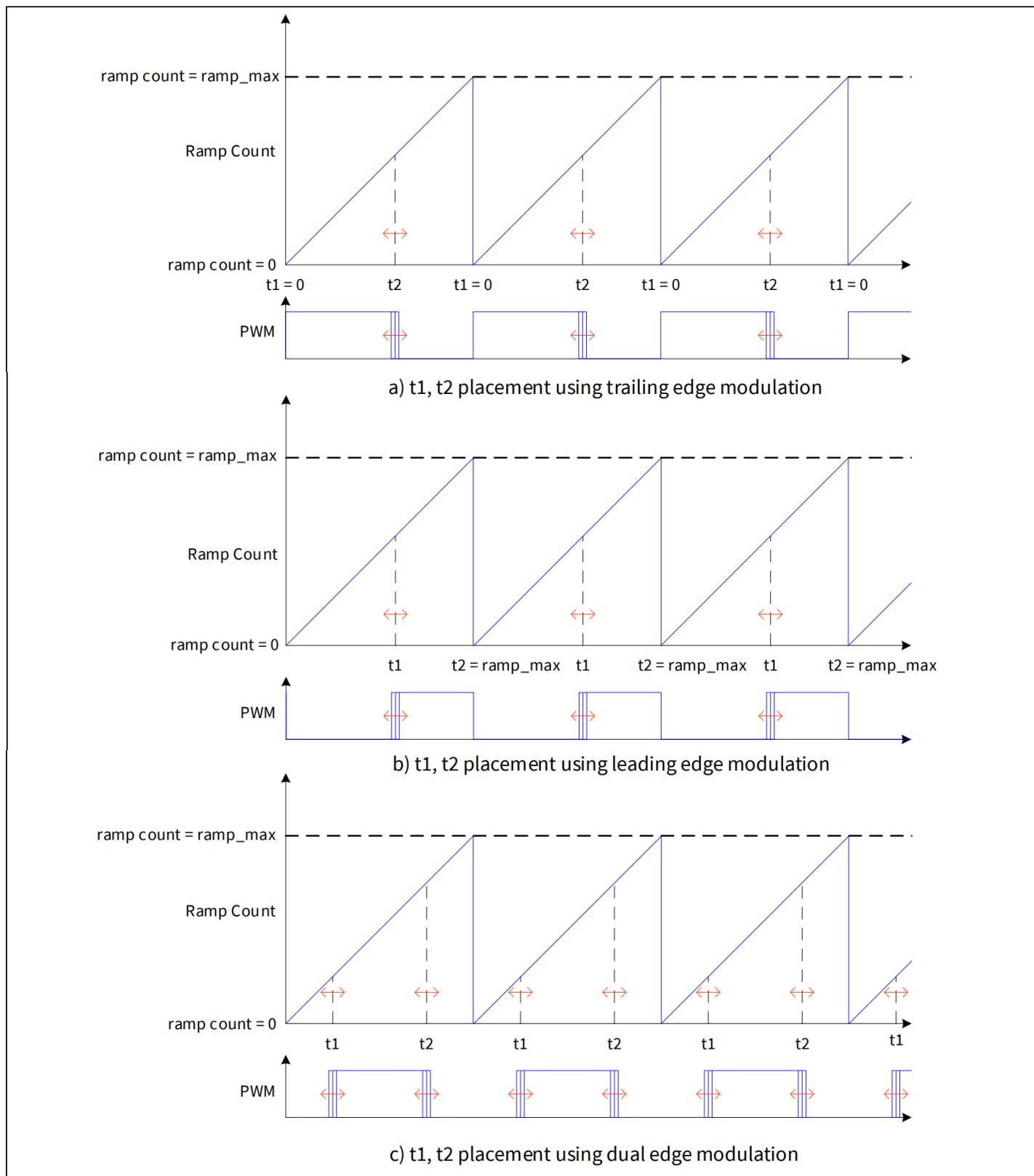

VMC 支持三种 PWM 调制模式：双边沿 (DE) 调制、后沿 (TE) 调制和前沿 (LE) 调制。这些调制方案如图 16 所示。

图 16a ) 中的第一个调制波形显示了后沿(TE)调制的情况。PWM 脉冲具有一个固定的前沿和一个调制的后沿。

第二种调制方案是前沿(LE)调制，如图 16b 所示。PWM 脉冲具有固定的后沿和调制的前沿。

最后一种调制方案是双边 (DE) 调制，如图 16 c) 所示。在此调制中，时间标记 t1 和 t2 均被调制。

## 功能概述

图 16 TE、LE 和 DE 调制的 T1 和 t2 位置。

## 5.3.4 峰值电流模式控制 (PCMC)

在峰值电流模式控制 (PCMC) 中，当电流达到给定阈值时，电流会被感应并关闭。补偿误差电压定义了该阈值。需要注意的是，要实现

## 功能概述

初级侧 PCMC，感测到的电流不是输出电流（如在 VMC 中）。相反，电流变压器或隔离放大器会感测一次设备中的电流并将其馈送到隔离屏障上。次级侧 PCMC 的补偿与初级侧 PCMC 的补偿类似，主要区别在于，在这种情况下，感测电流是输出（电感器）电流。

使用 PCMC，不需要补偿器网络的导数，只留下补偿网络的 PI。

PCMC 的一个问题是占空比大于 50% 的次谐波振荡，这会导致扰动增大而不是衰减。为了解决这个问题，添加了一个辅助斜坡。用户可以通过寄存器 Compensation\_slope 在  $V_o/L$ 、 $V_o/2L$  或  $V_o/4L$  之间选择斜坡的斜率。

在启动和受控关断期间，当占空比较窄时，一次电流信号较弱。建议启用最小脉冲宽度寄存器 (rampX\_min\_pw\_state = 1) 以避免周期跳跃。还可以在启动期间禁用峰值电流模式控制并使用电压模式控制，并在输出电压达到目标窗口时切换到 PCMC。

PCMC 仅支持后沿调制。

图 17 峰值电流模式控制环路

### 5.3.5 PID 和控制回路

控制器的每个环路都实现固定开关频率、数字 PID 电压环路和双边 PWM 架构。在运行期间，输出

电压被差分感测并由精密模数转换器 (ADC) 数字化。该电压与参考电压进行比较以产生误差电压。

然后将得到的数字误差信号馈入数字 PID 补偿器，其有效传递函数如下：

$$H_{PID}(z) = \left[ (K_p + K_d(1 - z^{-1})) \left( \frac{K_{fp2}}{1 - (1 - K_{fp2})z^{-1}} \right) + \frac{K_i}{1 - z^{-1}} \right] \left[ \frac{K_{fp1}}{1 - (1 - K_{fp1})z^{-1}} \right] z^{-1}$$

极点和零点的位置由数字环路系数  $K_p$ 、 $K_i$ 、 $K_d$  和  $K_{fp}$  确定，它们分别是 PID（比例、积分、微分）和低通滤波器极点项。它创建了与 III 型补偿网络等效的补偿网络。在电流模式控制中，不需要相位超前，因此微分项  $K_d$  被归零。

ARM M0 可以访问 PID 系数，并能够在不同的操作模式下优化值，即软启动、稳定状态、负载瞬态和省电状态。

## 功能概述

每个回路的数字 PID 补偿器的输出通过数字双边脉宽调制器转换为 PWM 脉冲。最大占空比限值可编程至 99.6%。除了使用 PID 补偿器进行调节外，控制器还具有非线性控制机制，例如快速瞬态响应 (5.3.9) 和输入电压前馈 (5.3.10)，以最大限度地减少瞬态事件期间的电压偏移。

### 5.3.6 关机

可以通过用户干预（取消激活 EN）或通过检测到的故障从软启动或主动调节状态进入关断状态。以下是一些故障情况的示例：过温 (OTP)、过流 (OCP)、输入欠压 (IUVP)、输入过压 (IOVP)、输出过压 (OOVP)、通量平衡故障。可以对电压环路进行编程，使其在发生故障时同时或单独关闭。

XDPP1100 支持两个用户可选择的关闭选项，以响应 EN 的取消激活。第一个选项是闭环关断，其中控制器以用户定义的斜率降低输出电压。第二种选择是热关断 (Hi-Z) 响应，其中输出级功率 FET 立即关闭。如果需要立即关闭，则应将 TOFF\_DELAY 设置为 0ms。对于因故障导致关断的情况，最终的关断响应始终为 Hi-Z。

一旦发生关机，固件将处理后续响应。关闭可能是最终的；或者转换器可能进入有限或无限的打嗝模式。

### 5.3.7 电流检测估计器

电流检测估计器 (CE) 对电感器电流进行采样并提供斜率估计和跟踪。根据 PWM 脉冲的状态，控制器不断预测每个单独的直流电流和纹波电流。预测（估计）的结果与实际测量的电流（跟踪）相结合，由控制器进行处理。用户可以通过寄存器 ceX\_ktrack\_hiz、ceX\_ktrack\_off、ceX\_ktrack\_on 定义跟踪过估计的权重。这些寄存器分别设置 HiZ 状态、关闭状态和开启状态下的跟踪增益。它可以配置为仅估计、仅跟踪或估计和跟踪的组合。

当用于输出电流感测时，能量传输间隔期间的斜率取决于整流电压的值，该值是输入电压和匝数比、滤波器电感和输出电压的函数。续流间隔可分为两部分：第一部分是 SR 体二极管导通，第二部分是 SR 导通，因此通道导通。在第一种情况下，斜率是输出电压、电感和二极管正向电压的函数。在第二种情况下，斜率是输出电压和滤波器电感的函数。寄存器 ceX\_kslope\_didv 定义了斜率估计的标准输出电感值。

输出电流可以在输出电容器组之前感测，该电流为带有纹波的电感电流；也可以在输出电容器组之后感测，该电流为不带纹波的直流电流。感应电感电流可实现次级峰值电流模式控制。感测直流输出电流不能使用次级 PCMC 或逐周期峰值电流限制。

当用于初级侧 PCMC 时，CE 会估计能量传输间隔期间电流的斜率。斜率是变压器的输入电压、输出电感、输出电压、匝数比 N 和磁化电感的函数。初级侧电流通过电流互感器感测并馈送到芯片的 ISEN 输入端；这意味着电流互感器的匝数比及其终端电阻引入了增益缩放项。寄存器 ceX\_kslope\_lm 定义了标准化变压器初级磁化电感。

## 功能概述

如果纹波电流幅度超出可配置范围，则会发出电流检测跟踪故障。电流轨道故障的启用是用户可以配置的。

CE 支持与典型砖型转换器电流感应方案相关的以下非理想情况的补偿：

- 电流检测走线电阻的寄生电感引起的阶跃

- 输出电感随输出电流的变化

- PWM 切换后噪声导致的前沿和下降沿消隐时间

### 5.3.8 载重线（下垂）

XDPP1100 支持 LINEAR11 格式的 VOUT\_DROOP，指数可配置为 -7 至 +2，对应分辨率为 0.0078125 mΩ 至 4 mΩ。每个环路都有独立配置的 VOUT\_DROOP。每个环路根据自己的输出电流值实现下垂计算。

采用多段下垂来实现恒流、恒功率运行。多段下垂是一种非线性下垂，允许用户定义不同负载电流下不同的下垂电阻。如果负载线电阻设置得较高，当电流超过设定的阈值时，输出电压将快速下降，其行为类似于恒定电流 (CC) 或恒定功率 (CP) 操作。

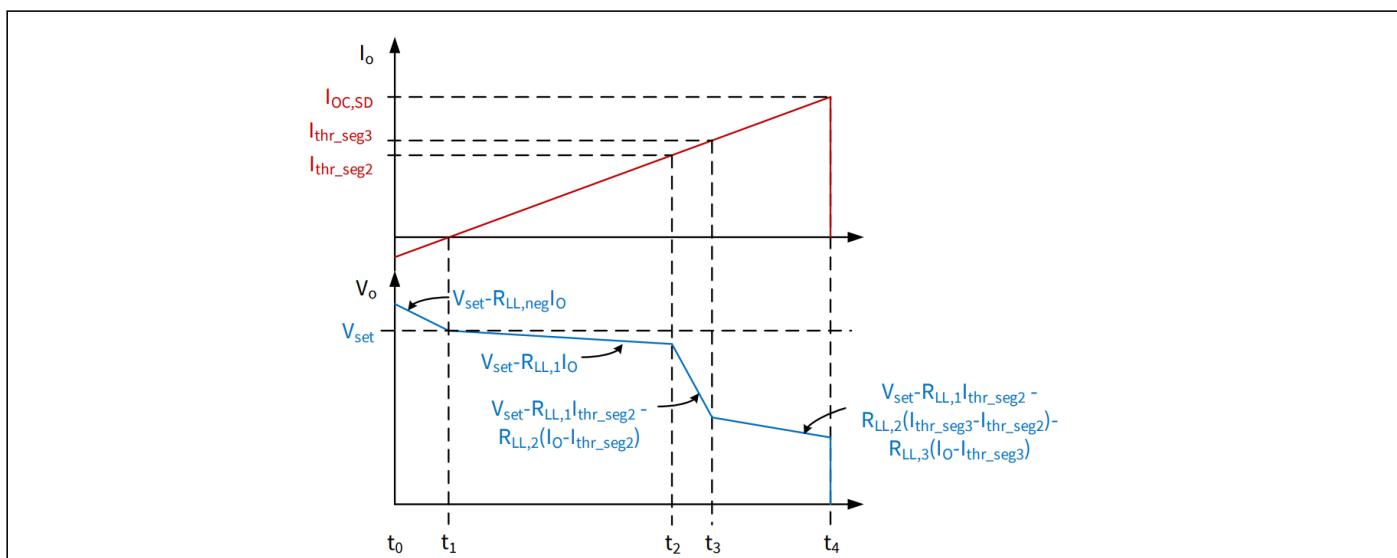

图 18 显示了多段负载线的行为。当输出电流  $I_o$  小于零时，使用负载线值  $R_{LL,neg}$  这有助于在并联模块应用中实现电流平衡。 $R_{LL,1}$  是由标准 PMBus 命令 VOUT\_DROOP 定义的常规压降电阻。从  $I_{thr\_seg2}$  到  $I_{thr\_seg3}$ ， $R_{LL,2}$  用于模拟恒流操作。从  $I_{thr\_seg3}$  到过流关断阈值  $I_{OC,SD}$ ， $R_{LL,3}$  用于近似恒功率操作。 $I_{OC,SD}$  等于 IOUT\_OC\_FAULT\_LIMIT。

图18 过流保护的负载线实现

### 5.3.9 最快的瞬态响应

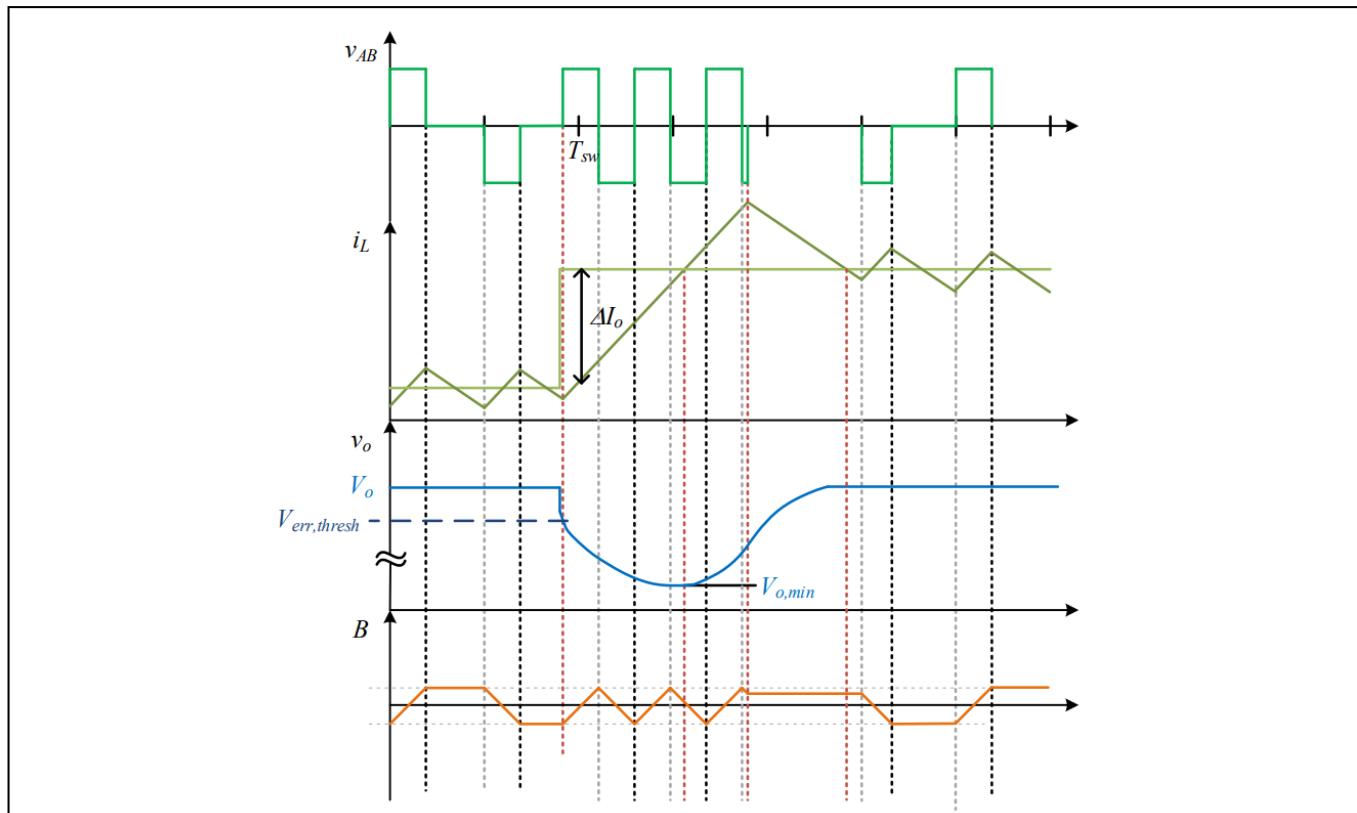

XDPP1100 可实现对半桥和全桥拓扑的快速瞬态响应。检测到正负载瞬态后，转换器通过将开关周期从  $T_{sw}$  更改为  $2T_{on}$ ，有效地使整流电压饱和，其中  $T_{on}$  是占空比 D 与开关周期的乘积。由于 D 随输入电压而变化，因此瞬态期间的工作频率也取决于输入电压。

## 功能概述

瞬态检测可以通过  $V_o$  方向的阈值电压检测（如图19所示）来实现，也可以通过误差电压导数的阈值（图中未显示）来实现，或者两者结合。峰值电感电流 ( $i_L$ ) 取决于负载阶跃  $\Delta i_o$  和输入电压（输入电压决定电感电流的上升速率）。

当输出电感器中的电流高于负载电流时，输出电压在几个 FTR 周期后开始恢复。为避免过冲，转换器应在  $V_{out}$  回到设定的目标电压之前退出 FTR 模式。XDPP1100 在可配置的误差电压阈值下退出 FTR 模式，该阈值始终低于目标  $V_{out}$ 。误差电压定义为（目标电压 - 检测电压）。当误差电压小于设定阈值时，XDPP1100 退出 FTR 模式。在退出 FTR 时，XDPP1100 将完成当前的 FTR 周期，然后恢复开关周期回到  $T_{sw}$ ，然后线性环路接管调节。

图19 变压器保护快速瞬态响应波形

### 5.3.10 输入电压前馈

输入电压前馈涉及使用输入和输出电压测量来设置给定条件的标称占空比。当感应到输入电压的变化时，XDPP1100 可以根据输入电压、输出电压和 SR 条件快速补偿占空比。在输入电压瞬态条件下，前馈响应比输出线性环路快得多。在控制器位于次级侧的隔离转换器中，快速准确的 VRS 感应对于实现高性能前馈至关重要。

XDPP1100 允许用户选择以下源之一进行前馈计算。

- 在 VRSEN 输入上感测到  $V_{RECT}$

- 在 BVRSEN 输入上感测到  $V_{RECT}$

- 在 PRISEN 输入上感测到的  $V_{IN}$  遥测感测 ( $V_{IN}$ )

- pid\_ff\_vrect\_override 用于 FW 覆盖感测到的  $V_{RECT}$

## 功能概述

前馈占空比的计算因拓扑结构而异，定义如下式所示。输入电压通过测量获得，而目标输出电压 ( $V_{o,target}$ ) 和匝数比则由寄存器设置。

$$D_{HB} = \frac{2 \times N \times V_{o,target}}{V_{in}}$$

$$D_{FB, ACF} = \frac{N \times V_{o,target}}{V_{in}}$$

$$DBuck = \frac{V_{o,target}}{V_{in}}$$

HB：半桥，FB：全桥，ACF：有源钳位正向。

### 5.3.11 电流平衡

交错拓扑结构需要电流平衡。电流平衡电路采用PI补偿网络。测量通过每个“相”的电流并将其与总电流的一半进行比较。该误差由 PI 网络补偿，然后适当调整占空比。

启用阈值适用于电流平衡块。仅当总电流高于启用阈值（选项为 0 A、3 A 和 5 A）时才会激活电流平衡。

### 5.3.12 电流均流

电流均流是指平衡提供公共输出电压的各个电源的电流。实现电流均流的一种方法是使用 IMON（第 5.2.5.1 节），如图 12 所示，其中每个转换器的 Ishare 引脚相连，并馈入外部电阻  $R_{ishare}$ 。IDAC 输出与模块负载电流成比例的电流。电流之和会在电阻两端产生一个电压，该电压由通用 ADC 测量，并用于确定两个模块之间电流分配的均衡程度。电流均流是一个慢速环路（例如，电压环路带宽的 10%）。

第二种电流均流方法是被动的，使用负载线（第 5.3.8 节）。

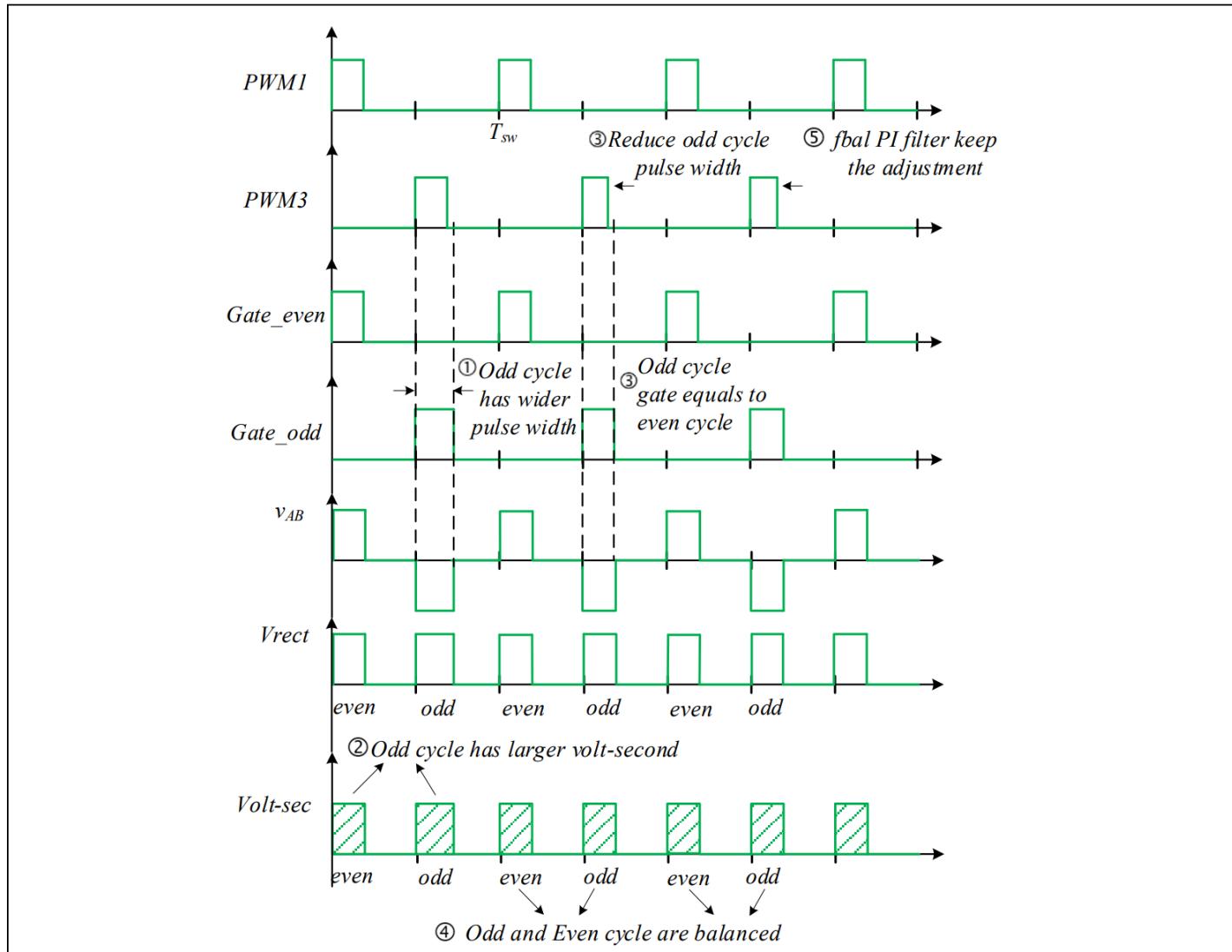

### 5.3.13 通量平衡

在全桥转换器中，时序不匹配可能导致在一个半周期内施加在变压器上的伏秒大于在另一个半周期内的伏秒。这会在变压器磁芯上产生直流电压，并因“磁通走开”而导致饱和。为了避免这种情况，必须调整 PWM 时序以平衡每个半周期，以解决实际时序差异。

XDPP1100 实现了基于伏秒的磁通平衡。它在每个半周期内进行输入电压测量和时序测量。每个半周期伏秒乘积之间的误差被馈送到 PI 补偿网络以增加占空比。XDPP1100 使用整流电压 ( $V_{RECT}$ ) 进行电压和时序测量。高速边沿比较器具有 5ns 的时序测量精度，可实现高性能磁通平衡。边沿比较器具有两个可配置的参考电压阈值：500mV 和 300mV。为了获得正确的电压感应，应适当调整  $V_{RECT}$  电压。VRSEN 的推荐电压范围为 600 mV 至 2 V。

如果在可编程的循环次数内无法达到通量平衡，就会产生故障。有关磁通平衡和磁通平衡故障保护的更多详细信息，请参阅应用说明。

## 功能概述

对于  $V_{RECT}$  感测，请勿将滤波电容连接到 VRSEN 引脚，以免波形失真。对于开尔文感测，VRSEN 和 VRREF 应成对布线；布线应远离其他开关节点，以避免噪声耦合。

图20 伏秒磁通平衡

## 5.3.14 突发模式

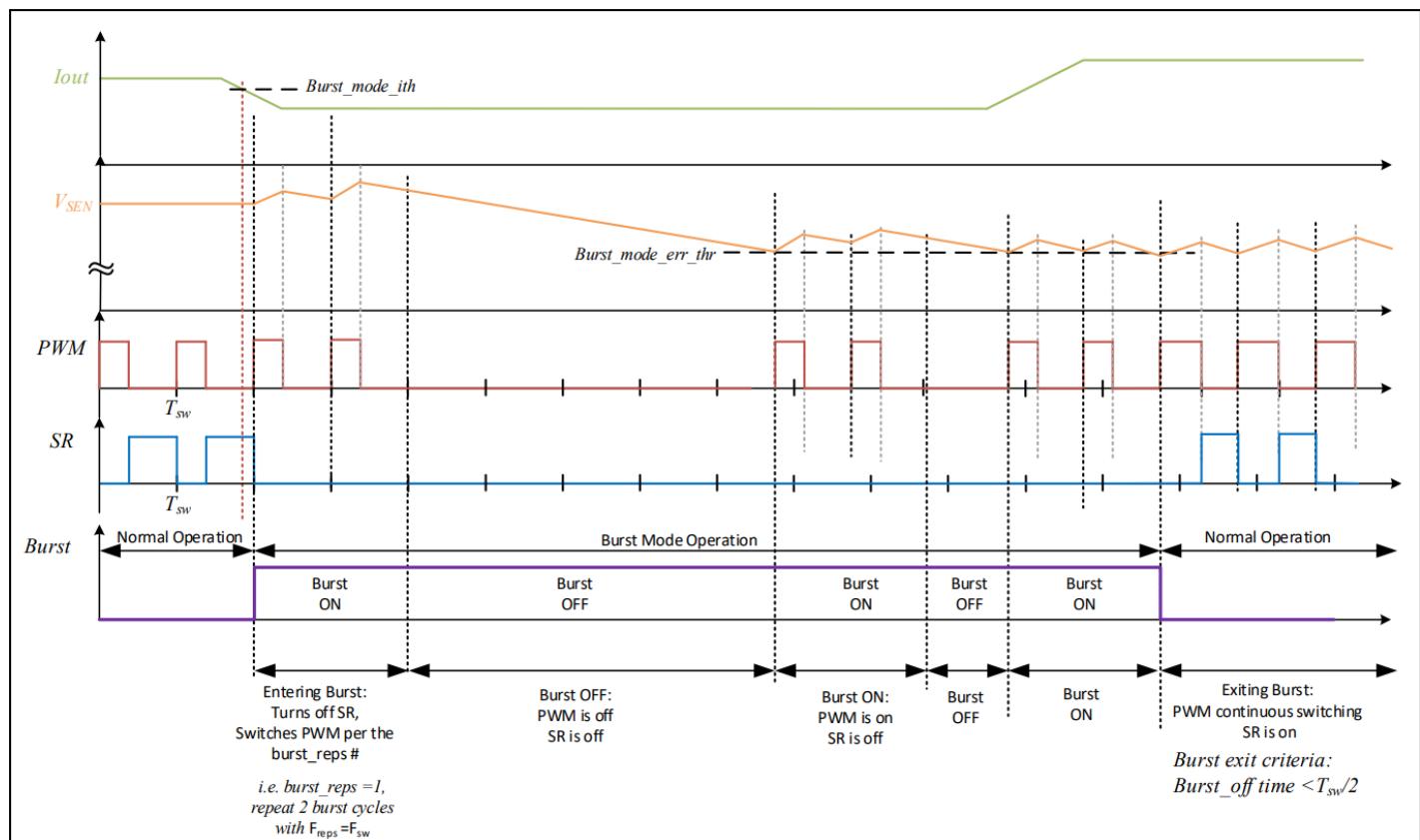

为了提高轻载效率，转换器可以进入突发模式以减少开关损耗。当负载电流降至所需的进入电流水平以下时，转换器应进入突发模式操作。进入突发（突发关断）时，转换器停止开关。当输出电压降至目标水平（突发开启）时，恢复开关。该目标水平定义了突发模式下的输出电压纹波。在突发模式下，PID 输出冻结为进入突发之前的值。因此，在突发开启期间，转换器以恒定导通时间模式工作。在突发模式下，SR 关闭。PWM 突发的频率将与开关频率相同。代表性波形如图 21 所示。有关突发操作的更多详细信息，请参阅应用笔记。

功能概述

图 21 突发模式操作中的波形

5.4 保护和故障

故障保护系统具有以下功能：

- 输入欠压/过压保护 (VIN\_UV/VIN\_OV)

- 输入过流保护 (IIN\_OC)

- 输入过功率警告 (PIN\_OP)

- 输出欠压/过压保护 (VOUT\_UV/VOUT\_OV)

- 输出欠流/过流保护 (IOUT\_UC/ IOUT\_OC)

- 输出过功率警告 (POUT\_OP)

- 逐脉冲峰值电流限制保护 (PCL)

- 短路保护 (SCP)

- 内部/外部温度保护 (OT/UT)

- 开路/短路感测线保护

- 通量平衡故障

- 同步故障

- 均流故障

- SMBALERT#

- 配置 (CRC) 失败

- I<sup>2</sup>C通信故障

## 功能概述

保护框图如图 22 所示。XDPP1100 无需使用外部比较器即可实现所有故障保护功能。更多故障保护功能详情，请参阅应用笔记。

图22 保护框图

## 6 应用信息

本节列出的所有拓扑都是 IC 支持的标准拓扑。这些拓扑的环路和 PWM 时序控制在芯片中预先定义，减少了用户的编程工作量。

### 6.1 PWM全桥变换器

#### 6.1.1 VMC 中带中心抽头输出的 PWM 全桥

带中心抽头整流器的全桥变换器的典型连接如图 23 所示：

图23 VMC中具有中心抽头输出的全桥转换器

XDPP1100 支持全桥转换器的磁通平衡电压模式控制。XDPP1100-Q024 能够控制全桥转换器，其中 2 个 PWM 输出驱动初级 MOSFET，另外 2 个 PWM 驱动次级同步整流器 MOSFET。ISEN ADC 用于输出电流感应。

输出电压被差分感测并馈送到电压 ADC 的 VSEN。次级电流通过 PCB 铜走线感测，并将温度传感器放置在靠近铜走线的位置以补偿电阻的温度变化。高精度电流 ADC 提供  $100 \mu\text{V}/\text{LSB}$  精度，允许

## 应用信息

将电流检测信号直接连接到ISEN，无需使用外部放大器。输入电压可通过辅助电源进行遥测，也可在变压器次级侧的中心抽头点V<sub>RECT</sub>处进行检测。V<sub>RECT</sub>检测是实现磁通平衡和高性能电压前馈功能所必需的。XDPP1100 允许使用不同的输入源配置输入电压遥测和输入电压前馈。

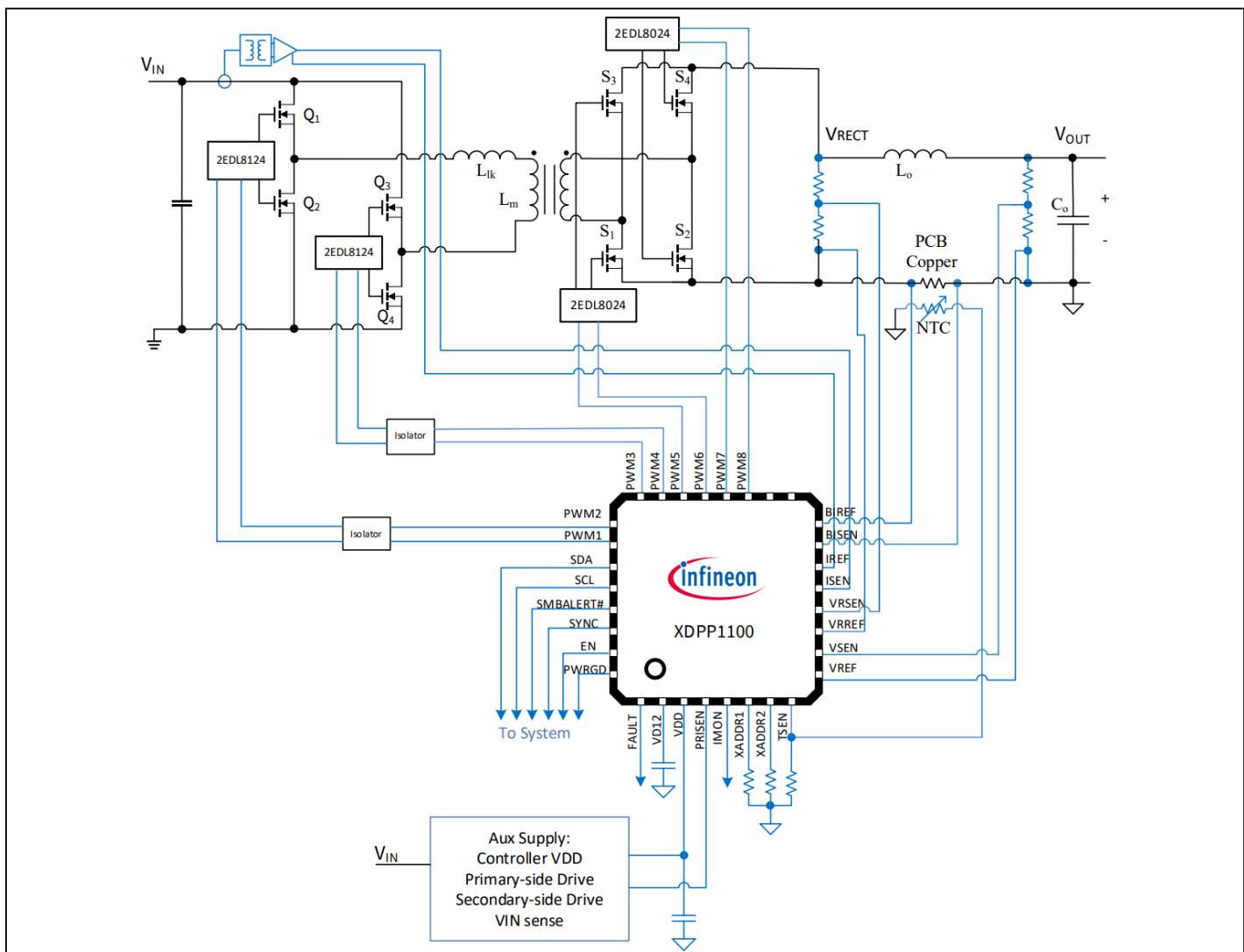

### 6.1.2 带 PCMC 的 PWM 全桥

PCMC 中全桥变换器与全桥整流器的典型连接如图 24 所示。

图24 全桥整流PCMC全桥变换器

对于全桥峰值电流模式控制，建议使用 XDPP1100-Q040，它可以实现初级和次级电流感应，并允许对每个开关的死区时间进行编程。在此图中，4 个 PWM 输出用于驱动初级 MOSFET，另外 4 个 PWM 驱动次级 SR MOSFET。每个MOSFET可以有独立的死区时间调整。

初级电流通过电流互感器感测并馈送到 ISEN/IREF 输入，从而启用初级 PCMC。

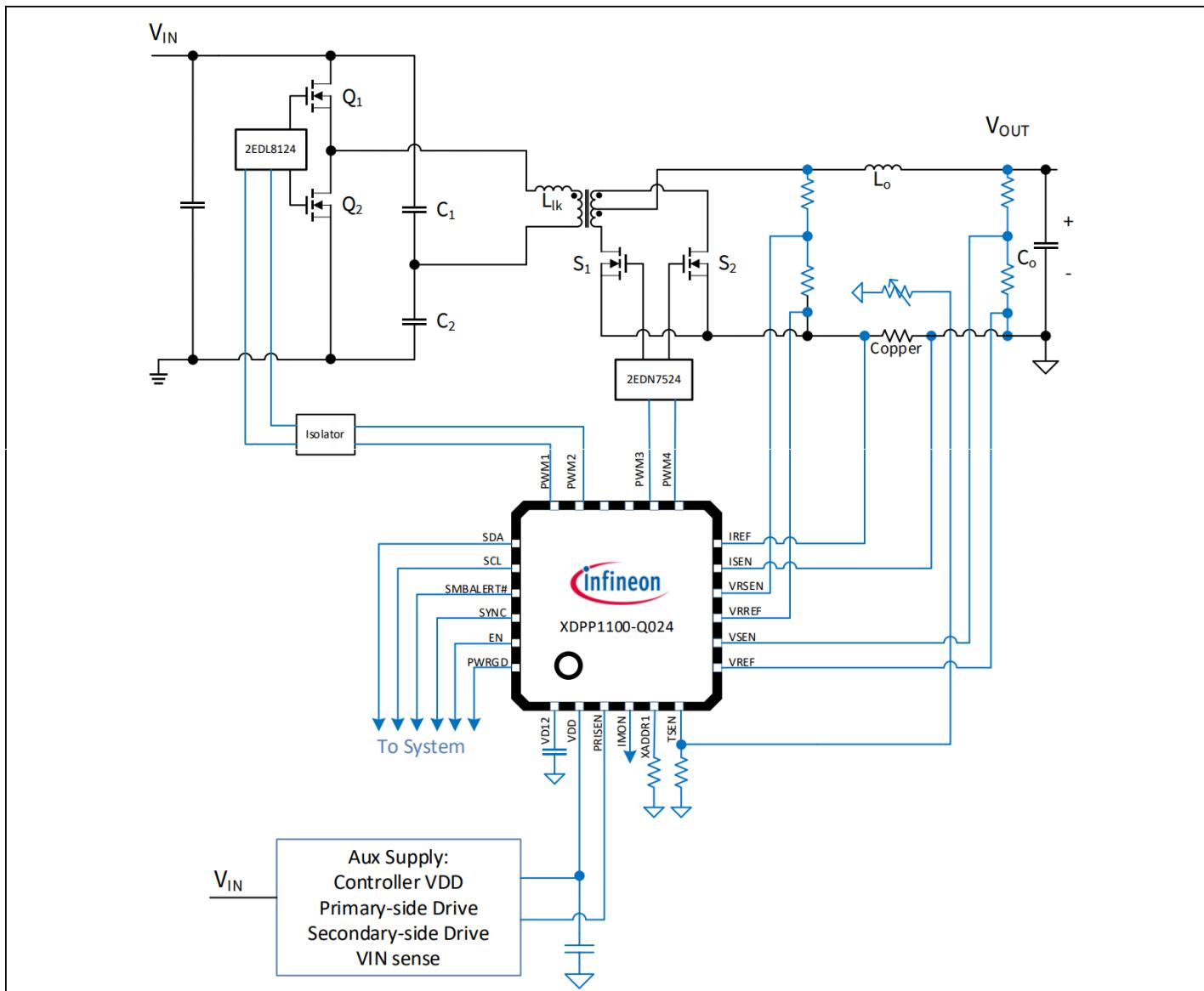

## 6.2 PWM半桥变换器

具有中心抽头输出的半桥变换器的典型连接如图 25 所示。

图25 具有中心抽头输出绕组的半桥转换器

本例中，XDPP1100 采用电压模式控制半桥。该控制器位于次级侧，通过变压器次级侧的整流电压感测一次侧输入电压。它还能够通过辅助电源的 PRISEN 引脚感测一次侧电压，从而在主转换器处于关闭状态时获取  $V_{IN}$  信息。一次侧电流是根据测量的次级电流、输入和输出电压估算的。

### 6.3 有源钳位正激变换器

电压模式控制的另一个例子是有源钳位正向 (ACF) , 如图 26 所示。原边钳位场效应晶体管 (FET) 采用 PMOS 晶体管, 便于栅极驱动。控制器位于副边, 用于检测整流电压、输出电压和输出电流。输出电流通过 PCB 铜走线检测, 以最大程度减少元件数量。NTC 热敏电阻应放置在非常靠近电流检测铜走线的位置, 用于温度补偿。

图26 有源钳位正激转换器

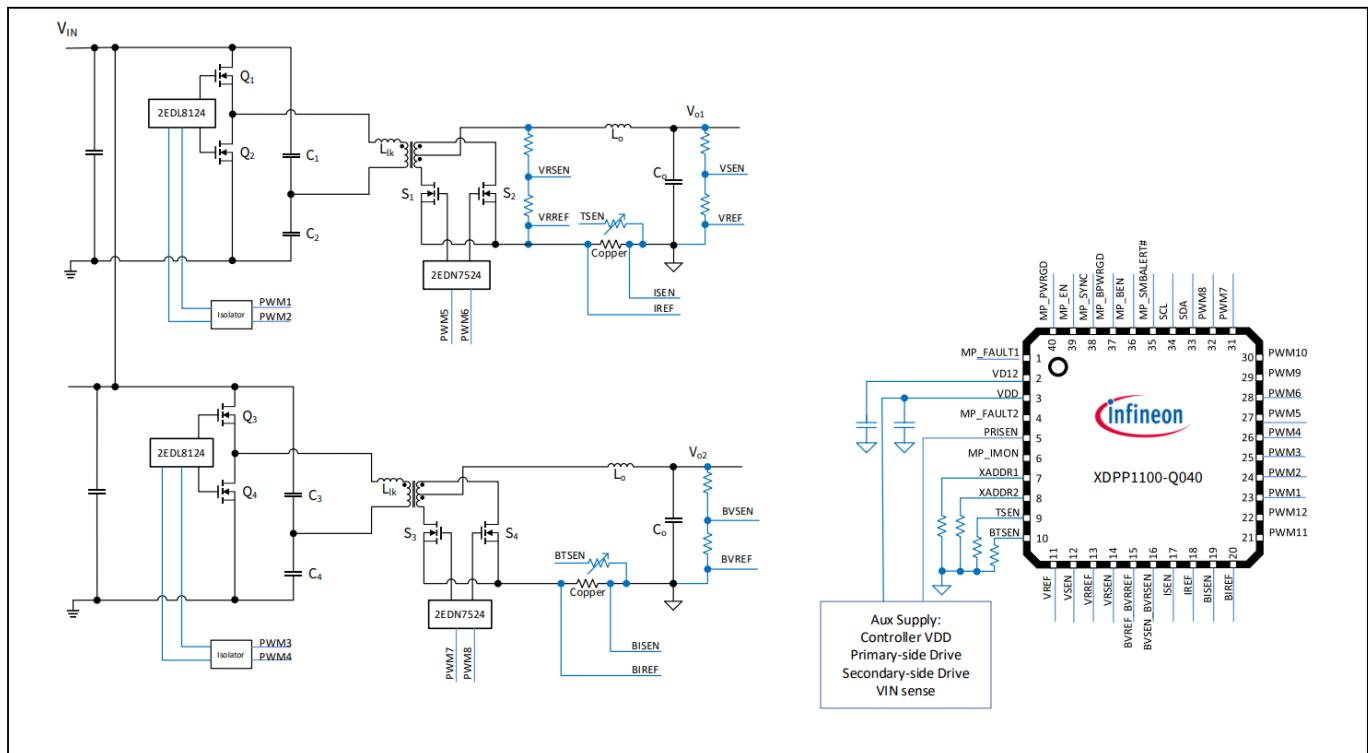

## 6.4 交错有源钳位正向

XDPP1100-Q040 支持交错拓扑。交错 ACF (IACF) 的示例如图 27 所示。

图 27 交错式 ACF 转换器

两个电源级由同一输入源供电，并联运行，其输出电感器连接到公共电容器组。为了消除纹波，交错相位之间的相移为 180°。检测两相的输出电流，转换器可以计算总输出电流并平衡每相的电流。

## 6.5 双环路转换器

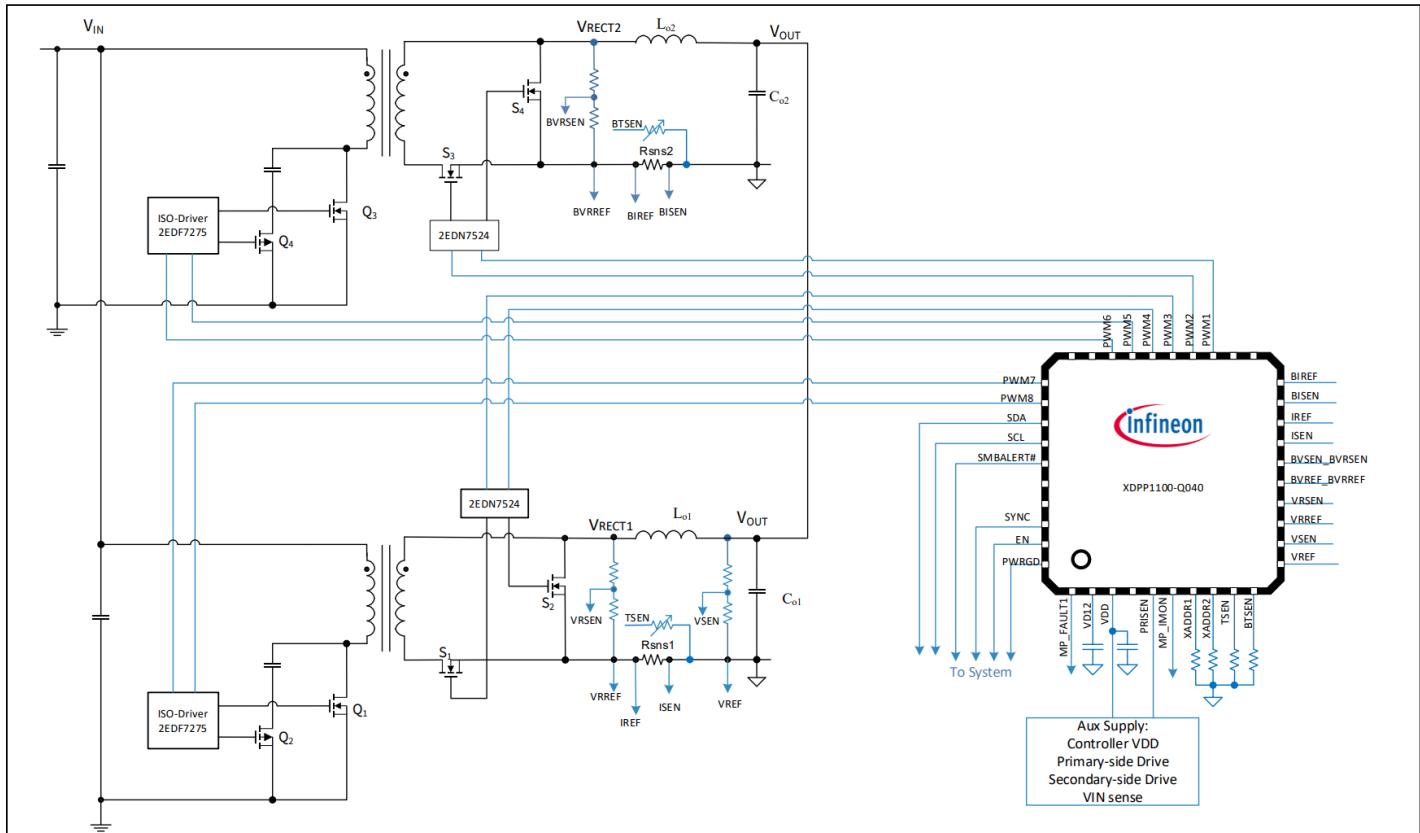

XDPP1100 支持最多两个独立环路，产生独立的输出电压。例如，具有中心抽头整流的 PWM 全桥可以实现 12 V 输出，而 ACF 可以实现 3.3 V 输出。另一种选择包括转换器级的串联连接，以便为主转换器提供预调节或后调节。

图 28 是一个用于两个独立输出的双半桥转换器示例。输入电压可在 VRSEN 或 PRISEN 引脚检测。两个环路可以独立配置输入电压源。由于 VRSEN 连接到第一个环路 ( $V_{O1}$ ) 的整流电压，因此第二个环路 ( $V_{O2}$ ) 应选择 PRISEN 作为输入电压源，或者选择 VRSEN 作为输入电压源，但仅在环路 1 处于稳压状态时开启。

## 应用信息

图 28 双半桥转换器

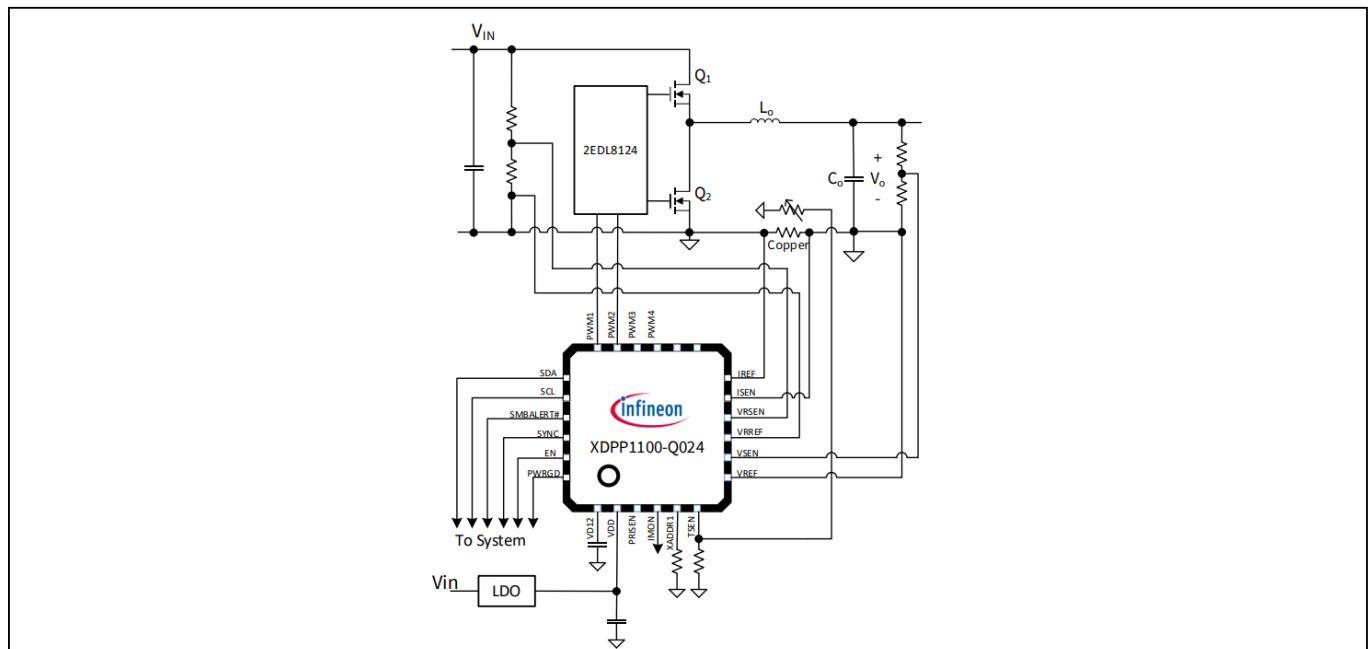

## 6.6 非隔离转换器

XDPP1100 支持非隔离 DC/DC 拓扑结构，例如 Buck、Boost 和反向 Buck-Boost。图 29 是典型的 Buck 转换器连接图。图 30 是反相 Buck-Boost 转换器的示例。对于反相 Buck-Boost 转换器，输入电压以输出地为负参考。

图 29 降压转换器

## 应用信息

图30 反相降压-升压转换器

## 6.7 布局指南

为了优化电压调节器的性能，重要的是尽量减少印刷电路板寄生阻抗对数字控制器的影响。以下布局技术重点介绍了在布局过程中应纳入的重要实践，以优化印刷电路板的散热能力。

### 6.7.1 元件放置

在分配的实施区域内，首先定位开关组件。开关元件最为关键，因为它们承载着大量能量，并且容易产生高水平的噪音。开关元件的放置应考虑功率耗散。对齐输出电感器和 MOSFET，以使组件之间的空间最小化。

关键的小信号元件（包括 VDD 和 VD12 去耦电容器、ISEN 电阻器、TSEN 电容器和电压反馈 RC 滤波器）应放置在控制器附近。

## 应用信息

图31 去耦电容的放置和布线

### 6.7.2 布线

对于每个电压检测和电流检测输入，即VSEN/VREF、ISEN/IREF，以差分对（开尔文连接）的形式路由信号及其参考。

避免将VRSEN/VRREF、BVRSEN/BVRREF布线在任何开关节点附近，尤其是在双环路或两相应用中。与输出电压感应不同，VRSEN测量脉冲信号，因此不能使用滤波电容来抑制噪声。建议使用接地层屏蔽走线。

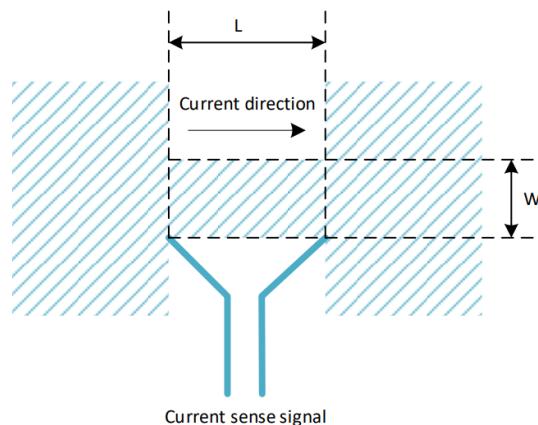

### 6.7.3 通过铜线感测输出电流

IADC的高分辨率允许XDPP1100通过非常小的PCB铜分流器感测输出电流，从而节省功率损耗以及精密感测电阻器和运算放大器的成本。使用以下公式计算铜走线电阻。

$$R_{copper} = \rho \cdot \frac{L}{T \cdot W} \cdot (1 + tc \cdot (temp - 25))$$

$\rho$ : 铜的电阻率,  $17 \cdot 10^{-6} \Omega \text{ mm}$

L: 铜线长度

W: 铜线宽度

T: 铜线厚度

tc: 温度系数,  $3.9 \cdot 10^{-3} / ^\circ\text{C}$

temp: 轨迹温度, 单位 $^\circ\text{C}$

铜线的厚度通常以盎司为单位，表示1盎司铜铺在1平方英尺面积上的厚度。1盎司。铜的厚度为1.4mils或0.0356mm。这是铜分流器的设计示例：130 mil x 100 mil（长x宽），顶层，4 Oz 铜，走线电阻为0.158 mΩ。

## 应用信息

建议将铜走线分流器布置在第一个中间层，以便 XDPP1100 控制器可以放置在分流走线的正上方，以实现最短的布线距离。还要在铜感应层旁边放置一个接地屏蔽层，以减少杂散电感，从而获得更好的电流感应精度。

图 32 通过铜线感测电流

7

封装信息

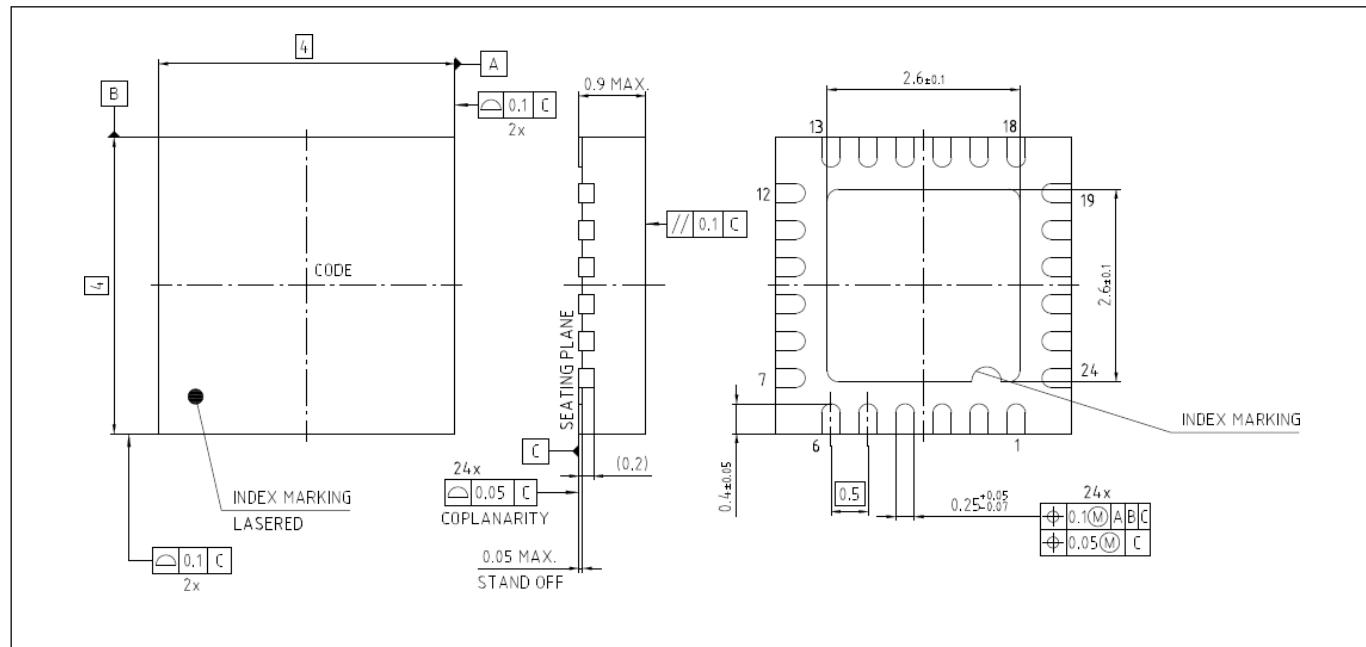

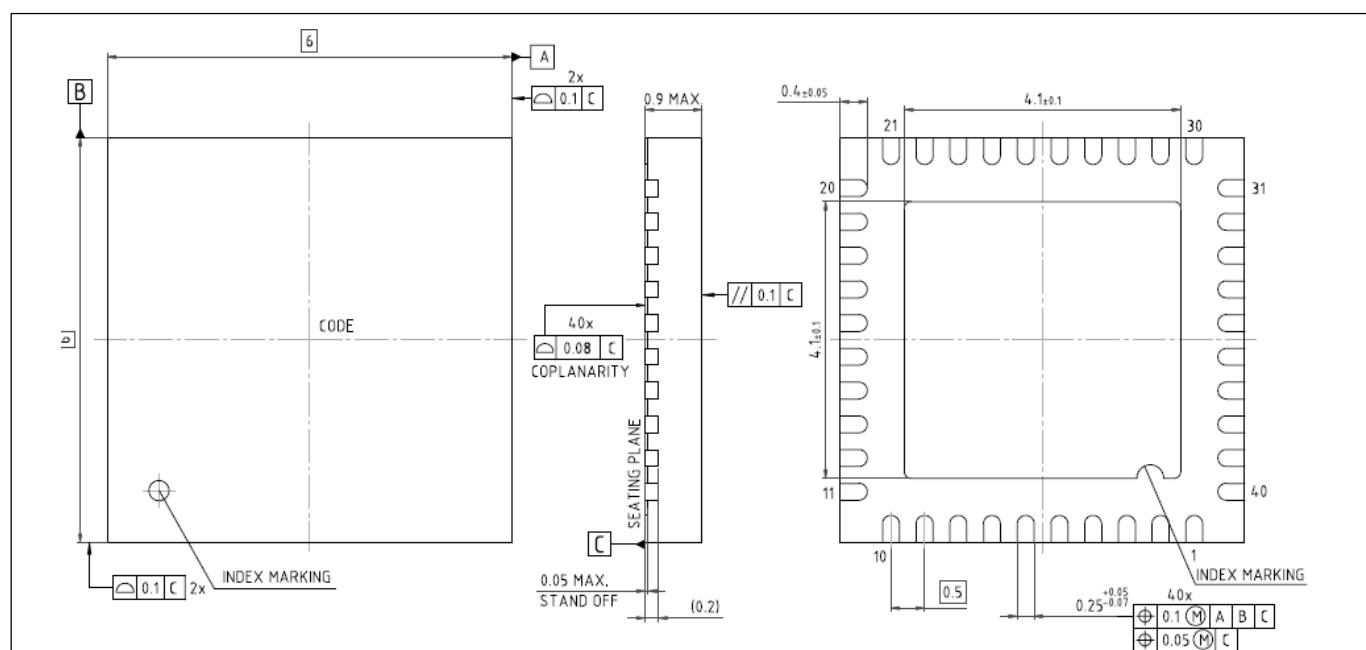

## 7.1 XDPP1100-Q024 QFN 4x4 – 24 引脚

图 33 PG-VQFN-24-20

## 7.2 XDPP1100-Q040 QFN 6x6 - 40 引脚

图 34 PG-VQFN-40-19

## 7.3 零件标记

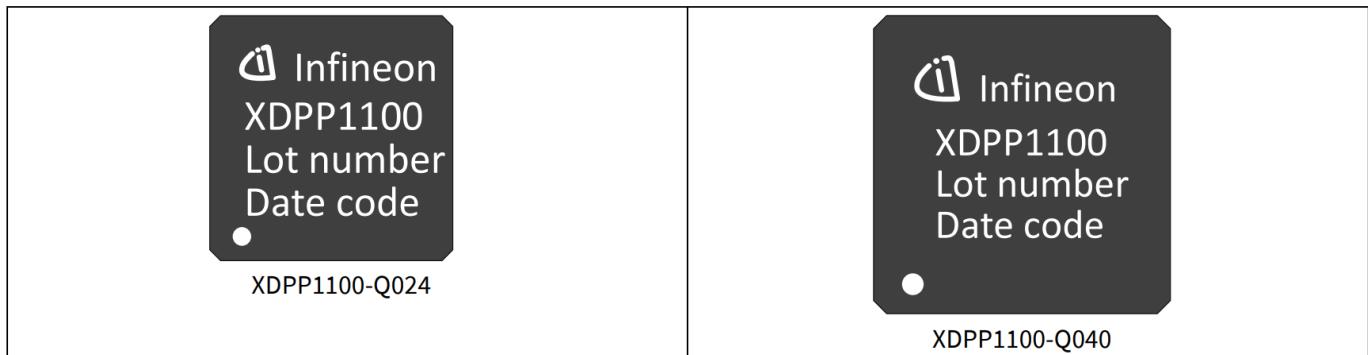

零件标记如图35所示。

图 35 封装标记

批号和日期代码示例：

批号：1YUS1ANNB03

日期代码：H2018B03

日期代码末尾的 B03 是批号的最后 3 位数字。

## 修订记录

## 修订记录

| Document version | Date of release | Description of changes                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision 2.0     | 2020-11-20      | Final data sheet                                                                                                                                                                                                                                                                                                           |

| Revision 2.1     | 2021-07-28      | <p>Update SDA, SCL, SMBALERT <math>V_{IH\_MIN}</math> threshold, from 2.3 V to 2.1 V (3.3 V mode), from 1.4 V to 1.35 V (1.8 V mode).</p> <p>Add GPIO spec GPIO Inputs/Outputs of PWRGD, BPWRGD, PWM6, PWM11 (Table 19)</p> <p>Update GPIO spec (Table 18), <math>V_{IH\_MIN}</math> threshold, from 2.3 V to 2.1 V</p>    |

| Revision 2.2     | 2022-04-25      | <p>Updated Table 8 thermal impedance. Corrected <math>R_{\theta JCT}</math> junction to case (top) and <math>R_{\theta JCB}</math> junction to case (bottom).</p> <p>Updated Table 10, removed <math>V_{DD}</math> falling threshold.</p> <p>5.3.1, updated valid VDD description.</p> <p>5.4, removed VDD UVLO fault.</p> |

| Revision 2.3     | 2023-1-18       | <p>Updated block diagram (removed XMER processor).</p> <p>Changed recommended supply voltage to 2.97 V to 3.63 V (from 3.0 V to 3.6 V). Updated the electrical test condition, VDD voltage = 2.97 V to 3.63 V.</p>                                                                                                         |

## **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2023-1-18**

**Published by**

**Infineon Technologies AG**

**81726 München, Germany**

**© 2023 Infineon Technologies AG. All Rights Reserved.**

**Do you have a question about

this document?**

**Email:** [erratum@infineon.com](mailto:erratum@infineon.com)

**Document**

**reference ifx1**

## **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office ([www.infineon.com](http://www.infineon.com)).

## **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the type in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.