# EZ-PD™ PMG1-S3 第1世代パワー・デリバリーMCU

## EZ-PD™ PMG1 ファミリの概要

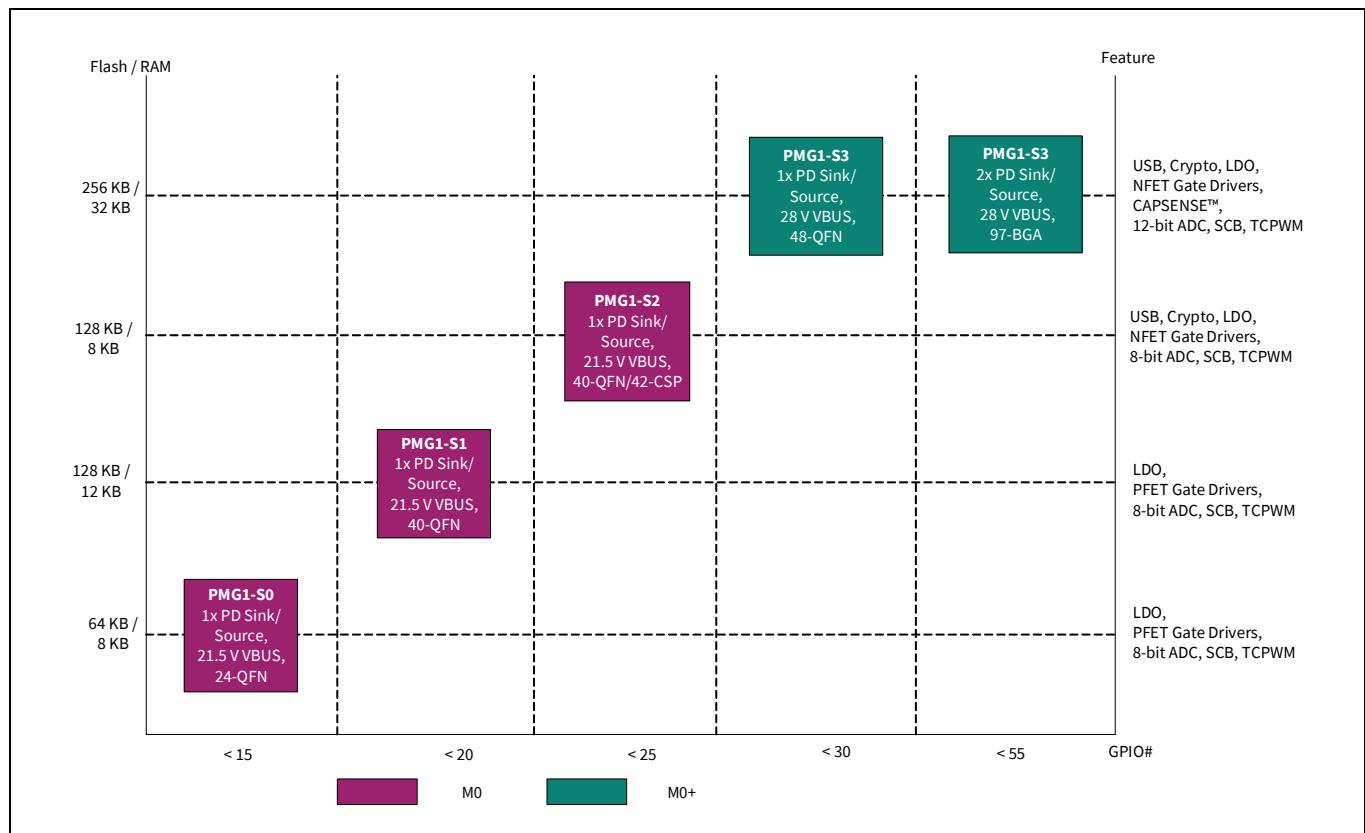

EZ-PD™ PMG1(第1世代パワー・デリバリーMCU)は、高電圧のUSB-Cパワーデリバリー(PD)マイクロコントローラー(MCU)のファミリです。これらのチップには、Arm® Cortex®-M0/M0+CPU、USB-C PDコントローラー、およびアナログとデジタルペリフェラルが搭載されます。EZ-PD™ PMG1は、高電圧USB-C PDポートとの間で電力を供給/消費し、マイクロコントローラーを活用して追加の制御機能を提供する組込みシステムを対象としています。Figure 1に、EZ-PD™ PMG1ファミリのセグメンテーションを示します。

Figure 1. PMG1 ファミリ セグメンテーション

## EZ-PD™ PMG1 ファミリの概要

Table 1 に、EZ-PD™ PMG1 ファミリのさまざまな MCU の機能の比較を示します。

Table 1. EZ-PD™ PMG1 ファミリのさまざまな MCU の機能の比較

| サブシステム<br>または範囲            | 項目                                                          | PMG1-S0                                                           | PMG1-S1                                                                   | PMG1-S2                                                           | PMG1-S3                                                                      |

|----------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------|

| CPU およびメモリ<br>サブシステム       | コア                                                          | Arm® Cortex®-M0                                                   | Arm® Cortex®-M0                                                           | Arm® Cortex®-M0                                                   | Arm® Cortex®-M0+                                                             |

|                            | 最大周波数 (MHz)                                                 | 48                                                                | 48                                                                        | 48                                                                | 48                                                                           |

|                            | フラッシュ (KB)                                                  | 64                                                                | 128                                                                       | 128                                                               | 256                                                                          |

|                            | SRAM (KB)                                                   | 8                                                                 | 12                                                                        | 8                                                                 | 32                                                                           |

| パワー<br>デリバリー               | パワー デリバリー<br>ポート                                            | 1                                                                 | 1                                                                         | 1                                                                 | 48-QFN の場合は<br>1 ポート<br>97-BGA の場合は<br>2 ポート                                 |

|                            | ロール                                                         | DRP                                                               | DRP                                                                       | DRP                                                               | DRP                                                                          |

|                            | MOSFET ゲート ド<br>ライバ                                         | 1x PFET                                                           | 2x PFET                                                                   | 2x NFET                                                           | 柔軟な 2x NFET                                                                  |

|                            | フォールト保護                                                     | VBUS OVP, UVP, お<br>よび OCP。<br>SCP<br>(ソース コンフィ<br>ギュレーションの<br>み) | VBUS OVP, UVP, お<br>よび OCP。<br>SCP および RCP<br>(ソース コンフィ<br>ギュレーションの<br>み) | VBUS OVP, UVP, お<br>よび OCP                                        | VBUS OVP, UVP, および<br>OCP。<br>SCP および RCP<br>(ソース コンフィギュ<br>レーションの<br>み)     |

| USB                        | Billboard クラスを<br>サポートする統合<br>されたフルスピード<br>USB 2.0 デバイ<br>ス | 無                                                                 | 無                                                                         | 有                                                                 | 有                                                                            |

| 電圧範囲                       | 電源電圧 (V)                                                    | VDDD (2.7 ~ 5.5)<br>VBUS (4.0 ~ 21.5)                             | VSYS (2.75 ~ 5.5)<br>VBUS (4 ~ 21.5)                                      | VSYS (2.7 ~ 5.5)<br>VBUS (4.0 ~ 21.5)                             | VSYS (2.8 ~ 5.5)<br>VBUS (4 ~ 28)                                            |

|                            | IO (V)                                                      | 1.71 ~ 5.5                                                        | 1.71 ~ 5.5                                                                | 1.71 ~ 5.5                                                        | 1.71 ~ 5.5                                                                   |

| デジタル                       | SCB (I <sup>2</sup> C/UART/SPI<br>として設定可能)                  | 2                                                                 | 4                                                                         | 4                                                                 | 48-QFN の場合は 7 (そ<br>のうち 5 のみを SPI お<br>よび UART として設定<br>可能)<br>97-BGA の場合は 8 |

|                            | TCPWM<br>ブロック<br>(タイマー, カウン<br>ター, パルス幅変<br>調器として設定可<br>能)  | 4                                                                 | 2                                                                         | 4                                                                 | 8                                                                            |

|                            | ハードウェア<br>認証ブロック<br>(暗号)                                    | 無                                                                 | 無                                                                         | 有<br>(AES-128/192/256,<br>SHA1, SHA2-224,<br>SHA2-256, PRNG, CRC) | 有<br>(AES-128, SHA2-256,<br>TRNG, ベクトルユニッ<br>ト)                              |

| アナログ                       | ADC                                                         | 2x 8 ビット SAR                                                      | 1x 8 ビット SAR                                                              | 2x 8 ビット SAR                                                      | 2x 8 ビット SAR<br>1x 12 ビット SAR                                                |

|                            | 内蔵温度<br>センサー                                                | 有                                                                 | 有                                                                         | 有                                                                 | 有                                                                            |

| ダイレクト<br>メモリ アクセス<br>(DMA) | DMA                                                         | 無                                                                 | 無                                                                         | 無                                                                 | 有                                                                            |

| GPIO                       | I/O の最大数                                                    | 12 (10 + 2 Fail-Safe)                                             | 17 (15 + 2 Fail-Safe)                                                     | 20 (18 + 2 Fail-Safe)                                             | 48-QFN の場合は 26<br>(24 + 2 Fail-Safe)<br>97-BGA の場合は 50<br>(48 + 2 Fail-Safe) |

## EZ-PD™ PMG1 ファミリの概要

Table 1. EZ-PD™ PMG1 ファミリのさまざまな MCU の機能の比較 ( 続き )

| サブシステム<br>または範囲 | 項目             | PMG1-S0                             | PMG1-S1                             | PMG1-S2                                                                          | PMG1-S3                                                                                   |

|-----------------|----------------|-------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 充電規格            | 充電ソース          | BC 1.2, AC, AFC,<br>および QC 3.0      | BC1.2, AC                           | BC1.2, AC                                                                        | BC 1.2, AC, AFC,<br>および QC 3.0                                                            |

|                 | 充電シンク          | BC 1.2, AC,<br>および QC 2.0           | BC1.2, AC                           | BC1.2, AC                                                                        | BC1.2, AC,<br>および QC 2.0                                                                  |

| ESD 保護          | ESD 保護         | 有<br>( 人体モデルと<br>デバイス帯電<br>モデル )    | 有<br>( 人体モデルと<br>デバイス帯電<br>モデル )    | 有<br>( 人体モデルと<br>デバイス帯電<br>モデル )                                                 | 有<br>( 人体モデルと<br>デバイス帯電<br>モデル )                                                          |

| パッケージ           | パッケージ<br>オプション | 24-QFN<br>( 4 × 4mm, 0.5mm<br>ピッチ ) | 40-QFN<br>( 6 × 6mm,<br>0.5mm ピッチ ) | 40-QFN<br>( 6 × 6mm,<br>0.5mm ピッチ )<br>42-CSP<br>( 2.63 × 3.18mm,<br>0.4mm ピッチ ) | 48-QFN<br>( 6 × 6mm,、<br>0.5mm ピッチ )<br>97-BGA<br>( 6 × 6mm,<br>0.5mm および 0.65mm<br>ピッチ ) |

本書の残りの部分では、EZ-PD™ PMG1-S3 デバイスについて詳しく説明します。

## EZ-PD™ PMG1-S3 の概要

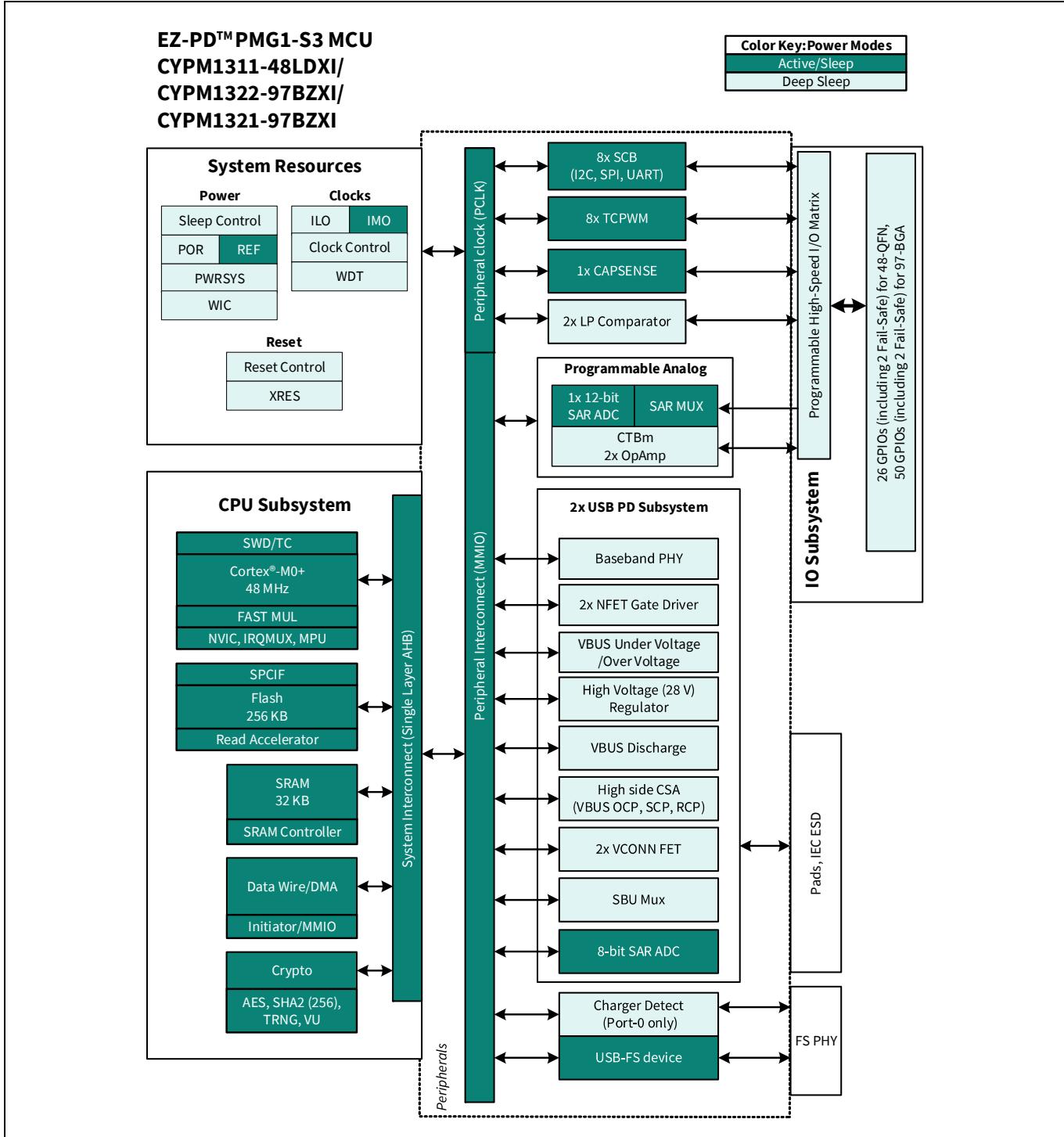

EZ-PD™ PMG1-S3 は PMG1 ファミリのデバイスであり、256KB フラッシュ、32KB SRAM、50 個の GPIO、フルスピード USB デバイス コントローラー、認証用暗号化エンジン、アナログリソース (ADC、オペアンプ、コンパレータ、CAPSENSE™) およびデュアル Type-C PD ポートを備えています。このデバイスは、デバイス、ドック、およびアクセサリ アプリケーションを対象としており、QFN および BGA パッケージで提供されています。

## 特長

- **32 ビット MCU サブシステム**

- DMA 付きの 48MHz Arm® Cortex®-M0+ CPU

- 256KB フラッシュ

- 32KB SRAM

- PD コード付きの 96KB ROM

- **Type-C/PD ブロック**

- それがベースバンドトランシーバを備えた最大 2 個の Type-C/PD ブロック

- 2 組の統合された VBUS NFET ゲートドライバ

- VBUS プロバイダまたはコンシユーマパスでの使用のために構成されたゲートドライバの突入電流を制限するスルーレート制御

- 統合された USB パワー デリバリー (USB-PD) 3.2 サポート

- 28V の Extended Power Range (EPR) に対応

- 高電圧 (28V) のレギュレータおよび VBUS 放電

- 構成可能な VBUS 過電圧保護 (OVP)、過電流保護 (OCP)、短絡保護 (SCP)、および逆電流保護 (RCP)

- OCP 付きの VCONN FET

- 97-BGA 製品の代替モード (DisplayPort と Thunderbolt) 用の 2 個の統合された 3:1 SBU アナログ マルチプレクサ

- 液体検知と腐食軽減

- Type-C コネクタで水分 / 液体検知をサポート

- 液体検知ブロックを内蔵

- 腐食軽減モードを実装

- インターフェース

- I<sup>2</sup>C、SPI または UART に実行時に再構成可能な最大 8 個のシリアル通信ブロック (SCB)

- 最大 8 個のタイマー / カウンター / パルス幅変調器 (TCPWM)

- プログラマブル GPIO ピン

- 最大 50 個の GPIO ピン

- すべての GPIO ピンは CAPSENSE™、アナログ、またはデジタルピンに対応

- プログラム可能な駆動モード、駆動強度およびスルーレート

- 内蔵アナログブロック

- 2 個の 8 ビット SAR ADC

- 1 個の 12 ビット SAR ADC

- 2 個のオペアンプ

- 2 個の LP コンパレータ

- 静電容量センシング

- CAPSENSE™ シグマ デルタ (CSD) はクラス最高の信号対ノイズ比 (SNR) および耐水性を提供

- インフィニオンが提供するソフトウェアコンポーネントによる容易な静電容量センシングの設計

- 自動ハードウェアチューニング (SmartSense)

- セキュアなファームウェアブートおよび署名付きファームウェア更新用のハードウェア暗号化エンジン

- **USB フルスピードデバイス**

- レガシー / 独自の充電をサポートする充電器検出ブロック

- 電源

- VSYS (2.8V ~ 5.5V)

- VBUS (4V ~ 28V)

- GPIO 用の独立した電源電圧ピンには I/O 上の 1.71V ~ 5.5V 信号方式が可能

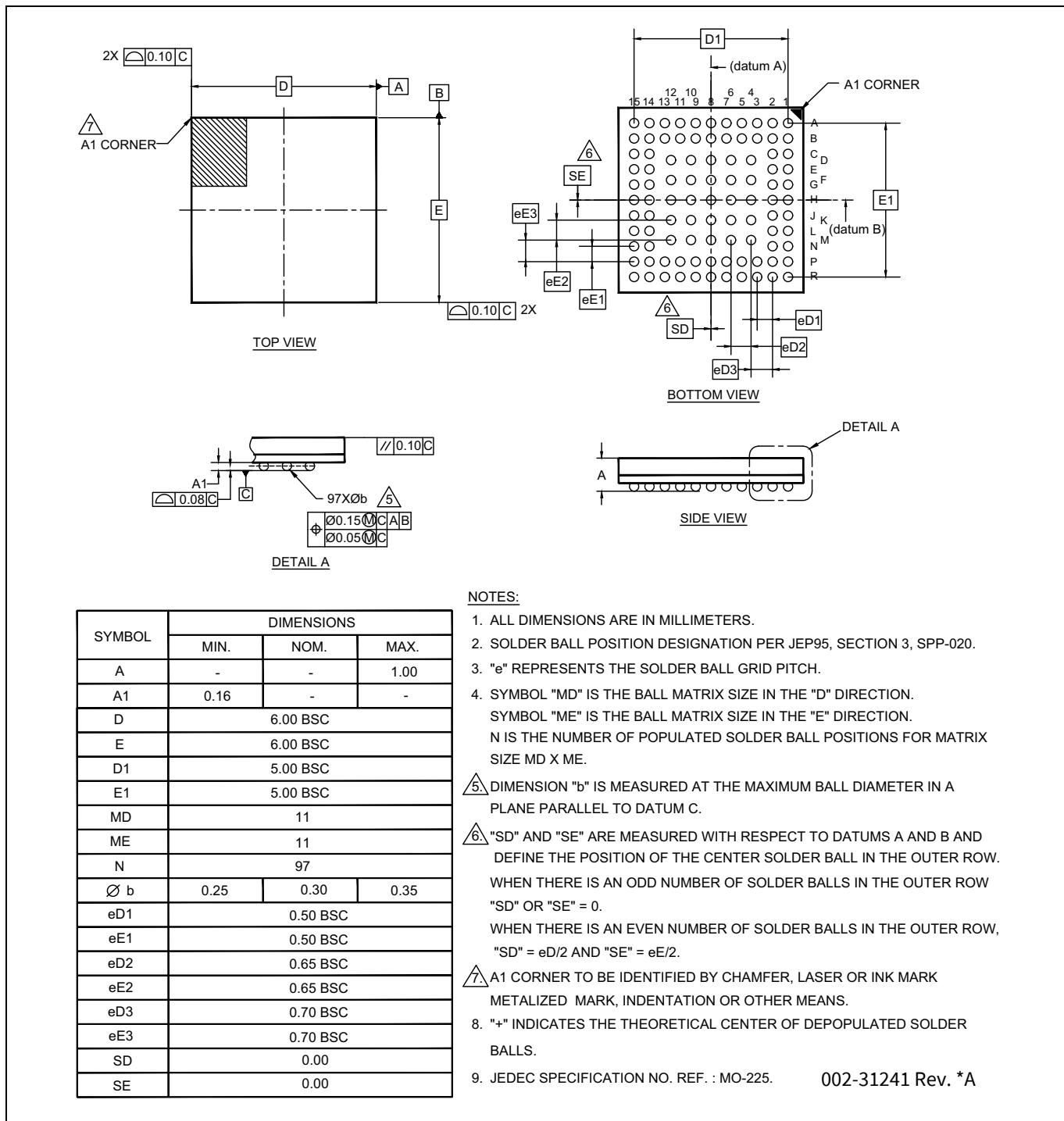

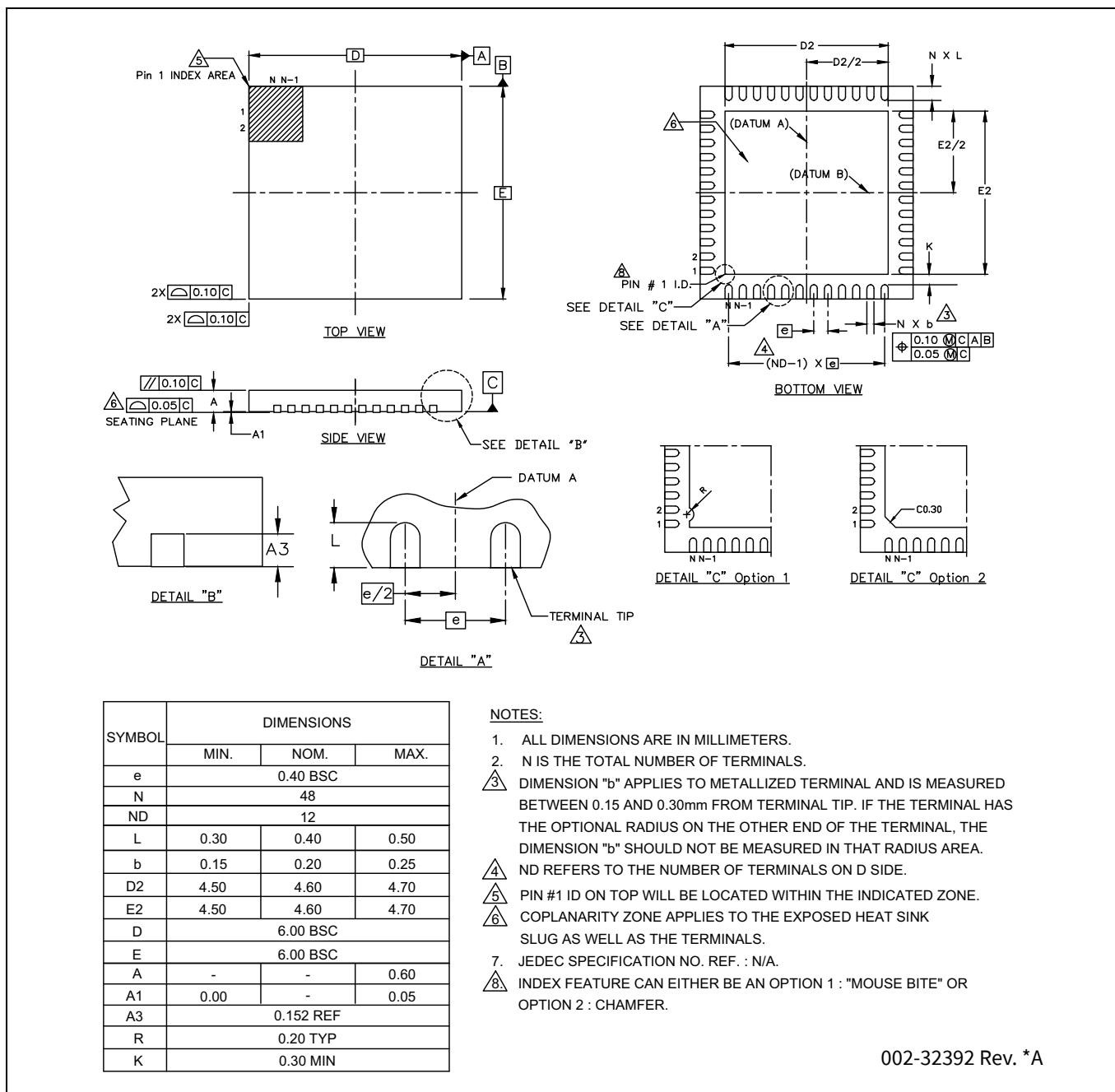

- パッケージ

- 48-QFN

- 97-BGA

- ソフトウェアツール

- ModusToolbox™

## ブロック図

## ブロック図

## 目次

## 目次

|                                           |    |

|-------------------------------------------|----|

| <b>EZ-PD™ PMG1 ファミリの概要</b>                | 1  |

| <b>EZ-PD™ PMG1-S3 の概要</b>                 | 4  |

| <b>特長</b>                                 | 4  |

| <b>ブロック図</b>                              | 5  |

| <b>目次</b>                                 | 6  |

| <b>1 開発サポート</b>                           | 7  |

| 1.1 ドキュメント                                | 7  |

| 1.2 オンライン                                 | 7  |

| 1.3 ツール                                   | 7  |

| 1.4 ModusToolbox™ IDE および EZ-PD™ PMG1 SDK | 7  |

| <b>2 機能概要</b>                             | 8  |

| 2.1 CPU およびメモリサブシステム                      | 8  |

| 2.2 システムリソース                              | 9  |

| 2.3 アナログブロック                              | 10 |

| 2.4 USB-PDサブシステム                          | 11 |

| 2.5 USB 2.0 フルスピードデバイスおよび充電検出             | 15 |

| 2.6 固定機能デジタルブロック                          | 15 |

| 2.7 特殊機能ペリフェラル                            | 16 |

| <b>3 電源システムの概要</b>                        | 17 |

| <b>4 ピン配置</b>                             | 18 |

| <b>5 アプリケーション図</b>                        | 25 |

| <b>6 電気的仕様</b>                            | 28 |

| 6.1 絶対最大定格                                | 28 |

| 6.2 デバイスレベルの仕様                            | 32 |

| 6.3 GPIO                                  | 35 |

| 6.4 アナログペリフェラル                            | 38 |

| 6.5 デジタルペリフェラル                            | 44 |

| 6.6 システムリソース                              | 49 |

| 6.7 USB PDペリフェラル                          | 51 |

| <b>7 注文情報</b>                             | 60 |

| 7.1 注文コードの定義                              | 61 |

| <b>8 パッケージ</b>                            | 62 |

| <b>9 略語</b>                               | 65 |

| <b>10 本書の表記法</b>                          | 67 |

| 10.1 測定単位                                 | 67 |

| 改訂履歴                                      | 68 |

| <b>免責事項</b>                               | 69 |

## 1. 開発サポート

EZ-PD™ PMG1 ファミリには、開発プロセスを支援する豊富なドキュメント、開発ツールおよびオンラインリソースが用意されています。[USB-C High Voltage Microcontroller](#)をご覧ください。

### 1.1 ドキュメント

EZ-PD™ PMG1 ファミリをサポートするドキュメント一式により、ユーザーは疑問点に対する答えを素早く見つけられます。重要なドキュメントのいくつかをここにリストアップします。

**ModusToolbox™ ドキュメント** : ModusToolbox™ (MTB) の使用に関する段階を追った手引き書です。ソフトウェアユーザー ガイドには、MTB によるビルド プロセスの詳細、MTB を用いたソース制御の使い方などが記載されています。

**コンポーネント データシート** : EZ-PD™ PMG1 の柔軟性によって、デバイスが量産に入って長期間経過した後でも新しいペリフェラル (コンポーネント) を作成できます。コンポーネント データシートには、機能説明、API ドキュメント、推奨サンプルコード、AC/DC 仕様を含む、特定のコンポーネントの選択および使用に必要な情報がすべて記載されています。

**アプリケーション ノート** : 入門のアプリケーション ノートとハードウェア設計ガイドラインが含まれます。

**テクニカル リファレンス マニュアル** : テクニカル リファレンス マニュアル (TRM) には、すべての EZ-PD™ PMG1 レジスタの詳細な説明など、EZ-PD™ PMG1 デバイスを使用する際に必要な技術的詳細がすべて記載されています。TRM は [USB High Voltage Microcontroller](#) の「Documentation」セクションにあります。

### 1.2 オンライン

印刷された資料のほかに、[Infineon community フォーラム](#)によって 24 時間 365 日、世界中の他のユーザーや PMG1 の専門家と連絡がとれます。

### 1.3 ツール

業界標準のコア、プログラミングおよびデバッグ インターフェースを備えた EZ-PD™ PMG1 ファミリは、開発ツール エコシステムの一部です。

革新的で使いやすい ModusToolbox™ IDE、サポートされるサードパーティのコンパイラ、プログラマ、デバッガおよび開発キットの最新情報については、Web サイト [ModusToolbox™ ソフトウェア](#) をご覧ください。

### 1.4 ModusToolbox™ IDE および EZ-PD™ PMG1 SDK

ModusToolbox™ は、Windows、macOS、および Linux プラットフォームで実行される Eclipse ベースの開発環境であり、ModusToolbox™ IDE と EZ-PD™ PMG1 SDK を含みます。ModusToolbox™ IDE はアプリケーションを構築するために、いくつかのデバイス リソース、ミドルウェアおよびファームウェアを組み合わせます。ModusToolbox™ を使用すると、デバイス リソースとミドルウェア ライブラリを有効にして構成し、C/C++/ アセンブリのソースコードを記述し、デバイスをプログラムしてデバッグできます。

PMG1 SDK は EZ-PD™ PMG1 MCU ファミリ向けのソフトウェア開発キットです。SDK を使用すると、デバイス リソースの複雑さを理解しなくとも、サポートされているデバイスのファームウェアを簡単に開発できます。

ModusToolbox™ の使用の詳細については、「[AN232553 - Modus Toolbox™ ソフトウェアを使用する EZ-PD™ PMG1 MCU 入門](#)」と、ModusToolbox™ に統合されたドキュメントおよびヘルプを参照してください。

## 機能概要

### 2. 機能概要

#### 2.1 CPU およびメモリ サブシステム

##### 2.1.1 CPU

PMG1-S3 の Cortex®-M0+ は 32 ビット MCU であり、広範なクロック ゲーティングに対応した低消費電力動作に最適化されています。ほとんどの場合、これは 16 ビット命令を使用し、Thumb-2 命令セットのサブセットを実行します。インフィニオンは本製品に、1 サイクルで 32 ビットの結果を出すハードウェア乗算器を実装しています。これは、32 の割込み入力を備えたネスト型ベクタ割込みコントローラー (NVIC) ブロックとウェイクアップ割込みコントローラー (WIC) を含みます。WIC はディープスリープモードからプロセッサを復帰させることができます。これにより、チップがディープスリープモードにあるときにメインプロセッサへの電源を切れます。

CPU サブシステムはまた、16 チャネルの DMA/DataWire ブロックと 2 線式 JTAG のシリアルワイヤデバッグ (SWD) インターフェースも備えています。PMG1-S3 に使用するデバッグコンフィギュレーションには、4 個のブレークポイント (アドレス) コンパレータと 2 個のウォッチポイント (データ) コンパレータがあります。

##### 2.1.2 フラッシュ, ROM, SRAM

PMG1-S3 は 256KB (2x128KB) フラッシュ モジュールを備えています。ブートおよびコンフィギュレーションルーチンを含む 96KB の監視 ROM も提供されています。PMG1-S3 用に搭載されている SROM には、フラッシュ消去およびプログラム ルーチンに加えて、フラッシュチェックサム ルーチンも含まれています。ディープスリープ中に保持される 32KB の SRAM も搭載されています。

##### 2.1.3 暗号化アクセラレータ

暗号アクセラレータ ブロックは以下の要件に対応しています。

- 非対称キー暗号化用のベクトル ユニット (VU)

- SHA2 (256 ビット)

- RSA-4096、3072、ECC-256 を実行できる非対称暗号化用のベクトル ユニット

- フォワード ブロック暗号をサポートする AES (128 ビット)

- 真性乱数発生器 (AIS-31 準拠)

- 48MHz での性能

- RSA-3072 検証性能 : 25ms

- 64KB データに対する SHA-2 (256 ビット) 性能 : 10ms

- セキュアブートからユーザー プログラムへの制御移転時間 : 50ms

- 公開鍵保管

- フラッシュ: フラッシュに保存された 2KB の RSA-3072 キー構造。キー構造はモジュラス、指数および 3 つの係数を含みます。

## 機能概要

### 2.2 システムリソース

#### 2.2.1 電源システム

電源システムは、「[電源システムの概要](#)」で詳細に説明されています。電源システムは各モードに応じた電圧レベルを保証します。これを実現するために、機能の正常な動作に必要な電圧レベルに達成するまでモードへの移行を遅延させる（例えば、パワーオンリセット(POR)のとき）、または安全でない電源電圧レベルが発生する可能性がある場合にリセット（電圧低下検出(BOD)）を発生させます。PMG1-S3は、2.8V～5.5V(VSYS)または4V～28V(VBUS)の単一の外部電源電圧で動作し、3つの電力モード（アクティブ、スリープ、ディープスリープ）があります。これらの電力モード間の遷移は電源システムによって管理されます。

PMG1-S3の電源システムは、内部ペリフェラルに基づいて60mAに対応するように設計されています。28Vレギュレータで動作する場合は、パッケージとVBUS電源電圧に応じて、（ペリフェラルをオフにすることで）消費電流を抑え、ダイの $T_{JA}$ が125°Cを超えないようにしてください。

#### 2.2.2 クロックシステム

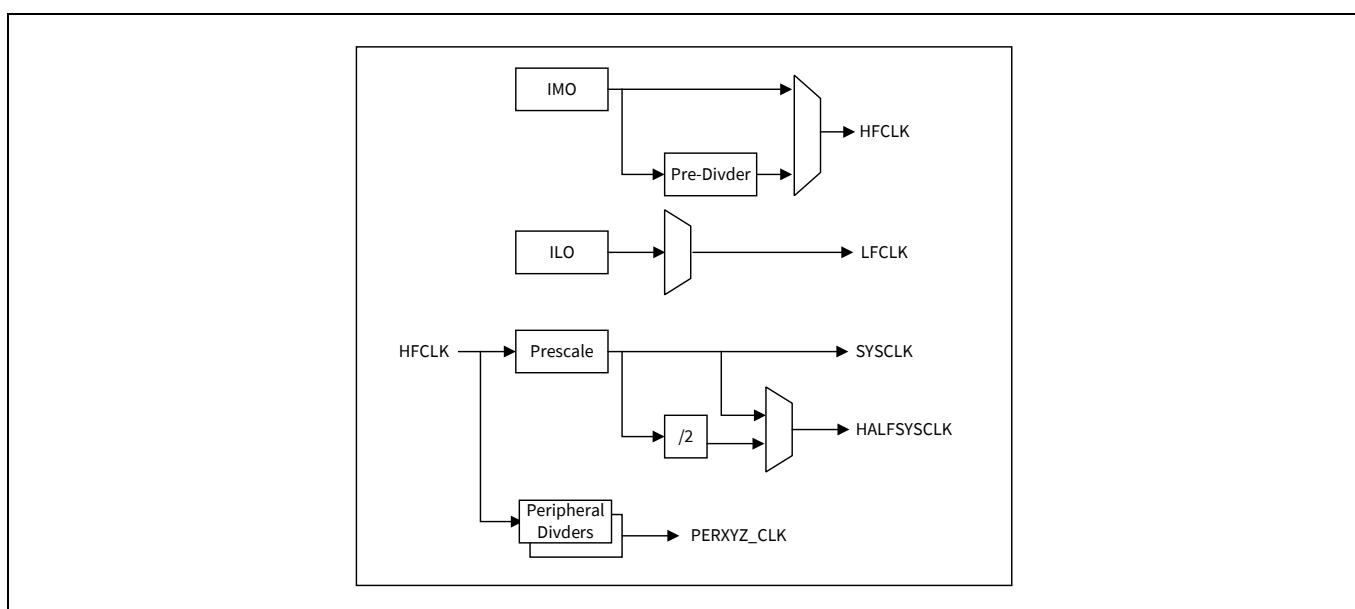

PMG1-S3のクロックシステムは、M0S8プラットフォームの一部として構成されています。PMG1-S3は完全に統合されたクロックを備えているため、外部水晶発振器を必要としません。クロックシステムは、クロックを必要とするすべてのサブシステム(SCB、TCPWM、プログラマブルアナログサブシステム(PASS)およびPD)にクロックを供給し、グリッチなしに異なるクロックソース間で切り替えます。また、メタステーブル状態が発生しないように保証します。

Figure 2に、内蔵主発振器(IMO)および内部低消費電力発振器(ILO)から成るPMG1-S3のクロックシステムを示します。PERXYZ\_CLKは、さまざまなペリフェラルのクロックを表します。

Figure 2. PMG1-S3 のクロックアーキテクチャ

HFCLK信号は、アナログとデジタルペリフェラル用に同期クロックを生成するために分周できます。PMG1-S3には21個のクロック分周器があります（5個の分数分周器、16個の整数分周器）。アナログクロックがデジタルクロックに先行し、デジタルクロック関連のノイズが発生する前にアナログイベントが起きるようにします。デジタルクロック分周器は、有効なクロックを生成します（つまり、「N」が除数のNクロッキングの1）。アナログクロック分周器は、許可されたすべての周波数でアナログ性能を維持するために、真の50%のデューティ比を提供する必要があります。

#### IMO クロックソース

IMOは、PMG1-S3の内部クロックの主要な供給源です。 $\pm 2\%$ の精度を達成するために製造中に調整されます。調整した値はフラッシュメモリの監視行に格納されています。変化を補正するために、フラッシュから追加された調整設定を使用することができます。IMOのデフォルト周波数は48MHz $\pm 2\%$ です。IMOのRMSジッタは12ビットSARの精度を実現します。

#### ILO クロックソース

ILOは超低消費電力かつ比較的不正確な発振器であり、主にUSBサスPEND（ディープスリープ）モードでペリフェラルの動作用にクロックを生成するために使用されます。これは、未調整の精度が-50%～+100%で、 $\pm 55\%$ 以内に調整可能な40kHzの発振器です。

## 機能概要

### 2.2.3 ウオッチドッグ タイマー

ウォッチドッグ タイマーは、ILO をクロック ソースとして動作するクロック ブロックに実装されます。ディープスリープ時のウォッチドッグ動作を可能にし、タイムアウトが発生する前に処理されなかった場合にウォッチドッグリセットを生成します。タイマーは、リセットの生成に加えて、必要に応じて割込みを生成するためにも使用できます。

### 2.2.4 リセット

PMG1-S3 は、ソフトウェア リセットを含むさまざまなソースからリセットできます。リセットイベントは非同期であり、既知の状態への復帰を保証しています。リセットの原因はレジスタに記録されます。そのレジスタはリセット中も保存され、ソフトウェアがリセットの原因を判断できます。電源投入またはリコンフィギュレーション中にコンフィギュレーションおよび複数のピン機能に伴う複雑さを避けるために、外部リセット用に予約されているピン (XRES) があります。

### 2.2.5 電圧リファレンス

PMG1-S3 リファレンス システムは、すべての必要となる内部リファレンス電圧を生成します。より優れた信号対ノイズ比 (SNR) と絶対精度を実現するために、GPIO ピンを使って内部リファレンスをバイパスするか、または 12 ビット SAR ADC のために外部リファレンスを使用できます。ピンの内部リファレンスは、内蔵オペアンプの 1 つを使ってバッファリングし、外部リファレンスとして使用できます。

## 2.3 アナログ ブロック

### 2.3.1 12 ビット SAR ADC

12 ビットの 1Msps SAR ADC は 18MHz の最大クロックレートで動作し、12 ビット変換を行うためにその周波数で少なくとも 18 クロックを必要とします。ADC クロック入力は、CPU クロック レートを整数値で割ることによって得られます。つまり、48MHz の CPU クロックレートでは、ADC の最大許容クロックレートは 16MHz です。16MHz のクロックレートでは、10 ビット変換が 1Msps で実行できます (10 ビット変換は少なくとも 16 クロックを要します)。整数分周器を使用すると、12 ビット ADC の性能は 48MHz で 890samples/s になり、1MS/s のピークは 18MHz または 36MHz で実現されます。ADC は、デューティ比が約 50% のクロックを必要とし、すべての整数分周器の値に提供します。

ユーザーに向けてブロック機能を拡張するため、ブロックにリファレンス バッファを追加し、また VDDA、VDDA/2、内部バンドギャップリファレンス (定格電圧が 1.2V) の 3 つの内部電圧リファレンス オプションおよび GPIO ピンを介した外部リファレンスを選択できるようにします。サンプルホールド (S/H) のアパートチャがプログラム可能であるため、SAR 入力を駆動するアンプのセトリング時間を規定するゲイン帯域幅要件を緩和でき、より安価な外部オペアンプを使用できるようにします。適切なリファレンス電圧が使用される限り、システム性能は真の 12 ビット精度で 68dB です。特に、内部リファレンス アンプ用の外部バイパスコンデンサ (P3.0: sar\_ext\_vref ピン経由) を設けることができます。

SAR は 8 入力シーケンサを介して固定した一連のピンに接続されます。シーケンサは、スイッチング オーバーヘッドの必要はなく、選択されたチャネルを自律的に巡回します (シーケンサ スキヤン) (つまり、合計サンプリング帯域幅は、単一のチャネルであれ複数のチャネルであれ 1Msps です)。シーケンサの切り替えは、ステートマシンを介して、またはファームウェア駆動の切り替えにより行われます。シーケンサの 1 つの機能は、CPU 割込みサービスの要件を緩和するための各チャネルのバッファリングです。信号をさまざまなソース インピーダンスと周波数に適合させるために、チャネルごとに異なるサンプリング時間をプログラムできます。また、デジタル化された値がプログラムされた範囲を超えた場合、レンジレジスタのペア (LOW レンジ値および HIGH レンジ値) による信号範囲の指定は、対応する範囲外の割込みで実施されます。これにより、シーケンサスキヤンが完了し、CPU が値を読み出してソフトウェア内で範囲外の値の有無を確認するのを待たず、範囲外の値を早く検出できます。

SAR は、CPU 帯域幅を節約するために、複数のサンプル平均化機能を持っています。SAR は校正およびその他の温度に依存する機能のために、内蔵温度センサーの出力を数値化します。SAR は高速クロック (最大 18MHz) を必要とするため、ディープスリープ モードに対応していません。SAR の動作範囲は 1.71V ~ 5.5V です。電源電圧 VDDA が 4V 未満の場合、パフォーマンスを維持するためにブースト ポンプを有効にする必要があります。

### 2.3.2 連続時間ブロック mini (CTBm)

PMG1-S3 には、2 個のオペアンプで構成される 1 個の CTBm ブロックがあります。オペアンプは、入力と出力が固定ピンに接続されており、3 つの電力モード (低、中、高) および 3 つの動作モード (コンパレーター、フォローアー、オペアンプ) を備えています。それらの出力は、SAR 入力のバッファとして使用できます。CTBm ブロックは、ポート 3 の IO ピンからアクセスすることで、すべての機能を提供します。また、アナログマルチプレクサバスを介して、ユーザーが希望する他のピンに接続することもできます。ブロックは、使用していないときは電源をオフにして (パワースイッチで) 電力を節約することもできます。また、ディープスリープ後のアナログシステムの高速起動を可能にするために、ディープスリープ モードで動作できます。オペアンプは、1mV より良いオフセット電圧を達成するために調整可能です。

### 2.3.3 溫度センサー

PMG1-S3 は、電流源によってバイアスされたダイオードから成る温度センサーを内蔵しています。この電流源は電力を節約するために無効にできます。ダイオードは、 $\pm 1\%$  の Typ 精度から最大  $\pm 5\%$  の誤差を達成するために生産時に校正されます。測定温度はダイオードの、オンチップ温度であるため、ダイオードは 12 ビット SAR ADC の近くに配置され、より正確な測定が可能になります。

## 機能概要

### 2.3.4 低消費電力コンパレータ

PMG1-S3 は、ディープスリープモードで動作できる低消費電力コンパレータのペアを内蔵しています。これにより、低消費電力モード中に外部電圧レベルを監視する能力を維持しながら、アナログシステムブロックを無効にすることが可能です。コンパレータ出力は、メタスタビリティを避けるために通常同期化されます。ただし、システム復帰回路がコンパレータの切り替えイベントによりアクティブになるような、非同期電力モード(ディープスリープ)で動作している場合を除きます。制御ループ(ヒステリシス制御など)を実装する目的で、同期化またはゲーティングなしでコンパレータ出力を使用できるようにするために、コンパレータ出力をピンにルーティングできます。

### 2.3.5 アナログマルチプレクサバス

PMG1-S3 は同心の、独立してチップの周辺を回る 2 個のバスを備えています。これらのバス (amux バスと呼ばれる) はファームウェアでプログラム可能なアナログスイッチに接続され、チップの内部リソース (SAR ADC、コンパレータ、CSD、およびオペアンプ) を I/O ポートのいずれのピンにも接続できます。2 個の amux はまた、CSD, 12 ビット ADC, および GPIO の接続を分離するために 3 分割することもできます。

## 2.4 USB-PD サブシステム

USB-PD サブシステムは、Type-C USB ポートへのインターフェースを提供します。

### 2.4.1 USB-PD 物理層

USB-PD サブシステムは、USB-PD 物理層ブロックとサポート回路で構成されています。物理層は、PD 3.1 規格に従って CC を介して BMC 符号化データを通信するトランスマッタとレシーバからなります。すべての通信は半二重です。物理層(PHY)は、チャネル上の通信エラーを最小限に抑えるために衝突回避を実行します。

### 2.4.2 VCONN FET

PMG1-S3 は、CC1 ピンまたは CC2 ピンのいずれかに電力を供給する 2 個の VCONN FET を内蔵しています。これらの VCONN FET を介して EMCA ケーブルに電力供給するための電源入力 (VCONN\_Source ピン) があります。FET は EMCA ケーブルに対して、CC1/CC2 ピン上で 4.85V ~ 5.5V の有効な VCONN 範囲でポートあたり 1.5W の電力を供給できます。一度に使用できる VCONN FET は 1 個のみです。

### 2.4.3 8 ビット SAR ADC

8 ビット SARADC はチップ上の汎用 AD 変換のアプリケーションに利用できる小 footprint の 8 ビット SARADC です。ファームウェア制御の適切なスプリッタを閉じることで、オンチップアナログマルチプレクサを介してすべての GPIO から ADC にアクセスできます。PMG1-S3 では、PD ポートごとに 1 個の ADC がインスタンス化されます。

## 機能概要

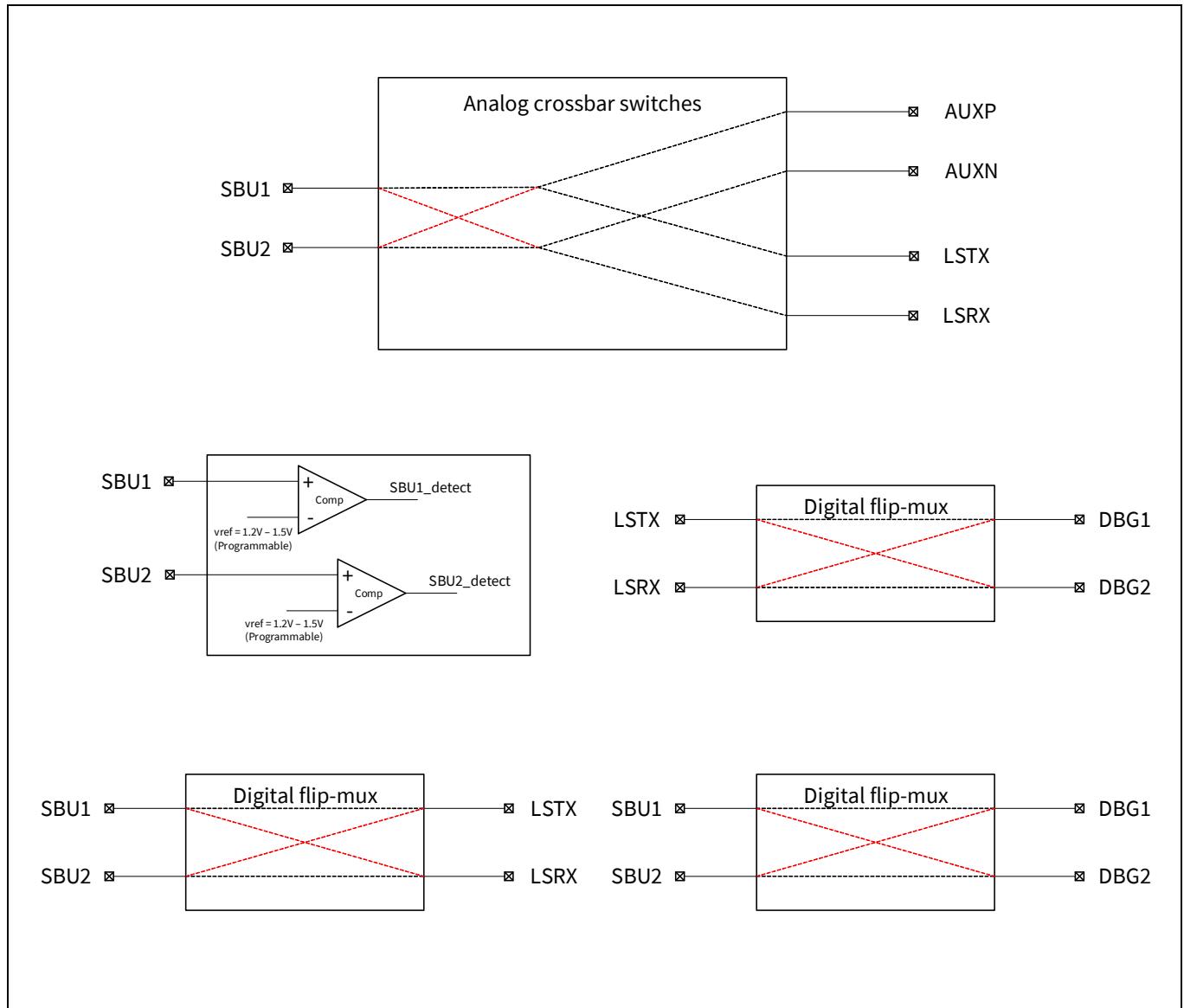

## 2.4.4 SBU マルチプレクサ

PMG1-S3 の 97-BGA パッケージは Type-C コネクタの SBU1 ピンと SBU2 ピンを、DisplayPort の AUX ピンまたは Thunderbolt の LSX ピンに接続するためのアナログスイッチを含みます。SBU ピンと LSTX/RX ピン、SBU ピンと UART デバッグ (DBG)、LSTX/RX ピンと UART デバッグピンは、Figure 3 に示すようにデジタル的に多重化されています。SBU ラインに接続された 2 組のコンペレタは、指定された基準電圧に基づいて SBU 信号を検出します。

Figure 3. SBU マルチプレクサ

## 機能概要

### 2.4.5 負荷スイッチ コントローラー

PMG1-S3 は、以下の機能を備えた負荷スイッチ コントローラーを搭載しています。

#### VBUS 過電圧と低電圧保護

チップは、VBUS 電源用の低電圧 / 過電圧 (UVOV) 検出回路を実装しています。UV と OV の両方の閾値はプログラム可能です。

#### VBUS 用の過電流 / 短絡電流 / 逆電流の障害検出コンパレータ

チップは、VBUS プロバイダ パス上の過電流 / 短絡電流 / 逆電流の障害検出をサポートしています。コネクタの VBUS パスに設けられた外付け抵抗 (5mΩ) がチップに接続されています。この抵抗の両端の電圧降下が監視され、障害を検出します。Type-C VBUS が VIN (VBUS\_NFET の前のプロバイダ 電圧) より大きい場合、PMG1-S3 は VBUS プロバイダ パス上の逆電流を 400mA に制限します。PMG1-S3 は迅速に反応し、VBUS プロバイダ の NFET をオフにします。この機能はコンシューマ パスではサポートされません。コンシューマ 側の電圧がコンシューマ パス上のコネクタ 側の電圧を上回ると常に逆電流が発生します。

#### VBUS 放電

PMG1-S3 は、高電圧 (28V) VBUS 放電回路を内蔵しています。ケーブルの取り外しが検出された後、チップは残留電荷を放電し、フローティング VBUS を vSafe0V に戻します。

#### VBUS レギュレータ

チップには、最大 3 つの入力電源 (VSYS および VBUS\_C (ポート 0 とポート 1)) があります。これらの電源で動作するレギュレータは、チップの動作電源電圧を生成します。VSYS は常に VBUS よりも優先されます。VSYS がない場合、レギュレータは VBUS (ポート 0 またはポート 1 のいずれか存在している方) からチップに電力を供給します。VBUS レギュレータは突入電流保護を提供しないため、最大 60mA の電流を供給できます。

#### VBUS\_NFET 用の柔軟なゲート ドライバ

PMG1-S3 は、外部 NFET を駆動するための 2 組の内蔵ゲート ドライバを備えています。これらは柔軟なゲート ドライバで、すなわち、プロバイダ または コンシューマ パスから独立しており、どちらのポートでも必要に応じて設定できます。プロバイダ / コンシューマ として設定されると、特定のボード / アプリケーションに対して、ボードの再製造なしで機能を変更することはできません。外部 NFET のみをサポートし、NFET は  $\pm$ VBUS\_NGDO\_MAX の最大 VGS をサポートできる必要があります。

### 2.4.6 Type-C コネクタの液体検知と腐食軽減

EZ-PD™ PMG1-S3 デバイスは、USB Type-C コネクタに統合された腐食軽減機能のオプションを提供します。

この機能は、内部ハードウェアとファームウェアの組み合わせによって実装されています。Type-C コネクタの未使用ピンのペアは、水分または液体検知ピンとして機能するように、EZ-PD™ PMG1-S3 MCU の特定のピンに接続する必要があります。Type-C ポートがソース /DRP モード (未接続状態) のときに、ファームウェアによって Type-C コネクタへの液体の存在が定期的にチェックされます。

EZ-PD™ PMG1-S3 デバイスにおける液体検知は、以下の 2 つの方法で行うことができます。

- MCU の SBU ピンを用いた液体検知

- MCU の Charger Detect ピンを用いた液体検知

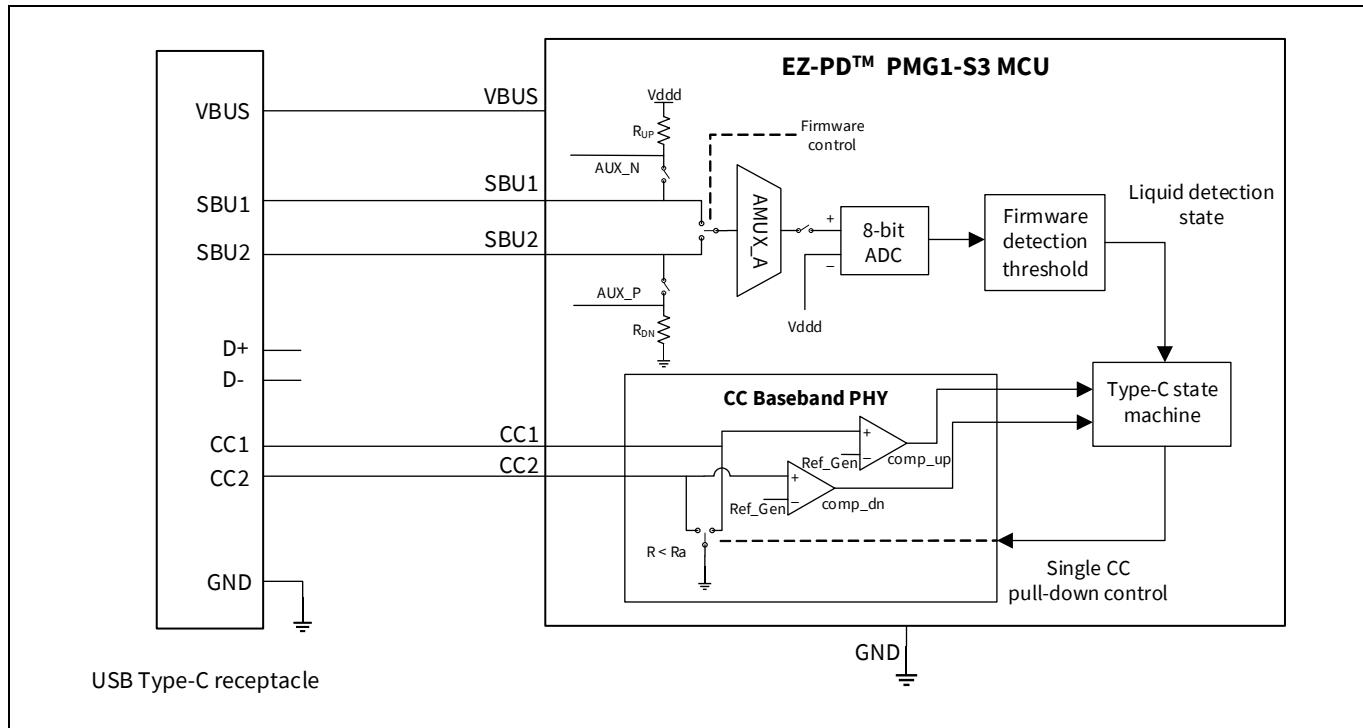

EZ-PD™ PMG1 MCU の SBU ピンを液体または水分の検知に使用する場合、Type-C コネクタの SBU1 ピンと SBU2 ピンは、Figure 4 に示すように、それぞれ MCU の SBU1 ピンと SBU2 ピンに接続されます。

## 機能概要

Figure 4. EZ-PD™ PMG1-S3 MCU の SBU ピンを使用した液体検出

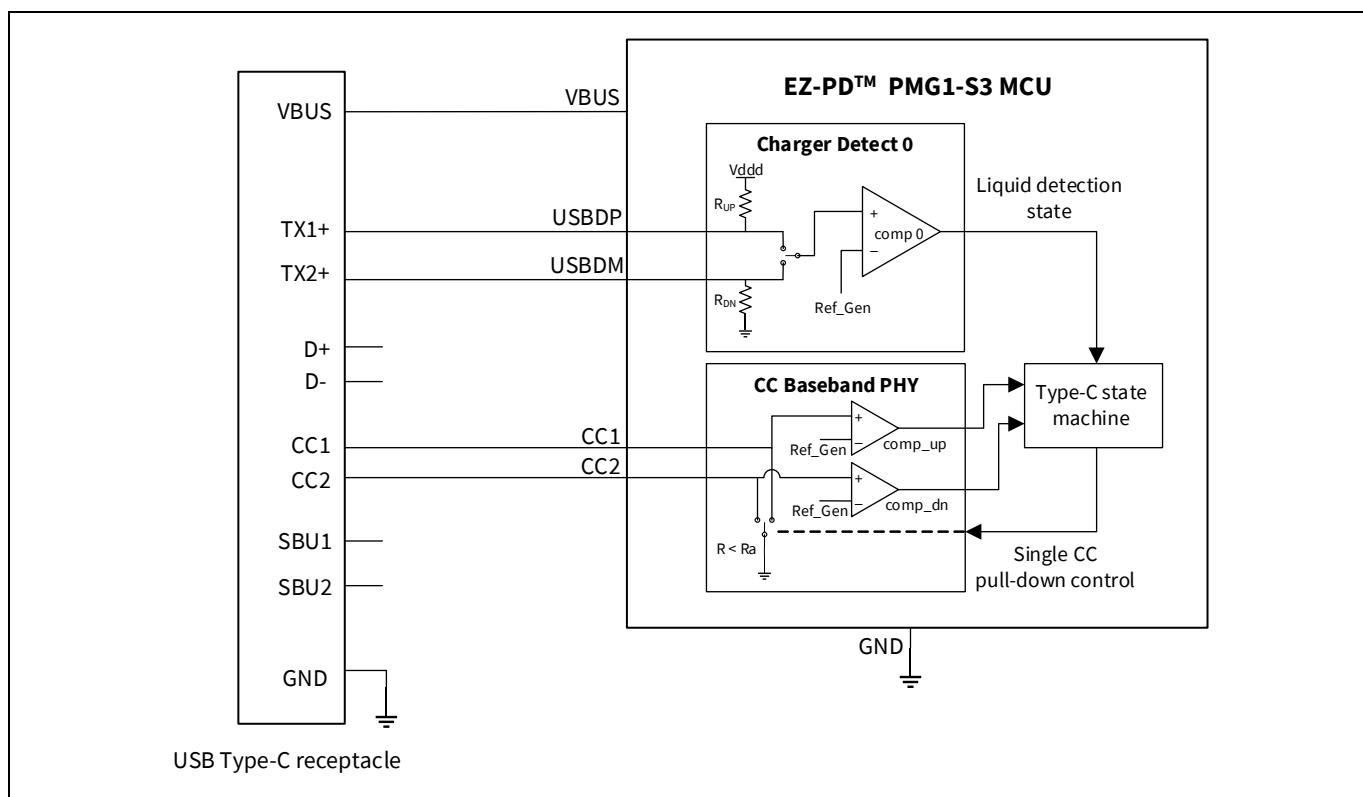

EZ-PD™ PMG1 MCU の充電器検出ピンを液体または湿気の検出に使用する場合、Figure 5 に示すように、Type-C コネクタの空き / 未使用のピンのペアが MCU の USBDP ピンと USBDM ピン (充電器検出ブロックに接続) に配線されます。

Figure 5. EZ-PD™ PMG1-S3 MCU の SBU ピンを使用した液体検出

## 機能概要

### 2.5 USB 2.0 フルスピード デバイスおよび充電検出

PMG1-S3 は、Billboard クラスおよびファームウェア ダウンロード用の HID クラスをサポートする 1 個の USB 2.0 FS デバイスを搭載しています。DP/DM ピンに接続された充電検出ブロックにより、PMG1-S3 は BC 1.2, Apple Charger, QC 3.0 および AFC 仕様に準拠した従来のバッテリ充電を検出できます。AFC プロトコルはソースモードでのみサポートされます。

### 2.6 固定機能デジタル ブロック

#### 2.6.1 タイマー / カウンター / PWM ブロック

タイマー / カウンター / PWM ブロックはユーザー プログラム可能な周期の 16 ビット カウンターからなります。キャプチャ レジスタは、I/O イベントなどのイベントのときにカウント値を記録します。周期 レジスタは、カウンターのカウントが周期 レジスタのカウントに等しくなるときにカウントを停止、または自動的にリロードします。比較 レジスタは、PWM デューティ比の出力として使用される比較 値信号を生成します。各 TCPWM カウンタには、スタート、ストップ、カウント、リロード、およびキャプチャの各入力があります。PWM モードでは、kill 入力を使用して出力を所定の状態に強制することができます。これは、例えばモーター駆動システムにおいて、過電流状態が示され、FET を駆動する PWM をソフトウェアによる介入なしに即座に遮断する必要がある場合などに使用されます。

PMG1-S3 は最大 8 個の TCPWM を持っています。これらは、ファームウェアによって内部タイマーとして使用、または GPIO 上で PWM ベースの機能の実装に使用できます。

#### 2.6.2 SCB

PMG1-S3 には、I<sup>2</sup>C, SPI, または UART に設定できる 8 個の SCB ブロックがあります。これらのブロックは、マルチマスター アービトレイションが可能なフルマルチマスターおよびスレーブの I<sup>2</sup>C インターフェースを実装します。I<sup>2</sup>C は、Philips 社の標準 I<sup>2</sup>C 仕様 V3.0 に準拠しています。これらのブロックは最大 1Mbps で動作し、CPU 用の割込みオーバヘッドとレイテンシを削減するためにバッファリング オプションを柔軟に選択できます。

さらに、SCB ブロックは受信 (RX) および送信 (TX) 用の深さ 8 の FIFO にも対応しています。これは、CPU がデータを読み出す時間を増加させて、CPU が時間どおりにデータを読み出せないことに起因したクロックストレッチの必要性を大幅に低減します。FIFO モードは、DMA がない場合に非常に有用です。データ スループットは、I<sup>2</sup>C にとって重要な考慮事項ではありません。SCB0 の I<sup>2</sup>C ポートのみがフェイルセーフです。SCB1 ~ 7 の I<sup>2</sup>C ポートはフェイルセーフではありません。これらの GPIO の論理レベルが高いと MCU に逆流電力が供給される可能性があるためです。

UART モード：最大 1Mbps で動作するフル機能の UART です。また、共通の RX と TX ラインを介して接続したペリフェラルのアドレス指定を可能にする 9 ビットマルチプロセッサ モードに対応しています。パリティ エラー、ブレーク検出、フレーム エラーなどの一般的な UART 機能に対応しています。

SPI モード：SPI モードは Motorola SPI、TI SSP (SPI コデックの同期化用の開始パルスを本質的に追加)、National Microwire (半二重の SPI) に完全に対応しています。SPI ブロックは FIFO も使用できます。

#### 2.6.3 GPIO インターフェース

PMG1-S3 には、GPIO として使用可能な SCB および SWD ピンを含む最大 50 個の GPIO があります。

GPIO ブロックは以下を実装します。

- 8 つの駆動強度モード：ストロング プッシュ プル、抵抗 プルアップと プルダウン、弱 (抵抗) プルアップと プルダウン、オープン ドレインと オープン ソース、入力、およびディスエーブル モード

- 入力 閾値選択 (CMOS または LVTTL)

- 入力と出力のディスエーブルの個別制御

- 前の状態をラッチするための保持モード (ディープスリープ モードで I/O 状態を維持するため)

- dV/dt 関連のノイズ制御用の選択可能なスルーレート

ピンは、8 ビット幅のポートと呼ばれる論理エンティティに構成されています。電源投入とリセットの間、入力に過電流を与える、過剰なターンオン電流を発生させないために、ブロックは無効状態にされます。高速 I/O マトリックスとして知られている多重化ネットワークは、1 本の I/O ピンに接続され得る複数の信号間を多重化するために使用されます。固定機能ペリフェラルのピン位置は、内部多重化の複雑さを減少させるために固定されています。データ出力レジスタとピンステート レジスタそれぞれはピン上で駆動される値とピンの状態を格納します。ピンのコンフィギュレーションは各デジタル I/O ポート用のソフトウェアを介してレジスタをプログラミングすることによって行うことができます。

各 I/O ピンは有効になった場合にエッジトリガーの割込みを生成できます。各 I/O ポートには、割込み要求 (IRQ) とそれに対応する割込みサービス ルーチン (ISR) のベクタがあります。

## 機能概要

I/O ポートはディープスリープモード中にその状態を保持するかオンのままになります。リセットにより動作が復元される場合、ピンは High-Z 状態になります。割込みイベントによって動作が復元されると、ファームウェアがそれを変更するまで、ピンドライバはその状態を保持します。I/O (データバス上) は、電源切断時に電流を引き出しません。

### GPIO パワードメイン

すべての GPIO は、VDDIO と呼ばれる個別の I/O パワードメインに存在します (SBU GPIO を除く)。独立した I/O 電源ドメインは、柔軟なシステムレベルのインターフェースを実現します。SBU (コネクタ側) に接続された GPIO は、VDDIO ドメインではなく、VDDD ドメインにあります。

Table 50 に、48-QFN および 97-BGA の VDDIO および VDDD ドメインにある GPIO の数を示します。97-BGA では、VDDIO での 38 個の GPIO のうち、合計 26 個の GPIO (ポート 1 (LP-Comp 入力のみ)、ポート 2、3、および 5) が、CTBm、12 ビット SAR ADC、CAPSENSE™ 入力および LPCOMP などの特殊なアナログペリフェラルブロックによって使用されます。これらの GPIO については、次のことを確認してください。

1. I/O に外部から印加される、または内部でルーティングされる電圧は、VDDIO 電源電圧を超えてはいけません ( $VDDIO \leq VDDA$  のため)。

2. 起動時に、すべての電源 (VDDIO、VDDD、および VDDA) が投入された後でのみ、I/O に外部電圧を印加できます。

- 97-BGA のすべての 50 個の GPIO については、AMUXBUSA および AMUXUSB ライン上の電圧は VDDA 電源を超えることはできません。

### 2.6.3.1 フェイルセーフ GPIO

EZ-PD™ PMG1-S3 には、フェイルセーフ GPIO ピンが 2 つあります。これらは P4.0 と P4.1 で、SCB0 の I<sup>2</sup>C ピンです。

フェイルセーフ機能により、VBUS/VSYS 電源が供給されていない場合でも、I<sup>2</sup>C ラインの動作によってこれらのピンがロジックハイレベルになっても、MCU に逆流電力が供給されることはありません。

## 2.7 特殊機能ペリフェラル

### 2.7.1 CAPSENSE™

CAPSENSE™ は、どの GPIO ピンも接続できるアナログマルチプレクサバスを介してどのピンにも接続できる CAPSENSE™ シグマデルタ (CSD) ブロックにより、PMG1-S3 の 16 個のピンでサポートされています。したがって、CAPSENSE™ 機能はソフトウェアで制御されるシステム内のいかなるピンあるいはピングループに提供できます。

各 CAPSENSE™ ブロックには、CAPSENSE™ を使用しない場合に一般的な目的に使用できる 2 個の IDAC があります。2 個の AMUX バスを持つことにより、CAPSENSE™ は片方の IDAC (防水なし) を使用し、他方の IDAC を汎用に使用できます。

耐水性のためのシールド駆動は、検知中に寄生容量を同じ充電レベルに維持するようにシールドを駆動するために 2 番目の IDAC により実装されます。CAPSENSE™ ブロックは、自己容量センシングと相互容量センシングの両方を提供します。

## 電源システムの概要

## 3. 電源システムの概要

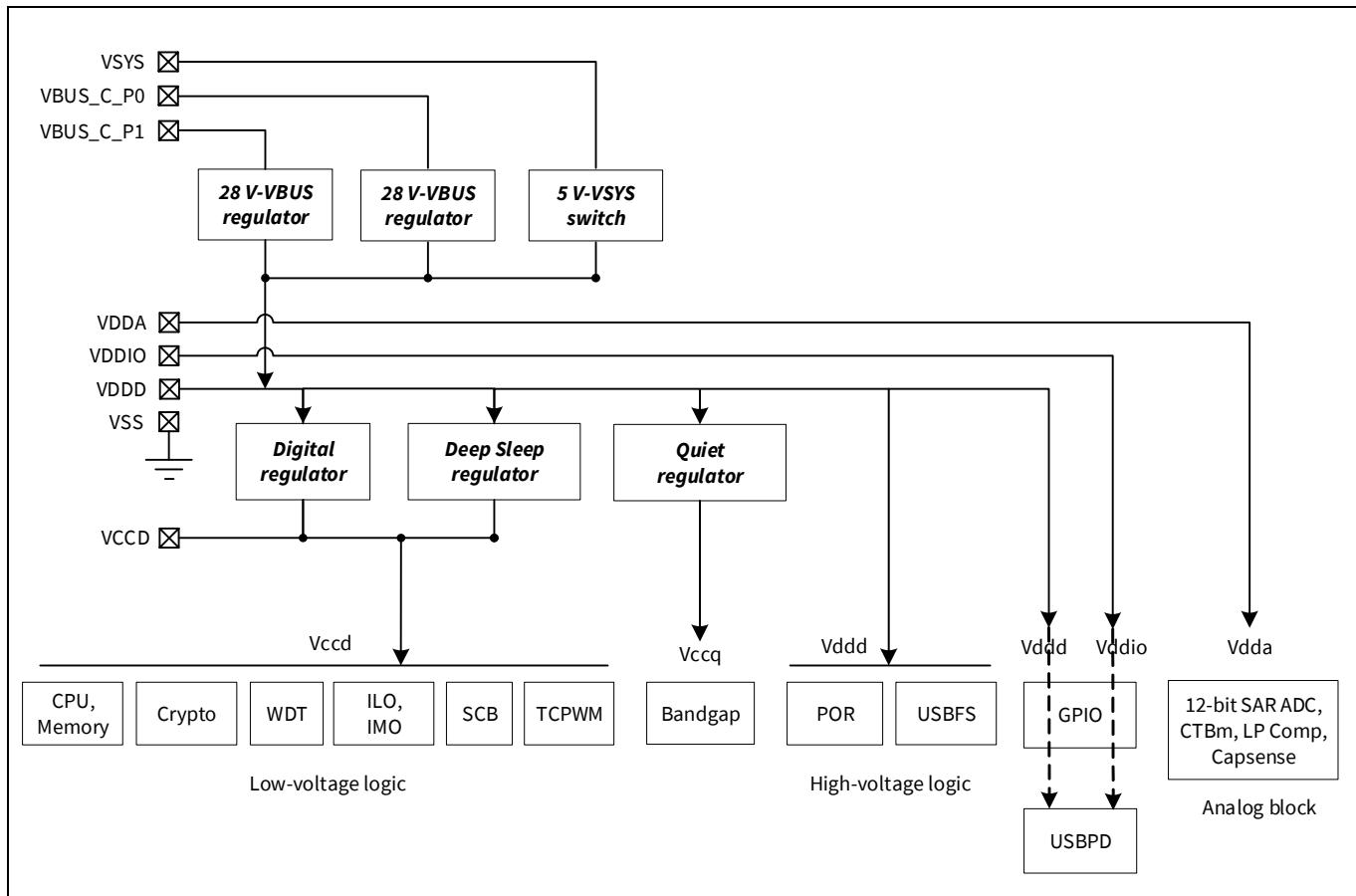

Figure 6 に、PMG1-S3 の電源ピンの一般的な要件を示します。Vccd は低電圧ロジックブロックに、Vddd は高電圧ロジックブロックに電源を供給します。アナログブロックは Vdda を使用して別途電源供給されます。Vccq は、バンドギャップリファレンスブロックに電源を供給する低消費電力レギュレータの出力です。Vddio はほとんどの GPIO の電源です。ただし、Vddd から電源供給されている GPIO はごくわずかです。PMG1-S3 の電源スキームにより、さまざまな VDDD および VDDA の接続が可能になります。シーケンスの要件はありません。Figure 6 は、VDDD と VDDA が別々のネットであり、チップ上でオーミック接続されていないことを示します。さまざまなパッケージ要件に応じて、これらはボンディング配置で互いに接続されるか、チップ外部で接続される必要があります。

Figure 6. PMG1-S3 電源システムのブロック図

## 4. ピン配置

Table 2. PMG1-S3 CYPM1322-97BZXI および CYPM1311-48LDXI のピン一覧

| グループ | 97-BGA | 48-QFN | ピン名  | 代替機能 (HSIOM_PORT_SEL)     |             |                      |                             |               |               |                              |              | ピン説明                                                              |

|------|--------|--------|------|---------------------------|-------------|----------------------|-----------------------------|---------------|---------------|------------------------------|--------------|-------------------------------------------------------------------|

|      |        |        |      | アナログ                      | ACT#0       | ACT#1                | ACT#2                       | ACT#3         | DS#0          | DS#2                         | DS#3         |                                                                   |

| GPIO | H2     | P1.0   | P1.0 | -                         | -           | -                    | -                           | -             | -             | -                            | -            | GPIO、CSD                                                          |

|      |        |        | P1.1 | lpcomp1_inp               | -           | -                    | scb3_uart_rx                | -             | swd_clk       | scb3_spi_clk                 | scb3_i2c_scl | GPIO、COMP1、SCB3、CSD、シリアル<br>ワイヤデバッグクロック                           |

|      |        |        | P1.2 | lpcomp1_inn               | -           | -                    | scb3_uart_tx                | -             | swd_data      | scb3_spi_miso                | scb3_i2c_sda | GPIO、COMP1、SCB3、CSD、シリアル<br>ワイヤデバッグデータ                            |

|      |        |        | P1.3 | -                         | tcpwm4_line | tcpwm4_compara_match | scb3_uart_cts               | tcpwmx_tr_in4 | -             | scb3_spi_mosi                | -            | GPIO、SCB3、TCPWM4 出力、CSD、<br>Thunderbolt 割込み PD ポート 0、<br>TCPWM 入力 |

|      |        |        | P1.4 | -                         | tcpwm5_line | tcpwm5_compara_match | scb3_uart_rts               | tcpwmx_tr_in5 | -             | scb3_spi_select              | -            | GPIO、SCB3、TCPWM5 出力、CSD、<br>ホットプラグ検出 PD ポート 0、<br>TCPWM 入力        |

|      |        |        | P1.5 | lpcomp0_inn               | -           | -                    | scb1_uart_tx <sup>[1]</sup> | -             | -             | scb1_spi_miso <sup>[1]</sup> | scb1_i2c_sda | GPIO、COMP0、SCB1、CSD                                               |

|      |        |        | P1.6 | lpcomp0_inp               | ext_clk0    | -                    | -                           | -             | -             | scb1_spi_clk <sup>[1]</sup>  | scb1_i2c_scl | GPIO、COMP0、SCB1、CSD、外部クロック入力                                      |

|      |        |        | P2.0 | sarmux_0                  | -           | -                    | scb5_uart_rts               | -             | -             | scb5_spi_select              | -            | GPIO、SAR 入力、SCB5、CSD                                              |

|      |        |        | P2.1 | sarmux_1                  | tcpwm2_line | tcpwm2_compara_match | scb0_uart_rts               | tcpwmx_tr_in2 | -             | scb0_spi_select              | -            | GPIO、SAR 入力、TCPWM2 出力、<br>SCB0、CSD、TCPWM 入力                       |

|      |        |        | P2.2 | sarmux_2                  | -           | -                    | scb5_uart_tx <sup>[1]</sup> | -             | -             | scb5_spi_miso <sup>[1]</sup> | scb5_i2c_sda | GPIO、SAR 入力、SCB5、CSD                                              |

|      |        |        | P2.3 | sarmux_3                  | -           | -                    | scb5_uart_rx <sup>[1]</sup> | -             | -             | scb5_spi_clk <sup>[1]</sup>  | scb5_i2c_scl | GPIO、SAR 入力、SCB5、CSD                                              |

|      |        |        | P2.4 | sarmux_4                  | tcpwm3_line | tcpwm3_compara_match | scb0_uart_cts               | tcpwmx_tr_in3 | -             | scb0_spi_miso                | -            | GPIO、SAR 入力、TCPWM3、SCB0、<br>CSD                                   |

|      |        |        | P2.5 | sarmux_5                  | -           | -                    | scb5_uart_cts               | -             | -             | scb5_spi_mosi                | -            | GPIO、SAR 入力、SCB5、CSD                                              |

|      |        |        | P2.6 | sarmux_6                  | -           | -                    | scb1_uart_rts               | -             | -             | scb1_spi_mosi                | -            | GPIO、SAR 入力、SCB1、CSD                                              |

|      |        |        | P2.7 | sarmux_7                  | -           | -                    | scb1_uart_cts               | -             | -             | scb1_spi_select              | -            | GPIO、SAR 入力、SCB1、CSD                                              |

|      |        |        | P3.0 | sar_ext_vref<br>ctb1_oa1+ | tcpwm6_line | tcpwm6_compara_match | scb4_uart_cts               | tcpwmx_tr_in6 | -             | scb4_spi_mosi                | -            | GPIO、CTBm、TCPWM6 出力、SCB4、<br>CSD、TCPWM 入力                         |

|      |        |        | P3.1 | ctb0_oa0+                 | -           | -                    | -                           | -             | -             | -                            | -            | GPIO、CTBm、CSD                                                     |

|      |        |        | P3.2 | ctb1_oa1+                 | -           | -                    | -                           | -             | -             | -                            | -            | GPIO、CTBm、CSD                                                     |

|      |        |        | P3.3 | ctb0_oa1-                 | tcpwm7_line | tcpwm7_compara_match | scb4_uart_rts               | tcpwmx_tr_in7 | -             | scb4_spi_select              | -            | GPIO、CTBm、TCPWM7 出力、SCB4、<br>CSD、TCPWM 入力                         |

|      |        |        | P3.4 | ctb0_oa1_out_1_0x         | -           | -                    | -                           | -             | -             | -                            | -            | CTBm、GPIO、CSD                                                     |

|      |        |        | P3.5 | ctb0_oa0_out_1_0x         | -           | -                    | scb4_uart_rx                | -             | -             | scb4_spi_clk                 | scb4_i2c_scl | GPIO、CTBm、SCB4、CSD                                                |

|      |        |        | P3.6 | ctb0_oa0-                 | -           | -                    | scb4_uart_tx                | -             | -             | scb4_spi_miso                | scb4_i2c_sda | GPIO、CTBm、SCB4、CSD                                                |

|      |        |        | P3.7 | ctb0_oa0+                 | -           | -                    | -                           | -             | -             | -                            | -            | GPIO、CTBm、CSD                                                     |

|      |        |        | P4.0 | -                         | -           | -                    | scb0_uart_rx                | -             | swd_clk(alt)  | scb0_spi_clk                 | scb0_i2c_scl | GPIO、SCB0、CSD                                                     |

|      |        |        | P4.1 | -                         | -           | -                    | scb0_uart_tx                | -             | swd_data(alt) | scb0_spi_mosi                | scb0_i2c_sda | GPIO、SCB0、CSD                                                     |

注：

- 48-QFN パッケージでは利用不可。

- I/O ロジックは VDDIO の代わりに VDDD に接続されます。

Table 2. PMG1-S3 CYPM1322-97BZXI および CYPM1311-48LDXI のピン一覧 ( 続き )

| グループ | 97-BGA | 48-QFN | ピン名  | 代替機能 (HSIOM_PORT_SEL) |       |       |               |       |      |                 |              | ピン説明                                   |

|------|--------|--------|------|-----------------------|-------|-------|---------------|-------|------|-----------------|--------------|----------------------------------------|

|      |        |        |      | アナログ                  | ACT#0 | ACT#1 | ACT#2         | ACT#3 | DS#0 | DS#2            | DS#3         |                                        |

| GPIO | G2     | 7      | P5.0 | csd_csh_tank          | -     | -     | scb2_uart_rx  | -     | -    | scb2_spi_clk    | scb2_i2c_scl | GPIO、SCB2、CSD                          |

|      | E1     | 8      | P5.1 | csd_c_mod             | -     | -     | scb2_uart_tx  | -     | -    | scb2_spi_mosi   | scb2_i2c_sda | GPIO、SCB2、CSD                          |

|      | H6     | 9      | P5.2 | csd_c_shield          | -     | -     | scb2_uart_cts | -     | -    | scb2_spi_miso   | lpcomp1_comp | GPIO、CSD                               |

|      | H1     | 10     | P5.3 | csd_vref_ext          | -     | -     | scb2_uart_rts | -     | -    | scb2_spi_select | lpcomp0_comp | GPIO、SCB2、CSD                          |

|      | G1     |        | P5.4 | -                     | -     | -     | -             | -     | -    | -               | -            | GPIO、CSD                               |

|      | H4     | 11     | P5.5 | -                     | -     | -     | -             | -     | -    | -               | -            | GPIO、CSD、組込みコントローラー割込み                 |

|      | G15    |        | P7.0 | -                     | -     | -     | scb1_uart_rx  | -     | -    | -               | -            | GPIO、SCB1、Thunderbolt 割込み PD ポート 1、CSD |

|      | G14    |        | P7.1 | -                     | -     | -     | -             | -     | -    | -               | -            | CSD、ホット プラグ検出 PD ポート 1                 |

|      | A14    |        | P7.2 | -                     | -     | -     | -             | -     | -    | -               | -            | GPIO、CSD                               |

|      | B13    |        | P7.3 | -                     | -     | -     | scb7_uart_tx  | -     | -    | scb7_spi_miso   | scb7_i2c_sda | GPIO、SCB7、CSD                          |

|      | B11    |        | P7.4 | -                     | -     | -     | scb7_uart_rx  | -     | -    | scb7_spi_clk    | scb7_i2c_scl | GPIO、SCB7、CSD                          |

|      | A9     |        | P7.5 | -                     | -     | -     | scb7_uart_cts | -     | -    | scb7_spi_mosi   | -            | GPIO、SCB7、CSD                          |

|      | B9     |        | P7.6 | -                     | -     | -     | scb7_uart_rts | -     | -    | scb7_spi_select | -            | GPIO、SCB7、CSD                          |

注:

1. 48-QFN パッケージでは利用不可。

2. I/O ロジックは VDDIO の代わりに VDDD に接続されます。

Table 2. PMG1-S3 CYPM1322-97BZXI および CYPM1311-48LDXI のピン一覧 ( 続き )

| グループ           | 97-BGA | 48-QFN | ピン名                         | 代替機能 (HSIOM_PORT_SEL) |             |                      |               |              |                                |                 |              | ピン説明                                                                                    |

|----------------|--------|--------|-----------------------------|-----------------------|-------------|----------------------|---------------|--------------|--------------------------------|-----------------|--------------|-----------------------------------------------------------------------------------------|

|                |        |        |                             | アナログ                  | ACT#0       | ACT#1                | ACT#2         | ACT#3        | DS#0                           | DS#2            | DS#3         |                                                                                         |

| マルチブレクサ / スイッチ | R8     | 17     | P0.0/LSRX_P1 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd1_sbu_lsrx <sup>[1]</sup> | -               | -            | CSD、GPIO、LSRX ポート 1                                                                     |

|                | R7     |        | P0.1/LSTX_P1 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd1_sbu_lstx                | -               | -            | CSD、GPIO、LSTX ポート 1                                                                     |

|                | P7     |        | P0.2/DBG1_P1 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd1_sbu_dbg1                | -               | -            | CSD、GPIO、SBU-LSTX デバッグ 1 ピン ポート 1                                                       |

|                | K6     |        | P0.3/DBG2_P1 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd1_sbu_dbg2                | -               | -            | CSD、GPIO、SBU-LSTX デバッグ 2 ピン ポート 1                                                       |

|                | P8     |        | P0.4/DBG2_P0 <sup>[2]</sup> | -                     | tcpwm1_line | tcpwm1_compare_match | -             | tcpwm1_tr_in | usbpd0_sbu_dbg2                | -               | -            | CSD、GPIO、TCPWM1 出力、SBU-LSTX デバッグ 2 ピン ポート 0、TCPWM 入力                                    |

|                | M8     |        | P0.5/DBG1_P0 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd0_sbu_dbg1                | -               | -            | CSD、GPIO、SBU-LSTX デバッグ 1 ピン ポート 0                                                       |

|                | R9     |        | P0.6/LSTX_P0 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd0_sbu_lstx                | -               | -            | CSD、GPIO、LSTX ポート 0                                                                     |

|                | R11    |        | P0.7/LSRX_P0 <sup>[2]</sup> | -                     | -           | -                    | -             | -            | usbpd0_sbu_lsrx                | -               | -            | CSD、GPIO、LSRX ポート 0                                                                     |

|                | R5     | 15     | P6.0/SBU1_P1 <sup>[2]</sup> | -                     | ext_clk1    | -                    | scb6_uart_tx  | -            | usbpd1_sbu_io1                 | scb6_spi_miso   | scb6_i2c_sda | CSD、GPIO、DisplayPort 用の Type-C 補助信号 - コネクタ側 : ポート 1、SCB6、外部クロック入力 (Type-C コネクタの液体検知用ピン) |

|                | P5     | 16     | P6.1/SBU2_P1 <sup>[2]</sup> | -                     | -           | -                    | scb6_uart_rx  | -            | usbpd1_sbu_io2                 | scb6_spi_clk    | scb6_i2c_scl | CSD、GPIO、DisplayPort 用の Type-C 補助信号 - コネクタ側 : ポート 1、SCB6 (Type-C コネクタの液体検知用ピン)          |

|                | P13    | 18     | P6.2/SBU2_P0 <sup>[2]</sup> | -                     | tcpwm0_line | tcpwm0_compare_match | scb6_uart_rts | tcpwm0_tr_in | usbpd0_sbu_io2                 | scb6_spi_select | -            | CSD、GPIO、DisplayPort 用の Type-C 補助信号 - コネクタ側 : ポート 0、SCB6 (Type-C コネクタの液体検知用ピン)          |

|                | R13    | 19     | P6.3/SBU1_P0 <sup>[2]</sup> | -                     | -           | -                    | scb6_uart_cts | -            | usbpd0_sbu_io1                 | scb6_spi_mosi   | -            | CSD、GPIO、DisplayPort 用の Type-C 補助信号 - コネクタ側 : ポート 0、SCB6 (Type-C コネクタの液体検知用ピン)          |

|                | M4     |        | AUX_P_P1                    | -                     | -           | -                    | -             | -            | -                              | -               | -            | DisplayPort 用の Type-C 補助信号 - システム側 : ポート 1                                              |

|                | M6     |        | AUX_N_P1                    | -                     | -           | -                    | -             | -            | -                              | -               | -            | DisplayPort 用の Type-C 補助信号 - システム側 : ポート 1                                              |

|                | P11    |        | AUX_P_P0                    | -                     | -           | -                    | -             | -            | -                              | -               | -            | DisplayPort 用の Type-C 補助信号 - システム側 : ポート 0                                              |

|                | P9     |        | AUX_N_P0                    | -                     | -           | -                    | -             | -            | -                              | -               | -            | DisplayPort 用の Type-C 補助信号 - システム側 : ポート 0                                              |

| USB FS         | A11    | 40     | USBDM                       | -                     | -           | -                    | -             | -            | -                              | -               | -            | USB 2.0 (FS-PHY) DM (Type-C コネクタの液体検知用ピン)                                               |

|                | A13    | 39     | USBDP                       | -                     | -           | -                    | -             | -            | -                              | -               | -            | USB 2.0 (FS-PHY) DP (Type-C コネクタの液体検知用ピン)                                               |

注 :

1. 48-QFN パッケージでは利用不可。

2. I/O ロジックは VDDIO の代わりに VDDD に接続されます。

Table 2. PMG1-S3 CYPM1322-97BZXI および CYPM1311-48LDXI のピン一覧 ( 続き )

| グループ                     | 97-BGA | 48-QFN | ピン名                  | 代替機能 (HSIOM_PORT_SEL) |       |       |       |       |      |      |      | ピン説明                                                          |

|--------------------------|--------|--------|----------------------|-----------------------|-------|-------|-------|-------|------|------|------|---------------------------------------------------------------|

|                          |        |        |                      | アナログ                  | ACT#0 | ACT#1 | ACT#2 | ACT#3 | DS#0 | DS#2 | DS#3 |                                                               |

| VBUS_OCP/<br>SCP/<br>RCP | A15    | 37     | CSN_P0               | -                     | -     | -     | -     | -     | -    | -    | -    | VBUS 側の外付け Rsense 用の電流検出<br>負入力 : ポート 0                       |

|                          | B15    | 38     | CSP_P0               | -                     | -     | -     | -     | -     | -    | -    | -    | VBUS 側の外付け Rsense 用の電流検出<br>正入力 : ポート 0                       |

|                          |        |        | CSN_P1               | -                     | -     | -     | -     | -     | -    | -    | -    | VBUS 側の外付け Rsense 用の電流検出<br>負入力 : ポート 1                       |

|                          |        |        | CSP_P1               | -                     | -     | -     | -     | -     | -    | -    | -    | VBUS 側の外付け Rsense 用の電流検出<br>正入力 : ポート 1                       |

| USB PD<br>Type-C         | N14    | 28     | CC1_P0               | -                     | -     | -     | -     | -     | -    | -    | -    | USB PD ポート 0 コネクタ検出 / コン<br>フィギュレーションチャネル 1                   |

|                          | N15    |        |                      |                       |       |       |       |       |      |      |      |                                                               |

|                          | N1     |        | CC1_P1               | -                     | -     | -     | -     | -     | -    | -    | -    | USB PD ポート 1 コネクタ検出 / コン<br>フィギュレーションチャネル 1                   |

|                          | N2     |        |                      |                       |       |       |       |       |      |      |      |                                                               |

|                          | J14    | 30     | CC2_P0               | -                     | -     | -     | -     | -     | -    | -    | -    | USB PD ポート 0 コネクタ検出 / コン<br>フィギュレーションチャネル 2                   |

|                          | J15    |        |                      |                       |       |       |       |       |      |      |      |                                                               |

|                          | J1     |        | CC2_P1               | -                     | -     | -     | -     | -     | -    | -    | -    | USB PD ポート 1 コネクタ検出 / コン<br>フィギュレーションチャネル 2                   |

|                          | J2     |        |                      |                       |       |       |       |       |      |      |      |                                                               |

| VBUS_NG<br>DO            | R14    | 24     | VBUS_IN_NGDO<br>_P0  | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 入力 - パス 0 (4V ~<br>30V)                          |

|                          | R2     |        | VBUS_IN_NGDO<br>_P1  | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 入力 - パス 1 (4V ~<br>30V)                          |

|                          | R15    | 25     | VBUS_OUT_NGD<br>O_P0 | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 出力 - パス 0 (4V ~<br>30V)                          |

|                          | R1     |        | VBUS_OUT_NGD<br>O_P1 | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 出力 - パス 1 (4V ~<br>30V)                          |

|                          | P14    | 27     | VBUS_IN_CTRL<br>_P0  | -                     | -     | -     | -     | -     | -    | -    | -    | USB Type-C ポート 0 の NFET ( 入力側 )<br>の有効化 / 無効化用のフルレール制御<br>I/O |

|                          | P2     |        | VBUS_IN_CTRL<br>_P1  | -                     | -     | -     | -     | -     | -    | -    | -    | USB Type-C ポート 1 の NFET ( 入力側 )<br>の有効化 / 無効化用のフルレール制御<br>I/O |

|                          | P15    | 26     | VBUS_OUT_CTR<br>L_P0 | -                     | -     | -     | -     | -     | -    | -    | -    | USB Type-C ポート 0 の NFET ( 出力側 )<br>の有効化 / 無効化用のフルレール制御<br>I/O |

|                          | P1     |        | VBUS_OUT_CTR<br>L_P1 | -                     | -     | -     | -     | -     | -    | -    | -    | USB Type-C ポート 1 の NFET ( 出力側 )<br>の有効化 / 無効化用のフルレール制御<br>I/O |

| リセット                     | E14    | 33     | XRES                 | -                     | -     | -     | -     | -     | -    | -    | -    | リセット入力                                                        |

注 :

1. 48-QFN パッケージでは利用不可。

2. I/O ロジックは VDDIO の代わりに VDDD に接続されます。

Table 2. PMG1-S3 CYPM1322-97BZXI および CYPM1311-48LDXI のピン一覧 ( 続き )

| グループ | 97-BGA | 48-QFN | ピン名             | 代替機能 (HSIOM_PORT_SEL) |       |       |       |       |      |      |      | ピン説明                                                                              |

|------|--------|--------|-----------------|-----------------------|-------|-------|-------|-------|------|------|------|-----------------------------------------------------------------------------------|

|      |        |        |                 | アナログ                  | ACT#0 | ACT#1 | ACT#2 | ACT#3 | DS#0 | DS#2 | DS#3 |                                                                                   |

| 電源   | B14    | 36     | VSYS            | -                     | -     | -     | -     | -     | -    | -    | -    | システム用の 2.8V ~ 5.5V 電源                                                             |

|      | D8     | 43     | VDDD            | -                     | -     | -     | -     | -     | -    | -    | -    | VDDD 電源出力<br>1.VSYS 電源 - (Min: VSYS-100mV) 2.7V ~ 5.5V<br>2.VBUS 電源 - 2.7V ~ 3.6V |

|      | D6     | 5      | VDDA            | -                     | -     | -     | -     | -     | -    | -    | -    | ボードレベルで VDDD に短絡されるブローバル アナログ電源 (2.7V ~ 5.5V)                                     |

|      | F6     |        |                 | -                     | -     | -     | -     | -     | -    | -    | -    | GPIO 電源 (1.71V ~ 5.5V)                                                            |

|      | B8     | 23     | VDDIO           | -                     | -     | -     | -     | -     | -    | -    | -    | GPIO 電源 (1.71V ~ 5.5V)                                                            |

|      | H12    | 42     |                 | -                     | -     | -     | -     | -     | -    | -    | -    | フィルター コンデンサ用の 1.8V レギュレータ出力。このピンは外部負荷を駆動不可                                        |

|      | D10    | 41     | VCCD            | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 入力 - ポート 0 (4V ~ 30V)                                                |

|      | H15    | 31     | VBUS_C_P0       | -                     | -     | -     | -     | -     | -    | -    | -    | NGDO 用の VBUS 入力 - ポート 1 (4V ~ 30V)                                                |

|      | H14    |        | VBUS_C_P1       | -                     | -     | -     | -     | -     | -    | -    | -    | Type-C の VCONN FET 用の 4.85V ~ 5.5V 電源 : ポート 0                                     |

|      | L14    | 29     | VCONN_Source_P0 | -                     | -     | -     | -     | -     | -    | -    | -    | Type-C の VCONN FET 用の 4.85V ~ 5.5V 電源 : ポート 1                                     |

|      | L15    |        |                 | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | L1     |        | VCONN_Source_P1 | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | L2     |        |                 | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

| グランド | F10    | 6      | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | F12    | 32     | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | F8     | 44     | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | H10    |        | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | H8     |        | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | K10    |        | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

|      | K8     |        | VSS             | -                     | -     | -     | -     | -     | -    | -    | -    | グランド                                                                              |

注:

- 48-QFN パッケージでは利用不可。

- I/O ロジックは VDDIO の代わりに VDDD に接続されます。

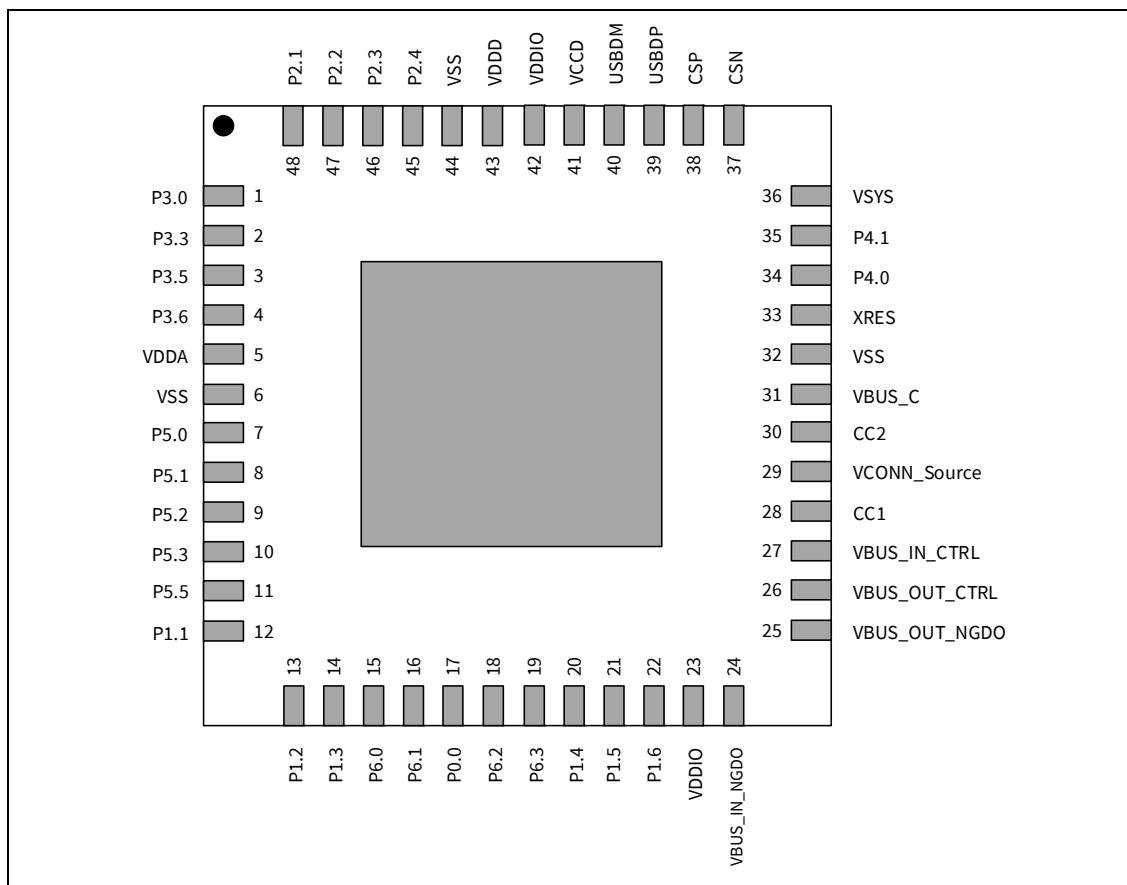

## ピン配置

Figure 7. CYPM1311-48LDXI: シングルポート 48 ピン QFN

## ピン配置

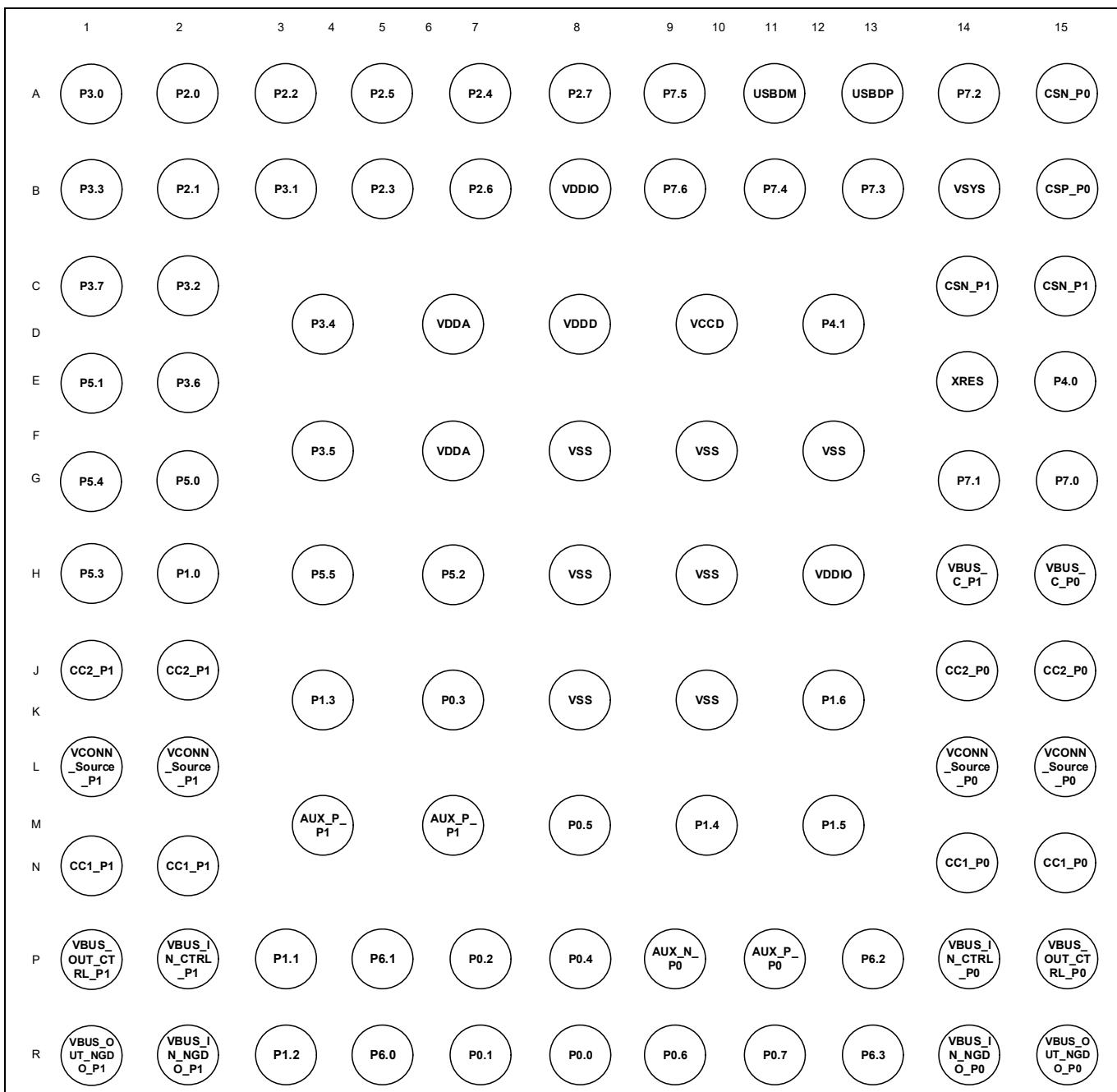

Figure 8. CYPM132x-97BZXI: デュアルポート 97 ボール BGA

## アプリケーション図

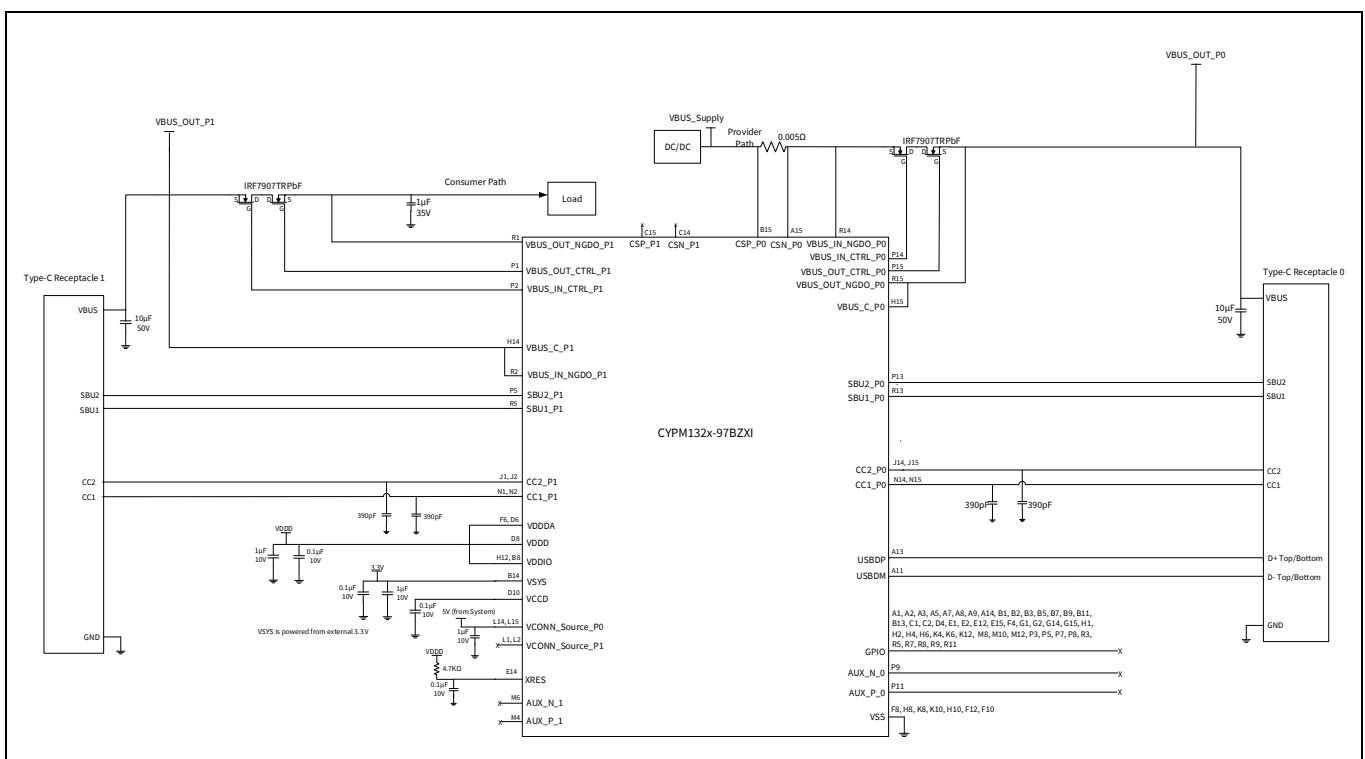

## 5. アプリケーション図

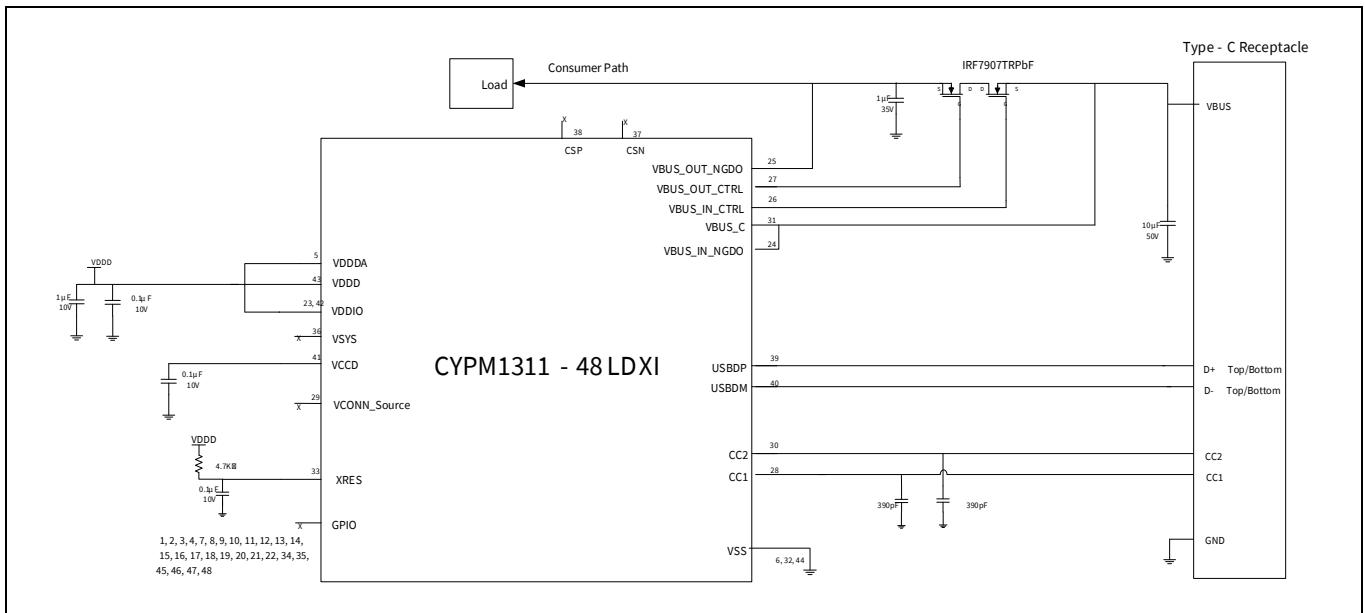

Figure 9 に、より高い電圧を得て、システム内で MCU として機能するために、接続された充電器と PD コントラクトをネゴシエートする単一ポートの電力コンシューマの役割を果たしている PMG1-S3 を示します。必要な Type-C ポートは 1 つだけなので、このデバイス アプリケーションには PMG1-S3 48 ピン QFN を使用できます。

Figure 9. 48 ピン QFN PMG1-S3 を使用したパワーシンク アプリケーション

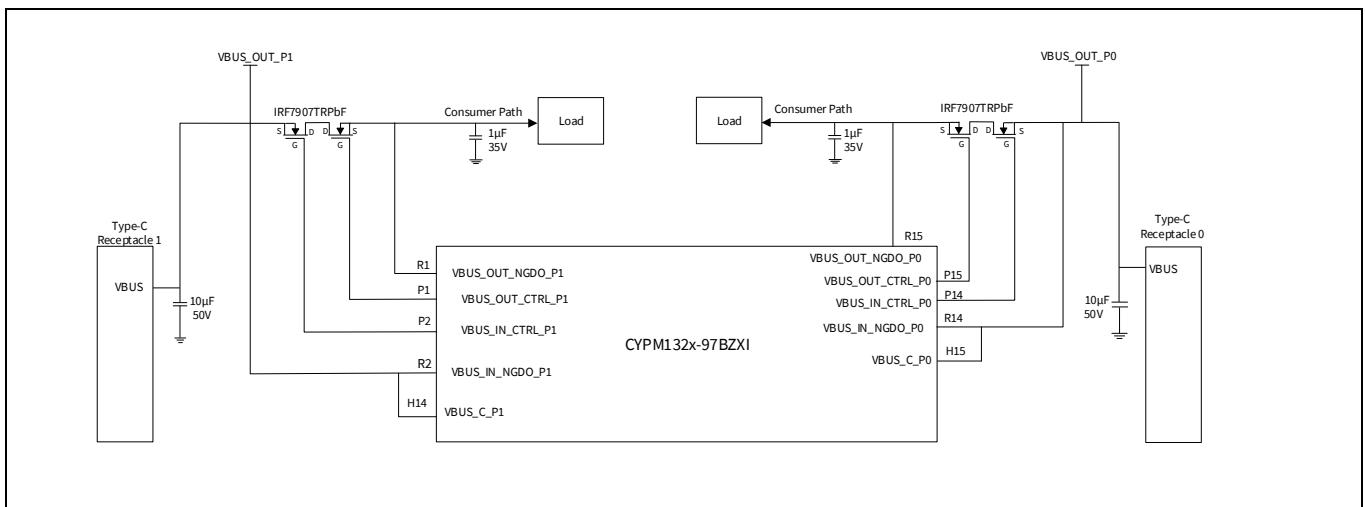

Figure 10 に、両方の Type-C ポートで電力コンシューマとして機能する 97 ボール BGA PMG1-S3 を使用するアプリケーションを示します。

Figure 10. 97 ボール BGA を使用した両方の Type-C ポートのシンク設定

## アプリケーション図

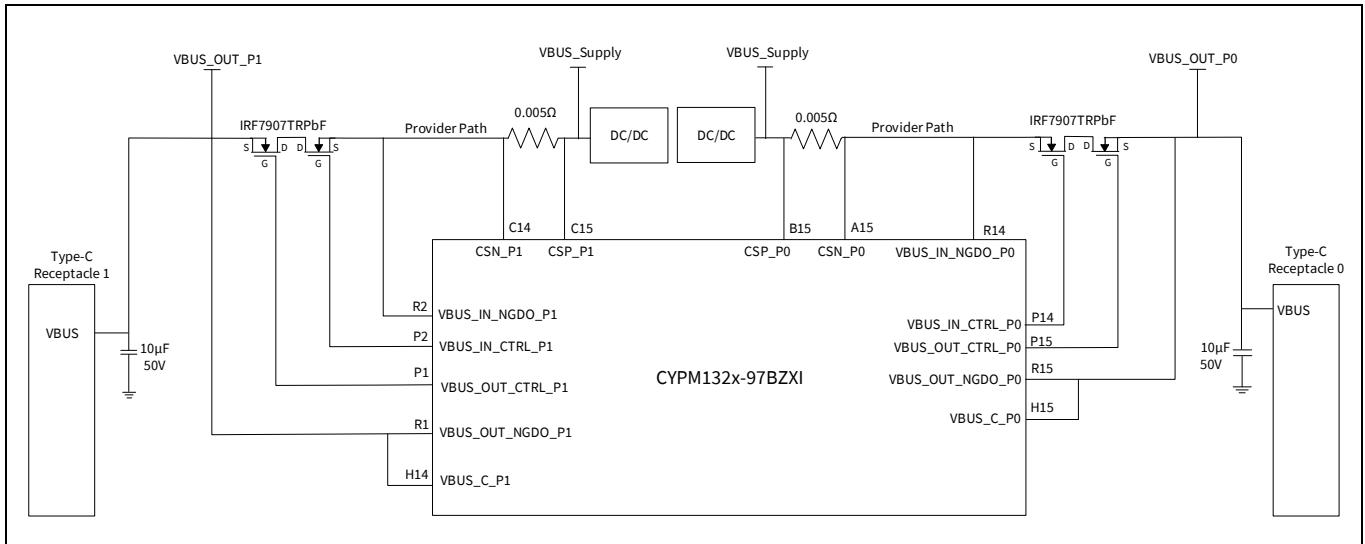

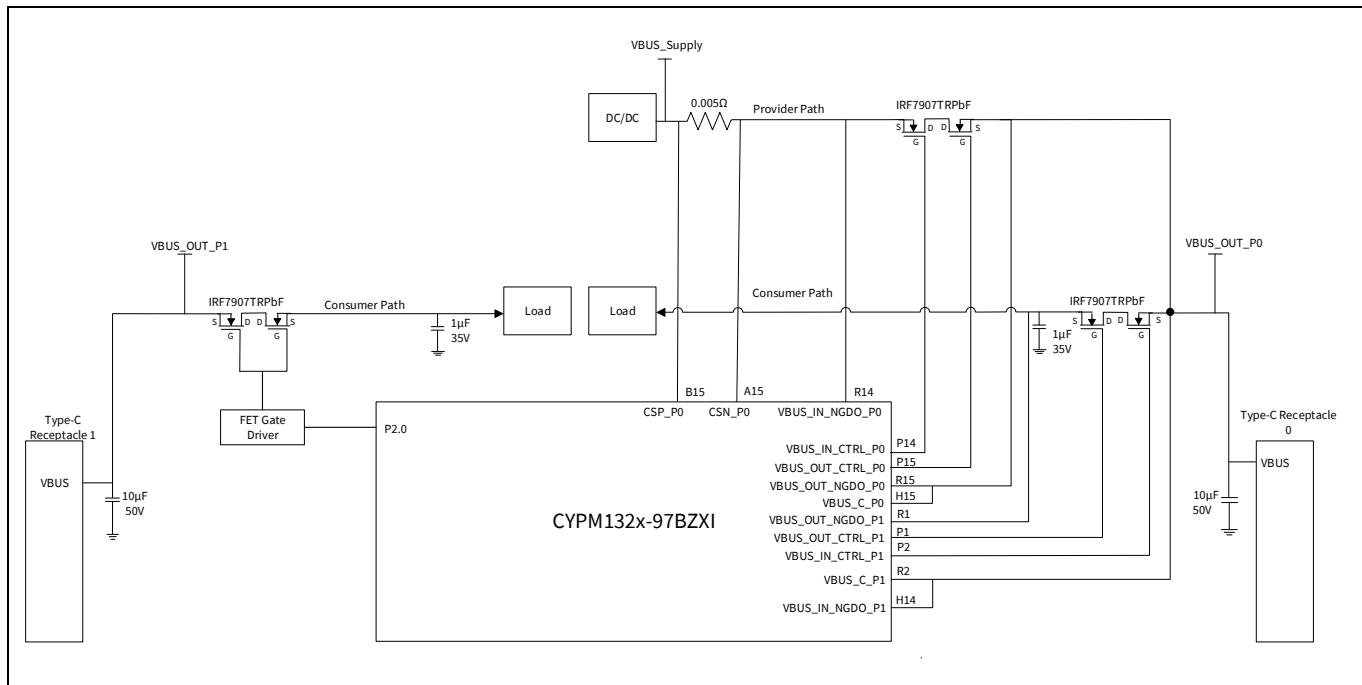

Figure 11 に、両方の Type-C ポートで電力プロバイダとして機能する 97 ボールボール BGA PMG1-S3 を使用するアプリケーションを示します。

Figure 11. 97 ボール BGA を使用した両方の Type-C ポートのソース設定

Figure 12 に、97 ボール BGA PMG1-S3 を使用するアプリケーションを示します。ここでは、一方の Type-C ポートでは電力プロバイダとして機能し、もう一方の Type-C ポートでは電力コンシューマとして機能します。

Figure 12. 97ボール BGA PMG1-S3を使用した電力プロバイダおよびコンシューマアプリケーション

## アプリケーション図

Figure 13 では、ポート 0 が Type-C ポートの一方で DRP として設定され、もう一方の Type-C ポートでコンシューマとして設定されます。DRP ポートの場合、PMG1-S3 ゲート ドライバピンの両方のペアが使用され、ポート 1 のコンシューマ パスでは GPIO によって制御される外部 FET が使用されます。

Figure 13. 97 ボール BGA を使用して 1 つの Type-C ポートに DRP を、もう 1 つの Type-C ポートにシンクを設定

## 電気的仕様

## 6. 電気的仕様

## 6.1 絶対最大定格

Table 3. 絶対最大定格<sup>[3]</sup>

| 仕様 ID            | パラメーター                    | 説明                                                          | Min                 | Typ | Max  | 単位               | 詳細 / 条件                                           |

|------------------|---------------------------|-------------------------------------------------------------|---------------------|-----|------|------------------|---------------------------------------------------|

| SID.PWR.ABS#1    | $V_{DDIO\_ABS}$           | $V_{SS}$ を基準にした I/O 電源電圧 ( $V_{SSIO} = V_{SSD} = V_{SSA}$ ) | -0.5 <sup>[4]</sup> | -   | 6    | V <sup>[5]</sup> | 絶対最小値 / 最大値                                       |

| SID.PWR.ABS#2    | $V_{CCD\_ABS}$            | $V_{SSD}$ を基準にした直接デジタルコア電圧入力                                | -0.5                | -   | 1.95 |                  | 絶対最小値 / 最大値                                       |

| SID.PWR.ABS#3    | $V_{GPIO\_ABS}$           | GPIO 電圧                                                     | -0.5                | -   | 6    | V                | 絶対最小値 / 最大値。<br>どの時点でも $V_{DDIO} + 0.5$ を超えてはいけない |

| SID.PWR.ABS#4    | $V_{GPIO\_FAILSAFE\_ABS}$ | フェイルセーフ GPIO 電圧                                             | -0.5                | -   | 6    |                  |                                                   |

| SID.PWR.ABS#5    | $I_{GPIO\_ABS}$           | GPIO ごとの電流                                                  | -25                 | -   | 25   | mA               | 絶対最小値 / 最大値                                       |

| SID.PWR.ABS#6    | $I_{GPIO\_injection}$     | ピンごとの GPIO 注入電流                                             | -0.5                | -   | 0.5  |                  |                                                   |

| SID.PD.PWR.ABS#1 | $V_{CONN\_SOURCE\_ABS}$   | $V_{SS}$ を基準にした最小 / 最大電源電圧                                  | -0.5                | -   | 6    |                  |                                                   |

| SID.PD.PWR.ABS#2 | $V_{SYS\_ABS}$            |                                                             |                     |     |      |                  |                                                   |

| SID.PD.PWR.ABS#3 | $V_{BUS\_ABS}$            | $V_{SS}$ を基準にした最小 / 最大 VBUS_C_P0/1 電圧                       | -0.3                | -   | 34   |                  | 最小値 / 絶対最大値                                       |

| SID.PD.PWR.ABS#4 | $V_{BUS\_NGDO\_ABS}$      | $V_{SS}$ を基準にした最小 / 最大 VBUS_IN/OUT_P0/1 電圧                  | -0.3                | -   | 34   |                  | 絶対最小値 / 最大値                                       |

| SID.PD.PIN.ABS#1 | $V_{CC\_PIN\_ABS}$        | CC1 と CC2 ピンの最小 / 最大電圧                                      | -0.5                | -   | 6    |                  |                                                   |

| SID.PD.PIN.ABS#2 | $V_{SBU\_PIN\_ABS}$       | SBU1 と SBU2 ピンの最小 / 最大電圧                                    | -0.5                | -   | 6    |                  | 絶対最小値 / 最大値。                                      |

| SID.PD.PIN.ABS#3 | $V_{USB\_PIN\_ABS}$       | USBDP と USBDM ピンの最小 / 最大電圧                                  | -0.5                | -   | 6    |                  | どの時点でも $V_{DD} + 0.5$ を超えてはいけない                   |

| SID.PD.PIN.ABS#4 | $V_{AUX\_PIN\_ABS}$       | AUX_N_P0/1 と AUX_P_P0/1 ピンの最小 / 最大電圧                        | -0.5                | -   | 6    |                  |                                                   |

| SID.PD.PIN.ABS#5 | $V_{CSA\_PIN\_ABS}$       | CSP_P0/1 と CSN_P0/1 ピンの最小 / 最大電圧                            | -0.3                | -   | 34   |                  | 絶対最小値 / 最大値                                       |

| BID1             | TSTG_AMAX                 | 保管温度                                                        | -55                 | 25  | 150  | °C               | 非動作温度。JESD22-A103 HTSL テストによる                     |

| BID44            | ESD_HBM                   | 静電気放電電圧                                                     | 2000                | -   | -    | V                | 人体モデル ESD                                         |

| BID45            | ESD_CDM                   |                                                             | 500                 |     |      |                  | デバイス帯電モデル ESD                                     |

| BID46            | $I_{LU}$                  | ラッチアップ電流制限                                                  | -100                | -   | 100  | mA               | 入力または出力、ピン間、ピンと電源間を流れる最大 / 最小電流                   |

注:

- Table 3 に記載されている絶対最大条件を超えて使用すると、デバイスに恒久的なダメージを与える可能性があります。長時間にわたって絶対最大条件下に置くと、デバイスの信頼性に影響する可能性があります。最大保管温度は JEDEC 標準 JESD22-A103, high temperature storage life に準拠した 150°C です。絶対最大条件以下で使用している場合でも、標準的な動作条件を超えると、デバイスが仕様に従って動作しない可能性があります。

- システムでは、負のスパイクがここで指定された最小電圧を超える場合は、ショットキーダイオードを追加して負のスパイクをクランプすることを推奨します。

- 特に指定がない限り、すべての電圧はグランドを基準にしています。

## 電気的仕様

Table 4. 端子ベースの絶対最大定格

| Sr. No. | 端子 (97 ボール BGA) | 端子 (48 ピン QFN) | 端子名  | 絶対最小値 (V) <sup>[6]</sup> | 絶対最大値 (V) <sup>[6]</sup> | 備考                    |

|---------|-----------------|----------------|------|--------------------------|--------------------------|-----------------------|

| 1       | H2              |                | P1.0 |                          |                          |                       |

| 2       | P3              | 12             | P1.1 |                          |                          |                       |

| 3       | R3              | 13             | P1.2 |                          |                          |                       |

| 4       | K4              | 14             | P1.3 |                          |                          |                       |

| 5       | M10             | 20             | P1.4 |                          |                          |                       |

| 6       | M12             | 21             | P1.5 |                          |                          |                       |

| 7       | K12             | 22             | P1.6 |                          |                          |                       |

| 8       | A2              |                | P2.0 |                          |                          |                       |

| 9       | B2              | 48             | P2.1 |                          |                          |                       |

| 10      | A3              | 47             | P2.2 |                          |                          |                       |

| 11      | B5              | 46             | P2.3 |                          |                          |                       |

| 12      | A7              | 45             | P2.4 |                          |                          |                       |

| 13      | A5              |                | P2.5 |                          |                          |                       |

| 14      | B7              |                | P2.6 |                          |                          |                       |

| 15      | A8              |                | P2.7 |                          |                          |                       |

| 16      | A1              | 1              | P3.0 |                          |                          |                       |

| 17      | B3              |                | P3.1 |                          |                          |                       |

| 18      | C2              |                | P3.2 |                          |                          |                       |

| 19      | B1              | 2              | P3.3 | -0.5                     | 6                        | 最大電圧は VDDIO+0.5 を超えない |

| 20      | D4              |                | P3.4 |                          |                          |                       |

| 21      | F4              | 3              | P3.5 |                          |                          |                       |

| 22      | E2              | 4              | P3.6 |                          |                          |                       |

| 23      | C1              |                | P3.7 |                          |                          |                       |

| 24      | E15             | 34             | P4.0 |                          |                          |                       |

| 25      | D12             | 35             | P4.1 |                          |                          |                       |

| 26      | G2              | 7              | P5.0 |                          |                          |                       |

| 27      | E1              | 8              | P5.1 |                          |                          |                       |

| 28      | H6              | 9              | P5.2 |                          |                          |                       |

| 29      | H1              | 10             | P5.3 |                          |                          |                       |

| 30      | G1              |                | P5.4 |                          |                          |                       |

| 31      | H4              | 11             | P5.5 |                          |                          |                       |

| 32      | G15             |                | P7.0 |                          |                          |                       |

| 33      | G14             |                | P7.1 |                          |                          |                       |

| 34      | A14             |                | P7.2 |                          |                          |                       |

| 35      | B13             |                | P7.3 |                          |                          |                       |

| 36      | B11             |                | P7.4 |                          |                          |                       |

| 37      | A9              |                | P7.5 |                          |                          |                       |

| 38      | B9              |                | P7.6 |                          |                          |                       |

注:

6. すべての電圧は  $V_{SS}$  を基準として測定されます。

## 電気的仕様

Table 4. 端子ベースの絶対最大定格 ( 続き )

| Sr. No. | 端子 (97 ボール BGA) | 端子 (48 ピン QFN) | 端子名              | 絶対最小値 (V) <sup>[6]</sup> | 絶対最大値 (V) <sup>[6]</sup> | 備考                  |  |  |  |

|---------|-----------------|----------------|------------------|--------------------------|--------------------------|---------------------|--|--|--|

| 39      | R8              | 17             | P0.0/LSRX_P1     | -0.5                     | 6                        | 最大電圧はVDDD+0.5を超えない  |  |  |  |

| 40      | R7              |                | P0.1/LSTX_P1     |                          |                          |                     |  |  |  |

| 41      | P7              |                | P0.2/DBG1_P1     |                          |                          |                     |  |  |  |

| 42      | K6              |                | P0.3/DBG2_P1     |                          |                          |                     |  |  |  |

| 43      | P8              |                | P0.4/DBG2_P0     |                          |                          |                     |  |  |  |

| 44      | M8              |                | P0.5/DBG1_P0     |                          |                          |                     |  |  |  |

| 45      | R9              |                | P0.6/LSTX_P0     |                          |                          |                     |  |  |  |

| 46      | R11             |                | P0.7/LSRX_P0     |                          |                          |                     |  |  |  |

| 47      | R5              | 15             | P6.0/SBU1_P1     |                          |                          |                     |  |  |  |

| 48      | P5              | 16             | P6.1/SBU2_P1     |                          |                          |                     |  |  |  |

| 49      | P13             | 18             | P6.2/SBU2_P0     |                          |                          |                     |  |  |  |

| 50      | R13             | 19             | P6.3/SBU1_P0     |                          |                          |                     |  |  |  |

| 51      | M4              |                | AUX_P_P1         | -0.5                     | 6                        | 最大電圧はVDDD+0.5を超えない  |  |  |  |

| 52      | M6              |                | AUX_N_P1         |                          |                          |                     |  |  |  |

| 53      | P11             |                | AUX_P_P0         |                          |                          |                     |  |  |  |

| 54      | P9              |                | AUX_N_P0         |                          |                          |                     |  |  |  |

| 55      | A11             | 40             | USBDM            | -0.5                     | 6                        | 最大電圧はVDDD+0.5を超えない  |  |  |  |

| 56      | A13             | 39             | USBDP            |                          |                          |                     |  |  |  |

| 57      | A15             | 37             | CSN_P0           | -0.3                     | 34                       | -                   |  |  |  |

| 58      | B15             | 38             | CSP_P0           |                          |                          |                     |  |  |  |

| 59      | C14             |                | CSN_P1           |                          |                          |                     |  |  |  |

| 60      | C15             |                | CSP_P1           |                          |                          |                     |  |  |  |

| 61      | N14             | 28             | CC1_P0           | -0.5                     | 6                        | -                   |  |  |  |

| 62      | N15             |                |                  |                          |                          |                     |  |  |  |

| 63      | N1              |                | CC1_P1           |                          |                          |                     |  |  |  |

| 64      | N2              |                |                  |                          |                          |                     |  |  |  |

| 65      | J14             |                |                  |                          |                          |                     |  |  |  |

| 66      | J15             | 30             | CC2_P0           |                          |                          |                     |  |  |  |

| 67      | J1              |                |                  |                          |                          |                     |  |  |  |

| 68      | J2              |                | CC2_P1           |                          |                          |                     |  |  |  |

| 69      | R14             | 24             | VBUS_IN_NGDO_P0  | -0.3                     | 34                       | -                   |  |  |  |

| 70      | R2              |                | VBUS_IN_NGDO_P1  |                          |                          |                     |  |  |  |

| 71      | R15             | 25             | VBUS_OUT_NGDO_P0 |                          |                          |                     |  |  |  |

| 72      | R1              |                | VBUS_OUT_NGDO_P1 |                          |                          |                     |  |  |  |

| 73      | P14             | 27             | VBUS_IN_CTRL_P0  |                          |                          |                     |  |  |  |

| 74      | P2              |                | VBUS_IN_CTRL_P1  | -0.3                     | 42                       | 出力専用端子です。           |  |  |  |

| 75      | P15             | 26             | VBUS_OUT_CTRL_P0 |                          |                          |                     |  |  |  |

| 76      | P1              |                | VBUS_OUT_CTRL_P1 |                          |                          |                     |  |  |  |

| 77      | E14             | 33             | XRES             | -0.5                     | 6                        | 最大電圧はVDDIO+0.5を超えない |  |  |  |

注:

6. すべての電圧はV<sub>SS</sub>を基準として測定されます。

## 電気的仕様

Table 4. 端子ベースの絶対最大定格 ( 続き )

| Sr. No. | 端子 (97 ボール BGA) | 端子 (48 ピン QFN) | 端子名             | 絶対最小値 (V) <sup>[6]</sup> | 絶対最大値 (V) <sup>[6]</sup> | 備考                                  |

|---------|-----------------|----------------|-----------------|--------------------------|--------------------------|-------------------------------------|

| 78      | B14             | 36             | VSYS            | -0.5                     | 6                        | -                                   |

| 79      | D8              | 43             | VDDD            | -                        |                          |                                     |

| 80      | D6              | 5              | VDDA            | -                        | 6                        | ボードレベルでVDDDとVDDAを短絡してください。          |

| 81      | F6              |                |                 |                          |                          |                                     |

| 82      | B8              | 23             | VDDIO           | -0.5                     | 6                        | VDDIOはVSYSと異なる電圧レベルも可能。VDDIO < VSYS |

| 83      | H12             | 42             |                 |                          |                          |                                     |

| 84      | D10             | 41             | VCCD            | -0.5                     | 1.95                     | 出力専用端子です。                           |

| 85      | H15             | 31             | VBUS_C_P0       | -0.3                     | 34                       | -                                   |

| 86      | H14             |                | VBUS_C_P1       |                          |                          |                                     |

| 87      | L14             | 29             | VCONN_Source_P0 | -0.5                     | 6                        | -                                   |

| 88      | L15             |                |                 |                          |                          |                                     |

| 89      | L1              |                | VCONN_Source_P1 | -0.5                     | 6                        | -                                   |

| 90      | L2              |                |                 |                          |                          |                                     |