# EZ-PD™ CCG3PA コンシューマ USB Type-C ポートコントローラー

## 概要

EZ-PD™ CCG3PA は、最新の USB Type-C および PD 規格に準拠しているインフィニオンの高度集積 USB Type-C ポートコントローラーであり、PC 電源アダプタ、モバイル充電器、車載充電器やパワーバンクのアプリケーションに向けて設計されました。そのようなアプリケーションに対し、CCG3PA は追加の機能および BOM 統合のメリットを提供します。CCG3PA は、32 ビット Arm® Cortex®-M0 プロセッサ、64KB フラッシュメモリ、完全な Type-C USB-PD トランシーバ、Type-C ポートに必要なすべての終端抵抗、電圧 (VBUS) 安定化用の統合フィードバック制御回路、およびシステムレベルの ESD 保護にインフィニオン独自の MOS8 技術を採用しています。24 ピン QFN および 16 ピン SOIC のパッケージで提供されています。

## 特長

### • Type-C および USB PD のサポート

- プログラマブルな電源 (PPS) モードを含む USB PD リビジョン 3.1 仕様に対応

- コンフィギュレーション可能な抵抗  $R_P$  と  $R_D$

- 1 個の USB Type-C ポートと 1 個の Type-A ポートに対応

### • 2 個のレガシー / 独自の充電ブロック

- QC 4.0, Apple 充電 2.4A, AFC, BC 1.2 に対応

- DP/DM ライン上ですべての必要な終端抵抗を提供

### • 統合された電圧 (VBUS) 安定化および電流検出アンプ

- 二次側フィードバックノードのアナログ安定化 (ダイレクトフィードバックまたは光カプラ)

- VBUS 制御用にシャントレギュレータ機能を統合

- 定電流または定電圧モード

- 定電流制御用にローサイド電流検出に対応

### • システム レベル フォールト保護

- VBUS から CC への短絡保護

- チップ搭載 OVP, OCP, UVP、および SCP

- 統合 ADC 回路により OTP に対応

### • 32 ビット MCU サブシステム

- Arm® Cortex®-M0 CPU

- 64KB フラッシュ

- 8KB SRAM

### • クロックおよび発振器

- 内蔵発振器により外部クロックが不要になる

### • 電源

- 3.0V ~ 24.5V 動作 (30V 許容)

### • システム レベル ESD 保護

- CC, VBUS\_C\_MON\_DISCHARGE, DP0, DM0, P2.2、および P2.3 ピンに適用

- IEC61000-4-2 レベル 4C に基づいた  $\pm 8\text{kV}$  接触放電および  $\pm 15\text{kV}$  空中放電

### • パッケージ

- 24 ピン QFN および 16 ピン SOIC

- 産業用拡張温度範囲 ( $-40^\circ\text{C} \sim +105^\circ\text{C}$ ) に対応

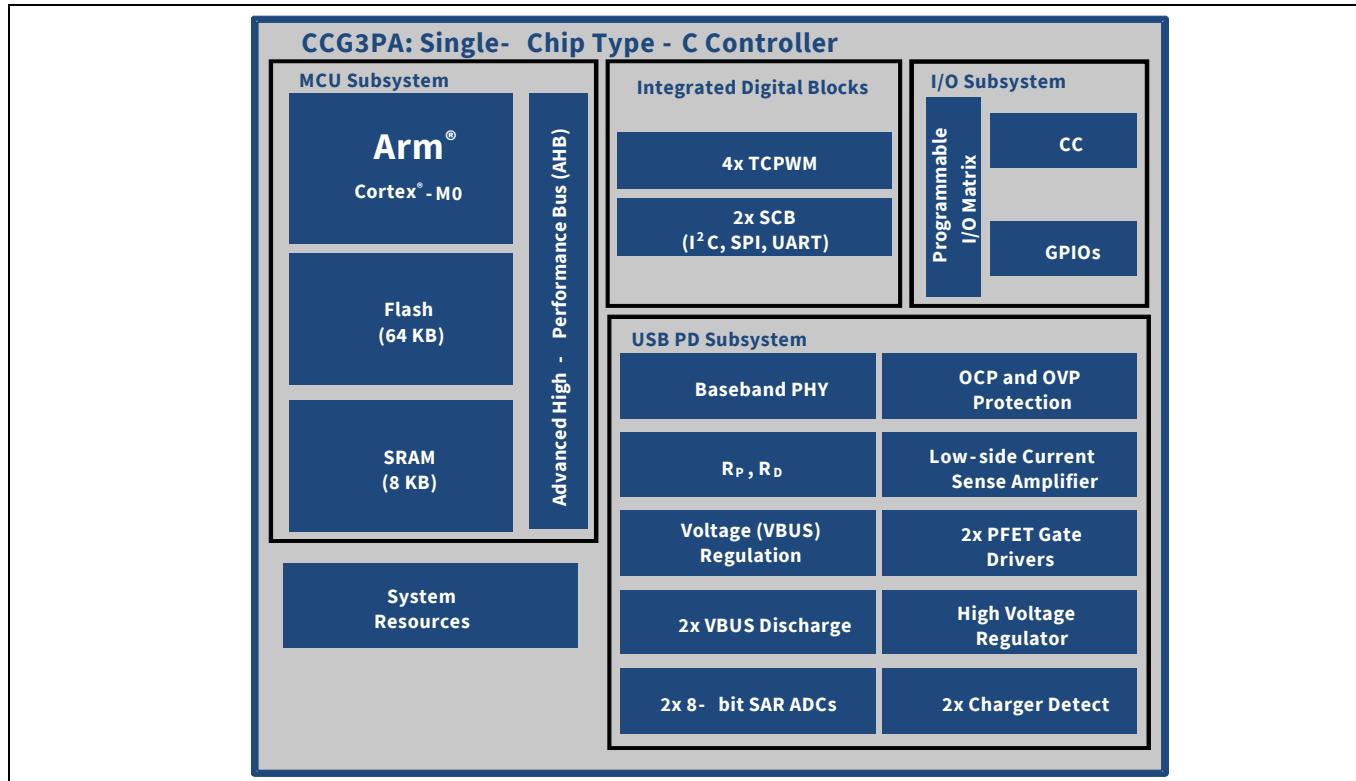

論理ブロック ダイヤグラム

## 論理ブロック ダイヤグラム

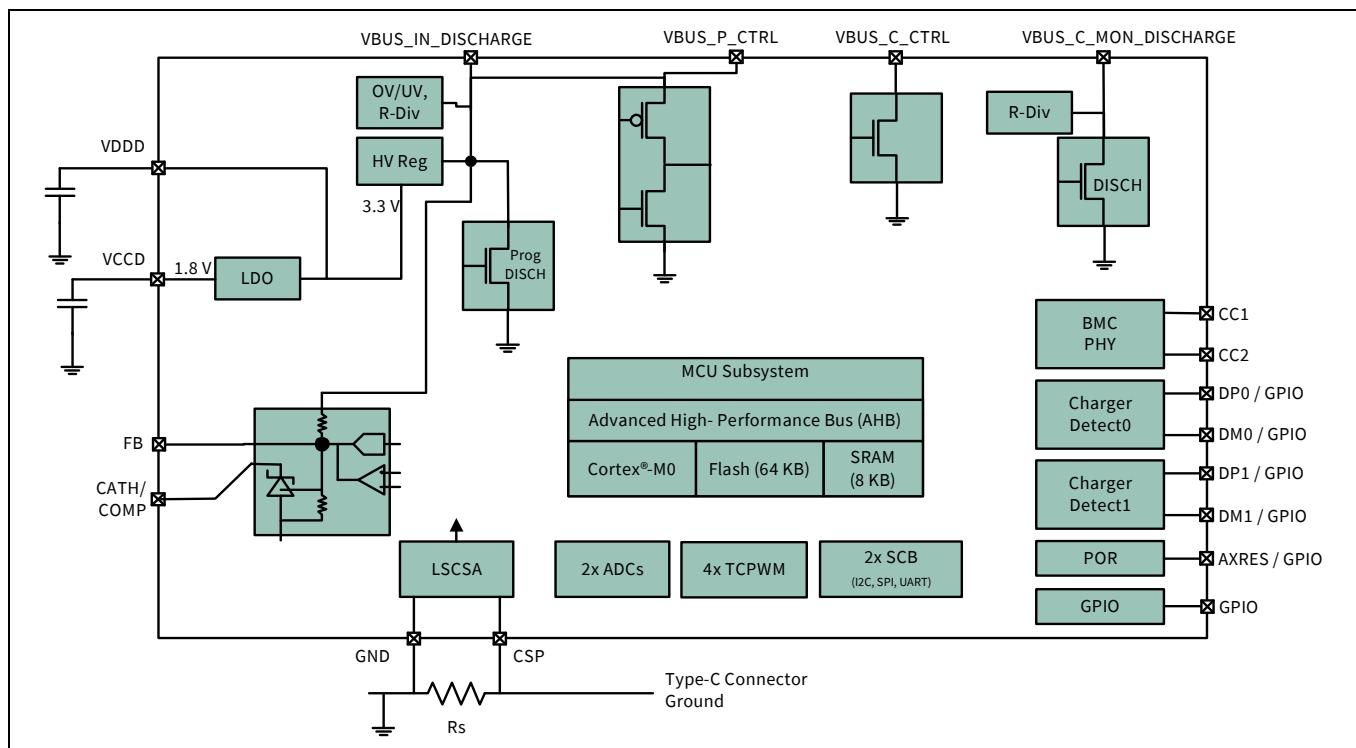

## 内部ブロック ダイヤグラム

## 目次

## 目次

|                                          |    |

|------------------------------------------|----|

| <b>概要</b>                                | 1  |

| <b>特長</b>                                | 1  |

| <b>論理ブロック ダイヤグラム</b>                     | 2  |

| <b>内部ブロック ダイヤグラム</b>                     | 2  |

| <b>目次</b>                                | 3  |

| <b>1 機能概要</b>                            | 4  |

| 1.1 MCU サブシステム                           | 4  |

| 1.1.1 CPU                                | 4  |

| 1.1.2 フラッシュ                              | 4  |

| 1.1.3 SROM                               | 4  |

| 1.2 USB PD サブシステム (SS)                   | 4  |

| 1.2.1 USB PD 物理層                         | 4  |

| 1.2.2 アナログ - デジタル変換器 (ADC)               | 4  |

| 1.2.3 充電器検出                              | 4  |

| 1.2.4 VBUS 過電流と過電圧保護                     | 5  |

| 1.2.5 VBUS 短絡保護                          | 5  |

| 1.2.6 Low サイド電流検出アンプ (CSA)               | 5  |

| 1.2.7 VBUS パス上の PFET ゲート ドライバー           | 5  |

| 1.2.8 VBUS 放電 FET                        | 5  |

| 1.2.9 電圧 (VBUS) 安定化                      | 5  |

| 1.3 内蔵デジタル ブロック                          | 5  |

| 1.3.1 シリアル通信ブロック (SCB)                   | 5  |

| 1.3.2 タイマー / カウンター /PWM (TCPWM) ブロック     | 6  |

| 1.4 I/O サブシステム                           | 6  |

| <b>2 電源システム概要</b>                        | 7  |

| <b>3 ピン配置</b>                            | 8  |

| <b>4 CCG3PA のプログラミングとブートロード</b>          | 12 |

| 4.1 SWD インターフェースを使用したデバイス フラッシュのプログラミング  | 12 |

| 4.2 CC インターフェースを使用したアプリケーション フームウェアの更新   | 13 |

| <b>5 アプリケーション図</b>                       | 14 |

| <b>6 電気的仕様</b>                           | 19 |

| 6.1 絶対最大定格                               | 19 |

| 6.2 デバイス レベルの仕様                          | 21 |

| 6.2.1 I/O                                | 23 |

| 6.3 デジタルペリフェラル                           | 25 |

| 6.3.1 GPIO ピン用のパルス幅変調 (PWM)              | 25 |

| 6.3.2 I <sup>2</sup> C                   | 25 |

| 6.4 システム リソース                            | 27 |

| 6.4.1 電圧低下 SWD インターフェースのパワー オンリセット (POR) | 27 |

| 6.4.2 内部主発振器                             | 27 |

| 6.4.3 内部低速発振器 - 電源切断                     | 28 |

| 6.4.4 ゲート ドライバー仕様                        | 30 |

| 6.4.5 アナログ - デジタル変換器                     | 33 |

| 6.4.6 メモリ                                | 33 |

| <b>7 注文情報</b>                            | 34 |

| 7.1 注文コードの定義                             | 34 |

| <b>8 パッケージ</b>                           | 34 |

| <b>9 略語</b>                              | 38 |

| <b>10 本書の表記法</b>                         | 40 |

| 10.1 測定単位                                | 40 |

| <b>改訂履歴</b>                              | 41 |

## 機能概要

# 1 機能概要

## 1.1 MCU サブシステム

### 1.1.1 CPU

EZ-PD™ CCG3PA 内の Cortex®-M0 CPU は 32 ビット MCU サブシステムの一部であり、広範なクロック ゲーティングに対応した低消費電力動作に最適化されています。

また、CPU はプログラムとデバッグのためのシリアルワイヤデバッグ (SWD) インターフェースも備えています。EZ-PD™ CCG3PA に使用するデバッグ コンフィギュレーションには、4 個のブレークポイント (アドレス) コンパレータと 2 個のウォッチポイント (データ) コンパレータがあります。

### 1.1.2 フラッシュ

EZ-PD™ CCG3PA デバイスは、フラッシュ ブロックからの平均アクセス時間を改善するために CPU に密結合されたフラッシュ アクセラレータと、1 つの 64KB バンクを備えたフラッシュ モジュールを持っています。

### 1.1.3 SROM

ブートおよびコンフィギュレーションルーチンを含んでいる監視 ROM が提供されています。

## 1.2 USB PD サブシステム (SS)

USB PD サブシステムは Type-C USB ポートへのインターフェースを提供します。このサブシステムは電流検出アンプ、高電圧レギュレータ、OVP、OCP、および電源スイッチ ブロックからなります。また、Type-C ポート上でサポートされているすべての必要な ESD も含まれます。

### 1.2.1 USB PD 物理層

USB PD 物理層は、PD 3.1 規格に従って CC チャネルを介して BMC 符号化データを通信するトランスマッタとレシーバから成ります。すべての通信は半二重です。物理層 (PHY) はチャネル上の通信エラーを最小限に抑えるために衝突回避を実行します。

USB PD ブロックは USB PD 仕様に従って必要とされるすべての終端抵抗 ( $R_P$  と  $R_D$ ) およびそれらのスイッチを含みます。 $R_P$  と  $R_D$  抵抗は、接続検出、プラグ方向検出および USB DFP/UFP 役割確立のために必要です。 $R_P$  抵抗は電流源として実装されています。

USB Type-C 仕様によると、CCG3PA などの Type-C コントローラーは電源が供給されていない状態での役割に応じて、特定の終端抵抗を用意する必要があります。パワー バンク アプリケーションでのシンクの役割は、CC ピン上で  $R_D$  抵抗が必要ですが、電源アダプタなどのアプリケーションでの DFP の役割は、両方の CC ラインが開放であることが必要です。このようなアプリケーション用に柔軟性を持たせるため、CCG3PA は電源が供給されていない状態で個別のパッドまたはピン上で必要な抵抗を提供します。デッド バッテリ  $R_D$  抵抗は個別のパッド上で利用可能です。デッド バッテリ  $R_D$  は、パワー バンク アプリケーション向けのデバイスで接続オプションとして実装されています。これらのデバイスでは、各 CC ピンはその対応する  $R_D$  抵抗に接続されています。DFP アプリケーション向けのデバイスでは、CC ピンはデッド バッテリ  $R_D$  に接続されていません。

### 1.2.2 アナログ - デジタル変換器 (ADC)

8 ビット SAR ADC はチップ上の汎用 AD 変換のアプリケーションに利用できます。この ADC はチップ搭載アナログマルチプレクサを介してすべての GPIO および DP/DM ピンからアクセスできます。CCG3PA は 2 個の ADC インスタンスを含みます。ADC の電圧リファレンスは、VDDD 電源または内部バンドギャップから生成されます。ADC で GPIO ピン電圧を検知する場合、ピン電圧は VDDIO 電源電圧の値を超えられません。

### 1.2.3 充電器検出

2 対の DP/DM ピンに接続された 2 個の充電器検出ブロックにより、CCG3PA は BC 1.2 に準拠した従来のバッテリ充電器および Apple, Qualcomm の QuickCharge 4.0 および Samsung AFC の独自の充電器仕様をエミュレートできます。

## 機能概要

### 1.2.4 VBUS 過電流と過電圧保護

CCG3PA チップは、Type C ポート上で VBUS 過電圧保護 (OVP) と過電流保護 (OCP) 用の、閾値と応答時間が設定可能な統合ハードウェア ブロックを備えています。

### 1.2.5 VBUS 短絡保護

CCG3PA は、高電圧 VBUS への偶発的な短絡に耐える CC1, CC2, P2.2, および P2.3 の 4 つの VBUS ピンを提供します。これらのピンは、誤って高電圧 VBUS と短絡しないように保護されています。CC1 と CC2 ピンが USB Type-C コネクタの VBUS ピンの隣に配置されているので、不慮の短絡が発生することがあります。高電圧 VBUS 短絡保護を備えないパワー デリバリー コントローラーは、偶発的な短絡の発生で損傷します。保護回路がトリガされると、過電圧耐性 (OVT) ピンで CCG3PA は最大 17V を永久に処理でき、17V ~ 22V DC を 1000 時間処理できます。CC ピンで VBUS 短絡イベントが発生すると、USB Type-C ケーブルの RLC 素子によって発生した一時的な高リング電圧が観測できます。CCG3PA の接続なしでは、このリング電圧は最大 VBUS 電圧 (21.5V) の 2 倍 (44V) になることがあります。しかし、CCG3PA が接続されている場合、一時的な高リング電圧をクランプし、IEC ESD 保護ダイオードを使用して CC ピンを保護できます。

### 1.2.6 Low サイド電流検出アンプ (CSA)

CCG3PA チップはまた、5mΩ の外付け抵抗を介して 100mA ~ 5.5A の範囲の電流レベルを検出できる Low サイド電流検出アンプも組み込まれています。さらに、電源アダプタのアプリケーションではプロバイダとして定電流動作モードに対応しています。

### 1.2.7 VBUS パス上の PFET ゲート ドライバー

CCG3PA は、VBUS のプロバイダとコンシューマのパス上で外部 PFET を駆動するための 2 個の統合 PFET ゲート ドライバーを備えています。VBUS\_P\_CTRL ゲート ドライバーはアクティブなプルアップ抵抗に接続されており、High, Low または High-Z の駆動が可能です。

VBUS\_C\_CTRL ゲート ドライバーは Low または High-Z の駆動のみが可能であり、外付けプルアップ抵抗が必要です。これらのピンは VBUS 電圧に耐えられます。

### 1.2.8 VBUS 放電 FET

CCG3PA はまた、取り外し時に USB-PD 仕様のタイミングを満たすように VBUS を放電するための 2 個の統合 VBUS 放電 FET を備えています。プロバイダ側の VBUS 放電 FET は、二次側でのデフォルトの 5V VBUS への下降を加速させるために使用できます。

### 1.2.9 電圧 (VBUS) 安定化

CCG3PA は、Type-C 経由でピア デバイスから取得した VBUS ピンの適切な電圧を得るために、二次側制御用の統合フィードバック制御回路 (AC/DC のアプリケーション向け) およびフィードバック / カソード ピンのアナログ安定化を備えています。

## 1.3 内蔵デジタル ブロック

### 1.3.1 シリアル通信ブロック (SCB)

EZ-PD™ CCG3PA は、I<sup>2</sup>C, SPI, または UART インターフェースを実装するように設定できる 2 個の SCB を内蔵しています。ハードウェア I<sup>2</sup>C ブロックは、マルチマスター アービトリエーションが可能なフルマルチマスターおよびスレーブ インターフェースを実装します。SPI モードでは、SCB ブロックはマスターまたはスレーブとして動作するようにコンフィギュレーションできます。

I<sup>2</sup>C モードでは、SCB ブロックは最大 1Mbps ( ファースト モード プラス ) で動作でき、CPU の割込みオーバヘッドとレイテンシを削減するためにバッファリング オプションを柔軟に選択できます。これらのブロックはまた、EZ-PD™ CCG3PA のメモリにメールボックス アドレス範囲を作る I<sup>2</sup>C に対応しており、メモリアレイへの読み書きをする I<sup>2</sup>C 通信を効果的に縮小します。さらに、このブロックは送受信用の深さ 8 の FIFO にも対応しています。これは、CPU がデータを読み出す時間の増加によって、時間どおりに読み出しデータを持たない CPU に起因したクロック ストレッチの必要性を大幅に縮小します。

## 機能概要

$I^2C$  ペリフェラルは NXP  $I^2C$  バス仕様とユーザー マニュアル (UM10204) で定義されたとおりに  $I^2C$  標準モード、ファースト モードおよびファースト モード プラスのデバイスと互換性があります。 $I^2C$  バス I/O は、オープンドレイン モードの GPIO で実装されます。

以下の点では、EZ-PD™ CCG3PA の SCB ブロック上の  $I^2C$  ポートは  $I^2C$  仕様に完全に準拠していません。

- SCB1 の  $I^2C$  ポート用の GPIO セルは、過電圧耐性がないため、他の  $I^2C$  システムから独立してホットスワップや電源投入できません。

- ファスト モード プラスは 0.4V の  $V_{OL}$  で 20mA の  $I_{OL}$  仕様があります。GPIO セルが吸い込めるのは最大 0.6V の  $V_{OL}$  で最大 8mA の  $I_{OL}$  です。

- ファスト モードとファスト モード プラスは、GPIO セルで満たせない最小立ち下り時間の仕様があります。低速ストロング モードはバス負荷によってはこの仕様を満たすことがあります。

### 1.3.2 タイマー / カウンター / PWM (TCPWM) ブロック

EZ-PD™ CCG3PA には 4 個の TCPWM ブロックがあります。各 TCPWM ブロックは、16 ビットタイマー、カウンター、パルス幅変調器 (PWM)、直交デコーダ機能を実装します。ブロックは入力信号の周期とパルス幅の測定 (タイマー) や特定のイベントが発生する回数のカウント (カウンター)、PWM 信号の生成、直交信号の復号に使用されます。

## 1.4 I/O サブシステム

EZ-PD™ CCG3PA は最大 12 の GPIO を持っており、その一部は SCB の機能 ( $I^2C$ , UART, SPI) をサポートするように使用できます。GPIO ピン P0.0 および P0.1 は、過電圧耐性 (OVT) (最大 6V) です。

GPIO ブロックは以下を実装します。

- 7 つの駆動強度モード :

- 入力のみ

- 弱プルアップ、強プルダウン

- 強プルアップ、弱プルダウン

- オープンドレイン、強プルダウン

- オープンドレイン、強プルアップ

- 強プルアップ、強プルダウン

- 弱プルアップ、弱プルダウン

- 入力閾値選択 (CMOS または LVTTL)

- 駆動強度モード以外に、入力と出力バッファのイネーブル / ディセーブルの個別制御

- 前の状態をラッチするためのホールド モード (ディープスリープ モードで I/O 状態を維持するため)

- EMI を改善するための  $dV/dt$  関連のノイズ制御用の選択可能なスルーレート

電源投入とリセットの間、入力に過電流を与えず、過剰なターンオン電流を発生させないために、I/O ピンは無効状態にされます。高速 I/O マトリックスとして知られている多重化ネットワークが、1 本の I/O ピンに接続され得る複数の信号間を多重化するのために使用されます。

ポート ピン P1.0 と P1.1 は OCP/SCP/OVP/UVP 状態のフォールトを示すよう設定できます。任意の 2 つのフォールト状態は 2 つの GPIO にマッピングできるか、または全 4 つのフォールト状態は論理和が取られ 1 つの GPIO にマッピングできます。

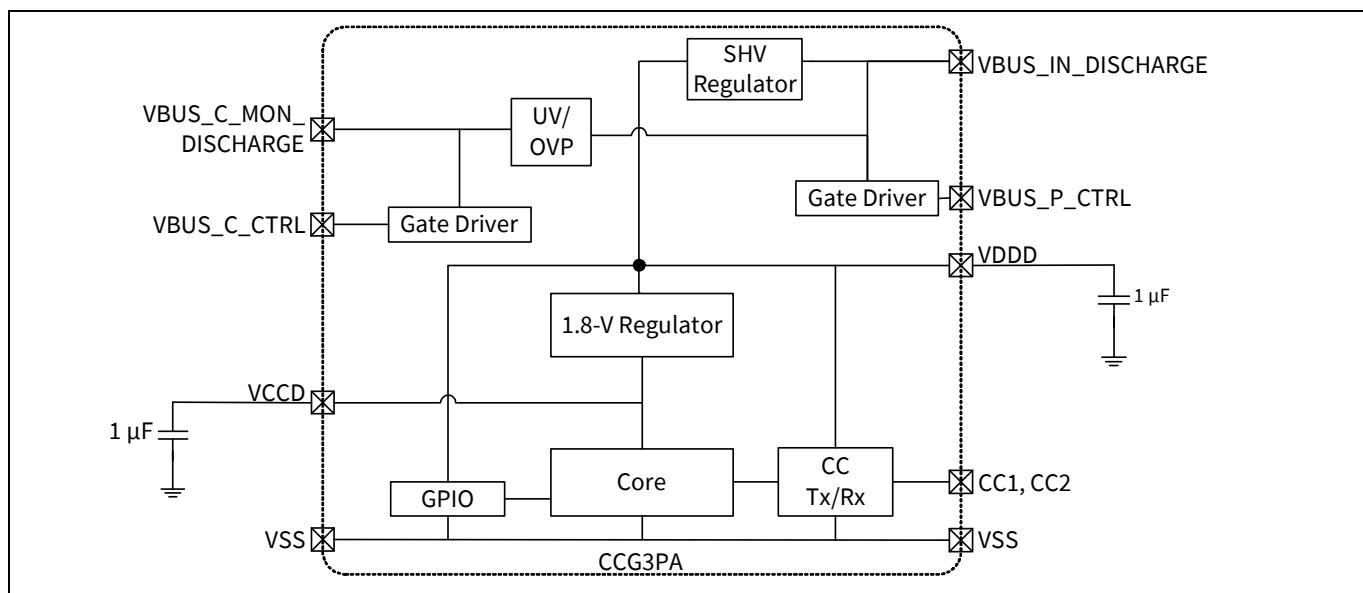

## 2 電源システム概要

CCG3PA は VBUS\_IN\_DISCHARGE (3.0V ~ 24.5V) または VDDD (2.7V ~ 5.5V) の外部電源から動作できます。VBUS\_IN\_DISCHARGE を介して電源供給される場合、内部レギュレータはチップ動作のために 3.3V の VDDD を生成します。安定化された電源 VDDD は、いくつかのアナログブロック内で直接使用されるか、またはコアの大部分に電源を供給する VCCD (1.8V) にさらに降圧されます。CCG3PA は 3 つの電力モードがあります。アクティブ、スリープ、ディープスリープ。これらの電力モード間の遷移は電力システムによって管理されます。VBUS\_IN\_DISCHARGE ピンを介した電源供給の場合、VDDD は外部デバイスに電源を供給するために使用できず、レギュレータの安定化のみを目的として 1mF コンデンサに接続する必要があります。これらのピンは電源としてサポートされていません。コンデンサの接続については、アプリケーション図を参照してください。

Table 1 CCG3PA 電力モード

| モード             | 説明                                                                   |

|-----------------|----------------------------------------------------------------------|

| パワーオンリセット (POR) | 電源が有効、内部リセットソースがアサートされたか、またはスリープコントローラーがシステムをリセット状態から起動している          |

| アクティブ           | 電源が有効、CPU が命令を実行している                                                 |

| スリープ            | 電源が有効、CPU が命令を実行していない。電力節約のために、動作中でないすべてのロジックはクロックゲートされる             |

| ディープスリープ        | 主レギュレータおよびほとんどのブロックがオフにされる。ディープスリープレギュレータがロジックに電源を供給するが、低速クロックのみ利用可能 |

Figure 1 電力システム要件のブロックダイヤグラム

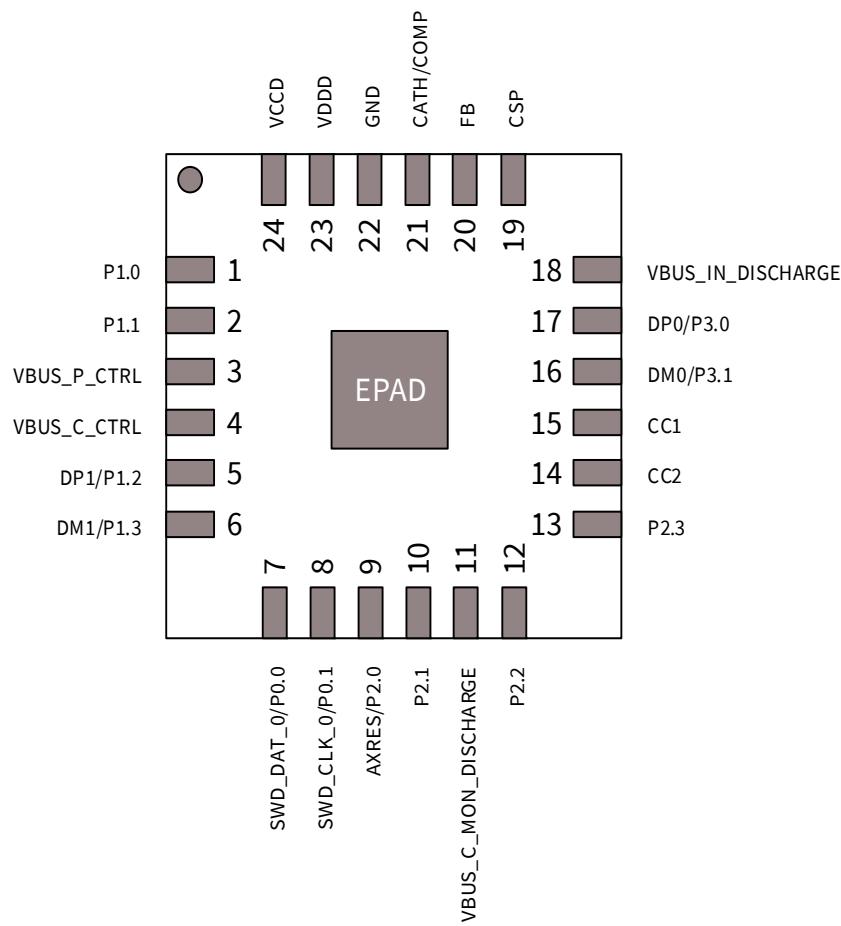

ピン配置

### 3 ピン配置

Table 2 CCG3PA ピンの説明

| 24 ピン QFN | 16 ピン SOIC | ピン名                  | 説明                                                                                                                   |

|-----------|------------|----------------------|----------------------------------------------------------------------------------------------------------------------|

| 1         | -          | P1.0                 | ポート 1 ピン 0: GPIO/UART_1_CTS/I2C_SDA_1 <sup>[1]</sup> / TCPWM_line_0 <sup>[2]</sup> , プログラマブル SCP/OCP/OVP/UVP フォールト表示 |

| 2         | -          | P1.1                 | ポート 1 ピン 1: GPIO/UART_1_RTS/I2C_SCL_1 <sup>[1]</sup> / TCPWM_line_1 <sup>[3]</sup> , プログラマブル SCP/OCP/OVP/UVP フォールト表示 |

| 3         | 5          | VBUS_P_CTRL          | プロバイダ (PMOS) FET 制御 (30V 許容)<br>0: パスが オン<br>1: パスが オフ                                                               |

| 4         | -          | VBUS_C_CTRL          | VBUS コンシューマ (PMOS) FET 制御 (30V 許容)<br>0: パスが オン<br>Z: パスが オフ                                                         |

| 5         | -          | DP1/P1.2             | USB D+/ ポート 1 ピン 2: GPIO/UART_1_TX1/AFC/QC/BC 1.2/Apple 充電 /IEC 非準拠                                                  |

| 6         | -          | DM1/P1.3             | USB D-/ ポート 1 ピン 3: GPIO/UART_1_RX1/AFC/QC/BC 1.2/Apple 充電 /IEC 非準拠                                                  |

| 7         | 6          | SWD_DAT_0/P0.0       | Port 0 pin 0: GPIO/OVT/I2C_SDA_0/TCPWM_line_0/UART_0_CTS                                                             |

| 8         | 7          | SWD_CLK_0/P0.1       | Port 0 pin 1: GPIO/OVT/I2C_SCL_0/TCPWM_line_1/UART_0_RTS                                                             |

| 9         | 8          | AXRES/P2.0           | Port 2 pin 0: GPIO/ 代替 XRES <sup>[4]</sup> /TCPWM_line_0//UART_0_TX0                                                 |

| 10        | -          | P2.1                 | Port 2 pin 1: GPIO/TCPWM_line_1//UART_0_RX0                                                                          |

| 11        | 9          | VBUS_C_MON_DISCHARGE | 内部放電 FET 付き Type C VBUS モニター                                                                                         |

| 12        | -          | P2.2                 | ポート 2 ピン 2: プルアップアシスト付きオープンドレイン付き GPIO。GPIO_20VT/I2C_SDA_1/IEC として設定可能。VBUS ピンとの一時的な短絡を許容                            |

| 13        | -          | P2.3                 | ポート 2 ピン 3: プルアップアシスト付きオープンドレイン付き GPIO。GPIO_20VT/I2C_SCL_1/IEC として設定可能。VBUS ピンとの一時的な短絡を許容                            |

| 14        | 10         | CC2                  | デッド バッテリ Rd 接続オプション付き通信チャネル 2/IEC 準拠。VBUS ピンとの一時的な短絡を許容                                                              |

| 15        | 11         | CC1                  | デッド バッテリ Rd 接続オプション付き通信チャネル 1/IEC 準拠。VBUS ピンとの一時的な短絡を許容                                                              |

| 16        | 12         | DM0/P3.1             | USB D-/ ポート 3 ピン 1: GPIO/UART_1_RX0/AFC/QC/BC 1.2/Apple 充電 /IEC 準拠                                                   |

| 17        | 13         | DP0/P3.0             | USB D+/ ポート 3 ピン 0: GPIO/UART_1_TX0/AFC/QC/BC 1.2/Apple 充電 /IEC 準拠                                                   |

## 注:

- 2 個の SCB ブロック (SCB0 と SCB1) のうち、SCB0 の I2C 機能は P0.0/P0.1 の GPIO ピンにマッピングする一方、SCB1 の I2C 機能は P1.0/P1.1 または P2.2/P2.3 の GPIO ピンにマッピングできる柔軟性があります。

- TCPWM\_line\_0 はポート ピン P1.0, P0.0, P2.0 または P2.2 にマッピングできます。

- TCPWM\_line\_1 はポート ピン P1.1, P0.1, P2.1 または P2.3 にマッピングできます。

- AXRES ピンは電源投入時の I/O 初期化時間 (詳細は [Table 7](#) を参照してください) の間内部でプルアップされます。

- これらのピンに関する仕様については、[Table 10](#) および [Table 11](#) を参照してください。

## ピン配置

**Table 2 CCG3PA ピンの説明 (continued)**

| 24 ピン QFN | 16 ピン SOIC | ピン名                   | 説明                                   |

|-----------|------------|-----------------------|--------------------------------------|

| 18        | 14         | VBUS_IN_DIS<br>CHARGE | 内部放電 FET 付き VBUS 電源入力 (3.0V ~ 24.5V) |

| 19        | 16         | CSP                   | CS +: 電流検出入力                         |

| 20        | 1          | FB                    | 電圧調整フィードバック ピン                       |

| 21        | 2          | CATH/COMP             | 他のアプリケーションの電圧調整および補正のカソード            |

| 22        | 15         | GND                   | グランド                                 |

| 23        | 3          | VDDD                  | 電源入力 : 2.7V ~ 5.5V                   |

| 24        | 4          | VCCD                  | 1.8V コア電圧ピン (電源として使用するためのものではない)     |

| -         | -          | EPAD                  | グランド                                 |

## 注:

- 2 個の SCB ブロック (SCB0 と SCB1) のうち、SCB0 の I2C 機能は P0.0/P0.1 の GPIO ピンにマッピングする一方、SCB1 の I2C 機能は P1.0/P1.1 または P2.2/P2.3 の GPIO ピンにマッピングできる柔軟性があります。

- TCPWM\_line\_0 はポートピン P1.0, P0.0, P2.0 または P2.2 にマッピングできます。

- TCPWM\_line\_1 はポートピン P1.1, P0.1, P2.1 または P2.3 にマッピングできます。

- AXRES ピンは電源投入時の I/O 初期化時間 (詳細は [Table 7](#) を参照してください) の間内部でプルアップされます。

- これらのピンに関する仕様については、[Table 10](#) および [Table 11](#) を参照してください。

Table 3 GPIO ポート, ピンおよびそれらの機能

| ポート  | 24-QFN   | 16-SOIC  | SCB 機能     |            |             | TCPWM          | フォールト<br>インジケータ | 保護容量       |     | USB 充電信号 |    |       |       | IEC4 |

|------|----------|----------|------------|------------|-------------|----------------|-----------------|------------|-----|----------|----|-------|-------|------|

|      | ピン<br>番号 | ピン<br>番号 | UART       | SPI        | I2C         |                |                 | VBUS<br>短絡 | OVT | AFC      | QC | BC1.2 | Apple |      |

| P0.0 | 7        | 6        | UART_0_CTS | SPI_1_MOSI | I2C_0_SDA   | TCPWM_line_0:0 | -               | -          | 有   | -        | -  | -     | -     | -    |

| P0.1 | 8        | 7        | UART_0_RTS | SPI_1_MISO | I2C_0_SCL   | TCPWM_line_1:0 | -               | -          | 有   | -        | -  | -     | -     | -    |

| P1.0 | 1        |          | UART_1_CTS | SPI_0_SEL  | I2C_1_SDA:1 | TCPWM_line_2:1 | 有               | -          | -   | -        | -  | -     | -     | -    |

| P1.1 | 2        |          | UART_1_RTS | SPI_0_MISO | I2C_1_SCL:1 | TCPWM_line_3:1 | 有               | -          | -   | -        | -  | -     | -     | -    |

| P1.2 | 5        |          | UART_1_TX1 | SPI_0_MOSI | -           | -              | -               | -          | -   | D+       | D+ | D+    | D+    | -    |

| P1.3 | 6        |          | UART_1_RX1 | SPI_0_CLK  | -           | -              | -               | -          | -   | D-       | D- | D-    | D-    | -    |

| P2.0 | 9        | 8        | UART_0_TX0 | SPI_1_SEL  | -           | TCPWM_line_2:0 | -               | -          | -   | -        | -  | -     | -     | -    |

| P2.1 | 10       |          | UART_0_RX0 | SPI_1_CLK  | -           | TCPWM_line_3:0 | -               | -          | -   | -        | -  | -     | -     | -    |

| P2.2 | 12       |          | UART_0_TX1 | -          | I2C_1_SDA:0 | TCPWM_line_0:1 | -               | 有          | -   | -        | -  | -     | -     | 有    |

| P2.3 | 13       |          | UART_0_RX1 | -          | I2C_1_SCL:0 | TCPWM_line_1:1 | -               | 有          | -   | -        | -  | -     | -     | 有    |

| P3.0 | 17       | 13       | UART_1_TX0 | -          | -           | -              | -               | -          | -   | D+       | D+ | D+    | D+    | 有    |

| P3.1 | 16       | 12       | UART_1_RX0 | -          | -           | -              | -               | -          | -   | D-       | D- | D-    | D-    | 有    |

## ピン配置

Figure 2 24-QFN パッケージのピン配置(上面図)

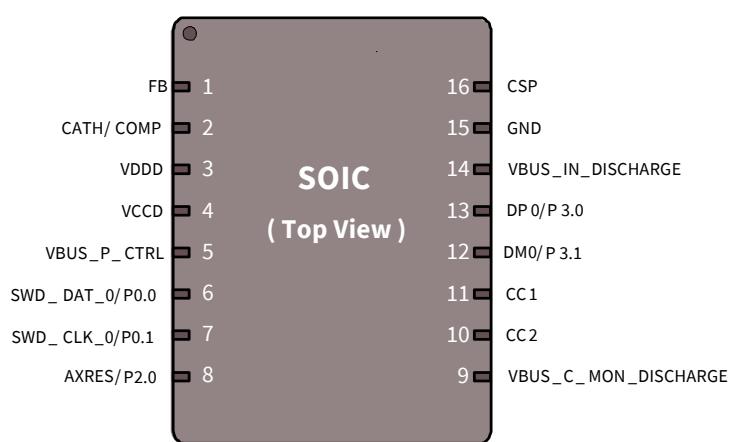

Figure 3 16-SOIC パッケージのピン配置 (上面図)

## 4 CCG3PA のプログラミングとブートロード

アプリケーションファームウェアを CCG3PA デバイスにプログラムするには、2 つの方法があります。

1. SWD インターフェースを使用したデバイス フラッシュのプログラミング

2. CC インターフェースを使用したアプリケーション ファームウェアの更新

1. SWD インターフェースを使用したデバイス フラッシュのプログラミング

2. CC インターフェースを使用したアプリケーション ファームウェアの更新

一般に、CCG3PA デバイスは開発中または最終製品の製造プロセス中にのみ、SWD インターフェースを介してプログラムされます。最終製品が製造されると、CC ブートローダ インターフェースを介して CCG3PA デバイスのアプリケーション ファームウェアを更新できます。

### 4.1 SWD インターフェースを使用したデバイス フラッシュのプログラミング

CCG3PA ファミリのデバイスは SWD インターフェースを介してプログラムできます。インフィニオンは、フラッシュのプログラミングおよびファームウェアのデバッグに使用できる MiniProg3 と呼ばれるプログラミングキット ([CY8CKIT-002 MiniProg3 kit](#)) と [PSoC™ Programmer ソフトウェア](#) を提供しています。フラッシュは、HEX ファイルから情報をダウンロードすることによってプログラムされます。この HEX ファイルは、[PSoC™ Creator ソフトウェア](#)でファームウェアプロジェクトをビルドした結果として生成されたバイナリ ファイルです。MiniProg3 プログラマの使用方法の詳細は [ここ](#) をクリックしてください。製造環境で大量のプログラミングをサポートする多くのサードパーティ製プログラマがあります。

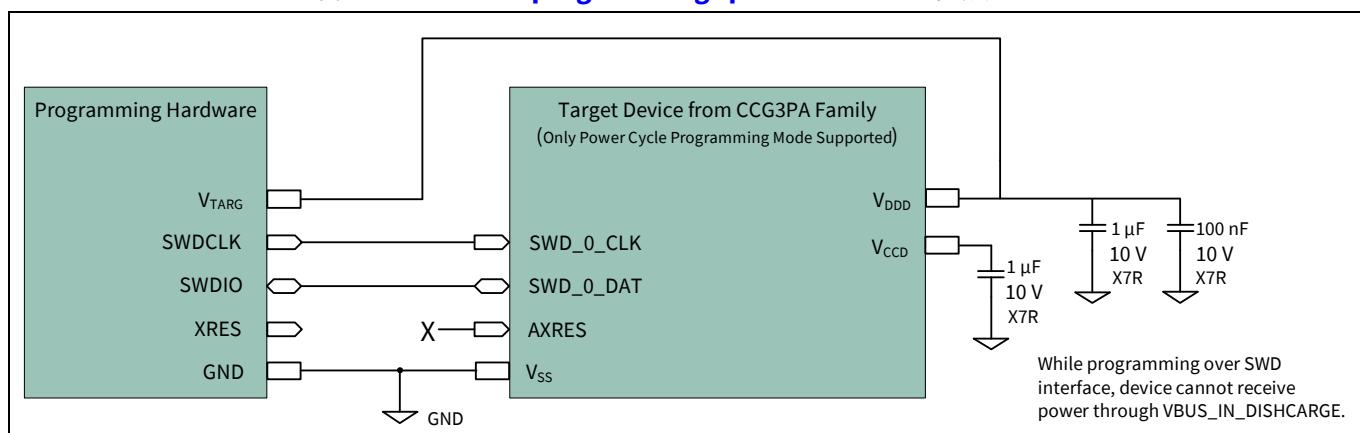

**Figure 4** のブロックダイヤグラムに示すように、SWD\_0\_DAT と SWD\_0\_CLK のピンは、ホストプログラマのそれぞれ SWDIO (データ) と SWDCLK (クロック) のピンに接続されています。SWD プログラミング中、ホストプログラマの VTARG (ターゲット デバイスへの電源) を CCG3PA デバイスの VDDD ピンに接続することで、CCG3PA デバイスはホストプログラマによって給電される必要があります。SWD インターフェースを介してプログラムしている間は、CCG3PA デバイスは VBUS\_IN\_DISCHARGE を介して電力供給を受けられません。

CCG3PA デバイス ファミリは XRES ピンを持っていません。そのため、ホストプログラマからの XRES ラインは未接続となり、リセット モードを使用したプログラミングはサポートされません。つまり、XRES ラインが使用されていないため、CCG3PA デバイスはパワーサイクル プログラミング モードだけがサポートされます。詳細は [CYPDxxxx programming specifications](#) を参照してください。

Figure 4 プログラマと CYPD317x デバイスの接続

## 4.2 CC インターフェースを使用したアプリケーションファームウェアの更新

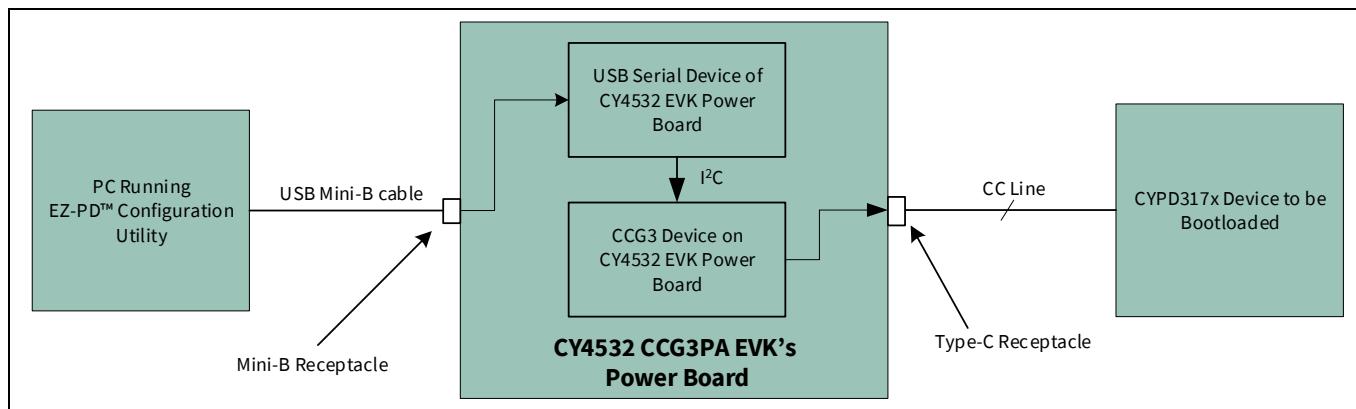

CCG3PA アプリケーションのブートロードでは、CY4532 CCG3PA EVK を使用し、CC ラインを介してプログラミングおよびコンフィギュレーションデータをインフィニオン固有のベンダ定義メッセージ (VDM) として送信できます。Figure 5 に示すように、CY4532 CCG3PA EVK の電源基板は、一方の端に CCG3PA デバイスを含むシステムに接続され、もう一方の端に EZ-PD™ コンフィギュレーションユーティリティを実行する Windows PC に接続され、CCG3PA デバイスをブートロードします。

Figure 5 CC インターフェースを使用したアプリケーションファームウェアの更新

CC インターフェースを介したアプリケーションファームウェア (FW) の更新機能は、開発および製造中に使用することを目的としています。インフィニオンは、EZ-PD™ Configuration Utility を使用して、大量生産の前に CCG3PA のフラッシュに更新されるファームウェアの CC インターフェースを介したアプリケーション FW 更新をオフにすることを強く推奨します。これにより、許可されていないファームウェアが現場の CC インターフェースを介して更新されるのを防ぎます。EZ-PD™ Configuration Utility でこれを設定する方法については、ナレッジベース記事 [KBA230192](#) を参照してください。

オンラインファームウェアアップデートのために、CC インターフェース機能を介したアプリケーションファームウェアアップデートを量産後に保持したい場合は、[弊社営業窓口](#) へ詳細なガイドラインについてお問い合わせください。

## アプリケーション図

## 5 アプリケーション図

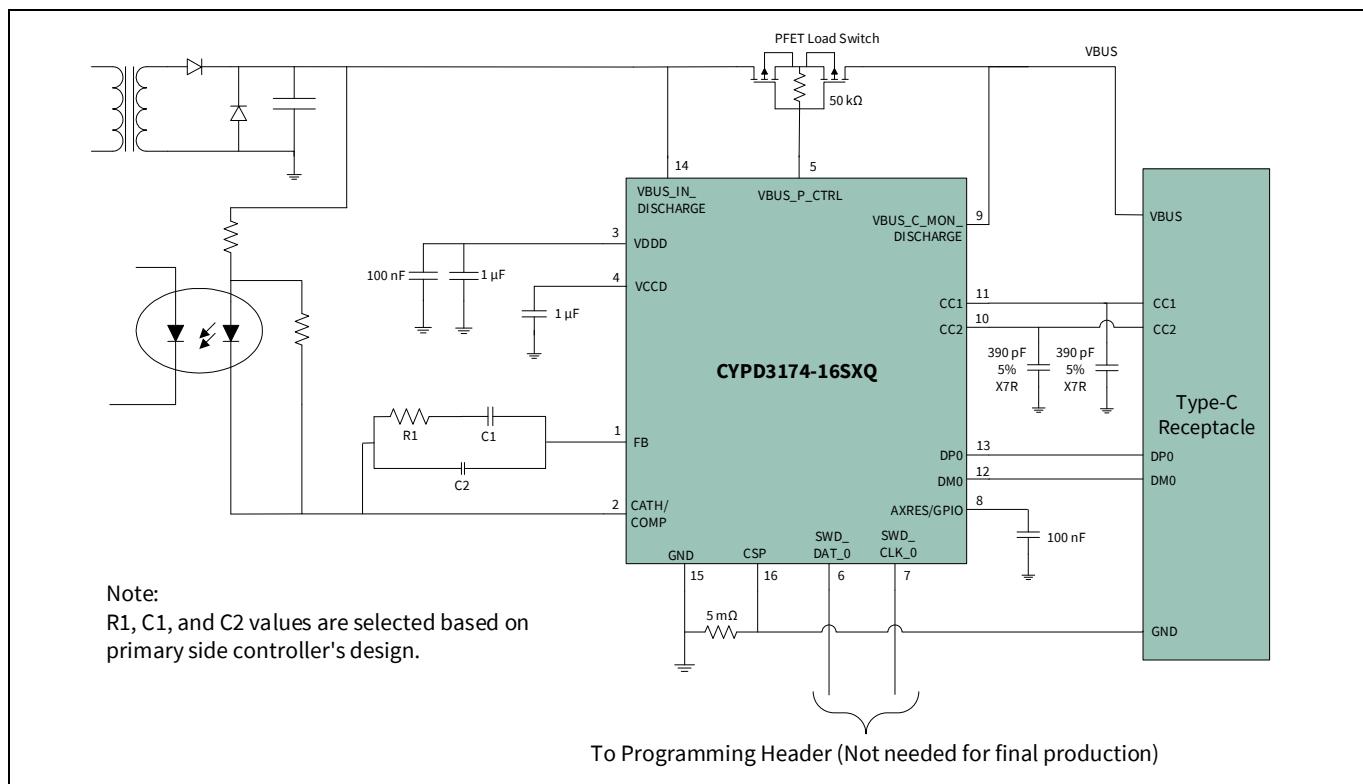

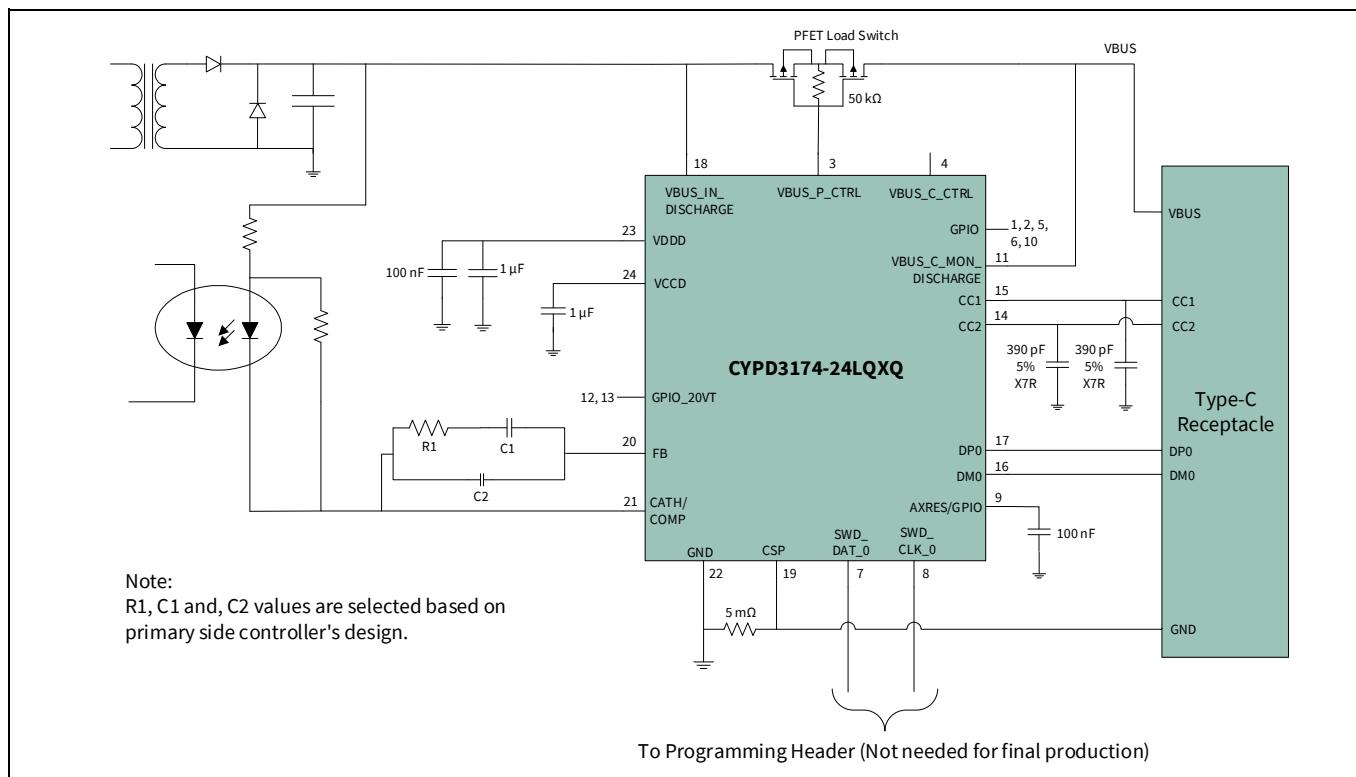

**Figure 6** と **Figure 7** に、それぞれ 16 ピン SOIC と 24 ピン QFN 製品を使用した光カプラ フィードバック制御付き CCG3PA ベースの PC 電源アダプタのアプリケーション図を示します。光フィードバック電源アダプタでは、CCG3PA はシャントレギュレータを実装しており、プライマリ コントローラーへのフィードバックは光カプラを介して行われます。CATH 経路を流れる電流は、FB ピンと内部バンドギャップリファレンス電圧の電位差に比例します。デフォルト 5V の VBUS では、FB ピンは内部 VBUS 抵抗分割器によって、バンドギャップリファレンス電圧でセットされた電圧に保持されます。

VBUS をデフォルトの 5V から変更する必要がある場合、CCG3PA は内部 IDAC と誤差アンプを使用して比例電流を CATH ピンを介して引き出します。したがって、これは光カプラを介してプライマリ コントローラーにカップリングされます。

**Figure 6** 光カプラ フィードバック制御付き CCG3PA ベースの電源アダプタ アプリケーション

(16 ピン SOIC デバイス )

## アプリケーション図

**Figure 7** 光力プラフィードバック制御付き CCG3PA ベースの電源アダプタ アプリケーション

(24 ピン QFN デバイス)

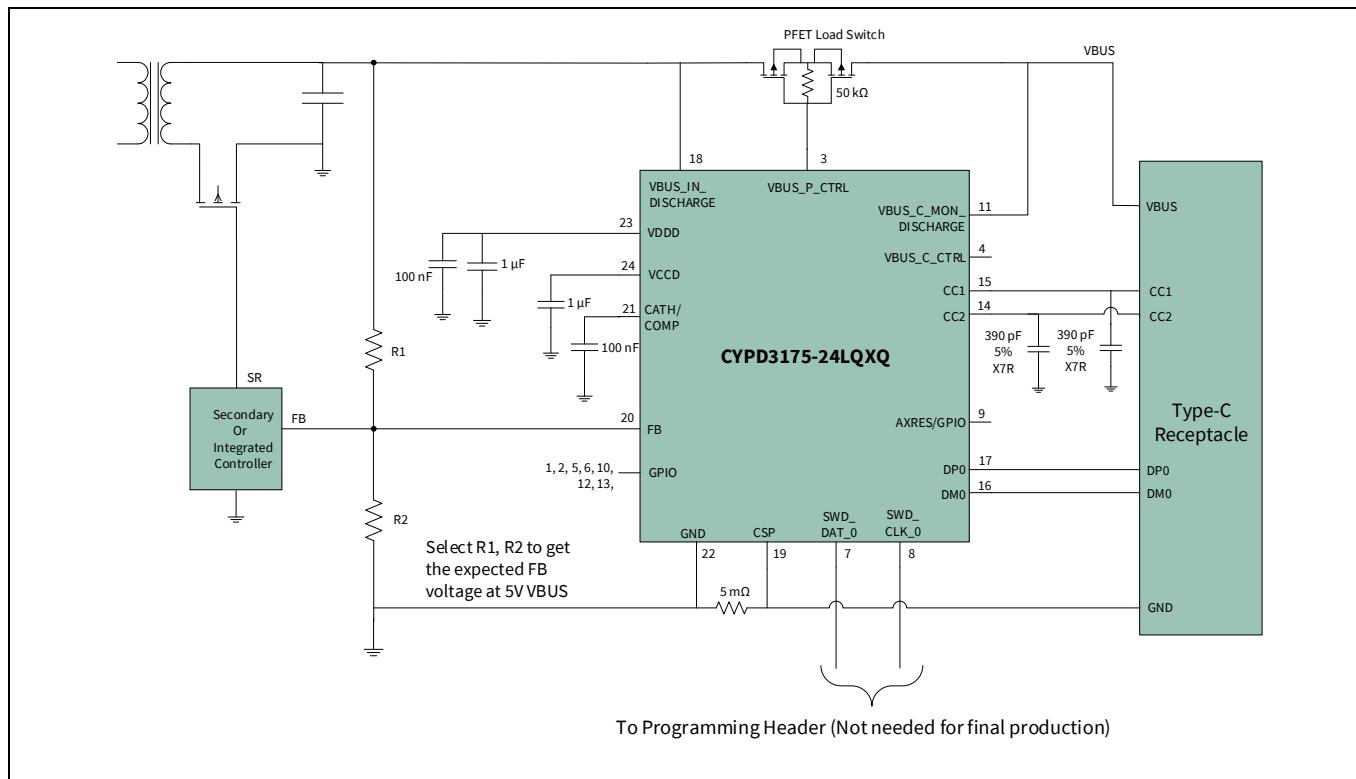

**Figure 8** に、ダイレクトフィードバック制御を備えた CCG3PA ベースの電源アダプタのアプリケーション図を示します。このアプリケーションでは VBUS は一定の電圧に維持されます。電源投入時の VBUS のデフォルト値(通常は 5V)は、セカンダリコントローラーが期待する電圧に FB ノードを設定する適切な抵抗分割器を選択することによって設定されます。

フィードバックノードは、内部 IDAC を使用して調整されます。Vbus 電圧を変更する必要がある時も、CCG3PA は必要な電圧変化の量に応じてフィードバックノードで比例電流をソースまたはシンクします。

## アプリケーション図

Figure 8 ダイレクトフィードバック制御付き CCG3PA ベースの電源アダプタ アプリケーション

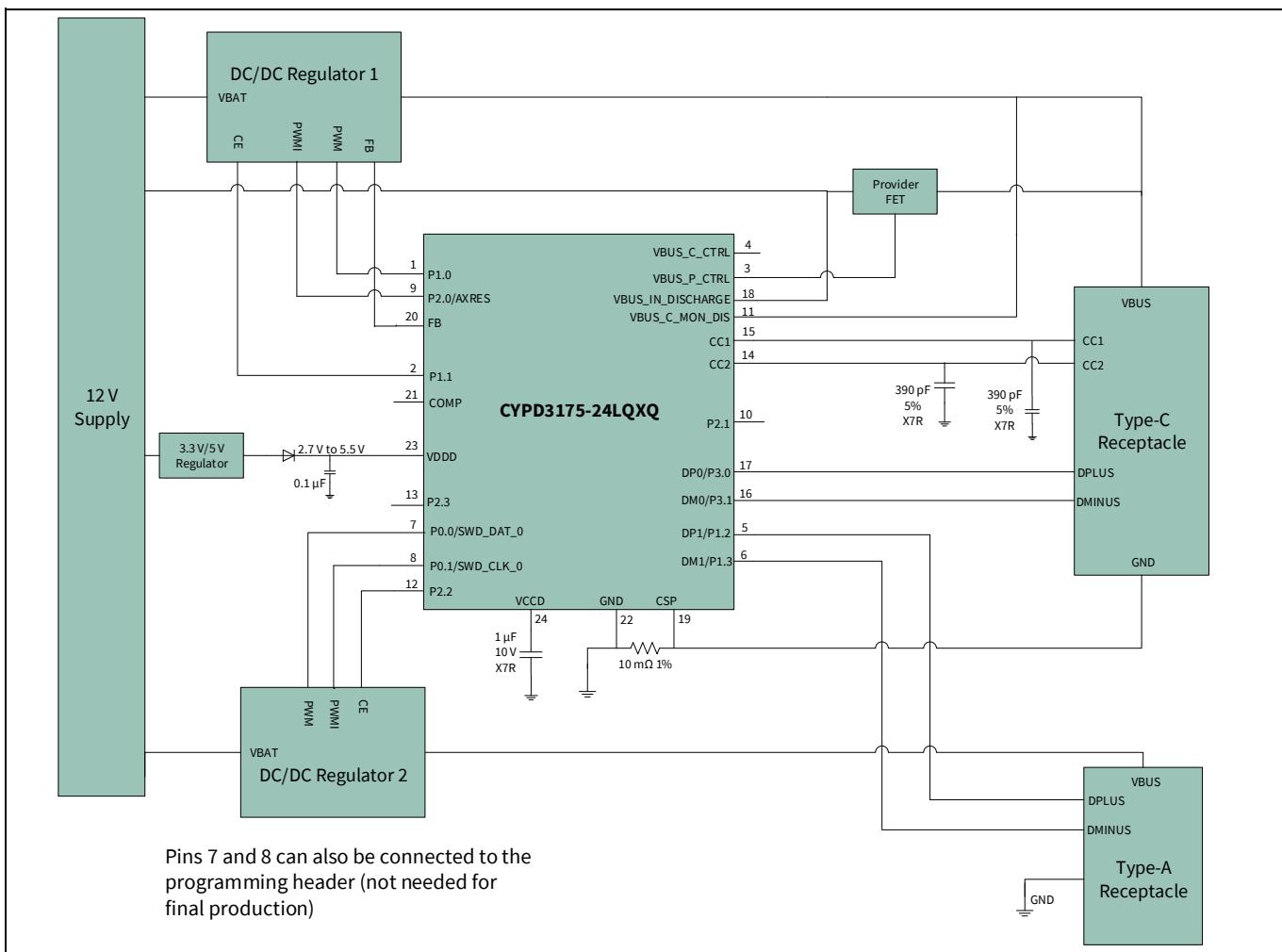

Figure 9 に、2 ポート車載充電器の直接フィードバック制御を備えた CCG3PA ベースの電源アダプタのアプリケーション図を示します。車載充電器アプリケーションは、Type-C と Type-A ポートに接続されたポータブルデバイスを同時に充電できます。Type-C ポートは USB PD 3.1, QC 4.0, Apple Charging 2.4A, および AFC をサポートします。Type-A ポートは QC 3.0, Apple Charging, および AFC をサポートします。

## アプリケーション図

**Figure 9 2ポート車載充電器用の直接フィードバック制御を備えた CCG3PA ベースの電源アダプタ アプリケーション**

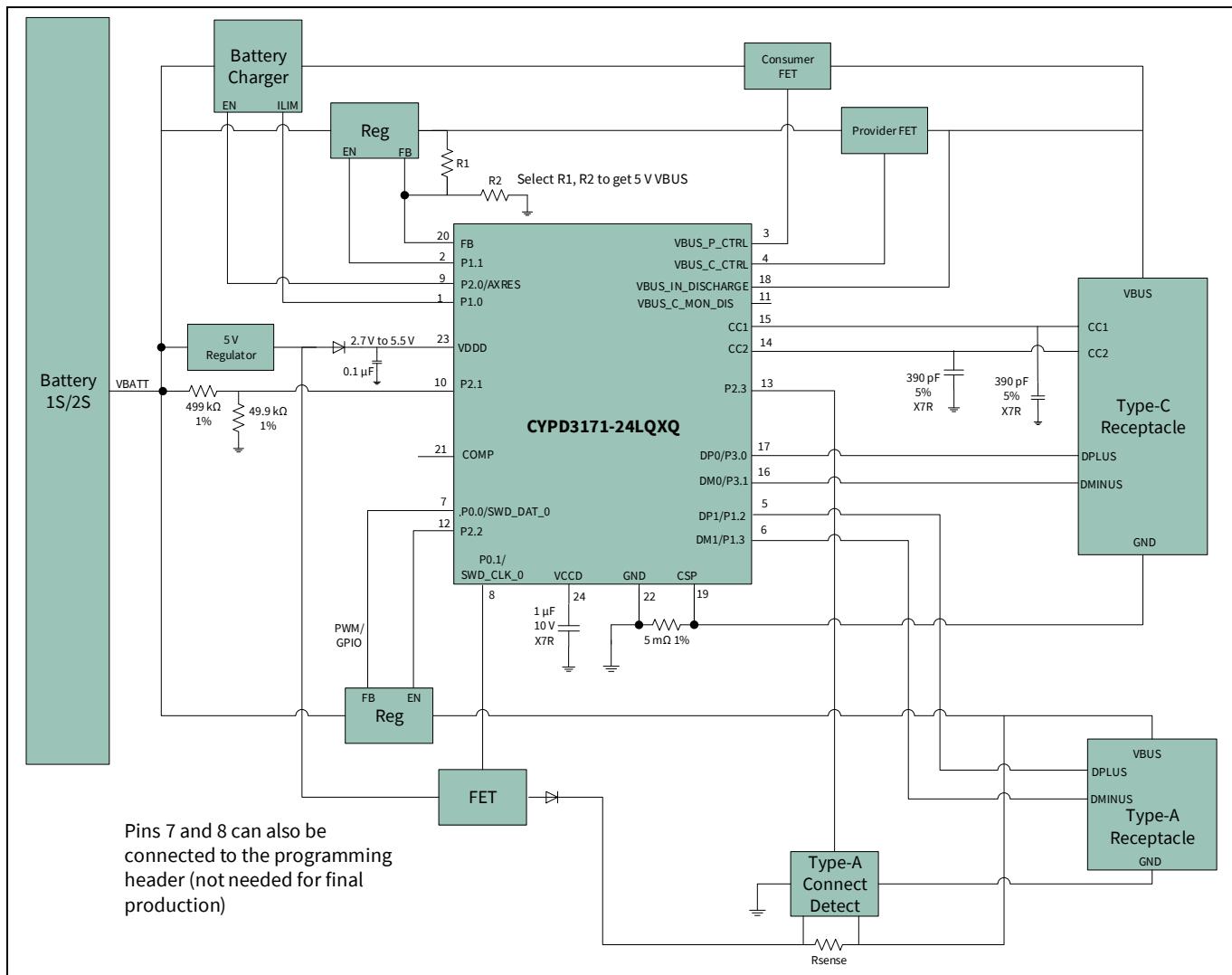

**Figure 10** に、CCG3PA ベースのパワー バンク アプリケーション図を示します。これは CCG3PA デバイスを使用したデュアルポート パワー バンクの実装を示します。パワー バンク アプリケーションは、Type-C と Type-A ポートに接続されたポータブル デバイスを同時に充電できます。Type-C ポートは USB PD 3.1, QC 4.0, Apple Charging 2.4A、および AFC をサポートする設定ができます。Type-A ポートは QC3.0, Apple Charging、および AFC をサポートする設定ができます。

バッテリは、Type-C および USB PD 電源アダプタまたは BC1.2 電源アダプタから充電できます。

## アプリケーション図

Figure 10 CCG3PA のパワー バンク アプリケーション図

電気的仕様

## 6 電気的仕様

### 6.1 絶対最大定格

Table 4 絶対最大定格

| パラメーター                | 説明                                                                                | Min   | Typ | Max               | 単位 | 詳細 / 条件                                              |

|-----------------------|-----------------------------------------------------------------------------------|-------|-----|-------------------|----|------------------------------------------------------|

| $V_{BUS\_MAX}$        | $V_{BUS\_IN\_DISCHARGE}$ と $V_{BUS\_C\_MON\_DISCHARGE}$ ピンの $V_{SS}$ を基準にした最大電源電圧 | -     | -   | 30                | V  |                                                      |

| $V_{DDD\_MAX}$        | $V_{SS}$ を基準にした最大電源電圧                                                             | -     | -   | 6                 | V  | 絶対最大値                                                |

| $V_{CC\_PIN\_ABS}$    | 該当デバイスにおける CC1 と CC2 ピンおよび P2.2 と P2.3 ポートピンの最大電圧                                 | -     | -   | 22 <sup>[6]</sup> | V  |                                                      |

| $V_{GPIO\_ABS}$       | GPIO 電圧                                                                           | -0.5  | -   | $V_{DDD} + 0.5$   | V  |                                                      |

| $I_{GPIO\_ABS}$       | GPIO ごとの最大電流                                                                      | -25   | -   | 25                | mA |                                                      |

| $I_{GPIO\_injection}$ | GPIO 注入電流, $V_{IH} > V_{DDD}$ の場合は Max, $V_{IL} < V_{SS}$ の場合は Min                | -0.5  | -   | 0.5               | mA | 絶対最大値, ピンごとの注入された電流                                  |

| $V_{GPIO\_OVT\_ABS}$  | OVT GPIO 電圧                                                                       | -0.5  | -   | 6                 | V  | P0.0 と P0.1 のポートピンに適用                                |

| ESD_HBM               | 静電気放電 (人体モデル)                                                                     | 2200  | -   | -                 | V  | -                                                    |

| ESD_CDM               | 静電気放電 (デバイス帯電モデル)                                                                 | 500   | -   | -                 | V  | -                                                    |

| LU                    | ラッチアップ時のピン電流                                                                      | -100  | -   | 100               | mA | -                                                    |

| ESD_IEC_CON           | 静電気放電 (IEC61000-4-2)                                                              | 8000  | -   | -                 | V  | CC1, CC2, VBUS, P2.2 および P2.3 ピンの接触放電                |

| ESD_IEC_AIR           | 静電気放電 (IEC61000-4-2)                                                              | 15000 | -   | -                 | V  | DPLUS, DMINUS, CC1, CC2, VBUS, P2.2 および P2.3 ピンの空中放電 |

## 注:

6. USB PD 仕様では、VBUS 最大許容電圧は 21.5V です。

Table 5 ピンベースの絶対最大定格

| ピン番号 | ピン名                                 | 絶対最小値 (V) | 絶対最大値 (V)  |

|------|-------------------------------------|-----------|------------|

| 1    | P1.0 <sup>[8, 9]</sup>              | -0.5      | VDDD + 0.5 |

| 2    | P1.1 <sup>[8, 9]</sup>              | -0.5      | VDDD + 0.5 |

| 3    | VBUS_P_CTRL <sup>[7]</sup>          | -0.3      | VBUS_MAX   |

| 4    | VBUS_C_CTRL <sup>[7]</sup>          | -0.3      | VBUS_MAX   |

| 5    | DP1/P1.2 <sup>[8, 9]</sup>          | -0.5      | VDDD + 0.5 |

| 6    | DM1/P1.3 <sup>[8, 9]</sup>          | -0.5      | VDDD + 0.5 |

| 7    | SWD_DAT_0/P0.0 <sup>[8]</sup>       | -0.5      | 6          |

| 8    | SWD_CLK_0/P0.1 <sup>[8]</sup>       | -0.5      | 6          |

| 9    | AXRES*/P2.0 <sup>[8, 9]</sup>       | -0.5      | VDDD + 0.5 |

| 10   | P2.1 <sup>[8, 9]</sup>              | -0.5      | VDDD + 0.5 |

| 11   | VBUS_C_MON_DISCHARGE <sup>[7]</sup> | -0.5      | VBUS_MAX   |

| 12   | SWD_DAT_1/P2.3/SBU <sup>[8]</sup>   | -0.5      | 22         |

| 13   | SWD_CLK_1/P2.2/SBU <sup>[8]</sup>   | -0.5      | 22         |

| 14   | CC1 <sup>[8]</sup>                  | -0.5      | 22         |

| 15   | CC2 <sup>[8]</sup>                  | -0.5      | 22         |

| 16   | DP0/P3.1 <sup>[8, 9]</sup>          | -0.5      | VDDD + 0.5 |

| 17   | DM0/P3.0 <sup>[8, 9]</sup>          | -0.5      | VDDD + 0.5 |

| 18   | VBUS_IN/ VBUS_IN_DISCHARGE          | -0.5      | VBUS_MAX   |

| 19   | CSP <sup>[8, 9]</sup>               | -0.5      | VDDD + 0.5 |

| 20   | FB <sup>[8, 9]</sup>                | -0.5      | VDDD + 0.5 |

| 21   | CATH/COMP <sup>[7]</sup>            | -0.5      | VBUS_MAX   |

| 22   | GND                                 | 0         | 0          |

| 23   | VDDD                                | -0.5      | 6          |

| 24   | VCCD                                | -0.5      | 2.3        |

## 注:

7. VBUS が動作最大値以下であれば、スタティック /DC 入力に最小限の制限をかけます。

8. VDDD が動作最大値以下であれば、スタティック /DC 入力に最小限の制限をかけます。

9. 最大 6V。

電気的仕様

## 6.2 デバイス レベルの仕様

特記されていない限り、すべての仕様は  $-40^{\circ}\text{C} \leq T_A \leq 105^{\circ}\text{C}$  および  $T_J \leq 120^{\circ}\text{C}$  の条件で有効です。

Table 6 DC 仕様

| 仕様 ID       | パラメーター               | 説明                                              | Min | Typ | Max  | 単位            | 詳細 / 条件                                                             |

|-------------|----------------------|-------------------------------------------------|-----|-----|------|---------------|---------------------------------------------------------------------|

| SID.PWR#2   | $V_{\text{DDD}}$     | 電源入力電圧                                          | 2.7 | -   | 5.5  | V             | シンク モード,<br>$-40^{\circ}\text{C} \leq T_A \leq 105^{\circ}\text{C}$ |

| SID.PWR#2_A | $V_{\text{DDD}}$     | 電源入力電圧                                          | 3.0 | -   | 5.5  | V             | ソース モード,<br>$-40^{\circ}\text{C} \leq T_A \leq 105^{\circ}\text{C}$ |

| SID.PWR#3   | $V_{\text{BUS\_IN}}$ | 電源入力電圧                                          | 3.0 | -   | 24.5 | V             | $-40^{\circ}\text{C} \leq T_A \leq 105^{\circ}\text{C}$             |

| SID.PWR#5   | $V_{\text{CCD}}$     | コアロジック用の出力電圧                                    | -   | 1.8 | -    | V             | -                                                                   |

| SID.PWR#13  | $C_{\text{exc}}$     | $V_{\text{DDD}}$ 用電源デカップリングコンデンサ                | 0.8 | 1   | -    | $\mu\text{F}$ | X5R セラミックまたはこれより良質のもの                                               |

| SID.PWR#14  | $C_{\text{exv}}$     | $V_{\text{BUS\_IN\_DISHCARGE}}$ 用電源デカップリングコンデンサ | -   | 0.1 | -    | $\mu\text{F}$ | X5R セラミックまたはこれより良質のもの                                               |

アクティブ モード。Typ 値は  $V_{\text{DDD}} = 5.0\text{V}$  または  $V_{\text{BUS}} = 5.0\text{V}$  および  $T_A = 25^{\circ}\text{C}$  の条件で測定

|           |                    |                                               |   |    |   |    |                                                                                                                                                                                                 |

|-----------|--------------------|-----------------------------------------------|---|----|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SID.PWR#8 | $I_{\text{DD\_A}}$ | $V_{\text{BUS}}$ または $V_{\text{DDD}}$ からの供給電流 | - | 10 | - | mA | $V_{\text{DDD}} = 5\text{V}$ または $V_{\text{BUS}} = 5\text{V}$ , $T_A = 25^{\circ}\text{C}$ 。<br>CC1/CC2 が Tx または Rx, I/O ソース電流なし, 2 個の SCB が 1Mbps で動作,<br>EA/ADC/CSA/UVOV がオン, CPU が 24MHz で動作 |

|-----------|--------------------|-----------------------------------------------|---|----|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

スリープ モード。Typ 値は  $V_{\text{DD}} = 3.3\text{V}$  および  $T_A = 25^{\circ}\text{C}$  の条件で測定

|        |                    |                                                  |   |   |   |    |                                                                                                                        |

|--------|--------------------|--------------------------------------------------|---|---|---|----|------------------------------------------------------------------------------------------------------------------------|

| SID25A | $I_{\text{DD\_S}}$ | CC, I <sup>2</sup> C, WDT ウェイクアップがオン。IMO が 24MHz | - | 3 | - | mA | $V_{\text{DDD}} = 3.3\text{V}$ , $T_A = 25^{\circ}\text{C}$ ,<br>CPU を除くすべてのブロックがオン, CC IO がオン,<br>EA/ADC/CSA/UVOV がオン |

|--------|--------------------|--------------------------------------------------|---|---|---|----|------------------------------------------------------------------------------------------------------------------------|

ディープスリープ モード。Typ 値は  $T_A = 25^{\circ}\text{C}$  の条件で測定。

|              |                             |                                                                                  |   |     |   |               |                                                                                                                                                   |

|--------------|-----------------------------|----------------------------------------------------------------------------------|---|-----|---|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| SID_PA_DS_UA | $I_{\text{DD\_PA\_DS\_UA}}$ | $V_{\text{BUS}} = 4.5 \sim 5.5\text{V}$ 。CC 接続, I <sup>2</sup> C, WDT ウェイクアップがオン | - | 100 | - | $\mu\text{A}$ | 電源アダプタ / 充電器アプリケーション<br>$V_{\text{BUS}} = 5\text{V}$ , $T_A = 25^{\circ}\text{C}$ ,<br>Type-C 接続なし。CC 接続, I <sup>2</sup> C および WDT ウェイクアップが有効     |

| SID_PA_DS_A  | $I_{\text{DD\_PA\_DS\_A}}$  | $V_{\text{BUS}} = 3.0 \sim 24.5\text{V}$ 。CC, I <sup>2</sup> C, WDT ウェイクアップが有効   | - | 500 | - | $\mu\text{A}$ | 電源アダプタ / 充電器アプリケーション<br>$V_{\text{BUS}} = 24.5\text{V}$ , $T_A = 25^{\circ}\text{C}$ ,<br>デバイスがディープスリープ モード。接続済み, CC I/O がオン,<br>ADC/CSA/UVOV がオン |

## 電気的仕様

Table 6 DC 仕様 (continued)

| 仕様 ID           | パラメーター                   | 説明                                                                 | Min | Typ | Max | 単位 | 詳細 / 条件                                                                                                                 |

|-----------------|--------------------------|--------------------------------------------------------------------|-----|-----|-----|----|-------------------------------------------------------------------------------------------------------------------------|

| SID_PB_DS_UA    | $I_{DD\_PB\_DS\_UA}$     | $V_{DDD} = 3.0 \sim 5.5V$ 。CC 接続, I <sup>2</sup> C, WDT ウェイクアップが有効 | -   | 100 | -   | μA | パワーバンク アプリケーション<br>電源 = $V_{DDD} = 5V$ , $T_A = 25^\circ C$ ,<br>Type-C 接続なし。CC 接続, I <sup>2</sup> C および WDT ウェイクアップが有効 |

| SID_PB_DS_A_SRC | $I_{DD\_PB\_DS\_A\_SRC}$ | $V_{DDD} = 3.0 \sim 5.5V$ 。CC, I <sup>2</sup> C, WDT ウェイクアップが有効    | -   | 500 | -   | μA | パワーバンク ソース アプリケーション<br>$V_{DDD} = 5V$ , $T_A = 25^\circ C$ ,<br>デバイスがディープスリープモード。接続済, CC I/O がオン, ADC/CSA/UVOV がオン      |

| SID_PB_DS_A_SNK | $I_{DD\_PB\_DS\_A\_SNK}$ | $V_{BUS} = 4.0 \sim 24.5V$ 。CC, I <sup>2</sup> C, WDT ウェイクアップが有効   | -   | 500 | -   | μA | パワーバンク シンク アプリケーション<br>$V_{BUS} = 24.5V$ , $T_A = 25^\circ C$ ,<br>デバイスがディープスリープモード。接続済, CC I/O がオン, ADC/CSA/UVOV がオン   |

Table 7 AC 仕様

(特性評価で保証)

| 仕様 ID       | パラメーター            | 説明                                          | Min | Typ | Max | 単位  | 詳細 / 条件        |

|-------------|-------------------|---------------------------------------------|-----|-----|-----|-----|----------------|

| SID.CLK#4   | $F_{CPU}$         | CPU 入力周波数                                   | DC  | -   | 48  | MHz | すべての $V_{DDD}$ |

| SID.PWR#17  | $T_{SLEEP}$       | スリープモードからの復帰時間                              | -   | 0   | -   | μs  | -              |

| SID.PWR#18  | $T_{DEEPSLEEP}$   | ディープスリープモードからの復帰時間                          | -   | -   | 35  | μs  | -              |

| SYS.FES#1   | $T_{PWR\_RDY}$    | 電源投入から「I <sup>2</sup> C/CC コマンドが受信できる」までの時間 | -   | 5   | 25  | ms  | -              |

| SID.PWR#18A | $T_{POR\_HIZ\_T}$ | 電源投入時の I/O 初期化時間                            | -   | 3   | -   | ms  | -              |

電気的仕様

### 6.2.1 I/O

Table 8 I/O の DC 仕様

| 仕様 ID       | パラメーター             | 説明                                  | Min                   | Typ | Max                  | 単位 | 詳細 / 条件                                                                     |

|-------------|--------------------|-------------------------------------|-----------------------|-----|----------------------|----|-----------------------------------------------------------------------------|

| SID.GIO#37  | $V_{IH\_CMOS}$     | 入力電圧 HIGH 閾値                        | $0.7 \times V_{DDD}$  | -   | -                    | V  | CMOS 入力                                                                     |

| SID.GIO#38  | $V_{IL\_CMOS}$     | 入力電圧 LOW 閾値                         | -                     | -   | $0.3 \times V_{DDD}$ | V  | CMOS 入力                                                                     |

| SID.GIO#39  | $V_{IH\_VDDD2.7-}$ | LVTTL 入力, $V_{DDD} < 2.7V$          | $0.7 \times V_{DDD}$  | -   | -                    | V  | -                                                                           |

| SID.GIO#40  | $V_{IL\_VDDD2.7-}$ | LVTTL 入力, $V_{DDD} < 2.7V$          | -                     | -   | $0.3 \times V_{DDD}$ | V  | -                                                                           |

| SID.GIO#41  | $V_{IH\_VDDD2.7+}$ | LVTTL 入力, $V_{DDD} \geq 2.7V$       | 2.0                   | -   | -                    | V  | -                                                                           |

| SID.GIO#42  | $V_{IL\_VDDD2.7+}$ | LVTTL 入力, $V_{DDD} \geq 2.7V$       | -                     | -   | 0.8                  | V  | -                                                                           |

| SID.GIO#33  | $V_{OH\_3V}$       | 出力 HIGH 電圧                          | $V_{DDD} - 0.6$       | -   | -                    | V  | $3V V_{DDD}$ の時 $I_{OH} = 4mA$                                              |

| SID.GIO#36  | $V_{OL\_3V}$       | 出力 LOW 電圧                           | -                     | -   | 0.6                  | V  | $3V V_{DDD}$ の時 $I_{OL} = 10mA$                                             |

| SID.GIO#5   | $R_{PU}$           | プルアップ抵抗値                            | 3.5                   | 5.6 | 8.5                  | kΩ | $+25^{\circ}C T_A$ , すべての $V_{DDD}$                                         |

| SID.GIO#6   | $R_{PD}$           | プルダウン抵抗値                            | 3.5                   | 5.6 | 8.5                  | kΩ | $+25^{\circ}C T_A$ , すべての $V_{DDD}$                                         |

| SID.GIO#16  | $I_{IL}$           | 入力リーコンデンサ電流 ( 絶対値 )                 | -                     | -   | 2                    | nA | $+25^{\circ}C T_A$ , $3V V_{DDD}$                                           |

| SID.GIO#17  | $C_{PIN\_A}$       | ピン最大負荷容量                            | -                     | -   | 22                   | pF | DP0, DM0, DP1, DMI ピンの容量。特性評価で保証                                            |

| SID.GIO#17A | $C_{PIN}$          | ピン最大負荷容量                            | -                     | 3   | 7                    | pF | $-40^{\circ}C \sim +85^{\circ}C T_A$ , すべての $V_{DDD}$ , その他すべての I/O。特性評価で保証 |

| SID.GIO#43  | $V_{HYSTTL}$       | 入力ヒステリシス, LVTTL $V_{DDD} > 2.7V$    | 15                    | 40  | -                    | mV | 特性評価で保証                                                                     |

| SID.GIO#44  | $V_{HYSCMOS}$      | 入力ヒステリシス CMOS                       | $0.05 \times V_{DDD}$ | -   | -                    | mV | $V_{DDD} < 4.5V$ 。特性評価で保証                                                   |

| SID69       | $I_{DIODE}$        | 保護ダイオードを通って $V_{DDD}/V_{SS}$ に流れる電流 | -                     | -   | 100                  | μA | 設計で保証                                                                       |

| SID.GIO#45  | $I_{TOT\_GPIO}$    | 最大の合計シンク電流                          | -                     | -   | 85                   | mA | 設計で保証                                                                       |

| <b>OVT</b>  |                    |                                     |                       |     |                      |    |                                                                             |

| SID.GIO#46  | $I_{IHS}$          | パッド電圧 > OVT 入力の $V_{DDD}$ の時の入力電流   | -                     | -   | 10.00                | μA | $I^2C$ 仕様による                                                                |

Table 9 I/O の AC 仕様

( 特性評価で保証 )

| 仕様 ID | パラメーター      | 説明                  | Min | Typ | Max | 単位 | 詳細 / 条件                             |

|-------|-------------|---------------------|-----|-----|-----|----|-------------------------------------|

| SID70 | $T_{RISEF}$ | 高速ストロング モードでの立ち上り時間 | 2   | -   | 12  | ns | $3.3V V_{DDD}$ , $C_{load} = 25 pF$ |

| SID71 | $T_{FALLF}$ | 高速ストロング モードでの立ち下り時間 | 2   | -   | 12  | ns | $3.3V V_{DDD}$ , $C_{load} = 25 pF$ |

## 電気的仕様

**Table 10** GPIO\_20VT の DC 仕様 (ポートピン P2.2 と P2.3 のみに適用)

(特性評価で保証)

| 仕様 ID#           | パラメーター              | 説明                                                              | Min  | Typ | Max | 単位 | 詳細 / 条件                                                         |

|------------------|---------------------|-----------------------------------------------------------------|------|-----|-----|----|-----------------------------------------------------------------|

| SID.GPIO_20VT#4  | GPIO_20VT_I_LU      | GPIO_20VT ラッチアップ電流制限                                            | -140 | -   | 140 | mA | 入力または出力, ピン間, ピンと電源間を流れる Max/min 電流                             |

| SID.GPIO_20VT#5  | GPIO_20VT_R_PU      | GPIO_20VT プルアップ抵抗値                                              | 1    | -   | 25  | kΩ | +25°C T <sub>A</sub> , GPIO_20VT_Voh(min) が 1.4V                |

| SID.GPIO_20VT#6  | GPIO_20VT_R_PD      | GPIO_20VT プルダウン抵抗値                                              | 2.5  | -   | 20  | kΩ | +25°C T <sub>A</sub> , V <sub>DDD</sub> が 1.4V                  |

| SID.GPIO_20VT#16 | GPIO_20VT_II_L      | GPIO_20VT 入力リーケ電流 (絶対値)                                         | -    | -   | 2   | nA | +25°C T <sub>A</sub> , V <sub>DDD</sub> が 3V                    |

| SID.GPIO_20VT#17 | GPIO_20VT_C_PIN     | GPIO_20VT ピン静電容量                                                | 15   | -   | 25  | pF | -40°C ~ +85°C T <sub>A</sub> , すべての V <sub>DDD</sub> , F = 1MHz |

| SID.GPIO_20VT#36 | GPIO_20VT_Vol       | GPIO_20VT 出力 LOW 電圧                                             | -    | -   | 0.4 | V  | I <sub>OL</sub> = 2mA                                           |

| SID.GPIO_20VT#41 | GPIO_20VT_Vih_LVTTL | GPIO_20VT LVTTL 入力 HIGH 電圧                                      | 2    | -   | -   | V  | V <sub>DDD</sub> ≥ 2.7V                                         |

| SID.GPIO_20VT#42 | GPIO_20VT_Vil_LVTTL | GPIO_20VT LVTTL 入力 LOW 電圧                                       | -    | -   | 0.8 | V  | V <sub>DDD</sub> ≥ 2.7V                                         |

| SID.GPIO_20VT#43 | GPIO_20VT_Vhysttl   | GPIO_20VT 入力ヒステリシス LVTTL                                        | 15   | 40  | -   | mV | V <sub>DDD</sub> ≥ 2.7V                                         |

| SID.GPIO_20VT#69 | GPIO_20VT_IDIODE    | 保護ダイオードを通つて V <sub>DDD</sub> /V <sub>SS</sub> に流れる GPIO_20VT 電流 | -    | -   | 100 | μA |                                                                 |

**Table 11** GPIO\_20VT の AC 仕様 (ポートピン P2.2 と P2.3 のみに適用)

(特性評価で保証)

| 仕様 ID#           | パラメーター           | 説明                            | Min | Typ | Max | 単位 | 詳細 / 条件                                          |

|------------------|------------------|-------------------------------|-----|-----|-----|----|--------------------------------------------------|

| SID.GPIO_20VT#70 | GPIO_20VT_TriseF | 高速ストロングモードでの GPIO_20VT 立ち上り時間 | 1   | -   | 45  | ns | すべての V <sub>DDD</sub> , C <sub>load</sub> = 25pF |

| SID.GPIO_20VT#71 | GPIO_20VT_TfallF | 高速ストロングモードでの GPIO_20VT 立ち下り時間 | 2   | -   | 15  | ns | すべての V <sub>DDD</sub> , C <sub>load</sub> = 25pF |

電気的仕様

## 6.3 デジタルペリフェラル

次の仕様は、タイマー モードでの タイマー / カウンター / PWM (TCPWM) ペリフェラルに適用されます。

### 6.3.1 GPIO ピン用のパルス幅変調 (PWM)

Table 12 PWM の AC 仕様

(特性評価で保証)

| 仕様 ID        | パラメーター          | 説明         | Min     | Typ | Max   | 単位  | 詳細 / 条件                                                                |

|--------------|-----------------|------------|---------|-----|-------|-----|------------------------------------------------------------------------|

| SID.TCPWM.3  | $T_{TCPWMFREQ}$ | 動作周波数      | -       | -   | $F_c$ | MHz | $F_c \text{ max} = \text{CLK\_SYS}$ 。<br>$\text{Max} = 48\text{MHz}$ . |

| SID.TCPWM.4  | $T_{PWMENEXT}$  | 入力トリガ パルス幅 | $2/F_c$ | -   | -     | ns  | すべてのトリガ イベント                                                           |

| SID.TCPWM.5  | $T_{PWMEXT}$    | 出力トリガ パルス幅 | $2/F_c$ | -   | -     | ns  | オーバーフロー, アンダーフロー, および CC (カウンター = 比較値) 出力の最小値                          |

| SID.TCPWM.5A | $T_{CRES}$      | カウンターの分解能  | $1/F_c$ | -   | -     | ns  | 逐次カウント同士間の最小時間                                                         |

| SID.TCPWM.5B | $PWM_{RES}$     | PWM 分解能    | $1/F_c$ | -   | -     | ns  | PWM 出力の最小パルス幅                                                          |

| SID.TCPWM.5C | $Q_{RES}$       | 直交位相入力分解能  | $1/F_c$ | -   | -     | ns  | 直角位相入力同士間の最小パルス幅                                                       |

### 6.3.2 I<sup>2</sup>C

Table 13 固定 I<sup>2</sup>C の DC 仕様

(特性評価で保証)

| 仕様 ID  | パラメーター     | 説明                        | Min | Typ | Max | 単位 | 詳細 / 条件 |

|--------|------------|---------------------------|-----|-----|-----|----|---------|

| SID149 | $I_{I2C1}$ | 100kHz でのブロック消費電流         | -   | -   | 100 | μA | -       |

| SID150 | $I_{I2C2}$ | 400kHz でのブロック消費電流         | -   | -   | 135 | μA | -       |

| SID151 | $I_{I2C3}$ | 1Mbps でのブロック消費電流          | -   | -   | 310 | μA | -       |

| SID152 | $I_{I2C4}$ | $I^2C$ がディープスリープモードで有効の場合 | -   | 1.4 | -   | μA | -       |

Table 14 固定 I<sup>2</sup>C の AC 仕様

(特性評価で保証)

| 仕様 ID  | パラメーター     | 説明     | Min | Typ | Max | 単位   | 詳細 / 条件 |

|--------|------------|--------|-----|-----|-----|------|---------|

| SID153 | $F_{I2C1}$ | ビットレート | -   | -   | 1   | Mbps | -       |

Table 15 固定 UART の DC 仕様

(特性評価で保証)

| 仕様 ID  | パラメーター      | 説明                  | Min | Typ | Max | 単位 | 詳細 / 条件 |

|--------|-------------|---------------------|-----|-----|-----|----|---------|

| SID160 | $I_{UART1}$ | 100kbps でのブロック消費電流  | -   | -   | 20  | μA | -       |

| SID161 | $I_{UART2}$ | 1000kbps でのブロック消費電流 | -   | -   | 312 | μA | -       |

Table 16 固定 UART の AC 仕様

(特性評価で保証)

| 仕様 ID  | パラメーター     | 説明     | Min | Typ | Max | 単位   | 詳細 / 条件 |

|--------|------------|--------|-----|-----|-----|------|---------|

| SID162 | $F_{UART}$ | ビットレート | -   | -   | 1   | Mbps | -       |

電気的仕様

**Table 17 固定 SPI の DC 仕様**

(特性評価で保証)

| 仕様 ID  | パラメーター            | 説明               | Min | Typ | Max | 単位            | 詳細 / 条件 |

|--------|-------------------|------------------|-----|-----|-----|---------------|---------|

| SID163 | $I_{\text{SPI1}}$ | 1Mb/s でのブロック消費電流 | -   | -   | 360 | $\mu\text{A}$ | -       |

| SID164 | $I_{\text{SPI2}}$ | 4Mb/s でのブロック消費電流 | -   | -   | 560 | $\mu\text{A}$ | -       |

| SID165 | $I_{\text{SPI3}}$ | 8Mb/s でのブロック消費電流 | -   | -   | 600 | $\mu\text{A}$ | -       |

**Table 18 固定 SPI の AC 仕様**

(特性評価で保証)

| 仕様 ID  | パラメーター           | 説明                               | Min | Typ | Max | 単位  | 詳細 / 条件 |

|--------|------------------|----------------------------------|-----|-----|-----|-----|---------|

| SID166 | $F_{\text{SPI}}$ | SPI 動作周波数 (マスター ; 6 倍オーバーサンプリング) | -   | -   | 8   | MHz | -       |

**Table 19 固定 SPI マスター モードの AC 仕様**

(特性評価で保証)

| 仕様 ID  | パラメーター           | 説明                       | Min | Typ | Max | 単位 | 詳細 / 条件                |

|--------|------------------|--------------------------|-----|-----|-----|----|------------------------|

| SID167 | $T_{\text{DMO}}$ | SClock 駆動エッジ後の MOSI 有効時間 | -   | -   | 15  | ns | -                      |

| SID168 | $T_{\text{DSI}}$ | SClock 取得エッジ前の MISO 有効時間 | 20  | -   | -   | ns | フルクロック, MISO の遅いサンプリング |

| SID169 | $T_{\text{HMO}}$ | 直前の MOSI データホールド時間       | 0   | -   | -   | ns | スレーブ取得エッジを基準にする        |

**Table 20 固定 SPI スレーブ モードの AC 仕様**

(特性評価で保証)

| 仕様 ID   | パラメーター                      | 説明                                    | Min | Typ | Max                            | 単位 | 詳細 / 条件                             |

|---------|-----------------------------|---------------------------------------|-----|-----|--------------------------------|----|-------------------------------------|

| SID170  | $T_{\text{DMI}}$            | Sclock 取得エッジ前の MOSI 有効時間              | 40  | -   | -                              | ns | -                                   |

| SID171  | $T_{\text{DSO}}$            | Sclock 駆動エッジ後の MISO 有効時間              | -   | -   | $42 + 3 \times T_{\text{CPU}}$ | ns | $T_{\text{CPU}} = 1/F_{\text{CPU}}$ |

| SID171A | $T_{\text{DSO\_EXT}}$       | 外部クロック モードでの Sclock 駆動エッジ後の MISO 有効時間 | -   | -   | 48                             | ns | -                                   |

| SID172  | $T_{\text{HSO}}$            | 直前の MISO データホールド時間                    | 0   | -   | -                              | ns | -                                   |

| SID172A | $T_{\text{SSEL}\text{SCK}}$ | SSEL 有効から最初の SCK 有効エッジまでの時間           | 100 | -   | -                              | ns | -                                   |

電気的仕様

## 6.4 システムリソース

### 6.4.1 電圧低下 SWD インターフェースのパワーオンリセット (POR)

Table 21 低精度パワーオンリセット (PRES)

(特性評価で保証)

| 仕様 ID  | パラメーター         | 説明                         | Min  | Typ | Max  | 単位 | 詳細 / 条件 |

|--------|----------------|----------------------------|------|-----|------|----|---------|

| SID185 | $V_{RISEIPOR}$ | パワーオンリセット (POR) 立ち上りトリップ電圧 | 0.80 | -   | 1.50 | V  | -       |

| SID186 | $V_{FALLIPOR}$ | POR 立ち下りトリップ電圧             | 0.70 | -   | 1.4  | V  | -       |

Table 22 高精度パワーオンリセット (POR)

(特性評価で保証)

| 仕様 ID  | パラメーター          | 説明                                   | Min  | Typ | Max  | 単位 | 詳細 / 条件 |

|--------|-----------------|--------------------------------------|------|-----|------|----|---------|

| SID190 | $V_{FALLPPOR}$  | アクティブ / スリープモードでの電圧低下検出 (BOD) トリップ電圧 | 1.48 | -   | 1.62 | V  | -       |

| SID192 | $V_{FALLDPSLP}$ | ディープスリープモードでの BOD トリップ電圧             | 1.1  | -   | 1.5  | V  | -       |

Table 23 SWD インターフェース仕様

(特性評価で保証)

| 仕様 ID     | パラメーター            | 説明                             | Min             | Typ | Max             | 単位  | 詳細 / 条件                       |

|-----------|-------------------|--------------------------------|-----------------|-----|-----------------|-----|-------------------------------|

| SID.SWD#1 | $F_{SWDCLK1}$     | $3.3V \leq V_{DDDD} \leq 5.5V$ | -               | -   | 14              | MHz | $SWDCLK \leq 1/3 CPU$ クロック周波数 |

| SID.SWD#2 | $F_{SWDCLK2}$     | $2.7V \leq V_{DDDD} \leq 3.3V$ | -               | -   | 7               | MHz | $SWDCLK \leq 1/3 CPU$ クロック周波数 |

| SID.SWD#3 | $T_{SWDI\_SETUP}$ | $T = 1/f_{SWDCLK}$             | $0.25 \times T$ | -   | -               | ns  | -                             |

| SID.SWD#4 | $T_{SWDI\_HOLD}$  | $T = 1/f_{SWDCLK}$             | $0.25 \times T$ | -   | -               | ns  | -                             |

| SID.SWD#5 | $T_{SWDO\_VALID}$ | $T = 1/f_{SWDCLK}$             | -               | -   | $0.50 \times T$ | ns  | -                             |

| SID.SWD#6 | $T_{SWDO\_HOLD}$  | $T = 1/f_{SWDCLK}$             | 1               | -   | -               | ns  | -                             |

### 6.4.2 内部主発振器

Table 24 IMO の DC 仕様

(特性評価で保証)

| 仕様 ID  | パラメーター     | 説明                | Min | Typ | Max  | 単位      | 詳細 / 条件 |

|--------|------------|-------------------|-----|-----|------|---------|---------|

| SID218 | $I_{IMO1}$ | 48MHz での IMO 動作電流 | -   | -   | 1000 | $\mu A$ | -       |

Table 25 IMO の AC 仕様

| 仕様 ID      | パラメーター           | 説明                                | Min | Typ | Max     | 単位      | 詳細 / 条件                              |

|------------|------------------|-----------------------------------|-----|-----|---------|---------|--------------------------------------|

| SID.CLK#13 | $F_{IMOTOL}$     | 24, 36, および 48MHz での周波数誤差 (トリム済み) | -   | -   | $\pm 2$ | %       | -                                    |

| SID226     | $T_{STARTIMO}$   | IMO 起動時間                          | -   | -   | 7       | $\mu s$ | 特性評価で保証                              |

| SID228     | $T_{JITRMSIMO2}$ | 24MHz での RMS ジッタ                  | -   | 145 | -       | ps      | 特性評価で保証                              |

| SID.CLK#1  | $F_{IMO}$        | IMO 周波数                           | 24  | 36  | 48      | MHz     | 24MHz, 36MHz, 48MHz の 3 つの周波数のみがサポート |

電気的仕様

### 6.4.3 内部低速発振器 - 電源切斷

**Table 26 ILO の DC 仕様**

( 設計で保証 )

| 仕様 ID  | パラメーター        | 説明             | Min | Typ | Max  | 単位      | 詳細 / 条件 |

|--------|---------------|----------------|-----|-----|------|---------|---------|

| SID231 | $I_{ILO1}$    | $I_{LO}$ 動作電流  | -   | 0.3 | 1.05 | $\mu A$ | -       |

| SID233 | $I_{ILOLEAK}$ | $I_{LO}$ リーク電流 | -   | 2   | 15   | nA      | -       |

**Table 27 ILO の AC 仕様**

| 仕様 ID     | パラメーター          | 説明               | Min | Typ | Max | 単位  | 詳細 / 条件 |

|-----------|-----------------|------------------|-----|-----|-----|-----|---------|

| SID234    | $T_{STARTILO1}$ | $I_{LO}$ 起動時間    | -   | -   | 2   | ms  | 特性評価で保証 |

| SID238    | $T_{ILODUTY}$   | $I_{LO}$ デューティー比 | 40  | 50  | 60  | %   | 特性評価で保証 |

| SID.CLK#5 | $F_{ILO}$       | $I_{LO}$ 周波数     | 20  | 40  | 80  | kHz | -       |

**Table 28 PD の DC 仕様**

| 仕様 ID    | パラメーター          | 説明                                           | Min  | Typ | Max   | 単位         | 詳細 / 条件                             |

|----------|-----------------|----------------------------------------------|------|-----|-------|------------|-------------------------------------|

| SID.PD.1 | $R_{p\_std}$    | デフォルト USB 電源用の DFP CC 終端                     | 64   | 80  | 96    | $\mu A$    | -                                   |

| SID.PD.2 | $R_{p\_1.5A}$   | 1.5A 電源用の DFP CC 終端                          | 166  | 180 | 194.4 | $\mu A$    | -                                   |

| SID.PD.3 | $R_{p\_3.0A}$   | 3.0A 電源用の DFP CC 終端                          | 304  | 330 | 356.4 | $\mu A$    | -                                   |

| SID.PD.4 | $R_d$           | UFP CC 終端抵抗                                  | 4.59 | 5.1 | 5.61  | k $\Omega$ | -                                   |

| SID.PD.5 | $R_{d\_DB}$     | CC1 と CC2 上の UFP ( パワーバンク ) デッド バッテリ CC 終端抵抗 | 4.08 | 5.1 | 6.12  | k $\Omega$ | 全電源が 0V および 1.32V が CC1 または CC2 に印加 |

| SID.PD.6 | $V_{gndoffset}$ | BMC レシーバで許容されるグランド オフセット                     | -500 | -   | 500   | mV         | リモート BMC トランスマッタを基準にする              |

**Table 29 LS-CSA 仕様**

| 仕様 ID        | パラメーター              | 説明                                         | Min   | Typ | Max | 単位  | 詳細 / 条件   |

|--------------|---------------------|--------------------------------------------|-------|-----|-----|-----|-----------|

| SID.LSCSA.1  | $C_{in\_inp}$       | CSP 入力静電容量                                 | 7     | -   | 10  | pF  | 特性評価で保証   |

| SID.LSCSA.2  | $C_{sa\_Acc1}$      | CSA 精度 , $5mV < V_{sense} < 10mV$          | -15   | -   | 15  | %   | アクティブ モード |

| SID.LSCSA.3  | $C_{sa\_Acc2}$      | CSA 精度 , $10mV < V_{sense} < 15mV$         | -10   | -   | 10  | %   |           |

| SID.LSCSA.4  | $C_{sa\_Acc3}$      | CSA 精度 , $15mV < V_{sense} < 20mV$         | -6    | -   | 6   | %   |           |

| SID.LSCSA.5  | $C_{sa\_Acc4}$      | CSA 精度 , $20mV < V_{sense} < 30mV$         | -5    | -   | 5   | %   |           |

| SID.LSCSA.6  | $C_{sa\_Acc5}$      | CSA 精度 , $30mV < V_{sense} < 50mV$         | -4    | -   | 4   | %   |           |

| SID.LSCSA.7  | $C_{sa\_Acc6}$      | CSA 精度 , $50mV < V_{sense}$                | -4    | -   | 4   | %   |           |

| SID.LSCSA.8  | $C_{sa\_SCP\_Acc1}$ | CSA SCP 80mV                               | -16.5 | -   | 30  | %   |           |

| SID.LSCSA.9  | $C_{sa\_SCP\_Acc2}$ | CSA SCP 100mV                              | -13.4 | -   | 24  | %   |           |

| SID.LSCSA.10 | $C_{sa\_SCP\_Acc3}$ | CSA SCP 150mV                              | -9.4  | -   | 16  | %   |           |

| SID.LSCSA.11 | $C_{sa\_SCP\_Acc4}$ | CSA SCP 200mV                              | -7.5  | -   | 12  | %   |           |

| SID.LSCSA.12 | $A_v$               | 対応公称ゲイン値 : 5, 10, 20, 35, 50, 75, 125, 150 | 5     | -   | 150 | V/V | -         |

| SID.LSCSA.24 | $A_{v1\_E\_Trim}$   | ゲイン誤差                                      | -3    | -   | 3   | %   | 特性評価で保証   |

| SID.LSCSA.31 | $A_{v\_E\_SCP}$     | SCP 状態のゲイン誤差                               | -3.5  | -   | 3.5 | %   | 特性評価で保証   |

## 電気的仕様

**Table 30 LS-CSA の AC 仕様**

(特性評価で保証)

| 仕様 ID          | パラメーター          | 説明                                  | Min | Typ | Max | 単位 | 詳細 / 条件           |

|----------------|-----------------|-------------------------------------|-----|-----|-----|----|-------------------|

| SID.LSCSA.AC.1 | $T_{OCP\_GPIO}$ | OCP 閾値トリップから出力 GPIO トグルまでの遅延時間      | -   | -   | 20  | μs | P1.0 または P1.1 に適用 |

| SID.LSCSA.AC.2 | $T_{OCP\_Gate}$ | OCP 閾値トリップから外部 PFET パワーゲートオフまでの遅延時間 | -   | -   | 50  | μs | -                 |

| SID.LSCSA.AC.3 | $T_{SCP\_GPIO}$ | SCP 閾値トリップから出力 GPIO トグルまでの遅延時間      | -   | -   | 15  | μs | P1.0 または P1.1 に適用 |

| SID.LSCSA.AC.4 | $T_{SCP\_Gate}$ | SCP 閾値トリップから外部 PFET パワーゲートオフまでの遅延時間 | -   | -   | 50  | μs | -                 |

| SID.LSCSA.AC.5 | $T_{SR\_GPIO}$  | SR 閾値トリップから出力 GPIO トグルまでの遅延時間       | -   | -   | 20  | μs | P1.0 または P1.1 に適用 |

**Table 31 UV/OV 仕様**

(特性評価で保証)

| 仕様 ID      | パラメーター      | 説明                      | Min  | Typ | Max | 単位 | 詳細 / 条件   |

|------------|-------------|-------------------------|------|-----|-----|----|-----------|

| SID.UVOV.1 | $V_{THOV1}$ | 過電圧閾値の精度, 4.0V ~ 11.0V  | -3   | -   | 3   | %  | アクティブ モード |

| SID.UVOV.2 | $V_{THOV2}$ | 過電圧閾値の精度, 11V ~ 27.4V   | -3.2 | -   | 3.2 | %  |           |

| SID.UVOV.3 | $V_{THUV1}$ | 低電圧閾値の精度, 2.7V ~ 3.3V   | -4   | -   | 4   | %  |           |

| SID.UVOV.4 | $V_{THUV2}$ | 低電圧閾値の精度, 3.3V ~ 4.0V   | -3.5 | -   | 3.5 | %  |           |

| SID.UVOV.5 | $V_{THUV3}$ | 低電圧閾値の精度, 4.0V ~ 11.0V  | -3   | -   | 3   | %  |           |

| SID.UVOV.6 | $V_{THUV4}$ | 低電圧閾値の精度, 11.0V ~ 22.0V | -2.9 | -   | 2.9 | %  |           |

**Table 32 UV/OV の AC 仕様**

(特性評価で保証)

| 仕様 ID         | パラメーター         | 説明                                 | Min | Typ | Max | 単位 | 詳細 / 条件           |

|---------------|----------------|------------------------------------|-----|-----|-----|----|-------------------|

| SID.UVOV.AC.1 | $T_{OV\_GPIO}$ | UV 閾値トリップから出力 GPIO トグルまでの遅延時間      | -   | -   | 20  | μs | P1.0 または P1.1 に適用 |

| SID.UVOV.AC.2 | $T_{OV\_GATE}$ | UV 閾値トリップから外部 PFET パワーゲートオフまでの遅延時間 | -   | -   | 50  | μs | -                 |

| SID.UVOV.AC.3 | $T_{UV\_GPIO}$ | UV 閾値トリップから出力 GPIO トグルまでの遅延時間      | -   | -   | 20  | μs | P1.0 または P1.1 に適用 |

電気的仕様

#### 6.4.4 ゲート ドライバー仕様

Table 33 ゲート ドライバーの DC 仕様

| 仕様 ID     | パラメーター         | 説明                      | Min  | Typ   | Max  | 単位 | 詳細 / 条件                                                                      |

|-----------|----------------|-------------------------|------|-------|------|----|------------------------------------------------------------------------------|

| SID.GD.1  | $R_{PD}$       | プルダウン抵抗                 | -    | -     | 3    | kΩ | 外部 PFET をオンにするために VBUS_P_CTRL と VBUS_C_CTRL に適用                              |

| SID.GD.2  | $R_{PU}$       | プルアップ抵抗                 | -    | -     | 4    | kΩ | 外部 PFET をオフにするために VBUS_P_CTRL に適用                                            |

| SID.GD.3  | $I_{PD0}$      | 1 の駆動強度での電圧引き下げ時のシンク電流  | 25   | -     | 75   | μA | 5V に電圧を引き下げた時の I モード (電流モード)。外部 PFET をオンにするために VBUS_P_CTRL と VBUS_C_CTRL に適用 |

| SID.GD.4  | $I_{PD1}$      | 2 の駆動強度での電圧引き下げ時のシンク電流  | 50   | -     | 150  | μA |                                                                              |

| SID.GD.5  | $I_{PD2}$      | 4 の駆動強度での電圧引き下げ時のシンク電流  | 140  | -     | 300  | μA |                                                                              |

| SID.GD.6  | $I_{PD3}$      | 8 の駆動強度での電圧引き下げ時のシンク電流  | 280  | -     | 580  | μA |                                                                              |

| SID.GD.7  | $I_{PD4}$      | 16 の駆動強度での電圧引き下げ時のシンク電流 | 560  | -     | 1200 | μA |                                                                              |

| SID.GD.8  | $I_{PD5}$      | 32 の駆動強度での電圧引き下げ時のシンク電流 | 1120 | -     | 2300 | μA |                                                                              |

| SID.GD.9  | $I_{leak\_p1}$ | VBUS_P_CTRL ピン上のリーケ電流   | -    | 0.003 | -    | μA | +25°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BUS}$                                   |

| SID.GD.10 | $I_{leak\_c1}$ | VBUS_C_CTRL ピン上のリーケ電流   | -    | 0.003 | -    | μA | +25°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BU}$                                    |

| SID.GD.11 | $I_{leak\_p2}$ | VBUS_P_CTRL ピン上のリーケ電流   | -    | -     | 2    | μA | +85°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BU}$                                    |

| SID.GD.12 | $I_{leak\_c2}$ | VBUS_C_CTRL ピン上のリーケ電流   | -    | -     | 2    | μA | +85°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BU}$                                    |

| SID.GD.13 | $I_{leak\_p3}$ | VBUS_P_CTRL ピン上のリーケ電流   | -    | -     | 7    | μA | +125°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BU}$                                   |

| SID.GD.14 | $I_{leak\_c3}$ | VBUS_C_CTRL ピン上のリーケ電流   | -    | -     | 7    | μA | +125°C $T_J$ , 5V $V_{DDD}$ , 20V $V_{BU}$                                   |

Table 34 ゲート ドライバーの AC 仕様

(特性評価で保証)

| 仕様 ID     | パラメーター             | 説明                       | Min | Typ | Max | 単位   | 詳細 / 条件                                                                                                         |

|-----------|--------------------|--------------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------|

| SID.GD.15 | $T_{PD1}$          | VBUS_C_CTRL 電圧引き下げ時の遅延時間 | -   | -   | 2   | μs   | $C_{load} = 2nF$ , 立ち下りエッジの開始から VBUS-1.5V までの遅延, $VBUS = 5V \sim 20V$ , VBUS_C_CTRL と VBUS の間に接続された $50K\Omega$ |

| SID.GD.16 | $T_{r\_discharge}$ | VBUS_C_CTRL 上の出力ノードの放電速度 | -   | -   | 5   | V/μs | 80% ~ 20%, VBUS_C_CTRL と VBUS の間に接続された $50K\Omega$ , $C_{load} = 2nF$ , $V_{initial} = 24V$                     |

## 電気的仕様

**Table 34 ゲート ドライバーの AC 仕様 (continued)**

(特性評価で保証) (continued)

| 仕様 ID     | パラメーター    | 説明                       | Min | Typ | Max | 単位   | 詳細 / 条件                                                                                                           |

|-----------|-----------|--------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------|

| SID.GD.17 | $T_{PD2}$ | VBUS_P_CTRL 電圧引き下げ時の遅延時間 | -   | -   | 2   | μs   | $C_{load} = 2nF$ , 立ち下りエッジの開始から VBUS-1.5V までの遅延, $V_{BUS} = 5V \sim 20V$ , VBUS_C_CTRL と VBUS の間に接続された $50\Omega$ |

| SID.GD.18 | $T_{PU}$  | VBUS_P_CTRL 電圧引き上げ時の遅延時間 | -   | -   | 18  | μs   | $C_{load} = 2nF$ , 立ち下りエッジの開始から VBUS-1.5V までの遅延, $V_{BUS} = 5V \sim 20V$ , VBUS_C_CTRL と VBUS の間に接続された $50\Omega$ |

| SID.GD.19 | $SR_{PU}$ | VBUS_P_CTRL 上の出力スルーレート   | -   | -   | 5   | V/μs | $C_{load} = 2nF$ , VBUS_P_CTRL 範囲の 20% ~ 80%                                                                      |

| SID.GD.20 | $SR_{PD}$ | VBUS_P_CTRL 上の出力スルーレート   | -   | -   | 5   | V/μs | $C_{load} = 2nF$ , VBUS_P_CTRL 範囲の 80% ~ 20%                                                                      |

**Table 35 VBUS 放電仕様**

| 仕様 ID#           | パラメーター          | 説明                       | Min  | Typ | Max | 単位 | 詳細 / 条件                        |

|------------------|-----------------|--------------------------|------|-----|-----|----|--------------------------------|

| SID.VBUS.DISC.6  | $I_1$           | 20V NMOS オン時の電流, DS = 1  | 0.15 | -   | 1   | mA | 0.5V で計測                       |

| SID.VBUS.DISC.7  | $I_2$           | 20V NMOS オン時の電流, DS = 2  | 0.4  | -   | 2   | mA |                                |

| SID.VBUS.DISC.8  | $I_4$           | 20V NMOS オン時の電流, DS = 4  | 0.9  | -   | 4   | mA |                                |

| SID.VBUS.DISC.9  | $I_8$           | 20V NMOS オン時の電流, DS = 8  | 2    | -   | 8   | mA |                                |

| SID.VBUS.DISC.10 | $I_{16}$        | 20V NMOS オン時の電流, DS = 16 | 4    | -   | 10  | mA |                                |

| SID.VBUS.DISC.11 | VBUS_Stop_Error | 最終 $V_{BUS}$ 値の設定からの誤差率  | -    | -   | 10  | %  | $V_{BUS}$ が 5V に放電された時。特性評価で保証 |

**Table 36 電圧 (VBUS) 安定化の DC 仕様**

| 仕様 ID#      | パラメーター       | 説明                                 | Min   | Typ | Max   | 単位 | 詳細 / 条件                            |

|-------------|--------------|------------------------------------|-------|-----|-------|----|------------------------------------|

| SID.DC.VR.1 | $V_{IN\_3}$  | 3V をターゲット電圧にする場合の $V_{(pad\_in)}$  | 2.85  | 3   | 3.15  | V  | バンド ギャップ使用時アクティブモードのシャントレギュレータが 3V |

| SID.DC.VR.2 | $V_{IN\_5}$  | 5V をターゲット電圧にする場合の $V_{(pad\_in)}$  | 4.75  | 5   | 5.25  | V  | アクティブモードのシャントレギュレータが 5V            |

| SID.DC.VR.3 | $V_{IN\_9}$  | 9V をターゲット電圧にする場合の $V_{(pad\_in)}$  | 8.55  | 9   | 9.45  | V  | アクティブモードのシャントレギュレータが 9V            |

| SID.DC.VR.4 | $V_{IN\_15}$ | 15V をターゲット電圧にする場合の $V_{(pad\_in)}$ | 14.25 | 15  | 15.75 | V  | アクティブモードのシャントレギュレータが 15V           |

## 電気的仕様

**Table 36** 電圧 (VBUS) 安定化の DC 仕様 (continued)

| 仕様 ID#       | パラメーター               | 説明                           | Min  | Typ | Max  | 単位 | 詳細 / 条件                               |

|--------------|----------------------|------------------------------|------|-----|------|----|---------------------------------------|

| SID.DC.VR.5  | V_IN_20              | 20V をターゲット電圧にする場合の V(pad_in) | 19   | 20  | 21   | V  | アクティブ モードのシャントレギュレータが 20V             |

| SID.DC.VR.6  | V_IN_3_DS            | 3V をターゲット電圧にする場合の V(pad_in)  | 2.7  | 3   | 3.3  | V  | バンド ギャップ使用時ディープスリープモードのシャントレギュレータが 3V |

| SID.DC.VR.7  | V_IN_5_DS            | 5V をターゲット電圧にする場合の V(pad_in)  | 4.5  | 5   | 5.5  | V  | ディープスリープモードのシャントレギュレータが 5V            |

| SID.DC.VR.8  | V_IN_9_DS            | 9V をターゲット電圧にする場合の V(pad_in)  | 8.1  | 9   | 9.1  | V  | ディープスリープモードのシャントレギュレータが 9V            |

| SID.DC.VR.9  | V_IN_15_DS           | 15V をターゲット電圧にする場合の V(pad_in) | 13.5 | 15  | 16.5 | V  | ディープスリープモードのシャントレギュレータが 15V           |

| SID.DC.VR.10 | V_IN_20_DS           | 20V をターゲット電圧にする場合の V(pad_in) | 18   | 20  | 22   | V  | ディープスリープモードのシャントレギュレータが 20V           |

| SID.DC.VR.11 | I <sub>KA</sub> _OFF | オフ状態のカソード電流                  | -    | -   | 10   | μA | -                                     |

| SID.DC.VR.12 | I <sub>KA</sub> _ON  | カソード ピンを通る電流                 | -    | -   | 10   | mA | -                                     |

**Table 37** VBUS 短絡保護仕様

| 仕様 ID     | パラメーター          | 説明                                     | Min | Typ | Max | 単位 | 詳細 / 条件 |

|-----------|-----------------|----------------------------------------|-----|-----|-----|----|---------|

| SID.VSP.1 | V_SHORT_TRIGGER | CC/P2.2/P2.3 ピン上の VBUS 短絡時のシステム側クランプ電圧 | -   | 9   | -   | V  | 特性評価で保証 |

**Table 38** VBUS の DC レギュレータ仕様

| 仕様 ID      | パラメーター      | 説明          | Min  | Typ | Max  | 単位 | 詳細 / 条件 |

|------------|-------------|-------------|------|-----|------|----|---------|

| SID.VREG.2 | VBUS_DETECT | VBUS 検出閾値電圧 | 1.08 | -   | 2.62 | V  | -       |

**Table 39** VBUS の AC レギュレータ仕様

| 仕様 ID      | パラメーター             | 説明                  | Min | Typ | Max | 単位 | 詳細 / 条件 |

|------------|--------------------|---------------------|-----|-----|-----|----|---------|

| SID.VREG.3 | T <sub>start</sub> | 安定化電源出力の合計スタートアップ時間 | -   | -   | 200 | μs | 特性評価で保証 |

電気的仕様

### 6.4.5 アナログ - デジタル変換器

**Table 40 ADC の DC 仕様**

(特性評価で保証)

| 仕様 ID      | パラメーター                | 説明                         | Min  | Typ | Max  | 単位  | 詳細 / 条件            |

|------------|-----------------------|----------------------------|------|-----|------|-----|--------------------|

| SID.ADC.1  | Resolution            | ADC 分解能                    | -    | 8   | -    | ビット | -                  |

| SID.ADC.2  | INL                   | 積分非直線性                     | -2.5 | -   | 2.5  | LSB | VDDD から生成された基準電圧   |

| SID.ADC.2A | INL                   | 積分非直線性                     | -1.5 | -   | 1.5  | LSB | バンドギャップから生成された基準電圧 |

| SID.ADC.3  | DNL                   | 微分非直線性                     | -2.5 | -   | 2.5  | LSB | VDDD から生成された基準電圧   |

| SID.ADC.3A | DNL                   | 微分非直線性                     | -1.5 | -   | 1.5  | LSB | バンドギャップから生成された基準電圧 |

| SID.ADC.4  | Gain Error            | ゲイン誤差                      | -1.5 | -   | 1.5  | LSB | -                  |

| SID.ADC.6  | V <sub>REF_ADC2</sub> | バンドギャップから生成された場合の ADC 基準電圧 | 1.96 | 2.0 | 2.04 | V   | バンドギャップから生成された基準電圧 |

**Table 41 ADC の AC 仕様**

(設計で保証)

| 仕様 ID     | パラメーター   | 説明                | Min | Typ | Max | 単位   | 詳細 / 条件 |

|-----------|----------|-------------------|-----|-----|-----|------|---------|

| SID.ADC.7 | SLEW_Max | サンプリングされた電圧信号の変化率 | -   | -   | 3   | V/ms | -       |

### 6.4.6 メモリ

**Table 42 フラッシュの AC 仕様**

| 仕様 ID     | パラメーター                 | 説明                                               | Min | Typ | Max  | 単位 | 詳細 / 条件                                              |

|-----------|------------------------|--------------------------------------------------|-----|-----|------|----|------------------------------------------------------|

| SID.MEM#3 | FLASH_ERASE            | 行消去時間                                            | -   | -   | 15.5 | ms | -40°C ≤ T <sub>A</sub> ≤ 85°C, すべての V <sub>DDD</sub> |

| SID.MEM#4 | FLASH_WRITE            | 行(ブロック)書き込み時間(消去 + プログラム)                        | -   | -   | 20   | ms | -40°C ≤ T <sub>A</sub> ≤ 85°C, すべての V <sub>DDD</sub> |

| SID.MEM#8 | FLASH_ROW_PGM          | 消去後の行プログラム時間                                     | -   | -   | 7    | ms | 25°C ≤ T <sub>A</sub> ≤ 55°C, すべての V <sub>DDD</sub>  |

| SID178    | T <sub>BULKERASE</sub> | バルク消去時間(32KB)                                    | -   | -   | 35   | ms | -                                                    |

| SID180    | T <sub>DEVPORG</sub>   | 総デバイス プログラム時間                                    | -   | -   | 7.5  | s  | -                                                    |

| SID182    | F <sub>RET1</sub>      | フラッシュデータ保持, T <sub>A</sub> ≤ 55°C, 100K P/E サイクル | 20  | -   | -    | 年  | -                                                    |

| SID182A   | F <sub>RET2</sub>      | フラッシュデータ保持, T <sub>A</sub> ≤ 85°C, 10K P/E サイクル  | 10  | -   | -    | 年  | -                                                    |

| SID182B   | F <sub>RET3</sub>      | フラッシュデータ保持, T <sub>A</sub> ≤ 105°C, 10K P/E サイクル | 3   | -   | -    | 年  | -                                                    |

注文情報

## 7 注文情報

Table 43 に、EZ-PD™ CCG3PA の製品番号と機能を示します。

Table 43 CCGPA 注文情報

| 製品番号            | アプリケーション                | 終端抵抗                                                | ロール | ブートローダ <sup>[10]</sup>          | パッケージタイプ   | Si ID |

|-----------------|-------------------------|-----------------------------------------------------|-----|---------------------------------|------------|-------|

| CYPD3171-24LQXQ | パワーバンク                  | R <sub>P</sub> , R <sub>D</sub> , R <sub>D-DB</sub> | DRP | UFP CC ブートローダ                   | 24 ピン QFN  | 2003  |

| CYPD3174-16SXQ  | 光カプラ フィード バックに基づく電源アダプタ | R <sub>P</sub>                                      | DFP | 光カプラ フィード バック ブートローダ 付き DFP CC  | 16 ピン SOIC | 2001  |

| CYPD3174-24LQXQ | 光カプラ フィード バックに基づく電源アダプタ | R <sub>P</sub>                                      | DFP | 光カプラ フィード バック ブートローダ 付き DFP CC  | 24 ピン QFN  | 2000  |

| CYPD3175-24LQXQ | ダイレクト フィードバックに基づく電源アダプタ | R <sub>P</sub>                                      | DFP | ダイレクト フィード バック ブートローダ 付き DFP CC | 24 ピン QFN  | 2002  |

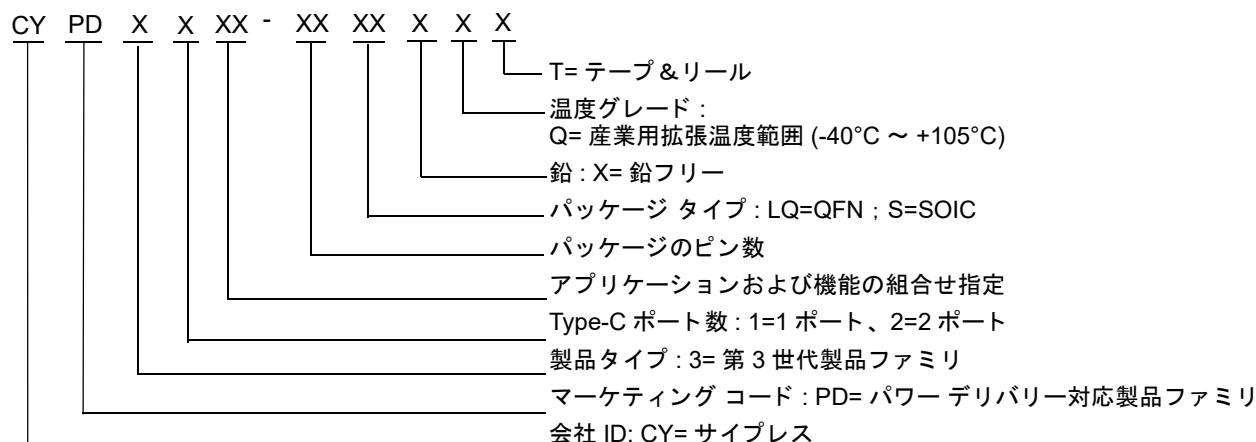

### 7.1 注文コードの定義

#### 注:

- デフォルトで VBUS が 5V であることを前提としています。ブートローダの実行は、5V VBUS 生成を制御しません。

パッケージ

## 8 パッケージ

Table 44 パッケージ特性

| パラメーター   | 説明                            | 条件        | Min | Typ | Max   | 単位   |

|----------|-------------------------------|-----------|-----|-----|-------|------|

| $T_A$    | 動作周囲温度                        | 産業用拡張温度範囲 | -40 | 25  | 105   | °C   |

| $T_J$    | 動作接合部温度                       | 産業用拡張温度範囲 | -40 | 25  | 120   | °C   |

| $T_{JA}$ | パッケージ $\theta_{JA}$ (24-QFN)  | -         | -   | -   | 19.98 | °C/W |

| $T_{JC}$ | パッケージ $\theta_{JC}$ (24-QFN)  | -         | -   | -   | 4.78  | °C/W |

| $T_{JA}$ | パッケージ $\theta_{JA}$ (16-SOIC) | -         | -   | -   | 84    | °C/W |

| $T_{JC}$ | パッケージ $\theta_{JC}$ (16-SOIC) | -         | -   | -   | 33.9  | °C/W |

Table 45 はんだリフロー ピーク温度

| パッケージ      | 最高ピーク温度 | ピーク温度 5°C 以内での最長時間 |

|------------|---------|--------------------|

| 24 ピン QFN  | 260°C   | 30 秒               |

| 16 ピン SOIC | 260°C   | 30 秒               |

Table 46 パッケージの湿度感度レベル (MSL), IPC/JEDEC J-STD-2

| パッケージ      | MSL  |

|------------|------|

| 24 ピン QFN  | MSL3 |

| 16 ピン SOIC | MSL3 |

## パッケージ

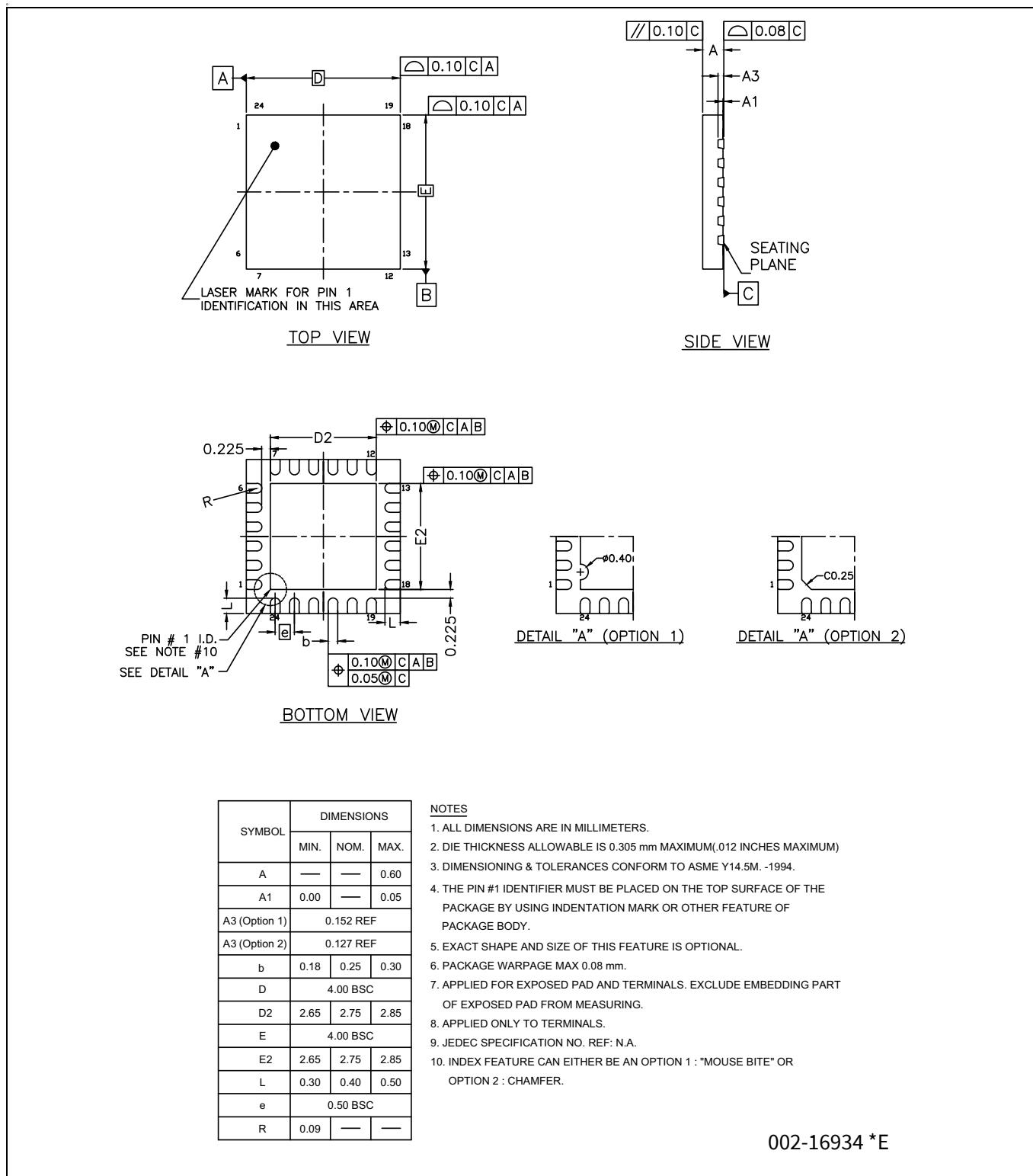

Figure 11 24 ピン QFN パッケージ外形図

## パッケージ

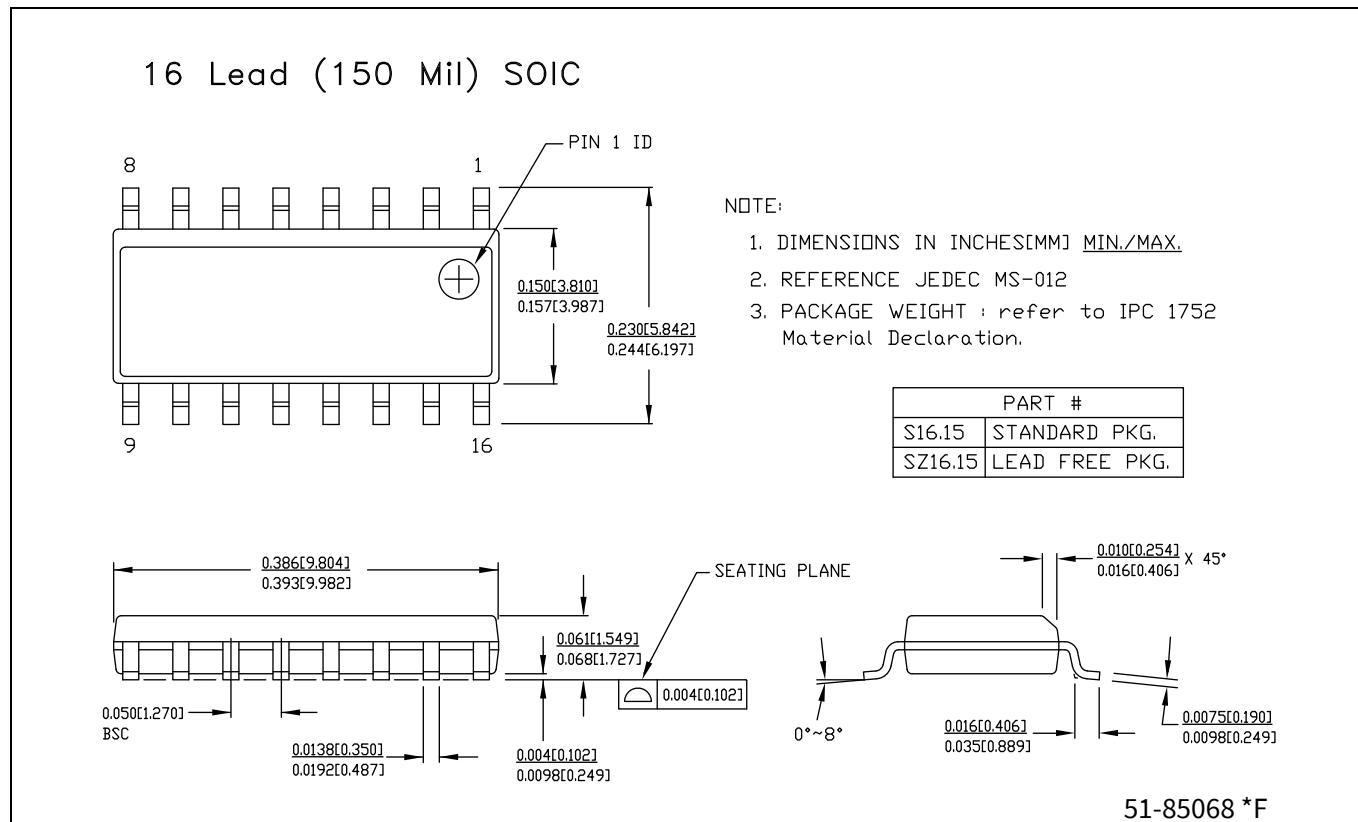

Figure 12 16 ピン SOIC パッケージ外形図

## 9 略語

Table 47 本書で使用される略語

| 略語                       | 説明                                                                                                            |

|--------------------------|---------------------------------------------------------------------------------------------------------------|

| ADC                      | analog-to-digital converter ( アナログ - デジタル変換器 )                                                                |

| AES                      | advanced encryption standard ( 高度暗号化標準 )                                                                      |

| API                      | application programming interface ( アプリケーション プログラミング インターフェース )                                               |

| Arm®                     | advanced RISC machine ( 高度な RISC マシン )。CPU アーキテクチャの一種                                                         |

| CC                       | configuration channel ( コンフィギュレーション チャネル )                                                                    |

| CCG3                     | Cable Controller Generation 3 ( 第 3 世代ケーブル コントローラー )                                                          |

| CPU                      | central processing unit ( 中央演算処理装置 )                                                                          |

| CRC                      | cyclic redundancy check ( 巡回冗長検査 )。エラー チェック プロトコルの一種                                                          |

| CS                       | current sense ( 電流検出 )                                                                                        |

| DFP                      | downstream facing port ( ダウンストリーム ポート )                                                                       |

| DIO                      | digital input/output ( デジタル入出力 )。アナログなし、デジタル機能のみを持つ GPIO。GPIO を参照してください。                                      |

| DRP                      | dual role port ( デュアル ロール ポート )                                                                               |

| EEPROM                   | electrically erasable programmable read-only memory ( 電気的消去書き込み可能読み出し専用メモリ )                                  |

| EMCA                     | electronically marked cable assembly ( 電子的マーク付きケーブル アセンブリ ); 定格電流などのケーブル特性を Type-C ポートに報告する IC を内蔵した USB ケーブル |

| EMI                      | electromagnetic interference ( 電磁干渉 )                                                                         |

| ESD                      | electrostatic discharge ( 静電気放電 )                                                                             |

| FS                       | full-speed ( フルスピード )                                                                                         |

| GPIO                     | general-purpose input/output ( 汎用入出力 )                                                                        |

| IC                       | integrated circuit ( 集積回路 )                                                                                   |

| IDE                      | integrated development environment ( 統合開発環境 )                                                                 |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit ( インターパーティクル インテグレーテッド サーキット )。通信プロトコルの一種                                            |

| ILO                      | internal low-speed oscillator ( 内部低速発振器 )。IMO も参照してください。                                                      |

| IMO                      | internal main oscillator ( 内部主発振器 )。ILO も参照してください。                                                            |

| I/O                      | input/output ( 入出力 ), GPIO も参照してください。                                                                         |