# EZ-PD™ PAG2S-QZ 集成 USB PD 和次级侧 QR-ZVS 控制器

## 概述

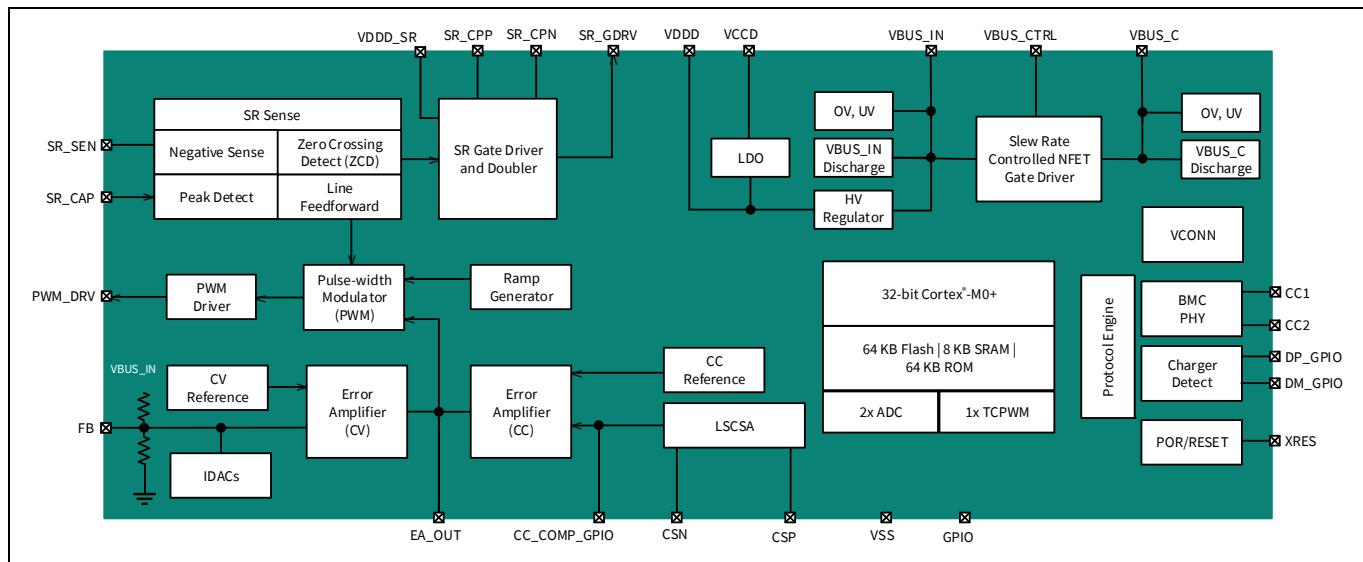

EZ-PD™ PAG2S-QZ CYPAS211 是一款集成次级侧 PWM 控制器和 USB 功率传输 (USB PD) 控制器。它集成了次级侧同步整流器 (SR)、脉宽调制器 (PWM) 和零电压开关 (ZVS) 控制。PAG2S-QZ 是针对 USB-C 电源适配器的产品，非常适合采用 USB PD、高通快速充电和其他标准充电协议的高效 AC-DC 反激式设计。PAG2S-QZ CYPAS211 还支持 USB PD 扩展功率范围 (EPR) 模式。

## 应用

- USB-C 充电器和适配器

- 支持 EPR 的 USB-C 充电器和适配器

- 支持 USB PD 和传统式充电的电源适配器

## 性能

- 集成的次级侧反激式控制器和充电端口控制器

- 集成了次级侧同步整流器 (SR)、支持 ZVS 的 PWM 控制

- 支持准谐振 (QR)、临界导通模式 (CrCM)、谷底开关、非连续导通模式 (DCM) 和连续导通模式 (CCM) 下的同步整流，并支持高达 300 kHz 的开关频率

- 支持轻负载操作的突发模式

- SR 驱动器可与标准 MOSFET 和逻辑电平 MOSFET 配合使用

- 符合 USB PD 3.1 标准，支持高达 28 V VBUS 的扩展功率范围 (EPR)

- 支持带可编程电源 (PPS) 的 USB PD 2.0、PD 3.0, QC5.0、QC4+、QC 4.0、QC 3.0、QC 2.0、Samsung AFC、Apple Charging 和 Battery Charging (BC) V1.2 等充电协议

- 集成了低侧电流检测放大器 (LSCSA)、两个 VBUS 放电 FET 和一个 NFET 栅极驱动器来驱动负载开关和 VCONN FET 来支持 EMCA 电缆

- 可配置的 VBUS 过压保护 (OVP)、欠压保护 (UVP)、过流保护 (OCP)、短路保护 (SCP) 和系统过热保护 (OTP)

- 防止 VBUS 到 CC 间的意外短路；CC、VBUS、DP/DM 线路上的静电放电 (ESD) 保护以及 DP/DM 线路上的过压保护

- 集成了具有 64 KB Flash、8 KB SRAM 和 64 KB ROM 的 32 位 Cortex®-M0+

- 32-pin QFN 封装，结温范围为 -40°C 至 +150°C

## 功能框图

## 功能框图

## 目录

## 目录

|                                                  |    |

|--------------------------------------------------|----|

| <b>概述</b>                                        | 1  |

| <b>应用</b>                                        | 1  |

| <b>性能</b>                                        | 1  |

| <b>功能框图</b>                                      | 2  |

| <b>目录</b>                                        | 3  |

| <b>1 应用概述</b>                                    | 4  |

| 1.1 USB PD 适配器 – 次级侧反激式控制                        | 4  |

| <b>2 引脚分布</b>                                    | 5  |

| 2.1 引脚定义                                         | 5  |

| 2.2 引脚说明                                         | 6  |

| 2.2.1 SR_GDRV、SR_VSS、SR_SEN、SR_CPP、SR_CPN、SR_CAP | 6  |

| 2.2.2 FB、EA_OUT、CC_COMP_GPIOx                    | 6  |

| 2.2.3 PWM_DRV                                    | 6  |

| 2.2.4 VBUS_IN、VDDD、VCCD                          | 7  |

| 2.2.5 VBUS_C、VBUS_CTRL                           | 7  |

| 2.2.6 CSP、CSN                                    | 7  |

| 2.2.7 CC1, CC2                                   | 7  |

| 2.2.8 DP_GPIOx、DM_GPIOx                          | 7  |

| 2.2.9 GPIOx、XRES                                 | 7  |

| <b>3 功能说明</b>                                    | 8  |

| 3.1 系统启动                                         | 8  |

| 3.2 操作模式 – SR                                    | 8  |

| 3.3 操作模式 – PWM 和 ZVS                             | 12 |

| 3.4 故障保护                                         | 15 |

| 3.4.1 VBUS OVP、UVP、OCP 和 SCP                     | 15 |

| 3.4.2 过温保护                                       | 15 |

| 3.4.3 ESD、CC OVP 和 DP/DM OVP                     | 15 |

| 3.5 电源模式                                         | 15 |

| 3.6 MCU 子系统                                      | 15 |

| <b>4 电气规范</b>                                    | 16 |

| 4.1 最大绝对额定值                                      | 16 |

| 4.2 器件级规范                                        | 16 |

| 4.3 功能模块规范                                       | 18 |

| <b>5 订购信息</b>                                    | 24 |

| 5.1 订购代码定义                                       | 24 |

| <b>6 封装</b>                                      | 25 |

| <b>7 缩略语</b>                                     | 27 |

| <b>8 文档规范</b>                                    | 29 |

| 8.1 测量单位                                         | 29 |

| <b>修订记录</b>                                      | 30 |

## 应用概述

# 1 应用概述

## 1.1 USB PD 适配器 – 次级侧反激式控制

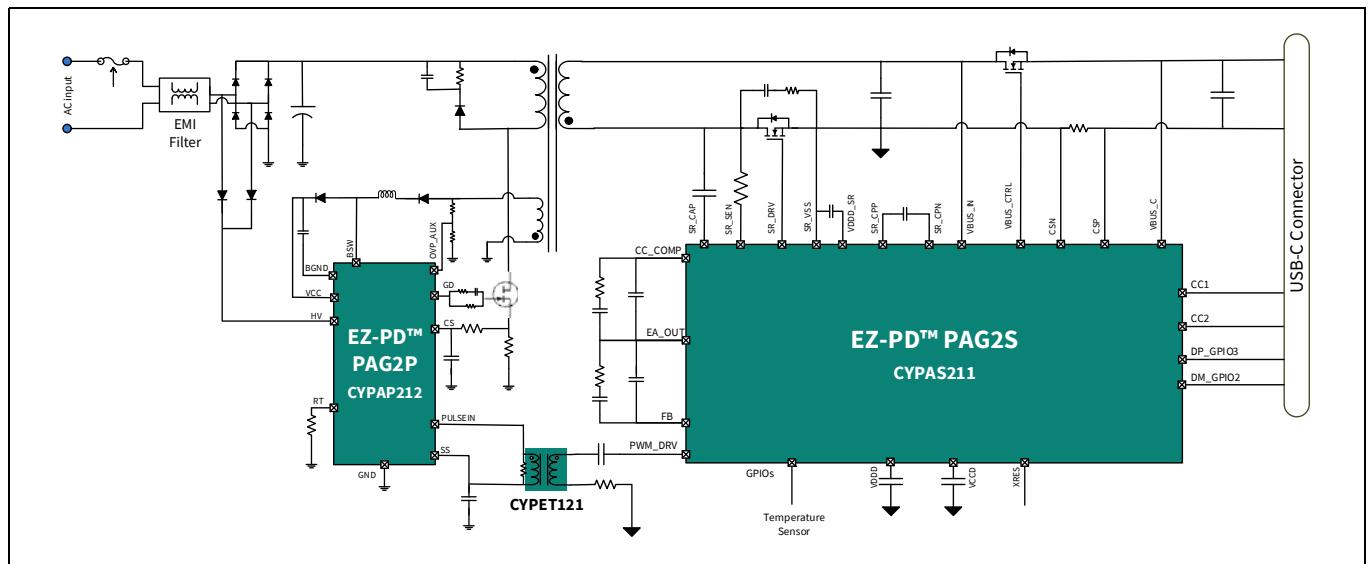

Figure 1 显示的是实现次级侧控制同步反激式系统的电源适配器应用图。在该系统中，EZ-PD™ PAG2S-QZ 在电压控制模式下调制初级 MOSFET 的脉冲宽度。PAG2S-QZ 使用内部误差放大器 (EA) 和可编程斜坡发生器来确定 PWM 的脉冲宽度。该 PWM 信号通过脉冲边沿变压器从次级传输到初级。在该拓扑结构中，PAG2S-QZ 集成了三个关键功能：次级侧 PWM 控制、充电协议控制和故障保护。在以下示例中，EZ-PD™ PAG2P 用作初级控制器并与 PAG2S-QZ 配合使用。

Figure 1 具有次级侧反激式控制的 USB PD 适配器

引脚分布

## 2 引脚分布

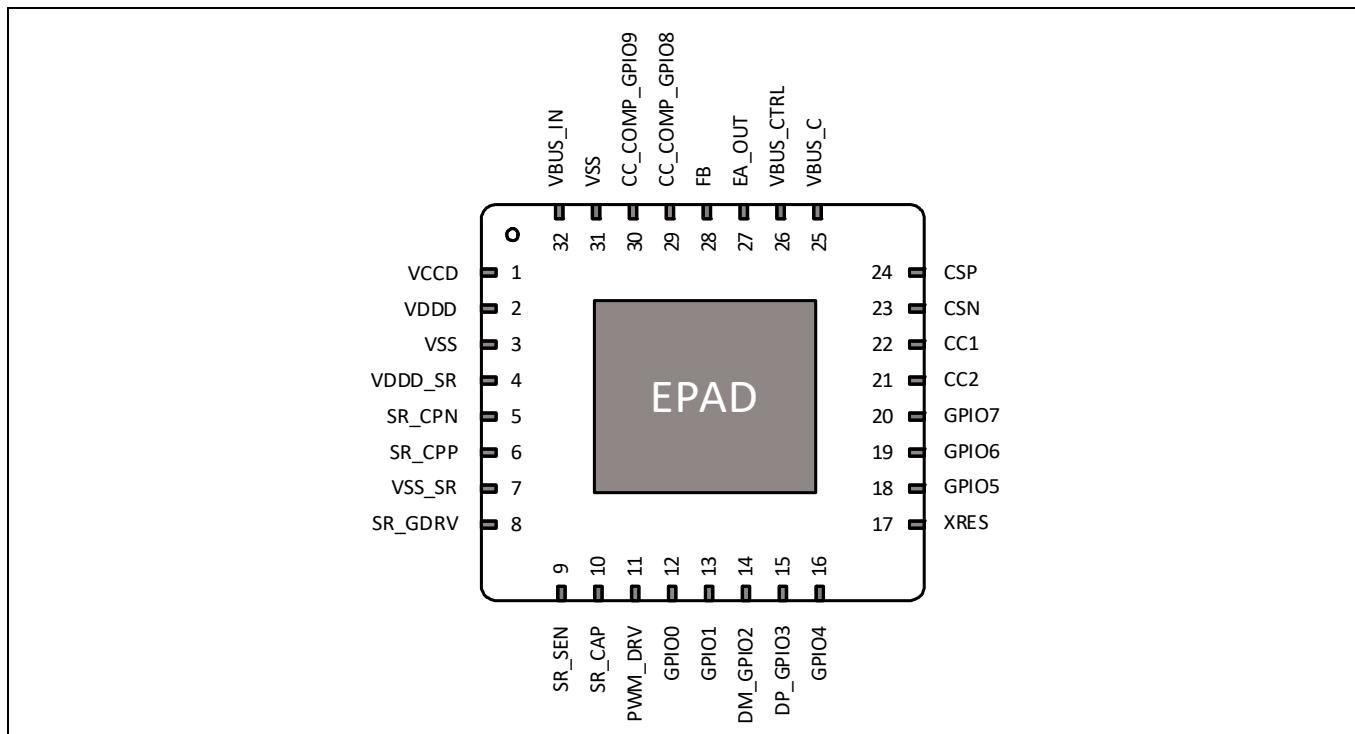

### 2.1 引脚定义

Table 1 32-pin QFN 引脚说明

| 序号 | 引脚名称          | 引脚说明                          |

|----|---------------|-------------------------------|

| 1  | VCCD          | 1.8 V 内核电压 LDO 输出             |

| 2  | VDDD          | 3.0 V 至 5.5 V 内部 LDO 输出       |

| 3  | VSS           | 接地                            |

| 4  | VDDD_SR       | 同步整流器驱动器的 V <sub>DDD</sub> 电源 |

| 5  | SR_CPN        | 同步整流倍增器电容器负极引脚                |

| 6  | SR_CPP        | 同步整流倍增器电容器正极引脚                |

| 7  | VSS_SR        | 同步整流器驱动器的接地                   |

| 8  | SR_GDRV       | 同步整流器 NFET 栅极驱动器              |

| 9  | SR_SEN        | 同步整流器 NFET 漏极终端检测             |

| 10 | SR_CAP        | 同步整流器 NFET 漏极检测, 谐振频率 > 4 MHz |

| 11 | PWM_DRV       | 脉冲边沿变压器驱动器                    |

| 12 | GPIO0         | GPIO                          |

| 13 | GPIO1         |                               |

| 14 | DM_GPIO2      | USB D-/GPIO/SWD_DAT           |

| 15 | DP_GPIO3      | USB D+/GPIO/SWD_DAT           |

| 16 | GPIO4         | 未连接                           |

| 17 | XRES          | 外部复位输入                        |

| 18 | GPIO5         | GPIO                          |

| 19 | GPIO6         | GPIO/TCPWM                    |

| 20 | GPIO7         | GPIO                          |

| 21 | CC2           | 功率传输通信通道 2                    |

| 22 | CC1           | 功率传输通信通道 1                    |

| 23 | CSN           | 低侧电流检测放大器负输入                  |

| 24 | CSP           | 低侧电流检测放大器正输入                  |

| 25 | VBUS_C        | USB Type-C 型 VBUS 监测输入        |

| 26 | VBUS_CTRL     | 负载开关 NFET 栅极控制                |

| 27 | EA_OUT        | EA 输出                         |

| 28 | FB            | EA 反馈                         |

| 29 | CC_COMP_GPIO8 | 恒流模式补偿电容 /GPIO/TCPWM 引脚       |

| 30 | CC_COMP_GPIO9 |                               |

| 31 | VSS           | 接地                            |

| 32 | VBUS_IN       | 3.3 V 至 30 V 稳压器的电源输入         |

## 引脚分布

Figure 2 32-pin QFN 引脚分布

## 2.2 引脚说明

## 2.2.1 SR\_GDRV、SR\_VSS、SR\_SEN、SR\_CPP、SR\_CPN、SR\_CAP

EZ-PD™ PAG2S-QZ 检测同步整流器 NFET 两端的电压并适当控制栅极驱动器以获取最佳效率。该器件支持标准 NFET 和逻辑电平 NFET。PAG2S-QZ 同步整流控制可工作在 QR/CrCM、谷底开关、非连续导通模式 (DCM) 和连续导通模式 (CCM) 下。SR 检测模块支持负值检测和过零检测 (ZCD)。对于 SR\_DRAIN 上谐振频率 > 4 MHz 的方案，通过 10 pF 电容器将 SR\_DRAIN 耦合到 SR\_CAP，这样可以在 SR\_CAP 引脚上检测到峰值。如果谐振频率 < 4 MHz，则 SR\_CAP 引脚必须悬空。

栅极驱动器 (SR\_GDRV) 的驱动电压可以用内部 VDDD 或两倍的 VDDD，从而实现外部 NFET 的低  $R_{DS(ON)}$ 。使用内部倍增电路可将栅极驱动器驱动电压调为两倍的 VDDD，具体是在 SR\_CPP 和 SR\_CPN 引脚之间放置一个倍增电容器。SR FET 的源端应连接到 SR\_VSS 引脚。使用电阻分配器时，可以通过 SR\_SEN 检测外部 NFET 漏极节点上的电压。

## 2.2.2 FB、EA\_OUT、CC\_COMP\_GPIOx

PAG2S-QZ 集成了两个误差放大器模块，可处理恒压和恒流操作模式的次级输出检测和调节。误差放大器输出被馈入到内部模拟 PWM 模块。误差放大器的负输入为反馈 (FB) 引脚，正输入为内部参考电压。根据所需的 VBUS 输出，可以使用内部源 / 灌电流 IDAC 更改 FB 引脚上的电压。FB 引脚和 EA\_OUT 引脚之间需要一个外部补偿网络，如应用图所示（参见 Figure 1）。恒流操作使用内部 LSCSA，其输出被馈入到一个独立的误差放大器，如功能框图所示。需要在 CC\_COMP\_GPIOx 和 EA\_OUT 之间放置一个外部补偿网络来实现恒流模式调节，如 Figure 1 所示。

## 2.2.3 PWM\_DRV

PAG2S-QZ 支持模拟 PWM 发生器，该发生器在电压控制模式下调制初级侧 FET 的脉冲宽度。具体是它生成一个可编程斜坡，然后通过将其与误差放大器的输出进行比较来确定 PWM 脉冲宽度。该斜坡由注入内部电容器的源电流生成；该源电流是某个固定电流和前馈电流的可编程组合。PWM 信号通过外部脉冲边沿变压器从次级侧传输到初级侧。

## 引脚分布

### 2.2.4 VBUS\_IN、VDDD、VCCD

PAG2S-QZ 集成了一个由 VBUS\_IN 脚供电的高电压稳压器，它的输出为 VDDD 脚供电。稳压器的输入电压范围为 3.3 V 至 30 V。该稳压器用于提供 PAG2S-QZ 电流消耗，不建议驱动任何外部负载或 IC。PAG2S-QZ 还具有用于 VBUS\_IN 脚的内部可配置放电路径，用于在负电压转换期间对 VBUS 脚放电。放电电阻强度可通过固件设置进行配置。

稳压源 VDDD 可用于直接为一些内部模拟模块供电，也可进一步稳压，使电压降至 1.8 V VCCD，用于为大部分内核供电。VDDD 和 VCCD 信号被传送到其各自引脚，用于连接外部电容器，从而实现稳压器稳定运行。这些引脚并不用作电源。

### 2.2.5 VBUS\_C、VBUS\_CTRL

VBUS\_C 用于监测 Type-C 连接器的电压。VBUS\_C 具有内部可配置放电路径，用于在负电压转换期间对 VBUS\_C 脚放电。放电电阻强度可通过固件设置进行配置。负载开关位于 VBUS\_IN 和 VBUS\_C 之间。PAG2S-QZ 集成了一个用于控制该负载开关的 NFET 栅极驱动器。VBUS\_CTRL 为该栅极驱动器的输出。有一个可选的慢速开启功能，用于避免突入的浪涌电流。

### 2.2.6 CSP、CSN

PAG2S-QZ 集成了一个 LSCSA，用于监测负载电流。CSP 和 CSN 分别是 LSCSA 的正输入和负输入引脚。LSCSA 的建议 Rsense 为 5 mΩ。

### 2.2.7 CC1, CC2

CC1 和 CC2 均为 USB PD 协议的通信通道。PAG2S-QZ 集成了一个由发送器 (TX) 和接收器 (RX) 组成的 USB PD 收发器，并通过配置通道 (CC) 传送双相标记编码 (BMC) 编码数据，符合 USB PD 标准。所有通信都是半双工的。通过使用物理层防止通信冲突，从而尽可能减少通道上的通信错误。该模块包括 USB PD 规范要求的所有终端电阻 (Rp) 及其开关。

为支持有源电缆应用，PAG2S-QZ 还集成了 VCONN FET，用于为 CC 线路供电。CC1 和 CC2 引脚都需要一个大小为 390 pF 的外部电容器。

### 2.2.8 DP\_GPIOx、DM\_GPIOx

DP 和 DM 线路均为标准的 USB D+ 和 D- 线。PAG2S-QZ 集成了一个充电检测模块，可处理传统充电协议，例如 BC 1.2、Quick Charge、Apple Charging 和 Samsung AFC。该模块集成了这些充电协议所需的所有终端，而无需任何外部组件。当系统不需要传统充电时，该 DP 和 DM 线路可重新作为标准 GPIO 使用。充电器检测模块还支持 DP/DM 线路上的阻抗检测。

### 2.2.9 GPIOx、XRES

PAG2S-QZ 具有多个 GPIO，一部分为专用 GPIO，其余部分则为与其他功能复用的引脚。这些 GPIO 支持多种驱动模式和可配置阈值选项。在上电和复位期间，GPIO 被强制进入三态，以免破坏任何输入和 / 或导致开启电流过大。

XRES 引脚可用于启动复位且其电平被内部上拉。要想启动复位，需要对该引脚进行外部下拉。

功能说明

## 3 功能说明

### 3.1 系统启动

上电时，初级侧启动控制器必须开始使用其软启动机制控制初级开关，并提供足够的电流为次级侧输出电容器充电以及满足 EZ-PD™ PAG2S-QZ 所需的启动电流。次级输出电压作为 PAG2S-QZ 的输入电源使用。一旦 VBUS\_IN 电压超过 3.3 V，PAG2S-QZ 固件将启动并控制初级开关。PAG2S-QZ 固件启动时间约为几毫秒。

启动完成后，固件会配置误差放大器以获取 5 V 次级输出，然后 PAG2S-QZ 将生成相应的 PWM 脉冲。PWM\_DRV 上的这些脉冲通过脉冲变压器耦合到初级启动控制器。接收到 PWM 脉冲后，初级侧启动控制器应将其内部振荡器与 PWM 脉冲进行同步，并从启动模式切换到次级控制模式。在次级控制模式下，初级开关直接由 PAG2S-QZ 生成的 PWM 脉冲控制。

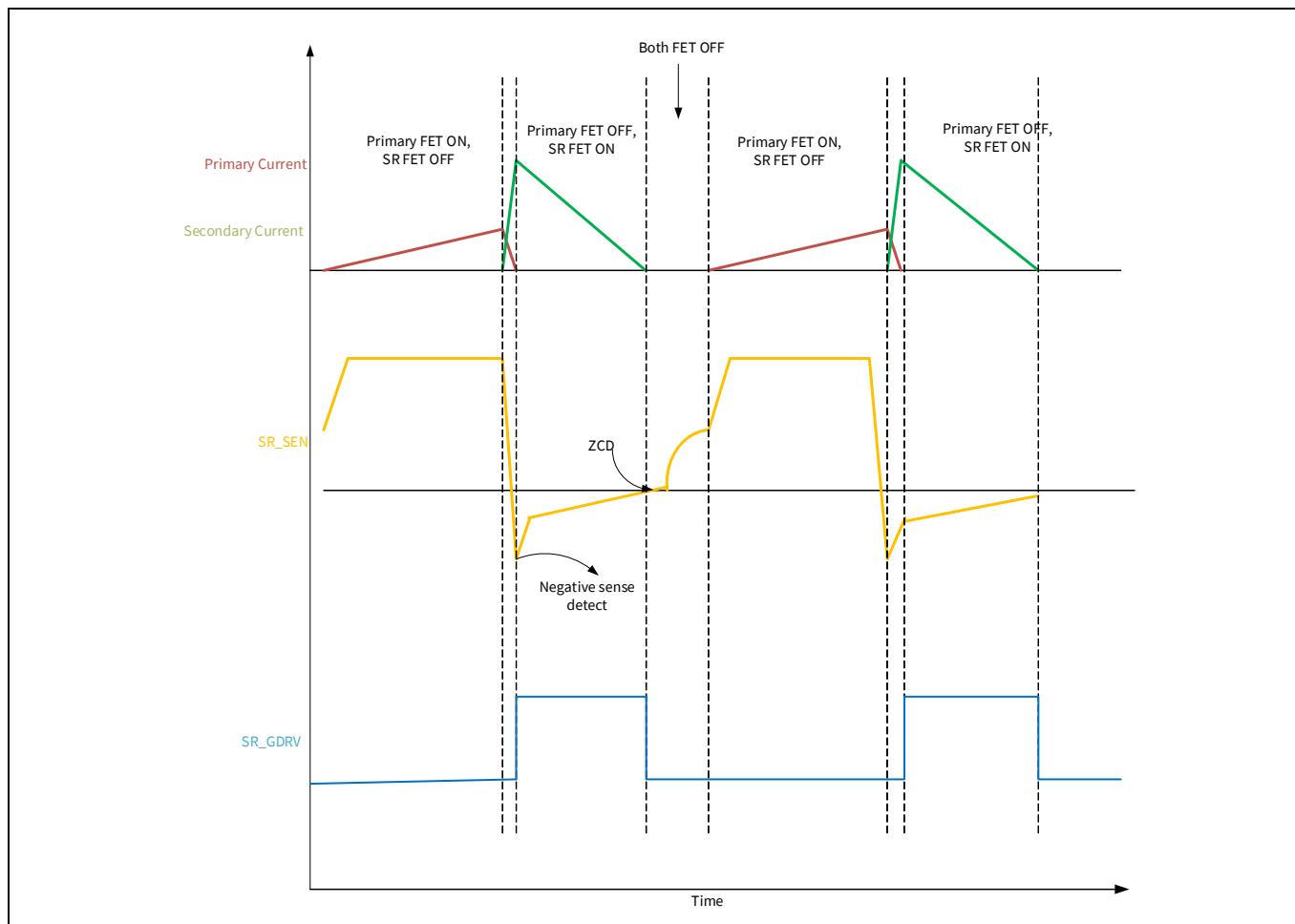

### 3.2 操作模式 – SR

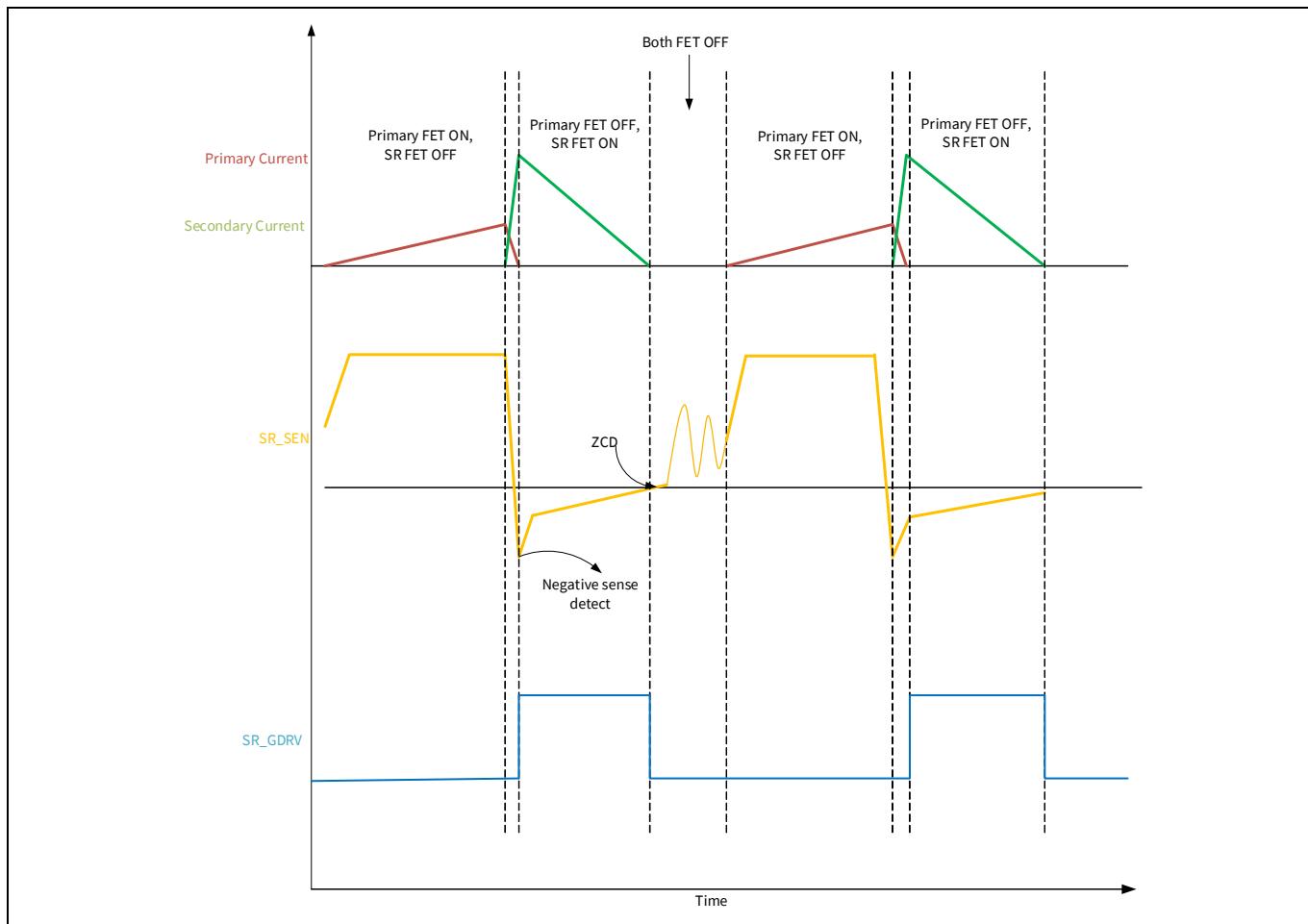

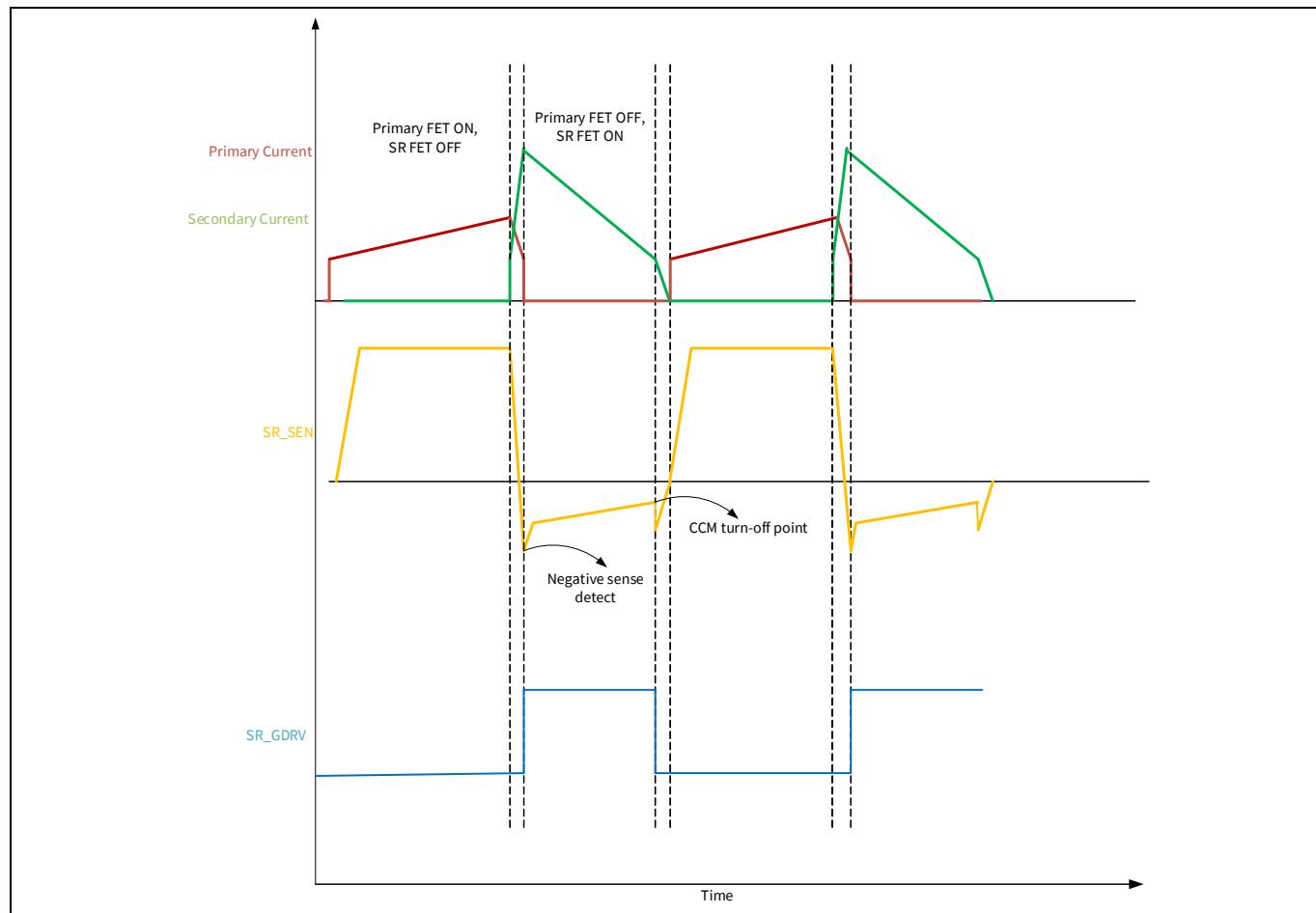

PAG2S-QZ 支持 DCM 和 CCM 模式下的同步整流。SR 检测模块支持负压检测和过零检测 (ZCD)。[Figure 3](#) 和 [Figure 5](#) 分别显示了 QR/CrCM、谷底开关和 CCM 模式下 SR\_GDRV 的功能。SR 控制器的开通延迟典型值为 40 ns，关断延迟典型值为 25 ns。

Figure 3 QR/CrCM 模式下的 SR\_SEN 和 SR\_GDRV

## 功能说明

Figure 4 DCM/ 谷底开关模式下的 SR\_SEN 和 SR\_GDRV

## 功能说明

Figure 5 CCM 模式下的 SR\_SEN 和 SR\_GDRV

## 功能说明

SR\_SEN 引脚与外部电阻连接，可以检测外部 NFET 漏极节点上的电压。使用该外部电阻是为了将 SR\_SEN 引脚上的电压限制在 34 V 以下。SR\_SEN 引脚上的外部电阻取决于电源变压器的匝数比。[Table 2](#) 介绍了不同匝数比所需的外部电阻值。

**Table 2 SR\_SEN 的外部电阻与匝数比**

| 初级与次级匝数比 | Rext (Ω) |

|----------|----------|

| 3:1      | 20k      |

| 4:1      | 20k      |

| 5:1      | 20k      |

| 6:1      | 12k      |

| 7:1      | 12k      |

| 8:1      | 12k      |

| 9:1      | 12k      |

| 10:1     | 12k      |

| 11:1     | 12k      |

| 12:1     | 12k      |

| 13:1     | 12k      |

| 14:1     | 12k      |

| 15:1     | 12k      |

功能说明

### 3.3 操作模式 – PWM 和 ZVS

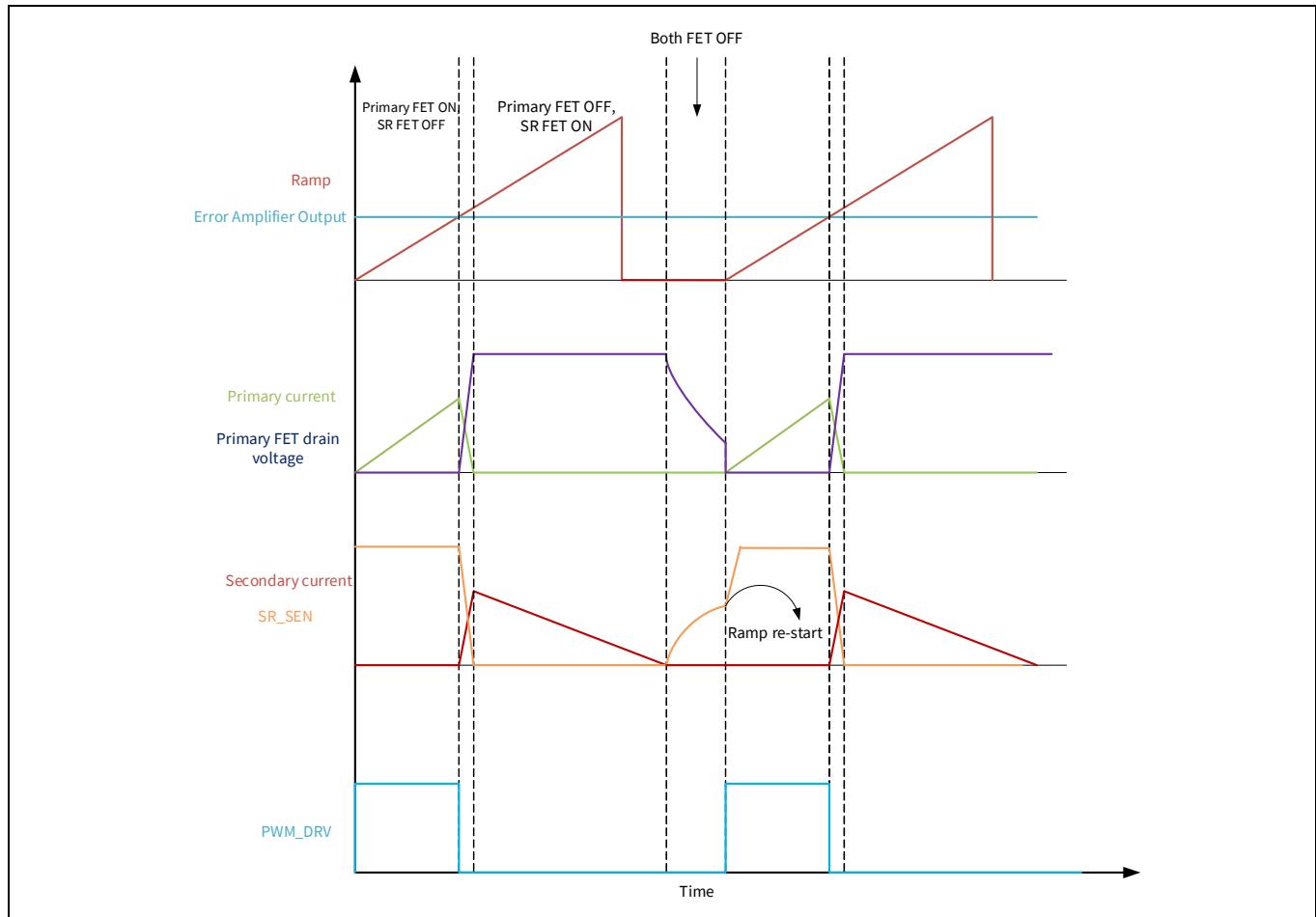

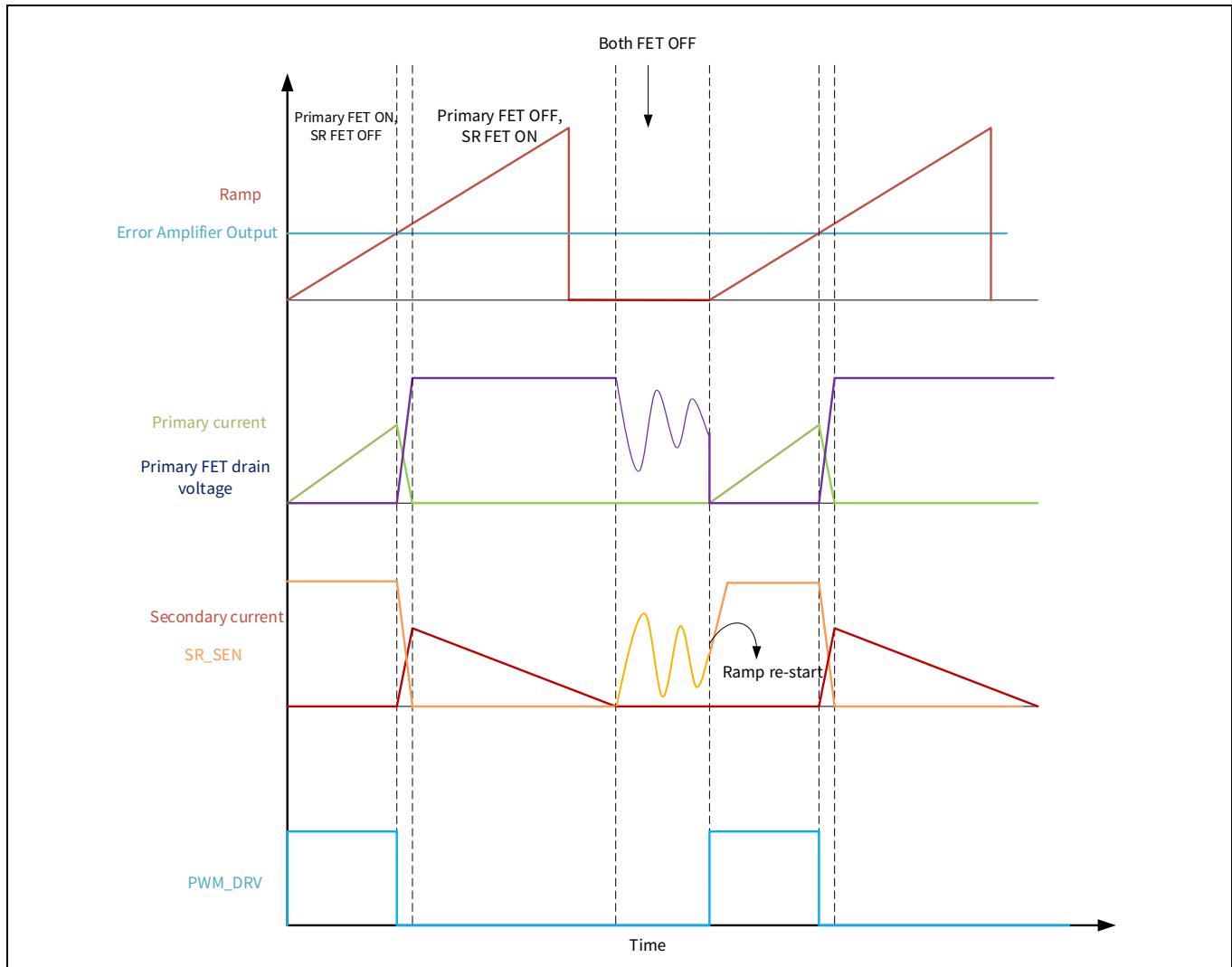

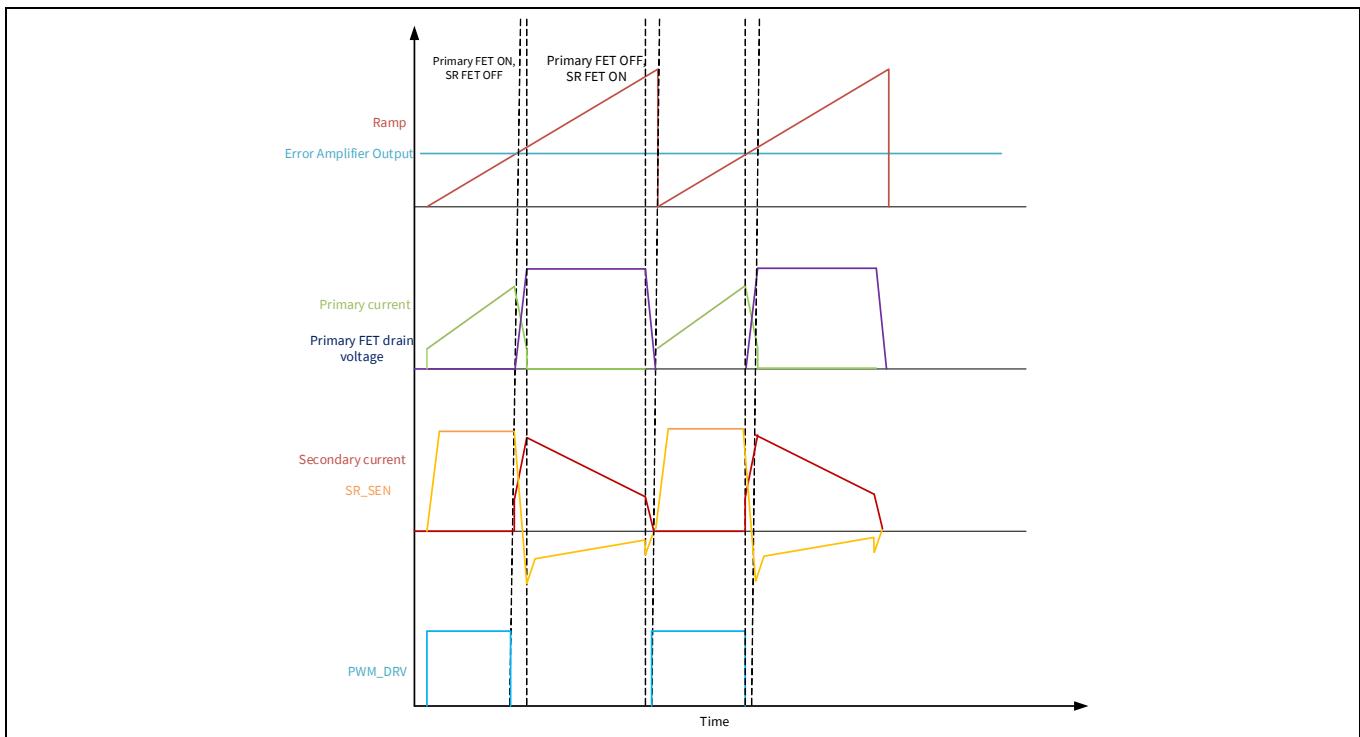

PAG2S-QZ 支持多种操作模式：QR 或 CrCM、谷底开关、DCM、CCM 和用于轻负载操作的突发模式。通过使用固件，可以配置最小 / 最大脉冲宽度、最小 / 最大周期以及脉冲跳跃或突发级别。[Figure 6](#) 到 [Figure 8](#) 显示了 QR/CrCM、谷底开关和 CCM 模式下 PWM\_DRV 的功能。

**Figure 6** QR/CrCM 模式下的 PWM\_DRV

## 功能说明

Figure 7 DCM/ 谷底开关模式下的 PWM\_DRV

## 功能说明

Figure 8 CCM 模式下的 PWM\_DRV

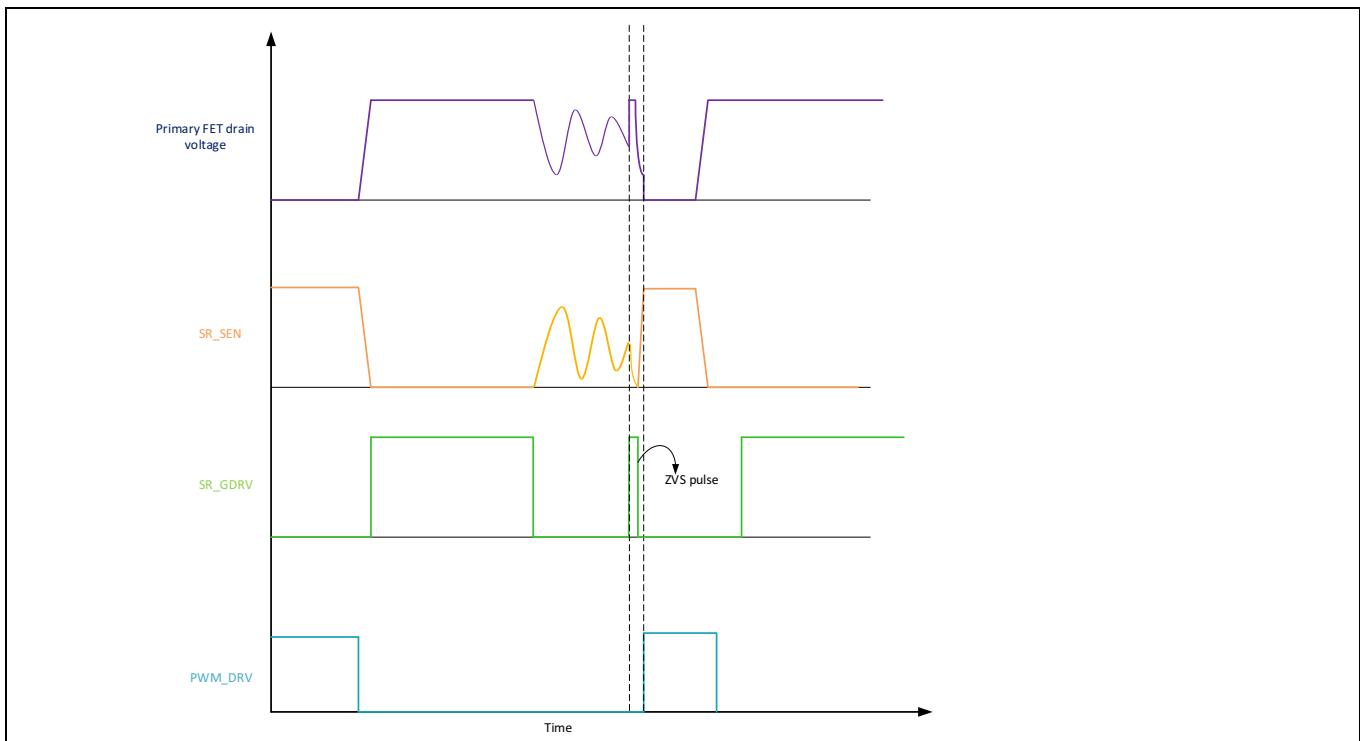

PAG2S-QZ 还支持零电压开关，即在驱动 PWM\_DRV 前短暂开启 SR\_GDRV，如图 Figure 9 所示。这意味着将初级漏极电压拉低，从而确保零电压开关。ZVS 脉冲宽度可通过固件配置，从而能够优化每个设计。

Figure 9 DCM 模式下的 ZVS

## 功能说明

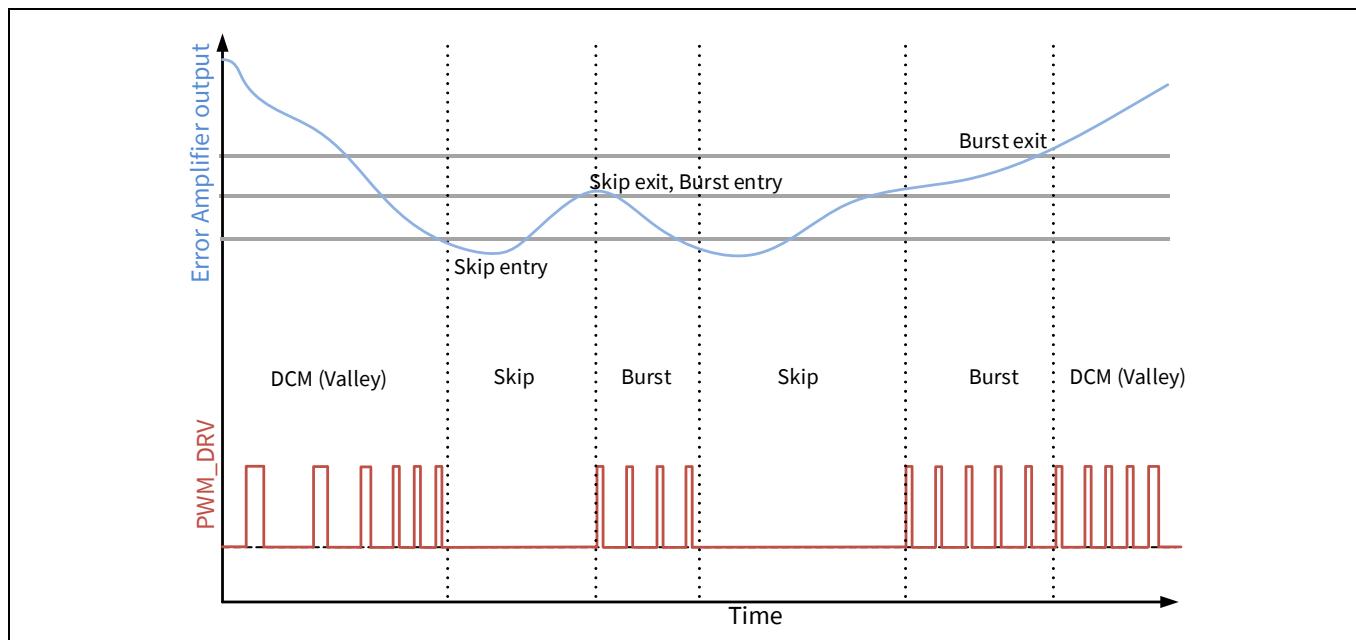

通过模拟 PWM 智能算法，可以根据输出功率要求在各种操作模式之间进行自动转换。对于较高负载，操作模式保持在 CrCM 中；对于中等负载，操作模式转为 DCM；对于低功率和超低功率负载，则操作模式切换到跳跃模式或突发模式（参见 Figure 10）。

Figure 10 误差放大器输出与操作模式

## 3.4 故障保护

### 3.4.1 VBUS OVP、UVP、OCP 和 SCP

VBUS 欠压和过压故障通过内部 VBUS\_IN/VBUS\_C 电阻分配器进行监控。VBus 过电流和短路故障均由内部电流检测放大器 (CSA) 监控。故障阈值和响应机制可通过固件配置。

### 3.4.2 过温保护

过温监控是通过使用一个外部热敏电阻和内部 ADC 完成的。热敏电阻可以连接到任何空闲的 GPIO。PAG2S-QZ 集成了 8 位 SAR ADC，可用于通用模数转换。故障阈值和响应机制可通过固件配置。

### 3.4.3 ESD、CC OVP 和 DP/DM OVP

PAG2S-QZ 为所有引脚提供 ESD 保护。此外，该芯片还集成了 CC 引脚到高电压 VBUS\_C 脚间的意外短路保护和 DP/DM 引脚上的过压保护。

## 3.5 电源模式

PAG2S-QZ 支持多种电源模式，包括运行、睡眠和深度睡眠等模式。这些模式之间的转换由应用程序固件根据操作条件进行处理。

## 3.6 MCU 子系统

PAG2S-QZ 不仅集成了一个具有 64 KB Flash、8 KB SRAM 和 64 KB ROM 的 32 位 Cortex®-M0+ MCU，还支持一个 TCPWM 和两个 ADC。

## 电气规范

**4 电气规范****4.1 最大绝对额定值****Table 3 最大绝对额定值**

| 参数             | 说明           | 最小值  | 典型值 | 最大值         | 单位 |

|----------------|--------------|------|-----|-------------|----|

| V_BUS_IN_MAX   | 最大输入供电电压     | -0.3 | -   | 34          | V  |

| V_DDD_MAX      | V_DDD 供电电压   | -    |     | 6           |    |

| V_SR_DRAIN_MAX | SR_SEN 引脚电压  |      |     | 34          |    |

| V_CC_PIN_ABS   | CC1、CC2 引脚电压 |      |     |             |    |

| V_GPIO_ABS     | GPIO 电压      | -0.5 |     | V_DDD + 0.5 |    |

| I_GPIO_ABS     | 每个 GPIO 上的电流 | -    |     | 25          | mA |

| I_LU           | 引脚闩锁电流       | -100 |     | 100         |    |

| ESD_HBM        | 人体静电放电模型     | -    |     | 2000        | V  |

| ESD_CDM        | ESD 带电器件模型   |      |     | 500         |    |

**4.2 器件级规范****Table 4 器件级规范**

| 参数           | 说明                             | 最小值         | 典型值 | 最大值  | 单位 | 详细信息 / 条件           |

|--------------|--------------------------------|-------------|-----|------|----|---------------------|

| <b>存储器大小</b> |                                |             |     |      |    |                     |

| FLASH_SIZE   | Flash 存储器大小                    | -           | 64  | -    | KB | SONOS Flash 容量 (字节) |

| SRAM_SIZE    | SRAM 存储器大小                     |             | 8   |      |    | SRAM 容量 (字节)        |

| SROM_SIZE    | SROM 存储器大小                     |             | 64  |      |    |                     |

| <b>芯片电源</b>  |                                |             |     |      |    |                     |

| V_DDD_REG    | VBUS 为 5.5V–30V 时的 VDDD 输出     | 4.6         | 5   | 5.4  | V  | -                   |

| V_DDD_MIN    | VBUS 为 3.15 V–5.5 V 时的 VDDD 输出 | VBUS – 0.33 | -   | -    |    |                     |

| V_BUS_IN     | 电源输入电压                         | 3.15        |     | 30.0 |    |                     |

| V_CCD        | 输出电压 (供给内核逻辑)                  | -           | 1.8 | -    |    |                     |

| V_DDWRITE    | 闪存写操作的供电电压                     | 3           | -   | 5.5  |    |                     |

| C_EFC        | 稳压器 V_CCD 脚外部的旁路电容             | 80          | 100 | 120  | nF | X5R 陶瓷电容器或性能更好的电容器  |

| C_EXC        | V_DDD 电源脚电容                    | 4           | 4.7 | -    | μF |                     |

| C_EXV        | V_BUS_IN 脚的去耦电容                | -           | 1   |      |    |                     |

| C_EXCPP      | SR_CPP 和 SR_CPN 引脚之间的电容        | 0.1         | -   |      |    |                     |

| I_GPIO_ABS   | 每个 GPIO 上的电流                   | -           |     | 25   | mA | 最大绝对值               |

## 电气规范

Table 4 器件级规范 (续)

| 参数                     | 说明                                                           | 最小值  | 典型值  | 最大值 | 单位            | 详细信息 / 条件                                                                                                                                                    |

|------------------------|--------------------------------------------------------------|------|------|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>SLEEP</sub>     | 从睡眠模式唤醒的时间                                                   | -    | 0    | -   | $\mu\text{s}$ | -                                                                                                                                                            |

| T <sub>DEEPSLEEP</sub> | 从深度睡眠模式唤醒的时间                                                 |      | 35   |     |               |                                                                                                                                                              |

| I <sub>DD_A</sub>      | 来自 V <sub>BUS_IN</sub> 的工作电流<br>(已连接 Type-C 型)               |      | 25.0 |     |               | V <sub>BUS_IN</sub> = 11 V,<br>T <sub>A</sub> = 25°C,<br>Tx 或 Rx 中的<br>CC1/CC2、<br>CPU 的工作频率为<br>24 MHz、<br>100 kHz 时的<br>SR/PWM<br>EA/ADC/CSA/UV OV<br>模块开启 |

| I <sub>DD_A1</sub>     | PWM 模式下来自 V <sub>BUS_IN</sub> 的电<br>流 (已连接 Type-C 型)         | 13.0 | 4    | 350 | $\mu\text{A}$ | V <sub>BUS_IN</sub> = 28 V,<br>T <sub>A</sub> = 25°C,<br>时钟频率为 24 MHz、<br>频率为 100 kHz 时的<br>SR/PWM、<br>SR Cap = 3 nF、<br>CC 上不发生切换                           |

| I <sub>DD_A3</sub>     | 低功耗 PWM 模式下来自<br>V <sub>BUS_IN</sub> 的电流<br>(已连接 Type-C 型)   |      |      |     |               |                                                                                                                                                              |

| I <sub>DD_DS1_UA</sub> | PWM 模式下来自 V <sub>BUS_IN</sub> 的深<br>度睡眠电流 (未连接 Type-C 型<br>) |      |      |     |               |                                                                                                                                                              |

| L <sub>SEC</sub>       | 次级侧电感                                                        | 3    | -    | -   | $\mu\text{H}$ | 次级侧电感                                                                                                                                                        |

电气规范

## 4.3 功能模块规范

**Table 5 功能模块规范**

| 参数             | 说明                                                                                                    | 最小值  | 典型值 | 最大值 | 单位  | 详细信息 / 条件                                          |

|----------------|-------------------------------------------------------------------------------------------------------|------|-----|-----|-----|----------------------------------------------------|

| <b>同步整流器</b>   |                                                                                                       |      |     |     |     |                                                    |

| VCPP1          | $V_{BUS} = 3.3\text{ V}-5.5\text{ V}$ 时倍压器的输出电压                                                       | 5    | -   | -   | V   | -                                                  |

| VCPP2          | $V_{BUS} = 5.5\text{ V}-30\text{ V}$ 时倍压器的输出电压                                                        | 9    |     | 11  |     |                                                    |

| TR_SR          | $C_L = 3\text{ nF}$ 时同步整流器栅极驱动器输出的上升时间 ( $1\text{ V}$ 至 $V_{OH} - 1\text{ V}$ ) (包括处于和不处于倍增器旁路模式两种情况) | -    |     | 60  | ns  |                                                    |

| TF_SR1         | $C_L = 3\text{ nF}$ 时同步整流器栅极驱动器输出的下降时间 ( $V_{OH} - 1\text{ V}$ 至 $1\text{ V}$ ) (处于倍增器模式)             |      | 25  | 50  |     |                                                    |

| TF_SR2         | $C_L = 3\text{ nF}$ 时同步整流器栅极驱动器输出的下降时间 ( $V_{OH} - 1\text{ V}$ 至 $1\text{ V}$ ) (处于倍增器旁路模式)           |      | 15  | 30  |     |                                                    |

| VTRIP_NSN_100  | 用于开启次级开关的负值检测触发电压                                                                                     | 50   | 100 | 150 | mV  |                                                    |

| VTRIP_ZCD      | 用于关闭次级开关的负值检测触发电压                                                                                     | -8   | -5  | -3  |     |                                                    |

| VTRIP_ZCDF     | 通过快速 ZCD 关闭次级开关时所需要的触发电压                                                                              | 0    | 7   | 10  |     |                                                    |

| TD_ON          | 从电压为 $100\text{ mV}$ 时的 SR_DRAIN 到 SR_GDRV 达到 $1\text{ V}$ 之间的开通延迟                                    | -    | 40  | 80  | ns  |                                                    |

| IO_SRC_SNK     | 输出峰值电流 (源电流和灌电流)                                                                                      | -    | 1   | -   | A   |                                                    |

| TR_SR1         | $C_L = 3\text{ nF}$ 时同步整流器栅极驱动器输出的上升时间 ( $1\text{ V}$ 至 $V_{OH} - 1\text{ V}$ ) (处于倍增器模式)             | -    | -   | 75  | ns  |                                                    |

| TR_SR2         | $C_L = 3\text{ nF}$ 时同步整流器栅极驱动器输出的上升时间 ( $1\text{ V}$ 至 $V_{OH} - 1\text{ V}$ ) (处于倍增器旁路模式)           | -    | -   | 30  |     |                                                    |

| <b>PWM</b>     |                                                                                                       |      |     |     |     |                                                    |

| FSW            | 工作静态电流                                                                                                | 20   | -   | 300 | kHz | -                                                  |

| PWM_ON         | 最短可控制开启时间                                                                                             | 100  |     | -   | ns  |                                                    |

| $V_{OL\_PTDR}$ | 脉冲边沿变压器驱动器输出端的低电平输出电压 ( $I_{Sink} = 8\text{ mA}$ )                                                    | -    | -   | 0.5 | V   | $V_{DDD} = 3\text{ V}$ ,<br>$I_{ol} = 8\text{ mA}$ |

| <b>GPIO</b>    |                                                                                                       |      |     |     |     |                                                    |

| I_LU           | 闩锁电流限制                                                                                                | -100 | -   | 100 | mA  | -                                                  |

| RPU            | 上拉电阻值                                                                                                 | 3.5  | 5.6 | 8.5 | kΩ  |                                                    |

| RPD            | 下拉电阻值                                                                                                 |      |     |     |     |                                                    |

## 电气规范

Table 5 功能模块规范 (续)

| 参数                     | 说明                                                                        | 最小值                    | 典型值  | 最大值                    | 单位                                  | 详细信息 / 条件                                          |  |  |

|------------------------|---------------------------------------------------------------------------|------------------------|------|------------------------|-------------------------------------|----------------------------------------------------|--|--|

| I <sub>IL</sub>        | 输入漏电流<br>( 绝对值 )                                                          | -                      | -    | 2                      | nA                                  | T <sub>A</sub> = +25 °C、<br>V <sub>DDD</sub> = 3 V |  |  |

| C <sub>PIN_A</sub>     | 最大引脚电容                                                                    |                        |      | 22                     | pF                                  | DP、DM 引脚上的电容                                       |  |  |

| C <sub>PIN</sub>       | 3                                                                         |                        | 7    |                        | 所有 V <sub>DDD</sub> 值、<br>所有其他 GPIO |                                                    |  |  |

| V <sub>OH</sub>        | 高电平输出电压                                                                   | V <sub>DDD</sub> - 0.6 | -    | -                      | V                                   | I <sub>oh</sub> = -4 mA                            |  |  |

| V <sub>OL</sub>        | 低电平输出电压                                                                   | -                      |      | 0.6                    |                                     | I <sub>ol</sub> = 10 mA                            |  |  |

| V <sub>IH_CMOS</sub>   | 高电平输入电压阈值                                                                 | 0.7 × V <sub>DDD</sub> |      | -                      |                                     | -                                                  |  |  |

| V <sub>IL_CMOS</sub>   | 低电平输入电压阈值                                                                 | -                      |      | 0.3 × V <sub>DDD</sub> |                                     |                                                    |  |  |

| V <sub>IH_TTL</sub>    | TTL 高电平输入                                                                 | 2                      |      | -                      |                                     |                                                    |  |  |

| V <sub>IL_TTL</sub>    | TTL 低电平输入                                                                 | -                      | 0.8  | 0.8                    | mV                                  |                                                    |  |  |

| V <sub>HYSTTTL</sub>   | LVTTL 输入迟滞电压                                                              | 80                     |      | -                      |                                     |                                                    |  |  |

| V <sub>HYSCMOS</sub>   | CMOS 输入迟滞电压                                                               | 0.1 × V <sub>DDD</sub> |      | -                      |                                     |                                                    |  |  |

| IDIODE                 | 通过保护二极管到达 V <sub>DDD</sub> /V <sub>SS</sub> 的电流                           | -                      |      | 100.0                  | μA                                  |                                                    |  |  |

| T <sub>RISEF</sub>     | 快速强驱动模式下的上升时间                                                             | 1                      | 15   | ns                     | C <sub>LOAD</sub> = 25 pF           |                                                    |  |  |

| T <sub>FALLF</sub>     | 快速强驱动模式下的下降时间                                                             |                        | 15.0 |                        |                                     | -                                                  |  |  |

| T <sub>RISES</sub>     | 慢速强驱动模式下的上升时间                                                             | 10                     | 70   |                        |                                     |                                                    |  |  |

| T <sub>FALLS</sub>     | 慢速强驱动模式下的下降时间                                                             |                        |      |                        |                                     |                                                    |  |  |

| F <sub>GPIO_OUT1</sub> | GPIO F <sub>OUT</sub> ;<br>2.85 V ≤ V <sub>DDD</sub> ≤ 5.5 V。<br>快速强驱动模式。 | -                      | -    | 28                     | MHz                                 | -                                                  |  |  |

| F <sub>GPIO_OUT2</sub> | GPIO F <sub>OUT</sub> ;<br>2.85 V ≤ V <sub>DDD</sub> ≤ 5.5 V。<br>慢速强驱动模式。 |                        |      | 6                      |                                     |                                                    |  |  |

| F <sub>GPIO_IN</sub>   | GPIO 输入工作频率;<br>2.85 V ≤ V <sub>DDD</sub> ≤ 5.5 V。                        |                        |      | 28                     |                                     |                                                    |  |  |

## 电气规范

**Table 5 功能模块规范 (续)**

| 参数                     | 说明                                  | 最小值      | 典型值 | 最大值      | 单位   | 详细信息 / 条件                                   |

|------------------------|-------------------------------------|----------|-----|----------|------|---------------------------------------------|

| <b>Flash 宏</b>         |                                     |          |     |          |      |                                             |

| FLASH_ERASE            | 行擦除时间                               | -        | -   | 15.5     | ms   | -                                           |

| FLASH_WRITE            | 行(块)编写时间(擦除和编程)                     |          |     | 20       |      |                                             |

| FLASH_DR               | 闪存数据保持时间                            | 15       |     | -        | 年    | 25°C ~ 55°C、所有 VDDD 值                       |

| FLASH_ENPB             | 闪存写入耐久次数                            | 100 K    |     |          | 周期   | 25°C ~ 85°C、所有 VDDD 值                       |

| FLASH_ENPB1            | 闪存写入耐久次数                            | 10 K     |     |          |      | 25°C ~ 125°C、所有 VDDD 值                      |

| FLASH_ROW_PGM          | 擦除后的行编程时间                           | -        |     | 7        | ms   | -                                           |

| T_BULKERASE            | 批量擦除时间(32 KB)                       |          |     | 35       |      |                                             |

| T_DEVPROG              | 器件总编程时间                             |          |     | 7.5      | 秒    |                                             |

| FRET1                  | 闪存数据保持时间、TA ≤ 55°C、100k P/E 周期      | 15       |     | -        | 年    | -                                           |

| FRET2                  | 闪存数据保持时间、TA ≤ 85°C、10k P/E 周期       | 10       |     |          |      |                                             |

| FRET3                  | 闪存数据保持时间、TA ≤ 105°C、10k P/E 周期      | 3        |     |          |      |                                             |

| <b>SWD</b>             |                                     |          |     |          |      |                                             |

| F_SWDCLK1              | 所有 VDDD 值                           | -        | -   | 14       | MHz  | -                                           |

| T_SWDI_SETUP           | T = 1/f SWDCLK                      | 0.25 × T |     | -        | ns   |                                             |

| T_SWDI_HOLD            |                                     |          |     |          |      |                                             |

| T_SWDO_VALID           |                                     |          |     | 0.50 × T |      |                                             |

| T_SWDO_HOLD            |                                     | 1        |     | -        |      |                                             |

| <b>ILO / IMO / POR</b> |                                     |          |     |          |      |                                             |

| FIMO                   | IMO 频率                              | 24       | 36  | 48       | MHz  | -                                           |

| IMO_STL                | 更改校准寄存器时的 IMO 建立时间                  | -        | -   | 200      | ns   | TA = 25 °C、所有 VDDD 值、48 MHz ≥ FIMO ≥ 24 MHz |

| FCPU                   | CPU 输入频率                            |          |     | 48       | MHz  | -                                           |

| FILO                   | ILO 频率                              | 15       | 40  | 80       | kHz  |                                             |

| SR_POWER_UP            | 上电期间的电源上电斜率                         | -        | -   | 67       | V/ms |                                             |

| FIMOTOL                | 在频率为 24 MHz 和 48 MHz 时测量频率差异(出厂调整后) | -2       |     | 2        | %    |                                             |

| TSTARTIMO              | IMO 启动时间                            | -        |     | 7        | μs   |                                             |

| TSTARTILO1             | ILO 启动时间                            |          |     | 2        | ms   |                                             |

| EXTCLKFREQ             | 外部时钟输入频率                            |          |     | 16       | MHz  |                                             |

| EXTCLKDUTY             | 占空比; 在 VDD/2 条件下测量得到                | 45       |     | 55       | %    |                                             |

| TCLKSWITCH             | 系统时钟源的切换时间                          | 3        |     | 4        | 周期   |                                             |

## 电气规范

**Table 5 功能模块规范 (续)**

| 参数                    | 说明                               | 最小值              | 典型值 | 最大值            | 单位  | 详细信息 / 条件                           |  |

|-----------------------|----------------------------------|------------------|-----|----------------|-----|-------------------------------------|--|

| $V_{RISEIPOR}$        | 上电复位 (POR) 上升触发电压                | 0.72             | -   | 1.5            | V   | -                                   |  |

| $V_{FALLIPOR}$        | POR 下降触发电压                       | 0.62             |     | 1.4            |     |                                     |  |

| $V_{DDD\_BOD}$        | 运行 / 睡眠模式下欠压检测 (BOD) 触发电压        | 2.34             |     | 3              |     |                                     |  |

| $V_{CCD\_BOD}$        |                                  | 1.64             |     | 2              |     |                                     |  |

| $V_{CCD\_BOD\_DPSLP}$ |                                  | 1.1              |     | 2              |     |                                     |  |

| <b>定时器</b>            |                                  |                  |     |                |     |                                     |  |

| SYS_TIM_RES           | 系统定时器分辨率                         | -                | 16  | -              | 位   | -                                   |  |

| WDT_RES               | WDT 分辨率                          |                  | 16  |                |     |                                     |  |

| <b>TCPWM</b>          |                                  |                  |     |                |     |                                     |  |

| TCPWM_FREQ            | 工作频率                             | -                | -   | F <sub>c</sub> | MHz | F <sub>c</sub> max = CLK_SYS        |  |

| T <sub>PWMEXT</sub>   | 输出触发脉冲宽度                         | 2/F <sub>c</sub> |     | -              | ns  | 上溢、下溢和 CC<br>(计数值等于比较值)<br>可输出的最小宽度 |  |

| T <sub>CRES</sub>     | 计数器分辨率                           | 1/F <sub>c</sub> |     |                |     | 连续计数间的最短时间                          |  |

| PWM_RES               | PWM 分辨率                          |                  |     |                |     | PWM 输出的最小脉宽                         |  |

| <b>PD 收发器</b>         |                                  |                  |     |                |     |                                     |  |

| vSwing                | 发送器输出高电压                         | 1.05             | -   | 1.2            | V   | -                                   |  |

| vSwing_low            | 发送器输出低电压                         |                  |     | 0.075          |     |                                     |  |

| zDriver               | 发送器输出阻抗                          | 33               |     | 75             |     |                                     |  |

| Idac_std              | USB 标准告示的源电流                     | 64               |     | 96             | μA  |                                     |  |

| Idac_1p5a             | 5 V 告示条件下 1.5 A 的源电流             | 166              |     | 194            |     |                                     |  |

| Idac_3a               | 5 V 告示条件下 3 A 的源电流               | 304              |     | 356            |     |                                     |  |

| zOPEN                 | 该信号被禁用时 CC 阻抗接地                  | 108              | -   | -              | kΩ  | -                                   |  |

| DFP_default_0p2       | DFP 侧的 CC 电压 - 标准 USB            | 0.15             |     | 0.25           | V   |                                     |  |

| DFP_1.5A_0p4          | DFP 侧的 CC 电压 - 1.5 A             | 0.35             |     | 0.5            |     |                                     |  |

| DFP_3A_0p8            | DFP 侧的 CC 电压 - 3 A               | 0.75             |     | 0.85           |     |                                     |  |

| DFP_3A_2p6            | DFP 侧的 CC 电压 - 3 A               | 2                |     | 2.75           |     |                                     |  |

| Vattach_ds            | 深度睡眠连接阈值                         | 0.30             |     | 0.6            | -   |                                     |  |

| Rattach_ds            | 深度睡眠上拉电阻                         | 10               |     | 50             | kΩ  |                                     |  |

| <b>LSCSA 直流规范</b>     |                                  |                  |     |                |     |                                     |  |

| Csa_Acc1              | 5 mV < Vsense < 10 mV 时的 CSA 精度  | -0.75            | -   | 0.75           | mV  | -                                   |  |

| Csa_Acc2              | 10 mV < Vsense < 15 mV 时的 CSA 精度 |                  |     |                |     |                                     |  |

| Csa_Acc3              | 15 mV < Vsense < 25 mV 时的 CSA 精度 |                  |     |                |     |                                     |  |

| Csa_Acc4              | Vsense = 50 mV 时的 CSA 精度         |                  |     |                |     |                                     |  |

## 电气规范

**Table 5 功能模块规范 (续)**

| 参数            | 说明                           | 最小值 | 典型值 | 最大值 | 单位  | 详细信息 / 条件 |

|---------------|------------------------------|-----|-----|-----|-----|-----------|

| SCP_6A        | 电流为 6 A 时的短路电流检测             | 5.4 | 6   | 6.6 | A   | -         |

| SCP_10A       | 电流为 10 A 时的短路电流检测            | 9   | 10  | 11  |     |           |

| SCP_20A       | 电流为 20 A 时的短路电流检测            | 18  | 20  | 22  |     |           |

| OCP threshold | 电阻为 5 mΩ、电流 > 4 A 时的 OCP 触发值 | 117 | 130 | 143 |     |           |

| Av            | 受支持的额定增益值：40、60              | 30  | -   | 60  | V/V |           |

**LSCSA 交流规范**

|                         |                                |   |     |   |    |                                           |

|-------------------------|--------------------------------|---|-----|---|----|-------------------------------------------|

| T <sub>SCP_GATE</sub>   | 从 SCP 阈值触发到外部 NFET 电源栅极关闭的延迟时间 | - | 2.5 | - | μs | 1 nF NFET 栅极电容、V <sub>BUS_IN</sub> = 28 V |

| T <sub>SCP_GATE_1</sub> |                                |   | 7.5 |   |    | 3 nF NFET 栅极电容、V <sub>BUS_IN</sub> = 28 V |

**UVOV**

|        |                 |    |   |   |   |   |

|--------|-----------------|----|---|---|---|---|

| VTTHOV | 过压阈值精度，4 V–30 V | -3 | - | 3 | % | - |

| VTHUV1 | 欠压阈值精度，3 V–4 V  | -4 |   | 4 |   |   |

| VTHUV2 | 欠压阈值精度，4 V–30 V | -3 |   | 3 |   |   |

**V<sub>BUS</sub> 栅极驱动器直流规范**

|        |                       |     |   |      |    |                                         |

|--------|-----------------------|-----|---|------|----|-----------------------------------------|

| GD_VGS | 在打开状态条件下栅极与源极之间的过驱动电压 | 5   | - | 10   | V  | NFET 驱动器为打开状态                           |

| GD_RPD | 下拉启用时的电阻              | -   |   | 2    | kΩ | 在 V <sub>BUS_CTRL</sub> 上使用该电阻关闭外部 NFET |

| GD_drv | 可编程的典型栅极电流            | 0.3 |   | 9.75 | μA | 栅极驱动器输出电流                               |

**V<sub>BUS</sub> 栅极驱动器交流规范**

|                  |                                                                                |   |     |    |    |                            |

|------------------|--------------------------------------------------------------------------------|---|-----|----|----|----------------------------|

| T <sub>ON</sub>  | 外部电容为 3 nF 时 V <sub>BUS_CTRL</sub> 从低电平到高电平 (1 V 到 V <sub>BUS</sub> + 1 V) 的时长 | 2 | 5   | 10 | ms | V <sub>BUS_IN</sub> = 5 V  |

| T <sub>OFF</sub> | 外部电容为 3 nF 时 V <sub>BUS_CTRL</sub> 从高电平到低电平 (从 90% 降至 10%) 的时长                 | - | 7.5 | -  | μs | V <sub>BUS_IN</sub> = 28 V |

**V<sub>BUS</sub> 放电**

|     |                                             |      |   |      |   |                  |

|-----|---------------------------------------------|------|---|------|---|------------------|

| R1  | DS = 1 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗  | 1000 | - | 4000 | Ω | 在电压为 0.5 V 时测量得到 |

| R2  | DS = 2 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗  | 500  |   | 2000 |   |                  |

| R4  | DS = 4 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗  | 250  |   | 1000 |   |                  |

| R8  | DS = 8 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗  | 125  |   | 500  |   |                  |

| R16 | DS = 16 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗 | 62.5 |   | 250  |   |                  |

## 电气规范

**Table 5 功能模块规范 (续)**

| 参数                          | 说明                                        | 最小值   | 典型值 | 最大值  | 单位 | 详细信息 / 条件                     |

|-----------------------------|-------------------------------------------|-------|-----|------|----|-------------------------------|

| R32                         | DS=32 时 V <sub>BUS_IN</sub> 上的 NMOS ON 阻抗 | 31.25 | -   | 150  | -  | 在电压为 0.5 V 时测量得到              |

| V <sub>BUS_Stop_Error</sub> | 最终V <sub>BUS</sub> 值与设置值的百分比差值            | -     |     | 10   | %  | V <sub>BUS</sub> 放电至 5 V 的情况下 |

| R1A                         | DS=1 时 V <sub>BUS_C</sub> 上的 NMOS ON 阻抗   | 1000  |     | 2000 | Ω  | 在电压为 0.5 V 时测量得到              |

| R127A                       | DS=127 时 V <sub>BUS_C</sub> 上的 NMOS ON 阻抗 | 6.5   |     | 38   |    |                               |

**电压调节直流规范**

|                     |                                |     |     |    |    |   |

|---------------------|--------------------------------|-----|-----|----|----|---|

| V <sub>OUT</sub>    | 典型的 V <sub>BUS_IN</sub> 输出电压范围 | 3.3 | -   | 28 | V  | - |

| VR                  | V <sub>BUS</sub> 电压调节精度        | -   | ±3  | ±5 | %  |   |

| I <sub>ka_off</sub> | 断开状态阴极电流                       |     | 2.2 | 10 | μA |   |

**V<sub>BUS</sub> 调节器规范**

|                    |                                |      |     |     |    |   |

|--------------------|--------------------------------|------|-----|-----|----|---|

| VOLTAGE_DETECT     | V <sub>BUS_IN</sub> 上的电压检测阈值电压 | 1.65 | 2.1 | 2.4 | V  | - |

| T <sub>START</sub> | 负载电容为 4.7 μF 时调节器电源输出的总启动时间    | -    | 50  | 200 | μs |   |

**ADC 直流规范**

|            |           |                     |   |                     |     |                            |

|------------|-----------|---------------------|---|---------------------|-----|----------------------------|

| Resolution | ADC 分辨率   | -                   | 8 | -                   | 位   | -                          |

| INL        | 积分非线性     | -2.5                | - | 2.5                 | LSB | 由 V <sub>DDD</sub> 生成的参考电压 |

| INL        | 积分非线性     | -1.5                | - | 1.5                 |     | 带隙生成的参考电压                  |

| VREF_ADC1  | ADC 的参考电压 | V <sub>DDDmin</sub> |   | V <sub>DDDmax</sub> | V   | 由 V <sub>DDD</sub> 生成的参考电压 |

| VREF_ADC2  |           | 1.96                | 2 | 2.04                |     | 带隙生成的参考电压                  |

**VCONN 开关规范**

|                   |                                                        |     |   |    |    |   |

|-------------------|--------------------------------------------------------|-----|---|----|----|---|

| VCONN_OUT         | 负载电流为 20 mA、V <sub>bus</sub> =5 V-30 V 时的 VCONN 最小输出电压 | 4.5 | - | -  | V  | - |

| I <sub>LEAK</sub> | 连接器端引脚漏电流                                              | -   |   | 10 | μA |   |

**VCONN 开关交流规范**

|                  |        |   |   |     |    |   |

|------------------|--------|---|---|-----|----|---|

| T <sub>ON</sub>  | 开关打开时间 | - | - | 600 | μs | - |

| T <sub>OFF</sub> | 开关关闭时间 |   |   | 10  |    |   |

## 订购信息

## 5 订购信息

**Table 6 PAG2S-QZ 订购信息**

| MPN                | 应用程序                          | 封装类型       | 芯片 ID | 芯片版本 |

|--------------------|-------------------------------|------------|-------|------|

| CYPAS211A1-32LQXQ  | USB PD 适配器 – 使用 ZVS 的次级侧反激式控制 | 32-pin QFN | 3B10  | A1   |

| CYPAS211A1-32LQXQT |                               |            |       |      |

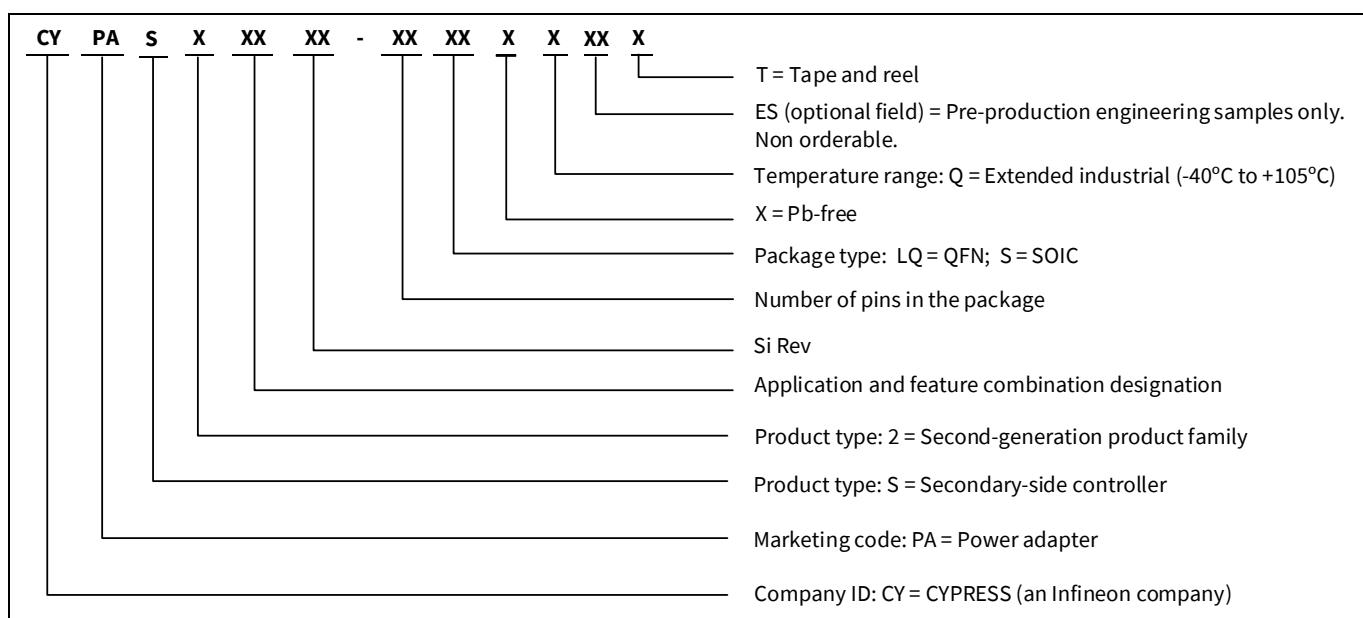

### 5.1 订购代码定义

封装

## 6 封装

**Table 7 封装特性**

| 参数              | 说明                                | 条件     | 最小值 | 典型值  | 最大值 | 单位   |

|-----------------|-----------------------------------|--------|-----|------|-----|------|

| T <sub>A</sub>  | 工作环境温度                            | 扩展的工业级 | -40 | -    | 105 | °C   |

| T <sub>J</sub>  | 工作结温                              |        |     |      | 150 |      |

| T <sub>JA</sub> | 用于 32-pin QFN 的封装 θ <sub>JA</sub> | -      | -   | 23.4 | -   | °C/W |

| T <sub>JB</sub> | 用于 32-pin QFN 的封装 θ <sub>JB</sub> |        |     | 4.85 |     |      |

| T <sub>JC</sub> | 用于 32-pin QFN 的封装 θ <sub>JC</sub> |        |     | 27.2 |     |      |

**Table 8 回流焊峰值温度**

| 封装         | 最高峰值温度 | 在与峰值温度相差 5 °C 时的最长时间 |

|------------|--------|----------------------|

| 32-pin QFN | 260 °C | 30 秒                 |

**Table 9 封装湿度敏感性等级 (MSL), IPC/JEDEC J-STD-2**

| 封装         | MSL  |

|------------|------|

| 32-pin QFN | MSL3 |

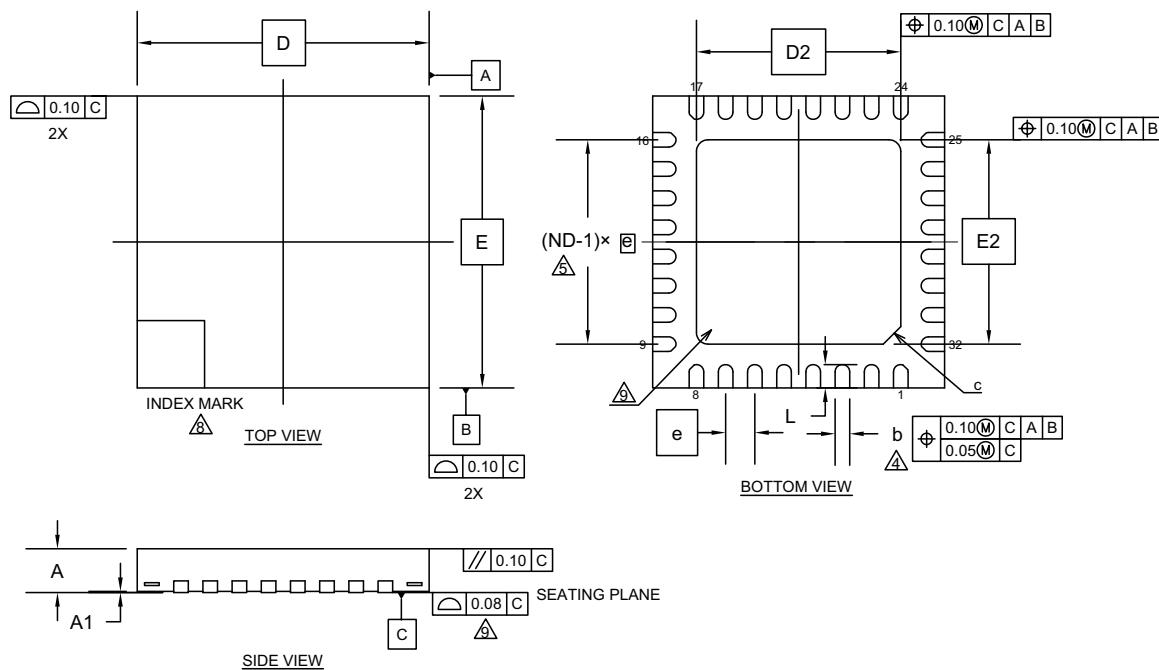

## 封装

| SYMBOL | DIMENSIONS |      |      |

|--------|------------|------|------|

|        | MIN.       | NOM. | MAX. |

| A      | —          | —    | 0.80 |

| A1     | 0.00       | —    | 0.05 |

| D      | 5.00 BSC   |      |      |

| E      | 5.00 BSC   |      |      |

| b      | 0.18       | 0.25 | 0.30 |

| D2     | 3.50 BSC   |      |      |

| E2     | 3.50 BSC   |      |      |

| e      | 0.50 BSC   |      |      |

| c      | 0.30 REF   |      |      |

| L      | 0.35       | 0.40 | 0.45 |

**NOTE**

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING CONFORMS TO ASME Y14.5-1994.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL TIP. IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION "b" SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

5. AND REFER TO THE NUMBER OF TERMINALS ON D OR E SIDE.

6. MAX. PACKAGE WARPAGE IS 0.05mm.

7. MAXIMUM ALLOWABLE BURRS IS 0.076mm IN ALL DIRECTIONS.

8. PIN #1 ID ON TOP WILL BE LOCATED WITHIN INDICATED ZONE.

9. BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

10. JEDEC SPECIFICATION NO. REF : N/A

002-15160 Rev. \*\*

**Figure 11 32-lead QFN ((5.0 × 5.0 × 0.8 mm) WNP032 3.5 × 3.5 mm E-pad (Sawn)) 封装外形 (PG-VQFN-32), 002-15160**

缩略语

## 7 缩略语

Table 10 本文档中使用的首字母缩略语

| 缩略语     | 说明                     |

|---------|------------------------|

| ADC     | 模数转换器                  |

| Arm®    | 高级 RISC 机器，即为一种 CPU 架构 |

| BOD     | 欠压检测                   |

| BMC     | 双相标记编码                 |

| CC      | 恒流                     |

| CCM     | 连续导通模式                 |

| CPU     | 中央处理单元                 |

| CrCM    | 临界导通模式                 |

| CS      | 电流感应                   |

| CSA     | 电流检测放大器                |

| CSN     | 电流检测负值                 |

| CSP     | 电流检测正值                 |

| DCM     | 非连续导通模式                |

| DFP     | 下行端口                   |

| DM      | 数据减                    |

| DP      | 数据加                    |

| DS      | 驱动强度                   |

| EA      | 误差放大器                  |

| EMI     | 电磁干扰                   |

| EPR     | 扩展功率范围                 |

| ESD     | 静电放电                   |

| ESD-HBM | 人体静电放电模型               |

| FB      | 反馈                     |

| FS      | 全速                     |

| GPIO    | 通用输入 / 输出              |

| ILO     | 内部低速振荡器，另请参见 IMO       |

| IMO     | 内部主振荡器，另请参见 ILO        |

| I/O     | 输入 / 输出，另请参见 GPIO      |

| LDO     | 低压差调节器                 |

| LSSCSA  | 低侧电流检测放大器              |

| LVTTL   | 低电压晶体管 – 晶体管逻辑         |

| NFET    | N 通道场效应晶体管             |

| NMOS    | N 型金属氧化物半导体            |

| OCP     | 过流保护                   |

| OVP     | 过压保护                   |

| OTP     | 过温保护                   |

| PD      | 功率传输                   |

## 缩略语

**Table 10 本文档中使用的首字母缩略语（续）**

| 缩略语    | 说明                                      |

|--------|-----------------------------------------|

| PHY    | 物理层                                     |

| POR    | 上电复位                                    |

| PPS    | 可编程电源                                   |

| PSM    | 脉冲跳跃模式                                  |

| PWM    | 脉宽调制器                                   |

| QR     | 准谐振                                     |

| RAM    | 随机存取存储器                                 |

| RISC   | 精简指令集计算                                 |

| RMS    | 均方根                                     |

| RX     | 接收                                      |

| SAR    | 逐次逼近寄存器                                 |

| SCL    | I <sup>2</sup> C 串行时钟                   |

| SCP    | 短路保护                                    |

| SDA    | I <sup>2</sup> C 串行数据                   |

| SPI    | 串行外设接口，即为一种通信协议                         |

| SR     | 同步整流器                                   |

| SRAM   | 静态随机访问存储器                               |

| SWD    | 串行线调试，即为一种测试协议                          |

| SWDCLK | 串行线调试时钟                                 |

| TCPWM  | 定时器 / 计数器 / PWM                         |

| TX     | 发送                                      |

| Type-C | USB 连接器更细长，并且线缆可反向使用的新标准，能够提供 100 W 的电源 |

| USB    | 通用串行总线                                  |

| USB PD | USB 功率传输                                |

| WDT    | 看门狗定时器                                  |

| XRES   | 外部复位 I/O 引脚                             |

| ZCD    | 过零检测                                    |

| ZVS    | 零电压开关                                   |

## 8 文档规范

### 8.1 测量单位

**Table 11 测量单位**

| 符号   | 测量单位    |

|------|---------|

| °C   | 摄氏度     |

| Hz   | 赫兹      |

| KB   | 1024 字节 |

| kHz  | 千赫兹     |

| kΩ   | 千欧      |

| Mbps | 兆比特每秒   |

| MHz  | 兆赫      |

| MΩ   | 兆欧姆     |

| MspS | 每秒采样百万次 |

| μA   | 微安      |

| μF   | 微法      |

| μs   | 微秒      |

| μV   | 微伏      |

| μW   | 微瓦      |

| mA   | 毫安      |

| ms   | 毫秒      |

| mV   | 毫伏      |

| nA   | 纳安      |

| ns   | 纳秒      |

| Ω    | 欧姆      |

| pF   | 皮法      |

| ppm  | 百万分比    |

| ps   | 皮秒      |

| s    | 秒       |

| sps  | 每秒采样数   |

| V    | 伏特      |

## 修订记录

## 修订记录

| 文档版本 | 日期         | 变更说明                     |

|------|------------|--------------------------|

| **   | 2023-11-30 | 翻译自 : 002-37216 Rev. *B。 |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2023-11-30**

**Published by**

**Infineon Technologies AG

81726 Munich, Germany**

**© 2023 Infineon Technologies AG.

All Rights Reserved.**

**Do you have a question about this

document?**

**Email:**

[erratum@infineon.com](mailto:erratum@infineon.com)

**Document reference

002-39077 Rev. \*\***

### 重要提示

本文档所提供的任何信息**绝不应当**被视为针对任何条件或者品质而做出的保证（质量保证）。英飞凌对于本文档中所提及的任何事例、提示或者任何特定数值及 / 或任何关于产品应用方面的信息均在此明确声明其不承担任何保证或者责任，包括但不限于其不侵犯任何第三方知识产权的保证均在此排除。

此外，本文档所提供的任何信息均取决于客户履行本文档所载明的义务和客户遵守适用于客户产品以及与客户对于英飞凌产品的应用所相关的任何法律要求、规范和标准。

本文档所含的数据仅供经过专业技术培训的人员使用。客户自身的技术部门有义务对于产品是否适宜于其预期的应用和针对该等应用而言本文档中所提供的信息是否充分自行予以评估。

### 警告事项

由于技术所需产品可能含有危险物质。如需了解该等物质的类型，请向离您最近的英飞凌科技办公室接洽。

除非由经英飞凌科技授权代表签署的书面文件中做出另行明确批准的情况下，英飞凌科技的产品不应当被用于任何一项一旦产品失效或者产品使用的后果可被合理地预料到可能导致人身伤害的任何应用领域。