# USB PD および二次側 QR-ZVS コントローラー 搭載 EZ-PD™ PAG2S-QZ

## 概要説明

EZ-PD™ PAG2S-QZ CYPAS211 は、二次側 PWM コントローラーと USB Power Delivery (USB PD) コントローラーを統合した製品です。PAG2S-QZ は、二次側同期整流器 (SR), パルス幅変調器 (PWM) およびゼロ電圧スイッチング (ZVS) 制御を搭載しています。PAG2S-QZ は USB-C 電源アダプタを対象として、USB PD, Qualcomm Quick Charge, およびその他の標準充電プロトコルを備えた高効率 AC-DC フライバック設計によく適合します。PAG2S-QZ CYPAS211 は、USB Power Delivery 拡張電力範囲 (EPR) モードもサポートしています。

## アプリケーション

- USB-C 充電器とアダプタ

- EPR 対応の USB-C 充電器とアダプタ

- USB PD とレガシー充電の両方をサポートする電源アダプタ

## 特長

- 二次側フライバック コントローラーと充電ポート コントローラーを統合

- 二次側同期整流器 (SR)、ZVS サポート付きの PWM 制御を搭載

- 擬似共振 (QR) または臨界導通モード (CrCM), バレースイッチング, 不連続導通モード (DCM), および連続導通モード (CCM) での同期整流に対応し、最大 300 kHz のスイッチング周波数をサポート

- 軽負荷動作用のバースト モードをサポート

- SR ドライバーは標準 MOSFET と論理レベル MOSFET の両方に対応

- USB PD 3.1 準拠であり、最大 28V VBUS の EPR に対応

- プログラマブル電源 (PPS) を含む USB PD 2.0 と PD 3.0, QC 5.0, QC4+, QC 4.0, QC 3.0, QC 2.0, Samsung AFC, Apple Charging, および Battery Charging (BC) v1.2 の充電プロトコルをサポート

- ローサイド電流検出アンプ (LSCSA)、2x VBUS 放電 FET、ロードスイッチを駆動する NFET ゲートドライバーと EMCA ケーブルをサポートする VCONN FET を内蔵

- 構成可能な VBUS 過電圧保護 (OVP), 低電圧保護 (UVP), 過電流保護 (OCP), 短絡保護 (SCP), およびシステム過熱保護 (OTP)

- VBUS-CC 短絡保護, CC, VBUS, DP/DM ライン上の静電気放電 (ESD) 保護, および DP/DM ライン上の過電圧保護

- 64 KB フラッシュ, 8 KB SRAM, および 64 KB ROM を備えた 32 ビット Cortex® M0+ を搭載

- ジャンクション温度範囲が -40°C ~ +150°C の 32 ピン QFN パッケージ

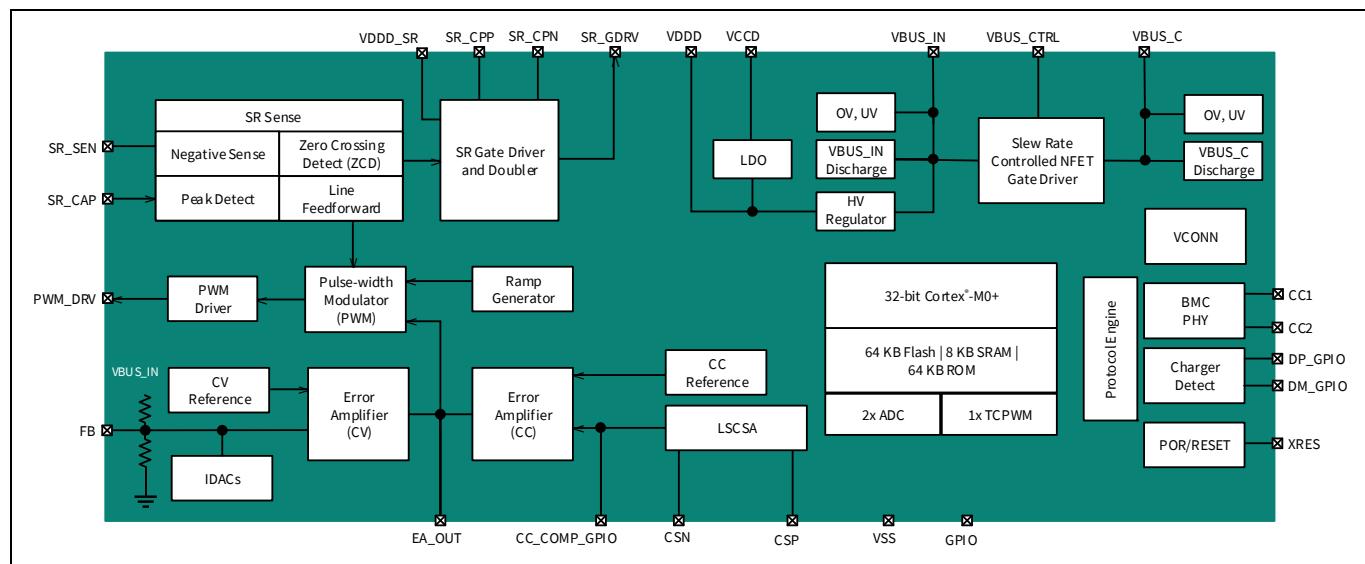

## 機能ブロック図

### 機能ブロック図

目次

## 目次

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 概要説明.....                                                   | 1         |

| アプリケーション .....                                              | 1         |

| 特長 .....                                                    | 1         |

| 機能ブロック図.....                                                | 2         |

| 目次 .....                                                    | 3         |

| <b>1 アプリケーション概要 .....</b>                                   | <b>4</b>  |

| 1.1 二次側フライバック制御付き USB PD アダプタ .....                         | 4         |

| <b>2 ピン配置 .....</b>                                         | <b>5</b>  |

| 2.1 ピン機能 .....                                              | 5         |

| 2.2 ピン説明 .....                                              | 6         |

| 2.2.1 SR_GDRV, SR_VSS, SR_SEN, SR_CPP, SR_CPN, SR_CAP ..... | 6         |

| 2.2.2 FB, EA_OUT, CC_COMP_GPIOx .....                       | 6         |

| 2.2.3 PWM_DRV .....                                         | 7         |

| 2.2.4 VBUS_IN, VDDD, VCCD .....                             | 7         |

| 2.2.5 VBUS_C, VBUS_CTRL .....                               | 7         |

| 2.2.6 CSP, CSN .....                                        | 7         |

| 2.2.7 CC1, CC2 .....                                        | 7         |

| 2.2.8 DP_GPIOx, DM_GPIOx .....                              | 7         |

| 2.2.9 GPIOx, XRES .....                                     | 7         |

| <b>3 機能説明 .....</b>                                         | <b>8</b>  |

| 3.1 システム起動 .....                                            | 8         |

| 3.2 動作モード - SR .....                                        | 8         |

| 3.3 動作モード - PWM および ZVS.....                                | 12        |

| 3.4 故障保護 .....                                              | 15        |

| 3.4.1 VBUSのOVP, UVP, OCP, SCP .....                         | 15        |

| 3.4.2 過熱保護 .....                                            | 15        |

| 3.4.3 ESD, CCのOVP, DP/DMのOVP .....                          | 15        |

| 3.5 電力モード .....                                             | 15        |

| 3.6 MCU サブシステム .....                                        | 15        |

| <b>4 電気的仕様 .....</b>                                        | <b>16</b> |

| 4.1 絶対最大定格 .....                                            | 16        |

| 4.2 デバイスレベルの仕様 .....                                        | 16        |

| 4.3 機能ブロック仕様 .....                                          | 18        |

| <b>5 注文情報 .....</b>                                         | <b>24</b> |

| 5.1 注文コードの定義 .....                                          | 24        |

| <b>6 パッケージ .....</b>                                        | <b>25</b> |

| <b>7 略語 .....</b>                                           | <b>27</b> |

| <b>8 本書の表記法 .....</b>                                       | <b>29</b> |

| 8.1 測定単位 .....                                              | 29        |

| 改訂履歴.....                                                   | 30        |

| 免責事項.....                                                   | 31        |

アプリケーション概要

## 1 アプリケーション概要

### 1.1 二次側フライバック制御付き USB PD アダプタ

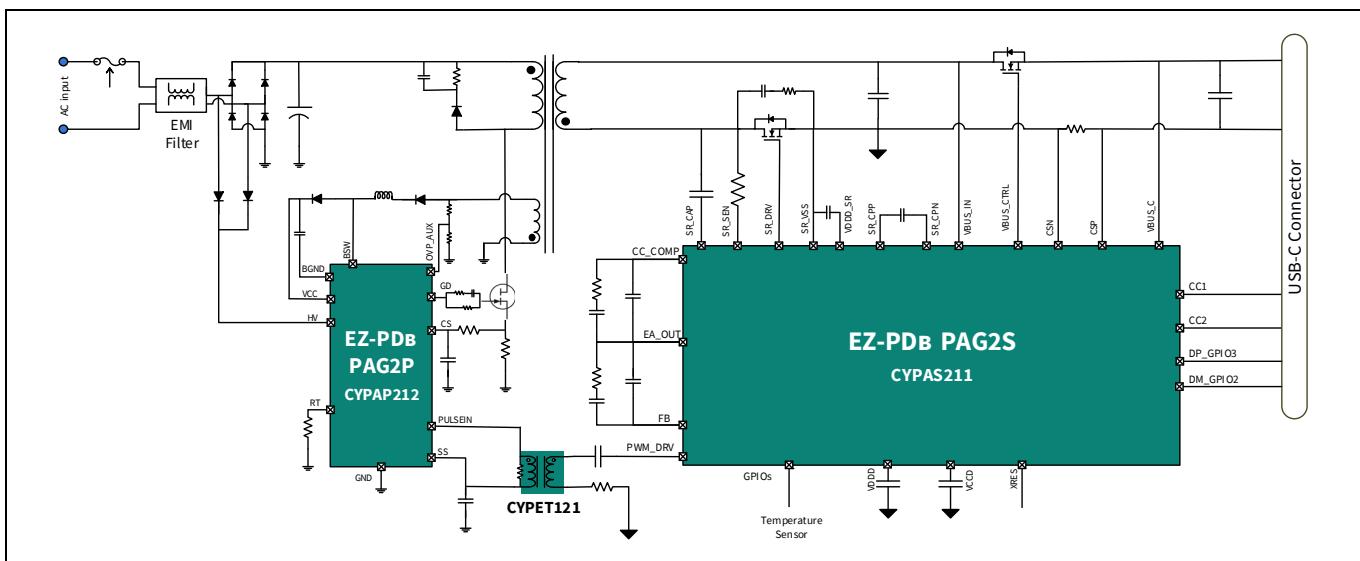

Figure 1 に、二次側制御の同期フライバックシステムを実装した電源アダプタのアプリケーション図を示します。このシステムでは、EZ-PD™ PAG2S-QZ は電圧制御モードでの一次側 MOSFET のパルス幅を変調します。PAG2S-QZ は、内部誤差アンプ (EA) とプログラマブルランプジェネレータを使用して PWM のパルス幅を決定します。PWM 信号は、パルスエッジトランジスタを介して二次側から一次側に送信されます。このトポロジでは、PAG2S-QZ は二次側 PWM 制御、充電プロトコル制御、および故障保護という 3 つの主要な機能を備えています。以下の例では、EZ-PD™ PAG2P は一次側コントローラー、PAG2S-QZ は二次側コントローラーとして使用されます。

Figure 1 二次側フライバック制御付き USB PD アダプタ

ピン配置

## 2 ピン配置

### 2.1 ピン機能

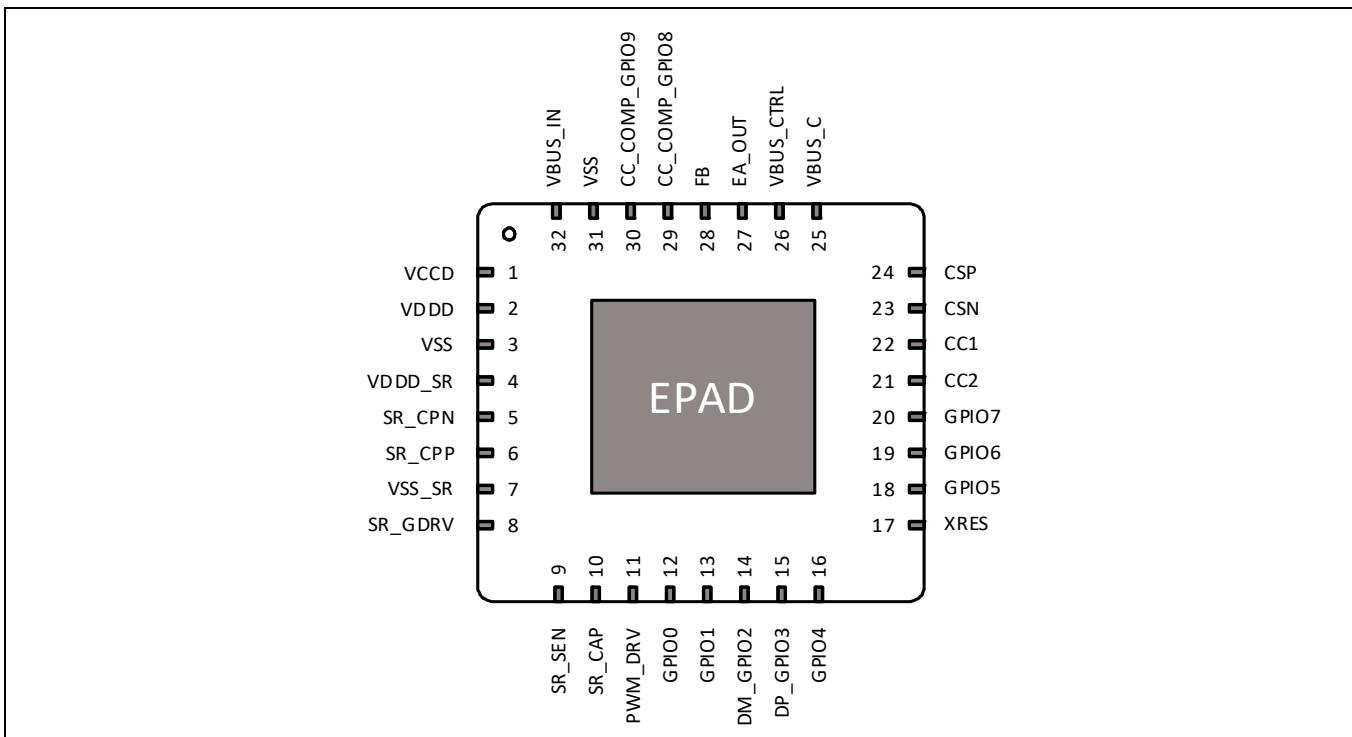

**Table 1 32 ピン QFN のピン説明**

| ピン番号 | ピン名           | ピン説明                                       |

|------|---------------|--------------------------------------------|

| 1    | VCCD          | 1.8V のコア電源電圧 LDO 出力                        |

| 2    | VDDD          | 3.0V ~ 5.5V の内部 LDO 出力                     |

| 3    | VSS           | グランド                                       |

| 4    | VDDD_SR       | 同期整流器ドライバー用 $V_{DDD}$ 電源                   |

| 5    | SR_CPN        | 同期整流用ダブラコンデンサの負端子                          |

| 6    | SR_CPP        | 同期整流用ダ布拉コンデンサの正端子                          |

| 7    | VSS_SR        | 同期整流器ドライバー用グランド                            |

| 8    | SR_GDRV       | 同期整流器の NFET ゲートドライバー                       |

| 9    | SR_SEN        | 同期整流器の NFET ドレイン端子センシング                    |

| 10   | SR_CAP        | 共振周波数が 4MHz を超えた場合の同期整流器の NFET ドレイン端子センシング |

| 11   | PWM_DRV       | パルスエッジトランスマスドライバー                          |

| 12   | GPIO0         | GPIO                                       |

| 13   | GPIO1         |                                            |

| 14   | DM_GPIO2      | USB D-/GPIO/SWD_DAT                        |

| 15   | DP_GPIO3      | USB D+/GPIO/SWD_DAT                        |

| 16   | GPIO4         | 未接続                                        |

| 17   | XRES          | 外部リセット入力                                   |

| 18   | GPIO5         | GPIO                                       |

| 19   | GPIO6         | GPIO/TCPWM                                 |

| 20   | GPIO7         | GPIO                                       |

| 21   | CC2           | パワー デリバリー通信チャネル 2                          |

| 22   | CC1           | パワー デリバリー通信チャネル 1                          |

| 23   | CSN           | ローサイド電流検出アンプの負入力                           |

| 24   | CSP           | ローサイド電流検出アンプの正入力                           |

| 25   | VBUS_C        | USB Type-C VBUS モニター入力                     |

| 26   | VBUS_CTRL     | ロードスイッチ NFET ゲート制御                         |

| 27   | EA_OUT        | EA の出力                                     |

| 28   | FB            | EA のフィードバック                                |

| 29   | CC_COMP_GPIO8 | 定電流モードでの補正コンデンサ /GPIO/TCPWM 用のピン           |

| 30   | CC_COMP_GPIO9 |                                            |

| 31   | VSS           | グランド                                       |

| 32   | VBUS_IN       | レギュレータ用の 3.3V ~ 30V 電源入力                   |

## ピン配置

Figure 2 32 ピン QFN のピン配置

## 2.2 ピン説明

### 2.2.1 SR\_GDRV, SR\_VSS, SR\_SEN, SR\_CPP, SR\_CPN, SR\_CAP

EZ-PD™ PAG2S-QZ は、同期整流器の NFET の両端の電圧を検出し、最適な効率のためにゲートドライバーを適切に制御します。標準 NFET と論理レベル NFET の両方をサポートします。このデバイスは、QR/CrCM、バレスイッチング、不連続導通モード (DCM)、および連続導通モード (CCM) での同期整流に対応します。SR センス ブロックは、ネガティブ センス検出とゼロクロッシング検出 (ZCD) をサポートします。SR\_DRAIN ピンの共振周波数が 4MHz より大きいソリューションの場合、10pF コンデンサを介して SR\_DRAIN ピンを SR\_CAP に接続することにより、SR\_CAP ピンを介してピーク周波数を検出します。共振周波数が 4MHz 未満の場合、SR\_CAP ピンは開放のままにする必要があります。

ゲートドライバー (SR\_GDRV) は内部  $V_{DDD}$  で動作するか、または  $V_{DDD}$  の 2 倍の電圧に駆動して、外部 NFET の  $R_{DS(ON)}$  抵抗を低下させることができます。 $V_{DDD}$  の倍増を実現するために、SR\_CPP ピンと SR\_CPN ピンに接続されたダブルコンデンサを備えた内部ダブル回路を使用します。SR FET のソース端子は、SR\_VSS ピンに接続する必要があります。外部 NFET のドレインノードの電圧は、抵抗分圧器を使用して SR\_SEN を介して検出されます。

### 2.2.2 FB, EA\_OUT, CC\_COMP\_GPIOx

PAG2S-QZ は、定電圧動作モードと定電流動作モードの両方で二次側出力の検出とレギュレーションを行う 2 個の誤差アンプ ブロックを内蔵しています。誤差アンプの出力は内部アナログ PWM ブロックに供給されます。誤差アンプの負入力はフィードバック (FB) ピンであり、正入力は内部電圧リファレンスです。FB ピンの電圧は、所望の VBUS 出力を達成するように内部電流ソース / シンク IDAC を使用して変更できます。アプリケーション図 (Figure 1) に示すように、FB ピンと EA\_OUT ピンの間に外部補正ネットワークが必要です。定電流動作モードでは、機能ブロック図に示すように、内部ローサイド電流検出アンプ (LSCSA) の出力が独立した誤差アンプに供給されます。Figure 1 に示すように、定電流モードにおけるレギュレーションには、CC\_COMP\_GPIOx と EA\_OUT の間に外部補正ネットワークが必要です。

ピン配置

### 2.2.3 PWM\_DRV

PAG2S-QZ は、電圧制御モードで一次側 FET のパルス幅を変調するアナログ PWM ジェネレータをサポートします。ジェネレータはプログラム可能なランプを生成し、それを誤差アンプの出力と比較して PWM パルス幅を決定します。ランプの生成は、内部コンデンサへの電流供給によって行われます。供給電流は、特定の固定電流とフィードフォワード電流のプログラム可能な組み合わせです。PWM 信号は、パルスエッジトランジスタを介して二次側から一次側に送信されます。

### 2.2.4 VBUS\_IN, VDDD, VCCD

PAG2S-QZ は、VBUS\_IN レールから電力供給される高電圧レギュレータを内蔵しています。その出力は VDDD レールに電力を供給します。レギュレータの入力範囲は 3.3V ~ 30V です。レギュレータは、PAG2S-QZ への電流供給を目的とし、外部負荷や IC を駆動するためのものではありません。また PAG2S-QZ は、負の電圧遷移中に VBUS レースの放電に使用する VBUS\_IN レール用に設定可能な内部放電パスを備えています。放電抵抗の強度はファームウェアで設定できます。

安定化された電源  $V_{DDD}$  は、いくつかのアナログブロックに直接電力供給するか、またはコアロジックの大部分に電力を供給する 1.8V  $V_{CCD}$  にさらに降圧されます。VDDD ピンと VCCD ピンは、レギュレータの安定性を目的として外付けコンデンサに接続するために引き出されるもので、電源として使用されるものではありません。

### 2.2.5 VBUS\_C, VBUS\_CTRL

VBUS\_C は、Type-C コネクタの電圧を監視するために使用されます。VBUS\_C レールには、負の電圧遷移中に VBUS\_C レールを放電するための設定可能な内部放電パスがあります。放電抵抗の強度はファームウェアで設定できます。VBUS\_IN と VBUS\_C の間にロードスイッチが設置されています。PAG2S-QZ は、ロードスイッチを制御するための NFET ゲートドライバーを搭載します。VBUS\_CTRL はゲートドライバーの出力です。急激な突入電流を回避するためのオプションの低速ターンオン機能があります。

### 2.2.6 CSP, CSN

PAG2S-QZ は、負荷電流を監視する LSCSA を内蔵しています。CSP は LSCSA の正入力ピンであり、CSN は負入力です。LSCSA の Rsense の推奨値は  $5m\Omega$  です。

### 2.2.7 CC1, CC2

CC1 と CC2 は、USB PD プロトコルの通信チャネルです。PAG2S-QZ は USB PD トランシーバを内蔵しています。このトランシーバは、USB PD 規格に従って、コンフィギュレーションチャネル (CC) を介してバイフェーズマークコード (BMC) でエンコードされたデータを通信するトランスマッタ (TX) とレシーバ (RX) で構成されます。すべての通信は半二重です。物理層は、チャネル上の通信エラーを最小限に抑えるために衝突回避を実装しています。このブロックには、USB PD 仕様で要求されるすべての終端抵抗 ( $R_p$ ) とそれらのスイッチが含まれています。

アクティブケーブルアプリケーションに対応するために、PAG2S-QZ は、CC ラインに電力供給する VCONN FET も内蔵しています。CC1 ピンと CC2 ピンの両方に  $390pF$  の外付けコンデンサが必要です。

### 2.2.8 DP\_GPIOx, DM\_GPIOx

DP ラインと DM ラインは、標準の USB D+ と D- ラインです。PAG2S-QZ は、BC 1.2, Quick Charge, Apple Charging, Samsung AFC などのレガシー充電プロトコルに対応する充電検出ブロックを内蔵しています。このブロックには、これらの充電プロトコルに必要なすべての終端が内蔵されており、外部コンポーネントは必要ありません。システムでレガシー充電が必要ない場合は、DP ラインと DM ラインは標準 GPIO として利用できます。充電検出ブロックは、DP ラインと DM ライン上のインピーダンス検出もサポートします。

### 2.2.9 GPIOx, XRES

PAG2S-QZ には複数の GPIO があり、そのうちのいくつかは GPIO 専用であり、残りは他の機能と多重化されています。GPIO は、複数の駆動モードと設定可能な閾値オプションに対応します。電源投入とリセットの間、入力に過電流を与えると、過剰なターンオン電流を発生させないように、GPIO はトライステートにされます。

XRES ピンは内部でプルアップされており、リセットを開始するには外部でプルダウンする必要があります。

機能説明

### 3 機能説明

#### 3.1 システム起動

電源投入時、一次側スタートアップコントローラーはソフトスタートメカニズムを使用して一次スイッチの制御を開始します。また、二次側出力コンデンサの充電に十分な電流と、EZ-PD™ PAG2S-QZ に必要な起動電流を供給します。二次側出力電圧は PAG2S-QZ の入力電源となります。VBUS\_IN 電圧が 3.3V を超えると、PAG2S-QZ フームウェアは起動し、一次側スイッチを制御します。PAG2S-QZ のファームウェア起動時間は数ミリ秒程度です。

起動が完了すると、ファームウェアは 5V の二次側出力を得るために誤差アンプを設定し、それに応じて PAG2S-QZ は PWM パルスを生成します。パルスは PWM\_DRV 上に生成され、パルストラnsを介して一次側スタートアップコントローラーに送信されます。一次側スタートアップコントローラーは、PWM パルスを受信すると、これらに内部発振器を同期させ、起動モードから二次側制御モードに切り替えます。二次側制御モードでは、一次側スイッチは PAG2S-QZ によって生成された PWM パルスで直接制御されます。

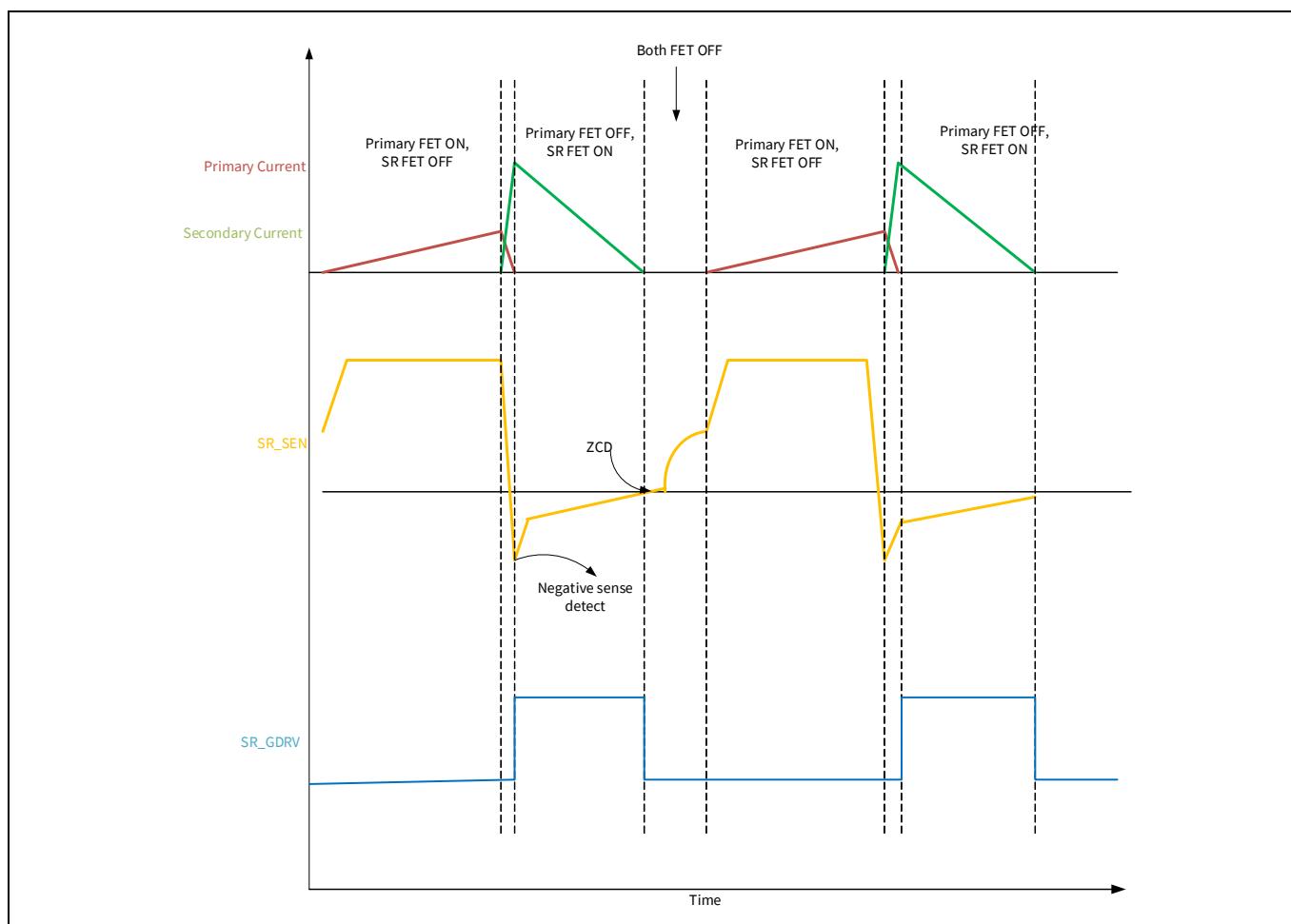

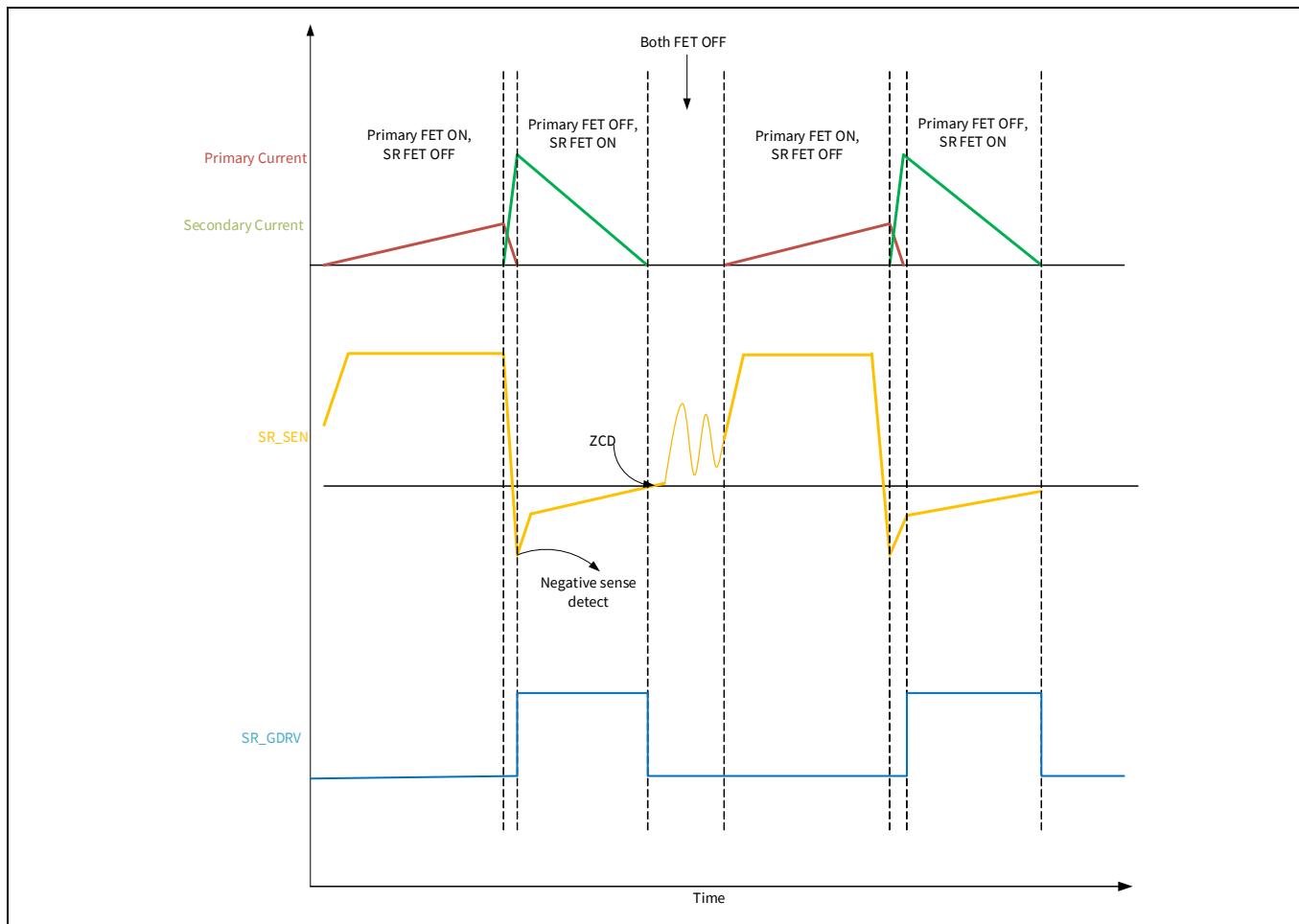

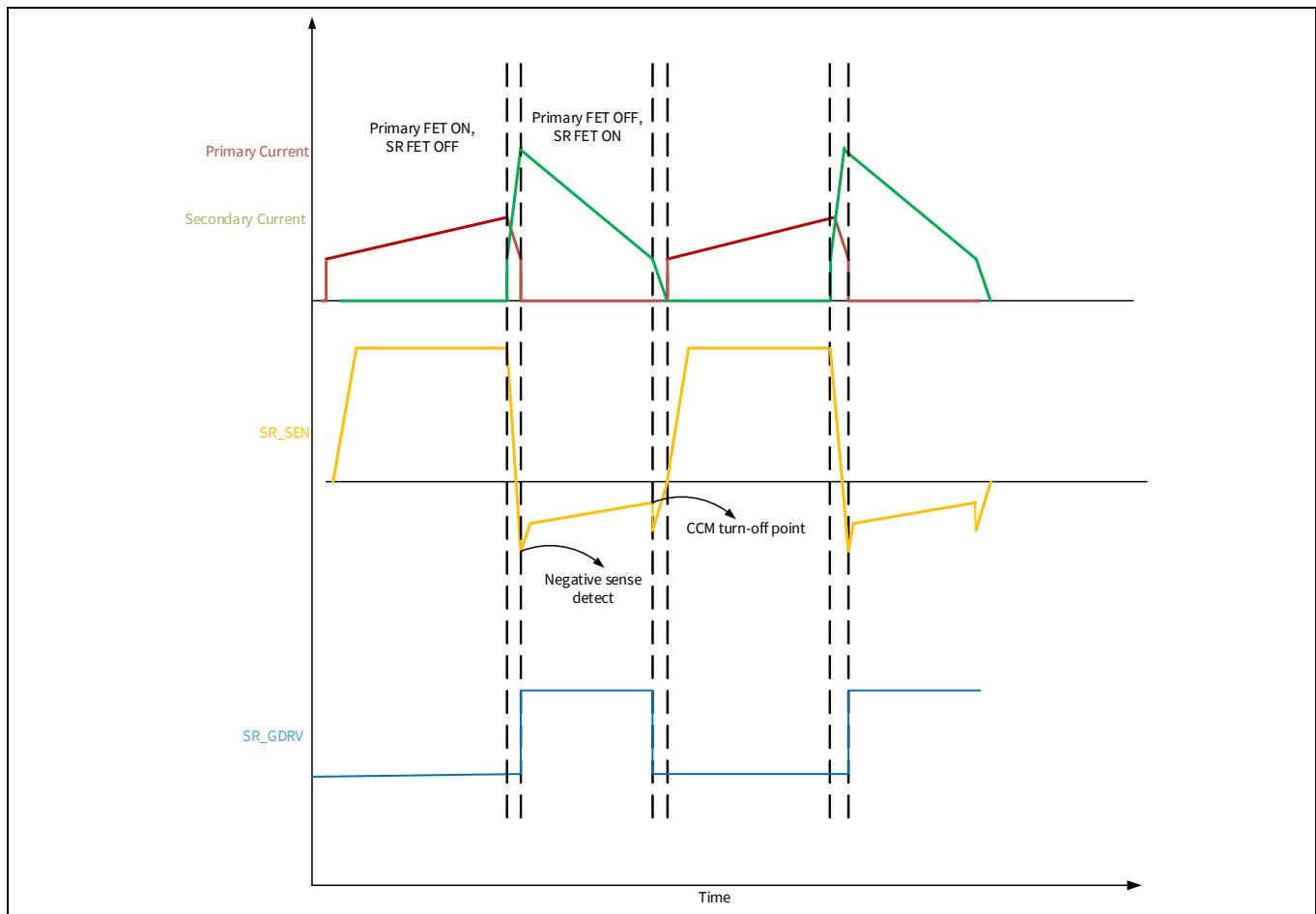

#### 3.2 動作モード - SR

PAG2S-QZ は、DCM と CCM の両方のモードで同期整流(SR)をサポートします。SR センスブロックは、ネガティブセンス検出とゼロクロッシング検出(ZCD)をサポートします。Figure 3 ~ Figure 5 に、QR/CrCM, バレースイッチング、および CCM のモードでの SR\_GDRV 機能を示します。SR コントローラーのターンオン伝播遅延は 40ns (Typ)、ターンオフ伝播遅延は 25ns (Typ) です。

Figure 3 QR/CrCM モードでの SR\_SEN および SR\_GDRV

## 機能説明

Figure 4 DCM/ バレー スイッチング モードでの SR\_SEN および SR\_GDRV

## 機能説明

Figure 5 CCM モードでの SR\_SEN および SR\_GDRV

## 機能説明

外部 NFET のドレイン ノードの電圧は、外部抵抗に接続された SR\_SEN で検出します。外部抵抗は、SR\_SEN ピンの電圧を 34V 未満に制限するために必要です。SR\_SEN ピンの外部抵抗は、電源トランスの巻数比に依存します。[Table 2](#) に、さまざまな巻数比に応じた外部抵抗を示します。

**Table 2** 巻数比と SR\_SEN の外部抵抗

| 一次側対二次側の巻数比 | Rext ( $\Omega$ ) |

|-------------|-------------------|

| 3:1         | 20k               |

| 4:1         | 20k               |

| 5:1         | 20k               |

| 6:1         | 12k               |

| 7:1         | 12k               |

| 8:1         | 12k               |

| 9:1         | 12k               |

| 10:1        | 12k               |

| 11:1        | 12k               |

| 12:1        | 12k               |

| 13:1        | 12k               |

| 14:1        | 12k               |

| 15:1        | 12k               |

機能説明

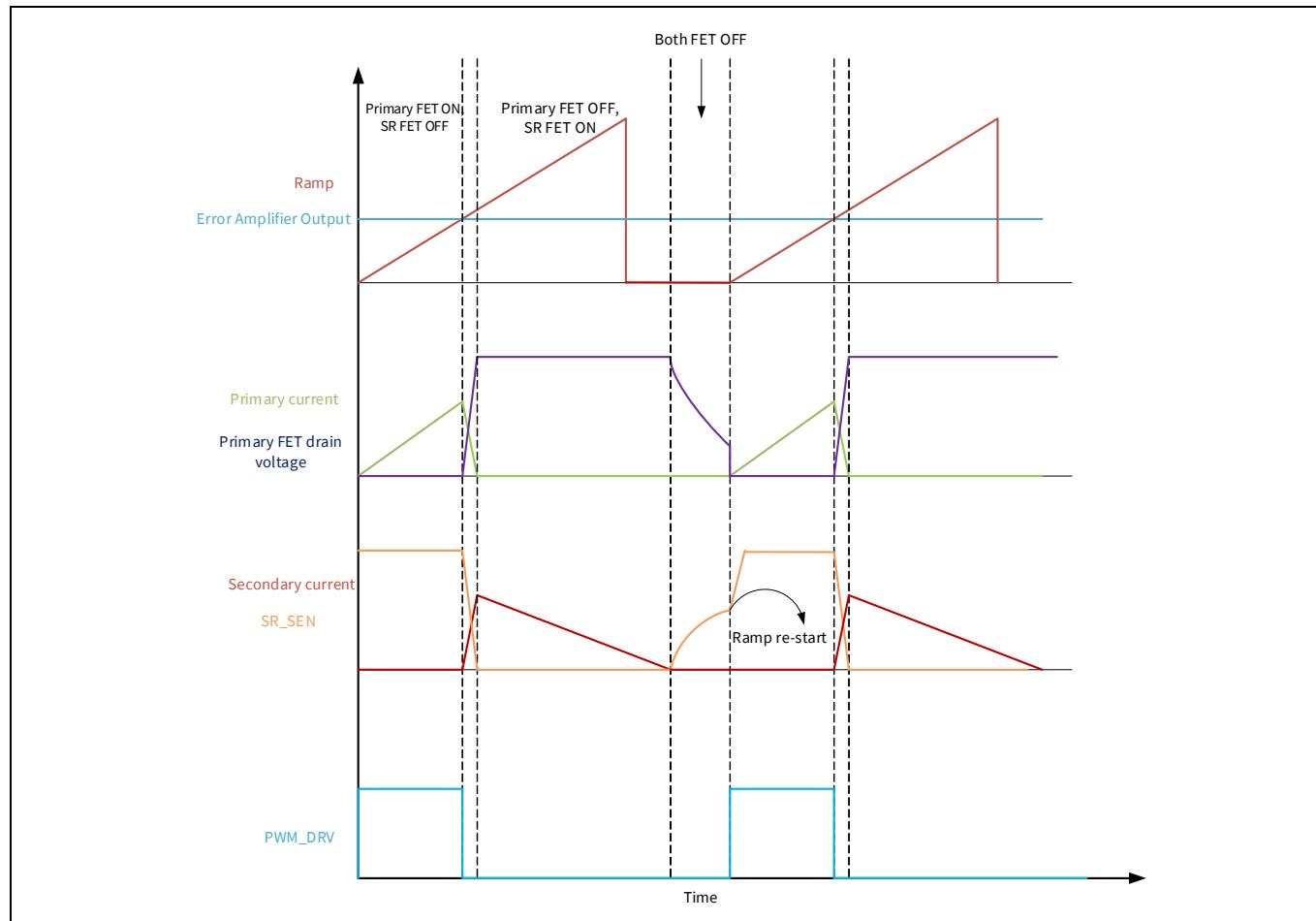

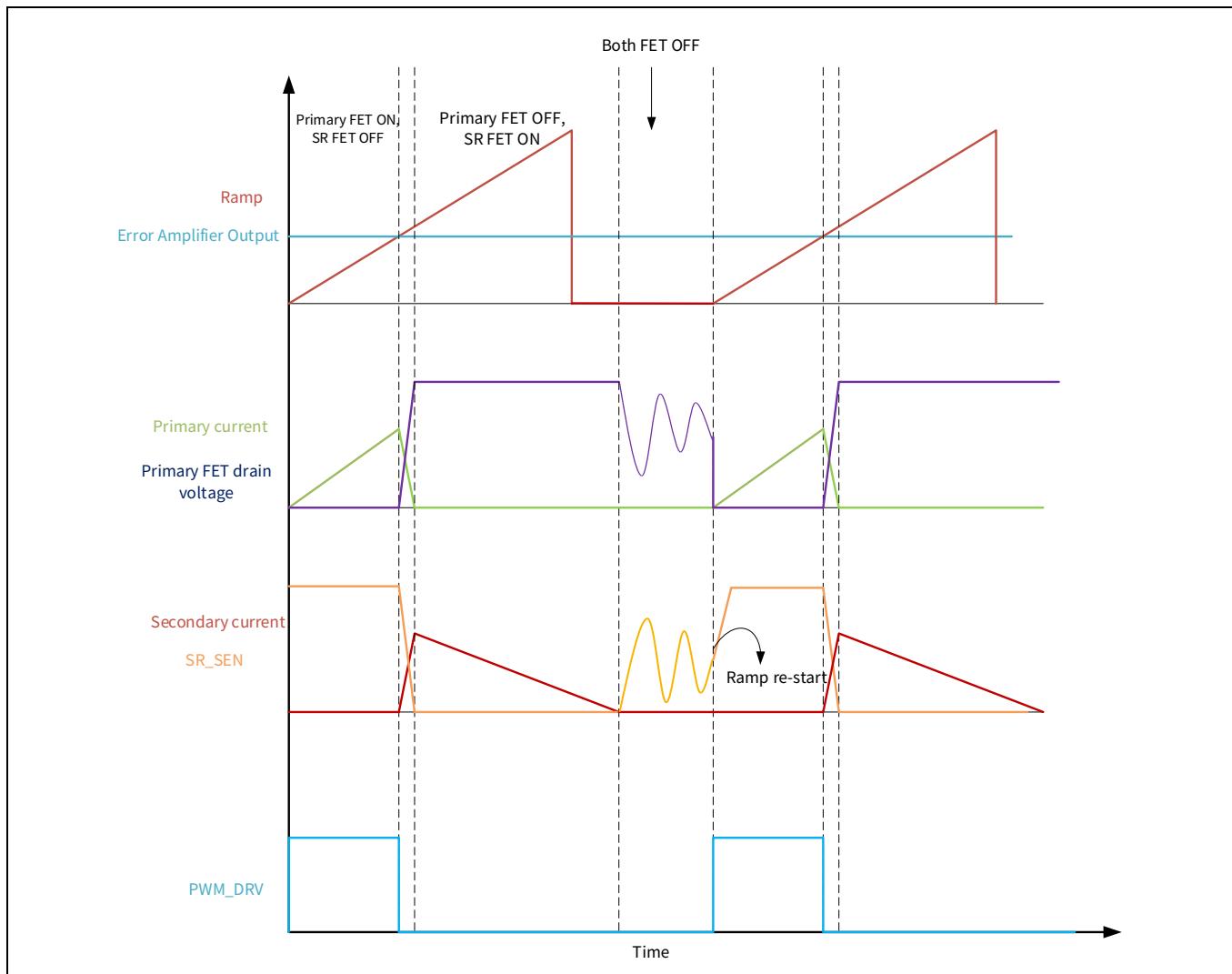

### 3.3 動作モード - PWM および ZVS

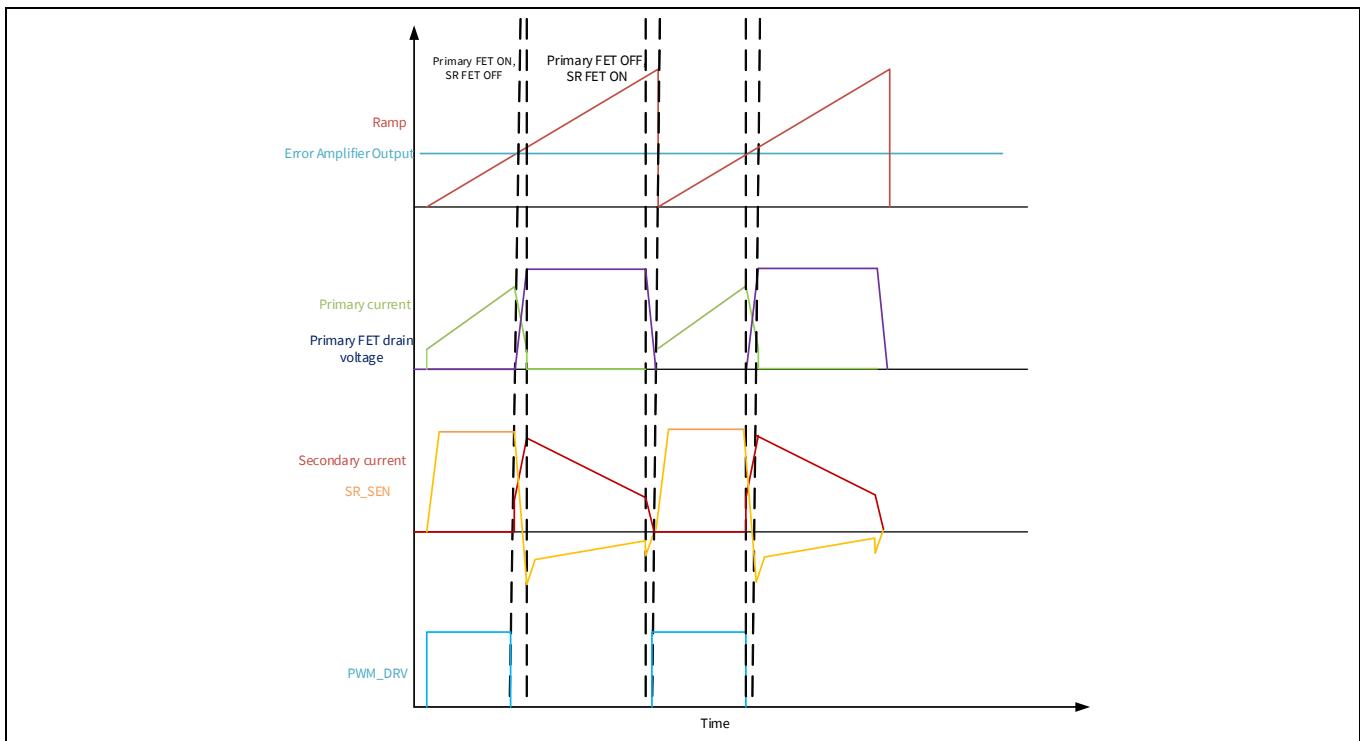

PAG2S-QZ は、QR / CrCM, バレー スイッチング , DCM, CCM, 軽負荷動作用のバーストモードの複数の動作モードをサポートします。ファームウェアでは、最小 / 最大パルス幅, 最小 / 最大期間, パルススキップまたはバーストレベルを設定できます。Figure 6 ~ Figure 8 に、QR/CrCM, バレー スイッチング, および CCM のモードでの PWM\_DRV 機能を示します。

Figure 6 QR/CrCM モードでの PWM\_DRV

## 機能説明

Figure 7 DCM/バレー スイッチング モードでの PWM\_DRV

## 機能説明

**Figure 8** CCM モードでの PWM\_DRV

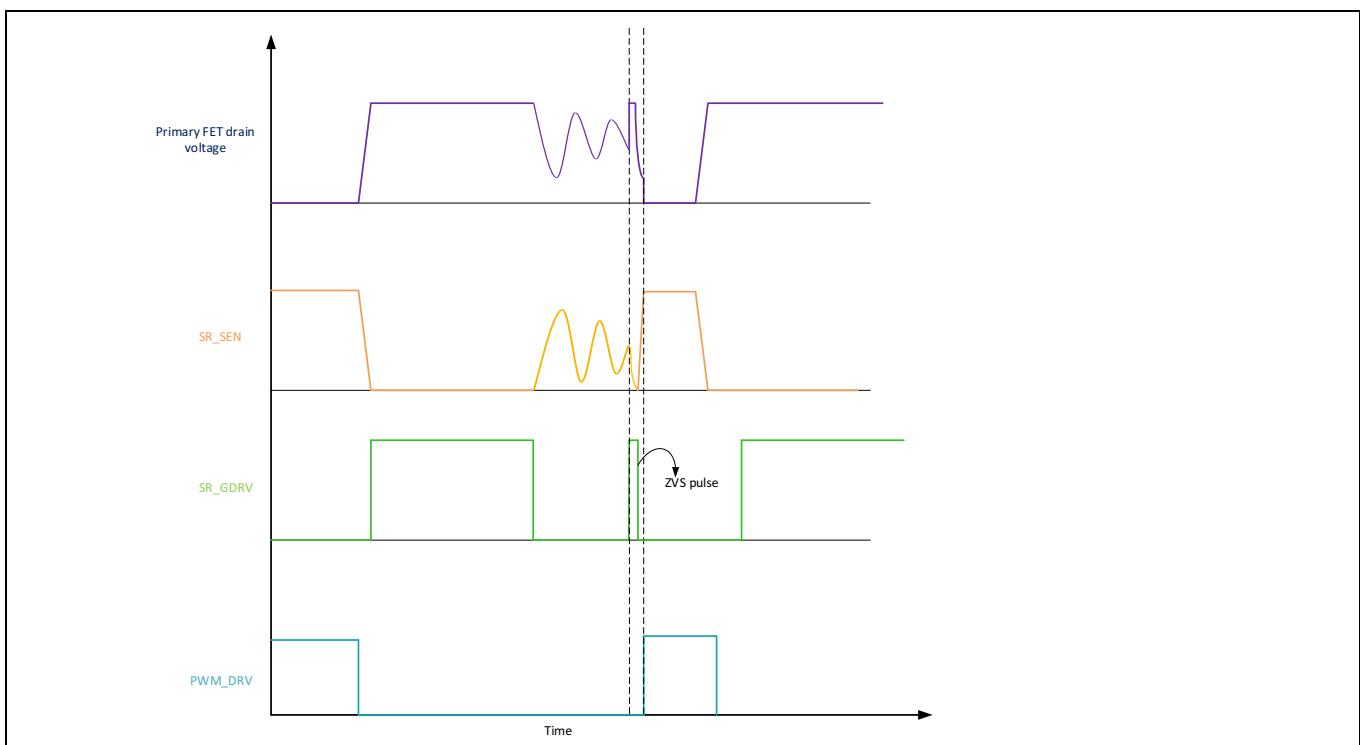

PAG2S-QZ はゼロ電圧スイッチングもサポートします。Figure 9 に示すように、PWM\_DRV の駆動前に短期間 SR\_GDRV をオンにします。目的は、一次側ドレイン電圧を低く引き下げて、ゼロ電圧スイッチングを保証することです。ZVS パルス幅はファームウェアで設定できるため、設計ごとの最適化が可能です。

**Figure 9** DCM モードでの ZVS

## 機能説明

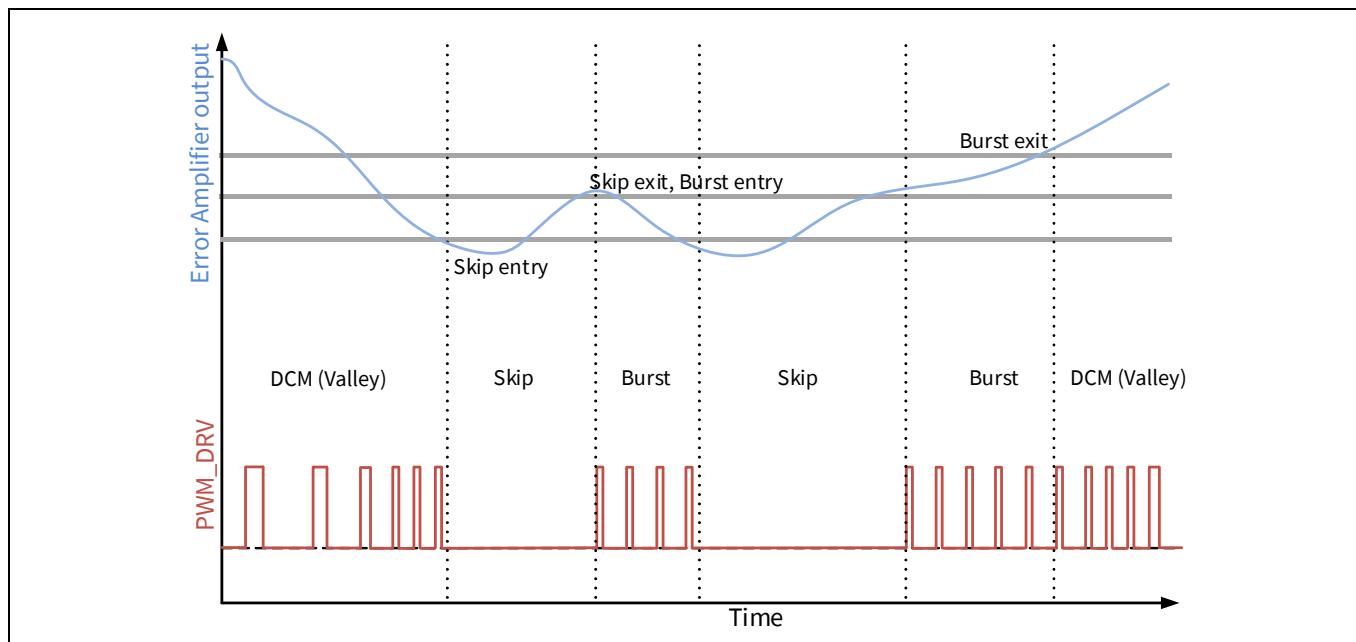

アナログ PWM のスマートアルゴリズムにより、出力電力要件に基づいてモード間の自動的な遷移が可能になります。高負荷の場合は CrCM で動作し、中負荷の場合は DCM に遷移し、低負荷 / 超低負荷の場合はスキップモードまたはバーストモードに切り替わります (Figure 10 を参照してください)。

Figure 10 誤差アンプ出力と動作モードの関係

## 3.4 故障保護

### 3.4.1 VBUS の OVP, UVP, OCP, SCP

VBUIS の低電圧および過電圧の故障は、内部 VBUS\_IN / VBUS\_C 抵抗分圧器を使用して監視されます。VBUIS の過電流および短絡の故障は、内部電流検出アンプ (CSA) を使用して監視されます。故障の閾値と応答メカニズムはファームウェアで設定可能です。

### 3.4.2 過熱保護

過熱の監視は、外部サーミスタと内部 ADC を使用して行われます。サーミスタは任意の GPIO に接続できます。PAG2S-QZ は、汎用のアナログ - デジタル変換に使用される 8 ビット SAR ADC を搭載しています。故障の閾値と応答メカニズムはファームウェアで設定可能です。

### 3.4.3 ESD, CC の OVP, DP/DM の OVP

PAG2S-QZ は、すべてのピンに ESD 保護を実装しています。また、高電圧 VBUS\_C レールとの不慮の短絡故障から CC ピンを保護でき、DP/DM ピン上の過電圧も防止します。

## 3.5 電力モード

PAG2S-QZ は、アクティブ、スリープ、ディープスリープの電力モードに対応します。これらのモード間の遷移は、動作条件に応じてアプリケーションファームウェアによって処理されます。

## 3.6 MCU サブシステム

PAG2S-QZ は 64KB フラッシュ、8KB SRAM、および 64KB ROM を備えた 32 ビット Cortex® M0+ を搭載します。また、1 個の TCPWM と 2 個の ADC も搭載しています。

電気的仕様

## 4 電気的仕様

### 4.1 絶対最大定格

Table 3 絶対最大定格

| パラメーター                    | 説明                    | Min  | Typ | Max                    | 単位 |

|---------------------------|-----------------------|------|-----|------------------------|----|

| V <sub>BUS_IN_MAX</sub>   | 最大入力電源電圧              | -0.3 | -   | 34                     | V  |

| V <sub>DDD_MAX</sub>      | V <sub>DDD</sub> 電源電圧 |      |     | 6                      |    |

| V <sub>SR_DRAIN_MAX</sub> | SR_SEN ピンの電圧          | -    |     | 34                     |    |

| V <sub>CC_PIN_ABS</sub>   | CC1 ピンと CC2 ピンの電圧     |      |     | V <sub>DDD</sub> + 0.5 |    |

| V <sub>GPIO_ABS</sub>     | GPIO 電圧               | -0.5 |     | 25                     | mA |

| I <sub>GPIO_ABS</sub>     | GPIO ごとの電流            | -    |     | 100                    |    |

| I <sub>LU</sub>           | ラッチアップ時のピン電流          | -100 |     | 2000                   | V  |

| ESD_HBM                   | 静電気放電(人体モデル)          | -    |     | 500                    |    |

| ESD_CDM                   | デバイス帯電モデル ESD         |      |     |                        |    |

### 4.2 デバイス レベルの仕様

Table 4 デバイス レベルの仕様

| パラメーター                | 説明                                           | Min         | Typ | Max  | 単位 | 詳細 / 条件               |

|-----------------------|----------------------------------------------|-------------|-----|------|----|-----------------------|

| <b>メモリ サイズ</b>        |                                              |             |     |      |    |                       |

| FLASH_SIZE            | フラッシュ メモリ サイズ                                | -           | 64  | -    | KB | SONOS フラッシュ サイズ(バイト)  |

| SRAM_SIZE             | SRAM メモリ サイズ                                 |             | 8   |      |    | SRAM サイズ(バイト)         |

| SROM_SIZE             | SROM メモリ サイズ                                 |             | 64  |      |    |                       |

| <b>シリコンチップの電源</b>     |                                              |             |     |      |    |                       |

| V <sub>DDD_REG</sub>  | VBUS = 5.5V ~ 30V の場合の V <sub>DDD</sub> 出力   | 4.6         | 5   | 5.4  | V  | X5R セラミックまたはこれより良質のもの |

| V <sub>DDD_MIN</sub>  | VBUS = 3.15V ~ 5.5V の場合の V <sub>DDD</sub> 出力 | VBUS - 0.33 | -   | -    |    |                       |

| V <sub>BUS_IN</sub>   | 電源入力電圧                                       | 3.15        |     | 30.0 |    |                       |

| V <sub>CCD</sub>      | コア ロジック用の出力電圧                                | -           | 1.8 | -    |    |                       |

| V <sub>DDWRITE</sub>  | フラッシュ書き込み動作用の電源電圧                            | 3           | -   | 5.5  |    |                       |

| C <sub>EFC</sub>      | V <sub>CCD</sub> の外部レギュレータ電圧バイパス             | 80          | 100 | 120  | nF |                       |

| C <sub>EXC</sub>      | V <sub>DDD</sub> 用の電源コンデンサ                   | 4           | 4.7 | -    | μF | X5R セラミックまたはこれより良質のもの |

| C <sub>EXV</sub>      | V <sub>BUS_IN</sub> 用の電源デカップリング コンデンサ        | -           | 1   |      |    |                       |

| C <sub>EXCPP</sub>    | SR_CPP ピンと SR_CPN ピン間のコンデンサ                  | 0.1         | -   |      |    |                       |

| I <sub>GPIO_ABS</sub> | GPIO ごとの電流                                   | -           |     | 25   | mA | 絶対最大値                 |

電気的仕様

Table 4 デバイス レベルの仕様 (continued)

| パラメーター            | 説明                                                 | Min | Typ  | Max           | 単位            | 詳細 / 条件                                                                                                                                           |

|-------------------|----------------------------------------------------|-----|------|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| $T_{SLEEP}$       | スリープ モードからの復帰時間                                    | -   | 0    | $\mu\text{s}$ | -             | $V_{BUS\_IN} = 11\text{V}$ 、<br>$T_A = 25^\circ\text{C}$ 、<br>CC1/CC2 が Tx または Rx、<br>CPU が 24MHz、<br>SR/PWM が 100kHz、<br>EA/ADC/CSA/UVOV ブロックがオン |

| $T_{DEEPSLEEP}$   | ディープスリープ モードからの復帰時間                                |     | 35   |               |               |                                                                                                                                                   |

| $I_{DD\_A}$       | $V_{BUS\_IN}$ からのアクティブ電流 (Type-C 接続)               |     | 25.0 |               |               |                                                                                                                                                   |

| $I_{DD\_A1}$      | PWM モード時の $V_{BUS\_IN}$ からの電流 (Type-C 接続)          | -   | 13.0 | mA            | -             | $V_{BUS\_IN} = 28\text{V}$ 、<br>$T_A = 25^\circ\text{C}$ 、<br>クロックが 24MHz、<br>SR/PWM が 100kHz、<br>SR コンデンサ = 3nF、<br>CC のトグルなし                    |

| $I_{DD\_A3}$      | 低電力 PWM モード時の $V_{BUS\_IN}$ からの電流 (Type-C 接続)      |     | 4    |               |               | $V_{BUS\_IN} = 28\text{V}$ 、<br>$T_A = 25^\circ\text{C}$ 、<br>クロックが 3MHz、<br>PWM モード、<br>CC のトグルなし                                                |

| $I_{DD\_DS1\_UA}$ | PWM モード時の $V_{BUS\_IN}$ からのディープスリープ電流 (Type-C 未接続) |     | 350  |               | $\mu\text{A}$ | $V_{BUS\_IN} = 5\text{V}$ 、<br>$T_A = 25^\circ\text{C}$ 、<br>Type-C 未接続、<br>PWM モード、ダウンストリーム ポート (DFP) モード                                        |

| $L_{SEC}$         | 二次側インダクタ                                           | 3   | -    | -             | $\mu\text{H}$ | 二次側インダクタ                                                                                                                                          |

電気的仕様

### 4.3 機能ブロック仕様

Table 5 機能ブロック仕様

| パラメーター         | 説明                                                                                            | Min  | Typ | Max | 単位  | 詳細 / 条件                            |

|----------------|-----------------------------------------------------------------------------------------------|------|-----|-----|-----|------------------------------------|

| <b>同期整流器</b>   |                                                                                               |      |     |     |     |                                    |

| VCPP1          | $V_{BUS} = 3.3V \sim 5.5V$ の場合の電圧ダブラの出力電圧                                                     | 5    | -   | -   | V   |                                    |

| VCPP2          | $V_{BUS} = 5.5V \sim 30V$ の場合の電圧ダ布拉の出力電圧                                                      | 9    | -   | 11  |     |                                    |

| TR_SR          | 同期整流器ゲート ドライバー出力の立ち上り時間 ( $1V$ から $V_{OH} - 1V$ まで)。<br>$C_L = 3nF$ (ダブラ バイパス モードの場合とそうでない場合) | -    | -   | 60  | ns  |                                    |

| TF_SR1         | 同期整流器ゲート ドライバー出力の立ち下り時間 ( $V_{OH} - 1V$ から $1V$ まで)。<br>$C_L = 3nF$ (ダブラ モードの場合)              | -    | 25  | 50  |     |                                    |

| TF_SR2         | 同期整流器ゲート ドライバー出力の立ち下り時間 ( $V_{OH} - 1V$ から $1V$ まで)。<br>$C_L = 3nF$ (ダブラ バイパス モードの場合)         | -    | 15  | 30  |     |                                    |

| VTRIP_NSN_100  | 二次側スイッチをオンにするためのネガティブセンストリップ電圧                                                                | 50   | 100 | 150 | mV  | -                                  |

| VTRIP_ZCD      | 二次側スイッチをオフにするためのネガティブセンストリップ電圧                                                                | -8   | -5  | -3  |     |                                    |

| VTRIP_ZCDF     | 高速 ZCD を介して二次側スイッチをオフにするためのトリップ電圧                                                             | 0    | 7   | 10  |     |                                    |

| TD_ON          | SR_DRAIN が $100mV$ のときから SR_GDRV が $1V$ に達するまでのターンオン伝播遅延                                      | -    | 40  | 80  | ns  |                                    |

| IO_SRC_SNK     | 出力ピーク電流 (ソースとシンク)                                                                             | -    | 1   | -   | A   |                                    |

| TR_SR1         | 同期整流器ゲート ドライバー出力の立ち上り時間 ( $1V$ から $V_{OH} - 1V$ まで)。<br>$C_L = 3nF$ (ダブラ モードの場合)              | -    | -   | 75  | ns  |                                    |

| TR_SR2         | 同期整流器ゲート ドライバー出力の立ち上り時間 ( $1V$ から $V_{OH} - 1V$ まで)。<br>$C_L = 3nF$ (ダ布拉 バイパス モードの場合)         | -    | -   | 30  |     |                                    |

| <b>PWM</b>     |                                                                                               |      |     |     |     |                                    |

| FSW            | スイッチング周波数                                                                                     | 20   | -   | 300 | kHz | -                                  |

| PWM_ON         | 制御可能な最小オン時間                                                                                   | 100  | -   | -   | ns  |                                    |

| $V_{OL\_PTDR}$ | パルスエッジトランスドライバーの出力 LOW 電圧<br>( $I_{Sink} = 8mA$ )                                             | -    | -   | 0.5 | V   | $V_{DDD} = 3V$ 、<br>$I_{OL} = 8mA$ |

| <b>GPIO</b>    |                                                                                               |      |     |     |     |                                    |

| I_LU           | ラッチアップ電流制限                                                                                    | -100 | -   | 100 | mA  |                                    |

| RPU            | プルアップ抵抗値                                                                                      | 3.5  | 5.6 | 8.5 | kΩ  | -                                  |

| RPD            | プルダウン抵抗値                                                                                      |      |     |     |     |                                    |

電気的仕様

Table 5 機能ブロック仕様 (continued)

| パラメーター                 | 説明                                                                         | Min                       | Typ | Max                       | 単位                       | 詳細 / 条件                                       |  |  |

|------------------------|----------------------------------------------------------------------------|---------------------------|-----|---------------------------|--------------------------|-----------------------------------------------|--|--|

| I <sub>IL</sub>        | 入力リーク電流<br>( 絶対値 )                                                         | -                         | -   | 2                         | nA                       | +25°C T <sub>A</sub> 、<br>3V V <sub>DDD</sub> |  |  |

| C <sub>PIN_A</sub>     | ピン最大負荷容量                                                                   |                           |     | 22                        | pF                       | DP ピンと DM<br>ピンの静電容量                          |  |  |

| C <sub>PIN</sub>       |                                                                            |                           |     | 3                         |                          | すべての V <sub>DDD</sub> 、<br>その他すべての<br>GPIO    |  |  |

| V <sub>OH</sub>        | 出力 HIGH 電圧                                                                 | V <sub>DDD</sub> -<br>0.6 | V   | -                         | -                        | I <sub>oh</sub> = -4mA                        |  |  |

| V <sub>OL</sub>        | 出力 LOW 電圧                                                                  | -                         |     | 0.6                       |                          | I <sub>ol</sub> = 10mA                        |  |  |

| V <sub>IH_CMOS</sub>   | 入力電圧 HIGH 閾値                                                               | 0.7 ×<br>V <sub>DDD</sub> |     | -                         |                          |                                               |  |  |

| V <sub>IL_CMOS</sub>   | 入力電圧 LOW 閾値                                                                | -                         |     | 0.3 ×<br>V <sub>DDD</sub> |                          |                                               |  |  |

| V <sub>IH_TTL</sub>    | LVTTL 入力                                                                   | 2                         |     | -                         |                          |                                               |  |  |

| V <sub>IL_TTL</sub>    | LVTTL 入力                                                                   | -                         |     | 0.8                       |                          |                                               |  |  |

| V <sub>HYSTTTL</sub>   | 入力ヒステリシス LVTTL                                                             | 80                        |     | -                         |                          |                                               |  |  |

| V <sub>HYSMOS</sub>    | 入力ヒステリシス CMOS                                                              | 0.1 ×<br>V <sub>DDD</sub> |     | -                         |                          |                                               |  |  |

| IDIODE                 | 保護ダイオードを通って V <sub>DDD</sub> /V <sub>SS</sub> に流れ<br>る電流                   | -                         |     | 100.0                     | μA                       |                                               |  |  |

| T <sub>RISEF</sub>     | 高速ストロング モードでの立ち上り時間                                                        | 1                         | ns  | 15                        | C <sub>LOAD</sub> = 25pF |                                               |  |  |

| T <sub>FALLF</sub>     | 高速ストロング モードでの立ち下り時間                                                        |                           |     | 15.0                      |                          |                                               |  |  |

| T <sub>RISES</sub>     | 低速ストロング モードでの立ち上り時間                                                        |                           |     | 70                        |                          | -                                             |  |  |

| T <sub>FALLS</sub>     | 低速ストロング モードでの立ち下り時間                                                        | 10                        | MHz | -                         | -                        |                                               |  |  |

| F <sub>GPIO_OUT1</sub> | GPIO F <sub>OUT</sub> ;<br>2.85V ≤ V <sub>DDD</sub> ≤ 5.5V。<br>高速ストロング モード |                           |     | 28                        |                          |                                               |  |  |

| F <sub>GPIO_OUT2</sub> | GPIO F <sub>OUT</sub> ;<br>2.85V ≤ V <sub>DDD</sub> ≤ 5.5V。<br>低速ストロング モード |                           |     | 6                         |                          |                                               |  |  |

| F <sub>GPIO_IN</sub>   | GPIO 入力動作周波数 ;<br>2.85V ≤ V <sub>DDD</sub> ≤ 5.5V。                         |                           |     | 28                        |                          |                                               |  |  |

#### フラッシュマクロ

|             |                                   |     |   |      |                                       |                                        |

|-------------|-----------------------------------|-----|---|------|---------------------------------------|----------------------------------------|

| FLASH_ERASE | 行消去時間                             | -   | - | 15.5 | ms                                    | -                                      |

| FLASH_WRITE | 行( ブロック )書き込み時間<br>( 消去 + プログラム ) |     |   | 20   |                                       |                                        |

| FLASH_DR    | フラッシュデータ保持期間                      | 15  | - | 年    | 25 °C～55 °C、<br>すべての V <sub>DDD</sub> | -                                      |

| FLASH_ENPB  | フラッシュ書き換え可能回数                     |     |   | -    |                                       |                                        |

| FLASH_ENPB1 | フラッシュ書き換え可能回数                     | 1 万 | - | 回    | 25 °C～85 °C、<br>すべての V <sub>DDD</sub> | 25 °C～125 °C、<br>すべての V <sub>DDD</sub> |

|             |                                   |     |   |      |                                       |                                        |

電気的仕様

Table 5 機能ブロック仕様 (continued)

| パラメーター                      | 説明                                                           | Min           | Typ | Max | 単位   | 詳細 / 条件                                                                   |

|-----------------------------|--------------------------------------------------------------|---------------|-----|-----|------|---------------------------------------------------------------------------|

| FLASH_ROW_PGM               | 消去後の行プログラム時間                                                 | -             | -   | 7   | ms   | -                                                                         |

| T_BULKERASE                 | バルク消去時間 (32KB)                                               | -             | -   | 35  | -    | -                                                                         |

| T_DEVPROG                   | 総デバイスプログラム時間                                                 | -             | -   | 7.5 | 秒    | -                                                                         |

| F <sub>RET1</sub>           | フラッシュデータ保持期間、<br>$T_A \leq 55^{\circ}\text{C}$ 、10万回のP/Eサイクル | 15            | -   | -   | -    | -                                                                         |

| F <sub>RET2</sub>           | フラッシュデータ保持期間、<br>$T_A \leq 85^{\circ}\text{C}$ 、1万回のP/Eサイクル  | 10            | -   | -   | 年    | -                                                                         |

| F <sub>RET3</sub>           | フラッシュデータ保持期間、<br>$T_A \leq 105^{\circ}\text{C}$ 、1万回のP/Eサイクル | 3             | -   | -   | -    | -                                                                         |

| <b>SWD</b>                  |                                                              |               |     |     |      |                                                                           |

| F_SWDCLK1                   | すべての $V_{DDD}$                                               | -             | -   | 14  | MHz  | -                                                                         |

| T_SWDI_SETUP                | T = 1/f SWDCLK                                               | 0.25 × T      | -   | -   | ns   | -<br>25°C $T_A$ 、<br>すべての $V_{DDD}$ 、<br>48MHz ≥ F <sub>IMO</sub> ≥ 24MHz |

| T_SWDI_HOLD                 |                                                              |               |     | -   |      |                                                                           |

| T_SWDO_VALID                |                                                              | -<br>0.50 × T | -   | -   |      |                                                                           |

| T_SWDO_HOLD                 |                                                              |               |     | 1   |      |                                                                           |

| <b>ILO / IMO / POR</b>      |                                                              |               |     |     |      |                                                                           |

| F <sub>IMO</sub>            | IMO 周波数                                                      | 24            | 36  | 48  | MHz  | -                                                                         |

| IMO_STL                     | トリムレジスタ変更時の IMO 整定時間                                         | -             | -   | 200 | ns   | 25°C $T_A$ 、<br>すべての $V_{DDD}$ 、<br>48MHz ≥ F <sub>IMO</sub> ≥ 24MHz      |

| F <sub>CPU</sub>            | CPU 入力周波数                                                    | -             | -   | 48  | MHz  |                                                                           |

| F <sub>ILO</sub>            | ILO 周波数                                                      | 15            | 40  | 80  | kHz  |                                                                           |

| SR_POWER_UP                 | 電源投入時の電源供給スルーレート                                             | -             | -   | 67  | V/ms |                                                                           |

| F <sub>IMOTOL</sub>         | 24MHz と 48MHz での周波数変動<br>(トリム済み)                             | -2            | -   | 2   | %    |                                                                           |

| T <sub>STARTIMO</sub>       | IMO 起動時間                                                     | -             | -   | 7   | μs   |                                                                           |

| T <sub>STARTILO1</sub>      | ILO 起動時間                                                     | -             | -   | 2   | ms   |                                                                           |

| EXTCLKFREQ                  | 外部クロック入力周波数                                                  | -             | -   | 16  | MHz  |                                                                           |

| EXTCLKDUTY                  | デューティ比。 $V_{DD}/2$ で測定                                       | 45            | -   | 55  | %    |                                                                           |

| TCLKSWITCH                  | システムクロックソースの切り替え時間                                           | 3             | -   | 4   | 周期   |                                                                           |

| V <sub>RSEIPOR</sub>        | パワーオンリセット(POR)立ち上りトライップ電圧                                    | 0.72          | -   | 1.5 | -    | V                                                                         |

| V <sub>FALLIPOR</sub>       | POR 立ち下りトライップ電圧                                              | 0.62          | -   | 1.4 | -    |                                                                           |

| V <sub>DDDD_BOD</sub>       | アクティブ / スリープモードでの電圧低下                                        | 2.34          | -   | 3   | -    |                                                                           |

| V <sub>CCD_BOD</sub>        |                                                              | 1.64          | -   | 2   | -    |                                                                           |

| V <sub>CCD_BOD_DP_SLP</sub> | 検出(BOD)トライップ電圧                                               | 1.1           | -   | 2   | -    |                                                                           |

電気的仕様

Table 5 機能ブロック仕様 (continued)

| パラメーター               | 説明                             | Min   | Typ | Max  | 単位                                     | 詳細 / 条件                                  |

|----------------------|--------------------------------|-------|-----|------|----------------------------------------|------------------------------------------|

| <b>タイマー</b>          |                                |       |     |      |                                        |                                          |

| SYS_TIM_RES          | システム タイマー分解能                   | -     | 16  | -    | ビット                                    | -                                        |

| WDT_RES              | ウォッチドッグ タイマー分解能                | -     | 16  | -    | ビット                                    | -                                        |

| <b>TCPWM</b>         |                                |       |     |      |                                        |                                          |

| TCPWM_FREQ           | 動作周波数                          | -     | Fc  | MHz  | Fc max = CLK_SYS                       | オーバーフロー、アンダーフローおよび CC(カウンター = 比較値)出力の最小幅 |

| T_PWMEXT             | 出力トリガー パルス幅                    | 2/Fc  |     |      |                                        |                                          |

| T_CRES               | カウンターの分解能                      | 1/Fc  |     |      |                                        | 逐次カウント同士間の最小時間                           |

| PWM_RES              | PWM 分解能                        | -     |     |      |                                        | PWM 出力の最小パルス幅                            |

| <b>PD トランシーバ</b>     |                                |       |     |      |                                        |                                          |

| vSwing               | トランスマッタ出力 HIGH 電圧              | 1.05  | -   | V    | 1.2<br>0.075<br>75<br>96<br>194<br>356 | -                                        |

| vSwing_low           | トランスマッタ出力 LOW 電圧               | -     |     |      |                                        |                                          |

| zDriver              | トランスマッタ出力インピーダンス               | 33    |     |      |                                        |                                          |

| Idac_std             | USB 標準アドバタイズメントのソース電流          | 64    |     |      |                                        |                                          |

| Idac_1p5a            | 5V アドバタイズメント、 1.5A でのソース電流     | 166   |     |      |                                        |                                          |

| Idac_3a              | 5V アドバタイズメント、 3A でのソース電流       | 304   |     |      |                                        |                                          |

| zOPEN                | 無効時のグランドへの CC インピーダンス          | 108   | -   | kΩ   | -                                      | -                                        |

| DFP_default_0_p2     | 標準 USB での DFP 側の CC 電圧         | 0.15  |     |      |                                        |                                          |

| DFP_1.5A_0p4         | 1.5A での DFP 側の CC 電圧           | 0.35  |     |      |                                        |                                          |

| DFP_3A_0p8           | 3A での DFP 側の CC 電圧             | 0.75  |     |      |                                        |                                          |

| DFP_3A_2p6           | 3A での DFP 側の CC 電圧             | 2     |     |      |                                        |                                          |

| Vattach_ds           | ディープスリープのアタッチ閾値                | 0.30  |     |      |                                        |                                          |

| Rattach_ds           | ディープスリープのプルアップ抵抗               | 10    |     |      |                                        |                                          |

| <b>LSCSA の DC 仕様</b> |                                |       |     |      |                                        |                                          |

| Csa_Acc1             | CSA 精度<br>5mV < Vsense < 10mV  | -0.75 | -   | 0.75 | mV                                     | -                                        |

| Csa_Acc2             | CSA 精度<br>10mV < Vsense < 15mV |       |     |      |                                        |                                          |

| Csa_Acc3             | CSA 精度<br>15mV < Vsense < 25mV |       |     |      |                                        |                                          |

| Csa_Acc4             | CSA 精度<br>Vsense = 50mV        |       |     |      |                                        |                                          |

電気的仕様

Table 5 機能ブロック仕様 (continued)

| パラメーター        | 説明                     | Min | Typ | Max | 単位  | 詳細 / 条件 |

|---------------|------------------------|-----|-----|-----|-----|---------|

| SCP_6A        | 短絡電流検出 @ 6A            | 5.4 | 6   | 6.6 | A   | -       |

| SCP_10A       | 短絡電流検出 @ 10A           | 9   | 10  | 11  |     |         |

| SCP_20A       | 短絡電流検出 @ 20A           | 18  | 20  | 22  |     |         |

| OCP threshold | 5mΩ、4A 以上での OCP トリップ閾値 | 117 | 130 | 143 |     |         |

| Av            | 対応公称ゲイン値 : 40、60       | 30  | -   | 60  | V/V |         |

#### LSCSA の AC 仕様

|                         |                                      |   |     |   |    |                                            |

|-------------------------|--------------------------------------|---|-----|---|----|--------------------------------------------|

| T <sub>SCP_GATE</sub>   | SCP 閾値トリップから外部 NFET パワーゲート オフまでの遅延時間 | - | 2.5 | - | μs | NFET ゲート容量 = 1nF、V <sub>BUS_IN</sub> = 28V |

| T <sub>SCP_GATE_1</sub> |                                      |   | 7.5 |   |    | NFET ゲート容量 = 3nF、V <sub>BUS_IN</sub> = 28V |

#### UVOV

|        |                     |    |   |   |   |   |

|--------|---------------------|----|---|---|---|---|

| VTHOV  | 過電圧閾値精度<br>4V ~ 30V | -3 | - | 3 | % | - |

| VTHUV1 | 低電圧閾値精度<br>3V ~ 4V  | -4 |   | 4 |   |   |

| VTHUV2 | 低電圧閾値精度<br>4V ~ 30V | -3 |   | 3 |   |   |

#### V<sub>BUS</sub> ゲートドライバーの DC 仕様

|        |                          |     |   |      |    |                                               |

|--------|--------------------------|-----|---|------|----|-----------------------------------------------|

| GD_VGS | オン時のゲート - ソース間オーバードライブ電圧 | 5   | - | 10   | V  | NFET ドライバーがオン                                 |

| GD_Rpd | 「プルダウン」有効時の抵抗            | -   |   | 2    | KΩ | 外部 NFET をオフにするために V <sub>BUS_CTRL</sub> に使用可能 |

| GD_drv | プログラム可能な標準ゲート電流          | 0.3 |   | 9.75 | μA | ゲートドライバー出力電流                                  |

#### V<sub>BUS</sub> ゲートドライバーの AC 仕様

|                  |                                                                                          |   |     |    |    |                           |

|------------------|------------------------------------------------------------------------------------------|---|-----|----|----|---------------------------|

| T <sub>ON</sub>  | V <sub>BUS_CTRL</sub> LOW から HIGH までの (1V から V <sub>BUS</sub> + 1V まで) の時間。3nF の外付けコンデンサ | 2 | 5   | 10 | ms | V <sub>BUS_IN</sub> = 5V  |

| T <sub>OFF</sub> | V <sub>BUS_CTRL</sub> HIGH から LOW までの (90% から 10% まで) の時間。3nF の外付けコンデンサ                  | - | 7.5 | -  | μs | V <sub>BUS_IN</sub> = 28V |

#### V<sub>BUS</sub> 放電

|     |                                            |      |   |      |   |          |

|-----|--------------------------------------------|------|---|------|---|----------|

| R1  | V <sub>BUS_IN</sub> 上の NMOS オン時の抵抗。DS = 1  | 1000 | - | 4000 | Ω | 0.5V で測定 |

| R2  | V <sub>BUS_IN</sub> 上の NMOS オン時の抵抗。DS = 2  | 500  |   | 2000 |   |          |

| R4  | V <sub>BUS_IN</sub> 上の NMOS オン時の抵抗。DS = 4  | 250  |   | 1000 |   |          |

| R8  | V <sub>BUS_IN</sub> 上の NMOS オン時の抵抗。DS = 8  | 125  |   | 500  |   |          |

| R16 | V <sub>BUS_IN</sub> 上の NMOS オン時の抵抗。DS = 16 | 62.5 |   | 250  |   |          |

電気的仕様

Table 5 機能ブロック仕様 (continued)

| パラメーター           | 説明                                   | Min   | Typ | Max  | 単位       | 詳細 / 条件       |

|------------------|--------------------------------------|-------|-----|------|----------|---------------|

| R32              | $V_{BUS\_IN}$ 上の NMOS オン時の抵抗。DS = 32 | 31.25 |     | 150  | -        | 0.5V で測定      |

| Vbus_stop_err or | 最終 VBUS 値の設定値からの誤差率                  | -     |     | 10   | %        | VBUS が 5V に放電 |

| R1A              | $V_{BUS\_C}$ 上の NMOS オン時の抵抗。DS = 1   | 1000  |     | 2000 |          |               |

| R127A            | $V_{BUS\_C}$ 上の NMOS オン時の抵抗。DS = 127 | 6.5   |     | 38   | $\Omega$ | 0.5V で測定      |

#### 電圧安定化の DC 仕様

|               |                        |     |         |         |         |   |

|---------------|------------------------|-----|---------|---------|---------|---|

| $V_{OUT}$     | $V_{BUS\_IN}$ 標準出力電圧範囲 | 3.3 | -       | 28      | V       |   |

| VR            | VBUS 電圧安定化精度           | -   | $\pm 3$ | $\pm 5$ | %       | - |

| $I_{KA\_OFF}$ | オフ状態のカソード電流            | -   | 2.2     | 10      | $\mu A$ |   |

#### VBUS レギュレータ仕様

|                    |                                      |      |     |     |         |   |

|--------------------|--------------------------------------|------|-----|-----|---------|---|

| VOLTAGE_DETECT     | $V_{BUS\_IN}$ 検出閾値電圧                 | 1.65 | 2.1 | 2.4 | V       |   |

| T <sub>START</sub> | 安定化電源出力の合計起動時間。<br>4.7 $\mu F$ の負荷容量 | -    | 50  | 200 | $\mu s$ | - |

#### ADC の DC 仕様

|           |               |              |   |              |     |                           |

|-----------|---------------|--------------|---|--------------|-----|---------------------------|

| 分解能       | ADC 分解能       | -            | 8 | -            | ビット | -                         |

| INL       | 積分非直線性        | -2.5         | - | 2.5          | LSB | $V_{DDD}$ から生成されたリファレンス電圧 |

| INL       | 積分非直線性        | -1.5         | - | 1.5          |     | バンドギャップから生成されたリファレンス電圧    |

| VREF_ADC1 |               | $V_{DDDmin}$ |   | $V_{DDDmax}$ |     | $V_{DDD}$ から生成されたリファレンス電圧 |

| VREF_ADC2 | ADC のリファレンス電圧 | 1.96         | 2 | 2.04         | V   | バンドギャップから生成されたリファレンス電圧    |

#### VCONN スイッチ仕様

|            |                                              |     |   |    |         |   |

|------------|----------------------------------------------|-----|---|----|---------|---|

| VCONN_OUT  | VCONN 最小出力電圧。<br>VBUS = 5V ~ 30V、負荷電流 = 20mA | 4.5 | - | -  | V       | - |

| $I_{LEAK}$ | コネクタ側のピンのリーク電流                               | -   |   | 10 | $\mu A$ |   |

#### VCONN スイッチの AC 仕様

|           |              |   |   |     |         |   |

|-----------|--------------|---|---|-----|---------|---|

| $T_{ON}$  | スイッチ ターンオン時間 | - | - | 600 | $\mu s$ | - |

| $T_{OFF}$ | スイッチ ターンオフ時間 | - |   | 10  | $\mu s$ | - |

注文情報

## 5 注文情報

**Table 6 PAG2S-QZ 注文情報**

| 製品番号               | アプリケーション           | パッケージタイプ  | Si ID | Si Rev |

|--------------------|--------------------|-----------|-------|--------|

| CYPAS211A1-32LQXQ  | ZVS 付き二次側フライバック制御の | 32 ピン QFN | 3B10  | A1     |

| CYPAS211A1-32LQXQT | USB PD アダプタ        |           |       |        |

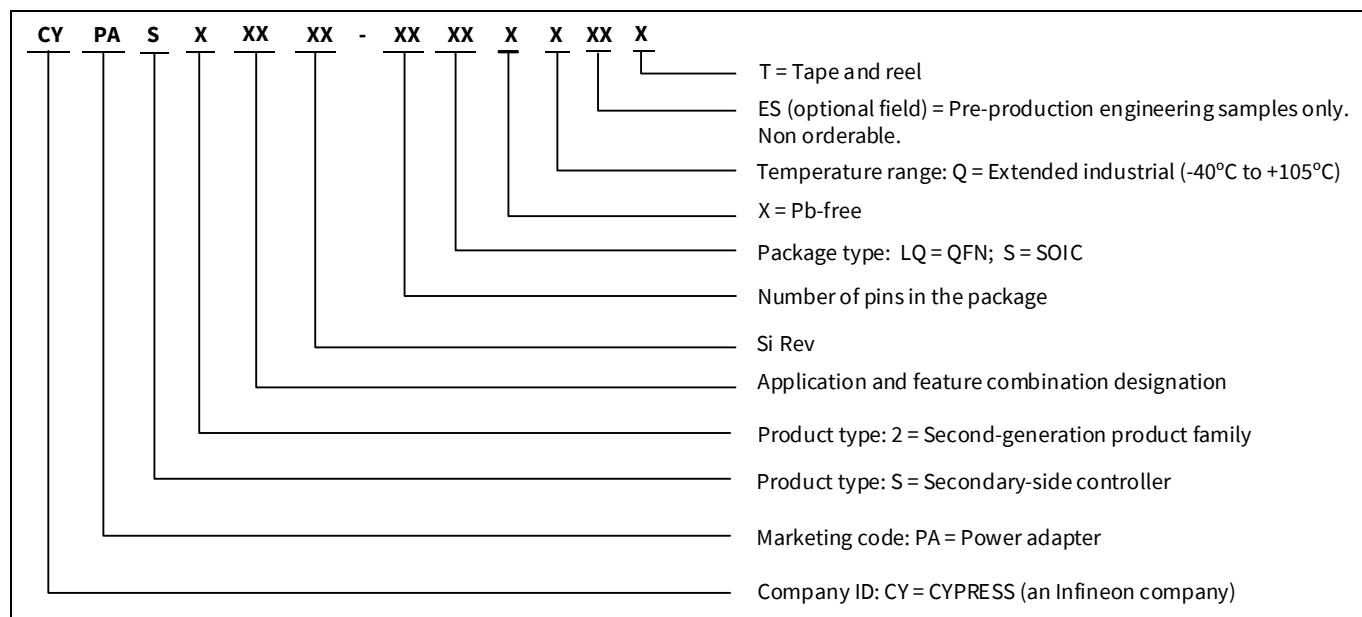

### 5.1 注文コードの定義

パッケージ

## 6 パッケージ

Table 7 パッケージの特性

| パラメーター          | 説明                               | 条件        | Min | Typ  | Max  | 単位   |

|-----------------|----------------------------------|-----------|-----|------|------|------|

| T <sub>A</sub>  | 動作周囲温度                           | 産業用拡張温度範囲 | -40 | -    | 105  | °C   |

| T <sub>J</sub>  | 動作ジャンクション温度                      |           |     |      | 150  |      |

| T <sub>JA</sub> | 32 ピン QFN のパッケージ θ <sub>JA</sub> |           |     | 23.4 |      |      |

| T <sub>JB</sub> | 32 ピン QFN のパッケージ θ <sub>JB</sub> | -         | -   | 4.85 | -    | °C/W |

| T <sub>JC</sub> | 32 ピン QFN のパッケージ θ <sub>JC</sub> |           |     |      | 27.2 |      |

Table 8 はんだリフロー ピーク温度

| パッケージ     | 最高ピーク温度 | ピーク温度の 5°C 以内での最長時間 |

|-----------|---------|---------------------|

| 32 ピン QFN | 260 °C  | 30 秒                |

Table 9 パッケージの湿度感度レベル (MSL)、IPC/JEDEC J-STD-2

| パッケージ     | MSL  |

|-----------|------|

| 32 ピン QFN | MSL3 |

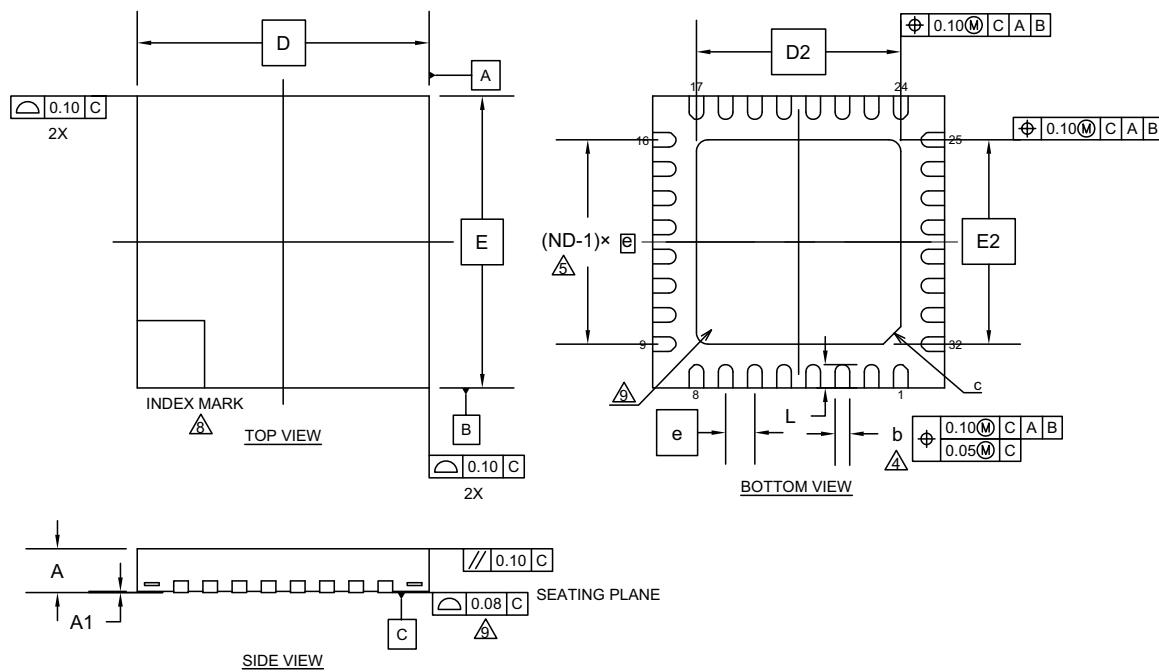

パッケージ

| SYMBOL | DIMENSIONS |      |      |

|--------|------------|------|------|

|        | MIN.       | NOM. | MAX. |

| A      | —          | —    | 0.80 |

| A1     | 0.00       | —    | 0.05 |

| D      | 5.00 BSC   |      |      |

| E      | 5.00 BSC   |      |      |

| b      | 0.18       | 0.25 | 0.30 |

| D2     | 3.50 BSC   |      |      |

| E2     | 3.50 BSC   |      |      |

| e      | 0.50 BSC   |      |      |

| c      | 0.30 REF   |      |      |

| L      | 0.35       | 0.40 | 0.45 |

NOTE

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING CONFORMS TO ASME Y14.5-1994.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL TIP. IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION "b" SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

5. AND REFER TO THE NUMBER OF TERMINALS ON D OR E SIDE.

6. MAX. PACKAGE WARPAGE IS 0.05mm.

7. MAXIMUM ALLOWABLE BURRS IS 0.076mm IN ALL DIRECTIONS.

8. PIN #1 ID ON TOP WILL BE LOCATED WITHIN INDICATED ZONE.

9. BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

10. JEDEC SPECIFICATION NO. REF : N/A

002-15160 Rev. \*\*

Figure 11 32 リード QFN ((5.0 × 5.0 × 0.8mm) WNP032 3.5 × 3.5mm E-pad (Sawn)) パッケージ外形図 (PG-VQFN-32)、002-15160

略語

## 7 略語

Table 10 本書で使用する略語

| 略語      | 説明                                                                  |

|---------|---------------------------------------------------------------------|

| ADC     | analog-to-digital converter ( アナログ - デジタル変換器 )                      |

| Arm®    | advanced RISC machine ( 高度な RISC マシン ): CPU アーキテクチャの一種              |

| BOD     | brown-out detect ( 電圧低下検出 )                                         |

| BMC     | biphase mark code ( バイフェーズ マーク コード )                                |

| CC      | constant current ( 定電流 )                                            |

| CCM     | continuous conduction mode ( 連続導通モード )                              |

| CPU     | central processing unit ( 中央演算処理装置 )                                |

| CrCM    | critical conduction mode ( 臨界導通モード )                                |

| CS      | current sense ( 電流検出 )                                              |

| CSA     | current sense amplifier ( 電流検出アンプ )                                 |

| CSN     | current sense negative ( 負の電流検出 )                                   |

| CSP     | current sense positive ( 正の電流検出 )                                   |

| DCM     | discontinuous conduction mode ( 不連続導通モード )                          |

| DFP     | downstream facing port ( ダウンストリーム ポート )                             |

| DM      | data minus ( データマイナス )                                              |

| DP      | data plus ( データプラス )                                                |

| DS      | drive strength ( 駆動強度 )                                             |

| EA      | error amplifier ( 誤差アンプ )                                           |

| EMI     | electromagnetic interference ( 電磁干渉 )                               |

| EPR     | extended power range ( 拡張電力範囲 )                                     |

| ESD     | electrostatic discharge ( 静電気放電 )                                   |

| ESD-HBM | electro static discharge human body model ( 静電気放電 ( 人体モデル ))        |

| FB      | feedback ( フィードバック )                                                |

| FS      | full-speed ( フルスピード )                                               |

| GPIO    | general-purpose input/output ( 汎用入出力 )                              |

| ILO     | internal low-speed oscillator ( 内部低速発振器 )。IMO を参照してください             |

| IMO     | internal main oscillator ( 内部主発振器 )。ILO を参照してください                   |

| I/O     | input/output ( 入出力 )。GPIO を参照してください                                 |

| LDO     | low-dropout regulator ( 低ドロップアウトレギュレータ )                            |

| LSCSA   | low-side current sense amplifier ( ローサイド電流検出アンプ )                   |

| LVTTL   | low-voltage transistor-transistor logic ( 低電圧トランジスタ - トランジスタ ロジック ) |

| NFET    | N-channel field effect transistor ( N チャネル電界効果トランジスタ )              |

| NMOS    | N-type metal-oxide-semiconductor ( n 型金属酸化膜半導体 )                    |

| OCP     | overcurrent protection ( 過電流保護 )                                    |

| OVP     | overvoltage protection ( 過電圧保護 )                                    |

| OTP     | over-temperature protection ( 過熱保護 )                                |

| PD      | power delivery ( パワー デリバリー )                                        |

略語

**Table 10** 本書で使用する略語 (continued)

| 略語     | 説明                                                             |

|--------|----------------------------------------------------------------|

| PHY    | physical layer ( 物理層 )                                         |

| POR    | power-on reset ( パワーオンリセット )                                   |

| PPS    | programmable power supply ( プログラマブル電源 )                        |

| PSM    | pulse-skipping mode ( パルススキップモード )                             |

| PWM    | pulse-width modulator ( パルス幅変調器 )                              |

| QR     | quasi-resonant ( 擬似共振 )                                        |

| RAM    | random-access memory ( ランダムアクセスメモリ )                           |

| RISC   | reduced-instruction-set computing ( 縮小命令セットコンピューティング )         |

| RMS    | root-mean-square ( 2乗平均平方根 )                                   |

| RX     | receive ( 受信 )                                                 |

| SAR    | successive approximation register ( 逐次比較レジスタ )                 |

| SCL    | I <sup>2</sup> C serial clock ( I <sup>2</sup> C シリアルクロック )    |

| SCP    | short-circuit protection ( 短絡保護 )                              |

| SDA    | I <sup>2</sup> C serial data ( I <sup>2</sup> C シリアルデータ )      |

| SPI    | Serial Peripheral Interface ( シリアルペリフェラルインターフェース ): 通信プロトコルの一種 |

| SR     | synchronous rectifier ( 同期整流器 )                                |

| SRAM   | static random access memory ( スタティックランダムアクセスメモリ )              |

| SWD    | serial wire debug ( シリアルワイヤデバッグ ): テストプロトコルの一種                 |

| SWDCLK | serial wire debug clock ( シリアルワイヤデバッグクロック )                    |

| TCPWM  | timer/counter/PWM ( タイマー / カウンター / PWM )                       |

| TX     | transmit ( 送信 )                                                |

| Type-C | 薄型 USB コネクタとリバーシブルなケーブルの新規格。最大 100W までの電力を提供することが可能            |

| USB    | universal serial bus ( ユニバーサルシリアルバス )                          |

| USB PD | USB Power Delivery ( USB パワー デリバリー )                           |

| WDT    | watchdog timer ( ウォッチドッグタイマー )                                 |

| XRES   | external reset I/O pin ( 外部リセット I/O ピン )                       |

| ZCD    | zero crossing defect ( ゼロクロッシング検出 )                            |

| ZVS    | zero voltage switching ( ゼロ電圧スイッチング )                          |

本書の表記法

## 8 本書の表記法

### 8.1 測定単位

**Table 11 測定単位**

| 記号   | 測定単位      |

|------|-----------|

| °C   | 摂氏温度      |

| Hz   | ヘルツ       |

| KB   | 1024 バイト  |

| kHz  | キロヘルツ     |

| kΩ   | キロオーム     |

| Mbps | メガビット毎秒   |

| MHz  | メガヘルツ     |

| MΩ   | メガオーム     |

| Msps | メガサンプル毎秒  |

| μA   | マイクロアンペア  |

| μF   | マイクロファラド  |

| μs   | マイクロ秒     |

| μV   | マイクロボルト   |

| μW   | マイクロワット   |

| mA   | ミリアンペア    |

| ms   | ミリ秒       |

| mV   | ミリボルト     |

| nA   | ナノアンペア    |

| ns   | ナノ秒       |

| Ω    | オーム       |

| pF   | ピコファラド    |

| ppm  | 100 万分の 1 |

| ps   | ピコ秒       |

| s    | 秒         |

| sps  | サンプル毎秒    |

| V    | ボルト       |

改訂履歴

## 改訂履歴

| 版  | 発行日        | 変更内容                                                     |

|----|------------|----------------------------------------------------------|

| ** | 2023-11-30 | これは英語版 002-37216 Rev. *B を翻訳した日本語版 002-39076 Rev. ** です。 |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2023-11-30**

**Published by**

**Infineon Technologies AG

81726 Munich, Germany**

**© 2023 Infineon Technologies AG.

All Rights Reserved.**

**Do you have a question about this

document?**

**Email:**

[erratum@infineon.com](mailto:erratum@infineon.com)

**Document reference

002-39076 Rev. \*\***

## 重要事項

本文書に記載された情報は、いかなる場合も、条件または特性の保証とみなされるものではありません（「品質の保証」）。

本文に記された一切の事例、手引き、もしくは一般的な価値、および／または本製品の用途に関する一切の情報に關し、インフィニオンテクノロジーズ（以下、「インフィニオン」）はここに、第三者の知的所有権の不侵害の保証を含むがこれに限らず、あらゆる種類の一切の保証および責任を否定いたします。

さらに、本文書に記載された一切の情報は、お客様の用途におけるお客様の製品およびインフィニオン製品の一切の使用に關し、本文書に記載された義務ならびに一切の関連する法的要件、規範、および基準をお客様が遵守することを条件としています。

本文書に含まれるデータは、技術的訓練を受けた従業員のみを対象としています。本製品の対象用途への適合性、およびこれら用途に関連して本文書に記載された製品情報の完全性についての評価は、お客様の技術部門の責任にて実施してください。

## 警告事項

技術的要件に伴い、製品には危険物質が含まれる可能性があります。当該種別の詳細については、インフィニオンの最寄りの営業所までお問い合わせください。

インフィニオンの正式代表者が署名した書面を通じ、インフィニオンによる明示の承認が存在する場合を除き、インフィニオンの製品は、当該製品の障害またはその使用に関する一切の結果が、合理的に人的傷害を招く恐れのある一切の用途に使用することはできないこと予めご了承ください。